# Silicon Carbide Technology

Philip G. Neudeck

NASA Glenn Research Center

#### 5.1 Introduction

Silicon carbide (SiC)-based semiconductor electronic devices and circuits are presently being developed for use in high-temperature, high-power, and high-radiation conditions under which conventional semiconductors cannot adequately perform. Silicon carbide's ability to function under such extreme conditions is expected to enable significant improvements to a far-ranging variety of applications and systems. These range from greatly improved high-voltage switching for energy savings in public electric power distribution and electric motor drives to more powerful microwave electronics for radar and communications to sensors and controls for cleaner-burning more fuel-efficient jet aircraft and automobile engines [1–7]. In the particular area of power devices, theoretical appraisals have indicated that SiC power MOSFET's and diode rectifiers would operate over higher voltage and temperature ranges, have superior switching characteristics, and yet have die sizes nearly 20 times smaller than correspondingly rated silicon-based devices [8]. However, these tremendous theoretical advantages have yet to be widely realized in commercially available SiC devices, primarily owing to the fact that SiC's relatively immature crystal growth and device fabrication technologies are not yet sufficiently developed to the degree required for reliable incorporation into most electronic systems.

This chapter briefly surveys the SiC semiconductor electronics technology. In particular, the differences (both good and bad) between SiC electronics technology and the well-known silicon VLSI technology are highlighted. Projected performance benefits of SiC electronics are highlighted for several large-scale applications. Key crystal growth and device-fabrication issues that presently limit the performance and capability of high-temperature and high-power SiC electronics are identified.

## 5.2 Fundamental SiC Material Properties

#### 5.2.1 SiC Crystallography: Important Polytypes and Definitions

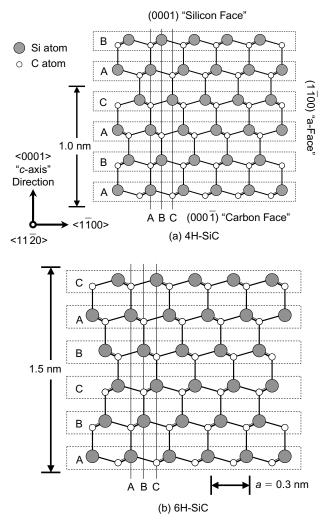

Silicon carbide occurs in many different crystal structures, called polytypes. A more comprehensive introduction to SiC crystallography and polytypism can be found in Reference 9. Despite the fact that all SiC polytypes chemically consist of 50% carbon atoms covalently bonded with 50% silicon atoms, each SiC polytype has its own distinct set of electrical semiconductor properties. While there are over 100 known polytypes of SiC, only a few are commonly grown in a reproducible form acceptable for use as an electronic semiconductor. The most common polytypes of SiC presently being developed for electronics are 3C-SiC, 4H-SiC, and 6H-SiC. The atomic crystal structure of the two most common polytypes is shown in the schematic cross section in Figure 5.1. As discussed much more thoroughly in References 9 and 10, the different polytypes of SiC are actually composed of different stacking sequences of Si-C bilayers (also called Si-C double layers), where each single Si-C bilayer is denoted by the dotted boxes in Figure 5.1. Each atom within a bilayer has three covalent chemical bonds with other atoms in the same (its own) bilayer, and only one bond to an atom in an adjacent bilayer. Figure 5.1a shows the bilayer of the stacking sequence of 4H-SiC polytype, which requires four Si-C bilayers to define the unit cell repeat distance along the c-axis stacking direction (denoted by <0.01 > Miller indices). Similarly, the 6H-SiC polytype illustrated in Figure 5.1b repeats its stacking sequence every six bilayers throughout the crystal along the stacking direction. The  $<1\overline{100}>$  direction depicted in Figure 5.1 is often referred to as one of (along with  $<11\overline{20}>$ ) the a-axis directions. SiC is a polar semiconductor across the c-axis, in that one surface normal to the c-axis is terminated with silicon atoms while the opposite normal c-axis surface is terminated with carbon atoms. As shown in Figure 5.1a, these surfaces are typically referred to as "silicon face" and "carbon face" surfaces, respectively. Atoms along the left-or right-side edge of Figure 5.1a would reside on  $(<1\overline{100}>)$  "a-face" crystal surface plane normal to the  $<1\overline{100}>$  direction. 3C-SiC, also referred to as  $\beta$ -SiC, is the only form of SiC with a cubic crystal lattice structure. The noncubic polytypes of SiC are sometimes ambiguously referred to as α-SiC. 4H-SiC and 6H-SiC are only two of the many

**FIGURE 5.1** Schematic cross-sectional depictions of (a) 4H-SiC and (b) 6H-SiC atomic crystal structure, showing important crystallographic directions and surfaces (see text).

possible SiC polytypes with hexagonal crystal structure. Similarly, 15R-SiC is the most common of the many possible SiC polytypes with a rhombohedral crystal structure.

#### **5.2.2** SiC Semiconductor Electrical Properties

Owing to the differing arrangement of Si and C atoms within the SiC crystal lattice, each SiC polytype exhibits unique fundamental electrical and optical properties. Some of the more important semiconductor electrical properties of the 3C, 4H, and 6H SiC polytypes are given in Table 5.1. Much more detailed electrical properties can be found in References 11–13 and references therein. Even within a given polytype, some important electrical properties are nonisotropic, in that they are strong functions of crystallographic direction of current flow and applied electric field (for example, electron mobility for 6H-SiC). Dopant impurities in SiC can incorporate into energetically inequivalent sites. While all dopant ionization energies associated with various dopant incorporation sites should normally be considered for utmost accuracy, Table 5.1 lists only the shallowest reported ionization energies of each impurity.

**TABLE 5.1** Comparison of Selected Important Semiconductor Electronic Properties of Major SiC Polytypes with Silicon, GaAs, and 2H-GaN at 300 K

| Property                                                                                        | Silicon   | GaAs                | 4H-SiC                                          | 6H-SiC                                         | 3C-SiC  | 2H-GaN             |

|-------------------------------------------------------------------------------------------------|-----------|---------------------|-------------------------------------------------|------------------------------------------------|---------|--------------------|

| Bandgap (eV)                                                                                    | 1.1       | 1.42                | 3.2                                             | 3.0                                            | 2.3     | 3.4                |

| Relative dielectric constant                                                                    | 11.9      | 13.1                | 9.7                                             | 9.7                                            | 9.7     | 9.5                |

| Breakdown field $N_{\rm D} = 10^{17}  {\rm cm}^{-3}  ({\rm MVcm}^{-1})$                         | 0.6       | 0.6                 | // <i>c</i> -axis: 3.0<br>⊥ <i>c</i> -axis: 2.5 | $//c$ -axis: 3.2 $\perp c$ -axis: > 1          | 1.8     | 2–3                |

| Thermal Conductivity (W/cm-K)                                                                   | 1.5       | 0.5                 | 3–5                                             | 3–5                                            | 3–5     | 1.3                |

| Intrinsic carrier concentration (cm <sup>-3</sup> )                                             | $10^{10}$ | $1.8 \times 10^{6}$ | ~10 <sup>-7</sup>                               | ~10 <sup>-5</sup>                              | ~10     | ~10 <sup>-10</sup> |

| Electron mobility at $N_D = 10^{16} \text{ cm}^{-3} \text{ (cm}^2 \text{V}^{-1} \text{s}^{-1})$ | 1200      | 6500                | // <i>c</i> -axis: 800<br>⊥ <i>c</i> -axis: 800 | // <i>c</i> -axis: 60<br>⊥ <i>c</i> -axis: 400 | 750     | 900                |

| Hole mobility at $N_A = 10^{16} \text{ cm}^{-3} (\text{cm}^2 \text{V}^{-1} \text{s}^{-1})$      | 420       | 320                 | 115                                             | 90                                             | 40      | 200                |

| Saturated electron velocity (10 <sup>7</sup> cms <sup>-1</sup> )                                | 1.0       | 1.2                 | 2                                               | 2                                              | 2.5     | 2.5                |

| Donor dopants and                                                                               | P: 45     | Si: 5.8             | N: 45                                           | N: 85                                          | N: 50   | Si: 20             |

| shallowest ionization<br>energy (meV)                                                           | As: 54    |                     | P: 80                                           | P: 80                                          |         |                    |

| Acceptor dopants and                                                                            | B: 45     | Be, Mg,             | Al: 200                                         | Al: 200                                        | Al: 270 | Mg: 140            |

| shallowest ionization<br>energy (meV)                                                           |           | C: 28               | B: 300                                          | B: 300                                         |         | Č                  |

| 2005 Commercial wafer<br>diameter (cm)                                                          | 30        | 15                  | 7.6                                             | 7.6                                            | 15      | None               |

Source: Data compiled from references [6,11,13,15,186,196-199] and references therein.

For comparison, Table 5.1 also includes comparable properties of silicon, GaAs, and GaN. Because silicon is the semiconductor employed in most commercial solid-state electronics, it is the standard against which other semiconductor materials must be evaluated. To varying degrees the major SiC polytypes exhibit advantages and disadvantages in basic material properties compared to silicon. The most beneficial inherent material superiorities of SiC over silicon listed in Table 5.1 are its exceptionally high breakdown electric field, wide bandgap energy, high thermal conductivity, and high carrier saturation velocity. The electrical device performance benefits that each of these properties enables are discussed in the next section, as are system-level benefits enabled by improved SiC devices.

## 5.3 Applications and Benefits of SiC Electronics

Two of the most beneficial advantages that SiC-based electronics offer are in the areas of high-temperature and high-power device operation. The specific SiC device physics that enables high-temperature and high-power capabilities will be examined first, followed by several examples of revolutionary system-level performance improvements these enhanced capabilities enable.

#### 5.3.1 High-Temperature Device Operation

The wide bandgap energy and low intrinsic carrier concentration of SiC allow SiC to maintain semiconductor behavior at much higher temperatures than silicon, which in turn permits SiC semiconductor device functionality at much higher temperatures than silicon [7]. As discussed in basic semiconductor electronic device physics textbooks [14,15], semiconductor electronic devices function in the temperature range where intrinsic carriers are negligible so that conductivity is controlled by intentionally introduced dopant impurities. Furthermore, the intrinsic carrier concentration  $n_i$  is a fundamental prefactor to well-known equations governing undesired junction reverse-bias leakage currents. As temperature increases, intrinsic carriers increase exponentially so that undesired leakage

currents grow unacceptably large, and eventually at still higher temperatures, the semiconductor device operation is overcome by uncontrolled conductivity as intrinsic carriers exceed intentional device dopings. Depending upon specific device design, the intrinsic carrier concentration of silicon generally confines silicon device operation to junction temperatures <300°C. SiC's much smaller intrinsic carrier concentration theoretically permits device operation at junction temperatures exceeding 800°C. 600°C SiC device operation has been experimentally demonstrated on a variety of SiC devices (Section 5.6.3).

The ability to place uncooled high-temperature semiconductor electronics directly into hot environments would enable important benefits to automotive, aerospace, and deep-well drilling industries [7,16]. In the case of automotive and aerospace engines, improved electronic telemetry and control from high-temperature engine regions are necessary to more precisely control the combustion process to improve fuel efficiency while reducing polluting emissions. High-temperature capability eliminates performance, reliability, and weight penalties associated with liquid cooling, fans, thermal shielding, and longer wire runs needed to realize similar functionality in engines using conventional silicon semiconductor electronics.

## 5.3.2 High-Power Device Operation

The high breakdown field and high thermal conductivity of SiC coupled with high operational junction temperatures theoretically permit extremely high-power densities and efficiencies to be realized in SiC devices. The high breakdown field of SiC relative to silicon enables the blocking voltage region of a power device to be roughly 10× thinner and 10× heavier doped, permitting a roughly 100-fold beneficial decrease in the blocking region resistance at the same voltage rating [8]. Significant energy losses in many silicon high-power system circuits, particularly hard-switching motor drive and power conversion circuits, arise from semiconductor switching energy loss [1,3,17]. While the physics of semiconductor device switching loss are discussed in detail elsewhere [18], switching energy loss is often a function of the turn-off time of the semiconductor switching device, generally defined as the time lapse between application of a turn-off bias and the time when the device actually cuts off most of the current flow. In general, the faster a device turns off, the smaller its energy loss in a switched power conversion circuit. For device-topology reasons discussed in References 3,8, and 19-21, SiC's high breakdown field and wide energy bandgap enable much faster power switching than is possible in comparably volt-ampere-rated silicon power-switching devices. The fact that high-voltage operation is achieved with much thinner blocking regions using SiC enables much faster switching (for comparable voltage rating) in both unipolar and bipolar power device structures. Therefore, SiC-based power converters could operate at higher switching frequencies with much greater efficiency (i.e., less switching energy loss) [1,22]. Higher switching frequency in power converters is highly desirable because it permits use of smaller capacitors, inductors, and transformers, which in turn can greatly reduce overall power converter size, weight, and cost [3,22,23].

While SiC's smaller on-resistance and faster switching helps minimize energy loss and heat generation, SiC's higher thermal conductivity enables more efficient removal of waste heat energy from the active device. Because heat energy radiation efficiency increases greatly with increasing temperature difference between the device and the cooling ambient, SiC's ability to operate at high junction temperatures permits much more efficient cooling to take place, so that heat sinks and other device-cooling hardware (i.e., fan cooling, liquid cooling, air conditioning, heat radiators, etc.) typically needed to keep high-power devices from overheating can be made much smaller or even eliminated.

While the preceding discussion focused on high-power switching for power conversion, many of the same arguments can be applied to devices used to generate and amplify RF signals used in radar and communications applications. In particular, the high breakdown voltage and high thermal conductivity coupled with high carrier saturation velocity allow SiC microwave devices to handle much higher power densities than their silicon or GaAs RF counterparts, despite SiC's disadvantage in low-field carrier mobility [5,6,24–26].

## 5.3.3 System Benefits of High-Power High-Temperature SiC Devices

Uncooled operation of high-temperature and high-power SiC electronics would enable revolutionary improvements to aerospace systems. Replacement of hydraulic controls and auxiliary power units with distributed "smart" electromechanical controls capable of harsh ambient operation will enable substantial jet-aircraft weight savings, reduced maintenance, reduced pollution, higher fuel efficiency, and increased operational reliability [7]. SiC high-power solid-state switches will also enable large efficiency gains in electric power management and control [1,4,27–31]. Performance gains from SiC electronics could enable the public power grid to provide increased consumer electricity demand without building additional generation plants, and improve power quality and operational reliability through "smart" power management. More efficient electric motor drives enabled by SiC will also benefit industrial production systems as well as transportation systems such as diesel-electric railroad locomotives, electric mass-transit systems, nuclear-powered ships, and electric automobiles and buses.

From the above discussions it should be apparent that SiC high-power and high-temperature solidstate electronics promise tremendous advantages that could significantly impact transportation systems and power usage on a global scale. By improving the way in which electricity is distributed and used, improving electric vehicles so that they become more viable replacements for internal combustion-engine vehicles, and improving the fuel efficiency and reducing pollution of the remaining fuel-burning engines and generation plants, SiC electronics promises the potential to better the daily lives of all citizens of planet Earth.

## 5.4 SiC Semiconductor Crystal Growth

As of this writing, much of the outstanding theoretical promise of SiC electronics highlighted in the previous section has largely gone unrealized. A brief historical examination quickly shows that serious shortcomings in SiC semiconductor material manufacturability and quality have greatly hindered the development of SiC semiconductor electronics. From a simple-minded point of view, SiC electronics development has very much followed the general rule of thumb that a solid-state electronic device can only be as good as the semiconductor material from which it is made.

#### 5.4.1 Historical Lack of SiC Wafers

Reproducible wafers of reasonable consistency, size, quality, and availability are a prerequisite for commercial mass production of semiconductor electronics. Many semiconductor materials can be melted and reproducibly recrystallized into large single crystals with the aid of a seed crystal, such as in the Czochralski method employed in the manufacture of almost all silicon wafers, enabling reasonably large wafers to be mass produced. However, because SiC sublimes instead of melting at reasonably attainable pressures, SiC cannot be grown by conventional melt-growth techniques. Prior to 1980, experimental SiC electronic devices were confined to small (typically ~1 cm²), irregularly shaped SiC crystal platelets grown as a byproduct of the Acheson process for manufacturing industrial abrasives (e.g., sandpaper) [32] or by the Lely process [33]. In the Lely process, SiC sublimed from polycrystalline SiC powder at temperatures near 2500°C are randomly condensed on the walls of a cavity forming small, hexagonally shaped platelets. While these small, nonreproducible crystals permitted some basic SiC electronics research, they were clearly not suitable for semiconductor mass production. As such, silicon became the dominant semiconductor fueling the solid-state technology revolution, while interest in SiC-based microelectronics was limited.

## 5.4.2 Growth of 3C-SiC on Large-Area (Silicon) Substrates

Despite the absence of SiC substrates, the potential benefits of SiC hostile-environment electronics nevertheless drove modest research efforts aimed at obtaining SiC in a manufacturable wafer form. Toward this end, the heteroepitaxial growth of single-crystal SiC layers on top of large-area silicon

substrates was first carried out in 1983 [34], and subsequently followed by a great many others over the years using a variety of growth techniques. Primarily owing to large differences in lattice constant (~20% difference between SiC and Si) and thermal expansion coefficient (~8% difference), heteroepitaxy of SiC using silicon as a substrate always results in growth of 3C-SiC with a very high density of crystallographic structural defects such as stacking faults, microtwins, and inversion domain boundaries [35]. Other largearea wafer materials besides silicon (such as sapphire, silicon-on-insulator, and TiC) have been employed as substrates for heteroepitaxial growth of SiC epilayers, but the resulting films have been of comparably poor quality with high crystallographic defect densities. The most promising 3C-SiC-on-silicon approach to date that has achieved the lowest crystallographic defect density involves the use of undulant silicon substrates [36]. However, even with this highly novel approach, dislocation densities remain very high compared to silicon and bulk hexagonal SiC wafers.

While some limited semiconductor electronic devices and circuits have been implemented in 3C-SiC grown on silicon, the performance of these electronics (as of this writing) can be summarized as severely limited by the high density of crystallographic defects to the degree that almost none of the operational benefits discussed in Section 5.3 has been viably realized. Among other problems, the crystal defects "leak" parasitic current across reverse-biased device junctions where current flow is not desired. Because excessive crystal defects lead to electrical device shortcomings, there are as yet no commercial electronics manufactured in 3C-SiC grown on large-area substrates. Thus, 3C-SiC grown on silicon presently has more potential as a mechanical material in microelectromechanical systems (MEMS) applications (Section 5.6.5) instead of being used purely as a semiconductor in traditional solid-state transistor electronics.

## 5.4.3 Growth of Hexagonal Polytype SiC Wafers

In the late 1970s, Tairov and Tzvetkov established the basic principles of a modified seeded sublimation growth process for growth of 6H-SiC [37,38]. This process, also referred to as the modified Lely process, was a breakthrough for SiC in that it offered the first possibility of reproducibly growing acceptably large single crystals of SiC that could be cut and polished into mass-produced SiC wafers. The basic growth process is based on heating polycrystalline SiC source material to ~2400°C under conditions, where it sublimes into the vapor phase and subsequently condenses onto a cooler SiC seed crystal [10,37–39]. This produces a somewhat cylindrical boule of single-crystal SiC that grows taller roughly at the rate of a few millimeters per hour. To date, the preferred orientation of the growth in the sublimation process is such that vertical growth of a taller cylindrical boule proceeds along the <0 0 0 1> crystallographic c-axis direction (i.e., vertical direction in Fig. 5.1). Circular "c-axis" wafers with surfaces that lie normal (i.e., perpendicular to within 10°) to the c-axis can be sawed from the roughly cylindrical boule. After years of further development of the sublimation growth process, Cree, Inc., became the first company [40] to sell 2.5 cm diameter semiconductor wafers of c-axis-oriented 6H-SiC in 1989. Correspondingly, the vast majority of SiC semiconductor electronics development and commercialization has taken place since 1990 using c-axis-oriented SiC wafers of the 6H and 4H-SiC polytypes. N-type, p-type, and semiinsulating SiC wafers of various sizes (presently as large as 7.6 cm in diameter) are now commercially available from a variety of vendors [10,39,41]. It is worth noting that attainable substrate conductivities for p-type SiC wafers are more than 10× smaller than for n-type substrates, which is largely due to the difference between donor and acceptor dopant ionization energies in SiC (Table 5.1). More recently, SiC wafers grown with gas sources instead of sublimation of solid sources or a combination of gas and solid sources have also been commercialized [42,43]. Growth of SiC boules and wafers oriented along other crystallographic directions, such as <1120> and <1100> "a-face" orientations, have also been investigated over the last decade [44]. While these other SiC wafer orientations offer some interesting differences in device properties compared to conventional c-axis-oriented wafers (mentioned briefly in Section 5.5.5), all commercial SiC electronic parts produced (as of this writing) are manufactured using c-axis-oriented wafers.

Wafer size, cost, and quality are all very critical to the manufacturability and process yield of mass-produced semiconductor microelectronics. Compared to commonplace silicon wafer standards, present-day 4H- and 6H-SiC wafers are smaller, more expensive, and generally of inferior quality containing far

more crystal imperfections (see Section 5.4.5 below). This disparity is not surprising considering that silicon wafers have undergone nearly five decades of commercial process refinement.

## 5.4.4 SiC Epilayers

Most SiC electronic devices are not fabricated directly in sublimation-grown wafers, but are instead fabricated in much higher quality epitaxial SiC layers that are grown on top of the initial sublimation-grown wafer. Well-grown SiC epilayers have superior electrical properties and are more controllable and reproducible than bulk sublimation-grown SiC wafer material. Therefore, the controlled growth of high-quality epilayers is highly important in the realization of useful SiC electronics.

## 5.4.4.1 SiC Epitaxial Growth Processes

An interesting variety of SiC epitaxial growth methodologies, ranging from liquid-phase epitaxy, molecular beam epitaxy, and chemical vapor deposition(CVD) have been investigated [10,45]. The CVD growth technique is generally accepted as the most promising method for attaining epilayer reproducibility, quality, and throughputs required for mass production. In the simplest terms, variations of SiC CVD are carried out by heating SiC substrates in a chamber "reactor" with flowing silicon- and carbon-containing gases that decompose and deposit Si and C onto the wafer allowing an epilayer to grow in a well-ordered single-crystal fashion under well-controlled conditions. Conventional SiC CVD epitaxial growth processes are carried out at substrate growth temperatures between 1400°C and 1600°C at pressures from 0.1 to 1 atm resulting in growth rates of the order of a few micrometers per hour [10,41,46]. Higher temperature (up to 2000°C) SiC CVD growth processes, some using halide-based growth chemistries, are also being pioneered to obtain higher SiC epilayer growth rates of the order of hundreds of micrometers per hour that appear sufficient for growth of bulk SiC boules in addition to very thick epitaxial layers needed for high-voltage devices [42,47,48].

Despite the fact that SiC growth temperatures significantly exceed epitaxial growth temperatures used for most other semiconductors, a variety of SiC CVD epitaxial growth reactor configurations have been developed and commercialized [41,46,49]. For example, some reactors employ horizontal reactant gas flow across the SiC wafer, while others rely on vertical flow of reactant gases; some reactors have wafers surrounded by heated "hot-wall" or "warm-wall" configurations, while other "cold-wall" reactors heat only a susceptor residing directly beneath the SiC wafer. Most reactors used for commercial production of SiC electronics rotate the sample to ensure high uniformity of epilayer parameters across the wafer. SiC CVD systems capable of simultaneously growing epilayers on multiple wafers have enabled higher wafer throughput for SiC electronic device manufacture.

#### 5.4.4.2 SiC Epitaxial Growth Polytype Control

Homoepitaxial growth, whereby the polytype of the SiC epilayer matches the polytype of the SiC substrate, is accomplished by "step-controlled" epitaxy [50–52]. Step-controlled epitaxy is based upon growing epilayers on an SiC wafer polished at an angle (called the "tilt-angle" or "off-axis angle") of typically 3°–8° off the (0001) basal plane, resulting in a surface with atomic steps and relatively long, flat terraces between steps. When growth conditions are properly controlled and there is a sufficiently short distance between steps, Si and C adatoms impinging onto the growth surface find their way to step risers, where they bond and incorporate into the crystal. Thus, ordered, lateral "step-flow" growth takes place which enables the polytypic stacking sequence of the substrate to be exactly mirrored in the growing epilayer. SiC wafers cut with nonconventional surface orientations such as (1120) and (0338), provide a favorable surface geometry for epilayers to inherit stacking sequence (i.e., polytype) via step flow from the substrate [53,54].

When growth conditions are not properly controlled when steps are too far apart, as can occur with poorly prepared SiC substrate surfaces that are polished to within <1° of the (0001) basal plane, growth adatoms island nucleate and bond in the middle of terraces instead of at the steps. Uncontrolled island nucleation (also referred to as terrace nucleation) on SiC surfaces leads to heteroepitaxial growth

of poor-quality 3C-SiC [51,52]. To help prevent spurious terrace nucleation of 3C-SiC during epitaxial growth, most commercial 4H- and 6H-SiC substrates are polished to tilt angles of 8° and 3.5° off the (0 0 0 1) basal plane, respectively. To date, all commercial SiC electronics rely on homoepitaxial layers that are grown on these "off-axis" prepared (0 0 0 1) *c*-axis SiC wafers.

Proper removal of residual surface contamination and defects left over from the SiC wafer cutting and polishing process is also vital to obtaining high-quality SiC epilayers with minimal dislocation defects. Techniques employed to better prepare the SiC wafer surface prior to epitaxial growth range from dry etching to chemical-mechanical polishing (CMP) [55]. As the SiC wafer is heated up in a growth chamber in preparation for initiation of epilayer growth, a high-temperature in-situ pregrowth gaseous etch (typically using  $H_2$  and/or HCl) is usually carried out to further eliminate surface contamination and defects [46,56,57]. It is worth noting that optimized pregrowth processing enables step-flow growth of high-quality homoepilayers even when the substrate tilt angle is reduced to <0.1° off-axis from the (0 0 0 1) basal plane [56]. In this case, axial screw dislocations are required to provide a continual spiral template of steps needed to grow epilayers in the <0 0 0 1> direction while maintaining the hexagonal polytype of the substrate [58].

#### 5.4.4.3 SiC Epilayer Doping

In-situ doping during CVD epitaxial growth is primarily accomplished through the introduction of nitrogen (usually N<sub>2</sub>) for n-type and aluminum (usually trimethyl- or triethylaluminum) for p-type epilayers [10,59]. Some alternative dopants such as phosphorus and boron have also been investigated for the n-and p-type epilayers, respectively [59,60]. While some variation in epilayer doping can be carried out strictly by varying the flow of dopant gases, the site-competition doping methodology has enabled a much broader range of SiC doping to be accomplished [59,61]. In addition, site competition has also made moderate epilayer dopings more reliable and repeatable. The site-competition dopantcontrol technique is based on the fact that many dopants of SiC preferentially incorporate into either Si lattice sites or C lattice sites. As an example, nitrogen preferentially incorporates into lattice sites normally occupied by carbon atoms. By epitaxially growing SiC under carbon-rich conditions, most of the nitrogen present in the CVD system (whether it is a residual contaminant or intentionally introduced) can be excluded from incorporating into the growing SiC crystal. Conversely, by growing in a carbon-deficient environment, the incorporation of nitrogen can be enhanced to form very heavily doped epilayers for ohmic contacts. Aluminum, which is opposite to nitrogen, prefers the Si site of SiC, and other dopants have also been controlled through site competition by properly varying the Si/C ratio during crystal growth. SiC epilayer dopings ranging from  $9 \times 10^{14}$  to  $1 \times 10^{19}$  cm<sup>-3</sup> are commercially available, and researchers have reported obtaining dopings over a factor of 10 larger and smaller than this range for the n- and p-type dopings [40]. The surface orientation of the wafer also affects the efficiency of doping incorporation during epilayer growth [54]. As of this writing, epilayers available for consumers to specify and purchase to meet their own device application needs have thickness and doping tolerances of ±25% and ±50%, respectively [40]. However, some SiC epilayers used for high-volume device production are far more optimized, exhibiting <5% variation in doping and thickness [41].

#### 5.4.5 SiC Crystal Dislocation Defects

Table 5.2 summarizes the major known dislocation defects found in present-day commercial 4H- and 6H-SiC wafers and epilayers [10,39,41,62,63]. Since the active regions of devices reside in epilayers, the epilayer defect content is clearly of primary importance to SiC device performance. However, as evidenced by Table 5.2, most epilayer defects originate from dislocations found in the underlying SiC substrate prior to epilayer deposition. More details on the electrical impact of some of these defects on specific devices are discussed later in Section 5.6.

The micropipe defect is regarded as the most obvious and damaging "device-killer" defect to SiC electronic devices [64]. A micropipe is an axial screw dislocation with a hollow core (diameter of the order of a micrometer) in the SiC wafer and epilayer that extends roughly parallel to the crystallographic

*c*-axis normal to the polished *c*-axis wafer surface [65–67]. These defects impart considerable local strain to the surrounding SiC crystal that can be observed using X-ray topography or optical cross polarizers [39,41,68,69]. Over the course of a decade, substantial efforts by SiC material vendors has succeeded in reducing SiC wafer micropipe densities nearly 100-fold, and some SiC boules completely free of micropipes have been demonstrated [10,41,70]. In addition, epitaxial growth techniques for closing SiC substrate micropipes (effectively dissociating the hollow-core axial dislocation into multiple closed-core dislocations) have been developed [71]. However, this approach has not yet met the demanding electronic reliability requirements for commercial SiC power devices that operate at high electric fields [72].

Even though micropipe "device-killer" defects have been almost eliminated, commercial 4H- and 6H-SiC wafers and epilayers still contain very high densities (>10,000 cm<sup>-2</sup>, summarized in Table 5.2) of other less-harmful dislocation defects. While these remaining dislocations are not presently specified in SiC material vendor specification sheets, they are nevertheless believed responsible for a variety of nonideal device behaviors that have hindered reproducibility and commercialization of some (particularly high electric field) SiC electronic devices [63,73,74]. Closed-core axial screw dislocation defects are similar in structure and strain properties to micropipes, except that their Burgers vectors are smaller so that the core is solid instead of a hollow void [66,67,75,76]. As shown in Table 5.2, basal plane dislocation defects and threading edge dislocation defects are also plentiful in commercial SiC wafers [39,62].

As discussed later in Section 5.6.4.1.2, 4H-SiC electrical device degradation caused by the expansion of stacking faults initiated from basal plane dislocation defects has hindered commercialization of bipolar power devices [63,74,77,78]. Similar stacking fault expansion has also been reported when doped 4H-SiC epilayers have been subjected to modest (~1150°C) thermal oxidation processing [79,80]. While epitaxial growth techniques to convert basal-plane dislocations into threading-edge dislocations have recently been reported, the electrical impact of threading-edge dislocations on the performance and reliability of high-electric field SiC devices remains to be fully ascertained [39]. It is also important to note that present-day commercial SiC epilayers still contain some undesirable surface morphological features such as "carrot defects" which could affect SiC device processing and performance [40,81,82].

In an exciting initial breakthrough, a Japanese team of researchers reported in 2004 that they achieved a 100-fold reduction in dislocation density in prototype 4H-SiC wafers of up to 3 in. in diameter [83]. While such greatly improved SiC wafer quality offered by this "multiple *a*-face" growth technique should prove highly beneficial to electronic (especially high-power) SiC device capabilities, it remains uncertain as of this writing as to when this significantly more complex (and therefore expensive) growth process will result in commercially viable mass-produced SiC wafers and devices.

#### 5.5 SiC Device Fundamentals

To minimize the development and production costs of SiC electronics, it is important that SiC device fabrication takes advantage of existing silicon and GaAs wafer processing infrastructure as much as possible. As will be discussed in this section, most of the steps necessary to fabricate SiC electronics starting from SiC wafers can be accomplished using somewhat modified commercial silicon electronics processes and fabrication tools.

## 5.5.1 Choice of Polytype for Devices

As discussed in Section 4, 4H- and 6H-SiC are the far superior forms of semiconductor device quality SiC commercially available in mass-produced wafer form. Therefore, only 4H- and 6H-SiC device processing methods will be explicitly considered in the rest of this section. It should be noted, however, that most of the processing methods discussed in this section are applicable to other polytypes of SiC, except for the case of a 3C-SiC layer still residing on a silicon substrate, where all processing temperatures need to be kept well below the melting temperature of silicon (~1400°C). It is generally accepted that 4H-SiC's substantially higher carrier mobility and shallower dopant ionization energies compared to 6H-SiC (Table 5.1) should make it the polytype of choice for most SiC electronic devices, provided that all other device processing,

performance, and cost-related issues play out as being roughly equal between the two polytypes. Furthermore, the inherent mobility anisotropy that degrades conduction parallel to the crystallographic *c*-axis in 6H-SiC particularly favors 4H-SiC for vertical power device configurations (Section the 5.6.4). Because the ionization energy of the p-type acceptor dopants is significantly deeper than for the n-type donors, a much higher conductivity can be obtained for the n-type SiC substrates than for the p-type substrates.

## 5.5.2 SiC-Selective Doping: Ion Implantation

The fact that diffusion coefficients of most SiC dopants are negligibly small (at ≤1800°C) is excellent for maintaining device junction stability, because dopants do not undesirably diffuse as the device is operated long term at high temperatures. Unfortunately, this characteristic also largely (except for B at extreme temperatures [84]) precludes the use of conventional dopant diffusion, a highly useful technique widely employed in silicon microelectronics manufacturing, for patterned doping of SiC.

Laterally patterned doping of SiC is carried out by ion implantation. This somewhat restricts the depth that most dopants can be conventionally implanted to  $<1~\mu m$  using conventional dopants and implantation equipment. Compared to silicon processes, SiC ion implantation requires a much higher thermal budget to achieve acceptable dopant implant electrical activation. Summaries of ion implantation processes for various dopants can be found in [85–96]. Most of these processes are based on carrying out implantation at temperatures ranging from room temperature to  $800^{\circ}$ C using a patterned (sometimes high-temperature) masking material. The elevated temperature during implantation promotes some lattice self-healing during the implant, so that damage and segregation of displaced silicon and carbon atoms does not become excessive, especially in high-dose implants often employed for ohmic contact formation. Co-implantation of carbon with dopants has been investigated as a means to improve the electrical conductivity of the more heavily doped implanted layers [88,95,97].

Following implantation, the patterning mask is stripped and a higher temperature (~1200 to 1800°C) anneal is carried out to achieve maximum electrical activation of dopant ions. The final annealing conditions are crucial to obtaining desired electrical properties from ion-implanted layers. At higher implant anneal temperature, the SiC surface morphology can seriously degrade [87,98]. Because sublimation etching is driven primarily by loss of silicon from the crystal surface, annealing in silicon overpressures can be used to reduce surface degradation during high-temperature anneals [99]. Such overpressure can be achieved by close-proximity solid sources such as using an enclosed SiC crucible with SiC lid and/or SiC powder near the wafer, or by annealing in a silane-containing atmosphere. Similarly, robust deposited capping layers such as AlN and graphite, have also proven effective at better preserving SiC surface morphology during high-temperature ion implantation annealing [91,92].

As evidenced by a number of works, the electrical properties and defect structure of 4H-SiC doped by ion implantation and annealing are generally inferior to SiC doped in-situ during epitaxial growth [89,100–103]. Naturally, the damage imposed on the SiC lattice roughly scales with implantation dose. Even though reasonable electrical dopant activations have been achieved, thermal annealing processes developed to date for SiC have not been able to thoroughly repair all damage imposed on the crystal lattice by higher-dose ion implantations (such as those often used to form heavily doped layers in preparation of ohmic contact formation, Section 5.5.3). The degraded crystal quality of highly implanted SiC layers has been observed to degrade carrier mobilities and minority carrier lifetimes, thereby causing significant degradation to the electrical performance of some devices [90,103]. Until large further improvements to ion-implanted doping of SiC are developed, SiC device designs will have to account for nonideal behavior associated with SiC-implanted layers.

#### 5.5.3 SiC Contacts and Interconnect

All useful semiconductor electronics require conductive signal paths in and out of each device as well as conductive interconnects to carry signals between devices on the same chip and to external circuit elements that reside off-chip. While SiC itself is theoretically capable of fantastic electrical operation

under extreme conditions (Section 5.3), such functionality is useless without contacts and interconnects that are also capable of operation under the same conditions. The durability and reliability of metal–semiconductor contacts and interconnects are one of the main factors limiting the operational high-temperature limits of SiC electronics. Similarly, SiC high-power device contacts and metallizations will have to withstand both high temperature and high current density stress never before encountered in silicon power electronics experience.

The subject of metal–semiconductor contact formation is a very important technical field too broad to be discussed in great detail here. For general background discussions on metal–semiconductor contact physics and formation, the reader should consult narratives presented in References 15 and 104. These references primarily discuss ohmic contacts to conventional narrow-bandgap semiconductors such as silicon and GaAs. Specific overviews of SiC metal–semiconductor contact technology can be found in References 105–110.

As discussed in References 105–110, there are both similarities and a few differences between SiC contacts and contacts to conventional narrow-bandgap semiconductors (e.g., silicon, GaAs). The same basic physics and current transport mechanisms that are present in narrow-bandgap contacts such as surface states, Fermi-pinning, thermionic emission, and tunneling, also apply to SiC contacts. A natural consequence of the wider bandgap of SiC is the higher effective Schottky barrier heights. Analogous with narrow-bandgap ohmic contact physics, the microstructural and chemical state of the SiC—metal interface is crucial to contact electrical properties. Therefore, premetal-deposition surface preparation, metal deposition process, choice of metal, and post-deposition annealing can all greatly impact the resulting performance of metal—SiC contacts. Because the chemical nature of the starting SiC surface is strongly dependent on surface polarity, it is not uncommon to obtain significantly different results when the same contact process is applied to the silicon face surface versus the carbon face surface.

#### 5.5.3.1 SiC Ohmic Contacts

Ohmic contacts serve the purpose of carrying electrical current into and out of the semiconductor, ideally with no parasitic resistance. The properties of various ohmic contacts to SiC reported to date are summarized elsewhere [107–110]. While SiC-specific ohmic contact resistances at room temperature are generally higher than in contacts to narrow-bandgap semiconductors, they are nevertheless sufficiently low for most envisioned SiC applications. Lower specific contact resistances are usually obtained to n-type than to p-type 4H- and 6H-SiC. Consistent with narrow-bandgap ohmic contact technology, it is easier to make low-resistance ohmic contacts to heavily doped SiC and thermal annealing is almost always employed to promote favorable interfacial reactions.

Truly enabling harsh-environment SiC electronics will require ohmic contacts that can reliably withstand prolonged harsh-environment operation. Most reported SiC ohmic metallizations appear sufficient for long-term device operation up to 300°C. SiC ohmic contacts that withstand heat soaking under no electrical bias at 500–600°C for hundreds or thousands of hours in nonoxidizing gas or vacuum environments have also been demonstrated [110]. Only recently has successful long-term electrical operation of n-type ohmic contacts in oxidizing 500–600°C air ambients been demonstrated in relatively low-current density devices [111,112]. Further research is needed to obtain similarly durable high-temperature contacts to p-type SiC. Electromigration, oxidation, and other electrochemical reactions driven by high-temperature electrical bias in a reactive oxidizing environment are likely to limit SiC ohmic contact reliability for the most demanding applications that simultaneously require both high temperature and high power (i.e., high current density). The durability and reliability of SiC ohmic contacts is one of the critical factors limiting the practical high-temperature limits of SiC electronics.

#### 5.5.3.2 SiC Schottky Contacts

Rectifying metal-semiconductor Schottky barrier contacts to SiC are useful for a number of devices, including commercialized SiC metal-semiconductor field-effect transistors (MESFETs) and fast-switching rectifiers [40,113]. References 105, 106, 108, and 114 summarize electrical results obtained in a variety

of SiC Schottky studies. Owing to the wide bandgap of SiC, almost all unannealed metal contacts to lightly doped 4H- and 6H-SiC are rectifying. Rectifying contacts permit extraction of Schottky barrier heights and diode ideality factors by well-known current-voltage (*I*–*V*) and capacitance-voltage (*C*–*V*) electrical measurement techniques [104]. While these measurements show a general trend that Schottky junction barrier height does somewhat depend on metal-semiconductor work function difference, the dependence is weak enough to suggest that surface state charge also plays a significant role in determining the effective barrier height of SiC Schottky junctions. At least some experimental scatter exhibited for identical metals can be attributed to surface cleaning and metal deposition process differences, as well as different barrier height measurement procedures. For example, the work by Teraji et al. [115], in which two different surface-cleaning procedures prior to titanium deposition lead to ohmic behavior in one case and rectifying behavior in the other, clearly shows that the process plays a significant role in determining SiC Schottky contact electrical properties.

It is important to note that nonuniformities in electrical behavior, many of which have been traced to SiC crystal defects (Section 5.4.5) have been documented to exist across the lateral area of most SiC Schottky contacts with areas >10<sup>-4</sup> cm² [116–118]. Furthermore, the reverse current drawn in experimental SiC diodes, while small, is nevertheless larger than expected based on theoretical substitution of SiC parameters into well-known Schottky diode reverse leakage current equations developed for narrow-bandgap semiconductors. Models based on spatially localized Schottky barrier lowering as well as quantum mechanical tunneling owing to higher SiC electric fields, have been proposed to explain the nonideal reverse leakage behavior of SiC Schottky diodes [119–121]. In addition, electric field crowding along the edge of a SiC Schottky contact can also lead to increased reverse-bias leakage current and reduced reverse breakdown voltage [15,18,104]. Edge-termination techniques to relieve electric field edge crowding and improve Schottky rectifier reverse properties are briefly discussed later in Section 5.6.4. The practical operation of rectifying SiC Schottky diodes is usually limited to temperatures below 400°C; above this temperature, reverse-bias thermionic emission leakage current and thermally driven SiC–metal interface degradation (via material intermixing and chemical reactions) tend to become undesirably large.

#### 5.5.4 Patterned Etching of SiC for Device Fabrication

At room temperature, there are no known conventional wet chemicals that etch single-crystal SiC. Most patterned etching of SiC for electronic devices and circuits is accomplished using dry etching techniques. The reader should consult References 122–124 which contain summaries of dry SiC etching results obtained to date. The most commonly employed process involves reactive ion etching (RIE) of SiC in fluorinated plasmas. Sacrificial etch masks (such as aluminum metal) are deposited and photolithographically patterned to protect desired areas from being etched. The SiC RIE process can be implemented using standard silicon RIE hardware and typical 4H- and 6H-SiC RIE etch rates of the order of hundreds of angstroms per minute. Well-optimized SiC RIE processes are typically highly anisotropic with little undercutting of the etch mask, leaving smooth surfaces. One of the keys to achieving smooth surfaces is preventing "micromasking", wherein the masking material is slightly etched and randomly redeposited onto the sample effectively masking very small areas on the sample that were intended for uniform etching. This can result in "grass"-like etch-residue features being formed in the unmasked regions, which is undesirable in most cases.

While RIE etch rates are sufficient for many electronic applications, much higher SiC etch rates are necessary to carve features of the order of tens to hundreds of micrometers deep that are needed to realize advanced sensors, MEMS, and through-wafer holes useful for SiC RF devices. High-density plasma dryetching techniques such as electron cyclotron resonance and inductively coupled plasma have been developed to meet the need for deep etching of SiC. Residue-free patterned etch rates exceeding a thousand angstroms a minute have been demonstrated [122,123,125–128].

Patterned etching of SiC at very high etch rates has also been demonstrated using photo-assisted and dark electrochemical wet etching [129,130]. By choosing proper etching conditions, this technique has demonstrated a very useful dopant-selective etch-stop capability. However, there are major incompatibilities

of the electrochemical process that make it undesirable for VLSI mass production, including extensive preetching and postetching sample preparation, etch isotropy and mask undercutting, and somewhat nonuniform etching across the sample. Laser etching techniques are capable of etching large features, such as via through-wafer holes useful for RF chips [131].

## 5.5.5 SiC Insulators: Thermal Oxides and MOS Technology

The vast majority of semiconductor-integrated circuit chips in use today rely on silicon metal-oxide-semiconductor field-effect transistors (MOSFETs), whose electronic advantages and operational device physics are summarized in Katsumata's chapter and elsewhere [15,18,132]. Given the extreme usefulness and success of inversion channel MOSFET-based electronics in VLSI silicon (as well as discrete silicon power devices), it is naturally desirable to implement high-performance inversion channel MOSFETs in SiC. Like silicon, SiC forms a thermal SiO<sub>2</sub> when it is sufficiently heated in an oxygen environment. While this enables SiC MOS technology to somewhat follow the highly successful path of silicon MOS technology, there are nevertheless important differences in insulator quality and device processing that are presently preventing SiC MOSFETs from realizing their full beneficial potential. While the following discourse attempts to quickly highlight key issues facing SiC MOSFET development, more detailed insights can be found in References 133–142.

From a purely electrical point of view, there are two prime operational deficiencies of SiC oxides and MOSFETs compared to silicon MOSFETs. First, effective inversion channel mobilities in most SiC MOSFETs are lower than one would expect based on silicon inversion channel MOSFET carrier mobilities. This seriously reduces the transistor gain and current-carrying capability of SiC MOSFETs, so that SiC MOSFETs are not nearly as advantageous as theoretically predicted. Second, SiC oxides have not proven as reliable and immutable as well-developed silicon oxides, in that SiC MOSFETs are more prone to threshold voltage shifts, gate leakage, and oxide failures than comparably biased silicon MOSFETs. In particular, SiC MOSFET oxide electrical performance deficiencies are attributed to differences between silicon and SiC thermal oxide quality and interface structure that cause the SiC oxide to exhibit undesirably higher levels of interface state densities (~10<sup>11</sup>–10<sup>13</sup> eV<sup>-1</sup> cm<sup>-2</sup>), fixed oxide charges (~10<sup>11</sup>–10<sup>12</sup> cm<sup>-2</sup>), charge trapping, carrier oxide tunneling, and lowered mobility of inversion channel carriers.

In highlighting the difficulties facing SiC MOSFET development, it is important to keep in mind that early silicon MOSFETs also faced developmental challenges that took many years of dedicated research efforts to successfully overcome. Indeed, tremendous improvements in 4H-SiC MOS device performance have been achieved in recent years, giving hope that beneficial 4H-SiC power MOSFET devices for operation up to 125°C ambient temperatures might become commercialized within the next few years. For example, 4H-SiC MOSFET inversion channel mobility for conventionally oriented (8° off (0001) c-axis) wafers has improved from <10 to >200 cm<sup>2</sup>/V<sup>-1</sup>s<sup>-1</sup>, while the density of electrically detrimental SiC-SiO<sub>2</sub> interface state defects energetically residing close to the conduction band edge has dropped by an order of magnitude [141,143,144]. Likewise, alternative SiC wafer surface orientations such as (1120) and (0338) that are obtained by making devices on wafers cut with different crystallographic orientations (Section 5.2.1), have also yielded significantly improved 4H-SiC MOS channel properties [54,139]. One key step to obtaining greatly improved 4H-SiC MOS devices has been the proper introduction of nitrogen-compound gases (in the form of N<sub>2</sub>, NO, N<sub>2</sub>O, or NH<sub>3</sub>) during the oxidation and postoxidation annealing process [136,137,141,142]. These nitrogen-based anneals have also improved the stability of 4H-SiC oxides to high electric field and high-temperature stressing used to qualify and quantify the reliability of MOSFETs [140]. However, as Agarwal et al. [145] have pointed out, the wide bandgap of SiC reduces the potential barrier impeding tunneling of damaging carriers through oxides grown on 4H-SiC, so that 4H-SiC oxides cannot be expected to attain identical high reliability as thermal oxides on silicon. It is highly probable that alternative gate insulators besides thermally grown SiO<sub>2</sub> will have to be developed for optimized implementation of inversion channel 4H-SiC insulated gate transistors for the most demanding high-temperature and high-power electronic applications. As with silicon MOSFET technology, multilayer dielectric stacks will likely be developed to further enhance SiC MOSFET performance [133,146].

## 5.5.6 SiC Device Packaging and System Considerations

Hostile-environment SiC semiconductor devices and ICs are of little advantage if they cannot be reliably packaged and connected to form a complete system capable of hostile-environment operation. With proper material selection, modifications of existing IC packaging technologies appear feasible for non-power SiC circuit packaging up to 300°C [147]. Recent work is beginning to address the needs of the most demanding aerospace electronic applications, whose requirements include operation in high-vibration 500–600°C oxidizing-ambient environments, sometimes with very high power [7,148–152]. For example, some prototype electronic packages and circuit boards that can withstand over a thousand hours at 500°C have been demonstrated. Harsh-environment passive components such as inductors, capacitors, and transformers, must also be developed for operation in demanding conditions before the full system-level benefits of SiC electronics discussed in Section 5.3 can be successfully realized.

## 5.6 SiC Electronic Devices and Circuits

This section briefly summarizes a variety of SiC electronic device designs broken down by major application areas. SiC process and material technology issues limiting the capabilities of various SiC device topologies are highlighted as key issues to be addressed in further SiC technology maturation. Throughout this section, it should become apparent to the reader that the most difficult general challenge preventing SiC electronics from fully attaining beneficial capabilities is attaining long-term high operational reliability, while operating in previously unattained temperature and power density regimes. Because many device reliability limitations can be traced to fundamental material and junction/interface issues already mentioned in Sections 5.4 and 5.5, efforts to enable useful (i.e., reliable) SiC electronics should focus on improvements to these fundamental areas.

## 5.6.1 SiC Optoelectronic Devices

The wide bandgap of SiC is useful for realizing short-wavelength blue and ultraviolet (UV) optoelectronics. 6H-SiC-based pn junction light-emitting diodes (LEDs) were the first semiconductor devices to cover the blue portion of the visible color spectrum, and became the first SiC-based devices to reach high-volume commercial sales [153]. Because SiC's bandgap is indirect (i.e., the conduction minimum and valence band maximum do not coincide in crystal momentum space), luminescent recombination is inherently inefficient [154]. Therefore, LEDs based on SiC pn junctions were rendered quite obsolete by the emergence of much brighter, much more efficient direct-bandgap Group III-nitride (III-N such as GaN, and InGaN) blue LEDs [155]. However, SiC wafers are still employed as one of the substrates (along with sapphire) for growth of III-N layers used in high-volume manufacture of green and blue nitride-based LEDs.

SiC has proven much more efficient at absorbing short-wavelength light, which has enabled the realization of SiC UV-sensitive photodiodes that serve as excellent flame sensors in turbine-engine combustion monitoring and control [153,156]. The wide bandgap of 6H-SiC is useful for realizing low photodiode dark currents as well as sensors that are blind to undesired near-infrared wavelengths produced by heat and solar radiation. Commercial SiC-based UV flame sensors, again based on epitaxially grown dry-etch mesa-isolated 6H-SiC pn junction diodes, have successfully reduced harmful pollution emissions from gas-fired ground-based turbines used in electrical power generation systems [156]. The low dark-currents of SiC diodes are also useful for X-ray, heavy ion, and neutron detection in nuclear reactor monitoring and enhanced scientific studies of high-energy particle collisions and cosmic radiation [157,158].

#### 5.6.2 SiC RF Devices

The main use of SiC RF devices appears to lie in high-frequency solid-state high-power amplification at frequencies from around 600 MHz (UHF-band) to perhaps as high as a few gigahertz (X-band). As discussed in far greater detail in References 5, 6, 25, 26, 159, and elsewhere, the high breakdown voltage and high thermal conductivity coupled with high carrier saturation velocity allow SiC RF transistors to handle much higher power densities than their silicon or GaAs RF counterparts, despite SiC's disadvantage in low-field carrier mobility (Table 5.1). The higher thermal conductivity of SiC is also crucial in minimizing channel self-heating so that phonon scattering does not seriously degrade carrier velocity. These material advantage RF power arguments apply to a variety of different transistor structures such as MESFETs and static induction transistors (SITs) and other wide bandgap semiconductors (such as Group III-nitrides) besides SiC. The high power density of wide bandgap transistors will prove quite useful in realizing solid-state transmitter applications, where higher power with smaller size and mass are crucial. Fewer transistors capable of operating at higher temperatures reduce matching and cooling requirements, leading to reduced overall size and cost of these systems.

SiC-based high-frequency RF MESFETs are now commercially available [40]. However, it is important to note that this occurred after years of fundamental research tracked down and eliminated poor reliability owing to charge-trapping effects arising from immature semi-insulating substrates, device epilayers, and surface passivation [159]. One key material advancement that enabled reliable operation was the development of "high-purity" semi-insulating SiC substrates (needed to minimize parasitic device capacitances) with far less charge trapping induced than the previously developed vanadium-doped semi-insulating SiC wafers. SiC MESFET devices fabricated on semi-insulating substrates are conceivably less susceptible to adverse yield consequences arising from micropipes than vertical high-power switching devices, primarily because a *c*-axis micropipe can no longer short together two conducting sides of a high field junction in most areas of the lateral channel MESFET structure.

SiC mixer diodes also show excellent promise for reducing undesired intermodulation interference in RF receivers [160–162]. More than 20 dB dynamic range improvement was demonstrated using non-optimized SiC Schottky diode mixers. Following further development and optimization, SiC-based mixers should improve the interference immunity in situations (such as in aircraft or ships) where receivers and high-power transmitters are closely located.

## 5.6.3 SiC High-Temperature Signal-Level Devices

Most analog signal conditioning and digital logic circuits are considered "signal level" in that individual transistors in these circuits do not typically require any more than a few milliamperes of current and <20 V to function properly. Commercially available silicon-on-insulator circuits can perform complex digital and analog signal-level functions up to 300°C when high-power output is not required [163]. Besides ICs in which it is advantageous to combine signal-level functions with high-power or unique SiC sensors/MEMS onto a single chip, more expensive SiC circuits solely performing low-power signal-level functions appear largely unjustifiable for low-radiation applications at temperatures below 250–300°C [7].

As of this writing, there are no commercially available semiconductor transistors or integrated circuits (SiC or otherwise) for use in ambient temperatures above 300°C. Even though SiC-based high-temperature laboratory prototypes have improved significantly over the last decade, achieving long-term operational reliability remains the primary challenge of realizing useful 300–600°C devices and circuits. Circuit technologies that have been used to successfully implement VLSI circuits in silicon and GaAs such as CMOS, ECL, BiCMOS, DCFL, etc., are to varying degrees candidates for T > 300°C SiC-integrated circuits. High-temperature gate-insulator reliability (Section 5.5.5) is critical to the successful realization of MOSFET-based integrated circuits. Gate-to-channel Schottky diode leakage limits the peak operating temperature of SiC MESFET circuits to around 400°C (Section 5.5.3.2). Therefore, pn junction-based devices such as bipolar junction transistors (BJTs) and junction field effect transistors (JFETs), appear to be stronger (at least in the nearer term) candidate technologies to attain long-duration operation in

300–600°C ambients. Because signal-level circuits are operated at relatively low electric fields well below the electrical failure voltage of most dislocations, micropipes and other SiC dislocations affect signal-level circuit process yields to a much lesser degree than they affect high-field power device yields.

As of this writing, some discrete transistors and small-scale prototype logic and analog amplifier SiC-based ICs have been demonstrated in the laboratory using SiC variations of NMOS, CMOS, JFET, and MESFET device topologies [164–170]. However, none of these prototypes are commercially viable as of this writing, largely owing to their inability to offer prolonged-duration electrically stable operation at ambient temperatures beyond the ~250–300°C realm of silicon-on-insulator technology. As discussed in Section 5.5, a common obstacle to all high-temperature SiC device technologies is reliable long-term operation of contacts, interconnect, passivation, and packaging at T > 300°C. By incorporating highly durable high-temperature ohmic contacts and packaging, prolonged continuous electrical operation of a packaged 6H-SiC field effect transistor at 500°C in oxidizing air environment was recently demonstrated [111,112,149].

As further improvements to fundamental SiC device processing technologies (Section 5.5) are made, increasingly durable  $T > 300^{\circ}\text{C}$  SiC-based transistor technology will evolve for beneficial use in harsh-environment applications. Increasingly complex high-temperature functionality will require robust circuit designs that accommodate large changes in device operating parameters over the much wider temperature ranges (as large as 650°C spread) enabled by SiC. Circuit models need to account for the fact that SiC device epilayers are significantly "frozen-out" owing to deeper donor and acceptor dopant ionization energies, so that nontrivial percentages of device-layer dopants are not ionized to conduct current near room temperature [171]. Because of these carrier freeze-out effects, it will be difficult to realize SiC-based ICs operational at junction temperatures much lower than  $-55^{\circ}$ C (the lower end of U.S. Mil-Spec. temperature range).

## 5.6.4 SiC High-Power Switching Devices

The inherent material properties and basic physics behind the large theoretical benefits of SiC over silicon for power switching devices were discussed Section 5.3.2. Similarly, it was discussed in Section 5.4.5 that crystallographic defects found in SiC wafers and epilayers are presently a primary factor limiting the commercialization of useful SiC high-power switching devices. This section focuses on the additional developmental aspects of SiC power rectifiers and power switching transistor technologies.

Most SiC power device prototypes employ similar topologies and features as their silicon-based counterparts such as vertical flow of high current through the substrate to maximize device current using minimal wafer area (i.e., maximize current density) [18]. In contrast to silicon, however, the relatively low conductivity of present-day p-type SiC substrates (Section 5.4.3) dictates that all vertical SiC power device structures be implemented using n-type substrates in order to achieve beneficially high vertical current densities. Many of the device design trade-offs roughly parallel well-known silicon power device trade-offs, except for the fact that numbers for current densities, voltages, power densities, and switching speeds are much higher in SiC.

For power devices to successfully function at high voltages, peripheral breakdown owing to edge-related electric field crowding [15,18,104] must be avoided through careful device design and proper choice of insulating/passivating dielectric materials. The peak voltage of many prototype high-voltage SiC devices has often been limited by destructive edge-related breakdown, especially in SiC devices capable of blocking multiple kilovolts. In addition, most testing of many prototype multikilovolt SiC devices has required the device to be immersed in specialized high-dielectric strength fluids or gas atmospheres to minimize damaging electrical arcing and surface flashover at device peripheries. A variety of edge-termination methodologies, many of which were originally pioneered in silicon high-voltage devices, have been applied to prototype SiC power devices with varying degrees of success, including tailored dopant and metal guard rings [172–179]. The higher voltages and higher local electric fields of SiC power devices will place larger stresses on packaging and on wafer insulating materials, so some of the materials used to insulate/passivate silicon high-voltage devices may not

prove sufficient for reliable use in SiC high-voltage devices, especially if those devices are to be operated at high temperatures.

## 5.6.4.1 SiC High-Power Rectifiers

The high-power diode rectifier is a critical building block of power conversion circuits. Recent reviews of experimental SiC rectifier results are given in References 3, 134, 172, 180, and 181. Most important SiC diode rectifier device design trade-offs roughly parallel well-known silicon rectifier trade-offs, except for the fact that current densities, voltages, power densities, and switching speeds are much higher in SiC. For example, semiconductor Schottky diode rectifiers are majority carrier devices that are well known to exhibit very fast switching owing to the absence of minority carrier charge storage that dominates (i.e., slows, adversely resulting in undesired waste power and heat) the switching operation of bipolar pn junction rectifiers. However, the high breakdown field and wide energy bandgap permit operation of SiC metal–semiconductor Schottky diodes at much higher voltages (above 1 kV) than is practical with silicon-based Schottky diodes that are limited to operation below ~200 V owing to much higher reverse-bias thermionic leakage.

#### 5.6.4.1.1 SiC Schottky Power Rectifiers.

4H-SiC power Schottky diodes (with rated blocking voltages up to 1200 V and rated on-state currents up to 20 A as of this writing) are now commercially available [40,113]. The basic structure of these unipolar diodes is a patterned metal Schottky anode contact residing on top of a relatively thin (roughly of the order of 10  $\mu m$  in thickness) lightly n-doped homoepitaxial layer grown on a much thicker (around 200–300  $\mu m$ ) low-resistivity n-type 4H-SiC substrate (8° off axis, as discussed in Section 5.4.4.2) with backside cathode contact metallization [172,182]. Guard ring structures (usually p-type implants) are usually employed to minimize electric field crowding effects around the edges of the anode contact. Die passivation and packaging help prevent arcing/surface flashover harmful to reliable device operation.

The primary application of these devices to date has been switched-mode power supplies, where (consistent with the discussion in Section 5.3.2) the SiC Schottky rectifier's faster switching with less power loss has enabled higher frequency operation and shrinking of capacitors, inductors and the overall power supply size and weight [3,23]. In particular, the effective absence of minority carrier charge storage enables the unipolar SiC Schottky devices to turn off much faster than the silicon rectifiers (which must be pn junction diodes above ~200 V blocking) which must dissipate injected minority carrier charge energy when turned off. Even though the part cost of SiC rectifiers has been higher than competing silicon rectifiers, an overall lower power supply system cost with useful performance benefits is nevertheless achieved. It should be noted, however, that changes in circuit design are sometimes necessary to best enhance circuit capabilities with acceptable reliability when replacing silicon with SiC components.

As discussed in Section 5.4.5, SiC material quality presently limits the current and voltage ratings of SiC Schottky diodes. Under high forward bias, Schottky diode current conduction is primarily limited by the series resistance of the lightly doped blocking layer. The fact that this series resistance increases with temperature (owing to decreased epilayer carrier mobility) drives equilization of high forward currents through each diode when multiple Schottky diodes are paralleled to handle higher on-state current ratings [17].

#### 5.6.4.1.2 Bipolar and Hybrid Power Rectifiers.

For higher voltage applications, bipolar minority carrier charge injection (i.e., conductivity modulation) should enable SiC pn diodes to carry higher current densities than unipolar Schottky diodes whose drift regions conduct solely using dopant-atom majority carriers [19–21,172,180]. Consistent with silicon rectifier experience, SiC pn junction generation-related reverse leakage is usually smaller than thermionic-assisted Schottky diode reverse leakage. As with silicon bipolar devices, reproducible control of minority carrier lifetime will be essential in optimizing the switching-speed versus on-state current density performance trade-offs of SiC bipolar devices for specific applications. Carrier lifetime reduction via intentional impurity incorporation and introduction of radiation-induced defects appears feasible. However,

TABLE 5.2 Major Types of Extended Crystal Defects Reported in SiC Wafers and Epilayers

| Crystal Defect                        | Density in<br>Wafer (cm <sup>-2</sup> ) | Density in<br>Epilayer (cm <sup>-2</sup> ) | Comments                                                                   |

|---------------------------------------|-----------------------------------------|--------------------------------------------|----------------------------------------------------------------------------|

| Micropipe                             | ~10–100                                 | ~10–100                                    | Known to cause severe reduction in power device                            |

| (Hollow-core axial screw dislocation) | (0)                                     | (0)                                        | breakdown voltage and increase in off-state leakage                        |

| Closed-core axial                     | $\sim 10^3 - 10^4$                      | $\sim 10^3 - 10^4$                         | Known to cause reduction in device breakdown voltage,                      |

| screw dislocation                     | (~10 <sup>2</sup> )                     | $(\sim 10^2)$                              | increase in leakage current, reduction in carrier lifetime                 |

| Basal plane                           | ~104                                    | $\sim 10^2 - 10^3$                         | Known nucleation source of expanding stacking faults                       |

| dislocation                           | (~10 <sup>2</sup> )                     | (<10)                                      | leading to bipolar power device degradation, reduction in carrier lifetime |

| Threading-edge                        | $\sim 10^2 - 10^3$                      | ~104                                       | Impact not well known                                                      |

| dislocation                           | $(\sim 10^2)$                           | $(\sim 10^2)$                              | _                                                                          |

| Stacking faults                       | ~10-104                                 | ~10-104                                    | Faults known to degrade bipolar power devices, reduce                      |

| (disruption of stacking sequence)     | (0)                                     | (0)                                        | carrier lifetime                                                           |

| Carrot defects                        | N/A                                     | 1-10                                       | Known to causes severe reduction in power device                           |