# This Research Was Sponsored by THE NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# UNPUBLISHED PRELIMINARY DATA

# A Digital Controller Using Multirate Sampling for Gain Control

Report No. EDC 1-64-29

by

#### Richard W. Van Pelt

Harry W. Mergler Professor of Engineering Principal Investigator Ns G 36-60 Digital

.

Systems

Laboratory

#### ABSTRACT

33194

The conventional continuous proportional plus integral control algorithm is converted to its sampled, incremental form, then approximated by a set of three differences which are computed digitally and applied to the process actuator at different times and rates. Computation of the three terms at different rates serves to reduce the amount of equipment needed to provide a wide range of integral gain while retaining the stabilizing effect provided by frequent sampling of the proportional term.

Tests demonstrate that the controller performs well for all types of industrial processes except flow loops with slow actuators. For this exception the controller can easily be modified to provide good response. The controller is designed to control a single loop either independently or in conjunction with a higher level control computer.

JUTHOR

ii

9-10-65

Corrected Table of Contents NsG-36/36-03-001 Report No. EDC-1-64-29

(Case Institute)

| Abstract                                                                                                           | Page<br>ii     |

|--------------------------------------------------------------------------------------------------------------------|----------------|

|                                                                                                                    |                |

| Acknowledgment                                                                                                     | iii            |

| List of Figures                                                                                                    | vii            |

| List of Tables                                                                                                     | ix             |

| List of Symbols                                                                                                    | x              |

| Logical Symbols Used                                                                                               | xiV            |

|                                                                                                                    |                |

| Chapter I N 65-33194                                                                                               |                |

| Introduction                                                                                                       | l              |

| Chapter II                                                                                                         |                |

| Nature of the Process Control Problem<br>Process, Transducer and Actuator<br>Analog Controller and Typical Process | 12<br>12<br>14 |

| Chapter III                                                                                                        |                |

| Digital Control Algorithm<br>Preliminary System Assumptions<br>Derivation of the Three Mode Incremental            | 20<br>20       |

| Control Algorithm                                                                                                  | 23             |

| Algorithm                                                                                                          | <b>2</b> 6     |

| Controller Gain Adjustment by Frequency<br>Manipulation                                                            | 28             |

| Priority Allocation and Computation Fre-<br>quency of Algorithm Terms                                              | 34             |

| Intermediate Storage Requirements                                                                                  | 34<br>38       |

| Summary                                                                                                            | 42             |

# Chapter IV

| Detailed Design of the Controller       | 43 |

|-----------------------------------------|----|

| Sequence of Controller Operations       | 43 |

| Conversion of Sequence Rules to Boolean |    |

| Statements                              | 52 |

| Implementation of Boolean Statements by | -  |

| Logical Elements                        | 60 |

| Contoller Modification for Smoothed     |    |

| Integral Effect                         | 64 |

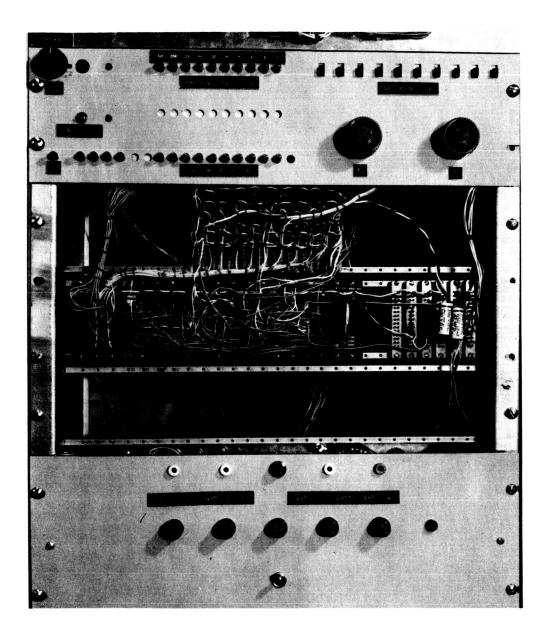

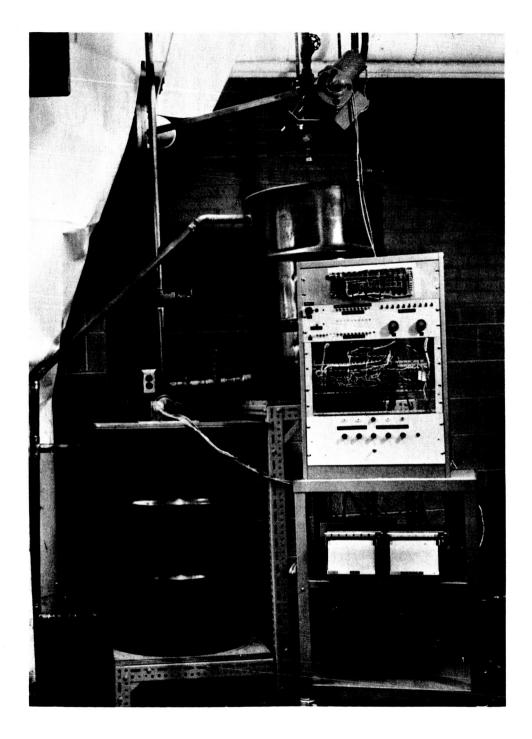

| System Photographs                      | 67 |

| Summary                                 |    |

# Chapter V

| Effect of Algorithm Approximations   |    |

|--------------------------------------|----|

| Upon Controller Performance          | 70 |

| First Difference Approximation       | 71 |

| Separation of Operate and Read Modes | 77 |

| Summary                              | 83 |

|                                      | ΟJ |

# Chapter VI

| Theoretical Closed Loop Response |    |

|----------------------------------|----|

| and Stability                    | 84 |

# Chapter VII

| Experimental Results                        | 91  |

|---------------------------------------------|-----|

| Observed Effects of Algorithm Approximation | 91  |

| Observed Effects of Multirate Sampling      | 96  |

| Summary                                     | 103 |

# Chapter VIII

| Conclusions and Recommendations for Further Work<br>Conclusions<br>Recommendations for Further Work | 104<br>104<br>105 |

|-----------------------------------------------------------------------------------------------------|-------------------|

| Appendix A                                                                                          |                   |

| Controller Tuning by Reaction Rate                                                                  | 109               |

| Appendix B                                                                                          |                   |

| Effect of Noise on Process Output                                                                   | 112               |

| Appendix C                                                                                          |                   |

| Use of Controller with a Higher Level Computer                                                      | 117               |

| List of References                                                                                  | 121               |

vi

#### LIST OF FIGURES

1

۰.

| Figure |                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------|------|

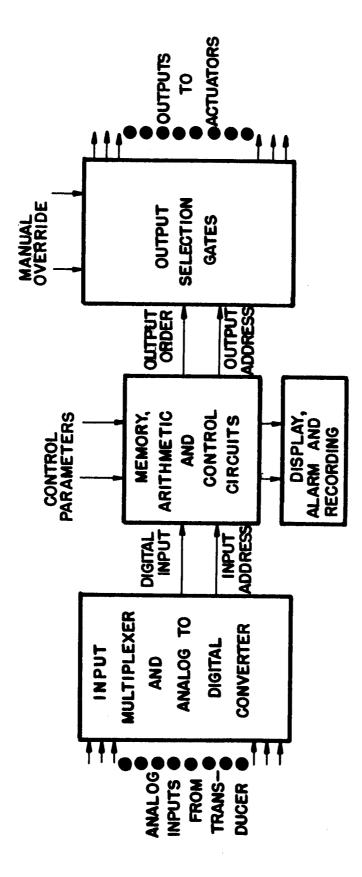

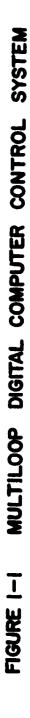

| 1.1    | Multiloop Digital Computer Control System                                              | 7    |

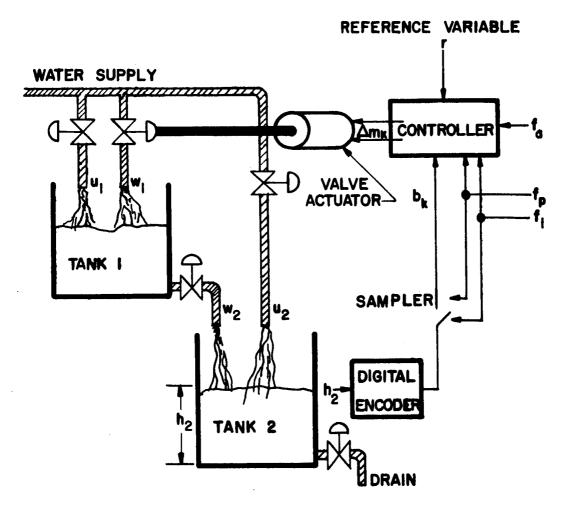

| 1. 2   | Single Loop Digital Controllers                                                        | 8    |

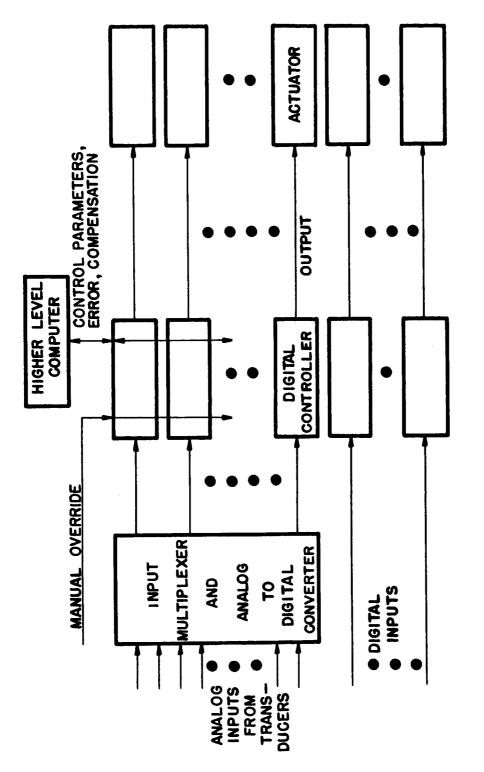

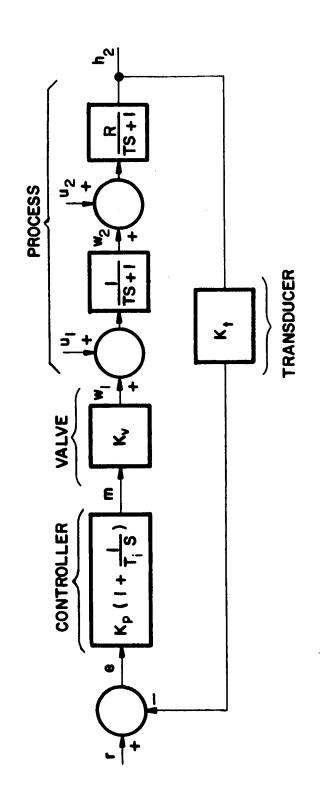

| 2. 1   | Elements of a Process Control Loop                                                     | 13   |

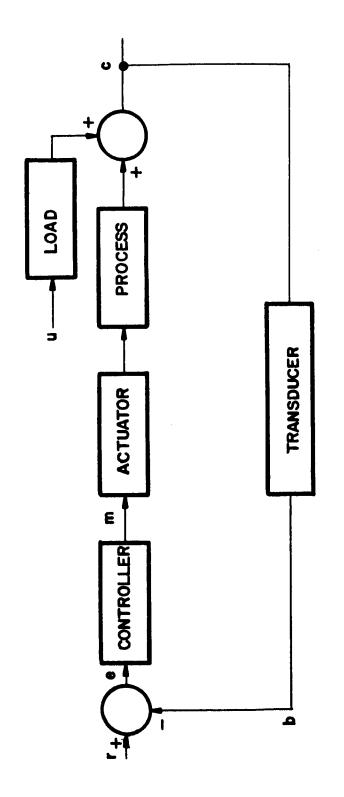

| 2.2    | Schematic of Water Level Control System                                                | 15   |

| 2.3    | Block Diagram of the Continuous Analog                                                 | 17   |

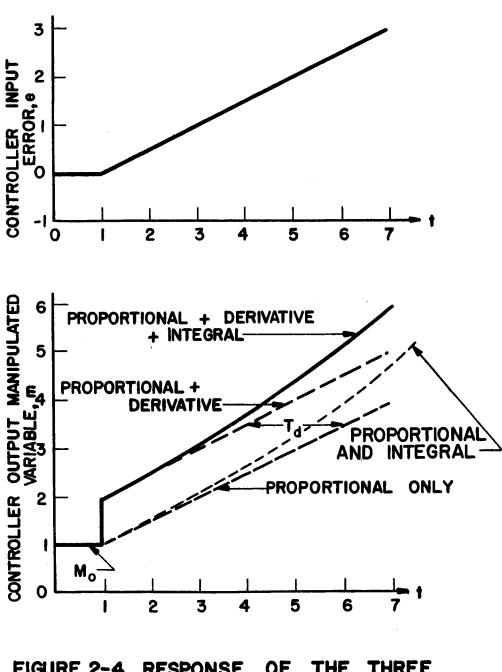

| 2. 4   | Response of the Three Control Modes to a<br>Ramp Error Input                           | 19   |

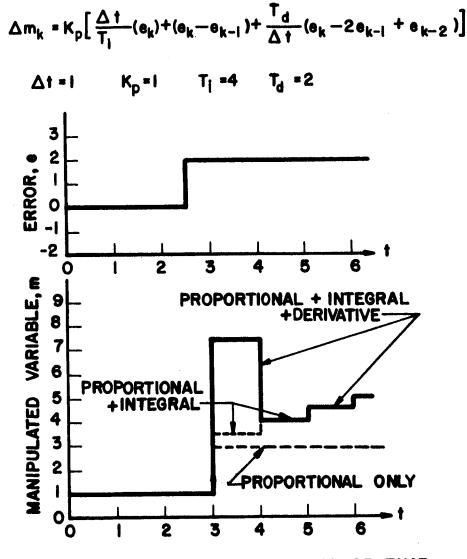

| 3. 1   | Output m of Sampled Three Mode Digital<br>Controller in Response to a Step Error Input | 25   |

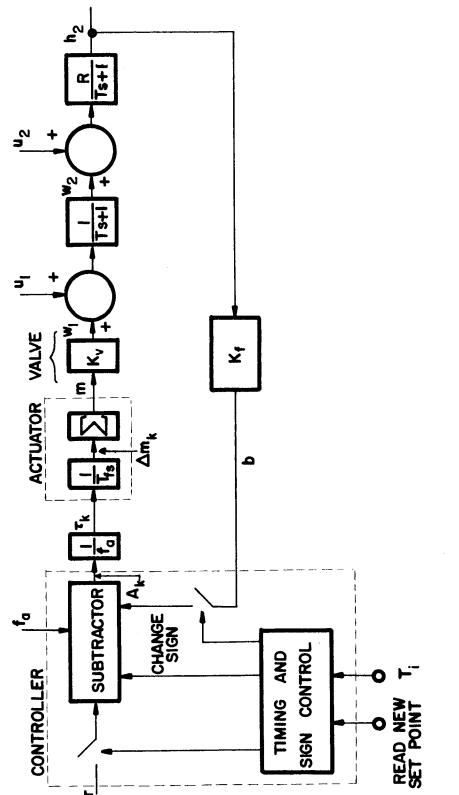

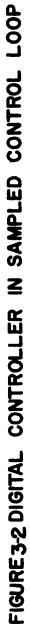

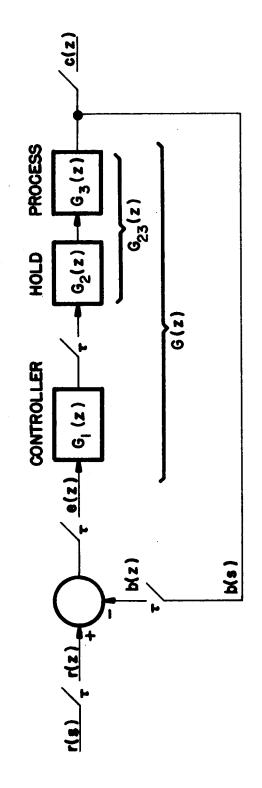

| 3. 2   | Digital Controller in Sampled Control Loop                                             | 30   |

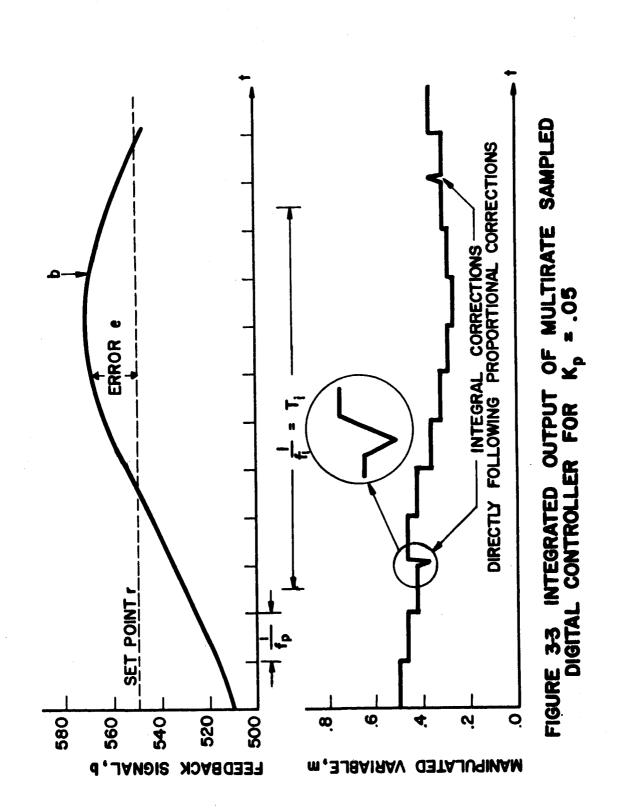

| 3.3    | Integrated Output of Multirate Sampled<br>Digital Controller for $K_p = .05 \dots p$   | 39   |

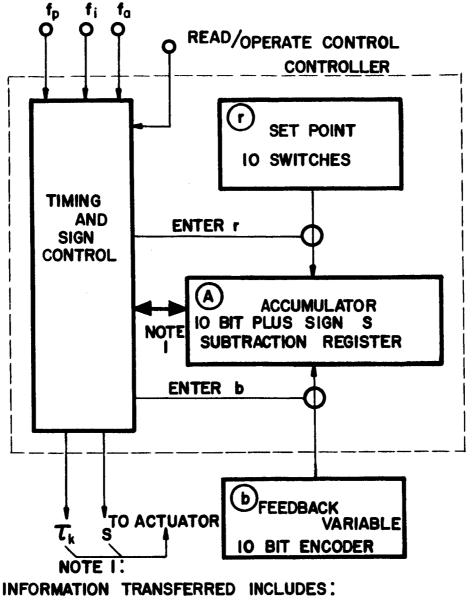

| 4. 1   | Schematic of Controller and Encoder                                                    | 45   |

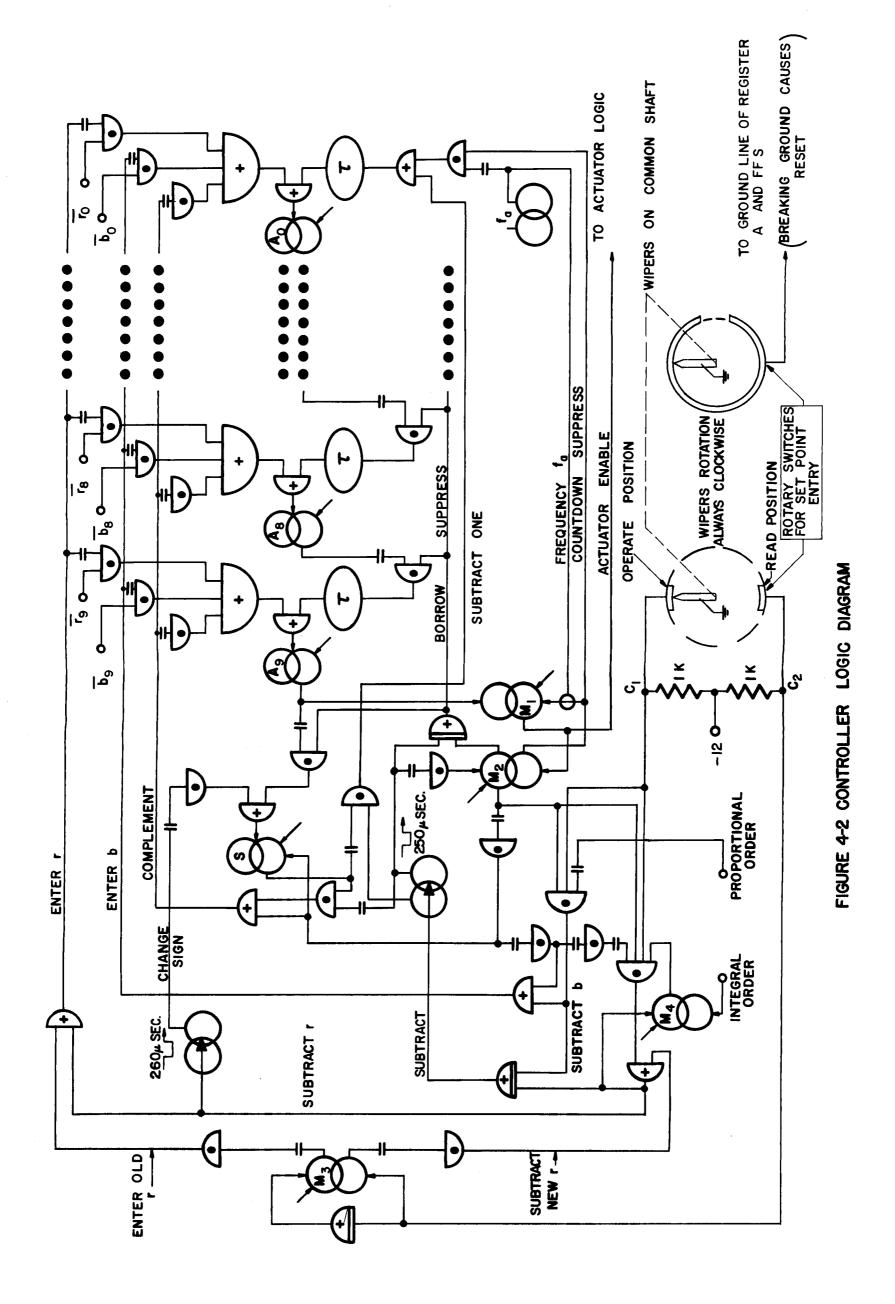

| 4. 2   | Controller Logic Diagram                                                               | 54   |

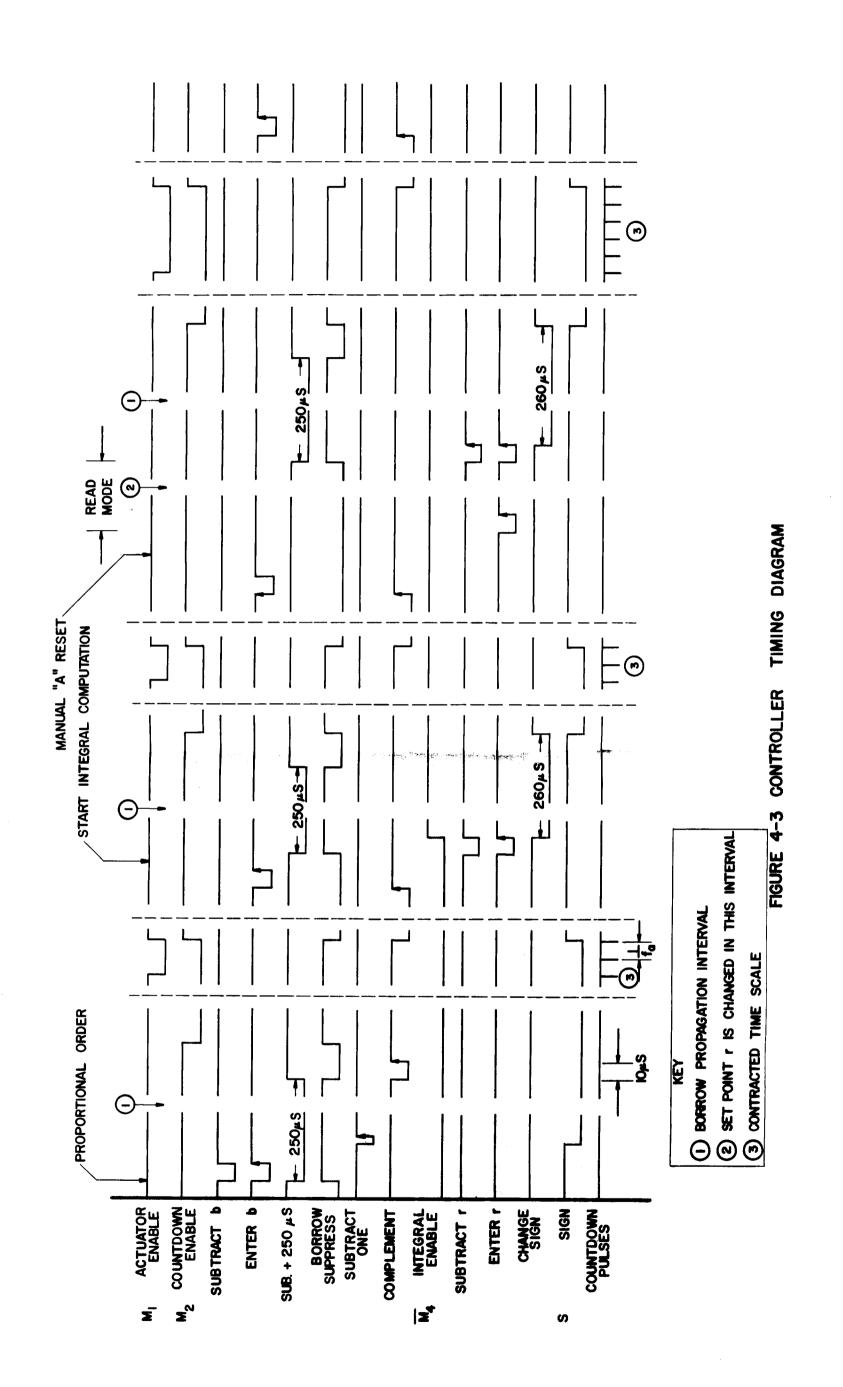

| 4.3    | Controller Timing Diagram                                                              | 61   |

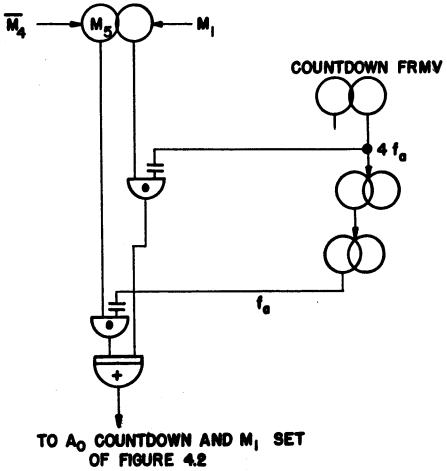

| 4.4    | Logic Required for Smoothed Integral Effect                                            | 66   |

| 4.5    | Controller                                                                             | 68   |

| 4.6    | Controlled System                                                                      | 69   |

| 5.1 | Actuator Speed Requirements Established by (5-9)                                                                        | 75  |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

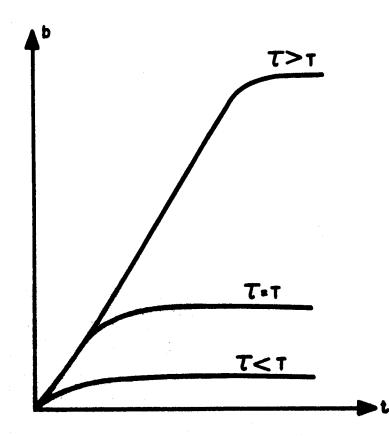

| 5.2 | Process Reaction Curves for Varying<br>Duration of Actuator Motion $\tau$ and Fixed<br>Value of Process Time Constant T | 82  |

| 6.1 | Sampled Data System with Sampling Interval $	au$                                                                        | 85  |

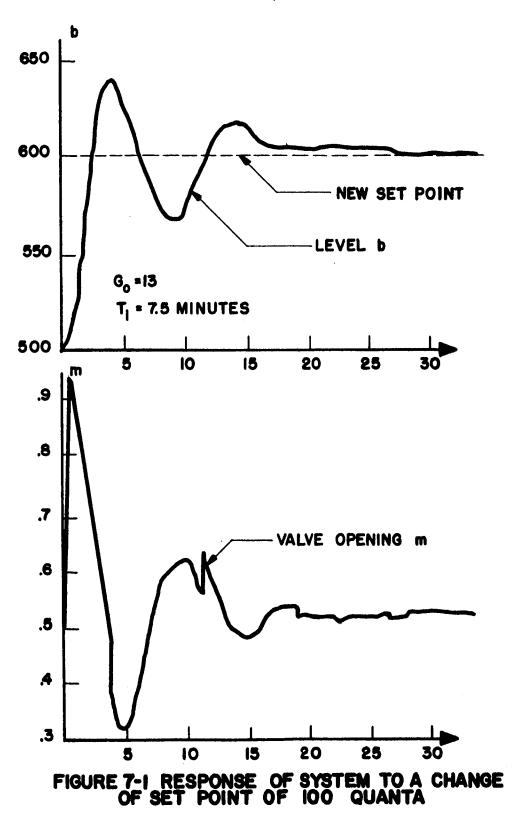

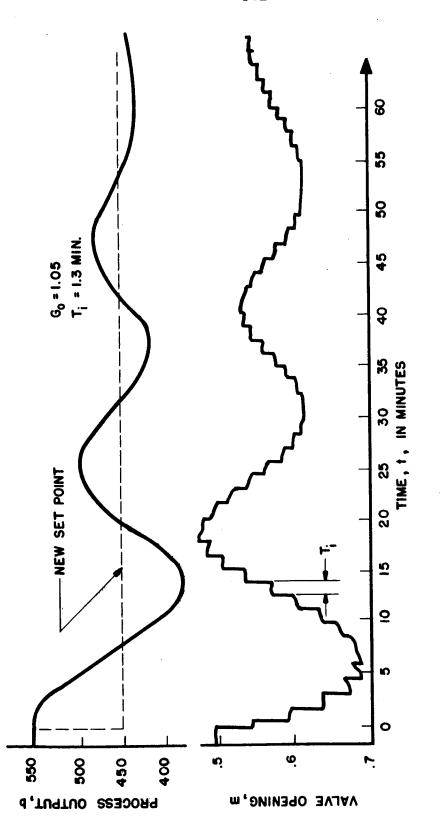

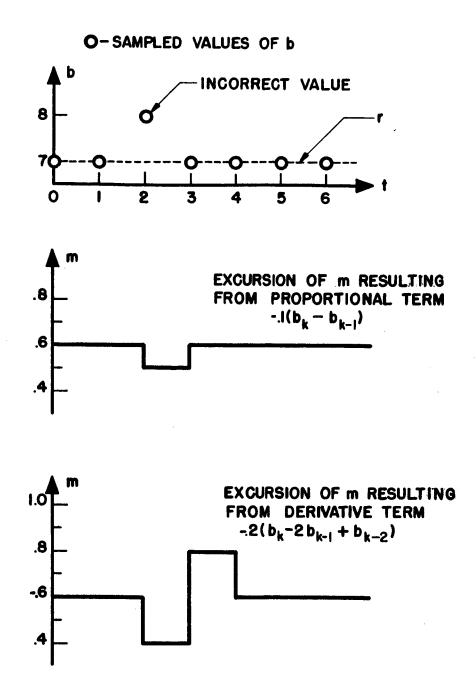

| 7.1 | Response of System to a Change of Set<br>Point of 100 Quanta                                                            | 92  |

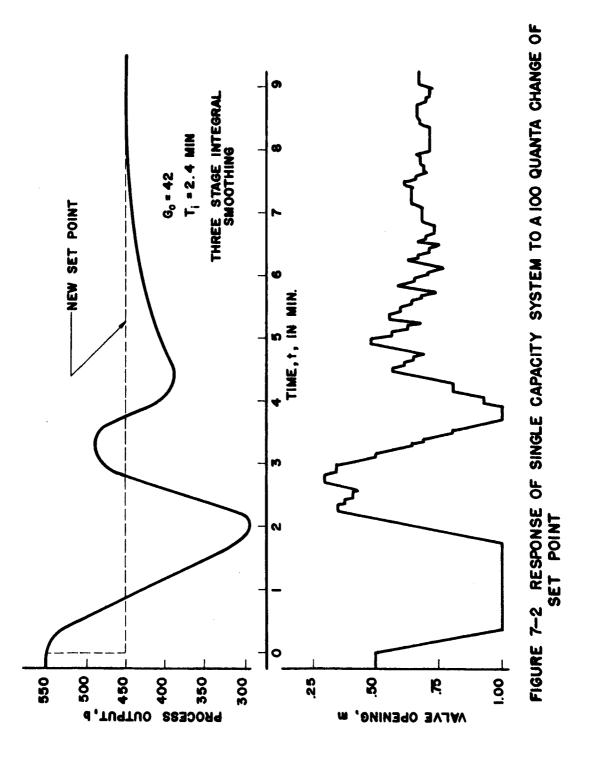

| 7.2 | Response of Single Capacity System to a 100 Quanta Change of Set Point                                                  | 95  |

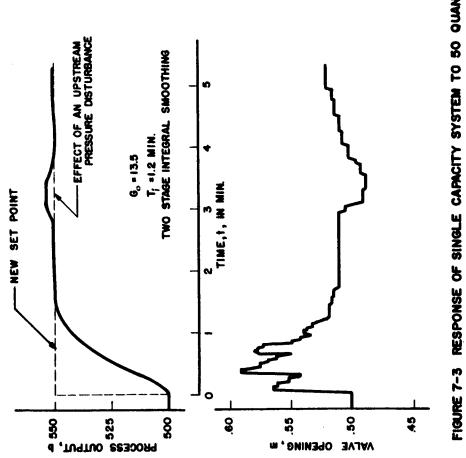

| 7.3 | Response of Single Capacity System to 50<br>Quanta Change of Set Point without use of<br>Read Mode                      | 97  |

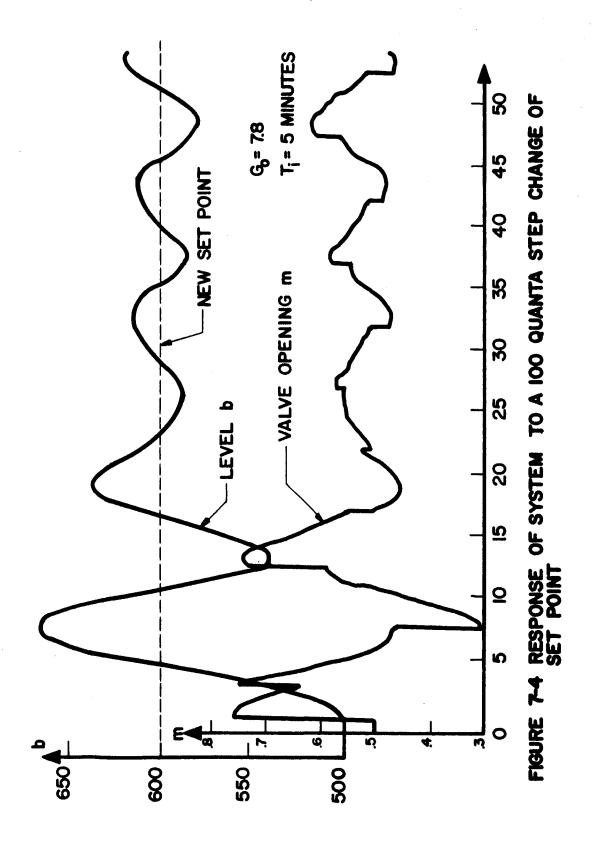

| 7.4 | Response of System to a 100 Quanta Step<br>Change of Set Point                                                          | 98  |

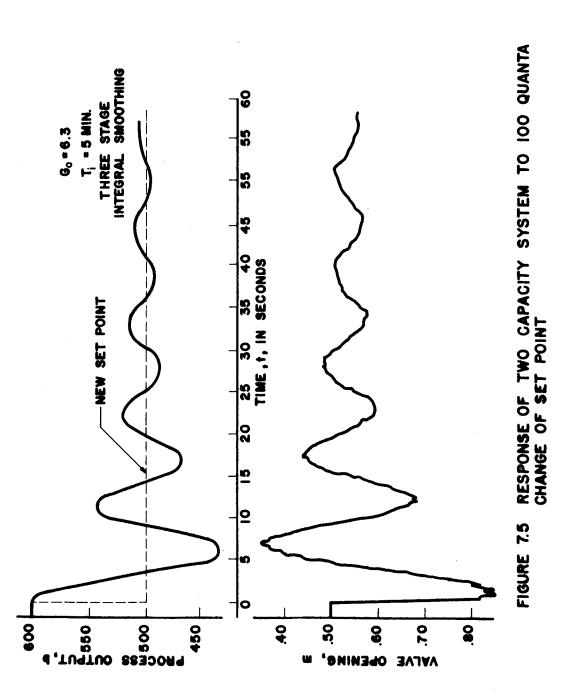

| 7.5 | Response of two Capacity System to 100<br>Quanta Change of Set Point                                                    | 101 |

| 7.6 | Response of Two Capacity System to a 100 Quanta Change of Set Point                                                     | 102 |

| A.1 | Open Loop Response of Process to 5.3 per-<br>cent Step Change in Input                                                  | 110 |

| B.1 | Effect of Noise on Manipulated Variable                                                                                 | 114 |

.

# LIST OF TABLES

.

•

| Table |                                    | Page |

|-------|------------------------------------|------|

| 3 - 1 | Priority of Computation            | 37   |

| 4 - 1 | Operations Performed by Controller | 47   |

| 4 - 2 | Operations Performed by Controller | 49   |

| 4 - 3 | Operations Performed by Controller | 51   |

| 6 - 1 | Conditions for Marginal Stability  | 89   |

.

.

### LIST OF SYMBOLS

Ì

T

}

| a <sub>i</sub>  | Coefficient of characteristic equation                 |

|-----------------|--------------------------------------------------------|

| А               | Binary number                                          |

| A <sub>i</sub>  | The i <sup>th</sup> bit of A                           |

| A <sub>kp</sub> | Defined by equation (3-18)                             |

| A <sub>kr</sub> | Defined by equation (3-19)                             |

| A <sub>ki</sub> | Defined by equation (3-20)                             |

| b               | A feedback variable                                    |

| b (s)           | Laplace transform of b                                 |

| <sup>b</sup> i  | The i <sup>th</sup> bit of b                           |

| <sup>b</sup> k  | The value of b at the k <sup>th</sup> sampling instant |

| Β <sup>μn</sup> | An event B delayed in time by n microseconds           |

| с               | Controlled variable                                    |

| d               | Measure of noise amplitude                             |

| е               | Natural logarithm base                                 |

| е               | Error signal                                           |

| ek              | Value of e at the k <sup>th</sup> sampling instant     |

| fa              | Countdown frequency applied to register A              |

| f <sub>i</sub>  | Frequency of integral mode sample order                |

$\mathbf{x}$

| f <sub>p</sub>             | Frequency of proportional mode sample order                                                 |

|----------------------------|---------------------------------------------------------------------------------------------|

| $f_s$                      | Frequency at which stepping motor is driven                                                 |

| FF                         | Flip flop                                                                                   |

| G <sub>0</sub>             | Open loop gain                                                                              |

| <sup>h</sup> 2             | Head of water in tank 2                                                                     |

| (J) <sub>\(\Delta\)r</sub> | Operation (J) to be performed when a change occurs in r                                     |

| (J) <sub>fi</sub>          | Operation (J) to be performed at a rate of $f_i$                                            |

| (J) <sub>fp</sub>          | Operation (J) to be performed at a rate of f $p$                                            |

| к                          | A Ziegler-Nichols reaction rate parameter                                                   |

| к <sub>1</sub>             | Open loop gain excluding controller                                                         |

| к <sub>f</sub>             | Gain of feedback transducer                                                                 |

| к <sub>р</sub>             | Proportional gain of controller                                                             |

| ĸ                          | Gain of valve                                                                               |

| k + δ +                    | An instant of time between $k + \delta$ and $k + 1$                                         |

| L                          | A Ziegler-Nichols reaction rate parameter                                                   |

| m                          | Valve position                                                                              |

| Δm <sub>k</sub>            | An increment of valve position computed immediately after taking the k <sup>th</sup> sample |

| m <sub>k</sub>             | Valve position after application of increment $\Delta m_k$                                  |

| M              | The i <sup>th</sup> control flip flop                  |

|----------------|--------------------------------------------------------|

| Ν              | An integer                                             |

| N              | A Ziegler-Nichols reaction rate parameter              |

| r              | Reference variable                                     |

| r <sub>i</sub> | The i <sup>th</sup> bit of r                           |

| r <sub>k</sub> | The value of r at the k <sup>th</sup> sampling instant |

| R              | Resistance of valve                                    |

| R              | A Ziegler-Nichols reaction rate parameter              |

| S              | Laplace operator                                       |

| S              | Sign of A                                              |

| t              | Time                                                   |

| Δt             | Sampling interval                                      |

| т              | Time constant                                          |

| т              | A Ziegler-Nichols reaction rate parameter              |

| т <sub>d</sub> | Derivative time of controller                          |

| т <sub>і</sub> | Integral time of controller                            |

| T <sub>n</sub> | Period of oscillation of closed loop                   |

| $T_{fs}$       | Time for full stroke of valve                          |

| u              | Load variable                                          |

| v                   | Amount of valve travel during a fixed period |

|---------------------|----------------------------------------------|

| w                   | A flow rate                                  |

| Z                   | z-transform operator                         |

| ° <sub>i</sub>      | 0 to 1 transition of binary variable "i"     |

| β <sub>i</sub>      | l to 0 transition of binary variable "i"     |

| δ                   | A fraction of the sampling interval          |

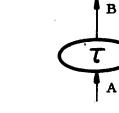

| au                  | A delay                                      |

| $\tau_{\mathbf{k}}$ | A time interval computed at sample instant k |

1 0

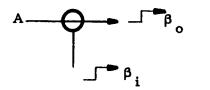

Flip Flop with Trigger Input

0 1

Flip Flop with Set and Reset Inputs

Diagonal Arrows are Manual Reset

One Shot Multivibrator

Free Running Multivibrator

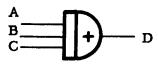

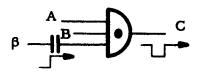

LOGICAL SYMBOLS USED

xiv

Steering Gate

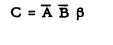

$\beta_{o} = \overline{A} \beta_{i}$

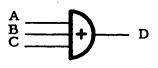

NOR Gate  $D = \overline{A + B + C}$

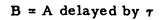

Delay

Gated Pulse Generator

OR Gate D = A + B + C

#### LOGICAL SYMBOLS USED

#### CHAPTER I

#### INTRODUCTION

Continuous analog controllers have come into widespread use for the automatic regulation of industrial processes. Their function is to compare the desired value of a process output with the measured output and to adjust the process input in accordance with the error. In a three mode controller the process input calculated by the controller is a combination of the present error, its rate of change and its time integral. Such a controller, containing proportional, integral and derivative modes, is commonly called a PID controller. All such controllers have, until recently, been analog devices.

Since World War II, the advances made in digital computers have steadily broadened the areas in which digital techniques can be profitably employed. The insensitivity of digital data to noise, both in transmission and manipulation, resulted in the use of digital control systems for aircraft and missiles. Machine tools were subjected to digital control in order to produce complicated parts economically and accurately. <sup>(1)</sup> In process control, starting in the 1950's, digital computers were used for data collection and reduction at large chemical and petroleum installations

in an effort to improve plant identification and operation. <sup>(2)</sup> In some cases the computer ordered new controller set points, but the direct controller function of valve control was not taken over by the digital computer. The public utilities also started using digital computers, but at first only to compute set points or load assignments. <sup>(3)</sup>

A number of people began about 1958 to investigate the possibility of direct digital control of many individual loops using a shared digital computer.<sup>(2)</sup> There were two major objectives. The first objective was, for the same quality of control, to reduce capital investment below that required for the analog controllers that would be displaced. The second objective was to improve control and to provide basic equipment compatible with higher level computer control functions such as interaction compensation, ratio, cascade, and optimization. The author took part in a feasibility study of a "first level" direct digital control computer at the Systems Research Center of Case under the direction of the late Professor D.P. Eckman in early 1962.<sup>(4)</sup> The study, sponsored by the Corning Glass Works and the Conoflow Corporation, included simulation of various algorithms and quantization techniques and included system planning for a computer capable of PI control of 96 loops, plus some additional

features. The study failed to show that the computer would be less expensive than 96 analog controllers, although the additional capabilities of the computer tended to justify any difference. No attempt was made to estimate reliability. In June 1962 Williams of Monsanto reported on the successful use of an RW 300 computer for direct digital control of 10 control loops, using a PI algorithm.<sup>(5)</sup> In November 1962 Yetter and Sanders of duPont reported on their studies of direct digital control.<sup>(6)</sup> They concluded that the digital time-shared system would show capital savings over electronic analog controllers for installations with at least 75-100 loops. They devoted considerable attention to the difficult problem of coupling the central high speed computing facility to the individual slow speed valve actuators. At the same time a report was published that Imperial Chemical Industries, Ltd. in England had been operating an ammonia plant for over a year using a Ferranti digital computer providing PID control.<sup>(7)</sup> In this case pneumatic actuators were used, requiring an auxiliary control loop for each manipulated variable just to maintain valve position.

Also about 1962 some single loop digital controllers appeared on the scene. Minnesota Mining and Mfg. announced a digital controller with only the I mode, and the French Lignes Télégraphiques et Téléphoniques

announced a PID controller that was part digital and part analog, designed to drive a truly digital actuator, a valve containing seven flow-weighted on-off valves. Development of digital process controllers in Russia resulted in several reports in 1962. (8, 9, 10, 11) They included consideration of single loop and multiloop controllers, both operating in the PI mode, and included also discussion of the extent to which sampling improves or degrades performance for the various controller structures proposed. Analog to digital conversion at the input of these controllers was apparently done after an analog error had been generated, thus avoiding one digital subtraction but at the same time losing the opportunity to use digital set point data. The point was made, however, that in the absence of digital sensors this procedure causes no loss of accuracy. Mergler, Peatman and Walker of the Case Digital Systems Engineering Group have developed single loop digital controllers, both PI and PID, in which a digital set point is used. (12, 13) The controller designed by the author makes use of the accumulator flip flops designed for Mergler's controller, but is distinguished from all of them by the means of adjustment of integral effect and by the simplifications made in the control algorithm.

The present trend, at least outside of the Soviet Union, is toward the use of a single time-shared computing unit for the control of many loops. Several such computers have been sold in the last two years. The main reason usually given for following the shared computer approach is that the only real justification for shifting to digital control is to get an improvement in control over analog controllers. The feeling seems to be that if any savings in equipment results from the switch it will be very small, so we must look for profit from higher level computer control functions. Since such functions can only be performed on a central computer with access to all loops, why not use that same computer for basic "first level" direct digital control? This is a compelling question, and one that no proponent of single loop controllers has tried to answer. My answer, however, is that there are two good reasons why first level control should not be performed by a shared computer.

The first reason for using single loop controllers instead of a shared computer is to obtain better reliability. Loss of control of a single loop can generally be corrected soon enough to avoid plant upset, especially since manual control can be used in the interim. The spectre that haunts potential digital control buyers is the prospect of simultaneous failure of all loops. Using the shared computer

of Figure 1.1, this could occur if either the A/D converter or the computer failed. When using separate controllers, as in Figure 1.2, only the failure of the A/D converter or of the power supply could cause catastrophic failure of all loops. Loops that had their own digital encoders on their transducers would have no common failure mode at all, if a stand-by power supply were provided. Preventive maintenance of individual controllers could be performed by replacing a controller with a spare and submitting it to whatever off-line checks might be useful. With a shared computer this would be possible only by having two entire duplicate computers. This has, in fact, been proposed by some to ensure reliability. Other measures for increasing computer reliability can be taken, but each costs money. It would seem less expensive to use the single loop controllers, provide a few spares, and ensure reliability at the critical shared part of the system by providing a duplicate input multiplexer and A/D converter. Whether such a procedure would in fact be less expensive depends on the cost of the single loop controller. The design used in this thesis uses 100 transistors for the PI modes, and might require 60 more for extension to PID control.

The second reason for using single loop controllers is to simplify the job of valve actuation. Referring to Figure 1.1

it is evident that multiplexing is necessary for both the input and output of the shared computer. The input transfer is relatively simple, since the digital feedback variable for each loop can be transferred in parallel in a matter of a few microseconds, and this needs to be done not more often than 10 times per second per loop. Transfer of the output orders to the actuators is a different sort of problem. If the output order is given only once, when the order is computed, then the actuator that receives the order must contain some sort of memory. The reason is that the actuators must move some specified distance in response to the order, and the time required for that motion is in many cases much longer than the time that the output multiplexer can afford to dwell on any one particular loop. The solutions to this problem can be broken into two classes; those in which the computer gives absolute actuator position orders and those in which it gives incremental actuator position orders.<sup>(6)</sup> One of the solutions proposed in the incremental category is to maintain one countdown register in the computer for each actuator. The position increment computed each sampling instant is put in this register and counted down to zero. The actuator is moved at a fixed rate in one direction or the other as long as the countdown is going on. This technique, explained more fully in Chapter III, can also

be used with single loop controllers. The advantage in doing so is that no output multiplexing is required, rather a given countdown register is simply wired to a given actuator. This is the technique chosen for the design proposed here, and is the one shown in Figure 1.2.

If the single loop controller approach does relieve the problems of reliability and actuator control, we still must show compatibility with higher level control computers. The plan is to require that a separate, shared computer perform all functions except the basic PI or PID control algorithm. It would have access to the shared A/D converter for its inputs, and would send its incremental output orders directly to the various single loop controllers, as shown in Figure 1.2. The controllers would apply these increments to their actuators, then return to their normal control duties until the next higher level control order comes along. Thus the higher level control computer is simplified by the fact that its output orders can be administered by the single loop controllers. Furthermore, its reliability requirements could be relaxed, since its failure would not effect first level control. If higher level control is not needed, the computer can be omitted and the user need pay only for what he uses. The detailed means of communications between the first level con-

trollers and the higher level computer will be covered in later chapters and in Appendix C. Chapters I and II are intended to provide background and motivation for the sections that follow on the actual design of the single loop digital controller.

ļ

#### CHAPTER II

#### NATURE OF THE PROCESS CONTROL PROBLEM

#### Process, Transducer and Actuator

The block diagram of Figure 2.1 identifies the elements of an industrial process control loop. The controller is provided in order to maintain the feedback variable b, an indication of the controlled variable c, equal to the reference variable or set point, r. There are two characteristics that typify industrial process control loops and distinguish them from servomechanism control loops. The first is that for industrial processes, especially continuous ones, the reference variable r is maintained at a constant value for long periods of time, so that the controller's principal job is to maintain the controlled variable at a constant value in the face of load changes or disturbances, u. This is in strong contrast to the duty cycle of a servomechanism, which is asked to produce a motion corresponding to an often varying reference signal r. The second characteristic of industrial processes is that the dynamic lag of the actuator is usually negligible in comparison to the lag inherent in the transducer or in the process being controlled. In flow loops, which may account for 40 percent of process loops, <sup>(6)</sup> the process time constant is usually negligible compared to that of the transducer, but where it is important one can generally select a valve actuator with quick

enough response to justify neglecting its dynamics in the control loop. Chapter III demonstrates how these two traits can permit a considerable simplification to be realized in the design of a digital process controller and later chapters establish guidelines showing the range of control loop characteristics for which this simplified control algorithm is effective.

#### Analog Controller and Typical Process

Figure 2.2 shows a process consisting of two tanks in cascade. The level of the lower tank is to be controlled by manipulation of input flow to the upper tank in the face of any arbitrary disturbance. Although such a system is not a common industrial process, its dynamic response is similar to that of thermal processes.<sup>(14)</sup> This liquid level process is the one actually used in this research. It permitted great flexibility in testing, for two reasons. First, it was possible, when desired, to bypass tank 1, directing flow  $w_1$  directly into tank 2, leaving only a single capacity system, with an attendant increase in response speed. Second, the valve actuator used was an electric stepping motor, which could be run at any speed up to 145 pulses per second, giving a time for full stroke of the valve of any value down to 32 seconds. It is shown in Chapter V that the ratio of time for full valve stroke to the dominant time constant of the system is an important parameter in

# FIGURE 2-2 SCHEMATIC OF WATER LEVEL CONTROL SYSTEM

predicting the effectiveness of the control technique described in this paper.

1

When a process like that shown in Figure 2.2 is controlled by an analog controller, the loop can be described in block diagram form by Figure 2.3, which gives the form of the transfer functions of the various elements of this analog control loop.

Analog controllers are most commonly available with either two or three "modes" of control. The LaPlace transformed output of a three mode analog controller is given by the equation

$$m(s) = K_{p} \left[ \frac{1}{T_{i}s} + 1 + T_{d}s \right] e(s)$$

(2-1)

The three modes are called respectively integral, proportional and derivative. Integral action provides a corrective ramp output from the controller for a steady error input and is included to reduce steady state error to zero. Proportional action provides a ramp output from the controller in a direction to stop the motion of an input error ramp. Derivative action provides an impulse output signal for a step input error signal, and, because of its stabilizing effect, is useful for permitting higher proportional and integral gains to be used.

Figure 2.4 illustrates how each of the three control modes contributes to produce controller output m.<sup>(14)</sup> The upper plot shows an arbitrary ramp error signal starting from zero at time 1. At time zero m has an arbitrary initial value of  $M_{0} = 1$ . For such a test the controller is understood to be running open loop, that is without the feedback connection shown completed in Figure 2.1. The proportional action, the lower dotted line, is simply  $K_p e$  added to  $M_{o}$ . In this case  $K_{p}$  is one. Therefore, the proportional part of m follows e exactly, in a direction that would tend to reduce error in a closed loop. Derivative action, shown in the figure with a value of 2, adds an increment of m equal to  $T_d$  multiplied by the slope of the error curve. This provides a lead action, yielding a given value of m a time  $T_d$  earlier than proportional action alone would have produced it. The integral mode adds a further increment of m. In the Figure  $T_i = 10$ , so that at any time the integral effect is equal to one tenth of the area under the error curve preceeding that time. The inverse of T<sub>i</sub> is called "reset rate" and is defined as the number of times per minute that the proportional action is duplicated by the integral action.

FIGURE 2-4 RESPONSE OF THE THREE CONTROL MODES TO A RAMP ERROR INPUT

#### CHAPTER III

#### DIGITAL CONTROL ALGORITHM

The aim of this research was to design a simple digital controller that would have roughly the same proportional and integral actions as the usual two mode, proportional plus integral analog controller, yet retain the inherent accuracy, resolution and flexibility of digital computation. In order to be usable on a wide variety of processes it was necessary to furnish the same wide range of gain and integral time that is provided on analog controllers. These requirements could not be considered, however, until it was decided what sort of digital input data the controller would have to work with, what sort of valve actuator the controller would drive, and how the controller's output would control the actuator. Once these decisions are made it is possible to develop a control algorithm for a digital controller using sampled data.

#### Preliminary System Assumptions

Controller Input Data:

The reference variable or set point, r, is provided in parallel binary form from a set of 10 on-off switches. The feedback variable, b, is available in 10 bit parallel form, either continuously from a digital encoder or upon command with negligible delay from an analog-to-digital converter. 20 Control parameters  $K_p$  and  $T_i$  are discussed later in this chapter.

#### Valve Actuator:

Analog controllers usually produce an output, m, which is a valve position order. The valve actuator is designed to open to a position proportional to m. Since the analog controller works on a continuous basis it is a simple matter for it to provide the continuous signal m for valve positioning. The output of a digital controller, however, must be converted to analog form before it can be used for actuator control. If the controller output is m, there are three choices open for actuator control:

- 1. Between controller sampling times the digital value m could be held in a memory register which would continuously be the input for a digital-to-analog converter whose output would then drive an analog actuator. This scheme is uneconomical because of the large expense for a DA converter for each manipulated variable.

- 2. After a new sample is taken and a new value of m is calculated, m could be converted to an analog signal which would then be stored by an analog memory device, a zero-order hold, until a new value of m is calculated. The stored analog value of m would drive the analog actuator. This technique has the advantage of requiring only a single DA converter for a number of control loops, but would still be complicated by the necessity for multiplexing the input and output of the converter between the various controller outputs and analog memory inputs. Furthermore, inexpensive analog memory units are subject to drift.

3. A combination of the first two methods could be used by converting m to an analog signal by a multiplexed DA converter and holding the converter on this value of m until the actuator had reached its new ordered position. Then the actuator could be mechanically or electrically locked in this position until the next sample time and the DA converter would be free for use on another controller output and actuator. If one chose an actuator designed so that the load could never drive the actuator, then no locking of the actuator would be necessary. This technique has the disadvantage of still requiring a DA converter, and it would not be possible to use it for many loops, because the converter must dwell on a given loop as long as the actuator of that loop is moving.

None of the above three schemes is well suited for actuator control, especially if separate digital controllers are used for each loop. It is considerably simpler, both from the point of view of actuator control and simplification of controller logic, to use an incremental scheme. In all three methods above the end effect of the DA conversion, actuation and holding was to move the actuator some increment  $\Delta m_{\rm b}$  where

$$\Delta m_k = m_k - m_{k-1}$$

(3-1)

and where  $m_k$  is defined as the value of m resulting from the computation following the k<sup>th</sup> sample. If we use an actuator capable of maintaining its last position, as discussed in method three above, then it is not necessary to compute  $m_k$  after each sample, but only  $\Delta m_k$ . This technique is what is meant by using an incremental scheme. The controller is designed to compute an increment of valve motion,  $\Delta m_k$ , and to apply this correction to a valve capable of maintaining its last position when the actuation signal is removed. Such an actuator can be called an incremental actuator, whether it be a stepping motor or perhaps a synchronous motor capable of moving a distance proportional to the time it is turned on, even if for only a small fraction of a second. The final preliminary design assumption is then, that the digital controller is to operate an incremental valve actuator.

## Derivation of the Three Mode Incremental Control Algorithm

Let  $\Delta t$  = time interval between samples For  $\Delta t$  small and quantum size small:

$$\frac{\Delta m_k}{\Delta t} \cong \frac{dm}{dt}$$

(3-2)

From equation (2-1):

$$\frac{\mathrm{dm}}{\mathrm{dt}} = K_{\mathrm{p}} \left[ \frac{1}{\mathrm{T}_{\mathrm{i}}} \mathrm{e} + \frac{\mathrm{de}}{\mathrm{dt}} + \mathrm{T}_{\mathrm{d}} \frac{\mathrm{d}^{2} \mathrm{e}}{\mathrm{dt}^{2}} \right]$$

(3-3)

Converting the error terms of (3-3) to their sampled equivalents, and combining (3-2) and (3-3):

$$\frac{\Delta m_k}{\Delta t} = K_p \left[ \frac{1}{T_i} e_k + \frac{e_k - e_{k-1}}{\Delta t} + T_d \frac{\frac{e_k - e_{k-1}}{\Delta t}}{\Delta t} - \frac{\frac{e_{k-1} - e_{k-2}}{\Delta t}}{(3-4)} \right]$$

where the substitution of  $e_k$  for e comes from using the rectangular approximation for e.

Solving (3-4) for

$$\Delta m_k$$

:

$$\Delta m_k = K_p \left[ \frac{\Delta t}{T_i} e_k + (e_k - e_{k-1}) + \frac{T_d}{\Delta t} (e_k - 2e_{k-1} + e_{k-2}) \right]$$

(3-5)

Figure 3.1 illustrates how this approximation to the continuous algorithm looks for finite  $\Delta t$ . At the first three sample instants the error e is zero and manipulated variable m remains at a constant value, arbitrarily chosen as one. A step change in e occurs between samples 2 and 3, but there can be no response at the output of the controller until sample 3 occurs. The controller output shown in the figure will be exactly the same whether the step change in e occurs at 2.01 time units or at 2.99. This is one reason for making the sampling interval as small as possible, to avoid adding unnecessary lag to the control loop. The response shown was computed using the following parameters:

$\Delta t = 1$   $K_p = 1$   $T_i = 4$   $T_d = 2$  (3-6) The proportional effect is virtually the same as what would be produced by an analog controller, differing only by the sampling delay. The integral effect is a staircase instead of a ramp, and the derivative action is an impulse of the

SAMPLING INSTANTS AT INTEGRAL UNITS OF TIME

# FIGURE 3-1 OUTPUT M OF SAMPLED THREE MODE DIGITAL CONTROLLER IN RESPONSE TO A STEP ERROR INPUT

proper area that has been broadened in duration and shortened in amplitude. This is not a great disadvantage, because it reduces the amount of non-linearity in response resulting from value saturation, if  $\Delta t$  is properly chosen.

### Functions of the Two Mode Control Algorithm

Because two mode, proportional plus integral, analog controllers are so widely used and so many users and vendors question the value of the derivative mode it was decided to limit this project to the design of a two mode controller. Therefore this paper will henceforth be concerned only with the two modes of control, allowing  $T_d$  of preceeding sections to go to zero. The only exception is in Chapter VIII, in which it is suggested that the technique developed later in this chapter could easily be extended to provide the third mode.

The two mode digital control algorithm is taken directly from (3-5), setting  $T_d = 0$ :

$$\Delta m_{k} = K_{p} \left[ \frac{\Delta t}{T_{i}} e_{k} + (e_{k} - e_{k-1}) \right]$$

(3-7)

By our nomenclature from Figure 2.3,

$\mathbf{e} = \mathbf{r} - \mathbf{b} \tag{3-8}$

Hence, in sampled form:

$$\mathbf{e}_{\mathbf{k}} = \mathbf{r}_{\mathbf{k}} - \mathbf{b}_{\mathbf{k}} \tag{3-9}$$

Substituting (3-9) into (3-7):

$$\Delta m_{k} = K_{p} \left[ \frac{\Delta t}{T_{i}} (r_{k} - b_{k}) + (r_{k} - b_{k}) - (r_{k-1} - b_{k-1}) \right] \quad (3-10)$$

Rearranging:

$$\Delta m_{k} = K_{p} \left[ (b_{k-1} - b_{k}) - (r_{k-1} - r_{k}) - \frac{\Delta t}{T_{i}} (b_{k} - r_{k}) \right] \quad (3-11)$$

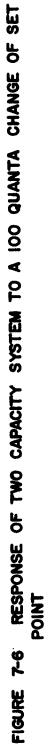

The first two terms in (3-11) make up the proportional part, and the third represents the integral. The second term,  $(r_{k-1} - r_k)$  will be non-zero only when there is a change in reference variable, r. There is no need for computing that term at any other time. We can rewrite (3-11) with a subscript  $\Delta r$  on the second term to indicate that that computation should only be performed when there is a change in r.

$$\Delta m_{k} = K_{p} \left[ (b_{k-1} - b_{k}) - (r_{k-1} - r_{k})_{\Delta r} - \frac{\Delta t}{T_{i}} (b_{k} - r_{k}) \right] (3-12)$$

The term  $(r_{k-1} - r_k)_{\Delta r}$  is now understood to mean the difference between the new value of r subtracted from the old value of r.

The first term of (3-12) represents change in the controlled variable between sampling instants k-l and k. As long as the reference variable r remains constant this first term is all that is required to give the incremental proportional effect.

To review the meaning of (3-12) recall that (3-7) was derived from the analog control equation (2-1). Based on the rectangular approximation for e and with very small  $\Delta t$ , (3-7) is the exact incremental equivalent of (2-1), minus the omitted derivative mode. Further, in going from (3-7) no approximations were made, since only differences equal to zero were left out. A digital controller that implements (3-12) will then provide precise proportional plus integral control, so called PI control, if sampling interval  $\Delta t$  is very small relative to the dominant time constant of the loop, and if quanta size is small enough to approximate analog resolution. The first condition, high sampling rate, can be fulfilled if desired, but it should be kept as low as possible while still retaining good control in order to reduce demands on the analog to digital converter to a minimum. The second condition, small quanta size, must be met in order to match the resolution capabilities of the analog transducer chosen.

## Controller Gain Adjustment by Frequency Manipulation

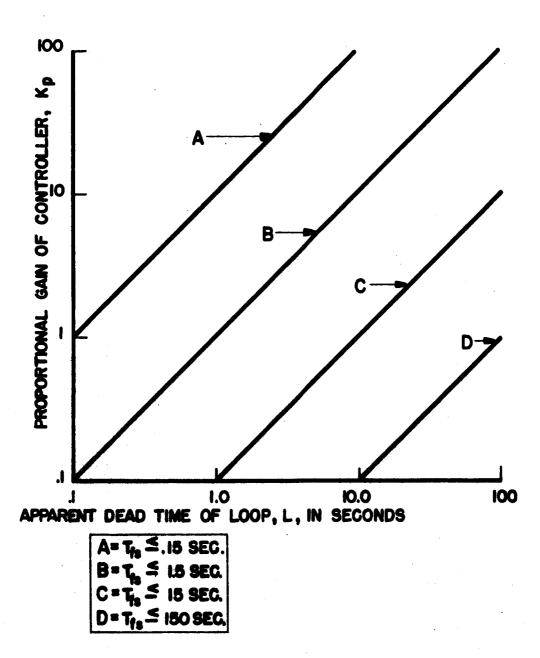

An important part of the controller design problem is finding a good way of providing a wide choice of values for

the gain parameters  $K_p$  and  $\Delta t/T_i$  in (3-12). In order for the controller to be applicable to a variety of processes these parameters should be variable over a range of at least 100 to 1. Analog controllers typically provide  $K_p$ from .5 to 50 and  $T_i$  from .1 minutes to 50 minutes, with other ranges available by field change.

Proportional Gain K

K<sub>n</sub>, although called only proportional gain, also acts as a gain coefficient on the integral term. It is therefore possible in implementing the controller to perform the multiplication just as indicated in (3-12), that is to wait until the sum inside the brackets is formed and then apply  $K_{p}$  to that sum. The easiest way to accomplish this multiplication is at the interface between controller and actuator. The technique chosen for digital to analog conversion is to convert  $\Delta m_k$  to a period of time  $\tau_k$  during which the actuator moves at full speed in one direction or the other depending upon the sign S of  $\Delta m_k$ . In the experimental loop used, shown in Figures 2.2 and 3.2, the actuator is a stepping motor, driven at a speed of f steps per second. At this speed the actuator requires T<sub>fs</sub> seconds to move full stroke. The number actually calculated in the subtracter is  $\Delta m_k / K_p$ . This number, called A<sub>k</sub> in Figure 3.2, is then converted to a time period by counting it down to zero at a frequency of f pulses per second. If full stroke of the valve is covered by m ranging from zero to one, then

$\Delta m_k$  is finally represented in terms of loop parameters by

$$\Delta m_{k} = \frac{A_{k}}{f_{a} T_{fs}} = \frac{\Delta m_{k}}{K_{p} f_{a} T_{fs}}$$

(3-13)

Then for this method of DA conversion:

$$K_{p} = \frac{1}{f_{a} T_{fs}}$$

(3-14)

and there are now two ways to vary  $K_p$  for a given value, process and encoder. Varying  $T_{fs}$  is the first way, but it would never be used because the tendency is to use the fastest value actuator that is economically available. All that is required by the other method is to provide a variable frequency pulse generator for  $f_a$ . In the controller tested the pulse generator used is a free-running multivibrator with a frequency range of 5 to 100 cps. Higher frequencies and hence lower values of gain  $K_p$  are available simply by changing a pair of capacitors.

Integral Time T;

Implementation of equation (3-12) requires forming the difference between the binary numbers  $b_k$  and  $r_k$  and multiplying that difference by a number equal to  $\Delta t/T_i$ , the sampling interval divided by a suitable value of the so-called integral time that was used on the analog controller. There are numerous ways to perform multiplication in a

digital device, but all of them require a considerable amount of hardware. Because the other two terms in (3-12) require no multiplication and because the multiplication by  $K_p$  of the expression in brackets can be performed in the DA conversion, a method was sought to avoid the necessity for multiplying the integral term by the coefficient  $\Delta t/T_i$ . The simplest way to do this is to let that coefficient be always equal to one. Thus far the only restriction on  $\Delta t$  has been that it should be small relative to the dominant system time constant. Letting  $\Delta t/T_i$  go to one would then dictate what  $\Delta t$  would have to be for a  $T_i$  suitable for the system. The criterion would be:

$\Delta t = T_{i} \qquad (3-15)$

Using this sampling interval, however, the condition that  $\Delta t$  be small relative to the dominant time constant would no longer be satisfied, because the value of  $T_i$  used in process control is often equal to or greater than the dominant time constant of the system.\* The only basis for this condition of small  $\Delta t$  is, however, the desire to keep the digital controller response as similar as possible to analog controller response. This paper will show that in fact satisfactory control is possible even when the simplification

Selection of K and T for a given process is discussed in Appendix A and references

of (3-15) is made, provided that the proportional term of the control algorithm is sampled and computed at a rate which is different from and sufficiently higher than the integral rate. The reason it is necessary to sample the proportional part often while the integral part can be sampled only every T; is concerned with system stability. The only function of the integral mode is to eliminate steady state error, whereas the proportional mode is a stabilizing action, acting to counteract change in the controlled variable. It is important that no extra lag be introduced in the determination of this rate of change, since in well tuned control loops the proportional mode generally causes the major share of manipulated variable motion. A sampling lag on the order of T<sub>i</sub> introduced in the proportional effect would act like an effective dead time and would decrease phase margin, requiring a much reduced proportional gain and hence a reduced speed of response for a given degree of stability. If this large sampling lag is introduced only into the integral effect, a certain reduction is required in integral gain, but the proportional gain and effect can remain nearly unchanged. Chapter VII discusses the extent to which this reasoning was borne out in experimental tests, and Chapter VIII proposes a method for providing a smoother integral effect without abandoning the desired feature of gain adjustment by frequency manipulation. The effect upon stability of various sampling

schemes is discussed further in Chapter VI. Appendix B evaluates the effect of noise in feedback signal b on the different control modes as a function of the sampling rate used in the different parts of the control algorithm.

## Priority Allocation and Computation Frequency of Algorithm Terms

Applying (3-15) to (3-12):

$$\Delta m_{k} = K_{p} \left[ (b_{k-1} - b_{k})_{f_{p}} - (r_{k-1} - r_{k})_{\Delta r} - (b_{k} - r_{k})_{f_{i}} \right]$$

(3-16)

where  $f_i = \frac{1}{T_i}$

and  $(b_k - r_k)_{f_i}$  means that this "integral" term is computed at a rate of  $f_i^i$ . The first term is computed at a higher rate  $f_p$ , while the second term is computed only when a change occurs in set point r. Since these terms are computed at different times it is no longer meaningful to keep them together in one equation, since the contributions to  $\Delta m$  do not all occur together at a given instant k. Therefore a new notation is introduced to describe the actual separate operations performed in the controller. In a previous section the binary output of the controller was defined as  $A_k$ , with  $A_k = \Delta m_k/K_p$ . Then

$$A_{k} = (b_{k-1} - b_{k})_{f_{p}} - (r_{k-1} - r_{k})_{\Delta r} - (b_{k} - r_{k})_{f_{i}}$$

(3-17)

Because the three components of A<sub>k</sub> are generated at different times, a separate expression is defined for each term:

Proportional terms:

$$A_{kp} = (b_{k-1} - b_k)_{f_p}$$

(3-18)

$$A_{kr} = -(r_{k-1} - r_k)_{\Delta r}$$

(3-19)

Integral term:

$$A_{ki} = -(b_k - r_k)_{f_i}$$

(3-20)

In normal operation set point r is a constant and A does krnot need to be computed.  $A_{kp}$  and  $A_{ki}$  are then sufficient to generate the corrections required for two mode PI control. When a change in set point r is ordered,  $A_{kr}$ of (3-19) must of course be computed and applied as a correction to the valve. While this is being done, however, there is no reason why A<sub>kp</sub> and A<sub>ki</sub> must continue to be computed since the process is most likely very near steady state, making A<sub>kp</sub> and A<sub>ki</sub> very small compared to A<sub>kr</sub>. After a change in r is initiated by application of the increment A<sub>kr</sub> to the actuator the other two terms of the control algorithm can again be computed in their usual sequence. When the algorithm is broken up in this way the controller has two distinct modes of operation. In the "Operate" mode the controller computes A<sub>kp</sub> and A<sub>ki</sub>, representing both proportional and integral effects for con-

stant r. Whenever r is changed, but at no other time, the controller is shifted to the "Read" mode to enable it to compute and apply  $A_{kr}$ . The expression "Read" indicates that a new r is to be read in. The controller returns to the Operate mode as soon as this computation is performed. It is evident that the Read mode has the higher priority, since whenever we wish to make a change in set point it is important to get the process started in that direction. Once it is started by the  $A_{kr}$  term there is time enough to return to the Operate mode for proper transient response.

The motivation for dividing up the duties of the controller is to permit a small amount of logic to perform several functions. We have seen that the Read and Operate modes are mutually exclusive. It is therefore possible to design the controller so that the logic that performs (3-18) and (3-20) in the Operate mode also performs (3-19) in the Read mode. This is especially easy since all three equations are simple subtractions. In the Operate mode equations (3-18) and (3-20) must be performed, but at different rates. It has been shown that for stability the sampling rate  $f_i$  for the integral term (3-20) must be a small fraction of the rate  $f_p$  for the proportional term. It is therefore possible to perform the integral computation during the interval between successive proportional

computations without causing any significant variation in the effective value of  $f_i$ . Thus, the two terms used while the controller is in the Operate mode can be computed and applied to the actuator successively, making it possible to perform both subtraction operations in the same register without an intermediate storage register. The sequence of events chosen for implementation of the controller is this: During Operate mode proceed with computation of the proportional term (3-18) at frequency  $f_p$ . When an integral order occurs, calling for execution of (3-20), wait until the next proportional computation (3-18) is completed, then immediately perform the subtraction (3-20). When (3-20) is complete, return to the proportional computation (3-18).

The following table summarizes the priority of the three computations, and the conditions that must be satisfied before they are carried out:

|                 | Conditions that must be met to enable computation of respective term |                 |                              |                          |  |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------|-----------------|------------------------------|--------------------------|--|--|--|--|--|--|--|

| Term            | Computation<br>Ordered                                               | Operate<br>Mode | Countdown not<br>in progress | Countdown just completed |  |  |  |  |  |  |  |

| Akr             | x                                                                    |                 |                              |                          |  |  |  |  |  |  |  |

| A <sub>kp</sub> | x                                                                    | x               | x                            |                          |  |  |  |  |  |  |  |

| Aki             | x                                                                    | x               | x                            | x                        |  |  |  |  |  |  |  |

Table 3-1

Figure 3.3 shows the valve position m as a function of time resulting from an arbitrary feedback signal b. It happens that the two integral corrections shown have signs opposite to the signs of the proportional corrections just preceeding them. The figure demonstrates how the addition of the proportional and integral effects is performed by the actuator itself, rather than by the controller. This same general principal was used in the controllers designed by Walker<sup>(12)</sup> and Peatman<sup>(13)</sup>, but in both those cases the adjustment of T<sub>i</sub> was accomplished by providing variable gain within the controller rather than variable integral sampling rate.

### Intermediate Storage Requirements

ł

Before starting the detailed logic design of the controller it is necessary to determine what intermediate storage capability is required.

In the Read mode the solution of (3-19) requires storage of the old value of r,  $r_{k-1}$ . It is sufficient to enter  $r_{k-1}$ into the subtraction register as soon as the controller is put into the Read mode. Then the switches representing r can be changed and the new value of r subtracted from the old. Thus no auxiliary storage is required, outside of the r switches and the subtraction register. The factor

that makes this savings possible is the restriction that no set point changes be made without first putting the controller into the Read mode.

In the Operate mode the solution of the integral term (3-20) requires the subtraction of present r from present b. No intermediate storage is required, but b must be entered into the subtraction register just before the subtraction is performed. This is done immediately after applying the proportional term, (3-18), to the actuator. (3-18) is the difference  $b_{k-1} - b_k$ , which obviously does require intermediate storage. According to the equation, the value of b, that is used as the subtrahend in the calculation of A would be retained and would then be used as the minuend in the computation of  $A_{(k+1)p}$ . To retain b, would require an extra memory register. This extra register can be avoided, however, by making a further approximation. In Chapter II it was pointed out that in process control the actuator time constant is usually small compared to that of the process. This statement is further developed in Chapter V to show that when using a constant speed incremental actuator the absolute average speed the actuator requires to maintain good control is small compared to its full speed capability. This is another way of saying that the average time required for

actuation during a sampling interval is small compared to the length of that sampling interval. This is evident in Figure 3.3, which is similar to test results obtained with the process of Figure 2.2. If we now define  $\delta$  as the fraction of the sampling interval required for computation and actuation we can, under certain conditions, make the approximation

$$b_{k} \stackrel{\simeq}{=} b_{k+\delta}$$

(3-21)

Using  $b_{k-1+\delta}$  instead of  $b_{k-1}$  in (3-18) means that at a sampling instant k the computation (3-18) can be made without retaining the value of  $b_k$ . At time  $k + \delta$ , immediately after  $A_{kp}$  has been applied to the actuator, b is resampled and stored in the subtraction register where it is ready for the next computation. If an integral sample has been ordered (3-20) is performed as soon as  $b_{k+\delta}$ is entered, since  $b_{k+\delta}$  is then the present value of b and can serve as the minuend. At time  $k + 2\delta$ , after  $A_{ki}$ has been applied to the actuator, b is again entered into the register where it serves as the minuend  $b_k$  for the next proportional term (3-18).  $\delta$  is understood to depend upon the magnitude of the difference term  $A_k$  and the countdown rate  $f_a$ .

The conditions under which (3-21) is valid are discussed in Chapter V and include consideration of the amount of noise on signal b, and the average value of  $\delta$ .

#### Summary

Data input and output requirements for a sampled digital controller were stated, including the decision to use 10 bit parallel binary input variables and an incremental output order in the form of a pulse width for the control of a constant speed actuator such as a synchronous motor or stepping motor. The continuous three mode control algorithm was converted to incremental, sampled form, then for the two most commonly used modes, proportional plus integral, the incremental equation was divided into three component parts well suited for serial computation in shared logic. The two salient characteristics of process control loops listed in Chapter II were the basis of a heuristic justification of the serial computation scheme, the method of gain adjustment by varying sampling rate and the approximation made in a first difference term to eliminate the need for an auxiliary storage register.

## CHAPTER IV DETAILED DESIGN OF THE CONTROLLER

The preceeding chapter has provided the sampled control algorithm roughly corresponding to continuous proportional plus integral control and has described how this algorithm can be implemented in a digital device without recourse to any electronic storage register beyond the basic subtraction register. In this chapter the steps necessary to perform the algorithm are tabulated and the digital logic built to implement those steps is described.

## Sequence of Controller Operations

The controller must compute the three differences of equations (3-18), (3-19) and (3-20), each at a different time. (3-18) and (3-20) are computed while the controller is in its Operate mode, whereas (3-19) is computed only once each time the set point r is changed, when the controller is momentarily put into the Read mode. Grouping these three terms by controller modes :

Computed during Operate mode :

$$A_{kp} = (b_{k-1} + \delta - b_k)f_p \qquad (4-1)$$

$$A_{ki} = -(b_k - r_k)_{f_i}$$

(4-2)

Computed during Read mode :

ļ

$$A_{kr} = -(r_{k-1} - r_k)\Delta r \qquad (4-3)$$

In accordance with the assumption made in Chapter III  $b_{k-1+\delta}$  is used in (4-1) instead of  $b_{k-1}$ . The serial computation scheme proposed permits (4-2) to be performed immediately following any (4-1) computation.

It was shown in Chapter III that it would be possible to perform the necessary computations with a controller of the structure shown in figure 4.1. The only electronic memory register of the controller is the accumulator A, which consists of a sign flip flop S and 10 data flip flops, all of which are trigger elements with sufficient input gating to permit a minuend to be entered into the register. Further gating is provided to permit a second number, the subtrahend, to enter the register and propagate the borrows necessary to form a difference.<sup>(15)</sup> Set point r is available as the level outputs of a set of 10 electromechanical switches. Feedback b is always available as level outputs from a binary encoder. The controller could also operate by requesting and waiting for a value of b from a shared A/D converter.

Using the structure shown in Figure 4.1, Table 4-1 lists the series of steps necessary to perform equation (4-1).

I-S

2- COMPLEMENT

3-BORROW ENABLE

- 4-COUNTDOWN ENABLE

- 5-SUBTRACT ONE

# FIGURE 4-I SCHEMATIC OF CONTROLLER AND ENCODER

Table 4-2 shows how the cycle of Table 4-1 must be varied to compute equation (4-2) between proportional samples.

Table 4-3 includes a change of set point to show a sequence in which all three algorithm equations are computed.

The first entry in Table 4-1 shows the contents of register A just before the k<sup>th</sup> proportional sampling instant. When the sample order comes at time k the solution of (4-1) requires that  $b_k$  be subtracted from A. The subtraction takes place in 250 microseconds, after which the difference  $A_{kp}$  is counted down to zero at a frequency of  $f_a$ . As long as counting is in progress the actuator is driven at full speed in the direction corresponding to S, the sign of A. If S is positive the output is decreasing and the actuator is therefore driven to open the valve. When A becomes zero the countdown is stopped and the present value of b,  $b_{k+\delta}$ , is transferred to A.  $b_{k+\delta}$  is then the minuend for the subtraction occurring at sample instant k + 1.

| Time<br>fp•t | Controller<br>Mode | Order                     | Contents of Register A<br>upon Completion of Order |

|--------------|--------------------|---------------------------|----------------------------------------------------|

| Х<br>I       | Operate            | 1                         | b <sub>k-1+8</sub>                                 |

|              | Operate            | Prop. Order: Sub b from A | A kp                                               |

| k + 8        |                    | Transfer b to A           | ь<br>bk+б                                          |

| k + 1        | Operate            | Prop. Order: Sub b from A | A(k+1)p                                            |

| k+1+8        |                    | Transfer b to A           | b <sub>k+1+6</sub>                                 |

| k + 2        | Operate            | Prop.Order: Sub b from A  | A(k+2)p<br>0                                       |

| k+2+8        |                    | Transfer b to A           | b <sub>k+2+</sub> ۇ                                |

Operations Performed by Controller Table 4-1

The same procedure is followed in Table 4-2 until after time  $k + \delta$ , when  $A_{kp}$  has been completely applied to the actuator. The pulse trains  $f_p$  and  $f_i$  for proportional and integral sampling orders need not be synchronized, making it possible for an integral order to arrive at the controller at any time in the proportional sample cycle. An integral order is shown occurring between proportional samples k and k + 1, at a time called "k +  $\delta$  +" in the table. To minimize degradation of proportional performance no action is taken on the integral order until the next proportional sample is completed. At time  $k + 1 + \delta$  the transfer of present b to A is completed and immediately thereafter the integral computation (4-2) is performed. The sign S of the difference is changed to provide the minus sign in front of the difference, then the countdown to the actuator proceeds exactly as for a proportional term. After countdown, b is transferred to A, ready for the next proportional order.

| Contents of Register A<br>upon Completion of Order          | b <sub>k-1+6</sub> | Akp<br>0 b <sub>k+6</sub>                                                    | ه<br>ه<br>لا+ ه                                           | A(k+1)p<br>0 <sup>b</sup> k+1+ô<br>-A(k+1)i                                                  | A(k+1)i<br>0 <sup>b</sup> k+1+25                                     | A(k+2)P<br>0 b <sub>k+2+</sub> 6                                             |

|-------------------------------------------------------------|--------------------|------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------|

| Order                                                       | 1                  | Prop.Order: Sub b from A<br>Countdown A at f <sub>a</sub><br>Transfer b to A | Int. Order: Execute after next<br>prop. order is complete | Prop.Order: Sub b from A<br>Countdown A at f <sub>a</sub><br>Transfer b to A<br>Sub r from A | Change sign of A<br>Countdown A at f <sub>a</sub><br>Transfer b to A | Prop.Order: Sub b from A<br>Countdown A at f <sub>a</sub><br>Transfer b to A |

| Controller<br>Mode                                          | Operate            | Operate                                                                      | Operate                                                   | Operate                                                                                      |                                                                      | Operate                                                                      |

| $\begin{array}{c} \text{Time} \\ f_{p} \cdot t \end{array}$ | k-                 | k<br>k<br>+<br>ô                                                             | k+8 +                                                     | k + 1<br>k+1+δ                                                                               | k+1+26.                                                              | k + 2<br>k+2+8                                                               |

Operations Performed by Controller

Table 4-2

|

ļ

ļ

ļ

Table 4-3 follows the same pattern as Table 4-2 until after time  $k+1+2\delta$ . At some time between then and the next sampling instant, called " $k+1+2\delta+$ " in the table, the manual mode control switch is turned to the Read position in preparation for a change of set point. A rotary Read switch can be used to permit register A to be manually reset by momentarily opening the ground line to the zero side of the flip flops just before the old value of r is transferred into A by means of the trigger inputs. With the old value of r recorded in A the set point can be changed at the operator's leisure. As long as the controller is in the Read mode no further computations can take place and the actuator stays where it is. As soon as the new value of r has been entered, shown in the table as time k + 3 +, the operator turns the switch from the Read position around to the Operate position. The transition causes the new r to be subtracted from A. The sign of A is changed and countdown to the actuator proceeds. After countdown, b is transferred to A and the controller is ready for further Operate mode computations.

| Contents of Register A<br>upon Completion of Order | b <sub>k-1+6</sub> | A kp                                           | b <sub>k+ő</sub> | p <sup>k+9</sup>                                          | A(k+1)p                                      | b <sub>k+1+8</sub> | -A(k+1)i     | A(k+1)i                                           | b <sub>k+1+2</sub> 8 | 0<br><sup>F</sup> k+1+26+      | -A <sub>k+3+</sub>        | Ak+3+<br>0<br>br+3+6+                                                | A(k+4)p                                       | ь <sub>k+4+б</sub> |

|----------------------------------------------------|--------------------|------------------------------------------------|------------------|-----------------------------------------------------------|----------------------------------------------|--------------------|--------------|---------------------------------------------------|----------------------|--------------------------------|---------------------------|----------------------------------------------------------------------|-----------------------------------------------|--------------------|

| Order                                              | •                  | Prop. Order: Sub b from A<br>Countdown A at f. | Transfer b to A  | Int. Order: Execute after next<br>prop. order is complete | Prop.Order: Sub b from A<br>Countdown A at f | Transfer b to A    | Sub r from A | Change sign of A<br>Countdown A at f <sub>a</sub> | Transfer b to A      | Reset A<br>Transfer old r to A | New r ready: Sub r from A | Change sign of A<br>Countdown A at f <sub>a</sub><br>Transfer b to A | Prop.Order: Sub b from A<br>Countdown A at f. | Transfer b to A    |

| Controller<br>Mode                                 | Operate            | Operate                                        |                  | Operate                                                   | Operate                                      |                    |              |                                                   |                      | Read                           | Ope rate                  |                                                                      | Operate                                       |                    |

| $\substack{f_{p} \cdot t\\ f_{p}}$                 |                    | *                                              | k+6              | k+8+                                                      | k+1                                          | k+1+8              |              |                                                   | k+1+2.6              | k+1+26+ Read                   | k+3+                      |                                                                      | k+4                                           | k+4+8              |

Operation Performed by Controller Table 4-3

#### Conversion of Sequence Rules to Boolean Statements

The next step necessary in the design of the controller is to convert the preceeding tables and explanations into explicit logical statements that lend themselves to implementation in digital logic. Boolean algebra terminology will be used not only for the combinational logic involved but also to state under what conditions one event or transition follows another. The latter function, vital in the synthesis of asynchronous logic, is discussed by Mergler<sup>(16)</sup>. It permits one to write, for instance, an expression  $T_c = A a_B$ , meaning "Trigger flip flop C when B makes an a transition if A is one at that time."  $a_B$  is defined as the 0 to 1 transition of binary variable B, and  $\beta_B$  as the 1 to 0 transition of B. The flip flops and delay devices used in the controller are all activated by  $\beta$  transitions.

In a sequential circuit it is often desirable to have one operation follow another after a finite delay. In one transfer operation, for instance, it is necessary to trigger all flip flops of register A to make them all zero, then trigger certain of them to enter a number. Depending upon how it is done, it may take anything from one to five microseconds for the first triggering operation to be completed. In such a case it is useful to be able to take the pulse that orders the first part of the operation, delay it about 10 microseconds, and use the delayed pulse to order the second part of the operation. This technique is used extensively in the design of the controller. To provide a symbol to cover this case we follow the lead of Arnstein<sup>(17)</sup> and represent an event B delayed by n microseconds as B with superscript  $\mu$ n. Thus if A is to take place 20 microseconds after pulse B, we would write A = B<sup>H20</sup>.

We are now prepared to make generalized rules from the sequences of tables 4-1 through 4-3 and convert them into Boolean statements as a preliminary step to implementation of the controller in digital logic.

Transfer of a Number to a Register For register A the decision was made to use a flip-flop with six separate gated trigger inputs and a manual reset capability. The controller logic diagram, Figure 4.2, shows that not quite all of these inputs are used, although they would be used in a suggested modification to the controller. Figure 4.2 also shows that two of the trigger inputs are delayed a time  $\tau$ . This time delay is about 4 µsec. Since there is no automatic set or reset input on the flip-flops chosen, transfer of a number to A is performed by taking advantage of the fact that every transfer order is immediately preceeded by a countdown order. As will be shown, the accumulator register A is all ones upon

completion of a countdown order. To enter a number b, then, it would be possible to simply trigger those flip flops of A for which the corresponding bits of b are zero. The number b would then be in A. To keep the transfer operation compatible with the subtraction operation, however, it was decided to first complement A after countdown, making A all zeroes, then trigger the flip flops of A corresponding to the bit positions of the incoming number whose values are one.

## Subtraction

The method of direct subtraction  $^{(15)}$  is used, whereby each bit of the minuend in A is decreased by the value of the corresponding bit of the subtrahend, and if a bit in A thereby becomes less than zero, it must become one and the next higher order bit must be reduced by one; that is, a one must be borrowed from the next higher order. When all borrows have been propagated the difference appears in register A. If, however, the difference is negative, a borrow is generated by an a transition in A<sub>9</sub>, making the sign bit S one, representing minus. The difference then appears in A in two's complement form and must be converted to one's complement form by subtracting one from  $A_0$ , the so-called "end-around-carry". A is then complemented to convert the one's complement form to natural binary form. Because borrows may propagate through all

ten stages of A, in the worst case, and further borrows may occur after the end-around-carry, it is necessary to delay the complement order until well after the subtraction begins. Another requirement is that no borrows can be permitted to propagate during the complement process, as is true also during the transfer process.

## Countdown of a Number