# NASA CONTRACTOR REPORT

LOAN COFY: RETURN TO AFWL (WLIL-2) KIRTLAND AFB, N MEX

# A PHASE LOCKED DUAL CHANNEL SPACECRAFT RECEIVER FOR PHASE AND GROUP PATH MEASUREMENTS

by R. L. Koehler

Prepared under Contract No. NAS 2-1759 and Grant No. NsG-329 by STANFORD ELECTRONICS LABORATORIES

Stanford, Calif.

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION . WASHINGTON, D. C. . NOVEMBER 1965

NASA CR-323

TECH LIBRARY KAFB, NM

# A PHASE LOCKED DUAL CHANNEL SPACECRAFT RECEIVER FOR PHASE AND GROUP PATH MEASUREMENTS

By R. L. Koehler

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

Prepared under Contract No. NAS 2-1759 and Grant No. NsG-329 by STANFORD ELECTRONICS LABORATORIES Stanford, Calif.

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

For sale by the Clearinghouse for Federal Scientific and Technical Information Springfield, Virginia 22151 — Price \$5.00

~ , . .

#### ABSTRACT

This report describes a 49.8 and 423.3 Mc phase locked receiver for group and phase path measurement aboard the Pioneer interplanetary spacecraft. A magnetometer aboard the spacecraft imposes a stringent low residual magnetic field requirement on the equipment. The receiver's magnetic field is only 1 gamma (10<sup>-5</sup> gauss) at 3 feet after exposure to a 25 oersted magnetizing field.

The experiment uses two high power ground based transmitters and a 150 foot parabolic antenna to transmit phase modulated signals to the receiver. Group and phase path measurements will be made as the spacecraft travels to 0.5 AU  $(7.5 \times 10^{10} \text{ m})$  from earth, and the results telemetered back to earth.

The minimum measureable increment of phase path is 1 wavelength of 49.8 Mc, corresponding to an integrated electron density of  $3.75 \times 10^{14}$  electrons/m<sup>2</sup> or a volume density of  $5 \times 10^3$  electrons/m<sup>3</sup> at 0.5 AU. The error in group path is 2 percent of a wavelength of the 8.692 kc modulation frequency, corresponding to an integrated electron density of  $4 \times 10^{16}$  electrons/m<sup>2</sup> or a volume density of  $6 \times 10^5$  electrons/m<sup>3</sup> at 0.5 AU.

The receiver will maintain phase lock for 10 hours before skipping a cycle in the 49.8 Mc channel at -130 dbm with 8000°K cosmic noise, and in the 423.3 Mc channel at -137 dbm with 100°K cosmic noise. These levels include the modulation sidebands which use 0.5 of the total signal power. The 49.8 Mc channel has a 3 db noise figure and the 423.3 Mc channel has a 6 to 7 db noise figure; the IF noise bandwidth is 45 kc. It weighs 5.0 lbs without antennas and uses less than 1.5 w power.

This report discusses the receiver performance and a detailed block diagram, followed by schematics with a description of their operation. Reasons for some of the design decisions are included, as well as a discussion of the areas for improvement. The calculated and measured phase lock loop performance are compared. Low residual magnetism construction techniques and other construction details are included.

|   | - |   |   |

|---|---|---|---|

|   |   | • |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

| * |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   | , |

|   |   |   |   |

|   |   |   | , |

|   |   |   |   |

|   |   |   |   |

|   |   |   | • |

|   |   |   | , |

|   |   |   | · |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

# TABLE OF CONTENTS

|    |          |          |       |                                                                        | Page |

|----|----------|----------|-------|------------------------------------------------------------------------|------|

| C  | HAPTER 1 | - INTRO  | DUCT: | ION                                                                    | 1.   |

| C  | HAPTER 2 | - SYSTE  | M PAI | RAMETERS AND PERFORMANCE                                               |      |

|    | Section  | 2.1      | -     | Electron Density Measurements                                          | 2    |

|    | Section  | 2.2      | -     | Receiver Performance at 0.5 AU                                         | 4    |

|    | Section  | 2.3      | -     | Communication Link Parameters                                          | 4    |

|    | Section  | 2.4      | -     | Receiver Performance                                                   | 4    |

|    | Section  | 2.5      | -     | Receiver Outputs                                                       | 6    |

|    |          | 2.5.1    | -     | Group path measurement                                                 | 6    |

|    |          | 2.5.2    | -     | Carrier amplitude and loop stress subcommutator output                 | 6    |

|    |          | 2.5.3    | -     | Phase path measurement                                                 | 8    |

|    |          | 2.5.4    | -     | Format D output. Sample and Hold                                       | 8    |

|    | Section  | 2.6      | -     | Specifications on the Signals Received from and Sent to the Spacecraft | 9    |

|    | Section  | 2.7      | -     | General                                                                | 9    |

|    | Section  | 2.8      | -     | Word Assignment for Instrument Outputs                                 | 11   |

| C] | HAPTER 3 | - RECEIV | VER S | SYSTEM                                                                 |      |

|    | Section  | 3.1      | -     | Dual Channel Phase Locked Receiver                                     | 13   |

|    |          | 3.1.1    | -     | 423.3 Mc phase locked receiver                                         | 13   |

|    |          | 3.1.2    | -     | 49.8 Mc phase locked receiver                                          | 14   |

|    |          | 3.1.3    | -     | Function of parts of the receiver                                      | 14   |

|    |          |          |       | $\Delta f$ comparison                                                  | 14   |

|    |          |          |       | Phase of the modulation out of the loop phase detector                 | 14   |

|    |          |          |       | Amplitude phase detector                                               | 15   |

|    |          |          |       | Crystal filter in the first IF                                         | 15   |

|    |          | 3.1.4    | -     | IF Switch                                                              | 15   |

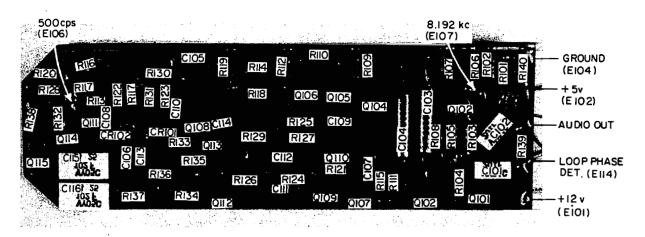

|    | Section  | 3.2      | -     | Modulation Phase Comparator                                            | 16   |

|    | Section  | 3.3      | _     | Analog Gates and Gate Selector                                         | 17   |

| Section   | 3.4         | -    | Counter Register                                      | 17       |

|-----------|-------------|------|-------------------------------------------------------|----------|

| Section   | <b>3.</b> 5 | -    | Sample and Hold                                       | 18       |

| Section   | 3.6         | -    | Power Converter                                       | 19       |

| CHAPTER 4 | - CIRCU     | TT : | DESCRIPTION AND SPECIFICATION FOR EACH SUBASSEN       | NBLY     |

| Section   | 4.1         | _    | Front End                                             | 23       |

| Section   | 4.2         | _    | IF Amplifier                                          | 25       |

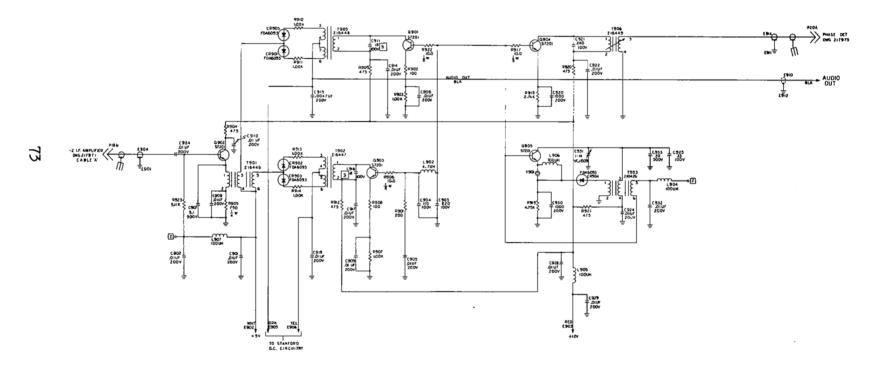

| Section   | 4.3         | -    | Reference Oscillator                                  | 28       |

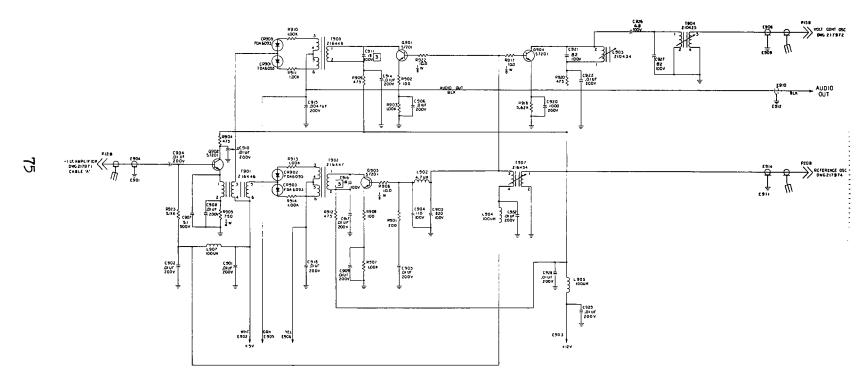

| Section   | 4.4         | -    | Phase Detector                                        | 3C       |

| Section   | 4.5         | -    | Voltage Controlled Oscillator (VCO)                   | 31       |

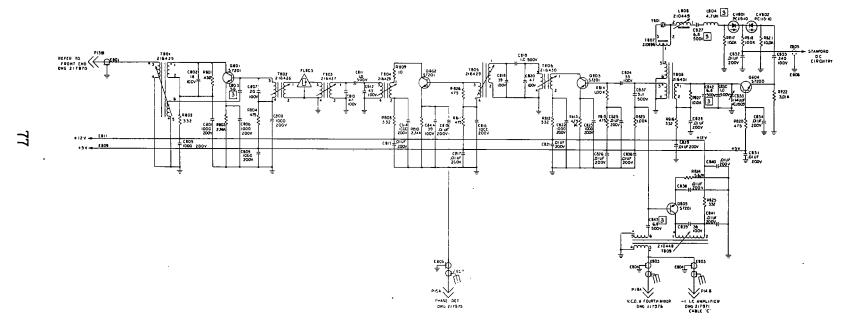

| Section   | 4.6         | -    | Voltage Controlled Oscillator (VCO) and Fourth Mixer  | 34       |

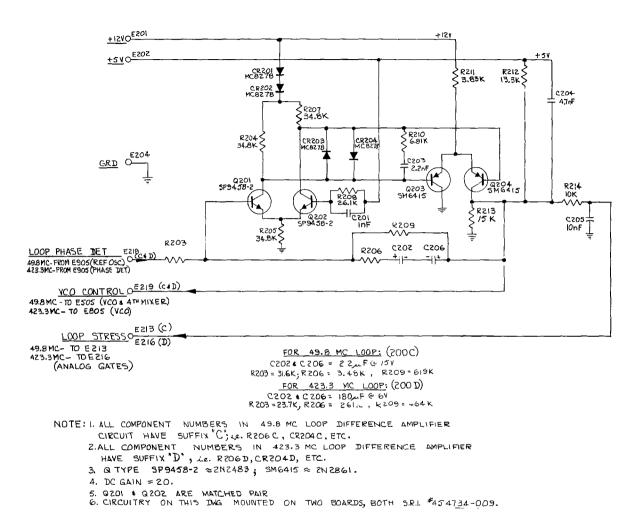

| Section   | 4.7         | -    | Loop Difference Amplifier                             | 35       |

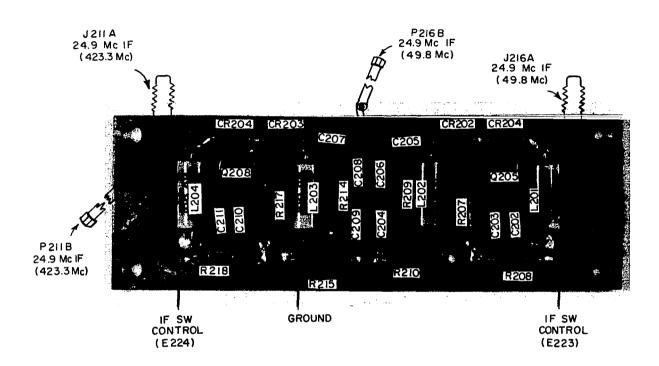

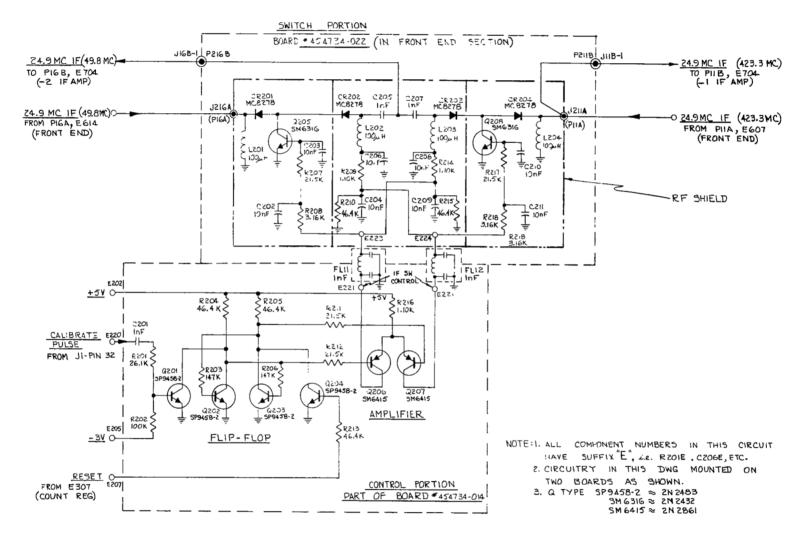

| Section   | 4.8         | -    | IF Switch                                             | 37       |

| Section   | 4.9         | -    | Modulation Phase Comparator                           | 39       |

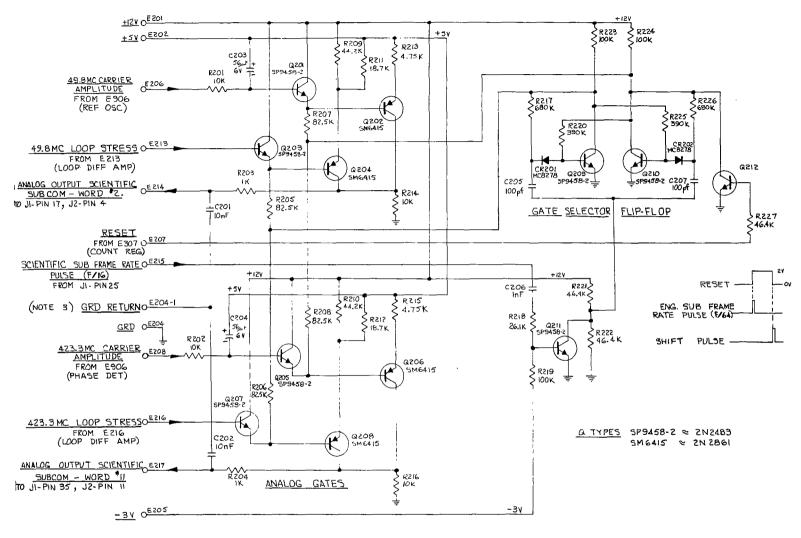

| Section   | 4.10        | -    | Analog Gates and Gate Selector                        | 43       |

| Section   | 4.11        | -    | Counter Register                                      | 45       |

| Section   | 4.12        | _    | Sample and Hold                                       | 48       |

| Section   | 4.13        | -    | Power Converter                                       | 52<br>57 |

| CHAPTER 5 | - AREAS     | FOI  | R IMPROVEMENT                                         |          |

| Section   | 5.1         | -    | 7 Mc Reference Oscillator                             | 101      |

| Section   | 5.2         | -    | 31.9 Mc VCO                                           | 102      |

| Section   | 5•3         | -    | Phase Detector Driver Amplifiers                      | 104      |

| Section   | 5.4         | -    | $\Delta f$ Phase Detector                             | 104      |

| Section   | 5•5         | -    | Front End                                             | 104      |

| Section   | 5.6         | -    | Ferrite Tuning Slugs                                  | 105      |

| Section   | 5•7         | -    | IF Switch                                             | 105      |

| Section   | 5.8         | -    | Sample and Hold                                       | 106      |

| Section   | 5•9         | -    | TI SNR51 Integrated Circuits                          | 107      |

| Section   | 5.10        | -    | Loop Difference Amplifier                             | 108      |

| Section   | 5.11        | -    | Power Converter Transistor                            | 108      |

| Section   | 5.12        | _    | Measurement of $\Delta f$ without an Offset Frequency | 109      |

| Section 5.13                              | -    | Modulation Phase Measurement                                      | 111          |  |

|-------------------------------------------|------|-------------------------------------------------------------------|--------------|--|

| APPENDIX A - RECE                         | IVER | PHASE LOCK LOOP PERFORMANCE                                       |              |  |

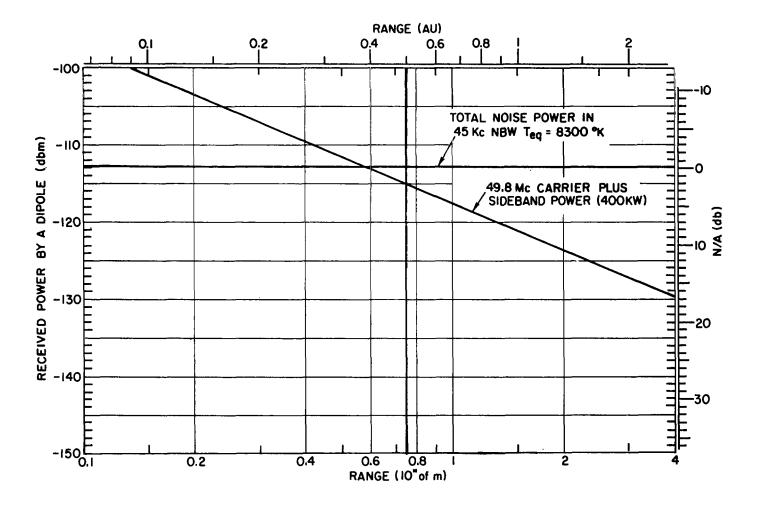

| Section A.1                               | -    | Anticipated Received Signal Level at the Receiver                 | A-1          |  |

| Section A.2                               | -    | Equivalent Input Noise Temperature of the Two Receiver Channels   | A-3          |  |

| Section A.3                               | -    | Total Noise to Total Signal Ratio (N/A) at the Limiter Output     | A-7          |  |

| Section A.4                               | -    | The Phase Lock Loop                                               | <b>A-</b> 8  |  |

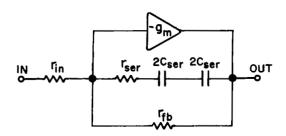

| Section A.5                               | -    | Loop Difference Amplifier Parameters                              | A-14         |  |

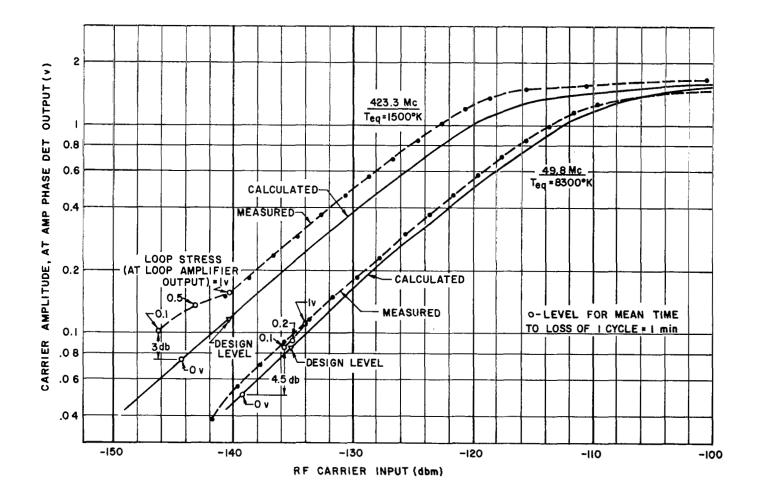

| Section A.6                               | -    | Comparison of Measured and Calculated Phase Lock Loop Performance | A-18         |  |

| Section A.7                               | -    | Selection of Transmitter Frequencies                              | A-18         |  |

| Section A.8                               | -    | Selection of the Modulation Frequencies                           | A-21         |  |

| APPENDIX B - DATA                         | SYSI | TEM                                                               |              |  |

| Section B.l                               | -    | Spacecraft Data Handling and Signals                              | B-l          |  |

| Section B.2                               | -    | Division of Subcommutation                                        | B <b>-</b> 3 |  |

| APPENDIX C - NON-MAGNETIC COMPONENTS      |      |                                                                   |              |  |

| APPENDIX D - PAINTS, ADHESIVES, AND FOAMS |      |                                                                   |              |  |

BIBLIOGRAPHY

# LIST OF FIGURES

| Figure |                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------|------|

| 1.1    | The Dual Channel Stanford/Pioneer Receiver                                              | xii  |

| 2.1    | Simplified Diagram of the Receiver                                                      | 3    |

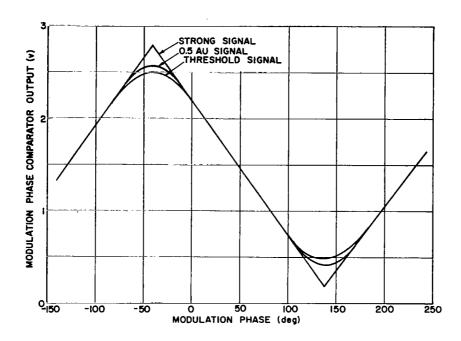

| 2.2    | Volts Output vs. Phase Input                                                            | 7    |

| 2.3    | Binary Digit Designation                                                                | 11   |

| 3.1    | Block Diagram of the Whole Dual Channel Receiver                                        | 21   |

| 4.1    | Simplified Schematic of a Single Gate                                                   | 44   |

| 4.2    | Location of all the Subassemblies in the Receiver                                       | 58   |

| 4.3    | The Front End, with Cover Off                                                           | 59   |

| 4.4    | Location of the Subassemblies under the Large Cover of Frame B                          | 60   |

| 4.5    | Location of the Subassemblies under the Small Covers of Frame B                         | 61   |

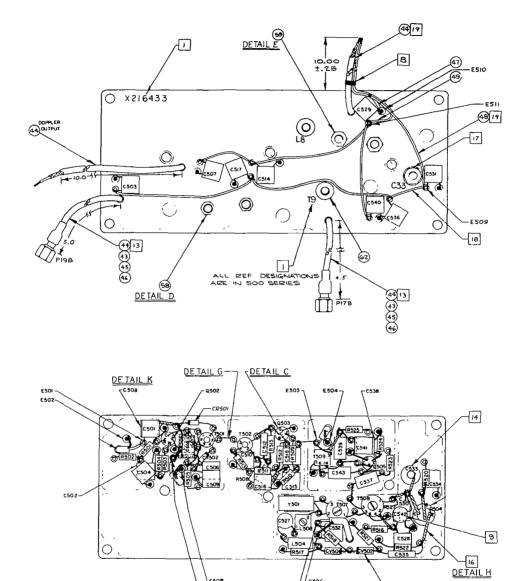

| 4.6    | Diagram of Frame A Wiring                                                               | 64   |

| 4.7    | Diagram of Frame B Wiring                                                               | 66   |

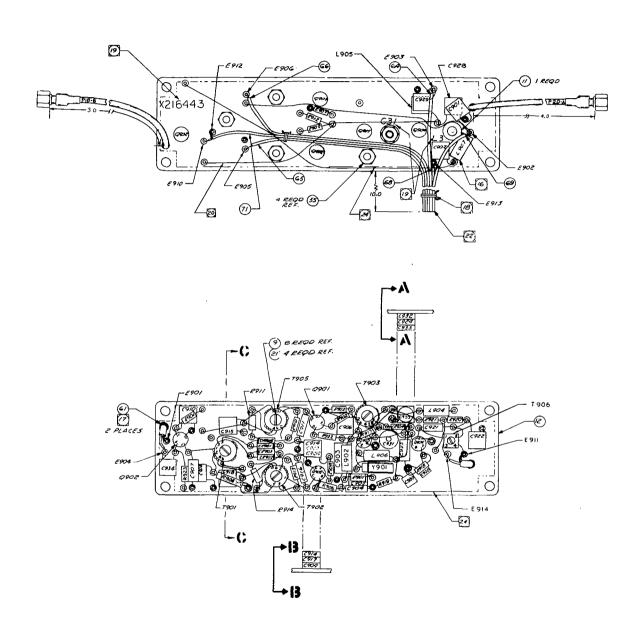

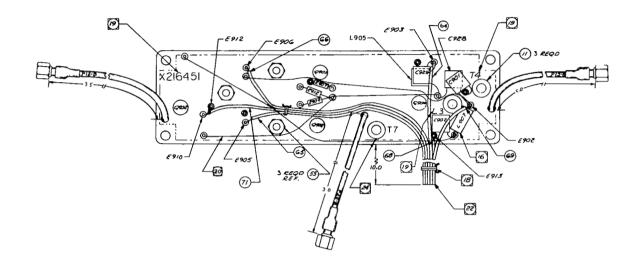

| 4.8    | Pictorial Diagram of the Front End                                                      | 68   |

| 4.9    | Schematic of Front End                                                                  | 69   |

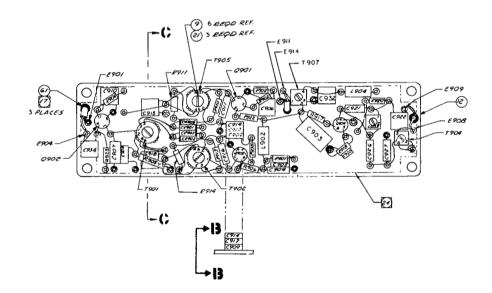

| 4.10   | Pictorial Diagram of the IF Amplifier                                                   | 70   |

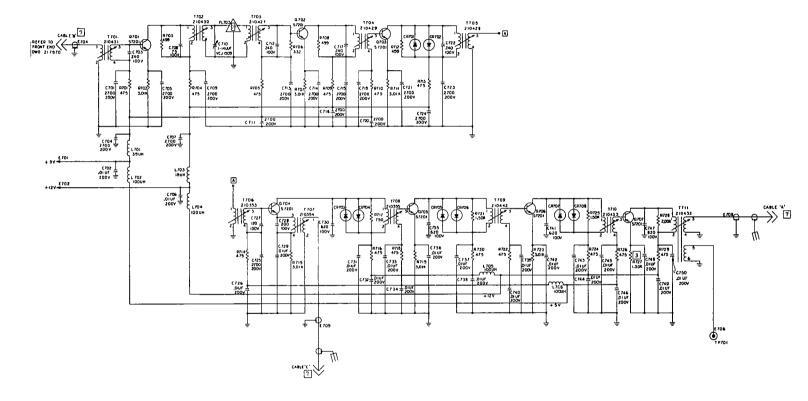

| 4.11   | Schematic of IF Amplifier                                                               | 71   |

| 4.12   | Pictorial Diagram of the Reference Oscillator                                           | 72   |

| 4.13   | Schematic of Reference Oscillator                                                       | 73   |

| 4.14   | Pictorial Diagram of the Phase Detector                                                 | 74   |

| 4.15   | Schematic of Phase Detector                                                             | 75   |

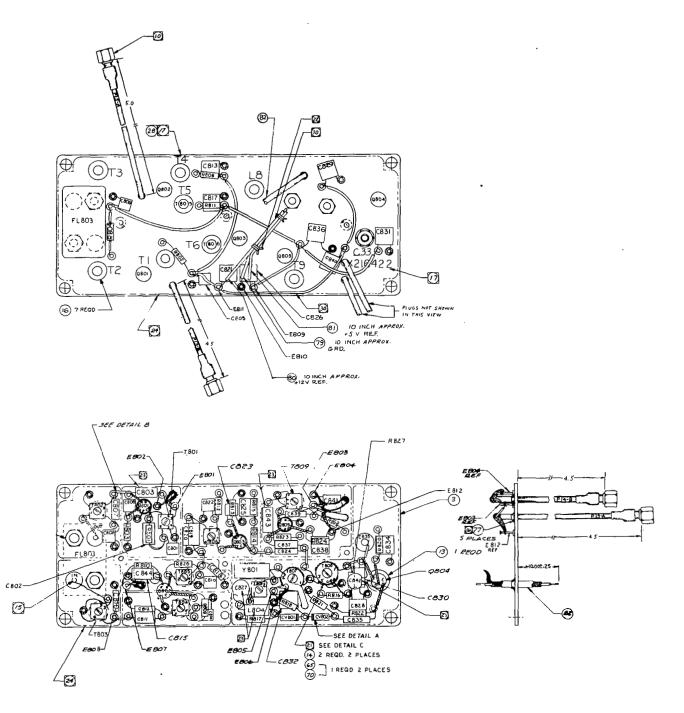

| 4.16   | Pictorial Diagram of the Voltage Controlled Oscillator                                  | 76   |

| 4.17   | Schematic of the Voltage Controlled Oscillator                                          | 77   |

| 4.18   | Pictorial Diagram of the VCO and Fourth Mixer                                           | 78   |

| 4.19   | Schematic of the VCO and Fourth Mixer                                                   | 79   |

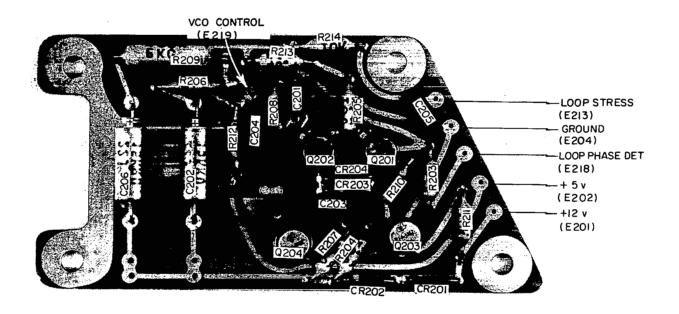

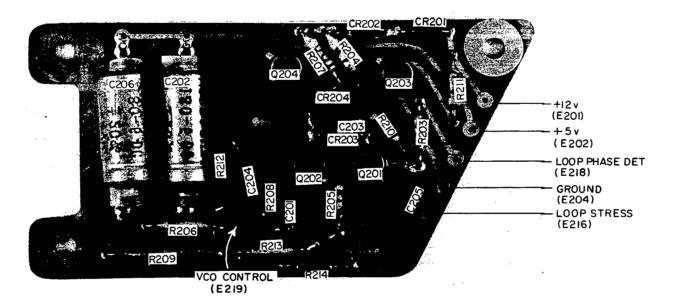

| 4.20   | Printed Circuit of the Loop Difference Amplifier for the 49.8 Mc channel - Wiring Side  | 80   |

| 4.21   | Printed Circuit of the Loop Difference Amplifier for the 423.3 Mc channel - Wiring Side | 80   |

| 4.22   | Schematic of the Loop Difference Amplifier                                              | 81   |

| Figure |                                                                                                               | Page         |

|--------|---------------------------------------------------------------------------------------------------------------|--------------|

| 4.23   | Printed Circuit of the Switch Portion of the IF Switch - Wiring Side                                          | 82           |

| 4.24   | Schematic of the IF Switch                                                                                    | 83           |

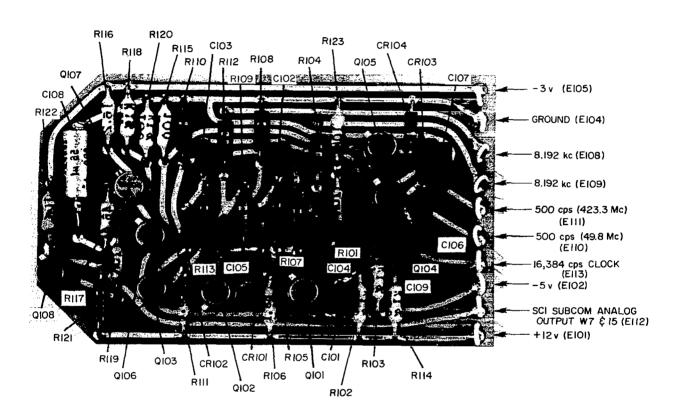

| 4.25   | Printed Circuit of the Modulation Phase Comparator, Section I - Wiring Side                                   | 84           |

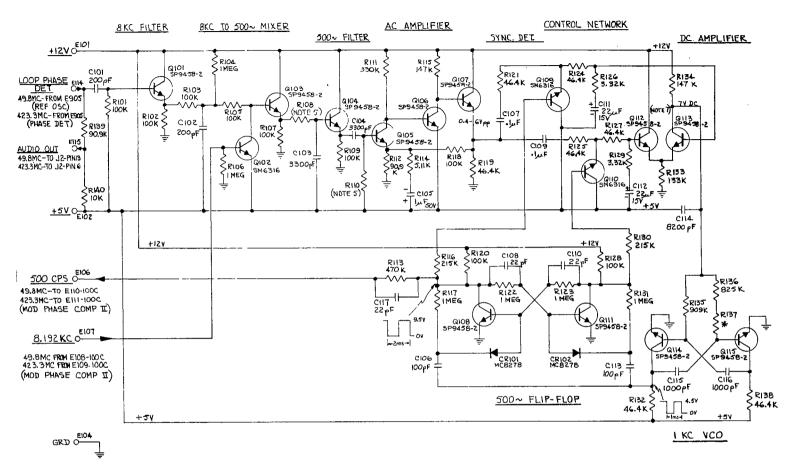

| 4.26   | Schematic of the Modulation Phase Comparator, Section                                                         | 85           |

| 4.27   | Printed Circuit of the Modulation Phase Comparator, Section II - Wiring Side                                  | 86           |

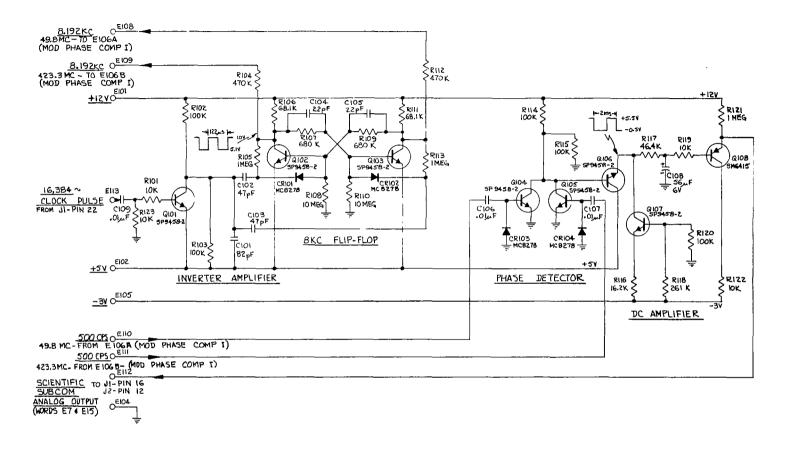

| 4.28   | Schematic of the Modulation Phase Comparator, Section II                                                      | 87           |

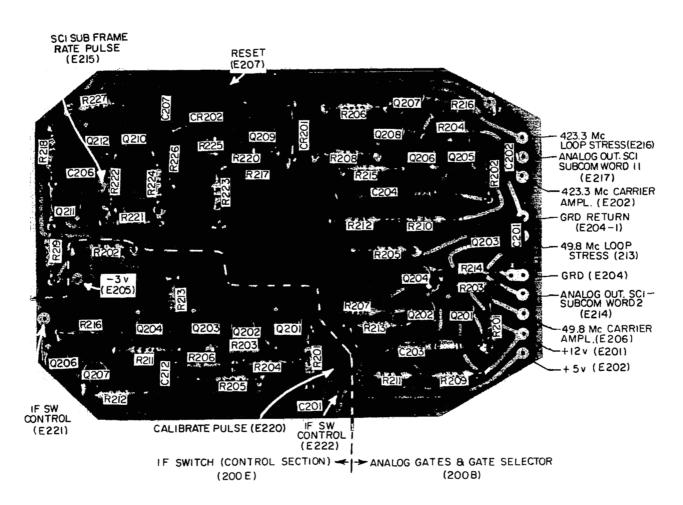

| 4.29   | Printed Circuit of the Analog Gates and Gate Selector, and the Control Portion of the IF Switch - Wiring Side | 88           |

| 4.30   | Schematic of the Analog Gates and Gate Selector                                                               | 89           |

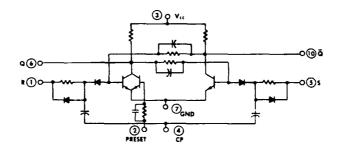

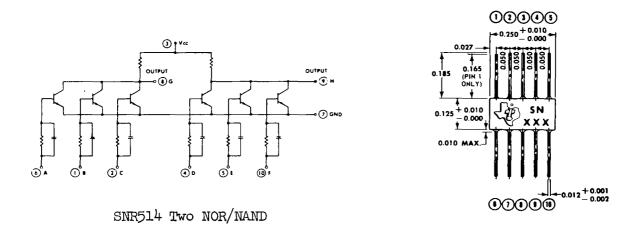

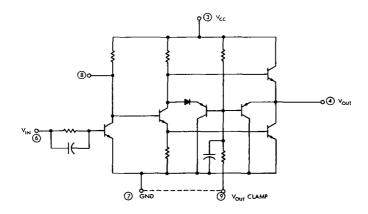

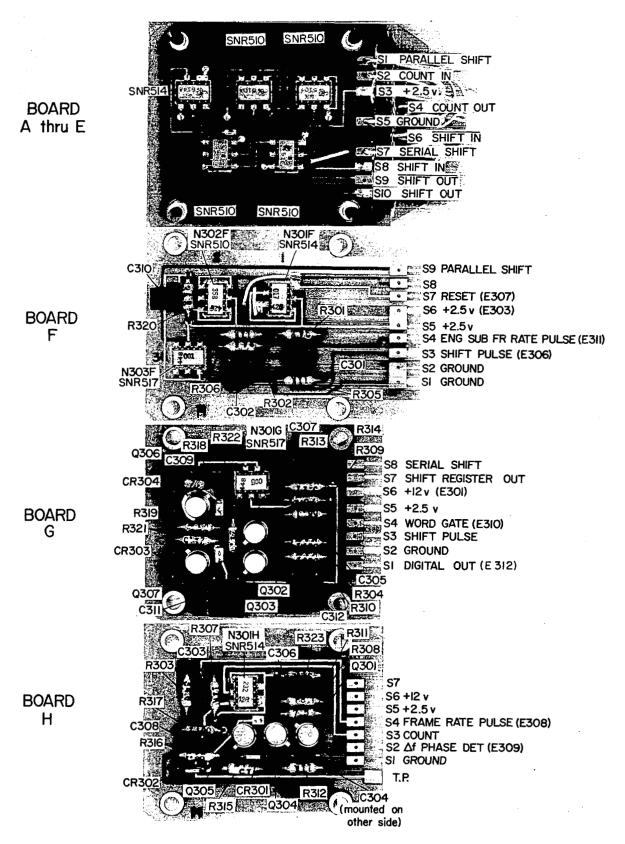

| 4.31   | The Three TI SNR51 Series Integrated Circuits used in the Counter Register                                    | 91           |

| 4.32   | The Four Types of Printed Circuit Boards used in the Counter Register                                         | 92           |

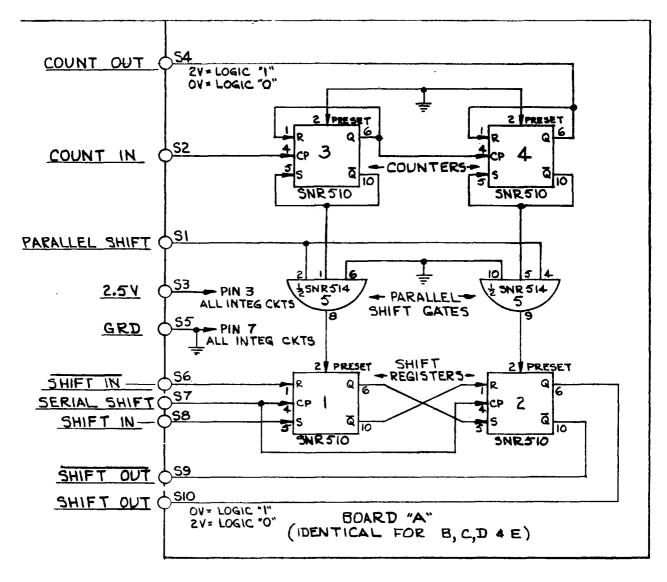

| 4.33   | Schematic of the Counter Register Boards A-E                                                                  | 93           |

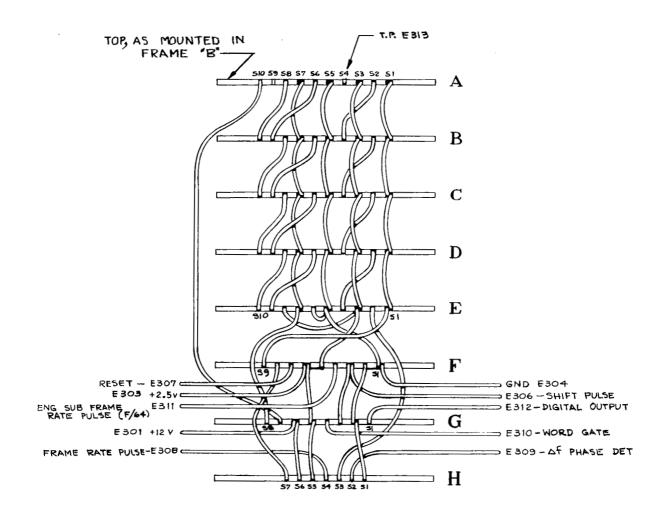

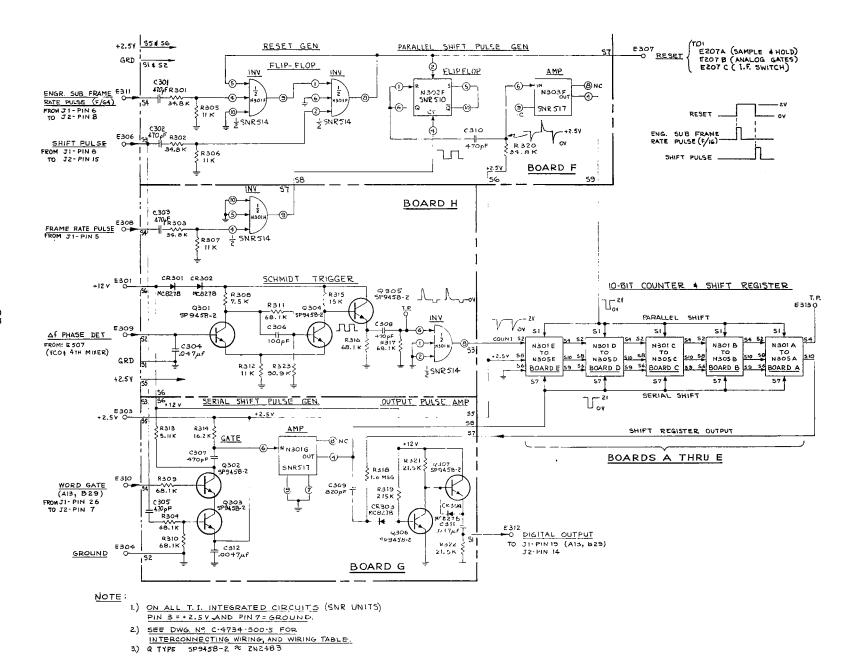

| 4.34   | Diagram of the Counter Register Boards Interconnection                                                        | 94           |

| 4.35   | Schematic of the Counter Register                                                                             | 95           |

| 4.36   | Printed Circuits of the Sample and Hold - Wiring Side .                                                       | 96           |

| 4.37   | Schematic of the Sample and Hold                                                                              | 97           |

| 4.38   | Power Converter                                                                                               | 98           |

| 4.39   | Schematic of the Power Converter                                                                              | 99           |

| 5.1    | Proposed Change in Reference Oscillator Module                                                                | 102          |

| 5.2    | Proposed 31.9 Mc VCO Circuit                                                                                  | 103          |

| 5•3    | Proposed Sample and Hold Circuit                                                                              | 106          |

| 5•4    | Proposed $\Delta f$ Phase Detector with Up-Down Counter                                                       | 110          |

| 5•5    | The $\Delta f$ Vector for Several Conditions                                                                  | 110          |

|        | APPENDIX FIGURES                                                                                              |              |

| A.l    | 423.3 Mc Power Received by a Dipole at the Spacecraft vs. Range                                               | A-4          |

| A•2    | 49.8 Mc Power Received by a Dipole at the Spacecraft vs. Range                                                | A <b>-</b> 5 |

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

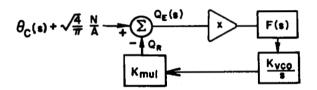

| A.3    | Linearized Phase Lock Loop                                               | A-9  |

| A• 4   | Difference Amplifier used for the Loop Amplifier and the Control Network | A-14 |

| A.5    | Carrier Amplitude vs. RF Carrier Input                                   | A-19 |

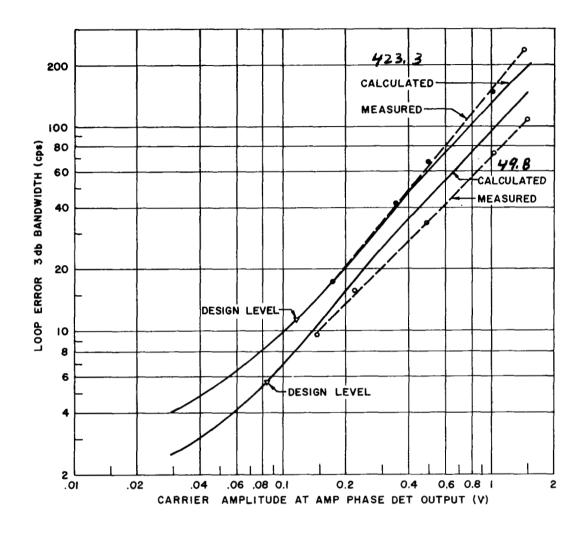

| A.6    | Phase Error 3 db Bandwidth vs. Carrier Amplitude                         | A-20 |

| B.l    | Form of the Main Frame Format for Formats A, B, and D $\mbox{.}$         | B-2  |

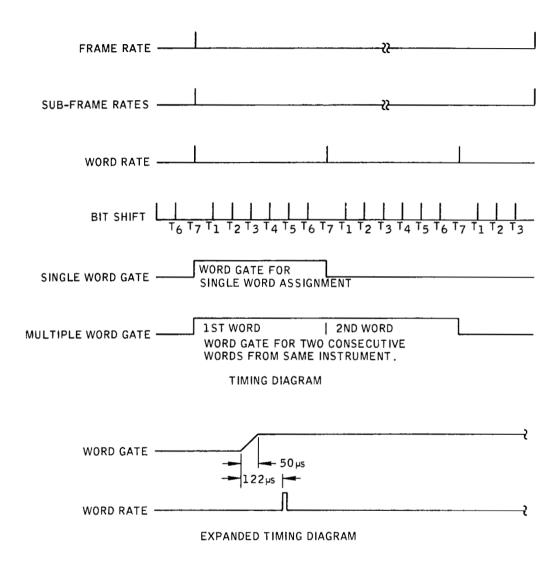

| B•2    | Timing Signal Relationships                                              | B-4  |

|        |                                                                          |      |

|        |                                                                          |      |

# LIST OF TABLES

| <u>Table</u> |                                                                 | Page |

|--------------|-----------------------------------------------------------------|------|

| 2.1          | Signals Received From and Sent to the Spacecraft Data System    | 10   |

| 4.1          | Pin Connections for the External Connectors                     | 62   |

| A.1          | 423.3 Mc Calculated Phase Lock Loop Performance                 | A-12 |

| A.2          | 49.8 Mc Calculated Phase Lock Loop Performance                  | A-13 |

| A•3          | 423.3 Mc Channel Loop Amplifier Parameters vs. Design Level N/A | A-16 |

| A•4          | 49.8 Mc Channel Loop Amplifier Parameters vs. Design Level N/A  | A-17 |

#### ACKNOWLEDGMENT

Work on the Stanford/Pioneer receiver was supported by the National Aeronautics and Space Administration. The initial design phase was supported by grant NsG 329. The final design phase and construction of flight equipment was supported by contract NAS 2-1759.

The overall receiver was designed and constructed at Stanford Research Institute (SRI), and the radio frequency modules were designed and constructed at TRW Space Technology Laboratories (STL).

Special thanks go to Roy Long, who headed the project at SRI and capably guided it through many problems, and to Lyle Nelson, who very ably and conscientiously supervised the partial redesign and construction of the radio frequency modules at STL.

Designers of various portions of the receiver at SRI deserve special mention: John Yarborough, Jim Woodbury, Hank Olsen, and Boyd Fair. Bruce Clark supervised the reliability program, and Vel Sanford and Ed Spitzer were responsible for the mechanical design.

At Stanford University, thanks to Professor Owen K. Garriott, who started the development project, Professor Von R. Eshleman, who assumed role as principal investigator for the flight on the Pioneer Spacecraft, and Professor Allen M. Peterson, who helped solve some of the knotty administrative problems and also started me on this project.

I greatly appreciate the work of many people on the receiver throughout the past year. I express gratitude to the many others for their support on problems concerning the overall Pioneer project, such as the spacecraft antenna, the ground antenna and transmitters, trajectories, and the NASA-SU interface.

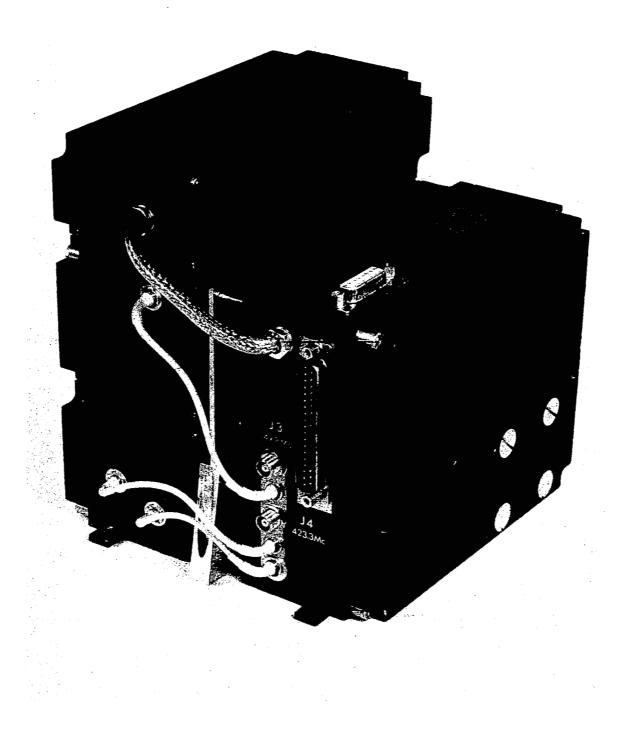

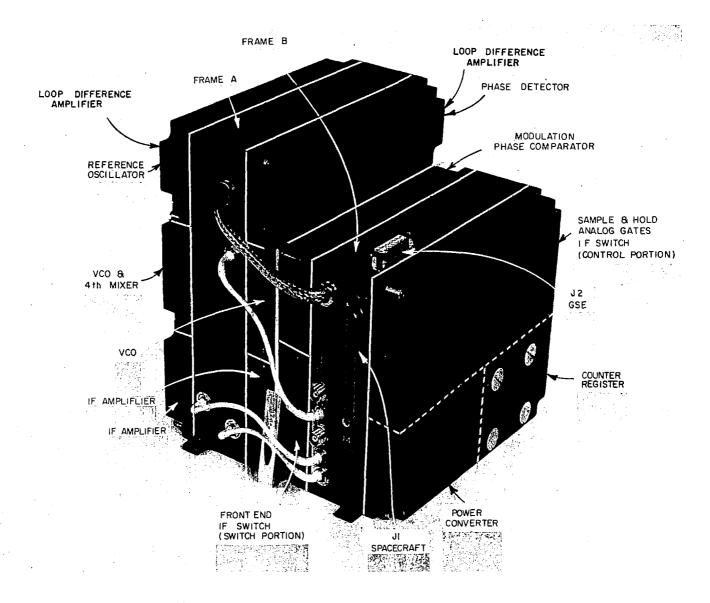

Figure 1.1 - The Dual Channel Stanford/Pioneer Receiver

#### I. INTRODUCTION

This report describes the design and construction of a receiver intended for operation as a part of a space probe experiment. The experiment involves the transmission of two modulated, coherent carriers from the ground (at approximately 50 Mc and 425 Mc) and the reception of these signals by the receiver in a space probe. From the relative phase of the received carriers and their sidebands, it is possible to deduce the integrated electron density between the earth and the space probe. This is the major purpose of the experiment.

It can be shown that the phase of a radio wave in passing through an ionized medium, will be advanced by an amount in meters  $\Delta P = (40.3/f^2) \int N \ ds, \ \text{where} \quad f \quad \text{is the wave frequency and the electron}$

density N is integrated along the ray path. It is also true that a wave packet (which may be described by the peak of a modulation envelope) is delayed by the same amount,  $\Delta P$  meters. The space probe receiver has been designed to measure the relative phase of the modulation envelopes on the two carrier frequencies and, since the higher frequency is relatively unaffected by the presence of the ionization, this will provide a value for the integrated electron density. In addition, the rate of change of phase of one carrier with respect to the other will be measured, thus very accurately determining the rate change of integrated electron density. The measurements will be transmitted back to earth by the space probe telemetry system.

In the following sections, the specifications and system parameters to which the receiver has been designed will be given. This is followed by a discussion of the entire system and a more detailed description of the individual unit operation. The report concludes with a discussion of possible areas for improvement in future receivers.

#### 2. SYSTEM PARAMETERS AND PERFORMANCE

While several system parameters such as weight, size, and VHF noise figure were determined by a combination of the state of the art and the time available for development, most were dictated by the scientific measurements to be performed. An introduction to ionospheric and interplanetary gas density measurements can be found in references 1 and 2. Performance of ground based facilities of the Stanford Center for Radar Astronomy, consisting of VHF and UHF transmitters and a fully steerable 150 foot parabolic antenna, sets the ultimate limit on signal strength available to the receiver.

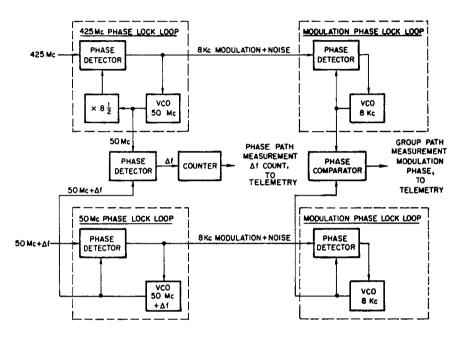

Figure 2.1 is a simplified, functional block diagram of the receiver. Radio frequency, phase locked loops enable the carrier to be filtered in a 10 to 20 cps noise bandwidth without frequency stability problems. This makes measurement of the normalized frequency difference between carriers (phase path) possible at very low signal levels. Contents of the Δf counter are telemetered at regular intervals. Audio phase locked loops are used to provide narrow bandwidth for the modulation frequencies so that group path data will be available at the full range of the space probe telemetry system.

# 2.1 - Electron Density Measurements

Group path measurements

Total integrated electron density error  $^{\pm}4.3 \times 10^{16}$  electrons/m<sup>2</sup> ( $^{\pm}6^{\circ}$  phase error at 8.692 kc)

Maximum unambiguous integrated electron  $^{1.7} \times 10^{19}$  electrons/m<sup>2</sup> density (8 cycles of 8.692 kc)

Phase path measurements

Rate of change of integrated electron  $^{+}6 \times 10^{12}$  electrons/m<sup>2</sup> -sec density error (1 min sampling interval) ( $^{+}1$  cycle of  $\Delta f$  in 1 min)

Maximum rate of change of integrated electron density, without ambiguity ( $\Delta f = 8.5$  cps)

(1 min sampling interval)

Figure 2.1 - Simplified Diagram of the Receiver

This diagram shows the concept of the phase path and group path measurements.

The actual implementation and frequencies are slightly different from those shown.

S

| 2.2 - Receiver Performance at 0.5 AU (75 x 10 km) |                                                                                                                                      |                  |           |                        |             |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|------------------------|-------------|

|                                                   | Frequency of operation                                                                                                               | 49.80            | ) Mc      | 423.30                 | Me          |

| Recei                                             | ver operating point at 0.5 AU                                                                                                        |                  |           |                        | <del></del> |

|                                                   | Total signal power (carrier plus modulation) at bottom of 8 db antenna null; includes 2.5 db fading loss on 49.8 Mc                  | -125.7           | dbm       | -134.2                 | dbm         |

|                                                   | N/A (total noise to total signal power) in 45 kc IF NBW                                                                              | 12.8             | db        | 12.5                   | db          |

|                                                   | Phase lock loop 3 db bandwidth                                                                                                       | 21.6             | cps       | 33.2                   | cps         |

|                                                   | Signal power margin over threshold (defined as the power which gives 1 cycle loss/10 hr) at 0 v loop stress                          | <b>3.</b> 5      | db        | 2.0                    | db          |

| 2.3 -                                             | Communication Link Parameters                                                                                                        |                  |           |                        |             |

|                                                   | Transmitting antenna                                                                                                                 |                  | 150 ft.   | dia parab              | oloid       |

|                                                   | Efficiency                                                                                                                           |                  | 50 perce  | _                      |             |

|                                                   | Transmission line loss                                                                                                               |                  | 1.0 db    |                        |             |

|                                                   | Polarization                                                                                                                         |                  | Circular  |                        |             |

|                                                   | Receiving antenna. Both have nulls of 8 db                                                                                           | Quarter<br>monop |           | Half wa                |             |

|                                                   | Transmission line loss                                                                                                               | 0                | đъ        | 0.78                   | đb          |

|                                                   | Polarization                                                                                                                         |                  | Approxima | ately line             | ear         |

|                                                   | Transmitter                                                                                                                          |                  |           |                        |             |

|                                                   | Power                                                                                                                                | 86.0<br>(400 ]   |           | 74.8<br>(30 kv         |             |

|                                                   | Modulation                                                                                                                           |                  | Phase mod | dulation               |             |

|                                                   | Fraction of power in carrier                                                                                                         |                  | 0.        | 5                      |             |

|                                                   | Maximum range desired                                                                                                                |                  | 0.5 AU (  | 75 x 10 <sup>6</sup> 1 | cm)         |

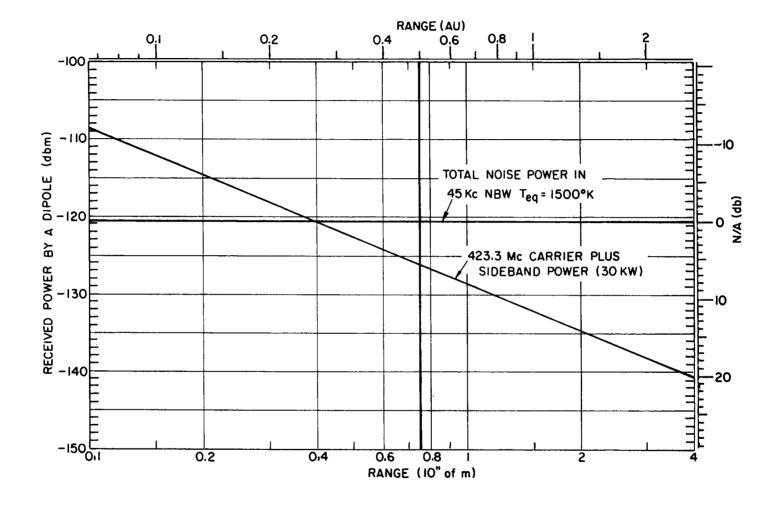

| 2.4 -                                             | Receiver Performance                                                                                                                 |                  |           |                        |             |

| á,                                                | Receiver system noise temperature, referred to antenna terminals; including cosmic noise, transmission line loss, and image response | 8300 <b>°</b> K  |           | 1500 <b>°</b> K        |             |

|                                                   | Cosmic noise temperature                                                                                                             | 8000 <b>°</b> K  |           | 100°K                  |             |

See Appendix A for calculations of receiver performance and expected signal levels.

| Receiver noise temperature alone,                                                                                                                                            | <u>49.80</u><br>300°K | Mc                | <u>423.30</u><br>1200°K | Мс         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|------------|

| including image response                                                                                                                                                     | (3 db NF              | ')                | (7 db NF                | )          |

| Input impedance                                                                                                                                                              |                       | 50 ohms           |                         |            |

| IF noise bandwidth                                                                                                                                                           |                       | 45 kc             |                         |            |

| Receiver threshold sensitivity (defined as the power which gives loss of 1 cycle/10 hr). This is total power (carrier plus side bands)                                       | -129•2                | dbm               | -136.2                  | d.bm       |

| Conditions: System noise temperature is 8300°K at 49.8 Mc; 1500°K at 423.3 Mc. Modulation sidebands use 0.5 of the power. Magnitude of loop stress < 0.1 v at the VCO input. |                       |                   |                         |            |

| Additional signal power required to maintain threshold because of loop stress of magnitude:                                                                                  |                       |                   |                         |            |

| 0.5 v at VCO input                                                                                                                                                           | 0.5                   | db                | 1.5                     | đЪ         |

| 1.0 v at VCO input                                                                                                                                                           | 2.3                   | db                | 3.3                     | db         |

| Threshold level parameters                                                                                                                                                   |                       |                   |                         |            |

| Loop noise bandwidth, $B_{T}$                                                                                                                                                | 24.8                  | cps               | 50                      | cps        |

| Loop error 3 db bandwidth                                                                                                                                                    | 9.0                   | cps               | 17.5                    | cps        |

| Loop 3 db bandwidth                                                                                                                                                          | 16.0                  | cps               | <b>3</b> 1.3            | cps        |

| Noise to signal ratio in IF noise bandwidth (45 kc)                                                                                                                          | 16.5                  | db                | 14.5                    | db         |

| Carrier amplitude, at amplitude phase detector output, relative to 5 v supply; with or without modulation                                                                    | -0.14                 | v                 | -0.17                   | ōν         |

| Strong signal parameters                                                                                                                                                     |                       |                   |                         |            |

| Loop error 3 db bandwidth                                                                                                                                                    |                       |                   |                         |            |

| with modulation without modulation                                                                                                                                           | 74<br>106             | cps<br>cps        | 160<br>230              | cps<br>cps |

| Loop 3 db bandwidth                                                                                                                                                          |                       |                   |                         |            |

| with modulation without modulation                                                                                                                                           | 80<br>111             | cps<br>cps        | 180<br>250              | cps<br>cps |

| Carrier amplitude, at amplitude phase detector output, relative to 5 v supply:                                                                                               |                       |                   |                         |            |

| with modulation without modulation                                                                                                                                           |                       | -1.5 v<br>-1.06 v |                         |            |

|                                 | 49.80 Mc | 423.30 Me |

|---------------------------------|----------|-----------|

| Interference level from other   | -87.5 db | -47.5 db  |

| channel, for equal input levels |          |           |

# 2.5 - Receiver Outputs

# 2.5.1 - Group path measurement

| Modulation Frequency                                                                | 7.192 or 8.192 kc <sup>±</sup> 2 cps |

|-------------------------------------------------------------------------------------|--------------------------------------|

| Error of modulation phase measurement at receiver threshold                         |                                      |

| Receiver alone, without use of calibration command (mean error)                     | <del>-</del> 6°                      |

| Receiver alone, with use of calibration command (mean error)                        | ± 3°                                 |

| Transmitter and receiver, together with use of calibration command (mean error)     | ± 6°                                 |

| Rms variation                                                                       | 1.6°                                 |

| Hold-in range at threshold (error increases with modulation phase lock loop stress) | + 50 cps                             |

| Output voltage (423.3 Mc channel is                                                 |                                      |

reference phase). See Figure 2.2

Linear from 0.20 to 2.80 v for -43° (317°) to 137°

Linear from 2.80 to 0.20 v for 137° to 317°

Output impedance

l kc

Output current (positive current flowing out of the output)

-50 to +10  $\mu a$

The 16.834 kc clock pulse is used by this circuit.

The rounded corners of the triangular shaped output, Figure 2.2, are caused by noise. The averaging circuit used cannot average the output at the corners.

# 2.5.2 - Carrier amplitude and loop stress subcommutator output

The carrier amplitude (amplitude phase detector output) and loop stress are subcommutated alternately. A flip flop alternates with each scientific subcom pulse. In the binary zero state, the carrier amplitude is connected to the subcommutator output. In the binary one state,

Figure 2.2 - Volts Output vs. Phase Input of the Modulation

Phase Comparator

The output is shown for strong signal, signal levels corresponding to operation at 0.5 AU (Section 2.2), and threshold signals (Section 2.4). The reference phase is the 423.3 Mc channel at the receiver input. the loop stress is connected. The reset signal resets the flip flop to the binary zero state. It begins with the engineering subframe pulse and ends one bit time later with the next shift pulse. The 423.3 Mc channel information is connected to one output line, and the 49.8 Mc information is connected to another.

Output levels are with the Thevenin equivalent of the load connected (4.75 v, 465 k).

| Output impedance                             | 11 k       |

|----------------------------------------------|------------|

| Carrier amplitude output                     | 0.2 to 3 v |

| no signal (minimum)                          | 0.2 v      |

| strong signal, no modulation (maximum)       | 2.83 v     |

| strong signal, with modulation               | 1.85 v     |

| threshold signal, with or without modulation |            |

| 423.3 Mc channel                             | 0.430 v    |

| 49.8 Mc channel                              | 0.375 v    |

| Carrier amplitude 3 db bandwidth             | 0.3 cps    |

| Loop stress output                           | 0.2 to 3 v |

Zero loop stress (zero loop stress is the loop stress output for no RF signal input)

1.6 v (nominally)

Loop stress scale factor

423.3 Mc channel 49.8 Mc channel -11 kc/v 0.63 kc/v

# 2.5.3 - Phase path measurement

$$\Delta f = \left| f_{49.8} - \frac{2}{17} f_{423.3} \right|$$

Af phase detector 3 db bandwidth

$\Delta f$  counter capacity

80 cps 1024 counts (10 bits)

Output - The contents of the 10 bit  $\Delta f$  counter are transferred to the serial shift register with alternate frame rate pulses; the counter is not reset. A flip flop alternates with each frame pulse. Transition to binary zero causes the contents of the counter to be transferred to the shift register. The reset signal (discussed in Section 2.5.2) resets this flip flop to binary zero.

When the word gate is on, the output is shifted out synchronously with each shift pulse. Binary zeros are entered serially into the shift register as the information is shifted out. Thus, only binary zeros are shifted out after the first 10 bits of information have been shifted out.

# 2.5.4 - Format Doutput. Sample and Hold

The carrier amplitude of each channel is subcommutated by a sample and hold circuit. The two channels are sampled alternately with each word pulse, and that sampled value is held until the next word pulse. A flip flop alternates state with each word pulse. Transition to binary one causes the 49.8 Mc channel to be sampled. The reset signal (discussed in Section 2.5.2) resets the flip flop to binary zero, without causing a sample to occur.

Carrier amplitude 3 db bandwidth

10 cps

Output level with Thevenin equivalent of load connected to output (4.75 v, 465 k)

No signal (minimum) 0.2 v Strong signal, no modulation 2.92 v (maximum)

Output impedance 11 k

Sample duration 0.5 ms

Drift for 1 sec hold time <2 percent of full

scale (.06 v)

Time to reach final level, in the < 100  $\mu s$  positive going direction

Time to reach final level, in the  $< 300 \ \mu s$  negative going direction

Sun Pulse - The sun pulse occurs once each spacecraft revolution (approximately 1 rps). With the bit rate 512 level on, the sun pulse causes the sample and hold output to be 0.2 v for 30 ms, or slightly more than 2 word times at the 512 bps rate. The sun pulse has no effect

2.6 - Specifications on the signals received from and sent to the spacecraft

These signals are listed in Table 2.1. Further information about the spacecraft data system is in Appendix B.

#### 2.7 - General

Power (constant power load) < 1.50 w

Voltage (primary power is isolated 20 to 35 v

from ground)

with the bit rate 512 level off.

depth requires approximately one additional inch for mounting feet

and connectors

Weight (without antennas) 5.0 lbs

Temperature, operating -15° to +60°C storage -45° to +85°C

Table 2.1 - Signals Received from and Sent to the Spacecraft Data System

|                                      |                                                                                                                                                                                                         |                            |                         | NO-LOAI                                  | CHARACTERISTICS AND TOLER                        | ANCES                                             | IMPE                                     | ANCE, OHMS                                                                                 |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|------------------------------------------|--------------------------------------------------|---------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|

| NOMENCLATURE                         | SIGNAL DESCRIPTION                                                                                                                                                                                      | AMPLITUDE,<br>(+)VOLTS     |                         | DURATION,<br>MICROSECONDS                | RISE TIME (at generator output),<br>MICROSECONDS | FALL TIME (at generator output),<br>MICROSECONDS, | SPACE-<br>CRAFT                          | INSTRUMENT                                                                                 |

|                                      |                                                                                                                                                                                                         | ON                         | 0FF                     | (50%-50%)                                | (10%-90%)                                        | (90%-10%)                                         | CRAFI                                    |                                                                                            |

| Main-Frame<br>Rate Pulse             | A pulse at beginning of each frame.                                                                                                                                                                     | 11 +2                      | 0 ±1                    | 10 ±3.5                                  | ≤1                                               | \$1                                               | <5                                       | ≥3.3 K No DC potential shall be introduced on line by instrument. Capacitive load <300 pf. |

| Instrument Sub-<br>Frame rate pulse  | A pulse every 16 frames.                                                                                                                                                                                | 11 ±2                      | 0 ±1                    | 10 =3.5                                  | ≤1                                               | ≤1                                                | <5                                       | As above                                                                                   |

| Engineering Sub-<br>frame rate pulse | A pulse every 64 frames.                                                                                                                                                                                | 11 ±2                      | 0 ±1                    | 10 ±3.5                                  | ≤1                                               | ≤l                                                | <5                                       | As above                                                                                   |

| 16.384 kc clock                      | A pulse train with a 16.384 kc repetition rate.                                                                                                                                                         | 11 ±2                      | 0 ±1                    | 2 +1.0<br>-0.5                           | ≤ 1                                              | ≤1                                                | <5                                       | As above                                                                                   |

| Word Rate pulse                      | A pulse generated during the last bit period of each word. Word rate pulse delayed 122 $\pm10~\mu s$ from word gate.                                                                                    | 11 ±2                      | 0 ±1                    | 10 ±3.5                                  | ≤1                                               | ≤1                                                | <5                                       | As above                                                                                   |

| Bit shift pulse                      | Pulses generated at the bit rate in groups of 6 pulses followed by a missing pulse. Parity is inserted in 7th pulse position.                                                                           | 11 ±2                      | 0 ±1                    | 10 ±3.5                                  | ≤1                                               | ≤1                                                | <5                                       | As above                                                                                   |

| 16 cps clock                         | A pulse train with a 16 cps repetition rate.                                                                                                                                                            | 11 ±2                      | 0 ±1                    | 10 ±3.5                                  | ≤ 1                                              | ≤ 1                                               | <5                                       | As above                                                                                   |

| Word Gate                            | Gate to each instrument to indicate time of reading out digital data to DTU. Separate line for main frame and sub-frame digital words.                                                                  | 9 +1                       | 0 ±1                    | Bit rate and<br>word format<br>dependent | Rise Time Constant<br>< 50                       | Fall Time Constant<br>< 1000                      | <5                                       | ≥20 K from interface<br>to ground. Capacitive<br>load <300 pf.                             |

| DTU Operational<br>Status            | Continuous states indicating operational conditions of the DTU as follows: Bit Rates - 512, 256, 64, 16, 8 Formats - A, B, C, D Storage - Duty cycle, telemetry Separate line required for each signal. | 9 +1                       | 0 ±1                    | Duration of condition                    | Rise Time Constant<br><10                        | Falt Time Constant<br>< 3000                      | 23 K                                     | ≥48 K in series.<br>≥100 K from interface to ground.<br>Capacitive load<br><300 pf.        |

| Command Pulse                        | Pulse upon receipt of a ground command,<br>Separate line for each command.                                                                                                                              | 10 ±2                      | 0 ±1                    | 10 ±2                                    | < 1                                              | 3 -15                                             | <1000                                    | > 1000                                                                                     |

| Sun Pulse                            | A single pulse per spacecraft revolution .                                                                                                                                                              | 10.5<br>±2                 | 0 ±1                    | 12.5 ±6                                  | ≤1                                               | ≤1                                                | <10                                      | ≥3.3 K No DC potential shall be introduced on line by instrument. Capacitive load <300 pf. |

| Digital Data                         | Series of pulses synchronized to within 10µs of bit shift pulse. A pulse shall indicate one and no pulse shall indicate zero.                                                                           | 10 ±1<br>Across<br>3.9 K   | 0 ±1<br>Across<br>3.9 K | 3 -13                                    | ≤1                                               | ≤ 3                                               | 3.9 K ±1%                                | _                                                                                          |

| Analog Data                          | Normalized analog voltage. One line required for each word.                                                                                                                                             | Normal-<br>ized<br>0 to +3 | _                       | Duration of word gate                    | -                                                | -                                                 | Current to instrument will be ≤25 µ amp. | ≤1000 for ±1<br>bit A/D<br>conversion<br>accuracy                                          |

| Instrument operational status        | Bi-level states indicating operational conditions of instruments. Separate line required for each signal.                                                                                               | 8 to<br>28                 | 0 to +1                 | Duration of condition                    | -                                                | _                                                 | 47 K                                     | ≤100 K                                                                                     |

NOTE: The capacitive load results from s/c wiring. (Max. 10 ft at 30 pf/ft.)

#### Vibration

Sinusoidal, swept once through each range at 2 octaves/min, in each of 3 orthogonal axes

| Fre<br>Ran | - | ncy<br>cps | Test Duration, min. | Acceleration g, 0 to peak |

|------------|---|------------|---------------------|---------------------------|

| 10         | _ | 50         | 1.25                | 7•5                       |

| 50         | - | 100        | •5                  | 30                        |

| 100        | - | 250        | .625                | 20                        |

| 250        | - | 500        | •5                  | 7•5                       |

| 500        | - | 2000       | 1.0                 | 21                        |

Gaussian random vibration is applied with the "G-peaks" clipped at three times the rms acceleration specified in the schedule.

Vibration is applied in each of 3 orthogonal axes.

| Frequency  | Test Duration, | Power spectral                    | Acceleration |

|------------|----------------|-----------------------------------|--------------|

| Range, cps | min.           | Power spectral density, $g^2/cps$ | g - rms      |

| 20 - 2000  | 4 each axis    | 0.7                               | 11.8         |

# 2.8 - Word Assignment for Instrument Outputs

# Af counter output (digital output)

Line Ea. Format A, word 13; Format B, word 29.

The 10 bit digital output is the contents of a 10 bit counter which counts the cycles difference between the 49.8 Mc carrier and  $\frac{2}{17}$  of the 423.3 Mc carrier. To obtain the difference in frequency ( $\Delta f$ ), the difference between successive 10 bit outputs is divided by the sampling interval. The counter is not reset by the sampling.

Figure 2.3 shows how the 10 bit word is read out on successive frames. This alternating read-out is continued in consecutive frames. Frame 1 in Figure 2.3 is read out in the first frame following the engineering subframe pulse.

| FRAME 1 | 1 29             | 2 28 | <sup>3</sup> <sub>2</sub> 7 | <sup>4</sup> <sub>2</sub> 6 | 5 <sub>2</sub> 5 | 6 214 |

|---------|------------------|------|-----------------------------|-----------------------------|------------------|-------|

| FRAME 2 | 1 2 <sup>3</sup> | 2 22 | <sup>3</sup> 2 <sup>1</sup> | 4 20                        | 5<br>0           | 6     |

Figure 2.3 - Binary Digit Designation

The number in the upper left hand corner of each box is the bit sequence number. The number in the center of each box is the weight of a binary one in that position. The last two 0's are always binary zeros.

#### Modulation phase

Line Eb. Format E (scientific subcom), words 7 and 15.

This analog voltage is the relative phase of the same modulation on the two carriers of 49.8 and 423.3 Mc. The modulation frequency can be 7.692 or 8.692 kc. The output ranges from 0.2 to 2.8 v. Figure 2.2 shows a calibration curve.

# 49.8 Mc channel carrier amplitude and loop stress

Line Ec. Format E (scientific subcom), word 2.

This analog voltage is alternately the carrier amplitude and the loop stress. The carrier amplitude is the first of the two quantities to be read out after the engineering subframe pulse. A carrier amplitude of 0.2 v represents no RF signal, and 2.85 v represents strong signal with no modulation. A loop stress signal of about 1.6 v represents zero loop stress.

# 423.3 Mc channel carrier amplitude and loop stress

Line Ed. Format E (scientific subcom), word 11.

This is the same as for the 49.8 Mc channel.

# Format D output. Carrier amplitude of the 49.8 and 423.3 Mc channels

Line Ee. Format D, words 4 through 16, and words 20 through 32.

This analog voltage is the carrier amplitude of the 49.8 and the 423.3 Mc channels, alternately. Words 4 and 20 are the 49.8 Mc channel. An output of 0.2 v represents no signal, and 2.92 v represents strong signal with no modulation. At 512 bps, the sun pulse causes the output to be 0.2 v for a duration of two word times, occurring asynchronously with the format.

#### RECEIVER SYSTEM

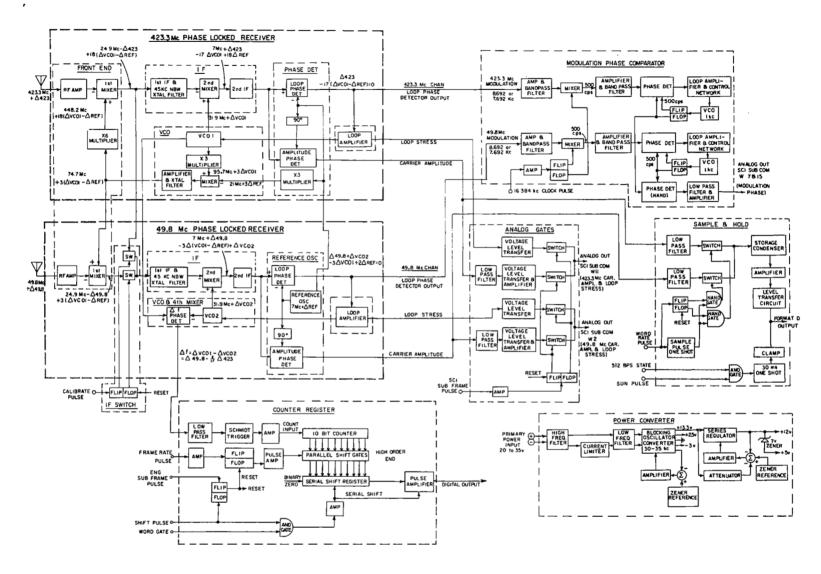

The block diagram, Figure 3.1, page 21, shows the whole receiver system.

# 3.1 - Dual channel phase locked receiver

The RF inputs are 423.3 Mc and 49.8 Mc and are phase modulated. The outputs of the phase locked receiver which will provide scientific information are:

- 1. The  $\triangle f$ , which is the normalized frequency difference between the carriers ( $\triangle f = \left| f_{49.8} \frac{2}{17} f_{423.3} \right|$ ).

- 2. The demodulated modulation from the loop phase detectors.

- 3. The carrier amplitude (the output of the amplitude phase detector), which is proportional to the signal to noise ratio, when the limiters are limiting on noise.

Additional outputs are the loop stress which, together with the carrier amplitude, are used to monitor the operation of the receiver.

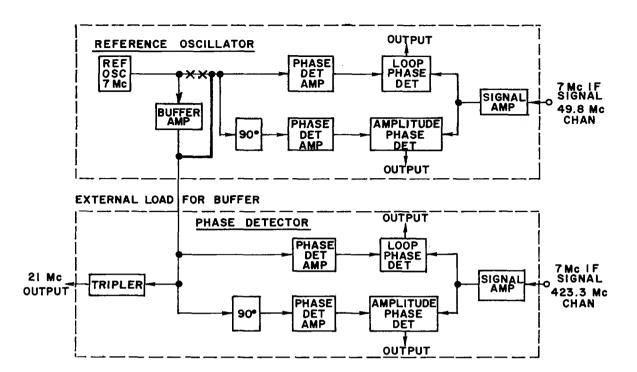

# 3.1.1 - 423.3 Mc phase locked receiver

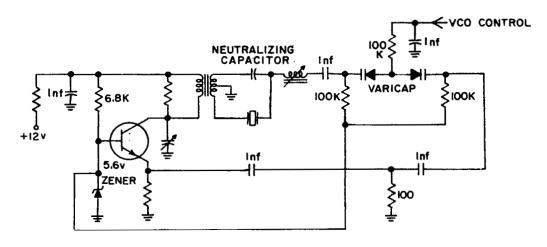

The 423.3 Mc channel is a coherent phase lock loop. The VCO-1 is controlled by the output of the loop phase detector; and the loop amplifier, which includes the control network.

The basic frequency in the receiver is 24.9 Mc. The input at 423.3 Mc is 17 x 24.9 Mc. The local oscillator frequency of the first mixer is 448.8 Mc = 18 x 24.9 Mc. The first IF is 24.9 Mc. The second IF is operating at an arbitrarily chosen 7 Mc, instead of some harmonic of 24.9 Mc. The reason for this is to avoid producing 24.9 Mc or its harmonics at high levels, in order to keep these harmonics from leaking into the inputs of the receiver or the first IF, where they could cause self lock.

The 423.3 Mc phase lock loop is coherent, despite the use of the 7 Mc second IF and the 7 Mc reference oscillator. The phase lock loop is coherent with the difference between the VCO-1 and the reference oscillator frequencies: 31.9 - 7.0 = 24.9 Mc.

The third harmonics of the VCO and reference oscillator are generated before mixing to prevent undesired harmonics of 24.9 Mc, especially

the first and second, from being produced. The 74.7 Mc third mixer output is multiplied by 6 to obtain the first mixer local oscillator frequency.

# 3.1.2 - 49.8 Mc phase locked receiver

The 49.8 Mc channel is phase locked, but not coherent. Like the 423.3 Mc channel, the VCO-2 is controlled by the output of the loop phase detector for the 49.8 Mc channel through the loop amplifier, which includes the control network.

The local oscillator frequency (74.7 Mc) for the first mixer is derived from the 423.3 Mc channel. Hence, the first mixer local oscillator frequency is coherent with the 423.3 Mc carrier and not with the 49.8 Mc carrier. The 74.7 Mc local oscillator could have been generated separately for the 49.8 Mc channel, but instead, it is derived from the 423.3 Mc channel receiver to avoid duplication of circuitry.

# 3.1.3 - Function of parts of the receiver

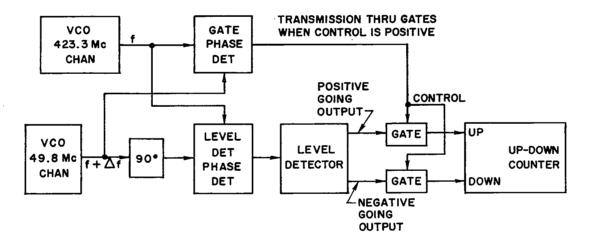

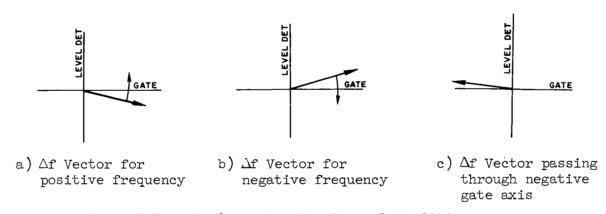

# $\Delta f$ comparison

The output frequency of the  $\Delta f$  phase detector is the same as the difference frequency between the normalized carrier frequencies,  $\Delta f = \left| f_{49.8} - \frac{2}{17} f_{423.3} \right|$ . An increment of frequency has been added to each frequency source in the two channel receiver in the block diagram, Figure 3.1. Each VCO must adjust its frequency increment,  $\Delta VCO-1$  or  $\Delta VCO-2$ , until the output of its corresponding loop phase detector is zero cps. The output of the  $\Delta f$  phase detector is then the difference frequency between the normalized carrier frequencies.

# Phase of the modulation out of the loop phase detector

At the output of the loop phase detector of the 423.3 Mc channel, Figure 3.1, the  $\triangle$ VCO-1 must change in the same direction as the input,  $\triangle$ 423. At the output of the 49.8 Mc channel, the  $\triangle$ VCO-2 must change in the opposite direction to the input,  $\triangle$ 49.8. To obtain this opposite polarity of  $\triangle$ VCO frequency, the loop phase detector for the 49.8 Mc channel must operate on the opposite slope of its detection characteristic

curve than the 423.3 Mc channel loop phase detector. This opposite slope causes output of the two loop phase detectors to be of opposite polarity when the RF carriers are of the same relative modulation phase.

#### Amplitude phase detector

The carrier amplitude (amplitude detector phase output) is detected with a 90° phase shifted reference signal. The phase lock loop holds the output of the loop phase detector near zero volts. This occurs when the reference signal is in quadrature with the input signal. Hence, the 90° phase shifted reference signal is in phase with the signal in the amplitude phase detector.

Thus, the output of the amplitude phase detector is proportional to the amplitude of the phase locked signal at its input. This amplitude is proportional to the signal to noise ratio in the IF noise bandwidth, when the limiters in the IF are limiting on noise. See Appendix A (page A-10) for the equation for A, a more exact expression for the amplitude.

#### Crystal filter in the first IF

The first IF crystal filter has a noise bandwidth of 45 kc. The two crystal filters in one dual receiver are phase matched within 2° of each other over the middle 21 kc of the passband, and are phase symmetric about the center of the passband within 20°. The amplitude is flat to within 0.25 db over the center 21 kc passband. All this accuracy is to insure that the phase of the modulation will be affected equally by both channels.

# 3.1.4 - IF Switch

The IF switch is used to establish the output of the modulation phase detector for zero modulation phase shift at the inputs to the receiver. Once this zero phase point is established, the modulation phase detector output vs. modulation phase can be calibrated by changing the modulation phase at the transmitters. Little error is expected, but this will serve as a check.

The IF switch, upon a calibrate command, disconnects the 49.8 Mc channel IF signal from the first mixer. It connects both first IF inputs

to the same signal, the output of the 423.3 Mc first mixer. An internal reset signal switches the IF switch back to normal operation. When the input signal to both channels is the same, there is zero modulation phase shift. This does not compare the modulation phase shift in the RF and first mixer stages, but since the first mixer stages have a bandwidth of 2 to 3 Mc and the RF stages are even wider, they contribute little to the uncertainty in the modulation phase measurement.

# 3.2 - Modulation phase comparator

The modulation phase comparator, Figure 3.1, measures the relative phase of the detected modulation from the two channels of the receiver and provides a dc cutput proportional to the relative phase. The phase comparator can measure the phase of signals at either 7.692 or 8.692 kc. The two frequencies allow ambiguities up to 7 or 8 cycles of phase shift to be resolved. The output is 0.2 v for -43° (317°), increasing linearly to 2.8 v for 137°, and then decreasing linearly to 0.2 v for 317°. However, the modulation phase shift out of the receiver is 180° when the inputs to the receiver have 0° modulation phase shift, as explained under "Fhase of the modulation out of the loop phase detector" (Section 3.1.3). Therefore, the modulation phase comparator output shifts 180° for modulation at the receiver input, to give 0.2 v for 137° and 2.8 v for 31.7°. This triangular shaped output was used instead of a linear output for a 360° range in order to obtain an error of less than 1 percent of 1 cycle, even though the spacecraft A-D converter quantizes to only 64 levels.

A broad bandpass filter centered on 8 kc precedes the mixer. The filtered signal (7.692 or 8.692 kc) is mixed with 8.192 kc; the output is 500 cps. The 8.192 kc is 500 cps above the input frequency for the 7.692 kc input, and 500 cps below for the 8.692 kc input. Hence, the phase meter is sensitive to either of the two frequencies without switching.

The 500 cps signal is filtered and amplified, and fed to the phase detector of a phase lock loop. The output of the phase detector goes through a control network and a dc amplifier to a 1 kc VCO. The VCO

output is divided by 2 to provide a symmetrical 500 cps signal for the phase detector, and for phase comparison with the other channel.

The second channel is identical to the first. The 16.384 kc pulses from the spacecraft are crystal controlled, and are expanded into the 8.192 kc square wave by an alternating flip flop. This flip flop output is used for the mixers.

The symmetrical 500 cps signal, from the phase locked flip flop from each channel, is cross correlated in the phase detector which is a digital NAND gate. The phase detector output is filtered to eliminate the 500 cps component and to provide additional filtering for the phase measurement.

# 3.3 - Analog gates and gate selector

The analog gates subcommutate the carrier amplitude and loop stress onto an output line for each channel. There are two identical subcommutation channels. Only the 423.3 Mc channel will be discussed. The loop stress voltage ranges from 3 to 7 v; this is transferred to 3 to 0.2 v respectively and connected to the output via the electronic switch. The carrier amplitude ranges from 5 to 3.5 v which is transferred to 0.2 to 2.85 v respectively and alternately connected to the same output as the loop stress via another electronic switch.

The two electronic switches are selected alternately by a flip flop, which changes state with the scientific subcom pulse. This flip flop is synchronized to the spacecraft subcommutation system via the reset signal (see Section 3.4 for the source of the reset signal).

# 3.4 - Counter register

The counter register accumulates the number of cycles of  $\Delta f$ , and shifts the count out periodically in serial form under spacecraft control. The  $\Delta f$  phase detector output has a frequency response from 0 to 80 cps, with the low pass filter of the counter register connected. Normally,  $\Delta f$  will be biased to about 5 cps, to enable detection of positive and negative excursions of  $\Delta f$ . The Schmitt trigger and following amplifier shape the sinusoidal-like  $\Delta f$  phase detector output to drive

the input of the 10 bit binary counter.

The 10 bits of the counter will not fit into one 6 bit spacecraft word. Therefore, part of it must be sent in one word, and the rest in the next word. The contents of the counter are non-destructively shifted in parallel into the 10 bit serial shift register once every two words. We have one word per frame. The frame rate pulse occurs at the beginning of each frame, and is divided by two in a flip flop. Transition of this flip flop to the zero state transfers the contents of the counter to the shift register.

The time to shift out of the serial shift register is defined by the word gate from the spacecraft. Shift pulses are always present. The word gate selects the group of 6 shift pulses in an AND gate. These pulses are amplified and drive the serial shift register and its output pulse amplifier. There is an output pulse for binary one and no pulse for binary zero. The first word out of the shift register is the 6 highest order bits, highest order bit first. The second word is the 4 lowest order bits, highest order bit first, followed by two binary zeros.

A reset pulse is initiated by the engineering frame pulse from the spacecraft (occuring once every 64 frame pulses) and terminated one bit time later by the next bit pulse. The reset is used to synchronize the order of the words out of the shift register with spacecraft telemetry format. The reset pulse is also used for telemetry format synchronization in the sample and hold circuit, and in the analog gates and gate selector.

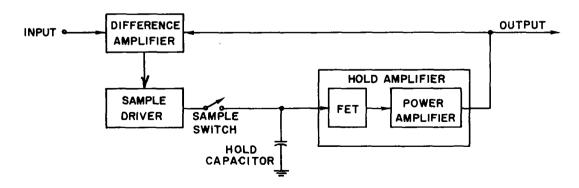

# 3.5 - Sample and hold

The sample and hold circuit, Figure 3.1, samples the carrier amplitude alternately from the 423.3 Mc channel and the 49.8 Mc channel. The "hold" function is necessary because the conversion rate of the spacecraft 6 bit A-D converter can be as slow as 8 bps. The circuit is used to measure the carrier amplitude (actually, signal to noise ratio) versus spacecraft rotation for one rotation of the spacecraft (approximately 1 second). It is also used to obtain the instantaneous carrier amplitude versus time for a measurement involving occultation by the

moon.

Each carrier amplitude signal is filtered by a 10 cps low pass filter. Each filter output is connected to an electronic switch. Either one switch or the other is turned on for 0.5 msec during which time the storage capacitor is charged to the same value as the input. This value is held until the alternate switch is turned on. The low input current hold amplifier, with a gain of one, follows the storage capacitor. A level transfer circuit shifts the amplifier's output voltage from a 5 v base line, going negative to 3.5 v, to an 0.2 v base line, going positive to 3 v. This level transfer circuit has a gain of about two.

The switches are operated by the NANDing of a flip flop output, which determines which switch will be operated; and a one shot output, which determines the 0.5 msec sample time. The word rate pulse triggers the one shot and changes the state of the flip flop. The reset input to the flip flop maintains synchronization with the spacecraft telemetry format.

The sun pulse occurs once each spacecraft rotation, and defines the angular position of the spacecraft. The 30 msec one shot, triggered by the sun pulse, is two words long at the 512 bps rate. Hence, the clamp will clamp the output to zero for at least one whole word, marking the angular position of the spacecraft. The sun pulse is ANDed with the 512 bps state so that at other bit rates, the sun pulse clamp will be inoperative.

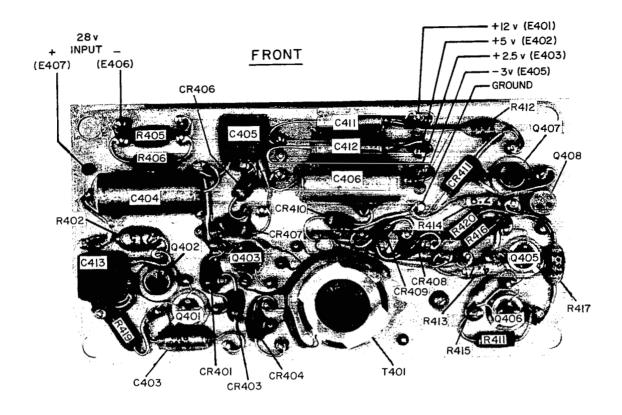

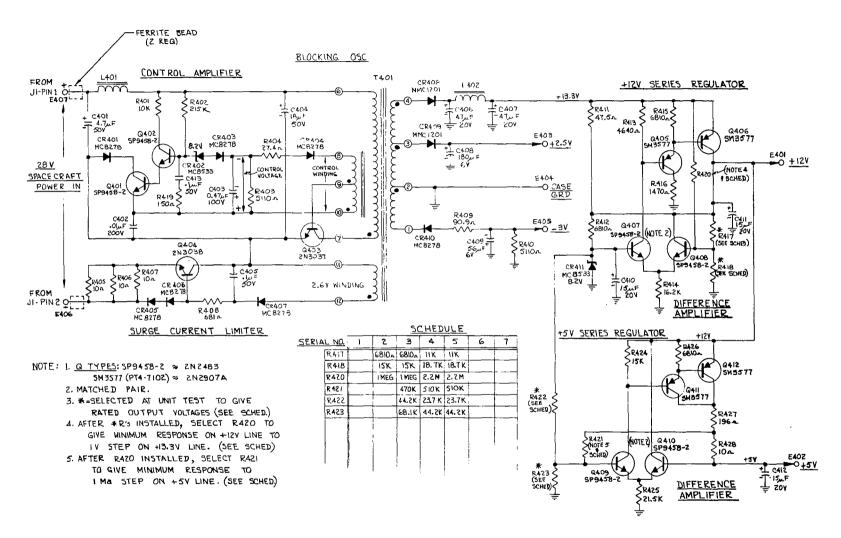

# 3.6 - Power Converter

The power converter, Figure 3.1, converts the nominally 28 v input to the supply voltages required by the system: 12, 5, 2.5 and -3 v. The 28 v input is electrically isolated from ground and from the output supplies in order to eliminate the magnetic field due to ground currents. The blocking oscillator power converter is a constant power type, over a supplied input voltage range of 24 to 33 v. The output voltage change of the blocking oscillator portion of the converter is about 100 mv for a 9 v change in input. This voltage change is sufficiently low for the

2.5 and -3 v supplies. A post regulator for the 12 and 5 v supplies gives an output voltage change of<0.5 mv for the 9 v change in input.

The 28 v input passes first through a high frequency filter (for blocking oscillator frequencies greater than 1 Mc), and then to an active current limiter. The turn on and other transient current surges are limited to less than 250 ma by the current limiter. A low pass filter provides instantaneous peak power to the blocking oscillator and keeps the blocking oscillator transients from the 28 v supply.

The blocking oscillator portion of the converter is controlled by a feedback loop. The output voltage is compared with a zener reference; the difference is amplified and used to control the blocking oscillator base current.

The converter transformer provides 2.5 v and -3 v for direct use, and 13.3 v for the post regulator. The post regulator for the 12 v compares the 12 v with a zener, and the difference is amplified and applied to the series regulator. An additional input from the 13.3 v supply into the summing point further reduces the effect of input transients.

The 5~v is dropped from the 12 v through a zener diode.

A more complete description of the blocking oscillator converter (without the current limiter or series regulator) can be found in Reference 3.

Figure 3.1 - Block Diagram of the Whole Dual Channel Receiver

|   | <br> |  |

|---|------|--|

| - |      |  |

|   |      |  |

|   |      |  |

|   |      |  |

|   |      |  |

|   |      |  |

#### 4. CIRCUIT DESCRIPTION AND SPECIFICATION FOR EACH SUBASSEMBLY

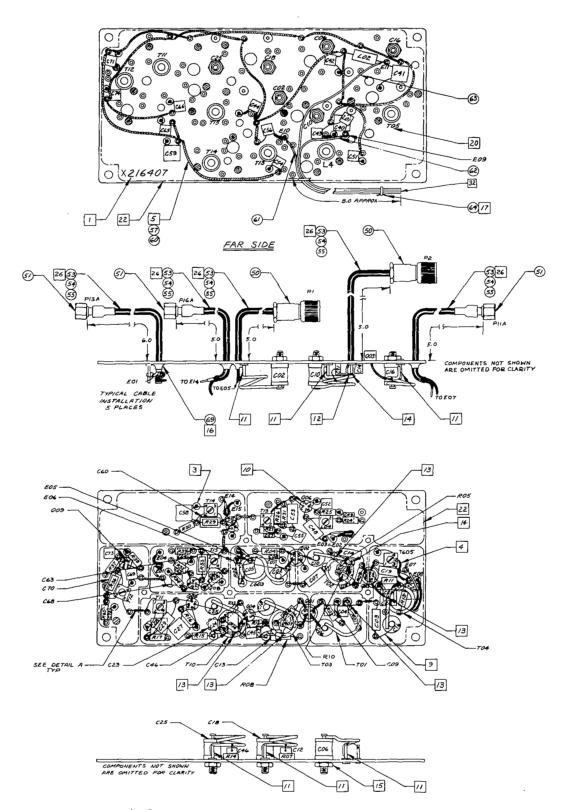

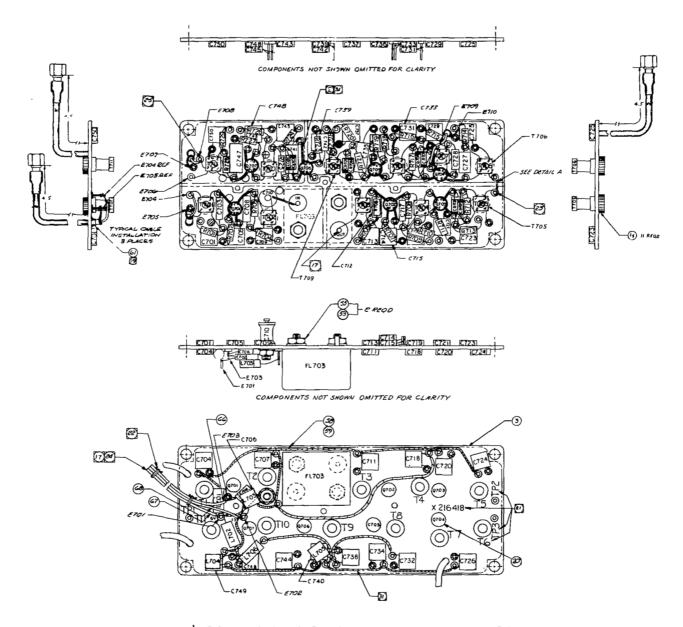

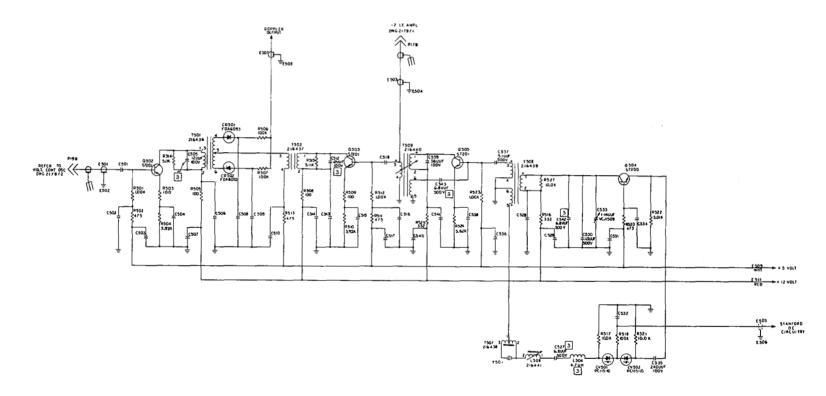

This section contains the specifications and circuit description of each subassembly. Schematics, pictorial diagrams and photographs of the various units are located at the end of the section beginning on page 57.

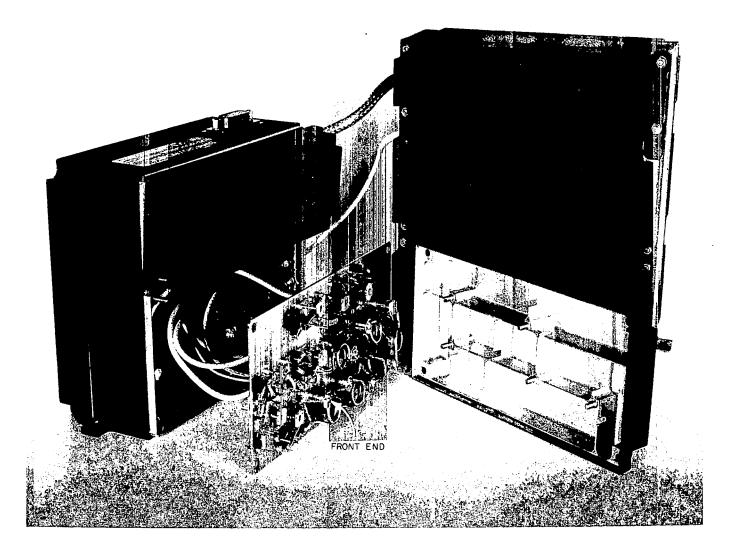

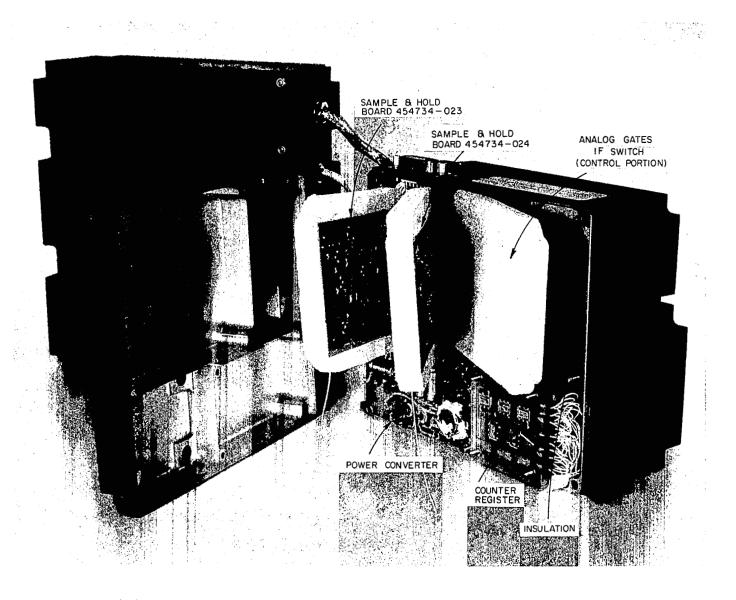

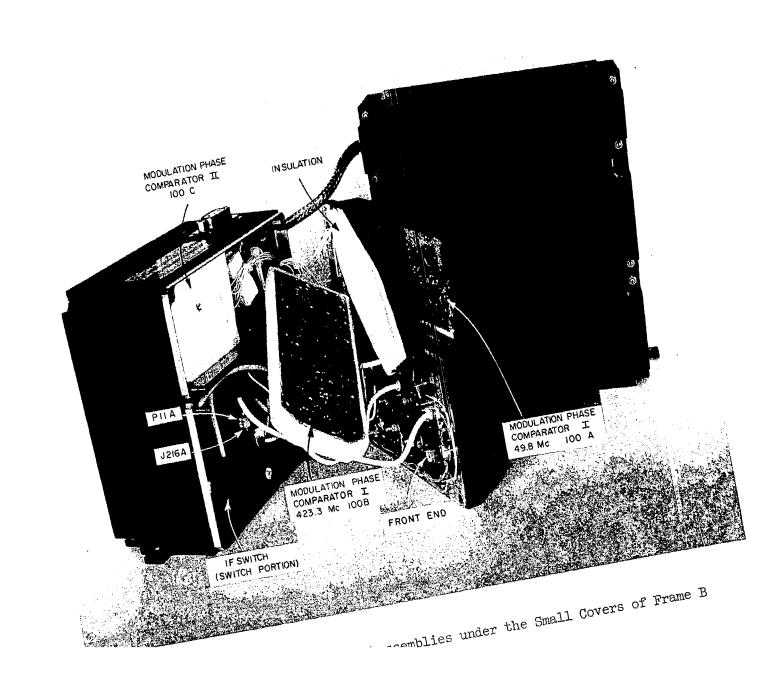

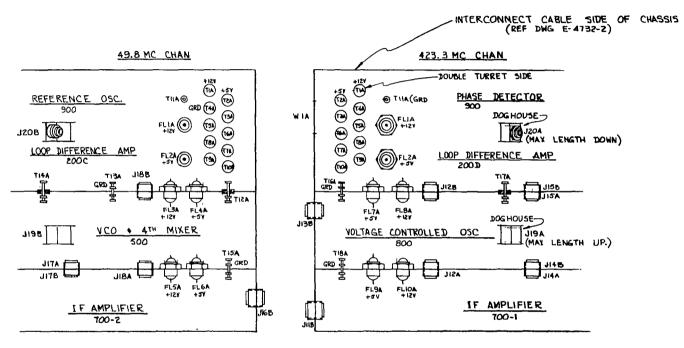

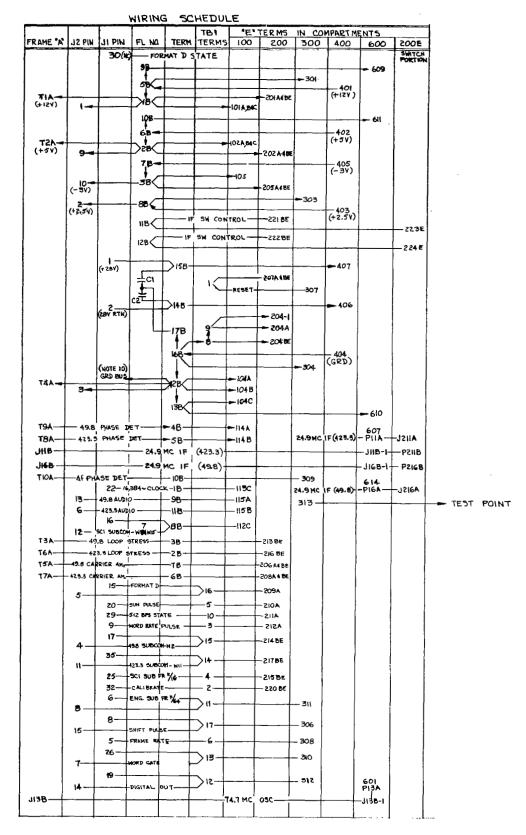

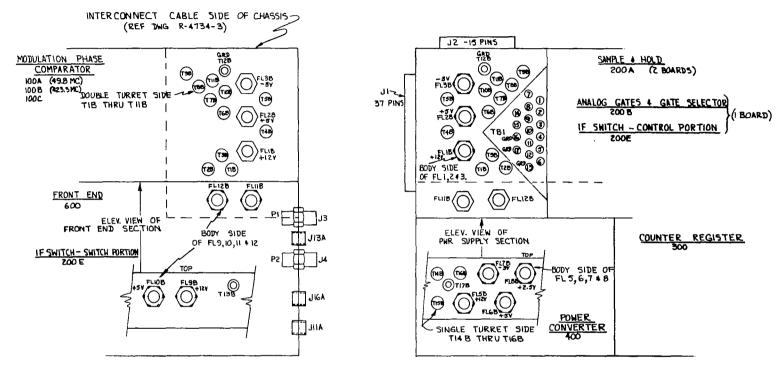

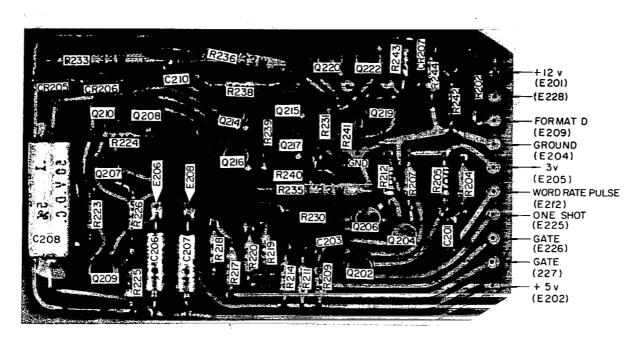

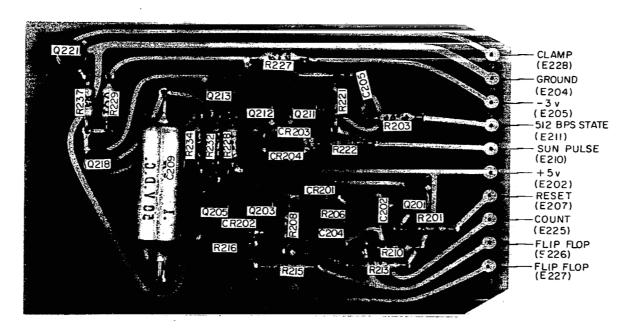

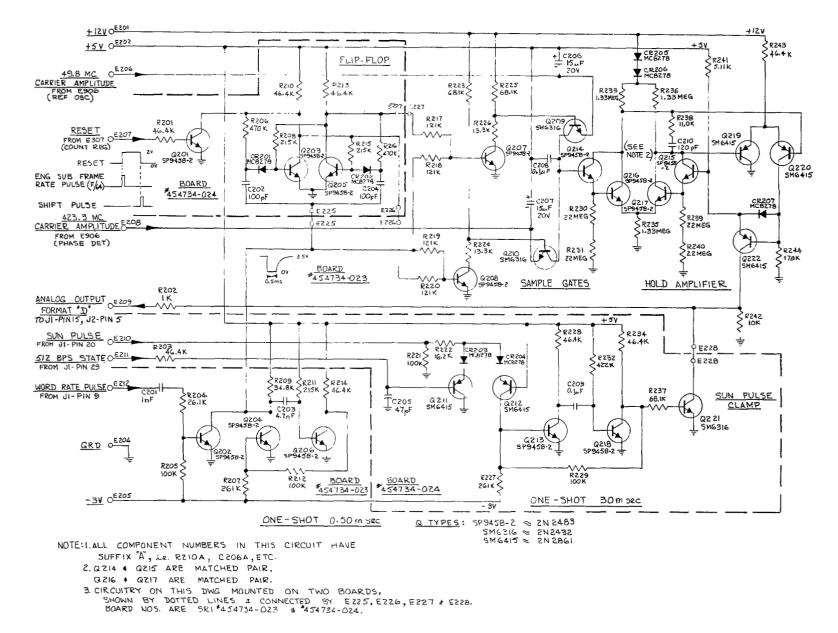

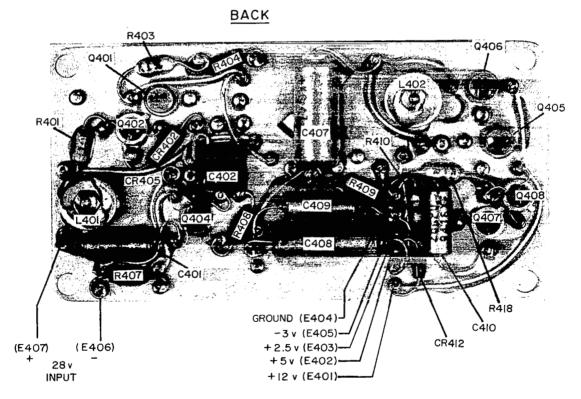

Figures 4.2, 4.3, 4.4, and 4.5 are photographs which show the location of subassemblies in the receiver. Table 4.1 lists pin connections for all external connectors. The frame A wiring diagram is Figure 4.6 and frame B wiring diagram is Figure 4.7.