https://ntrs.nasa.gov/search.jsp?R=19660007125 2020-03-16T23:09:40+00:00Z

RELIABLE MINIATURE SPACEBORNE MEMORY

Interim Engineering Report

November 19, 1964 Through July 26, 1965

Contract No. NAS5-9518

National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland

6414 FACILITY FORM 603 (ACCESSIC (THRU) (CODE) INASA CR R TMX OR AD NUMBER) (CATEGORY)

| GPO PRICE \$_     |      |

|-------------------|------|

| CFSTI PRICE(S) \$ |      |

| Hard copy (HC)    |      |

| Microfiche (MF)   | 1.57 |

ff 653 July 65

DIVISION OF SPERRY RAND CORPORATION P.O. BOX 500 - BLUE BELL, PENNSYLVANIÁ

# RELIABLE MINIATURE SPACEBORNE MEMORY

\$

Interim Engineering Report

1

November 19, 1964 Through July 26, 1965

Contract No. NAS5-9518

# National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland

DIVISION OF SPERRY RAND CORPORATION P.O. BOX 500 - BLUE BELL, PENNSYLVANIA

,

# Abstract

This report presents the results of work done during the 8-month design phase (Phase I) of an 18-month contract to design and build an engineering model of a miniature spaceborne memory. The memory system which has been designed has the following characteristics:

| Memory Element    | Magnetic, thin film, plated-wire.                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Capacity  | 2,949,120 bits.                                                                                                                                                                  |

| Speed             | 500-kilocycle serial bit rate.<br>125-kilocycle 4-bit character rate.                                                                                                            |

| Organization      | Two independent half-memories of 1,474,560 bits per-<br>mit simultaneous reading and writing.                                                                                    |

| Operating Mode    | Nondestructive readout, serially addressed buffer memories.                                                                                                                      |

| Input Voltage     | $-24.5 \pm 2\%$ volts.                                                                                                                                                           |

| Input Power       | 0.5 watt - Standby (design objective).<br>1.5 watt - Continuous 500-kilocycle writing (design objective).                                                                        |

| Temperature Range | Operating, -20 <sup>°</sup> C to + 80 <sup>°</sup> C.<br>Storage, +150 <sup>°</sup> C for 48 hours.                                                                              |

| Memory Stack      | The 1,474,560 bits of memory, 2592 diodes, and 96 transistors associated with the memory stack fit into a space 6 inches by 13 inches by 2.2 inches in-cluding an external case. |

#### Foreword

This report describes work performed during the 8-month phase I of the 18-month contract NAS5-9518 for a Reliable Miniature Spaceborne Memory. This contract with the UNIVAC Division of Sperry Rand Corporation, P. O. Box 500, Blue Bell, Pa., has been directed by Mr. A. Whitehead and Mrs. M. Townsend, NASA Goddard Space Flight Center Technical Officer.

The work is being performed under the supervision of Mr. G. A. Fedde, Engineering Manager of the Advanced Memory Development Laboratory. Mr. W. J. Bartik, Manager of the Advanced Electronics Section, provides technical consultation and general management of the contract. The following persons are assigned directly to the project and, along with others, have made valuable contributions: E. N. Schwartz, R. Mosenkis, C. A. Nelson, and A. L. Salamon of the Advanced Memory Development Laboratory; Dr. J. S. Mathias and F. J. Hanson of the Materials & Processes Research Laboratory; G. R. Reid and R. W. Hoffman of the Advanced Packaging Laboratory; and P. C. Candelori and R. A. Grossman of the Reliability & Engineering Laboratory.

# CONTENTS

Heading

.

## Title

Page

# SECTION 1. INTRODUCTION

# SECTION 2. MEMORY SYSTEM ORGANIZATION

| 2.1. | Interface With External Equipment | 3/4 |

|------|-----------------------------------|-----|

| 2.2. | Organization for Minimum Power    | 7/8 |

| 2.3. | Timing and Control Functions      | 15  |

| 2.4. | Reliability Calculations          | 15  |

| 2.5. | Summary                           | 15  |

## SECTION 3. MEMORY CIRCUIT DESIGNS

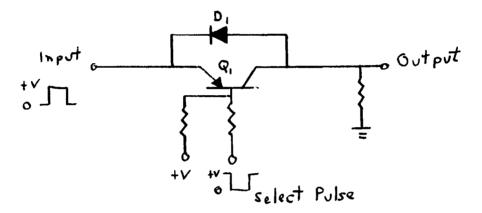

| 3.1.   | Logic and Control Circuits               | 21         |

|--------|------------------------------------------|------------|

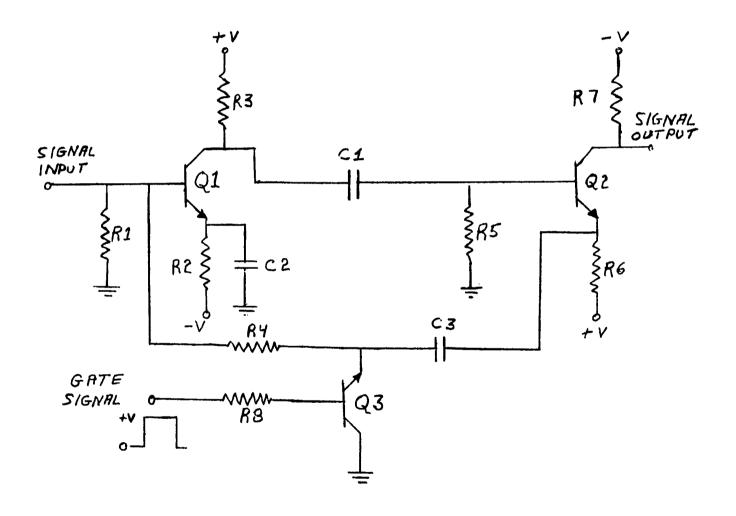

| 3.2.   | Information Path Circuits                | 21         |

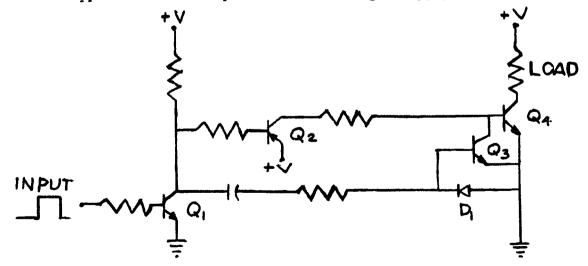

| 3.2.1. | Read Amplifier                           | 22         |

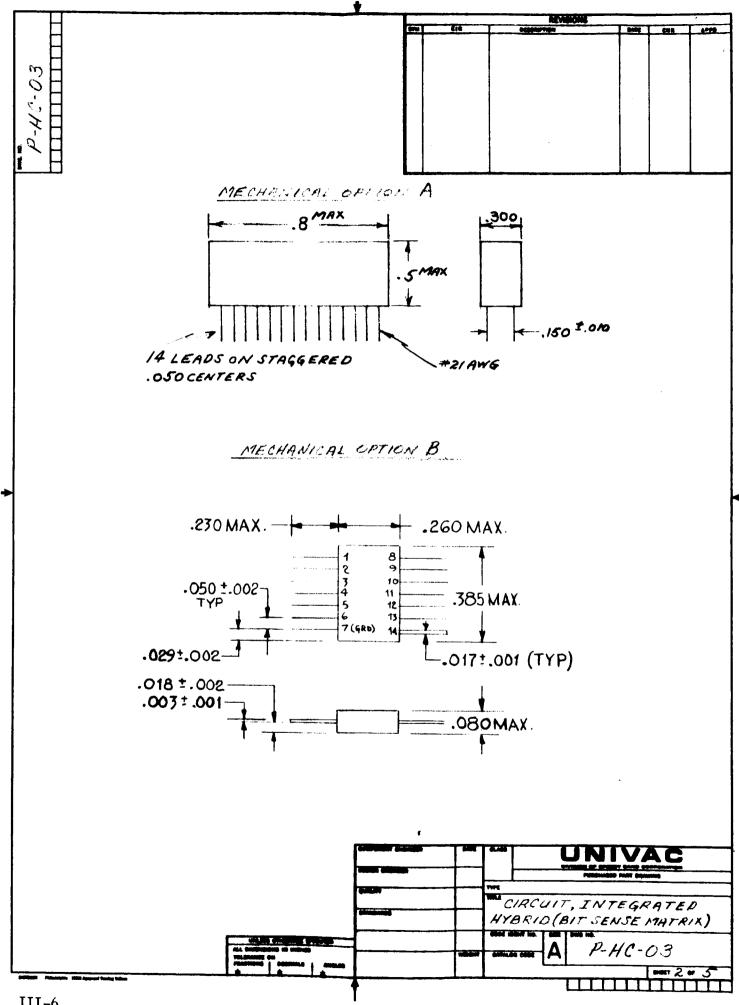

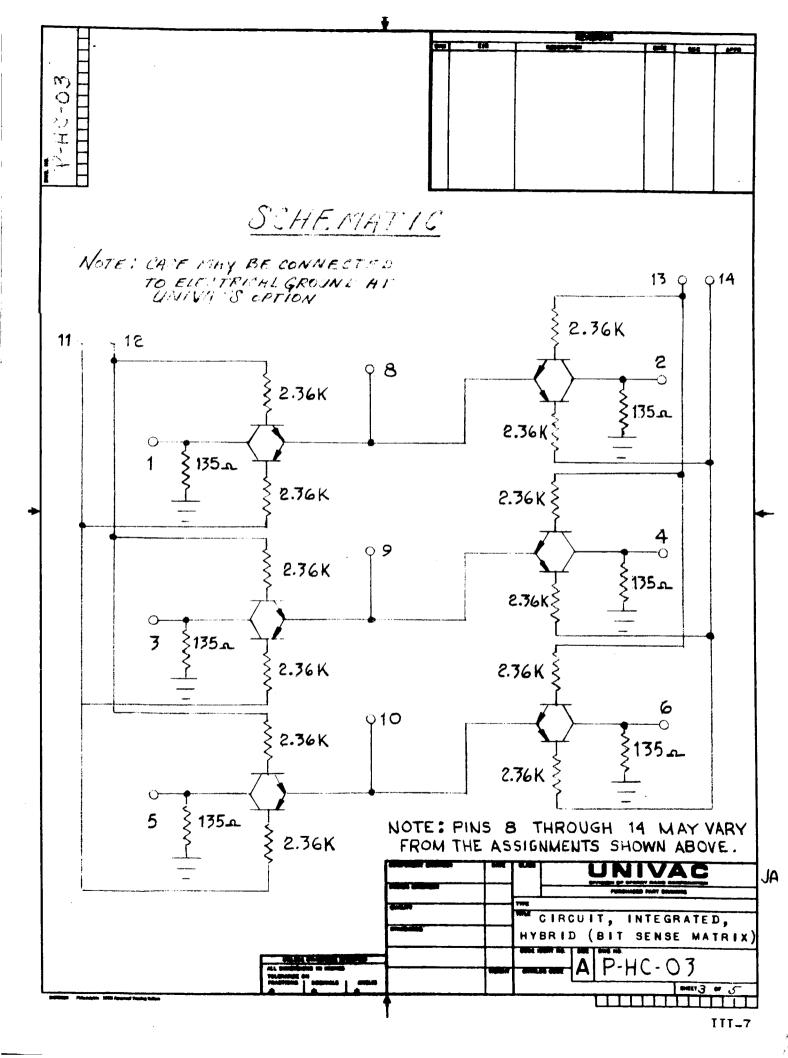

| 3.2.2. | Bit-Sense Switch Matrix                  | 22         |

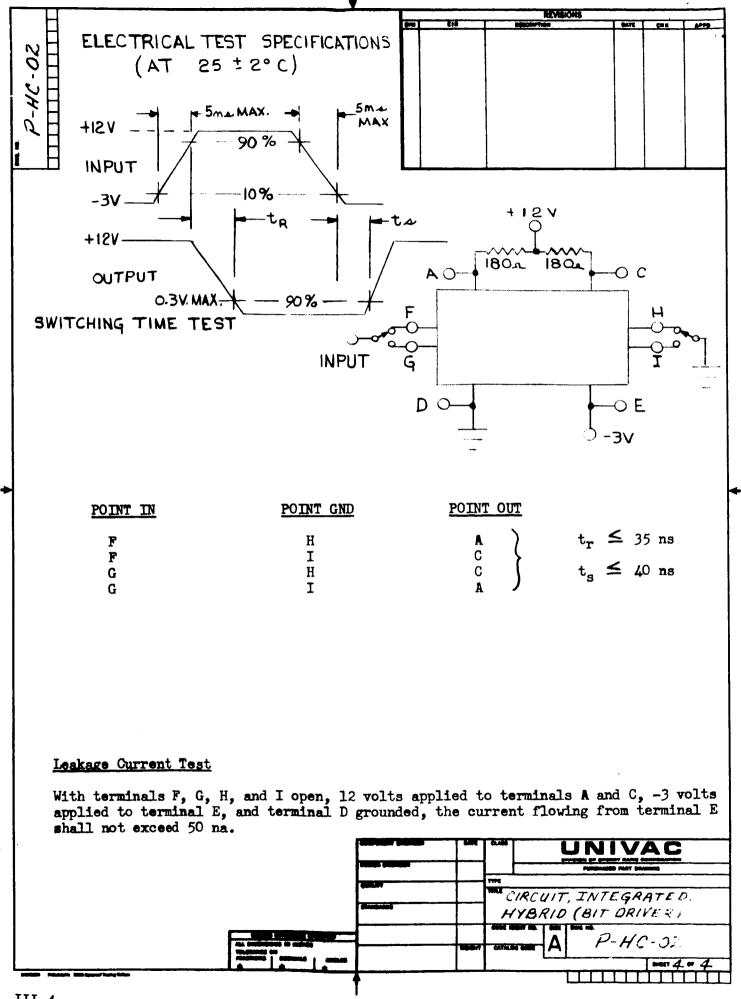

| 3.2.3. | Bit Driver                               | 22         |

| 3.2.4. | Matrix Drivers                           | <b>2</b> 3 |

| 3.2.5. | Bit Path Interface Circuits              | 23         |

| 3.3.   | Word-Line Drive, Selection, and Counter  |            |

|        | Circuits                                 | 23         |

| 3.3.1. | Word Current Source                      | 24         |

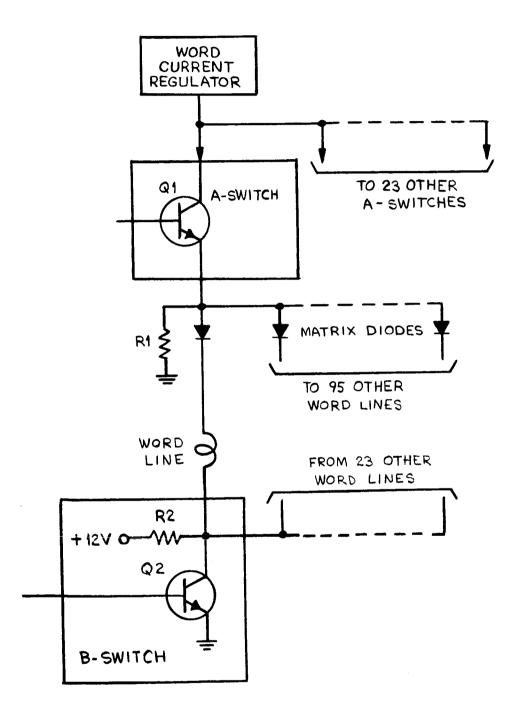

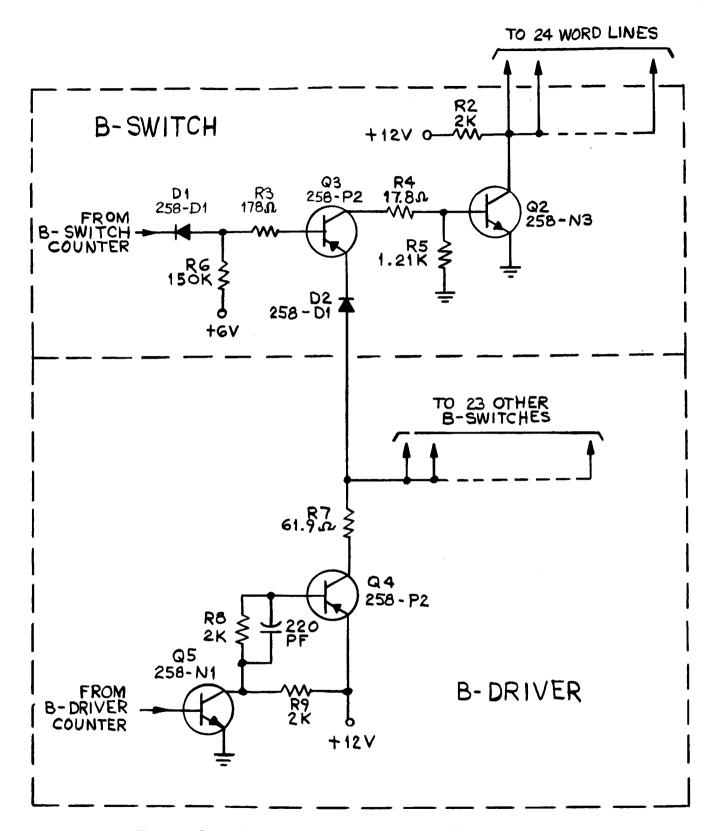

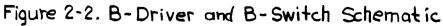

| 3.3.2. | Word Current Switches and Switch Drivers | <b>24</b>  |

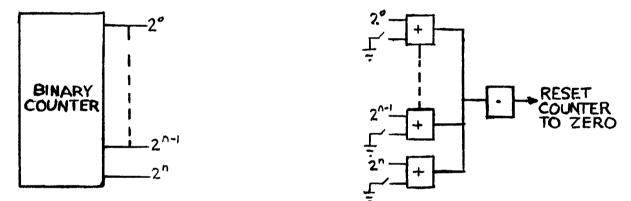

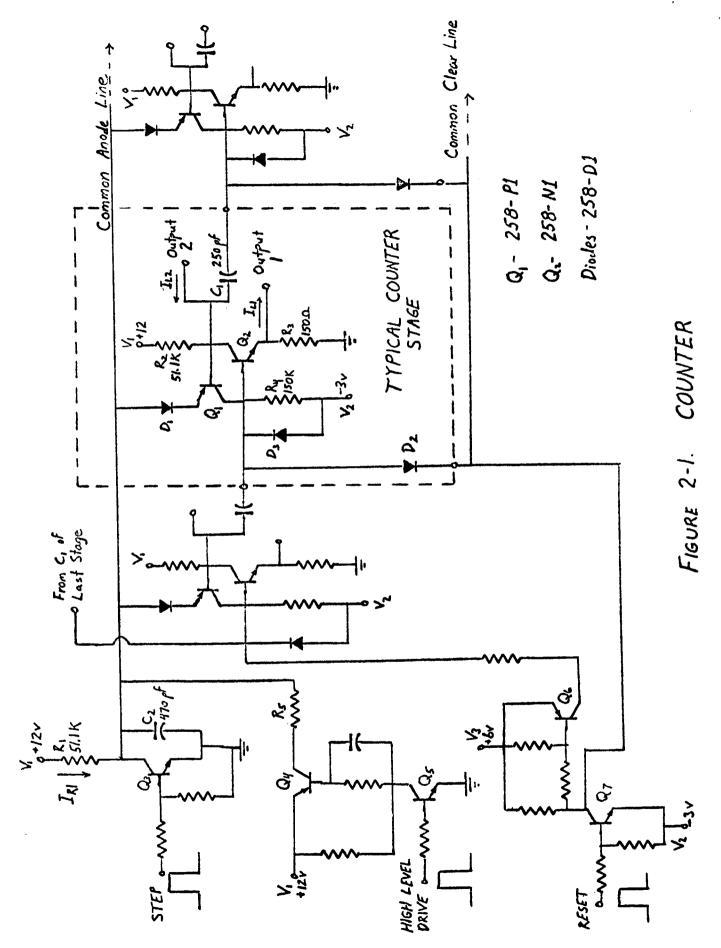

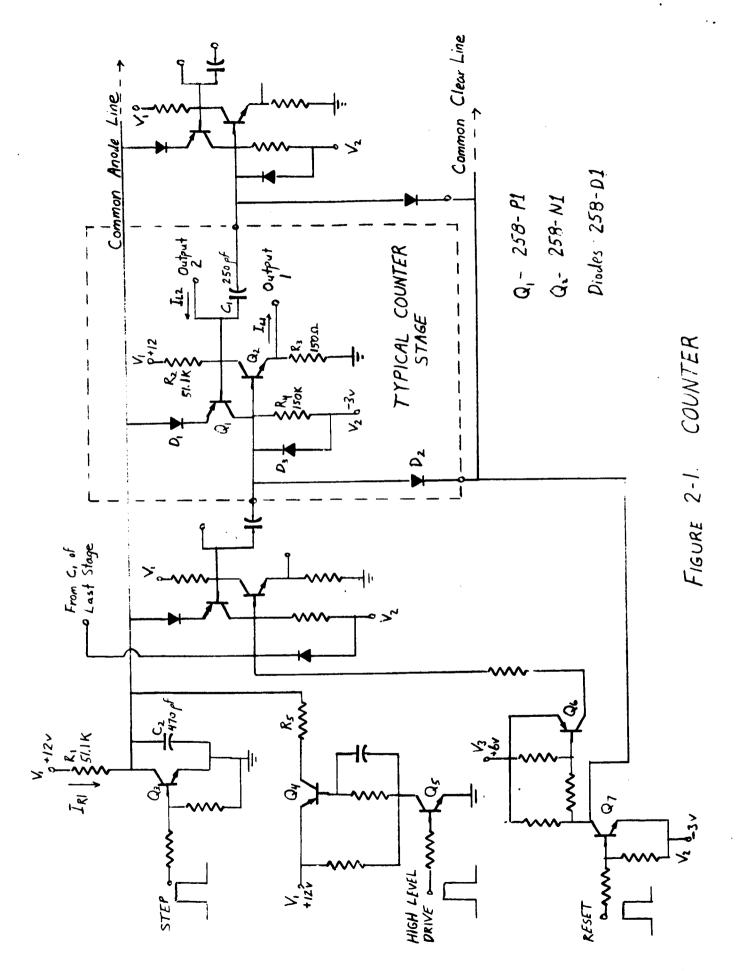

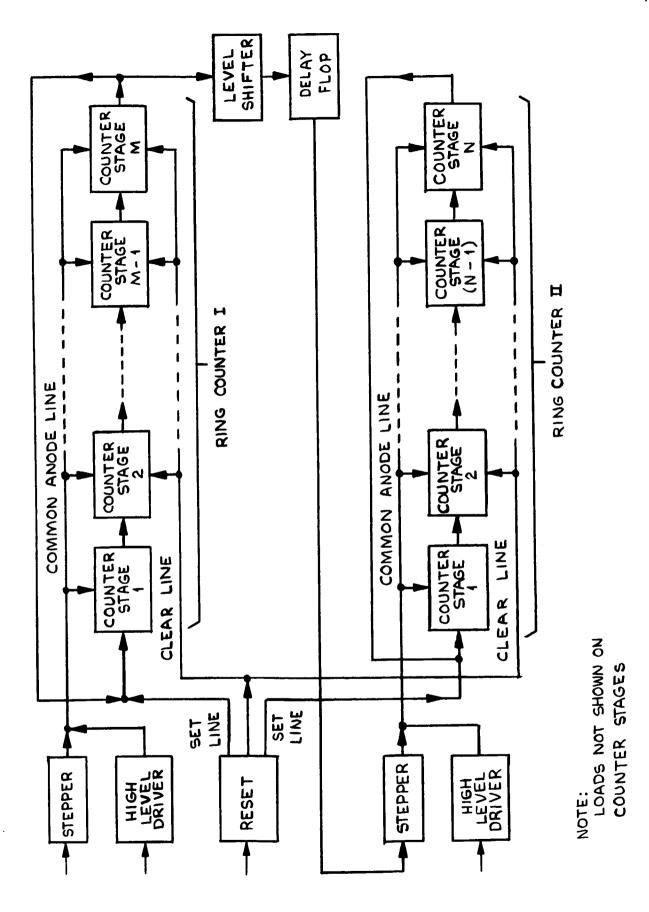

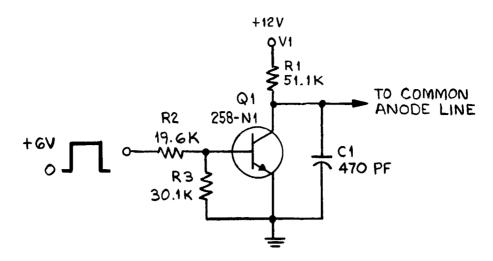

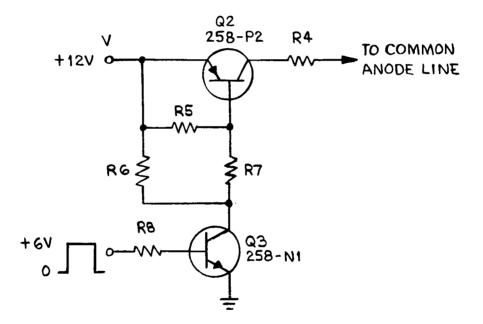

| 3.3.3. | Low Power Ring Counter                   | <b>24</b>  |

| 3.3.4. | Ring Counter Auxiliary Circuits          | <b>24</b>  |

|        | 0                                        |            |

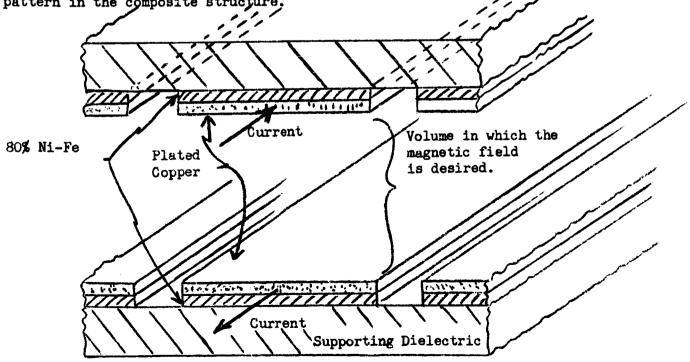

## SECTION 4. THE PLATED-WIRE MEMORY ELEMENT

| 4.1.   | Plated-Wire Test Specifications      | 27 |

|--------|--------------------------------------|----|

| 4.1.1. | Phase I                              | 29 |

| 4.1.2. | Phase II                             | 41 |

| 4.2.   | Corrosion Protection of Plated Wires | 51 |

| 4.3.   | Life Tests                           | 51 |

# SECTION 5. MEMORY PACKAGING AND INTERCONNECTIONS

| 5.1. | Packaging Summary . |   | • | • |   | • | • | • | • | • | • | • | • | 53 |

|------|---------------------|---|---|---|---|---|---|---|---|---|---|---|---|----|

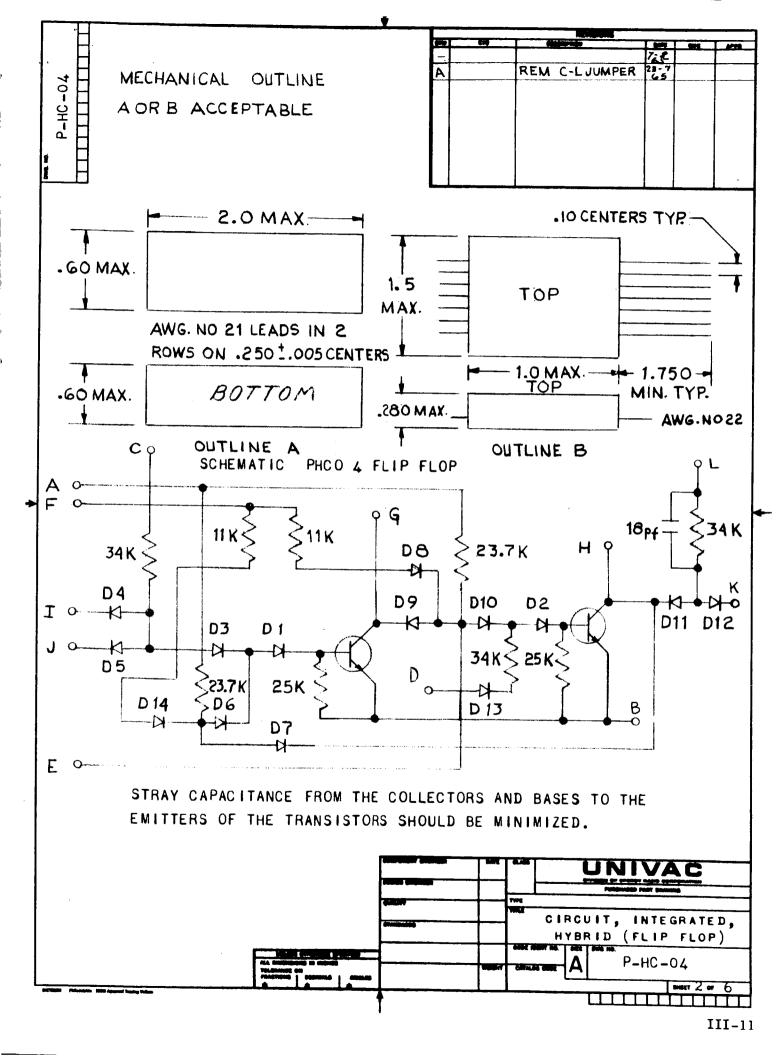

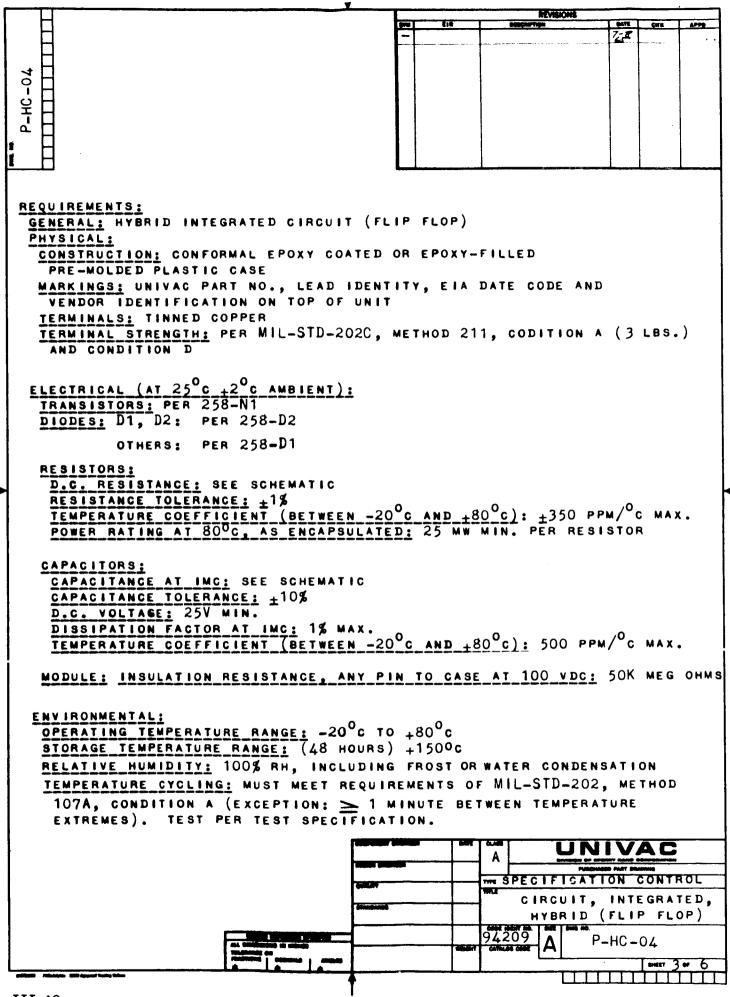

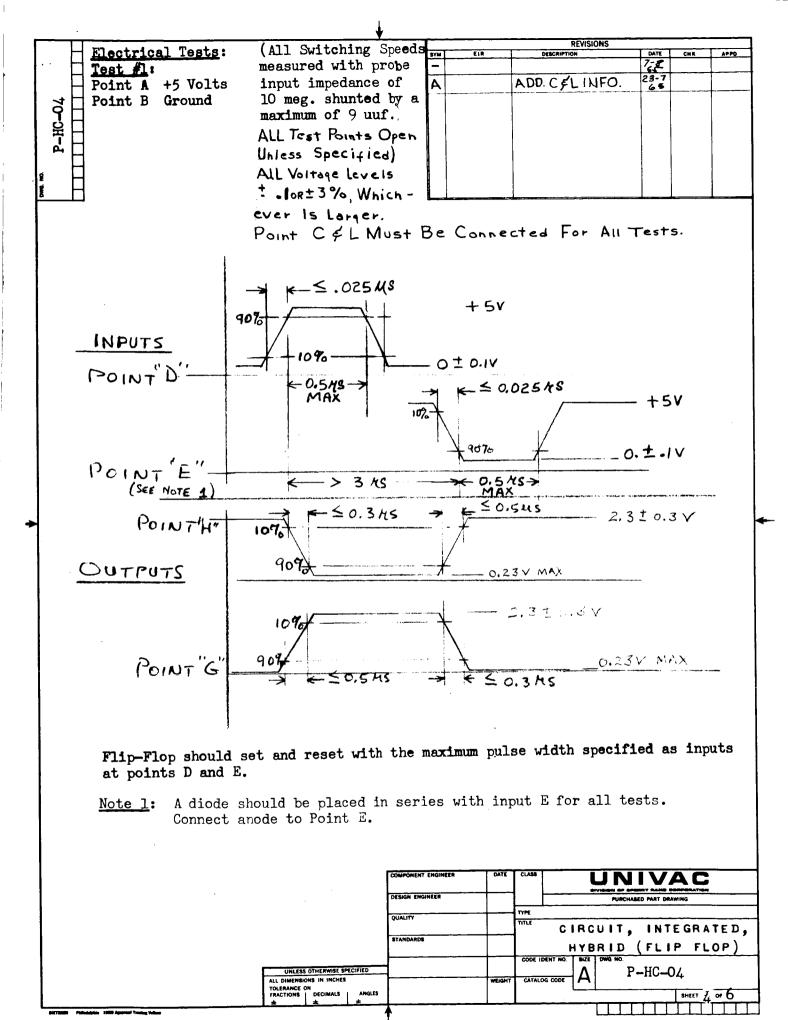

| 5.2. | Hybrid Circuits     |   |   |   |   |   |   |   |   |   |   |   |   | 54 |

| 5.3. | Glossary            | • | • | • | • | • | • | • | • | • | • | • | • | 54 |

#### Title

Page

\_ \_

| 5.4.   | Mechanical Design                          | 55             |

|--------|--------------------------------------------|----------------|

| 5.4.1. | The Design Criteria Applicable to a Memory |                |

|        | Plane                                      | 55             |

| 5.4.2. | Environmental Design Criteria              | 56             |

| 5.4.3. | Mechanical Configuration of Entire Memory  |                |

|        |                                            |                |

|        | Package                                    | 56             |

| 5.5.   |                                            | 56<br>58<br>58 |

# SECTION 6. NEW TECHNOLOGY REPORT

# APPENDIX I. DETAILED DESCRIPTIONS OF ALL CIRCUITS DESIGNED FOR THE MINIATURE SPACEBORNE MEMORY

APPENDIX II. COMPONENT PARTS LIST

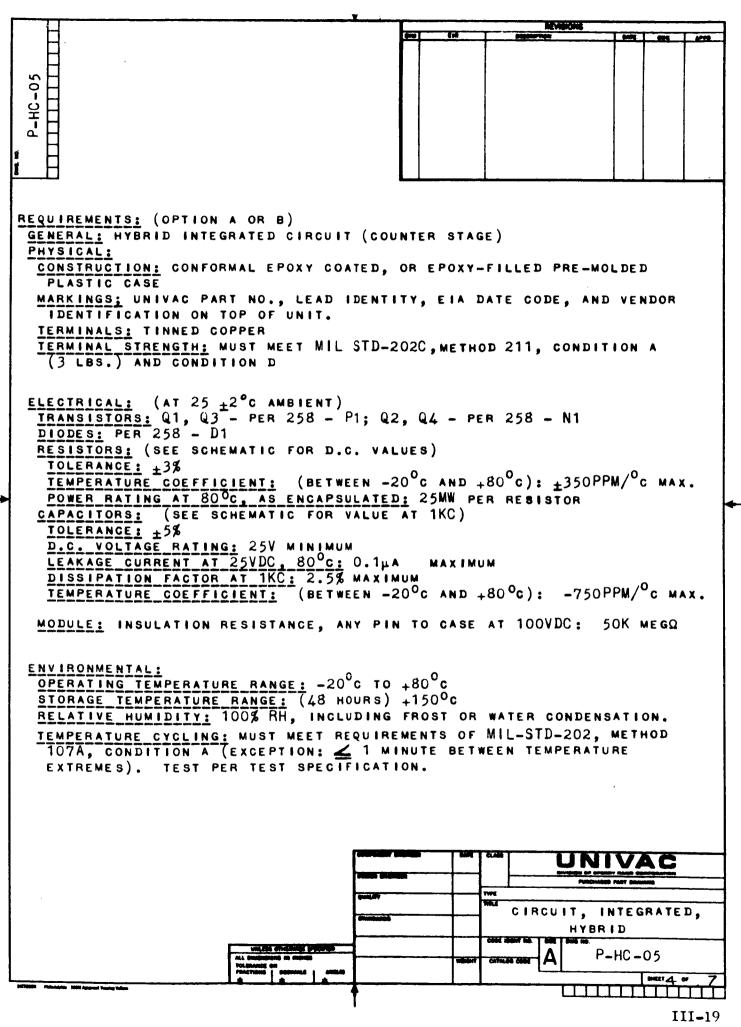

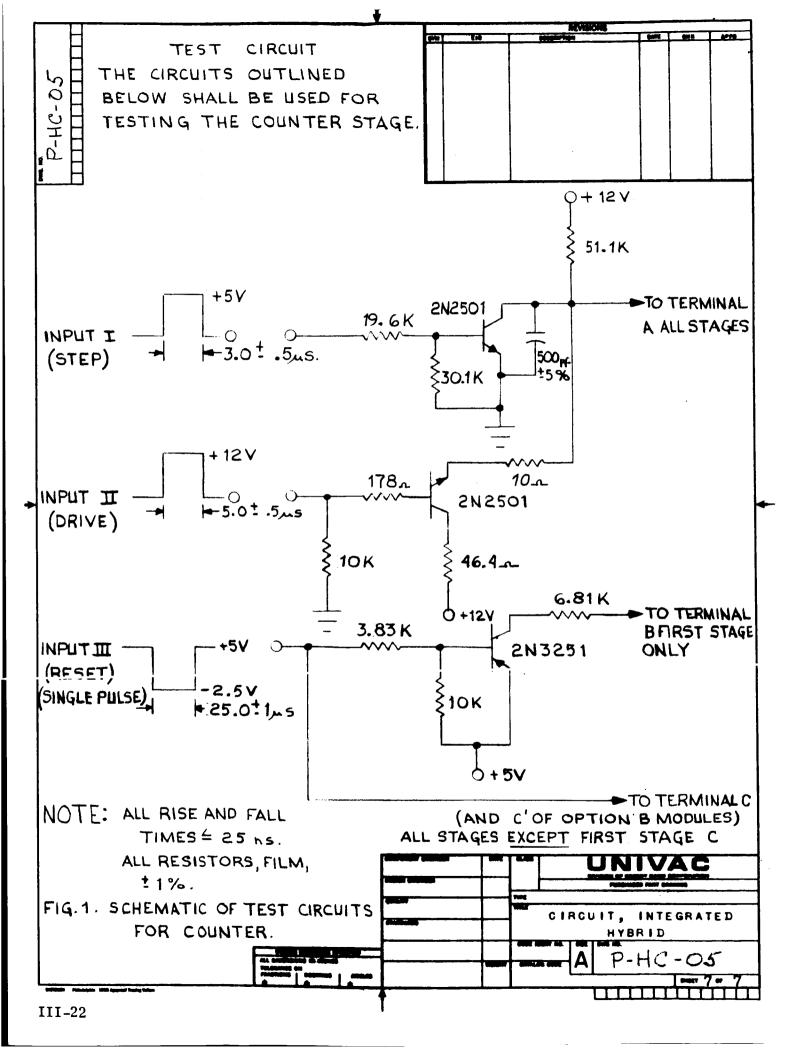

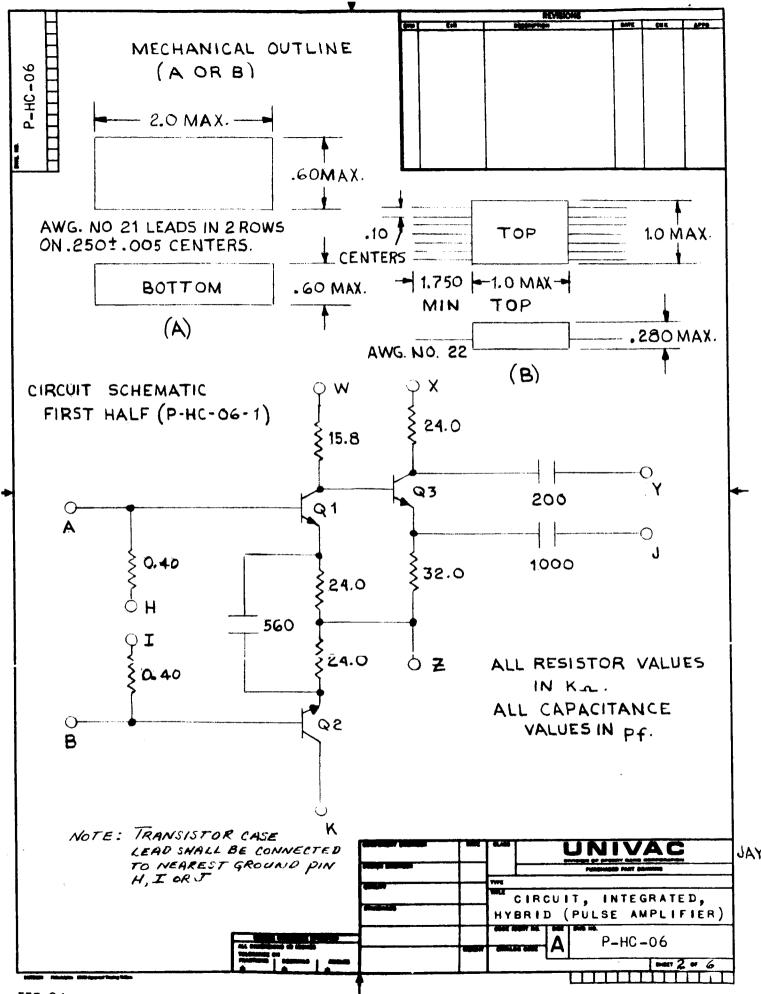

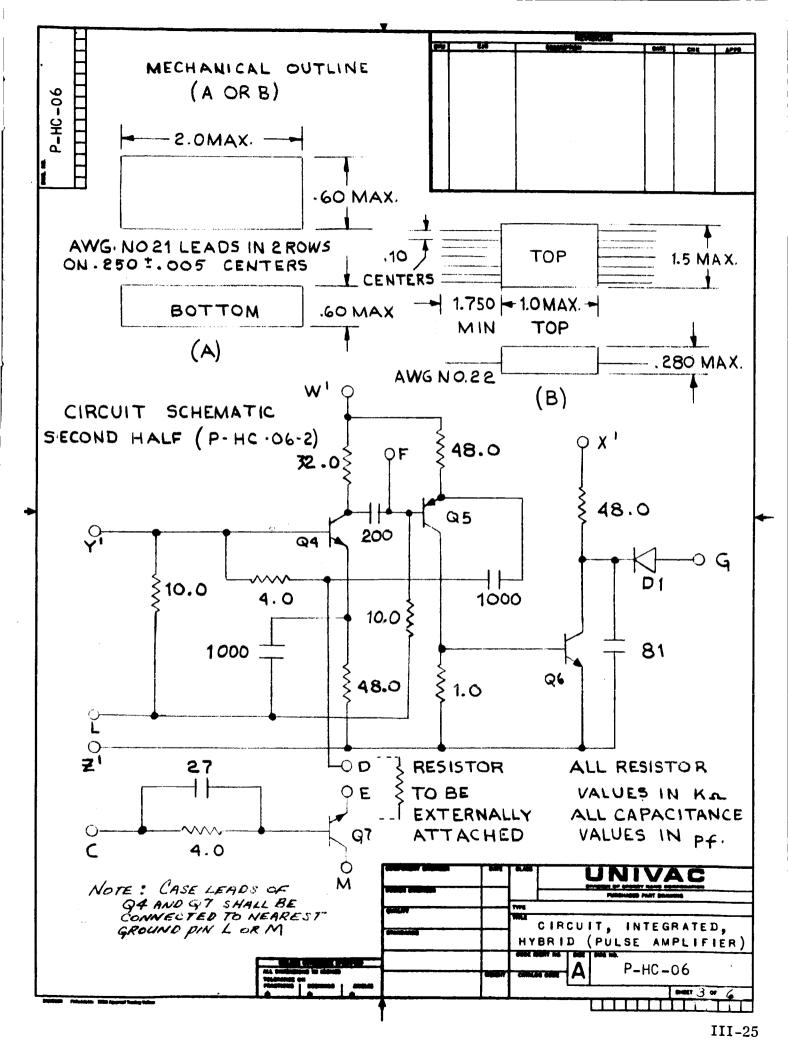

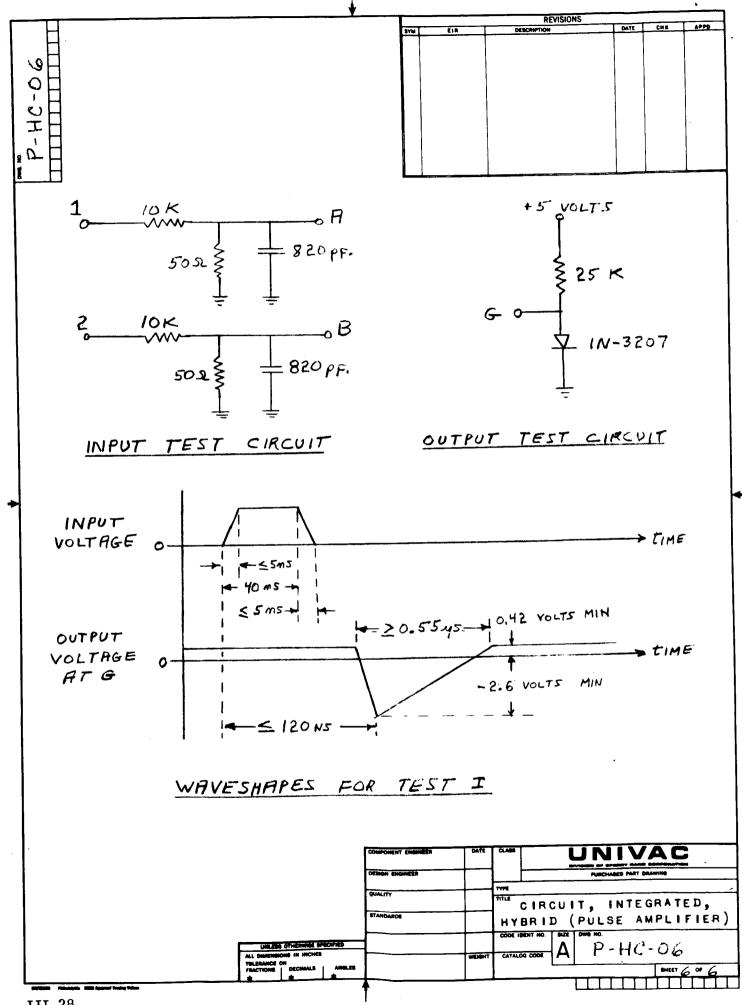

# APPENDIX III. SPECIFICATIONS FOR HYBRID CIRCUITS AND SEMICONDUCTORS

APPENDIX IV. CORROSION PROTECTION OF PLATED WIRES

> APPENDIX V. MATERIALS REPORT NUMBER ONE

# ILLUSTRATIONS

Figure

•

۰,

# Title

Page

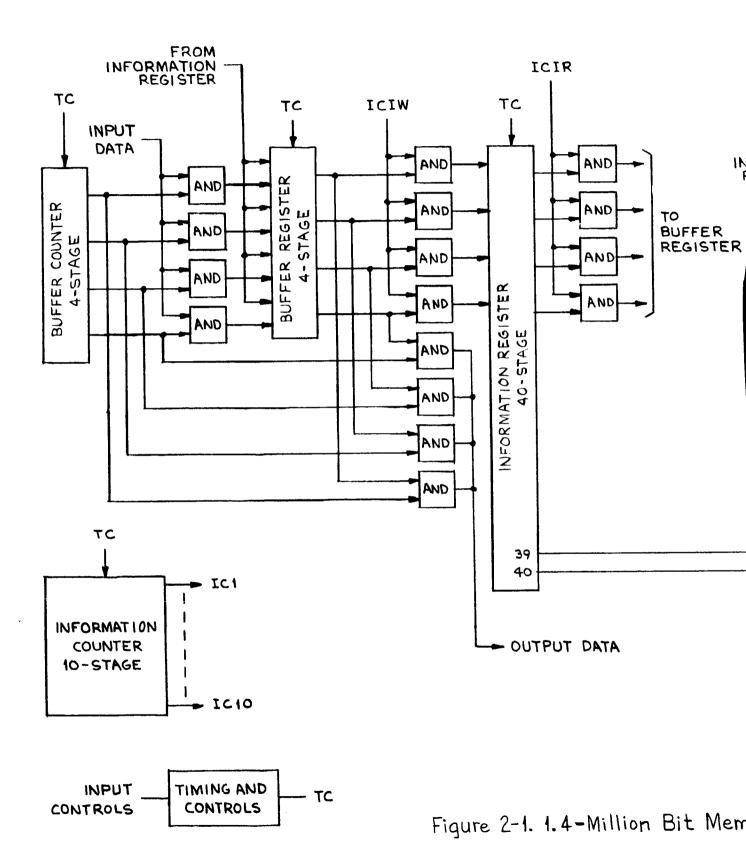

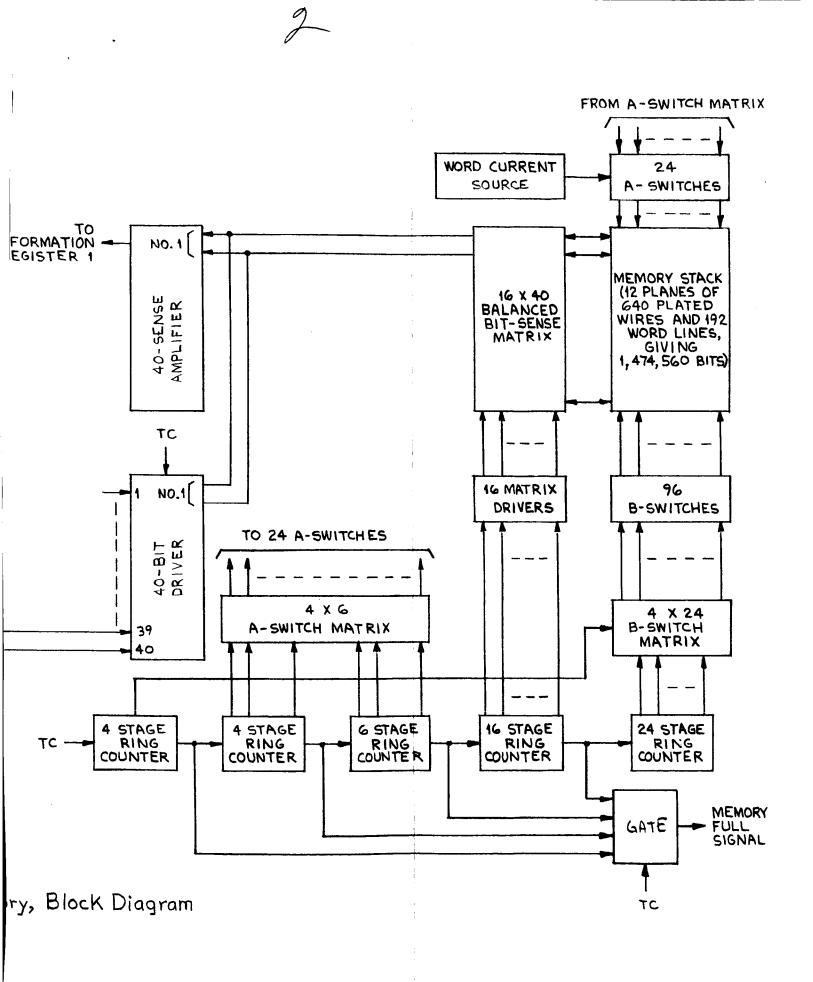

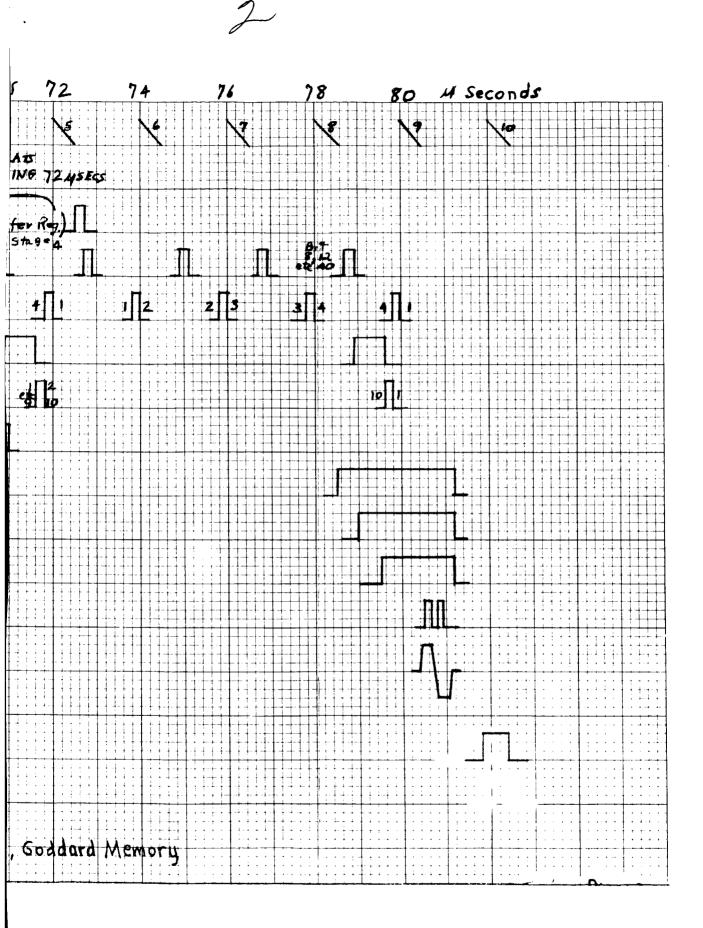

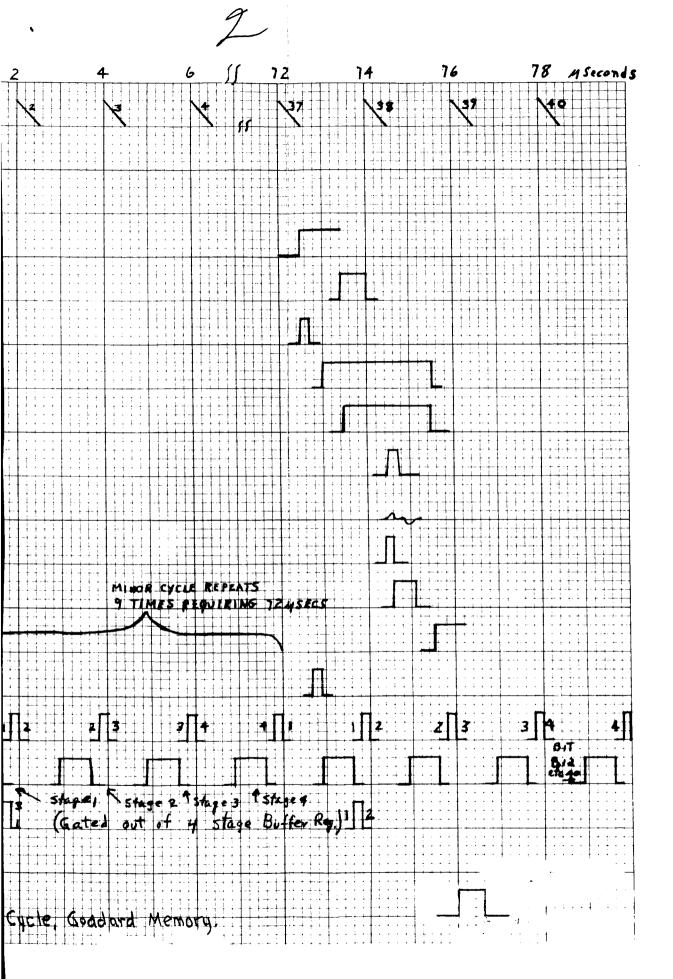

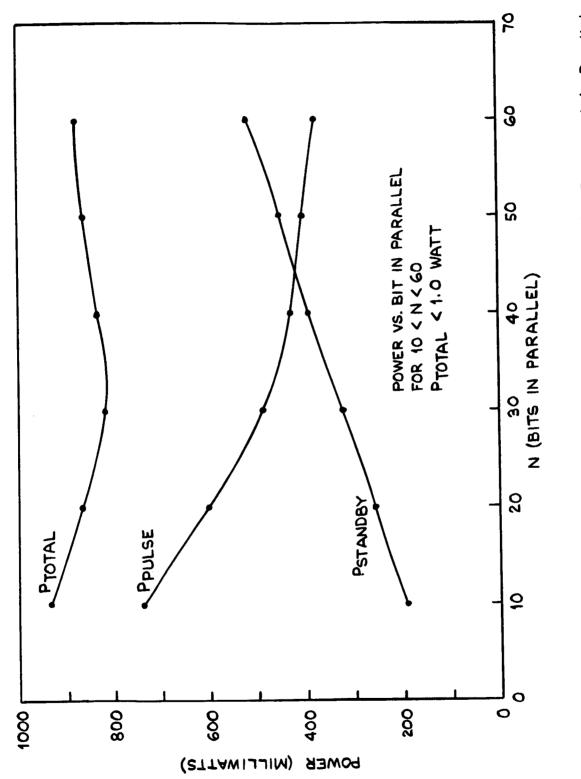

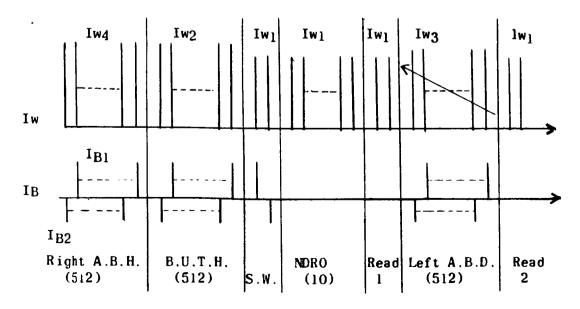

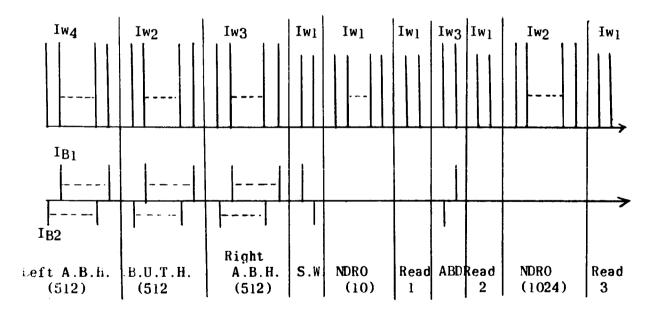

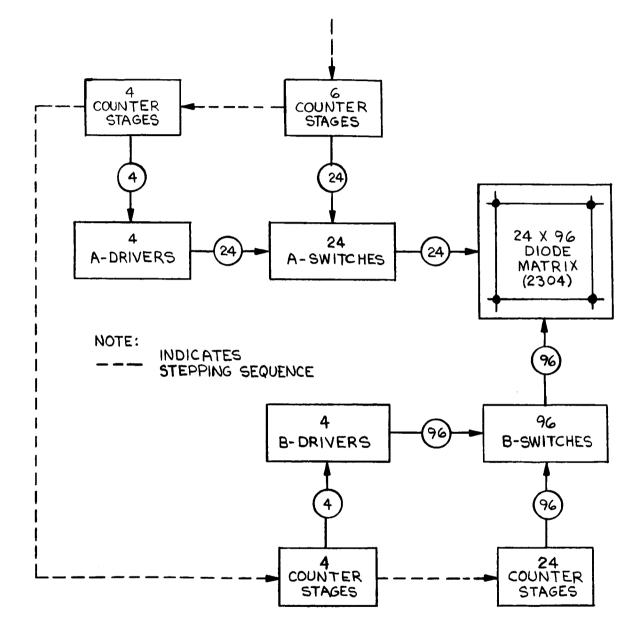

| 2-2.       Timing Diagram, Write Cycle.       9/10         2-3.       Timing Diagram, Read Cycle.       11/12         2-4.       Power Consumption vs. Number of Bits Proceessed in Parallel.       11/12         2-4.       Power Consumption vs. Number of Bits Proceessed in Parallel.       14         4-1.       Wire Plater and Tester .       26         4-2.       Information Storage on Plated Wire .       26         4-3.       Read and Write Operations.       26         4-4.       Phase Modulated Write .       26         4-5.       Iwp and Iwd vs. No. of Adjacent Wires       26         4-6.       Iwp and Iwd vs. No. of Adjacent Wires       34         4-6.       Iwp and Iwd vs. No. of Adjacent Wires.       36         4-7.       Operating Parameters vs. Word Strap Width       38         4-8.       Operating Parameters vs. Word Strap Width       39         4-9.       Operating Parameters vs. Word Strap Width       41         11.       Operating Parameters vs. Word Strap Width       41         4-10.       Operating Parameters vs. Word Strap Width       41         4-11.       Operating Parameters vs. Word Strap Width       42         4-12.       Operating Parameters vs. Word Strap Width       42         4-13. <th>2-1.</th> <th>1.4-Million-Bit Memory, Block Diagram</th> <th>5/6</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1.  | 1.4-Million-Bit Memory, Block Diagram          | 5/6   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------|-------|

| 2-3.       Timing Diagram, Read Cycle       11/12         2-4.       Power Consumption vs. Number of Bits Proceessed in Parallel       11/12         2-4.       Power Consumption vs. Number of Bits Proceessed in Parallel       14         4-1.       Wire Plater and Tester       14         4-1.       Wire Plater and Tester       26         4-2.       Information Storage on Plated Wire       26         4-3.       Read and Write Operations       26         4-4.       Phase Modulated Write.       26         4-4.       Phase Modulated Write.       26         4-5.       Iwp and Iwd vs. No. of Adjacent Wires       28         (Plane EP1)        34         4-6.       Iwp and Iwd vs. No. of Adjacent Wires.       36         4-7.       Operating Parameters vs. Word Strap Width       36         (Copper)         38         4-8.       Operating Parameters vs. Word Strap Width       39         4-9.       Operating Parameters vs. Word Strap Width       41         (I Turn Mu-metal Word Lines).       43       4-10.         Operating Parameters vs. Word Strap Width       34       44         4-11.       Operating Parameters vs. Word Strap Width       34      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-2.  | Timing Diagram, Write Cycle                    | 9/10  |

| 2-4.       Power Consumption vs. Number of Bits Proc-<br>essed in Parallel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-3.  |                                                | •     |

| essed in Parallel144-1.Wire Plater and Tester264-2.Information Storage on Plated Wire264-3.Read and Write Operations264-3.Read and Write Operations264-4.Phase Modulated Write284-5.Iwp and Iwd vs. No. of Adjacent Wires284-6.Iwp and Iwd vs. No. of Adjacent Wires344-6.Iwp and Iwd vs. No. of Adjacent Wires364-7.Operating Parameters vs. Word Strap Width384-8.Operating Parameters vs. Word Strap Width394-9.Operating Parameters vs. Word Strap Width394-10.Operating Parameters vs. Word Strap Width41(1 Turn Copper Word Lines).444-11.Operating Parameters vs. Word Strap Width444-12.Operating Parameters vs. Word Strap Width44(½ Turn Cu Word Lines).474-13.Operating Parameters vs. Word Strap Width474-14.Operating Parameters vs. Word Strap Width495-1.Miniature Spaceborne Memory Frame Side 1575-2.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge505-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                                                | ,     |

| <ul> <li>4-2. Information Storage on Plated Wire</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                | 14    |

| <ul> <li>4-2. Information Storage on Plated Wire</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                |       |

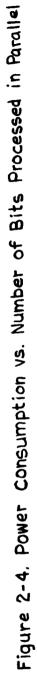

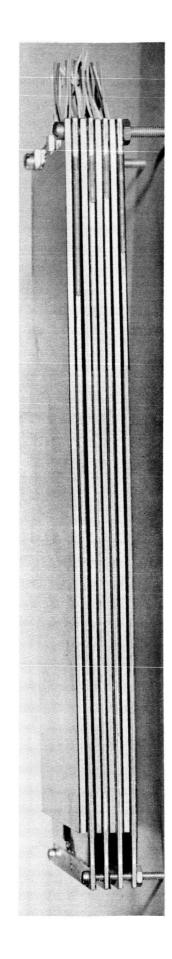

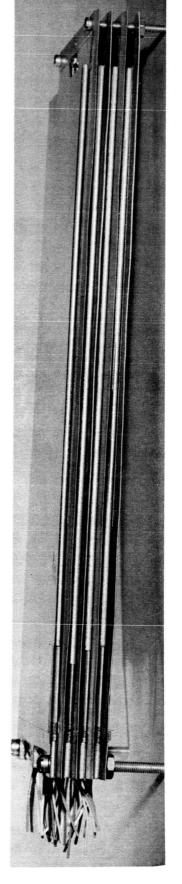

| <ul> <li>4-3. Read and Write Operations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1.  |                                                | 26    |

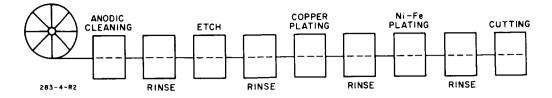

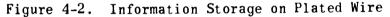

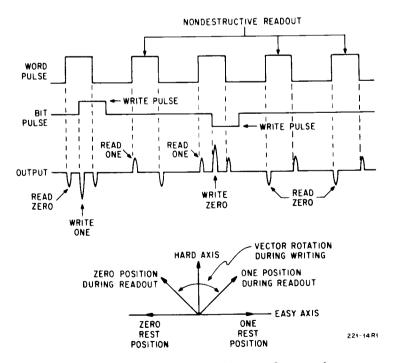

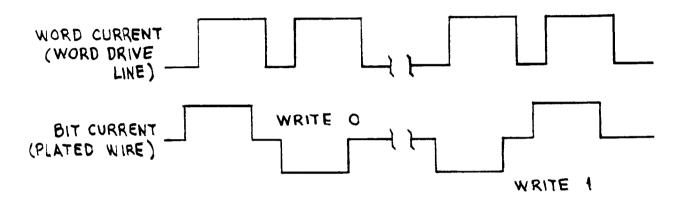

| <ul> <li>4-4. Phase Modulated Write</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-2.  |                                                | 26    |

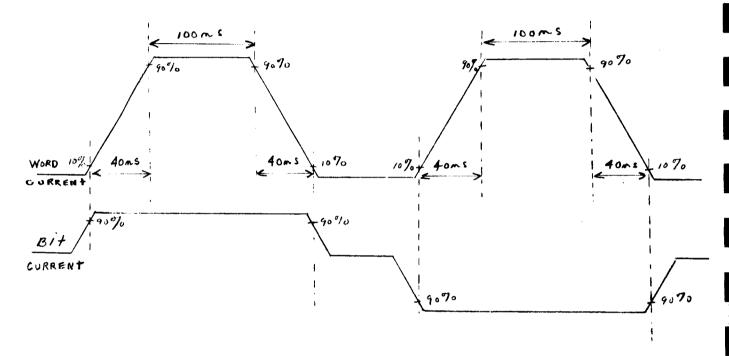

| <ul> <li>4-5. Iwp and Iwd vs. No. of Adjacent Wires<br/>(Plane EP<sub>1</sub>)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-3.  |                                                | 26    |

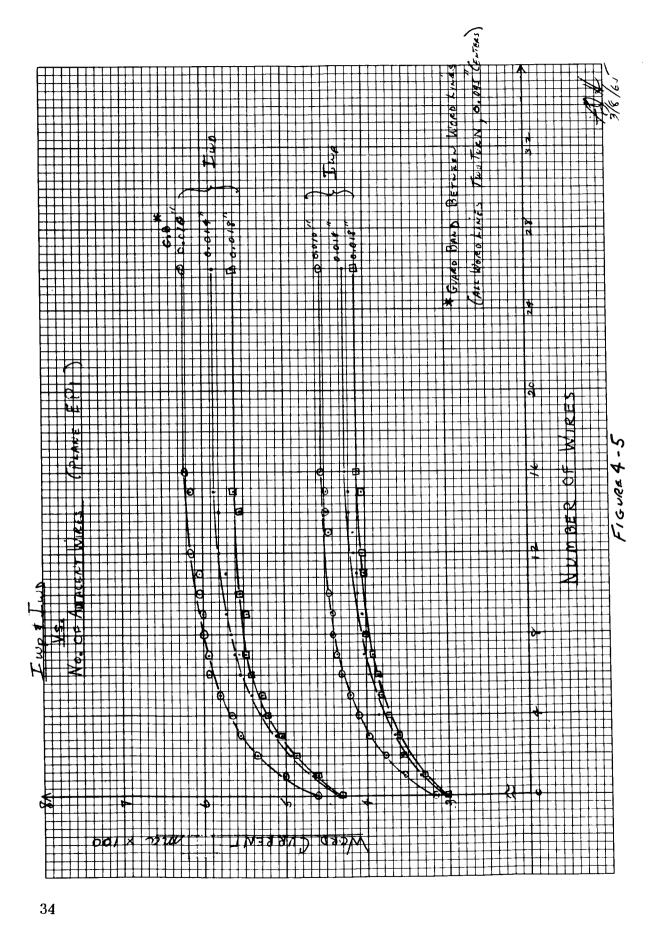

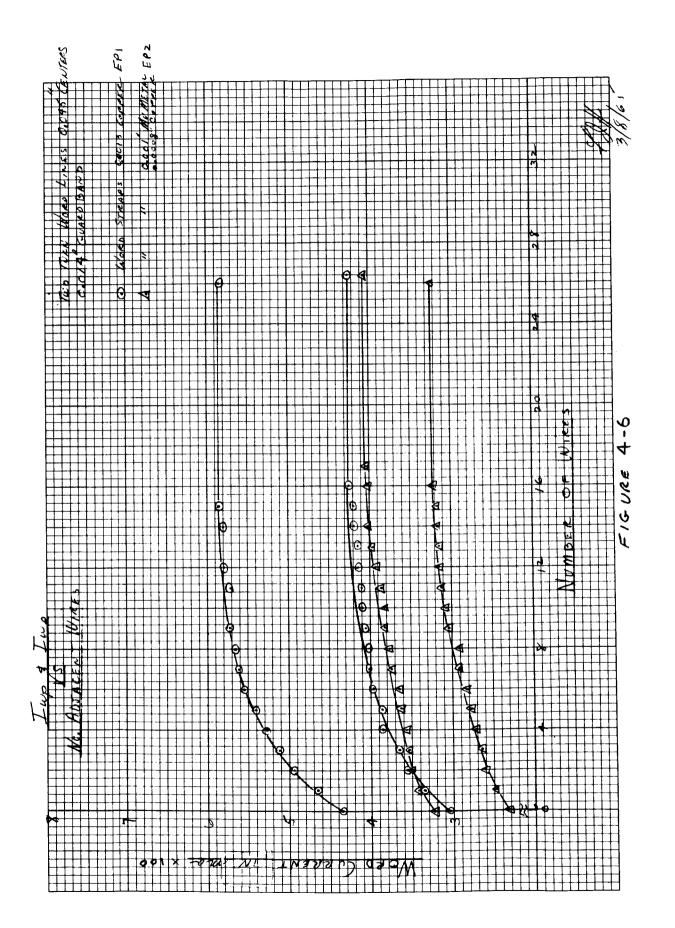

| (Plane EP1)344-6.Iwp and Iwd vs. No. of Adjacent Wires.364-7.Operating Parameters vs. Word Strap Width<br>(Copper).384-8.Operating Parameters vs. Word Strap Width<br>(Mu-metal and Copper).394-9.Operating Parameters vs. Word Strap Width<br>(1 Turn Copper Word Lines).394-10.Operating Parameters vs. Word Strap Width<br>(1 Turn Mu-metal Word Lines).434-11.Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).464-12.Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).474-13.Operating Parameters vs. Word Strap Width<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-4.  |                                                | 28    |

| <ul> <li>4-6. Iwp and Iwd vs. No. of Adjacent Wires</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-5.  |                                                |       |

| <ul> <li>4-7. Operating Parameters vs. Word Strap Width<br/>(Copper)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | $(Plane EP_1)$                                 | 34    |

| <ul> <li>4-7. Operating Parameters vs. Word Strap Width<br/>(Copper)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | $Iw_p$ and $Iw_d$ vs. No. of Adjacent Wires    | 36    |

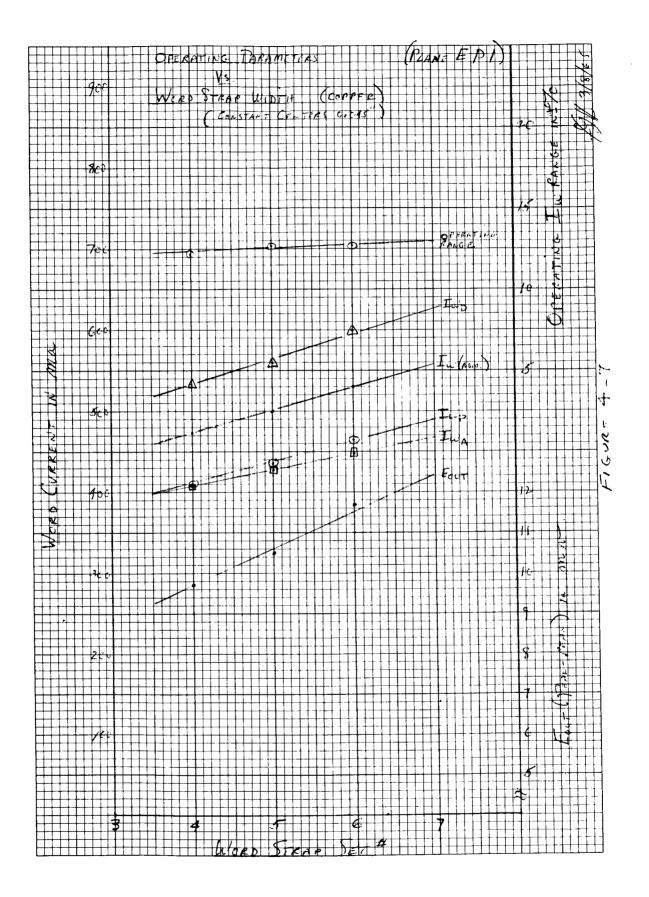

| <ul> <li>4-8. Operating Parameters vs. Word Strap Width<br/>(Mu-metal and Copper)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-7.  | Operating Parameters vs. Word Strap Width      |       |

| (Mu-metal and Copper)394-9.Operating Parameters vs. Word Strap Width<br>(1 Turn Copper Word Lines).434-10.Operating Parameters vs. Word Strap Width<br>(1 Turn Mu-metal Word Lines).444-11.Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).444-12.Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).464-13.Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).474-14.Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).484-14.Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).495-1.Miniature Spaceborne Memory Frame Side 1575-2.Miniature Spaceborne Memory Stack.595-3.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _     |                                                | 38    |

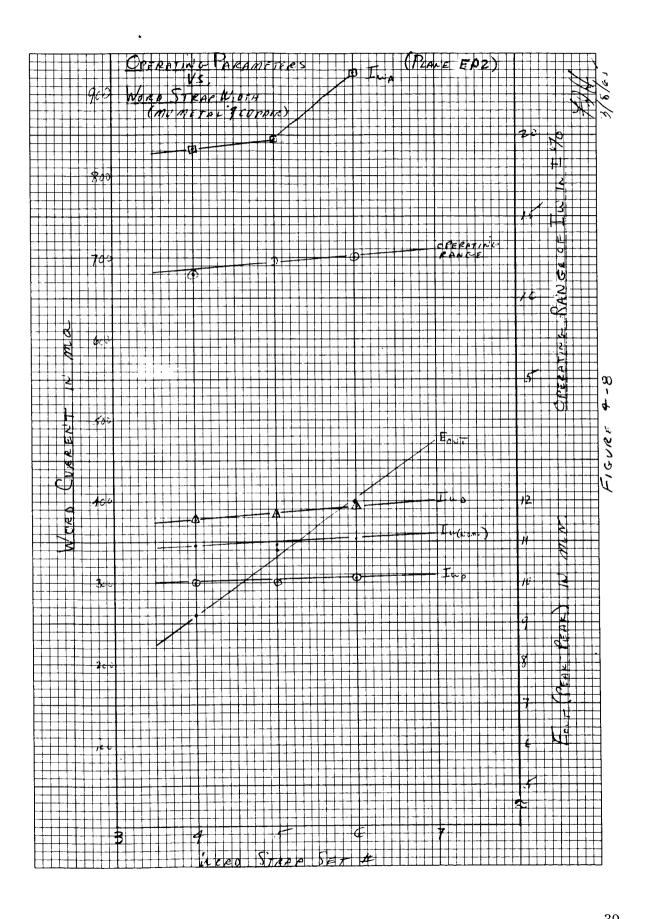

| <ul> <li>4-9. Operating Parameters vs. Word Strap Width <ul> <li>(1 Turn Copper Word Lines).</li> <li>43</li> </ul> </li> <li>4-10. Operating Parameters vs. Word Strap Width <ul> <li>(1 Turn Mu-metal Word Lines).</li> <li>44</li> </ul> </li> <li>4-11. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>46</li> </ul> </li> <li>4-12. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>47</li> </ul> </li> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>47</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>49</li> </ul> </li> <li>5-1. Miniature Spaceborne Memory Frame Side 1.</li> <li>57</li> <li>5-2. Miniature Spaceborne Memory Stack.</li> <li>59</li> <li>5-3. Miniature Spaceborne Memory Stack (end views).</li> <li>60</li> <li>5-4. Miniature Spaceborne Memory Stack (edge <ul> <li>views).</li> <li>views).</li> <li>41</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-8.  |                                                |       |

| (1 Turn Copper Word Lines).434-10. Operating Parameters vs. Word Strap Width<br>(1 Turn Mu-metal Word Lines).444-11. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).464-12. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).474-13. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).474-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).484-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).495-1. Miniature Spaceborne Memory Frame Side 1575-2. Miniature Spaceborne Memory Stack.595-3. Miniature Spaceborne Memory Stack (end views).605-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing61/62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                | 39    |

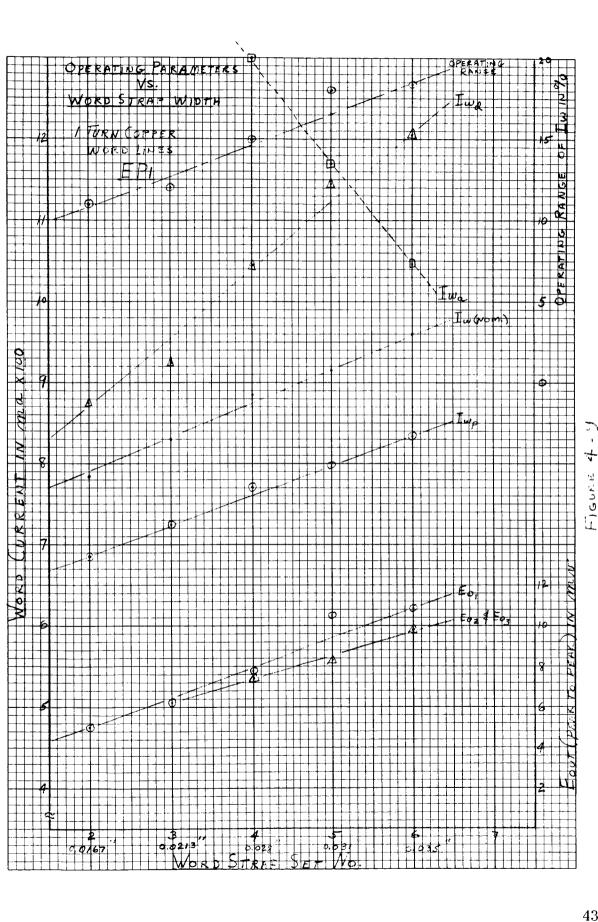

| <ul> <li>4-10. Operating Parameters vs. Word Strap Width <ul> <li>(1 Turn Mu-metal Word Lines).</li> <li>44</li> </ul> </li> <li>4-11. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>46</li> </ul> </li> <li>4-12. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>47</li> </ul> </li> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>47</li> </ul> </li> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>49</li> </ul> </li> <li>5-1. Miniature Spaceborne Memory Frame Side 1.</li> <li>57</li> <li>5-2. Miniature Spaceborne Memory Stack.</li> <li>59</li> <li>5-3. Miniature Spaceborne Memory Stack (end views).</li> <li>60</li> <li>5-4. Miniature Spaceborne Memory Stack (edge <ul> <li>views).</li> <li>views).</li> <li>41</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-9.  |                                                |       |

| (1 Turn Mu-metal Word Lines).444-11. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).464-12. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).474-13. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).474-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).484-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).495-1. Miniature Spaceborne Memory Frame Side 1575-2. Miniature Spaceborne Memory Stack.595-3. Miniature Spaceborne Memory Stack (end views).605-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing61/62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                | 43    |

| <ul> <li>4-11. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>46</li> </ul> </li> <li>4-12. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>47</li> </ul> </li> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>49</li> </ul> </li> <li>5-1. Miniature Spaceborne Memory Frame Side 1.</li> <li>57</li> <li>5-2. Miniature Spaceborne Memory Stack.</li> <li>59</li> <li>5-3. Miniature Spaceborne Memory Stack (end views).</li> <li>60</li> <li>5-4. Miniature Spaceborne Memory Stack (edge <ul> <li>views).</li> <li>.</li> <li>5-5a. Plane Assembly Drawing.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-10. |                                                |       |

| (½ Turn Cu Word Lines).464-12. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).474-13. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).474-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).485-1. Miniature Spaceborne Memory Frame Side 1575-2. Miniature Spaceborne Memory Stack.595-3. Miniature Spaceborne Memory Stack (end views).605-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                                                | 44    |

| <ul> <li>4-12. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>49</li> </ul> </li> <li>5-1. Miniature Spaceborne Memory Frame Side 1.</li> <li>57</li> <li>5-2. Miniature Spaceborne Memory Stack.</li> <li>59</li> <li>5-3. Miniature Spaceborne Memory Stack (end views).</li> <li>60</li> <li>5-4. Miniature Spaceborne Memory Stack (edge <ul> <li>views).</li> <li>1.</li> <li>1.<td>4-11.</td><td></td><td></td></li></ul></li></ul></li></ul> | 4-11. |                                                |       |

| (½ Turn Mu-metal Word Lines).474-13. Operating Parameters vs. Word Strap Width<br>(½ Turn Cu Word Lines).484-14. Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).485-1. Miniature Spaceborne Memory Frame Side 1575-2. Miniature Spaceborne Memory Stack.595-3. Miniature Spaceborne Memory Stack (end views).605-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                | 46    |

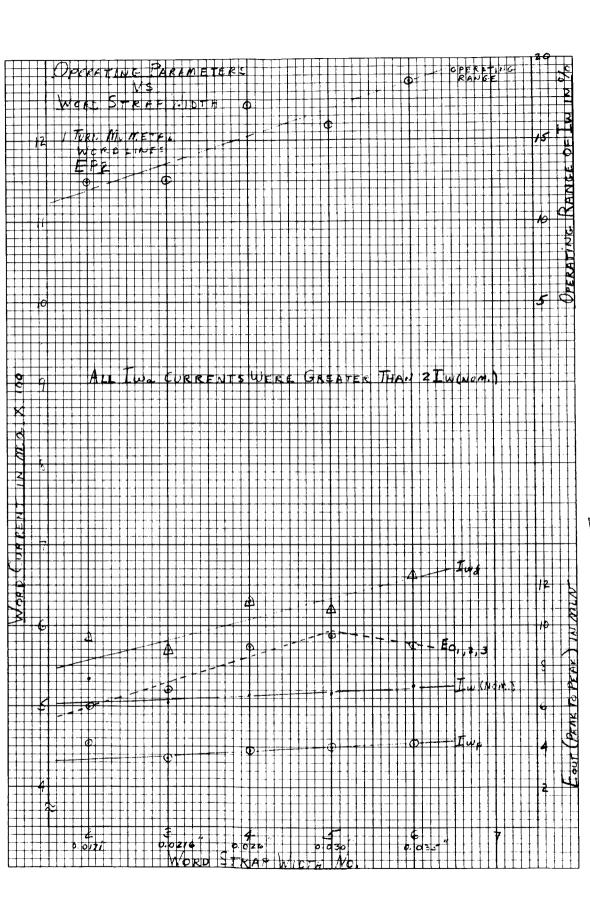

| <ul> <li>4-13. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Cu Word Lines).</li> <li>48</li> </ul> </li> <li>4-14. Operating Parameters vs. Word Strap Width <ul> <li>(½ Turn Mu-metal Word Lines).</li> <li>49</li> </ul> </li> <li>5-1. Miniature Spaceborne Memory Frame Side 1 57</li> <li>5-2. Miniature Spaceborne Memory Stack.</li> <li>59</li> <li>5-3. Miniature Spaceborne Memory Stack (end views).</li> <li>60</li> <li>5-4. Miniature Spaceborne Memory Stack (edge <ul> <li>views).</li> <li></li> <li>61/62</li> </ul> </li> <li>5-5a. Plane Assembly Drawing.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-12. |                                                |       |

| (½ Turn Cu Word Lines).484-14.Operating Parameters vs. Word Strap Width<br>(½ Turn Mu-metal Word Lines).495-1.Miniature Spaceborne Memory Frame Side 1575-2.Miniature Spaceborne Memory Stack.595-3.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                                                | 47    |

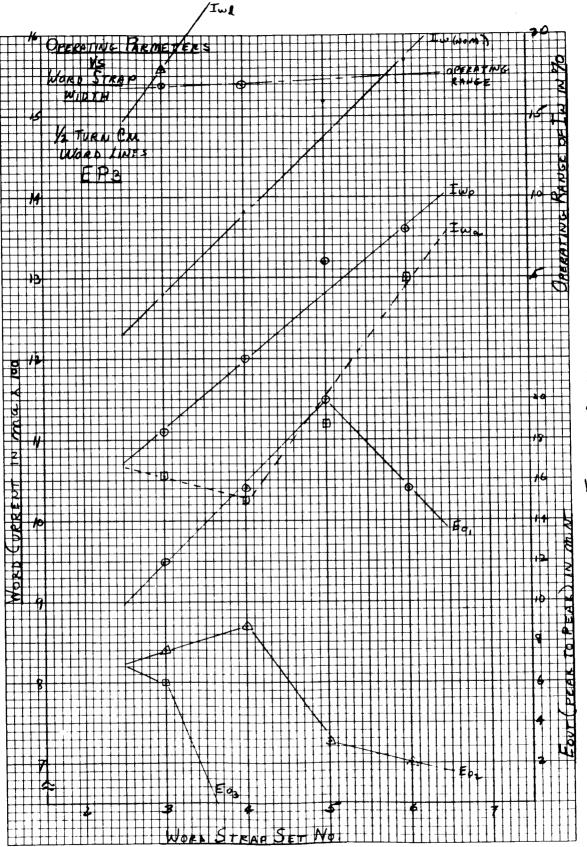

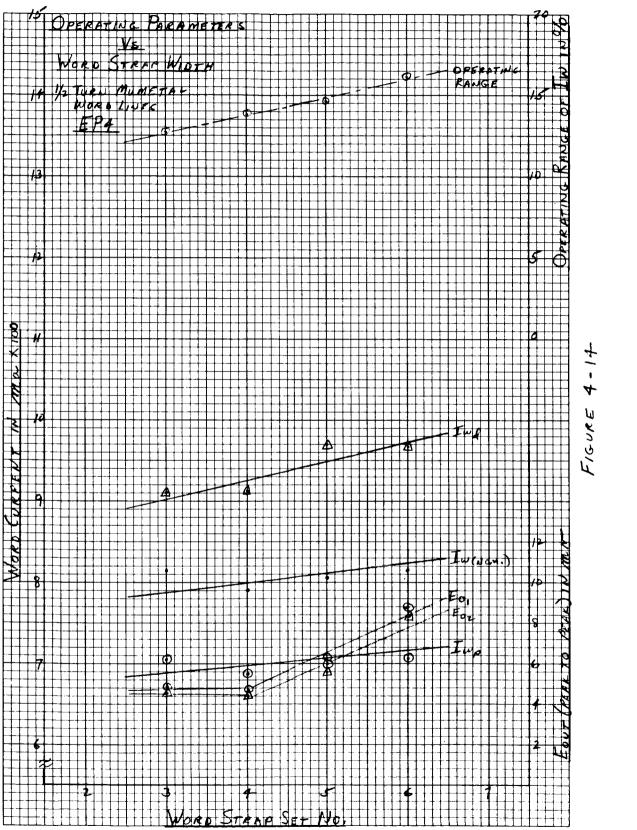

| <ul> <li>4-14. Operating Parameters vs. Word Strap Width<br/>(½ Turn Mu-metal Word Lines)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-13. |                                                |       |

| (½ Turn Mu-metal Word Lines).495-1. Miniature Spaceborne Memory Frame Side 1575-2. Miniature Spaceborne Memory Stack.595-3. Miniature Spaceborne Memory Stack (end views).605-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                                | 48    |

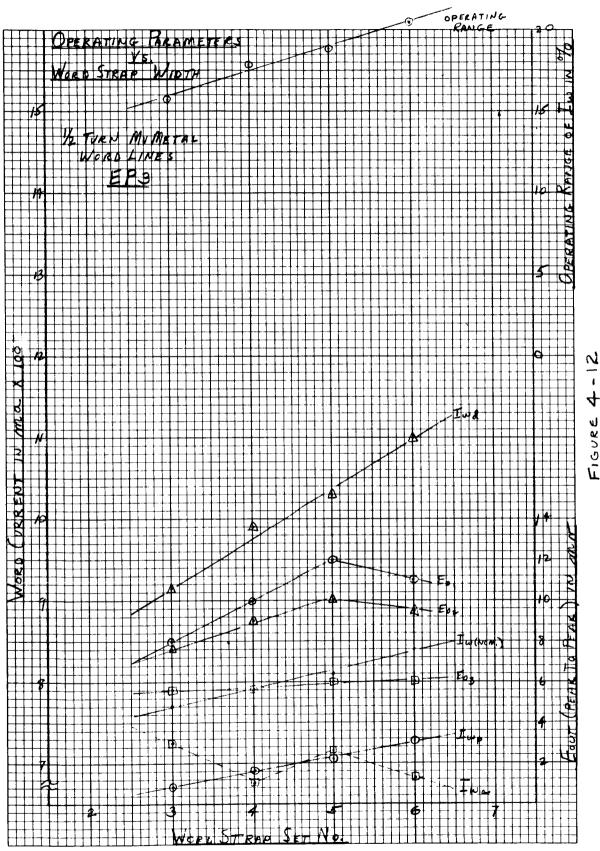

| 5-1.Miniature Spaceborne Memory Frame Side 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-14. |                                                |       |

| 5-2.Miniature Spaceborne Memory Stack.595-3.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | (½ Turn Mu-metal Word Lines)                   | 49    |

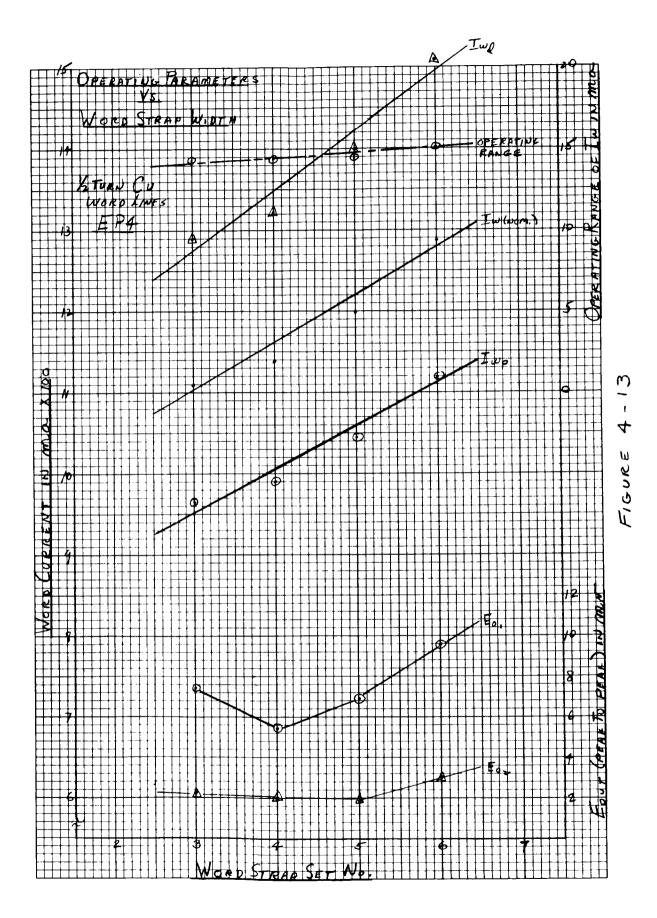

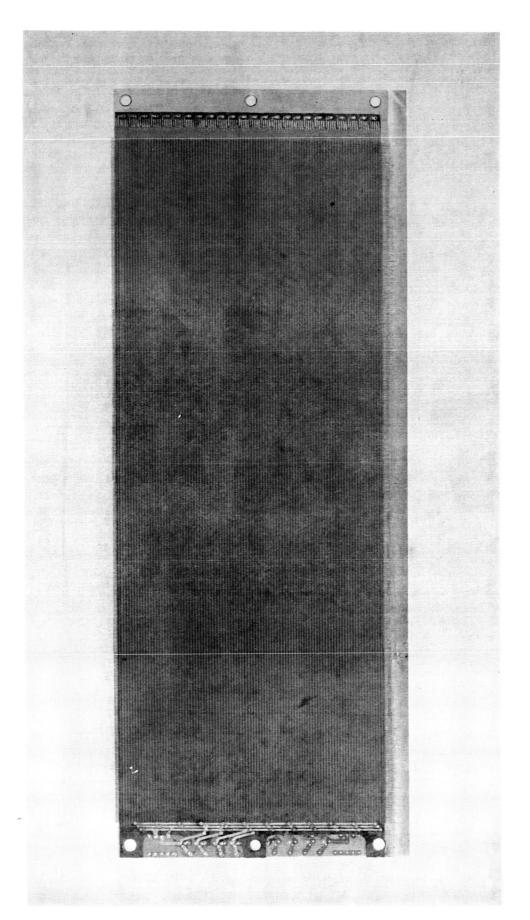

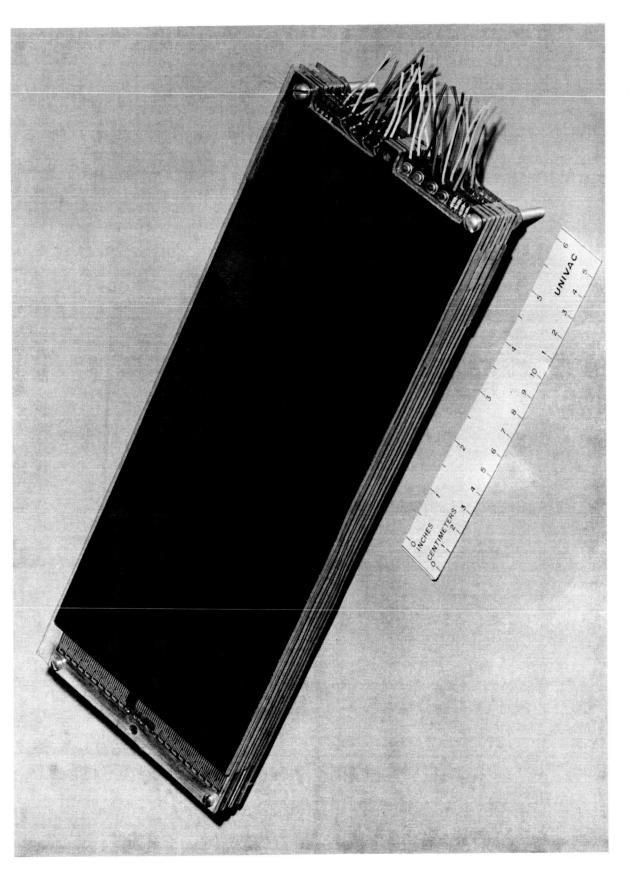

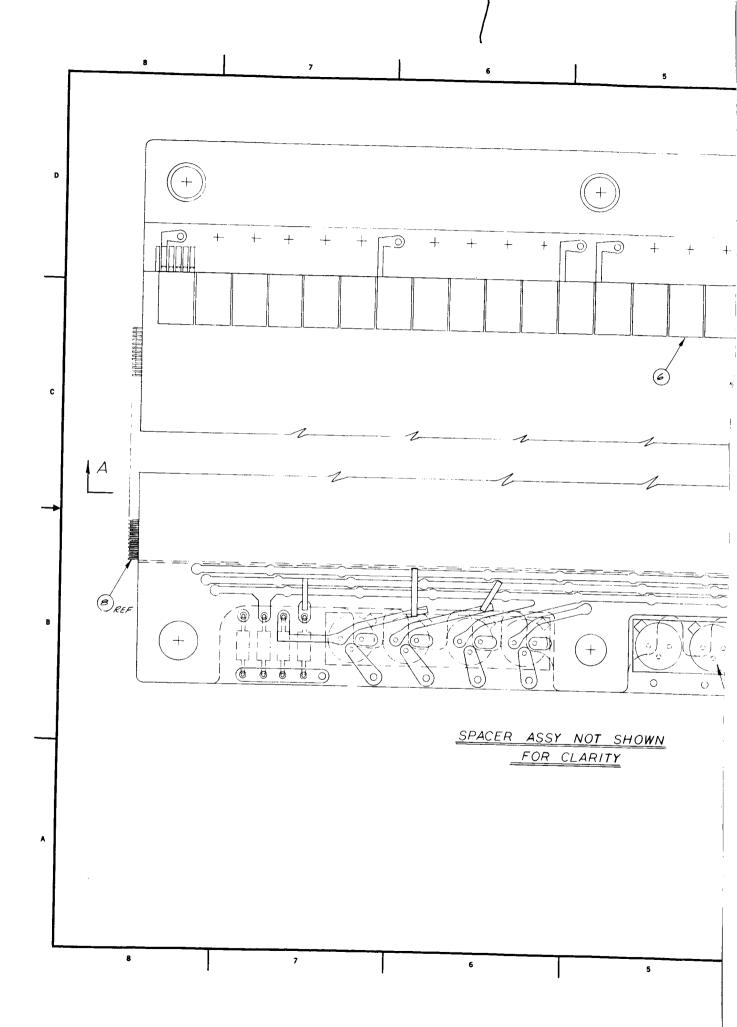

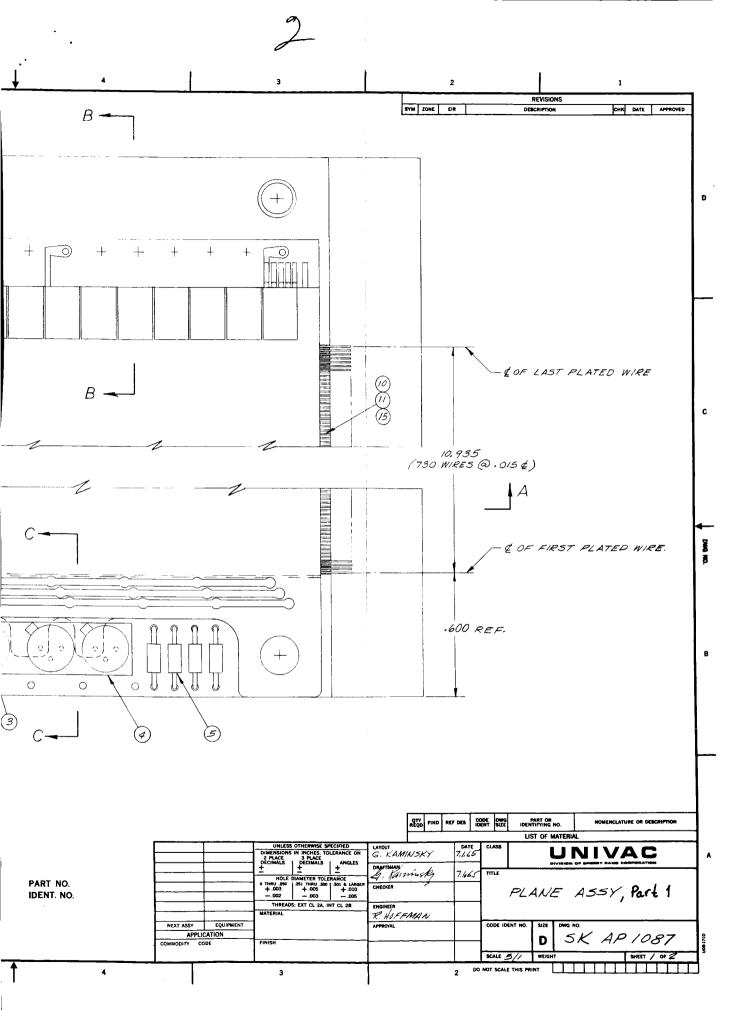

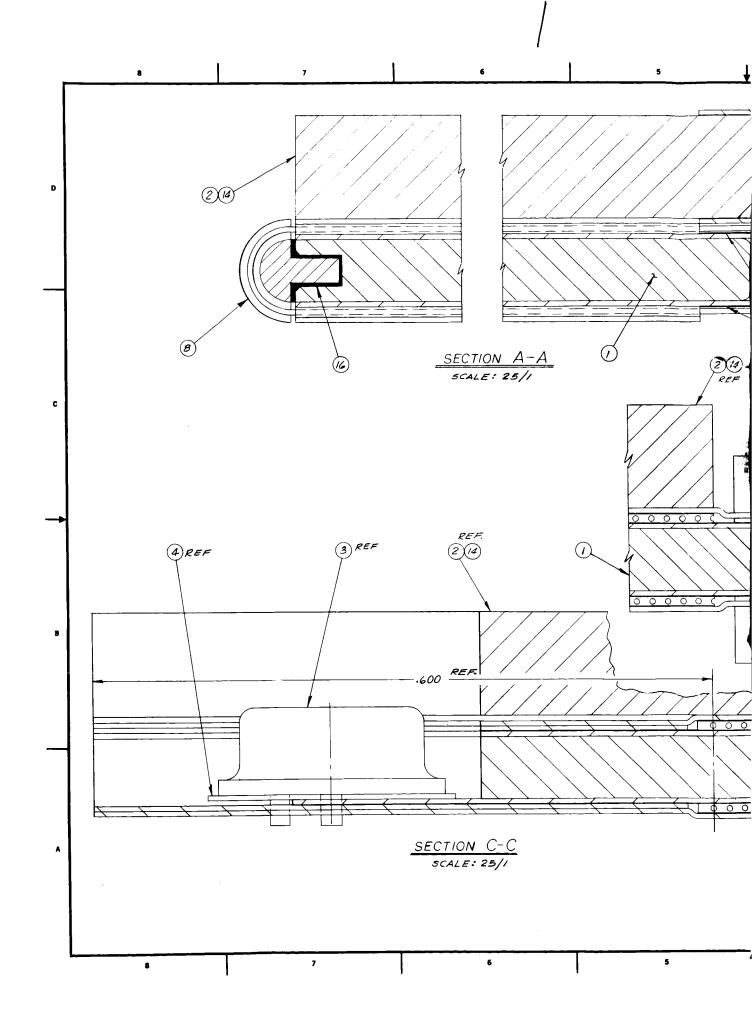

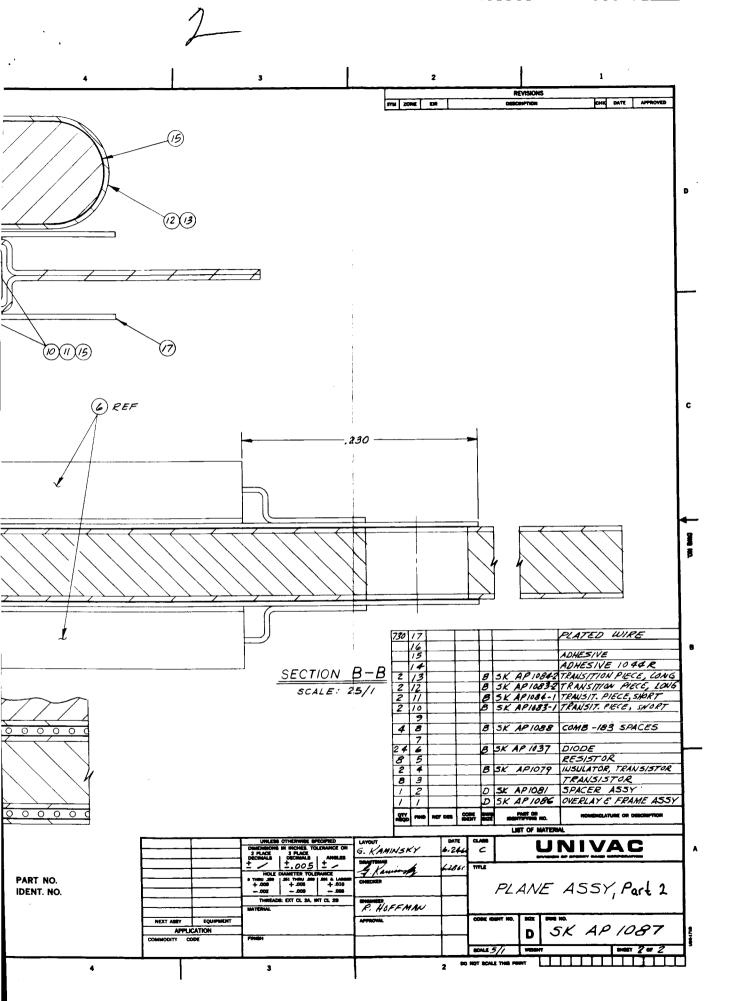

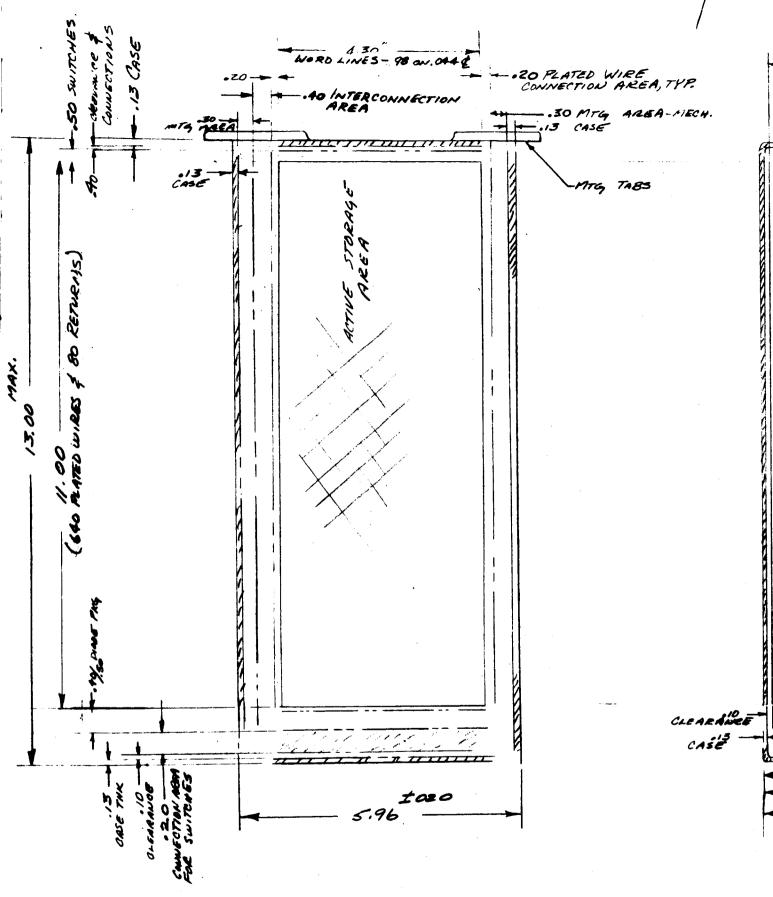

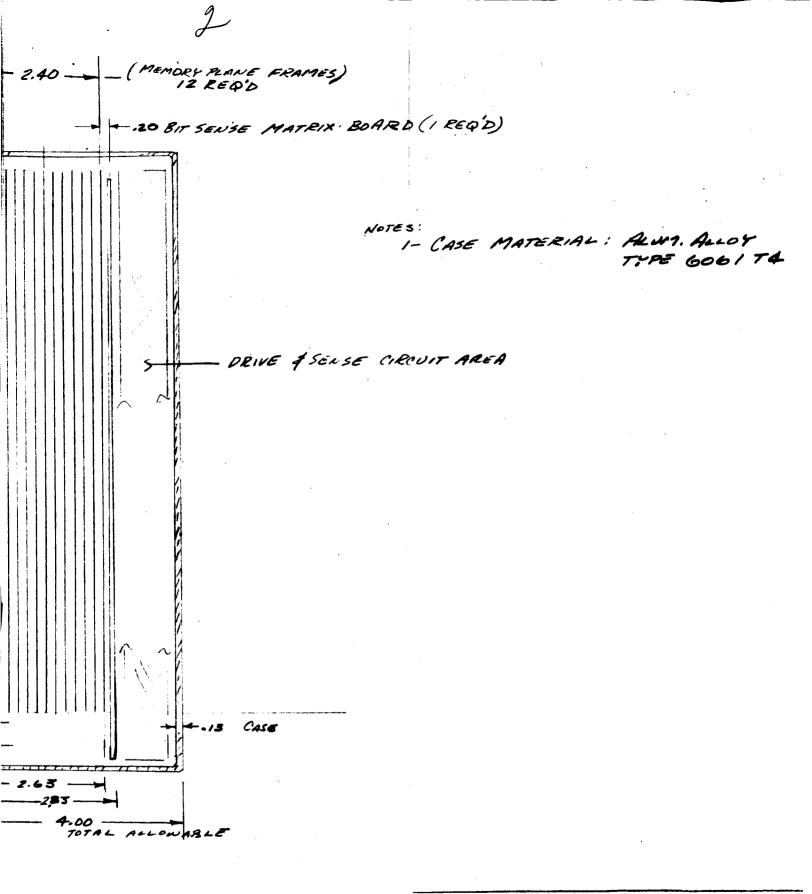

| 5-2.Miniature Spaceborne Memory Stack.595-3.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1.  | Miniature Spaceborne Memory Frame Side 1       | 57    |

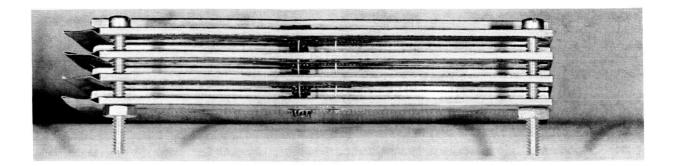

| 5-3.Miniature Spaceborne Memory Stack (end views).605-4.Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a.Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | Miniature Spaceborne Memory Stack              |       |

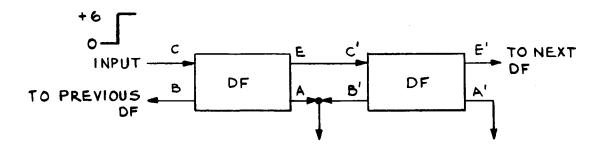

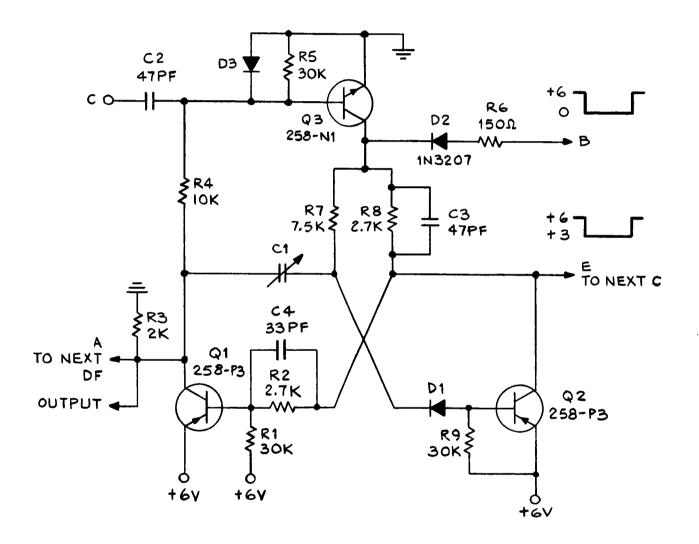

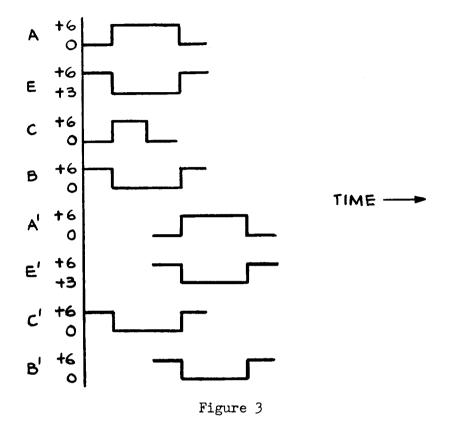

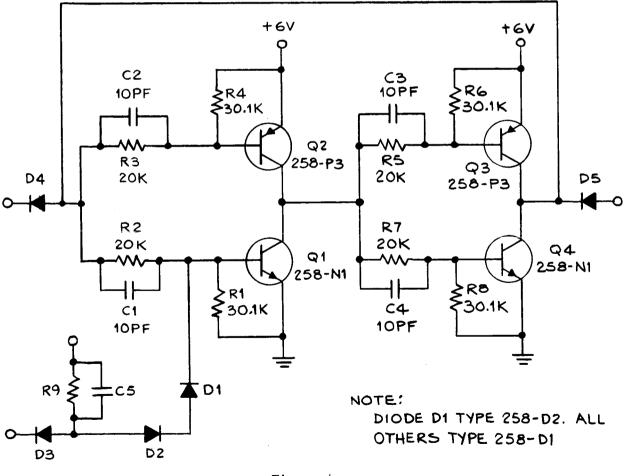

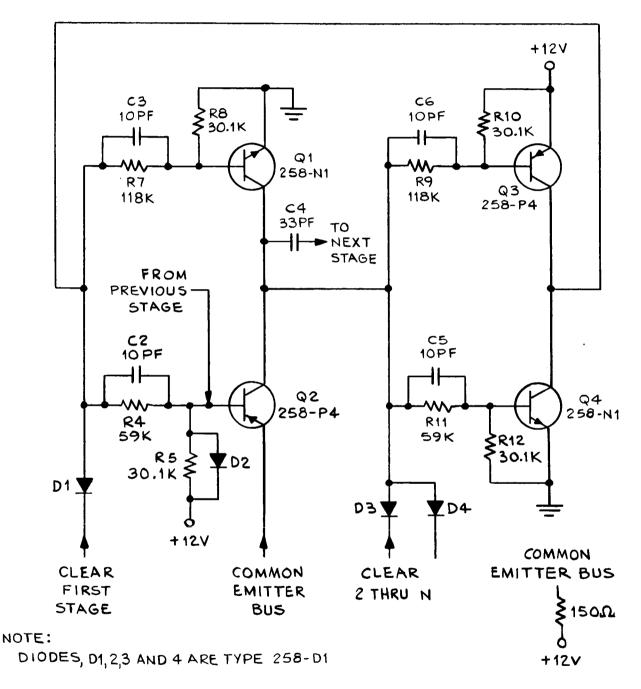

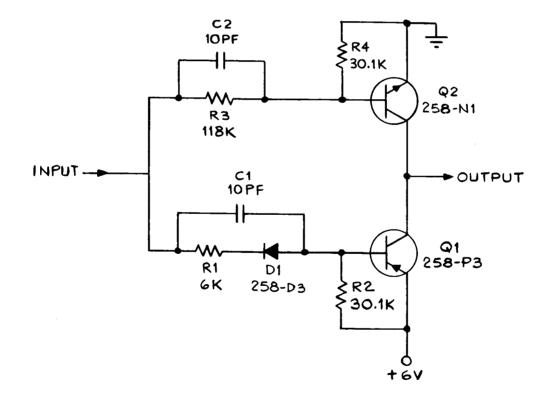

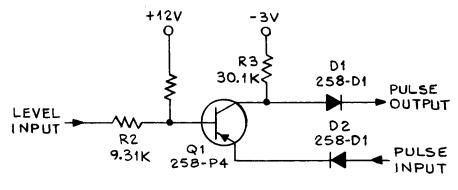

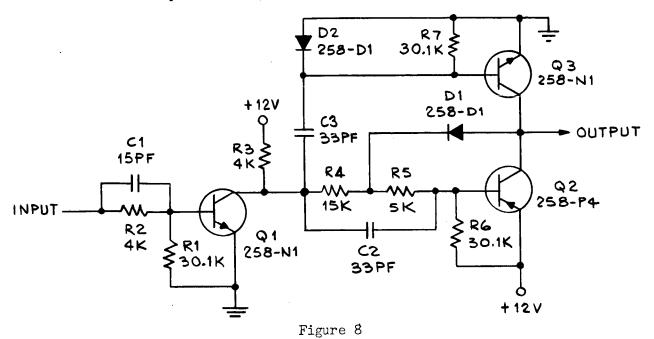

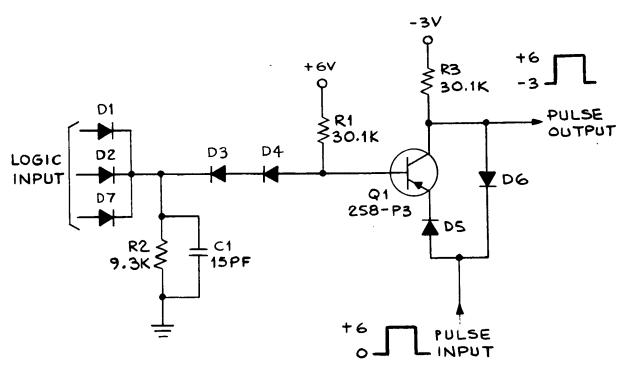

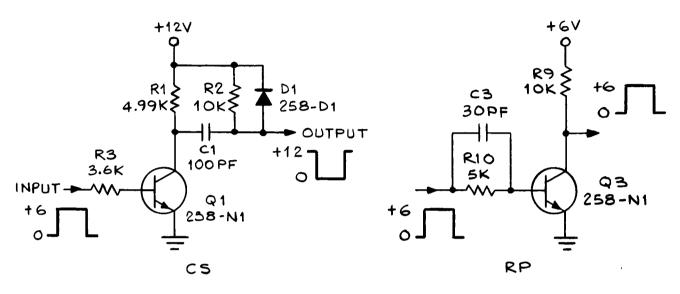

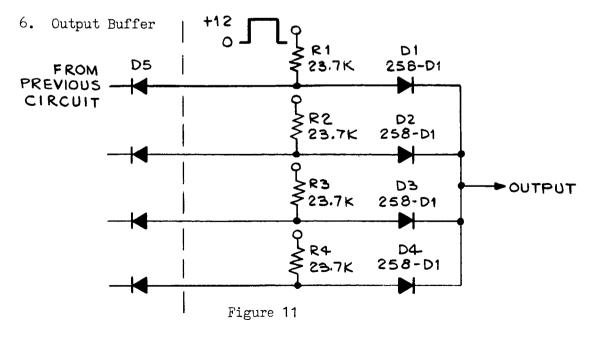

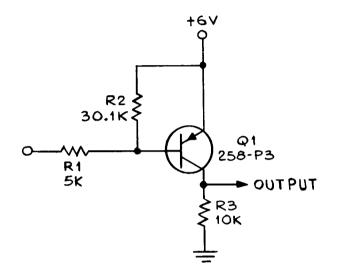

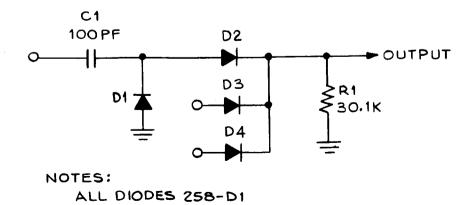

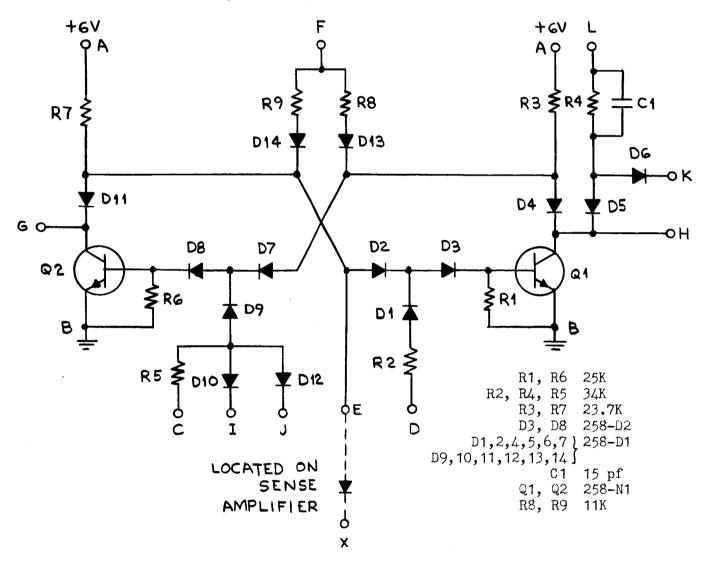

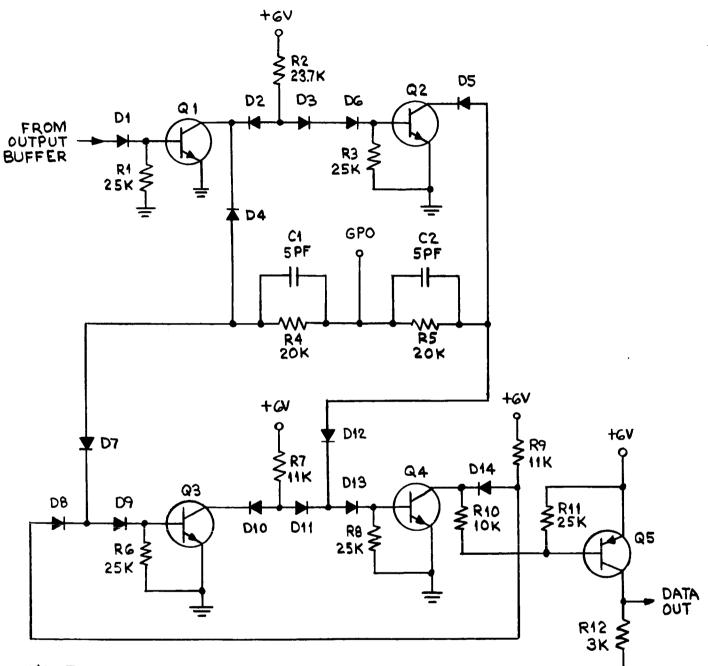

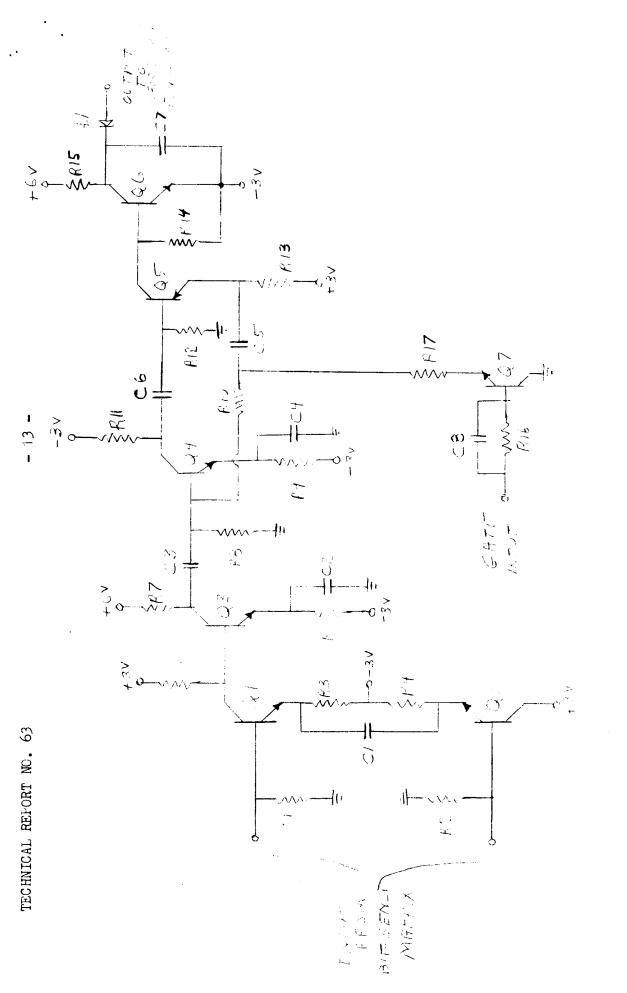

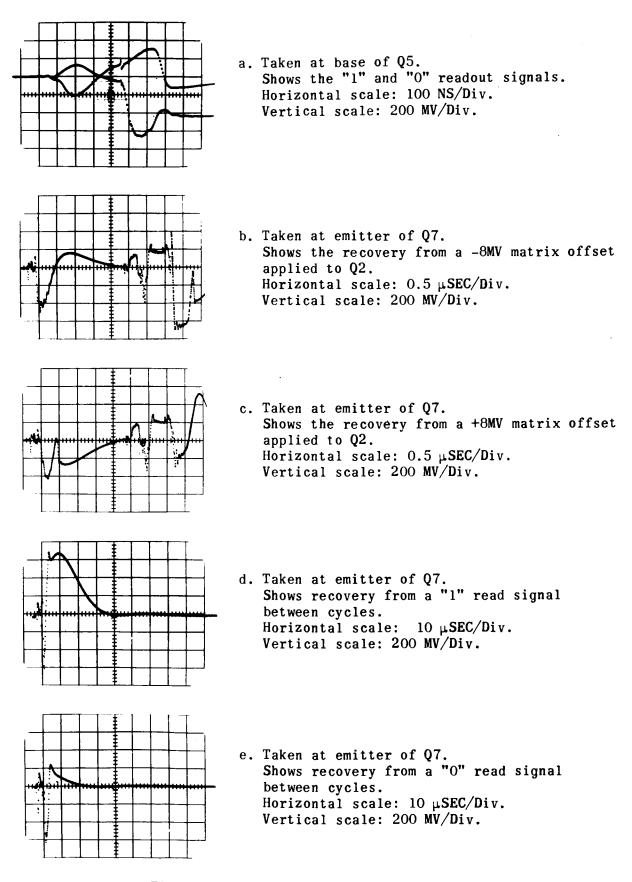

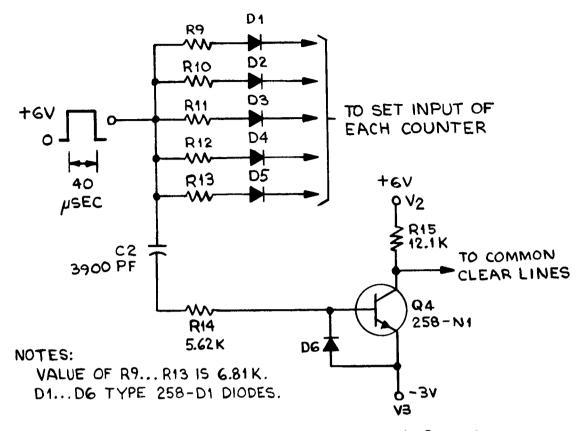

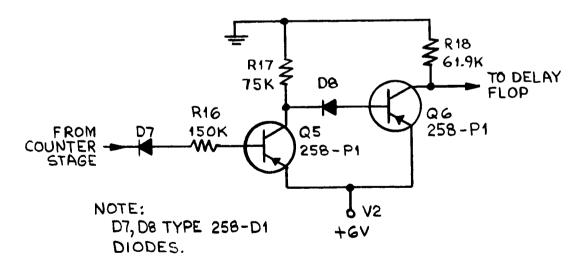

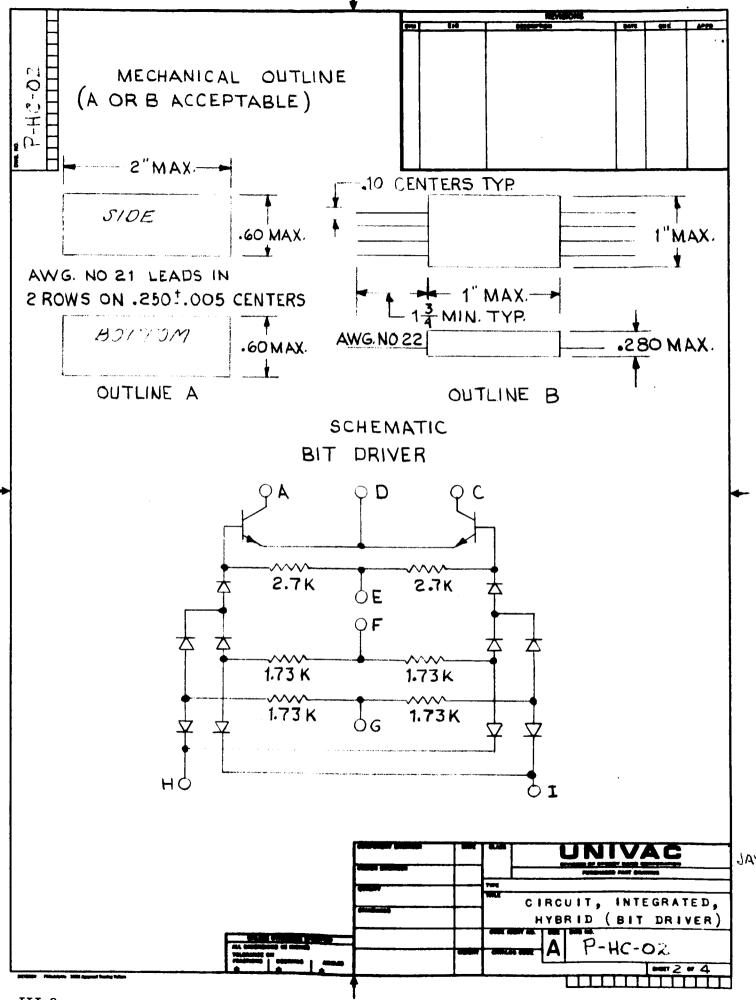

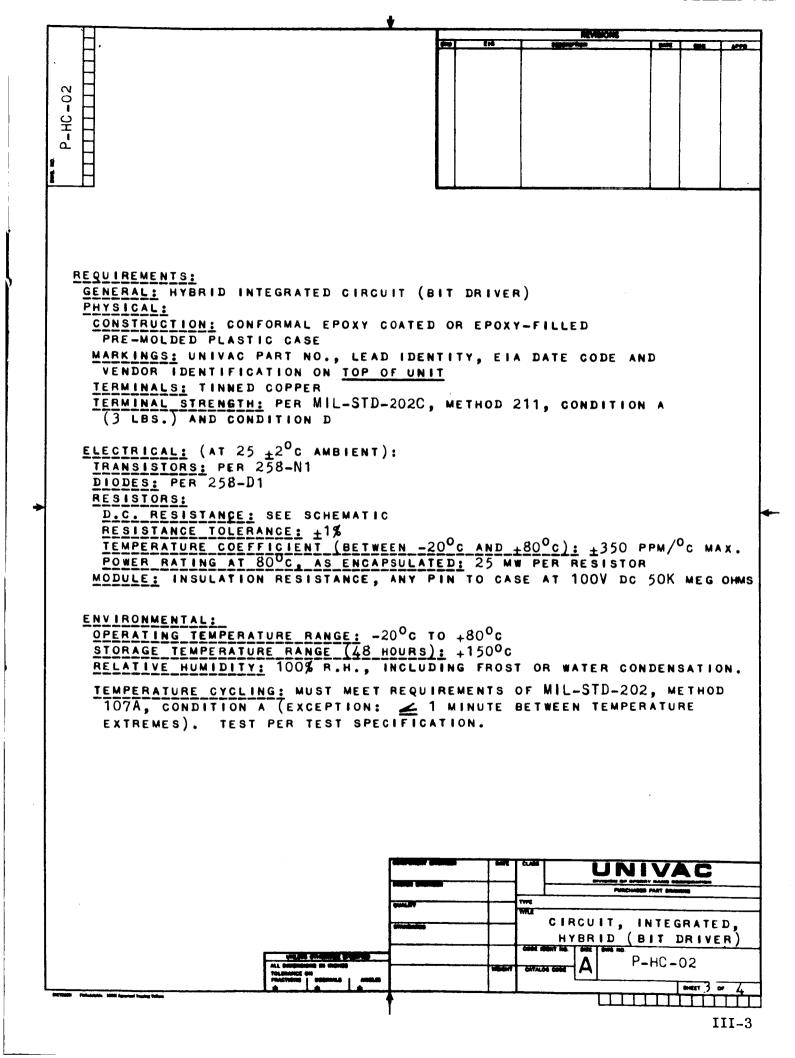

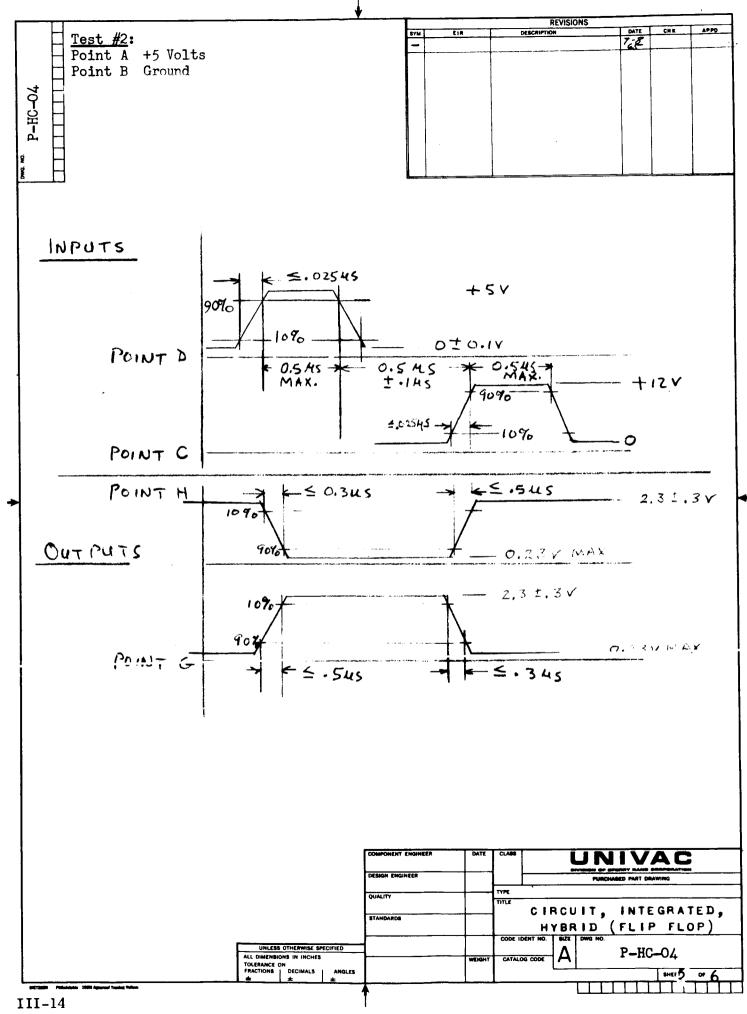

| 5-4. Miniature Spaceborne Memory Stack (edge<br>views).61/625-5a. Plane Assembly Drawing63/64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Miniature Spaceborne Memory Stack (end views). |       |