@ https://ntrs.nasa.gov/search.jsp?R=19660011715 2020-03-16T22:35:05+00:00Z

Masa CR 45254

# AES-EPO STUDY PROGRAM FINAL STUDY REPORT Volume II

N66-21004 ACCESSION NUMBER (THRU) CODE) GORY) 399

GPO PRICE CFSTI PRICE(S) \$\_

Hard copy (HC) \_\_\_\_\_ Microfiche (MF) \_\_\_\_\_ 25

ff 653 July 65

[]]別

FACILITY FORM 502

## LIBRARY COPY

JAN 17 1965

MANNED SPACECRAFT CENTER HOUSTON, TEXAS

Federal Systems Division, Electronics Systems Center, Owego, New York

### AES-EPO STUDY PROGRAM Final Study Report Volume Π

| ORIGINATED:                               | AES-EPO Staff        |

|-------------------------------------------|----------------------|

| CLASSIFICATION AND<br>CONTENTS APPROVAL:_ | 7B fewia             |

| PROJECT OFFICE APPRO                      | VAL: Joseph a. Duffy |

| IBM NUMBER:                               | 65-562-012           |

CONTRACT NUMBER: NAS 9-4570

3.0

Prepared for the MANNED SPACECRAFT CENTER National Aeronautics and Space Administration Houston, Texas

Electronics Systems Center, Owego, New York

31 December 1965

!

#### FOREWORD

A computer concepts study was conducted at the IBM Electronic Systems Center at Owego, New York, under IBM contract NAS9-4570, for the Manned Spacecraft Center, Houston, Texas. The objective of the study was to investigate possible solutions to long term and time critical reliability problems as they affect the Apollo Command Module guidance and control computer in its application to the AES mission. Volume I of this final report presents a summary of the work performed during the study, and Volume II presents detailed technical descriptions of the various investigations.

## TABLE OF CONTENTS

| Section |                                        | Page    |

|---------|----------------------------------------|---------|

| 1.0     | PACKAGING                              | <br>1   |

|         | 1.1 Limiting Exposure                  | 1       |

|         | 1.2 Connector Sealing                  | <br>8   |

|         | 1.3 Contact Considerations             | 14      |

|         | 1.4 Replaceability                     | 23      |

|         | 1.5 Module Size                        | 24      |

| 2.0     | MACHINE ORGANIZATION                   | <br>35  |

|         | 2.1 TMR Characteristics                | 35      |

|         | 2.2 Trade-off Criteria                 | 41      |

|         | 2.3 Basic Subsystem Configuration      | 43      |

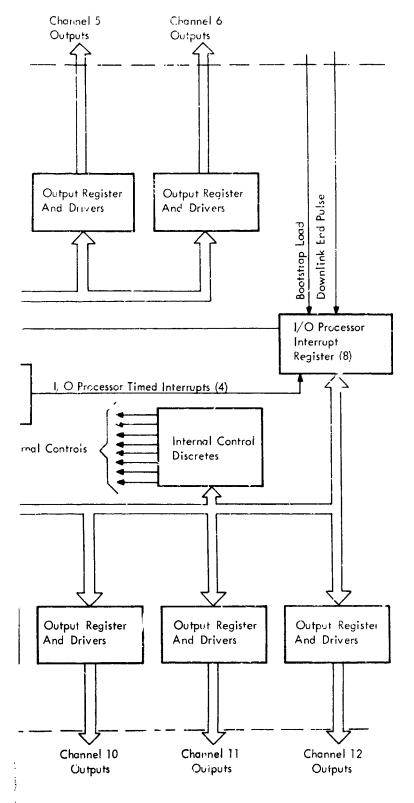

|         | 2.4 Oscillator                         | 63      |

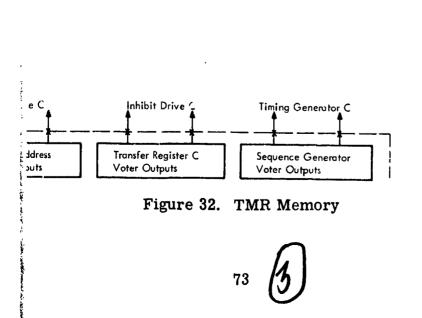

|         | 2.5 Memory                             | 70      |

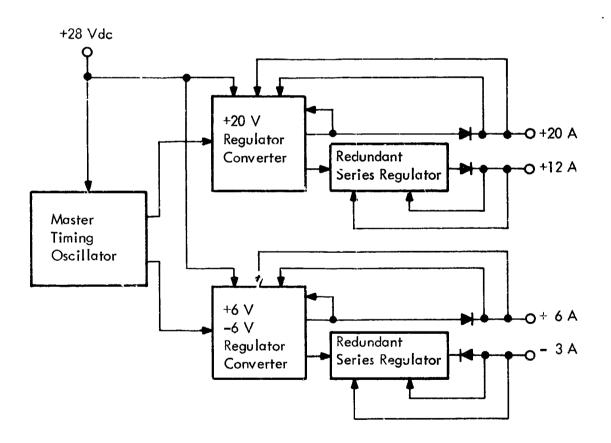

|         | 2.6 Power Supplies and Distribution    | 80      |

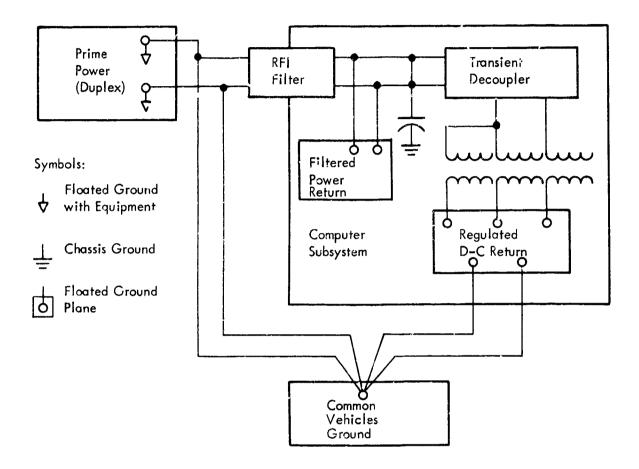

|         | 2.7 Greunding                          | 86      |

|         | 2.8 TMR/Simplex Mode                   | 95      |

|         | 2.9 Reorganized Subsystem              | <br>99  |

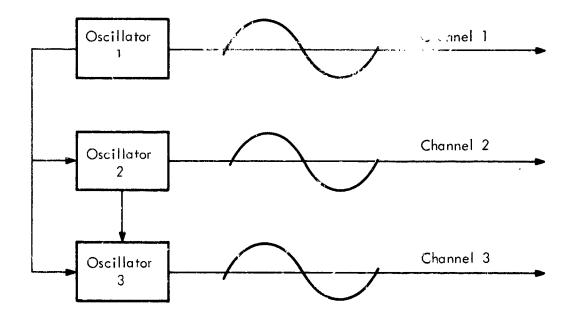

|         | 2.10 Transient Protection              | 125     |

| 3.0     | ERROR DETECTION AND DIAGNOSIS          | <br>135 |

|         | 3.1 Approach                           | 135     |

|         | 3.2 Disagreement Detectors             | 140     |

|         | 3.3 Switching                          | 150     |

|         | 3.4 Crew Requirements                  | 156     |

|         | 3.5 Programming Requirements           | 156     |

| 4.0     | FABRICATION AND TEST                   | <br>166 |

|         | 4.1 Equipment Mockup                   | 166     |

|         | 4.2 Exploratory Tests                  | 167     |

|         | 4.3 Environmental Simulation Equipment | 172     |

|         | 4.4 Evaluation Tests                   | 176     |

|         | 4.5 Test Results                       | 177     |

## LIST OF ILLUSTRATIONS

## Figure

## Page

| 1          | Unit Packaging Approach                                  |

|------------|----------------------------------------------------------|

| 2          | Computer Casting 4                                       |

| 3          | Channel Packaging Approach 5                             |

| 4          | Cell Packaging Approach                                  |

| 5          | Initial Leakage Rate                                     |

| 6          | Seal Deterioration with Use                              |

| 7          | Connector Sealing Technique (Modified Saturn - V         |

|            | Connector) 11                                            |

| 8          | Phase I Test Model 12                                    |

| 9          | Change in Contact Resistance Versus Time (Gold and       |

|            | Gold Allov)                                              |

| 10         | Porosity Versus Thickness for Gold Plating 18            |

| 11         | Constriction Resistance Versus Load                      |

| 12         | Contact Resistance Versus Alloy Gold Content             |

| 13         | Interconnections per Circuit Versus Circuits per Page 25 |

| 14         | Connections Versus Logic Blocks                          |

| 15         | Interconnections per Circuit Versus Circuits per Page 28 |

| 16         | Voters per Page Versus Circuits per Page                 |

| 17         | Circuits per Machine Versus Circuits per Page 31         |

| 18         | Channel Packaging                                        |

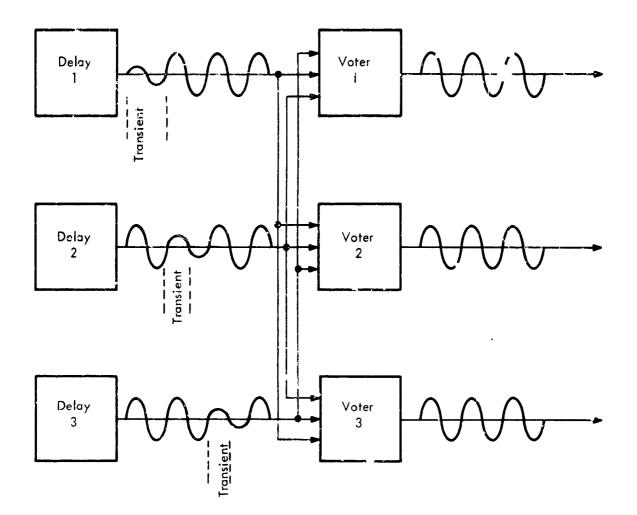

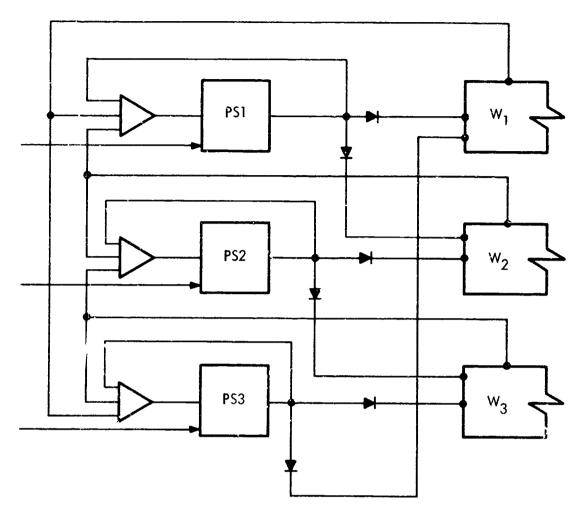

| 19         | TMR Voting                                               |

| 20         | TMR Versus Simplex Reliability38                         |

| 21         | Channel Switching                                        |

| <b>2</b> 2 | Module Switching                                         |

| 23         | Saturn-V Voter                                           |

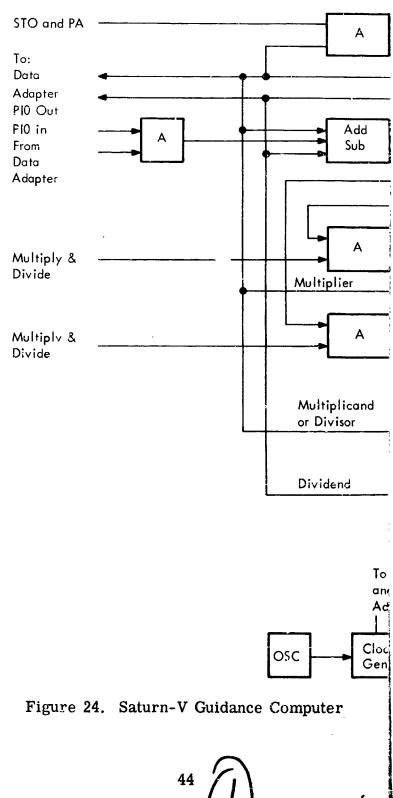

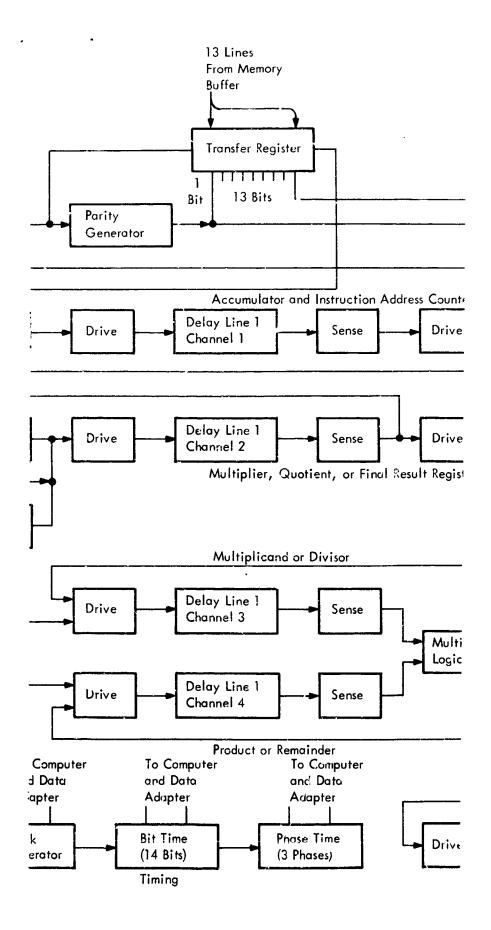

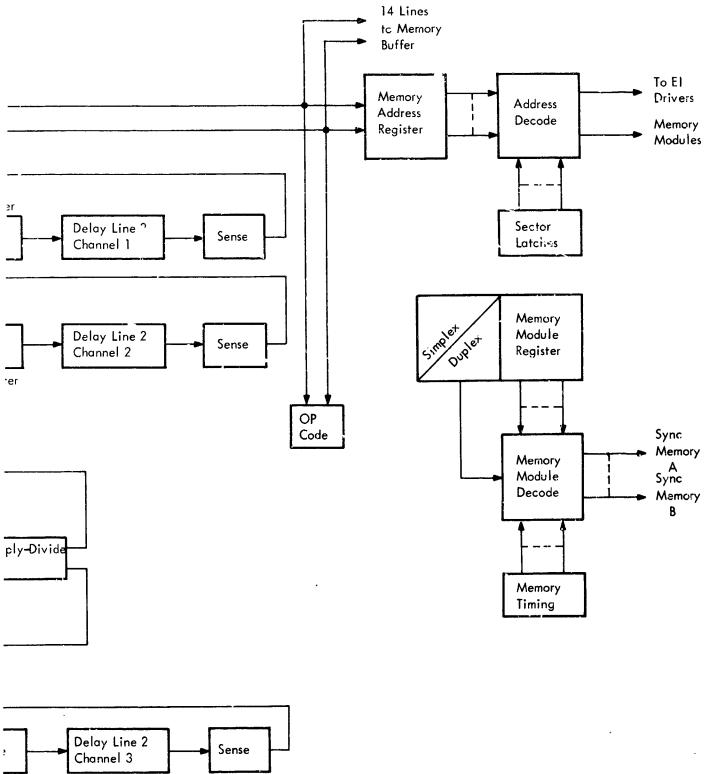

| 24         | Saturn-V Guidance Computer                               |

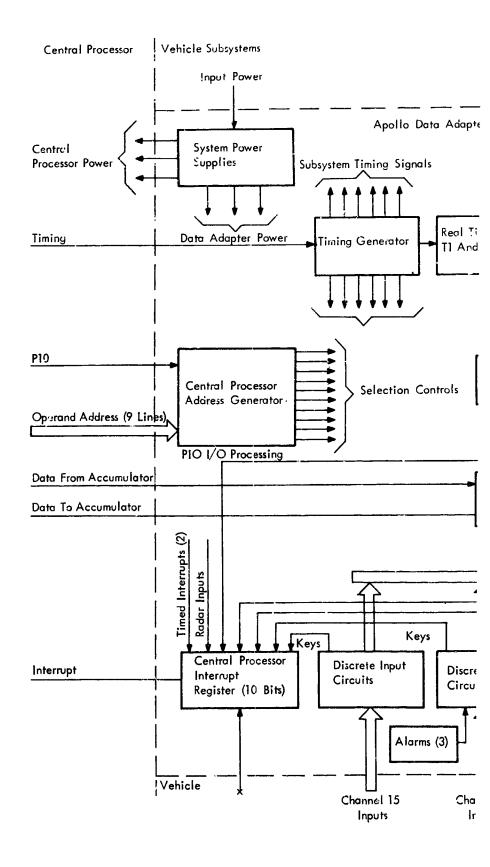

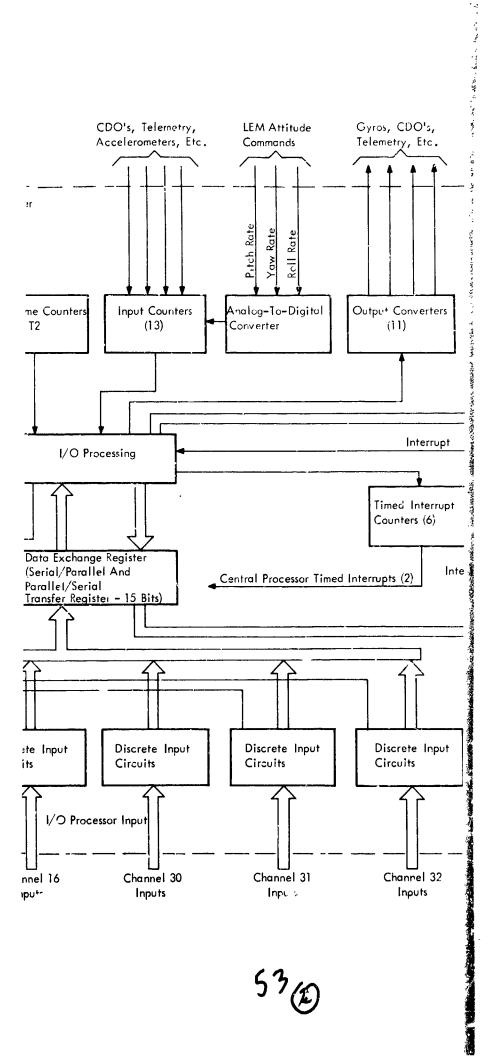

| 25         | Data Adapter Block Diagram                               |

| 26         | Oscillator Synchronization                               |

| 27         | Transient Filter                                         |

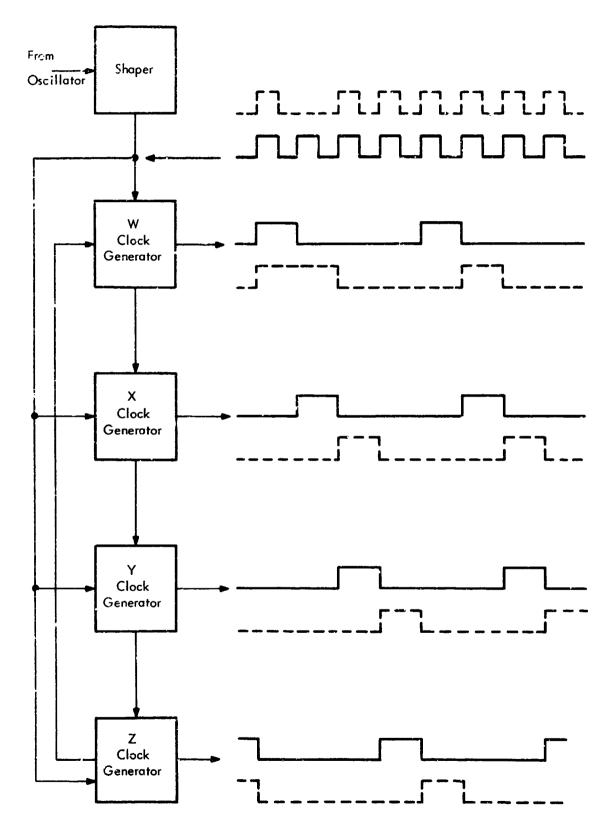

| 28         | Clock Generator                                          |

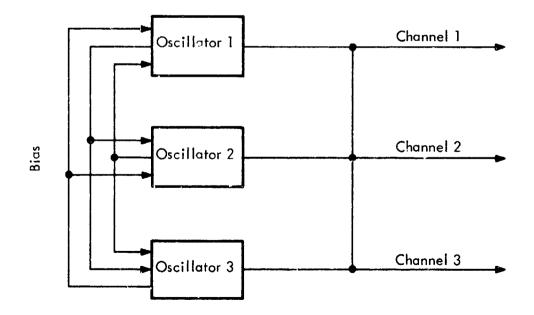

| 29         | Biased Oscillators                                       |

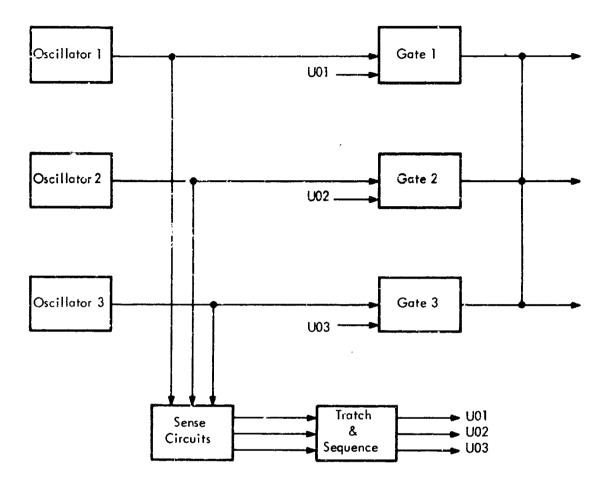

| 30         | Gated Oscillators                                        |

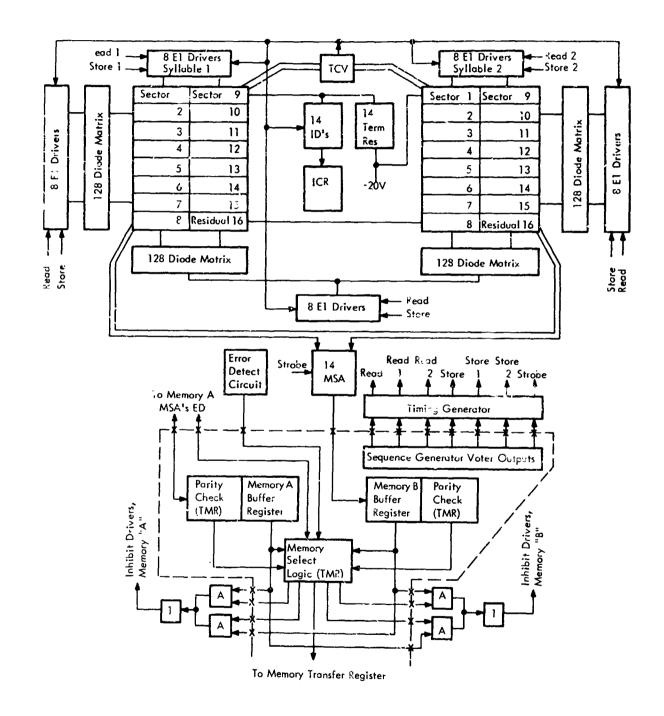

| 31         | Duplex Memory                                            |

| 32         | TMR Memory                                               |

| 33         | Triplex-Duplex Power System ,                            |

| 34         | Interrelated Power System                                |

| 35         | Grounding System                                         |

|            |                                                          |

## LIST OF ILLUSTRATIONS (Continued)

i.

| Figure |

|--------|

|--------|

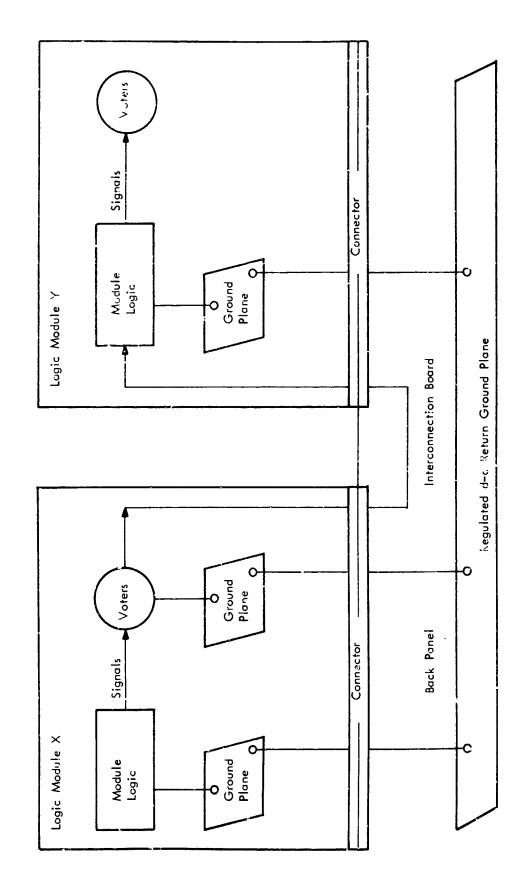

| 36             | Regulated DC Return Ground Planes                 | 88         |

|----------------|---------------------------------------------------|------------|

| 37             | Module Cround Planes                              | 90         |

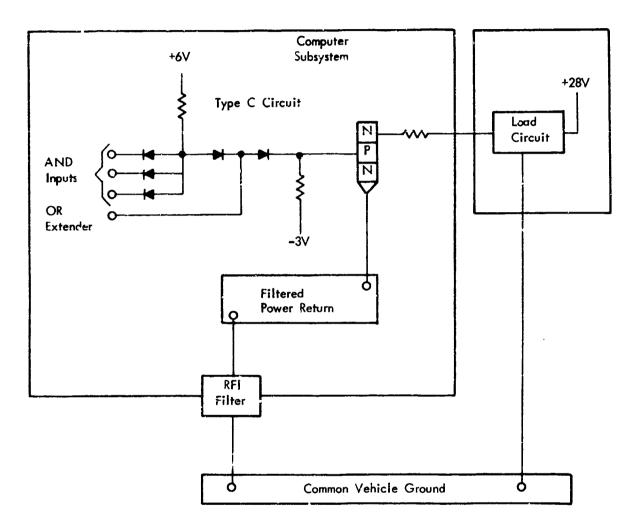

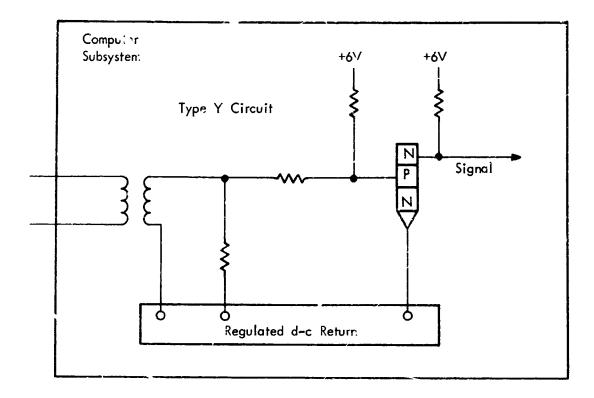

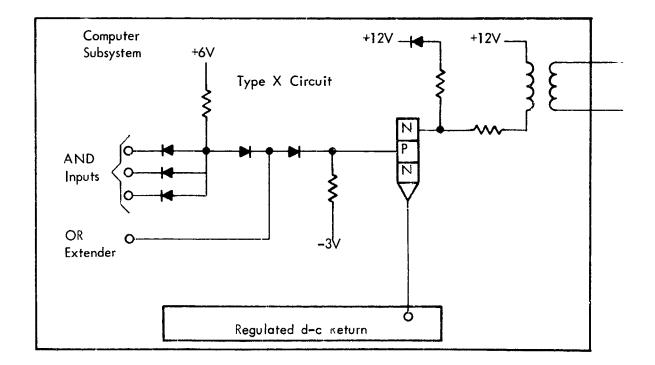

| 38             | Discrete Input Circuit                            | 91         |

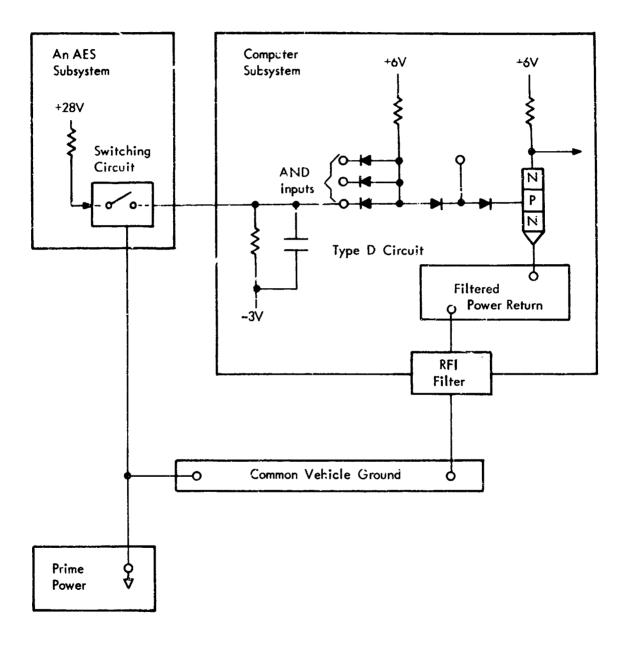

| 39             | Discrete Output Circuit                           | 93         |

| 40             | Pulse Input Circuit                               | 94         |

| 41             | Pulse Output Circuit                              | 94         |

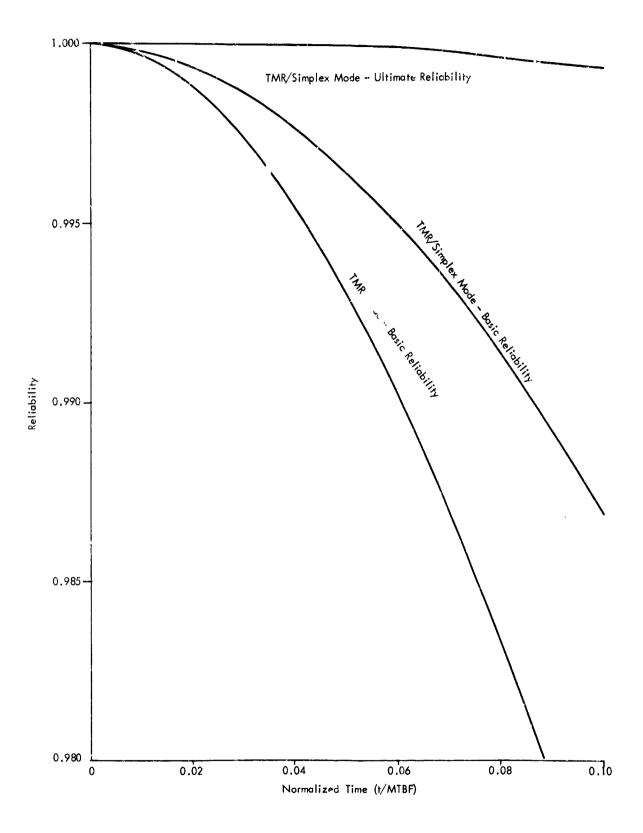

| 42             | Generalized Reliability Curves                    | 96         |

| 43             | Reliability Comparison (TMR and TMR/Simplex)      | 100        |

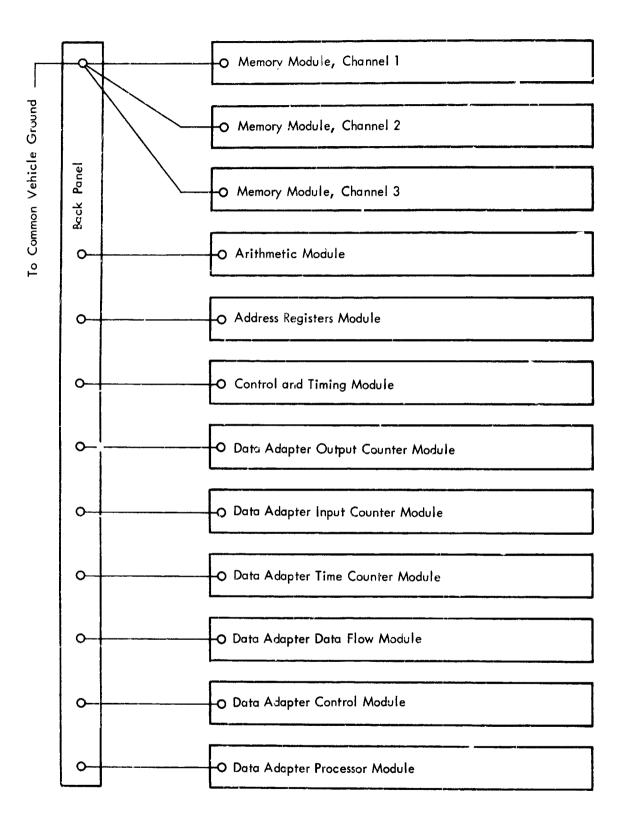

| 44             | Four-Module Partitioning of the Saturn-V Computer | 102        |

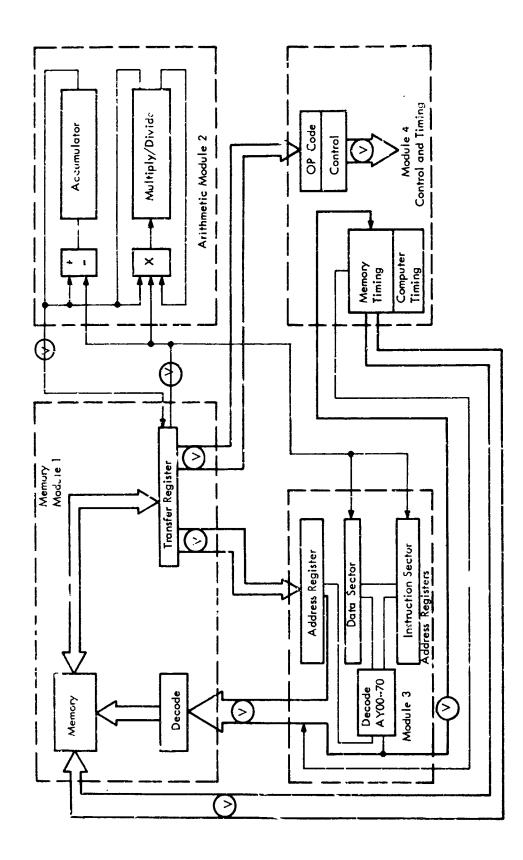

| 45             | AES Computer Flow Diagram                         | 105        |

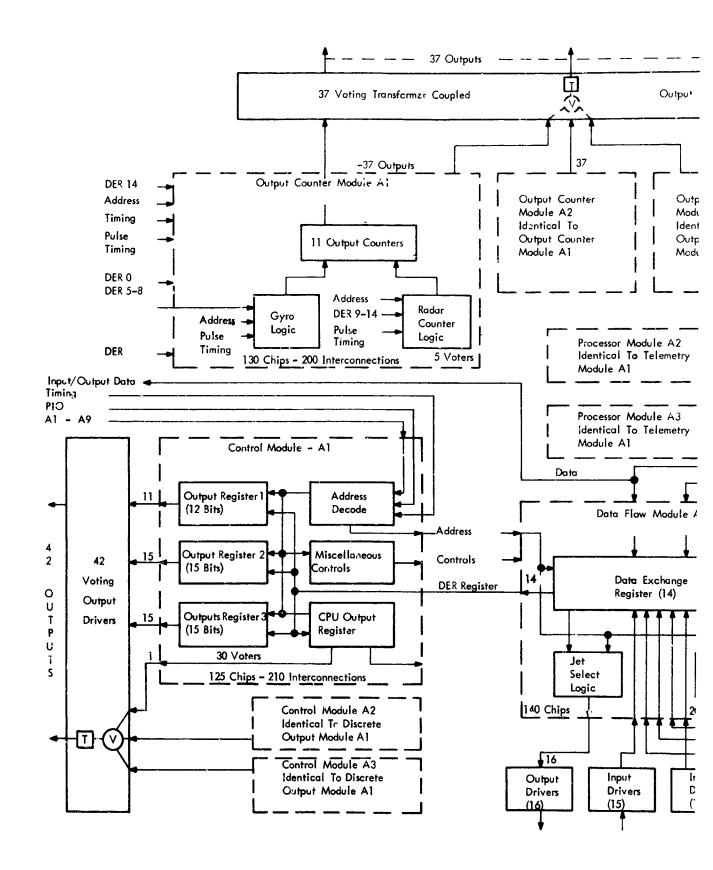

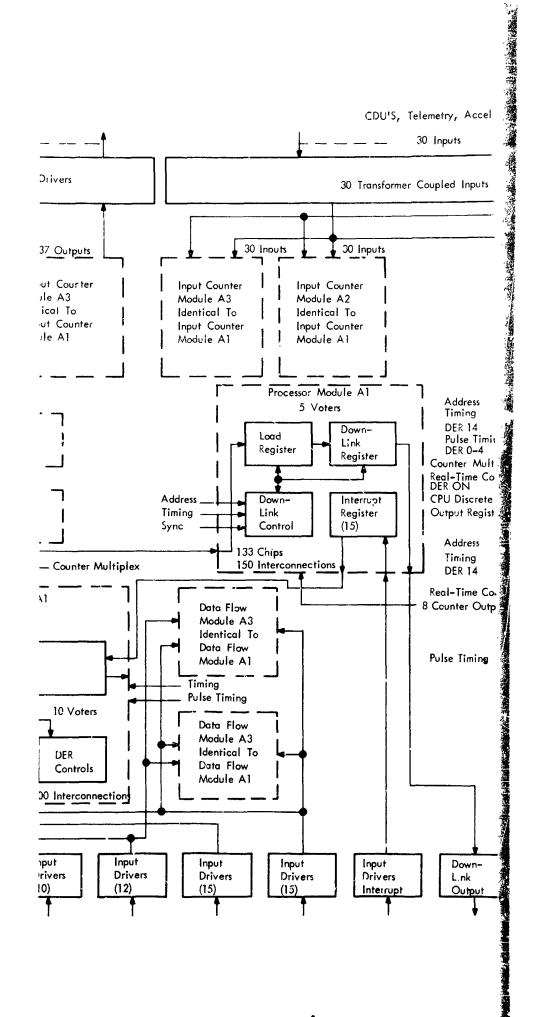

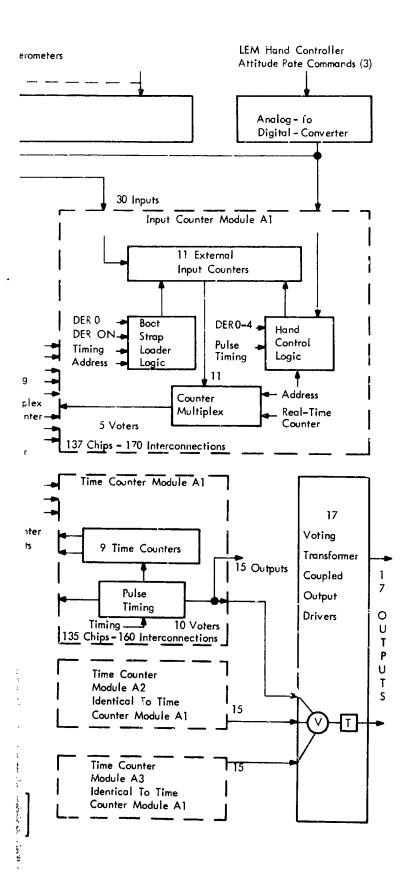

| 46             | AES Data Adapter Flow Diagram                     | 107        |

| 47             | AES Computer Subsystem Package                    | 110        |

| 48             | Voting and Disagreement Detection                 | 136        |

| 49             | Module Switching                                  | 137        |

| 50             | Saturn-V System Simulator Flow Diagram            | 139        |

| 51             | Methods of Error Detection                        | 141        |

| 5 <b>2</b>     | TMR/Simplex Operation                             | 152        |

| 53             | Logic Voter                                       | 155        |

| 54             | Detection Distribution in a Diagnostic Program    | 161        |

| 55             | Apollo Computer - AES                             | 168        |

| 56             | Completed Mockup                                  | A-2        |

| 57             | Representative Module for Phase II Testing        | 169        |

| 58             | Phase I Test Model                                | 171        |

| 5 <del>9</del> | Environmental Test Chamber                        | A-3        |

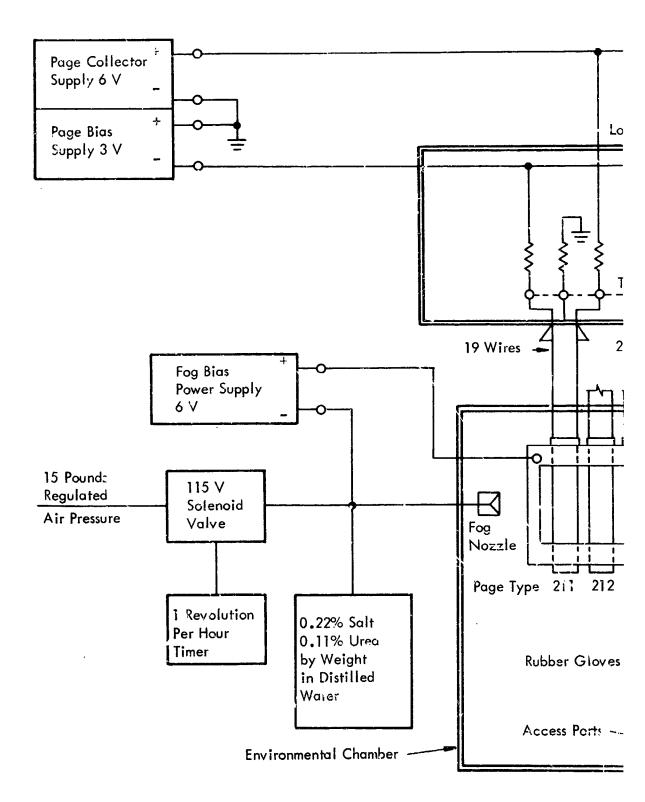

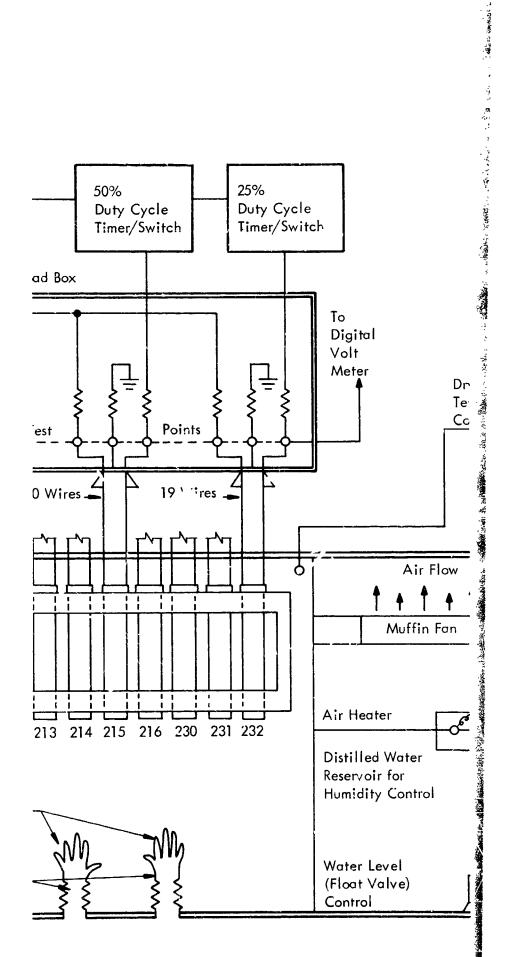

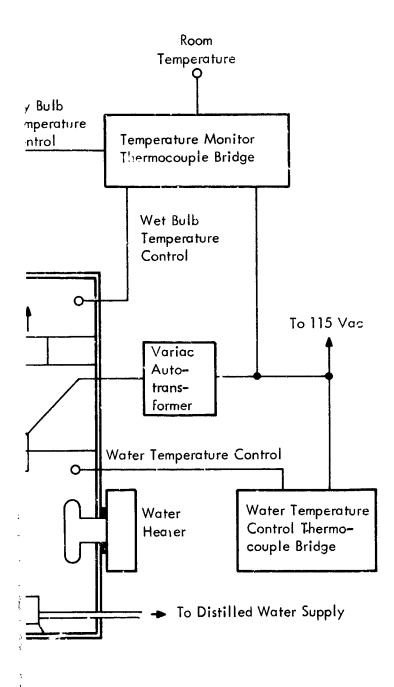

| 60             | Functional Diagram-Test Chamber                   | 173        |

| 61             | Chamber During Test                               | A-4        |

| 62             | Test Fixture                                      | A-5        |

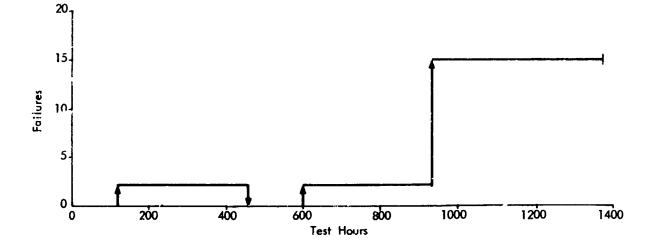

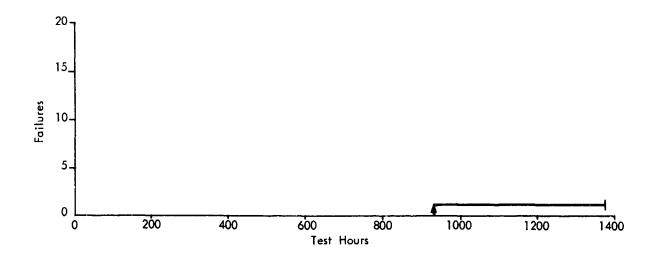

| 63             | Phase II Module Failures (>25 Millivolts)-        |            |

|                | Module No. 211                                    | 180        |

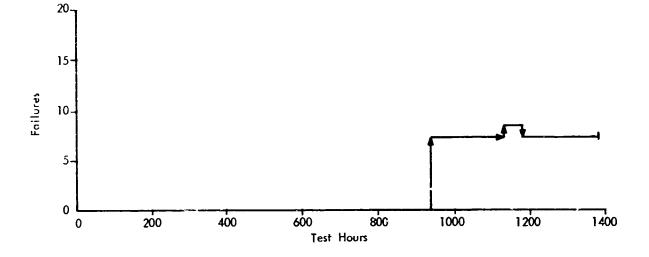

| 64             | Phase II Module Failures (>25 Millivolts)-        | •          |

|                | Module No. 212                                    | 180        |

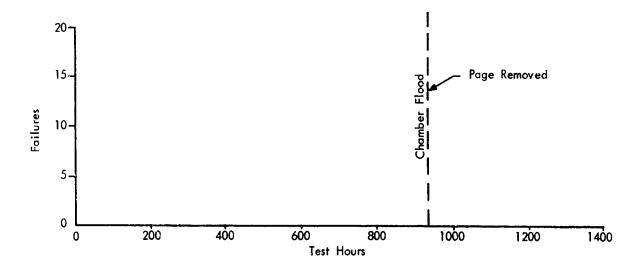

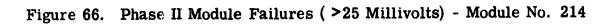

| 65             | Phase II Module Failures (>25 Millivolts)-        |            |

|                | Module No. 213                                    | 181        |

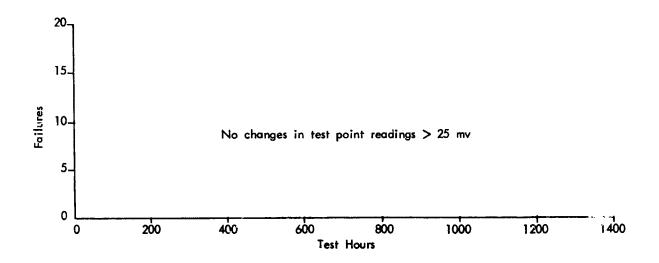

| 66             | Phase II Module Failures (>25 Millivolts)-        |            |

| ••             | Module No. 214                                    | 181        |

| 67             | Phase II Module Failures (>25 Millivolts)-        |            |

| •••            | Module No. 215                                    | 182        |

| 68             | Phase II Module Failures (>25 Millivolts)-        | - <b>V</b> |

|                | Module No. 216                                    | 182        |

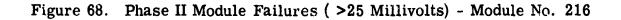

| 69             | Phase II Module Failures (>25 Millivolts)-        |            |

|                | Module No. 230                                    | 183        |

|                |                                                   | 100        |

## LIST CF ILLUSTRATIONS (Continued)

Fignre

| 70 | Phase II Module Failures (>25 Millivolts)- |    |

|----|--------------------------------------------|----|

|    | Module No. 231                             | 13 |

| 71 | Phase II Module Failures (>25 Millivolts)- |    |

|    | Module No. 232 18                          |    |

| 72 | Summary of Failures 18                     | 5  |

| 73 | Nine Modules Under Test - 9 Days A-        | .7 |

| 74 | Nine Modules Under Test - 27 Days A-       | -8 |

| 75 | Seven Modules - 27 Days A-                 | .9 |

| 76 | Individual Module - 32 Days A-1            | 10 |

| 77 | Individual Module - 32 Days A-1            | 1  |

| 78 | Individual Module - 32 Days A-1            | 12 |

| 79 | Individual Module - 32 Days A-1            | 13 |

| 80 | Individual Module - 32 Days A-1            | 4  |

| 81 | Individual Module - 32 Days A-1            | 15 |

| 82 | Individual Module - 32 Days A-1            | 6  |

| 83 | Individual Module - 32 Days A-1            | 17 |

| 84 | Module 212 - 32 Days                       | 18 |

| 85 | Module 212 Enlargement - 32 Days A-1       | 19 |

| 86 | Module 212 Female Connector - 32 Days A-2  | 20 |

| 87 | Module Pin Discoloration - 32 Days A-2     | 21 |

| 88 | Individual Module - 57 Days A-2            | 22 |

| 89 | Individual Module - 57 Days A-2            | 23 |

| 90 | Individual Module - 57 Days A-2            | 24 |

| 91 | Individual Module - 57 Days A-2            | 25 |

| 92 | Individual Module - 57 Days A-2            | 26 |

| 93 | Individual Module - 57 Days A-2            | 27 |

| 94 | Individual Module - 57 Days A-2            | 28 |

|    | -                                          |    |

## LIST OF TABLES

## Table

.

| 1          | Physical Comparisons of Packaging Approaches            | 10   |

|------------|---------------------------------------------------------|------|

| 2          | Contact Resistance (Average of Several Field Sites)     | 15   |

| 3          | Reliability States for TMR Modules                      | 37   |

| 4          | TMR Computer Characteristics                            | 50   |

| 5          | Data Adapter Characteristics                            | 52   |

| 6          | Address Groups                                          | 52   |

| 7          | Reliability Estimates (Basic System)                    | 64   |

| 8          | Regulated DC Power per Section                          | 83   |

| 9          | Power System Component Count                            | 85   |

| 10         | Computer Sizing                                         | 101  |

| 11         | TMR Computer Characteristics (AES)                      | 1.06 |

| 12         | Data Adapter Modules                                    | 109  |

| 13         | Reliability Estimates (AES System - TMR Mode)           | 115  |

| 14         | Reliability Estimates (AES System - TMR/Simplex Mode)   | 115  |

| 15         | List of Available Spares                                | 117  |

| 16         | On-board Spares - 100-Percent Duty Cycle                | 118  |

| 17         | On-board Spares - 50-Percent Duty Cycle, Non-op Failure |      |

|            | Rate > 0                                                | 118  |

| 18         | On-board Spares - 25-Percent Duty Cycle, Non-op Failure |      |

|            |                                                         | 119  |

| 19         | On-board Spares - 50-Percent Duty Cycle, Non-op Failure | -    |

|            | Rate = 0                                                | 119  |

| 20         | On-board Spares - 25-Percent Duty Cycle, Non-op Failure |      |

|            | Rate = $0$                                              | 120  |

| 21         | Reliability Improvement Due to Sparing                  | 120  |

| 22         | AES System Reliability - Re-entry Phase                 | 121  |

| 23         | AES System Mission Reliability                          | 121  |

| 24         | AES System Reliability - Switchable Spare Mode          | 122  |

| 25         | AES System Reliability - Total Mission                  | 122  |

| <b>2</b> 6 | Disagreement Patterns                                   | 125  |

| 27         | Diagnostic Listings                                     | 126  |

| 28         | Signals, Logic, and Voters                              | 144  |

| 29         | Additional Disagreement Detectors                       | 145  |

| 30         | Distribution of Detectors                               | 145  |

| 31         | Error Signal Propagation                                | 147  |

| 32         | Typical Print-out from Redundant Computer Simulation    | 149  |

| 33         | Typical Redundant Computer Simulation                   | 150  |

| 34         | Symptom - Failure Correlation                           | 162  |

| 35         | Computer Symptoms                                       | 163  |

| 36         | Test Equipment Listing                                  | 174  |

| 37         | Test Schedule                                           | 177  |

.

#### 1.0 PACKAGING

The packaging scheme of the Saturn V computer and Apollo backup data adapter was examined to determine its applicability to inflight maintenance, sparing, and module and channel switching in the high humidity - zero gravity AES environment. Consideration was then given to other packaging techniques which would improve operation in this environment without resorting to hermetic sealing. Techniques that required maintenance tools which could not be used by a suited astronaut were not considered in this study.

The study approach to the packaging problem was to first examine methods for sealing the replaceable modules within the computer and data adapter frame to provide gross protection against the high humidityzero gravity environment and then to examine methods for providing additional environmental protection on the replaceable module level, especially at the connectors. Since any sealing method is imperfect, especially over long periods of time, a study was made of available contact materials and connection techniques to ensure proper operation of the module and cable connectors in the presence of the contaminants which manage to penetrate the equipment sealing features. Finally, consideration was given to size and connection constraints on the replaceable module which would affect the physical organization of the computer and data adapter.

### 1.1 Limiting Exposure

A repackaging study was performed to determine the feasibility of sealing the computer and data adapter circuits for operation and maintenance in the high humidity-zero gravity AES environment. The approach investigated to provide operation in the adverse environment was gasket sealing with a slight overpressurization of the units maintained by periodic repressurization. Maintenance of the circuits would be allowed by resealing, purging, and repressurization after repair.

Almost perfect purging of gasses and water vapor and very short purging time periods are feasible by venting the seal d equipment to space. The installation of heaters within the computer and data adapter to operate during periods when a cover is removed and during purging would provide additional assurance against the accumulation of contaminant gasses and vapors. The circulation of hot fluid through the coolant system of the unit being purged or repaired would provide protection equivalent to heaters, as would the application of external infrared heaters or dry air blowers.

1

Treatment of the internal surfaces of the computer (including electrical connections) with hydrophobic film would tend to prevent the condensation of moisture on critical areas, and where moisture did condense it would tend to form into droplets instead of thin films. The entire interior of the computer could be treated with any of several available silicone sprays on assembly, and solid silicone compounds could be applied during maintenance in the zero gravity environment where sprays would be impractical.

Closed loop pressure systems were considered but will not be emphasized in the study. The use of freon in a closed loop system (or even in a static system) offers several advantages including moisture repellent characteristics.

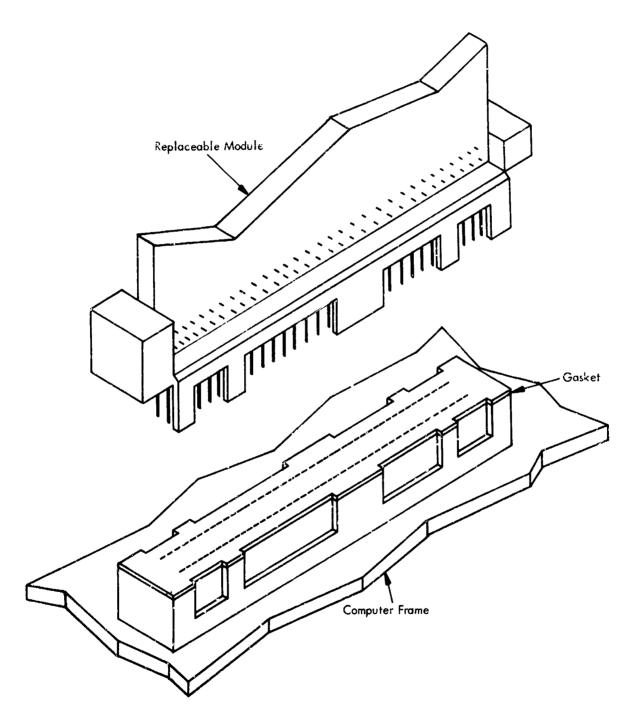

Three approaches to packaging the computer for operation and maintenance in the AES environment were examined and compared. These three approaches differ in the level of packaging to which the sealing and purging techniques are applied. Although the preliminary investigations were related only to the computer, the concepts apply as well to the data adapter.

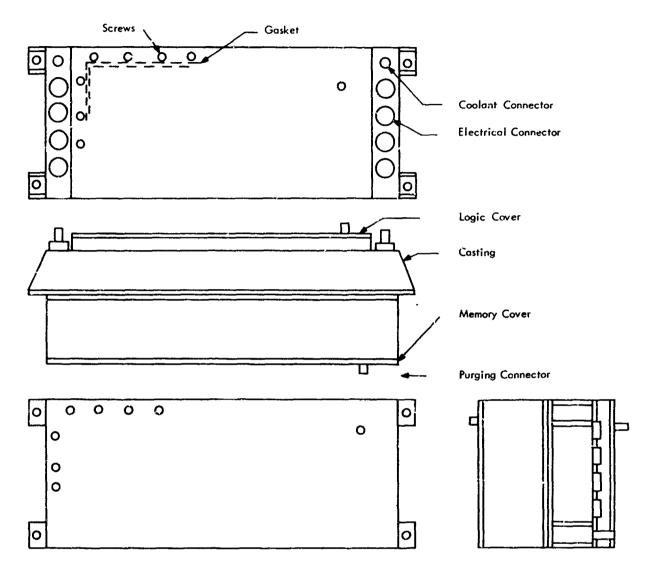

In the first approach the entire computer is sealed as a unit as shown in Figure 1. Upon removing one of its two covers to replace a failed module, the entire computer is exposed to the adverse AES environment. When the cover is replaced after repair, the free moisture and contaminants trapped in the computer are purged and the computer repressurized to somewhat greater than cabin pressure with dry gas.

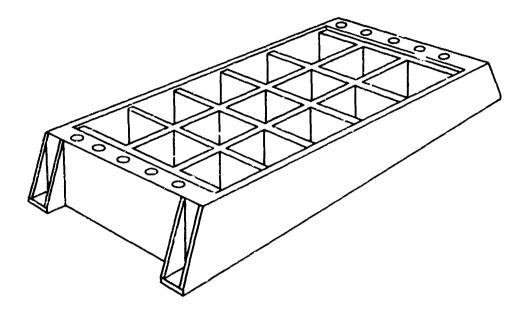

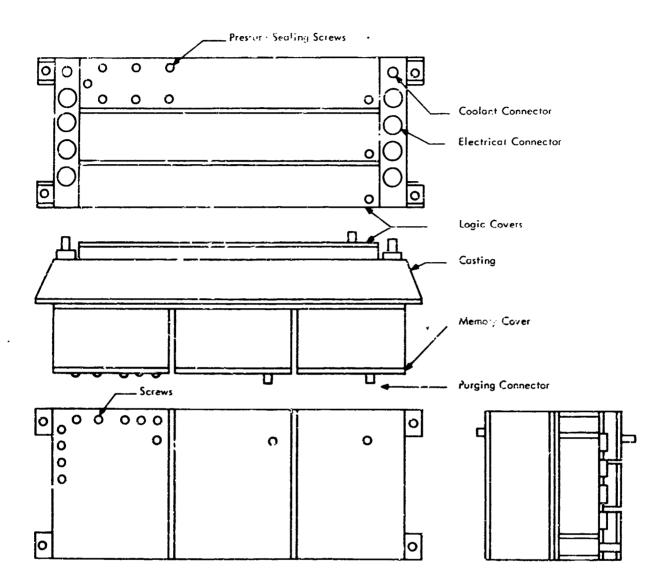

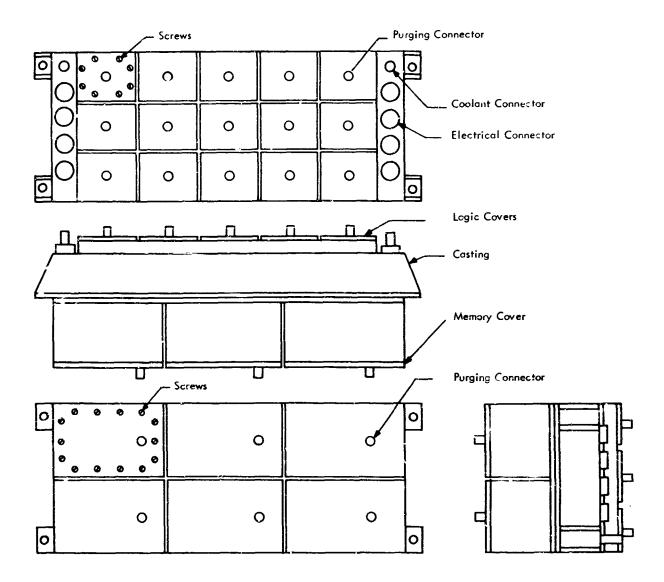

In the second and third approaches an attempt is made to limit the degree of exposure during a maintenance action by sealing various portions of the computer independently. Since a triple modular redundant (TMR) computer consists of essentially three individual computers, each channel can be separately sealed so that one third or less of the computer is exposed each time a repair is attempted. The casting of the Saturn V computer is designed such that each logic channel is partitioned into effectively five cells as shown in Figure 2. If each cell is separately sealed, then a fifteenth or less of the computer is exposed each time a repair is attempted. These second and third packaging approaches are illustrated in Figures 3 and 4, respectively.

The computer covers can be sealed by means of special gaskets or modified O-rings. Gasket-sealed electronic units have been produced at IBM to provide leakage rates as low as  $10^{-7}$  cubic centimeters per second per inch of linear seal length for ASQ-38, Gemini, and other applications. The larger covers, especially those of the first approach above, would preclude leakage rates as low as this so that periodic

Figure 1. Unit Packaging Approach

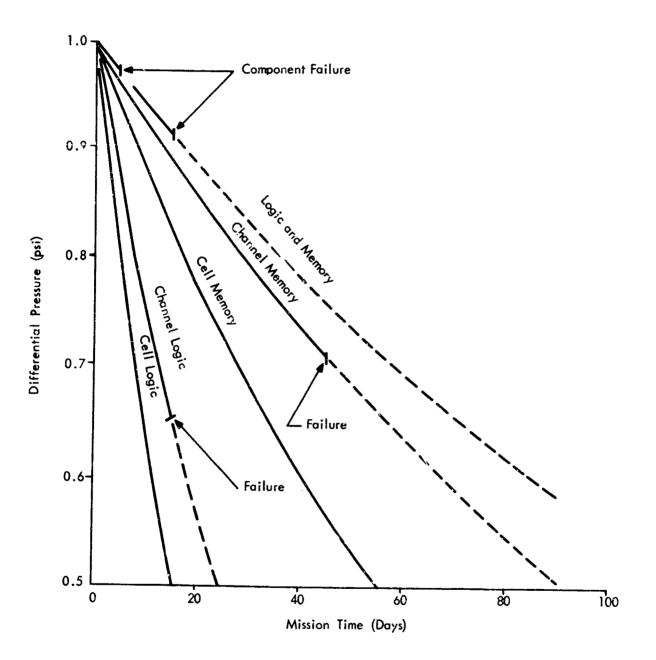

repressurization of the computer and data adapter would be required. Figure 5 shows how the residual gas pressure of the proposed designs would decrease with mission time.

An examination of Figure 5 reveals the following information:

1) The unit-seal approach affords the lowest leak rate (because its linear seal length to volume ratio is the smallest). For the same reason, the leakage rates from the memory modules are less than the leakage rates from the logic modules for both the cell-seal and channel-seal designs.

Figure 2. Computer Casting

2) If the assumption is made that a module replacement occurs on the average of once a week during the 90-day mission (10 logic failures and 3 memory failures per mission), then the time period for which the seal is effective (defined as the period during which the residual pressure exceeds 50 percent of the initial overpressure) is determined by the component failure rate of the computer rather than by the leakage rates for both the unit-seal and channel-seal designs. These factors are tabulated from Figure 5 as follows:

|                | Time Period (days) to |              |  |

|----------------|-----------------------|--------------|--|

| Sealing Level  | Failure               | 50% Pressure |  |

| Unit Logic     | 4 1/2                 | 90           |  |

| Unit Memory    | 15                    | 90           |  |

| Channel Logic  | 15                    | 25           |  |

| Channel Memory | 45                    | 90           |  |

|                |                       |              |  |

Figure 3. Channel Packaging Approach

3) For the same assumptions, the time period for which the seal is effective for the cell-seal design is determined by leakage rate rather than component failure rate. The following values were taken from Figure 5.

|               | Time Period (days) to |              |

|---------------|-----------------------|--------------|

| Sealing Level | Failure               | 50% Pressure |

| Cell Logic    | 67                    | 16           |

| Cell Memory   | 90                    | 55           |

Figure 4. Cell Packaging Approach

No attempt was made in the leakage rate computations to account for the probable differences in efficiency of the various sealing approaches. Experience at IBM has indicated that the leakage rate of a large seal (such as an entire computer cover) compared to that of a small seal (such as an individual cell cover) is greater than that predicted simply by a difference in the linear length of the seal. This effect is due to the greater difficulty in maintaining tolerances, parallel sealing surfaces, and uniform sealing pressure with larger units. If this effect were taken into account, the curves of differential pressure versus mission time would be grouped closer together.

Figure 5. Initial Leakage Rate

In addition, other maintenance features favor the cell-seal design. An average of about 9 screws would have to be removed every time a failed module is replaced in the cell-seal design compared to 23 screws for the channel-seal and 32 screws for the unit-seal designs. The exposed volume per repair is about as follows:

|               | Volume Exposed (in <sup>3</sup> ) |         |      |

|---------------|-----------------------------------|---------|------|

| Cover Removed | Unit                              | Channel | Cell |

| Logic         | 1500                              | 125     | 25   |

| Memory        | 1500                              | 300     | 150  |

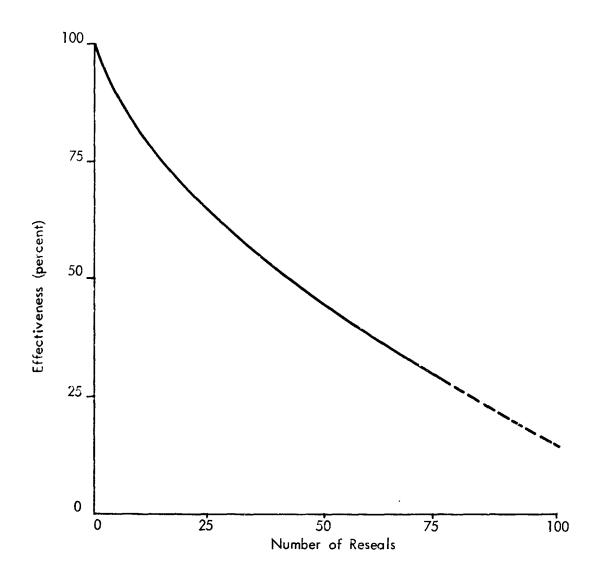

Gasket seals have a tendency to deteriorate with usage. Each time a seal is broken and then resealed, the effectiveness of the seal is compromised. Figure 6 is an estimate, based on IBM experience, of the effectiveness of a gasket seal versus use in the AES mission.

Repackaging the computer into independently sealed cells provides an improvement in ease of maintenance and in exposure to the AES environment during repair. The average number of screws which must be removed to replace a failed module is less than a third and a half, respectively, of that of unit and channel sealing, respectively. The amount of circuitry exposed during a repair is less than a twentieth that of unit sealing and a fifth that of channel sealing.

The advantages of cell sealing over the other two approaches are obtained at the cost of somewhat increased size and weight, as indicated in Table 1. Since the advantages appear to outweigh the disadvantages, the cell or honeycomb approach would be recommended over the other two approaches.

### 1.2 Connector Sealing

Even if fairly efficient protection of the replaceable modules is achieved by sealing the modules within the computer and data adapter frame and by limiting the exposure of the modules to the high humidityzero gravity environment, some free moisture and contaminants will collect eventually at the module connectors. Whatever packaging techniques are selected for AES applications, the problem of sealing the intermodule and inter equipment connectors against the high humidityzero gravity environment will exist.

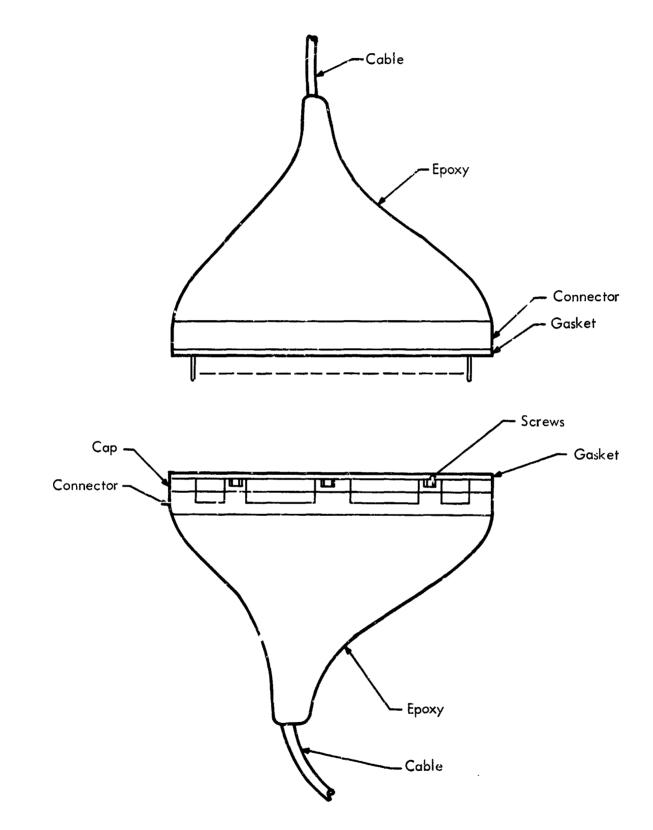

Figure 6. Seal Deterioration with Use

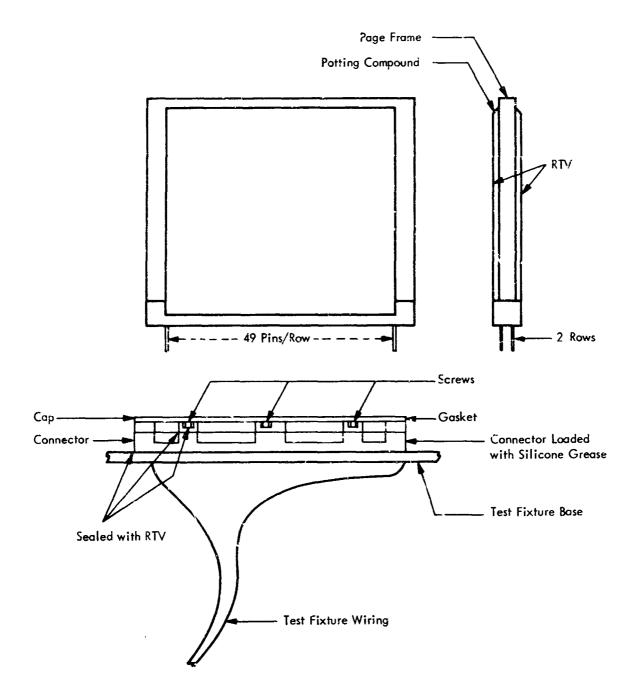

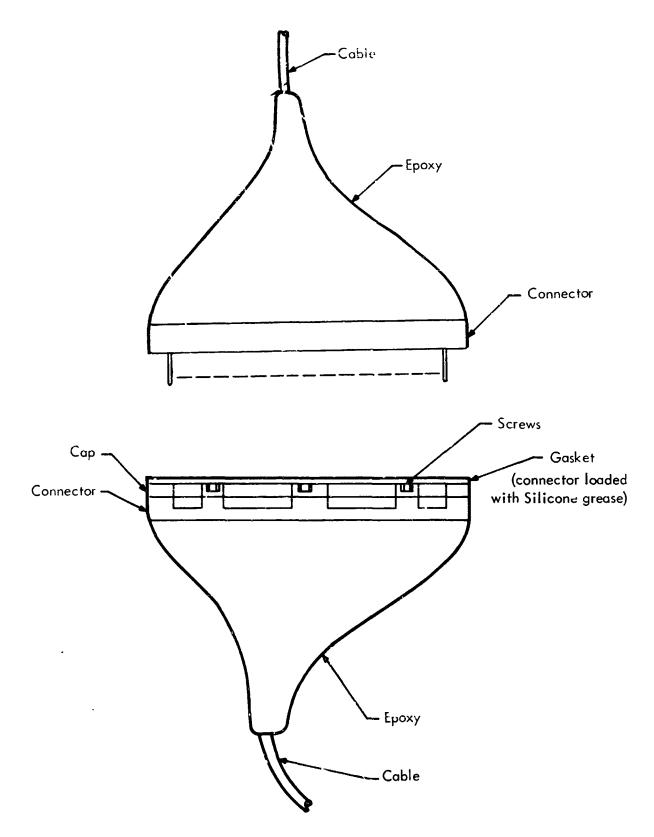

Design analysis and exploratory testing of methods of sealing the connector of a replaceable module resulted in the selection of a gasketsilicone gel technique for the representative module to be demonstrated according to the study test plan. As shown in Figure 7, a silicone rubber gasket was cemented to the face of the female connector. The female connector was then loaded with a silicone gel. The male pins on the replaceable module were also coated with silicone. Since the slotted holes in the gasket are somewhat smaller than the male pins, a wiping action occurs both on insertion and on removal of the replaceable module. This wiping action serves to remove moisture from the male pins on insertion and to retain the silicone gel in the female receptacle upon removal of the replaceable module. This concept was used in the Phase II Testing.

| Dhygionl Characteristics   | Deviation from Saturn V<br>(percent) |         |      |

|----------------------------|--------------------------------------|---------|------|

| Physical Characteristics   | Unit                                 | Channel | Cell |

| Volume and Mounting Area   | + 6                                  | + 13    | + 17 |

| Weight                     | + 1                                  | + 3     | + 5  |

| Screws/Maintenance Action  | Ref.                                 | - 25    | - 75 |

| Exposed Volume/Maintenance | Ref.                                 | - 65    | - 90 |

| Leakage Rate Initial       | Ref.                                 | + 75    | - 25 |

| End of Mission             | Ref.                                 | + 30    | - 80 |

## TABLE 1 - Physical Comparisons of Packaging Approaches

Phase I testing included investigations of gasket seals on the interface between the male and female connectors, sealing of the connectors with various greases, and combinations of gaskets and greases. The technique showing the most promise is sketched in Figure 8. A male and female Saturn-V page connector were wired and sealed with epoxy on their rear surfaces. A silicone rubber gasket was glued to the face of the female connector with Dow-Corning A9-4000. The female cap was removed and DC-3 silicone grease packed inside the connector. The pins of the male connector were also saturated with DC-3 silicone grease. Contact measurements before and after application of silicone grease indicated that the grease had no measurable effects on the contact resistance between male and female connections. Leakage resistance checks between adjacent pins were made under the following conditions:

- 1) Initial leakage resistance of mated test model 500,000 megohms;

- 2) Immersed mated connector in fresh water for 15 seconds and shook off excess water -2,000 to 10,000 megohms, erratic

6 -

Figure 7. Connective Sealing Technique (Modified Saturn-V Connector)

¥

Figure 8. Phase I Test Model

- 3) Unmated connector, dried male for 2<sup>o</sup> seconds at 125 degrees Fahrenheit, remated – 140,000 megohms

- 4) Unmated connector, immersed both halves in fresh water for 15 seconds, shook off excess water, remated - 70,000 megohms

- 5) Unmated connector and remated 5,000 megohms

- 6) Unmated connector and remated -70,000 megohms

- 7) Unmated connector and remated 85,000 megohms

- 8) Unmated connector and remated -60,000 megohms

- 9) Unmated and remated connector under fresh water reading erratic;

- 10) Unmated connector and shocked water of male connector on desk top, remated 50,000 megohms

- 11)  $U^r$  nated connector and remated -10,000 megohms.

Although the preceding readings appeared erratic, they were very encouraging from the following viewpoints:

- 1) The lowest leakage resistances were still in the thousands of megohms

- 2) The surface between the cap and connector of the female and the screw holes in the female presented sources for leakage which were sealed during Phase II tests.

- 3) The large holes in the female gasket which allow penetration of the male pins also allowed penetration of excess moisture.

The same test was essentially repeated in a salt water solution with no significant changes.

Another material used to seal the female connector was Dow Corning Sylgard 51 dielectric gel. When cured, it develops into a soft, transparent, jelly-like mass having good self-healing qualities. Different consistencies were used, but none were found to be satisfactory. All had a tendency to be drawn out when the connector was unmated. The most optimum sealing would be achieved by sealing the female connector with a gasket without the need of impregnating with silicone gels. A most promising concept is that of a membrane which has qualities of self-sealing when unmated. Special tools would be required to fabricate this type of gasket.

Under any conditions, a new development program would have to be initiated for a connector for this application. The new connector would be a molded one-piece connector with a self-contained gasket containing approximately 200 self-sealing holes.

#### **1.3** Contact Considerations

An investigation was performed to determine the best contact material for use in the AES connector application. Work performed in IBM's field test program was included in this investigation.

The data of Table 2 presents partial results of a continuing IBM environmental field test program to determine certain properties of electrical contact materials. The tests were performed for a period of over a year at several test sites representative of a variety of environmental conditions. Relative humidity at these sites varied from around 10 to over 80 percent. Measured airborne contaminants included various amounts of NO<sub>2</sub>, HF, NH<sub>3</sub>, SO<sub>2</sub>, O<sub>3</sub>, CL<sub>2</sub>, and H<sub>2</sub>S. Ambient temperatures varied over a range from 60° to 100° F. Table 2 shows a summary of the original values of contact resistance for the contact materials tested and the values after 1 year of environmental exposure. The values in the table were obtained by averaging the data from several test sites.

Use of copper alloys or other of the high resistance materials listed in Table 2 would not be considered for use as contact material in AES applications. Some of the data showed practically infinite resistance after 1 year of exposure to the most adverse environments. Although not indicated in the table, caution should be exercised in the use of palladium or palladium alloys containing copper where high concentrations of organic materials may be encountered. Because of the catalytic nature of palladium, polymers may form in a high organic atmosphere.

| Resistance<br>(ohms) | Original                                                                                        | After 1 Year                                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 100                  |                                                                                                 | Aluminum, Nickel-Silver,<br>Beryllium Copper, Cop-<br>per, Phosphor Bronze,<br>Brass, Nickel, Silver-<br>Cadmium Oxide |

| 0.01 to 100          | Aluminum, Nickel-Silver,<br>Phosphor Bronze, Brass,<br>Nickel                                   | Red Gold, Green Gold,<br>Silver                                                                                        |

| 0.001 to 0.01        | Beryllium Copper, Cop-<br>per, Red Gold, Green<br>Gold                                          | Tin, Tin-Lead, Rhodium,<br>Platinum, Platinum-<br>Iridium                                                              |

| 0.001                | Silver, Silver-Cadmium<br>Oxide, Tin, Tin-Lead,<br>Rhodium, Platinum,<br>Platinum-Iridium, Gold | Gold                                                                                                                   |

# TABLE 2 - Contact Resistance<br/>of Several Field Sites)(Average

The films that form on the surface of silver tend to be highly resistive, coherent. and tenacious if the major ingredient is silver sulfide. However, if appreciable amounts of silver chloride are present, the film may be nonadherent and of moderately low electrical resistance. Although the average contact resistance after 1 year was indicated in Table 2 as 0.01 to 100 ohms, the measured values at the various sites varied over the range bracket of 0.001 to over 100 chms. Although silver would be very applicable in controlled environments, it will not be considered further in this study.

Samples of 10, 14, and 18 carat green-gold alloys (simple solid solutions of gold and silver) showed characteristics similar to silver in wide variations of contact resistance with environment. Although the variations were less extreme because the films were thinner in proportion to the gold content, caution should be used in the use of green gold alloys for AES applications. Red gold alloys (solid solutions of gold and copper) compared generally with green gold and the same conclusions apply. The oxide films of tin, lead, and other soft metals tend to be coherent, self-limiting, and thin. These films are easily penetrated under pressure as the soft-bulk material yields. Despite the apparent attractions of tin, lead, indium etc., their use is not recommended for low-load separable-contact applications, especially in sliding situations where wear debris can build up.

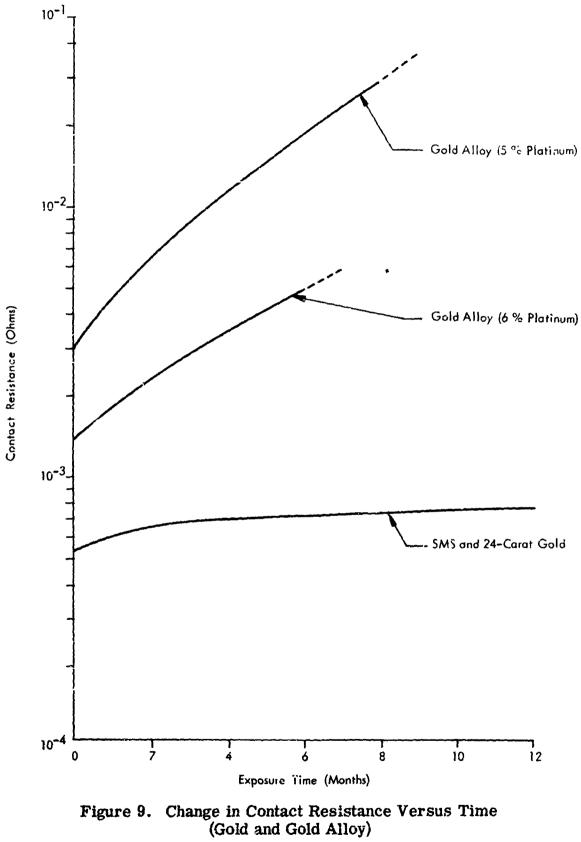

Gold and gold alloys would seem to be best applicable as contact materials for AES connectors. The excellent behavior of gold and gold alloy with exposure time is shown in Figure 9. The higher platinum content alloy (6-percent platinum, 25-percent silver, 69-percent gold) is probably preferred although more test data is required for a firm decision. Visible films do exist on exposed gold surfaces but consist of absorbed material rather than tarnish products. SMS gold and 24carat gold showed similar properties during the tests.

Since gold and low resistance gold alloys are soft materials, their primary use as contact materials to date has been in the form of gold plating over base materials such as nickel or copper. The major problem in this application has been the porosity of the plating, which leaves the porous areas of the basic materials exposed to contamination. Resulting degradation of the contact surface can occur in two different ways.

When the base material exposed under the pores in the gold plating are attacked by contaminants such as sulfur, chlorine, and nitrous oxide, the resulting sulfides, chlorides, and nitrates will migrate through the gold pores and spread out over the surface of tige contact, forming high resistance films. Although these creeping films may be controlled by means of surface lubricants or choice of base material, the primary solution will probably be controlled porosity.

The second phenomenon which porous plating invites is electrolytic activity at the base material in the presence of moisture and active atmospheric contaminants. Flaking of the gold plating itself can result as well as formation of resistant films by the migration of corrosion products to the contact surface.

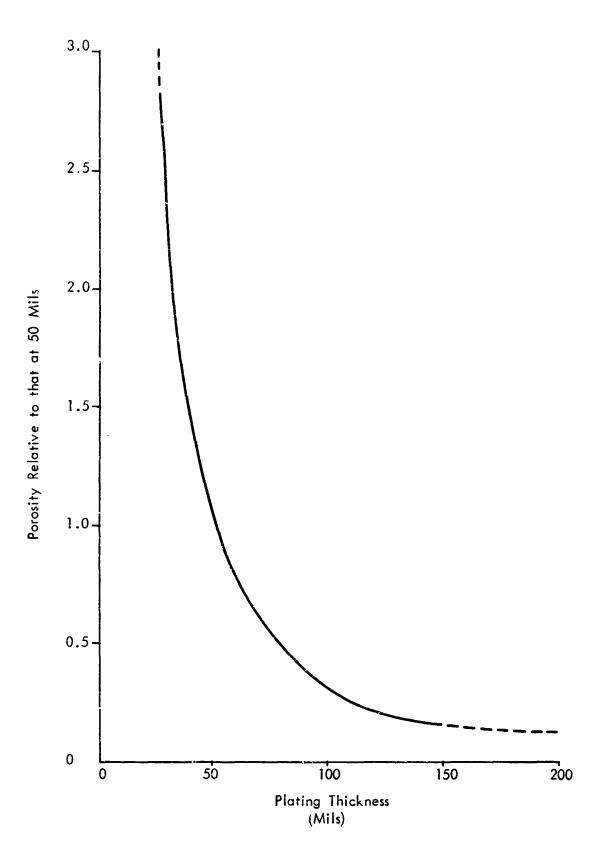

Both types of contact degradation dictate that the porosity of the gold plating be minimized. The obvious (pproach is to increase the thickness of the plating. However, Figure 10 shows that although the porosity does decrease as plating thickness increases, the curve levels off at the higher thicknesses. This curve represents an average of data at IBM and elsewhere and is plotted relative to the plating porosity at 50 mils plating thickness as standard (or unity). Because of practical considerations, plating thicknesses over 150 mils are not being considered at IBM.

Figure 10. Porosity Versus Thickness for Gold Plating

.

However, experience has shown that other considerations such as production and testing methods tend to predominate over actual plating thickness in determining porosity at the higher thicknesses. For example, an increase in thickness from 50 to 150 mils was obtained in one case by increasing current density rather than increasing processing time, and the resulting thick plating had higher porosity than the thin plate. The degree to which porosity can be minimized is very sensitive to the cleaning and handling techniques used on the base material.

Porosity of the final product can be controlled by adequate testing of the plating to screen out those samples exceeding a predetermined limit. For critical applications such as AES, the limit can be set much more stringently than the limits set for commercial grade platings. Very sensitive electrographic testing methods are used at IBM in which an electrolyte-saturated filter pad is wrapped around each contact and a small current made to flow from the contact through the pad. After a fixed time period, a reagent applied to the pad indicates the porosity by color test.

Protective contact coatings have been produced by welding gold foil onto the base contact material rather than by plating. Although this method has essentially eliminated the porosity problem associated with plating methods, it has not proven suitable for commercial applications because of the inherent cost of the process and because of the difficulty in producing uniform coating thickness. This technique should not be overlooked, however, for low quantity-highly critical applications such as AES.

Multilayer platings are generally more expensive than single layer platings of the same total thickness and are therefore not favored for high production commercial applications. However, when a contact surface is built up from several layers of gold plating, there will exist some misalignment of the porosity of the individual layers and a resulting decrease in effective porosity over that of a thick coating deposited as a single layer.

Even if the problem of porosity is solved by pursuing those methods which have been rejected for commercial applications because of cost or of the difficulties in mass production, a problem may still exist in the form of diffusion, which in the migration of base contact material or impurities through the plating material itself rather than through the pores. The transferred materials form resistive films on the surface of the gold plating in the same manner as those caused by porosity. Some commercial applications use an intermediate barrier layer of nickel between a base material of copper and the gold plating to retard diffusion. Rhodium was found to exhibit the highest retardation capability as a barrier layer but was considered too expensive, too difficult to process, and too brittle for commercial use. The choice of plating and base contact materials must also be made after consideration of the possibility of galvanic corrosion. To prevent galvanic action, metals in relatively close position in the electromotive series chould be chosen for plating and base materials.

It appears that the choice of nickel as the base material with gold as a thick-film surface material is best suited for AES applications in view of all the preceding considerations. The thick film should be built up by several successive electrodeposits or, preferably, by welding gold foil on the nickel contact pins. Very stringent process and testing methods must be applied, which will surely result in very high rejection rates. Although the resulting connector costs will be considerably higher than the costs of presently employed commercial connectors, the pin corrosion problem would be minimized for the AES applications, and the costs seem to be justified for low quantity, highly critical usages.

The resistance of an electrical contact is made up of two components: 1) constriction resistance due to the convergence of current flow lines to points of contact and 2) film resistance due to impedance of electron flow by the surface films.

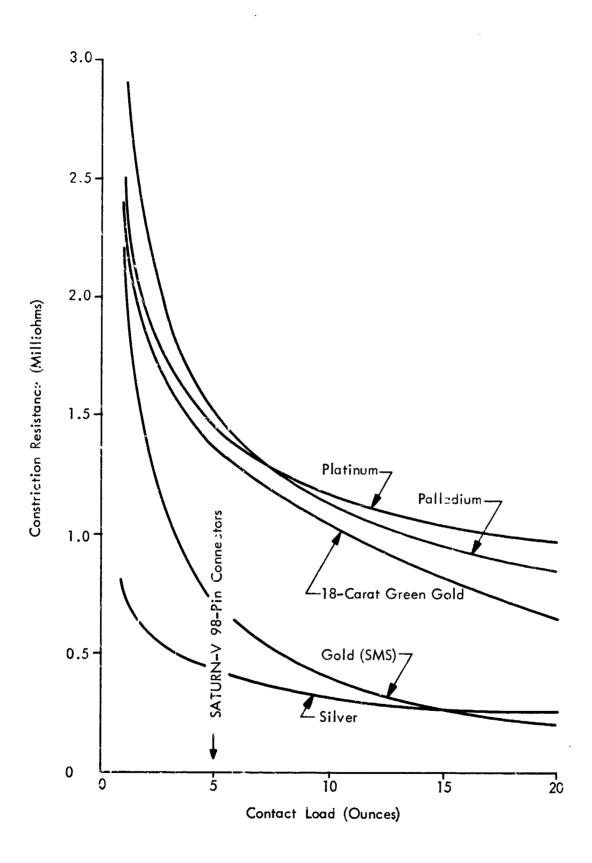

Constriction resistance varies primarily with the resistivity of the contact material, the contact load, and the contact geometry. Figure 11 shows the resistance of several contact materials measured with a 1/8-inch diameter, spherically shaped gold probe tip. The curves indicate the manner in which constriction resistance varies with contact load for given contact geometry and material. Note that some of the curves cross, suggesting that the choice of contact material for a given connector design may be made on the basis of the contact load of that connector. However, consideration must first be given to film resistance.

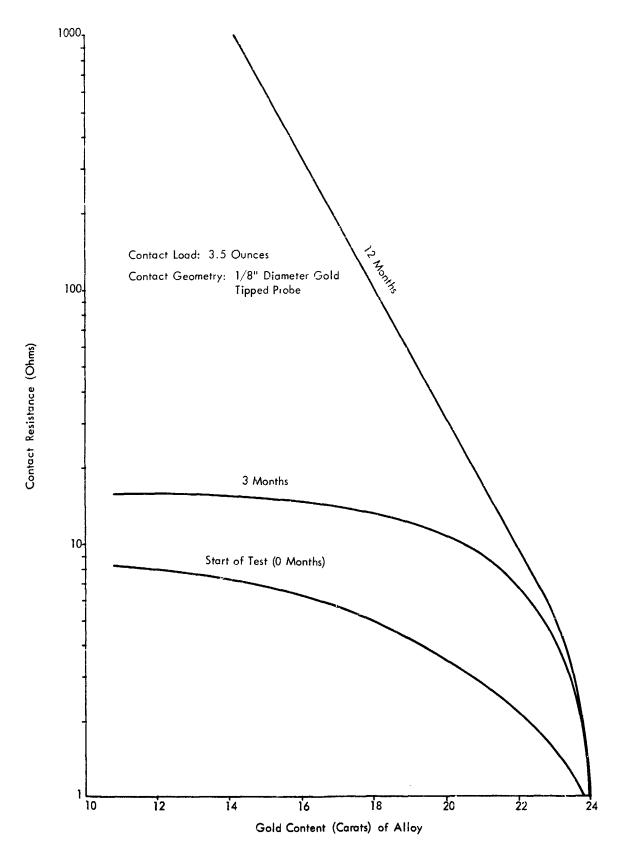

Contact films are the result of reaction of the contact material with one or more contaminants in the environment or absorption of impurities by the contact surface. In general, all metals except pure gold will form reaction films. Gold alloys will form reactant films in proportion to the amount of alloying material as indicated in Figure 12. The curves were derived from IBM field test data. Gold alloys may be required in AES applications to provide sufficient hardness and wear resistance.

Figure 11. Constriction Resistance Versus Load

Figure 12. Contact Resistance Versus Alloy Gold Content

#### 1.4 Replaceability

Inflight maintenance, for prolonged missions, requires the careful analysis of certain aspects of packaging and accessibility requirements of man-rated electronic equipment. One of these aspects is replaceability.

Replaceability is defined as the proper restoration or substitution of like modules in a system or unit in the minimum period of time without the use of any special tools. In the AES computer-adapter packaging configuration, it was decided that all the modules were to be designed as pluggable units. Each would have a connector on its mating face. The AES equipment is basically divided into five major modules: logic circuits, memories, power supplies, filters, and interface drive circuits. All these modules will be designed as hermetically sealed units. Similar units, filled with a nontoxic gas, have been extensively used in the IBM designed B-52 bombing-navigation equipment.

All the logic circuits such as timing, control register, and arithmetic logic, will be mounted on a page similar to the ones used in the Saturn-V Launch Vehicle Digital Computer. The page will be slightly larger, measuring 4 inches square and will be mounted on a 200-pin connector. This assembly will then be covered with a can and joined hermetically with a tear strip. The tear strip has been successfully used in the B-52 aircraft electronic equipment. The tear strip concept lends itself to manufacturing checkout, testing, and depot repair.

The sealed can could be made out of either stainless steel or aluminum. Before a recommendation is given, trade-offs would be made of heat transmission, weight, corrosion, and cost. The canned pages will be packed with silicon grease, RTV, or sylgard to prevent moisture penetration. The hermetically scaled cans will be made with guides on each side to assist in aligning the connector and to assist in heat transmission.

Once aligned the page will be mated by a screw action. The screw will be made a part of the page assembly. Its purpose will be to firmly set the connector and lock it into place by means of a camming action. No additional covers will be used.

The power supplies and filter will be approximately 4-inch cubes. Power supplies will be hermetically sealed in either stainless steel or aluminum cans. Modules will be made self-aligning. They will be secured into place either by a screw-cam affair similar to the logic pages, or a ball-type camming arrangement will be used. End item design will depend on size, weight, and accessibility in the vehicle. Three double density memories will be required. The memories will be approximately  $6 \times 5-1/2 \times 4$ -inches in size and will be mated in position using a scheme similar to that used for the power supplies. Repairability will be the prime factor in deciding a packaging concept. This is due to the high cost of the memories.

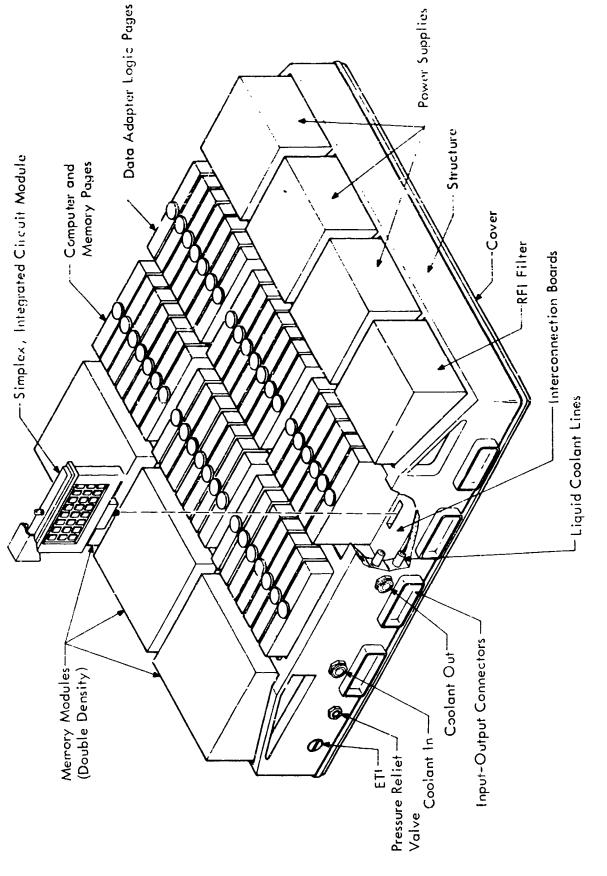

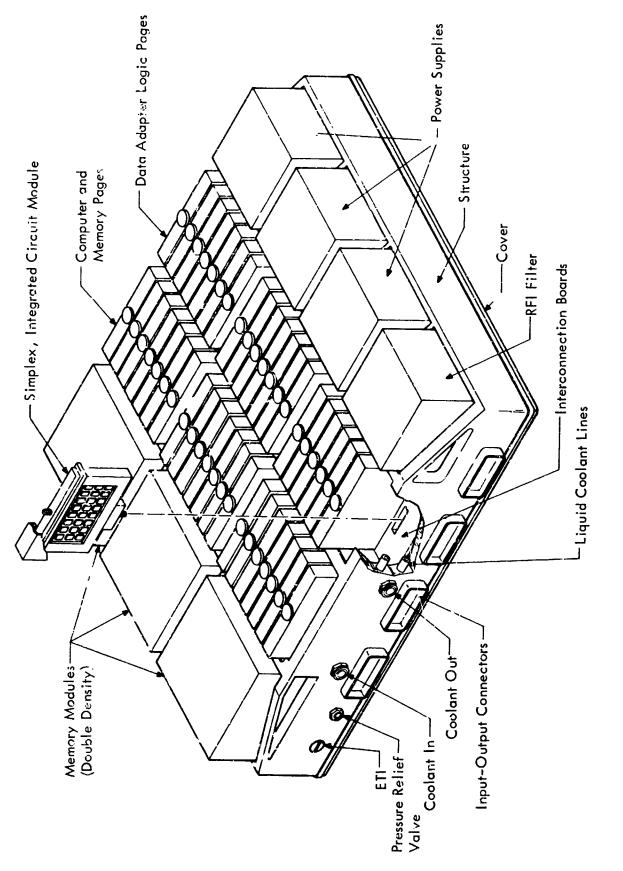

The present design has all modules mounted on the top face of a chassis. Integral cooling, similar to that used for the Saturn-V LVDC, will be used. The bottom face of the chassis will contain the interconnection wiring. The bottom section will be hermetically sealed. The estimated weight of the entire package is 69 pounds.

The present packaging configuration, discussed in the prec ling paragraph, may be slightly altered when the vehicle mounting and installation requirements are more completely defined. At present, the package will be installed face up, rack-and-panel style. Other packaging configurations can be used, i.e., a page type package hinged on one side or a spindle package mounted in a merry-go-round style. All these form factors will be fully considered in the final design when requirements are fully defined.

### 1.5 Module Size

Every consideration was given to designing the computer as compactly as possible without sacrificing the maintainability and reliability of the equipment. The present data processing equipment consists of two pieces of hard vare, a computer unit and a data adapter unit. Every attempt in this program was made to combine the equipment into one unit and still have a small, light unit.

The AES computer and data adapter consist of memories, power supplies, filter, logic pages, and drive circuits. Every effort was exerted to combine circuits for minimum package density. Different machine packaging trade-offs, were considered. It is envisioned that the computer will be fabricated with integrated circuits; however, it can be made applicable to the present ULD circuit family.

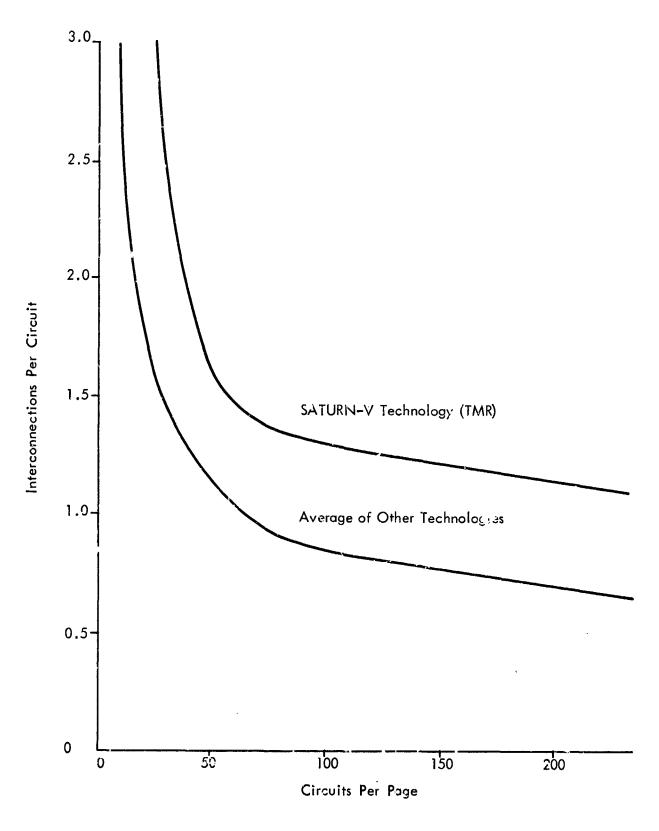

One significant parameter which is frequently used in machine packaging trade-offs is the ratio of required module (page) interconnections per circuit (ULD, flatpack, etc.). Figure 13 shows the results of available data on this parameter for Saturn-V and for the average of other technologies including integrated circuits. Both curves show a general trend that the ratio decreases rapidly as the packing density increases up to about 50 circuits per module and then iends to level off.

Figure 13. Interconnections per Circuit Versus Circuits per Page

The total number of pluggable interconnections of a machine can now be found for any packing density (circuits per page) by multiplying the total number of machine circuits by the interconnection per circuit value for that packing density.

The curves of Figure 13 indicate that consideration for the total number of pluggable interconnections places a lower limit on the packing density. That is, interconnections limit the module size to some minimum number of circuits per module. The vertical displacement of the Saturn-V curve from the average is due to the reliability requirement of the TMR machine as well as to the difference between Saturn technology and integrated circuit technology. In general, redundancy techniques should increase the number of circuits per page to provide an area sufficiently large enough to accommodate a reasonable block of logic.

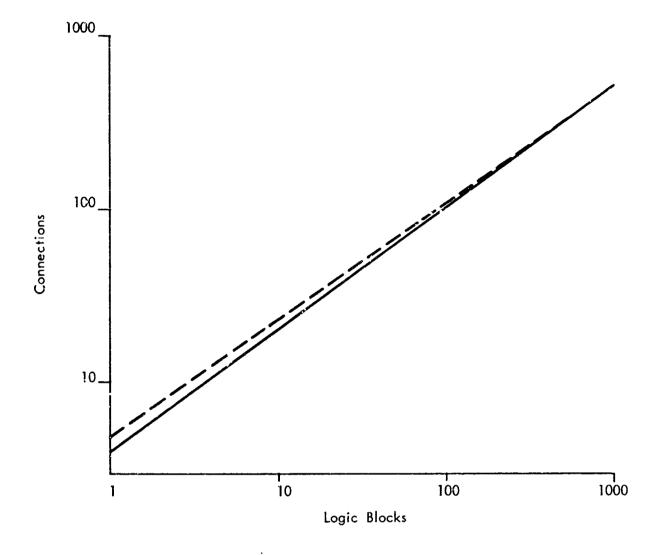

The curves in Figure 13 were found to be similar to recently published curves by Meade and Geller<sup>1</sup> and by Keyes<sup>2</sup>. They showed the relation which has been found to hold using SLT technology between the number of connecting pins in a part of a computer such as a card, board, or chassis and the number of logic blocks contained in the part. The curve is reproduced as the solid line in Figure 14. Two observations were made.

The first observation is illustrated by the dotted line in Figure 14. The dotted line represents the ratio of surface volume of a sphere,  $S = \pi \frac{1}{3} \frac{62}{3} \frac{\sqrt{2}}{3}$ , when an interconnection is regarded as a unit of surface and a logic block as a unit of volume. These relations are almost identical. It is as though the logic blocks were closely packed into a sphere and connections made to those blocks that were on the surface. It appears that computer interconnections have an essentially three-dimensional character.

The second observation is based on the fact that the human eye contains about  $10^8$  photoreceptors. It is connected to the brain by an optic nerve which contains about  $10^6$  fibers. The point ( $10^6$  connections), ( $10^8$  logic blocks) falls on the extrapolated curve of Mead and Geller. It seems quite reasonable to regard a nerve fiber as a connection. The relation of a photoreceptor to a logic block is less clear. It may be, however, that the amount of data processing which takes place in the eye is about what a computer designer would have put there.

<sup>1</sup>R.M. Meade and H. Geller, "Solid State Design," 6, (7), 21 (July 1965).

<sup>2</sup>Robert W. Keyes, "On the Relation Between Number of Connecting Pins and Number of Logic Blocks," 28 July 1965.

Figure 14. Connections Versus Logic Blocks

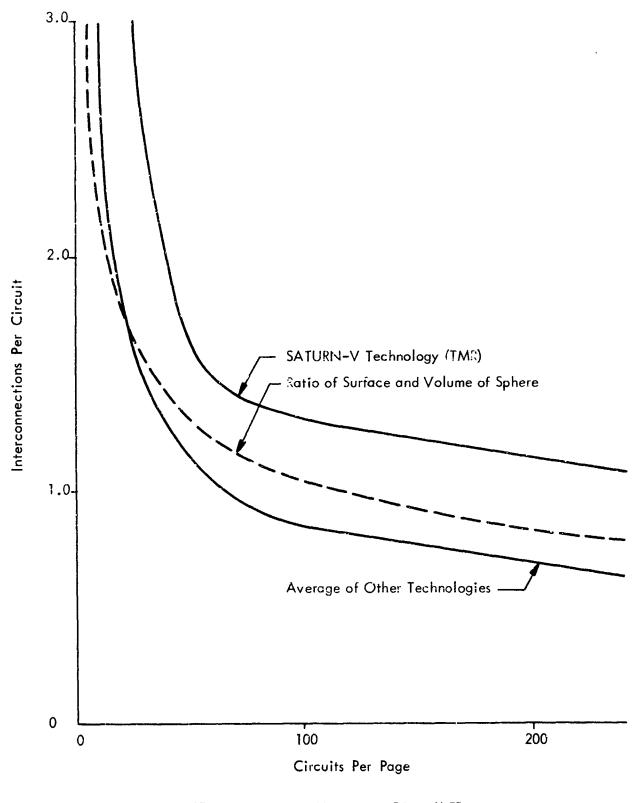

Taking this information and interfacing it with Figure 13 results in Figure 15. The dotted curve shows the ratio of surface to volume plotted on Figure 14, and it falls in between Saturn-V technology and the average of other technologies. It also shows that the ratio decreases rapidly as the package density increases up to about 50 circuits per module and then tends to level off.

The placement of voters in a TMR machine is an important consideration in machine organization. Maximum machine reliability is theoretically obtained with an organization in which the voting level is such that the reliability of the voter is equal to the reliability of the logic being voted upon. However, in practical aerospace machines, the fan-in and fan-out complexity makes voter placement according to this simple rule far from obvious, especially with restricted packing densities.

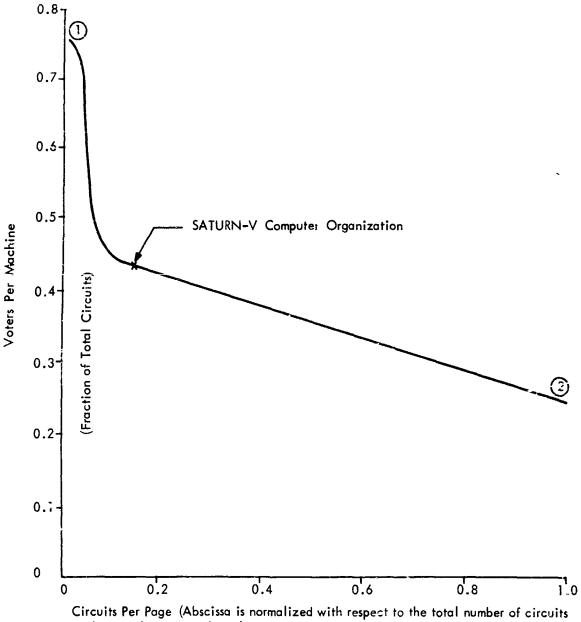

A normalized curve of voters per machine versus packing density is given in Figure 16. Although this curve was derived from Saturn data, it should apply generally to other advanced technologies. The curve was constructed according to the rule that voters would be placed on all intermodule signals.

The minimum packing density was taken as the inverter level, point 1 on Figure 16. That is, each inverter is packaged individually as a replaceable module, along with associated AND's and OR's, and the number of voters is equal to the number of inverters in the machine. The ordinate at this point is about 0.75, the ratio of inverter circuits to total circuits in the machine. As the size of the replaceable module is increased to include more inverters, the number of voters required decreases relatively slowly at first because most inverter outputs fan out to several other modules. As these small modules are absorbed into larger modules, the number of inverters feeding out of the module decreases rapidly, and the curve decreases accordingly. Then, in the density region of about 0.05 to 0.10 circuits per page (that is, each replaceable module contains from 5 to 10 percent of the total machine logic), the curve flattens out as the organization tends toward "isolated" functional modules. As the machine organization progresses from ten towards one module per machine, the curve linearly approaches point 2 where the number or voters required has reduced to the logic interface (memory and input-output).

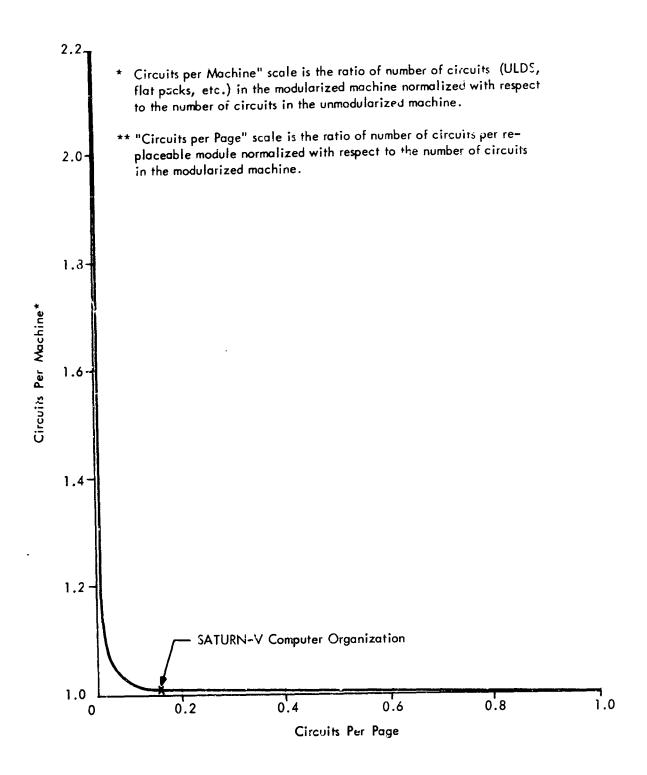

One of the costs of organizing a machine into individual replaceable modules is the increased circuitry required. This increase is due primarily to the additional drivers and decreased circuit-sharing imposed by the modular design. The effect is small except for organizations in which the machine is broken into ten or more modules, as shown in Figure 17.

Figure 17 is a normalized curve of circuits per machine versus circuits per page derived from Saturn-V computer design data. The conclusion from this curve, if it represents the general case and not just Saturn, is that the AES computer should be organized into ten or less modules.

۱

in the modularized machine.)

# F gure 16. Voters per Page Versus Circuits per Page

Figure 17. Circuits per Machine Versus Circuits per Page

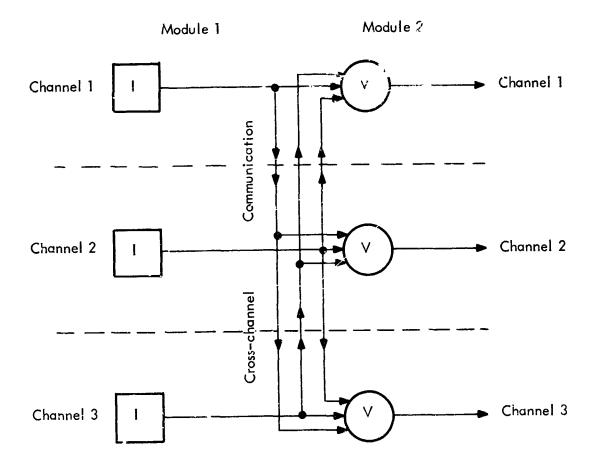

A TMR machine organization in which all three channels are routed through the same physical replaceat's modules has been found to result in the minimum interconnection requirements. This is shown in Figure 18, which represents output voters for module 1 of a TMR computer. If the individual channels of module 1 are packaged on separate physical pages, then the cross-channel communication is external to the page and two inputs and two outputs are required per channel, as shown, or a total of 12 interconnections are required in all. If, on the other hand, the three channels are routed through the same page, then the crosschannel communication signals are internal to the page and only one output is required per channel, or a total of three interconnections in all.

Figure 18. Channel Pac ging

The reduction in interconnections which can be realized on the computer level by packaging all three channels on the same physical page has been found to be as high as 25 percent over those required by packaging the channels individually. The feasibility of packaging partial trios (more than one but less than three channels per page) has been investigated and found to offer little advantage over either single-channel or triple-channel packaging.

A preliminary machine organization for the TMR computer assumed ten modules (about the knee of each of the curves of the figures) of about the same size. The resulting module size was about 40 circuits of logic, which increases to 60 as the required drivers and voters are added. Packaging all three channels on the same page results in a packaging density of 180 circuits per page and 160 inputoutput terminals.

Since the latter number is not compatible with a 98-pin connector, a higher capacity connector must be designed or a replaceable module design containing more than one connector per page must be derived. The first solution is feasible but will result in an appreciable increase per machine in the total number of circuits, voters, and interconnections. The second solution seems feasible at this time after discussing the problem with connector manufacturers. The use of lubricants also assists in fabricating connectors with 200 pins. The third solution is feasible, nevertheless, it does increase alignment problems.

Since the interconnection limitation imposed by the 98-pin capacity of the Saturn-V page connector appeared to be a very severe constraint on the machine reorganization configuration, a quick survey of the connection lubrication state-of-the-art was made to determine if lubrication techniques might allow higher capacity connectors to be used. The results of a continuing study at IBM of the characteristics of thin film lubricants to reduce contact wear were reviewed. Consideration was also given to the possible use of lubricants as protective coatings for contact surfaces in adverse environments.

A lubrication study by the U.S. Army Electronics Laboratories and Stanford Pesearch Institute resulted in the recommendation of octadecylair le-hydrochloride (ODA-HCL) for use with gold contact surfaces. Tests at IBM have verified the excellent properties of this lubricant. Octadecylamine-hydrochloride lubricant forms a very stable and tenacious film on gold surfaces. These properties are probably due to physical absorption of the lubricant by the gold surface, and perhaps also due to electrostatic attraction between the lubricant and the gold. The thin film does not affect the electrical resistance of the gold contact while decreasing its coefficient of friction up to 75 percent. The films are stable with time, contaminants, and hard vacuum. The film maintained its lubricating properties and its low electrical resistance characteristics after prolonged exposure of several weeks to atmospheres containing sulphur dioxide, hydrogen sulfide, and water vapor.

Since the test results on octadecylamine-hydrochloride were so consistently encouraging, it is recommended for AES connector lubrication applications, even if small capacity connectors are used. The decrease in insertion forces which it apparently affords, however, would seem to indicate that page connectors with capacities of at least 150 to 200 pins may well be feasible.

#### 2.0 MACHINE ORGANIZATION

The machine organization of the Saturn-V computer and the Apollo backup data adapter was examined to determine its applicability to the critical phases of the mission as well as its applicability to inflight maintenance during the noncritical phases of the mission. Considerable study effort was then expended on modifying those areas of the machine organization representing serious constraints on the mission capabilities of the computer and data adapter. The reorganized version of the computer system included major changes in the oscillator, memories, power supplier power, and timing distributions, and internal grounding. A TMR/simplex mode was developed which incorporates certain automatic switching features and provides appreciable increase in reliability over the basic TMR mode. A portion of the organization study was directed at reducing the susceptibility of the computer system to externally generated voltage transients.

#### 2.1 TMR Characteristics

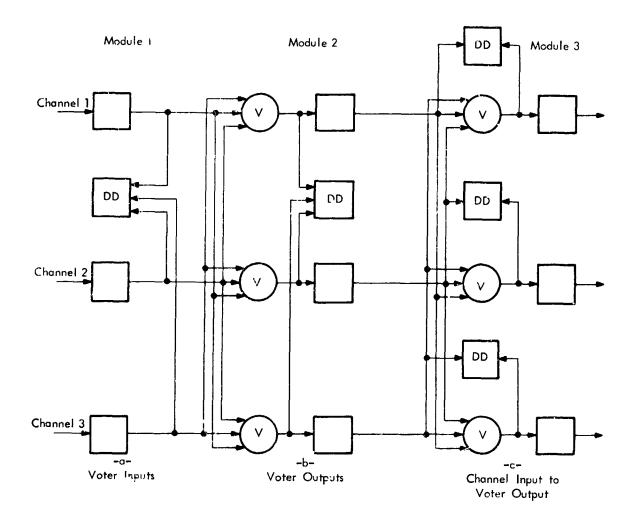

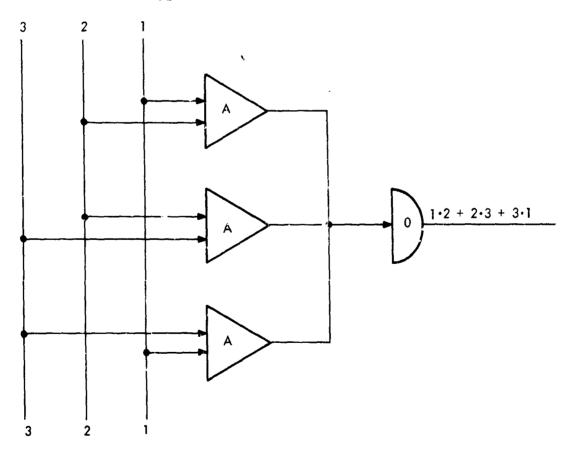

One of the primary objectives of this study was to determine the feasibility of a triple modular redundancy configuration as a solution to the short-term reliability problem in AES missions. TMR is a form of redundancy incorporating two-out-three voting as shown in Figure 19. Even if one module fails (dotted lines), the outputs of all three voters are correct. The TMR organization therefore possesses the unique characteristic that component failures can be tolerated and their disruptive effects on system performance masked automatically by voting without the need for error detection, diagnosis, and repair. This error masking occurs without interruption of the operational program, a characteristic found in few other forms of redundancy.

The reliability models for the TMR portions of the computer configurations examined during this study were based on the following analysis of the reliability states of a TMR module. A TMR module is defined as a section of the instrumentation isolated from other sections by voters. In the computer configurations of this study, this reliability module corresponds generally to the physical modules since most of the voters were used at the physical interfaces.

Figure 19. TMR Voting

#### 2.1.1 Reliability States

The primary reliability states of a TMR module are shown in Table 3. State 1 represents the condition of all channels operating. State 2 represents the condition of two channels operating and one failed. The coefficient 3 indicates that there are three ways the module can be in State 2: channel 1 or channel 2 or channel 3 failed. State 3 represents the condition of one channel operating and two failed, and State 4 represents the condition of all three channels failed.

States 1 and 2 are operating states and state 4 is a failed state. State 3, however, can be operating or failed depending on whether the failures in the two failed channels are in the opposite or in the same logic direction, respectively. If one channel is failed to a logic "zero" and the second channel failed to a logic "one", for example, the third channel dominates the voting and the system will continue to operate correctly.

| Sta' י | Operating                   | Failed                   |

|--------|-----------------------------|--------------------------|

| 1      | R <sub>c</sub> <sup>3</sup> |                          |

| 2      | $3 R_c^2 (1 R_c)$           |                          |

| 3      | 3 P(o) $R_c (1 - R_c)^2$    | $3 P(s) R_c (1 - R_c)^2$ |

| 4      |                             | $(1 - R_c)^3$            |

### TABLE 3 - Reliability States for TMR Modules

State 1 - All modules operating

- 2 One module failed

- 3 Two modules failed

- 4 Three modules failed

- P(o) Probability that the two failures are in the opposite logic direction

- P(s) Probability that the two failures are in the same logic direction

- $R_c$  Reliability of one channel of the TMR module.

#### 2.1.2 Basic TMR Reliability

The basic reliability of a TMR module is derived by adding the probabilities of the operating states. From Table 3, the reliability of the TMR module is:

$$R_{TM} = R_c^3 + 3 R_c^2 (1 - R_c) + 3 P(0) R_c (1 - R_c)^2$$

where  $R_c$  is the reliability of one channel of the module and P(o) is the conditional probability that, if two failures occur, they occur in opposite logic directions and their votes therefore cancel.

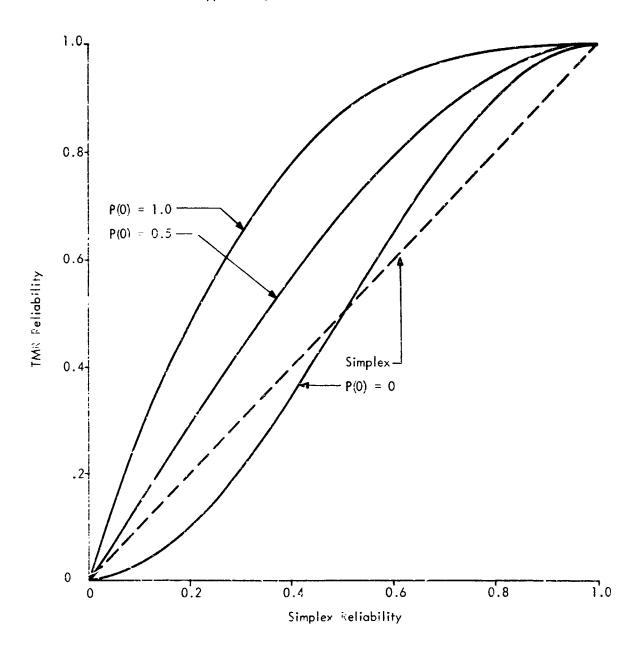

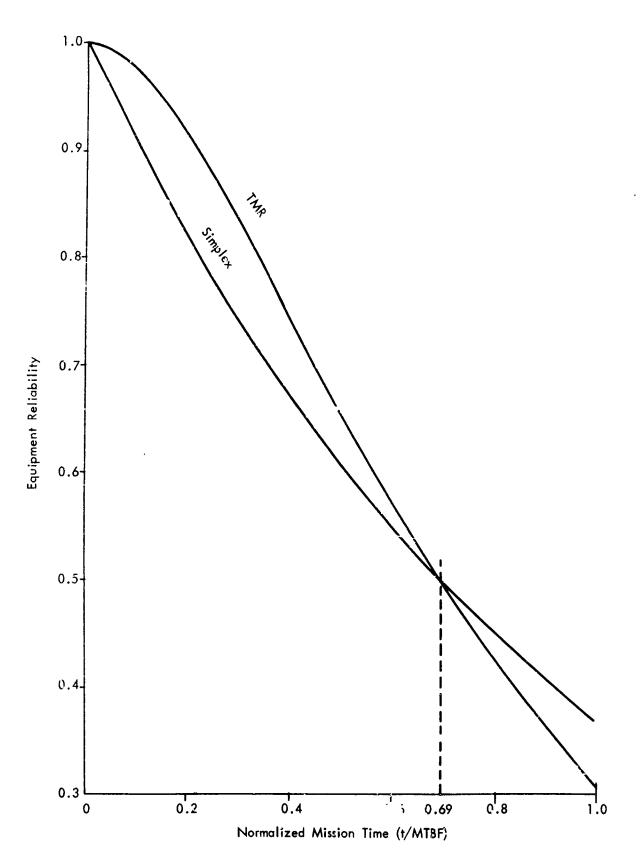

Module reliability is plotted against channel (or simplex) reliability in Figure 20 for three values of P(o). Note that TMR redundancy actually provides less reliability than simplex if the reliability

$$Rtm = Rc^{3} + 3 Rc^{2} (1 - Rc) + 3 P(0) Rc (1 - Rc)^{2}$$

Rtm = TMR Module Reliability

Rc = Simplex (Channel) Mcdule Reliability

P(0) = Probability that two failures will occur in opposite logical directions

Figure 20. TMR Versus Simplex Reliability

•

of the simplex channel is less than 0.5 and if it is assumed that all related logic failures occur in the same logical direction. This conservative assumption is usually made in estimating the reliability of actual TMR systems such as the Saturn-V computer and data adapter. The assumption of equal probability of failure to "one" or "zero" states would be applicable to a system constructed of symmetrical double-line-transfer logic, but such systems rarely exist in practice since circuit minimization requirements normally dictate an appreciable amount of unsymmetrical single-line-transfer logic.

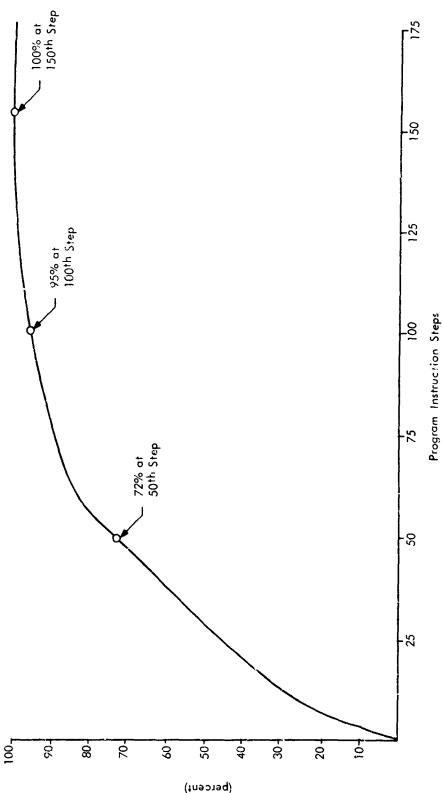

# 2.1.3 Intermittent Masking

In the case of intermittent failures in a TMR module, the effects of the failure are voted out as in the case of solid failures, but when the period of the intermittent ends, the module automatically recovers its original reliability state. This automatic recovery is a unique characteristic of TMR system organizations and a few isolated subsystem units such as the duplex Saturn-V memories. Flight failures on present and past programs tend to be mostly intermittent in nature, probably because of the much higher screening efficiency of present checkout methods for solid faults than for intermittents resulting in most of the solid faults being corrected before flight. In fact, as the level of testing progresses from preassembly screening of modules to preflight checkout of computer systems, the ratio of intermittent to solid failures found during test apparently increases monotonically with time and usage.

Data relating to failures detected in past computers from acceptance testing through end-use indicate that over 30 percent of the expected AES computer failures would be masked and would not degrade reliability. Although some rough calculations of the increase in reliability estimates due to consideration of the failure mechanisms of intermittents in TMR organizations were made in the preproposal study, this item was not pursued further during the study. All failures were assumed solid, and the reliability estimates are therefore conservative.

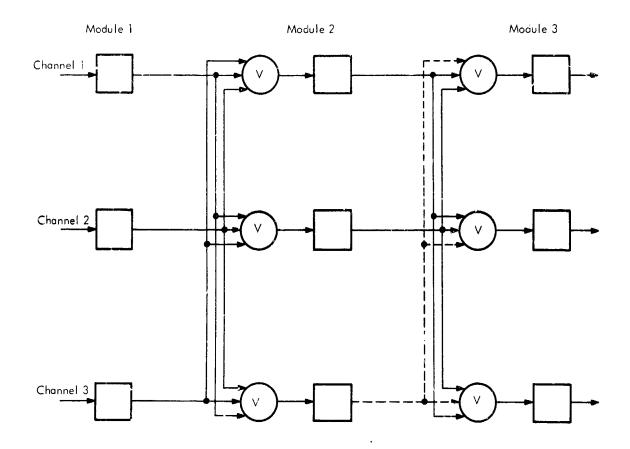

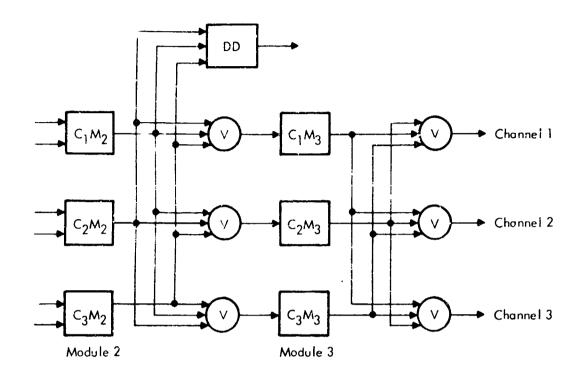

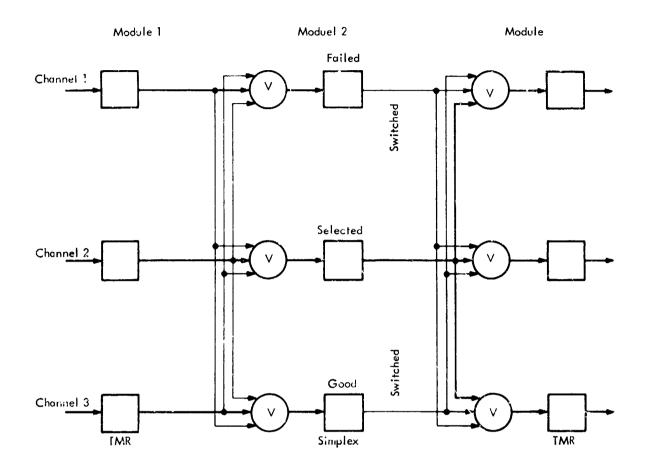

### 2.1.4 Channel/Module Switching

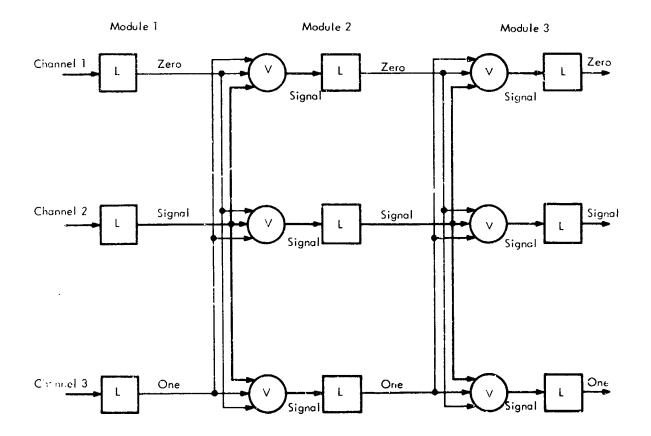

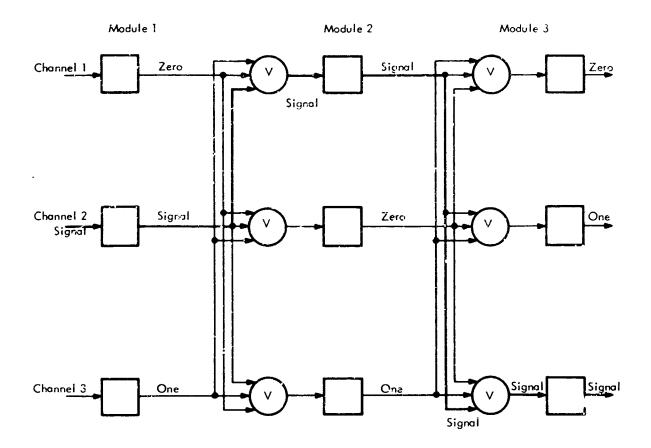

Channel and module switching capabilities are provided in the Saturn-V computer and force the computer to operate in a simplex mode. Channel switching forces the computer to operate on any one of the three simplex channels while module switching allows mixed channel operation. In either case, the operating channel is selected by setting one voter input to a logical zero and a second voter input to a logical one so that their "votes" cancel and the third input determines the voter output. Channel switching is shown in Figure 21 and module switching is shown in Figure 22. The heavy lines indicate the selected data paths in both figures.

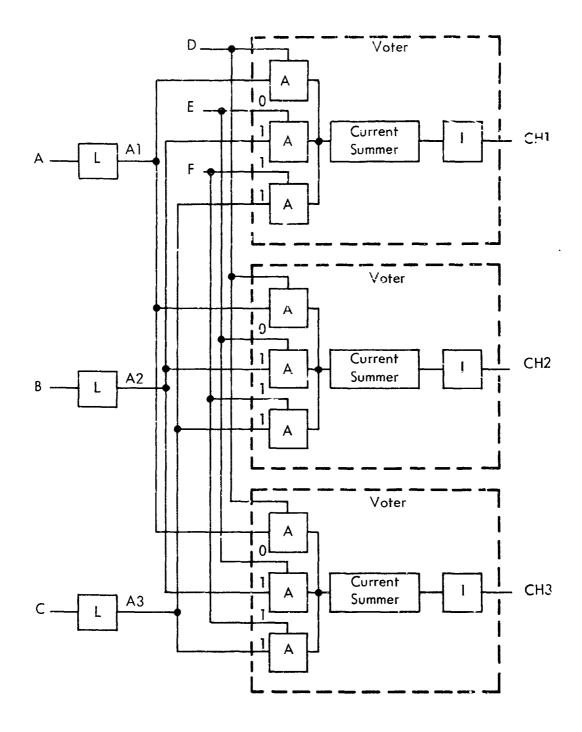

The Saturn-V voter is shown logically in Figure 23. Normally inputs A1, A2, and A3 and outputs CH1, CH2, and CH3 are all alike (all zeros or all ones). Points A, B, and C (inputs to the logic elements driving the voter) are connected to +6 volts, and points D, E, and F are connected to +12 volts. To select channel 1 (CH1), inputs A2 and A3 must be set to a logical one, input E to a zero, and input F to a one. Inputs E and F could be reversed. Outputs CH1, CH2, and CH3 now correspond to input A1 because the threshold of the current summers are set for two units of current; A3 supplies one unit, A2 supplies none, and the state of A1 therefore determines whether the current threshold of the voter is rc\_ched or not.

Figure 21. Channel Switching

Figure 22. Module Switching

# 2.2 Trade-off Criteria

Any system optimization effort will involve trade-offs among mutually conflicting parameters or criteria. The machine organization trade-offs of this study involved considerations of reliability, error detection and fault isolation, module replaceability and sparing, machine size and complexity, and susceptibility to transients. The last criteria dictated reinstrumentation of simplex and duplex components of the Saturn-V computer and Apollo backup data adapter to TMR (with special consideration for memory protection) and did not conflict with the trade-off criteria.

Figure 23. Saturn-V Voter

Reliability, maintenance, and size criteria were mutually conflicting. Reliability maximization dictated that the computer system be partitioned into small modules at a logic level where the reliability of the circuits being voted is equal to the reliability of the voter. The requirement for automatic failure isolation, however, dictated that the computer system be partitioned into functional modules (such as arithmetic or timing). The minimization of circuits and interconnections could be achieved only with a completely unmodularized computer system.

After some consideration of these conflicting requirements, it was decided to ignore reliability as a trade-off criteria until partitioning of the machine was completed on the basis of maintainability and size trade-offs, and then to test the reconfigured machine to determine whether the reliability requirements of the AES-EPO mission could be satisfied with that configuration. In addition, preliminary examination of the relationship between machine size (number of components or circuits) and modularization level showed that relatively little increase in size occurred as the machine was partitioned into larger numbers of modules up to about ten, beyond which the size increased very rapidly. The optimization studies of machine partitioning therefore were based on maintainability criteria alone (since these criteria dictated less than ten modules).

Error detection and fault isolation dictated a functional partitioning of the computer system which also satisfied the module replaceability and sparing requirements.

## 2.3 Basic Subsystem Configuration

The basic system upon which the study was based consisted of the TMR Saturn-V computer and a redundant version of the Apollo backup data adapter. This basic system was examined to determine to what extent it could meet the functional and availability requirements of the 90-day AES-EPO mission and where redesign was necessary. Special attention was given to the reliability and failure isolation capabilities of the basic computer and data adapter.

#### 2.3.1 Saturn V Computer Description

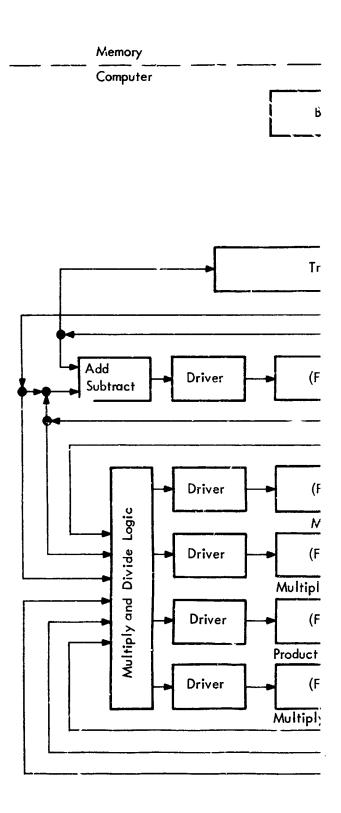

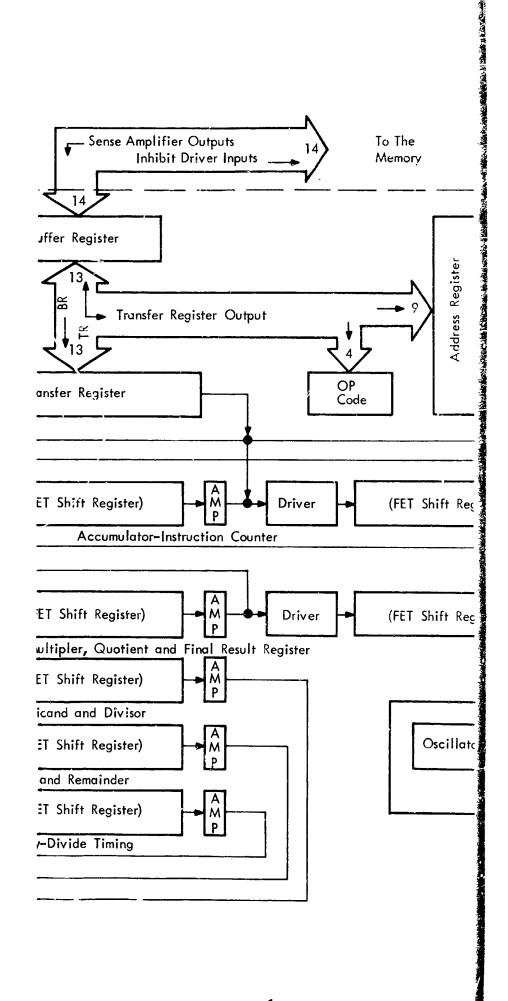

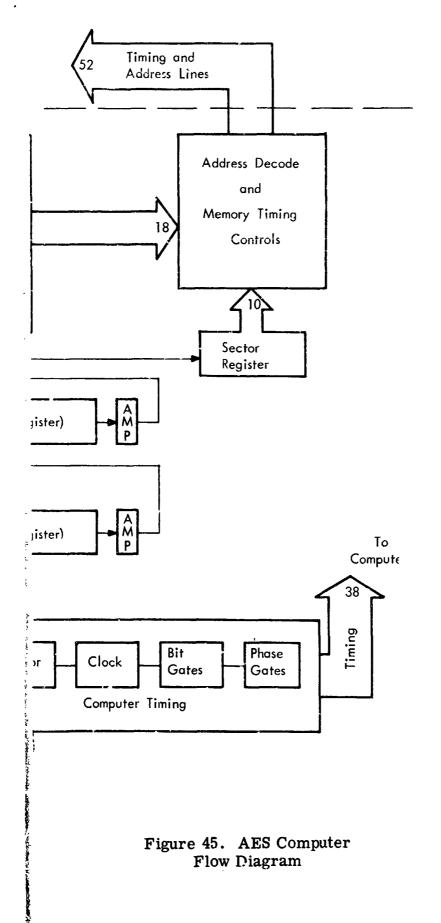

The computer information flow is illustrated in Figure 24. This simplified block diagram depicts the major data flow paths and associated register level logic. The timing logic and input/output (I/O) section are not shown.

.

44 0

Timing for Multiply and Divide

4 4 3

...

The computer is a serial, fixed-point, stored-program, generalpurpose machine which processes data using "two's complement" arithmetic. Two's complement arithmetic obviates the recomplementation cycle required when using "sign plus magnitude" arithmetic. Special algorithms have been developed and implemented for multiplication and division of two's complement numbers. Multiplication is done four bits at a time and division two bits at a time.

A random-access magnetic core memory is used as the computer storage unit. A serial data rate of 512 kilobits per second is maintained by operating the memory units in a "serial-by-byte, parallel-by-bit" operating mode. This allows the memory to work with a serial arithmetic unit. The parallel read-write word length of 14 bits includes one parity bit to allow checking of the memory operations.

Storage external to the memory is located predominantly in the shift register area. High reliability in this area is achieved by using glass delay lines for arithmetic registers and counters.

Each instruction is comprised of 4-bit operation code and a ninebit operand address. The 9-bit address allows 512 locations to be directly addressed. The total memory is divided into sectors of 256 words, and contains a residual memory of 256 words. The  $\vartheta$ -bit address specifies a location in either the previously selected sector (data sector latches) or in the residual memory. If the operand address bit (A9) is a binary "0", then the data will come from the sector specified by the sector register; if A9 is a "1" the data will come from residual memory.

Instructions are addressed from an 8-bit instruction counter augmented by a 4-bit instruction sector register. Sector memory selection is changed by special instructions which change the contents of the sector register. Sector size is large enough so that this is not a frequent operation.

Data words consist of 26 bits. Instruction words consist of 13 bits and are stored in memory two-instructions per data word. Hence instructions are described as being stored in syllable 1 or syllable 2 of a memory word. Two additional bits are used in the memory to provide parity checking for each of the two syllables. The computer is programmed by means of single-address instructions. Each instruction specifies an operation and an operand address. Instructions are addressed sequentially from the memory under control of the instruction counter. Each time the instruction counter is used, it is incremented by one to develop the address of the next instruction. After the instruction is read from memory and parity checked, the operation code is sent from the transfer register to the operation (OP) code register, a static register which stores the operation code for the duration of the execution cycle.

The operand address portion of the instruction is transferred in parallel (9 bits) from the transfer register (TR) to the memory address register. The TR is then cleared.

If the operation code requires reading the memory, the contents of the operand address are read 14 bits at a time (including parity) from the memory into the buffer register where a parity check is made. Data bits are then sent in parallel to the 'TR. This information is then serially transferred to the arithmetic section of the computer. If the operation code is a store (STO), the contents of the accumulator are transferred serially into the TR and stored in two 14-bit bytes. A parity bit is generated for each byte.

Upon completion of the arithmetic operation, the contents of the instruction counter are transferred serially into the TR. This information is then transferred in parallel (just as the operand address had previously been transferred) into the memory address register. The TR is then cleared and the next instruction is read, thus completing one computer cycle.

The data word is read from the memory address specified by the memory address register and from the sector specified by the sector register. Data from the memory go directly to the arithmetic section of the computer where it is operated on as directed by the OP code.

The arithmetic section contains an add-subtract element, a multiply-divide element, and storage registers for the operands. Registers are required for the accumulator, product, quotient, multiplicand, multiplier, positive remainder, and negative remainder. The add-subtract and the multiply-divide elements operate independently of each other. Therefore, they can be programmed to operate concurrently if desired; i.e., the add-subtract element can do several short operations while the multiply-divide element is in operation. No dividend register is shown in Figure 24 because it is considered to be the first remainder. The divisor is read from the accumulator during the first cycle time and can be regenerated from the two remainders on subsequent cycles. As indicated, both multiply and divide require more time for execution than the rest of the computer operations. A special counter is used to keep track of the multiplydivide progress and stop the operation when completed. The productquotient (PQ) register has been assigned an address and is addressable from the operand address of any instruction. The answer will remain in the PQ register until another multiply-divide is initiated.

A limited program interrupt feature is provided to aid the I/O processing. An external signal can interrupt the computer program and cause a transfer to a subprogram. Interrupt occurs when the instruction in progress is completed. The interrupt forces a HOP constant to be retrieved from the reserved residual memory location (octal address 400). The constant designates the start of the subprogram. The instruction counter, sector and module registers, and syllable latch can be stored in a reserved residual memory location by programming a STO 776 on 120 777 as the first instruction in the subprogram. Automatic storage of the accumulator and product-quotient registers is not provide 1; this must be accomplished by the subprogram. Protection against multiple interrupts and interrupts during MPY, DIV, HOP, and EXM operations is provided.

The interrupt signal may be generated by a timed source. The rate at which it is generated is controlled by changing the inagnitude of a number which is being continually summed. When the summed number reaches a predetermined value, the interrupt signal is generated. This is accomplished in the data adapter.

The main program can be resumed by addressing the contents of residual memory word 776 or 777 with a HOP instruction, after restoring the accumulator and PQ register to their pre-interrupt values.

Certain discrete input signals are allowed to cause interrupt. These are useful in causing the I/O subprogram to give immediate attention to an input or output operation.

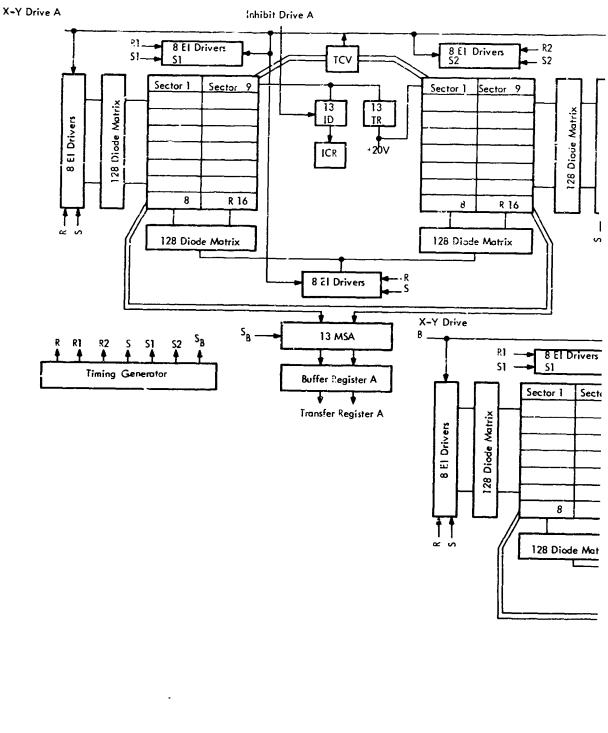

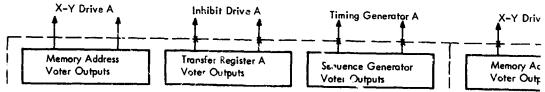

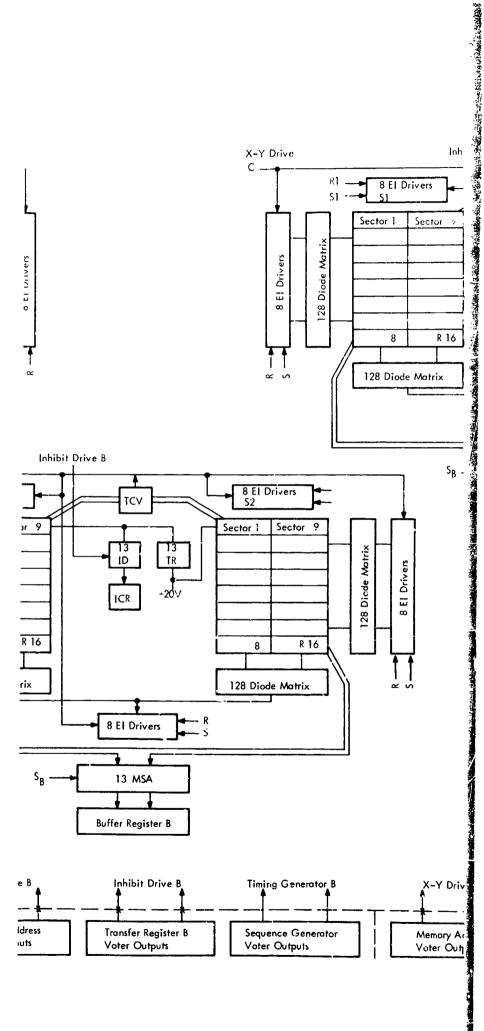

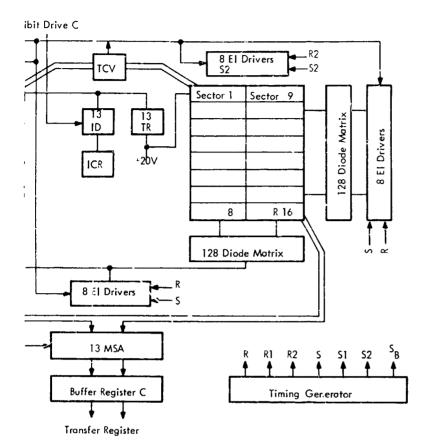

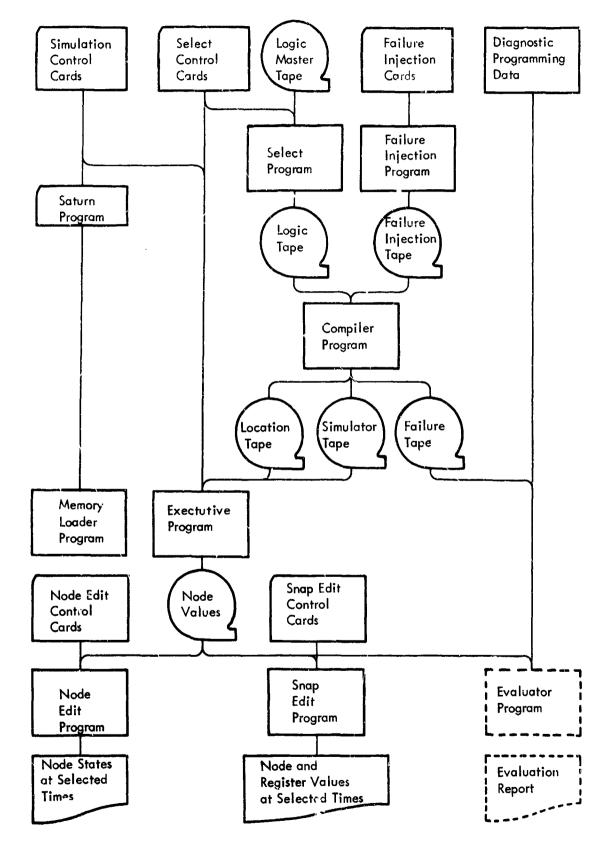

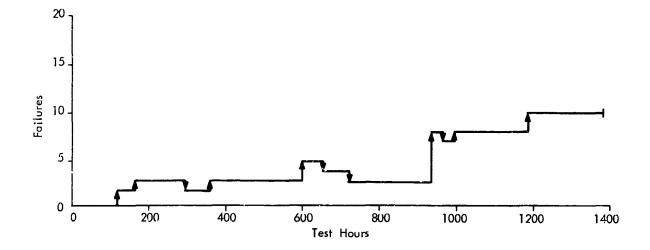

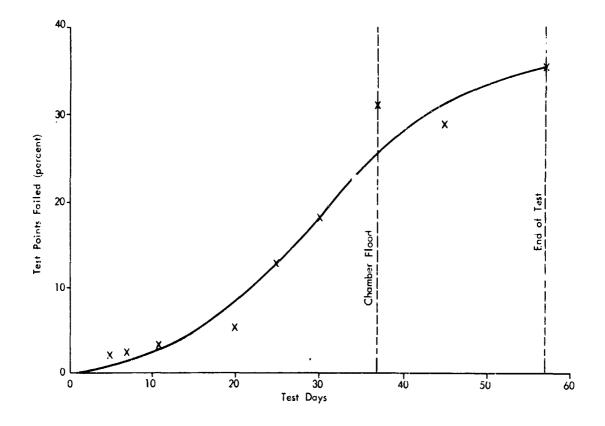

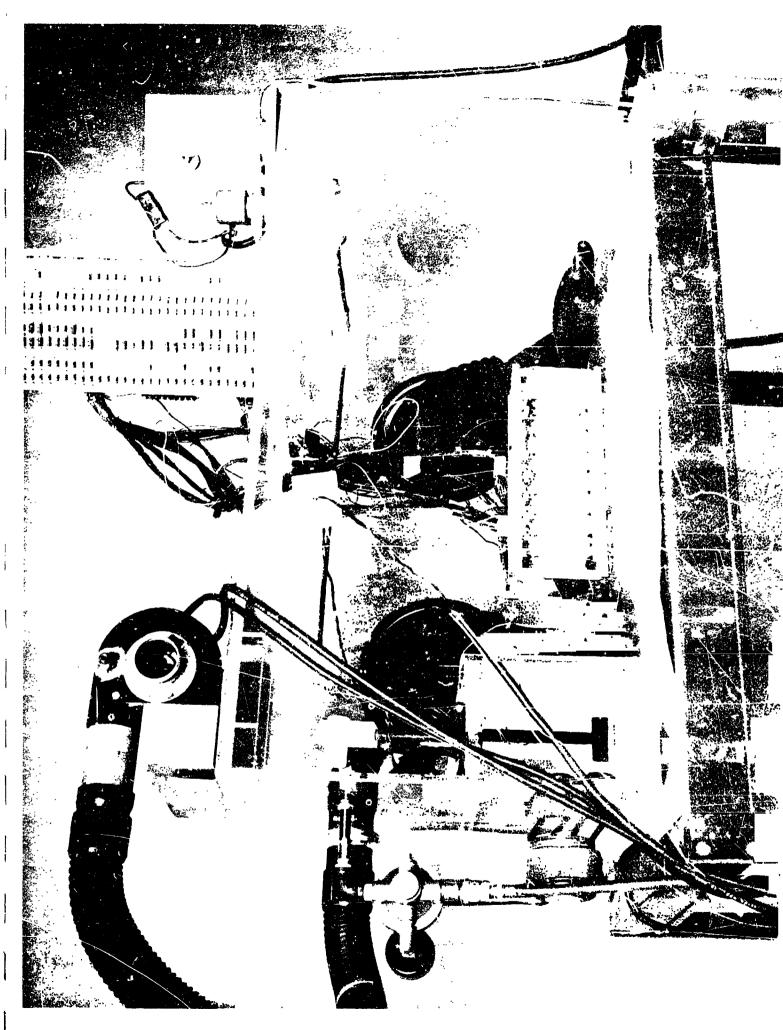

The memory for the Saturn-V Guidance Computer uses conventional toroidal cores in a unique self-correcting duplex system. The memory unit consists of up to eight identical 4096-word memory modules which may be operated in simplex for increased storage capability or in duplex pairs for high reliability. The basic computer program can be loaded into the instruction and constants sectors of the memory at electronic speeds on the ground or just prior to launch. Thereafter, the information content of constants and data can be electrically altered but only under control of the computer program.