LOCKHEED MISSILES & SPACE COMPANY HUNTSVILLE RESEARCH & ENGINEERING CENTER HUNTSVILLE RESEARCH PARK 4800 BRADFORD DRIVE, HUNTSVILLE, ALABAMA

FINAL REPORT

DESIGN GUIDELINES FOR CIRCUITRY IN A NUCLEAR REACTOR-PROPELLED SPACECRAFT

Contract NAS8-11755

by John L. Westrom

APPROVED BY:

S. Paulnock, Manager Systems Engineering

J. S. Farrior Resident Manager APPROVED BY:

1 July 1966

#### FOREWORD

This document is the final report for Guidelines and Design Efforts for Radiation Resistant Circuitry performed for the Astrionics Laboratory of Marshall Space Flight Center, National Aeronautics and Space Administration by the Huntsville Research & Engineering Center of the Lockheed Missiles & Space Company.

The work was performed under Contract NAS8-11755. Technical aid and direction for the Guidelines were provided by Mr. William T. White, Special Projects, Astrionics Laboratory, R-ASTR-BP, MSFC.

Technical aid and direction for the design efforts were provided by Messrs. John M. Caudle and John H. Owens, Jr., of R-ASTR-NFE, Astrionics Laboratory, Marshall Space Flight Center.

# TABLE OF CONTENTS

|     | FOREWORD                                                                           | ii  |

|-----|------------------------------------------------------------------------------------|-----|

| 1.0 | INTRODUCTION & SUMMARY                                                             | 1   |

| 2.0 | PHASE I: RADIATION GUIDELINES MANUAL                                               | 8   |

| 3.0 | PHASE I: CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE<br>EFFORT IN RADIATION EFFECTS | 9   |

| 4.0 | PHASE II: DESIGN OF RADIATION TOLERANT POWER SUPPLIES                              | 23  |

| 5.0 | PHASE II: CONCLUSIONS AND RECOMMENDATIONS FOR RADIATION .                          | 104 |

## 1.0 INTRODUCTION AND SUMMARY

The effort on this contract was divided into two major phases: that concerned with the generation of a circuit designer's guidelines manual for radiation resistant circuitry; and that concerned with the design and analysis of radiation resistant power supplies.

The guidelines manual effort involved a literature search on the theory and measurement of radiation effects; the compilation of data of radiation effects on components; the testing of components for which insufficient data were available; the design, fabrication and irradiation of a 200 watt power supply and a voltage regulator as typical of the type of circuitry most adversely affected by radiation, and the generation of the manual "Design Guidelines for Circuitry in a Nuclear Reactor-Fropelled Spacecraft." Because of the size of the manual and the fact that it has already been completed and delivered, it is not included with this report. Mr. William T. White, Special Projects, Astrionics Laboratory, R-ASTR-BP, MSFC, is in charge of the manual and its distribution.

The second phase involved the design and breadboarding of power supplies using the techniques indicated in the manual to minimize the susceptibility to radiation. A novel 400 Hz inverter was built after the initial design proved to be theoretically possible but required transistors with a combination of properties not yet available. A dc to dc converter was also designed. A detailed analysis of switching regulation was made to assist the circuit designer to optimize circuit performance and minimize radiation effects.

## 1.1 Literature Search

A literature search was initiated to obtain as much information as possible on the effects of the radiation environment on electronic circuitry. To this end letters were sent to selected system manufacturers requesting any non-classified information which could be compiled by IMSC/HREC and included in the Radiation Guidelines Manual. Although circuit information was particularly emphasized, the majority of information which was received contained only component level studies. Some microwave and TIMM circuitry information was received, but this information generally attempted to cover facility capability rather than useful data.

Most of the technical articles uncovered by this literature search which offered circuit design techniques for radiation hardening invariably confined their discussion to compensating the degradation effects of the nuclear environment on semiconductors.

## 1.2 Testing of "Building Blocks" and Circuits

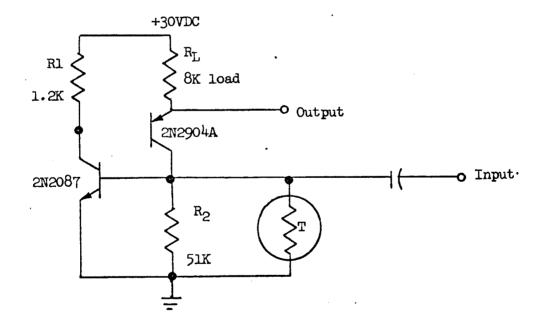

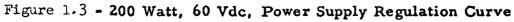

Several circuits and "building blocks" were breadboarded by HREC and irradiated at the Georgia Nuclear Laboratory Facility in Dawsonville, Georgia. The testing and their results are described in the Guidelines except for two circuits which failed during the radiation testing. One of these circuits involved using a two-transistor equivalency for the silicon controlled switch (see Figure 1.1). The mechanization had been successfully tried as an equivalency for the unijunction transistor, but unfortunately a compensating diode which tracked the base-to-emitter voltage variations in the device was not put into the breadboard tested at Dawsonville. The results were an abrupt failure as this sensitive voltage increased. The other circuit will be discussed under a separate heading entitled: "200 Watt Power Supply."

Figure 1.1

# 1.3 SNAPSHOT Program Conference in Sunnyvale, California

One member of the HREC/LMSC staff visited LMSC's Sunnyvale facility for the purpose of obtaining practical design guidelines from the design engineers working on the SNAPSHOT Program. This trip proved very fruitful in gaining a realistic insight into the radiation environment as viewed through the more experienced eyes of these program members. They were more cognizant of the limitations in measuring the actual radiation environment and had an excellent knowledge of the grey areas surrounding surface effects and actual permanent damage directly attributable to gamma radiation. A rough draft copy of the Guidelines Manual was reviewed by their staff and their helpful comments and criticisms increased the readability and factual content of the manual.

# 1.4 The Radiation Guidelines Manual

The guidelines manual consists of three sections. The first section consists of general background information in atomic and nuclear physics necessary for interpreting the results and guidelines set forth in the remainder of the text. The second section is divided into two parts. One is the careful inclusion of state-of-the-art limitations in the semiconductor family caused by the radiation environment. The reader is then invited to examine in detail some of the reasons behind the limitations and methods by which they can be circumvented. The second part of this section discusses other materials and electronic components which would be subjected to the same environment. As would be anticipated, the inescapable conclusion is that the semiconductor is the weak link in any electrical circuit subject to nuclear radiation.

The final section consists of a compendium of design guidelines and detailed derivations and formulae which are useful for designing radiationtolerant equipment. Also included are circuits tested and qualified for the environment including actual performance curves. An appendix is included which covers the derivation of some design equations and a glossary of useful radiation terms.

## 1.5 The 200 Watt Power Supply

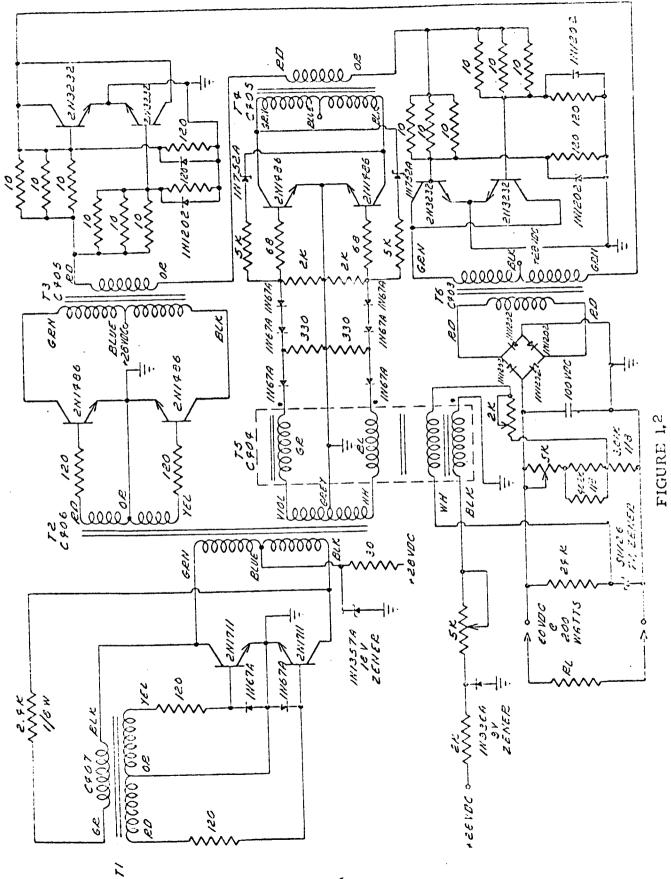

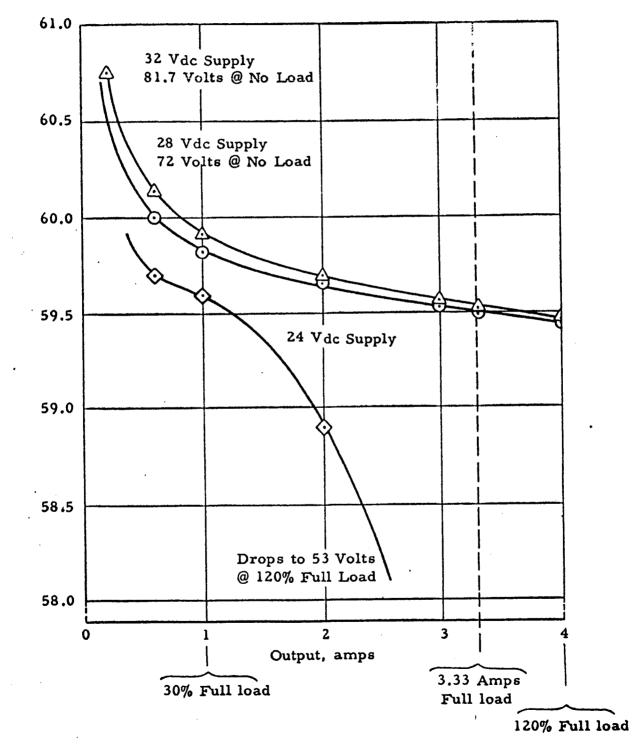

A 200 watt power supply was built for irradiation utilizing a switching/summing waveform technique (see Figure 1.2). The breadboard version was first tested at HREC/LMSC and the results indicated that satisfactory performance might be achieved if the power transistors used could continue to provide a useful gain. However, upon receipt at GNL in Dawsonville, the circuit failed to meet specifications initially, and also failed catastrophically early in the test program. Since HREC was not informed of the faulty circuit until after the testing, no attempt was made to remedy the circuit or improve the performance. This perhaps points up the need to have the design engineer available at the test site to help avert this lack of communication. Performance data for the 200 watt Vdc power supply is as follows:

| Chopper Frequency | 1.6 kc                                              |

|-------------------|-----------------------------------------------------|

| Regulation*       | + 0.5% at 20% to 120%<br>full load (see Figure 1.3) |

| Efficiency        | 83.5% at 20% full load<br>90% at full load          |

| Ripple            | 2.0% full voltage                                   |

\*No regulation under low supply voltage (24 Vdc); see text.

Figure 1.3 represents the regulation of the 200 watt power supply as given by a developmental breadboard utilizing two 2N3232 transistors in parallel rather than the 2N2125 transistors originally called out in the circuit diagram. Figure 1.2 represents the 200 watt power supply.

The output voltage did not hold up under low supply voltage (24 Vdc); however, this may be corrected by adding some turns to the secondary of the output transformer. Some rise in the output voltage under light load conditions will also occur, but this is not expected to interfere with good regulation in the 30% to 120% full load area.

# 1.6 <u>Regulator</u> Operation

The voltage applied to driver B is  $180^{\circ}$  out of phase with that applied to driver A. With no current in the bias or feedback windings, there is no delay of the applied signal through the mag-amp and therefore the output of driver B is  $180^{\circ}$  out of phase with respect to driver A. The resultant sum, which is applied to the power amplifier, is zero. As bias current is applied, the magamp comes out of saturation, with the resulting conditions causing the applied wave to be delayed before triggering driver B's transistors. The outputs of A & B now start to come into phase with each other, resulting in a signal to be applied to the power amplifier. At 1.6 kc, a full cycle is  $625\mu$ s long. Therefore, when enough current is applied to the bias winding, the mag-amp can delay the applied signal  $312.5\mu$ s (equal to  $180^{\circ}$ ) resulting in full matching of drivers A & B, and full output power.

The feedback winding and sensor are arranged to force the mag-amp back into saturation and thus reduce the output power. The common base amplifier in the sensor plus the choice of operating point and load resistor (2K) provide enough gain to establish a 0.5% regulation between 20% and 120% full load.

The mag-amp is capable of delaying the applied signal longer than  $312.5\,\mu$ s. When this happens, the power supply becomes unstable. In some cases using the sensor shown in the Sixth Monthly Progress Report, the output voltage stabilized around 30 Vdc. This condition occurred most often under heavy load

starting tests. To correct this instability, the diode-capacitor gates to the bases of driver B's transistors were added. These ensure that the output of B will never be delayed beyond maximum (in phase) matching with driver A.

With the present circuit, the bias is adjusted to provide enough delay and resulting output power to supply 120% full load. The feedback winding then regulates the output voltage for lighter loads.

Output, Volts

### 2.0 GUIDELINES MANUAL

The "Design Guidelines for Circuitry in A Nuclear Reactor-Propelled Spacecraft" manual is the principal product of Phase I of this contract. It is intended to assist circuit designers to understand the nature of nuclear radiation, its effects on components and circuitry and the ways in which these effects can be avoided or minimized.

The manual has been delivered previously and is under the control of Mr. William T. White of the Astrionics Laboratory, MSFC.

### 3.0 PHASE I: CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE EFFORT IN RADIATION EFFECTS

The level of design quality for space applications has increased steadily. As a means of reducing cost, there is an increasing demand for off-the-shelf hardware as functional building blocks. State-of-the-art improvements which continuously evolve are incorporated into programs only when they can demonstrate a significant improvement with their use. However, future planning must reflect adaptability to the anticipated improvements which will appreciably alter the scope of many present programs.

It is becoming apparent in the rapidly evolving semiconductor field that those products which are now used in off-the-shelf hardware must be compatible with anticipated improvements in future space programs. The alternatives range from complete redesign of the sub-system in question to simple replacement of undesirable devices with compatible higher performance substitutes.

Many future space programs, as well as present ones, plan to subject electronic circuitry to a new environment which severely degrades semiconductor performance...the nuclear radiation environment. Much has been written on circuit design for survival in this environment, but unfortunately, there are too many disjointed, parallel efforts attempting to qualify and demonstrate component and circuit effects in many different nuclear radiation environments.

If an equivalency can be demonstrated and statistically correlated to show that the radiation tolerance of semiconductors depends upon device geometry and manufacturing processes, then the first step in unifying the multitude of test programs, either planned or in progress, would be accomplished. Further, if this equivalency can be used to predict device performance in one radiation environment by subjecting the device to another radiation environment, less expensive and readily available, then it becomes feasible to specify and design all systems to be "radiation-rated". This major increase in mission flexibility can be obtained at an insignificant increase in time and money costs.

The semiconductor device is the most seriously affected component of the electronic circuit performing in the nuclear radiation environment (see Reference 2). The very properties of the semiconductor which achieve its desired electrical response are, unfortunately, the most volatile when subjected to any external energy source. Since heat, light, and electrical fields bias and restrict semiconductor performance, it is not surprising that radiation fields having a high energy content can cause "unpredictable" and "unnatural" property changes in the device.

## 3.1 The Damaging Effects of Radiation on Semiconductors

Only two major effects actually impart significant performance changes to semiconductor circuits in the radiation environment. These are <u>ionizing effect</u> induced by the electrical charge content of the radiation flux, and the <u>displacement effect</u> damage produced by the "brute force" high energy impact of the radiation particle with the target material's lattice structure. The ionizing effect will cause build up, storage, or transfer of electrical charge in a semiconductor device which can be minimized by careful circuit design or removed once the energy source has been removed. In this event, the circuit can again perform at desired specifications. The displacement effect, on the other hand, causes an irreversible change in the physical properties of the materials, which will usually cause serious degradation of transistor action, increased leakage across reversed-biased junctions, and decreased conductivity in each doped substrate (see Reference 2).

#### 3.2 Selecting Radiation-Tolerant Semiconductors

The selection of a semiconductor device for optimum performance in the radiation environment first involves careful selection of the device geometry and power requirements necessary to satisfy the system's performance requirements without compromising the necessary device capabilities. Quite often, the applications engineer will require high power, as well as low power, high frequency operation as well as audio and dc operation, and high voltage as well as low voltage capability in a system. He will quite naturally specify semiconductor devices which are rated by the manufacturer for these appli-He considers doing otherwise to be inefficient and an annoying cations. inconvenience. On the contrary, it is important to make the applications engineer realize how different is the semiconductor's performance in a radiation environment. Thus, when transistor selection is required, any manufacturing technique which reduces the active geometry or increases the impurity doping concentration or optimizes the base-to-emitter perimeter ratio is worthy of consideration, even if it is less efficient from a purely circuit point of view (see References 3 and 6).

#### 3.3 Limitations of Commercially Available Semiconductors

Unfortunately, the manufacturing processes spelled out by these requirements do not reliably restrict system failure due to semiconductor degradation. The fact remains that the semiconductor registration system currently employed completely ignores radiation tolerances. Therefore, transistor parameter design can be accomplished by various manufacturers under widely differing processes all meeting the registered design centers and tolerances. Radiation-induced damage thresholds on the other hand can be several orders of magnitude apart. To further complicate the picture each manufacturer states quite openly on every transistor specification sheet that he reserves the right to "improve" his product at any time without notice. Since his only restraints are the "registered" parameter design centers and their tolerance, he is free to meet these requirements with any process which suits fancy and up-date or change the process whenever economy or change in the state-of-the-art dictates. For example, he can change the chemical composition of the epoxy seal or use different annodizing or protective coating processes. He can use large junction connections of one base metal or smaller junctions of another. He may fill the case with inert gas or plain air, or sometimes, when conditions demand, he will evacuate it. Many of these "beneficial improvements" reduce the radiation tolerance of the devices.

It therefore becomes necessary for the user to examine and select his semiconductor device on a lot-by-lot basis. He can intelligently select a device class based upon manufacturing process, power requirements, and device geometry, but he must insure that the minor construction techniques do not produce harmful side effects under radiation. From past performance of semiconductor manufacturers, he can expect that uniformly frozen manufacturing processes will be the exception rather than the rule over a long period of time so that he must expect to have to requalify his semiconductor selection lot-to-lot (see Reference 2).

#### 3.4 The Selective Sampling Procedure

Numerous methods can be used to select a transistor from a given lot to insure that it can be reliably used for a given radiation environment. In the limit, every electrical parameter variation caused by incident high energy radiation flux can be used as a sensor for monitoring this induced damage. As the radiation flux is allowed to accumulate with time, the damage or degradation rate of the electrical parameters ( $h_{fe}$ , hie, Icbo, etc.) increases. As the total integrated flux exposure on the target area increases, this changing rate may tend to level off or not, depending upon the nature of the devices under test. However, one point is assured: that increasing the total integrated flux exposure always decreases the effective transistor action.

Methods of Selection: The various rates at which the individual transistors degrade, if sensed early enough, can be used as a selection technique for identifying the more tolerant devices. Variations in the most sensitive parameter of transistor action, current gain, would be the easiest to instrument and measure (see References 1 and 2).

There is also the possibility that the devices can be irradiated through their maximum anticipated radiation environment; the most tolerant devices selected and then under carefully controlled temperature annealed to a condition approaching their pre-irradiated state. It has yet to be demonstrated that significant post-irradiation correlation will occur with previously irradiated properties. NASA/MSFC attempted to show this correlation with a number of silicon power transistors (2N2125) without success (see Reference 7).

Some evidence exists that the leakage current of a transistor group sample can be monitored and the device, which has the highest leakage levels or which exhibits the greatest leakage change during radiation, can be rejected as a poor choice for radiation tolerance. However, because of the high impedances and extremely low-level leakage currents involved in silicon devices and the necessarily long test lines which couple the circuit in the radiation environment to the external test equipment, it is doubtful that consistently accurate data points can be recorded (Reference 1).

Since the diffusion process allows the doping density of the substrates involved to be large over the major portion of the active area, manufacturing processes involving diffusion and grading techniques should improve the transistor's tolerance to radiation. Planar and planar epitaxial processes usually employ diffusion techniques for forming at least the base and emitter and, in the latter case, all three junction greas. Since the masking, etching, and timing of the diffusion growth can be accurately controlled and reproduced, the electrical parameter variations between transistors (especially in the same lot) can be held much closer than the older techniques such as the alloy junction devices. Because of this close correlation of the physical size and geometry relationships in each transistor of the lot, more nearly uniform radiation damage from device-to-device can be anticipated as well. Thus, when a flux intensity is uniformly incident upon an entire target sample with the precise geometry and size set by the above manufacturing processes, the result should produce a reasonably uniform degradation of the entire lot (Reference 3).

Application Requirements in the Selection Process: The applications engineer must have in mind the desired response which the device will be asked to generate before he can specify and interpret a selection process. For example, a transistor for use in a high gain operational amplifier with feedback would be selected primarily for high gain. On the other hand, an openended amplifier would require a transistor whose gain variation was minimized over the radiation environment range. Thus, a transistor with a pre-irradiated  $h_{fe}$  of 100 and a post irradiation  $h_{fe}$  of 30 would be a better choice for the operational amplifier than one which has a pre-irradiated  $h_{fe}$  of 20 and a post-irradiated  $h_{fe}$  gain of 12. The latter, however, would be better suited for the open-ended amplifier (Reference 2).

When switching applications are desired, the designer must be aware of the current ranges being switched so that the optimum emitter-periphery ratio commensurate with device rating can be selected. For example, a transistor switching 0.2 to 1 ampere would probably be selected from a device capable of 5 amperes maximum collector current (Reference 2).

Program for Statistically Correlating Sample Sets: Before discussing the statistical program, the pertinent terms need defining and a typical selection program for a high frequency transistor class is used as an illustration of these terms:

> o <u>Samples</u>: The significant number of devices necessary to insure that an accurate population of devices' parameter changes can be correlated.

- o <u>Sample Set</u>: The samples in one class of device selected from one manufacturer's lot.

- o Class: A particular type of semiconductor with closely correlated physical size and uniform material composition per set.

To illustrate this procedure, assume that a 2N708 high frequency, switching-type transistor manufactured by planar techniques is selected as one class of device for testing. It is calculated that the sample number necessary to provide accurate population sampling to a 90% confidence limit is 30. Therefore, for each environmental test proposed, a manufacturer's lot will provide one sample set per test. Since four radiation environments are projected, each manufacturer must provide four sample sets or a total of 120 devices purchased from each manufacturer's lot. Thus, for example, Transitron, General Electric, and Fairchild may be selected to provide the 2N708 transistors for the testing, and each would provide four sample sets of thirty for a total class sampling number of 360 devices.

The testing program is defined explicitly in the following outline:

- o Three sample sets in each class will be exposed to three separate radiation environments. One sensitive electrical parameter will be monitored before, during, and after their radiation. The integrated exposure flux of each environment will exceed:

- 1. for neutron flux:  $10^{13} \text{ n/cm}^2$  (E  $\approx$  3.2 Mev)

- 2. for electron flux:  $10^{16} \text{ e/cm}^2$  (E = 1.5 Mev)

- 3. for gamma flux: until the class is destroyed

- o There will therefore be nine sample sets exposed to each independent radiation environment:

| Radiation Environment | Class I                                          | Class II                                         | Class III                                        |

|-----------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Neutron               | A <sub>1</sub> , B <sub>1</sub> , C <sub>1</sub> | D <sub>1</sub> , E <sub>1</sub> , F <sub>1</sub> | G <sub>1</sub> , H <sub>1</sub> , J <sub>1</sub> |

| Electron              | A <sub>2</sub> , B <sub>2</sub> , C <sub>2</sub> | D <sub>2</sub> , E <sub>2</sub> , F <sub>2</sub> | G <sub>2</sub> , H <sub>2</sub> , J <sub>2</sub> |

| Gamma                 | A3, B3, C3                                       | D <sub>3</sub> , E <sub>3</sub> , F <sub>3</sub> | G3, H3, J3                                       |

where letter designates specific manufacturer's lot and number subscript identifies one sample set.

- o Using the data from each sample set, curves of the electrical parameter degradation versus integrated radiation exposure flux will be plotted on a semi-log basis. Damage correlation between gamma, neutron and electron flux will be achieved by first fitting together the three curves corresponding to a manufactured lot. This will be accomplished by varying the logarithmic scales of two of the sample set curves. Then the equivalency should be verified by cross-checking the equivalencies determined from the other two fitted curves in the class.

- o The same procedure will be used to establish the equivalency factors for the other two classes.

### 3.5 The Case for Radiation Equivalency

There has been effort in the past attempting to correlate electronto-proton-to-neutron equivalency at various energy thresholds (usually 1 Mev or above). These studies have shown, for example, that one proton at 10 Mev will do as much damage as 4.2 neutrons from an unshielded reactor which does as much damage as 70 electrons at 10 Mev on a particular target material (References 4 and 5). This equivalency holds only for a particular type material (silicon solar cell) and cannot be expected to convert for other materials. However, it is entirely plausible that particular classes of semiconductors (high frequency, switching type transistor for example) can also be degraded by various radiation sources and a damage equivalency established. Of course, the semiconductor's primary permanent damage mechanization results from the displacement effect. This is directly attributable to high energy particle bombardment of the semiconductor substrate. It is the energy content of the particle which imparts the Frenkel Defect upon the lattice structure and alters the substrates physical and electrical properties.

Consider the following analogy. A child's wagon rolling down.a steep hill will have little effect upon a brick wall at the bottom. On the other hand, a diesel locomotive would only slow slightly upon impact with the same wall. The same disruptive result will occur to the wall if struck by a large truck, a cannon ball, or even a hurricane. Except for the wagon, all of these devices had one property in common; each device contained high energy. The wall's physical configuration was as surely changed by each high energy impact. Since the energy content of the radiation flux is the primary, permanently-damaging mechanism and ionization, secondary emission, and radioactive decay can be classified at best as second order effects, it is reasonable to assume that permanent damage to a semiconductor will result regardless of the carrier used. Thus the semiconductor itself can be used as the sensor to "estimate" the degree of damage imparted from any given radiation flux environment. Therefore, if a class of semiconductors is selected whose physical properties are very uniform through the samples (as should result for planar devices for example), they can be irradiated under different radiation fields to an equivalent electrical parameter degradation with the integrated flux exposures of each flux field recorded.

Then for this class of device an equivalent damage correspondence can readily be formulated empirically. Once established for this semiconductor class, then only one flux field need be utilized thereafter to qualify the devices for each type environment (proton-electron for example).

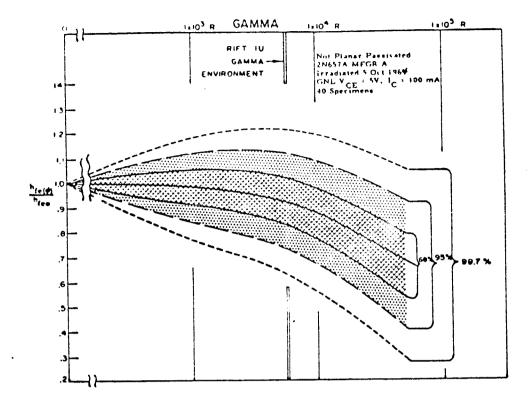

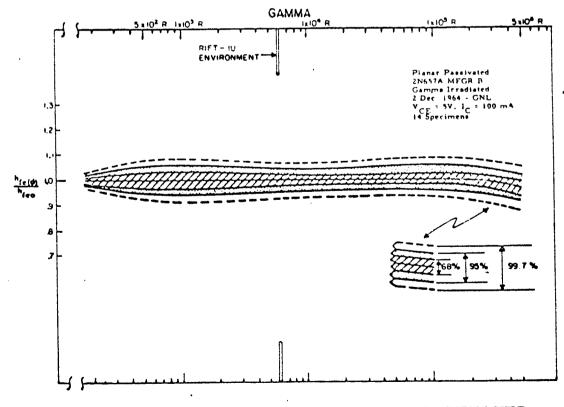

Evidence exists that the electrical parameters of silicon transistors are degraded considerably in high energy, pure gamma flux fields. Both LMSC in qualifying semiconductors for their SNAPSHOT Program and the Astrionics Laboratory of NASA/MSFC for a similar semiconductor qualifying program encountored this effect (References 1 and 7). Because of the definite economic advantage as well as the testing flexibility from the numerous gamma sources available, an equivalency correlation between gamma-radiation-induced semiconductor damage and electron, proton, and neutron-induced damage will be highly attractive (see Figures 3.1 and 3.2).

Once the equivalency is established, the low cost selection technique can provide semiconductor devices for most radiations where duration of exposure and high energy fields limit the choice of semiconductors to the screened, radiation-tolerant type. Thus, job lots of commercially available semiconductors can be qualified by the manufacturer for use in most missions, including long duration space probes, nuclear-propelled boosters, Van Allen Belt and other space located radiation belts, and perhaps nuclear detonations.

# 3.6 Establishing the Variance of Device Parameters for Transistors

Present day manufacturing processes offer excellent control stability over the basic device geometry and most of the doping impurity densities. The planar process, for example, offers precise masking and etching techniques with carefully-timed, gaseous diffusion building at least the base and emitter substrates. However, if the current gain of each device in a lot is measured, a relatively large spread is observed. With the geometry tolerances held as tightly as they are, the major contributing factor lies in the degree of doping provided each base substrate. The base thickness is orders-of-magnitude less than that of either the collector or emitter. Since the doping is controlled by timing the gaseous diffusion of impurity atoms, this timing requires much higher precision for forming the base region than for the emitter. Therefore, a small variation in this timing will strongly affect the base area doping concentration.

One of the basic rules in transistor physics states that the degree of transistor action is controlled by the relative differences in dopant density between the base and the emitter. Therefore, the first order reason for observing the current gain variation in a large sample is due to the relative fluctuations of the base dopant density.

Displacement-effect damage, if imposed upon the same class material, will tend to impart equal damage. However, based upon the above discussion the higher gain devices in a lot will have fewer impurity atoms present in their base region than their lower gain counter-parts. Therefore, there will be a tendency for these higher gain devices to "lose" relatively more impurity

Figure 3.1 - GAIN DEGRADATION OF A NON-PLANAR PASSIVATED 2N657A TRANSISTOR DUE TO GAMMA EXPOSURE

Figure 3.2 - GAIN DEGRADATION OF A PLANAR PASSIVATED 2N657A TRANSISTOR DUE TO GAMMA EXPOSURE

carriers per Frenkel Defect than the higher-doped base, lower gain devices which have a physically larger number of impurity carriers to lose.

The trend for damage change as a function of current gain was observed at the Lockheed Georgia Nuclear Laboratory where small samples of transistors were irradiated (Reference 8). It was noted that in choosing an arbitrary failure point of 50% gain degradation, many of the devices with high gain failed first, the lowest gain devices failing last. Of course, only a small number of devices (10 to 20) were tested and no significant analyses were attempted. However, many of the semiconductor testing results repeat this observation while at other times this correlation cannot be shown. It is anticipated that manufacturing defects, which can significantly alter the device electrical performance under radiation, will be observed as "unpredictable" and "unexpected" variations in a small number of lot samples which must be disqualified.

Fortunately, the manufacturer can provide a much tighter correlation of his devices at a small increase in cost. Since yields in his transistors tend to fall into selective distributions (i.e., 5000 devices in a lot of 12,000 may fall into a narrow gain strata between 55-65  $h_{fe}$ ), the manufacturer can easily select transistors lying in this high yield range. A sample distribution of these devices will inherently have a small variance and easily estimated mean. Thus, not only can this distribution be readily provided, but any statistical sampling method will necessitate fewer samples to provide equal confidence limits than a more random selection from the entire lot's sample distribution uniformly since not only are the geometry parameter tolerances small, but the doping concentrations in the base regions are similar as well. The damage or degradation changes versus total integrated flux of any high energy radiation can be correlated with confidence due to the controlled uniformity of the sampled detectors. The damage equivalency between different radiation fields can then be correlated for the particular semiconductor class.

After verifying the damage equivalency for a class at a particular current gain range, the manufacturer will be required to select a significant sample number from a lot in the low and high current gain ranges. To reduce the cost of testing, these devices will be irradiated and measured at the same time as the high yield range of devices. With this information a family of curves can be drawn so that expected current gain degradation as a function of integrated flux is shown with current gain as a parameter.

By qualifying several manufacturer's transistors of the same class and by substantiating that the equivalency can then be established for a class rather than for a particular manufacturer, this significant performance history can be used to continue qualifying and rejecting transistor lots and individual samples in the same class. Thus, the device may be qualified with only the relatively inexpensive gamma radiation.

## 3.7 Integrated Circuit Considerations

The integrated circuit (IC) is a relatively new device which is rapidly coming into widespread usage because of the great system flexibility it permits without compromising system reliability. As herein used, the term integrated circuit is understood to mean a monolithic, silicon, planar-epitaxial, digital circuit in either a flat-pak or TO-5 metal can. Analog integrated circuits have recently become available, but the number is still small and the availability so uncertain that it is questionable whether to include them at this time. However, the techniques described can be employed for integrated analog circuits if desired.

The first consideration is to limit the selection to the five major suppliers: Texas Instruments, Fairchild, Westinghouse, Motorola, and Siliconix, since only these companies are firmly committed to continued IC production, the others being still in the pilot-run stage and subject to abrupt withdrawal from the market. These five companies share 90% of the IC market and thus are more apt to have consistent production runs, extensive quality assurance programs, etc. Thus, the results of the recommended program are more likely to be applicable in the years immediately following.

The second consideration is the type of integrated circuit to be tested. It is recommended that a single-gate, DIL NAND/NOR be the circuit used for testing. This choice is predicated on several basic facts. A singlegate chip is somewhat less expensive and much less work to test, record, and analyze. Since multiple gates will consist of the same geometry as on the first gate, much less variation will be encountered than among the same number of gates on separate chips. Thus, a given amount of testing effort will produce more useful data if separate chips are used.

The diode transistor logic (DTL) is preferred over other types of logic for reasons of inherent tolerance of performance degradation and widespread availability. SUHL or Sylvania Universal High Level logic is a multipleemitter configuration available essentially only from Sylvania. This lack of widespread availability severely limits its usefulness in a selective sampling program.

Emitter-coupled logic (ECL) such as Motorola produces is very high speed but achieves this speed by means of a very small signal swing. To operate over a temperature range, a temperature-sensitive threshold voltage supply must be incorporated. Thus, very little additional variation can be tolerated by the system. It is to be anticipated that this will be the logic system most susceptible to radiation damage.

The resistor-transistor logic (RTL) as employed by Fairchild Micrologic (and a similar form produced by Siliconix) is in reality an analog summing of resistor currents to bias a transistor base above or below its cutoff voltage. The resistors are formed from doped areas of the substrate and are difficult to control accurately. This, plus the inherent analog nature of the system, limits the normal fan-out to three. Any appreciable radiation-induced degradation would render the system completely unusable.

Thus the field is for all practical purposes limited to the most widespread and reliable logic of all, diode transistor logic (DTL). In this form, the logic is performed by diodes with the transistors providing power gain and signal inversion. This type of logic uses large signal swings, a current steering type of circuit and transistor overdrive. It is characterized by large fanout and high noise rejection and thus inherently possesses a large performance degradation tolerance.

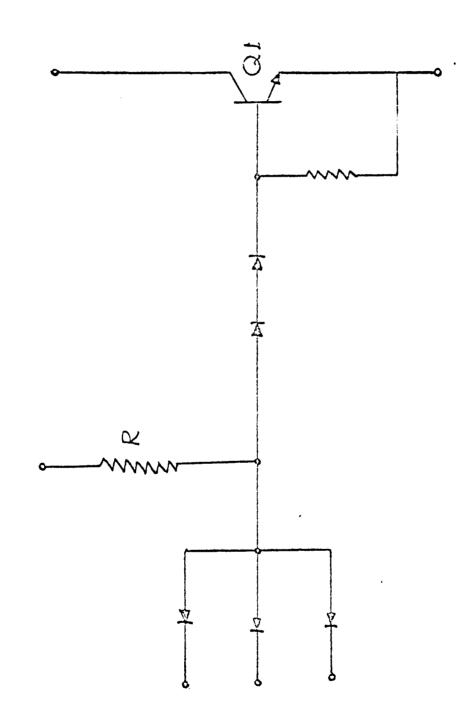

Figure 3.3 shows basic NAND gate. The input resistor, R, provides a relatively constant current which is either shunted to ground via one or more of the input diodes and the transistor of the driving circuit or is shunted into the base of transistor  $Q_1$ .

The IC equivalent of current gain is fan-out, inasmuch as the base drive is fixed. By selecting a NAND without an internal connection to the collector resistor, the total collector current is available for measurement via an external load.  $H_{fe}$  is defined as  $h_{FE}(sat)$  in terms of the maximum output current which can be supplied to an external load without causing the collector-to-emitter voltage to exceed the maximum allowable saturated voltage. Except for this minor difference, the previous remarks about current gain apply to integrated circuits. Since integrated circuits are by nature small-geometry, high-speed transistors and diodes, they might be thought to be inherently radiation tolerant. However, it is not quite that simple. In addition to the logic diodes and the transistor, there are also biasing diodes and the gate resistor, each of which is affected by radiation. Thus, circuit failure is not so much a question of the transistor itself as the associated elements. Unfortunately, the diode forward voltage and the resistor both tend to increase with radiation. Both effects decrease the current available to the transistor base and thus aggravate the decreasing current gain of the transistor. Since various manufacturers use different resistor values, current levels, doping levels, etc., it cannot be predicted what the radiation resistance of a manufactured device will be until actual tests are conducted. However, it is certainly advisable to select devices capable of high fan-out and to derate this parameter considerably.

## 3.8 Other Advantages

Rejection of Ionization-Sensitive Devices: The gamma radiation testing program can be used to reject devices which are highly sensitive to ionizing radiation. When sample sets are exposed to shorter time durations of gammaradiation some, or many, of the individual samples, depending upon the manufacturing techniques, will diverge rapidly from the expected class degradation curve. The precise reason for this divergence is unimportant so long as manufacturing processes are available which allow highly reliable qualification. The divergent samples are rejected as unreliable and poor risks. This method should reject many individual devices which have flaws and weaknesses which are uncovered by the punishing radiation environment. Some of these rejects will be the occasional, unexplained failure which survives the current testing methods.

Figure 3.3 - NAND/NOR Gate

Therefore, the same class degradation curve initially qualified for radiation-equivalency correlation can be used for detecting, to a high confidence limit, devices of this class which will not only survive the radiation exposure but also select those devices whose electrical parameters can be depended upon to remain stable. This is a currently anticipated problem which will exist at the gamma flux levels encountered by the instrument unit of a spacecraft using a nuclear propelled booster.

Early Detection of Unreliable Devices: Individual samples can be rejected (when conditions demand 100% testing to assure very high confidence levels for survival) if the class damage curves are scaled with confidence levels as a parameter. Then, any particular device which falls below a minimum threshold level at a fixed lower radiation exposure will be disqualified. The integrated flux exposure will be chosen to allow significant data points but still allow a usable range of qualified radiation tolerance. The threshold will be determined from the class qualification data.

Supply of Post-Irradiated Devices for Worst Case Design: Another byproduct of this testing under gamma radiation will also provide the applications engineer with irradiated transistors for proving out circuit performance. The circuits can be designed for operation before and after the total radiation exposure and the results verified by interchanging each pre-irradiated or screened device with its post-irradiated counterpart. This method will further enhance the chances of success for that circuit during the mission.

#### REFERENCES

- 1. Lockheed Missiles & Space Company, Summary Report: Radiation Effects Program (U), TRD No. SSD-TDR-64-190, December 1964.

- 2. Westrom, J. L. & D. C. Atorthy, <u>Design Guidelines for Circuitry in a</u> Nuclear Reactor-Propelled Spacecraft, IMSC/HREC A712479, October 1965.

- 3. Kane, J. F., Transistor Parameter Tradeoffs, EDN February 1966, pp 58-71.

- 4. Brown, R. R., Equivalence of Radiation Particles for Permanent Damage in Semiconductor Devices, IEEE Trans. on Nuclear Science, Vol. NS-10, Nov. 1963, pp 54-59.

- Bilinski, J. R., et. al., Proton-Neutron Damage Equivalence in Si and Ge Semiconductors, IEEE Trans. on Nuclear Science, Vol. NS-10, Nov. 1963, pp 71-86.

- 6. Lauritzen, P. O., & D. J. Fitzgerald, Design Tradeoffs for a Neutron Radiation-Tolerant Silicon Transistor, TEEE Trans. on Nuclear Science, Vol. NS-11, Nov. 1964, pp 39-46.

- 7. Unpublished Report, Astrionics Laboratory MSFC-NASA Special Projects, October - December 1964.

- 8. Components Irradiation Test, No. 4 (ER 7483); No. 7 (ER 7620); No. 12 (ER 7824); No. 13 (ER 7899); Georgia Nuclear Laboratories, Lockheed Georgia Company.

## 4.0 PHASE II: DESIGN OF RADIATION TOLERANT POWER SUPPLIES

## 4.1 400 Hz Inverter Development

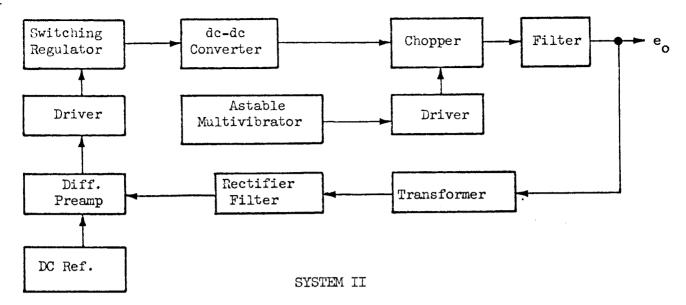

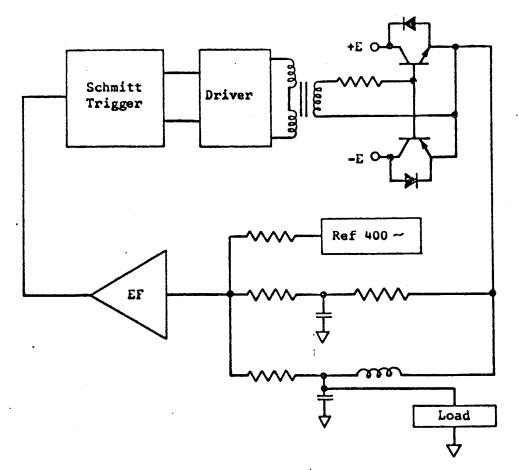

Figure 4.1 presents an amplitude modulation system similar to the existing mechanization except the voltage reference in the switching regulator is a.c. This combines the voltage regulation and power amplification functions into a single switching circuit and results in a synthesized sinusoidal output waveform. The technique has much merit but these design problems are apparent:

- 1. The filter on the switch output must accommodate a large dynamic swing.

- 2. An additional circuit is required to establish the initial magnetization conditions on the core.

- 3. Proper circuit operation requires a minimum load.

Again a size reduction may be accomplished by the addition of a dc to dc converter on the input. This would eliminate the latter two problems.

It was suggested that the amplitude modulation system with an integral dc to dc converter be used for the final design. This configuration combines design simplicity, high frequency conversion, and efficient operation.

Briefly, the proposed inverter mechanizations to be studied were:

Each of these uses a high-frequency converter to reduce transformer size as well as a switching regulator for efficiency. The mechanization difference is the utilization of an ac reference for the first system as opposed to a dc reference, thereby combining the regulator and chopper functions into a single component and reducing filter size. The primary effort has been on this system.

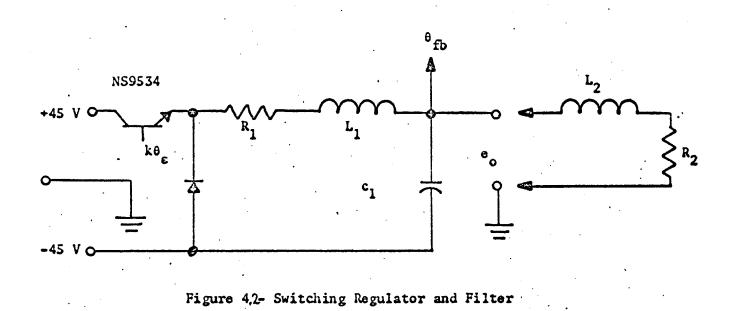

Before the inverter design continued, it was necessary to determine if the filter is realizable for this mechanization. To simplify the procedure, the following assumptions were made:

1. The high frequency pulses from the chopper, which are bridgerectified and capacity filtered before the switching regulator, will be considered a firm DC voltage of  $\pm$  E volts.

2. The saturation resistance of the switching transistor and the diode (which conducts when the transistor is off) are considered equal and called R. Also, the resistance of the filter inductor is lumped in this term.

3. The inductance and capacitance are considered ideal lumped parameters.

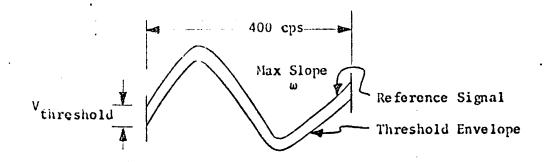

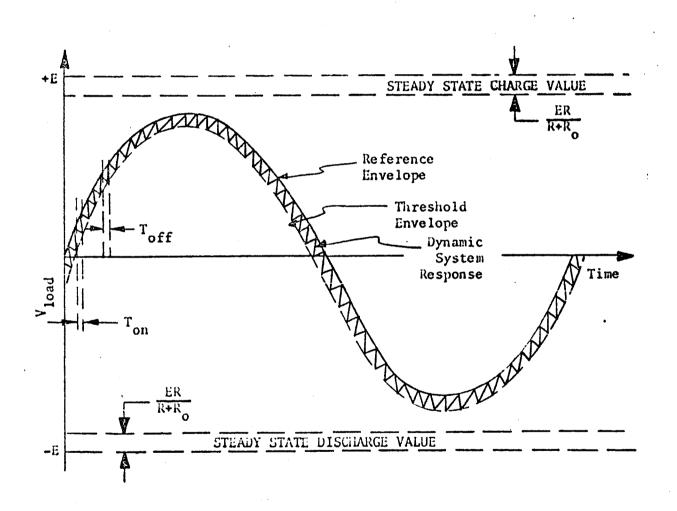

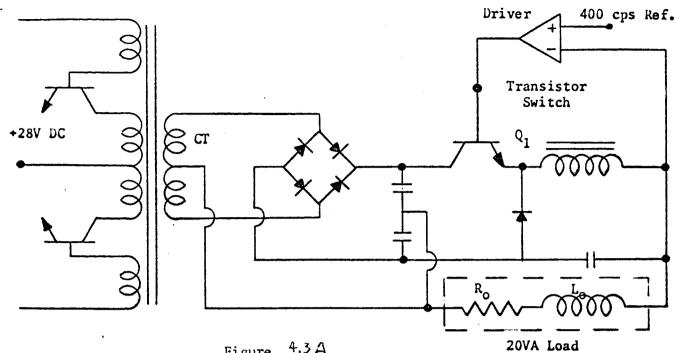

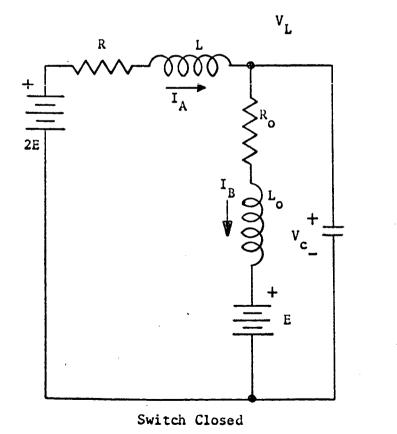

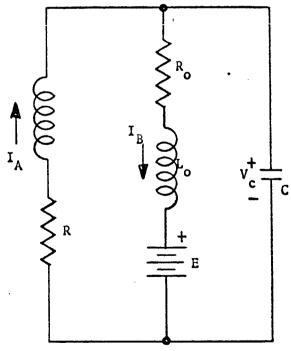

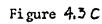

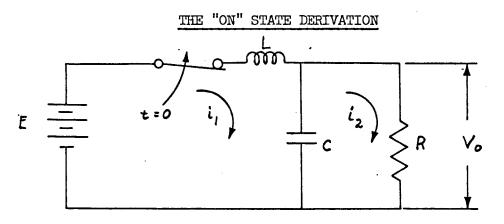

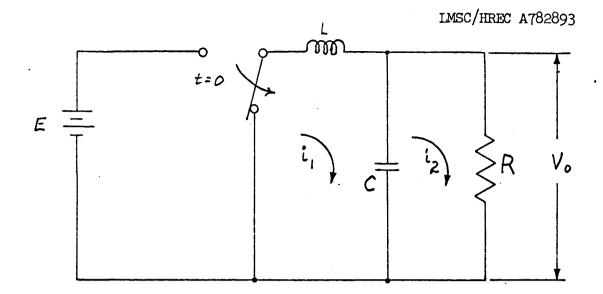

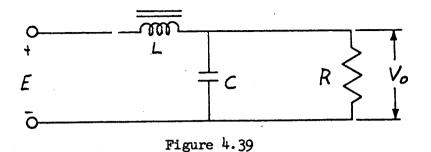

Figure 4.2 shows the circuit to be considered for analysis with its equivalent circuits for the "on" state and "off" state. Whenever the reference voltage exceeds the load voltage, the driver turns on the transistor switch. When the load voltage exceeds the reference, the switch is turned off. Thus, if a threshold voltage is assumed, it is of interest to determine the charging and discharging times of the switching regulator at various phases of the 400 cycle output voltage waveform. These charging and discharging times along with this threshold level are critical in determining system response, maximum switching speed, ripple, and regulation. The switch driver responds to any deviation from the reference level with this threshold tolerance.

. .

LMSC/HREC A782893

25

;

tote that the discharge and charge rates must always be greater than the maximum rate of change of the reference envelope which is  $\hat{E}\omega$  (the derivative of E sin $\omega$ t with  $\omega t = 0$ ).

This charging and discharging rate is defined as follows:

For charging:

$$\frac{V_{L_{on}} - V_{L_{off}}}{T_{on}}$$

For discharging:  $\frac{V_{L_{off}} - V_{L_{on}}}{T_{off}}$

If an ideal system is assumed (no transport time lag), the voltage at the load is described below.

The equivalent circuit (Figure 4.3, B and C) reveals that the charging and discharging pulses are working into a biased level. To illustrate, note that when the reference envelope is at a maximum level, the system will discharge toward the steady state value of  $RE/R+R_0$ . The time it takes at this point to discharge through the threshold level is less than the time it takes' to discharge through the threshold level on the other extreme of the envelope, the minimum voltage point. The same reasoning applies to the charging times. At the minimum value of load voltage, the system charges at a much faster rate than at the maximum load voltage has the lowest charging rate and the highest discharge rate while the minimum load voltage has the highest charge rate and the lowest discharge rate.

At this point, it is necessary to describe the system's dynamic response with time. For this analysis, circuit B in Figure 4.3 is used when the switch is on and circuit C when the switch is off. The initial conditions must be determined from the circuit condition preceding the time of switching. If we assume symmetrical operation, that is, that  $T_{ON}$  of maximum load voltage is identical to  $T_{Off}$  for minimum load voltage, and  $T_{Off}$  for maximum load voltage is identical to  $T_{On}$  for minimum load voltage, then only two conditions need be evaluated as the extreme cases for our analysis. If Toff is chosen with maximum voltage existing across the load, the maximum charging/discharging rate can be determined with the initial conditions at this point equal to the reference envelope  $\vec{E} \sin \omega t$ . If the Toff is chosen with minimum voltage existing across the load, the minimum charging/discharging rate is determined and the initial conditions are still evaluated at  $\vec{E} \sin \omega t$ . For the analysis, then, it is only necessary to consider circuit C, the equivalent circuit with the switch off.

Evaluation of the Initial Conditions: As long as the system turns off when it coincides with the reference envelope  $E \sin \omega t$ , a statement of the current through the filter inductor and the voltage on the capacitor at any time is sufficient. This approximation is valid as long as the threshold level is a very small portion of the load voltage as it is at the chosen points of interest.

The following equations are derived from the equivalent circuit of Figure 4.3C.

when  $V_{L} = V_{REF}$  at that time called  $t = t_{0}$ at  $t = t_{0} V_{L} = \hat{E} \sin \omega_{n} t_{n}$  where  $\omega_{n} = \text{freq. of inverter}$  $= (2\pi) (400 \text{ cps})$

= 2512

29

4.3 A Figure

V<sub>L</sub>

Switch Open

Figure 4,38

(1)

$$V_c = E + \hat{E} \sin \omega_n t_n$$

(2)

$$I_A = I_c + I_L$$

$I_L = \frac{\hat{E} \sin \omega_n t_n}{Z(\omega_n)} = \frac{\hat{E}}{|Z(\omega_n)|} \sin (\omega_n t_n - \Phi)$

For the equivalent circuit condition:

(3)

$$I_{L} = \frac{\hat{E} \sin \left[\omega_{n} t_{n} - \tan^{-1} \frac{\omega_{n} L_{0}}{R_{0}}\right]}{\sqrt{R_{0}^{2} + (\omega_{n} L_{0})^{2}}}$$

In the diagram below, note that the total increase of voltage over the threshold range during time  $T_{on}$  is defined as

$$V_{f} - V_{i} = V_{T} + \hat{E} \left[ \sin\omega_{n}t_{n} - \sin\omega_{n}(t_{n} - T_{on}) \right]$$

$$\sin\omega_{n}t_{n} - \sin\omega_{n}(t_{n} - T_{on}) = \sin\omega_{n}t_{n} - \sin\omega_{n}t_{n} \cos\omega_{n}T_{on} + \sin\omega_{n}T_{on} \cos\omega_{n}t_{n}.$$

but

so that if  $T_{on} \ll t_n$

$$\varepsilon = \hat{E} \left[ \sin\omega_n t_n - \sin\omega_n t_n \cos\omega_n T_{on} + \sin\omega_n T_{on} \cos\omega_n t_n \right]$$

$$\cos\omega_n T_{on} + 1$$

$$\sin\omega_n T_{on} + \omega_n T_{on}$$

$$\therefore \varepsilon = \hat{E} \omega_n T_{on} \cos\omega_n t_n.$$

and the total voltage differential is

(4)

$$V_f - V_i = \hat{E} \omega_n T_{on} \cos \omega_n t_n + V_{th}$$

$\frac{V_f - V_i}{T_{on}} = \frac{\Delta V_L}{\Delta t} = \hat{E} \omega_n \cos \omega_n t_n + \frac{V_{th}}{T_{on}}$

$\therefore$  The current I through the capacit

. The current  $I_c$  through the capacitor is:

(5)

$$I_c = C \frac{\Delta V_L}{\Delta t} = \frac{CV_{th}}{T_{on}} + \omega_n C \hat{E} \cos \omega_n t_n.$$

thus the current in the filter inductor can be closely approximated from (3) and (5).

(6)

$$I_{A} = \frac{\hat{E}}{\sqrt{R_{o}^{2} + (\omega_{n}L_{o})^{2}}} \sin \left[\omega_{n}t_{n} - \tan^{-1}\frac{\omega_{n}L_{o}}{R_{o}}\right] + \omega_{n}C \hat{E} \cos\omega_{n}t_{n} + \frac{CV_{th}}{T_{on}}$$

Now the initial conditions at turn-off can be estimated from equations (1) and (6). It is necessary to select the voltage of interest and estimate the turn-on time, T. If this turn-on time estimate correlates with the calculated time, it acts as an excellent check on the actual system calculations.

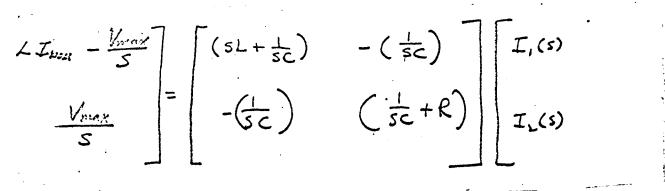

Derivation of the Filter's Dynamic Response: Using the equivalent circuit of Figure 4.36, the following mesh equations are written:

(7)

$$-\frac{E}{S} + LI_A = [R + R_o + (L + L_o)S]I_1(S) - [R_o + SL_o]I_2(S)$$

(8)

$$\frac{E}{S} - \frac{V_{c}}{S} = -\left[R_{o} + SL_{o}\right]I_{1}(S) + \left[\frac{L_{o}CS^{2} + R_{o}CS + 1}{SC}\right]I_{2}(S)$$

(9)

$$V_{L}(S) = [I_{1}(S) - I_{2}(S)] Z_{o}(S)$$

where  $Z_{o}(S) = R_{o} + S L_{o}$

(10)

$$\Delta I_1(S) = \begin{vmatrix} \frac{SLI_A - E}{S} & - [R_o + SL_o] \\ \frac{E - V_c}{S} & \frac{L_o CS^2 + R_o CS + 1}{SC} \end{vmatrix}$$

$$(11) \Delta I_{2}(S) = \begin{bmatrix} R + R_{o} + (L + L_{o})S \end{bmatrix} \frac{SLI_{A} - E}{S} \\ - \begin{bmatrix} R_{o} + SL_{o} \end{bmatrix} \frac{E - V_{c}}{S}$$

ſ

(12)

$$\Delta = \begin{vmatrix} \left[ R + R_{o} + (L + L_{o})S \right] - \left[ R_{o} + SL_{o} \right] \\ - \left[ R_{o} + SL_{o} \right] & \left[ \frac{L_{o}CS^{2} + R_{o}CS + 1}{SC} \right] \\ \Delta I_{1} = \frac{(SLI_{A} - E)(L_{o}CS^{2} + R_{o}CS + 1)}{S^{2}C} + \frac{(E - V_{c})(R_{o} + SL_{o})}{S} \cdot \frac{SC}{SC} \\ = LL_{o}CI_{A}S^{3} + (LCR_{o}I_{A} - EL_{o}C)S^{2} + (LI_{A} - R_{o}EC)S - E \end{vmatrix}$$

+

$$EL_{o}CS^{2} - V_{c}L_{o}CS^{2} + ER_{o}CS - V_{c}R_{o}CS$$

$$(13) \quad \Delta I_{1} = \frac{LL_{0}CI_{A}S^{3} + (LCR_{0}I_{A} - V_{c}L_{0}C)S^{2} + (LI_{A} - R_{0}CV_{c})S - E}{S^{2}C}$$

$$\Delta I_{2} = \left[R + R_{0} + (L + L_{0})S\right] \left(\frac{E - V_{c}}{S}\right) + \left(\frac{SLI_{A} - E}{S}\right) (R_{0} + SL_{0})$$

$$\Delta I_{2} = (R + R_{0})(E - V_{c}) + (L + L_{0})(E - V_{c})S + S^{2}LL_{0}I_{A} + SR_{0}LI_{A} - EL_{0}S - ER_{0}$$

$$(14) \quad \Delta I_{2} = \frac{ER - V_{c}(R + R_{0}) + \left[L(E + R_{0}I_{A}) - V_{c}(L + L_{0})\right]S + LL_{0}I_{A}S^{2}}{S}$$

$$(15) \quad \Delta (I_{1} - I_{2}) = \frac{LC(E - V_{c})S^{2} + \left[LI_{A} + RC(E - V_{c})\right]S - E}{S^{2}C}$$

$$\Delta = \frac{\left[(L + L_{0})S + R + R_{0}\right]\left[L_{0}CS^{2} + R_{0}CS + 1\right]}{CS} - R_{0}^{2} - 2L_{0}R_{0}S - L_{0}^{2}S^{2}$$

$$\Delta = (L + L_{0}) L_{0}CS^{3} + \left[LR_{0}C + L_{0}R_{0}C + RL_{0}C + R_{0}L_{0}C - 2L_{0}R_{0}C\right]S^{2}$$

SC

$\hat{}$

(16)  $\Delta = \frac{LL_{o}}{S} \left[ S^{3} + \left( \frac{R_{o}}{L_{o}} + \frac{R}{L} \right) S^{2} + \left( \frac{1}{LC} + \frac{1}{L_{o}C} + \frac{RR_{o}}{LL_{o}} \right) S + \frac{R + R_{o}}{LL_{o}C} \right]$

LMSC/HREC A782893

$$I_{1}(S) - I_{2}(S) = \frac{LC(E - V_{c})S^{2} + [LI_{A} + RC(E - V_{c})]S - E}{LL_{o}CS[S^{3} + (\frac{R_{o}}{L_{o}} + \frac{R}{L})S^{2} + (\frac{1}{LC} + \frac{1}{L_{o}C} + \frac{RR_{o}}{LL_{o}}]S + \frac{R + R_{o}}{LL_{o}C}]$$

(17)

$$I_1(S) - I_2(S) = \frac{\frac{E - V_c}{L_o} S^2 + \left[\frac{I_A}{L_oC} + \frac{R}{LL_o}(E - V_c)\right]S - \frac{E}{LL_oC}}{S\left[S^3 + \left(\frac{R_o}{L_o} + \frac{R}{L}\right)S^2 + \left(\frac{1}{LC} + \frac{1}{L_oC} + \frac{RR_o}{LL_o}\right)S + \frac{R+R_o}{LL_oC}\right]}$$

(18)

$$V_{L}(S) = \left[I_{1}(S) - I_{2}(S)\right]\left[R_{o} + SL_{o}\right]$$

(19)

$$V_{L}(S) = \frac{L_{o}\left(\frac{E - V_{c}}{L_{o}}S^{2} + \left[\frac{I_{A}}{L_{o}C} + \frac{R}{LL_{o}}(E - V_{c})\right]S + \frac{E}{LL_{o}C}\right)\left(S + \frac{R_{o}}{L_{o}}\right)}{S\left[S^{3} + \left(\frac{R_{o}}{L_{o}} + \frac{R}{L}\right)S^{2} + \left(\frac{1}{LC} + \frac{1}{L_{o}C} + \frac{RR_{o}}{LL_{o}}\right)S + \frac{R + R_{o}}{LL_{o}C}\right]}$$

(20) Define D =

$$S\left[S^3 + \left(\frac{R_o}{L_o} + \frac{R}{L}\right)S^2 + \left(\frac{1}{LC} + \frac{1}{L_oC} + \frac{RR_o}{LL_o}\right)S + \frac{R + R_o}{LL_oC}\right]$$

Then:

(21)

$$DV_{L}(S) = (E - V_{c})S^{3} + \left[\frac{I_{A}}{C} + \left(\frac{R}{L} + \frac{R_{o}}{L_{o}}\right)(E - V_{c})\right]S^{2} + \left[\frac{I_{A}R_{o}}{L_{o}C} + \frac{E}{LC} + \frac{RR_{o}}{LL_{o}}(E - V_{c})\right]S + \frac{ER_{o}}{LL_{o}C}.$$

Assuming values for the system parameters allow the calculation of D in (20) above.

Using synthetic division to find the real root, the expression factors into:

(23)

$$D = (S + 2.19 \times 10^3) [(S + 1.958 \times 10^3)^2 + (4.57 \times 10^4)^2].$$

The numerator (21) can be combined in terms of initial conditions in the following manner:

(24)

$$DV_{L}(S) = E\left[S^{3} + \left(\frac{R}{L} + \frac{R_{o}}{L_{o}}\right)S^{2} + \left(\frac{RR_{o}}{LL_{o}} - \frac{1}{LC}\right)S - \frac{R_{o}}{LL_{o}C}\right] - V_{c}\left[S^{3} + \left(\frac{R}{L} + \frac{R_{o}}{L_{o}}\right)S^{2} + \frac{RR_{o}}{LL_{o}}S\right] + \frac{I_{A}}{C}\left[S^{2} + \frac{R_{o}}{L_{o}}S\right].$$

Knowing the initial conditions allows the S-plane evaluation of this response. The total  $V_{\tau}$  (S) can be written:

(25)

$$V_{L}(S) = \frac{E\left[S^{3} + \left(\frac{R}{L} + \frac{R_{o}}{L_{o}}\right)S^{2} + \left(\frac{RR_{o}}{LL_{o}} - \frac{1}{LC}\right)S - \frac{R_{o}}{LL_{o}C}\right]}{S(S + 2.19 \times 10^{3})\left[(S + 1.958 \times 10^{3})^{2} + (4.57 \times 10^{4})^{2}\right]} + \frac{\frac{I_{A}}{C}\left[S^{2} + \frac{R_{o}}{L_{o}}S\right] - V_{c}\left[S^{3} + \left(\frac{R}{L} + \frac{R_{o}}{L_{o}}\right)S^{2} + \frac{RR_{o}}{LL_{o}}S\right]}{S(S + 2.19 \times 10^{3})\left[(S + 1.958 \times 10^{3})^{2} + (4.57 \times 10^{4})^{2}\right]}$$

These equations can be expanded using partial fraction expansion and the inverse LaPlace transformation taken to yield the load voltage variation in the time domain.

If the natural damping ratio for this equation is examined, it is found to be entirely too small to be useful and the circuit will oscillate near the natural frequency, since the voltage will not damp out before the next pulse appears.

$$\alpha = 1.958 \times 10^3 = 2^{\delta} \omega_n$$

$\delta = \frac{\alpha}{2\omega_n} = \frac{1.958}{(2)(45.7)} = .0214$

By decreasing L and increasing C, the damping is increased.

$$L = 50 \ \mu h$$

and  $C = 10 \ \mu f$ .

IMSC/HREC A782893

Then:

(26)

$$D = S^3 + 42.1 \times 10^3 S^2 + 201 \times 10^3 S + 4.6 \times 10^8$$

(27)

$$D = (S + 2.4 \times 10^3) (S + 19.88 \times 10^3)^2 + (43.7 \times 10^3)^2$$

Now the damping ratio is:

$$= \frac{19.88}{(2)(43.7)} = 0.227$$

In order to prevent the undershoot from exceeding the threshold level, the damping ratio must increase to near 0.8. This can be accomplished by allowing  $L = 10 \mu h$  and  $C = 10 \mu f$ .

| (28) | $D = S^3 + 2.02 \times 10^5 S^2 + 14.21 \times 10^9 S + 2.3 \times 10^{13}$ |

|------|-----------------------------------------------------------------------------|

| (29) | $D = (S + 1.66 \times 10^3) (S + 10^5)^2 + (.622 \times 10^5)^2$            |

|      | = <u>1</u> = 0.804<br>1.244                                                 |

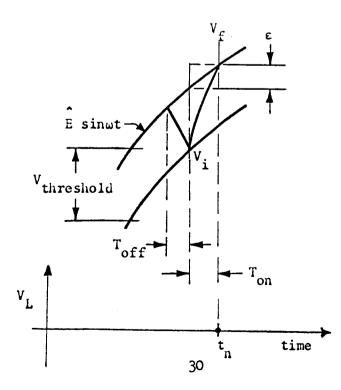

Since the calculations involved are very laborious and the results for switching time determination appear inconclusive because it is necessary to settle upon an optimum damping ratio which will still allow size reduction and good frequency and amplitude stability, the filter circuit was programmed on Lockheed's analog computer. 400 Hz Inverter's Computer Mechanization: The circuit below depicts the electronic equivalent programmed on the analog computer.

Current equations are used to describe this system's response. They are derived below.

Writing the node equations:

$$\frac{V_1 - V_2}{R_2 + SL_2} + \frac{0 - V_2}{(1/C_2S)} + \frac{0 - V_2}{R_3} + \frac{0 - V_2}{R_0 + L_0S} = 0$$

expanding, this becomes:

$$\begin{split} v_{1} R_{3} &= v_{2} R_{3} + v_{2} R_{3} C_{2} S(R_{2} + L_{2} S) + v_{2} (R_{2} + L_{2} S) + v_{2} R_{3} \left( \frac{R_{2} + L_{2} S}{R_{0} + L_{0} S} \right) \\ v_{1} &= v_{2} \left[ 1 + C_{2} S(R_{2} + L_{2} S) + \frac{R_{2} + L_{2} S}{R_{3}} + \frac{R_{2} + L_{2} S}{R_{0} + L_{0} S} \right] \\ v_{1} &= v_{2} \left[ L_{2} C_{2} S^{2} + \left( R_{2} C_{2} + \frac{L_{2}}{R_{3}} \right) S + 1 + \frac{R_{2}}{R_{3}} + \frac{R_{2} + L_{2} S}{R_{0} + L_{0} S} \right] \\ v_{2} S^{2} &= - \left\{ \left( \frac{R_{2} C_{2}}{L_{2} C_{2}} + \frac{L_{2}}{R_{3} L_{2} C_{2}} \right) Sv_{2} + \left( \frac{1}{L_{2} C_{2}} + \frac{R_{2}}{R_{3} L_{2} C_{2}} \right) v_{2} + \left( \frac{R_{2} + L_{2} S}{R_{0} + L_{0} S} \right) \frac{V_{2}}{L_{2} C_{2}} - \frac{V_{1}}{L_{2} C_{2}} \right\} \\ \ddot{v}_{2} &= - \left( \frac{R_{2}}{L_{2}} + \frac{1}{C_{2} R_{3}} \right) \dot{v}_{2} - \left( 1 + \frac{R_{2}}{R_{3}} \right) \frac{1}{C_{2} L_{2}} v_{2} - \frac{R_{2}}{R_{0}} \left( \frac{1 + \frac{L_{2}}{R_{2}} P}{1 + \frac{R_{0}}{R_{0}} P} \right) \frac{1}{L_{2} C_{2}} v_{2} \\ &+ \frac{V_{1}}{L_{2} C_{2}} \end{split}$$

Let A'' =

$$\begin{pmatrix} C_2 R_2 + \frac{L_2}{R_3} \end{pmatrix} \frac{1}{C_2 L_2}$$

B'' =  $\begin{pmatrix} 1 + \frac{R_2}{R_3} \end{pmatrix} \frac{1}{C_2 L_2}$

C'' =  $\frac{R_2}{R_0 L_2 C_2}$

D'' =  $\frac{1}{C_2 L_2}$

D'' =  $\frac{1}{C_2 L_2}$

D'' =  $\frac{1}{C_2 L_2}$

D'' =  $\frac{1}{C_2 L_2}$

LMSC/HREC A782893

Then:

(1)

Let

.

ł

1

$$\begin{split} \ddot{v}_{2} &= -A^{**}V_{2} - B^{**}V_{2} - C^{**} \left(\frac{1+\tau_{2}P}{1+\tau_{0}P}\right) + D^{**}V_{1} \\ &= \frac{e_{1n} - V_{1}}{R_{1} + L_{1}S} + \left[0 - V_{1}\right] C_{1}S + \frac{V_{2} - V_{1}}{R_{2} + L_{2}S} = 0 \\ e_{1n} \left[R_{2} + L_{2}S\right] + V_{2} \left[R_{1} + L_{1}S\right] = \\ \left[R_{2} + L_{2}S\right] + V_{2} \left[R_{1} + L_{1}S\right] + V_{1} \left[R_{2} + L_{2}S\right] + V_{1} \left[R_{1} + L_{1}S\right] \\ e_{1n} \left[R_{2} + L_{2}S\right] + V_{2} \left[R_{1} + L_{1}S\right] = \left\{C_{1}L_{1}L_{2}S^{3} + C_{1} \left[R_{1}L_{2} + R_{2}L_{1}\right] S^{2} \\ + \left(C_{1}R_{1}R_{2} + L_{1} + L_{2}\right)S + R_{1} + R_{2}\right] V_{1} \\ \left\{S^{3} + \frac{R_{1}L_{2} + R_{2}L_{1}}{L_{1}L_{2}}S^{2} + \frac{C_{1}R_{1}R_{2} + L_{1} + L_{2}}{C_{1}L_{1}L_{2}}S + \frac{R_{1} + R_{2}}{C_{1}L_{1}L_{2}}\right\} V_{1} = \\ \frac{R_{2}}{C_{1}L_{1}L_{2}}e_{1n} + \frac{L_{2}S e_{1n}}{C_{1}L_{1}L_{2}} + \frac{V_{2}R_{1}}{C_{1}L_{1}L_{2}} + \frac{L_{1}S V_{2}}{C_{1}L_{1}L_{2}} \\ E^{**} = \left(\frac{R_{2}L_{1} + R_{1}L_{2}}{C_{1}L_{1}L_{2}}\right)C_{1} \qquad I^{**} = \frac{L_{2}}{C_{1}L_{1}L_{2}} \\ F^{**} = \frac{C_{1}R_{1}R_{2} + L_{2} + L_{1}}{C_{1}L_{1}L_{2}} \qquad J^{**} = \frac{R_{1}}{C_{1}L_{1}L_{2}} \\ F^{**} = \frac{R_{2} + R_{1}}{C_{1}L_{1}L_{2}} \qquad K^{**} = \frac{L_{1}}{C_{1}L_{1}L_{2}} \end{split}$$

i si

$$H'' = \frac{R_2}{C_1 L_1 L_2} L''$$

39

$C_1L_1L_2$

$$\vec{V}_{1} = -E'' \vec{V}_{1} - F'' \vec{V}_{1} - G'' V_{1} + H'' e_{in} + I'' e_{in} + J'' V_{2} + K'' \vec{V}_{2}$$

$$(2) \quad \vec{V}_{1} = -E'' \vec{V}_{1} - F'' V_{1} - G'' \int V_{1} dt + H'' \int e_{in} dt + I'' e_{in} + J'' \int V_{2} dt + K'' V_{2}$$

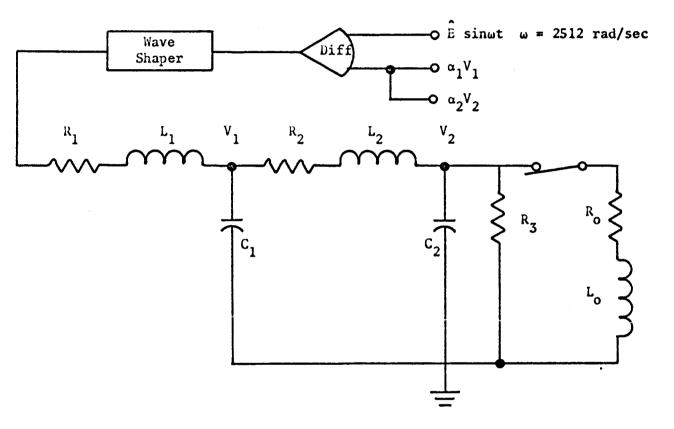

Equations (1) and (2) are now generated on the analog computer along with an electronic switch for positive and negative  $e_{in}$  (see Figure 4.4). The reference voltage and portions of  $V_1$  and  $V_2$  are summed into amplifier 12 which drives the electronic switch. Table I lists the calculated values and coefficient of each pot used in the program. The amplitude and time scaling are also given in the table. Systems 3 and 5 are the third and fifth computer runs respectively with the following circuit values used.

$\begin{array}{cccc} R_{1} = 2 \ \Omega & R_{2} = 0.5 \ \Omega & R_{3} = 3 \ k \ \Omega \\ L_{1} = 60 \ \mu h & L_{2} = 1.5 \ m H & L_{0} = 10.3 \ m H \\ C_{1} = 0.5 \ \mu F & C_{2} = 2 \ \mu F & R_{0} = 21.7 \ \Omega \end{array} \right\}$  System #3  $\begin{array}{c} \alpha_{1} = \alpha_{2} = 0.30 \end{array}$

Same as System #3 except

$\begin{array}{c} L_2 = 0.75 \text{ mH} \\ C_2 = 4 \mu \text{F} \end{array} \end{array} \right\} \qquad \text{System #5} \\ \text{System #5} \\ \text{System #5} \end{array}$

It was found that a minimum voltage level of  $\frac{1}{2}$  60 VDC was needed to drive the filter sections without causing the loop to open at the high or low voltage level. The ripple shown on the computer runs was below 1/2 V peak to peak, and the regulation scaled from the no-load to full-load switching on the computer run for System #5 was below 1 per cent. There was no noticeable change in output voltage with variations in  $e_{in}$  as long as the 60 V margin was maintained.

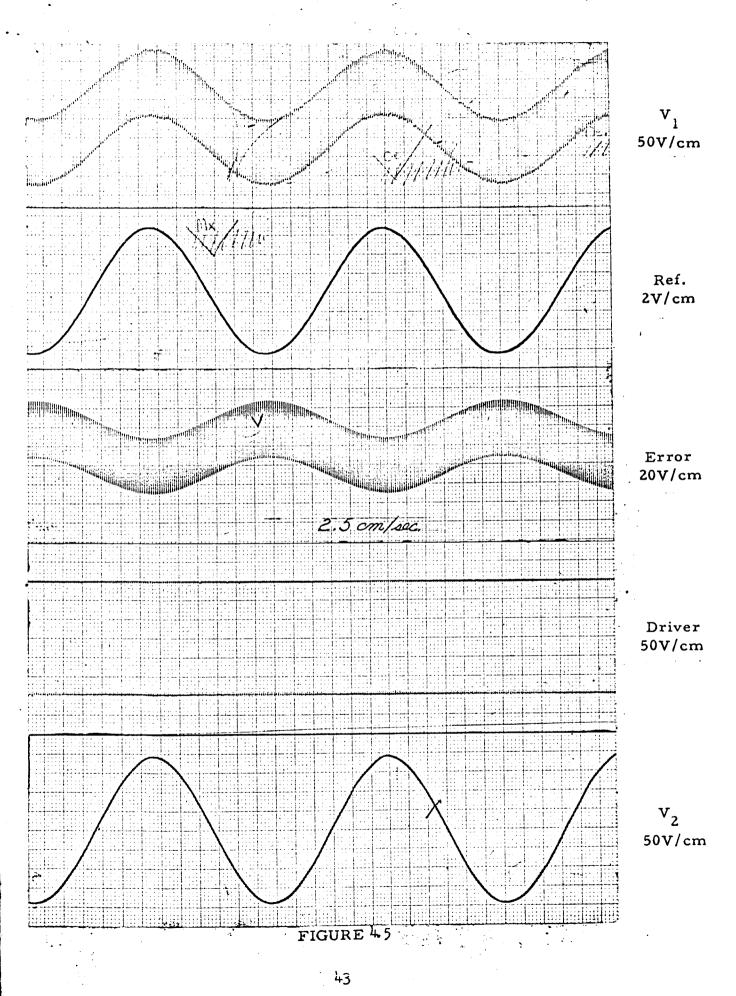

Figure 4.5 shows the output voltage  $V_2$  as a function of time first in the unloaded and then switched to the loaded case. Note that on all these figures, that the time t = 0 begins on the right.

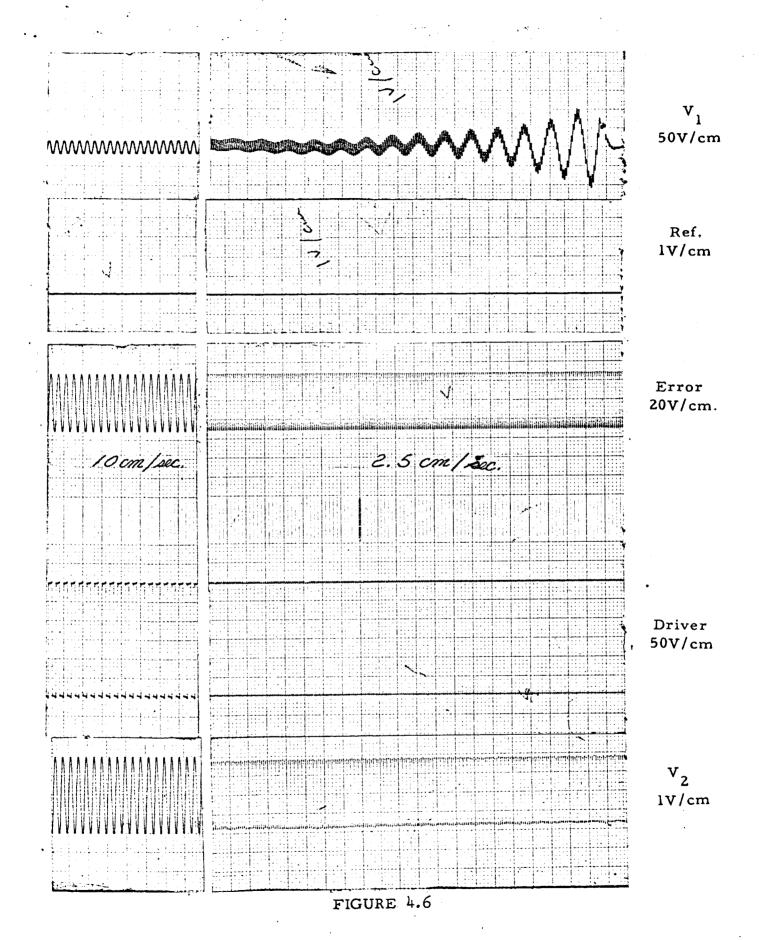

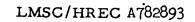

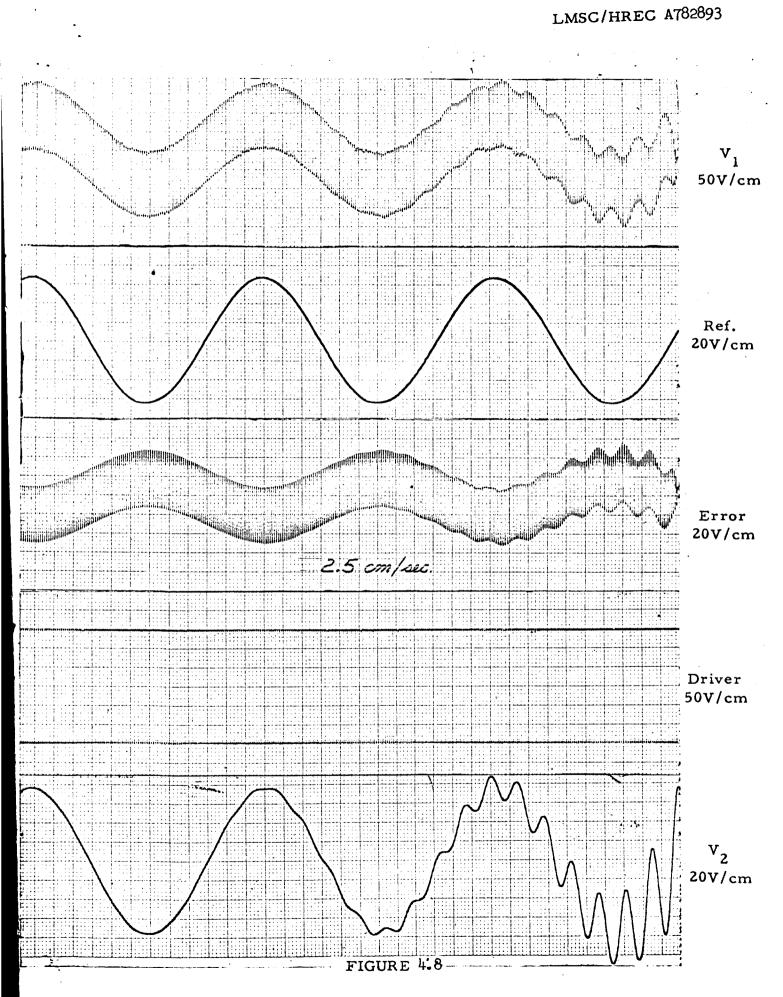

Figure 4.6 shows the output ripple and indicates the system stability when a small perturbation was applied. Note the time scale change on the left. Figures 4.7 and 4.8 show the number of cycles it takes for the output to stabilize when the system is first turned on. Figure 4.7 is the no-load condition and Figure 4.8 is the loaded condition.

TABLE I

•

.0622 .5556 5556 .2107 .8997 .0163 .6733 0.0667 .6667 ,8333 .075 .333 .333 .333 0.888 System 5 1.63×10<sup>10</sup> 3.599<sup>10</sup> 3.333<sup>10</sup> 2.222<sup>13</sup> 11.111<sup>13</sup> 8.88<sup>13</sup> 2.667<sup>9</sup> 1.667<sup>4</sup> 0.333<sup>5</sup> .2107<sup>4</sup> 33, 66<sup>3</sup> . 3339 4.444<sup>3</sup> .753 .622 1/39 0.6733 0.8333 0.8669 0.5556 0.6667 0.5556 0.3333 0.0162 0.4854 0.2107 0.4444 0.0667 0.05 System 3 0.001618<sup>13</sup> 0.21066<sup>4</sup> 22.2222<sup>12</sup> 55.5556<sup>12</sup> 11.1111<sup>12</sup> 0.04854<sup>4</sup> 33, 3333<sup>9</sup> 34.6778<sup>9</sup> 44.444<sup>12</sup> 0.3333<sup>9</sup> 0.3333<sup>9</sup> 1.3333<sup>9</sup> 33.6667<sup>3</sup> 0.5 Pot No. 23 చ 10 12 16 ŝ ഹ 9 ω 6 11 17 24 2 ~ 22 -12 -10 -10 -10 -13 - 14 - 14 Multiplier 4 °° 6-ຸ ທ പ് 6-4 ഹ ഹ 0.5 ഹ ഹ ਂ **.** . . 2 2 2 ----Coefficient 0.003236<sup>13</sup> 22.2222<sup>12</sup> 5,5556<sup>12</sup> 11.1111<sup>12</sup> 0.09707<sup>9</sup> 0.21066<sup>4</sup> 27.7778<sup>12</sup> 0.6667<sup>3</sup> 0.6668<sup>9</sup> 16.6667<sup>9</sup> 1.6667<sup>4</sup> Value 0.6667<sup>9</sup> 3.3333<sup>4</sup> 0.6667<sup>9</sup> F=(C1.21.22+442)[ |17.34449 E = C, (E2 L, + E, L) 33.66673 6= (e++e)2"  $A_{z}^{\prime\prime} \left( C_{z} R_{z} + L_{z} \right)_{D}^{\prime\prime}$ 62= 61, 82 D"  $B''=\left(7+\frac{R_{a}}{R_{a}}\right)D''$ Coefficient C3= C2 22 J" (B) 2' L= C122L H= 22C" Formula I=22 <" んぶくしょ 01=20 A"= R1/6 0 2262 1/2 n ž D 42

FIGURE 4.10

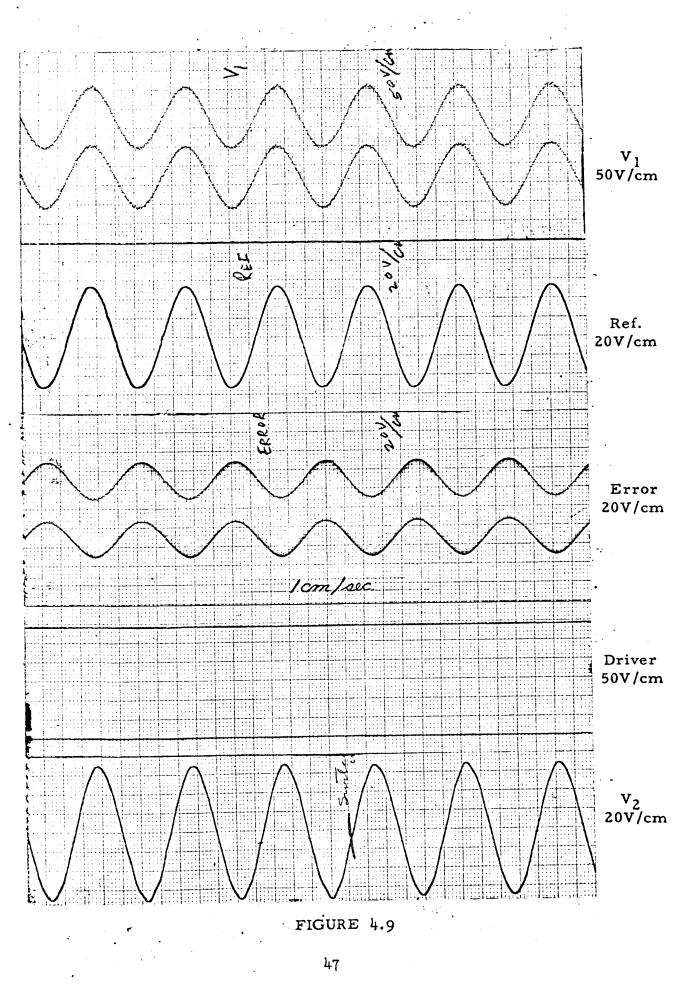

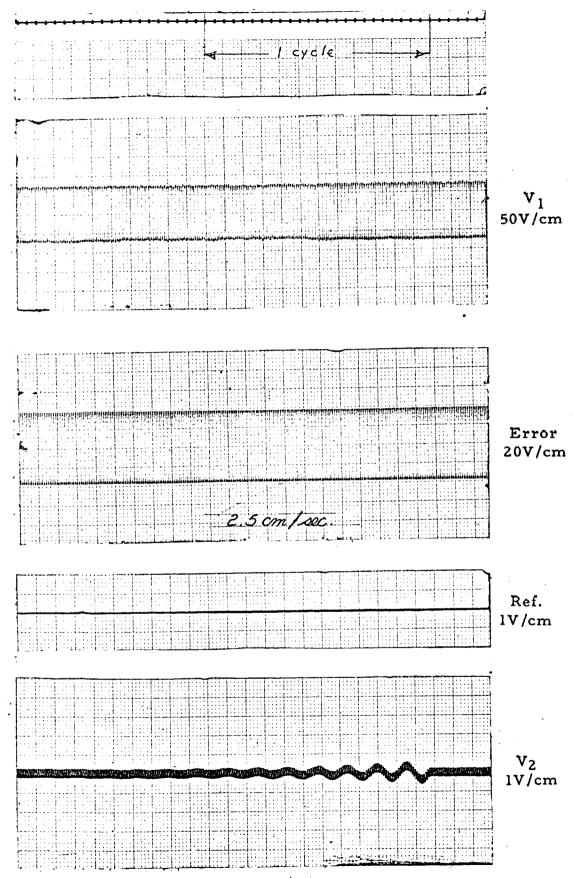

Figures 4.9 and 4.10 are from the fifth computer run while the previous figures were made on the third run. Figure 4.9 shows the regulation when the load is switched in and out. The slight distortion which appears on the output traces damped out after 15 cycles. Figure 4.10, again, shows the ripple and response to a small perturbation. Note the scale change to 1V/cm.

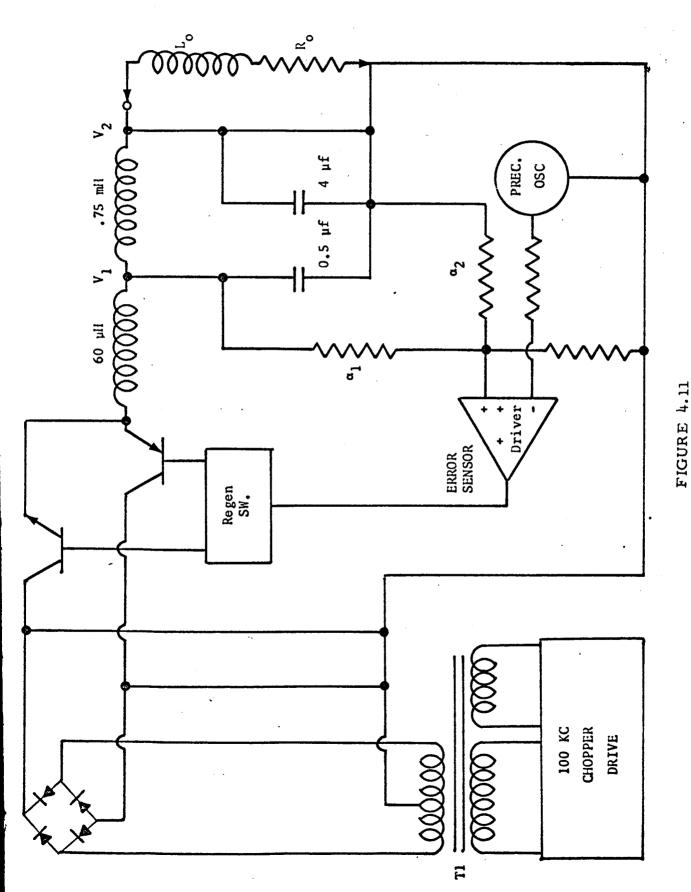

General Mechanization of the 400 Cycle Inverter: The block schematic, Figure 4.11, incorporates the filter results from the computer study with a general method for mechanization. As pointed out by Mr. Owens and verified by the computer run, a simple diode will not perform the commutating function due to the reversal of load current. It is necessary to switch from the plus to minus side of the line. A gating method was incorporated to accomplish this. Silicon-controlled switches lend themselves to this type of operation, but because of their instability under radiation and frequency, other limitation methods of gating with transistors were explored.

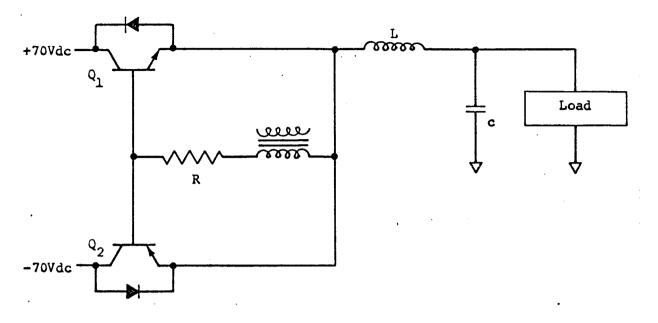

Driver Mechanization: Two basic forms of drivers involving both bistable and tristable circuits have been used to study the power switch characteristics. The prime requirement placed upon the driver has been to provide the fastest possible switching signal for the power switch. Basic physical properties of the power switch have delayed the development of the device.

There are many high power transistors which can withstand 150 watts. However, these transistors typically have switching times of 5-7 $\mu$  sec. Laboratory tests of this circuit, with power supplies of + volts, have developed current transients of 2 amperes with transistors which switch in 200 nsec. Hence, a 5 $\mu$  sec, 150 volt short circuit cannot be tolerated.

A base driver circuit can be designed to account for a 5, sec switching time by delaying the turn-on of the second transistor by an equal time. However, the switching circuit now under development uses a switching frequency of 50 kc. A 5, sec storage time at this frequency would reduce the maximum possible modulation to 50%. Thus, a higher supply voltage is required in order to maintain the required current.

A lower switching frequency can be used, but this will require a larger filter-inductor and a higher supply voltage. The larger inductor will be required to support current longer during the opposite voltage cycle. The higher supply voltage will be required to provide the same initial L/R slope through the larger inductor.

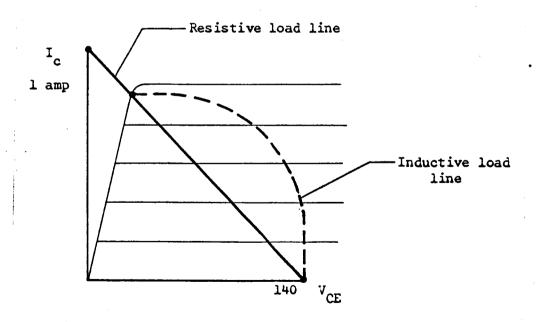

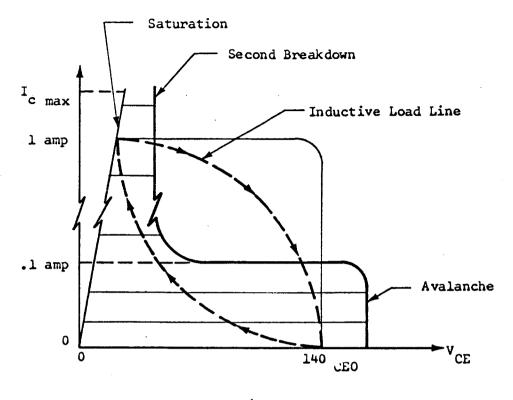

Higher speed transistors rated for  $I_c$  max of 2 or 3 amperes and  $V_{CE}$  max of 180 volts are still unacceptable because they experience secondary breakdown (see Figure 4.15) when called upon to switch the inductive load.

LMSC/HREC A782893

Figure 4.12

The emitter follower input provides isolation from the voltage transients seen at the Schmitt trigger input. The transformer-coupled complimentary pair are turned off by positive pulses from the Schmitt circuit and provide the required 200 mwatts for driving the power switch.

The sensor voltage will be resistively summed with the reference voltage. The resulting error voltage will modulate the integrated square wave feedback required for self oscillation.

Some minor circuit changes will be required to provide temperature compensation.

The power switch calls upon the best properties of a power transistor and a high-speed logic transistor. Referring to Figure 4.13, the transistors must have a fast switching time in order to avoid shorting the positive and negative power supplies. This implies a thin film, low base capacitance transistor.

The same transistor must turn off a maximum load current for an inductive load of about one ampere with a  $V_{\rm CE}$  maximum of 140 volts.

Figure 4.13

Figure 4.14 shows that the power switch must be capable of both high (current and high voltage for a short duty cycle.

Figure 4.14

Figure 4.15

No single transistor now available can meet all the requirements for the power switch, therefore, a multiple device approach would appear the only method feasible.

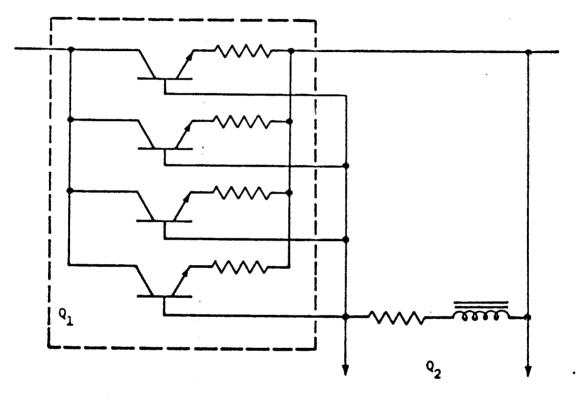

A number of high current-low voltage transistors may be placed in series as in Figure 4.16.

Figure 4.16

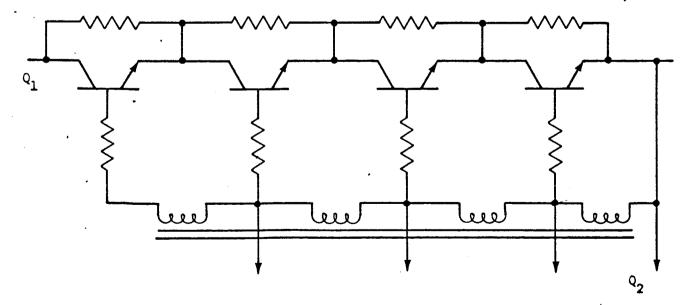

Paralleling many high speed transistors (Figure 4.17) and dividing the current between them appears to be the best solution. The transient current can be kept low and current division appears more reliable than voltage division. Secondary breakdown may also be avoided by keeping the current in each transistor below the secondary breakdown power level. However, attempts to mechanize either combination did not prove practicable. The requirement for high switching speed (i.e., low storage time) was not met for either mechanization.

## Figure 4.17

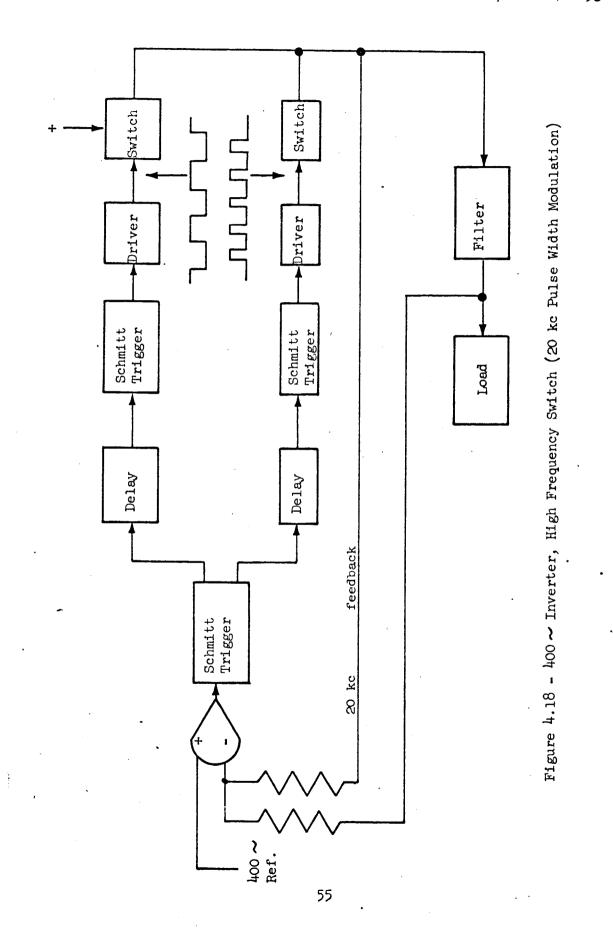

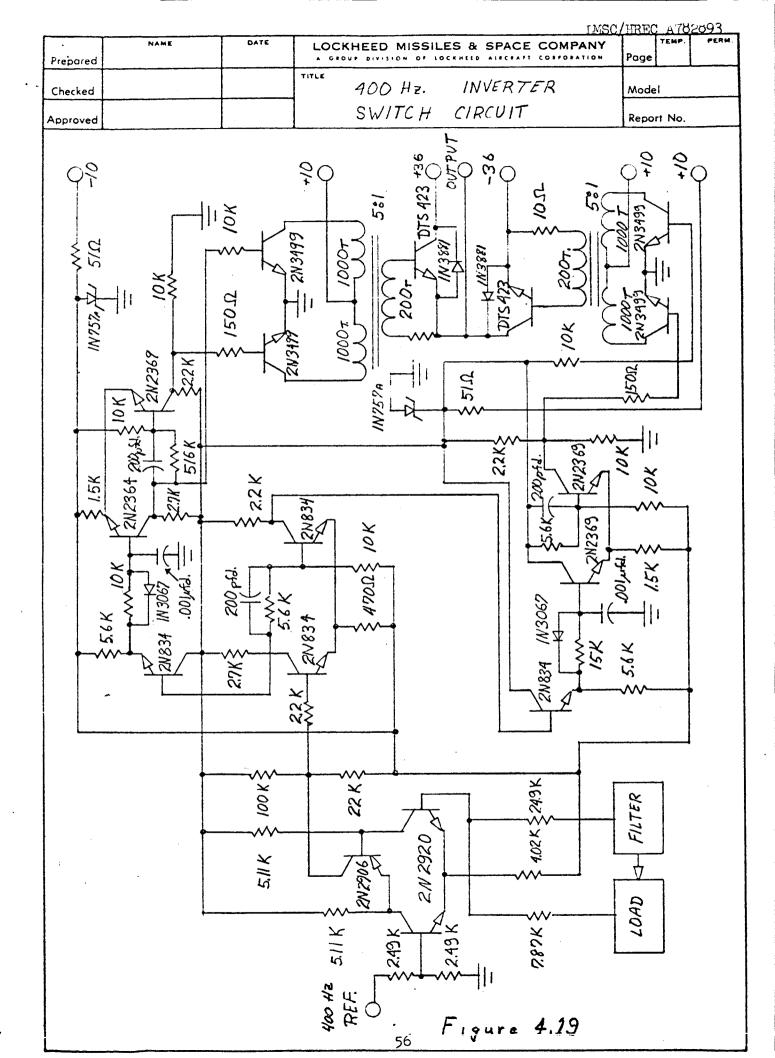

A different approach was tried. The switch problem was solved by simply using high power switching transistors and accepting the 2-5 microsecond storage time. The circuit is shown in block diagram form in Figure 4.18, and in schematic form in Figure 4.19. The system requires that each transistor be driven separately and that the turn-on of each switch is delayed until the other is off. Six to ten microseconds per cycle were allowed for the delay time. In order to achieve a high degree of modulation, the switching frequency was dropped to about 20 kc. The system functions well with a high voltage power input but because of the limited closed loop frequency response, the output was limited to 30 volts P-P.

LMSC/HREC A782893

## 100 kc DC to DC Converter for the Inverter

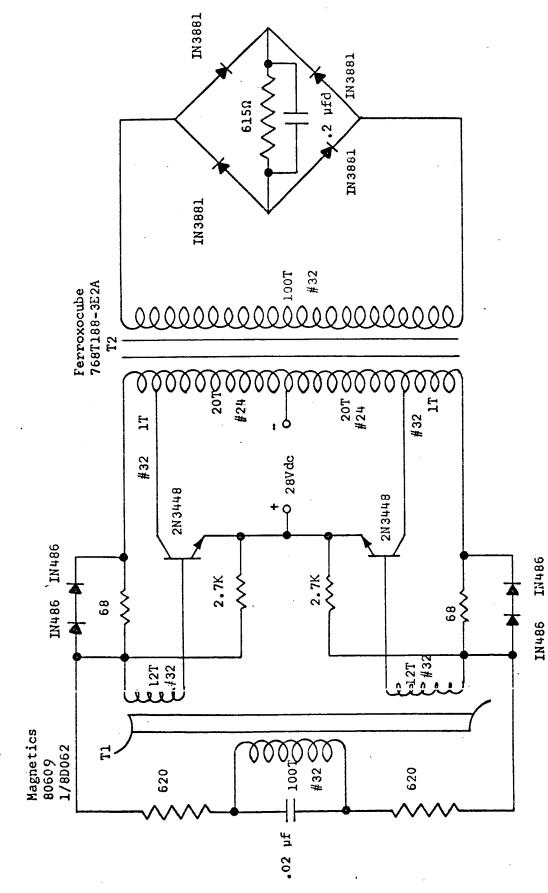

The converter was mechanized utilizing a positive feedback, nonsaturating output transformer for sensing when the 2N3448 transistors have turned off (stored charge removed from the saturated ON transistor) and then reversing polarity. The saturating core was used to energize the ON transistor's base until saturation; then the loss of voltage across the primary of the transformer affords a negative drive for the base, turning off the transistor. Both transistor's bases have negative bias until the output transformer switches, since the rate of change of current reverses. This is due to the increasing impedance of the ON transistor while turning OFF after removal of the storage charge. The di/dt reversal generates an opposite polarity voltage waveform.

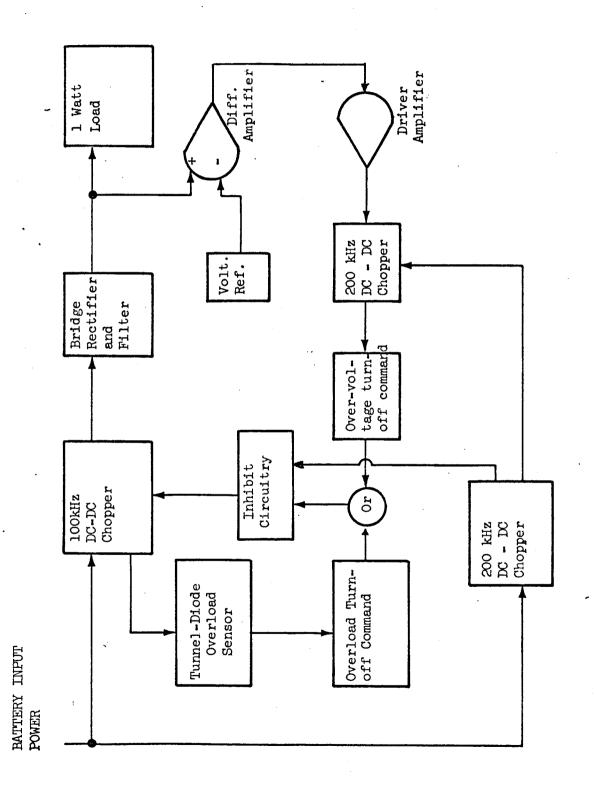

The converter's electrical schematic is shown in Figure 4.20 and the efficiency calculations are in Table 1. Figure 4.21 shows the test setup for making the power measurements.

Results of this 400 Hz Inverter Mechanization: This mechanization finally had to be dropped. Since the switch voltage capability prevented the generation of the + 36.8 volt peak amplitude because of the large reverse-bias requirements on the collector to base region and the operation into an inductive load causing very high power spikes during switching necessitated a reevaluation of the switching concept. The regulation requirements dictated a high gain closed loop system which required much lower corner frequencies that anticipated to stabilize the system. This then presented a sluggish response to the tracking error signal/output difference so that the high voltage output could not be achieved with necessary regulation requirements.

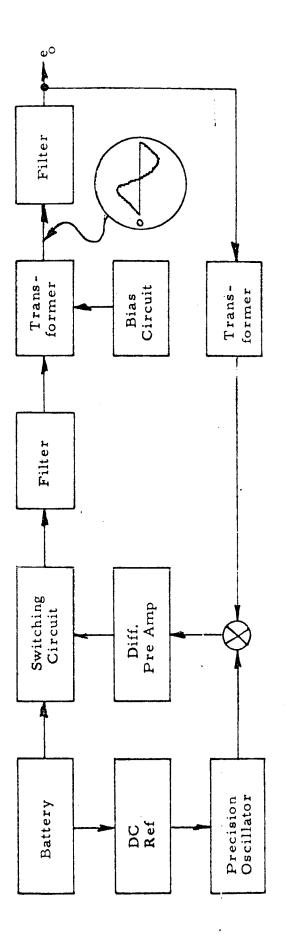

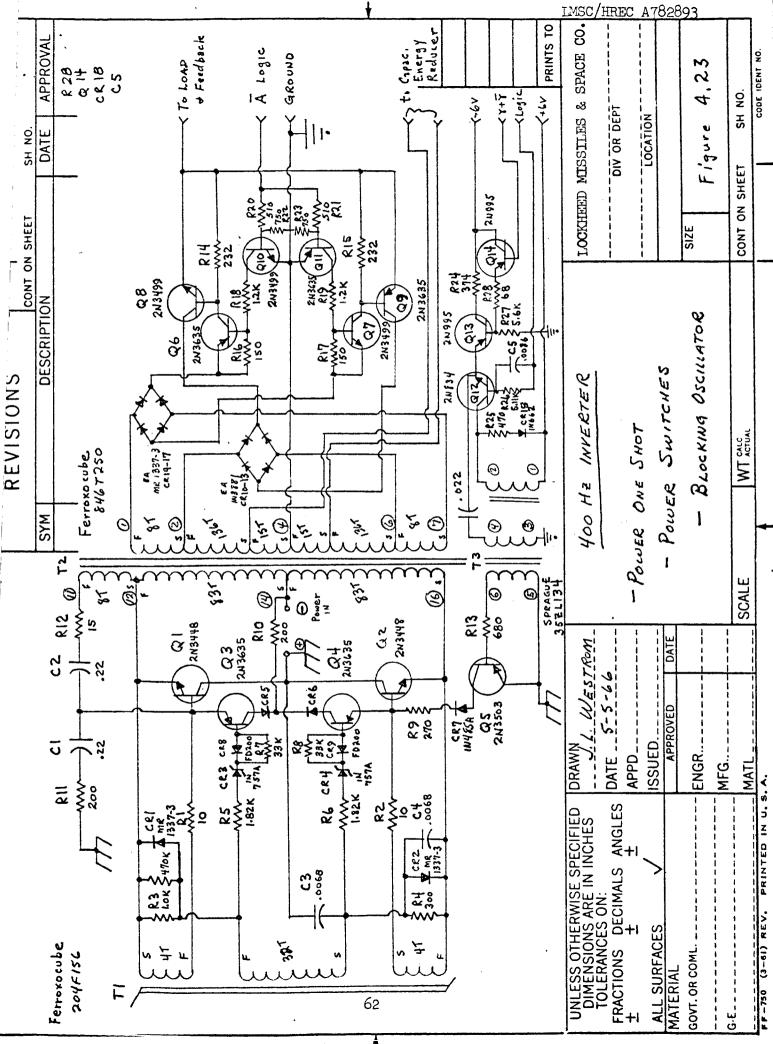

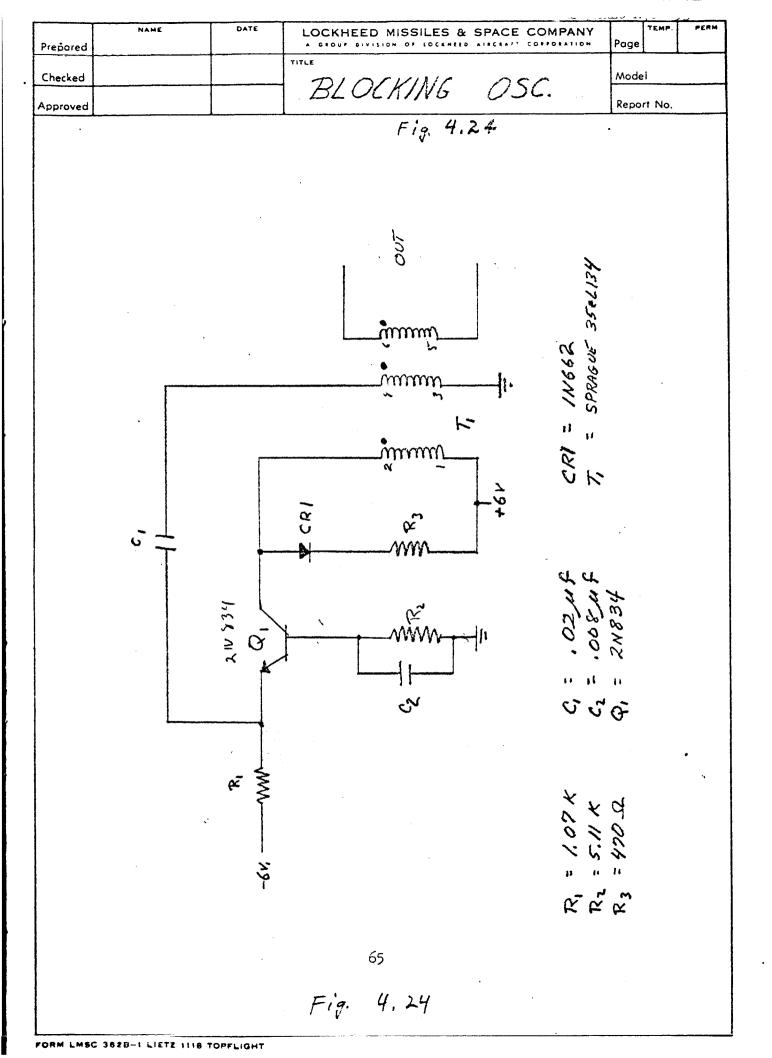

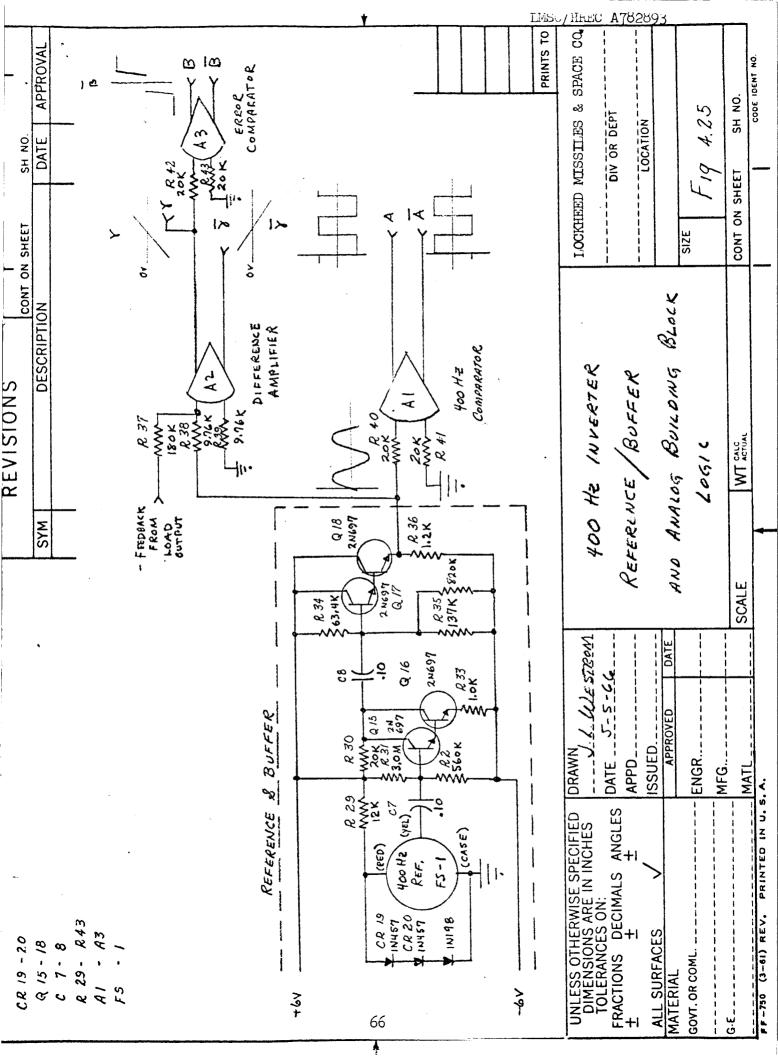

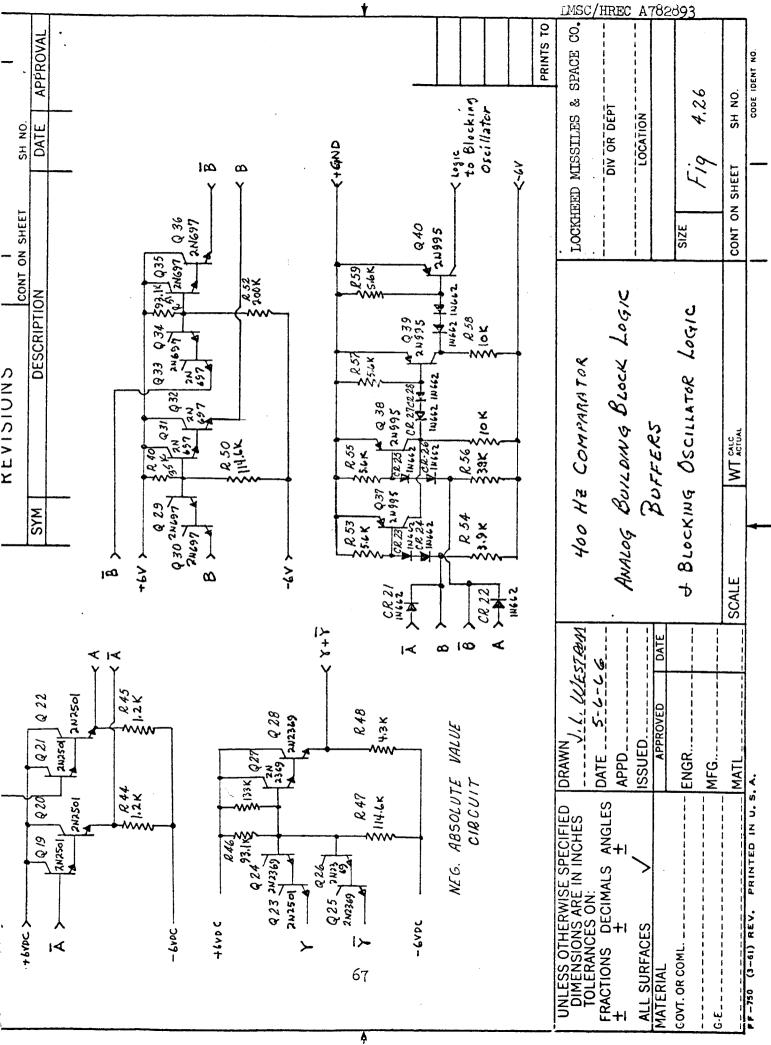

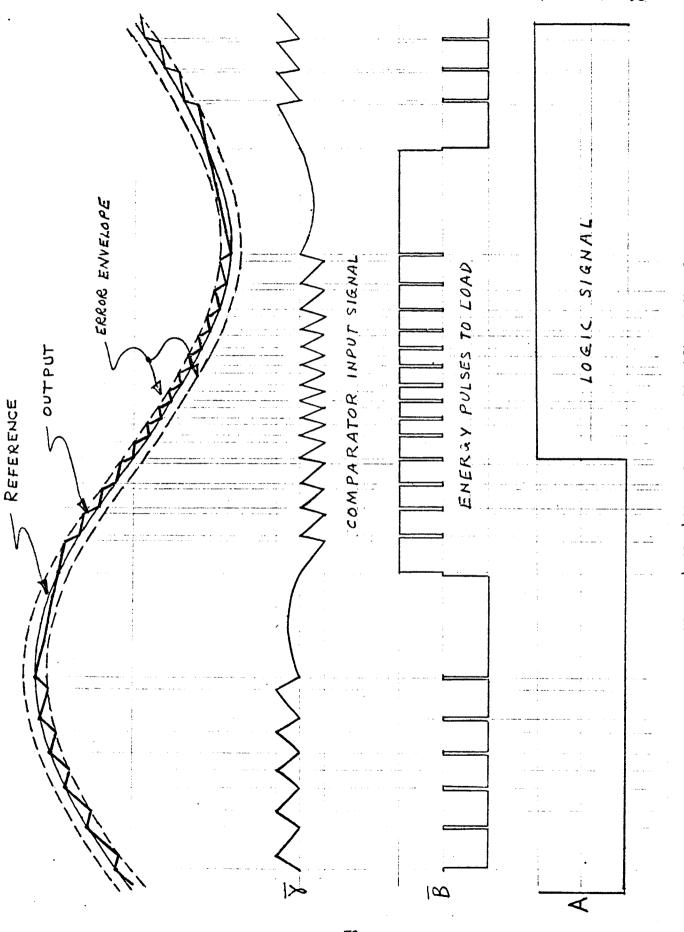

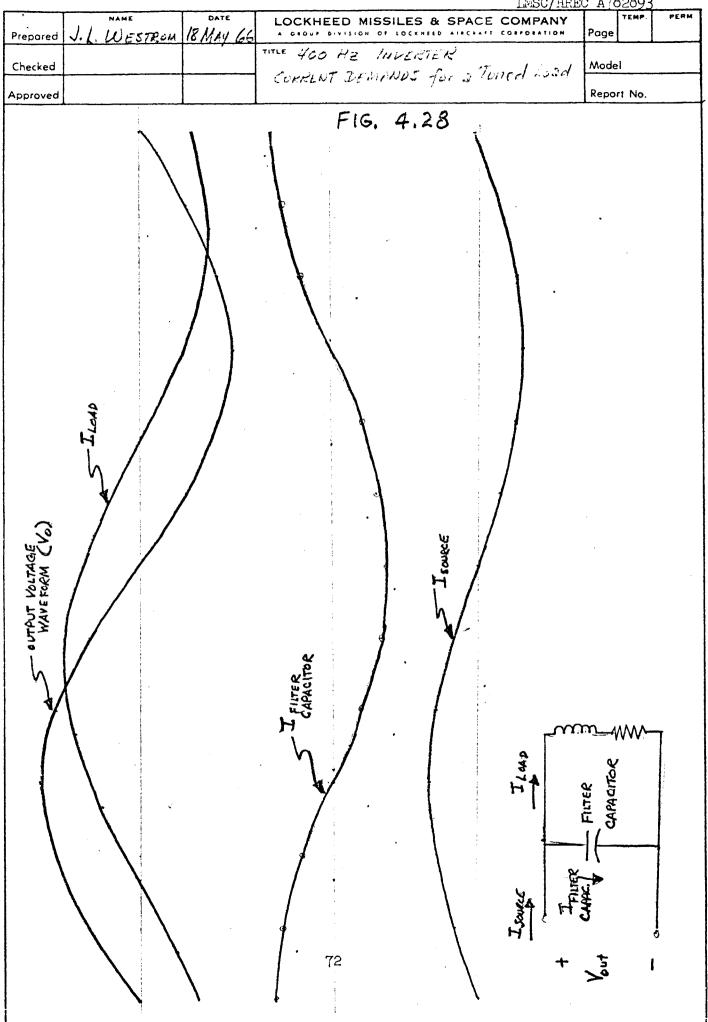

Final 400 Hz Inverter: The general design of this 400 Hz inverter is similar to a dc-to-dc converter with two distinct differences: (1) the error signal is held to a dynamic null by the active feedback of the difference between an externally generated 400 Hz reference oscillator and the output waveform; (2) the power is switched across a transformer at high frequency. This power is controlled on the secondary side by sensing both error magnitude and polarity of error signal synchronized with the 400 Hz reference benerated on the same secondary side of the transformer, and finally coupled to the primary side by means of a blocking oscillator. By controlling the blocking oscillator repetition rate and by the initiation of pulses, either a burst of pulses or relatively few pulses can be coupled across the power transformer by means of a unique power one-shot circuit. The duty cycle of these pulses is a direct function of the load and line demands.

Since the power transfer is accomplished in a switching mode of circuit operation, inherently high efficiency is offered with transformer size being dictated by the switching frequency. By handling the power switching on the primary side, the transformer turns ratio can be utilized to increase the voltage where necessary. Of course, the same circuit philosophy can be used to generate any arbitrary function by substituting that function for the 400 Hz reference. Natural restraints are imposed by the frequency, voltage amplitude, and power requirements.

Figure 4.20 - DC-to-DC Converter

|         | f<br>(kc)                 | 67.2  | 68.5  | 69 • 5 | 71.5  | 73.5  | 75.8  | 79.5  | er 6150                                            |

|---------|---------------------------|-------|-------|--------|-------|-------|-------|-------|----------------------------------------------------|

|         | л<br>(8)                  | 84.5  | 86.2  | 85.8   | 85.1  | 86.4  | 85.0  | 83.5  | Ammeter                                            |

|         | Po<br>(watt)              | 21.9  | 23.6  | 25.6   | 27.3  | 29.1  | 32.8  | 36,65 | dc - dc<br>Converter                               |

| TABLE I | I<br>(amp)                | .189  | ,196  | .204   | .211  | .218  | .231  | • 244 |                                                    |

|         | Vo<br>(volt)              | 116   | 120.5 | 125.2  | 129.5 | 133.6 | 142.0 | 150.4 | 6.3V Filament<br>Transformer<br>Primary<br>100 ufd |

|         | P <sub>in</sub><br>(watt) | 25.95 | 27.4  | 29.8   | 32.0  | 33.75 | 38,55 | 43.8  |                                                    |

|         | lin<br>(amp)              | 1.09  | 1.11  | 1.16   | 1.20  | 1.22  | 1.305 | 1.39  | + Amreter                                          |

|         | V <sub>in</sub><br>(volt) | 23.8  | 24.7  | 25.7   | 26.7  | 27.65 | 29.55 | 31.5  | 0 - 36V<br>15 amp<br>P. S.                         |

LMSC/HREC A782893

Figure 4.21- Measurement Circuit

The circuit has been laid out with the idea of utilizing presently available commercial microcircuits, both analog and digital, for substitution in most of the control and timing functions. The power switching circuitry could perhaps be manufactured in a hybrid flat-pack to reduce size and offer better matching characteristics.

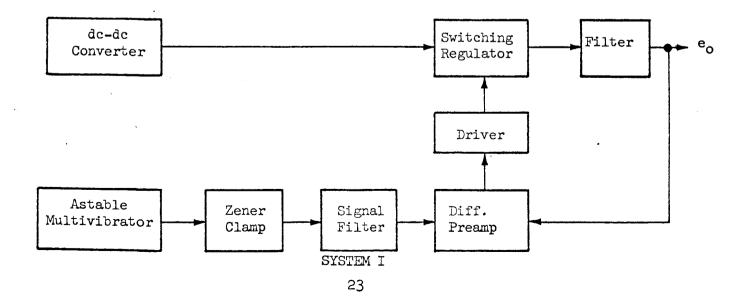

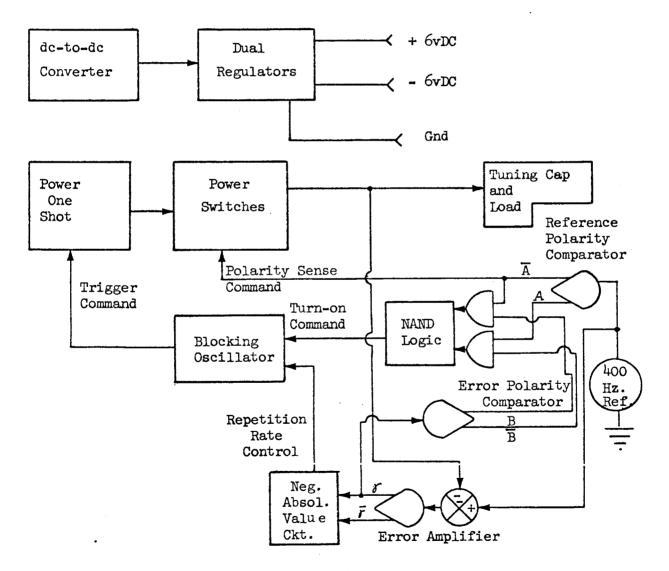

Generalized Block Diagram: Figure 4.22 shows the generalized block diagram of the circuit. No attempt is made to present impedance matching and coupling circuits, but only the necessary explicit functions. Each of the functional circuits is discussed in detail.

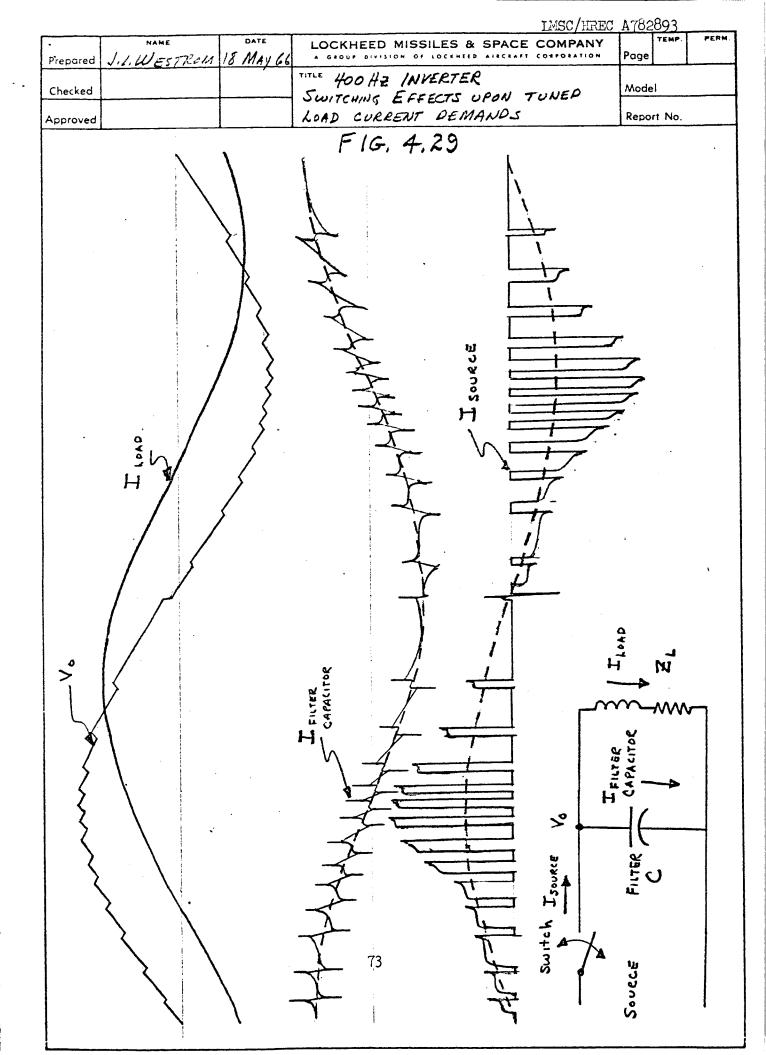

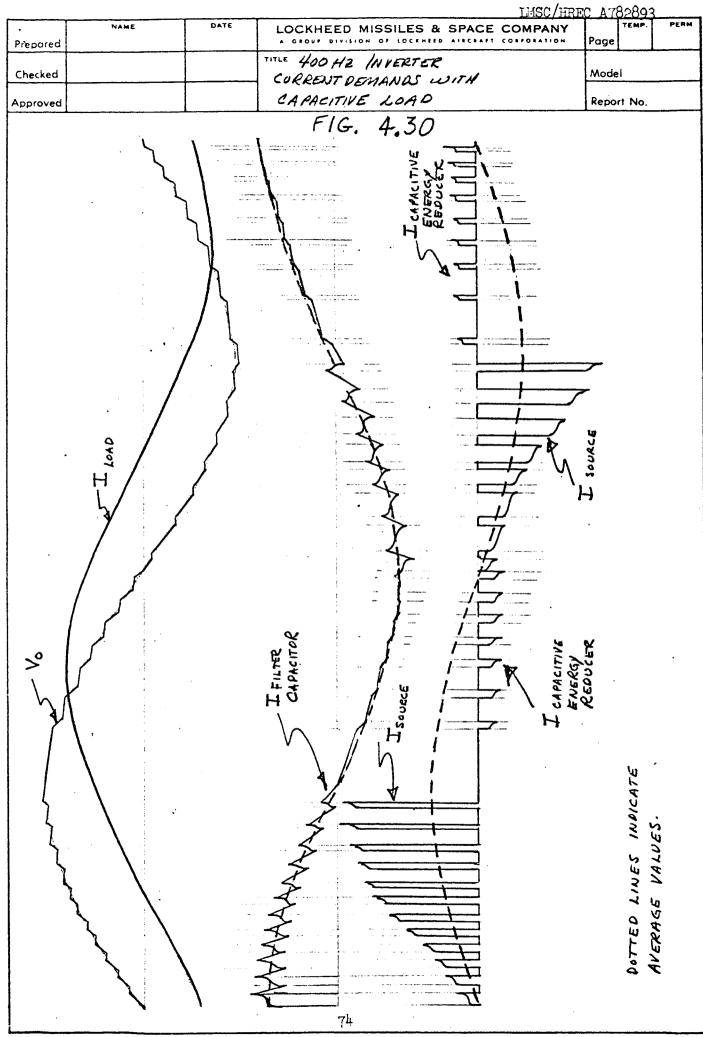

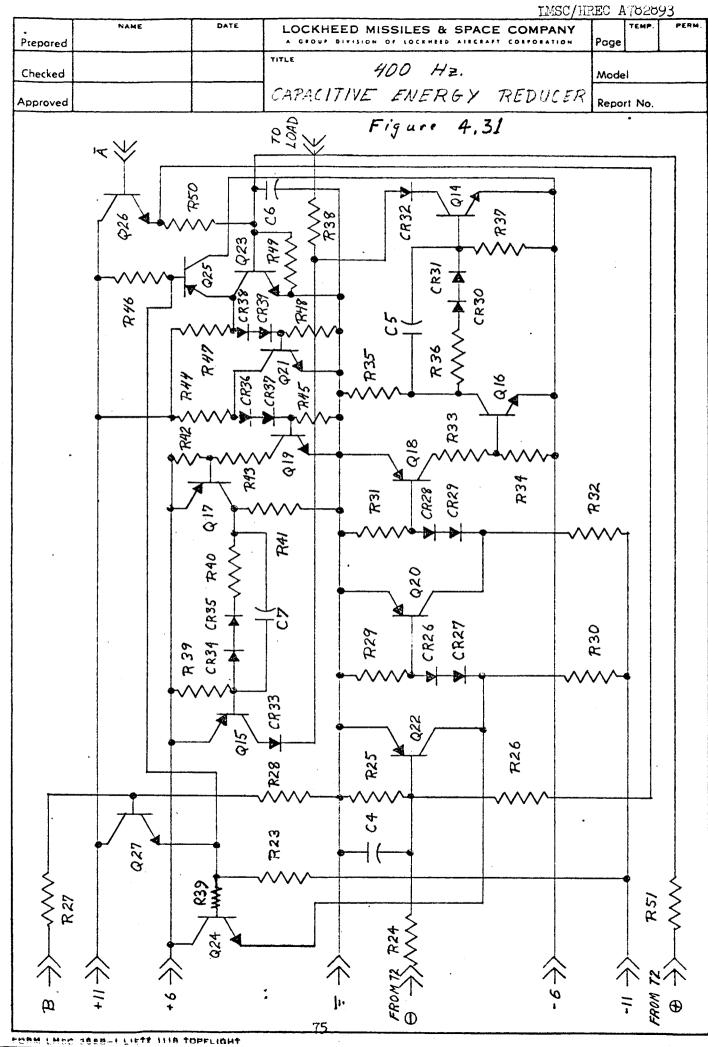

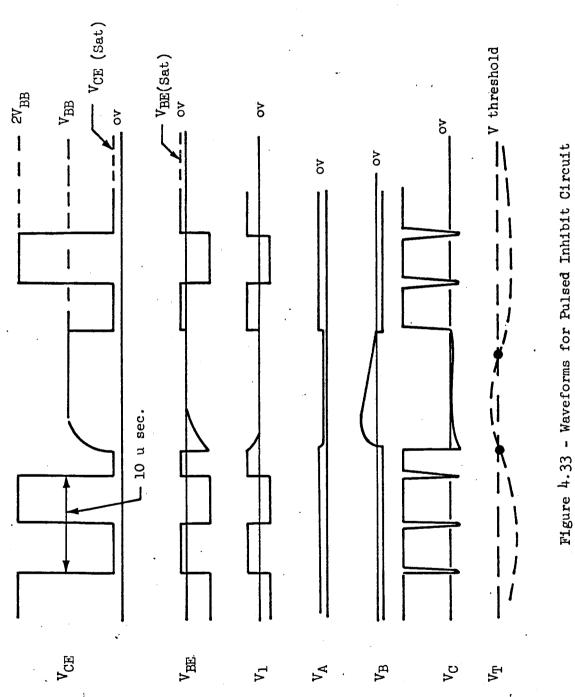

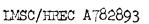

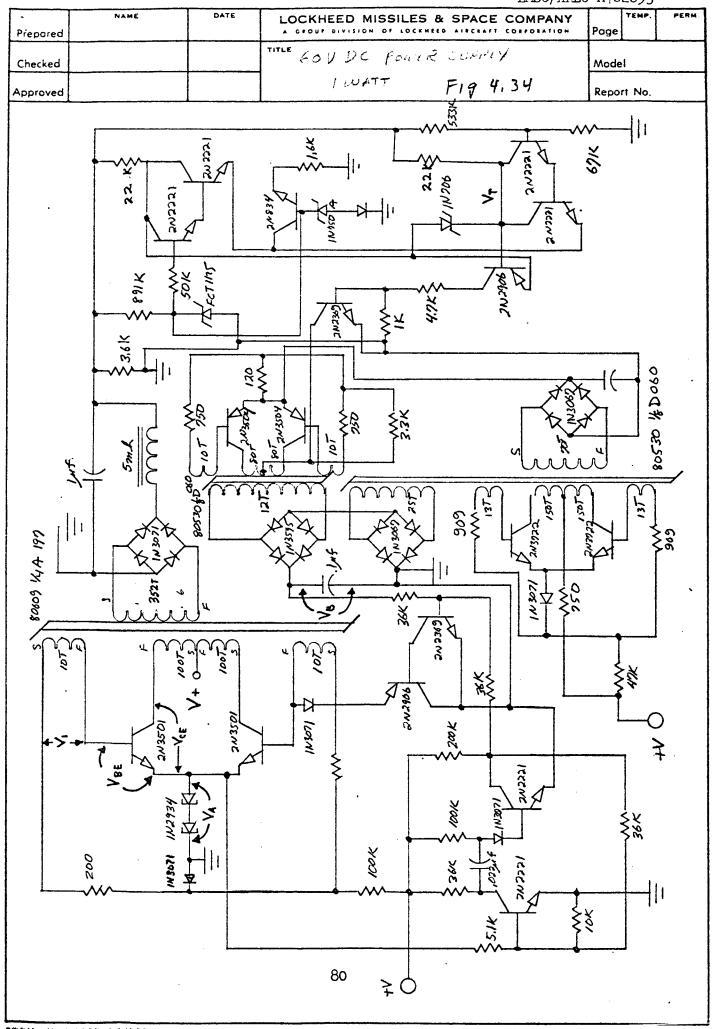

Figure 4.22