Final Report

on

STUDY IN OPTIMIZATION OF

MICROCIRCUIT DESIGN

Prepared for

National Aeronautics and Space Adminstration Cambridge, Massachusetts Contract No. NAS 12-34

Prepared by:

S. K. Ghandhi

D. N. Arden

F. L. Thiel

E. Henry

R. Wooley

Electrical Engineering Department Rensselaer Polytechnic Institute Troy, New York

July 1, 1966

# CONTENTS

| 1.    | Introduction                                            |

|-------|---------------------------------------------------------|

| 2.    | Suitable Alternatives to Gold in Silicon                |

| 2.1   | The Problem                                             |

| 2.2   | The Approach                                            |

| 2.3   | Program Effort                                          |

| 2.3.1 | Literature Survey                                       |

| 2.3.2 | Compensation Effects                                    |

| 2.3.3 | Minority Carrier Lifetime                               |

| 2.3.4 | Diffusion from a Glassy Source                          |

| 2.4   | Conclusions                                             |

| 3.    | Noise Immunity in Microcircuits                         |

| 3.1   | The Problem                                             |

| 3.2   | The Approach                                            |

| 3.3   | Program Effort                                          |

| 3.3.1 | A Study of Pulse Noise                                  |

| 3.3.2 | D.C. Terminal Characteristics                           |

| 3.3.3 | Switching Characteristics                               |

| 3.3.4 | Noise Immunity                                          |

| 3.4   | Conclusions                                             |

| 4.    | Oscillation Hazards in Asynchronous Sequential Circuits |

| 4.1   | The Problem                                             |

| 4.2   | The Approach                                            |

| 4.3   | Program Effort                                          |

| 4.4   | Conclusions                                             |

#### STUDY IN OPTIMIZATION OF MICROCIRCUIT DESIGN

#### 1. INTRODUCTION

The last three years has seen an extremely rapid growth in the technology and application of microcircuits. Much of this growth is the direct result of a heavy investment on the part of both military and civilian agencies in this area. While initial efforts were based on the hope of obtaining reduced weight and power requirements, much of the present emphasis on microcircuits is based on the desire to provide electrical functions more reliably than are obtained by their hand-wired macroscale counterparts. As such, many studies have already been made in the area of system design and organization with a view towards achieving this goal. Simultaneously, considerable work has been undertaken to study the basic physics of failure, and to obtain an understanding of the fundamental mechanisms that affect reliability.

In addition to the above studies, the development of microcircuits has taken place in a rapidly changing technological environment. Most of these technological developments have greatly increased the performance of microcircuits, while simultaneously reducing their cost.

This program is aimed at investigating problems pertaining to aspects of device technology, circuit design, and logical design which directly influence the reliable operation of a microcircuit subsystem. A program of this sort is, of necessity, interdisciplinary in nature. In contrast to the use of personnel whose specialty interests are in these areas, we have attempted to pull together at Rensselaer an organization in which each member has a broad range of interest in all these areas.

Three tasks have been selected for this effort. The specific aims of these tasks are as follows.

- a) To investigate the use of Nickel as a substitute for Gold in the fabrication of high speed microcircuits.

- b) To investigate the noise immunity of high speed saturated logic microcircuits.

- c) To investigate oscillation hazards in asynchronous sequential circuits.

These problems cover, respectively, important aspects of device technology, circuit design, and logical design which bear directly on the reliable operation of high speed microcircuit subsystems.

In this report, a brief outline of each program is first presented, with a summary of the work accomplished. Details of this work are referred to a series of Appendixes which follow. Suggestions for further work along these lines are also made.

#### 2. SUITABLE ALTERNATIVES TO GOLD IN SILICON

#### 2.1 The Problem

At the present time, gold is used extensively in the fabrication of silicon devices requiring low minority carrier lifetime. Usually, gold diffusion is the final process in fabrication, prior to metallization and encapsulation. The introduction of gold results in a number of problems:

a) Gold has an extremely high diffusion constant, about five to six orders of magnitude greater than that of the usual semiconductor dopants (Boron and Phosphorus). Thus, the gold atoms cannot be considered immobile in devices which must be stored at 300° C or higher.

- b) Gold is a noble metal. Diffusion can only occur out of the elemental metal, since all presently known gold salts dissociate at typical diffusion temperatures  $(1100^{\circ} \text{ C} 1200^{\circ} \text{ C})$ .

- c) Gold forms a cutectic with silicon at 375° C. Thus, the diffusion proceeds from a gold-silicon alloy, resulting in damage of the surface to a depth of many microns. This is of no consequence when the entire microcircuit must be gold doped. In this case, gold is applied to the side of the wafer that constitutes the substrate, and the damaged layer is mechanically removed prior to encapsulation. In some important microcircuit applications, selective lifetime reduction is necessary for optimum performance (an example of a circuit of this type is the diode-transistor logic gate.) Here, it is necessary to use the actual side of the wafer on which the microcircuit is fabricated. Since modern microcircuit devices are fabricated within the first few microns of semiconductor material, the use of gold is not feasible in this instance.

- d) Gold is metallurgically incompatible with aluminum, which is ordinarily used for making contacts to the devices in the microcircuit. At elevated temperature, gold in the presence of aluminum and silicon gives rise to the well-known "purple plague", which is a serious mechanism for semiconductor failure.

#### 2.2 The Approach

There are a number of materials that are potentially useful for reducing lifetime in silicon. Thus, almost all of the transition elements (iron, nickel, cobalt, and copper) are suitable candidates for this application. In general, all these elements exhibit one or more deep lying impurity levels in silicon, and provide recombination centers for minority carriers. These elements provide the starting point for a search for a substitute for gold. Ideally, such a substitute

would have a lower diffusion constant than that for gold in silicon, the ability to be diffused from a glass-like source which does not damage the surface of the silicon, a suitable capture cross-section so as to provide sufficient reduction in the lifetime of minority carriers, and metallurgical compatibility with the material used for making electrical contacts.

For the purpose of this program, nickel was selected as a candidate for study. The choice of this material was based on the fact that there is already in existence a body of knowledge concerning some of its properties in silicon. In addition, we have considerable past experience at Rensselaer on the utilization of nickel in microwave devices\*.

### 2.3 Program Effort

### 2.3.1 Literature Study

The program was initiated with a short survey of the existing literature on nickel in silicon. The findings of this survey are as follows:

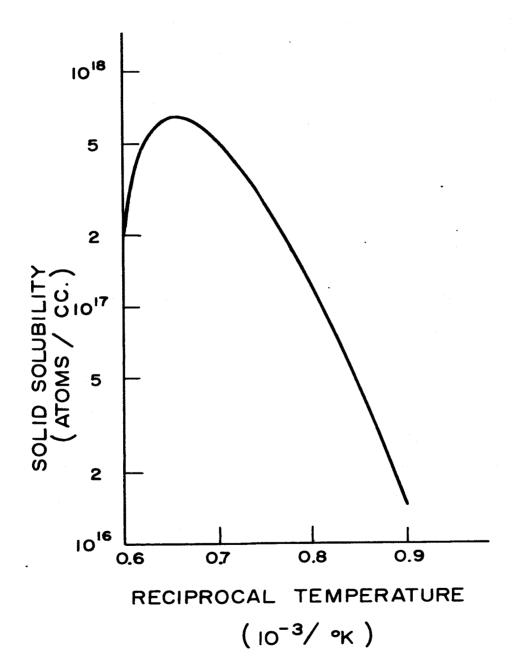

- a) Using radioactive tracer analysis, the solid solubility of nickel in silicon is seen\*\* to be retrograde in character, peaking at 5 x 10<sup>17</sup> atoms per cc. at 1260° C. Figure 1 shows this solid solubility characteristic. It should be emphasized that this curve indicates the total nickel content that can be present in silicon. In addition to electronically active nickel, this includes inactive nickel in its various forms (oxides, silicides, precipitates and interstitials).

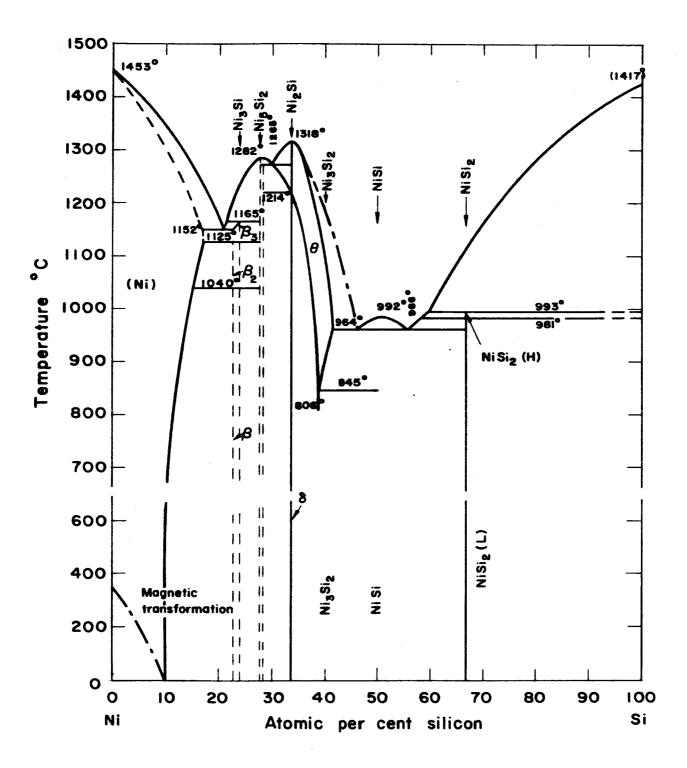

- b) Figure 2 shows the phase diagram for the nickel-silicon system. The phase indicating solid solution of nickel in silicon is not shown in this diagram. The formation of NiSi<sub>2</sub> by a peritectic reaction is of importance, and is seen to take place at temperatures above 993°C. This compound (48.90 wt % of Si)

<sup>\*</sup> Ghandhi, S. K. et al, "Impact Ionization Devices", Trans. IEEE Group on Electron Devices, ED-13, no. 6, p. 515-519, 1966.

<sup>\*\*</sup> Yoshida, M. and Furusho, K., "Behavior of Nickel as an Impurity in Silicon", Japan J. Appl. Phys., v. 3, no. 9, p. 521-529 (1964).

is formed on the surface of the wafers during our experiments, and it is expected that it is also present within the wafer to some extent.

c) Nickel diffuses interstitially into the silicon lattice, and freezes into both substitutional and interstitial sites. In addition, compound formation is present in increasingly large amounts at diffusion temperatures above 1000°C.

Consequently, we may expect only a fraction of the nickel to be electronically active in silicon. Over the range  $1100^{\circ}$  to  $1200^{\circ}$  C, the diffusion constant has been estimated\* to be on the order of  $10^{-14}$  to  $10^{-5}$  cm<sup>2</sup>/sec.

d) Nickel is weakly p-type in silicon. Hall measurements and concentration temperature dependence measurements have established two acceptor states, at  $0.35^{+}_{-}0.03$  eV. below conduction band and  $0.23^{+}_{-}0.03$  eV. above the valence band. These are both deep lying states, and can serve as centers about which the recombination of minority carriers can take place. In contrast, gold is amphoteric in nature, and provides one donor and one acceptor state in silicon.

#### 2.3.2 Compensation Effects

A study has been made of the compensation effects of nickel in silicon. The aim of this study (theoretical as well as experimental) was to determine the percentage of electronically active nickel in silicon. In this manner, it is possible to predict such device properties as parasitic series resistence when nickel is used for lifetime degredation in semiconductor devices.

A theoretical analysis was made of the compensation effects of nickel in ntype silicon. This analysis considered the statistics of multiple-charge states,

<sup>\*</sup> Alberts, J. H., and Verheyhe, M. L., Appl. Phys. Letters, v. 1, p. 19-20 (1962).

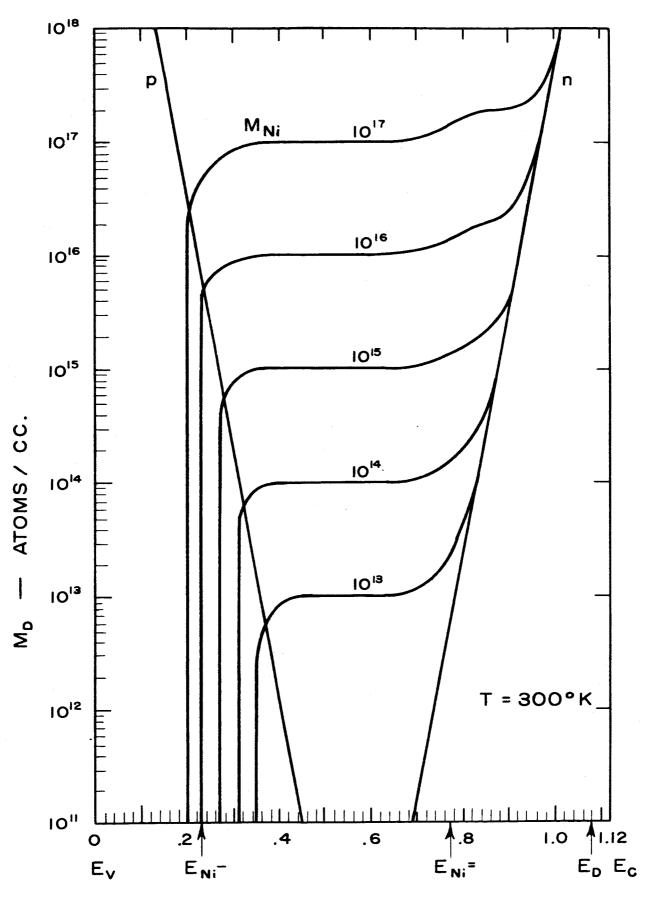

and resulted in the development of a design curve relating the majority carrier concentration both before and after nickel doping, as a function of nickel concentration. Details of this analysis are outlined in Appendix A. With the aid of this curve, it is possible to determine the shift in the Fermi level, and also the degree of resistivity change when nickel is added to n-type silicon. By correlating with actual resistivity changes determined by experiment, it is possible to use this analysis to determine the amount of nickel that is electronically active at various diffusion temperatures.

Experiments were conducted to determine the compensation effects of nickel in silicon. A number of slices of n-silicon, ranging in resistivity from 0.1 ohm-cm to 2.5 ohm-cm were used in the experimental study. This is generally considered to be the useful range of resistivities for the fabrication of semi-conductor diodes and transistors. Resistivities as high as 6.0 ohm-cm were used in a few of the experiments.

These slices were first lapped to 1000 grit and etched, and specific resistivity measurements made with a four-point probe. Next, the wafers were coated with nickel. Many experiments in the gold doping of silicon have stressed the necessity of complete removal of SiO<sub>2</sub> prior to the coating step, if uniform diffusion is desired. To this end, Wilcox\* and co-workers have noted (with gold) that electroless plating methods are superior to vacuum deposition, if the electroless deposition step is carried out in a oxide-dissolving solution. Consequently, a highly basic electroless nickel bath was used in our experiments.

It is worth noting at this point that the use of a plated diffusion source often leads to many contaminants entering the host lattice. These contaminants

<sup>\*</sup>Wilcox, W. R., et al, Jour. Electrochem. Soc., v. 111, no. 12, p. 1377-1380, 1964.

fall into two classes -- the highly soluble shallow impurities (such as phosphorous and aluminum) and the relatively insoluble deep lying impurities (such as cobalt, manganese, iron, and copper). A comparison of the widely differing diffusion constants of nickel and the shallow lying impurities shows that a lapping step, after diffusion, is effective in eliminating any trace of the latter slow diffusion impurities. In addition, a comparison of the solid solubility of nickel with that of other deep lying impurities shows that, even in the presence of the latter, the former is predominant. A final check on the freedom from detectable amounts of unwanted contaminants was seen in infrared transmission runs (performed on another program at Rensselaer) of samples doped in this manner, which were singularly free from spurious absorptions.

Diffusion runs were made at temperatures ranging from 900°C to 1250°C. In each case, the diffusion time for nickel was computed on the basis of the known diffusion constant for gold (a good guess, at best!) and a generous safety factor used to ensure uniform doping. Since infinite source diffusion was used, the doping level of the samples was considered to be that set by the solid solubility limit for that temperature.

After diffusion, the samples were rapidly quenched in air, and cleaned and etched to remove all surface contamination. At this point, the specific resistivity was again measured by the four-point probe.

Since the four-point probe technique leaves considerable margin for error, additional measurements were taken by an alternate technique, as follows:

Individual wafers of differing resistivity were selected. These wafers were quartered. The first quarter from each wafer was plated with N+ contacts, sintered, and diced. Measurements were made of the physical dimensions and resistance of individual dice after ensuring that the contacts were "ohmic". From this data,

resistivity values were obtained, and an average taken. In each case, a correction was made for the fact that the effective thickness of the wafer was reduced because of the lapped nature of its surface (prior to the application of N+ contacts).

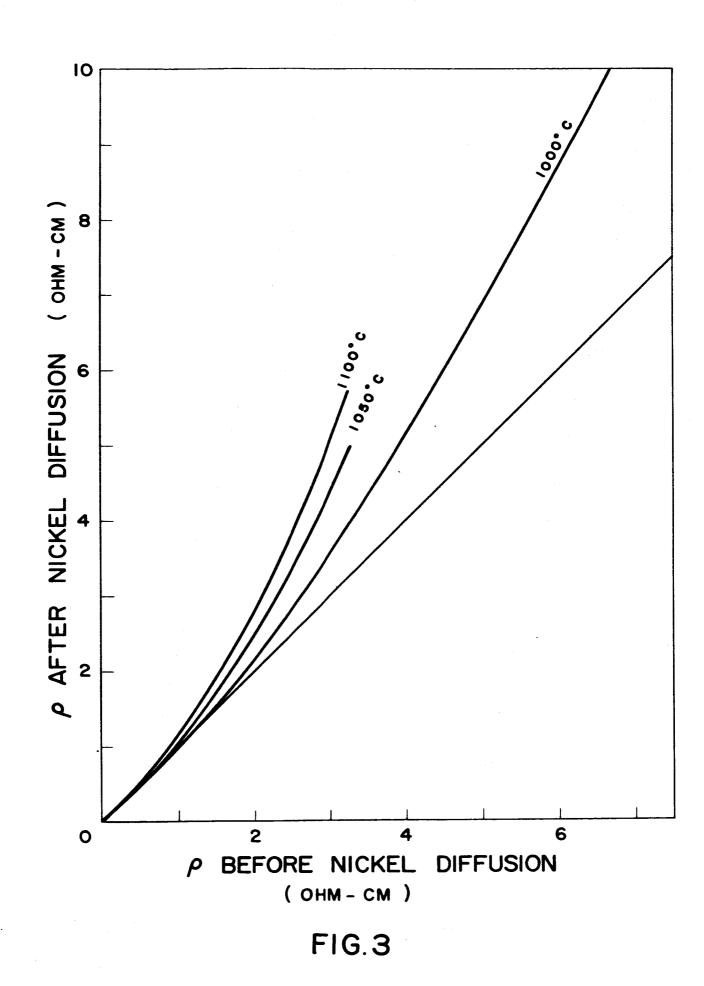

The experiment was repeated on the other quarters, after nickel diffusion at temperatures ranging from  $900^{\circ}$  C to  $1150^{\circ}$  C. The curves for resistivity before and after nickel diffusion are shown in Figure 3. Data on the  $900^{\circ}$  and  $950^{\circ}$  C nickel diffusions showed essentially no detectable increase in resistivity. Using the data from the  $1000^{\circ}$  C diffusion curve, it is seen that the resistivity is increased from 6.75 ohm-cm to 10 ohm-cm due to nickel diffusion at  $1000^{\circ}$  C. With the aid of Appendix A, we calculate an active nickel concentration of 1.035 x  $10^{14}$  atoms/cc for this case, of which 7% is singly ionized and 93% doubly ionized. With the aid of the solid solubility curve, this would indicate that about 0.10% of the nickel is in active sites for this diffusion temperature.

The fraction of active nickel in silicon is seen to fall off at higher temperatures. This would appear reasonable, because of the increased formation of compounds at higher temperatures. By 1150°C, highly variable results were noted from sample to sample. In fact, at 1250°C, the resistivity of the material after diffusion was actually found to be less than that before diffusion! No attempts were made to explain these diffusion anomalies. It was decided that further experiments would be confined to the temperature range of 1150°C and lower.

## 2.3.3 Minority Carrier Lifetime

Experiments were conducted to determine the effect of nickel doping on the minority carrier lifetime. Initially it was planned to conduct these experiments with wafers of 0.25, 0.5, 1.0 and 2.5 ohm-cm resistivities. However, time did not permit such a complete study to be undertaken, and the lifetime experiments were confined to the use of 0.5 ohm-cm wafers. It was felt that this was not an undue restriction, since there is no reason to believe that effects will be significantly different for other resistivities.

Minority carrier lifetime was measured by the recovery time method. In this method, p-n diodes are fabricated and their recovery time correlated to the minority carrier lifetime by the technique outlined in Appendix B. This approach was used because (for our range of lifetime values) it is easier to instrument than the photo-conductive decay method. In addition, the method has self-checking features on its accuracy, as described in Appendix B.

Devices were fabricated in the following manner:

- a) Wafers of 0.5 n cm resistivity were cleaned and lapped with 1000 grit. One side of the wafers was wax masked and the wafers etched to remove surface damage. A relatively slow etch (HF-HNO<sub>3</sub>-CH<sub>3</sub>COOH system) with an etch rate of about 10  $\mu$  per minute was used.

- b) The wafers were now pre-deposited with  $B_2O_3$  for 10 minutes at  $1175^{\circ}$  C, a closed box technique being used for this step.

c) Drive-in was conducted at  $1175^{\circ}$  C for varying periods of time. In each case, this comprised a half hour period in pure oxygen, with the rest of the period in a 97% N<sub>2</sub>, 3% O<sub>2</sub> gas mixture.

Initially, wafers were diffused to a junction depth of 10  $\mu$ . In later experiments, however, the diffusion depth was reduced to under 5  $\mu$ . This had the advantage of considerably reducing diffusion time, and thus reducing the possibility of contamination during the diffusion run.

d) After drive-in, the wafers were washed in HF to remove the boro-silicate glass, and the reverse side was lapped and nickel-plated. Each wafer was quartered; the nickel was stripped off one of these quarters, while the other three were diffused at different diffusion temperatures. In some of the experiments, diffusion temperatures were nominally 1150° C, 1100° C and 1050° C while in yet others, diffusion temperatures of 900° C, 950° C and 1000° C were used. In this manner, the range from 900° C to 1150° C was covered. Adequate time was allowed for the diffusions in each case. Experimental data showed that the diffusion time was relatively unimportant in all cases as long as it was in excess of half an hour. In some of our early experiments, nickel diffusion was done while the boro-silicate glass was still remaining on one side of the wafer. This was found to give extremely variable results, especially for high diffusion temperatures. Often, there was noted a strong gettering effect\* at these temperatures, (1000° C upwards) and the procedure was discontinued. All the test data on minority carrier lifetime was thus taken on wafers which were nickel diffused from one side, and free from boro-silicate glass on the other.

<sup>\*</sup> Ing, S. W., et al, <u>Jour</u>. <u>Electrochem Soc.</u>, v. 110, no. 6, p. 533-537, 1963.

This ensured the absence of competing mechanisms of nickel diffusion and nickel gettering, and lead to consistent experimental results.

- e) After diffusion, the wafers were air quenched, and back-lapped to remove the nickel-silicon interface region. The upper face of the wafer (in which the boron diffusion was conducted) was vacuum coated with aluminum. The metallized wafers were diced and sintered, and individual dice used to make devices.

- f) The individual dice were bonded to TO-5 headers using 0.25% Sb-doped gold-germanium eutectic preforms. Considerable trouble was experienced with this fabrication step. The problem was ultimately traced to the fact that our die-bonder (home-made) had no provisions for scrubbing the die on the header to facilitate the removal of surface oxides. The problem was eliminated by using the following subroutine:

After sintering, the individual dice were bedded, aluminum face down, on a lap block coated with wax. These dice were lapped for about a minute in 1000 grit, and the freshly lapped dice stored in trichloroethylene (TCE) prior to their use. In addition, the headers were boiled in TCE for five minutes prior to the bonding operation. This series of steps resulted in a consistently successful bonding operation.

- g) A nail head bonder was used to make the thermo-compression bond to the wafer. Three-mil gold wire was used, with a preheated capillary. No problems were encountered here, once operator skill was developed. The other end of the bonding wire was spot welded to the post in the TO-5 header.

- h) Devices were next etched in CP4. Since the nail head bond is made with gold wire, this served as a mask, while the CP4 etched away the exposed

material. In this manner, a mesa structure was produced. Early devices, with a 10  $\mu$  junction depth, required rather heavy mesa-etching. Often, this resulted in undercutting of the aluminum layer below the gold bond, with resultant separation of the bond from the device. This problem was not experienced in the 5  $\mu$  structures, where the etching cycle was considerably shorter.

i) After etching, the devices were boiled in deionized water and trichloroethylene, and baked out at 250°C for a short interval of time. Considerable

trouble with surface phenomena was encountered at this juncture. The results

were quite erratic, with leakage currents ranging from under 1 na to values

in excess of 50 µa! In addition, devices with excessive leakage showed

excessively low values of breakdown voltage. Since this problem was experienced on over 50% of the devices, experiments were conducted to improve the

yields leading to the following processing steps which were found to be

successful:

The devices were rinsed in dilute hydrochloric acid for a few seconds to remove the unmasked aluminum layer. After a brief rinse in deionized water, the devices were etched for 30 seconds in CP-4. Fresh etchant was used with each device. Devices were rinsed in de-ionized water and then air dried. The devices were boiled in Transcene (a proprietary cleaning agent similar to C  $\text{Cl}_4$ , available in an ultrapure grade). A 30 minute bake-out was provided at  $250^{\circ}$  C.

As a result of the above processing, over 80% of our devices were satisfactory (leakage current ≤ 10 na at 10 volts reverse bias). Consequently, no further attempts were made to improve upon this procedure.

- j) With a number of devices, angle lap and staining techniques were used to display the junction, which was typically 10  $\mu$  deep in the initial diffusions, and 4  $\mu$  deep in the more recent devices.

- k) Diodes, with "satisfactory" reverse characteristics (under 10 na at 10 volts) were next checked for capacitance at three values of reverse bias (3, 4.5 and 7.5 volts). A plot of the C-V curve showed that the diodes were graded (n = 1/3). The capacitance data allowed checking the comparative areas of the different diodes. Only slight variation was seen from device to device (Values of C at 7.5 volts ranged from 4.95 pf to 3.81 pf). Using design curves\* for the capacitance of a graded junction, this would indicate junction areas from 105 sq. mils to 81 sq. mils.

For each device, the breakdown voltage was noted as well as the nature of the breakdown characteristics (i.e. hard vs. soft breakdown). In addition, the forward voltage drop was also measured at two values of forward current (10 ma and 50 ma) in order to determine if the forward parasitic resistance had been increased by the introduction of nickel.

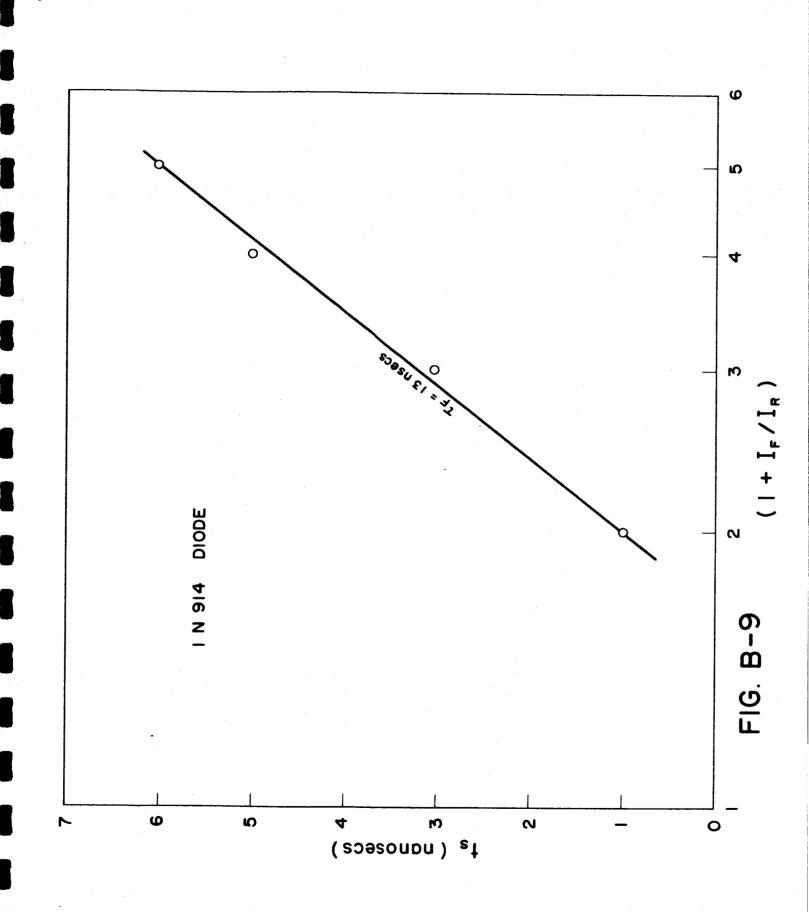

At this point the diodes were tested for reverse recovery in a special test jig that was used in conjunction with a sampling oscilloscope. Details of the actual measurement procedure and its theoretical basis are given in Appendix B. Included are also examples of the application of this method to representative devices nickel-doped at temperatures from 900°C to 1150°C. For comparison, data on a high speed gold doped diode (type 1N914) is also shown.

<sup>\*</sup> Warner, R. M. and Lawrence, H., <u>Bell System Tech. J.</u>, vol. 39, p. 389-404 March, 1960.

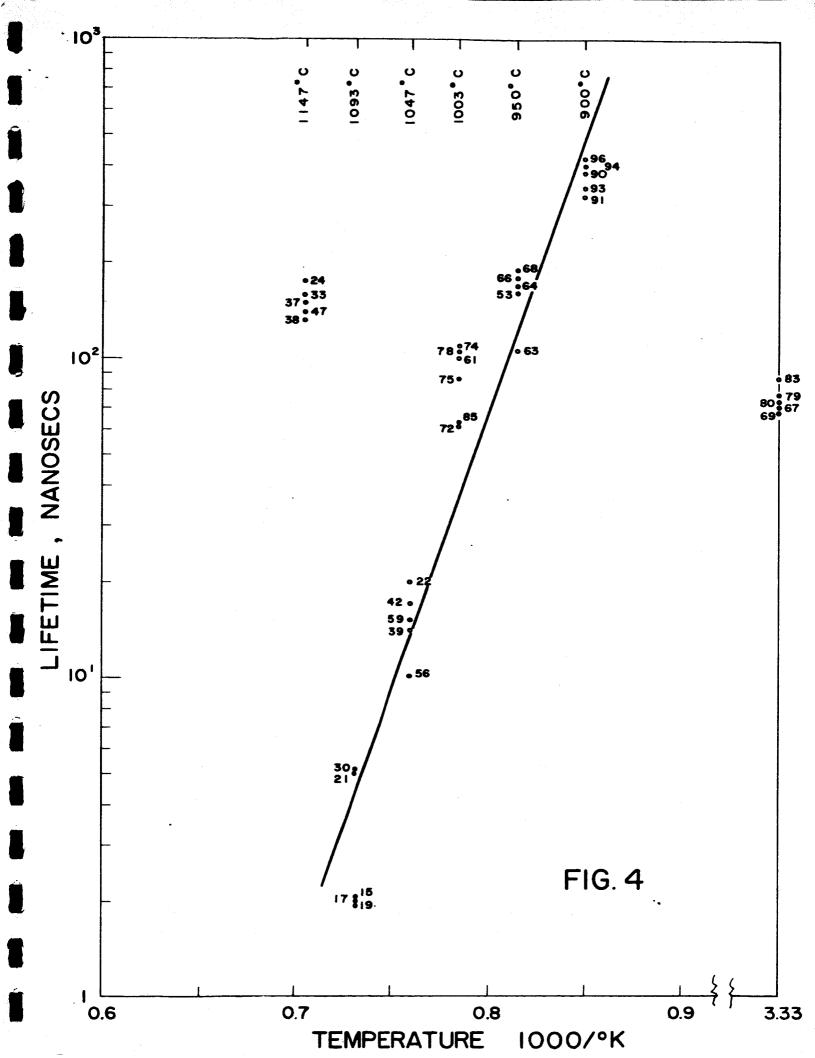

Figure 4 shows the results of lifetime measurements on various devices that were nickel diffused over the range of 900°C to 1147°C. The individual points correspond to separate devices, with the device number marked in each case. In this manner, the degree of spread in the data is shown in addition to the magnitude of the lifetime.

The following points of interest are noted:

- a) The initial material (rotated Czochralski-grown n-silicon) had a lifetime of about 70 nanosecs.

- b) On nickel diffusion at 900° C for one hour, the lifetime rose to 400 nanosecs. This is due to the gettering action\* of initially present deep lying impurities (such as copper and gold) by the nickel. Since the solid solubility of active nickel is considerably less than that of these impurities, the lifetime enhancement effect due to their removal predominates over the lifetime degredation effect due to nickel diffusion.

- c) With increasing temperature, the minority carrier lifetime falls until a diffusion temperature of 1093°C is reached. This is due to the fact that increasingly large amounts of active nickel are present at higher temperatures.

Bakanowski and Forster\*\* have shown that, for gold in low resistivity silicon, the lifetime is inversely proportional to the number of gold centers. We do not find this to be the case with nickel, and ascribe this to the fact that nickel is a two-level recombination center, and also to the fact that nickel provides initially a gettering action for impurities already present in the silicon. A best-fit straight line is drawn through the points over the range 900° C to 1093° C.

<sup>\*</sup> Silverman, S. J. and Singleton, J. B., <u>Jour. Electrochem. Soc.</u>, v. 105, p. 591, 1958.

<sup>\*\*</sup> Bakanowski, A. E. and Forster, J. H., Bell System Tech. Jour., v. 39, p. 87 (1960).

d) Diffusion at 1147°C results in a rapid increase in lifetime, to a value close to that for the undoped material. This anomaly was verified on a number of devices from different wafers, and has been ascribed to the fact that a large amount of the nickel is essentially combined with the silicon to form nickel silicides, having a lower capture crossection to minority carriers than that of the original active nickel.

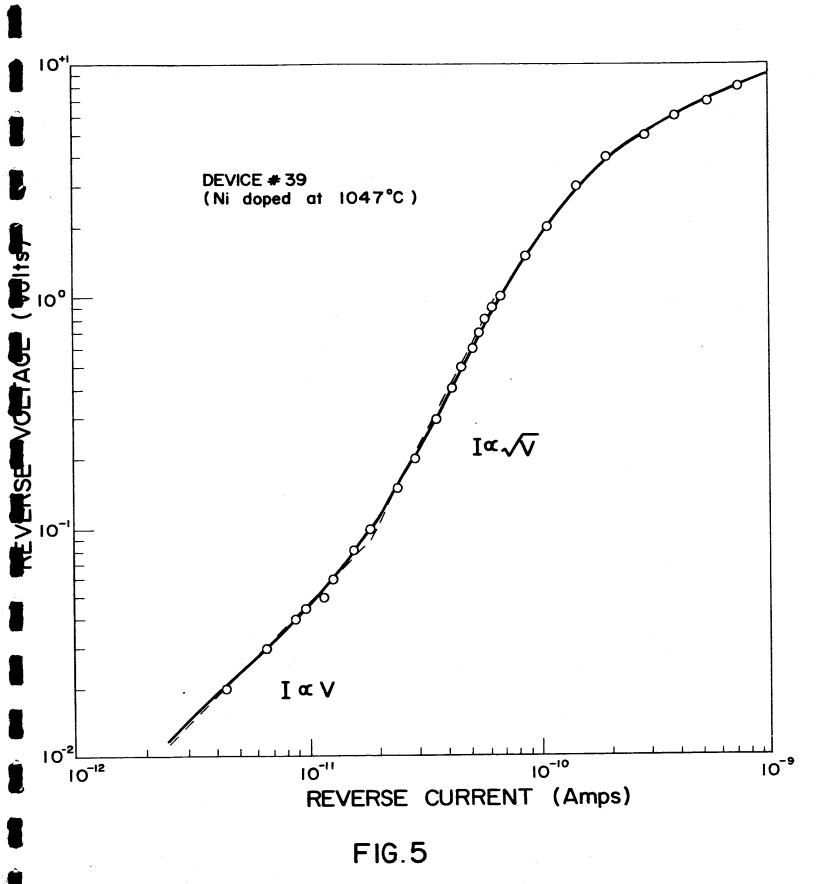

It was not possible to show the manner in which the leakage current varied with the nickel doping level. This was due to the fact that this current (in our mesa structures) was often dominated by the presence of surface states. The leakage current was measured on some devices which were heavily doped with nickel, in which surface effects appeared small (i.e., diodes with sharp breakdown characteristics, in the neighborhood of 60 volts). Figure 5 shows the leakage current of a representative diode of this type, nickel diffused at 1047° C. As expected, this leakage current is predominantly due to charge generation\* in the depletion layer. This charge generation takes place at various deep lying sites in the forbidden band and is thus enhanced by the presence of nickel. In passing, it should be noted that this leakage current is about 100 times as large as what would be expected for a typical silicon p-n junction diode that was not nickel doped.

## 2.3.4 <u>Diffusion from a Glassy Source</u>

A number of attempts were made to diffuse nickel from a glassy source. These met with no success at first. However, some success was achieved in our later experiments. These experiments have shown that it is possible to obtain a reasonable quality glass containing nickel on the surface of

<sup>\*</sup> Sah, C. T. et al, "Carrier Generation and Recombination in PN Junctions and PN Junction Characteristics", Proc. IRE, v. 45, p. 1228-1243 (1957).

a silicon wafer. It has also been shown that this glass (NiO-V<sub>2</sub>O<sub>5</sub> system) can be removed without apparent surface damage to the silicon. In addition, compensation effects have been noted when this glass was used as a diffusion source. Details of these experiments are provided in Appendix C, with suggestions for additional work that is required before a completely satisfactory process can be considered to have been developed.

### 2.4 Conclusions

This study has investigated the feasibility of using nickel as a substitute for gold in silicon. It has been shown that

- a) Nickel can be used to reduce lifetime to the level normally required in high speed switching devices. However, the behavior of nickel in silicon is considerably more complex than that of gold due to effects at both extremes of the diffusion temperature range. In addition, the lifetime degredation effect is a more strong function of temperature than for gold, leading to a more severe control problem during the diffusion step.

- b) Compensation effects of nickel in silicon are not of importance in high speed switching devices where low resistivity materials are used (≤ 0.5 ohm-cm). This is true, not withstanding the fact that the active nickel is doubly ionized in these materials.

- c) Nickel can be diffused from a glassy source. In addition, this source can be stripped (with difficulty) without apparent damage to the silicon wafer. Thus, it should be possible to diffuse nickel from the top surface of a silicon microcircuit.

#### 3. NOISE IMMUNITY IN MICROCIRCUITS

## 3.1 The Problem

The microcircuit, with its small size, low power dissipation, and high reliability, has already found wide usage in complex subsystems that were considered impractical a few years ago. The present trend to the integration of even more complex subsystems places an increasing emphasis on the design of microcircuits that can be easily combined in large ensembles. Most present day microcircuits are designed with the emphasis placed on the attainment of performance parameters. These include such terms as propagation delay, fan-in, fan-out, and power dissipation. Of equal (but often considered secondary) importance are those characteristics which will determine the ability of a single circuit to be used in a variety of environments with a minimum of "hand trimming" and "de-bugging". The most important of these characteristics is the ability to have a high degree of immunity to noise, in both the "on" and "off" states. This ability will reduce, or eliminate, the need for attention to precise clocking and phasing, as well as the need for elaborate shielding and grounding.

The saturated logic gate is today the most widely used building block for microelectronic computing elements. It is operable over a wide range of temperatures and parameter spread; while not as fast as its non-saturated counterpart, it operates at lower power dissipation levels, and does not amplify signals (both wanted and unwanted) in their passage through the gate.

At low operating speeds, the noise immunity of a saturated gate can be made arbitrarily high by increasing the threshold at which the gate operates. This technique results in increasing the propagation delay through the gate, but this increase can be avoided by using an inherently faster device in the gate design.

With high speed gates (≤ 4 nsecs propagation delay), it is necessary to effect a trade between the noise immunity and the propagation delay. Thus, it is necessary to critically determine the noise capability of the gate, taking into consideration the nature of the noise signals to which it is subjected.

### 3.2 The Approach

In this program we have concentrated our study on the saturated transistor-transistor-logic  $(T^2L)$  gate. This gate is becoming recognized as the one that has the greatest potential for high speed operation in the saturated mode. Over the last two years, an increasing number of manufacturers have been developing circuit lines using this type of gate.

There are essentially two types of "noise" that can cause malfunction in a digital circuit. The first of these, commonly referred to as d-c noise, is characterized by its presence in the form of pulses that are so wide that they present, in essence, a d-c input to the gates. Such pulses are commonly associated with power supply transients and resistively coupled paths. The second type of noise is known as pulsed noise. Far more frequently encountered, this noise consists of low duty cycle pulses, and is capable of being generated or picked-up whenever short rise-time signals are being transmitted or processed.

In this study we have attempted to evaluate these sources of pulsed noise in microcircuits, and determined the manner in which this noise pick-up can cause a malfunction in the basic  $T^2L$  gate. In addition, we have shown a correlation between this pulsed noise immunity and the internal device parameters of the gate. Finally, we have shown that it is possible to design the gate for a specified value of pulsed noise immunity without unnecessarily compromising its performance.

## 3.3 Program Effort

## 3.3.1 A Study of Pulsed Noise

A detailed study of pulsed noise has been undertaken. Since the transistor is essentially a charge controlled device, this study has concentrated on determining the charge content of the various forms of noise that may be encountered. Details of the study are outlined in Appendix D.

The following conclusions have been made concerning the nature of noise signals generated in digital circuits:

- a) The most serious forms of pulse noise (having wide pulse widths and high charge content) are those generated in coupled interconnection paths between circuit boards, and those caused by mistiming.

- b) Other noise sources are of secondary importance. Thus, if the logic stage is capable of tolerating noise signals of the former type, it is not necessary to consider the latter.

### 3.3.2 D.C. Terminal Characteristics

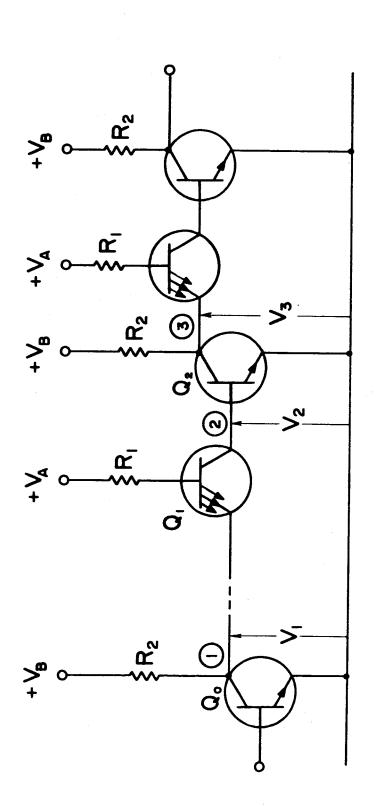

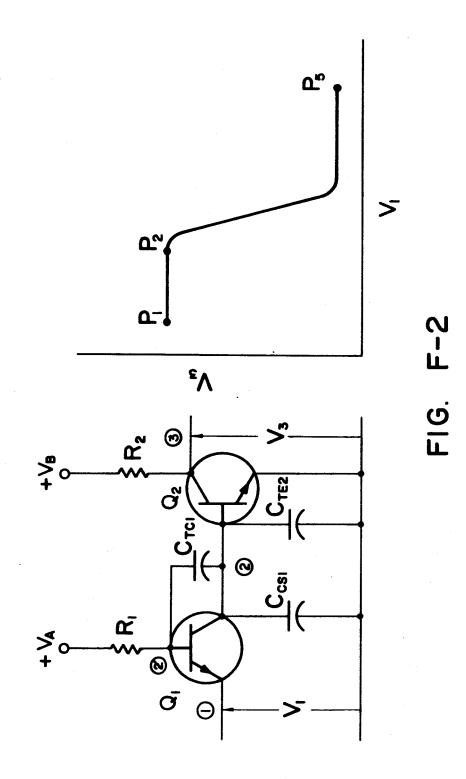

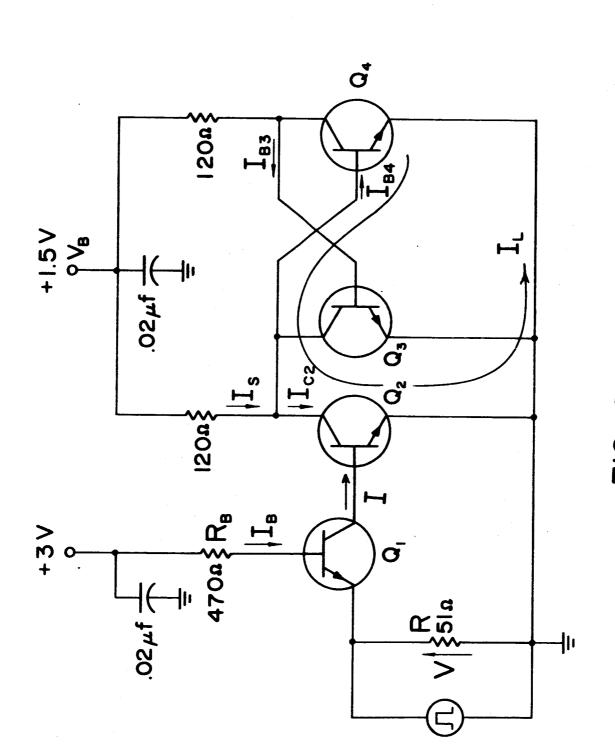

A T<sup>2</sup>L gate was designed and constructed using high speed transistors (2N709) for both the coupling and inverting elements. Under test, this gate was operated with a propagation delay of 3-4 nsecs into a fan-out of 4. This gate was used as the vehicle for test in the experiments.

An elementary analysis was made of the input and transfer characteristics of this gate. Correlation with the experimentally measured characteristics was sufficiently close so that a more detailed analysis was not found necessary. This analysis, together with the experimental data for this gate, are outlined in Appendix E. Using the analysis, the d.c. noise margin of the gate was obtained.

The noise immunity of a gate of this type is commonly expressed by manufacturers in terms of this d-c transfer characteristic (10% by some and 50% by others). This is quite misleading, since it does not take into account the nature of the malfunction signals that are presented to the gate, and also since it refers to a region of the gate where the characteristics are rapidly changing.

#### 3.3.3 Switching Characteristics

A dynamic analysis was made of the switching characteristics of the gate in order to determine which internal parameters are of significance in computing the propagation delay. This analysis is outlined in Appendix F. It is seen that the turn-on delay is a significant factor in the propagation delay. This term is controlled by the parasitic capacitance at the base of the inverter transistors, and by the base

resistance of the coupling transistor through which it is charged.

In addition, it is seen that the storage time of the inverter transistor  $\mathbf{Q}_2$  is controlled by the parasitic resistances associated with the collector of  $\mathbf{Q}_1$  and  $\mathbf{Q}_0$ , and with the base spreading resistance of  $\mathbf{Q}_2$ . The expression for fall time is complicated since the equation governing this parameter is nonlinear\* due to the fact that the base is essentially shorted to ground (through the coupling transistor and the previous inverter stage).

### 3.3.4 Noise Immunity

The noise immunity for the gate was measured, by feeding into its input narrow pulses with short rise times. A mercury relay pulse generator was used for this purpose, the pulse length being set by means of delay lines of variable length. At the outset, there was considerable difficulty in determining the magnitude of the output signal that should be interpreted as a malfunction indication. (This problem is especially serious with fast rise time pulses where the effect of Miller capacitance in the transistors results in an output for <u>all</u> values of input signal.)

It was decided that a digital indication of malfunction should be used. With this in mind, a sensitive, high speed unloaded flip-flop was hung on the gate to provide this information.

Experiments conducted with this circuit showed that the malfunction signal was a critical function of the malfunction indicator as well as of the gate under test. Accordingly, it was decided that a malfunction indicator, made with gates identical to the one under test, would have

<sup>\*</sup> Thiney, A. "Rise and Fall Times of Transistors in Switching Operation Regardless of the Driving Source Impedance", IEEE Trans. on Elec. Comp., vol. EC-13, p. 616-620, 1964.

significant advantages over the previous indicator. Thus,

- a) The noise immunity would now be only a function of the gate (or rather, gates) under test.

- b) The results would specify a more functional value of noise immunity. Thus, we consider malfunction to have occurred when the input noise pulse to a gate is sufficiently large so as to transmit logical information to the succeeding stages. In this manner, we define the noise immunity of a gate in terms of its ability to prevent the flow of error-causing signals to successive circuits.

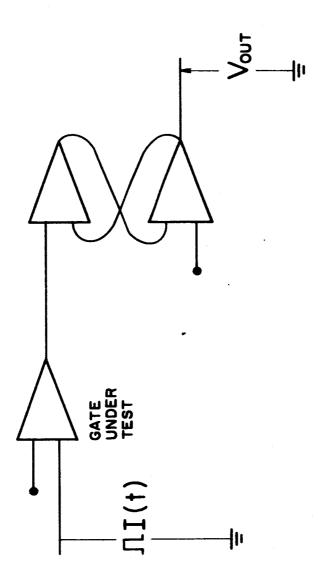

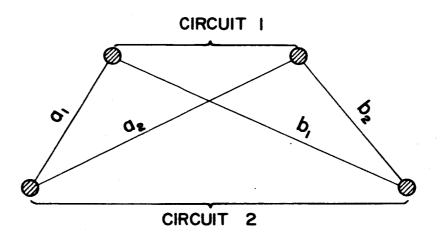

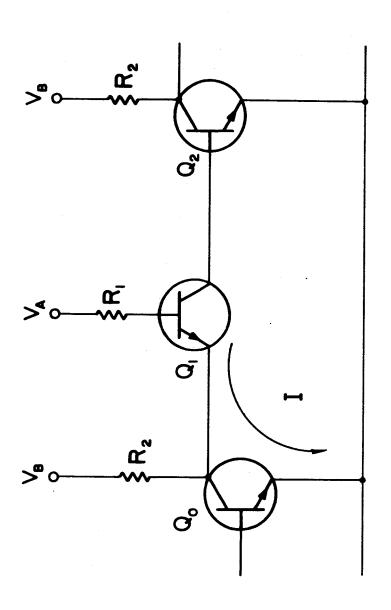

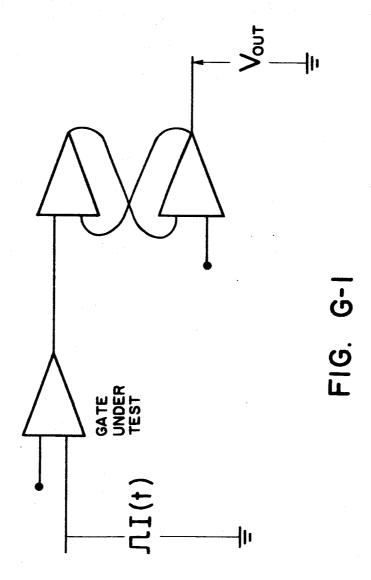

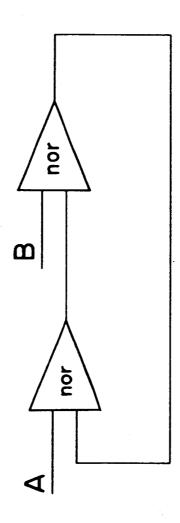

Our experiments were conducted with discrete components, to which parasitic capacitances were added whenever necessary. If actual microcircuit gates are being tested, the measurement of pulse noise immunity should be done by interconnecting them at their terminals, without the necessity of making internal connections. The advantages of this approach for evaluating competitive microcircuits are immediately apparent. The measurement scheme thus takes the form shown in Figure 6.

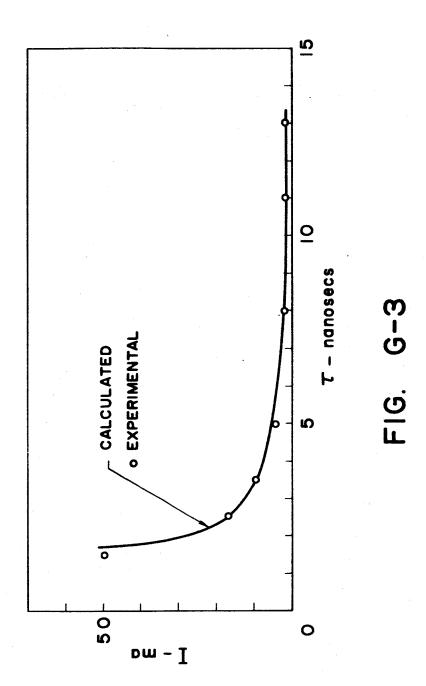

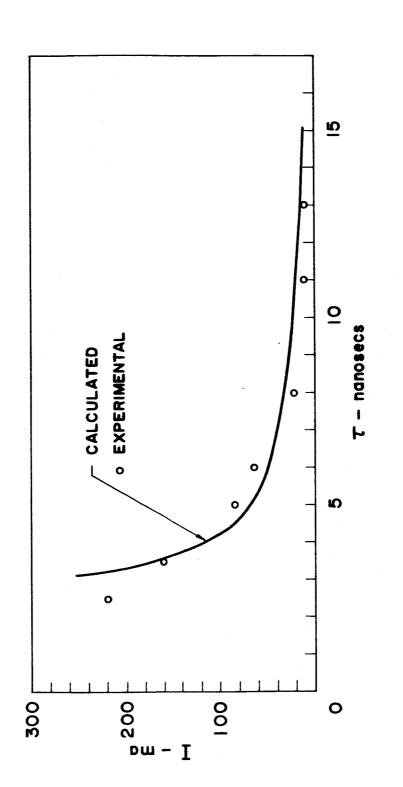

The analysis for the pulse noise immunity of the T<sup>2</sup>L gate is detailed in Appendix G. Here, expressions are derived for the input current as a function of pulse width required to cause malfunction, and excellent correlation is seen to exist between theory and experiment. The experiment was repeated for the same circuit, using 2N706 devices (which are considerably slower) for the individual elements. Again, the results were predictable from the theoretical analysis.

The analysis shows that  $\gamma$  , the width of the pulse required to cause a malfunction, is given by

$$\Upsilon = K/I + \Upsilon_0$$

where  $\pmb{\gamma}_{o}$  and K are constants for a given circuits, and I is the current. In addition, it is shown that K is a function of the rise time alone, while  $\pmb{\gamma}_{o}$  is a function of turn on delay and storage time.

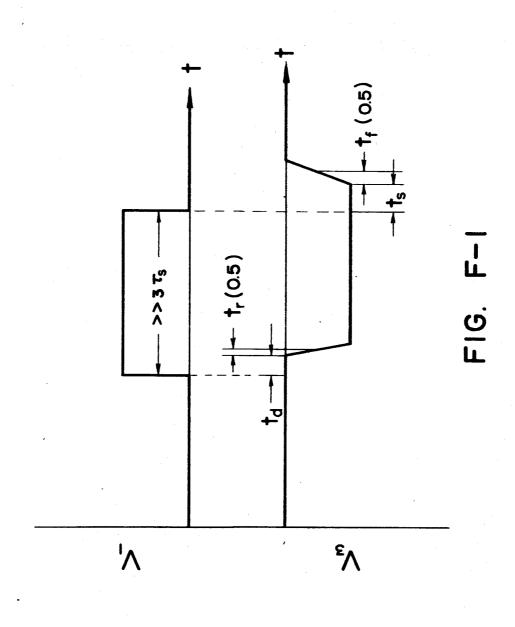

The circuit has essentially infinite pulse immunity when the input noise pulse width is less than the sume of the turn on delay and the storage time. On the other hand, the propagation delay through the stage is given by

$$t_{pd} = t_{d} + 0.5 t_{r}, \text{ or}$$

$t_{pd} = t_{s} + 0.5 t_{f}.$

whichever is larger\*. Thus, there is some degree of independence between these parameters, so that there is design freedome in the choice of these two circuit properties.

It is clear that the proposed method of test can be directly applied, if required, to a measurement of the d.c noise margin of the gate.

Because of the feedback action of the cross-coupled gates, the transfer function has an abrupt transition region, and there is thus no problem of interpretation in computing this data from the curve.

## 3.4 Conclusions

In this program, a study has been made of the sources of spurious noise signals in high speed switching circuits using saturated logic gates. A new method has been proposed for characterising the performance of such gates to noise pulses. This method involves the direct use of three interconnected gates without any additional circuitry, and provides a functional determination of the noise immunity characteristics of the gate.

<sup>\*</sup> Industry practice is to average these two. This, of course, always gives a more optimistic value for  $t_{\rm pd}$ .

The noise immunity has been calculated as a function of device parameters. This calculation has been experimentally verified for both "fast" as well as "slow" gates. It is shown that many of the parameters that govern the propagation delay through the gate also control its noise immunity. On the other hand, there is some freedom in designing a gate with optimum noise immunity for a fixed propagation delay. This may be attained by designing the circuit with a short rise time, and relatively long turn on delay and storage time.

## 4. OSCILLATION HAZARDS IN ASYNCHRONOUS SEQUENTIAL CIRCUITS

### 4.1 The Problem

It has been observed that some sequential circuits constructed from very fast nor gates ( = 4 nanosecond delay) will oscillate when inputs are changed simultaneously. In synchronous circuits this difficulty does not arise since a single clock transition is used to initiate computation of the next state. However, at the interface between computer and external device (i.e. a radar) such synchronization is not possible. It is of considerable interest to determine if such problems can be eliminated by proper design or if fundamental difficulties are involved.

## 4.2 The Approach

Many special circuits have been investigated and in all cases no design was found which eliminated the possibility of oscillation when the circuit required that a terminal state depends on the sequence of changes of a pair of input variables. It was therefore decided to see if it could be proved that such a design was impossible.

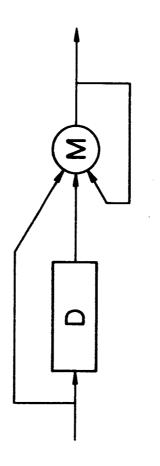

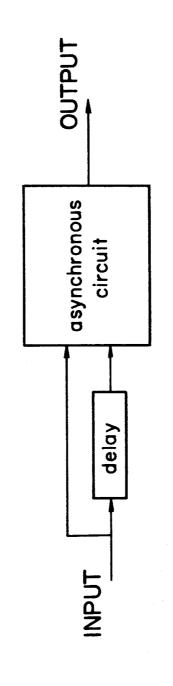

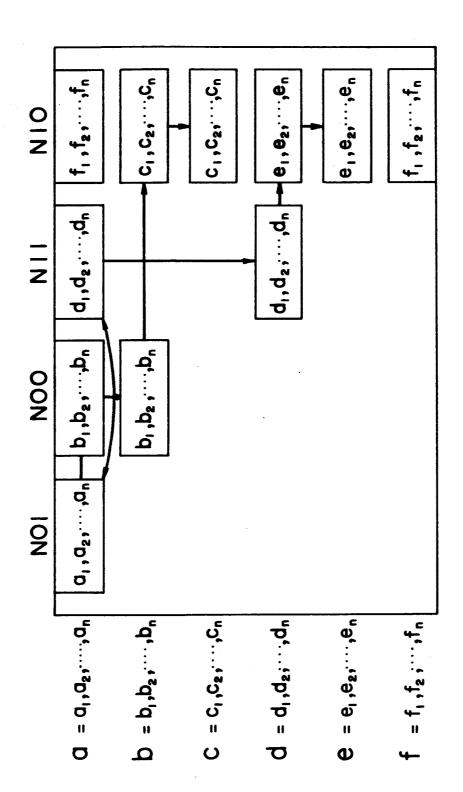

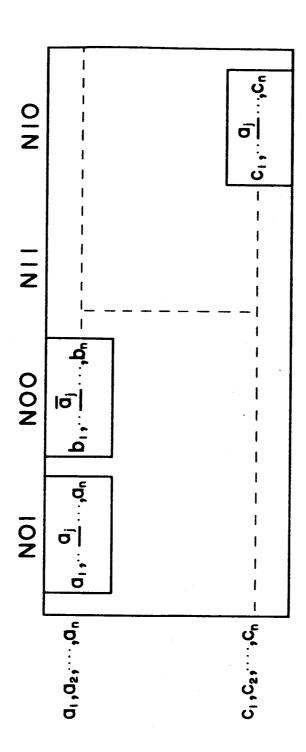

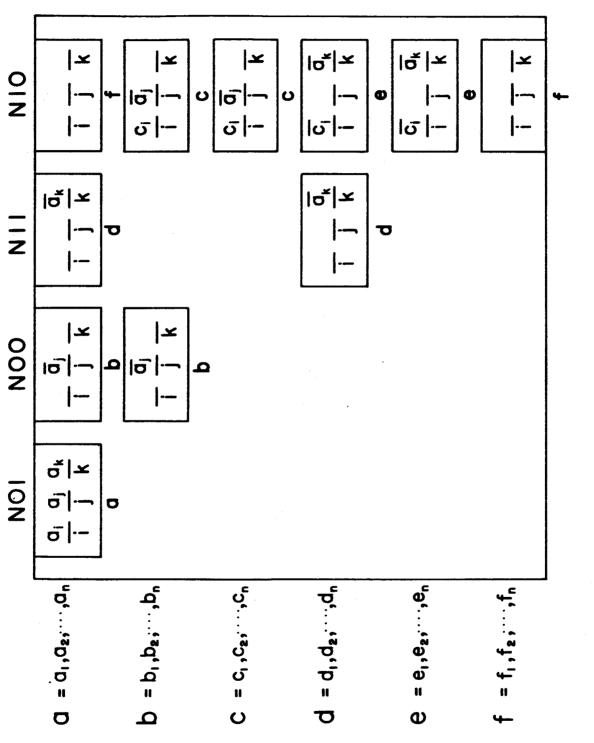

### 4.3 Program Effort

Two theorems have been proved which show, under assumptions usually valid in the design of sequential circuits, that such a design is in fact impossible without the use of frequency band limiting devices in the feedback loops. The first theorem shows that no state assignment can be found for which the combinational logic is hazard free when simultaneous input changes are allowed. The second theorem indicates that even with hazard free combinational logic, correct sequential action places strigent limitations on the narrowness of pulses which can be passed through the feedback connections.

A detailed discussion of the background of the problem and the statement of the theorems is given in Appendix H, and their proofs in Appendix I.

### 4.4 Conclusions

It has been concluded that asynchronous circuits cannot be reliably constructed from very fast logical devices if simultaneous input changes are possible, unless some method is available for eliminating short pulses in the feedback loops. The inertial delay of Unger is one element that can be used for this purpose. However, it has been shown that the realization of this device as described by Unger is itself subject to the hazards described here.

### Appendix A

# Statistical Consideration of Nickel as an Impurity in n-type Silicon

In order to find the free carrier densities which would occur if a sample of n-type silicon were doped with nickel, one needs to know only the original donor concentration M<sub>D</sub> and the energy levels of nickel in silicon. From this information the Fermi level, and thus the carrier densities, of the nickel-doped sample can be obtained statistically.

Let  $M_{N\bar{1}}$  be the total concentration of active nickel,  $M_{N\bar{1}}$  be the concentration of nickel in the double acceptor state, and  $M_{N\bar{1}}$  be the concentration of nickel in the single acceptor state. It is assumed that the density of nickel states is low, so that interactions between them can be ignored. In addition, considerations of degeneracy can be neglected, since these are only important in determining the limiting resistivity of the doped material.

Using the arguments of Shockley and Last\*, it may be shown that

$$M_{N_{1}^{-}} = \frac{M_{N_{1}^{-}}}{1 + \exp \left[ (E_{N_{1}^{-}} - E_{F})/kT \right] + \exp \left[ (E_{N_{1}^{-}} + E_{N_{1}^{-}} - 2 E_{F})/kT \right]}$$

$$M_{N\bar{1}} = \frac{M_{N\bar{1}}}{1 + \exp \left[ (E_{N\bar{1}} - E_{F})/kT \right] + \exp \left[ (E_{F} - E_{N\bar{1}})/kT \right]}$$

Writing the charge neutrality equation, assuming that all of the shallow donor states may not necessarily be ionized, we obtain

$$p - n + M_D - N_D - 2M_{N_1} - M_{N_1} = 0$$

where  $N_{\widetilde{D}}$  is the density of electrons at the donor level.

<sup>\*</sup>Shockley, W. and Last, J. T., Phys. Rev., v. 107, no. 2, p. 392-396, July 15, 1957.

Inserting the known statistical relationships, gives

$$-\frac{M_{\text{Ni}}}{1 + \exp \left[ (E_{\text{Ni}} - E_{\text{F}})/kT \right] + \exp \left[ (E_{\text{F}} - E_{\text{Ni}})/kT \right]}$$

= 0

where  $E_i = 0.57$  ev above valence band

$E_{\text{Ni-}}$  = 0.23 ev above valence band

$E_{\text{Ni}} = 0.35$  ev below conduction band, and

$E_{D}$  = 0.04 below conduction band for phosphorous-doped silicon at 300° K.

Graphical solutions to this equation, showing the Fermi level  $\mathbf{E}_{\mathbf{F}}$  as a function of  $\mathbf{M}_{\mathbf{D}}$  for various  $\mathbf{M}_{\mathbf{Ni}}$  (at 300°K) are shown in Figure A-1. This figure relates the original donor concentration prior to nickel doping, the concentration of "active" nickel with which the samples are doped, and the resulting free carrier concentrations. The Fermi level for the sample is also displayed in this figure.

In conclusion it must be emphasized that  $M_{

m Ni}$  is the concentration of active nickel, and not the total nickel content given by the solid solubility limit.

#### Appendix B

## The Measurement of Minority Carrier Lifetime

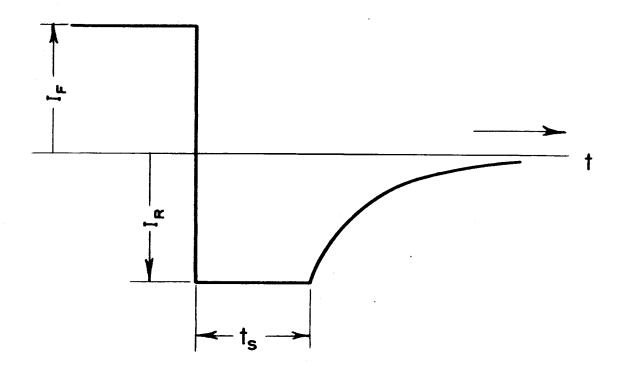

The diode recovery method is commonly used for the measurement of short recovery times (in the nanosecond range) since it is considerably easier to implement than the more common "photoconductive decay" method. The method, as described by Kingston\*, consists of applying a step of current,  $\mathbf{I_F}$ , to a p-n junction and suddenly reversing the current to a new value,  $\mathbf{I_R}$ . This sudden reversal is maintained until all minority carriers are swept out of the device, resulting in a "flat-top region", denoted by  $\mathbf{t_S}$  in Figure B-1. Once the carriers are swept out, the current decays to a final value given by the diode leakage current. Knowledge of the length of the flat-top, and of the decay time, can be used to compute device lifetime. The results of Kingston can only be applied to alloy junction devices, and are not applicable to high speed diffused structures with any degree of accuracy.

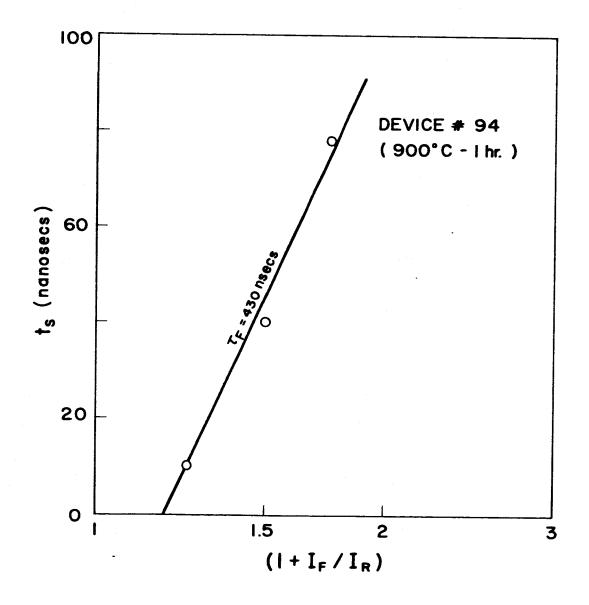

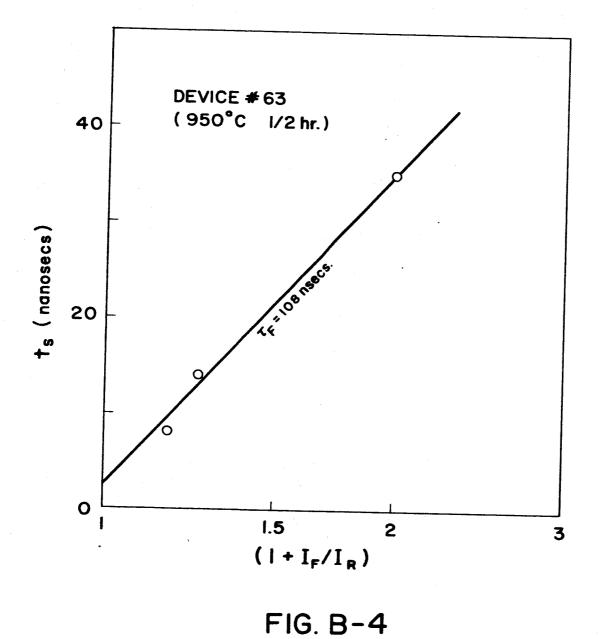

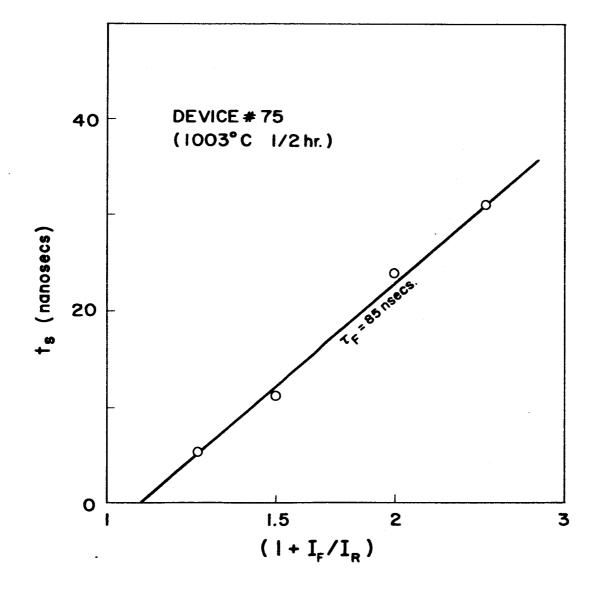

This method has recently been extended by Kuno\*\* to high speed structures, using the charge control method of analysis. Following the analysis of Kuno, we define forward and reverse recombination rate constants  $\mathcal{T}_F$  and  $\mathcal{T}_R$  respectively pertaining to the dynamics of decay of stored charge in a diode during the forward and reverse switching time. If the diode is swtiched instantaneously from a forward current of  $I_F$  to a reverse current of  $I_R$ , Kuno has shown that the "flat-top" region is given by

$$t_s = \tau_F \left[ \ln (1 + I_F/I_R) - \ln (1 + \tau_R/\tau_F) \right]$$

.

<sup>\*</sup>Kingston, R. H. "Switching Time in Junction Diodes and Transistors", Proc. IRE, v. 42, No. 3, p. 829-834, 1954.

<sup>\*\*</sup>Kuno, H. J. "Analysis and Characterization of P-N Junction Diode Switching", IEEE Trans. on Electron Devices, ED-11, No. 1, p. 8-14, 1964.

Thus, if we plot  $t_s$  as a function of  $\ln(1+I_F/I_R)$ , a straight line is obtained with a slope of  $\boldsymbol{\tau}_F$ . It has also been shown that  $\boldsymbol{\tau}_F$  is the minority carrier lifetime for the n region of the diode, if  $\boldsymbol{\sigma}_p\gg\boldsymbol{\sigma}_n$  (as is the case in our structures).

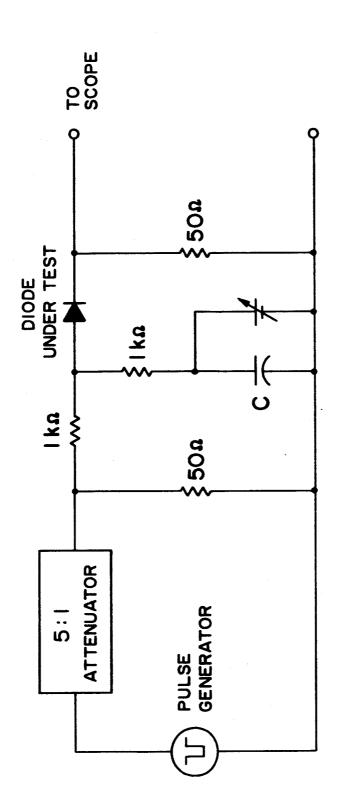

Figure B-2 shows the test jig used to make these measurements. In each case, the values of forward and reverse current were read directly off the oscilloscope. The method provided a simple check on the accuracy of the measurements, since this curve should be a straight line over a large range of  $I_{\overline{F}}/I_{\overline{R}}$  values. This was indeed found to be the case for our devices.

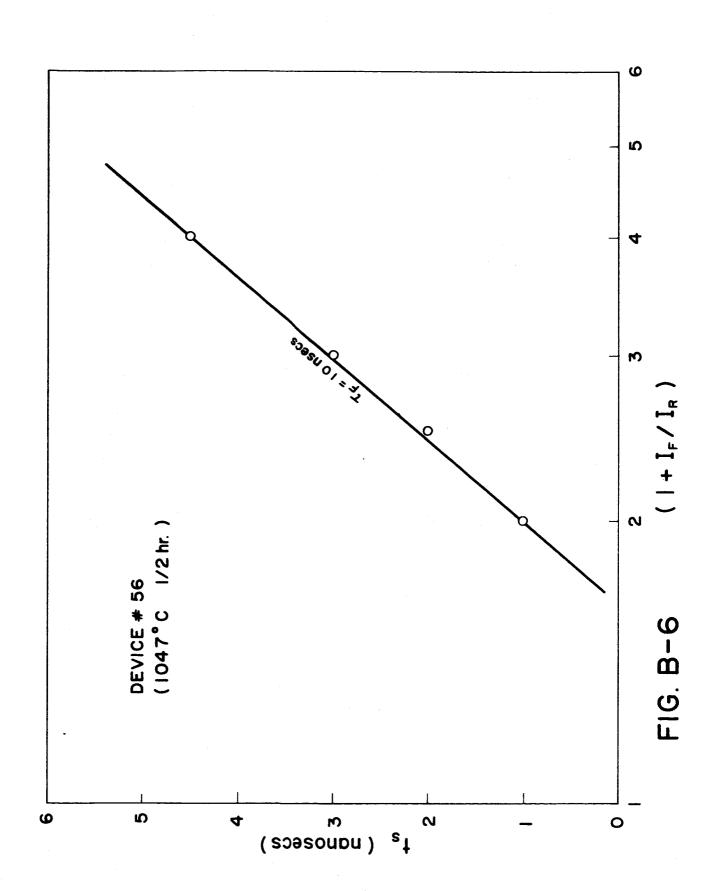

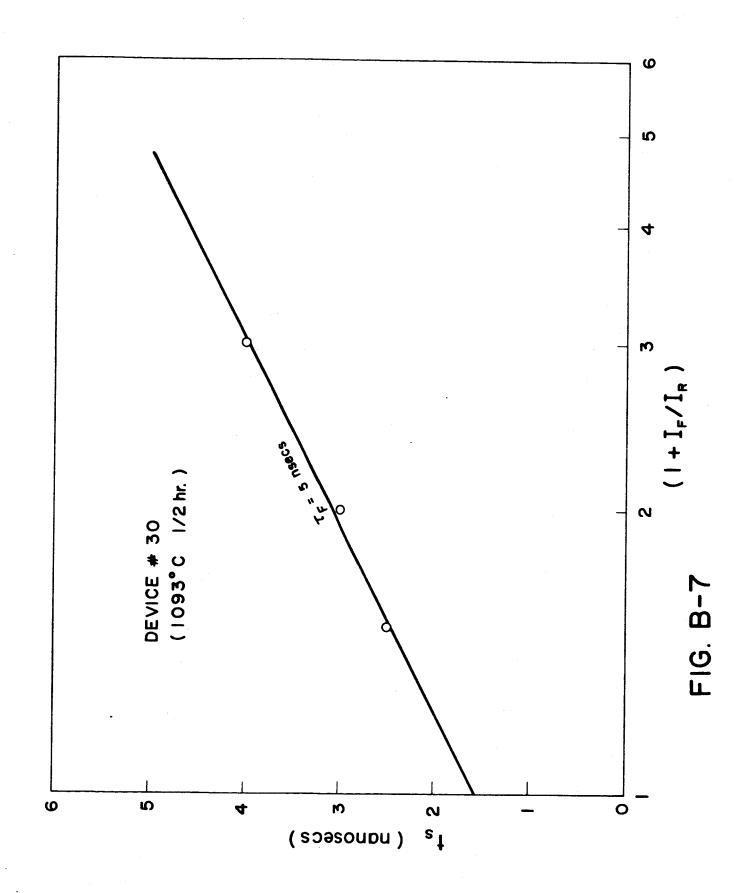

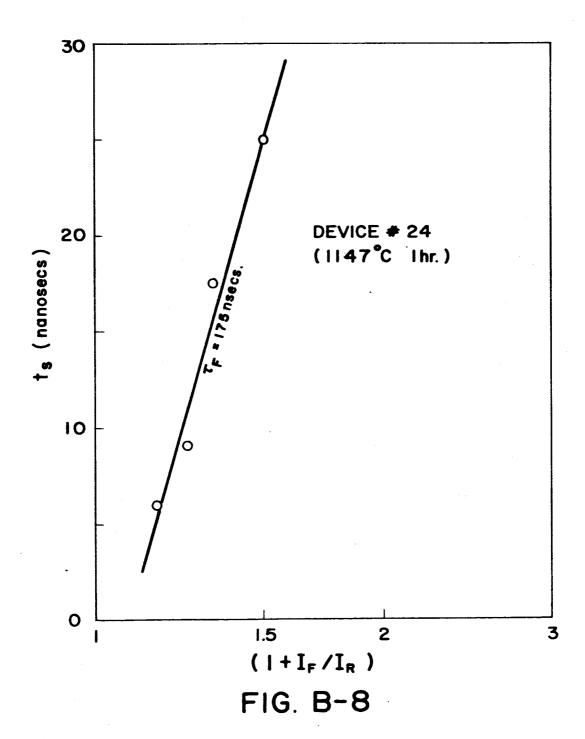

Figure B-3 to B-9 show representative measurements made on our structure, as well as comparative measurements on a 1N914 diode. In each case, the slope  $\mathcal{T}_F$  is marked on the surve. A sampling oscilloscope was used for taking these measurements, with atleast taken in each case as a check on the measurement method.

### Appendix C

## The Diffusion of Nickel from a Glassy Source

The following is a description of the work conducted to date on investigating the feasibility of diffusing nickel from a glassy source:

- a) A study has been made of the chemistry of nickel compounds to ascertain which of these is most suited for this application. This has concentrated our efforts to the use of nickel oxide, NiO. This oxide takes the form of a greenish powder, which melts at 1990°C.

- b) A literature search was made for the phase diagram of the NiO-SiO<sub>2</sub> system. Such a diagram was not found. Consequently, an attempt was made to see if NiO was soluble in SiO<sub>2</sub> at diffusion temperatures. A wafer of silicon was thermally oxidized at 1000°C (using a dry O<sub>2</sub>-steam-dry O<sub>2</sub> cycle). Dry NiO was dusted on the oxidized surface and the wafer heated for one hour at 1150°C. On removal, the wafer was subjected to microscopic examination. While the NiO had sintered to the SiO<sub>2</sub> layer, no signs of a solution were found.

- c) The next experiment was conducted in an attempt to dissolve NiO into a glass that is formed on the wafer using  $\mathrm{SiO}_2$  and an electronically inactive oxide. The PbO-SiO $_2$  system was selected, since lead is known to be inactive in silicon.

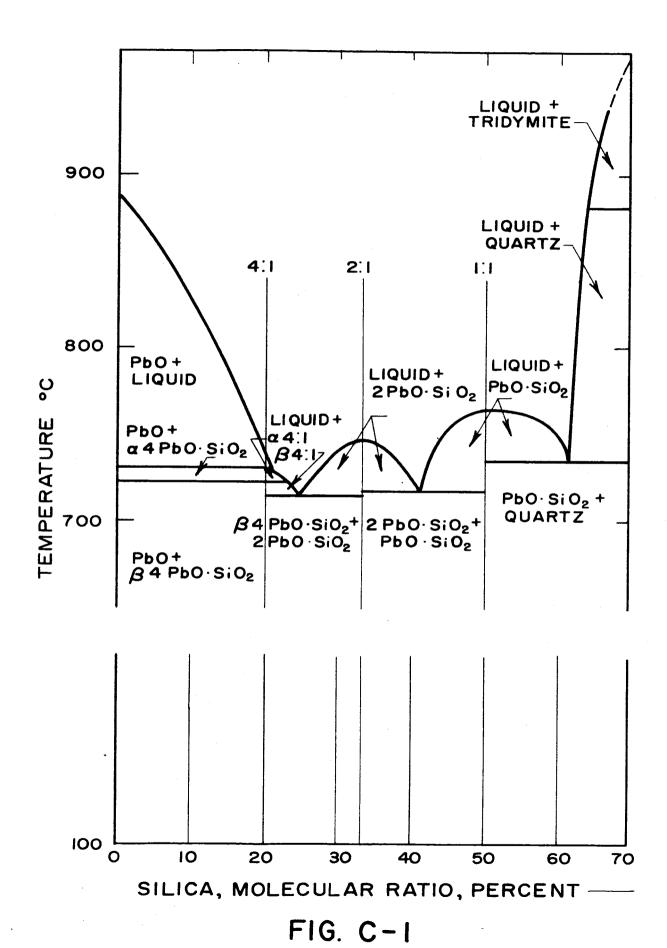

Figure C - 1 shows the phase diagram for the PbO-SiO $_2$  system. It is seen that a liquid phase exists at temperatures above  $720^{\circ}$  C. A wafer of

silicon was oxidized as described before, and inserted in a closed box with a PbO source. The wafer was heated to 900°C for one hour, and examined. While a PbO-SiO<sub>2</sub> glass was certainly formed, the surface condition was very poor with signs of excessive pitting and crazing. It would appear that a suitable technique could most probably be developed for forming a uniform crack-free glass on the wafer. However, time did not permit refining this step, so the experiment was extended to see if nickel would dissolve in this glass. A layer of NiO was dusted on the wafer and the wafer subjected to a one hour diffusion cycle at 1000°C. After diffusion, the wafer was optically inspected for signs of solution of NiO in the glass. Results were inconclusive.

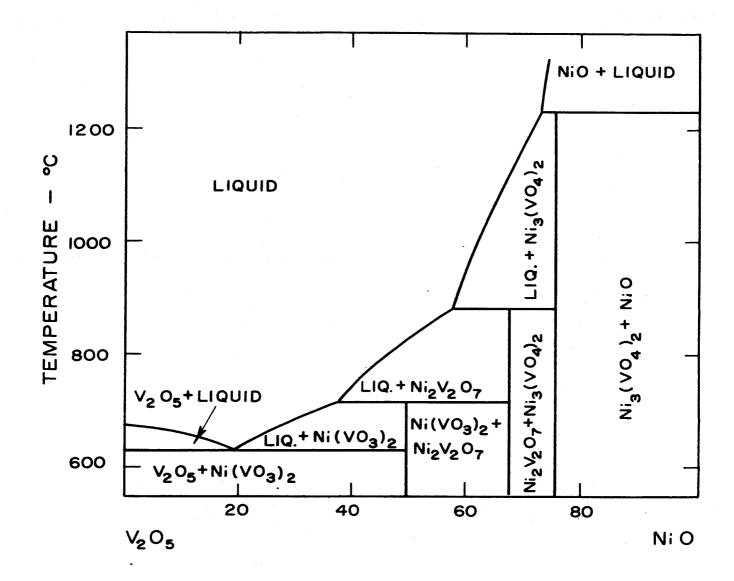

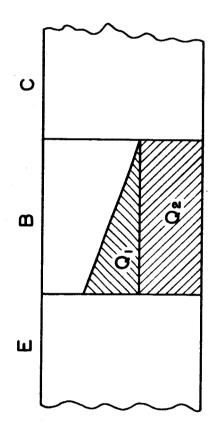

) A study of the metal-oxide phase diagram literature revealed that NiO can be used with vanadium pentoxide  $(V_2O_5)$  to produce a glass at temperatures in excess of  $650^{\circ}$  C. (The phase diagram for this system is shown in Fig. C-2) Since vanadium is also inactive in silicon, the scheme was attempted as follows: First,  $V_2O_5$  was dusted over a wafer of silicon and placed in a diffusion furnace for an hour at  $1000^{\circ}$  C. On removal from the furnace, the wafer was cleaned in hot KOH. This removed the  $V_2O_5$  readily, leaving an undamaged silicon surface.

In order to test the feasibility of using this oxide as a carrier of nickel, a freshly etched sample of silicon was coated with a slurry of NiO and  $V_2O_5$  (one part by weight of NiO to ten parts by weight of  $V_2O_5$  in an ethylene glycol base) and diffused for one hour at  $1000^{\circ}$  C. On removal from the furnace, the glass was removed, with some difficulty, by a hot KOH treatment. The surface of the silicon was inspected visually, and found

to be undamaged. The resistivity of the was round to be increased by the diffusion, and it has been concluded that this is due to the diffusion of Ni from the  $\rm V_2O_5$ -NiO source. Time did not permit the detailed investigation of nickel diffusion from this source over a range of typical diffusion temperatures. However, it is concluded that

- a) Nickel can be diffused from a NiO- $V_2^{0}_5$  glass with no damage to the silicon surface.

- b) The resulting nickel-vanadium compounds can be removed by the use of hot KOH.

- c) The nickel that is diffuse in this manner show signs of electrical activity.

Considerable further investigation is needed in order to actually devise a practical process for the diffusion of nickel in silicon. Specifically, it is necessary to search for alternate methods for removing the nickel-vanadium compounds from the surface of the wafer. In addition, it is necessary to conduct an extensive series of compensation experiments to determine the amount of nickel that enters the lattice, and also to determine the optimum NiO- $V_2O_5$  ratio to be used. Finally, improved methods should be sought for transporting the NiO- $V_2O_5$  mixture to the silicon wafer.

#### APPENDIX D

### Pulse Noise in Digital Circuits

large scale digital subsystems are usually composed of a number of iterated, interconnected, logic function blocks. Thus, the problem of pulse transmission in these circuits is one of transmitting high frequency signals in a large, wideband circuit. For any individual logic gate in this circuit, spurious signals presenting themselves at its input are due to one or more of the following reasons:

- a) Noise generated in the transmission line between gates,

- b) Noise picked up in the transmission line between gates,

- c) Noise transmitted from the output of the preceding gate, and

- d) Logic Noise

In addition, the transmission line between different gates is of variable length, being under 1/2" long when interconnecting two gates that are side by side, and more than a foot in length when the transmission line connects gates on separate circuit boards.

### D.1 Noise Generated in Transmission Lines

Noise generated in transmission lines is a result of reflections from improper terminations at either end of the line. If a short line is used, such as is commonly the case between gates on the same circuit board, this noise has the nature of extremely high frequency ringing, at a frequency determined by the time delay of the line. Thus, a transmission line 1/2<sup>4</sup> long gives rise to noise components at frequencies of 9 GHz and higher if improperly terminated. Since the fundamental frequency associated with this noise is well beyond the band-width of the

circuit, the problem may safely be ignored. This is especially true in high speed digital circuits which operate at reasonably low impedance levels, and consequently are highly damped.

The situation is quite different with transmission lines whose lengths are comparable to the rise time of the circuit. Here, reflections that occur are sufficiently long in duration that their presence cannot be ignored. Since digital circuits present nonlinear impedances, it is only possible at best to provide a crudely matched termination at both ends of the transmission line. This noise takes the form of distortion of an otherwise rectangular pulse, and also results in spurious pulses, having a width equal to twice the delay time associated with the transmission line.

Pulse distortion in transmission lines may be computed readily\* by considering separately the incident and reflected waves on the line.

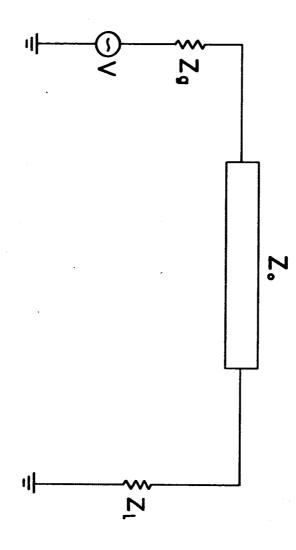

Figure D-1 shows the equivalent circuit of such a line. At either end of the line,

the Voltage Reflection Coefficient,  $\rho_{\rm v}$ , is given by

$$\rho_{\rm v} = \frac{Z - Z_{\rm o}}{Z + Z_{\rm o}};$$

the Current Reflection Coefficient,  $ho_{ ext{i}}$ , is given by

$$\rho_{i} = \frac{Z_{o} - Z}{Z_{o} + Z};$$

the Voltage Transmission Coefficient,  $t_v$ , is given by

$$t_{v} = \frac{2Z}{Z_{o} + Z};$$

<sup>\*</sup> Millman, J. and Taub, H. "Pulse and Digital Circuita", McGraw Hill Book Co., New York (1956).

and the Current Transmission Coefficient,  $t_1$ , is given by

$$t_{i} = \frac{2 Z_{o}}{Z_{o} + Z}$$

The substitution,  $Z=Z_g$  must be made in order for these expressions to apply to the generator end. In like manner, the substitution  $Z=Z_1$  will make the expressions applicable to the load end.

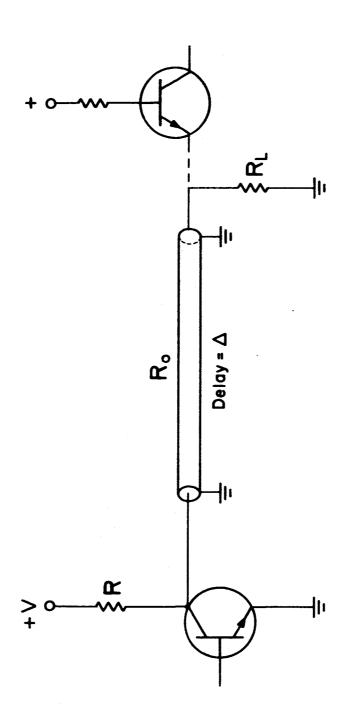

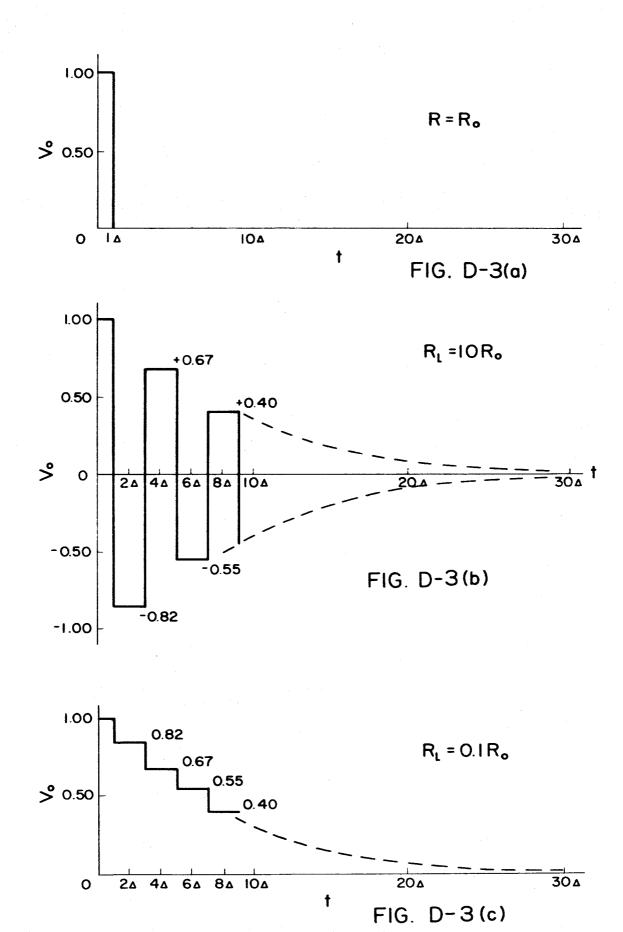

Figure D-2 shows a situation that occurs typically in a digital circuit. The line (having a characteristic impedance  $R_{\rm o}$ ) is initially charged with the transistor open. At time t = 0, the transistor is turned on, thus shorting the previously charged line. Figure D-3 shows the waveforms across the load end  $(R_{\rm l})$  for the case where  $R_{\rm l}=R_{\rm o}$ , as well as for the cases where  $R_{\rm l}=10$  R and  $R_{\rm l}=0.1$  R. It is assumed that the line is charged to the steady state in each case prior to turning on the transistor, and that the transistor is a perfect switch.

Figure D-3a shows the waveform at the load when the load and transmission line are matched. For this case, the signal across the load terminates after delay of  $\Delta$  seconds, where  $\Delta$  is the time delay of the line. Thus, a nett delay of  $\Delta$  is incorporated into the circuit for this condition.

Figure D-3b shows the load waveform when  $R_1 = 10 R_o$ . For this case, the voltage across the load goes through many reversals until it is finally damped. Here, the charge associated with the first of these positive going reversals is given by

$$Q = 0.67 V_{cc} \Delta / R_1 \text{ coulombs}$$

where  $V_{\rm cc}$  is the supply voltage for the transistor. In order to avoid malfunction, it is necessary that the load circuit have a pulse noise immunity in excess of this value.

Figure D-3c shows the case where  $R_1 = 0.1 R_0$ . For this termination, we note the absence of pulses that can cause malfunction. However, excessive pulse delay is the result, since the circuit recognizes the cessation of the signal many delay times after its actual termination.

The situation is somewhat more complicated by the fact that the load impedance is, in reality, not constant, but is given by the input impedance of a  $T^2L$  gate. Thus, for the first two cases, the load transistor would start to conduct after a time delay of  $\Delta$ . At this point, the load impedance would abruptly fall, and closely approximate that of a charged line, shorted at both ends. Thus, it is probable that the actual waveform would be rapidly damped after one or two oscillations.

# D.2 Noise Pickup in Transmission Lines

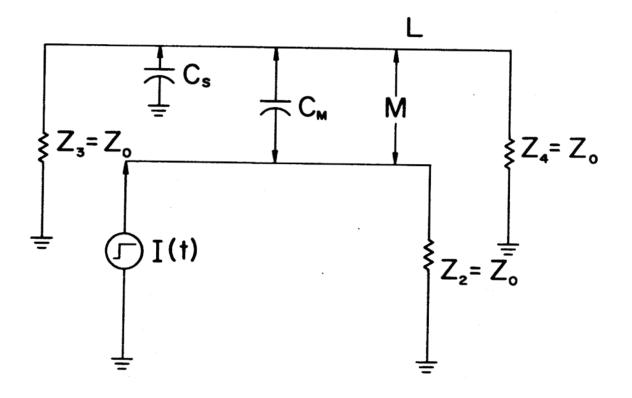

One component of this noise is associated with crosstalk between lines. Figure D-4 shows an elementary system of two loosely coupled transmission lines, terminated in their characteristic impedance  $\mathbf{Z}_{0}$ .

If  $C_M$  and  $C_S$  are the mutual and shunt coupling capacitances per unit length, and M and L the mutual and series inductances per unit length, it can be shown\* that the charge delivered to  $Z_3$  via the backward wave is approximately given by

$$Q = \frac{M}{L} \cdot \frac{K+1}{2 K} \cdot \Delta \cdot dI$$

where  $\Delta$  is the delay of the line,

$\mbox{\em dI}$  is the magnitude of the current excursion at the generator  $\mbox{\em end,}$  and

$$K = \frac{M}{L} \cdot \frac{C_S}{C_M}$$

Following directional coupler theory, it may be shown that the charge delivered to  $\mathbf{Z}_{\mathbf{l}_{4}}$  is considerably smaller in magnitude. In a practical circuit with varying loads, good design practice indicates that both  $\mathbf{Z}_{3}$  and  $\mathbf{Z}_{\mathbf{l}_{4}}$  should be capable of tolerating the malfunction charge that is normally delivered to  $\mathbf{Z}_{3}$ .

While the expression for malfunction charge indicates that the current level can be adjusted to reduce this type of noise, it is usually found in practice that the high speed pulse circuit designer is limited to a prescribed range of current values in order to achieve the desired system performance. The reason for this is clear in the fundamental equations for the charging time of the various elements of a transistor.

<sup>\*</sup> Jarvis, D. B. "The Effect of Interconnections on High Speed Logic Circuits," IEEE Trans. on Elec. Comp., v. EC-12, p. 476-487, 1963.

Thus, for any parasitic capacitance that must be charged,

$$\int_0^{t_1} I(t) dt = \int_{V_1}^{V_2} C(V) dV$$

where  $t_1$  is the charging time and  $V_1$  and  $V_2$  are the initial and final values to which the capacitor must be charged. In addition, the time taken to charge the various internal regions of the transistor is given directly by

$$t_2 =$$

$\lesssim Q_j/I_j$  (t)

where t<sub>2</sub> is the charging time, and Q<sub>j</sub> the individual charge elements of the transistor (e.g., base charge, collector storage charge, and so on).

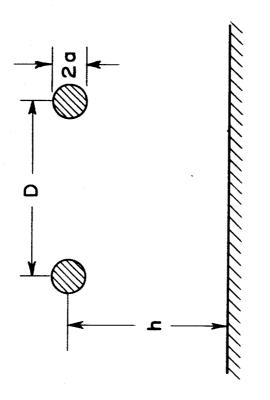

In a typical situation, the mutual inductance is that associated with point to point wiring over a ground plane. Thus, for the configuration of Figure D-5, the mutual coupling inductance is approximately given\* (for long wires) by

$$M = 0.2 ln \sqrt{(1 + 4h^2/D^2)} \mu h/meter.$$

Therefore, as the wiring is brought closer to the ground plane, the mutual inductive coupling is reduced.

For the configuration of Figure D-5, it may also be shown that the capacitance to ground is inversely proportional to  $\ln (2h/a) \sqrt{(1 + 4h^2/D^2)}$ . Thus, there is, in essence, a trade off between inductive pickup and charging capacitance.

<sup>\*</sup> Grover, W. C., "Inductance Calculations", D. Van Nostrand Co., Princeton, New Jersey (1946).

It should be noted that the magnitude of the current pickup is a function of the rise time of the transmitted signal. On the other hand, the nett charge pickup is only given by the current excursion alone, and is thus relatively independent of the rise time.

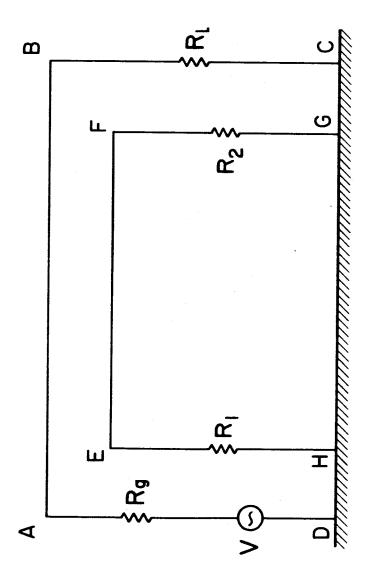

Figure D-6 shows two loops, A B C D and E F G H, both of which are coupled by the mutual impedance associated with the areas of the loops as well as by the self-inductance of the ground line GH, which is common to both. In such a system, it is possible to eliminate the effects of self-impedance by providing separate return paths for both loops, as shown in Figure D-7. Such a system still has mutual inductive pickup, but the self-inductive pickup is eliminated by having separate return paths which are electrically connected at a single point. Figure D-8 shows a crossection through a circuit of this type. For this circuit, assuming parallel wires,

$$M = 0.2 \ln (a_1 b_2/a_2 b_1) \mu h/meter.$$

The use of twisted pairs leads to an almost complete elimination of mutual coupling between two circuit boards. In fact, the mutual coupling of such a system is strictly a function of second order effects, such as non-uniformity of twisting.

More complex schemes may also be used to reduce the mutual coupling between circuits. Thus, the use of coaxial pairs leads to values of mutual inductance that are one decade below the figure normally obtained with twisted pairs.

Stripline techniques provide an increasingly popular alternative to the use of twisted pairs in modern microsystems. due to the fact that they can be fabricated by photolithographic processes, and are thus compatible with microcircuits in terms of their compactness and ease of fabrication. The most popular technique is microstrip\*, where then conductors are printed on one side of a flexible low-loss dielectric such as teflon-loaded fiberglass, about 10 to 20 mils thick. The reverse side of this strip is coated with a conductive layer and serves as a ground plane. Propagation of signals along such a conductor system take place (ideally) in the TEM mode, with essentially all of the power flow being confined to a region of the ground plane equal to approximately three times the strip width. The crosstalk between two parallel conductors in a microstrip configuration is a function of the fringing radiation field from each conductor. This radiation field falls as the square of the spacing between conductors, and can be further reduced by decreasing the thickness of the dielectric layer.

The configuration of two parallel microstrip conductors on a common ground plane is essentially that of a microwave directional coupler, and has been analysed by Jones and Bolljahn\*\*, using coupled mode theory.

<sup>\*</sup> Grieg, D. D. and Engelmann, H. F., "Microstrip - A New Transmission Technique for the Kilomegacycle Range", Proc. IRE, v. 40, no. 12, p. 1644-1650 (1952).

<sup>\*\*</sup> Jones, E. M. T. and Bolljahn, J. T., "Coupled-strip Transmission line Filters and Directional Couplers" IRE Trans. on Microwave Theory and Techniques, vol. MTT-4, p. 75-81, 1956.

The work has been extended by Connolly\* to the analysis of the response of coupled microstrip lines to a step input pulse. In addition to determining the amplitude of the various signals induced in a coupled line (terminated at both ends in its characteristic impedance), he has shown that the crosstalk pulse appearing at the sending end is  $2\Delta$  to  $4\Delta$  in width. For his balanced matched-load system, the signal induced at the receiving end is essentially due to end effects and anisotropic behavior of the dielectric constant. In a typical (mismatched) circuit, this signal could be as large as that induced at the sending end.

The mutual impedance of coupled microstrip lines can be made comparable to that of twisted pairs. However, signal pickup due to the common ground return is still present in these structures. The coupling associated with this common ground can be eliminated by resorting to microstrip techniques with separate ground returns. Unfortunately, this leads to a considerable increase in the physical size of the interconnections.

# D.3 Noise Transmitted from the Output of the Preceeding Gate

This noise can be generated within a logic gate because of the imperfect nature of circuit elements, both active and passive. The problem with passive elements is due to the nature of the parasitics associated with them. Thus, the offset diodes used to obtain d-c noise

<sup>\*</sup> Connolly, J. B. "Cross coupling in High Speed Digital Systems", IEEE Trans. on Electronic Computers, v. EC-15, no. 3, p. 323-327, 1966.

immunity in DTL circuits results in the transfer of current pulses because of their parasitic shunt capacitance.

The noise generated in active elements is more serious in nature, and results from the limitations of the devices themselves. Some of these sources are considered here.

Impulse Widening. Impulse widening can sometimes result in converting a very narrow noise pulse into a wider pulse that may be mistaken for a signal. Thus, if an impulse of current, representing a charge q, arrives at the base of a transistor, its collector current is given by

$$I_c(t) = \omega_T q \exp(-\omega_T t / \mathbf{d}_{eo})$$

where  $\omega_{\rm T}$  is the transistor gain-bandwidth product in radians and  $\mathbf{d}_{\rm e0}$  is the common emitter current gain. The charge associated with this current waveform is given by q  $\mathbf{d}_{\rm e0}$ . Thus, the effect of impulse widening is to multiply the charge by the transistor current gain, and also to redistribute its frequency components towards the lower end of the spectrum, within the bandwidth of succeeding devices.

Noise Generated in Circuits With Switched Loads. This is one form of noise that occurs when a transistor in the ON condition is suddenly required to feed additional loads. This is a potential problem with both DTL and T<sup>2</sup>L circuits where the nature of the load is nonlinear and may suddenly change at random times\*.

<sup>\*</sup> For example, in DTL and  $T^2L$  designs when all but one gate input are switched off.

Consider a transistor with a base current of  $I_B$ . Let the collector current initially be  $I_{Cl}$ . Then Figure D-9 shows the charge distribution in the base, with

$$Q_1 = \Upsilon_T I_{C1}/d_{eo}$$

$Q_2 = \Upsilon_S [I_B - I_{C1}/d_{eo}]$

where  $d_{\rm eo}$  is the common emitter current gain,  $\tau_{\rm T}$  is the reciprocal gain bandwidth product, and  $\tau_{\rm S}$  is the storage time constant. Thus, the total charge in the base is  $Q_1+Q_2$ . At this point, let the demanded collector current be suddenly increased by  $I_{\rm C2}$ , and let us assume that the transistor remains saturated. Since this current must be instantaneously supplied by the base charge, it is clear that the charge  $Q_2$  must supply it all, or else the transistor will momentarily drop out of saturation, until the base current re-establishes the base charge to its steady state value.

In order for the transistor to remain in saturation

Thus, the total collector current that can be handled by this stage without dropping out of saturation is given by

$$I_{C} = I_{C1} + I_{C2} \leq I_{B} \gamma_{s} / \gamma_{T} + I_{C1} - [\gamma_{s} / \chi_{eo} \gamma_{T}]$$

In general,

$$T_{\rm s}/T_{\rm T} < L_{\rm eo}$$

Thus, for the worst case situation

$$I_{C} \leq I_{R} \gamma_{S} \gamma_{T}$$

Beaufoy and Sparkes\* have defined an "on-demand" current gain for a transistor as

$$\mathbf{A}_{\mathrm{es}} = \mathbf{T}_{\mathrm{s}} / \mathbf{T}_{\mathrm{T}}$$

In typical transistors,  $\mathbf{d}_{es} = 0.5 \,\mathbf{d}_{eo}$ . If  $\mathbf{d}_{es}$  is used as the basis of design instead of  $\mathbf{d}_{eo}$ , this noise pulse generation can be avoided. Thus, the problem of malfunction due to this cause can be directly avoided by using the on-demand current gain of a transistor instead of its common emitter current gain as a basis of circuit design.

Noise Due to Mistiming. This noise is often present in high speed systems where a signal, after being processed in two channels of slightly different length (i.e., slightly different delay time), arrives at two inputs to a gate with a slight time displacement. In asynchronous systems, care must be taken to minimize the resulting noise signal at all times, with careful attention being paid to equalizing all such delay paths.

The problem is considerably less important in clocked synchronous systems, where clocking is done at regular intervals. In such systems, as long as the delay through any combinational logic path is less than one half of the clock interval, the problem is corrected at each clocking point. In asynchronous circuits, mistiming results in a pulse of amplitude equal to the logical signal, and of width given by the difference in timing delays.

<sup>\*</sup> Beaufoy and J. Sparkes - Transistor Switching Performance Analyzed in Terms of Base Charge (British) Telecommunications Research LTD., Taplow, England Technical Report, May, 1958.

Consider a signal that must pass through M gates on one channel and N gates on the other, prior to recombination. If  $\langle t_{pd} \rangle$  is the average propagation delay of each gate, with a  $\frac{+}{2}$  20% tolerance, and M is greater than N, the maximum pulse width due to mistiming is given by

$$\Delta = (1.2 \text{ M} - 0.8 \text{ N}) < t_{pd} >$$

and the charge associated with a current pulse of amplitude I is given by

$$Q = I (1.2 M - 0.8 N) < t_{pd} >$$

Thus, the pulse noise immunity of the gate will determine the number of stage delays that can be tolerated before re-timing is necessitated.

Alternately, as is usually the case, artifical delays are used in order to balance the delay time of the channels. If this is done, and the channels equalized to a delay of M stages, the worst case situation results in a malfunction pulse with a charge given by

$$Q = 0.4 \text{ M I} \text{ t}_{pd} > \text{coulombs},$$

where I is the peak current associated with the pulse.

### D.4 Logic Noise

While this type of noise is also transmitted from the output of a circuit, its presence only occurs at the output of certain types of high speed, asynchronous sequential circuits. These circuits are characterized by the presence of feedback loops and their problems are considered in some detail in the Section 4.

#### APPENDIX E

# Terminal Characteristics of the T2L Gate

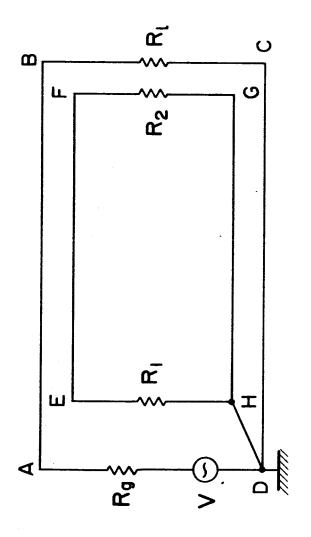

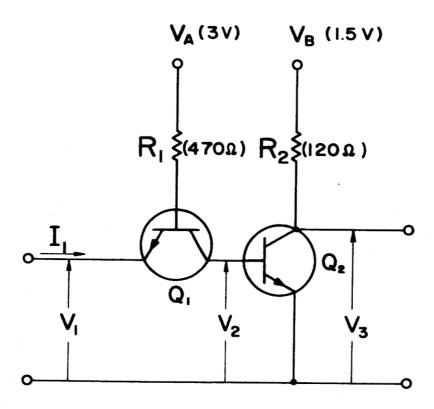

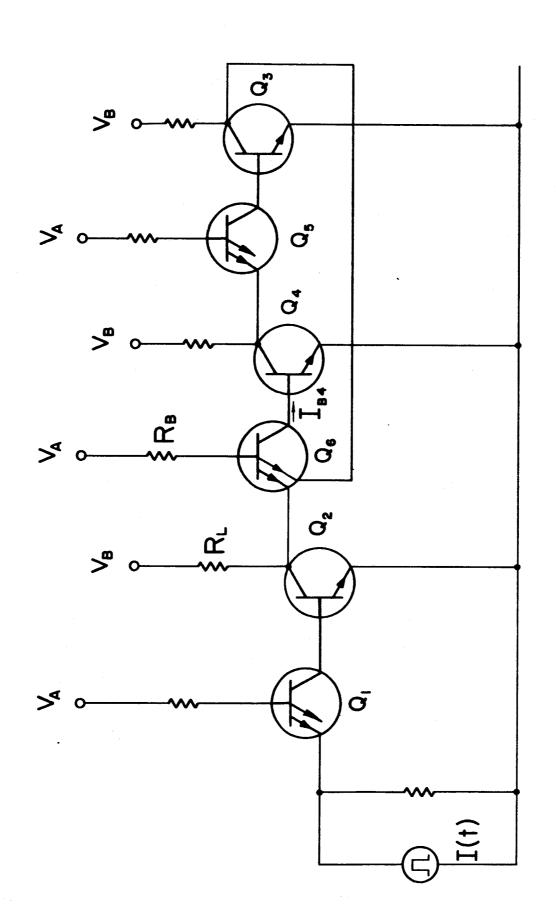

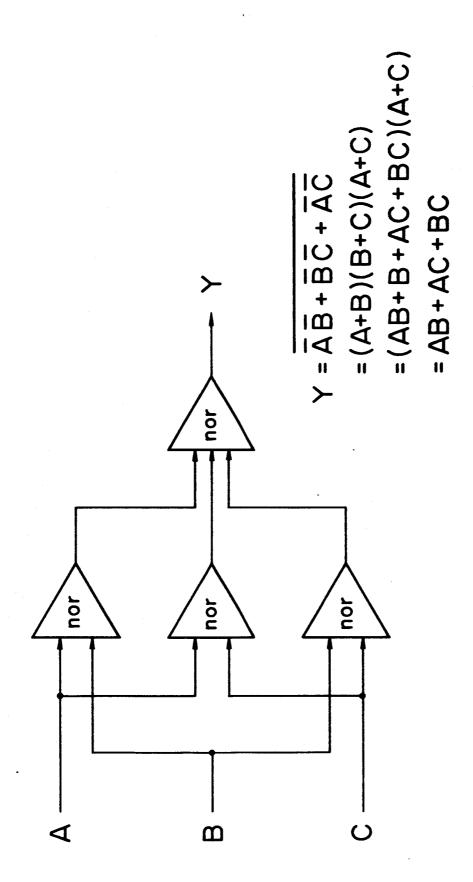

The basic configuration of the  $T^2L$  gate is shown in Figure E-1. The operation of the gate is as follows:

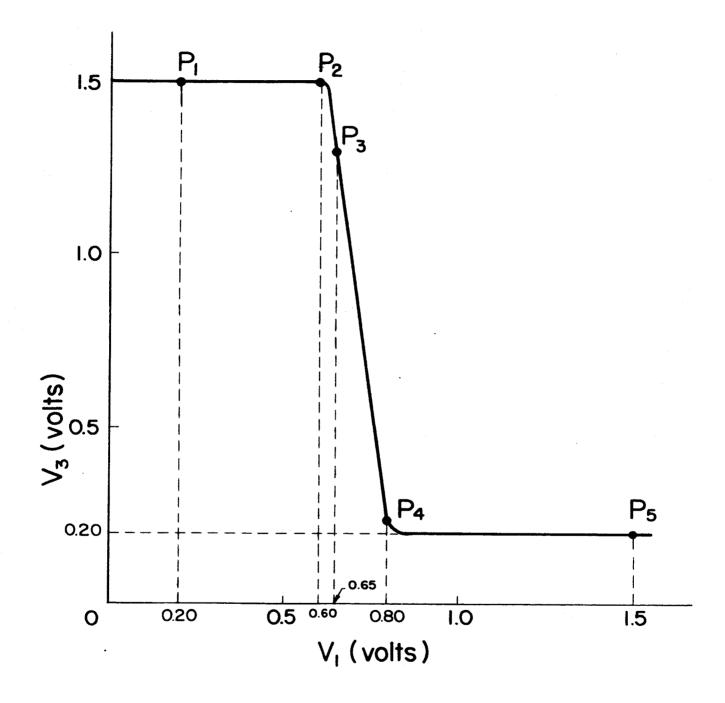

When  $Q_0$  is driven into the ON condition, the voltage at the point 1 assumes a value equal to its saturation voltage. Assuming a low resistivity collector structure, with a buried layer, this voltage is typically 0.2 volts. For this condition, the base current of  $Q_1$  is driven through its emitter to ground via  $Q_0$ , and  $Q_1$  is in the ON condition. The voltage drop across  $Q_1$  can be neglected to a first order approximation, since the current drawn by this stage is much less than that drawn by the inverter transistors (i.e., base drive current as opposed to collector current). At this point, the base of  $Q_2$  is slightly over 0.2 volts to ground, and this transistor is in the OFF condition.

When  $Q_0$  is driven into the OFF condition, the base current of  $Q_1$  is diverted through its collector to the base of  $Q_2$ , driving this stage ON. For this condition, the final value of the base voltage of  $Q_2$  assumes a value of approximately 0.85 volts. Once again,  $Q_1$  is in the ON condition, and the voltage drop across this stage may be ignored. Thus, the collector voltage of  $Q_0$  assumes a value of approximately 0.85 volts at this point. From this point onwards,  $Q_0$  goes further into the OFF condition, until it reaches the supply voltage  $V_B$  with no additional effect on the inverter transistor.

The state of the transistors as well as the relative voltages are summarized in the following Table.

| State of       |    |                 | v <sub>l</sub>    | v <sub>2</sub> | <b>v</b> <sub>3</sub> |

|----------------|----|-----------------|-------------------|----------------|-----------------------|

| Q <sub>O</sub> | 원  | e <sup>n2</sup> |                   |                |                       |

| ON             | ON | OFF             | 0.2 v             | 0.2 <b>v</b>   | $v_{_{ m B}}$         |

| OFF            | ON | ON              | ${f v}_{_{ m B}}$ | 0.85 v         | 0 <b>.</b> 2 v        |

A few significant features of this circuit may be noted.

- a) The multi-emitter transistor  $Q_{\eta}$  is always ON.

- b) The d.c. logic swing at the base of  $Q_2$  is 0.2 volts to 0.85 volts at room temperature.

The values of  $V_1$  and  $V_2$  vary with temperature, as follows:  $V_1$  is directly proportional to the resistivity of the collector body material. Assuming a collector resistivity of 0.1 to 0.25  $\Lambda$  cm (entirely adequate for a device designed to operate at supply the voltages below 6 volts), the collector resistance at 125°C (and hence  $V_1$ ), will be about 125% of its value at 25°C. Thus,  $V_1$  increases to about 0.25 volts at 125°C.  $V_2$  is the voltage drop associated with a forward biased diode, and falls at the rate of 1.8 m v/°C. Thus, the lower bound of  $V_2$ , obtained at 125°C, is approximately 0.67 volts. Consequently, the logic swing at the base of  $V_2$  is 0.25 volts to 0.67 volts at 125°C. Since the difference between these levels represents the discrimination of the inverter, (to d.c. signal levels changes), we note that the worst case d.c. noise margin occurs at elevated temperatures.

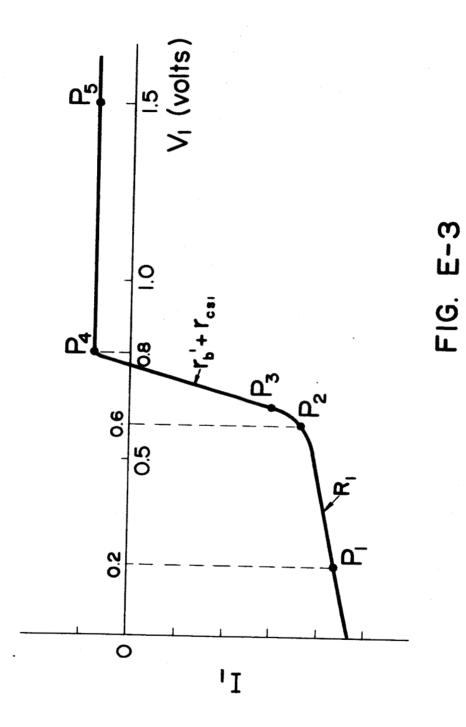

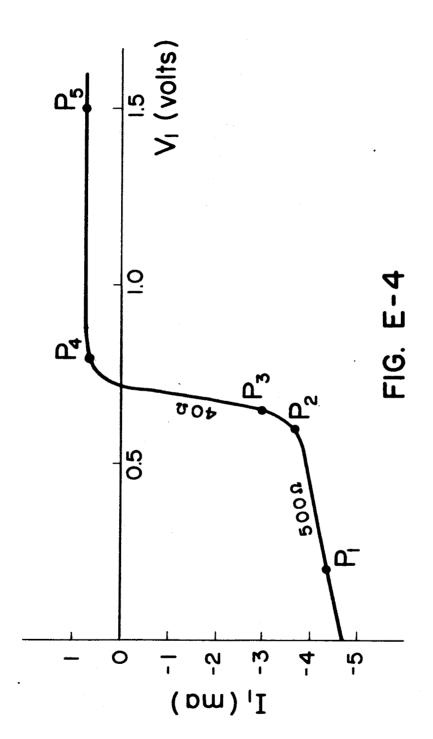

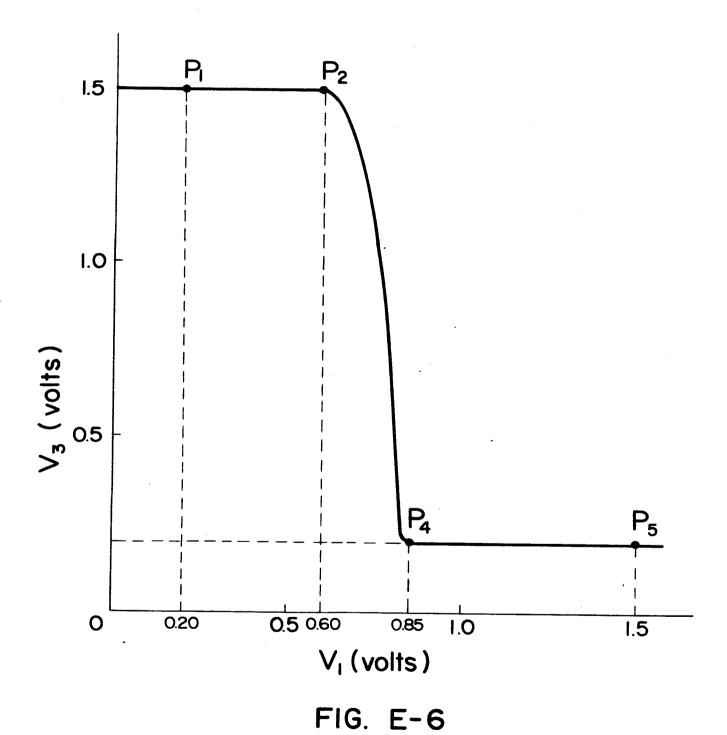

The input characteristic of the gate may now be assesed. Figure E-2 shows the actual gate used, with the input voltage  $V_1$  as the variable. Initially,  $Q_0$  is in the ON condition, and  $V_1$  is approximately 0.2 volts. Thus,  $I_1 = -(V_A - V_{EB1} - 0.2)/R_1$  where  $V_{EB1}$  is the forward drop across the emitter-base diode  $Q_1$ . For the actual values quoted in Figure E-2,  $I_1 \cong -4.2$  m a.

As  $V_1$  is increased, the V-I characteristic moves along a straight line with a slope of  $R_1$  until the onset of conduction of  $Q_2$  (at about 0.6 volts). At this point,  $Q_2$  enters its active region, and the input characteristic has a slope given by the sum of the collector body resistance of  $Q_1$  and the input impedance of  $Q_2$ . Shortly thereafter, transistor  $Q_2$  becomes saturated.

In saturation, the input impedance of  $Q_{2}$  is given by

$$R_{in} = r_{b2}' + (kT/qI_{E2})$$

where  $r_{b2}$  is the base spreading resistance of the inverter transistor, and  $I_{E2}$  is its emitter current. The slope of the input characteristic during this region is thus given by the sum of the collector saturation resistance of the coupling transistor, the base spreading resistance of the inverter, and the forward impedance of the emitter-base diode of the inverter transistor. Since  $I_{E2}$  is large (about 15-20 ma for this circuit), this last term is usually negligible.

This slope is maintained until the current supplied by  $V_A$  is all diverted to the base of  $Q_2$ , at which point the input impedance rapidly increases to that of a reverse biased emitter-base diode. At this point, the input current of

the gate is given by

$$I_1 = I_{B1} d_R/(1 - d_R),$$