https://ntrs.nasa.gov/search.jsp?R=19670008693 2020-03-16T18:59:02+00:00Z

Contract Number: NAS8-20594 15 October 1966

7 DESIGN AND DEVELOP A

MOS MAGNETIC MEMORY

## FINAL REPORT OF STUDY PHASE

$\sim$  11 March 1966 through 11 September 1966 (

Prepared by: 6 F. H. Edelman, Project Leader

> E. L. Daniel, Principal Design and Development Engineer

Prepared for: George C. Marshall Space Flight Center Huntsville, Alabama 0

llivan Approved: ()

A. W. Sullivan Chief Engineer, Computer Group

PRECEDING PAGE BLANK NOT FILMED.

## NAS8-20594

· · · · · · · · · · ·

## TABLE OF CONTENTS

|           |                                                                 |                                                              | Page     |

|-----------|-----------------------------------------------------------------|--------------------------------------------------------------|----------|

| List of ] | llustrations                                                    | 3                                                            | v        |

| 1.0       | FOREWORD                                                        |                                                              |          |

| 2.0       | REVIEW OF OBJECTIVES                                            |                                                              | 1        |

| 3.0       | INTRODUCTION                                                    |                                                              | 1        |

|           |                                                                 | ed Wire<br>5 Devices                                         | 2<br>5   |

| 4.0       | SUMMARY                                                         | ζ                                                            | 10       |

| 5.0       | PACKAGE COMPATIBILITY BETWEEN THE MEMORY<br>AND THE MOS DEVICES |                                                              | 11       |

| 6.0       | INTERCO                                                         | NNECTIONS OF MEMORY TO MOS DEVICES                           | 15       |

|           |                                                                 | 5 Word Driver<br>5 Sense Amplifier                           | 15<br>23 |

| 7.0       | INTERCO                                                         | NNECTION OF MOST LSIS AND PLATED WIRE                        | 36       |

| 8.0       | TOTAL REDUCTION OF INTERFACES AND INTERFACE CONNECTIONS         |                                                              | 38       |

|           |                                                                 | cuit Organization and Layout                                 | 39       |

|           |                                                                 | uction of MOST Interfaces<br>nterface-Free Packaging Concept | 40<br>53 |

| 9.0       | MANUFAG                                                         | CTURING COMPATIBILITY OF THE MAGNETIC<br>D THE MOS DEVICES   |          |

|           |                                                                 | 5 Manufacturing Process<br>ed Wire Manufacturing Process     | 70<br>80 |

| 10.0      | POWER AND SPEED REQUIREMENTS                                    |                                                              | 86       |

|           |                                                                 | nory Cycle Time<br>plementary MOST Logic Circuit             | 86<br>88 |

| 11.0      | PROGRAM FOR THE NEXT PHASE 9                                    |                                                              |          |

| 12.0      | BIBLIOGRAPHY                                                    |                                                              | 91       |

|           |                                                                 |                                                              |          |

PRECEDING PAGE BLANK NOT FILMED.

## NAS8-20594

## LIST OF ILLUSTRATIONS

| Figure | Title                                                                                                                                                       | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | Information Stored on Plated Wire                                                                                                                           | 3    |

| 2      | Stoner-Wohlfarth Astroid                                                                                                                                    | 4    |

| 3      | Current and Voltage Output of Plated Wire                                                                                                                   |      |

| 4      | Ideal Magnetization Curves                                                                                                                                  | 7    |

| 5      | Cross-Section of MOS Transistor and Associated<br>Characteristic Curves                                                                                     |      |

| 6      | MOS Plated Wire Memory - 512 Words 26 Bits Each                                                                                                             | 13   |

| 7      | Memory Stack Construction                                                                                                                                   |      |

| 8      | Cross-Sectional Schematic Diagram of A MOS<br>Transistor Chip Showing the Location of Capacitive<br>and Resistive Elements                                  |      |

| 9      | Cross-Sectional Schematic Diagram of General<br>Instrument's MEM517A Showing Gate Metalization<br>Overlap of Source and Drain                               | 29   |

| 10     | Equivalent Circuit of a MOS Transistor                                                                                                                      | 30   |

| 11     | Compositive Equivalent Circuit of a High Current MOS<br>Transistor and Its Driving Source Impedance Used to<br>Determine Output Current Rise and Fall Times |      |

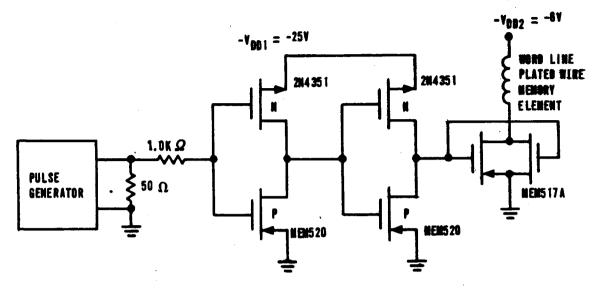

| 12     | Schematic Diagram of MOS Test Circuit Used to Drive<br>The Plated Wire Memory Element                                                                       |      |

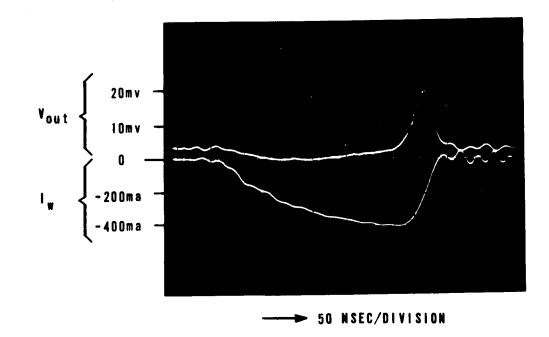

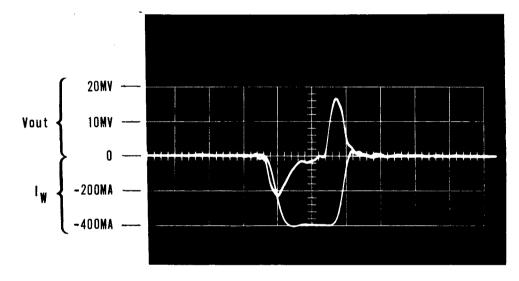

| 13     | Photograph of Word Current Waveform and Sense<br>Voltage Waveform Obtained With the Above Circuit                                                           |      |

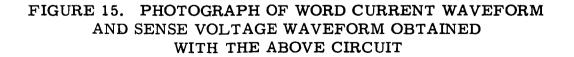

| 14     | Schematic Diagram of Complementary MOS Transistor<br>Word Driver                                                                                            |      |

| 15     | Photograph of Word Current Waveform and Sense<br>Voltage Waveform Obtained With the Above Circuit                                                           |      |

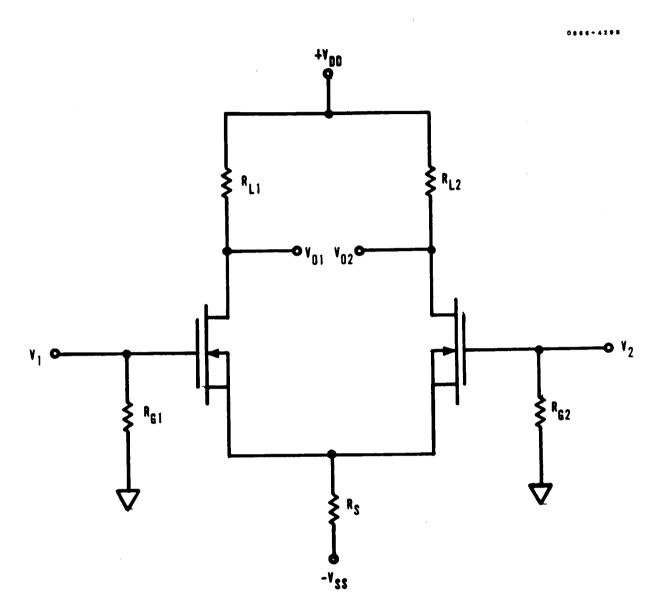

| 16     | MOST Differential Amplifier                                                                                                                                 | 34   |

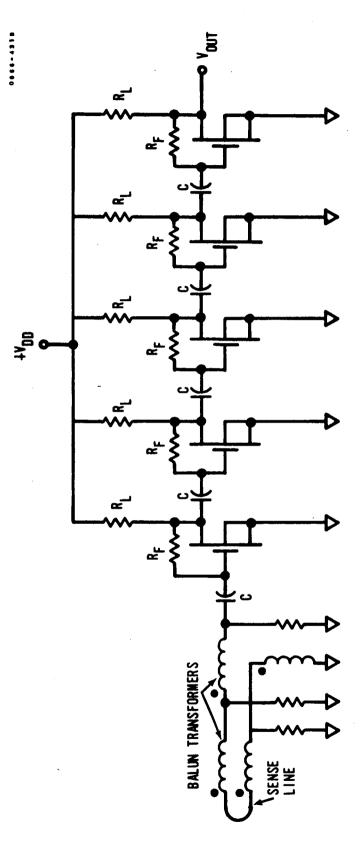

| 17     | AC Coupled MOST Sense Amplifier                                                                                                                             | 35   |

## LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                                                                                                      | Page  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 18     | Monometallic Interconnection Technique For the Elimination of Conductor Interfaces                                                         | 37    |

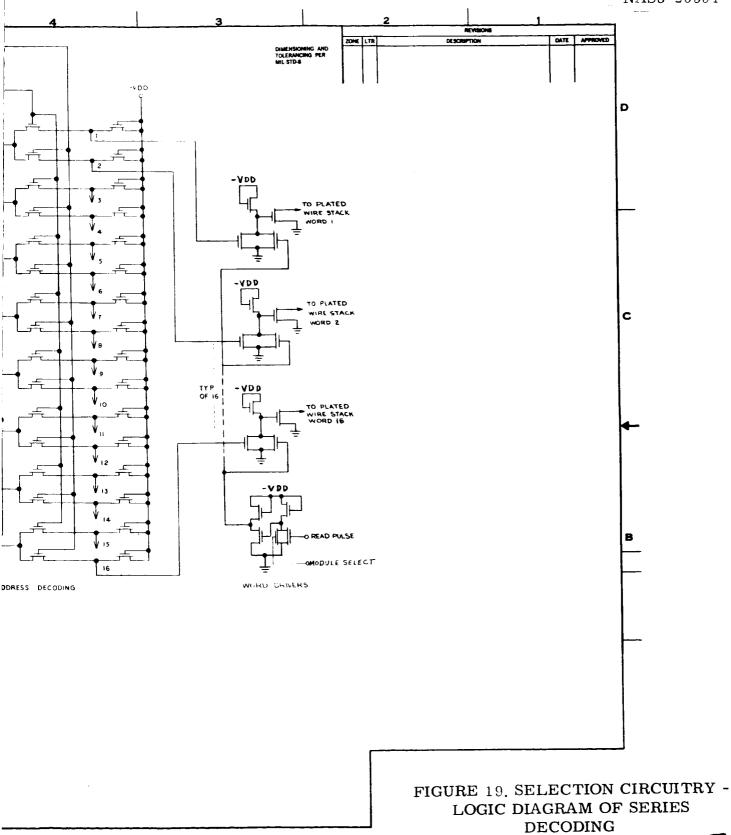

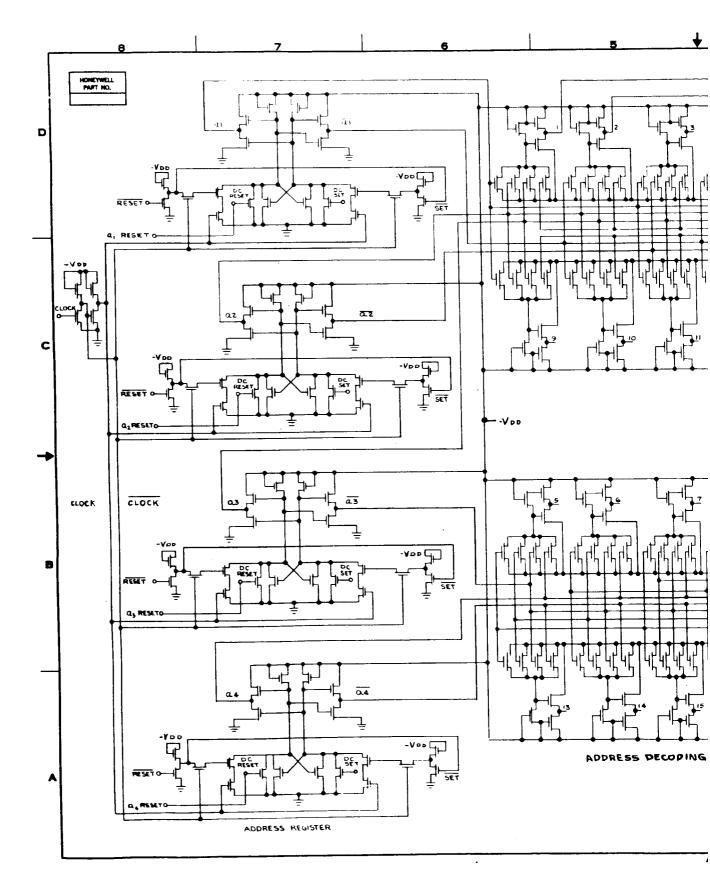

| 19     | Selection Circuitry - Logic Diagram of Series Decoding                                                                                     | 41/42 |

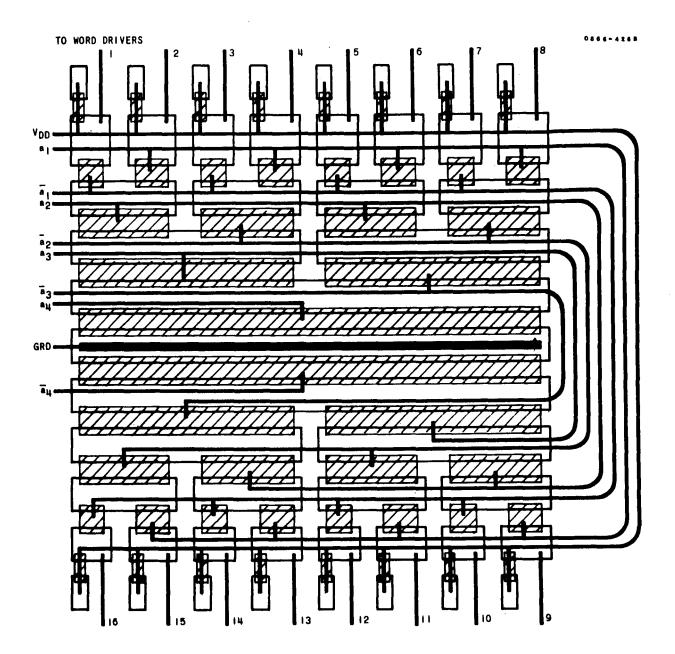

| 20     | Selection Circuitry - Logic Diagram of Parallel<br>Decoding                                                                                |       |

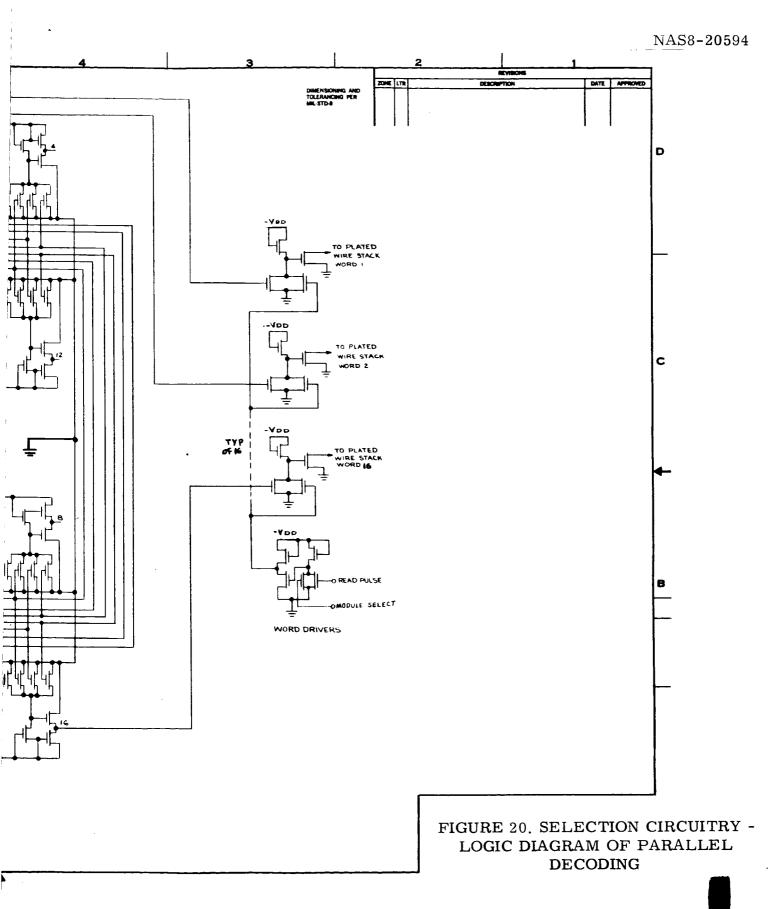

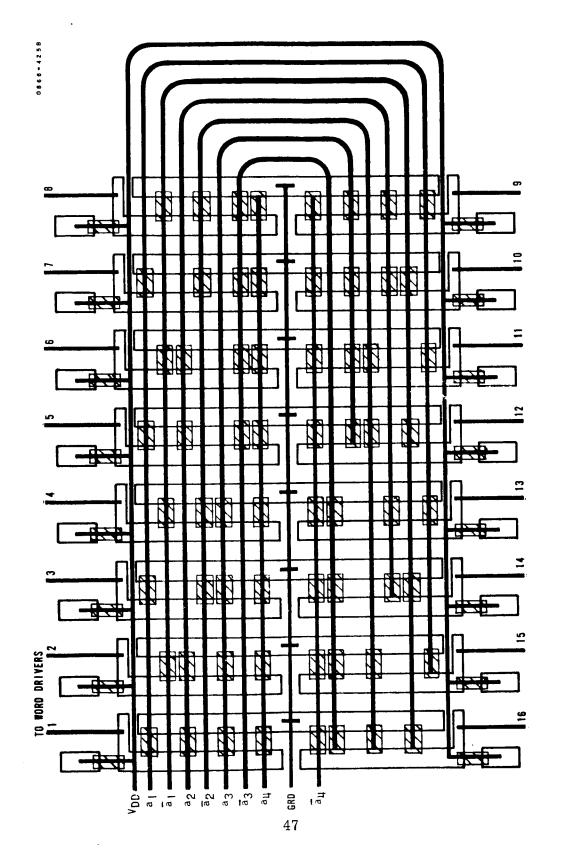

| 21     | Selection Circuit Chip - 16 Words                                                                                                          | 45    |

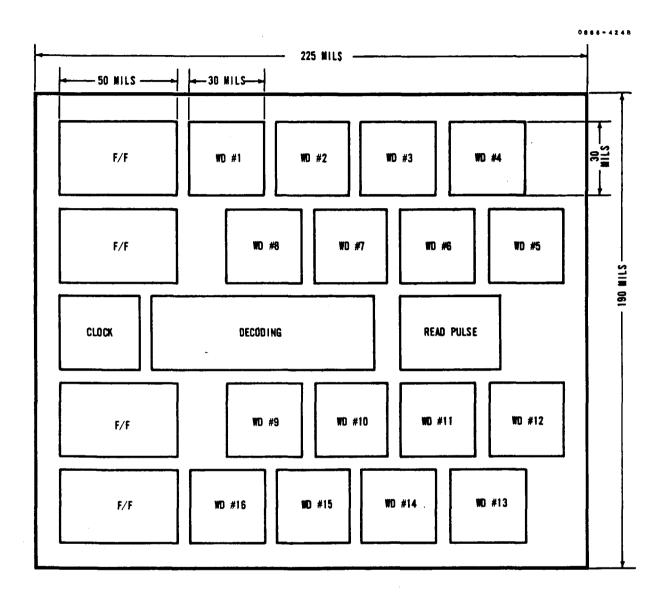

| 22     | Chip Layout of Four-Bit Series Decoding                                                                                                    | 46    |

| 23     | Chip Layout of Four-Bit Parallel Decoding                                                                                                  |       |

| 24     | A 3-Input NAND Gate Constructed With Both Bipolar<br>Devices and MOS Devices. (The Metal-To-Silicon<br>Contacts are Marked With An ''X''.) |       |

| 25     | Cross-Section of A Silicon MOST Chip Showing the Diffused Crossover Technique                                                              | 50    |

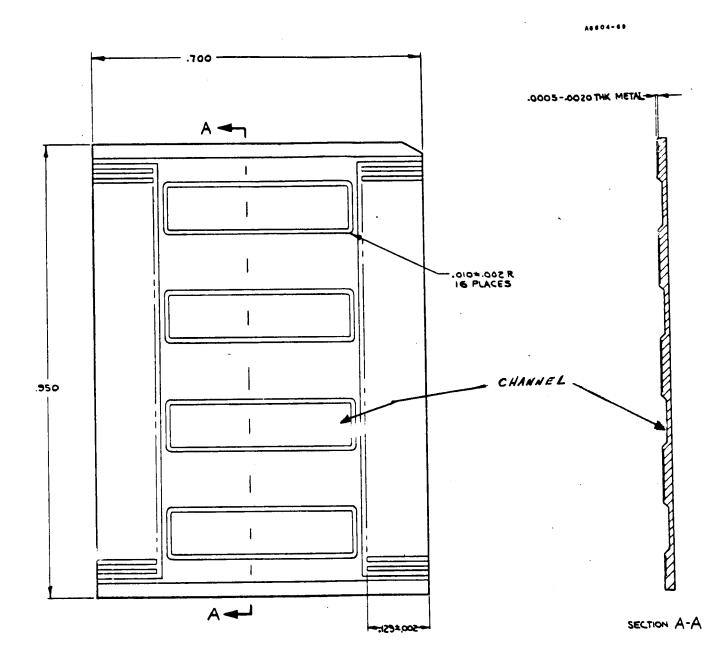

| 26     | Substrate Sketch                                                                                                                           | 54    |

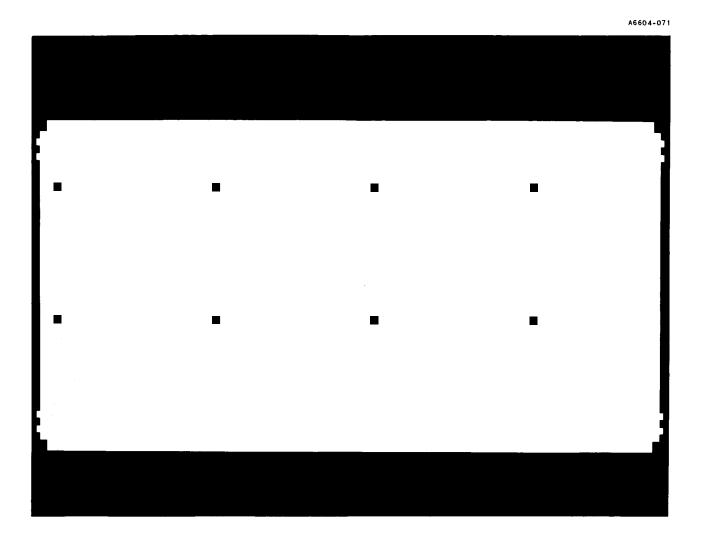

| 27     | SiO Mask Layout                                                                                                                            | 55    |

| 28     | Conductor Layout                                                                                                                           | 56    |

| 29     | Cross-Sectional View of A Silicon Dice Mounted In<br>A Channel of the Substrate                                                            |       |

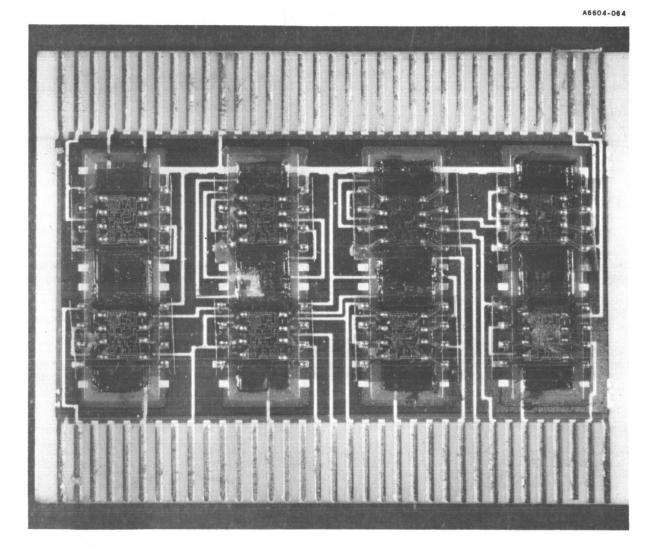

| 30     | Completely Assembled Package Prior to Sealing                                                                                              | 59    |

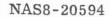

| 31     | Printed Circuit Board Soldered Connection                                                                                                  | 60    |

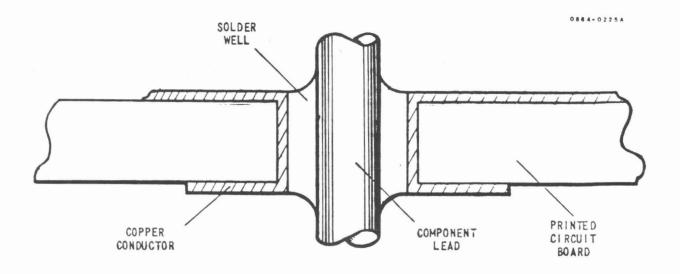

| 32     | Eyeleted Bond                                                                                                                              | 60    |

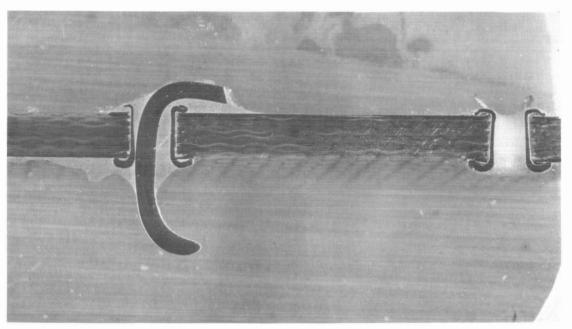

| 33     | Weld Bond                                                                                                                                  | 61    |

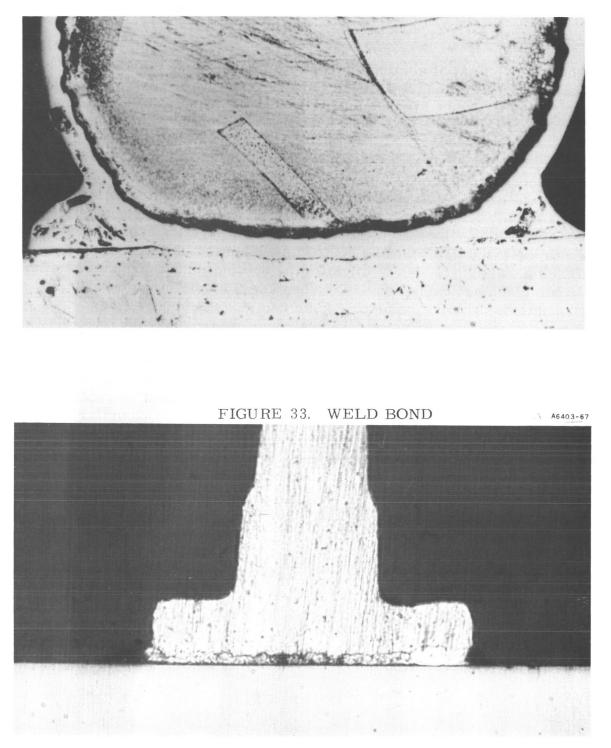

| 34     | Thermal Compression Bond                                                                                                                   | 61    |

| 35     | Sketch of Molecular Bond                                                                                                                   | 63    |

| 36     | Microphoto of Molecular Bond                                                                                                               | 64    |

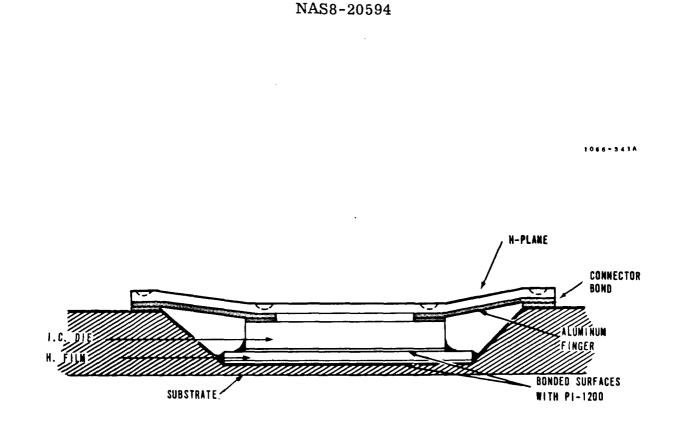

| 37     | H-Plane Diffusion Bond Concept                                                                                                             | 66    |

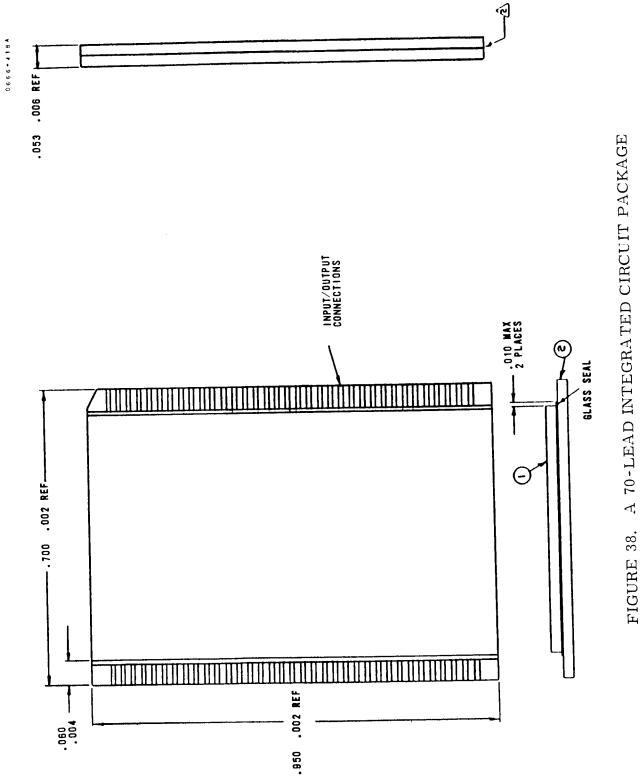

| 38     | A 70-Lead Integrated Circuit Package                                                                                                       | 68    |

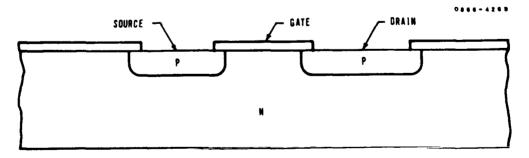

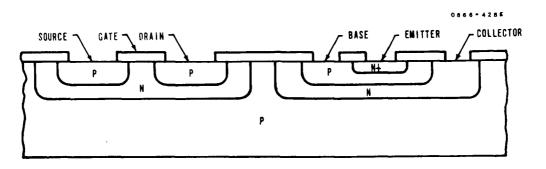

| 39     | Sketch of P Channel Enhancement Mode MOST Chip                                                                                             | 70    |

.

r ,

. . . .

## LIST OF ILLUSTRATIONS (Continued)

| Figure | Title                                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------|------|

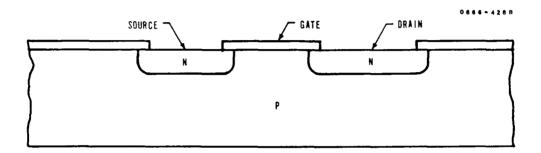

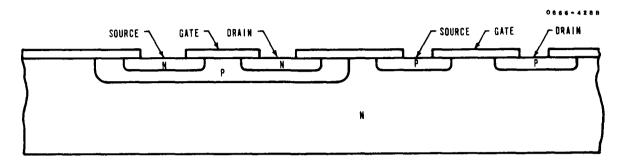

| 40     | Sketch of N Channel Enhancement Mode MOST Chip<br>Using P Type Starting Material                                           | 72   |

| 41     | Sketch of N Channel Enhancement Mode MOST Chip<br>Using N Type Starting Material                                           | 72   |

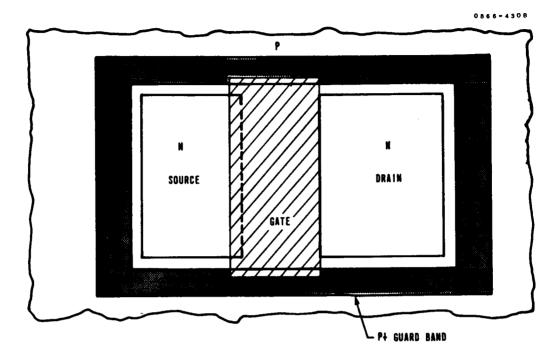

| 42     | A Depletion Mode N Channel MOST Utilizing A P+ Guard<br>Band For Controlling Surface Inversion Between Source<br>and Drain |      |

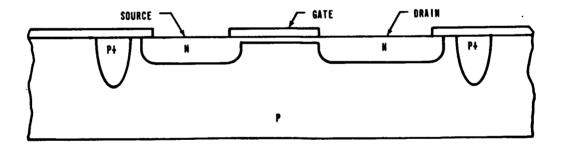

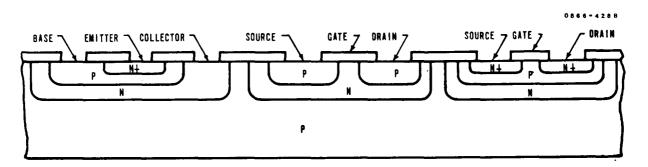

| 43     | Sketch of P Channel MOST and Bipolar NPN Transistor<br>(Common Collector) in the Same Chip                                 |      |

| 44     | Sketch of Isolated P Channel MOST and NPN Bipolar<br>Transistor in the Same Chip                                           |      |

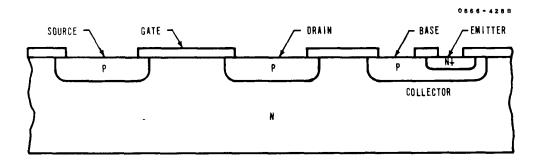

| 45     | Sketch of Complementary P Channel and N Channel MOSTs in the Same Chip                                                     |      |

| 46     | Sketch of Complementary MOSTs and NPN Bipolar<br>Transistor in the Same Chip                                               |      |

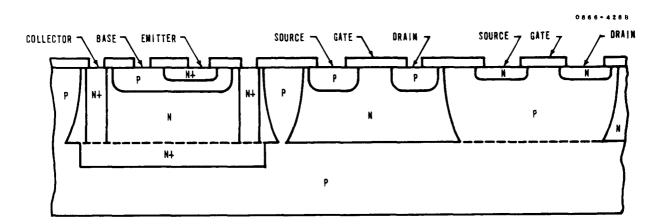

| 47     | Sketch of Complementary MOSTs and A High Current<br>NPN Bipolar Transistor in the Same Chip Constructed                    |      |

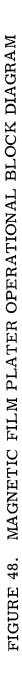

| 48     | Magnetic Film Plater Operational Block Diagram                                                                             | 81   |

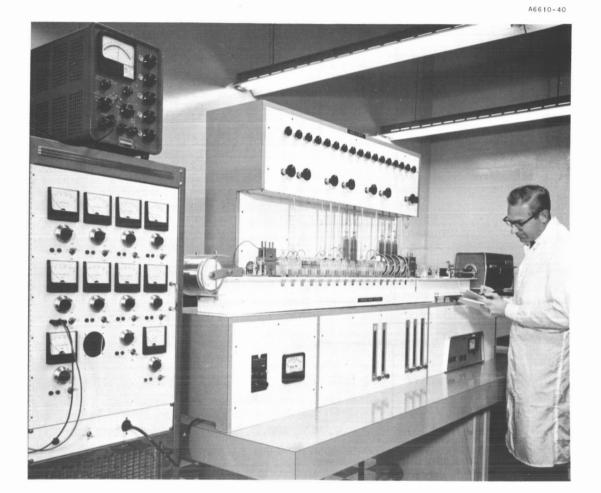

| 49     | Magnetic Thin Film Wire Plater                                                                                             | 82   |

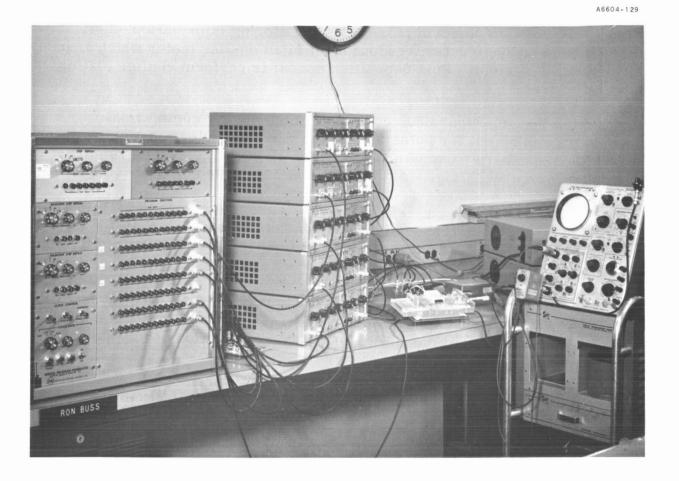

| 50     | Pulse Test Equipment                                                                                                       | 84   |

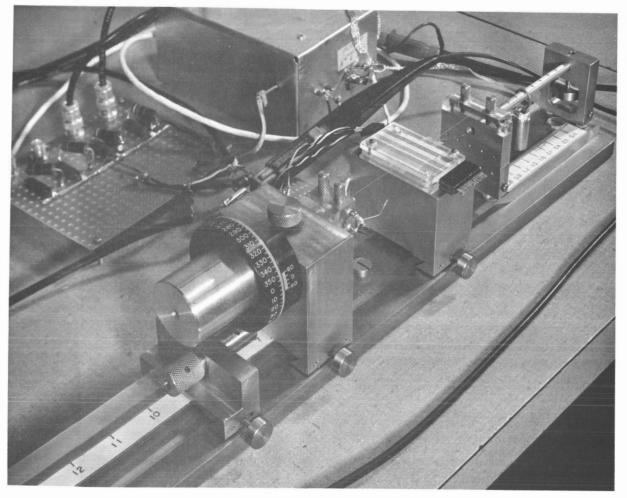

| 51     | Torsional Strain - Skew Equipment                                                                                          | 85   |

| 52     | Schematic Diagram of an Address Decoding Network                                                                           | 87   |

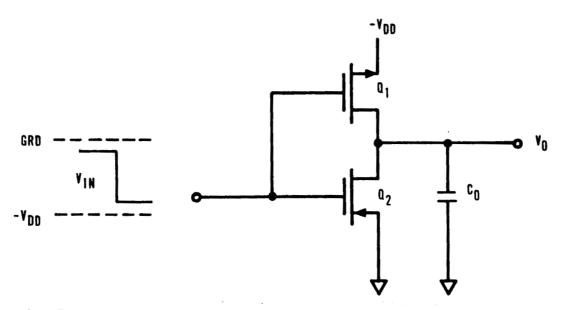

| 53     | MOST Inverter Circuit Constructed As (a) Single Type<br>MOSTs (b) Complementary MOSTs                                      | 89   |

| 54     | Complementary MOST Logic Power Dissipation As A<br>Function of Clock Rate For A 1,000-Circuit System                       |      |

| 55     | Complementary N and P Channel MOST Logic<br>Mechanization                                                                  | 93   |

#### 1.0 FOREWORD

This is the final report for the six-month study phase of contract NAS8-20594 and covers the six-month period beginning 11 March 1966 and ending 11 September 1966.

#### 2.0 REVIEW OF OBJECTIVES

The objective of this program is to determine the interface problems which exist between and within plated wire memories and MOS memory electronics, with an ultimate view of reducing the total number of such interfaces.

#### 3.0 INTRODUCTION

Metal oxide semiconductor (MOS) integrated circuitry has been heavily investigated as a means of producing low cost, low power, highly reliable digital computer logic circuits.

Plated wire elements have been investigated in a similar manner to produce the identical goals within the memory area.

While these separate efforts have proven successful, the large gray area of memory electronics remained untouched. This interface area has been thoroughly investigated during the study phase of this contract and it has been shown feasible to design the memory electronics with MOS devices. A spaceborne computer constructed of MOS circuitry and a plated wire memory can provide considerable improvement in reliability over present day computers.

The interface problems between plated wire memories and MOS devices were determined, and solutions to these problems investigated and evaluated. The most important interface areas are:

- 1. Package compatibility between the plated wire stack and the MOS devices.

- 2. Interconnection of the memory and MOS devices.

- 3. Interconnection of the various MOS functional blocks.

- 4. Total reduction of interfaces and interface connections.

- 5. Manufacturing compatibility of the plated wire and the MOS devices.

- 6. Power and speed requirements.

Each of these areas is discussed in detail in the following sections of this report.

Brief descriptions of the plated wire element and the MOS devices are contained in the following paragraphs.

#### 3.1 Plated Wire

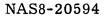

A plated wire memory element consists of a plated wire with an orthogonal current drive strap, as shown in Figure 1. Since the magnetic film has a preferred orientation of magnetization in the circumferential or easy direction, and exhibits a rectangular hysteresis loop, the two remanent storage states are oriented either clockwise or counterclockwise. In the axial or hard direction, the magnetization is reversible and linear.

During the READ mode a current passed through the word strap produces a field which is parallel to the hard axis. This field rotates the stored remanent magnetization from its circumferential direction into alignment with the hard axis thereby inducing a voltage in the bit wire, which functions as a sense line during the read operation. The polarity of the induced voltage is dependent upon the direction of the remanent state. When the word field is less than the film anisotropy,  $H_k$ , the removal of the word current will permit the magnetization vector to fall back to its original position. This constitutes a nondestructive readout (NDRO).

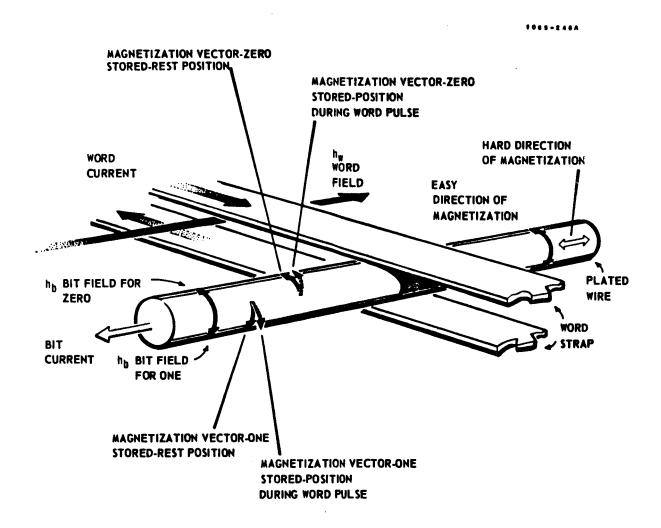

The conditions necessary for magnetization reversal by the application of circumferential and axial fields to result in an NDRO memory may be understood by referring to Figure 2. This figure is the Stoner-Wohlfarth astroid<sup>(1)</sup> as corrected for the existing conditons of nonpure rotational switching. Outside the astroid, reversible switching occurs. In between are areas where the switching mechanism is not clearly defined, and the extent of this area is a measure of the quality of the film. The smaller the area, the better the film. For NDRO operation, the orthogonal components ( $h_w$  and  $h_b$ ) of the applied field H must each be within the NDRO zone, and their simultaneous vector sum must also not exceed the inner curve of the astroid. Not shown in Figure 2 are the effects of

•

#### FIGURE 1. INFORMATION STORED ON PLATED WIRE

FIGURE 2. STONER-WOHLFARTH ASTROID

skew and dispersion which occur to some extent with all films. Skew is the term used for the angle between the easy axis distribution median value and some reference direction, while angular dispersion refers to the angular dispersion around this median. Both these effects are undesirable, and in effect reduce the effective working area for reversible switching.

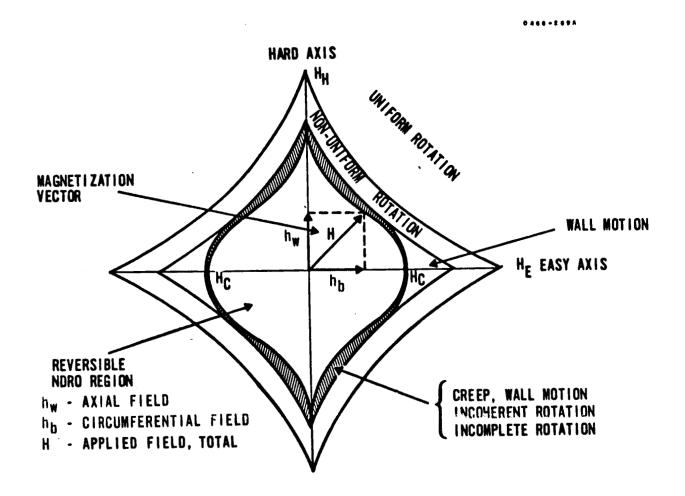

The output of a single plated wire bit is shown in Figure 3.

During the WRITE mode the bit current produces a circumferentially oriented field. This field, when applied in coincidence with the word field, will incline the magnetization in an axial magnitude and polarity of the bit field. Subsequent removal of the word field aligns the net magnetization in the proper bit field direction. The removal of the bit field then completes the write cycle.

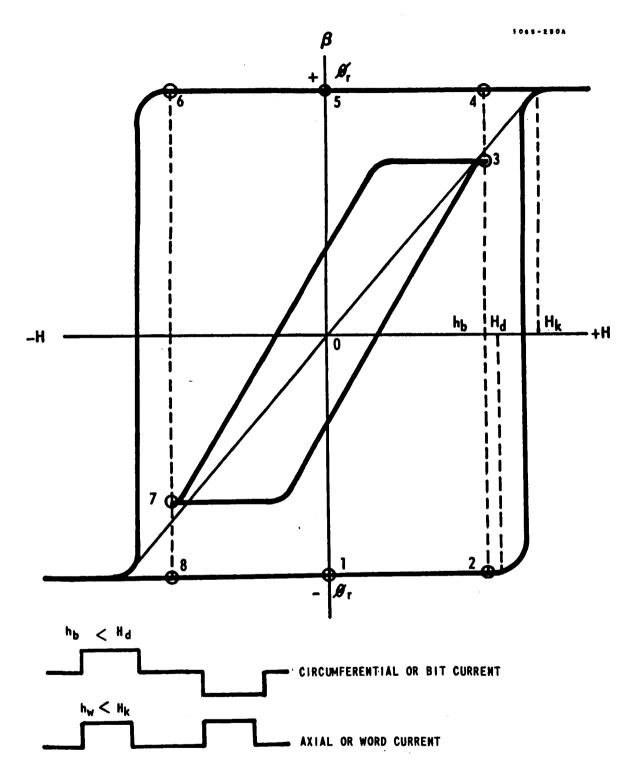

Figure 4 illustrates the write switching cycle using the idealized hysteresis loops of the easy and hard directions. The outer large loop results from solely applying a bit current, and is the easy direction loop. The inner linear curve results from the application of only an axial or word field. The remaining third curve represents the magnetization characteristics when both an axial and circumferential field are applied.

Assuming an initial condition of remanence at point 1, a circumferential bit field  $(H_b)$ , less than the disturb value  $(H_d)$ , is applied resulting in a flux change to point 2. With the addition of an axial field  $(H_w)$ , less than the film anisotropy field  $(H_k)$ , the magnetization vector is inclined in a direction established by the resultant field  $(H_r)$ . This is indicated by a flux change to point 3 on the inner loop. Removal of the axial field aligns the magnetization in the circumferential direction established by the bit field, and is shown as point 4 on the easy direction loop. Subsequently, the circumferential field is removed and point 5 represents the new remanent flux state. Flux reversal from point 5 to point 1 can be described in an identical manner.

#### 3.2 MOS Devices

Switching circuits are normally designed with enhancement mode MOS transistors. These devices are normally off with zero gate voltage; therefore, they act as on-off switches and require only a single supply voltage.

.

SWITCHING CURRENT & VOLTAGE OUTPUT: 1 BIT: PLATED WIRE 1 $\omega$  - WORD CURRENT: ma V<sub>0</sub> - VOLTAGE OUTPUT: mv

HORIZONTAL SCALE: 50 nsec/DIVISION Vertical scale: 5 mv/DIVISION

FIGURE 3. CURRENT AND VOLTAGE OUTPUT OF PLATED WIRE

FIGURE 4. IDEAL MAGNETIZATION CURVES

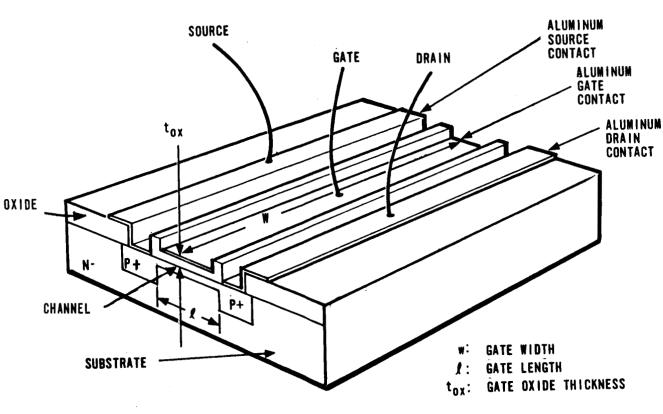

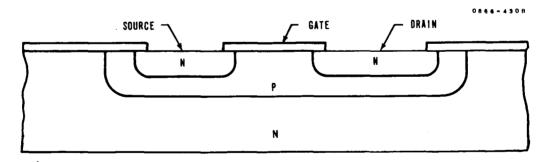

Figure 5a shows the cross-section of a single MOS transistor. It consists of a block of N type silicon called the "body" or "substrate", into which  $P^+$  impurities have been diffused in two parallel strips called, respectively, the "source" and the "drain". In operation, an induced P-region known as the "channel" connects source and drain. The surface of the silicon is covered by a protective layer of silicon dioxide formed during the silicon planar process and etched away along the longitudinal axes of the source and drain, exposing the silicon beneath. Metallic contacts are deposited over the exposed silicon area in the source and drain. The "gate" is a metallic conductor deposited over the oxide between the source and drain and separated from the source, drain, and substrate by the oxide.

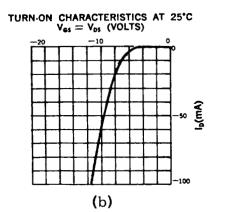

If the gate, source, and substrate are grounded and a negative voltage is applied to the drain, no current will flow between source and drain since the drain-to-body P-N junction is reverse-biased. As a result, the source and drain are isolated from each other. However, if a negative voltage is also applied to the gate, electrons are repelled from the surface region of the silicon immediately beneath the gate and holes are attracted to it. As the gate-to-source voltage, VGS, becomes more negative, this surface region finally changes or "inverts", becoming P-type instead of N-type. This inverted region, called the "channel", provides a path for conduction of the charge carriers between the source and drain so that, if the drain voltage is made appreciably more negative than the source, current flows from source to drain. Before the surface can be inverted to form a channel, the gate voltage must reach a certain threshold value  $V_{T}$  sufficient to neutralize surface charges. Typical processing can achieve a  $V_T$  of approximately -5V. Turn-on characteristics of a typical MOS FET are shown in Figure 5b.

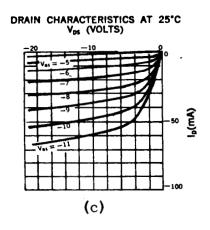

As the gate voltage  $V_{GS}$  becomes more negative than  $V_T$ , the channel depth-- and hence conduction-- increases. For low currents, the channel behaves like a normal ohmic resistance, and the device operates in the linear region of its characteristic curve (Figure 5c), where the drain-to-source current  $I_{DS}$  is proportional to the drain-to-source voltage  $V_{DS}$ . As  $V_{DS}$  becomes more negative, however, the current eventually levels off or "saturates". The magnitude of current flow is now relatively independent of the drain-to-source voltage.

Depletion mode MOSTs operate in a similar manner except for the condition of zero gate voltage. Under this condition, the depletion mode MOST is turned on and conducts a finite value of drain current. This is due to the method of fabrication; a channel is formed in the device during

.

(a)

ł

;

- - - - -

0466-268A

FIGURE 5. CROSS-SECTION OF MOS TRANSISTOR AND ASSOCIATED CHARACTERISTIC CURVES

the manufacturing process. It becomes necessary to reverse bias the gate in order to reduce the drain current to zero. This reverse bias causes the cross-sectional area of the channel to be reduced to zero; hence the source and drain regions become back-to-back diodes and only diode leakage current is present. The depletion mode device has certain characteristics which make it more useful as an amplifier.

The more detailed characteristics of both the enhancement mode and the depletion mode MOSTs are discussed in other sections of this report.

#### 4.0 SUMMARY

A comparison of address selection methods using MOS transistors was made. The interconnections were minimum where individual word drivers were used for each line. The complete selection circuitry and the associated word drivers are located on the same memory plane as the word lines, hence reducing the stack interconnections considerably.

The circuitry interfacing with the plated wire elements was investigated extensively. This consisted of the word driver and sense amplifier circuits. The limitations of the MOS transistor as a high current switching device were analyzed in terms of its geometry and operating parameters. Data were presented to demonstrate that the projected improvement in geometry and processing of the MOS transistor could enable it to be used effectively as a word driver for a plated wire memory element.

The detailed analysis of an all-MOST differential amplifier was performed to determine its limitations as a memory sense amplifier. The common mode rejection capability, utilizing present devices, does not appear to be sufficient for large common mode voltages, although the future fabrication of devices with better control of  $g_m$  and  $r_d$  will certainly show considerable improvement.

Both the word driver and the sense amplifier functions can be accomplished with MOS devices as will be demonstrated by the feasibility memory to be fabricated during the next phase of the contract.

The reduction of interfaces within a monolithic MOST logic function was investigated. Interconnections and crossovers are accomplished by the

utilization of common diffused regions, diffused "tunnels", and multilayer conductors. Materials and techniques for performing the interconnection and insulation of conductors was investigated also. An additional reduction of interconnection interfaces can be accomplished by the utilization of monometallic interconnection systems. The two most promising approaches appear to be either an all aluminum system or an all gold system. Interface interconnections are further reduced by the utilization of the interconnection concepts developed under a separate contract for use in the MICPAK packaging technique.

The complete selection circuitry for 16 word drivers was designed and a possible chip layout configuration investigated. The selection circuit consists of a four-stage F/F address register, decoding logic, word drivers, and clock circuits.

The fabrication processes of single type MOSTs, and combinations of MOSTs and bipolar transistors were investigated. The major process steps are outlined within the text of this report. As the number of types of devices increases, the complexity of the fabrication processes also increases. The plated wire manufacturing process is discussed briefly, showing the nonexistence of any manufacturing incompatibilities between MOS Devices and plated wires.

The advantages of complementary MOST logic circuitry were investigated. The major advantages over single type MOSTs are a significant increase in operating speed and a considerable reduction in power dissipation.

The cycle time of a 1,000-word plated wire memory utilizing P channel logic and N channel amplifier MOSTs was calculated to be 2.5 microsecond with a power dissipation of approximately 45 watts.

# 5.0 PACKAGE COMPATIBILITY BETWEEN THE MEMORY AND THE MOS DEVICES

The plated wire memory elements and the MOS functional blocks are physically smaller than ferrite toroids and discrete transistors hence, they can be very compatible when contained in the same package. During the course of the study phase of this contract, no aspects of the overall package revealed any incompatibilities between the memory and the MOS devices. The memory organization and package configuration is discussed in more detail in the following paragraphs.

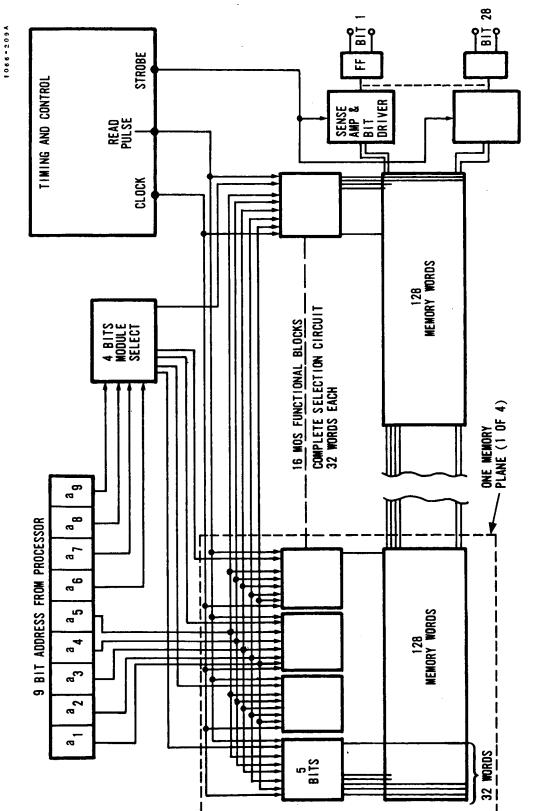

Several approaches to the memory organization were discussed in the third monthly report. The most efficient organization is shown in Figure 6. A 512-word 28-bit (26 active and 2 spares) is used for illustration. The nine address bits from the processor are broken into two groups. The five lower bits are used for word selection in each of the 16 selection circuits. The remaining four bits are decoded and used to select the individual selection circuit. Each selection circuit module contains a five-bit storage register, a decoding tree, and 32 word driver MOSTs. Each word line has its own word driver device instead of the normal selection diode. Each complete plane contains 128 memory words and all the associated selection circuitry. There is one multilayer board for each stack which contains the timing and control, module select, sense amplifiers, bit drivers, and any necessary buffer circuitry required between the memory and processor.

The size of the memory stack is dictated by the following parameters:

- 1. Sense wire spacing

- 2. Word line size and spacing

- 3. Sense line replaceability

- 4. Memory word expansion

- 5. External interface requirements

- 6. Grounding requirements.

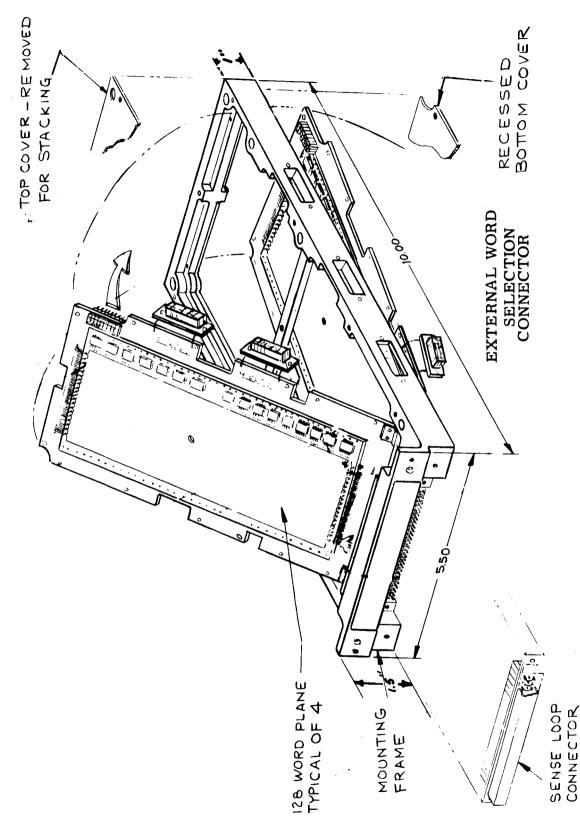

The solution to the optimization of these parameters led to the design of a multilayer memory plane on each side of two multilayer substrate boards as in Figure 7. The substrate boards are hinged on the frame to provide direct accessibility to the MOS functional blocks and sense wires.

FIGURE 6. MOS PLATED WIRE MEMORY - 512 WORDS 26 BITS EACH

NAS8-20594

FIGURE 7. MEMORY STACK CONSTRUCTION

#### 6.0 INTERCONNECTIONS OF MEMORY TO MOS DEVICES

The interconnection of the memory and the MOS devices involves both electrical and mechanical interfaces.

The two major areas of electrical interfacing is the Word Driver and the Sense Amplifier. The MOS word driver circuit has the responsibility of generating current pulses of relatively large magnitude (200 to 400 ma) and with fast rise times (typically 50 nanoseconds). The MOS sense amplifier has the responsibility of detecting a very small signal (typically 5 millivolts) which occurs simultaneously with noise in the range of 50 to 200 millivolts and amplifying it to the voltage level required of the logic circuitry. These two functions can be accomplished with MOS transistors as will be shown in this section of the report.

The mechanical interface involves the reduction of interconnections and the reduction of the intermetallic interfaces present in the remaining interconnections. These are discussed in Sections 7 and 8.

#### 6.1 MOS WORD DRIVER

6

1

The limitations of the MOS transistor as a high current switching device can be analyzed in terms of its geometry and its operating parameters.

Any device used as a word driver must be capable of supplying a pulse of 200 to 400 ma of current with a rise time or fall time of 50 nanoseconds, since the readout of an NDRO plated wire memory element occurs during both the rise and fall time of the word current pulse. The output can be sampled at either time. The magnitude of the output is a direct function of rise time or fall time which is about 50 nanoseconds for a reasonable output. The word driver device considered during this phase of the program is an enhancement type P channel MOS transistor.

The MOS transistor parameters which have the greatest effect on the word driver performance are as follows:

- Drain current: ID

- Input capacitance: C<sub>i</sub>

- Drain-to-Source "On" resistance: R<sub>on</sub>

- Power dissipation

- Device Size (area)

- Breakdown voltages.

The drain current must be of the magnitude of 200 to 400 ma to drive a plated wire memory element. It is desirable to keep the input capacitance as low as possible in order to obtain the fastest possible rise or fall time of the gate-to-source input voltage. The drain "On" resistance contributes to the  $I^2$  R losses, current regulator requirements, and switching speeds. The maximum operating voltages are limited by device breakdown voltages. The device size and power dissipation dictates how many of these devices can be contained in a single integrated circuit chip.

#### Drain Current

The equation for the drain current capability of a MOS transistor is given by Sah (2) as:

$$I_{\rm D} = \frac{\mu_{\rm p} C_{\rm G}}{L^2} \left[ (V_{\rm GS} - V_{\rm T}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right] \text{ in amperes}$$

(1)

where:

$\mu_{\rm p}$  is the surface mobility of holes in cm<sup>2</sup>/volt-second.

$C_{C}$  is the gate to channel capacitance in farads.

L is the gate length (separation of drain and source) in cm.

$V_{GS}$  is the input gate-to-source voltage in volts.

- $V_{T}$  is the turn-on threshold of an enhancement type MOS transistor in volts.

- $V_{DS}$  is the drain-to-source voltage in volts.

The gate capacitance,  $C_G$  is the parallel plate capacitance of the gate electrode and the channel and is given as:

$$C_{G} = 0.08842 \frac{\epsilon_{r L W}}{t_{ox}} pf$$

(2)

where:

$\epsilon_r$  is the relative dielectric constant of the oxide

L is the gate length: cm

W is the gate width: cm

$t_{ox}$  is the oxide thickness: cm

Substituting for  $C_G$ , Equation 1 becomes:

$$I_{\rm D} = 0.08842 \times 10^{-12} \frac{\mu_{\rm p} \epsilon_{\rm r} W}{L t_{\rm ox}} \left[ (V_{\rm GS} - V_{\rm T}) V_{\rm DS} - \frac{V_{\rm DS}^2}{2} \right] \text{ amperes}$$

(3)

The properties  $\mu_p$ ,  $\epsilon_r$ ,  $t_{ox}$ , and L are limited by the materials and processing techniques used in manufacturing the MOS transistors. Surface mobility,  $\mu$ , is a function of the conditions existing at the silicon surface and within the gate oxide, which are very hard to predict and control. (3, 4, 5, 6)

The cited references (2 through 6) indicate that the surface mobility of holes can vary from 94 to  $204 \frac{\text{cm}^2}{\text{volt-sec}}$  and the surface mobility of electrons can vary from 200 to  $500 \frac{\text{cm}^2}{\text{volt-sec}}$ . Therefore, an N channel MOS transistor with similar geometry should be able to handle approximately twice the drain current.

The dielectric constant of the gate insulator is fixed as a result of the use of silicon dioxide which has a dielectric constant of approximately 4.0. Present processes use an oxide thickness,  $t_{OX}$ , of approximately 1000 Å, in order to obtain theoretical breakdown voltages up to 100 volts. The finished oxide surface is highly irregular, with many small areas which are considerably less than the desired 1000 Å thickness. These are the areas that limit the maximum usable gate voltage. This will also allow an increase in device drain current.

The gate length, L, of available devices is nominally 5 microns. This is an optimum value in keeping with present photolithographic techniques. Without pushing the state of the art gate lengths of 3 microns can be produced, and future processes should reduce this to 2 microns.

The gate-to-source threshold voltage,  $V_{\rm T}$ , is not an inherent property of the basic material from which the MOS transistor is constructed, as is the case of the bipolar transistor. The bipolar base emitter threshold voltage is a function of the semiconductor material and doping. The MOS transistor threshold voltage is a function of the conditions existing at the semiconductor surface and within the gate oxide. Since these conditions are more a result of processing than material properties, the threshold voltage varies considerably from device to device (7). (A typical MOS transistor will have a value of  $V_{\rm T}$  equal to 5 volts with a ±1.0 to ±1.5-volt tolerance.) Therefore, the gate width, W, is by far the most practical method used today to control the final current handling capability of the MOS transistor.

The terminal characteristics of the optimum P channel word driver MOS transistor are:

Drain to source voltage: -25 Vdc Gate to source voltage: -25 Vdc Gate to drain voltage: -25 Vdc Gate to source threshold voltage: -5 Vdc Gate to source capacitance: 8 pf Gate to drain capacitance: 5 pf Drain to source capacitance: 5 pf

Drain to source "on" resistance: 12 ohms

This dictates a device with the following approximate geometrical dimensions:

$L_{GC} = Length of channel = 2.0 microns$   $L_{SO} = L_{DO} = Length of entire overlap of gate metalization over source region = 2.0 microns$   $T_{GOX} = Thickness of gate oxide = 750 \text{ Å}$   $W_{G} = Width of gate (channel = 180 mils)$ Chip size: 15 mils x 15 mils

A presently available P-channel MOS transistor capable of handling a maximum of 250 ma dc was examined in order to become more familiar with the device geometry necessary to handle this magnitude of drain current. (This device can handle current pulses in excess of 400 ma with power dissipation being the limiting factor.)

The General Instrument Corp. MEM517A was chosen for this purpose. The most important features of this device, other than the large value of drain current are:

- Drain to source voltage: -30 Vdc

- Gate to source voltage: -25 Vdc

- Gate to drain voltage: -25 Vdc

- Gate to source capacitance: 16 pf

- Gate to drain capacitance: 10 pf

- Drain to source capacitance: 10 pf

- Drain to source "on" resistance: 30 ohms

- Gate length: 0.45 mil

- Gate width: 180 mils

- Chip size: 45 mils x 45 mils

<u>Input Capacitance</u>. The input capacitance of a MOS transistor, together with the driving source impedance determine, to a great extent, the maximum switching speed of the drain current.

As discussed in the previous paragraphs, a MOS transistor capable of handling the required word current will have a very wide gate region which results in a large value of input capacitance (15 to 25 pf). The input capacitance consists of the active gate capacitance, the drain and source overlap capacitances, and the stray capacitance associated with the gate metalization which extends out over the body where external contact to the chip is made. The sum of these capacitances is given as:

$$C_{i} = C_{G} + C_{GS} + (A-1) C_{GD} + C_{GB}$$

(4)

where:

C; = total input capacitance

- $C_{C}$  = active gate capacitance (between gate and channel)

- C<sub>GS</sub> = capacitance between the source and that part of the gate electrode which overlaps the source region.

- $C_{GD}$  = Capacitance between the drain and that part of the gate electrode which overlaps the drain region.

$(A-1)C_{CD}$  = Miller feedback capacitance

C<sub>GB</sub> = capacitance between that part of the gate electrode which extends out over the silicon body (substrate) and provides the bonding area for the external connection.

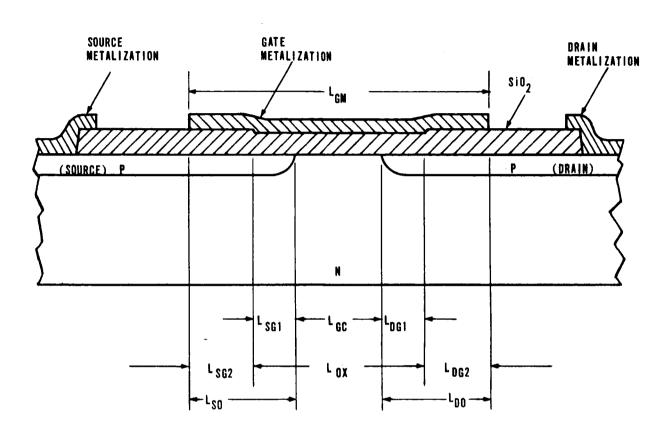

The locations of these capacitive elements within the silicon chip are shown in Figure 8. The input capacitance measures approximately 25 pf which is approximately equal to  $C_i$  of Equation 4, including the Miller effect. In current mode applications such as the word driver, the voltage gain is normally very low, hence the Miller effect becomes negligible. A MEM517A was cross-sectioned to determine its geometrical dimensions. A schematic diagram of the device cross-section is shown in Figure 9. The dimension designations and the measured values are:

$$L_{GM} = Length of gate metalization = 12.5 micron = 9.5 mils$$

$$L_{OX} = Length of gate oxide = 7.5 microns = 0.3 mil$$

$$L_{GC} = Length of channel = 3.5 microns = 0.14 mil$$

$$L_{SG1} = L_{DG1} = Length of lateral diffusion of source and drain respectively under gate oxide = 2 microns = 0.08 mil$$

$$L_{SG2} = L_{DG2} = Length of overlap of gate metalization over source oxide and drain oxide respectively = 2.5 micron = 0.1 mil$$

$$L_{SO} = L_{DO} = Length of entire overlap of gate metalization oversource and drain regions respectively ( $L_{SG1} + L_{SG2}$

and  $L_{DG1} + L_{DG2}$ ) = 4.5 microns = 0.18 mil.

$$T_{GOX} = Thickness of gate oxide = 1000 \text{ Å} = 0.004 mil$$

$$T_{SOX} = Thickness of source oxide = 1000 \text{ Å} = 0.004 mil$$

$$T_{DOX} = Thickness of drain oxide = 1000 \text{ Å} = 0.004 mil$$

From these measurements, the capacitive elements were calculated and are:$$

$$C_{GC}$$

= Gate to channel capacitance = 5.7 pf

$C_{GS}$  = Gate to source overlap capacitance = 7.2 pf

$C_{GD}$  = Gate to drain overlap capacitance = 7.2 pf

$C_{in}$  =  $C_{GC} + C_{GS} + C_{GD}$  = 20.1 pf

This value of  $C_{in}$  does not include the capacitance contributed by the gate protection zener. Taking the zener capacitance into consideration, the total input capacitance compares favorably with the measured value (25.5 pf). Since drain current is a function of gate to channel capacitance,  $C_{GC}$ , only a small part of the total input capacitance contributes to drain current. The remaining capacitances are parasitic and degrading to circuit performance and should be minimized as much as practical. Tolerances associated with present day photolithographic techniques result in the large values of overlap capacitances. Future improvements should reduce this considerably.

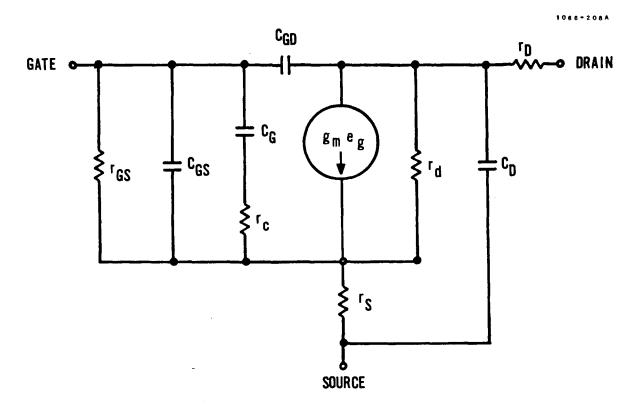

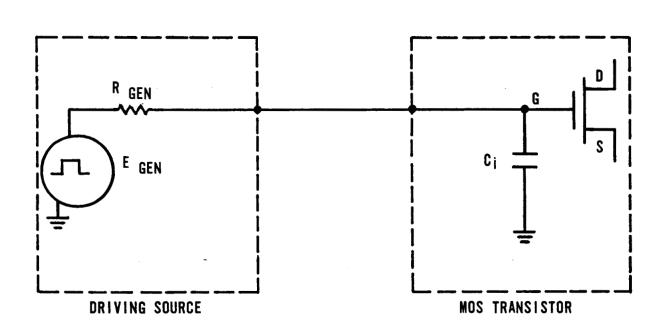

The rise and fall times of the word driver drain current are a direct function of the input capacitance  $C_i$  and the driving source impedance. MOS transistors normally have negligible storage and delay times, therefore the drain current follows the voltage applied to the gate electrode. Since the driving source impedance is normally much greater than the values of  $r_D$ ,  $r_S$ , and  $r_C$ , the equivalent circuit shown in Figure 10 can be reduced to a lumped capacitance  $C_i$ , as expressed by Equation 4. The composite equivalent circuit of the driving source and the MOS transistor can be represented by a simple RC network as shown

in Figure 11. Once the word driver device characteristics have been defined, the input capacitance becomes fixed. The maximum allowable driving source impedance can now be determined. For example, to obtain a word current rise and/or fall time on the order of 50 nanosec with a single MEM517A requires a driving source impedance of:

$$R_{gen} = \frac{50 \text{ nsec}}{4 C_i}$$

$$= \frac{50 \times 10^{-9}}{4 \times 25 \times 10^{-12}} = 500 \text{ ohms}$$

This information can be used to define the geometry of the MOS transistor which drives the word driver device.

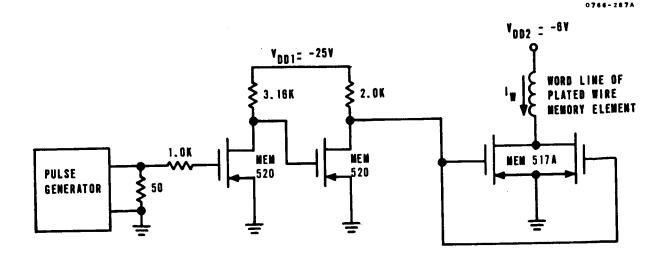

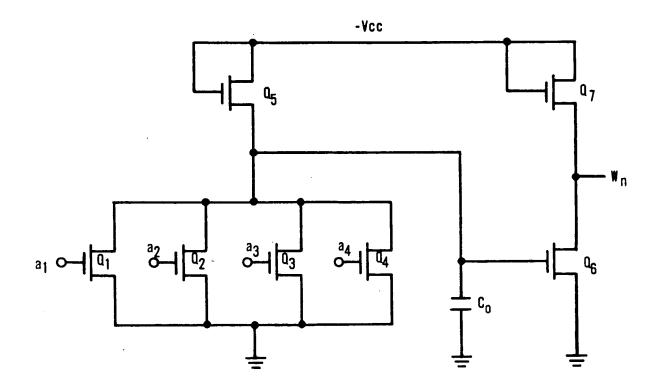

Word Driver Test Circuit. A word driver circuit was implemented as shown in Figure 12. The circuit was used to drive an actual plated wire memory element. Information was stored on the wire by use of a dc writing technique where a current is passed through the plated wire in either of two directions. A "1" or "0" is stored as a result of the direction of current flow. The NDRO mode of reading was utilized and the resultant output voltage waveform and the word current is shown in Figure 13. The magnitude of  $I_w$  was 400 milliamps and was controlled by adjusting the supply voltage  $V_{DD2}$ . The output voltage was approximately 17 millivolts. The value can be expected to be reduced to 8 to 10 millivolts under normal stack operating conditions where the stored bit becomes disturbed and the output signal becomes attenuated. The large rise time of the word current  $(I_w)$  was a result of the RC time constant associated with the 2.0 k ohm resistor and the input capacitance of the MEM517As. Since the "on" resistance of the MEM520 is typically 250 ohms, the capacitance discharges very rapidly, and a 50 nanosecond fall time of the word current is obtained. It is during this fast fall time that the output of the plated wire is sensed. This circuit illustrates the duty cycle problem inherent when only P channel devices are used. In order to obtain the proper output voltage swing, the load resistor must be at least 10 times as large as the "on" resistance of the active MOS device. This results in a long RC time constant, hence a low duty cycle. The use of complementary (N channel and P channel) enhancement mode MOS transistors allows a more efficient circuit to be mechanized as illustrated in Figure 14. The on resistance of both MOSTs is on the order of 250 ohms, providing a short RC time constant during both turnon and turn-off of the word current transistor. The word current pulse

and the output signal are shown in Figure 15. As can be seen the use of complementary MOSTs allows the memory to operate at a faster cycle time. The overall cycle time (including address and decoding logic) of a large memory may be reduced from about 8 to 10 microseconds to about 2 to 4 microseconds.

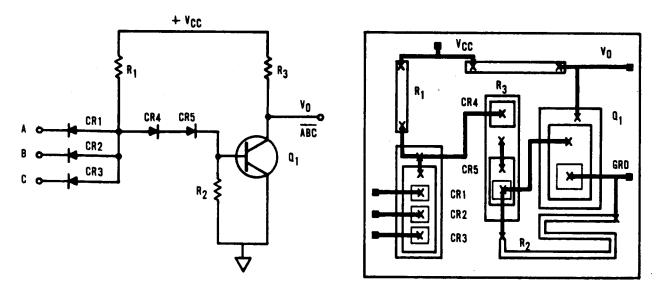

#### 6.2 MOS SENSE AMPLIFIER

The requirements of a circuit to amplify the small, high frequency output of a plated wire memory stack into a usable logic level signal, can be summarized as follows: Each data signal is typically a few millivolts in amplitude and generally contains a fundamental of at least 20 MHz. The amplifier must be capable of rejecting large common mode signals both during and before signal time. The largest transient signal occurs prior to "read-time" as a result of a preceding "write" or "store" operation. Naturally, the circuit must recover from these input transients in order to accept the next data output signal. Since the operating output signals from a memory sense line cannot be predicted on a repetitive basis, the amplifier requirements are more of a quasi-transient nature.

A common, straightforward approach to the design of this circuit is a dc-coupled, differential amplifier. This approach minimizes the number of associated discrete components, thus resulting in minimum interconnects and package size. Direct coupling the stages of the amplifier also improves the recovery characteristics of the circuit. This improvement is simply a result of the much lower inter-stage RC time constant. As usual, however, a trade-off between this advantage and the dc offset problem must be considered. Offset is a result of differences in the linear region characteristics of the individual stage devices, i.e., in the case of the FET's the quiescent levels of the drains are important. Naturally, the offset of one stage will affect the operating point of the following stage. In all direct coupled differential amplifiers this problem is minimized by matching devices; however, the remaining value is referred to the input in order to evaluate its significance in the application. The worst case memory stack output must be capable of overcoming the amplifier's input offset and provide enough signal to be amplified to the detector to the trigger level.

Typical Amplifier Specifications:

Operating temperature range: -55°C to 125°C Voltage supply tolerance: ±5 percent

| Voltage gain:                | 6000 to 8000 volts/volt |  |

|------------------------------|-------------------------|--|

| Operating frequency range:   | 0 to 20 mHz             |  |

| Common mode rejection ratio: | 1000 : 1 (to 1V)        |  |

| Common mode frequency range: | 0 to 20 mHz             |  |

| Minimum input voltage range: | 1 to 10 mv              |  |

| Offset (referred to input):  | 1 mv                    |  |

The most difficult specification to meet, using MOS devices, is the common mode rejection ratio. To obtain common mode rejection, a balanced circuit such as a differential amplifier is required. In a differential amplifier the first stage must provide the common mode rejection since differential signals at the output of the first stage that are caused by common mode input signals are indistinguishable from differential outputs caused by differential inputs. Therefore, the common mode rejection ratio of a differential amplifier depends upon the symmetry of the first stage of the differential amplifier. For the circuit shown in Figure 16, it was shown in the 5th monthly report that the common mode rejection ratio is limited by

$$CMRR = (1 + \mu) \left( \frac{\mu}{\delta \mu} \right)$$

where  $\mu$  is the average voltage gain,  $\delta\mu$  is the deviation of  $\mu$  from the average in each side. For a common mode rejection ratio of 1,000 the change in voltage gain must be less than

$$\frac{1+\mu}{1,000}$$

$$\frac{\delta\mu}{\mu} = \frac{\delta \mathbf{r}_{d}}{\mathbf{r}_{d}} + \frac{\delta g_{m}}{g_{m}} \leq \frac{1+\mu}{1,000}$$

The  $\mu$  is usually less than 30 so that

$$\frac{\delta\mu}{\mu} = \frac{\delta r_{d}}{r_{d}} + \frac{\delta g_{m}}{g_{m}} < 0.03$$

Obtaining a three percent match in voltage gain is unrealistic at the present time especially with an integrated MOST circuit. Other unbalances in circuit parameters will also decrease the common mode rejection ratio so that a slightly tighter specification on  $\mu$  would be required in an actual circuit.

Another factor which affects the design is the bandwidth. For an MOS transistor the maximum bandwidth is approximately.

$$f = \frac{1}{2 \pi R_{L} \left[ C_{ds} + C_{dg} + C_{i} \right]}$$

where  $C_{ds}$  is the drain to source capacitance,  $C_{dg}$  is the drain to gate capacitance,  $C_i$  is the input capacitance to the next stage, and  $R_L$  is the load resistor. The approximate gain that can be obtained with one stage is:

$$G = g_m R_{I}$$

The gain bandwidth product is

$$GBW = Gf = \frac{g_m}{2\pi \left[C_{ds} + C_{dg} + C_i\right]}$$

Using typical values for  $C_{dg}$ ,  $C_{ds}$ , and  $C_i$  of 0.5, 1.5 and 6 pf's respectively gives

GBW =

$$(g_m)$$

(2) 10<sup>10</sup>

For a bandwidth of 20 MHz

$$G = g_m \times 10^3$$

At the present time the transconductance is between 5 and 10 millimhos for the values of capacitance that were assumed. The gain per stage is between five and ten and  $R_L \cong 1 \text{ K } \Omega$ . Thus at least four stages are required, and probably five will be necessary, to meet the gain requirements.

The above considerations indicate that a differential amplifier meeting all the requirements listed is not feasible at the present time. Additional effort in reducing the variations in the MOST parameters could lead to a practical differential type sense amplifier.

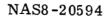

An approach to a sense amplifier which appears to be more practical is shown in Figure 17. In this approach the desired common mode rejection ratio is obtained with balum transformers. Obtaining the common mode rejection in this way permits the use of a single-ended amplifier. To obtain a gain of 8000, five stages are needed. Several features of the single-ended amplifier are:

<u>Biasing</u> - an enhancement mode MOS transistor is easy to bias with a single drain to gate resistor.

<u>Drift</u> - MOS transistors are noted for high drift rates. Therefore, the dc gain must be much less than the ac gain. Two methods are available for reducing the dc gain: ac coupling, and dc feedback. AC coupling is shown in Figure 17 since dc feedback has the disadvantage of requiring the feedback path to have a very low cutoff frequency. The low frequency break would occur at about 100 Hz. DC feedback around each stage is an alternative method that could be used, but it would require more parts that are more difficult to integrate.

<u>Strobing</u> - a five stage sense amplifier would present problems in strobing since each sense amplifier may have a different time delay. The strobe pulse must arrive at the amplifier at the proper time to block the read noise and pass the signal.

<u>Recovery</u> - an ac coupled sense amplifier requires time to recover from large differential signals that occur during the "write" mode. The recovery time depends upon the coupling capacitors and the saturation impedance levels.

Assuming the gain and bandpass requirements could be met, the remaining general problem areas are in interstage coupling, frequency stability, and threshold drift. If the drift characteristics cannot be more closely controlled, the amplifier would necessarily need to be RC coupled. As previously mentioned, this coupling technique is undesirable where large input transients can be expected. With the use of a more stable gate insulation such as silicon nitride, the device's drift characteristics may be more closely controlled.

The gain-bandwidth (GBW) product may be increased by the optimization of the device geometry. The gain-bandwidth product is given as (8).

$$GBW = \frac{g_m}{2 \pi C_T}$$

(7)

$\mathbf{26}$

where:

for a single stage amplifier:  $C_T = C_{DG} + C_{DS}$

for several cascaded stages:  $C_T = C_{DG} + C_{DS} + C_{GS}$

It can be shown that the GBW product is inversely proportional to the gate length. By reducing the gate length by a factor of 2;  $g_m$ , and as a direct result, GBW will be increased by a factor of 2. Other factors which can be used to increase the GBW product are: N channel transistors have a carrier mobility factor at the surface which is greater than that of a P channel device by at least a factor of 2; gate-to-source overlap capacitance can be minimized by the use of more accurate photolithographic techniques; the gate-to-drain capacitance (which is the familiar Miller feedback capacitance) can be minimized by using a depletion mode device which has the gate electrode offset from the drain region; and drain to source junction capacitance can be minimized by the reduction of the drain surface area. The implementation of all these factors tend to indicate that the GBW of a multistage MOS transistor amplifier could be increased by a factor of 2 to 5. This should provide an N channel device with the following parameters:

Breakdown voltages: 30 Vdc minimum

$g_m$ , transconductance: 12,000  $\mu$ mhos

C<sub>DG</sub>, drain to gate capacitance: 0.1 pf

$C_{DS}$ , drain to source capacitance: 0.8 pf

C<sub>GS</sub>, gate to source capacitance: 3.4 pf

GBW, gain bandwidth product: 450 mc

1066-2104

## DRAIN SOURCE GATE METALIZATION \$i0<sub>2</sub> Z' GS C<sub>gd</sub> C<sub>G</sub> . C<sub>GS</sub> rgd r c r s ٢D °s C D BODY

FIGURE 8. CROSS-SECTIONAL SCHEMATIC DIAGRAM OF A MOS TRANSISTOR CHIP SHOWING THE LOCATION OF CAPACITIVE AND RESISTIVE ELEMENTS

0766-289/

$L_{\rm GM}$  - LENGTH OF GATE NETALIZATION.

L<sub>OX</sub> - LENGTH OF GATE OXIDE.

L<sub>SG1</sub> - LENGTH OF LATERAL DIFFUSION OF SOURCE UNDER GATE OXIDE.

L<sub>DG1</sub> - LENGTH OF LATERAL DIFFUSION OF DRAIN UNDER GATE OXIDE.

$L_{S62}$  - Length of overlap of gate metalization over source oxide.

$\mathbf{L}_{\textbf{DG2}}$  - Length of overlap of gate metalization over drain oxide.

L<sub>GC</sub> - LENGTH OF CHANNEL.

L<sub>SO</sub> - LENGTH OF ENTIRE OVERLAP OF GATE METALIZATION OVER SOURCE REGION

LDO - LENGTH OF ENTIRE OVERLAP OF GATE METALIZATION OVER DRAIN REGION

FIGURE 9. CROSS-SECTIONAL SCHEMATIC DIAGRAM OF GENERAL INSTRUMENT'S MEM517A SHOWING GATE METALIZATION OVERLAP OF SOURCE AND DRAIN

where: r<sub>GS</sub> = Gate-to-Source oxide leakage resistance

C<sub>GS</sub> = Gate-to-Source capacitance (includes the capacitance contributed by the extension of the gate contact region and over the body).

$C_G$  = True Gate-to-Channel capacitance

$r_c$  = Channel resistance

$C_{GD}$  = Gate-to-Drain overlap capacitance

r<sub>d</sub> = Dynamic drain resistance

$r_S$  = Resistance of source region and ohmic contact

$r_{D}$  = Resistance of drain region and ohmic contact

$C_D$  = Drain-to-Body (or source) capacitance

FIGURE 10. EQUIVALENT CIRCUIT OF A MOS TRANSISTOR

NAS 8-20594

1066-2114

### FIGURE 11. COMPOSITIVE EQUIVALENT CIRCUIT OF A HIGH CURRENT MOS TRANSISTOR AND ITS DRIVING SOURCE IMPEDANCE USED TO DETERMINE OUTPUT CURRENT RISE AND FALL TIMES

FIGURE 12. SCHEMATIC DIAGRAM OF MOS TEST CIRCUIT USED TO DRIVE THE PLATED WIRE MEMORY ELEMENT

32

0766-288A

FIGURE 14. SCHEMATIC DIAGRAM OF COMPLEMENTARY MOS TRANSISTOR WORD DRIVER

50 NSEC/DIVISION

FIGURE 16. MOST DIFFERENTIAL AMPLIFIER

35

## 7.0 INTERCONNECTION OF MOST LSIs AND PLATED WIRE

Once the interconnection system has been solved at the LSI chip level, it becomes desirable to provide a compatible system of external interconnections so that circuit continuity is provided with a minimization of metallic interfaces. The LSI interconnection system is discussed in more detail in Section 8. The technique presently being developed is compatible with an all-aluminum interconnection system.

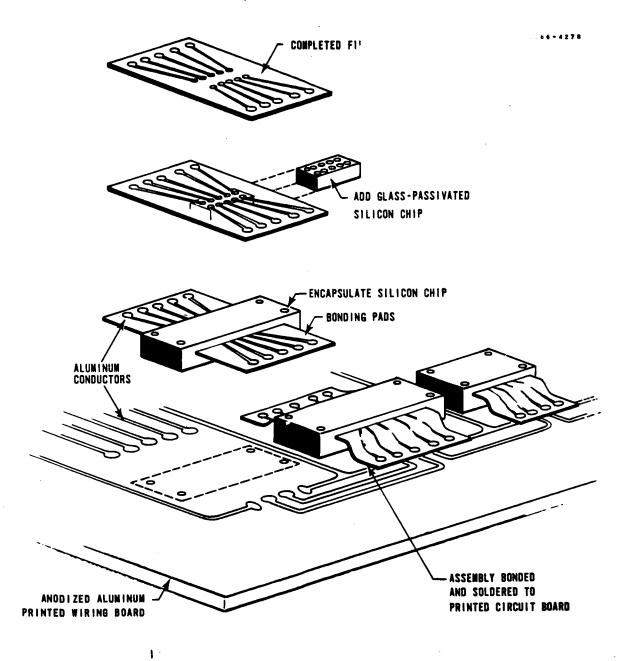

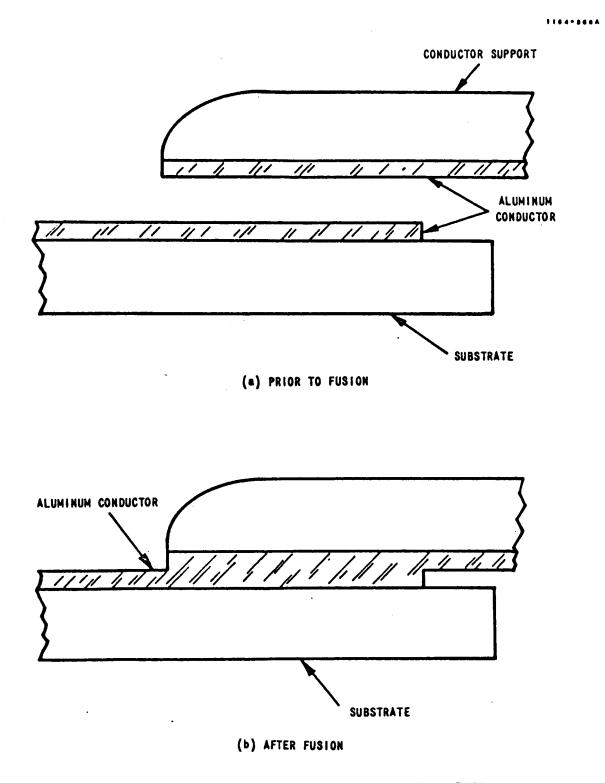

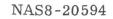

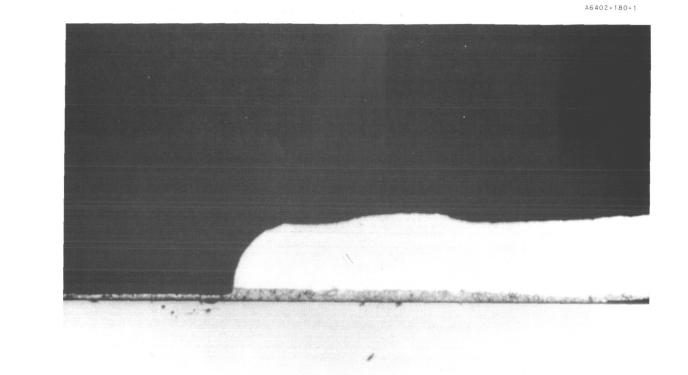

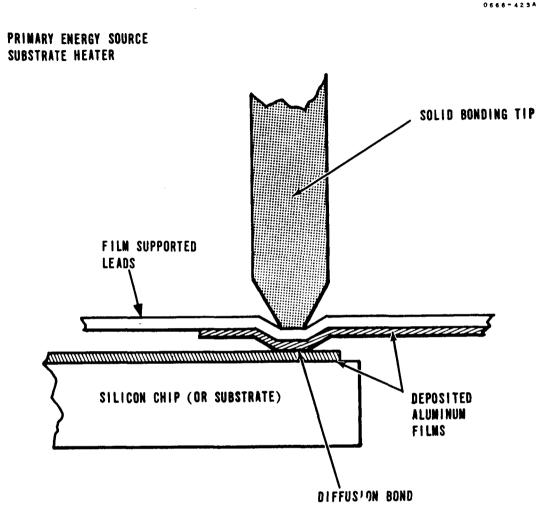

Honeywell has developed a technique for depositing aluminum on a polyimide, "H", film\* This development (partially funded by NADC and RADC development contracts) has proven the feasibility of using vapordeposited aluminum conductors on a supporting polyimide film to perform this interconnection. Polyimide film is similar to Mylar in properties except it can withstand all process temperatures encountered in integrated circuit assembly. The application of this technique to the interconnection of integrated circuits is shown schematically in Figure 18. Briefly stated, the process is:

- 1. Evaporate the conductor onto the film.

- 2. Photoetch the desired interconnect pattern into the conductor metal in a manner analogous to making flexible printed circuits.

- 3. Bond the aluminum conductors on the film to the contact pads on the chip using thermo-compression or ultrasonic bonding.

- 4. Electrically test the chip/lead film assembly.

- 5. Package completed assembly.

- 6. Assemble the packaged circuits onto the anodized printed wiring board (PWB) and attach the lead film conductors to the pads on the substrate.

The use of a polyimide film as a lead support material is discussed in Section 8.

<sup>\*</sup> Manufactured by DuPont under the trade name of KAPTON.

FIGURE 18. MONOMETALLIC INTERCONNECTION TECHNIQUE FOR THE ELIMINATION OF CONDUCTOR INTERFACES Advantages of Film-Supported Leads - The principal advantages of this technique are:

- 1. Elimination of flying leads gives support to leads.

- 2. Prepositioning of leads, eliminating alignment of each individual lead.

- 3. Testing before assembly is packaged will substantially reduce cost by eliminating rejects after packaging.

- 4. Several chips can be attached to the lead film with interconnections provided between chips as well as for external connections. Circuit crossovers are the major limitation on the number of chips that can be attached within a single package.

- 5. The film supported leads along with an anodized aluminum printed wiring board provide a completely monometallic interconnection system.

A plated wire memory plane can be assembled in the same manner as shown in Figure 18. Sufficient space may be allotted on the printed wiring board for the placement of the plated wires and word straps. All the LSIs required for the operation of a single plane can be mounted alongside the memory devices. The interconnection of the LSIs is provided by thin film aluminum conductors which have been deposited on the anodized surface of the aluminum plate. By plating the ends of the memory wires and word straps with a thin film of aluminum, an aluminumto-aluminum bond can be made between the memory wires and the PWB. Therefore the interconnections between the MOST LSIs and the memory wires is performed by a system completely free of bimetallic interfaces.

## 8.0 TOTAL REDUCTION OF INTERFACES AND INTERFACE CONNECTIONS

The reduction of interfaces within the memory system envolves all of the following areas:

- 1. The circuit organization and layout

- 2. The interconnection of MOS devices within a single chip

- 3. The circuit package

- 4. The interconnection of MOS circuitry and the plated wire stack.

The first three areas are discussed in this section of the report and the fourth area is discussed in Section 7.

#### 8.1 CIRCUIT ORGANIZATION AND LAYOUT

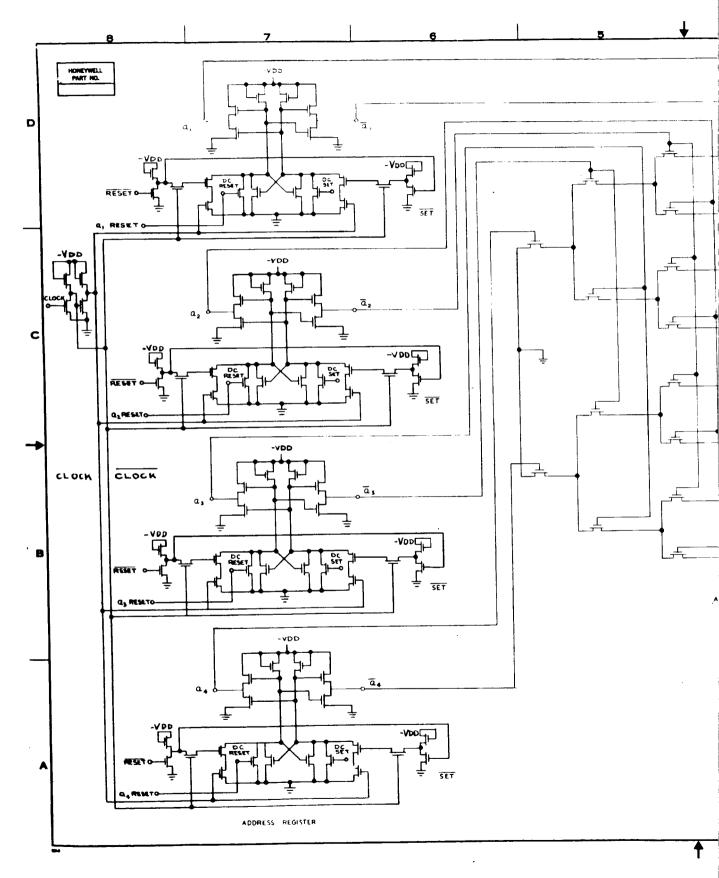

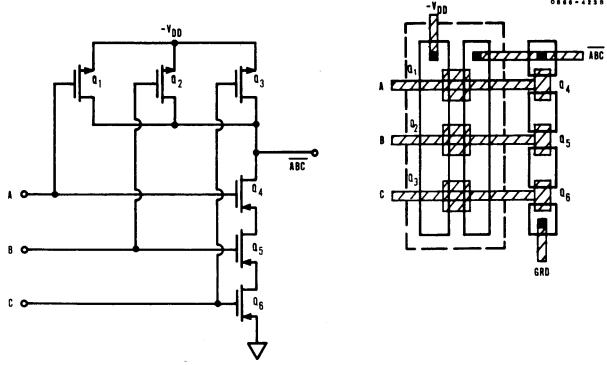

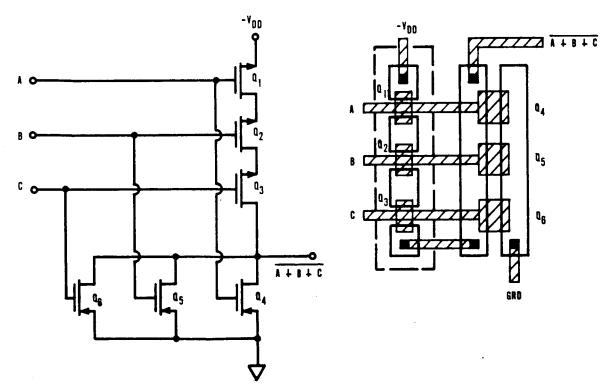

The area allowing the most progress toward the reduction of interfaces is the circuit organization and chip layout. Each MOS chip should contain as much circuitry as practical, being limited only by power dissipation and/or pinouts. The word driver selection circuitry is used to describe how interfaces and interconnections can be reduced at the chip level. The complete address selection circuitry (including address register, decoding logic, word drivers, and clock circuits) for 16 words is shown schematically in Figures 19 and 20. The selection circuitry can be expanded to 32 or 64 words by utilizing larger area chips. The circuit is constructed entirely of P channel MOSTs, all contained within the same silicon chip. The address decoding is mechanized with both series logic and parallel logic. The series decoding logic is illustrated in Figure 19 where the four MOSTs associated with each address are connected in series. The parallel decoding logic is illustrated in Figure 20 where the four MOSTs are connected in parallel. The series decoding has the advantage of requiring fewer MOSTs and less chip area for its implementation.

The four-stage address register has been included as part of the selection circuitry for two reasons: (1) the total number of conductors into the memory stack is reduced considerably and as a result the number of interfaces and interconnections is reduced, (2) the drive requirements imposed upon the address register are reduced considerably. A memory plane will contain one of these modules for each 16 words and only one wire for each address bit will be wired into the plane instead of one wire per word, hence reducing interconnections considerably. An additional logic signal will be required to select the proper module and this signal is coupled into the "Module Select/Read Pulse" circuit.

The decoding logic will be relatively slow due to the high impedance of the MOSTs used (the higher impedance MOSTs require less chip area), hence the turn-on time of the output word driver would be much greater

than the required 50 nanoseconds. The 50 nanosecond current fall time is accomplished by the use of a high speed Read pulse which is gated with the decoding logic and the module select signal to turn the word driver off.

The first approximation to the chip size for a 16-word function is shown in Figure 21. Each small block indicates the area required for the respective circuit. It appears entirely feasible that the complete selection circuitry could be contained on a chip 190 mils by 225 mils. A chip of this size can be produced with reasonable yields in the not too distant future. The larger area chips required for 32 and 64 words should become practical within the next two years.

The decoding logic was laid out into more detail as shown in Figures 22 and 23. The individual MOSTs are shown along with the address signal lines. The layout is not drawn to scale and is used for illustration only. It can be seen that the decoding logic can be mechanized with no crossovers, which reduces potential interfaces within the chip.

#### 8.2 REDUCTION OF MOST INTERFACES

The advent of large scale integration (LSI) allows complete functions to be contained within a single chip. Chips containing 1,000 to 2,000 logic type MOS devices become feasible. This reduces the number of interconnections significantly. For example, consider the selection circuitry for 16 words shown in Figure 19. To implement this with normal integrated circuits would require approximately 23 flat-packs of 14 leads each. Fabrication of the complete circuit within a single chip reduces the number of external leads from 182 (for the 23 flat-packs) to 30 for the LSI version, which amounts to a reduction of approximately 85 percent. Increasing the complexity from 16 words to 32 words would allow an even greater reduction. The intraconnections within a device of this complexity is accomplished by a combination of:

Common diffused drain and source regions.

Diffused crossovers (crossunders or tunnels).

Multilayer interconnections on the passivated surface of the chip.

These are discussed in the following paragraphs.

4/

• •

· · · · ·

NAS8-20594

FIGURE 21. SELECTION CIRCUIT CHIP - 16 WORDS

FIGURE 22. CHIP LAYOUT OF FOUR-BIT SERIES DECODING

FIGURE 23. CHIP LAYOUT OF FOUR-BIT PARALLEL DECODING

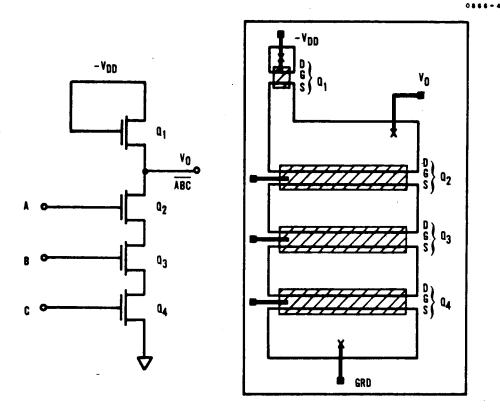

Common Diffused Regions. The MOSTs within the same logic gate may be interconnected by a common diffused region. This is illustrated in Figure 24a where the drain of Q4 and the source of Q3 are contained within the same diffused region. This is also true of the drain and source of Q3 and Q2 and the drain and source of Q2 and Q1. This same figure compares the number of metal-to-silicon interfaces contained in a MOST integrated circuit chip to that of a similar bipolar chip (Figure 24b). There are three metal-to-silicon interfaces in the MOST chip and 18 in the bipolar chip. This is a significant reduction.

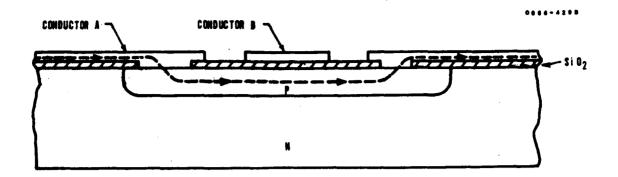

Diffused Crossovers. These are sometimes referred to as "crossunders" or "tunnels". In even the simplest integrated circuit it is not always possible to eliminate crossovers. This can be provided by a high concentration diffused region as illustrated in Figure 25. Two conductors, "a" and "b" must cross each other. A P-type isolated region is diffused in the chip during the source and drain diffusion. Contact windows are opened over the left-hand and right-hand sides of the P region in the SiO<sub>2</sub>. Circuit continuity for conductor "a" is provided by the diffused P region, hence a "tunnel" is formed. Conductor "b" crosses over the P region as shown and the insulation between "a" and "b" is provided by a thin layer of SiO<sub>2</sub>.

The disadvantages of the diffused crossover are increased series resistance and increased stray capacitance. The sheet resistance of a typical source and drain diffusion varies from approximately 100 to 200 ohms per square. This can be reduced to less than 10 ohms per square by an additional P+ diffusion step. The stray capacitance is contributed by the junction capacitance between the P region and the N type substrate. Both of these components tend to reduce circuit speed and increase power dissipation.

<u>Multilayer Interconnections</u>. As the circuit complexity of the chip increases all crossovers cannot be made with the above techniques. More than a single layer of crossovers is required. The interconnections within an LSI are comparable to those of present day multilayer boards. It then becomes necessary to develop a microminiature version of multilayer interconnections which can be deposited on the semiconductor surface and made an integral part of the completed circuit. This required a highly compatible system of metals and insulators.

# (a) MOST 3-INPUT NAND GATE

## (b) BIPOLAR 3-INPUT NAND GATE

FIGURE 24. A 3-INPUT NAND GATE CONSTRUCTED WITH BOTH BIPOLAR DEVICES AND MOS DEVICES. (THE METAL-TO-SILICON CONTACTS ARE MARKED WITH AN "X".)

FIGURE 25. CROSS-SECTION OF A SILICON MOST CHIP SHOWING THE DIFFUSED CROSSOVER TECHNIQUE

The problems associated with utilizing the bimetallic system of gold and aluminum in the interconnection and packaging of transistors and integrated circuits has compelled the industry to develop monometallic systems. A monometallic system becomes even more desirable in the development of multiple layers of conductors on the surface of the silicon chip. The two most practical monometallic systems are all-aluminum and all-gold.

Both of these systems are presently being successfully used by the semiconductor industry in the fabrication of transistors and integrated circuits. The following paragraphs discuss some of the properties of the above systems and some of the methods for providing insulation between conductor layers.

Aluminum has the advantages of adhering well to silicon and silicon dioxide. It is easily evaporated to form a wide range of layer thicknesses; it is a good electrical conductor. It is easily etched with conventional photoresist techniques. It can be bonded by either wedge thermocompression bonding or ultrasonic bonding, and is fairly corrosion resistant. (9) Aluminum also has some shortcomings. A thin layer of oxide rapidly forms on the surface of the aluminum conductor and this requires the bonding process to be very precisely established and controlled to obtain strong bonds between the aluminum film and the aluminum wire. Aluminum requires a completely hermetically sealed package since continued exposure to air, moisture, and other contaminants causes a gradual deterioration of the bonds and thin film conductors. It reacts with the silicon dioxide surface to create inversion layers in the underlying silicon which could be a problem in MOS devices. (The thickness of the SiO<sub>2</sub> layer can normally be made thick enough so that the inversion effects are negligible.)

Gold has the advantages of being completely corrosion resistant, it is easily bonded by thermocompression techniques; it is easily evaporated or sputtered, it is a good electrical conductor; and it is easily etched. (9)Gold, too, has its shortcomings. It does not adhere well to  $SiO_2$  and it reacts with silicon at the eutectic temperature of 370°C. These two problems make it necessary to have an underlying metal layer between the gold and/or silicon and silicon dioxide. Molybdenum and chromium are the two most practical choices. Either one forms a compatible system with gold and silicon. The gold system, using molybdenum as the underlying metal, is fabricated as follows. Molybdenum is deposited on the semiconductor surface by either electron beam evaporation or sputtering. Contact to the silicon is provided in those areas where openings have been opened in the silicon dioxide. Gold is next evaporated over the surface, making good contact with the previous layer of molybdenum. The interconnection pattern is formed by using conventional photoresist techniques and a two step etching process.

The gold interconnect system is presently being pursued for use in LSI circuitry requiring more than a single layer of conductors.

Types of insulating layers investigated and being pursued consist of both organic and inorganic materials. Specifically, they are photoresist, lead monoxide, and silicon monoxide.\*

A limited amount of work was performed to determine the feasibility of using photoresist as an insulting medium. A three to four micron film of KTFR was applied to a standard metallized wafer and exposed without a mask. The coated wafer was vacuum baked at 250°C and then 20,000 Å of aluminum was evaporated over the surface. The completed wafer was stored at high temperature to determine if the photoresist would provide insulation between the aluminum layer on top and the metallized devices below. After three days at 300°C, the insulation was still good. The temperature was increased to 325°C, and at the end of 13 days short circuits began to appear as a result of the decomposition of the photoresist. The results indicate that multilayer conductors using photoresists for insulation are probably feasible at lower temperatures and thicker insulating films.

The effort to use lead monoxide (PbO) as the insulating medium was terminated because all of the etchants used to etch the aluminum conductors also attacked the PbO. Aluminum conductors were used in the above investigation because the process for the gold interconnection system has not been completely established.

\* This effort was supported by funds available under a separate contract.

The present multilayer interconnection system being developed consists of SiO as the insulating medium and gold as the conductors with chromium or molybdenum as the underlying metal. The development is in such an early stage that no conclusive results are available, but there are no apparent reasons that the system cannot be perfected.

## 8.3 AN INTERFACE-FREE PACKAGING CONCEPT

#### Introduction

A concept for the reduction of interface connections has been conceived and investigated. The concept was implemented in the form of a molecular integrated circuit package (MICPAK) which will interconnect many discrete integrated circuit elements on a single substrate without introducing undesirable interfaces normally found in more conventional packaging.\*

In electronic circuit design, two dissimilar packaging interconnection problems are evidenced by digital and analog circuits. In digital circuitry the power requirements are usually low, but the quantity and complexity of interconnection systems can be very large.

Analog circuitry, however, frequently dissipates relatively large amounts of power and presents problems in feedback and shielding, while having straightforward simple interconnection systems.

In the MICPAK concept both of these areas are adequately considered. The substrate is designed with a built-in, low resistivity ground plane over which are routed the electrical circuit conductors formed by conventional photoetch techniques used in the semiconductor industry. This approach provides a comparable technology at the subsystem level to that previously provided at the device components level. The conductor lead inductance, capacitance to ground, resistance, etc., can be optimized for each specific conductor in the circuit.

The material used for the substrate is a high density magnesium oxide which has a layer of metal fused to it to form a ground plane and input/ output termination pads. Over this metal film is deposited a dielectric film of silicon monoxide which serves to insulate the subsequent interconnection plane from the ground plane.

Processing of the various planes involved is accomplished by means of photoetching techniques similar to those of the semiconductor industry. A layout is made from which a graphic art drawing is cut to a high degree of precision. This graphic art work is made 50 to 100 times scale and reduced to photo emulsion on a glass plate. Figures 26 through 28 show the substrate, SiO and conductor layout drawings. The conductor plane

<sup>\*</sup> A large part of this effort was supported by the NAVAL AIR DEVELOP-MENT CENTER under contract number N62269-3118.

FIGURE 26. SUBSTRATE SKETCH

...

# FIGURE 27. SIO MASK LAYOUT

J [ \_ \_ . ..... ......

FIGURE 28. CONDUCTOR LAYOUT

NAS8-20594

A6604-070

is produced by evaporation of a metal film over the SiO which is then etched to the required configuration. Where connection to the ground plane is required the SiO will have previously been etched to produce a window, when the conductor film is evaporated over the SiO the windows will provide electrical connection from the circuit path to the ground plane. Reliability of this connection is assured by alloying the two metals at an elevated temperature.

The integrated circuit dice are mounted in the channels provided by the substrate. The substrate channels are shown in Figure 26 and a cross-sectional view of the mounted dice is illustrated in Figure 29. A feasibility package containing an 8-stage binary counter is shown in Figure 30.

#### Interconnection Interfaces

A significant failure mode in microcircuitry has been the connection interface between the circuit path and the interconnection lead or conductor. Although basic to electronic equipment fabrication, it is not always recognized that a typical solder connection (Figure 31 shows lead to printed circuit board conductor) has an interface between the conductor and the solder, and another between the solder and the component lead. In Figure 32 (which shows an actual photograph of an eyeleted pc board) there are interfaces between the conductor to solder to eyelet to solder to component lead. Since each interface constitutes a connection, it is the number of interfaces which affect the reliability.

The considerable reliability improvement which has resulted from the introduction of welded interconnection techniques is due in large measures to the reduction in the number of interfaces. Figure 33 shows the weld of a gold plated dumet wire and a nickel ribbon. Although a satisfactory joint was made, an interface can be seen completely across the junction and is typical for this type of interconnection technique. Thermal compression bonding, another microattachment technique, has characteristics similar to those of the welded technique as shown in Figure 34. The number and type of interfaces determines the reliability.

A single NAND circuit was analyzed for various interface connection techniques. For the soldered techniques, 130 interfaces existed; for the welded techniques, 94 interfaces; and for an integrated circuit device with thermal compression bonds, 14 interfaces were required to provide connection to associated circuitry.

# FIGURE 29. CROSS-SECTIONAL VIEW OF A SILICON DICE MOUNTED IN A CHANNEL OF THE SUBSTRATE

FIGURE 30. COMPLETELY ASSEMBLED PACKAGE PRIOR TO SEALING

FIGURE 31. PRINTED CIRCUIT BOARD SOLDERED CONNECTION

A6402-181-1

FIGURE 32. EYELETED BOND

FIGURE 34. THERMAL COMPRESSION BOND

#### Intraconnections

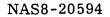

In the development of semiconductor technology, a new term, intraconnections, describes a process of connection of two or more points or elements in a circuit in such a manner that the separate connection elements are diffused with NO INTERFACE or change in material composition.

The application of intraconnection techniques to subsystem packages accommodating a variety of separate circuit devices or functions would result in ultra-reliability previously available only within the single integrated circuit device itself. This approach was pursued successfully by producing a highly localized diffusion of the metal film used as the lead wire to the circuit film on the device as substate. The object of the diffusion bonding process is to cause the two individual conductor materials to become homogeneous, that is, to become a single monometallic, monolithic electrical conductor. This can be achieved by means of a controlled selective diffusion process resulting from a very precisely controlled cycle, using relatively thin films (5,000 Å - 100,000 Å).