Final Report - Phase I

# TECHNIQUES FOR THE REALIZATION OF ULTRA-RELIABLE SPACEBORNE COMPUTERS

By: J. GOLDBERG K. N. LEVITT R. A. SHORT

Prepared for:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION ELECTRONICS RESEARCH CENTER 575 TECHNOLOGY SQUARE CAMBRIDGE, MASSACHUSETTS 02139

CONTRACT NAS 12-33

STANFORD RESEARCH INSTITUTE

MENLO PARK, CALIFORNIA

|          | 67-23 <b>952</b>                                    |   |          |

|----------|-----------------------------------------------------|---|----------|

| FORM 602 | (ACCESSION NUMBER)                                  |   | (THRU)   |

| FACILITY | (PAGES)  CH - 8 OC/G  (NASA CR OR TMX OR AD NUMBER) | _ | (CODE) 8 |

## STANFORD RESEARCH INSTITUTE

MENLO PARK, CALIFORNIA

September 1966/

Final Report - Phase I

## TECHNIQUES FOR THE REALIZATION OF ULTRA-RELIABLE SPACEBORNE COMPUTERS

By: J. GOLDBERG K. N. LEVITT R. A. SHORT

Prepared for:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION ELECTRONICS RESEARCH CENTER 575 TECHNOLOGY SQUARE CAMBRIDGE, MASSACHUSETTS 02139

CONTRACT NAS 12-33

SRI Project 5580

Approved: D. R. BROWN, MANAGER

COMPUTER TECHNIQUES LABORATORY

J. D. NOE, EXECUTIVE DIRECTOR ENGINEERING SCIENCES AND INDUSTRIAL DEVELOPMENT

Copy No. 30

#### ABSTRACT

This is a report of a study of techniques for the realization of ultrareliable, high-performance, spaceborne computers. The study included the evaluation of, and several new contributions to, the most significant known techniques and the proposal and investigation of several promising new techniques. The state of the art of existing redundancy techniques for fault-detecting and fault-masking is assessed, with special emphasis on multiple-line voting redundancy, error-correcting codes, and redundantstate schemes for sequential networks. A number of directions for the improvement of these techniques are described. Significant potential improvements in reliability are available in designs allowing for a high degree of reconfigurability in structure and programs, and system schemes and design techniques needed for such behavior are proposed and investigated. In particular, we discuss the design of minimal test schedules for fault detection and diagnosis, the design of highly modular processing networks and of programmable interconnection networks, and the overall organization of maintenance and computation functions in a computer system. The application of error control techniques to memory systems and to power supplies is considered, and the possible use of all-magnetic logic networks is examined. Included in the report is a critical and selective survey of the literature that is relevant to the attainment of reliable systems and networks through the judicious use of redundant structures. Finally, recommendations are made for further research into the development of techniques for ultrareliable system design.

#### FOREWORD

This is a report of a one-year research study of techniques for the realization of ultrareliable spaceborne computers. This study was conducted in the Computer Techniques Laboratory of Stanford Research Institute, under the sponsorship of the Electronics Research Center of the National Aeronautics and Space Administration.

The major objective of the study was to provide guidelines for the design of computers intended to function reliably under the severe conditions imposed by spaceborne missions. It is clear that the spaceborne requirement introduces design difficulties which are not attendant to other applications. For example, the possibility of unprogrammed maintenance and inspection routines is severely limited; the successful use of a radio link cannot always be assured; the computations are complex and highly varied; the performance requirements are very high; and there are special physical constraints on the construction and operation of the computer. In order to attain an acceptably reliable system the judicious use of redundant structures is mandatory. Of course, the observation that redundancy is required to improve reliability is not unique to this study, and hence in the course of our investigation we utilized many well-established (at least in principle) techniques, e.g., fault masking by multiple-line voting and adaptive replacement of faulty subsystems with standby units. In order to properly assess the myriad of proposed redundancy measures, a considerable portion of the report is devoted to commentaries on state-of-the-art developments. This inclusion of review material enables an engineer who is related to this area solely as a user to satisfy his requirements with minimal recourse to other documents.

However, many novel developments are reported herein, and our concern in this Foreword is to guide the reader--whether he is a research specialist or one with little prior knowledge of the subject matter-- to those sections which are of most interest to him.†

The report is organized into four chapters and four appendices. Each major section of the chapters contains conclusions and a detailed listing of outstanding research problems; the major conclusions of the research study and recommendations for further research are presented in Chapter IV. The first chapter serves as an overall introduction to the report. It contains (1) the statement of the problem—in particular a detailed discussion of the characteristics of advanced spaceborne computers; (2) the goals, methods and assumptions of the study; (3) the criteria of performance, including a discussion of relevant reliability and cost measures; and (4) the organization of the report.

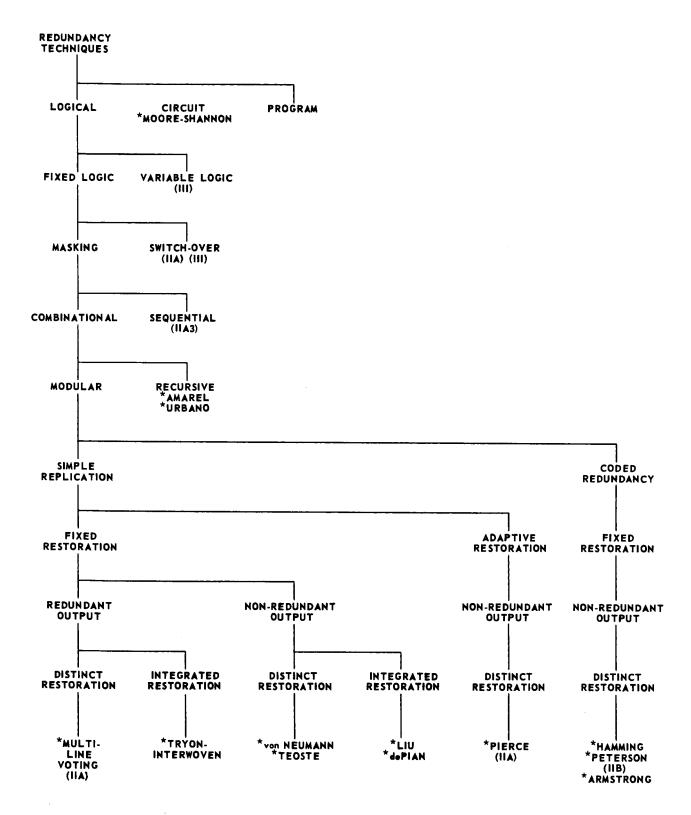

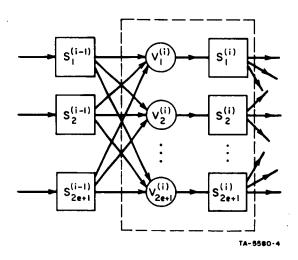

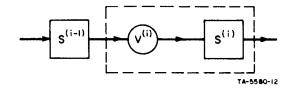

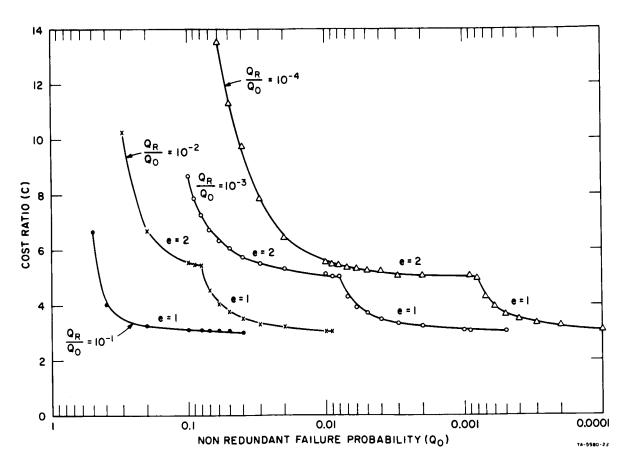

The second chapter is concerned with those logical design techniques for fault masking and error detection in which the error control is passive. In Sec. II-A-1\* we present a detailed (historical) review of the most important known fault-masking techniques. Specific combinational fault-masking design techniques are given in Sec. II-A-2. Included herein are reviews of the multiple-line voting approaches [Sec. II-A-2-a-2)]\* as applied to such simple network models as cascades and trees, and also some embellishments of known techniques [Sec. II-A-2-a-3)] for the analysis of arbitrary replicated networks. Some new results are presented on bounds on the reliability of arbitrary replicated networks [Sec. II-A-2-a-4)] and also on optimum techniques for the realization of multipleoutput networks which are replicated [Sec. II-A-2-a-5)]. In Sec. II-A-2-b we present some unique digital realizations of the extremely powerful adaptive-voting scheme, along with a detailed examination of schemes which combine fault masking and network replacement. Such schemes have heretofore not been reported in the literature. In Sec. II-A-2-c\* a review is

<sup>†</sup> Sections containing reviews of prior techniques are marked, in this Foreword, by an asterisk.

presented of the known techniques for the realization of voting networks—much of the prior work has related to networks which realize the majority function of 3 or 5 inputs—and also some novel designs (which are approximately minimal) are given for majority—function networks with an arbitrary number of inputs, suitable for different technologies. A review of the known techniques of fault control for sequential networks is presented in Sec. II-A-3\* along with some (apparently) novel fault-detection schemes relying upon state—parity checking and state—weight checking. Chapter II concludes with Sec. II-B, which surveys in detail the known coding techniques which appear to be appropriate for checking computer operations.

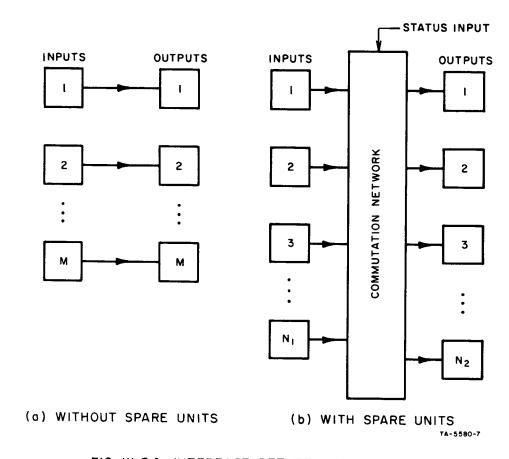

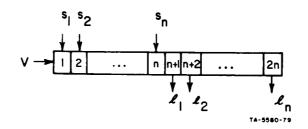

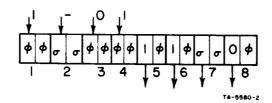

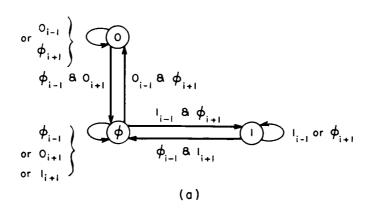

Chapter III is concerned with techniques for dynamic error control, i.e., ways in which the logical interconnections among the components of the computer may be altered. In Sec. III-A we discuss the particular system organization features that facilitate dynamic maintenance processes. Section III-B is concerned with the design of test schedules of minimal length, for the fault diagnosis of combinational networks. Included here is a review of the state of the art of diagnosis (Sec. III-B-3)\* along with a discussion of some novel techniques for fixed-schedule and serialschedule types of tests based upon reduction of a fault table. In Sec. III-C we consider the design of networks for a reconfigurable network--an area which has received little prior attention. The design of commutation networks--networks whose function is to provide interconnection between operating modules and to disconnect faulty modules for the system-is discussed in Sec. III-C-2. Two types of structures are presented--a unique sequential network and a combinational type of network which is somewhat suggestive of the central telephone exchange. In Sec. III-C-3 we consider the design of a modular arithmetic processor wherein the functions of computation, storage, and primitive control are all combined in an iterated set of replaceable modules. The chapter concludes with brief descriptions of some novel techniques for realizing programmable control units. This remains a major area for further research.

Appendix A\* emphasizes the practical problems of applying redundancy to spaceborne memories. Included here is an evaluation and comparison of several state-of-the-art schemes, e.g., the use of codes to protect the

data channels and the access circuits, in addition to some suggestions for future research such as a consideration of those reliability techniques which relate to special memory types.

Appendix B is a detailed discussion of the reliability problems peculiar to power supplies. Suggestions are given for novel means of error control, including considerations of weight and volume.

Appendix C is an examination of the possible role of magnetic logic for attaining ultrareliable operation, with special attention to applications wherein the low speed of operation attendant to magnetic logic does not limit overall computation speed.

Appendix D<sup>#</sup> is a critical and selective survey of the literature that is relevant to the attainment of reliable systems and networks through the judicious use of redundant structures. Although several complete bibliographies of the literature have appeared previously, no surveys were available which could be used to quickly distinguish those contributions which are concerned with tactical expositions, applications, or advanced mathematical theories.

The technical studies reported here are the work of the following members of the Computer Techniques Laboratory:

Mr. J. A. Baer

Mr. C. B. Clark

Dr. B. Elspas

Mr. J. Goldberg

Dr. W. H. Kautz

Dr. K. N. Levitt

Mr. S. W. Miller

Dr. R. A. Short

Dr. H. S. Stone.

All of these individuals contributed to the writing of the various sections of the report. The report was organized and edited by Mr. J. Goldberg, who was Project Leader, Dr. K. N. Levitt, and Dr. R. A. Short.

#### CONTENTS

| ABST  | RACI | ٠.       | i                                                                                                                                                                  | ii       |

|-------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| FOREV | WORI |          |                                                                                                                                                                    | v        |

| LIST  | OF   | ILLU     | USTRATIONS                                                                                                                                                         | ii       |

| LIST  | OF   | TABL     | ES                                                                                                                                                                 | хi       |

| I     | OBJ  | JECTI    | VES AND APPROACH                                                                                                                                                   | 1        |

|       | A.   | Sta      | tement of the Problem                                                                                                                                              | 1        |

|       |      | 1.       | Basic Characteristics of an Advanced Spaceborne                                                                                                                    |          |

|       |      |          | Computer                                                                                                                                                           | 1        |

|       |      |          | <ul><li>a. Special Requirements and Constraints in Computation, Maintenance, and Construction</li><li>b. Design Consequences of the Special Requirements</li></ul> | 1        |

|       |      |          | and Constraints                                                                                                                                                    | 3        |

|       |      | 2.       | Problems of Design for Reliability                                                                                                                                 | 5        |

|       | В.   | Goa      | als, Methods, and Assumptions of the Study                                                                                                                         | 7        |

|       |      | 1.<br>2. | Goals of the Study                                                                                                                                                 | 7<br>8   |

|       |      |          | a. Survey of Known Techniques                                                                                                                                      | 8        |

|       |      |          | <ul><li>b. Conception of New Schemes</li></ul>                                                                                                                     | 9        |

|       |      |          | Research                                                                                                                                                           | 9        |

|       |      | 3.       | Technical Assumptions of the Study; Definition of Terms                                                                                                            | 10       |

|       |      |          |                                                                                                                                                                    | 10       |

|       |      |          | •                                                                                                                                                                  | 11<br>12 |

|       | ~    | G4       | <del>-</del>                                                                                                                                                       |          |

|       | С.   |          |                                                                                                                                                                    | 12       |

|       | D.   | Org      | ganization of the Report                                                                                                                                           | 15       |

| ΙΙ | TEC | HNIQ     | UES OF LOGICAL DESIGN FOR FAULT MASKING                                                                                                                           | _              |

|----|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | AND | ERR      | OR DETECTION                                                                                                                                                      | 7              |

|    | Α.  | Fau      | lt-Masking Techniques for General Logic Functions 18                                                                                                              | 3              |

|    |     | 1.<br>2. | Review of Significant Techniques                                                                                                                                  |                |

|    |     |          |                                                                                                                                                                   |                |

|    |     |          | a. Techniques for the Design of Multiple-<br>Line Fault-Masking Networks                                                                                          | 7              |

|    |     |          | <ol> <li>Introduction and Summary of Prior Work 27</li> <li>Techniques for the Analysis of Simple</li> </ol>                                                      |                |

|    |     |          | Models                                                                                                                                                            |                |

|    |     |          | Triplicated Networks 4                                                                                                                                            |                |

|    |     |          | <ul> <li>4) Bounds on Network-Failure Probability 55</li> <li>5) Techniques for the Realization of Multiple-<br/>Output Networks with Voter Redundancy</li> </ul> |                |

|    |     |          | for Fault Masking 6                                                                                                                                               |                |

|    |     |          | 6) Conclusions and Future Problems for Study 6:                                                                                                                   | 5              |

|    |     |          | b. Techniques for the Combination of Fault Masking and Replacement 6                                                                                              | 8              |

|    |     |          | 1) Introduction 6 2) Techniques for the Realization                                                                                                               |                |

|    |     |          | of the Adaptive-Voting Scheme                                                                                                                                     |                |

|    |     |          | Voting Scheme                                                                                                                                                     |                |

|    |     |          | Switching Scheme                                                                                                                                                  |                |

|    |     |          | o, comparisons and concentrations of the contentrations                                                                                                           |                |

|    |     |          | c. Voting Networks                                                                                                                                                |                |

|    |     |          | <ul><li>1) Introduction</li></ul>                                                                                                                                 |                |

|    |     |          | Networks                                                                                                                                                          | '9             |

|    |     |          |                                                                                                                                                                   | 3              |

|    |     | 3.       | Sequential Networks                                                                                                                                               | 90             |

|    |     |          | u, indicadorion v v v v v v v v v v v v v v v v v v v                                                                                                             | ) (            |

|    |     |          | 2) Delay-Element Faults                                                                                                                                           | 93<br>93<br>94 |

|    |     |          | 1/ output like monthly life like the transfer of the                                                                                                              | ) 5<br>) 5     |

|    |     |          | O' OACTUTT HERMOTY TURES                                                                                                                                          | _              |

|     |     | c<br>d           |                                                                                                                                          |

|-----|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|     |     |                  | 1) State-Parity Checking                                                                                                                 |

|     | В.  | Use o            | f Codes for Storage and Arithmetic Operations 109                                                                                        |

|     |     |                  | ntroduction                                                                                                                              |

|     |     | a<br>b           | • • • • • • • • • • • • • • • • • • • •                                                                                                  |

|     |     |                  | and Error Probability                                                                                                                    |

|     |     | 3. C             | odes for Checking Arithmetic Operations 117                                                                                              |

|     |     | a<br>b<br>c      | Nonseparable Codes                                                                                                                       |

| III | TEC | HNIQUE           | S FOR DYNAMIC ERROR CONTROL                                                                                                              |

|     | Α.  | Probl            | ems of System Organization                                                                                                               |

|     |     | o<br>2. 0        | Approaches to Structural Parallelism and Functional Specialization for General Computation 140 Factors of Module Size and Specialization |

|     |     | g                | Problems of Subsystem Design                                                                                                             |

|     | В.  | 1. I             | for Diagnosis of Fault Conditions                                                                                                        |

|     |     | U                | sing Fixed Test Schedules 149                                                                                                            |

|     |     | a<br>b<br>c<br>d | Formulation of the Problem                                                                                                               |

|     |     | e<br>f           | <ul> <li>Some Bounds on the Number of Tests Required 165</li> <li>Reductions in the Size of the Fault Table 167</li> </ul>               |

|     |     | g                |                                                                                                                                          |

|     |     | h                |                                                                                                                                          |

|    | 3.   | Fau<br>Usi | lt Diagnosis in Combinational Circuits<br>ng Serial Test Schedules |

|----|------|------------|--------------------------------------------------------------------|

|    |      |            |                                                                    |

|    |      | a.         | Introduction                                                       |

|    |      | b.         | Fault Detection                                                    |

|    |      | c.         | Fault Location                                                     |

|    |      | d.         | Fault Location to Within Modules 181                               |

|    |      | e.         | Bounds                                                             |

|    |      | f.         | Potential Economies of Serial Test Schedules                       |

|    |      |            | for Fault Location                                                 |

|    | 4.   | Fau        | lt Diagnosis in Digital Computers:                                 |

|    |      | Pre        | sent State of the Art                                              |

| c. | Dec. |            | of Networks for a Reconfigurable Computer 189                      |

| •  |      |            |                                                                    |

|    | 1.   |            | roduction                                                          |

|    | 2.   | Pro        | grammable Interconnection Networks 190                             |

|    |      | a.         | Introduction                                                       |

|    |      | b.         | A Sequential Commutation Network                                   |

|    |      |            |                                                                    |

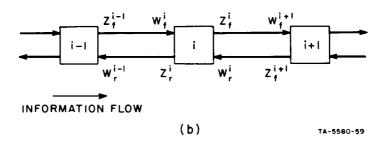

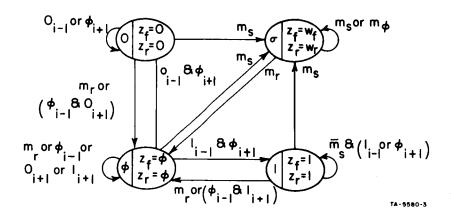

|    |      |            | 1) Overall Behavior of the Network 193                             |

|    |      |            | 2) General Description of the Propagation                          |

|    |      |            | Mode                                                               |

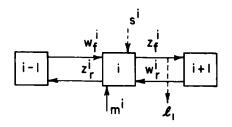

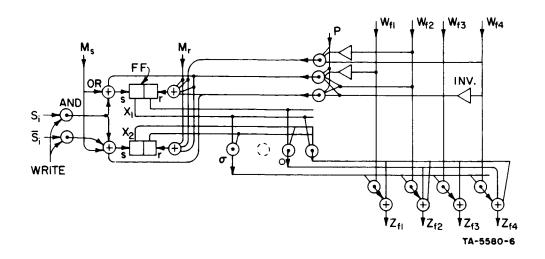

|    |      |            | 3) Description of the Cell Design 197                              |

|    |      |            | 4) Summary                                                         |

|    |      | c.         | Combinational Commutation NetworksMinimization                     |

|    |      |            | of Number of Switches                                              |

|    |      |            | 1) Introduction                                                    |

|    |      |            | 2) Single-Level Order-Preserving Network 201                       |

|    |      |            | 3) Double-Level Order-Preserving Network 205                       |

|    |      |            | 4) Single-Level Non-Order-Preserving Network 208                   |

|    |      |            | 5) Double-Level Non-Order-Preserving Network 212                   |

|    |      | _          |                                                                    |

|    |      | d.         | Setup and Control Circuits                                         |

|    |      | e.         | Failure-Tolerant Interconnection Networks 225                      |

|    |      | f.         | Conclusions and Problems for Future Study 229                      |

|    | 3.   | Prog       | grammable Processing Modules 230                                   |

|    |      | a.         | General Structure of a Modular Processor 230                       |

|    |      | b.         | Module Description                                                 |

|    |      | c.         | Microprograms for Common Functions                                 |

|    |      | d.         | Other Uses of the Module 241                                       |

|    |      | e.         | Problems for Further Study                                         |

|       |      | 4. Programmable Control Units 24                                                                                                                       |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      | <ul> <li>a. Uses of Programmability in a Control Unit 24</li> <li>b. Approaches to the Structuring of Modular<br/>Programmable Control Units</li></ul> |

|       |      | 1) Control Based Upon a Microprogram  Memory Store                                                                                                     |

|       |      | Network                                                                                                                                                |

|       |      | of "Universal" Logic Modules 24                                                                                                                        |

| IV    | CONC | LUSIONS AND RECOMMENDATIONS FOR FUTURE STUDY 25                                                                                                        |

|       | Α.   | Conclusions                                                                                                                                            |

|       | В.   | Summary of Needs for Technique Development                                                                                                             |

|       | C.   | Summary of Suggested Problems for Future Research 25                                                                                                   |

| Apper | ndix | A ERROR-CONTROL TECHNIQUES FOR MEMORY SYSTEMS 26                                                                                                       |

|       | 1.   | Introduction                                                                                                                                           |

|       | 2.   | General Discussion of the Problem                                                                                                                      |

|       | 3.   | Error Protection by Replication of Whole Memories 27                                                                                                   |

|       |      | <ul><li>a. Triplication with Voting</li></ul>                                                                                                          |

|       | 4.   | Error Protection by Redundancy Within a Memory 27                                                                                                      |

|       |      | a. Redundant Bit Channels                                                                                                                              |

|       |      | b. Redundant Words                                                                                                                                     |

|       |      | c. Accommodation to Access Faults 28                                                                                                                   |

|       |      | d. Addition of Access Redundancy 28                                                                                                                    |

|       |      | e. Redundant Access Circuits 28                                                                                                                        |

|       |      | f. Redundant Material in the Storage Module 28                                                                                                         |

|       |      | g. Redundant Cycle Control 28                                                                                                                          |

|       |      | h. Redundant Power and Environment Control 28                                                                                                          |

|       | 5.   | Design of a Parallel Encoder/Decoder                                                                                                                   |

|       | 6.   | Conclusions                                                                                                                                            |

| Apper | ndix | B DISTRIBUTED POWER-SUPPLY SYSTEMS                                                                                                                     |

|       | 1.   | Introduction                                                                                                                                           |

|       | 2.   | Advantages of Distributed-Power-Supply Systems 29                                                                                                      |

|       | 3.   | Disadvantages of Distributed-Power-Supply Systems                                                                                                      |

|       | 4.       | The Interdependence Between Power-Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _  |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       |          | and Logic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|       |          | a. Noise Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _  |

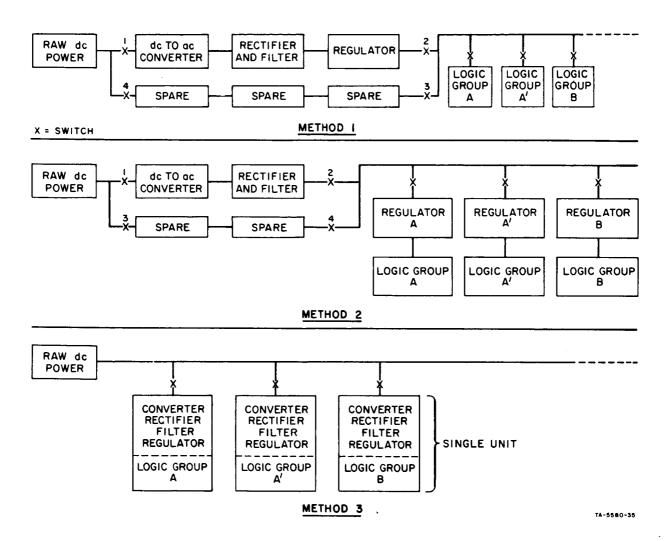

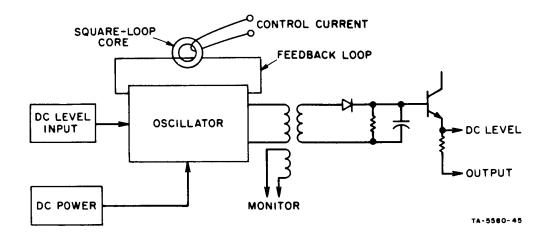

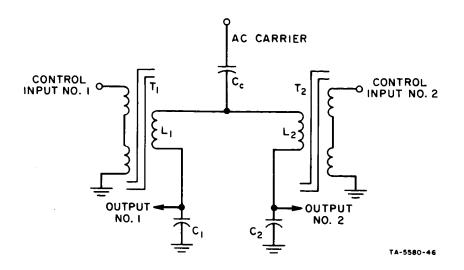

|       | 5.       | Examples of Three Possible Designs for Power-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _  |

|       |          | Supply Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

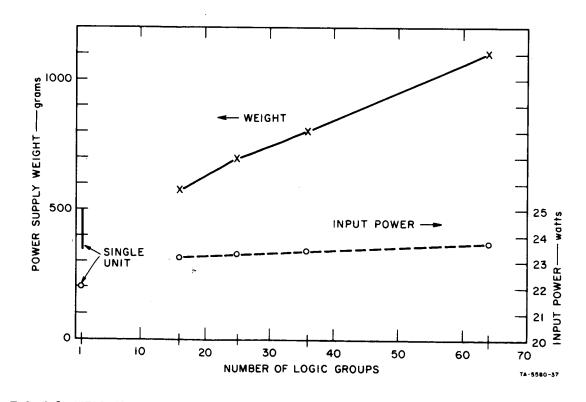

|       | 6.<br>7. | Weight and Power Required for a Distributed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|       |          | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|       | 8.       | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | J  |

| Appen | dix      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|       | 1.       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|       | 2.       | Reliability of Magnetics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|       | 3.       | A Magnetic-Monitor Concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|       |          | a. A Metering Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2  |

|       |          | b. An Information-Sampling Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  |

|       | 4.       | Implementation of Magnetic Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  |

|       | 5.       | Magnetic Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

|       |          | a. Converging Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5  |

|       |          | b. Interconnection Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6  |

|       |          | c. Data-Path Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

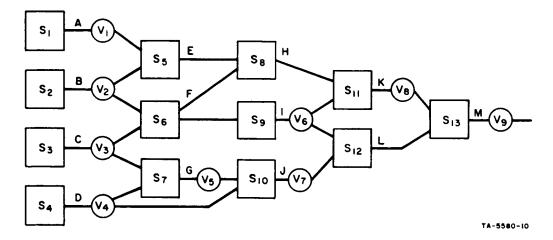

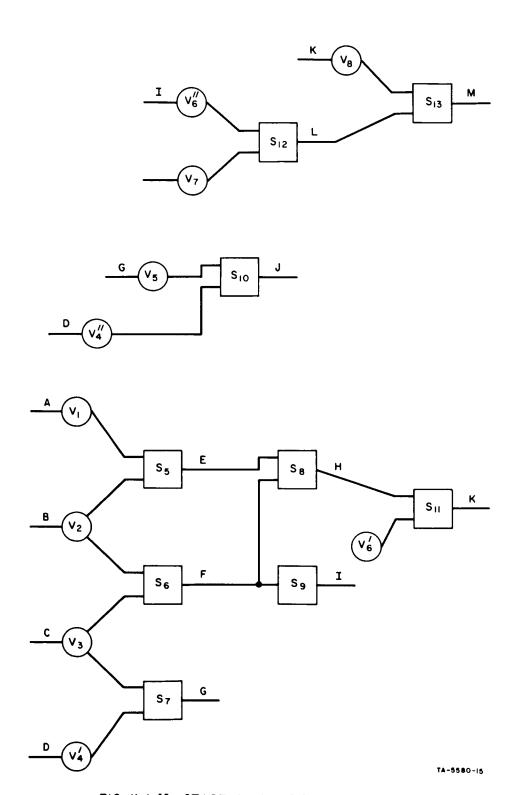

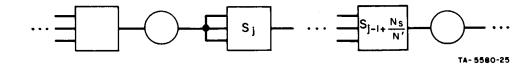

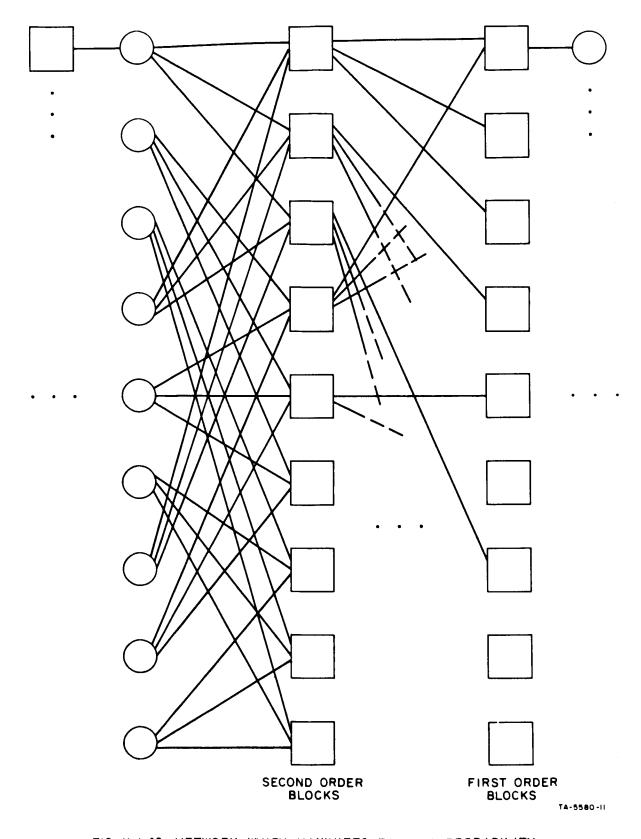

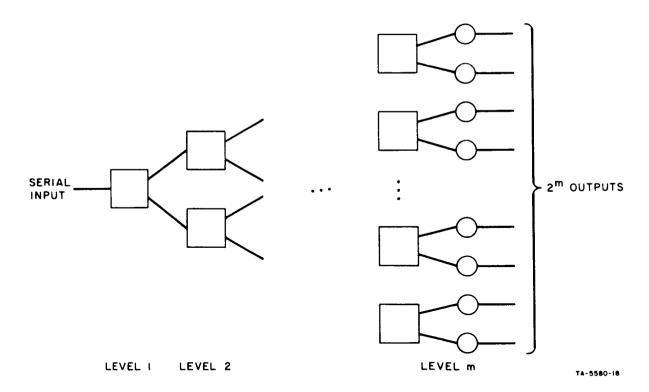

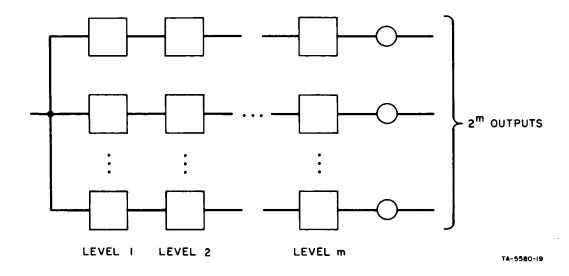

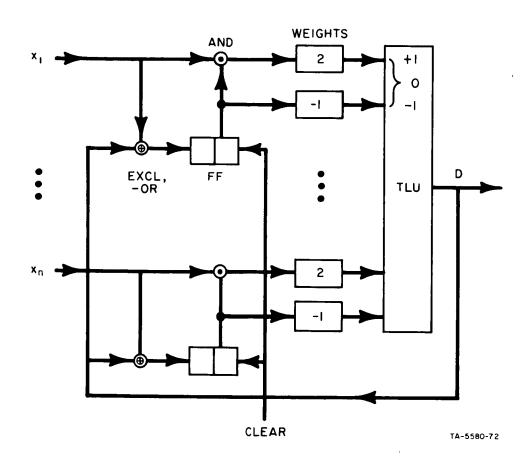

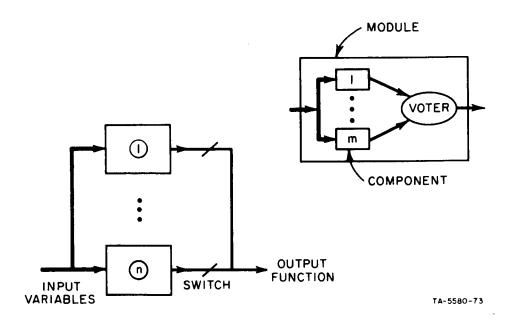

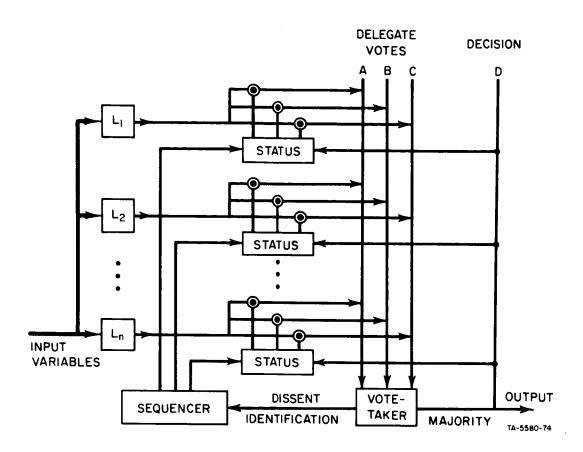

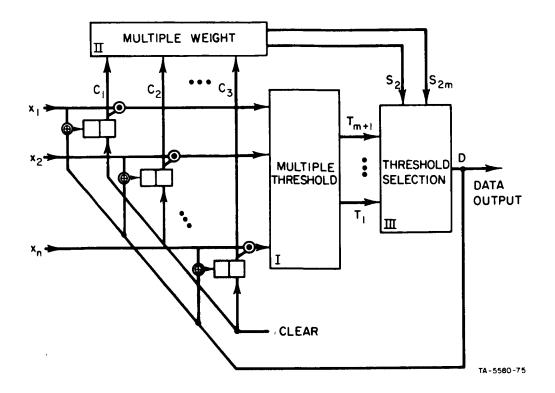

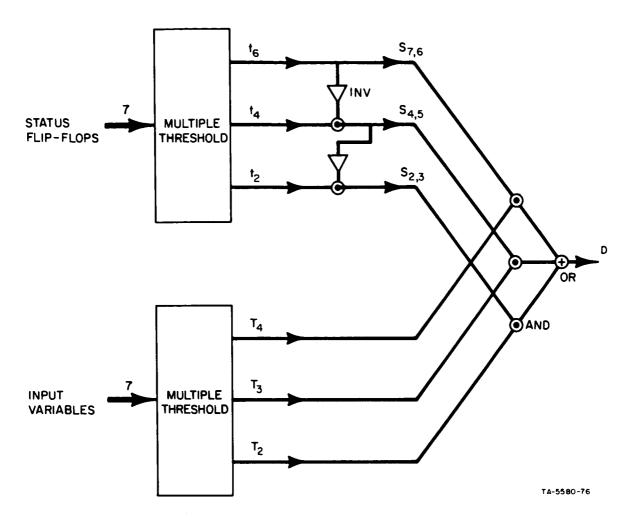

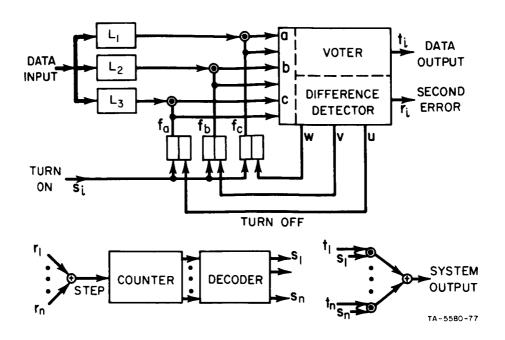

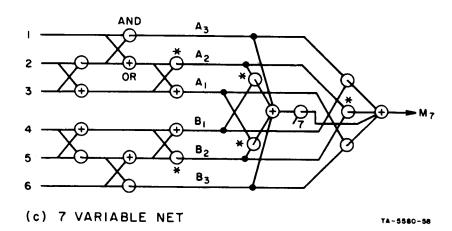

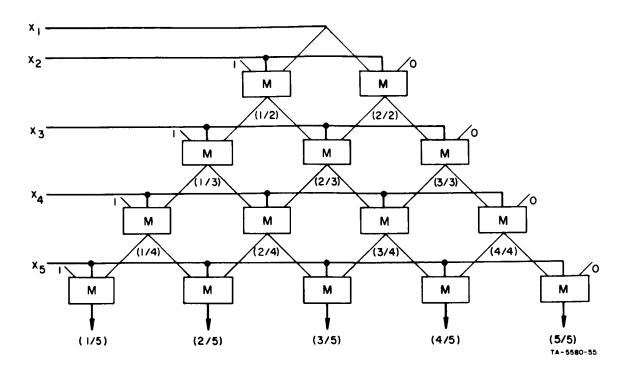

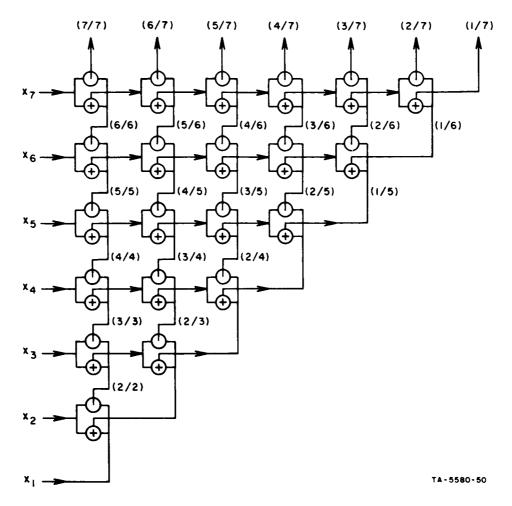

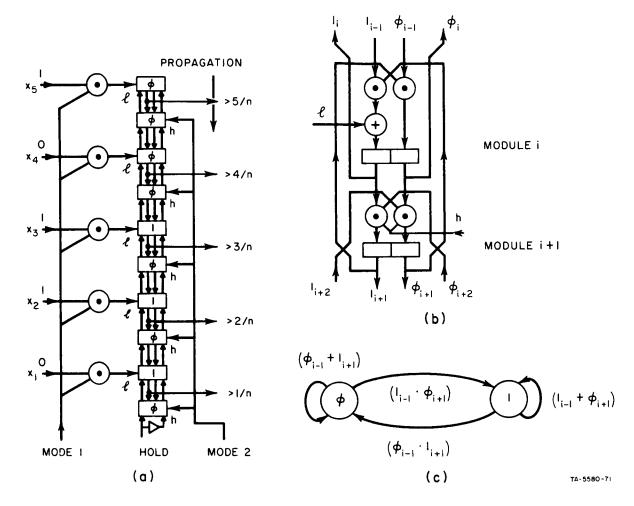

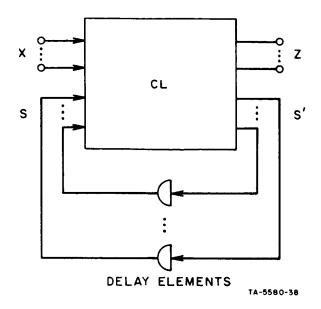

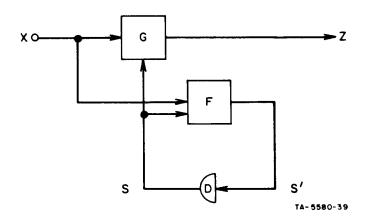

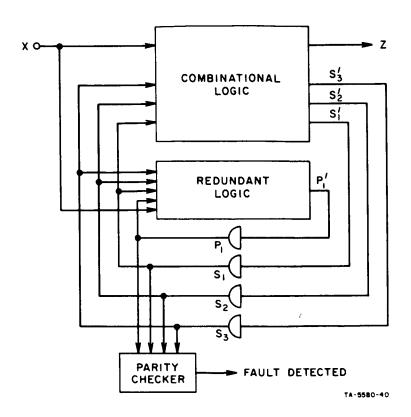

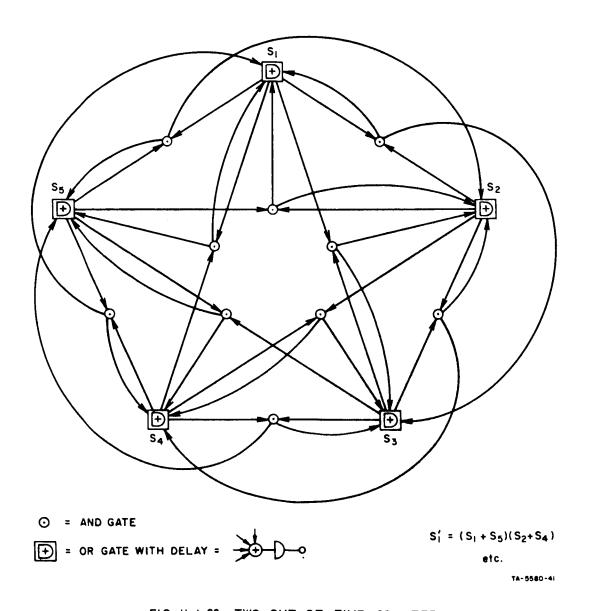

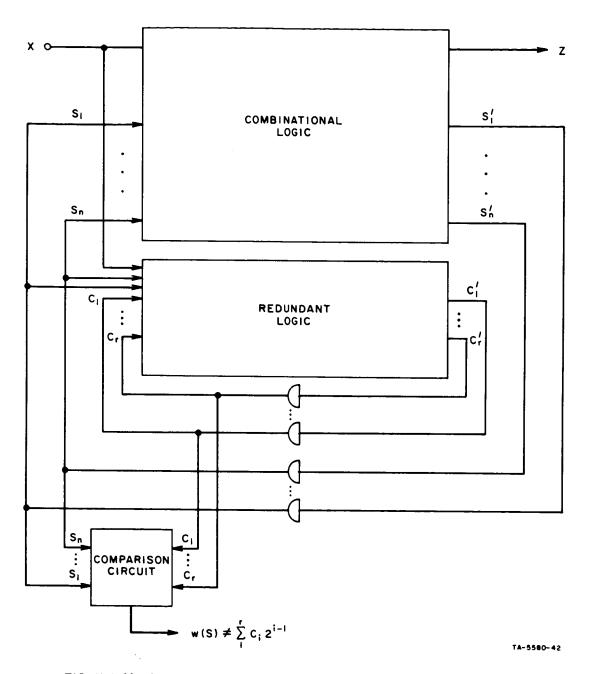

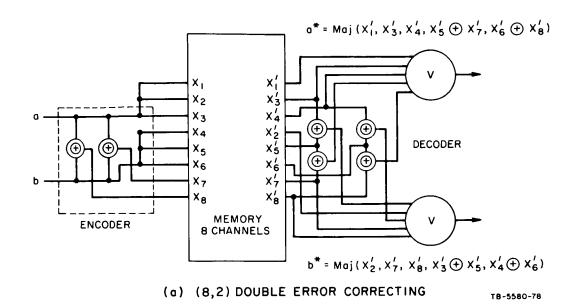

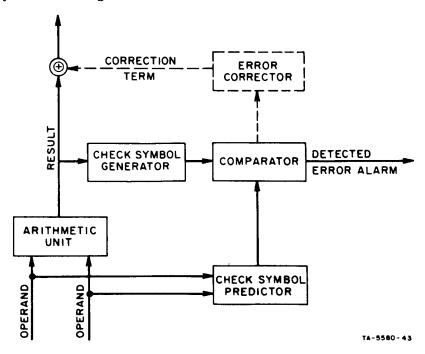

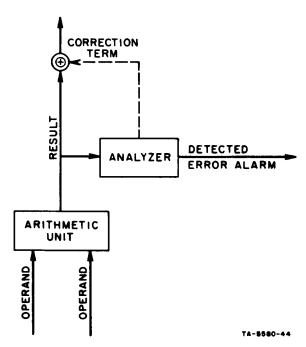

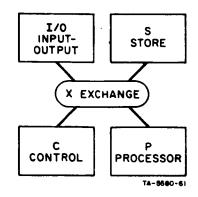

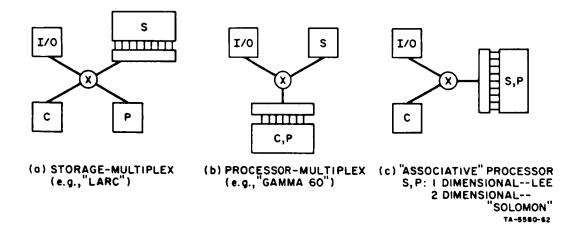

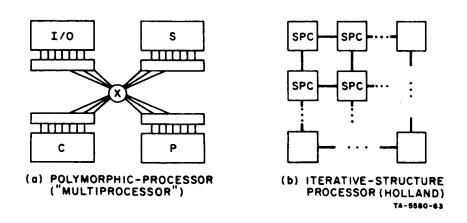

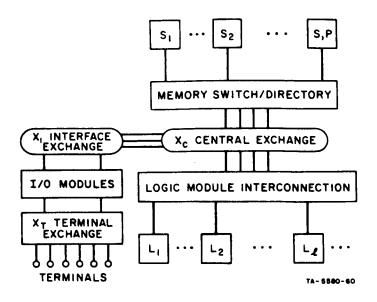

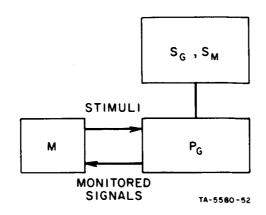

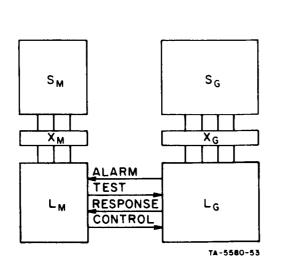

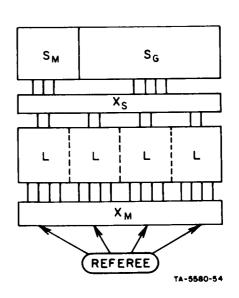

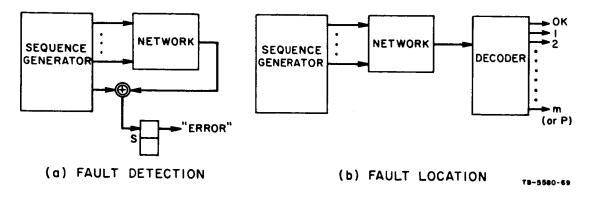

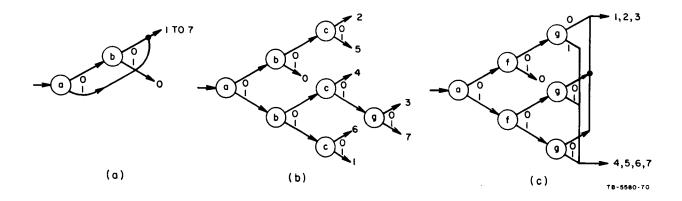

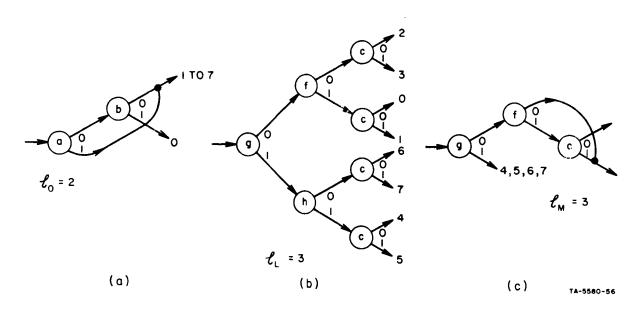

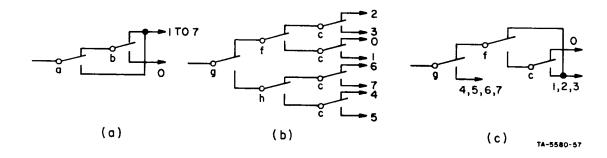

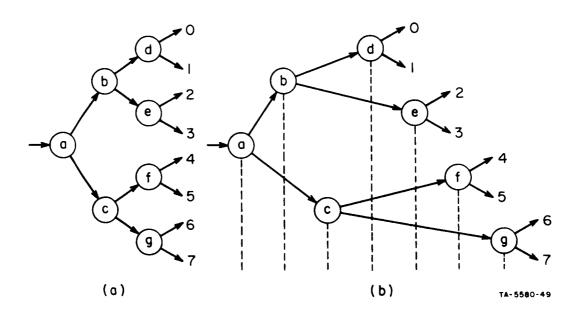

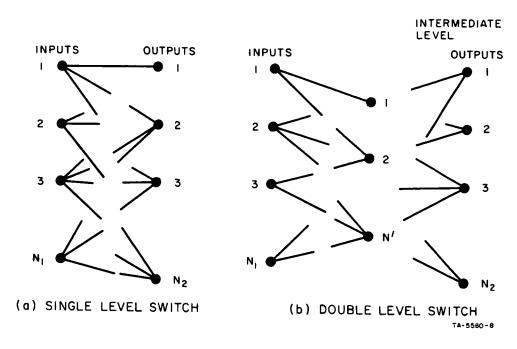

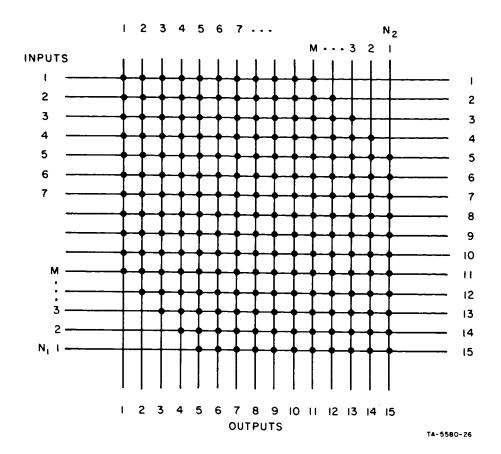

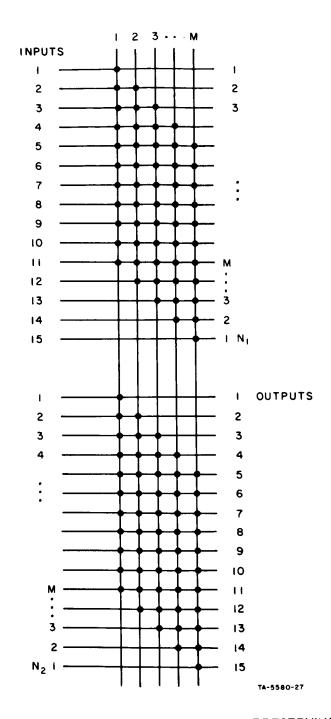

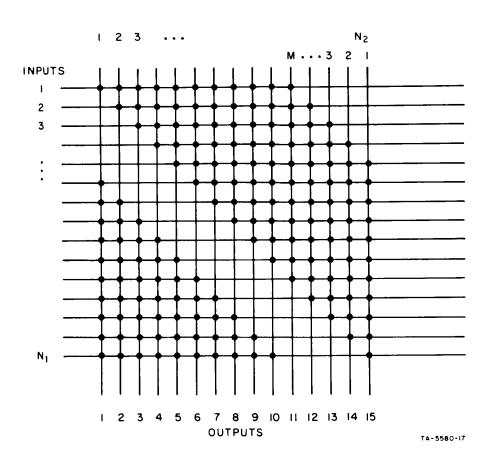

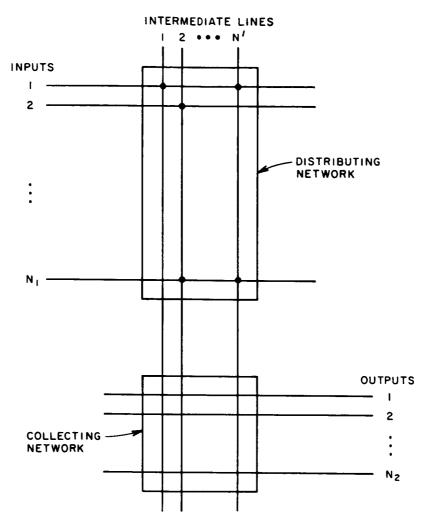

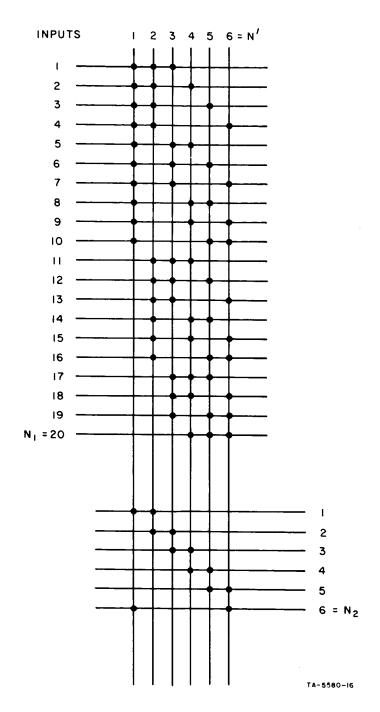

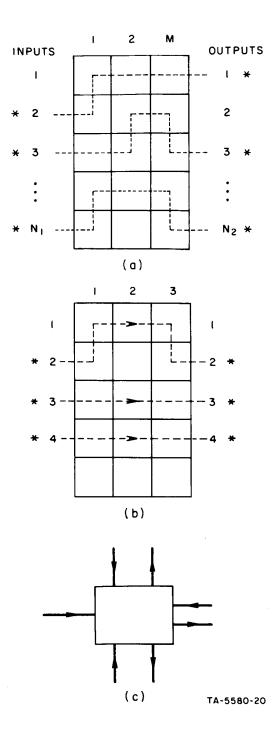

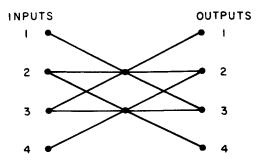

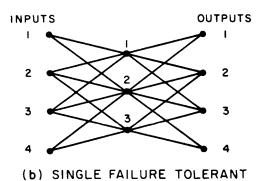

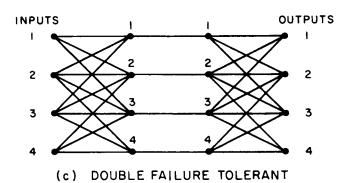

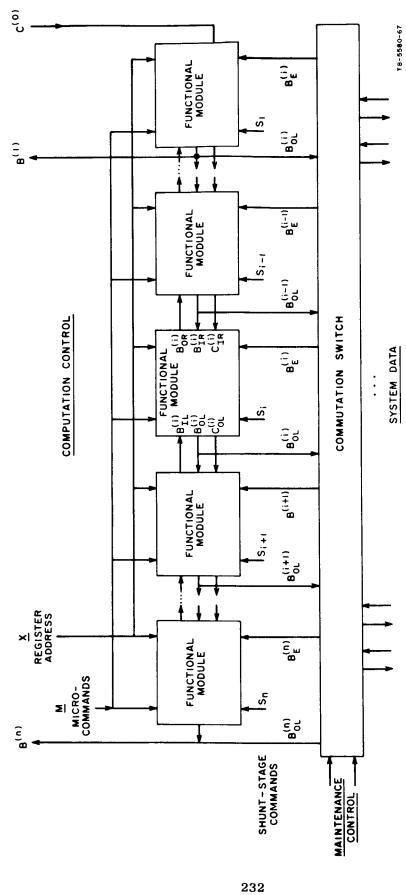

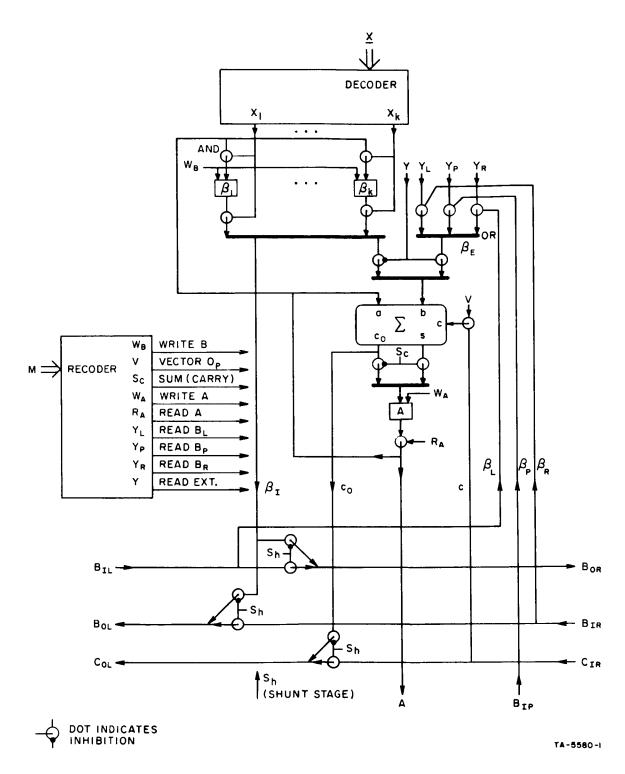

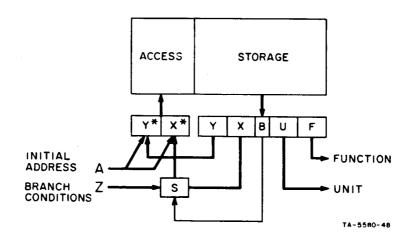

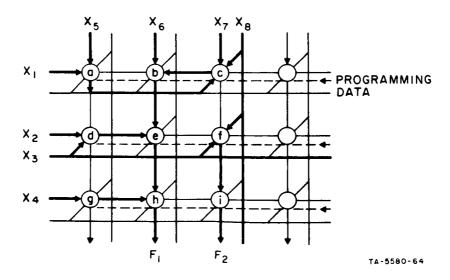

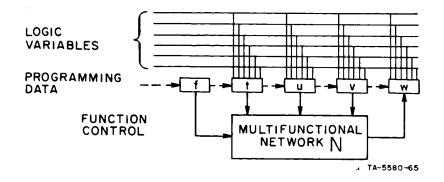

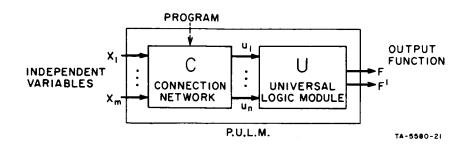

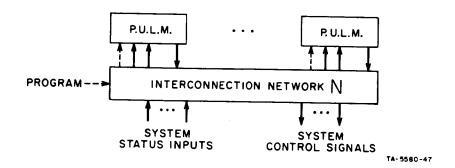

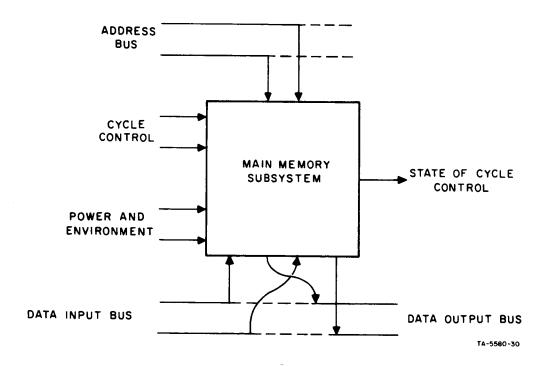

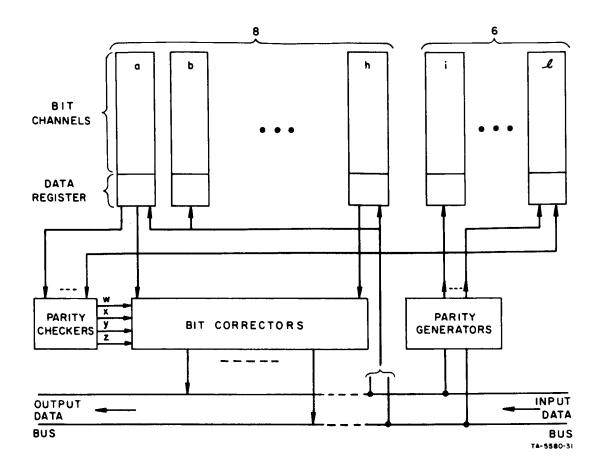

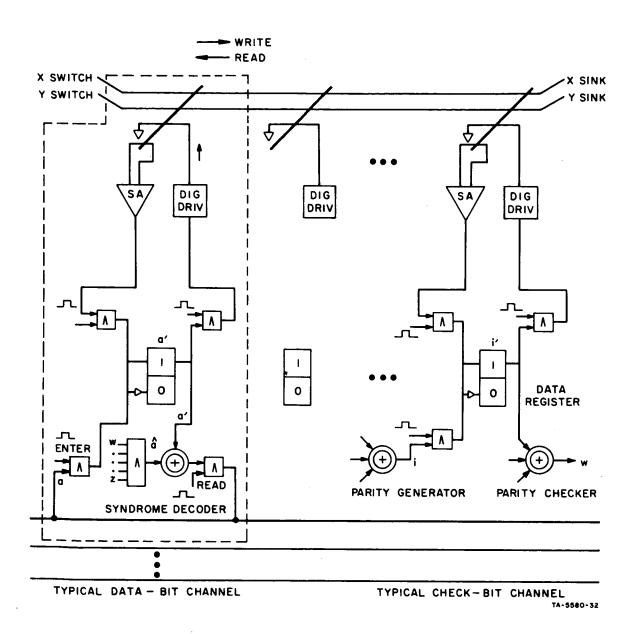

|       |          | d. Power Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |