### EES SERIES REPORT NO. 12

LE . 12

# PROGRESS OF ANALOG-HYBRID COMPUTATION 1966

| 1 N67 26071                   |            |

|-------------------------------|------------|

| 36                            | (THRU)     |

| (PAGES)                       | (CODE)     |

| (NASA CR OR TMX OR AD NUMBER) | (CATEGORY) |

ENGINEERING EXPERIMENT STATION

COLLEGE OF ENGINEERING

THE UNIVERSITY OF ARIZONA

TUCSON, ARIZONA

Granino Arthur Korn was born in Berlin, Germany, on May 7, 1922. He was graduated from Brown University, Providence, R. I., in 1942, and received the M.A. and Ph.D. degrees in physics from Columbia University, New York,

N. Y., and Brown in 1943 and 1948, respectively.

After wartime service in the U. S. Navy, he was, successively, a Project Engineer with Sperry Gyroscope, Great Neck, N. Y., head of the analysis group at Curtiss-Wright/Columbus, a staff engineer with Lockheed/Burbank, and a consultant under his own name. Since 1957, he has been a Professor of Electrical Engineering at the University of Arizona, Tucson, where he teaches courses on electronic computers and random-process measurements; he is also a Director of Computer Research, Inc., Lafayette,

With his wife, Theresa M. Korn, he is the author of Electronic Analog Computers (1952 and 1956), Mathematical Handbook for Scientists and Engineers (1961), Electronic Analog and Hybrid Computers (1964), Basic Tables for Electrical Engineering (1965), Random-Process Simulation and Measurements (1966), and Manual of Mathematics (1966). He is co-editor-in chief of the McGraw-Hill Computer Handbook (1962) and the Digital Computer User's Handbook (1967) and has contributed articles to seven other engineering handbooks. He edits Mc-Graw-Hill's new series of short numerical tables and is chairman of the editorial board of Simulation. He has taught in Mexico and surveyed engineering education in Chile as a Consultant to the National Academy of Sciences.

Dr. Korn is a member of Sigma Xi, Simulation Councils, Inc., and the International Analog Computer Association.

### Progress of Analog Hybrid Computation

G. A. KORN

Abstract—Solid-state circuits and the integrated circuits succeeding them are improving analog-computing-element reliability by an order of magnitude, speed by two orders of magnitude, and still reducing system cost. The effects of integrated-circuit technology on the price, reliability, and sophistication of digital computers are even more pronounced, and the resulting system-design tradeoffs shape the future course of hybrid-computer techniques. This review article discusses the design of fast analog/hybrid computer systems, including recent developments in integrated operational amplifiers, electronic mode-control switches, digital attenuators, and new packaging techniques.

### SURVEY

NOMPUTERS are physical systems designed to implement the idealized relationships of mathematical models. Computers are conventionally classified as analog computers if the machine variables representing mathematical quantities are considered to vary continuously (voltages, shaft rotations), while a digital computer is a discrete-state system. The engineer's most noticeable impression of an analog computer is likely to be a fast, only moderately accurate differential-equation solver (differential analyzer) employing separate (parallel) analog computing elements to implement each mathematical relation; while the most important digital computers perform numerical operations accurately and sequentially and incorporate considerable decision-making ability and a large memory to permit stored-program control of computation and iterative operations. Advancing technology has evolved

Manuscript received August 16, 1966. This work is one of the University of Arizona's ASTRAC II and LOCUST projects, under NASA Grant NsG-646, together with various grant supplements and institutional grants. The APE II educational iterative differential analyzer was developed under NSF Grant GY-379; ASTRAC II was begun under joint NASA/U. S. Air Force sponsorship.

The author is with the University of Arizona, Tucson, Ariz.

the familiar analog computer into a wide class of *hybrid-analog-digital computers* which may combine high analog computing speed with accurate digital operations, decision making, and memory.

Computers, analog, digital, or hybrid, have two principal applications. They may set up mathematical relations to produce desired unknown or otherwise desired quantities and/or functions (problem solving, simulation of engineering systems). The second (and at least as important) application of computing devices is as *system components* used for instrumentation, control, and display: here, the computer forces at least a portion of a reluctant physical system to act like a mathematical model and thus recreates it nearer to the heart's desire.

Up to 1960, the simulation of dynamic systems such as aircraft, missiles, space vehicles, and nuclear and chemical plants was accomplished almost entirely by means of electronic analog computers. The parallel computing elements of such machines permit high-speed real-time solution of differential equations, and establish a block-diagramoriented, live mathematical model offering a good deal of intuitive insight into system operation. "Hands on" changes of system parameters, programs, and subsystems are readily possible with analog computers; solutions can be observed on multi-trace and xy recorders to provide the investigator with immediate feedback about the results of system changes. Analog-computer studies of large dynamic systems also show up significant disadvantages of this type of computation; the relatively low component accuracies permit long-term trajectory studies only if sophisticated mathematical perturbation techniques are applicable, and such techniques destroy much of the intuitive insight of direct

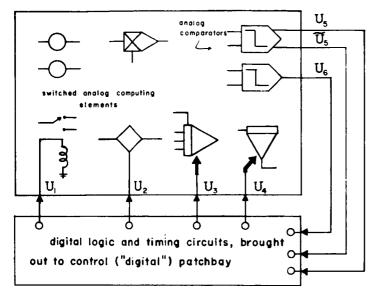

### analog computing elements

O control-patchbay termination

(a)

Fig. 1. (a) Iterative-differential-analyzer operation. (b) Flow diagram. The principal operations are analog-computer (differential-analyzer) runs simulating a physical system, as ordered by electronic switches actuated by corresponding digital control variables  $U_i$ . Control-variable changes may be preset by timers and counters and/or "computed" by analog comparators and digital logic. Switches and comparators form the digital-analog and analog-digital interfaces. Typical applica-

simulation. Moreover, scale factor estimation and problem checkout can become very cumbersome.

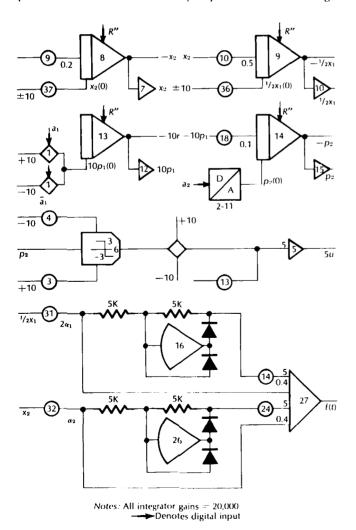

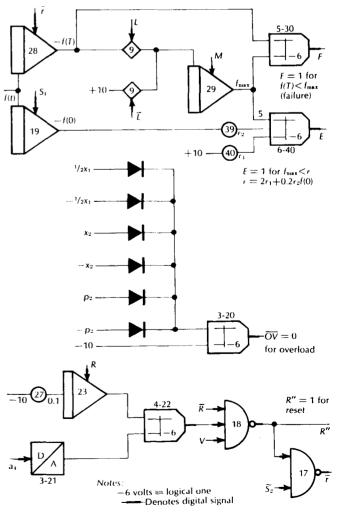

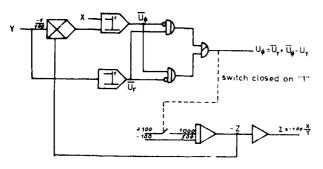

Improved simulation techniques combining analog and digital computation take two essential forms, which are often used in combination. An iterative differential analyzer is an electronic analog computer incorporating analog memory in the form of track-hold circuits and equipped with analog comparators, patchable digital logic elements, and comparator- or logic-operated D/A switches, and timing circuits (Fig. 1).

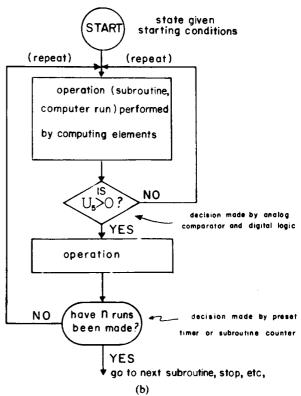

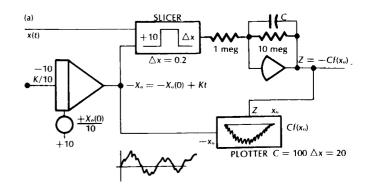

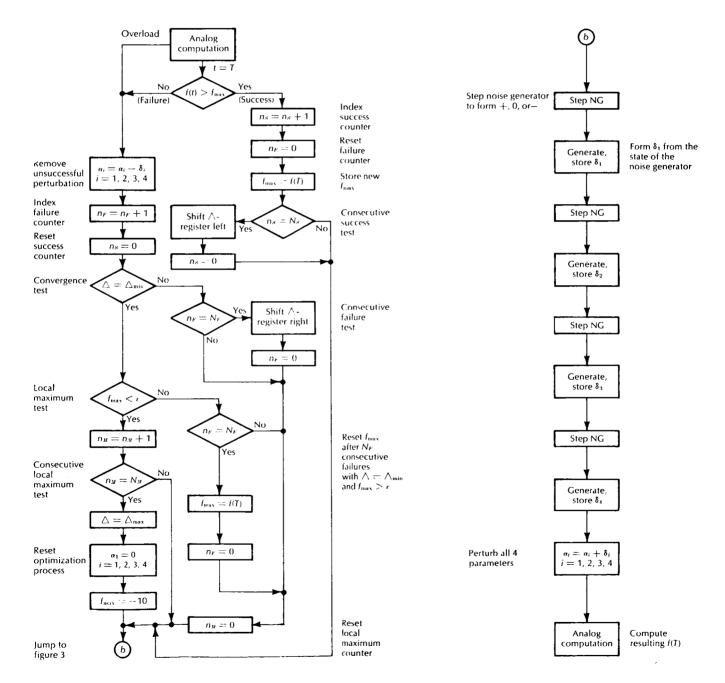

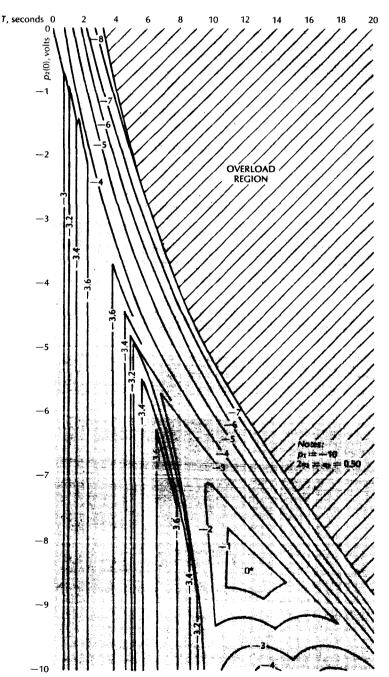

Such machines have, thus, a measure of the memory and decision-making ability of a digital computer; integrator mode control and, to some extent, analog-computer programs and system parameters can be changed by the digital logic which, in turn, takes account of analogcomparator decisions. This permits complex subroutine control, branching, simulation of digital computers, multiplexing of computing elements, and, above all, automatic iteration and system optimization. The iterative differential analyzer is at its best in its more recent ultra-high-speed versions permitting iteration of as many as 2000 complete system simulations per second under digital-logic control. Such fast iterative computations permit rapid computation of statistics (Monte Carlo methods), so that the system designer receives practically immediate feedback of the effects of system parameter changes on statistics, and automatic optimization of statistics becomes possible (Fig. 2) [2].

tions are to iterative optimization of the simulated system and to statistical computations. A small or large general-purpose digital computer may be added and will communicate with the analog computer via A/D and D/A converters, and with the control logic via interrupt and sense lines and by digital commands fed into the control patchbay [19].

True combined analog-digital simulation with an analog computer (usually an iterative differential analyzer) joined to a general-purpose digital computer through a converter linkage [1] has permitted real-time simulation of large and very complicated systems. The digital computer is, in particular, employed for accurate and relatively slow trajectory integration, while the analog computer deals with the high-speed dynamics; in addition, the digital computer can conveniently store and/or compute complicated functions of several variables and, also, perform many housekeeping tasks such as potentiometer setup, static checking, and the computation of accurate check solutions. Combined simulation is often made mandatory by stringent combinations of speed and accuracy requirements. But it should be remembered that combined simulation joins not only the advantages of analog and digital computers but their disadvantages as well, for the simulation suffers both from the low precision of the analog computer and the sampled-data bandwidth limitation of the digital machine. In addition, large combined systems tend to be complex and very expensive, and the difficult and sophisticated programming required destroys much of the intuitive appeal of the simulation.

By contrast, the use of one of the increasingly inexpensive small (12- to 16-bit) general-purpose data processors as an—immeasurably improved—logic and control unit for a fast iterative differential analyzer has proved to be an extra-

Fig. 2. This example illustrates the possibilities of combining a fast iterative analog computer with a small stored-program digital data processor.

Analog computing elements produce successive samples of the squared-error time average

$$\langle {}^k e^2(t) \rangle_T = (1/T) \int_0^T {}^k e^2(t) dt$$

for a simulated control system with random input and noise. The digital computer finds successive values of the sample average

$$\overline{\langle^k e^2(t)\rangle_T} = (1/n) \sum_{k=1}^n \langle^k e^2(t)\rangle_T$$

for n = 100 to 10 000 computer runs and changes control-system parameters so as to optimize the sample average. Note that each analog-digital and digital-analog conversion and digital-computation sequence is required only once per analog-computer run (from G. A. Korn, "Hybrid-computer Monte-Carlo techniques," *Proc. IFIP Cong.*, New York, May 1965; see also [2]).

ordinarily successful combination of analog and digital computers. The small digital computer performs timing and mode-control functions, computes statistics, and optimizes parameter combinations; even with 2000 analog-computer runs per second, most digital-computer operations take place only once per analog-computer run, so that the digital computer can perform very sophisticated logic and statistical operations at a comfortable rate. At the same time, the small digital computer again performs housekeeping functions such as the setting of potentiometers (more recently replaced by digital attenuators), static checks, and various routine computing chores around the simulation laboratory.

The essential components of electronic analog computers are resistor-capacitor-diode networks and operational amplifiers; as electronic-analog/hybrid computation enters its third decade, a technical revolution has made the use of vacuum tubes in analog computers as wholly obsolete as it is in portable radios or in digital computers. The advent of monolithic integrated circuits—linear as well as digital—and new field-effect devices promises to decrease prices of

operational amplifiers by a factor of three while frequently eliminating the need for chopper stabilization and extending attainable bandwidths to tens of megacycles. At the same time, mean-time-between-failures has increased by at least an order of magnitude, while integrated-circuit miniaturization further reduces computer cost by eliminating much interunit wiring. The new technology is beginning to produce reliable, exceptionally flexible, very fast iterative differential analyzers in the medium-size 50 to 100 amplifier class; they are well equipped with modern nonlinear computing elements, digital logic, and all-electronic mode control. Somewhat smaller machines are beginning to make a pronounced impact on modern engineering education: as an example, the University of Arizona, Tucson, in the last quarter of 1966, had 29 analog computers distributed over at least six departments; all engineering students learn FORTRAN and analog-computer simulation in a special course integrated with their progress in advanced calculus and ordinary differential equations.

The development of analog and hybrid-analog/digital computation is intimately bound up with the corresponding

progress of digital computation. The integrated-circuit revolution is producing excellent flexible and fast digital computers whose price tags read below \$20 000; at the same time, larger digital computers are conveniently time-shared by many users through multiple stations. Coupled with ever-increasing digital-computer speeds, both methods increasingly permit direct intercourse between man and digital computer, an advantage heretofore reserved for analog computers. While the cost of both small digital computers and time-shared large installations is continually decreasing, improved graphical displays and programming consoles, together with the freedom from analog scaling afforded by floating-point hardware, make digital simulation increasingly attractive. The replacement of many large analog and even hybrid-analog-digital simulations, such as three-dimensional flight simulations, by new all-digital simulators has already overtaken training-type flight simulators and is proceeding into the engineering departments of larger aircraft companies. The coming breakthrough of digital dynamic-system simulation will require design effort on more powerful human-factor engineered display consoles permitting instant interaction between operator and machine, improved numerical techniques, and multiple digital processing with the aid of special-purpose digital computing elements implementing time-consuming subroutines. The perfection of all these techniques awaits only the pleasure of the digital-computer manufacturers, for whom simulation represents only a relatively small fraction of the market. In the meantime, a number of new digital block-diagram interpreter and compiler programs permit simulation of an analog computer with a conventional digital computer.

A common feature of iterative-differential-analyzer operation, digital simulation, and combined analog-digital simulation is an ever-increasing need for more sophisticated mathematical techniques and, in consequence, for better-educated investigators. The use of computers for excessively complete simulation can rarely substitute for mathematical insight into a problem; automatic system optimization requires knowledge of an increasing body of mathematical theory; perturbation techniques permit the attainment of astonishing accuracies with simple analog computers; combined simulation requires a knowledge of sampled-data theory; and effective utilization of the computer consoles now within easy reach of every researcher or system designer will require much re-education of our modes of thinking in research and system design.

### REQUIREMENTS FOR REALLY FAST ANALOG COMPUTATION

While "slow" analog computation at signal frequencies below about 100 Hz still constitutes the bulk of simulation work, at least the larger "slow" analog computers will tend to be displaced by new general-purpose digital computers as the latter improve. Even at present, modern hybrid-computer installations tend to replace every possible analog operation with digital routines to save maintenance and scaling; one might say that the analog-digital interface of existing hybrids is moving so that more and more of the

"slow" analog equipment is associated with crew-station simulation and other partial system tests. The most fruitful applications of really fast iterative analog computation (iterative rates > 200 Hz, signal frequencies > 2 kHz) is to statistical applications (Monte Carlo simulation), to rapid system optimization, and to combinations of these (Fig. 2). The real advantage of fast computation is not the mass production of data (this could be done by a digital computer working at night), but the possibility of direct on-line-operator interaction with the results from, say, a sample of 1000 computer runs completed in a second or less.

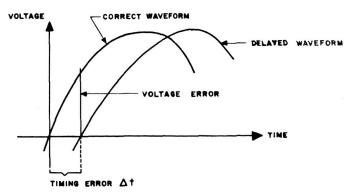

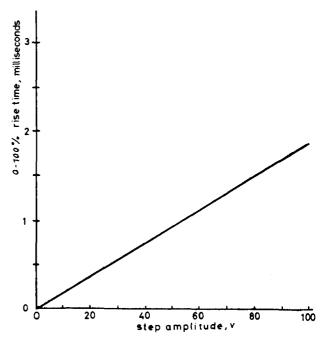

As a matter of competitive advertising, most commercially available analog/hybrid computers offer repetitive operation at 1000 computer runs per second, but this is usually wholly misleading. It is easy to supply computerreset pulses at 1 kHz, but meaningful computation at such iteration rates requires, at least, component accuracies within 0.2 percent at signal frequencies of 5 to 10 kHz. It is instructive to investigate just what such a requirement means. Before one can even think of dealing with possible amplitude errors, it is necessary to control errors due to phase shift and switching time delays [1]. The effects of phase shift in amplifiers and passive networks and those of time delays caused by late operation of integrator and track-hold mode-control switches and analog comparators cause quite similar delay errors, as illustrated in Fig. 3. Given a signal waveform changing at the rate  $2\pi a$  (typically a sinusoidal voltage  $a \cos 2\pi f t$  of frequency f Hz), a timing error of  $\Delta t$  seconds, or an equivalent phase-shift error,  $\Delta \phi$ radians cause the true percentage error

$$\varepsilon = 200\pi f \Delta t = 100\Delta \phi. \tag{1}$$

The "magic equation" (1) spells the doom of high-frequency computation with most commercially made equipment. Consider the very lenient requirement of 0.2 percent error at a computing frequency of 5 kHz. This requires:

- 1) Phase-shift errors  $\Delta \phi$  below 0.002 radians or about 0.12 degrees at 5 kHz. Even in a unity-gain phase inverter, this requires amplifiers with a zero-dB crossover frequency of 10 MHz with a 20 dB/octave rolloff, and perhaps 2 MHz for a less conservative rolloff. The situation becomes exactly ten times worse for a gain-of-10 phase inverter, not to speak of multipliers and function generators. Nevertheless, such requirements can be met with  $\pm$  10-V feedforward amplifiers (described further in the following) and clever equalization.

- 2) The above phase-shift requirements extend to all passive networks, attenuators, and interconnection lines (if any) in the computer. Distributed capacitances make the 100-K resistors used in commercial analog computers act like veritable delay lines at high frequencies. While some of these ills can be cured with equalizing capacitors, probably the best solution is the use of 1-K to 10-K summing resistors and similarly low impedance levels in all attenuators. Solid-state computing elements can be mounted directly behind

Fig. 3. Timing errors  $\Delta t$  or phase errors  $\Delta \phi = 2\pi f \Delta t$  are crucial in fast analog computation.

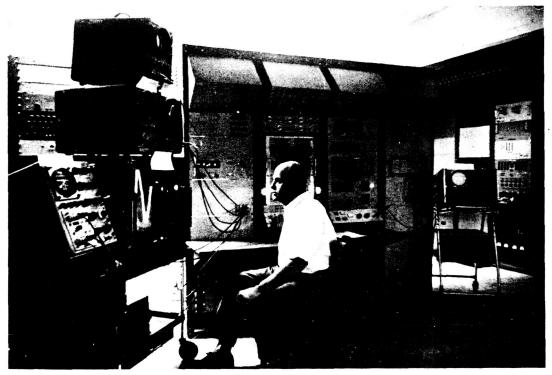

Fig. 4. Operating with signal frequencies as large as 60 kHz, the digitally controlled ASTRAC II here displays the complete input-output cross-correlation function of a fast-time simulated control system with

random input once every second. The operator can immediately assess effects of system-parameter changes on statistics computed from hundreds of analog-computer runs.

the analog-computer patchbay without any interconnecting lines.

- 3) A glance at the "magic equation" (1) shows clearly that 0.2 percent accuracy at 5 kHz requires all integrator mode-control switches to initiate computation within 65 ns of one another. Such *differential* switching times for integrators and track-hold circuits are possible only if the total switching time is below about 200 ns.

- 4) If an analog comparator or D/A switch must respond in the course of a computer run, its *total* (not differential) response time must be within 65 ns. Fortunately, most fast iterative computation requires comparators to respond to track-hold outputs only, so that timing does not cause errors.

A frequently redeeming feature is the fact that the highest

signal-frequency components constitute only, say, 10 percent of the total analog signal, so that the total percentage error is reduced. In any case, (1) indicates that some commercially available analog computers can compute with fair accuracy at repetition rates of the order of 50 to 200 Hz. The ASTRAC II and LOCUST iterative analyzers (Fig. 4) developed at the University of Arizona under NASA and U. S. Air Force sponsorship do permit 1 kHz iteration; unity-gain-inverter phase shift is below 0.1 deg at 10 kHz, with integrator differential switching times below 20 ns, and comparator response time below 80 ns.

### SOME HYBRID-COMPUTER SYSTEM CONSIDERATIONS

Since their inception about a decade ago, combined analog-digital computer systems have developed from true monstrosities into reasonably finished hardware; software and programming know-how are still lagging component

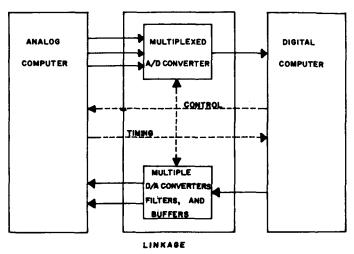

Fig. 5. Simplified hybrid-computer loop.

developments. In addition to the usual computing errors inherent in analog and digital computers as such, the hybrid-computer system (Fig. 5) adds some errors of its own; these error sources are nicely discussed in [3]-[7]. Briefly, the errors due to hybrid-computer operation as such are:

- Conversion errors due to poor A/D and D/A converters.

- 2) Quantization errors due to the finite number of digital bits; with the usual 13- to 14-bit systems, these are rarely serious and can often be further reduced through the application of dither [2]. Reference [6] presents a sophisticated theory for quantization-error estimation, but the best estimates are obtained by digital-computer test routines which simply reduce the number of bits used for a test run.

- 3) Errors due to digital processing and conversion time delays. While elaborate studies of such errors by means of Z-transform analysis are possible at least for linear systems [4], [5], we can simply consider the entire digital computer and linkage (Fig. 5) as an analog computing element having a time-delay error  $\Delta t$ ; then the "magic equation" (1) estimates the component error, which in each hybrid-computer setup affects the solution very much like a phase-shift error  $\Delta \phi$ =  $2\pi f \Delta t$  for sinusoidal components of frequency f.

- 4) Skewing errors due to nonsimultaneous analog-digital and/or digital-analog conversion of different computer variables.

To minimize the effects of the various timing errors, one makes the processing delay  $\Delta t$  constant through suitable interruptions of the digital computation. Partial compensation of the time-delay error is then obtained with the aid of ordinary lead networks ahead of the analog-to-digital converter, or by the more sophisticated method of predictive extrapolation, either in the digital computer or with extrapolating digital-to-analog converters [1], [5], [7]. The processing delay  $\Delta t$  is essentially reduced to the time taken for the digital computations on each analog sample if the

digital computer is equipped with a direct memory-access channel. With this option, which should be included in every digital computer used for hybrid computation, it will usually be found that the skewing errors are small compared to the time-delay errors.

### **ANALOG-SYSTEM COMPONENTS**

We turn next to the design of the analog-computer system.  $\pm 100\text{-V}$  analog computing elements may be preferred for optimal accuracy in "slow" simulation, because static accuracy in nonlinear computing elements is less expensive to obtain and maintain in a  $\pm 100\text{-V}$  system. Note, however, that static errors within 0.02 percent of half-scale can be maintained with  $\pm 10\text{-V}$  summers and multipliers as well as with  $\pm 100\text{-V}$  components [7].  $\pm 10\text{-V}$  amplifiers can be faster and less costly than  $\pm 100\text{-V}$  amplifiers; but the main advantage of  $\pm 10\text{-V}$  systems is the possibility of utilizing lower computing impedances to improve bandwidth, integrator drift, and computer noise. Miniaturization, which brings further bandwidth advantages, is also managed more easily at  $\pm 10\text{-V}$  because of the reduced heat-dissipation requirements.

The most accurate "slow" analog computers still employ wirewound resistors, but these are giving way to new precision metal-film resistors, at least wherever bandwidth is a consideration. Carbon-film resistors may be regarded as obsolete for analog-computer applications.

In the most accurate analog computers, capacitor dielectric absorption, calibration, electroelastic, thermal, and hysteresis effects are critical accuracy-limiting factors; they cause component errors of the order of 0.02 percent [1]. Fine-grain polystyrene film is still the preferred dielectric. Compression trimming of plastic-film capacitors, which implies the possibility of mechanical deformation of foil and dielectric, is apt to cause more trouble than it cures. A significant step forward was the 1965 development of a simple equalizer circuit [8] capable of reducing dielectric-absorption effects to below 0.005 percent. An important consequence is the possibility of a more favorable compromise between capacitor dielectric absorption and the temperature coefficient of capacitance.

The hybrid-computer era has seen relatively little improvement in the design of analog multipliers and function generators, although it is now possible to compensate both special-purpose and general-purpose diode function generators accurately for diode-breakpoint drift with temperature by including matched diodes in the bias supplies [7]. Diode quarter-square multipliers have almost entirely displaced servos and time-division multipliers and have attained component accuracies of better than 0.05 percent of half-scale; special wide-band multipliers have errors as low as 0.5 percent at 10 to 50 kHz [2]. Accurate diode quarter-square multipliers are expensive and have obvious disadvantages due to their inherent piecewise-linear approximation of the product. Some renewed investigation of time-division multipliers employing new types of solid-state switches may well be in order.

Where bandwidth considerations permit, nonlinear op-

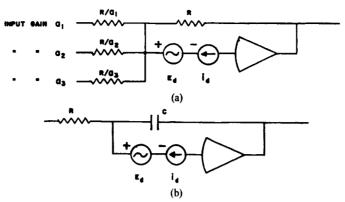

Fig. 6. (a) Summing amplifier. (b) Electronic integrator. Both show offset voltage and current sources.

TABLE I

TYPICAL DRIFT ERRORS IN GENERAL-PURPOSE ANALOG COMPUTERS (1966)

(Maintained at 25 ± 5 deg C, with regulated power supplies (2))

|                                                     | Integrated Circuit $\pm 10$ V, no chopper $R = 10$ K | $\pm 10 \text{ V FET}$<br>input, no chopper<br>R = 10  K to 100 K | High-quality chopper-stabilized amplifier (FET chopper) |                                         |

|-----------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------|

|                                                     |                                                      |                                                                   | $\pm 10 \text{ V}$<br>R = 10 K to 100 K                 | $\pm 100 \text{ V}$<br>R = 100 K to 1 M |

| $E_d$                                               | ± 30 μV                                              | ± 60 μV                                                           | ± 10 μV                                                 | ±40 μV                                  |

| $i_d$                                               | ± 30 nA                                              | negligible                                                        | negligible                                              | negligible                              |

| $e_{\text{sum}} (a_1 + a_2 + a_3 = 1)$              | $\pm 360 \mu V$                                      | $\pm 120 \mu V$                                                   | $\pm 20 \mu\text{V}$                                    | $\pm 80 \mu V$                          |

| $e_{\text{sum}} (a_1 + a_2 + a_3 = 21)$             | $\pm 960 \mu V$                                      | ± 1.3 mV                                                          | $\pm 220 \mu V$                                         | $\pm 880 \mu V$                         |

| $e_{int}$ (typical computer run, $t/RC = 50$ )      | $\pm 16.7 \text{ mV}$                                | $\pm 3 \text{ mV}$                                                | $\pm 500 \mu\text{V}$                                   | $\pm 2 \text{ mV}$                      |

| $e_{\text{int}}$ (long integration, $t/RC = 1000$ ) | ±0.33 V                                              | ± 60 mV                                                           | $\pm 10 \text{ mV}$                                     | $\pm 40 \text{ mV}$                     |

erations are performed digitally, or by multiplying D/A converters. Even after 20 years of development, setup procedures for diode function generators are still cumbersome; a number of manufacturers have developed card- and patch-board-programmed diode function generators to simplify function storage. The problem of generating functions of two or more variables is as bad as ever [1]. With small general-purpose digital computers available at prices as low as \$10 000, the best solution for function generation, at least in "slow" analog simulation, appears to be to utilize such a small digital computer for the generation of between five and ten analog functions: at a price of \$10 000 for the digital computer, plus \$5000 for a simple linkage, the cost per function is still comparable to that of commercially available card-programmed function generators [9].

### LOW-DRIFT DC AMPLIFERS

Solid-state dc amplifiers can have substantially lower drift than vacuum-tube amplifiers. Dc amplifier drift is specified in terms of the equivalent voltage and current offset after a given time interval, power-supply-voltage change, or temperature change. Referring to Fig. 6, the equivalent-input-offset voltage  $E_d$  and current  $i_d$  are, respectively, defined as minus the input voltage and current needed to return the open-loop output to zero (balance condition) with a grounded voltage source and a current source at the summing point. In the summer and integrator circuits of Fig. 6,

the output-voltage errors due to drift, assuming high amplifier gain, are [1]

$$e_{\text{sum}} = -(a_1 + a_2 + a_3 + 1)E_d - Ri_d \quad \text{(summer)}$$

$$e_{\text{int}} = -\frac{t}{RC}(E_d + Ri_d) \quad \text{(integrator)} \quad (2)$$

where t is the computing time. Table I illustrates drift-error effects for typical computer dc amplifiers operated over normal room-temperature ranges.

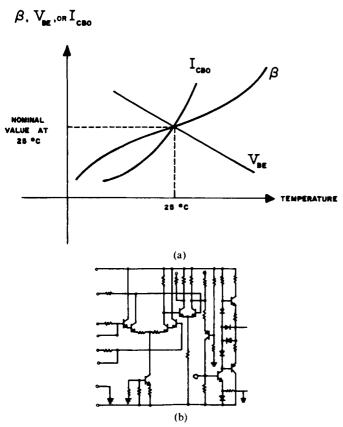

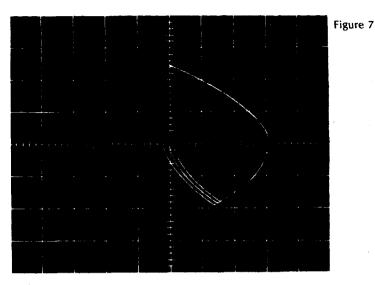

The design of high-quality solid-state dc amplifiers, both discrete-component and integrated-circuit types, has reached a high state of development. Figure 7(b) illustrates an amplifier circuit typical of recent integrated-circuit design. It is worthwhile to list the circuit features used to obtain low drift in such amplifiers.

A differential input stage with a current-source transistor in the emitter return ties the temperature dependence of the first-stage output to the difference of two transistor  $V_{BE}$ 's; transistor matching for  $V_{BE}$  and  $\beta$  can reduce voltage drift from 2.5 mV/deg C to as little as 5  $\mu$ V/deg C [1]. Matching is especially favorable in monolithic integrated circuits; differential heating of the two input transistors must be minimized by low values of the collector current (<200  $\mu$ A). The first-stage gain should be sufficiently high (at least 10) to make drift effects in later stages negligible. A roughly matched second differential-amplifier stage may

Fig. 7. (a) Temperature dependence of transistor parameters. (b) Typical integrated-circuit dc amplifier (similar to Westinghouse Type 174Q).

follow the first for more perfect common-mode rejection, or common-mode feedback from a succeeding stage may be used [1].

Differential-amplifier voltage drift can, we note in passing, be reduced below 0.5  $\mu$ V/deg C if the  $V_{BE}$  temperature coefficients are matched through individual collector-current adjustments [1], but this has not been applied in production.

Current drift, which may be thought of as a change in input-transistor bias-current requirements, is due to changes in  $i_c/\beta$  and in the leakage current  $I_{CBO}$ . The latter is negligible for silicon transistors at room temperatures; at higher temperatures, the I<sub>CBO</sub> change will, in fact, counteract the  $i_c/\beta$  change with temperature. It is possible to compensate for the current drift with the aid of temperature-dependent current sources comprising thermistors, diodes, or transistors, or to counteract changes in  $\beta$  by corresponding temperature-dependent changes in  $i_c$  [1]; but such compensation schemes work best over limited temperature ranges (perhaps 10 to 20°C) because of the nonlinear temperature dependence of  $\beta$  [Fig. 7(a)]. In general, the best method for reducing current drift is to use high-\beta transistors and to keep the first-stage collector currents below 100 to 200  $\mu$ A. This reduces  $i_c/\beta$  in toto and, hence, also its changes with temperature. In Fig. 7(b), the input current has been further reduced through the inclusion of common-collector input transistors, which roughly divide the bias-current requirement by another factor of  $\beta$ . It is thus possible to reduce the *total* input current well below 100 nA between -50 deg C and 180 deg C. The differential-amplifier connection as such can reduce current drift only if both input transistors are connected to similar source impedances; this is rarely the case in general-purpose computers.

In dc amplifiers requiring very low input currents and high input impedances, junction FET's may replace the input transistors to reduce input currents to the order of picoampères; MOSFET's are not recommended for dc-amplifier input stages, since they may tend to change their properties with time. The voltage drift of FET dc-amplifier stages can be reduced through selection of an optimal operating point [12] and by matching of differential-amplifier stages. The best FET amplifiers now have about the same voltage drift as high-quality bipolar transistor stages (3 to  $10 \, \mu\text{V/deg C}$ ; also see Table I).

### IMPROVED ELECTRONIC CHOPPERS

In accurate general-purpose analog computers, the possibility of open-loop integration of offset voltages and currents still makes dc amplifier chopper stabilization [1] mandatory. MOSFET choppers operated at frequencies of 100 to 1000 Hz have long-term input voltage offsets below 20  $\mu$ V and negligible current offset over a wide range of temperatures. Sinusoidal drive to the input chopper reduces switching spikes. FET choppers permit low-voltage drive at higher frequencies than neon-bulb/photoresistor choppers and are also more reliable.

#### INTEGRATED-CIRCUIT CONSIDERATIONS

Special integrated-circuit considerations in amplifier design require that voltage levels depend on resistance ratios rather than resistance values. Large resistance values should be avoided whenever possible, extra transistors can be added just about as easily as resistors, and transistor matching and thermal coupling must be generally excellent. While earlier types of monolithic integrated circuits had only NPN transistors, complementary transistors are readily included in more recent designs, a very important advantage. Breakdown voltages have been greatly improved recently, so that  $\pm 10$ -V operation is possible without much adverse effect on bandwidth. New ceramic insulation [23] can be expected to improve monolithic dc amplifiers still further.

### THE STRIKING ADVANTAGES OF FEEDFORWARD AMPLIFIERS

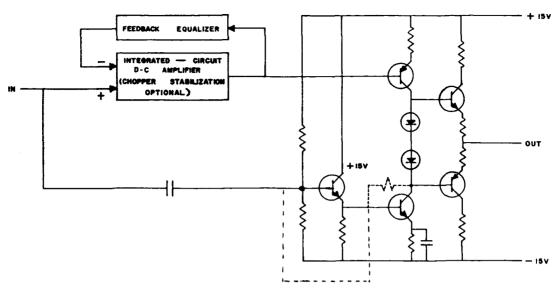

Feedforward amplifiers (Fig. 8) pass high-frequency-signal components through a high-pass filter directly to a wide-band output stage, while cascading a high-gain dc amplifier with the output stage for lower frequencies; the well-known chopper stabilizers for dc amplifiers are special cases of feedforward circuits [1].

The now widely used  $\pm 10$ -V high-gain class AB complementary output stage of Fig. 8 can have a gain as high as 2000 at 20 kc with unity gain at 25 to 100 MHz, depending on transistors and load. It has relatively low quiescent current and is especially well suited to feedforward operation,

Fig. 8. Feedforward dc amplifier employing a fast class AB output stage and an integrated-circuit dc amplifier (LOCUST computer, University of Arizona).

since high- and low-frequency signals are added without the usual mixing loss [1]. The combination of such a feed-forward output stage with a modern low-cost integrated-circuit input amplifier yields a number of remarkable advantages:

- The amplifier high-frequency response is essentially that

of a single wide-band stage followed by an emitter follower, and no shunt rolloff networks are required for

stabilization. As a result, such amplifiers can produce

full ±10 V, 30 mA output all the way up to 2 MHz.

- 2) The feedforward combination completely avoids the usual compromise between high-frequency response and low-drift/low-noise design of the dc-amplifier input stage. If this fact were more generally realized, the current drift and low-frequency-flicker noise of many general-purpose integrated-circuit dc amplifiers could be improved by at least a factor of three by the simple expedient of reducing their input-stage collector current; the feedforward connection would take care of the frequency response.

The circuit of Fig. 8, intended for the University of Arizona's LOCUST iterative differential analyzer, combines a commercially available, low-cost, low-drift integrated-circuit amplifier with the discrete-circuit output stage to produce a high-quality, wide-band amplifier at very low cost. A chopper-stabilizer stage can be added to permit more accurate low-frequency integration.

A very similar circuit also permits the design of inexpensive  $\pm 100$ -V, 25-mA dc amplifiers: one merely replaces the class-AB complementary output stage shown in Fig. 8 by an NPN/NPN 100-V totem-pole output stage having a gain of approximately 12.

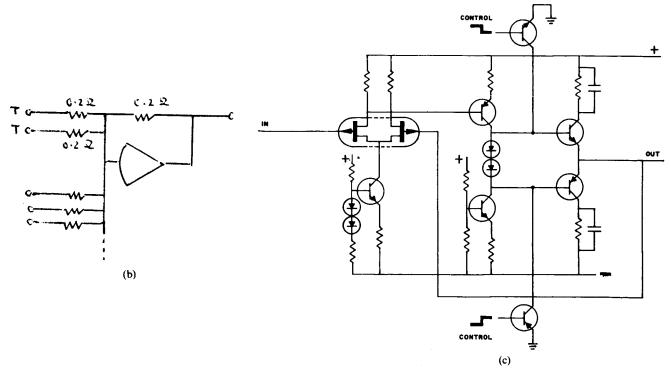

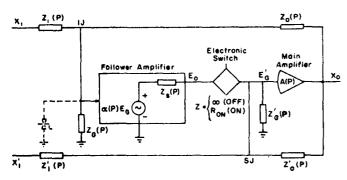

IMPROVEMENTS IN ELECTRONIC MODE-CONTROL SWITCHING

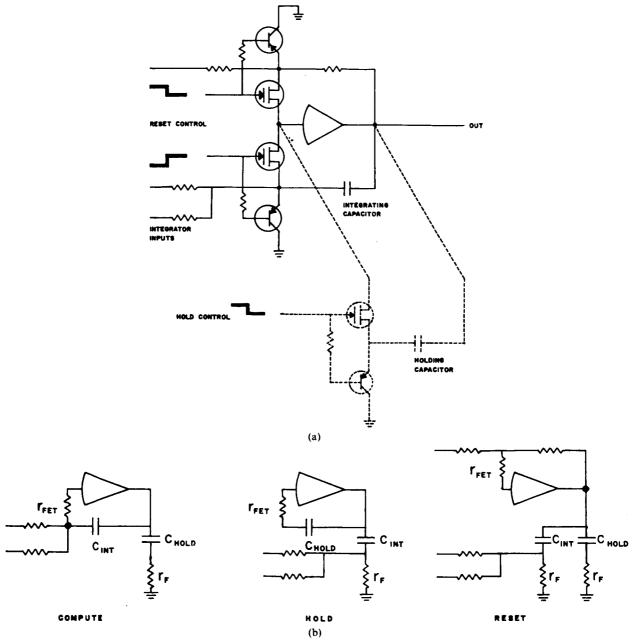

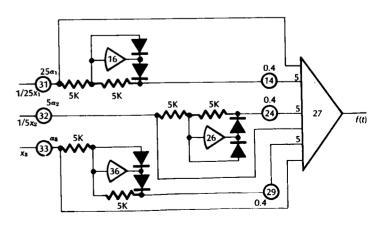

The computing errors caused by electronic mode-control switching for integrators and track-hold circuits are dis-

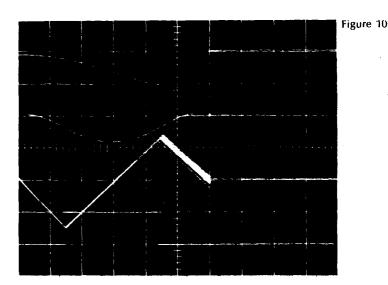

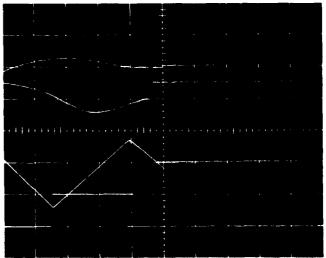

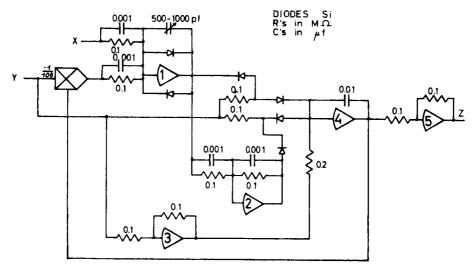

cussed in detail in [1], [7], [16], and [17]. In addition to the high switching speeds already discussed, high-quality electronic switches must have high back resistance, low forward resistance, minimum voltage and current offset, and low spike-causing capacitance between logic (control) and signal circuits. Figures 9 and 10 illustrate two modern electronic switching schemes for integrator control; others are described in [1]. In particular, the circuit of Fig. 9 employs 200 to 800 ns FET switches inside feedback loops to avoid FET forward-resistance effects: it practically duplicates the static accuracy of relay switching. The circuit also permits fast integrator resetting: in RESET, the integrating capacitor charges through a low-impedance path. On the other hand, the requirement for a separate holding capacitor (in reality, one capacitor for each time scale provided), as well as multiple switching, makes this circuit quite cumbersome. The finite forward resistance  $r_F$ of the bipolar transistor grounding the holding capacitor causes the stored value to be in error by 200  $\pi f r_F C$  percent for sinusoids of frequency f[1].  $r_F$ , which is of the order of 10 ohms, will also cause some feedthrough from the integrator inputs in RESET. This mode-control circuit is, therefore, best suited for relatively slow, high-impedance computers.

The switched-amplifier method [Fig. 10(a), (b)] used in the University of Arizona's ASTRAC II, APE II, and LOCUST computers employs a switched feedback amplifier whose very low output impedance (less than 0.2 ohms in ASTRAC II) practically shortcircuits the effect of the integrator inputs so that they need not be opened by a separate switch in RESET. No HOLD mode is provided; all holding is done with separate track-hold circuits, which greatly simplifies digital control and improves frequency response, but may require additional equipment. Since the high-current switch is never saturated, switches of this type are the fastest integrator mode-control switches available (total switching time 40 to 80 ns, differential switching time less than 20 ns). The ASTRAC-II circuit is described in

Fig. 9. FET mode-control circuit with optional HOLD circuit indicated (a) in dash lines and (b) equivalent circuits.

detail in [17]; Fig. 10(c) shows a developmental switch with a low-drift FET input stage.

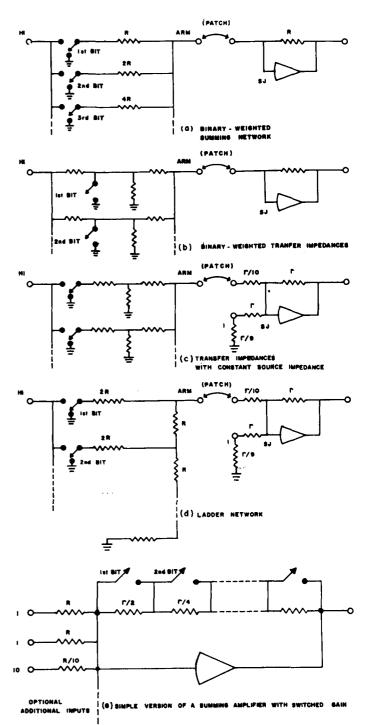

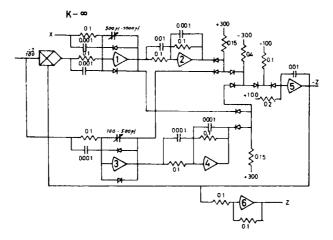

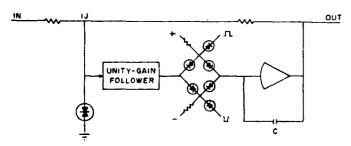

### DIGITAL ATTENUATORS FOR COEFFICIENT SETTING

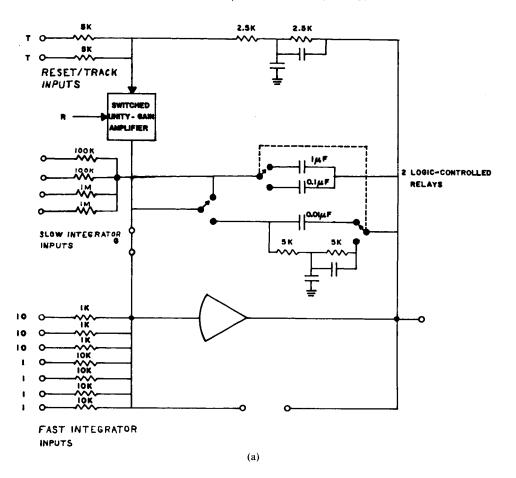

Digital attenuators for coefficient setting are simplified D/A multipliers designed to switch only in the computer RESET (or POTSET) and HOLD modes. Digital attenuators are set up either by keyboard or, more frequently, by digital computer commands. They offer higher setting speeds and, hopefully, greater reliability than servo-set coefficient-potentiometer systems.

The earliest commercially available system set the last few bits of its digital attenuators through a feedback loop similar to a servo-set-potentiometer system. This permitted the use of low-offset FET switches without special compensation for the FET resistances. It seems simpler, however, to employ open-loop setting of bistable reed relays, which give each attenuator a nondestructive memory and use no control current during computation. After each attenuator is set, its output for a constant reference input is readily read out into a digital voltmeter or the digital computer, so that visual and/or automatic checking is still achieved. With the computer reference voltage turned off while attenuators are being set, relay contacts never interrupt current; they are operated well below their ratings and should last a long time. For any reasonable number of attenuators, relay switching is not more time consuming than electronic switching: in the University of Arizona's

Fig. 10. (a) LOCUST summer/integrator employing switched-amplifier mode control to obtain differential switching times below 20 ns (see also [17]). Separate low- and high-impedance summing networks are used for fast and slow computation, so that three logic-switched capacitors yield five different time-scale ranges with integrator input gains all the way from 10<sup>5</sup> s<sup>-1</sup>to 1 s<sup>-1</sup>. The fourth state of the two-relay combina-

tion produces a low-impedance summer without any need for bottle plugs. The circuit employs a 30 MHz,  $\pm$ 10-V amplifier similar to that of Fig. 8. (b) Simplified equivalent circuit of a switched-amplifier mode-control system in RESET or TRACK. (c) Switched FET-input amplifier proposed for the LOCUST system.

new digital-attenuator system, C. Pracht introduced the notion of making all relay driver bistable devices (transistor flip-flops) [18], so that the digital control system can go on to set the entire attenuator system while the first few relays are still settling. All attenuators are thus set in little more than the time required to set a single relay. The system is, in fact, so fast that it becomes possible to combine the relay-driving flip-flops into shift registers with *serial* input: this greatly simplifies the digital addressing of individual attenuators (one control line per attenuator, instead of 14 to 16).

Another question to be resolved is whether digital attenuators should employ binary or BCD weighting. The latter favors the use of manual keyboards, while binary weighting offers equipment savings and is more natural for most digital computers. The University of Arizona's system employs binary weighting and has replaced the coefficient-setting keyboard by a digit switch presetting a BCD counter; the latter counts the preset number of clock pulses into a binary counter/shift register, which can also accept parallel input from the digital-computer output bus and controls attenuator settings [18]. All manual settings are read back at once on the computer digital voltmeter.

The reader may have begun to note that the design of a practical digital-attenuator system is a rather sophisticated problem. Figure 11 illustrates some attenuator-network designs; many combinations are possible. Figure 11(a) shows a simple binary-weighted summing network employing SPDT (form C) relays to prevent capacitive feedthrough. Since the required 2<sup>14</sup> to 1 resistance range is too large, Fig. 11(b) implements at least the low-current branches with network transfer impedances; this circuit also permits the use of the somewhat cheaper SPST (form A or B) relays. Both Fig. 11(a) and 11(b) require summing-junction patching. The circuit of Fig. 11(c) permits patching to summing amplifier or integrator gain-of-10 or gain-of-1 inputs if the latter are loaded as shown. The simple ladder network of Fig. 11(d) can be similarly patched and permits especially simple construction since an entire set of similar metal-film resistors can be deposited in a single operation.

The choice of resistance values in Fig. 11(a) to (d) must satisfy the following requirements.

- 1) The load on the driving amplifier must not be larger than that of a comparable coefficient potentiometer.

- 2) The summing-junction-to-ground impedance of the attenuator has a lower limit determined by bandwidth specifications (i.e., the attenuator must not kill the operational amplifier feedback).

- 3) The attenuator must not attenuate high frequencies unduly; with suitable lead capacitors, digital attenuators, which can be located directly behind the computer patchbay, should create less phase shift than coefficient potentiometers.

Note that even with the best possible resistance values, the attenuator circuits of Fig. 11(c) and (d) cannot produce a

Fig. 11. Digital-attenuator design.

full gain of 1 or 10 when patched into the corresponding amplifier inputs. Maximum coefficients of the order of 0.5 and 5, respectively, seem practical.

To improve the network compromises, some digitalattenuator systems associate an amplifier with each digital attenuator. If the added cost of such an amplifier is accepted, it would seem desirable to provide it with summing inputs and to switch the feedback network rather than the input network, so that amplifier offset and noise are not amplified together with the signal [Fig. 11(e)].

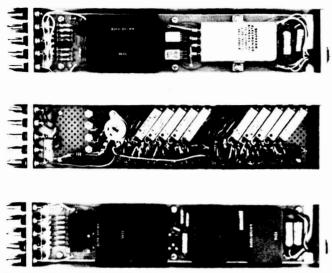

Fig. 12. These ASTRAC II  $\pm$  10-V computing elements plug directly into the rear of the shielded analog-computer patchbay (University of Arizona).

### **NEW PACKAGING TECHNIQUES**

To improve maintainability and convenient system expansion as well as computing bandwidth, analog computing elements ought to be plugged directly into the rear of a shielded analog-computer patchbay whenever it is at all possible. With reasonably designed transistor and integrated-circuit packages, such patchbay mounting of all analog computing elements is possible for  $\pm 100$ -V as well as for  $\pm 10$ -V computers, although the  $\pm 100$ -V machine will require careful management of forced-air cooling. In the  $\pm 10$ -V ASTRAC II computer shown in Fig. 4, the *only* analog computing elements not located directly in the patchbay are the coefficient-setting potentiometers, which must necessarily be situated on the front panel. Digital attenuators, however, can be plugged into the patchbay, so that the last remaining analog signal wiring is eliminated. If the top and/or bottom rows of patchbay terminations are used for attenuator connections, the attenuator assemblies can be located above or below the analog patchbay, so that they do not take up much of the valuable space behind the analog patchbay.

In the ASTRAC II and LOCUST computers, amplifiers, electronic switches, multipliers, etc., are mounted in individual shielded boxes plugged into the rear of the patchbay (Fig. 12). Figure 13 illustrates the construction of a small educational iterative differential analyzer at much lower cost. Here, simple printed-circuit cards having a shielded ground plane on one side replace the shielded amplifier boxes. Sets of such cards bearing integrated-circuit analog and digital computing elements are plugged directly into the rear of the analog and digital patchbays. Note that the amplifier overload lights and balance controls are mounted on the front of the amplifier cards, so as to be accessible from the front panel. There is no wiring to the cards at all; even power supply wiring is supplied by spare patchbay terminations.

Fig. 13. APE II amplifier card plugged into the patchbay (here removed from the computer), and an integrated-circuit logic card.

In any fast hybrid-computer system, grounding and shielding systems designed to minimize crosstalk and digital-noise effects become a first-class design problem, which must be considered from the start. Reference [22] summarizes the principal design considerations.

### DIGITAL CONTROL AND STATISTICAL MEASUREMENTS

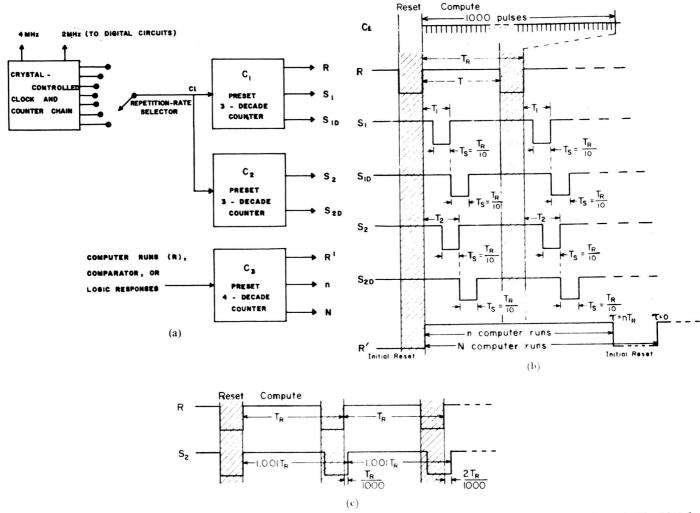

Integrated-circuit logic permits accurate timing and flexible control of iterative-analog-computer subroutines at very low cost. The ASTRAC II/LOCUST digital control system illustrated in Fig. 14 counts digital-clock pulses to produce not only analog-computer reset pulses but, also, precisely timed sampling pulse trains used to read out solution values and to compile random-process statistics. A crystal-controlled clock provides pulses at switch-selected rates of 1000, 500, 250, 100, 50, 25, and 10 kHz. A threedecade decimal counter  $(C_1)$  then produces a computerreset pulse (R pulse) after 1000 clock pulses, so that computer runs or data samples can be generated at rates of 1000, 500, 250, 100, 50, 25, and 10 Hz; an external clock can also be used. Counters  $C_1$  and  $C_2$  are preset to produce readout sampling pulses  $S_1$ ,  $S_{1D}$ ,  $S_2$ ,  $S_{2D}$  at digit-switch-selected multiples of 1/1000 computer run to permit flexible control of integrators, track-hold circuits, and track-hold pairs [1], [2], [19]. The logic-switched integrator capacitors are normally slaved to the repetition-rate switch, so that timescale changes are automatic.  $C_3$  is a subroutine counter counting computer runs, comparator responses, or other events.

Additional simple logic circuits produce automatic progressive delay of the sampling pulses  $S_1$ ,  $S_{1D}$  after a preset number of n computer runs. This "scan mode" permits sampling readout of repetitive computer solutions into slow recorders and digital computers and is also used for

Fig. 14. (a) ASTRAC II/LOCUST digital-control system. (b), (c) Timing scheme. The reset period (R=1) lasts for 100 clock pulses once every 1000 clock pulses for repetitive operation; manually controlled real-time operation is also possible. Sampling pulses  $S_1$ ,  $S_2$ ,  $S_{1D}$ ,  $S_{2D}$  occur at digit-switch-selected times after the start of each computer run. Sampling pulses can also be made to advance after a programmed

number of n=1 to 100 000 computer runs (shown in Fig. 14(c) for n=1). This permits automatic plotting of repetitive analog-computer solutions and correlation functions (see also [1], [2], and [19]). All these clock functions can be implemented with only two integrated-circuit cards bearing multiple preset counters.

Fig. 15. Analog computer, space-vehicle mockup, and digital computer are the essential components of a complex launch-system simulation, this composite photograph shows only a small portion of the comput-

ing equipment committed to a large simulation (Boeing Huntsville Simulation Center).

automatic plotting of correlation functions. Such statistical measurements, an especially fruitful application of hybrid computers, are discussed in detail in [2] and [21].

#### REFERENCES

- [1] G. A. Korn and T. M. Korn, Electronic Analog and Hybrid Computers. New York: McGraw-Hill, 1964.

- [2] G. A. Korn, Random-process Simulation and Measurements. New York: McGraw-Hill, 1966.

- [3] J. McLeod, Simulation: Dynamic Modelling of Things and Ideas. New York: McGraw-Hill, to be published, 1967.

- [4] W. J. Karplus, "Error analysis of hybrid-computer systems," Simulation, vol. 6, pp. 120-136, February 1966.

- [5] E. G. Gilbert, "Dynamic-error analysis of digital and combined analog-digital computer systems," Simulation, vol. 6, pp. 241-257, April 1966.

- [6] J. Vidal and W. J. Karplus, "Characterization and compensation of quantization errors in hybrid-computer systems," 1965 IEEE Internat'l Conv. Rec., pt. 3, pp. 236-241.

- [7] W. Giloi, A. Kley, and G. Meyer-Brötz, "Arbeiten über Analog-Rechentechnik, Telefunken Ztg., vol. 39, no. 1, 1966.

- [8] C. H. Single, U. S. Patent Application, 1965.

- [9] D. M. Tutelman, "A hybrid-computer technique for nonlinear-

- function generation," Simulation, vol. 6, pp. 308-322, May 1966.

[10] G. Meyer-Brötz and A. Kley, "The design of d-c amplifiers with high common-mode rejection." Electron. Engrg., February 1966.

- -, Zur Verbesserung der Bandbreite gegengekoppelter Verstärker durch Vorwartskoppelung, Arch. Elek. Übertragung., vol. 19, p. 546, 1965.

- [12] J. R. Miller et al., Communications Handbook, pt. I, Texas Instruments, Inc., Dallas, Tex., 1965.

- [13] T. B. Bergersen, "Field effect transistors in chopper and analog switching circuits," Motorola Semiconductor Products, Inc., Phoenix, Ariz., Application Note 220, 1965.

- [14] R. J. Widlar, "A monolithic operational amplifier," Fairchild Semiconductor, Mountain View, Calif., Appl. Bull. 105/2, 1965.

- [15] S. T. Robertson and J. J. Wisseman, "High-performance integrated operational amplifiers," Motorola Semiconductor Products, Inc., Phoenix, Ariz., Application Note 204, 1965.

- [16] G. A. Korn, "Performance of operational amplifiers with electronic mode switching," IEEE Trans. on Electronic Computers, vol. EC-12, pp. 310-312, June 1963.

- [17] H. R. Eckes, "A fast mode-control switch for iterative differential analyzers," IEEE Trans. on Electronic Computers, vol. EC-14, pp. 946-950, December 1965.

- [18] C. Pracht, M.S. thesis, Dept. of Elec. Engrg., University of Arizona, 1966, in preparation.

- [19] H. R. Eckes, and G. A. Korn, "Digital program control for iterative differential analyzers," Simulation, vol. 2, pp. 33-41, February 1964; see also [1].

- [20] G. A. Korn, "Hybrid-computer techniques for measuring statistics from quantized data," Simulation, vol. 4, pp. 229-239, April 1965; see also [2].

- ----, "Hybrid-computer Monte-Carlo techniques," Simulation, vol. 5, pp. 234-245, October 1965; see also [2].

- -, "Reduction of digital noise in hybrid analog-digital computers," Simulation, vol. 6, pp. 151-152, March 1966.

- M. Leeds, "Better isolation boosts IC performance," Electronic Design, vol. 14, pp. 17-19, September 1966.

#### Measurement of Phase Shift

In analog computer circuitry, the need for accurate phase measurements often arises. Inverting amplifiers contribute significant phase shifts at frequencies well below the 3-db frequency. These phase shifts cause large errors in a problem solution. Conventional phase measuring equipment does not operate at the higher frequencies where high-speed computers now operate. A simple procedure has been developed which utilizes a dual beam oscilloscope, or any indicating device with a differential input, to measure the phase shift between two sinusoids.

Consider the difference of two sinusoids whose phase shift is to be determined.

$$E(t) = a \sin wt - b \sin (wt + \theta).$$

(1)

By simple trigonometric manipulation, E(t) may be expressed as follows:

$$E(t) = [a^{2} + b^{2} - 2ab\cos\theta]^{1/2} [\sin(wt + \alpha)] (2)$$

where

$$\alpha = \tan^{-1} \frac{b \sin \theta}{a - b \cos \theta}$$

Assume that the amplitude of the second sinusoid is adjusted until the amplitude of the difference signal is a minimum. This condition occurs when

$$b = a \cos \theta, \tag{3}$$

as simple differentiation of the amplitude of E(t) will show. Under this minimum condition the difference signal is given by

$$E(t) = a \sin \theta \sin (wt + \alpha). \tag{4}$$

To determine the unknown phase difference  $\theta$  between a sin wt and  $b \sin (wt + \theta)$ , (e.g., amplifier input and output!), apply these voltages to the differential input of a Tektronix or similar oscilloscope, and vary the second input gain so as to minimize the difference signal seen on the screen. The ratio

of the difference amplitude to a equals  $\sin \theta$ . the sine of the desired phase angle.

It is still necessary to determine the quadrant in which  $\theta$  is to be found. Unless this is known a priori, it becomes necessary to either view the waveforms on a dualtrace scope or examine the zero crossings in a logical fashion to determine the qudarant. In addition, the sensitivity of the null is quite poor for angles close to multiples of 90°. For such angles, it would be necessary to compare the signal whose phase angle is to be determined with cos wt, rather than sin wt.

> HOWARD HANDLER Dept. of Elec. Engrg. University of Arizona Tuscon, Ariz.

# Acoustical simulation of a randomly fading communication channel

by A. M. MANDERS, University of Florida and J. V. WAIT, University of Arizona

JOHN V. WAIT received his BSEE from the University of Iowa in 1955, MSEE from the University of New Mexico in 1959, and PhD from the University of Arizona in 1963. He has worked in the general field of computing and signal processing systems for a number of years, and has published papers on hybrid-code differential analyzers, binary correlators, and hybrid computer circuit design. More recently he has held teaching positions at the University of California, Santa Barbara, and the University of Florida GENESYS facility at Cape Kennedy. In September, 1966 he returned to the high, dry lands of the Southwest, where he will again be associated with Granino Korn's Analog/Hybrid Computer Laboratory at the University of Arizona.

ARNFINN MOE MANDERS was born in Oslo, Norway in 1932. He came to the United States in 1955 after completing his studies at Schous Institute of Technology in Oslo. In 1957 he received the BS and MS degrees in Electrical Engineering from Michigan Technological University and in 1963 the PhD in Electrical Engineering from the Polytechnic Institute of Brooklyn.

Dr. Manders has been employed by Western Electric, IBM Research, and ITT. He has served as instructor at PBI and Assistant Professor at MIT. Since 1964 he has been employed by the University of Florida, GENESYS, where he is an Associate Professor of Electrical Engineering. He is currently conducting research in coding and design of signals for fading channels.

### **SUMMARY**

Experimental studies of fading RF communication channels are usually very difficult to perform under actual operating conditions. This paper describes a fading channel simulator which is easily constructed and flexible in operation. Using this simulator, modulation and coding techniques suitable for use in communication and ranging equipment can be tested and optimized for operation during periods of severe fading. The simulator uses ultrasonic acoustical waves transmitted through water to achieve favorable changes in the space and time scales; typical fading rates are from 2 to 30 fades per second.

The paper also describes simple hybrid statistical measurement equipment used in studying the probability distributions and correlation functions of the received signals.

### **INTRODUCTION**

Although today we normally think of *simulation* of systems primarily by means of analog, digital, or hybrid computing setups, we should not forget that some important phenomena are not easily modeled by a finite number of ordinary differential-difference equations which can then be "solved" by conventional computer methods.

An important case where a different approach is required is the simulation of a (randomly) fading radio-communication channel. Here we have a system with randomly varying, space- and time-dependent distributed parameters. Simulation of such channels is important to the study of many communication and ranging systems.

Although the establishment of a real-world channel using a conventional radio transmitter/receiver link is not too difficult, this approach has several obvious disadvantages:

- 1. Useful studies of many long-distance propagation phenomena require great distances between transmitter and receiver, with the attendant difficulties of logistics, off-line communication, etc.

- Even if the physical distance were not enough of a problem, one has the additional problem of accurately establishing precise, coherent frequency and time references at both ends of a long-distance channel.

- 3. Most real-world propagation paths do not possess a sufficient degree of stationarity in their statistical properties to permit precise, reproducible studies.

- 4. One cannot easily change the location of the transmitting and receiving stations, antennas, etc., and then return to some previous configuration for comparative purposes.

- 5. The rates-of-change of real-world fading phenomena are relatively slow, thus making statistical measurements tedious and time-consuming.

This paper describes a relatively inexpensive channel simulator that operates with much more convenient distance and time scales. It is useful both as an instructional device and as a reliable research tool. A simple statistical analyzer for making amplitude distribution and correlation measurements is also described.

The technique involves the use of ultrasonic (200 kHz) acoustic waves, in our case transmitted through a water tank. This method, although not new, is perhaps not as well known as it should be (see, e.g., reference 1). We have found the simulator to be a surprisingly stable, reliable mechanism for studying fading-channel phenomena. For example, the envelope and phase statistics of transmitted signals may be studied using a variety of propagation modes, including pure random (incoherent) scattering, pure specular, and mixtures of random and specular. We have used the simulator in the testing of new designs for phase-lock loops and other received-signal processing systems.

### GENERAL DESCRIPTION

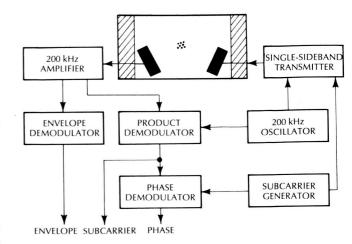

Figure 1 shows a sketch of a typical tank setup, including a block diagram of the associated electronics. The simulator consists of a  $5 \times 3 \times 2$ -foot plywood tank partially filled with tap water (figure 2). Two narrow-beam ultrasonic transducers (figure 3) are used as receiving and transmitting "antennas." Sound-absorbent material is placed along the walls of the tanks as needed, to prevent undesired reflections and standing waves.

The nominal carrier frequency is 200 kHz, corresponding to an acoustic wavelength of about 7 mm. This short wave length allows farfield operation in a relatively small tank, and permits strong reflections from small objects.

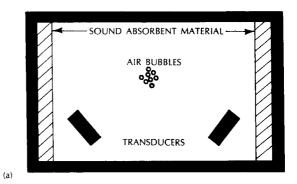

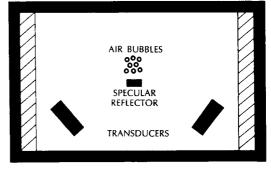

Two interesting conditions that have been studied extensively are the case where all the received signal is due to reflection from random scatterers, and the case where a steady (specular) component is added to the randomly-scattered signal. The random scattering is produced by reflecting the signal off a column of air bubbles; the specular component is produced by placing a solid reflecting object near the bubble column.

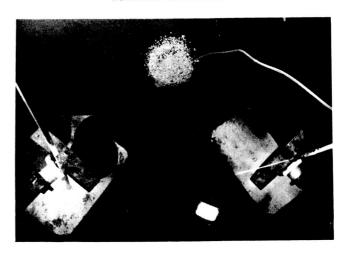

### The water tank (figure 2)

This unit was constructed from <sup>3</sup>/<sub>4</sub>-inch top-grade marine plywood; the corners and bottom are reinforced with 2-inch angle iron. The seams are caulked with Dow SIL-ASTIC clear sealer, and the inside walls are coated with an epoxy-based marine paint. An occasional addition of swimming-pool chlorinating compound keeps the water free of algae, etc., so that water changes are infrequent. A garden-hose siphon to a floor drain provides an adequate method for water removal.

### Acoustic transducers (figure 3)

Identical units are used for transmitting and receiving. They are ordinary acoustic transducers used in marine depth finders (APELCO Model 1443A00), mounted on movable stands. They exhibit an impedance of 200 ohms and a lateral 3-dB beamwidth of  $\pm 6.5$  degrees.

### Turbulence generators, reflectors, absorbers

Rapidly varying (10-30 cps) random scattering can be obtained by bouncing the acoustic waves off a column of air bubbles that is generated by a group of three or four ordinary aquarium aerators. Several aerators may be supplied from a single small reciprocating air pump (the entire bubble system, with control valves and plastic tubing, was purchased at a local dime store). Aluminum plates and strips on movable stands serve as specular reflectors. Two-inch-thick batts of rubberized horse hair serve as effective (and surprisingly durable) signal absorbing pads.

A more slowly changing turbulence may be created by using an electric heating element or motor-driven vanes. (The suggestion of using a small school of piranha-fish was discarded, due to the obvious hazards to operating personnel.)

Figure 1 – Typical tank setup, including SSB transmitter and receiver

Figure 2 - Photograph of water tank

Figure 3 - Photograph of acoustic transducer

### CHANNEL CHARACTERISTICS: TYPICAL SETUPS

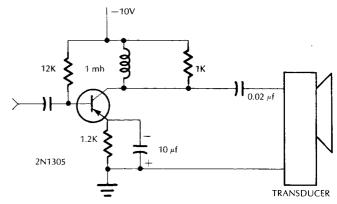

The transmitting transducer must be driven by a signal of the order of 3-4 V peak-to-peak; a suitable driving circuit is shown in figure 4. Channel measurements indicate that the attenuation (expressed in terms of the ratio between the transmitting and receiving transducer voltage levels) may be estimated by the following formula

Attenuation in dB = (10 + 0.35D), where *D* is in inches Path lengths of over 40 inches have been successfully used.

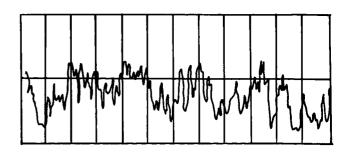

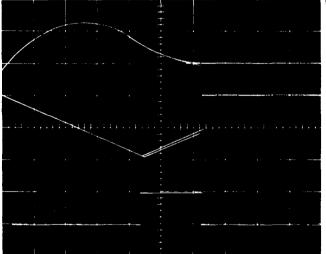

Figure 5a shows a typical setup to obtain an almost completely random scatter mode of transmission, with little or no specular component. A sample of the received signal is shown in figure 6; it typically exhibits 5-10 deep fades per second and 20-30 minor fades per second.

Figure 5b shows the method for obtaining a strong specular component. A solid object (e.g., a metal strip) is placed in *front* of the air bubbles. This permits independent adjustment of the specular and random reflection components over a reasonably wide range. It is essential that the bubble generators, transducers, specular reflectors and absorbing pads be carefully positioned to insure elimination of secondary reflection components. It has been found that the extraneous signal content in the simulated channel can be made negligible (—60 dB or less).<sup>6</sup>

### A TYPICAL COMMUNICATION SYSTEM MODEL (figure 1)

The communication system currently used in connection with the multipath simulator is shown in figure 1. The transmitter has a crystal-controlled carrier frequency of 200 kHz. This carrier is single-sideband (SSB) modulated with a 4 kHz subcarrier. The resulting SSB signal is fed to the transmitting transducer, whence it is radiated in the water. The receiving transducer picks up the signal reflected from the air bubbles and other reflecting objects placed in intersection of the two transducer patterns. This signal is amplified and demodulated in the receiver. The receiver performs both envelope and product demodulation. The output from the envelope demodulator provides information about the fading of the envelope of the received signal. The output from the product demodulator is used to extract information about the phase of the fading signal. Reference signals for the product demodulator and for the subcarrier phase comparison are obtained directly from the transmitter by means of cables. This results in one great additional advantage of using the multipath simulator rather than "the real thing." Since the reference signals used at the receiver can be obtained directly from the transmitter, they do not have to be generated locally at the receiver. This eliminates a great source of uncertainty as to whether observed effects are due to the channel behavior or due to time-, frequency-, and phase-reference errors at the receiver.

Figure 4 - Transducer driving circuit

Figure 5 – Two types of multipath channels: (a) pure random scattering, (b) random scattering plus strong specular

Figure 6 – Amplitude record of the fading carrier envelope, pure random scattering

### Statistical analyzer

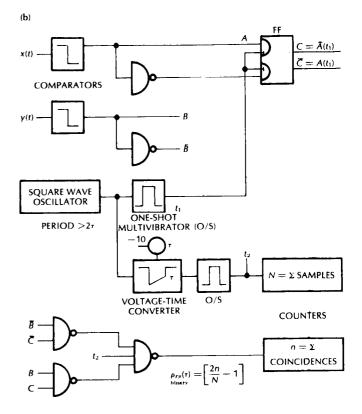

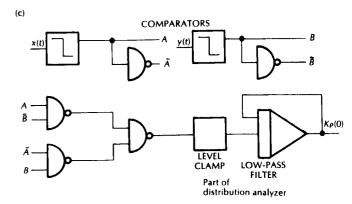

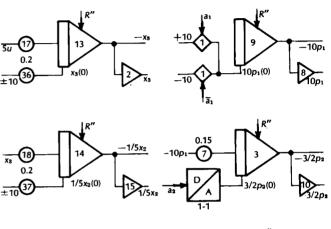

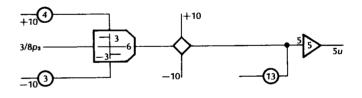

Relatively simple statistical analyzing equipment may be used to study many properties of a typical communication model. Figure 7 shows block diagrams of the systems used for measuring amplitude distributions and binary (two-level) correlation functions. The design of these systems was based upon the following characteristics of the received signals:

- a. Over a period of several hours, the statistical properties of the received signals are essentially *stationary*, thus permitting time-averaged measurements.

- b. Many of the signals for which auto- and cross-correlation measurements were desired are approximately Gaussian with zero mean; this permits the results of simple binary (two-level) correlation measurements to be used to reconstruct the true analog correlation. Two-level correlation techniques are also self-normalizing, i.e., they yield the normalized correlation coefficient of the ac component of a Gaussian signal directly, so that precise monitoring of signal levels is not required during a test.

- c. Signal bandwidths of the order of 10 to 30 Hz permit the use of either continuous or sampled-data averaging techniques where desired.

Amplitude distribution analyzer

(see also reference 3, section 5-12)

The system shown in figure 7a performs a continuous averaging of the output of a dual-slicer circuit to derive an estimate of the amplitude probability density function f(X), where

$$f(X) = \text{Prob } (X - \delta X < x \le X + \delta X)$$

by measuring  $(1/\triangle X)$  · Prob  $[X - (\triangle X/2) < X < X + (\triangle X/2)]$ ;  $\triangle X$  small compared to the variance of X.

The rate-of-change of the ramp  $X_o$  and the output filter time constant, T=10 C (T in seconds, C in  $\mu f$ ), must be chosen for the particular process to be measured. In particular we must choose K and C such that (for "low-pass" processes):

$$K = dX_0/dt < < \triangle X/T \text{ v/sec}$$

and

$$T = 10C_{\rm mfd} >> N_o \simeq 1/f_o$$

where  $\triangle X$  is the total width of the slicer window = 0.2 v

T = 10C is the output filter time constant

$f_n =$  approximate bandwidth of the process x(t) in Hz.

(i.e.,  $N_o$ , the zero-crossing rate of x is of the order of  $1/f_o$ )

In our case,  $f_0$  is of the order of 10 Hz. Successful distribution plots were made with  $C=2 \mu f$ ,  $T=20 \, \mathrm{sec}$ . The ramp rate was kept small compared to  $\Delta X/T=0.05$ ; typically  $K=0.005 \, \mathrm{v/sec}$ . Faster sweep rates cause excessive distortion of the plot due to filter time lag. Wider output filter bandwidth causes the "noise" in the plot to be excessive, due to inadequate averaging time. The input process should be scaled so that its rms value is about 3 volts, and its mean is close enough to zero so that the range of

Figure 7 – Block diagrams of statistical measuring systems:

(a) amplitude distribution analyzer, (b) sampled-data binary correlator, (c) binary cross-power estimator

the process is within  $\pm 10\,\mathrm{v}$  range of the sweep voltage. For Gaussian- and Rayleigh-distributed signals this is straightforward. A complete plot typically requires 200/0.005 = 4000 seconds (1 hr, 15 min)! This demonstrates the need for good stationarity of the channel parameters and the advantages of being able to simulate a channel on as fast a time scale as possible. This type of distribution measurement proved suitable for our case, but would be cumbersome, if the fading rates were appreciably slower.

Binary correlator (figure 7b; see also reference 5 and reference 3, section 6-5)

The binary (or polarity-coincidence) correlator is suitable for making estimate of the auto- and cross-correlation functions of zero-mean Gaussian stationary random processes. It was useful in our case for studying the phase components of the receiver signal, but would not be valid for performing correlation analysis of envelope signals (which may nevertheless be studied with a low-frequency spectrum analyzer).

The binary correlator yields an estimate of the two-level or one-bit correlation function

$$\rho_{xy}(\tau) = E\left[\operatorname{sgn} x(t_1) \operatorname{sgn} y(t_2)\right] = \frac{2}{N} (\sum n_i - 1); \quad \tau = t_2 - t_1$$

binary

where  $n_i = 1$  if  $x(t_1)$  and  $y(t_2)$  have the same polarity on the *i*th sample.

It may be shown that, if x(t) and y(t) are zero-mean Gaussian processes

$$\rho_{xy}\left(\tau\right) = \sin\frac{\pi}{2} \rho_{xy}\left(\tau\right) = \frac{E\left\{\left[x(t) - x_{dc}\right] \left[y(t+\tau) - y_{dc}\right]\right\}}{\left(X_{\text{rms}} Y_{\text{rms}}\right)}$$

Again, considerable time is required for measuring a correlation function, since at least 2000 samples must be taken for each value of  $\tau$ . In our case,  $\tau$  ranged from 5 milliseconds to 0.1 second. If the actual unnormalized correlation function is desired, one must also make careful measurements of the mean and rms values of X(t) and Y(t) during the measurement period; then one can estimate the correlation function by

$$R_{xy}(\tau) = X_{dc}Y_{dc} + X_{rms}Y_{rms}\rho_{xy}(\tau)$$

analog

Cross-power measurement (figure 7c)

In many cases, we are interested in only  $\rho_{xy}(0)$ , and an analog averaging method may be used in place of the sampled-data method used in the correlator above. Here the output is related to

$$\rho_{xy} (\tau = 0) = \frac{2}{\pi} \arcsin \rho(0)$$

$$\rho(0) = \frac{E\{[x(t) - X_{dc}][y(t) - Y_{dc}]\}}{(X_{rms} Y_{rms})}$$

Although these simple hybrid statistical analysis systems used in the initial studies proved satisfactory for studying many basic channel properties, faster, more accurate, and more sophisticated measurements could be made with a

small general-purpose digital computer and analog/digital converter interface. Faster-than-real-time processing of channel output signals could be accomplished by using a precision instrumentation tape recorder with servo speed control to record the signals and a reference carrier for playback at a faster tape speed.

### **CONCLUSIONS**

A multipath simulator has been described that is readily constructed and flexible in operation. The multipath characteristics of the channel can be varied over a wide range of conditions, allowing simulation of nearly all desired types of multipath channels.

Since the transmitter and receiver are located close together, reference and synchronization signals required at the receiver can, if desired, be obtained by cables directly from the transmitter. Difficulties with the local reference signals can thus be avoided, allowing a more exact investigation of the effects of multipath conditions on the transmitted signal and on the operation of the receiver.

#### **ACKNOWLEDGMENTS**

The authors wish to express their appreciation to Dean T. L. Martin and Dr. J. L. Hummer, GENESYS Director, for providing the facilities used in this project. Thanks must also go to Mr. W. R. Nyren for his invaluable assistance in the equipment design and construction. Mssrs. E. J. Claire, L. Lerner, J. G. Stoides, and K. W. Dunipace also assisted in performing the experimental work.

### **REFERENCES**

- 1 H E GULLSTAD W K ROBERTS A radio propagation simulator using radio-frequency acoustic waves in a liquid

- FCC Laboratory Division Project No 32801 May 18 1965

- 2 A M MANDERS A multipath simulator for use in evaluation of spacecraft ranging and communication systems Proceedings Third Space Congress Cocoa Beach Florida March 1966

- 3 G A KORN

Random-process simulation and measurement

McGraw-Hill New York 1966

- 4 M SCHWARTZ

Information transmission modulation and noise

McGraw-Hill New York 1959

- 5 C L BECKER J V WAIT Two-level correlation on an analog computer Transactions IRE/PGEC Vol EC-10 No 4 pp 752-758 Dec 1961 (Also Aug 1962)

- 6 E J CLAIRE L LERNER D M NEWLANDS J G STOIDES A system analysis of the GENESYS multipath simulator utilizing a receiver with a unique phase-locked loop design Unpublished Laboratory Report University of Florida GENESYS April 18 1966

- 7 G A KORN T M KORN Electronic analog and hybrid computers McGraw-Hill New York 1964

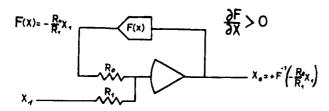

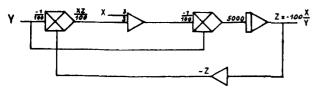

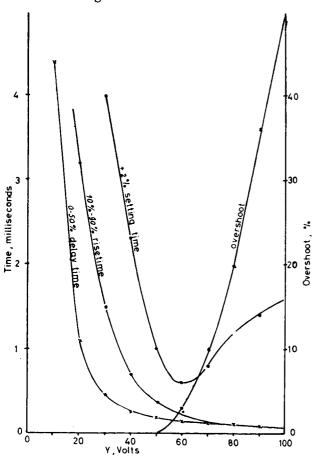

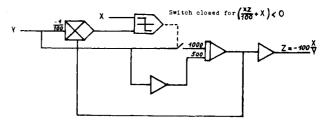

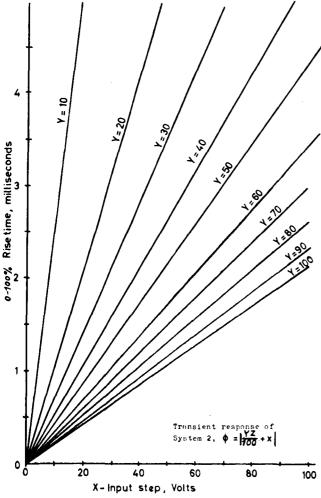

### Solution of optimal control problems on a high-speed

RICHARD MAYBACH grew up in the paper-mill town of Camas, Washington on the lower Columbia River. From there he went south to Corvallis, Oregon and a BS degree in electrical engineering from Oregon State in 1959. Then, ignorant of the effects of thermal shock on physical bodies, he moved to Tucson, Arizona to enroll in graduate school. It was during this time that he was introduced to Dr. G. A. Korn, who said, "Glad to know you; here is your project." Nothing was seen of Dick for several days while he attempted to find out: (1) What is a servo multiplier? (2) How is the thing on this chassis (purportedly a servo multiplier) supposed to work? (3) Why doesn't it? Presumably he found out, for he received his MS degree in 1961.