https://ntrs.nasa.gov/search.jsp?R=19680006536 2020-03-12T11:58:51+00:00Z

# RESEARCH AND DEVELOPMENT STUDY ON MULTIMODE SYSTEM APPLICATIONS IN THE AREA OF TIME OF FLIGHT AND COINCIDENCE MEASUREMENTS

## RESEARCH AND DEVELOPMENT STUDY

## ON MULTIMODE SYSTEM APPLICATIONS IN THE AREA OF TIME

## OF FLIGHT AND COINCIDENCE MEASUREMENTS

## William J. O'Neill and Gerald W. Gaughran

## October 1967

Distribution of this report is provided in the interest of information exchanged and should not be construed as endorsement by NASA of the material presented. Responsibility for the contents resides in the organization that prepared it.

## Prepared under Contract No. NAS 12–516 by Nuclear Data Incorporated Palatine, Illinois

Electronic Research Center

National Aeronautics and Space Administration

Dr. John Oberholtzer Technical Monitor NAS 12–516 Electronics Research Center Cambridge, Massachusetts 02139

Requests for copies of this report should be referred to:

# TABLE OF CONTENTS

|                                       | rage |

|---------------------------------------|------|

| Summary-Multimode Systems             | · 1  |

| Introduction-Multimode Systems        | 2    |

| General Information-Multimode Systems | 4    |

| Summary-Time of Flight System         | 7    |

| Introduction-Time of Flight System    | . 9  |

| The Time of Flight Module             | 12   |

| Main Oscillator                       | 12   |

| Double Derandomizer                   | 12   |

| Pre-scaler                            | 14   |

| Main Scaler                           | 15   |

| Update Scaler                         | 16   |

| Delay Scaler                          | 17   |

| Operation of Time of Flight Unit      | 18   |

| The Event Pulse                       | 19   |

| Stop                                  | 19   |

| Single Particle Analysis              | 20   |

| Pulse Width Analysis                  | 20   |

| Packaging Flexibility                 | 20   |

| Experimental Flexibility              | 21   |

| Conclusion                            | 21   |

| Summary Coincidence System            | 22   |

## TABLE OF CONTENTS

|                                                       | rage |

|-------------------------------------------------------|------|

| Introduction Coincidence System                       | 25   |

| Packaging Considerations                              |      |

| High Voltage Power Supply                             |      |

| Preamplifier                                          |      |

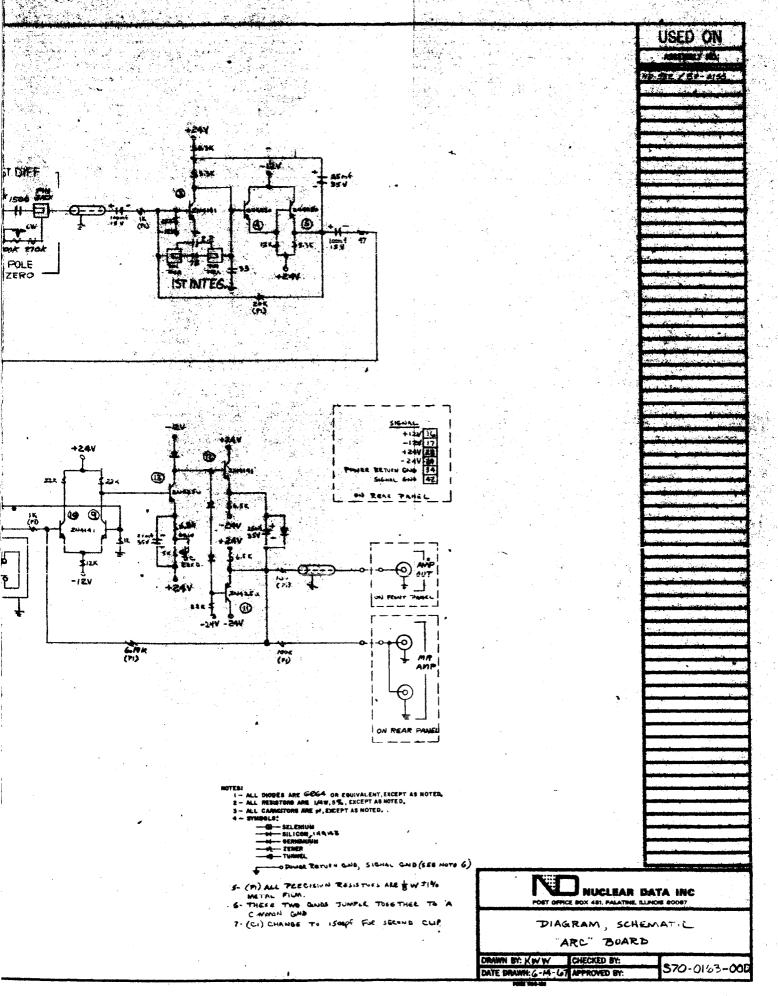

| Amplifier                                             | 33   |

| Time Pick/Off Delay Module                            | 38   |

| Coincidence Gate                                      |      |

| Conclusion                                            |      |

| Appendix I Time of Flight Instruction Manual          |      |

| Appendix II Amplifier Instruction Manual              | 49   |

| Appendix III References                               | 50   |

| Appendix IV Data Sheets                               | 51   |

| Appendix V Multimode Systems Technical Specifications | 52   |

# TABLE OF ILLUSTRATIONS (FIGURES)

| Number | Illustration                 | Page        |

|--------|------------------------------|-------------|

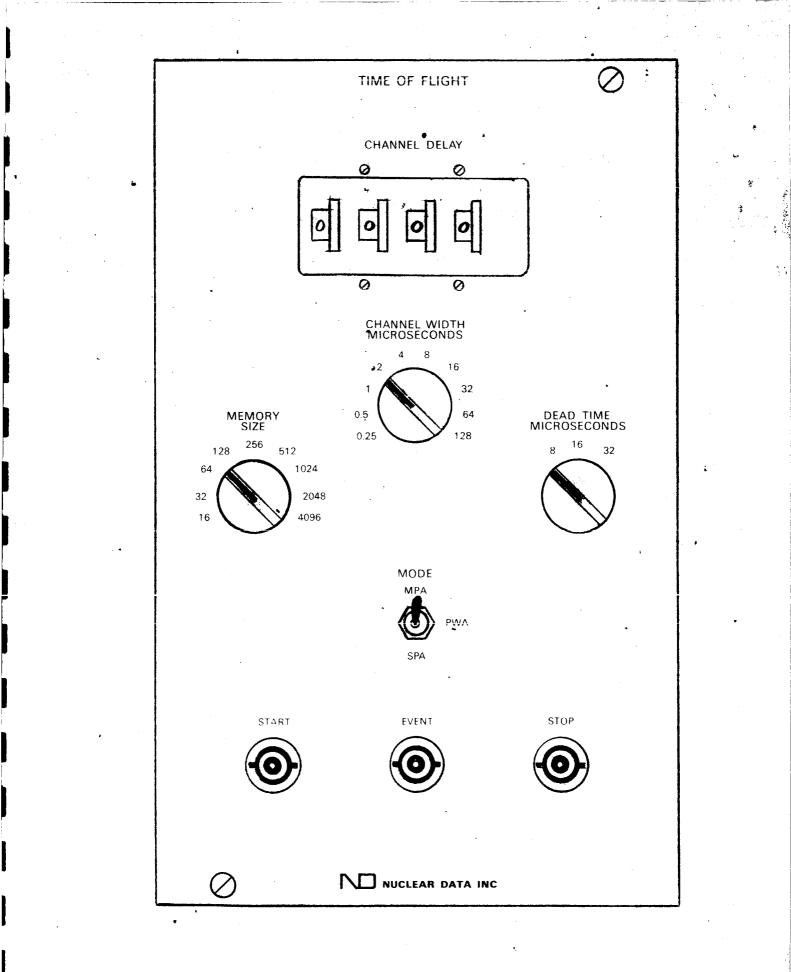

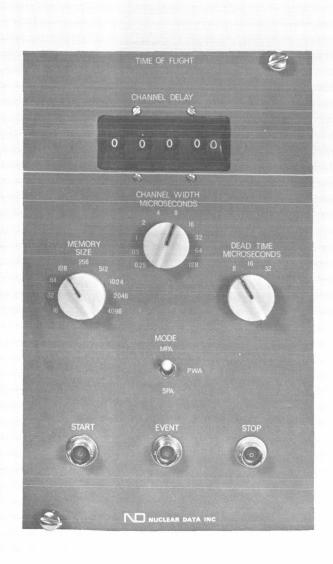

| 1      | Time of Flight               | 12a _       |

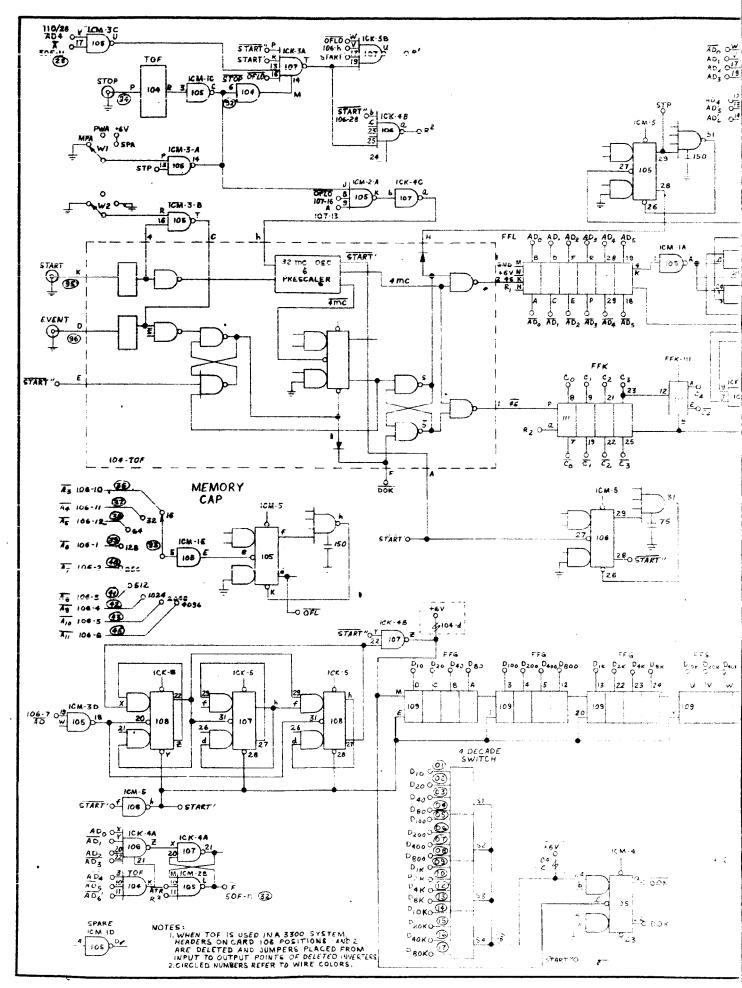

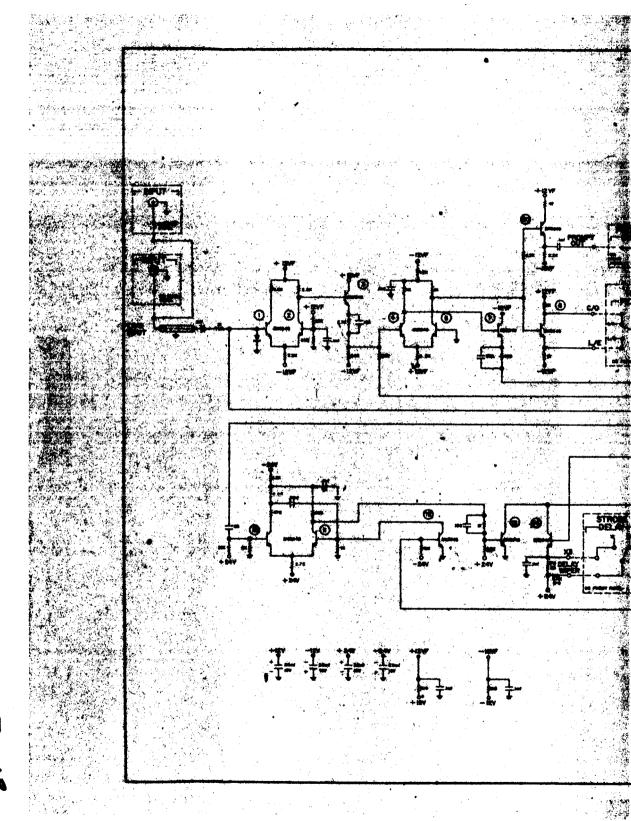

| 2      | Time of Flight Diagram       | 12b         |

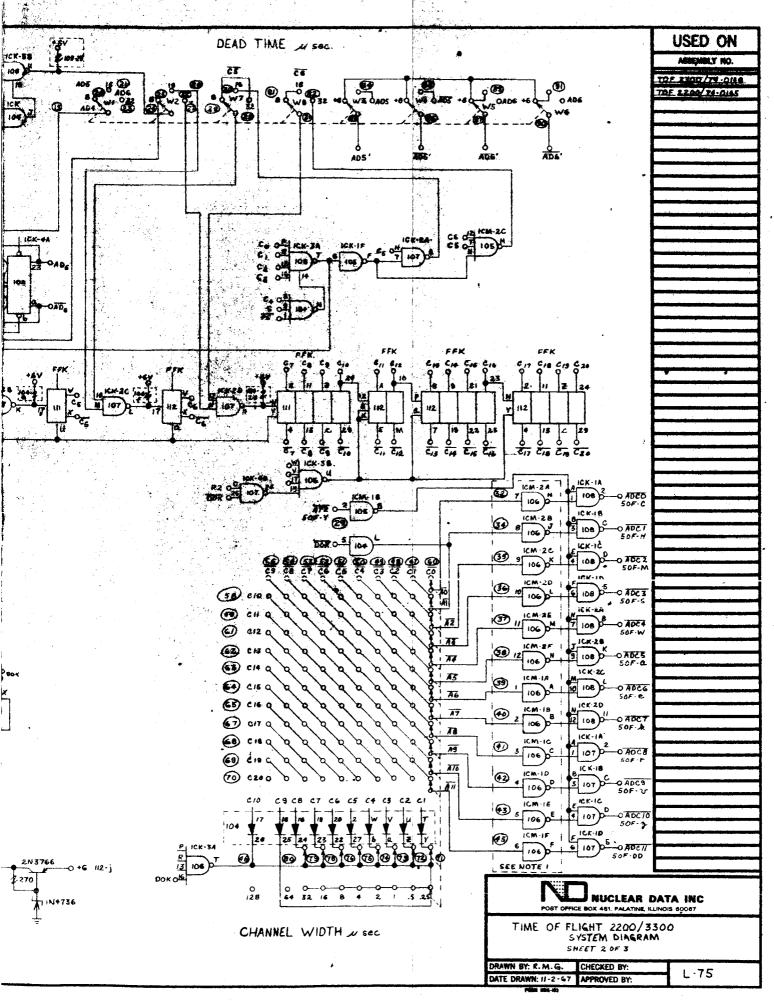

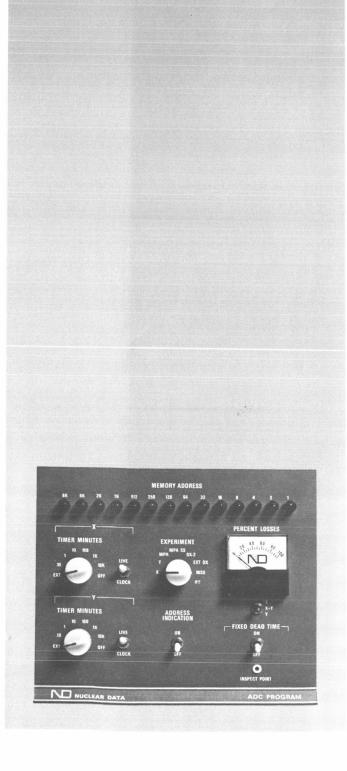

| 3      | Modular Instrument Bin       | 26a         |

| 4      | Bias Power Supply            | 27a         |

| 5      | (HVS) Board                  | 28a         |

| 6      | High Resolution Preamplifier | 30a         |

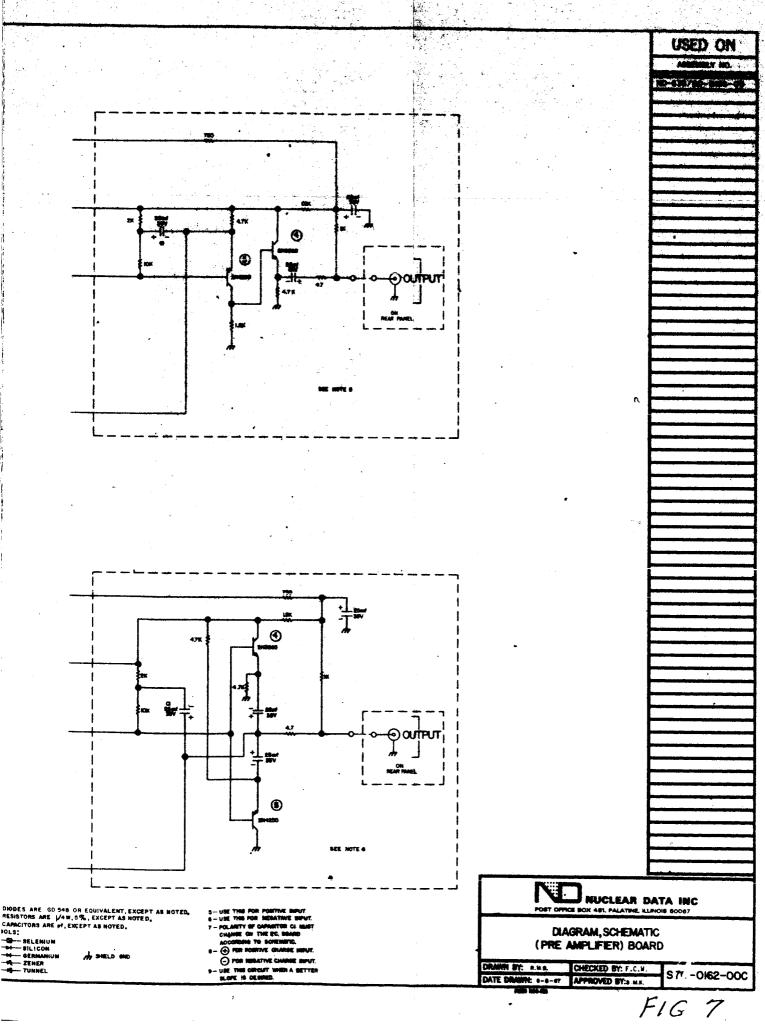

| 7      | Preamplifier Board           | 31a         |

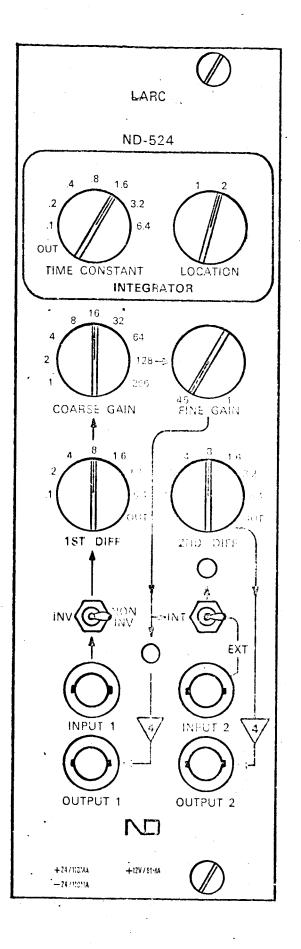

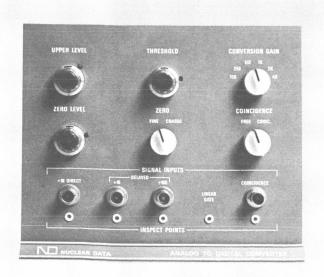

| 8      | Larc Linear Amplifier        | 33a         |

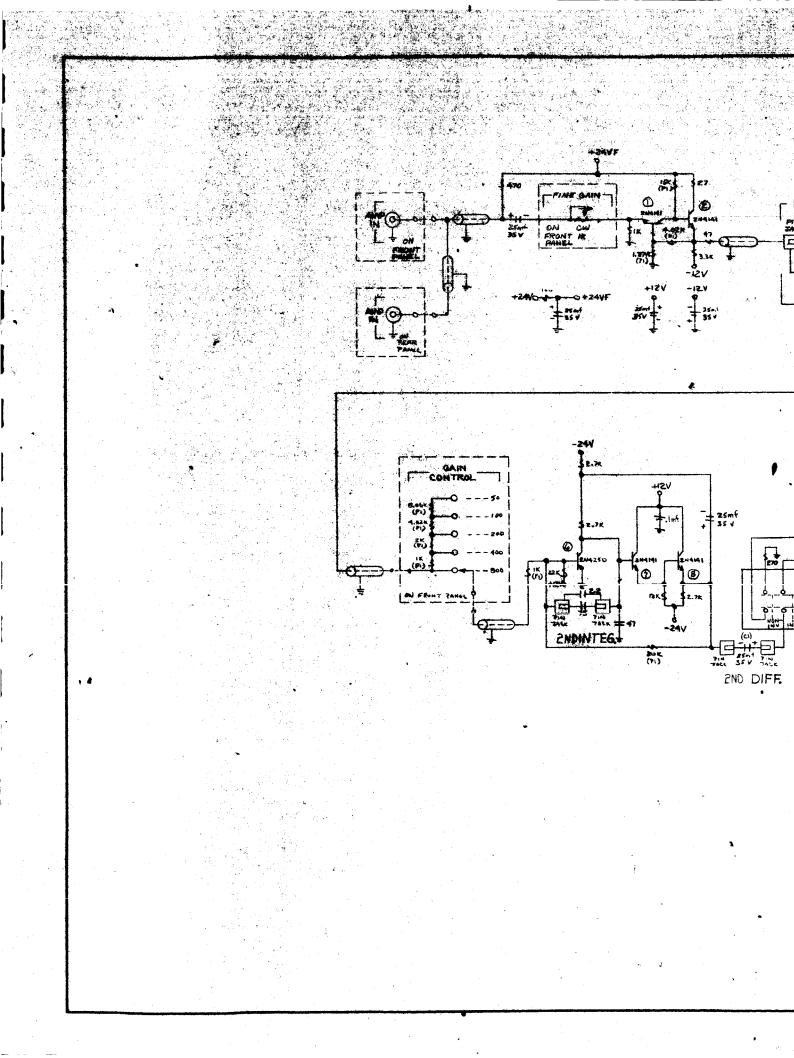

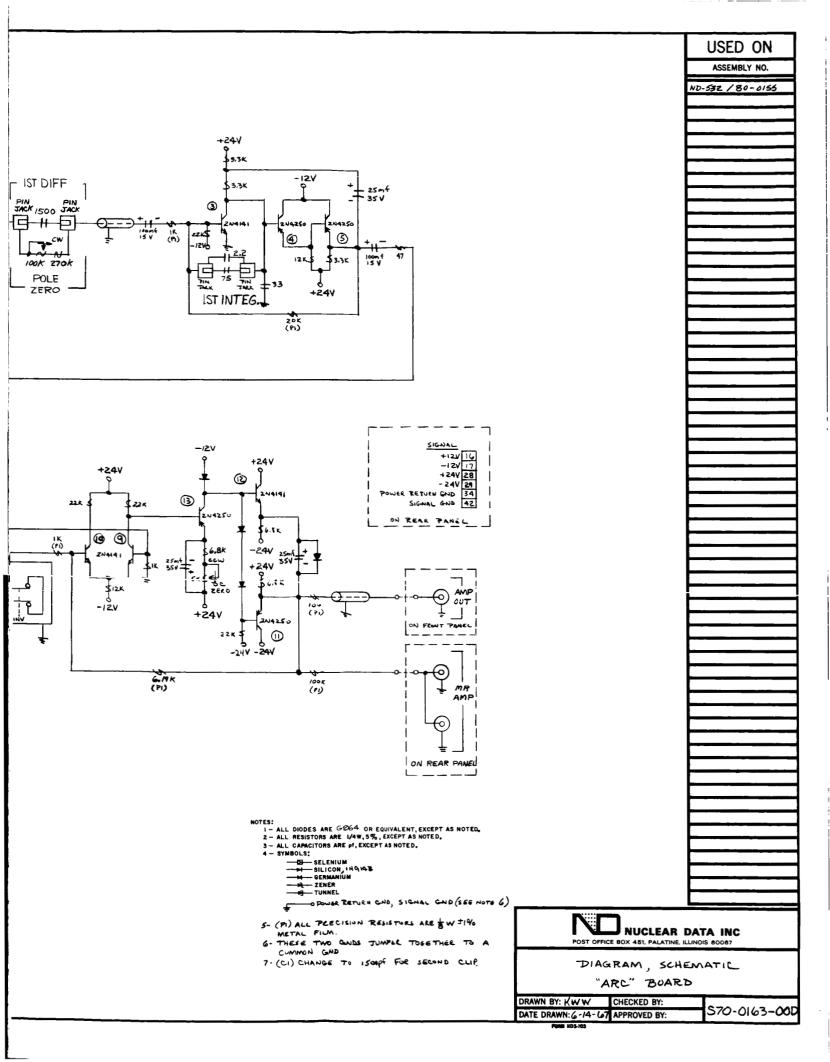

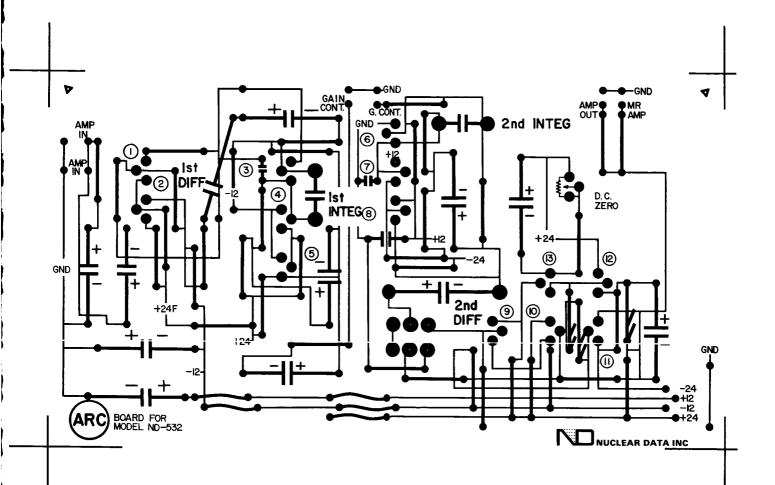

| 9      | "Arc" Board                  | 34a         |

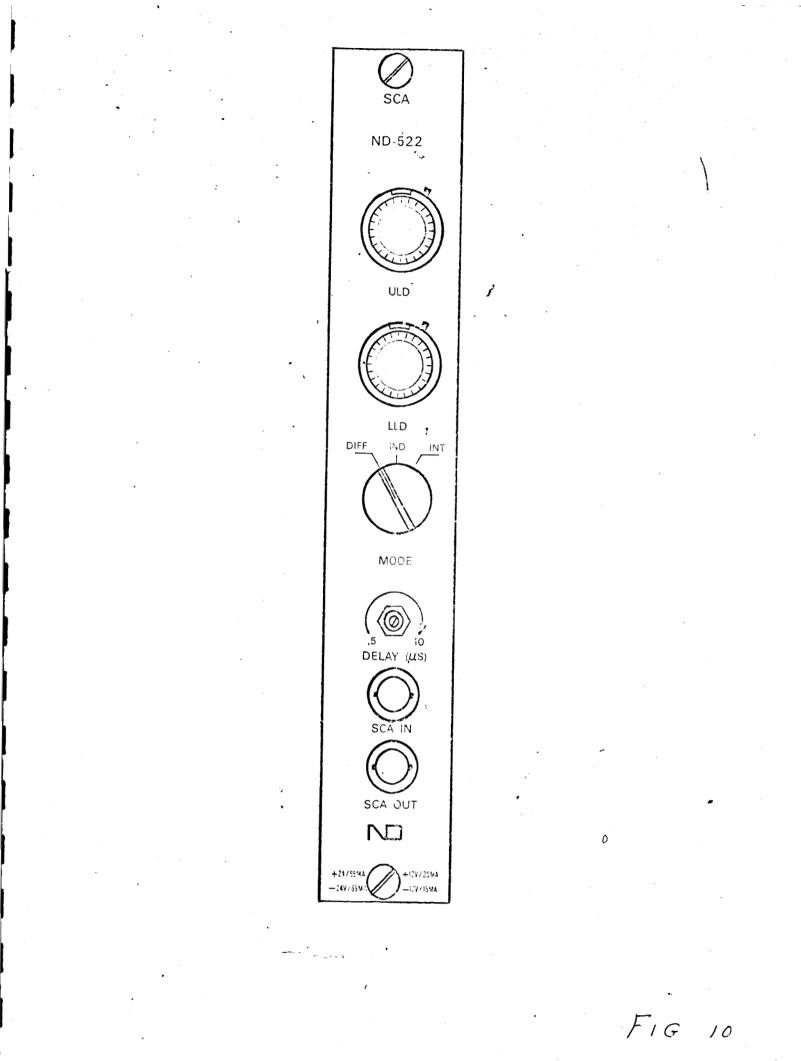

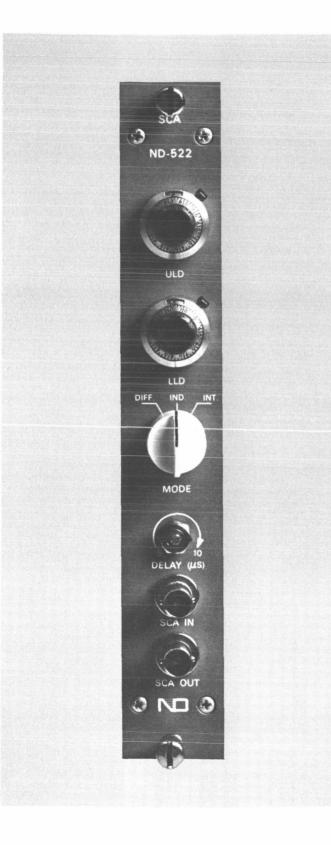

| 10     | SCA Module                   | 37a         |

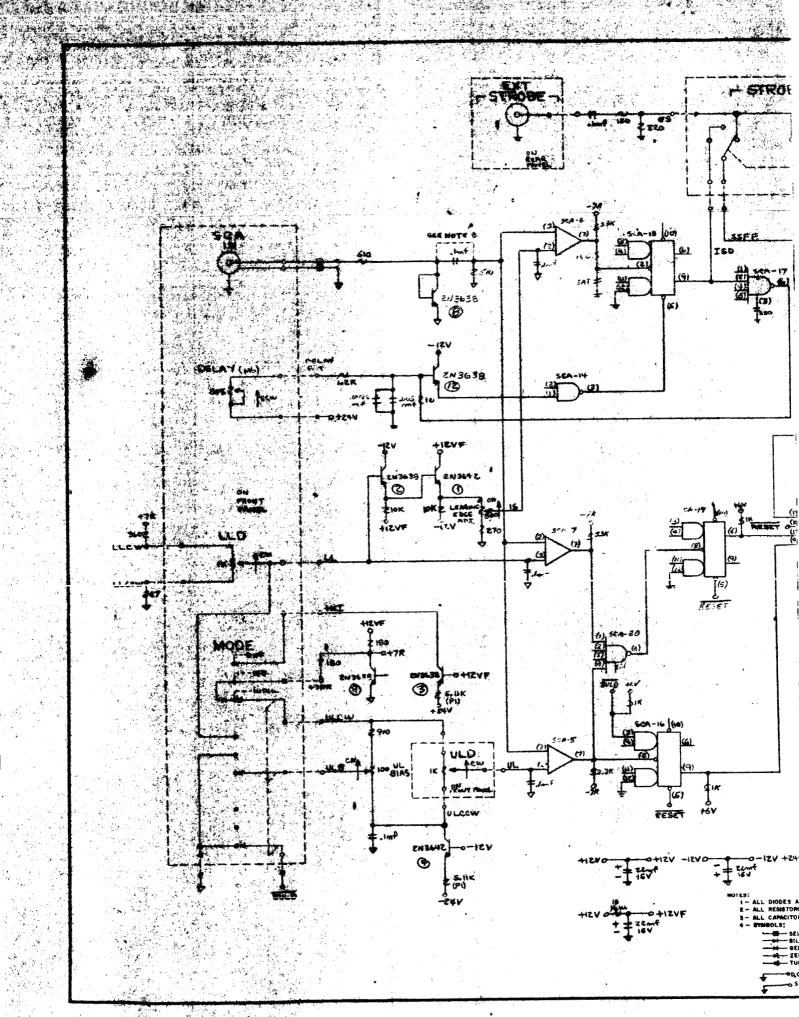

| 11     | SCA Board                    | 37ь         |

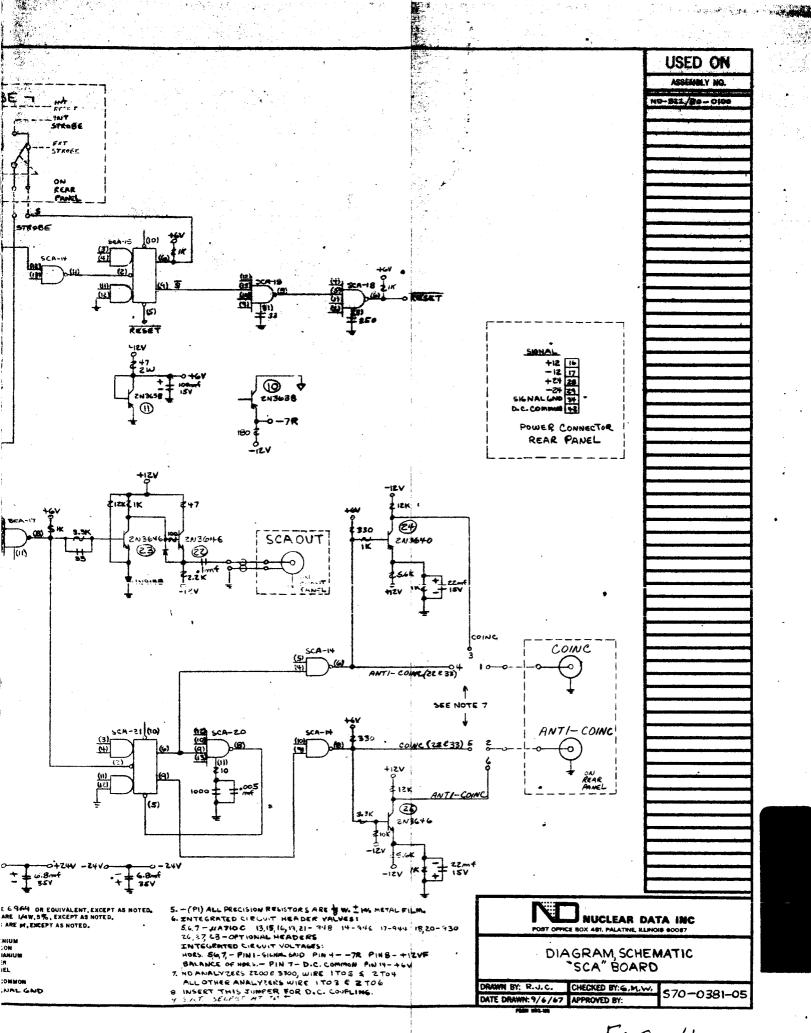

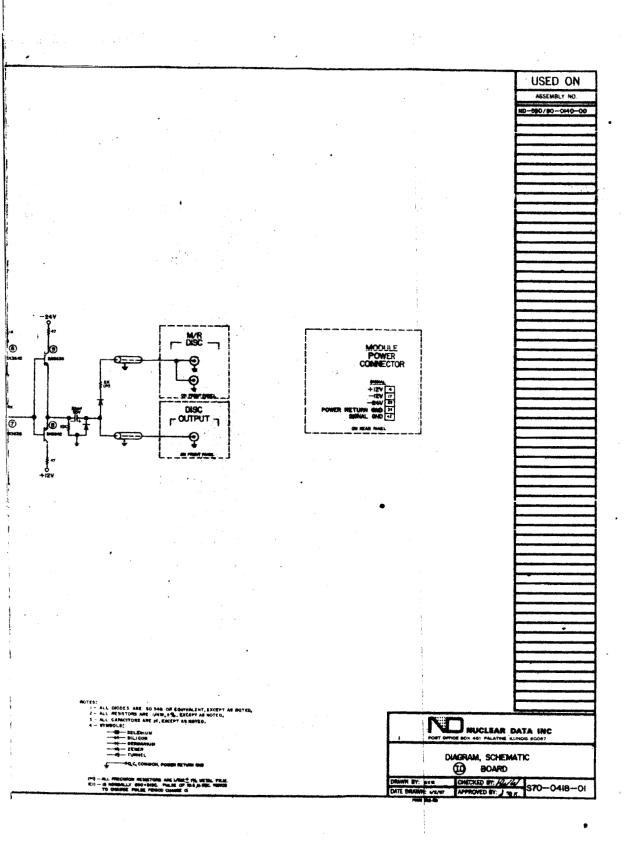

| 12     | (ID) Board                   | 37c         |

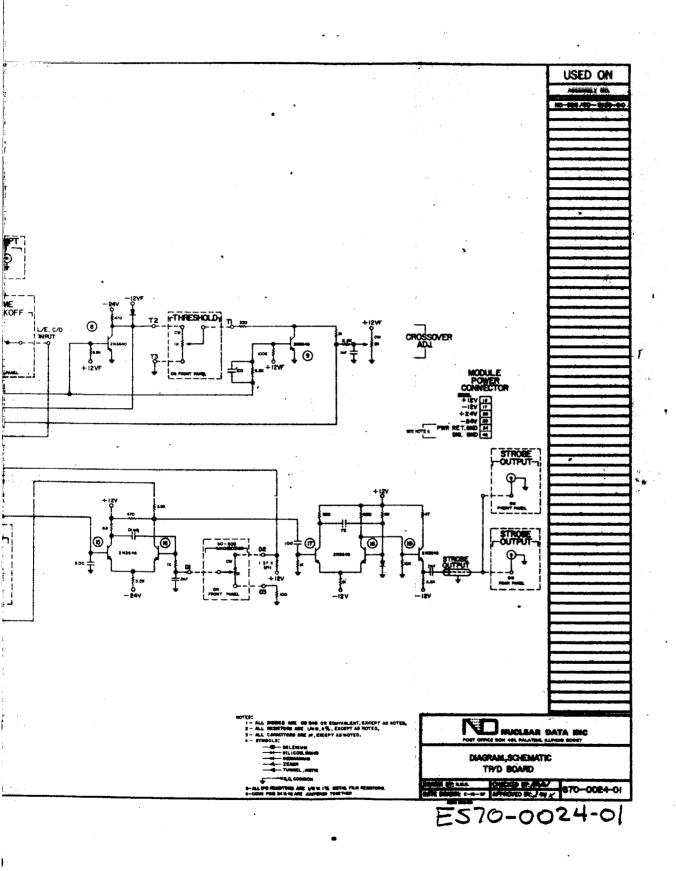

| 13     | TP/D Board                   | <b>3</b> 8a |

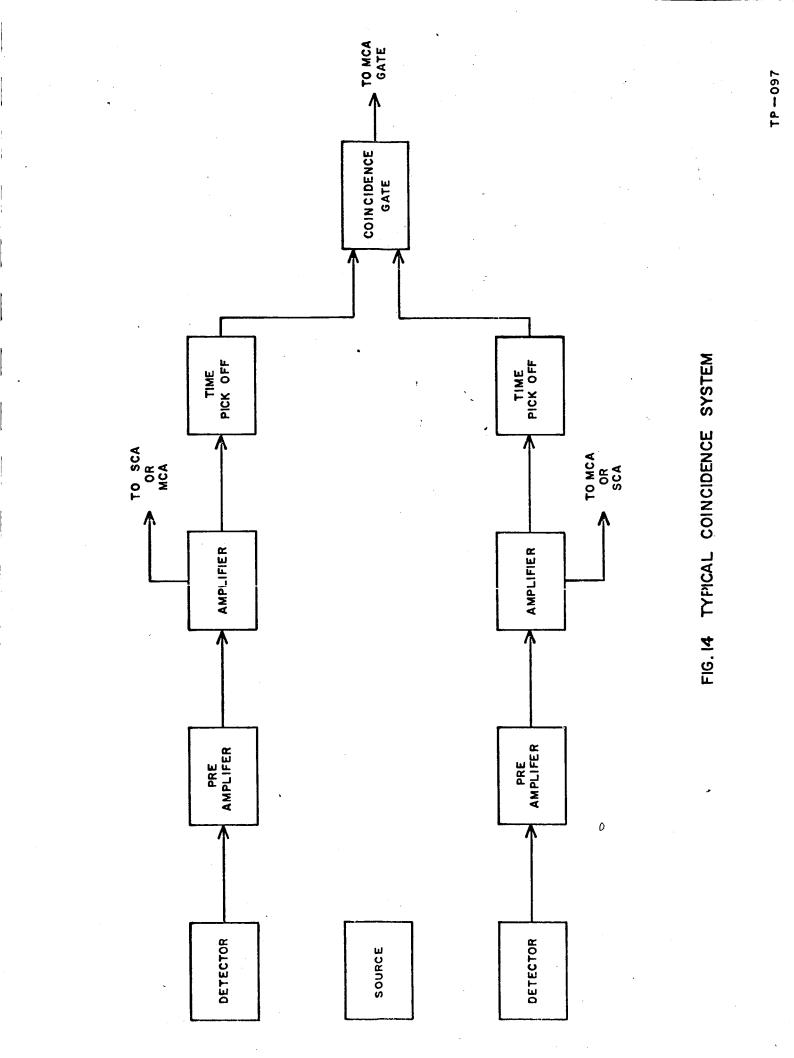

| 14     | Typical Coincidence System   | 38b         |

## SUMMARY - Multimode System

Recently the need for a multimode digital storage device has become more and more pronounced. The utilization of such a system offers significant economic benefits to user groups by eliminating duplication of expensive components not compatible with all applications. Such a system has been designed, fabricated and installed at NASA Electronics Research Center, Cambridge, Massachusetts by Nuclear Data, Inc. It incorporates a 4096 channel memory with 20 binary bit storage (1,048,575 counts), a 4 µsec memory cycle time, 16 megahertz analog to digital converters and built in arithmetic capability. Display and data manipulation have been incorporated which provide the latest in visual interpretation techniques. The analog to digital converters contain inputs for uni-polar and bi-polar pulses, coincidence and anti-coincidence inputs, D.C. or slowly varying A.C. signal analysis.

These various input capabilities and data manipulation features were incorporated to facilitate the many input requirements as outlined later in this report.

It is most strongly felt that this portion of the system greatly exceeded the expectations and requirements outlined in the contract.

## INTRODUCTION - Multimode Systems

A multimode system was designed and delivered to fulfill the first section of this contract. The design parameters for this device were established through the joint efforts of Nuclear Data, Inc. and the National Aeronautics and Space Administration. The primary objective at the conceptual level was to develop a digital storage device capable of performing both routine and complex experiments, utilizing the same instrument in various experimental endeavors. It was concluded that many areas of research, although unrelated, required the use of similar counting and analysis systems and this served as the foundation on which the design was based.

The research areas for which investigations were planned were listed and catagorized as a function of instrument utilization. The results of this listing were somewhat startling. It was determined that as many as ten areas of research can be served by one single instrument system resulting in a considerable economy in terms of specialized instrumentation. The utilization of this single instrument system covers the following research areas:

> 1. Digital time of flight measurements in the area of slow neutron energies.

- 2. Coincidence experiments, both of single and multi-dimensional nature.

- 3. Compatibility with all nuclear radiation detectors and related detection systems.

- 4. Measuring mass and velocity of simulated micrometeoroids.

- 5. Measurements of time dependent de-excitation spectra of nuclear radiation from a standard source.

- 6. Mossbauer effect analysis.

- 7. Measurement of time dependent de-excita tion spectra of electromagnetic radiation from excited atoms.

- 8. Measurement of spatial and time dependent distribution of temperature along one axis of a shock tube.

- 9. Pulse width analysis measurement of the total time a pulse exists above a pre-de-termined reference level.

- Pulse height vs time of flight measuring both parameters of a time dependent relationship and storing this information in a two dimensional matrix.

Many more applications for such a system exist and are currently

0

in use; however, a discussion of those applications is beyond the scope of

this report.

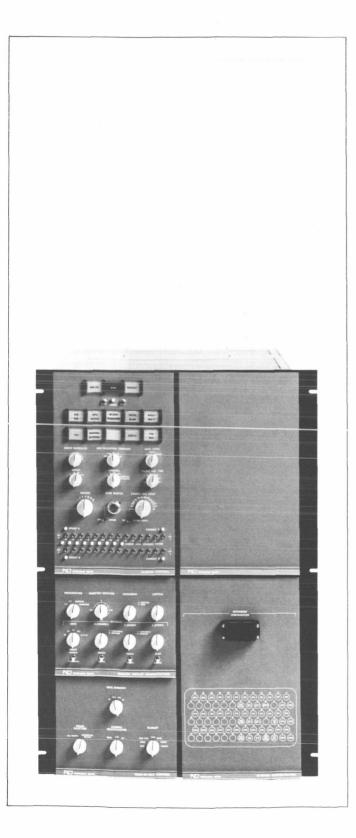

## GENERAL INFORMATION - Multimode System

The series 3300 analyzer system manufactured by Nuclear Data has the following advantages:

It is modular (including circuit cards and mechanical assembly) and, therefore, can be tailored to the needs of researchers in the nuclear, medical, and aerospace fields. Identical modules are used for a wide range of special-purpose data acquisition and processing systems. By substituting different modules, such variables as data storage capacity and types of information input/output are easily changed. Modular construction makes possible a system that expands from the two analog to digital converters provided to eight; from 4096 memory channels to 16,384 channels; from single or dual parameter real time totalizing to a delayed time totalizing buffer tape system handling eight dependent coincident parameters, one, two, or three dependent parameters out of any total up to eight, eight independent parameters, four dual independent parameters of different count rates, or any other data source with comparable logic levels operating on the "ready-resume" data transmission concept.

Detailed specifications covering the entire series 3300 systems are included in Appendix V.

Note should be made of the following specifications which typify the engineering advancements made with this system and which contribute to its flexibility and usefulness.

Memory Cycle Time: 4 µsec. This very fast memory storage time provides NASA with data acquisition rates unavailable in any other system. Due to reduced dead time, time related experiments can be performed faster and with greater precision.

2. <u>Analysis Capability:</u> Multiple input independent, and multiple input dependent experiments are routine. Up to four independent, nonrelated inputs or two dependent inputs can be processed simultaneously. These inputs can originate in widely different detectors without varying the system operation.

3. <u>Readout and Visual Presentation</u>: Controls are provided to present memory data in three different display configurations: slice, contour, isometric. Additional display controls affect display angle, digital region selection, analog region selection, area intensification, area blanking and expanded selectable area viewing (scanmaster). Digital memory readout is also under these controls.

ť.

4. <u>Patch programming:</u> Any desired experimental configuration canbe programed through the use of front panel patch plugs.

5. <u>Readout device selection</u>: Digital readout devices, analog recorders, or magnetic tape systems can be switch selected by front panel controls. All circuitry for controlling digital and analog recorders is included.

Because of this multimode system, the applications anticipated by NASA represent a small number of the total experiments for which the series 3300 is currently being used. Assembling a list of all applications is beyond the scope of this report but a representative list is included in the "INTRODUCTION – Multimode Systems".

## SUMMARY - Time of Flight Systems

Digital time of flight measurements have been accomplished for several years to determine the mass and velocity of both nuclear particles and microparticles. In general, these devices suffered from drawbacks which did not allow simple incorporation into a flexible multi mode system. In addition to these "interface" considerations, a basic design approach was desired which would lend itself to digitizing speeds beyond the slow neutron region. This was considered to be essential to future experimental demands to easily facilitate high speed endeavors without fear of obsolescence and troublesome interfaces.

Under this contract, a time of flight unit was designed to more than fill these basic demands. This design can be used in areas where high digitizing rates are required without starting anew. The basic design incorporates a time range (channel width) which is switch selectable in ten (10) steps (Figure 1). The range is variable from 0.25 µsec/channel to 128 µsec/ channel. The time uncertainty (jitter) <sup>(3)</sup> per channel is greatly reduced through the use of a prescaler. The function of the prescaler is to divide the basic oscillator frequency of 32 megahertz to 4 megahertz by a binary factor.

7

(3) See Footnote Page 12

Time jitter is further reduced through the use of a double derandomizing circuit which is incorporated within the prescaler. In essence the double derandomizer serves to insure starting and stopping the scaling of the digital pulse train in synchronization with the pulse train itself. In other words, this device eliminates the uncertainty concerning the arrival of a start pulse with respect to the pulse train.

Time resolution has been improved by the incorporation of a new technique which eliminates propagation time errors in the delay circuitry. This technique represents an important improvement over conventional devices due to the automatic correction for propagation time in the delay circuit. The primary effect created by propagation time is that the address register will not settle down sufficiently upon completion of delay to allow acceptance of the next pulse. The next pulse is, of course, the first channel of data and must not be subjected to uncertainty.

Another meaningful contributor to the flexibility of this instrument is its A.E.C. modular construction. This insures compatability with other instrument manufacturers both mechanically and electronically.

We feel our goals under this section of the contract were 100% achieved and we also made a significant advance in the state-of-the-art.

## **INTRODUCTION** - Time of Flight

Digital measurements of the flight time for nuclear particles have been performed for many years. The measurement involves the gating of a crystal-controlled oscillator by the departure of a particle from a source (chopper) and the interaction of the particle within a detector. The total travel time along the flight path is determined by counting the number of oscillator pulses occuring during the interval between the departure and interaction of the particle. Various time of flight devices have been commercially available for some time. Some of these devices suffered from drawbacks ranging from minor to severe. A partial list of these limitations is shown:

1. Channel width selection: 7 or 8 selections.

2. <u>Total delay available</u>: Limited to a maximum of 8192 channels; usually less. In some units, the delay was a multiple of the time range selected.

3. Number of channels available: 1024 maximum.

4. Time jitter: Typically large, due to small pre-scaling factor.

5. Pulse width analysis: Not available.

6. <u>Fixed delay</u>: Inherent in all systems as a result of the use of the main scaler for delay scaling. The propagation time of the final pulse through the scaler introduced a fixed delay which must be normalized in data.

7. Interface & Packaging: Limited to use with one memory.

8. Channel Profile: Usually poor.

9. <u>Price:</u> \$5,000.00 to \$65,000.00. The more expensive units normally require special memories.

A research and development effort was undertaken to eliminate as many of the above problems as possible. Another guideline was to utilize the basic design over a wide range of oscillator frequencies. This goal was established in an effort to fulfill all time of flight application by changing logic speed, thereby, utilizing the same package for all applications.

As preliminary studies progressed, it became apparent that a tradeoff of features was required due to interaction within the logic. In selecting the capabilities of the system, we had to limit the choices to those features which did not conflict with the performance of others. For example, by utilizing the main scaler as a delay scaler, the delay range of the instrument increased which increased the fixed delay, thereby, solving one problem while aggravating another. Several similar approaches were tried with similar results.

Various approaches were attempted to solve secondary prablems; as

in transfer techniques. One such technique is referred to as a "reading on the fly". In operation, the sequence is as follows: Upon the arrival of a detector pulse, the number in the register is transferred to the memory in a time shorter than the period of the oscillator. The register is not interrupted and continues to scale until the next event occurs. Events will not be transferred if storage of the previous event is still under way. The shadow time <sup>(2)</sup> becomes equal to the memory cycle time of the storage device. Unfortunately, this technique does not próve to be practical from either an economic or engineering viewpoint. The transfer time becomes a function of the oscillator frequency which imposes extremely strict requirements on the transfer process. To date, high speed transfers have proved to be unreliable at speeds beyond 250 nsec. As a result of these findings, this approach was abandoned. Our goal for a prototype to operate at all oscillator frequencies, greatly influenced this decision.

The final design is based on the update scaler technique which eliminates the problems associated with "on the fly" transfers but does introduce a "shadow". This technique is described below:

(2) Shadow: This term refers to the time in which the time of flight module is unable to process data. A shadow occurs after every event and consists of transfer and storage time.

#### THE TIME OF FLIGHT MODULE

The time of flight module consists of six main sections and a unique system for tying these together. The oscillator, update scaler, and the main register are found in all digital time of flight units. The unique aspects of the design are found in the delay scaler and the double derandomizer, while the final component, the pre-scaler may or may not be found in other units.

## THE MAIN OSCILLATOR

The main oscillator is a 32 megahertz crystal controlled oscillator. (see Figure 2). The oscillator is free running and is gated randomly by the start pulse. 32 megahertz was chosen to provide significant pre-scaling thereby, directing pulses to the main scaler which suffered from a minimum of jitter<sup>(3)</sup>. The jitter associated with this device is 1/64 µsec maximum when operating in the 1/4 µsec per channel mode. The frequency of the pulse train as it enters the main scaler is 4 megahertz.

#### DOUBLE DERANDOMIZER

The double derandomizer (Figure 2) is used to improve the absolute time profile of the channel. Channel profile is required to be as good as possible in any digitizing system to insure the accuracy of the measurement.

(3) Time jitter is normally defined as being the total time uncertainty in any given measurement. Time jitter is composed of start time errors and stop time errors directly and internal delays indirectly. To reduce time jitter, a high speed oscillator should be used which is gated into a prescaler. The prescaler divides this frequency to the desired range. When a start pulse occurs, the most time uncertainty involved, is one high frequency pulse which is some fraction of the prescaler output or considerably less than one channel.

FIG 1

F162-1

FIG 2-2

In essence, channel profile is a determination of the absolute width of any channel within the system. Each channel should be exactly 250 nsec wide (if that scale is chosen) and the center line from channel to channel must also be 250 nsec. Time jitter will influence channel profile. Double derandomization reduces the time jitter associated with the arrival of a start and stop signal with respect to the main oscillator period. Two things contribute to time jitter: (a) the error associated with the determination of a start signal ( $t_0$ ) with respect to the main oscillator and (b) the error associated with the determination of an event signal (detected event) with respect to the main oscillator. Assuming the main oscillator is stable (in this case, approximate stability is 1 part in  $10^6$ ), these two factors are the only influence on time jitter, ignoring secondary effects such as fixed delay, etc. In any case, these two factors can only influence the first event detected when measurements are made without delay time.

The term double derandomization is derived from two primary considerations: (1) The start signal (t<sub>o</sub>) and the oscillator pulse train must enable the electronic circuits through an "AND" Gate (2). The arrival of these two pulses trigger a pair of flip-flops which then insure absolute synchronization with the pulse train. In other words, the start signal can only satisfy the

"AND" gate requirement when the oscillator is undergoing a positive excursion. This insures a maximum delay in enabling, of one half cycle or 1/64 of a microsecond. After enabling has occured, the next oscillator pulse is used to direct the pulse train into the pre-scaler. Double derandomization is derived from the use of two consecutive pulses to trigger the gate to the pre-scaler. This insures absolute time synchronization in all measurements due to accurate time reference with respect to  $t_0$ . The arrival of an event signal can occur at any time during one complete cycle, hence, a synchronized start is essential to eliminate errors at both ends of the measurement. Care has been taken to gate at the 32 MHz input to the pre-scaler to avoid large uncertaintities in the start time. As the prescaler serves to reduce the frequency to 4 MHz, the greatest error which can occur is 1/32 µsec or 1/8 channel.

#### PRE-SCALER

The function of the pre-scaler is to reduce the frequency from 32 MHz to 4 MHz to increase accuracy in measurements and to reduce time jitter. The pre-scaler is a 3 bit binary scaler, constructed of M.E.C.L.<sup>(4)</sup>

(4) Motorola emitter coupled logic.

blocks, and is located in the circuit between the double derandomizer, the main oscillator, and the main scaler. With the incorporation of the divide by 8 pre-scaler, this module possesses the least time jitter of all units available.

### MAIN SCALER

The main scaler contains 21 binary bits (see Figure 2) which provides the widest selectable time range of all units available. A front panel switch allows selection of channel width ranging from 0.25 µsec to 128 µsec in binary increments. Two other front panel switches affect the operation of this scaler. The first switch, channel width, determines the number of bits to be used for dividing the 4 MHz pulse train by the proper factor to equal the channel width selected. The second switch determines the total number of bits used as a function of total time range and memory size.

Considering the 21 bits as lying in a row from left to right, the bits are arranged in increasing weight from MS2<sup>0</sup> to MS2<sup>20</sup>. If a 4096 channel memory is used, the maximum number of bits is 12. The channel width

switch selects which bit is the one to be wired to the least significant bit of the memory, while the range or memory size switch selects which scaler bit represents the most significant bit of the memory. As the channel width is increased, the least significant bit selected moves from left to right while as the memory size is decreased, the most significant bit selected moves from right to left. The total number of bits selected can be extended to 13 or 14 if an 8192 or 16,384 channel memory is used.

## THE UPDATE OR DEAD TIME SCALER

The dead time scaler is a 7 bit binary scaler covering a selectable time range which is equal to 8, 16, or 32 channel widths. The purpose of this scaler is to correct the main scaler for the time it is busy in transferring event information to the memory, and therefore, not able to keep track of time. At the exact instant an event signal occurs, the 4 MHz pulse train is gated off to the main scaler and gated on to the update scaler. When the dead time selected has elapsed, the main scaler is updated equal to the content of the update scaler and the 4 MHz pulse train is gated back to the main scaler. The dead time provided insures compatibility with slower memory systems such as computer systems and older equipment.

## DELAY SCALER

The purpose of the delay scaler is to provide selectable delays before the pulse train is directed to the main scaler. The delay scaler is located between the pre-scaler and the main scaler. The function of this scaler is to provide a delay in counting in the main scaler until some pre-set time has elapsed. An example might be in an experiment where 1/4 µsec time widths were selected but the range of interest was longer than the total time available with the memory used. A delay of up to 99,990 channels can be selected to compensate for the memory size and until this delay time has elapsed, counting will not occur in the main scaler.

The delay scaler is a separate component, which is unique to time-of-flight units, and is a decimal device. Front panel switches allow selection of delays from 0 to 99,990 channels in increments of 10 channels. A unique operating technique eliminates all propagation delays which normally affect the main scaler. It does so in the following manner: Propagation delays are a result of the time required for a scaler to "carry" an event throughout the entire scaler and produce an output indicating this process has been completed. The delay time is a function of the length of the scaler and the circuitry used. Our circuit utilizes an innovation incorporating a "set-ten"principle. In this manner when a start puise is

generated, the delay scaler is set to 10. This, of course, means that the delay scaler will stop 10 channels sooner than it should. The propagation time to inform the circuitry that delay -10 has occured may be in the order of 2 or 3 channels. At this point, the signal may be present 7 or 8 channels before the real delay has occured. The output of the delay scaler is gated by the first decade of its scaler, however, resulting in the delay of the signal until the first decade carries a 10. This method completely eliminates propagation times and further improves the accuracy of the measurement.

## OPERATION OF THE TIME OF FLIGHT UNIT

The preceding discussion of the major components in this module demonstrates how many of the problems in previous units have been eliminated. The only serious drawback not eliminated is the shadow time. The shadow results from the dead time associated with event storage. It can be referred to as a pulse pair resolution. During the period of dead time, the timeof-flight unit cannot detect the arrival of another event resulting in a blind period or shadow.

When a start pulse arrives, it simultaneously resets the main scaler and up-date scaler, sets 10 in the delay scaler, and sets the double derandomizer gate. The next clock pulse directs the synchronized pulse train to the main scaler or the delay scaler if a delay has been set. If a delay of zero is set, the delay scaler is switched out and the pulse train is directed to the main scaler. The number of pulses required to equal one channel is determined by the position of the front panel switch. If the scaler reaches the memory size selected before an event occurs, the scaler automatically resets and waits for the next start signal. If an event were to occur before the delay time expired or before the pre-scaling was completed, this event would be ignored.

#### THE EVENT PULSE .

When an event pulse arrives after scaling has begun in the main scaler, the pulse train is interrupted while storage occurs in the memory. The update scaler monitors time for its pre-selected duration after which the main scaler is updated and counting is resumed. This process is continued until the register overflows which causes an automatic reset and awaits the arrival of the next start pulse.

#### STOP

A stop signal aborts the run, clears all scalers, inhibits transfer and awaits the next signal.

#### SINGLE PARTICLE ANALYSIS

In this mode, the time-of-flight module stops after an event signal is transferred to the memory and awaits another start signal.

#### PULSE WIDTH ANALYSIS

This mode of operation is used to determine the length of time a pulse exists above a predetermined value. The signal to be measured is connected to the start input. The leading edge of the pulse, or its rise above baseline, acts as a start signal. The scaler continues to count until the trailing edge or its decay to baseline occurs, and counting is stopped. The leading edge acts as a start pulse while the trailing edge acts as the event pulse. Reset is automatic upon the arrival of the next pulse.

#### PACKAGING FLEXIBILITY

Construction of this unit is almost exclusively of integrated circuits. The components are mounted on plug-in cards and packaged in N IM -NASA standard modules. Voltage levels were standardized in agreement with the AEC Committee Report TID-20893.

## EXPERIMENTAL FLEXIBILITY

This module is designed to plug-in the data acquisition section of the multimode system. It can be used independently or in conjunction with other multimode modules. Experiments of single parameter or N-parameter can be performed without circuit modification. It can be used with other time of flight modules or an analog to digital converter in multi-parameter experiments. Two time of flight units can be used simultaneously with external logic, to eliminate shadow areas or to increase the range. Several units can be used to provide several windows.

## CONCLUSION

The results of research and development work on the time of flight unit exceeded our most optimistic goals. The module can satisfy experimentalists in several fields. It can be built for \$2500.00.

Future work in the time of flight area would be limited to a design of a unit using faster logic to obtain increased resolution.

A prototype time of flight unit will be provided NASA for extended evaluation.

0

# SUMMARY - COINCIDENCE SYSTEMS

Coincidence experiments are increasing in importance in experimental endeavors ranging from nuclear structure studies to determination of elemental composition of materials. The wide variety of detectors and coincidence time requirements encountered in these experiments meant a sizable investment in equipment to meet the electronic demands of the individual experimenter. Due to the large assortment of devices necessary to perform typical experiments of this nature, the experimenter was forced to pay relatively high prices for each module because the economic benefit derived from high volume production was totally lacking.

Improvements in both commercially available components and circuit design indicated that a consolidation of functions in the components of the system might contribute to higher volumn production and lower overall cost. An attempt was made to reduce the cost of coincidence systems while simultaneously improving the operation and performance characteristics of the individual system components. This contract provided for studies of this nature to be carried out. As a result of this work, a new pre-amplifier, amplifier, time pick off/delay module, fast coincidence gate module

and power supply were designed. The modules were designed to comprise a versatile coincidence system applicable in all areas of coincidence counting experiments.

The primary motivation behind the pre-amplifier design was to produce a pre-amplifier which would be compatible with any detector. This eliminates the necessity for a pre-amplifier performing a single role in an overall counting system. The results of this design were very impressive; not only is the preamplifier compatible with all types of detector, but the low noise characteristics of the device make it very desirable in the most sophisticated high resolution counting system. The amplifier, like the preamplifier, proved to be beyond design expectations and in recent studies contributed the least distortion and noise contribution of any amplifier tested. The combination of the pre-amplifier and amplifier where pre-amplifier power is provided by the amplifier, is ideally suited for high resolution studies with or without coincidence operation. These two devices appear to be significantly better than those previously available in the same price region.

The time pick off/delay module design incorporates operational features superior to existing units, allows a reduced selling price, and provides a

variable delay for detector system time matching. In general, the test results obtained with this module, although impressive, indicated more thought should be given to this problem. As a result of this further investigation, another design is presently under way to improve the time reference for each pulse. The present studies indicate that high gain, nonlinear amplification at the pre-amplifier input might provide greater accuracy. However, the present time pick off/delay module has proved to be comparable with the specifications of other units of this type.

The final module within the coincidence system is the fast coincidence gate. The module contains continuously variable time resolution, 2 t from 20 nanoseconds to 200 nanoseconds. At the time this report was written, tests were still being conducted on this module. Additional work is required to insure complete satisfaction of the design specifications.

## INTRODUCTION-COINCIDENCE SYSTEMS

The value of fast coincidence systems in studying nuclear reactions or in determinations involving the elemental mixtures in materials has been adequately established. In routine counting systems coincidence techniques have not been widely used due to a variety of reasons. One primary restriction on widespread use of such techniques is the relatively high investment required to assemble a system. Of secondary importance are such things as timing limitations, adaptability with existing equipment, and duplication of routine system components.

Our initial goal under this contract was to attempt to solve the timing problems associated with coincidence systems. In particular we were interested in the problems involved when using dissimiliar detectors; i.e., lithium drifted germanium and sodium iodide. The primary reason for interest being the difference in signal rise time. As work progressed, it became apparent that the possibility existed of producing an entire coincidence system. The project was expanded to include: High Voltage Supply, Pre-Amplifier, Amplifier, Single Channel Analyzer, Time Pick Off/Delay Module, and Fast Coincidence Gate modulø.

The main effort under this contract centered about the Time Pick Off/Delay Module and Coincidence Gate Module. Additional engineers were added to the project to design and construct the remainder of the modules. The entire coincidence system is outlined below:

## PACKAGING CONSIDERATIONS

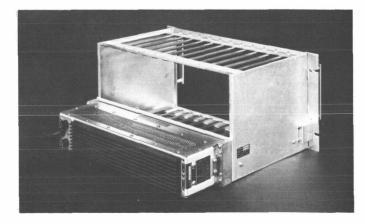

Prior to starting design of the coincidence system, it was decided that any instrument developed should conform to the AEC Committee on Nuclear Instrumentation Report TID-20893. NASA has also widely accepted these standards for size, power requirements, connectors and other features. As a result of using these standards, any resulting instrument would be usable in any bin available, regardless of the manufacturer. Figure 3 shows a standard bin and power supply. Further effort would be made to keep module sizes to a minimum in order to conserve space and save on the number of module widths used. Each modular width costs approximately \$60.00 in bin space.

0

# TECHNICAL SPECIFICATIONS

NUCLEAR DATA INC. 100 West Golf Road Palatine, Illinois 60067 Phone A.C. 312 • 529-4600

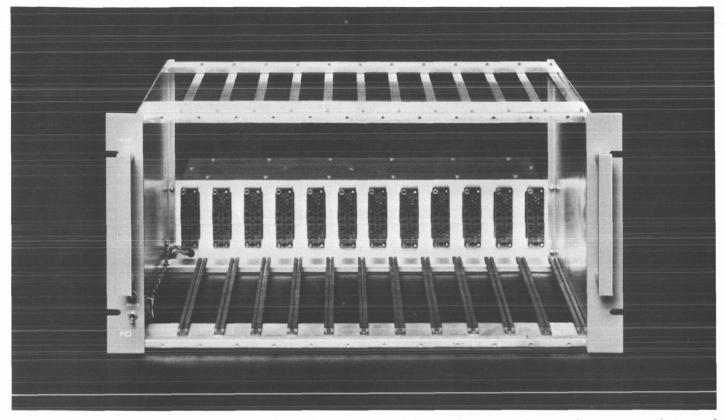

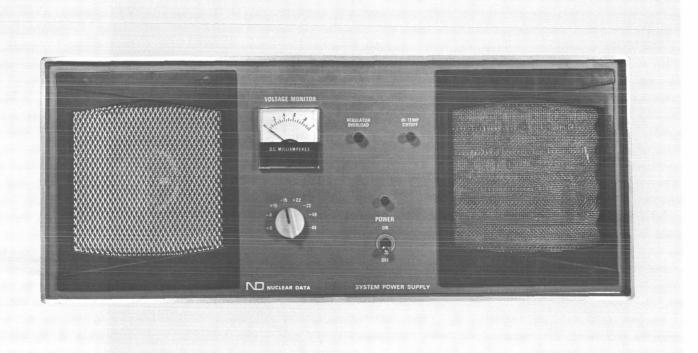

#### ND-510 MODULAR INSTRUMENTATION BIN AND ND-527 BIN POWER SUPPLY

The ND-510 Modular Instrumentation Bin and ND-527 Bin Power Supply provide mechanical and electrical facilities to accommodate a wide variety of nuclear instrument

#### ND-510 MODULAR INSTRUMENTATION BIN

Up to twelve single width modules, or combinations of multiple width modules can be mounted in the ND-510 Bin. A welded cadmium-plated steel frame, combined with aluminum module guides and rear panel, provides exceptional strength and lightness. The bin power switch and indicator lamp are located on the front mounting flange for ease of accessibility without sacrifice of module space.

**Dimensions:** 8-3/4" high x 19" wide x 10-3/4" deep (depth with power supply is 16-1/4").

Weight: Approximately 9 pounds (less power supply).

Module Receptacles: Twelve AMP type 202516-3.

**Receptacle Wiring:** All receptacles are wired in parallel in accordance with AEC Report TID-20893.

modules. Both units conform to the recommendations of the A.E.C. Committee on Nuclear Instrumentation as outlined in AEC Report TID-20893.

#### ND-527 BIN POWER SUPPLY

All D.C. operating voltages required for module operation, as outlined in AEC Report TID-20893, are provided by the ND-527 Bin Power Supply. This unit is the Power Designs Model AEC-320-3, a multi-output silicon solid state D.C. power supply.

FIG 3

#### MECHANICAL

**Dimensions:** 3.5" high x 16.9" wide x 5.5" deep.

Weight: Approximately 18 pounds.

#### ELECTRICAL

Power Requirements: 103-129 or 206-258 vac, 50-65 Hz, single phase, 200 watts maximum.

**Operating Temperature Range:** 0-50° centigrade (0-60° centigrade with 3% derating).

**Output Voltage and Current Rating:**

- A Supply = +12 vdc at 2 amperes.

- B Supply = -12 vdc at 2 amperes.

- C Supply = +24 vdc at 1 ampere.

- D Supply = -24 vdc at 1 ampere.

Note: Total combined output must not exceed 72 watts.

**Regulation:** ±0.1% for 100% change in load or line variations within operating range.

Ripple and Noise: 3MV peak-to-peak, max.

- Temperature Coefficient: 0.02%/°C between 0°C and 60°C.

- **Stability:** ±0.3% maximum voltage variation over 24hour period after 60-minute warm-up including variations due to load or line changes within the operating range.

- **Long-Term Stability:** Maximum drift less than  $\pm 0.5\%$  over 6-month period at constant load, line or ambient temperature conditions after 24-hour warm-up.

Voltage Adjustment Range:  $\pm 1\%$ , nominal.

Voltage Resettability: ±0.05%, max.

#### **Current Limiting Threshold:**

2.2 amperes, min., for 12-volt supplies.

1.2 amperes, min., for 24-volt supplies.

# HIGH VOLTAGE POWER SUPPLY

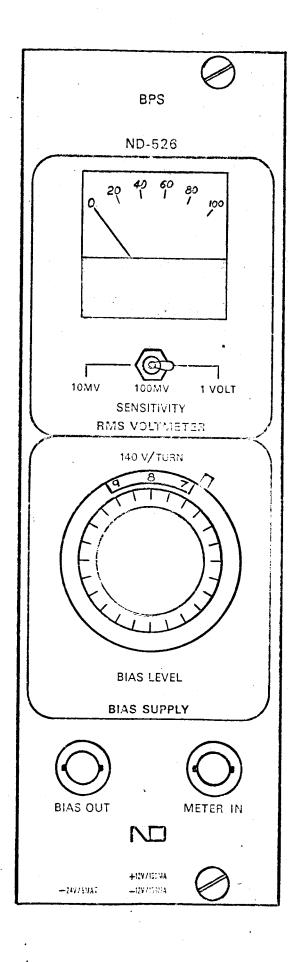

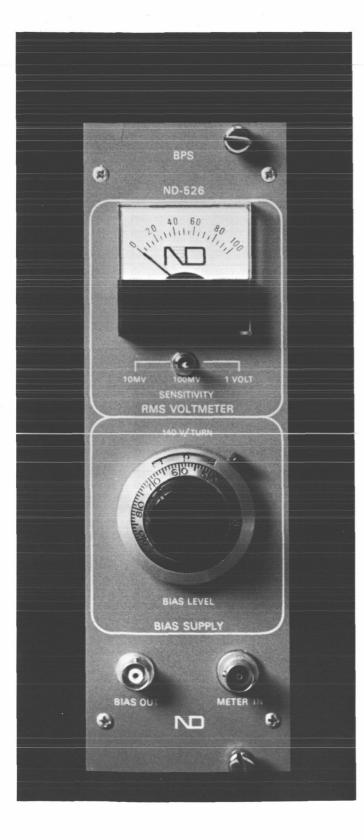

One expensive requirement of coincidence systems or of any detector system, is the power supply. Normally, several different types of power supplies are needed to satisfy experimental requirements Nal systems consume a large amount of current. Ge(Li) systems require exceptional stability and protection against sudden power failure (actually, the FETs in the preamp of Ge(Li) systems require this protection). Proportional counters require higher voltages than other detectors. A typical power supply is shown in Figure 4. Note that it is specifically designed for solid state detectors.

With these various and divergent requirements in mind, an attempt was made to design an all purpose power supply to aid in the reduction of costs of total coincidence systems. It was recognized that different power supplies were needed for detectors in use in any coincidence experiment. These extra components contributed greatly to the overall system cost. Another routine variable in all systems was the pre-amplifier which again contributed to the system cost. The high voltage supply and preamplifier were considered to represent one phase of this project. Work was begun on the simultaneous development of both modules.

F16 4

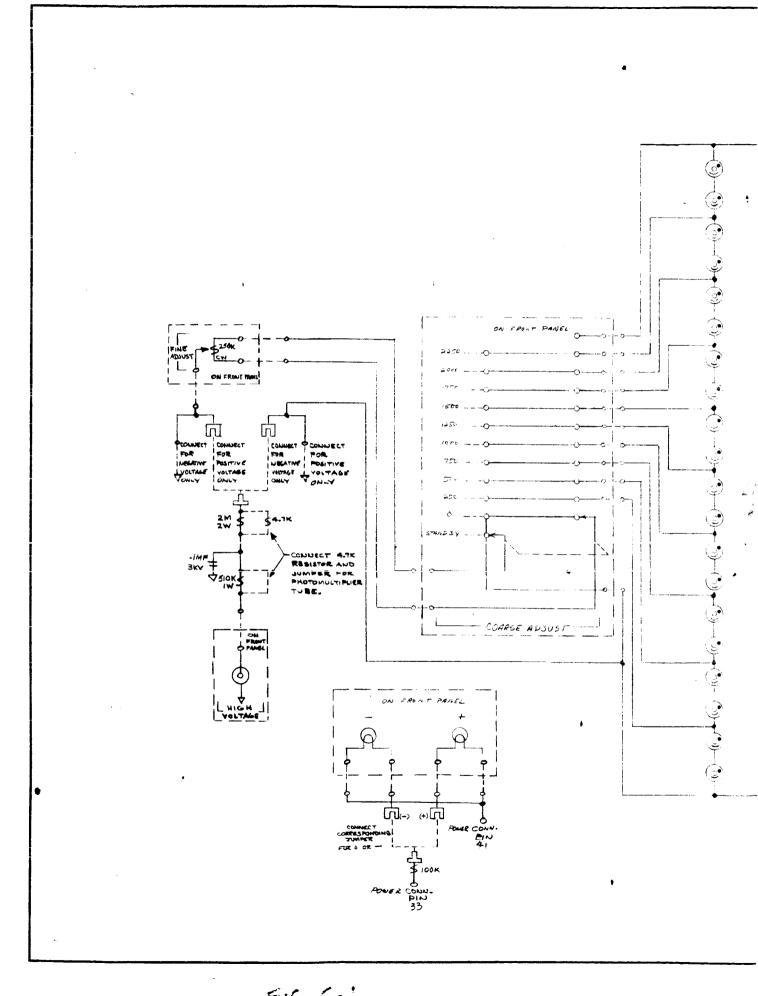

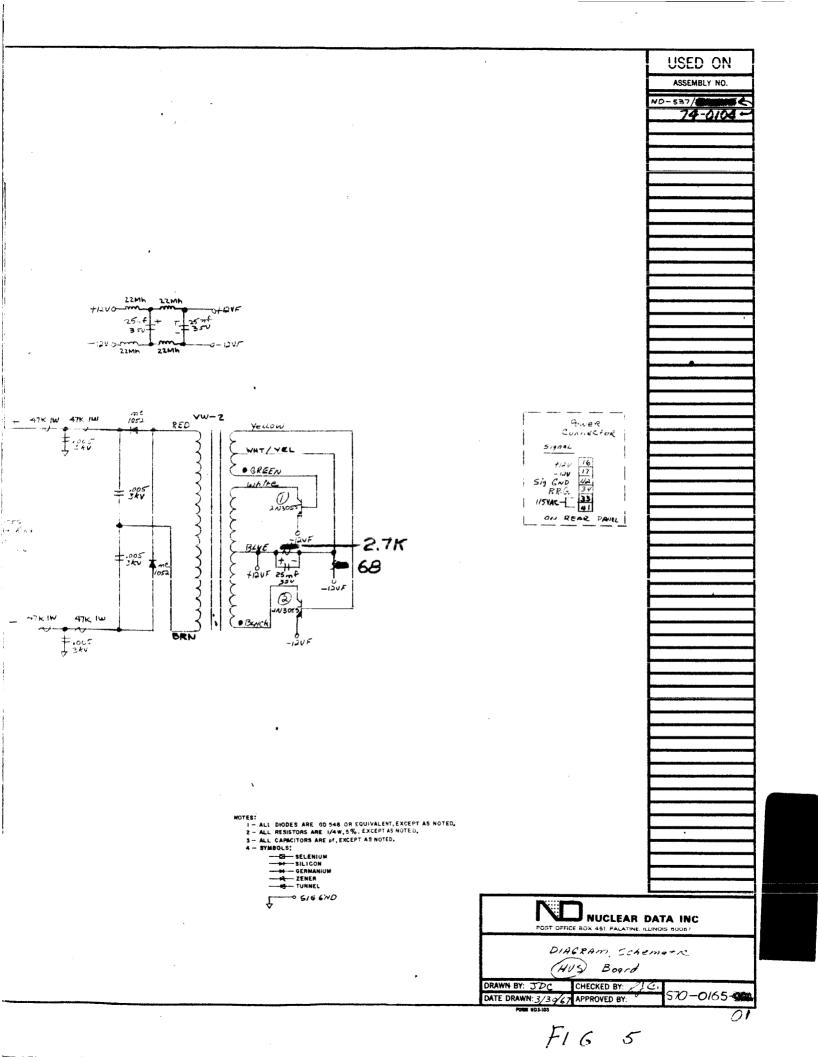

The result of this effort was a very stable high voltage power supply designed for biasing all types of detectors (Figure 4). Detector bias voltages up to 2500 volts D.C. were obtained by conversion of a relatively low D.C. voltage to a 25 kilohertz, A.C. voltage by means of an electronic "chopper". This A.C. voltage is rectified, doubled, filtered and applied across a series combination of miniature gaseous reference elements which provide a highly stable source voltage for constant current loads. (See Figure 5.)

Two front panel controls provide adjustment of the output voltage over a range of 0 to 2500 volts. An eleven position switch provides coarse adjustment with a range of 0 to 2250 volts in 250 volt steps, and a single turn potentiometer provides fine adjustment with a continuous control range of 250 volts for each increment of the coarse adjust switch.

Two separate controls were required because a potentiometer with a range of 0 to 2500 volts is not commercially available. The maximum rate of change of the output voltage is limited by a 0.2 second time constant. This protects both the detector and preamplifier inputs from damage which may result from sudden adjustment-induced voltage changes.

F16 5-1

Versatility is a prime factor in the design of the high voltage supply module in that, by simply relocating internal jumpers, the module is adapted for biasing photomultiplier type detectors or detectors requiring negative bias voltages.

The high voltage supply is housed in a standard AEC double width module and operates with standard bin power supply voltages.

Specifications of the high voltage supply are as follows: <u>Output Voltage:</u> 0 to 2500 volts D.C. <u>Output Current:</u> 1 milliampere, maximum. <u>Output Polarity:</u> Positive (negative output obtained by relocating two jumper wires).

<u>Output Impedance:</u> 510 kilohms (4.7 kilohms output impedance obtained by adding a resistor and a jumper wire for use with photomultiplier type detectors)

<u>Output Ripple:</u> 0.001% (25 millivolts peak to peak at full load; 2500 volts D.C. at 1 milliampere).

<u>Bias Stability:</u> Temperature - 0.013% per degree centigrade, A.C. line voltage -- 0.0005% per 10% change in line

0

voltage.

Regulation: 0.8% full load to no load.

Bias Control: Coarse -- 0 to 2250 volts in 250 volt steps.

Fine ----250 volt continuous range for each coarse step.

Output Time Constant: A 0.2 second time constant limits the maximum rate of change of the output voltage.

The final design, therefore, has the voltage range required by proportional counters, the stability required by Ge(Li) detectors, the current output for Nal detectors, and the protection required by Field Effect Transistor preamplifiers. All design goals on the high voltage supply were accomplished.

## PRE-AMPLIFIER

The goal in pre-amplifier design was to simplify the circuitry and at the same time develop an all purpose pre-amplifier. Previous preamplifiers were designed for specific applications.

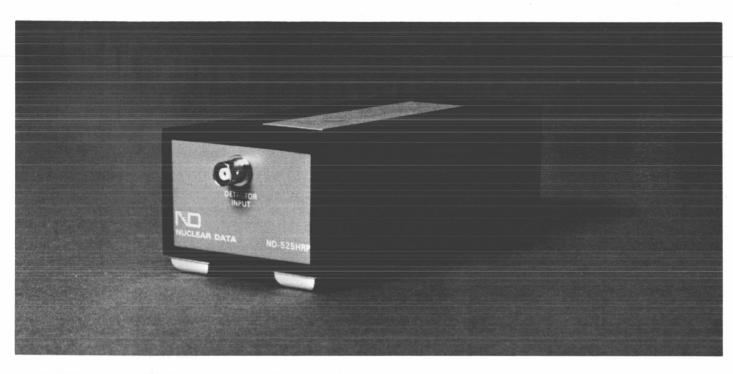

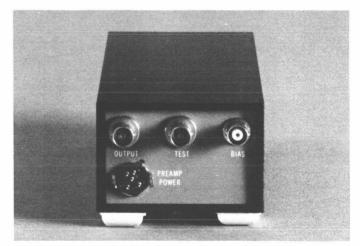

The result of this development is a charge-sensitive pre-amplifier which provides good resolution for use with semi-conductor detectors operating at room temperatures and has the necessary sensitivity for use with low-energy scintillation detectors and proportional counters (Figure 6).

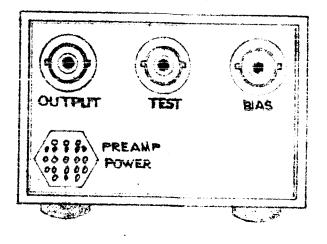

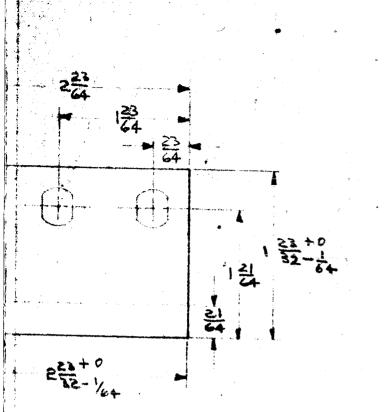

REAR

| FRONT  | AND RE | AR PANEL |  |

|--------|--------|----------|--|

| ND-52  | 5 HRP  | LAYOUT.  |  |

| G.M.W. |        | 8/3/66   |  |

FIG 6

÷

のないたい

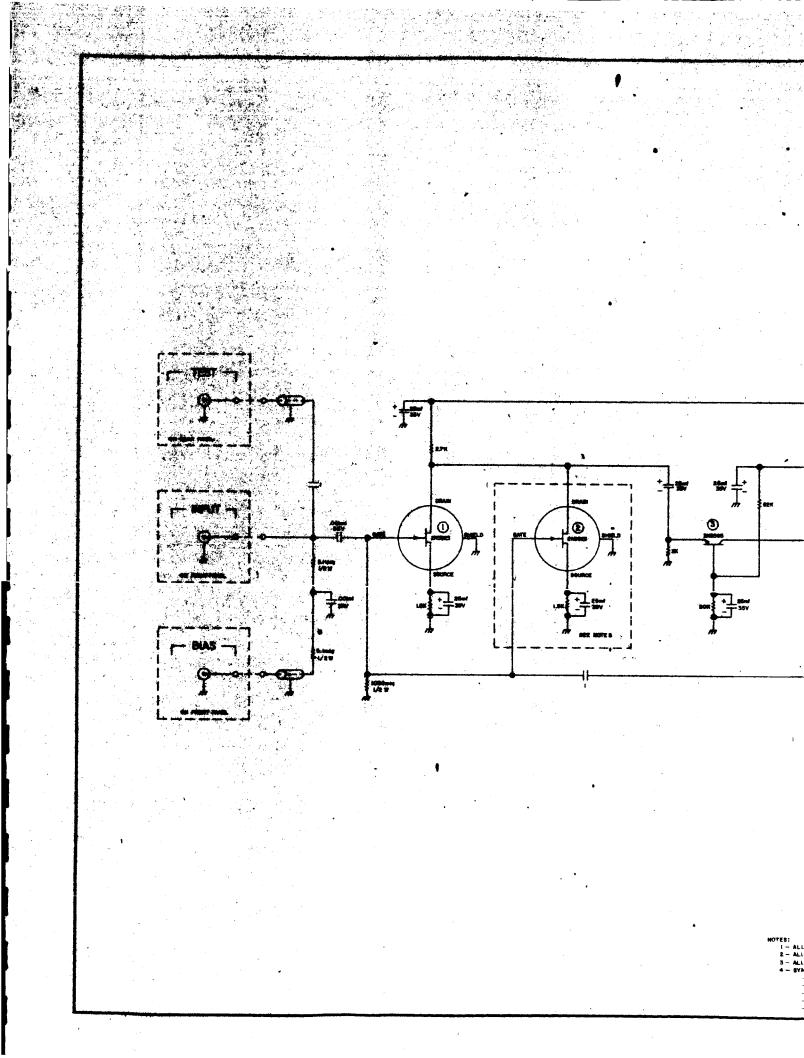

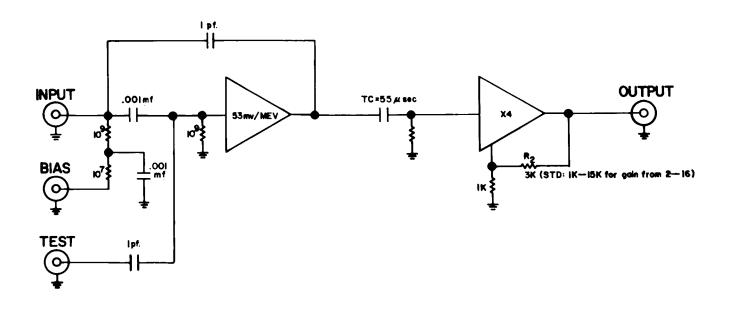

The pre-amplifier is comprised of a double field effect transistor (FET) input and a line driver (Figure 7). The preamplifier normally accepts negative charge inputs, however, by relocating three jumper wires, it will accommodate positive charge inputs.

The change-over from solid state detectors to scintillation detectors or proportional counters requires the change of two components, the input capacitor and resistor in the bias circuit. The required values are as follows:

| Type Detector        | Input Capacitor | Bias Resistor |

|----------------------|-----------------|---------------|

| Ge(Li)               | .001mf          | 5.1 meg -^-   |

| Proportional Counter | .010 mf         | 1.0 meg 🕂     |

| Scintillators -      | .100 mf         | 100K -^-      |

An additional saving was made possible by bringing operating power, +24 V d.c. through the same cable that carries the output signals. By tying this preamplifier to the amplifier designed for the coincidence system, additional savings were made possible. In addition to the preamplifier input and output connectors, two connectors, designated TEST and BIAS, were provided. The TEST connectors provide an input for application of a proper polarity voltage pulse to check system performance. The BIAS connector provides an input for application of high

voltage (up to 2500 volts) to bias an external detector.

# SPECIFICATIONS:

Input Polarity: Normally negative charge inputs; by relocating

three jumper wires, positive charge inputs are accommodated.

Noise (Ge): 2 keV at 10 pF, external capacitance.

Noise Slope: .04 keV/pF, external capacitance.

Rise Time: 75 nanoseconds at 0 pF, external capacitance.

200 nanoseconds at 100 pF, external capacitance. Output Polarity: Always positive.

Saturation Levels: +6 volts and -3 volts.

Integral Linearity: 0 to 1 volt, 0.1% or better.

Temperature Stability: 0.1% per degree centigrade.

Power Requirements: +24 V d.c. at 5 milliamperes.

The preamplifier design achieved the majority of the design requirements originally outlined. It can be used with all types of detectors by merely changing plug-in components; it can carry the high voltage requirements of proportional counters, it can be built for significantly less than the price of competitive instruments which can be used with only one type of detector.

Further improvement is possible. The FETs used in this preamp have Gm of 4,000 to 5,000 and Cgs (capacitance gate to source) of 0.6pF. It appears that FETs with Gm of 15,000 and Cgs of 0.3pF could result in an improvement in preamplifier specifications from 2 keV noise to 1.5 keV and from 0.04 keV/pF noise slope for external capacitance to 0.2 keV/pF.

Another improvement which seems possible is the introduction of **positive** feedback. This could eliminate the noise slope increase with increased capacitance. Noise would be limited to 2 keV regardless of input capacitance.

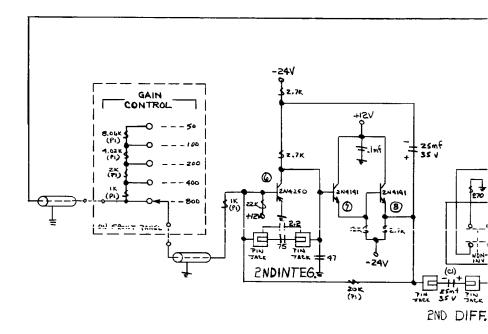

## AMPLIFIER

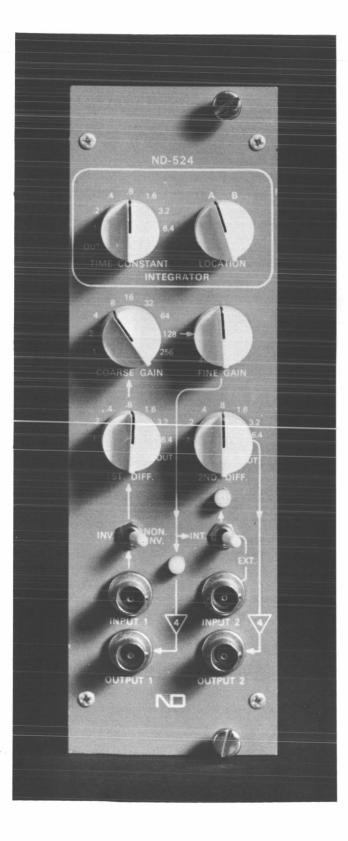

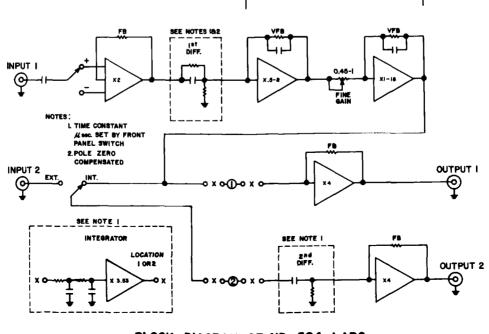

Generally speaking, amplifiers are the most complex module in a detection system. Since two or more are required in a coincidence experiment, amplifiers usually require large space and a sizeable portion of the investment in a coincidence system. A great deal of effort was, therefore, expended in designing the amplifiers for the coincidence system. A typical multipurpose amplifier is shown in (Figure 8).

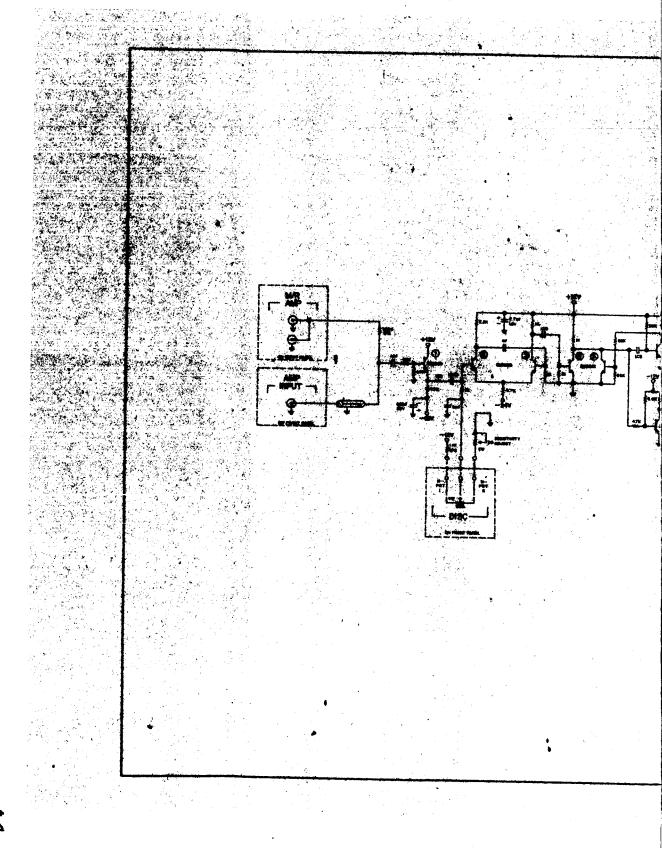

The result of the amplifier development can be seen in Pigure 9.

FIG 8

A number of features were incorporated to provide an excellent amplifier at a minimum cost. First, +24 volts was made available to drive the pre-amplifier through the amplifier input cable. This arrangement provided economies in both the pre-amplifier and amplifier.

The next design feature of the system was to build in variable pole zero clipping.<sup>4</sup> By making this clipping adjustable, it was found that the pre-amplifier did not require pole zero clipping, and that the clipping need not be compensated for changes in time constants within the amplifier.

Another feature of the design was the removal of differentiator and integrator controls from the front panel. (See Figure 9). These controls have been replaced with plug-in capacitors on pin jacks for selection of time constants. There are four capacitors, two each for differentiators and integrators. This design has been incorporated because many users select optimum settings on their amplifiers and lock the amplifier in that position. The user still has the choice of single or double differentiation.

It should be pointed out that this amplifier was designed around two stages of differentiation and two stages of integration only. In theory, the larger the number of integration stages, the smaller the noise. By

(4) See"Elimination of Undesirable Undershoot in the Operation and Testing of Nuclear Pulse Amplifiers" - Nowlin and Blankenship -Review of Scientific Instruments, Volume 36 - number 12 - December 1965.

$i \in \mathcal{I}^*$

FIG 9

carefully designing the two stages of integration, a noise figure of 4.0 microvolts referred to the input was achieved with single differentiation and 5.0 microvolts with double differentiation. These figures are a factor of 2 or 3 better than existing amplifiers. Other specifications of the amplifier are also as good as or better than existing designs. We are quite happy with the results of the design effort on this amplifier.

Specifications of the amplifier are as follows:

Amplifier Input: Two BNCs (one front, one rear) accept positive,

low level signals from a pre-amplifier. Input impedance is approximately 1000ohms.

Gain Stability: 0.03% per degree centigrade.

Gain Controls: Coarse: 50 to 800 in binary steps.

Fine: 0.5 to 1 continuous range between coarse steps.

<u>Pulse Shaping</u>: Two passive differentiators and two active integrators. First differentiator is pole-zero compensated to cancel undershoot effects. The RC shaping time constants can be changed by replacing four capacitors. These capacitors are equipped with pin jacks for easy insertion or removal.

- <u>Noise:</u> 4.0 microvolts, referred to the input at maximum gain and with single differentiation and double integration or 5.0 microvolts with double differentiation and integration.

- Overload: With single differentiation and double integration--Recovers from 500 x overload in 3 non-overloaded pulse widths.

- Characteristic Rise Time: With single differentiation--300 nanoseconds.

- <u>Amplifier Output:</u> Signal Characteristics--Front panel BNC provides positive or negative monopolar or bipolar voltage pulses (internal switch selectable).

Impedence -- 100 ohms

Saturation Levels --+12 volts and

-12 volts.

Integral Linearity -- 0.1% from 0 to 10 volts.

M/R Amplifier Output: Signal Characteristics - Rear Panel BNC provides

0

positive, monopolar current pulses.

Impedance -- 100K ohms.

Saturation Levels -- +0.12 milliampere and -0.12 milliampere. Integral Linearity -- 0.1% Single Channel Analyzer

Development of a single channel analyzer has not, as yet, started as part of this program. The design would be based on the single channel analyzer shown in Figure 10 and Figure 11.

As part of the program, however, it was found that integral discriminators could be useful in simple coincidence systems. A simple discriminator was, therefore, designed. Its mechanical configuration was such that it could fit into the amplifier module or be separately packaged in pairs (Figure 12).

Specifications on the discriminator are as follows:

Input: Impedance -- approximately 7.5 kilohms.

Sensitivity -- 30 millivolts to 10 volts, selected by a

۵

front panel control

Linearity: 0.5%, 30 millivolts to 10 volts.

Stability: 0.1% per degree centigrade.

FIG //

FIG 12

Discriminator Output: Signal Characteristics -- Front panel BNC provides a positive 10 volt rectangular pulse.

Impedance -- 50 ohms.

Pulse Shape -- Nominally 10 microseconds FWHM, 0.15 microsecond rise and fall times. Pulse width may be decreased to 0.5 microsecond minimum by a single component value change.

Time Pick-Off/Delay Module

The time pick-off module, Figure 13, is the portion of the coincidence system that provides an output pulse timed to a point on the input pulse. This point may be the leading edge of a unipolar or bipolar pulse or the cross-over point of a bipolar pulse. The outputs, or lack of one, from two or more time pick-off units are then fed to a coincidence gate, where a decision is made as to whether a coincidence or anti-coincidence occurred within some preset time.

A typical coincidence system may appear as indicated in Figure 14. Since there are two distinct sets of detectors and electronics up until the coincidence gate, the first problem we wished to eliminate was that of different timing lags on the two legs. In any coincident event, two particles interacting within the detectors simultaneously may not appear to be

Tic/s

FIG 13

.

coincident. Differences in response of the detectors, differences in the pre-amplifiers and amplifiers may make the two pulses at the time pickoff module appear to arrive at different times. In order to eliminate this problem and to give the time pick-off module greater flexibility, a variable delay was built into the module.

This circuit allows 50 nanoseconds to 1.5 useconds delay prior to issuing a strobe pulse. By using the inspect point on the coincident gate module, the delays can now be established to compensate for detection system differences. This feature considerably simplifies properly setting up the coincidence system.

This module was designed with both leading edge and cross-over timing modes. Some controversy exists as to when to use which mode and exactly where in the circuit to place the time pick-off module. A number of variables may interact and the experimenter has to make a decision as to which parameter is most important to him.

Count rate is one factor. In general, the higher the count rate, the more advantageous is cross-over timing, hence, placing the time pickoff unit after the amplifiers.

٥

The energy of interest is another factor.

If a wide band of energies is desired in the Nal systems, or very high resolution is desired in Ge(Li) systems, placing the time pick-off unit after the amplifier is again advantageous.

However, if energies of interest are restricted in Nal experiments or if timing accuracy is more important than resolution in Ge(Li) experiments, it appears that leading edge timing after the pre-amplifier and amplifier is, however, somewhat detrimental to energy resolution.

We have favored energy resolution in the design of the time pickoff module rather than time resolution. The time pick-off module has been designed to be used after an amplifier and to provide high resolution at the cost of time resolution.

Specifications on this unit are as follows:

<u>Input:</u> 0 – 10 volt initially positive, bipolar, linear signal, double RC differentiated or double delay line. Input impedance is approximately 1 kilohm.

<u>Timing</u>: Delay Range: Adjustable in the X1 position from 50 to 500 nanoseconds; in the X3 position, from 0.15 to 1.5 microseconds.

Threshold: Sensitivity Range: Variable from 0.5 to 9.6 volts.

Time walk: Less than 4 nanoseconds over full range.

- Temperature Stability: Time walk as a function of temperature, including both time pick-off and delay circuits, is 0.7% of delay, or 0.1 nanoseconds per <sup>o</sup>C, whichever is greater.

- Time Walk: For an input amplitude change of 10 volts to 1 volt, time walk is less than 4 nanoseconds. For an input amplitude change of 10 volts to 0.5 volt, time walk is less than 10 nanoseconds.

- <u>Strobe Output:</u> For a resistive load of 100 ohms -- +6.5 volts rise time of 15 nanoseconds, fall time of 20 nanoseconds, duration of 300 nanoseconds at FWHM.

For a capacitive load of 100 Picofarads -- +8 volts, rise time of 12 nanoseconds, fall time of 200 nanoseconds, duration of 320 nanoseconds at FWHM.

Prompt Output (rear panel): +3.8 volts, rise time of 20 nanoseconds, fall time of 20 nanoseconds, pulse duration determined by

the time between the leading edge and cross-over points of

the input pulse, occurs 40 nanoseconds before strobe output (with delay controls set at minimum). Output impedance, 50 ohms.

Work will continue in this area in order to 1) reduce the walk of the unit and 2) investigate further the adaptability of this unit to leading edge timing of signals from pre-amplifiers.

## COINCIDENCE GATE

Of the many modules under development, this proved to be the most difficult to perfect. Work is continuing in this area but the results are somewhat disappointing. The primary cause for concern lies in the area of generating a single gate pulse for every coincident event. A simplified discussion of the problem encountered is as follows: When an input arrives at the fast coincidence gate from either Time Pickoff unit, an internal pulse of 2 t width is generated. If an input from the other Time Pickoff unit should arrive during this time, an output gate signal is generated. If the time requirements are not fulfilled, an output pulse cannot be originated. To date, accidental coincidence rates were determined to have been much too high and the cause of this has been traced to the following: Whenever an internal pulse has occurred, it is accompanied by a series of smaller amplitude pulses caused by ringing of the primary pulse. These ringing pulses double, triple or even quadruple the acceptable coincident time

period. This effect is further complicated by the provision for variable coincidence resolving times which does not provide a convenient means for establishing a fixed time window.

As work on this project has progressed, little attention was given to absolute values regarding laboratory type coincidence experiments. Many tests were performed using pulse generators which did not exhibit this phenomena due to the lack of random inputs. Before this report was prepared in final draft, more extensive random input tests were performed with rather critical analysis given to experimental results. At that time, the abnormally high accidental rates were detected and time has not permitted rectification of the problem.

The design of this module contains a number of features useful in setting up coincident experiments. Any input may be selected for coincidence, anti-coincidence, or disabled. In addition, singles, doubles, or triples in any combination may be selected.

Specifications on this system are as follows:

Inputs: Three front panel BNC connectors accept positive 3-10 volt pulses with a maximum rise time of 25 nanoseconds and a minimum input pulse width of 30 nanoseconds, Input impedance is

approximately 1 kilohm.

Logic Function Selection: Three toggle switches, one per input, select the logic function to be performed.

<u>Coincidence Threshold:</u> The acceptance level of the output logic can be selected as follows: In singles, any one input, or one or more in coincidence, provides an output; in doubles, any two coincident inputs; in triples, three coincident inputs.

<u>Resolving time:</u> The pulse width of the signals generated by each input, as applied to the output logic circuits, can be varied from 10 - 110 nanoseconds with a resultant 2t range of 20 -220 nanoseconds.

When any one input is switched to anti-coincidence, its pulse width is extended from t to 2t, insuring optimum anti-coincidence operation.

<u>Timing Inspect:</u> The timing inspect point presents the sum of all three inputs for observation, allowing normalization of system delays by direct observation.

Gate Outputs: D.C. coupled outputs with the following levels:

+ Gate: "0" - 12 volts "1" + 1 volt - Gate: "0" + 1 volt "1" - 12 volts

This unit requires further work and Nuclear Data is continuing efforts in this area.

44

## CONCLUSION

The total work performed under this contract has been shown to be both extensive and economical. The Multimode System itself is more than adequate for the experimental program anticipated. It contains useful features from input to output which greatly enhance its flexibility. Its speed and resolution in analysis, minimum storage time, and versatility in display and readout contribute to the continued high performance the system has thus far demonstrated. This portion of the contract has proven to fulfill each detail of the requirements with the majority of the specifications exceeded.

The time of flight development work has, like the Multimode system, exceeded the early expectations of the designers. The high frequency oscillator, prescaler, double derandomizer, expanded delay, and channel width range have added significantly to the current state of the art. As the report clearly indicates work on this project was a complete success.

The results of the total coincidence system are somewhat disappointing in the light of the success achieved in the Multimode system and the time of flight. These results should be reviewed from a more positive viewpoint, however, when serious consideration is given to the development of a preamplifier, amplifier, bias supply, and the upward trend in the time pick-off unit and the coincidence gate program. We have successfully completed work on the former Modules while work is continuing on the latter two.

To summarize some of the advances made over the period covered by the contract, an impressive list of user orientated advantages has been assembled:

- (1) Duplication of power supplies has been éliminated.

- (2) Duplication of preamplifiers has been eliminated.

- (3) Special power supplies have been eliminated.

- (4) A great reduction in size has been achieved.

- (5) Bothersome delay lines have been eliminated.

- (6) High quality-high performance amplifiers are now availableat a great reduction in cost.

- (7) Physical packaging in agreement with AEC/NASA standards.

- (8) Integrated circuitry used extensively.

- (9) Preamplifier power supplies have been eliminated.

(10) Interchangeability of components is assured through standard NIM modules.

This total project has contributed several significant advantages over systems previously available. Because of the additional effort made by Nuclear Data, Inc. to expand the special coincidence modules into a total spectroscopy system we feel we have contributed significantly in bringing that phase of the contract to a successful completion.

The authors wish to acknowledge the diligent efforts by Mr. William Jacobs in amplifier design, Mr. Mitchell Leifer and Mr. Frank Spokas in Time of Flight design.

Total time extended on this system was as follows:

| High voltage supply                                 | 160 hours |

|-----------------------------------------------------|-----------|

| Pre-amplifier                                       | 200 hours |

| Amplifier                                           | 320 hours |

| Single channel analyzer<br>(Integral discriminator) | 40 hours  |

| Time pick-off/Delay Module                          | 320 hours |

| Coincidence gate                                    | 360 hours |

| Time of Flight                                      | 480 hours |

## **APPENDIX** I

## TIME OF FLIGHT MODULE

## INSTRUCTION MANUAL

Interim Edition September, 1967

NUCLEAR DATA, INC. Post Office Box 451 Palatine, Illinois 60067

Copyright 1967, by Nuclear Data, Inc. Printed in U.S.A.

## CONTENTS

| Section             | Page  |

|---------------------|-------|

|                     | . 1   |

| General             | , . 1 |

| Specifications      | . 1   |

| PREPARATION FOR USE | . 3   |

| Interconnections    | 3     |

| Control Functions   | . 3   |

| OPERATION           | . 5   |

## INTRODUCTION

## GENERAL

This NIM compatible Digital Time of Flight Module is a highly accurate and versatile unit that can be used with the Series 3300 or 2200 System Analyzer (as specified when ordered) to measure one-quarter microsecond minimum channel widths when performing operations such as encountered in neutron time of flight measurements. Pulse width analysis and single pulse analysis experiments may also be performed as selected by a front panel switch. A 32 MHz, crystal controlled oscillator minimizes channel time jitter and insures long term stability. A switch selectable, delay time control is included that incorporates no fixed internal delay and can be used to delay the start of analysis for up to 99,990 channels. A variable dead time, and memory capacity switch completes the complement of controls.

## **SPECIFICATIONS**

## Start Input

## Pulse Requirements

|                    | Amplitude: | 2 to 20 volts.                  |

|--------------------|------------|---------------------------------|

|                    | Polarity:  | Positive.                       |

|                    | Rise Time: | Noncritical; should be uniform. |

| Input Impeda       | nce        | Approximately 2000 ohms.        |

| Event Input        |            |                                 |

| Pulse Require      | ements     |                                 |

|                    | Amplitude: | 2 to 20 volts.                  |

|                    | Polarity:  | Positive.                       |

|                    | Rise Time: | Noncritical; should be uniform. |

| Input Impedance    |            | Approximately 2000 ohms.        |

| Stop Input         |            |                                 |

| Pulse Requirements |            |                                 |

|                    | Amplitude: | 2 to 20 volts.                  |

|                    | Polarity:  | Positive.                       |

|                    | Rise Time: | Noncritical; should be uniform. |

| Input Impeda       | ance       | Approximately 2000 ohms.<br>–1– |

## Input Signal Attenuation

None required as long as signal returns to less than one volt prior to completion of operation.

## Clock Oscillator

32 MHz, crystal-controlled.

Channel Width (Time Duration)

0.25 to 128 microseconds switch selectable in binary increments.

## **Channel Time Jitter**

+ 1/64 microsecond.

## Delay Time

0 to 99,990 channels thumbwheel switch selectable in 10 channel increments.

## Fixed Delay

No fixed delay is incorporated in this unit. Delay times are as selected.

## Dead Time

8, 16 or 32 microseconds, switch selectable.

## Memory Size

16 to 4,096. Channels switch selectable in binary increments. 8192 or 16,384 sizes optional.

## Power Requirements

+12 volts D.C. at 1 ampere.

-12 volts D.C. at 250 milliamperes.

## Size

8.71" high x 5.36" wide x 9.7" deep (equivalent to four standard AEC single width modules).

## PREPARATION FOR USE

## INTERCONNECTIONS

## SERIES 3300 SYSTEM

- 1. Insert the Time of Flight Module into any standard AEC bin with a power supply.

- 2. On the Series 3300 System remove the cable between the DATA ACQUISITION receptacle on the Data Handling Section and the PROGRAM INPUT receptacle on the Data Acquisition Section and connect it from the DATA ACQUISITION receptacle to the TIME OF FLIGHT 50 receptacle on this module.

## SERIES 2200 SYSTEM

- 1. Insert the Time of Flight Module into any standard AEC bin with a power supply.

- Remove the ADC pigtail connector (on the Master Control Module) from the Series 2200 ADC and connect it to the TIME OF FLIGHT - 50 receptacle on this module.

## CONTROL FUNCTIONS

## CHANNEL WIDTH (MICROSECONDS)

This control establishes the time duration, during which a given event will be accepted for storage in a given channel.

## CHANNEL DELAY

This thumbwheel switch selects the number of channels for which the unit will not accept any events and the program counter will remain at the reset state. This control enables the user to gain better resolution of data that normally appears at the end of the time of flight measurement.

## DEAD TIME (MICROSECONDS)

This three position switch selects the time for which the unit, after accepting an event for processing, will not accept another. The time selected should be that minimum time which is greater than the memory cycle time. The DEAD TIME Control corrects for the time required to complete a memory cycle so that multiple events may be processed during a single sweep cycle.

## MEMORY SIZE

This switch selects the memory size that is required or available.

## MODE

This three position switch selects the operating mode of the Time of Flight Module.

MPA (Multiple Pulse Analysis)

This position permits multiple pulse analysis during a single cycle.

PWA (Pulse Width Analysis)

This position permits pulse width analysis, i.e., channel number is proportional to the incoming pulse width.

SPA (Single Pulse Analysis)

This position permits single pulse analysis per cycle. After event storage, the Time of Flight Module is reset and awaits another start signal.

## OPERATION

The following instructions describe the normal method of set-up of this Time of Flight Module. In all cases, specific control settings depend upon experiment requirements. These instructions assume that all ancillary equipment is interconnected and operating properly and all power is on. All modes of operation are set up in the same manner. The procedure is as follows:

- 1. On the MEMORY SIZE Switch, select the number corresponding to the number of channels being used.

- 2. Select the desired channel width using the CHANNEL WIDTH Switch.

- 3. Using the CHANNEL DELAY Thumbwheel, select the amount of channel delay desired.

- 4. Select the dead time required using the DEAD TIME Switch. When this unit is used with a Series 2200 System in Live/Static display or a Series 3300 System with the display off, the memory cycle time is 6 microseconds. The DEAD TIME Switch is then normally set at position 8.

- 5. Select the mode of operation desired, using the MODE Switch.

- 6. Supply the proper signals to the START and EVENT BNC connectors on the front panel. The signals required are described in the SPECIFICATION Section of this manual. The STOP input is used only to externally stop and reset the unit. It is normally not used.

### NOTE

When in the PWA mode, the pulse to be measured should

be connected to the START BNC. The STOP and EVENT

BNC's are not used in this mode.

APPENDIX II

49

## ND-532ARC AMPLIFIER RC

1

## INSTRUCTION MANUAL

First Edition September, 1967

NUCLEAR DATA, INC. Post Office Box 451 Palatine, Illinois 60067

Copyright 1967, by Nuclear Data, Inc. Printed in U.S.A.

## CONTENTS

| Section                   | Page | 2 |

|---------------------------|------|---|

|                           | . 1  |   |

| General Description       | . 1  |   |

| Specifications            | . 1  |   |

|                           | . 4  | • |

| Front Panel               | . 4  | • |

| Rear Panel                | . 4  |   |

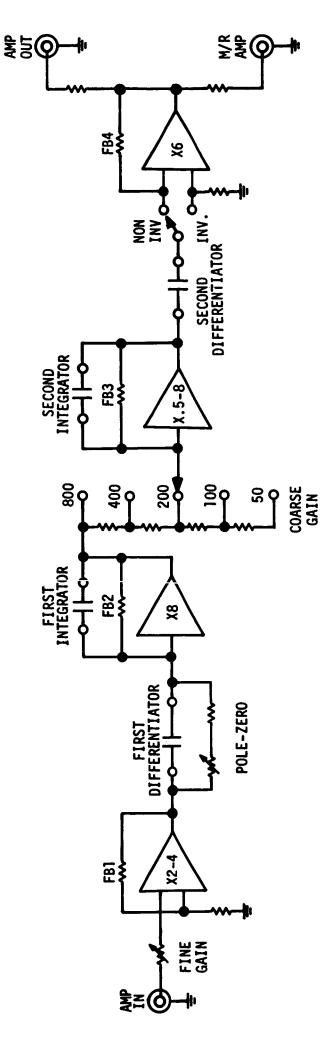

| BLOCK DIAGRAM DESCRIPTION | . 6  | ) |

| Block Diagram             | . 7  | , |

| SCHEMATIC DIAGRAM         | . 8  | } |

## INTRODUCTION

### GENERAL DESCRIPTION

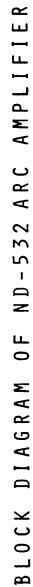

The ND-532ARC Module is a linear amplifier with RC pulse shaping designed for nuclear pulse spectroscopy. When used with its companion, ND-533 Preamplifier Module, the ND-532ARC provides the necessary resolution and gain for use with Mössbauer systems, proportional detectors or low energy scintillation detectors.

Note: When the ND-532ARC Module is used with a preamplifier

other than its companion, ND-533 Preamplifier, the 470 ohm

resister at the input must be disconnected. This resistor supplies

+24 volts D.C. operating power to the ND-533 Preamplifier

through the AMP IN BNC.

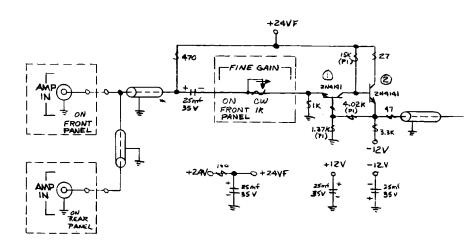

RC pulse shaping is provided by two passive differentiators and two active integrators. The first differentiator is pole-zero compensated to cancel under shoot effects. The RC shaping time constants can be changed by replacing four capacitors. These capacitors are equipped with pin jacks for easy insertion or removal. A switch, mounted on the printed circuit board, provides for selection of either a positive or negative output pulse. Maximum gain with double differentiation and integration is 800 and with single differentiation and double integration, 1600. Gain is adjusted by two front panel controls: a five position switch for coarse gain adjustment with a 16:1 range in 2:1 stops and a single turn potentiometer for fine gain adjustment with a 2:1 continuous range between coarse steps. Noise, referred to the input at maximum gain and with double differentiation and integration and integration, is 5.0 microvolts and with single differentiation.

In addition to the normal amplifier output, the ND-532ARC provides a simultaneous standardized current pulse output at the rear panel M/R AMP BNC. This output is appropriate for use in a multiple input mixer/router system for multichannel analyzers, or can be applied in a variety of other spectrometer and signal gating configurations.

#### SPECIFICATIONS

#### AMPLIFIER INPUT

Two BNC's (one front, one rear) accept positive, low level signals from a preamplifier. Input impedance is approximately 1000 ohms.

## GAIN STABILITY

0.03% per degree centigrade.

## GAIN CONTROLS

Coarse -- 50 to 800 in binary steps.

Fine -- 0.5 to 1 continuous range between coarse steps.

## PULSE SHAPING

Two passive differentiators and two active integrators. First differentiator is pole-zero compensated to cancel undershoot effects. The RC shaping time constants can be changed by replacing four capacitors. These capacitors are equipped with pin jacks for easy insertion or removal.

## NOISE

4.0 microvolts, referred to the input at maximum gain and with single differentiation and double integration or 5.0 microvolts with double differentiation and integration.

### OVERLOAD

With single differentiation and double integration -- Recovers from 500 x overload in 3 non-overloaded pulse widths.

CHARACTERISTIC RISE TIME

With single differentiation -- 300 nanoseconds.

**AMPLIFIER OUTPUT**

Signal Characteristics -- Front panel BNC provides positive or negative, monopolar or bipolar voltage pulses (internal switch selectable).

Impedance -- 100 ohms.

Saturation Levels -- +12 volts and -12 volts.

Integral Linearity -- 0.1% from 0 to +10 volts.

M/R AMPLIFIER OUTPUT

Signal Characteristics -- Rear Panel BNC provides positive or negative, monopolar or bipolar current pulses (internal switch selectable).

Impedance -- 100K ohms.

Saturation Levels -- +0.12 milliampere and -0.12 milliampere.

Integral Linearity -- 0.1% from 0 to +0. 10 milliampere.

## POWER REQUIREMENTS

- +24 volts D.C. at 25 milliamperes.

- -24 volts D.C. at 10 milliamperes.

- +12 volts D.C. at 15 milliamperes.

- -12 volts D.C. at 25 milliamperes.

- SIZE

- 8.71" high x 1.34" wide x 9.7" deep (standard AEC single width module).

## WEIGHT

Approximately 1.5 pounds.

## CONTROLS AND CONNECTORS

## FRONT PANEL

## COARSE GAIN CONTROL

Provides adjustment of the overall amplifier gain from 50 to 800 in binary steps. The overall amplifier gain with double differentiation and integration corresponds to the setting of the COARSE GAIN control.

## FINE GAIN CONTROL

Provides an overlapping adjustment of the overall amplifier gain with a .5 to 1 continuous range for each setting of the COARSE GAIN control.

AMP IN (Amplifier Input) BNC

Accepts positive, low-level signals from an external preamplifier. Also provides +24 volts D.C. operating power to the ND-533 Preamplifier.

Note: When a preamplifier other than the ND-533 is used, the

470 ohm resistor at the input must be disconnected as this resistor

supplies the +24 volts D.C. operating power to the ND-533 Preamplifier.

AMP OUT (Amplifier Output) BNC

Provides positive or negative, monopolar or bipolar voltage pulses for use with an external analog to digital converter, single channel analyzer or crossover timing unit.

Note: Positive or negative output is selected by the

internal INV/NON INV switch.

## REAR PANEL

AMP IN (Amplifier Input) BNC

Accepts positive low-level signals from an external preamplifier. This BNC is connected directly to the front panel AMP IN BNC.

M/R AMP (Mixer/Rejector Amplifier Output) BNC

Provides positive or negative, monopolar or bipolar current pulses for use with an external multiple input mixer/router system or a variety of other spectrometer and signal gating configurations.

Note: Positive or negative output is selected by the internal INV/NON INV switch. This switch must be in the NON INV position when output is used with a multiple input mixer/router system as this system will only accept positive current pulse inputs.

## BLOCK DIAGRAM DESCRIPTION

Positive low-level signals at the AMP IN BNC are coupled through the FINE GAIN control to an operational amplifier having a variable gain of two to four. The gain of the operational amplifier is determined by the ratio established by the setting of the FINE GAIN control and the feedback resistor (FB1). The output of the operational amplifier is applied to the first differentiator circuit which is pole-zero compensated to cancel the undershoot effect of pulse differentiation. Signals from the first differentiator circuit enter the first operational integrator which has a fixed gain of eight. The output of the first operational integrator is coupled through the COARSE GAIN switch to the second operational integrator which has a variable gain of 0.5 to 8. The gain of the second operational integrator is determined by the ratio established by the setting of the COARSE GAIN switch and the feedback resistor (FB3). The output of the second operational integrator is coupled through the second differentiator circuit and the INV/NON INV switch to another operational amplifier having a fixed gain of six. The output of this operational amplifier is applied to two output BNC's: AMP OUT which provides positive voltage pulses when the INV/NON INV switch is in the NON INV position or negative voltage pulses when the INV/NON INV switch is in the INV position and M/R AMP which provides positive or negative current pulses again depending upon the positioning of the INV/NON INV switch.

Note: If the M/R AMP output is applied to the input of the

ND-521 M/R Mixer/Rejector Module, the INV/NON INV

switch must be in the NON INV position as the ND-530 M/R will

only accept positive current pulses.