# THE DESIGN OF A NEW SOLID STATE ELECTRONIC ITERATIVE DIFFERENTIAL ANALYZER MAKING MAXIMUM USE OF INTEGRATED CIRCUITS

by

Brian Kendall Conant

224FORM 602 (THRU) (CODE) FACILITY (CATEGORY OR TMX OR AD NUMBER)

A Dissertation Submitted to the Faculty of the

DEPARTMENT OF ELECTRICAL ENGINEERING

In Partial Fulfillment of the Requirements For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

1968

| <b>ADA</b> | DDICE | Ś |  |

|------------|-------|---|--|

CFSTI PRICE(S) \$ \_\_\_\_\_

Hard copy (HC)

Microfiche (MF) \_\_\_\_\_

ff 653 July 65

### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the major department or the Dean of the Graduate College when in his judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

SIGNED: Brian R. Conant

### ACKNOWLEDGMENTS

The hybrid computer described in this dissertation is part of the hybrid analog-digital studies at The University of Arizona directed by Professor Granino A. Korn. The writer is grateful to Professor Korn for his suggestion of the topic and his encouragement and guidance during the development of the new computer.

The writer is grateful to the following individuals and organizations:

The National Science Foundation (Grant GY-379 and Institutional Grant to The University of Arizona);

The National Aeronautics and Space Administration (Grant NsG-646);

Drs. David L. Patrick and Edward N. Wise, The University of Arizona Coordinators of Research (for allocating institutional grant funds);

Dr. George W. Howard, Director, The University of Arizona, Engineering Experiment Station; and

Dr. Howard S. Coleman, Dean of Engineering, and Dr. Roy H. Mattson, Head of Electrical Engineering Department, for their contribution of University funds and facilities.

iii

## TABLE OF CONTENTS

Page

| LIST OF IL | LUSTRATIONS                                   | vi |

|------------|-----------------------------------------------|----|

| LIST OF TA | BLES                                          | x  |

| ABSTRACT   |                                               | xi |

| Chapter 1  | INTRODUCTION                                  | 1  |

| 1.1        | Iterative Differential Analyzers              | 2  |

| 1.2        | Iterative Differential Analyzer Applications  | 5  |

| 1.3        | The Impact of Integrated Circuits             | 6  |

| 1.4        | APE II and LOCUST                             | 8  |

| T•4        |                                               | 0  |

| Chapter 2  | THE APE II SYSTEM                             | 12 |

| 2.1        | Packaging                                     | 14 |

| 2.2        | The Analog Module                             | 16 |

| 2.3        | The Digital Module                            | 21 |

| 2.4        | Digital Control of Analog Computer Operations | 22 |

| 2.5        | Operating Conditions                          | 27 |

| 2.5        |                                               | 29 |

|            |                                               |    |

| 2.7        | Discussion                                    | 31 |

| Chapter 3  | THE LOCUST SYSTEM                             | 33 |

| 3.1        | High-speed Computing Requirements             | 35 |

| 3.2        | LOCUST Integrator/Track-hold Module           | 38 |

| 3.3        | LOCUST Analog Patchbay System                 | 38 |

| 3.4        | Analog-patchpanel Layout                      | 46 |

| 3.5        |                                               | 49 |

| Chapter 4  | LOCUST ANALOG COMPUTING ELEMENTS              | 50 |

| aucheer 4  |                                               | 30 |

| 4.1        | The LOCUST Operational Amplifiers             | 51 |

| 4.2        | Integrator/Track-hold Circuit                 | 57 |

| 4.3        | Digital Attenuator System                     | 65 |

| 4.4        | Analog Multiplier/Divider                     | 70 |

| 4.5        | General-purpose Diode Function Generator      | 72 |

| 4.6        | Circle-test Performance                       | 72 |

## Table of Contents (Continued)

| Chapter 5  | LOCUST DIGITAL SYSTEM                                    | 76         |

|------------|----------------------------------------------------------|------------|

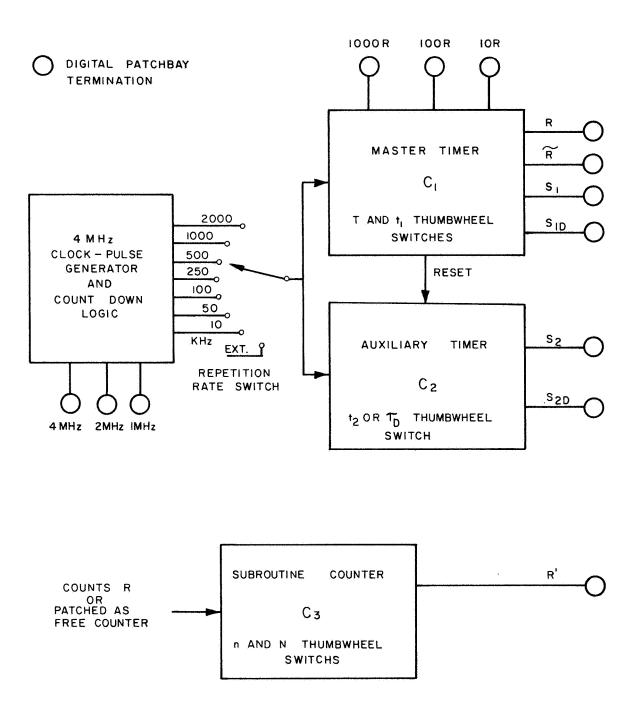

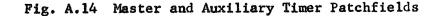

| 5.1        | Clock and Repetition-rate Selection                      | 80         |

| 5.2        | The Master Timer                                         | 83         |

| 5.3        | The Auxiliary Timer                                      | 84         |

| 5.4        | Subroutine Counter                                       | 86         |

| 5.5        |                                                          | 88         |

| Chapter 6  | SPECIAL COMPUTING ELEMENTS                               | 90         |

| 6.1        | Analog Comparator                                        | <b>9</b> 0 |

| 6.2        |                                                          | 91         |

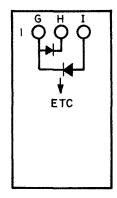

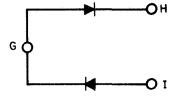

| 6.3        | Diode Bridge and Diode Pair                              | 96         |

| 6.4        |                                                          | 96         |

| 6.5        |                                                          | 99         |

| 6.6        | Multiplying D/A Converter                                | 104        |

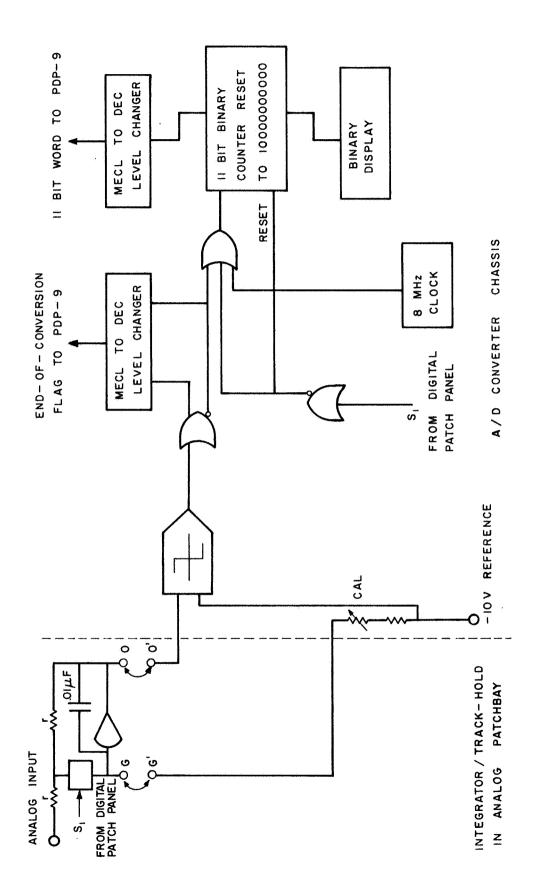

| 6.7        | Analog-to-digital Converter                              | 104        |

| 6.8        | LOCUST/PDP-9 Interface                                   | 108        |

| Chapter 7  | APPLICATIONS AND CONCLUSION                              | 109        |

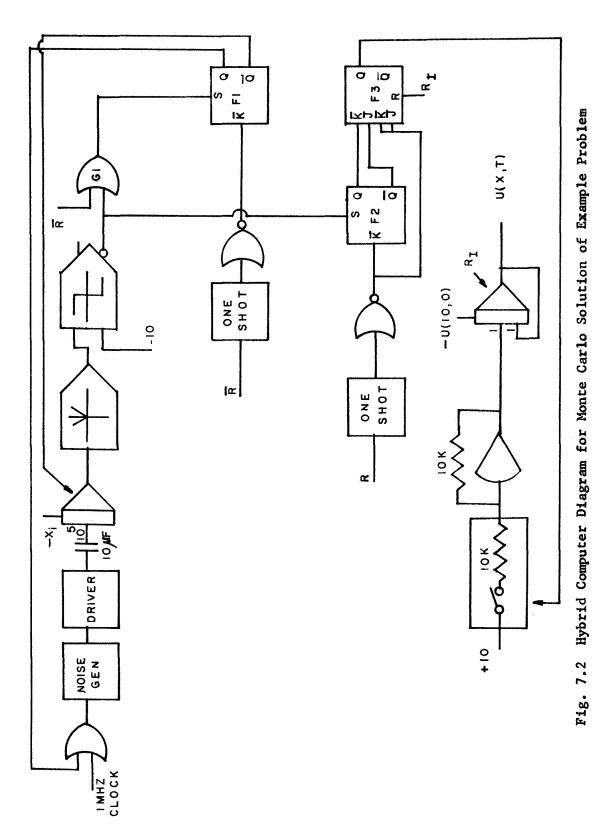

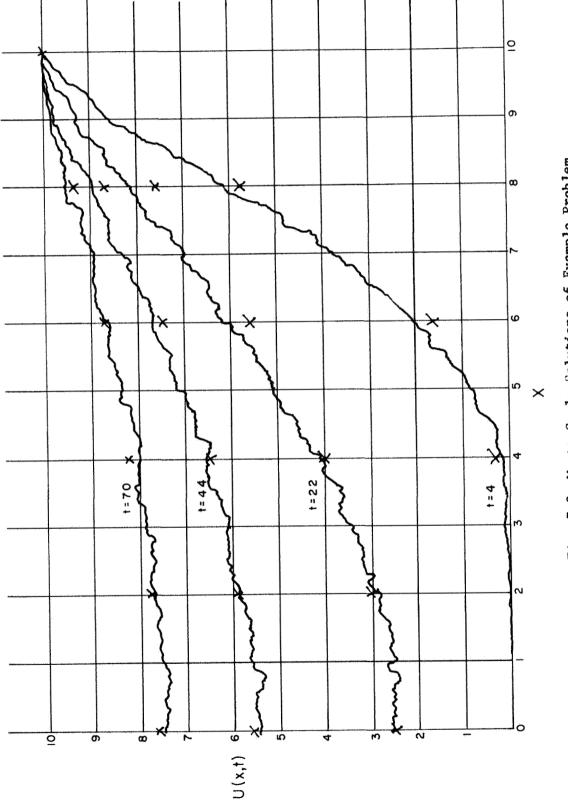

| 7.1        | Monte Carlo Solution of a Partial Differential Equation. | 109        |

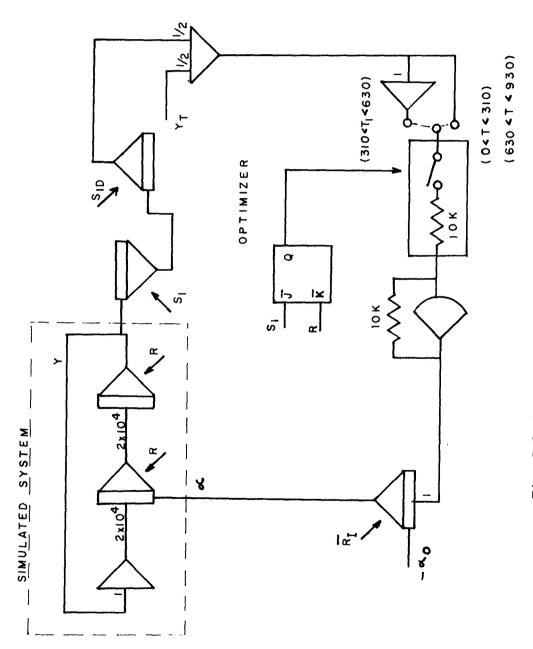

| 7.2        | Parameter Optimization                                   | 115        |

| 7.3        | Conclusions                                              | 118        |

| APPENDIX   |                                                          | 120        |

| REFERENCES | 8                                                        | 162        |

v

Page

## LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                                                | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Iterative-differential Analyzer System                                                                                                                                         | 4    |

| 2.1    | APE II Front Panel                                                                                                                                                             | 13   |

| 2,2    | APE II Packaging System                                                                                                                                                        | 17   |

| 2.3    | Ground planes on one side of double-sided printed circuit<br>boards serve as a shield between cards                                                                            | 18   |

| 2.4    | Specially fabricated taper pins permit direct plug-in connections to the rear of the patchbay                                                                                  | 19   |

| 2.5    | APE II Switched-Integrator/Summer Module                                                                                                                                       | 20   |

| 2.6    | Block Diagram of APE II Control Unit                                                                                                                                           | 23   |

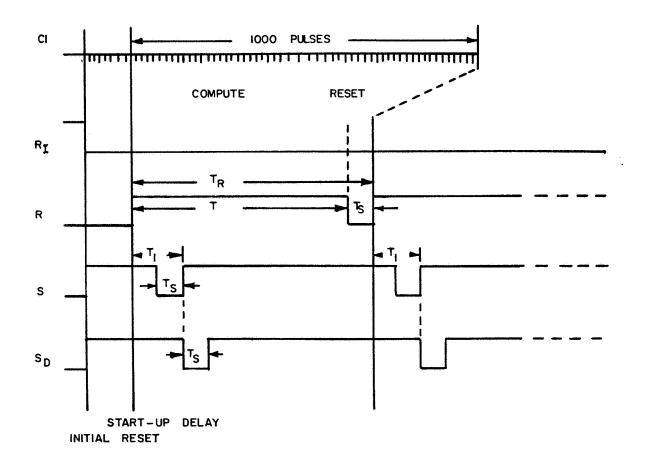

| 2.7    | APE II Timing Diagram                                                                                                                                                          | 25   |

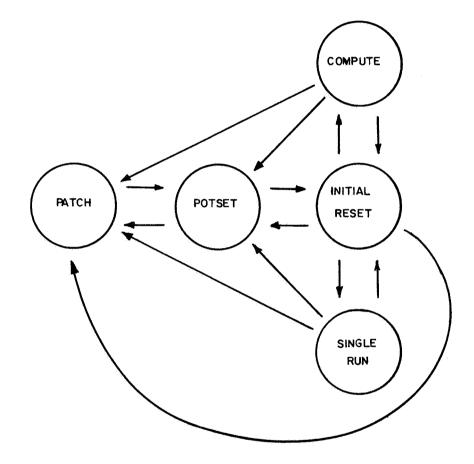

| 2.8    | Pushbutton Control State-diagram                                                                                                                                               | 26   |

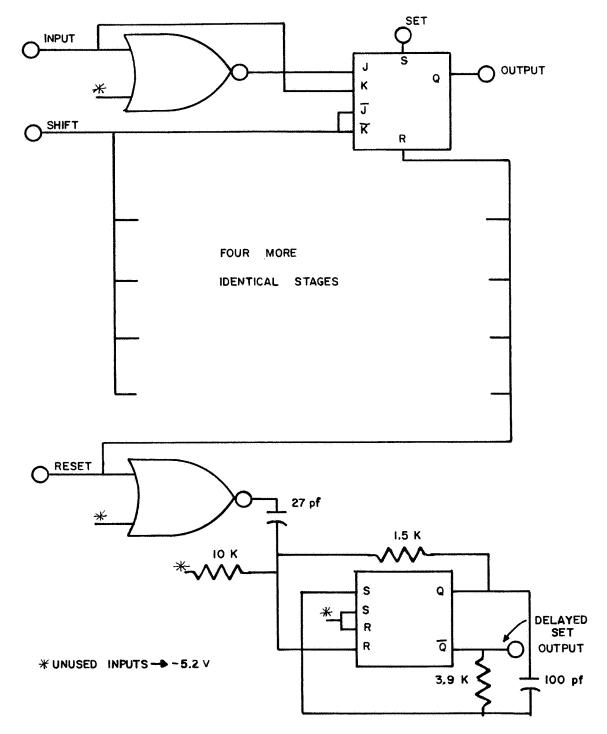

| 2.9    | APE II Shift Register Card Schematic                                                                                                                                           | 30   |

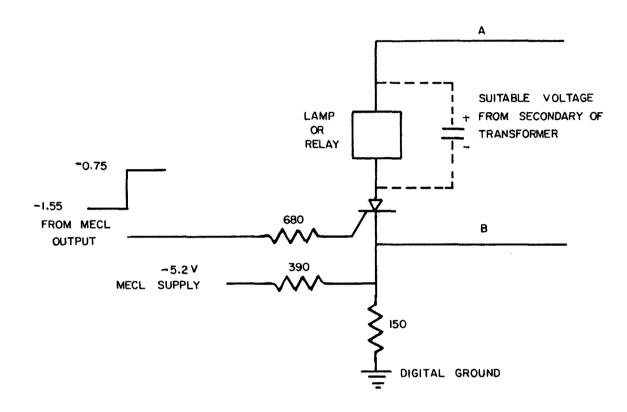

| 2.10   | Indicator Lamp and Relay Driver Circuit                                                                                                                                        | 32   |

| 3.1    | The LOCUST System                                                                                                                                                              | 34   |

| 3.2    | Block Diagram of LOCUST Integrator/Track-hold Module                                                                                                                           | 39   |

| 3.3    | Patchbay capacitances between inputs cause gain errors                                                                                                                         | 41   |

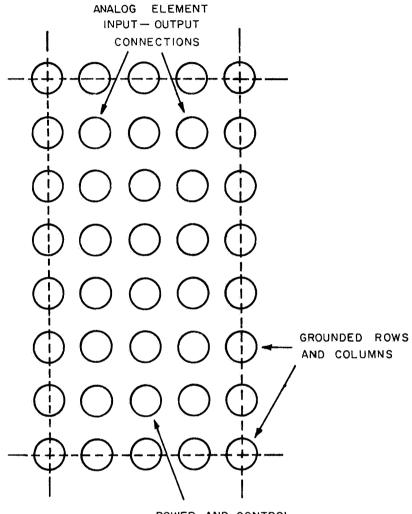

| 3.4    | Rows and columns of terminations provide shielding between<br>modules. Power-supply and logic-control wiring is made<br>directly to the patchbay receiver                      | 43   |

| 3.5    | LOCUST Analog Module Patchbay Field                                                                                                                                            | 44   |

| 3.6    | <ul> <li>(a) Analog elements are housed in aluminum cans and</li> <li>(b) plugged directly into the rear of the patchbay</li> <li>receiver and held by simple frames</li></ul> | . 45 |

| 3.7    | All aluminum patchboards are drilled only for the termina-<br>tions used and silkscreened and color-coded for<br>identification                                                | . 47 |

# List of Illustrations (Continued)

| Figure |                                                                                                                                                                                                                                    | Page       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

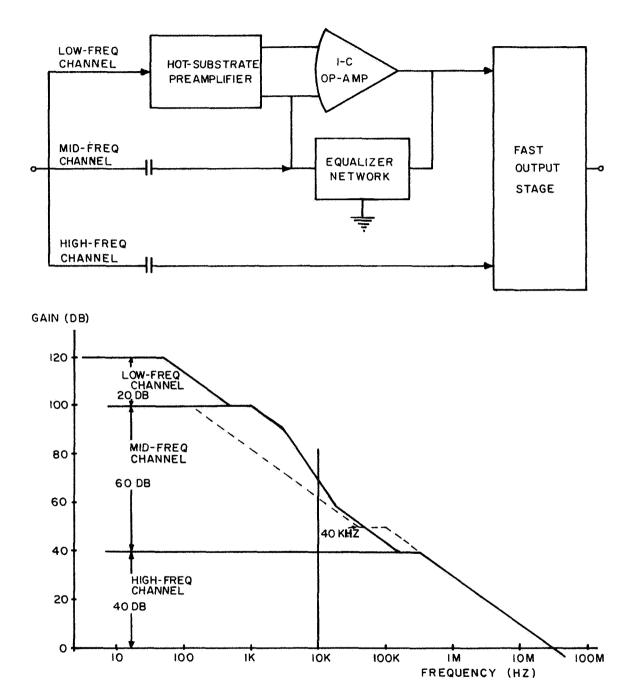

| 4.1    | <ul><li>(a) Block diagram showing signal flow through the three channels.</li><li>(b) Open-loop Bode plot of the three channels and their combination</li></ul>                                                                    | 52         |

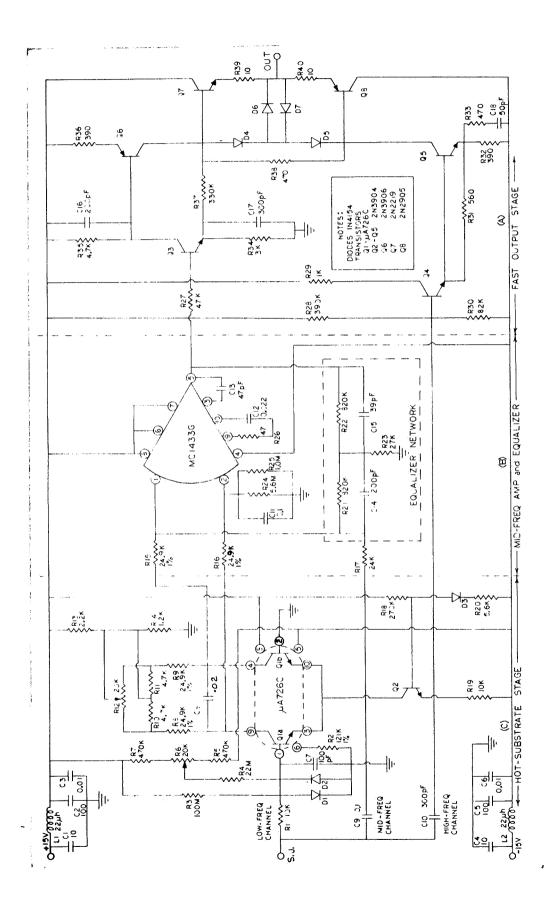

| 4.2    | Circuit Diagram of the Computer d-c Amplifier                                                                                                                                                                                      | 54         |

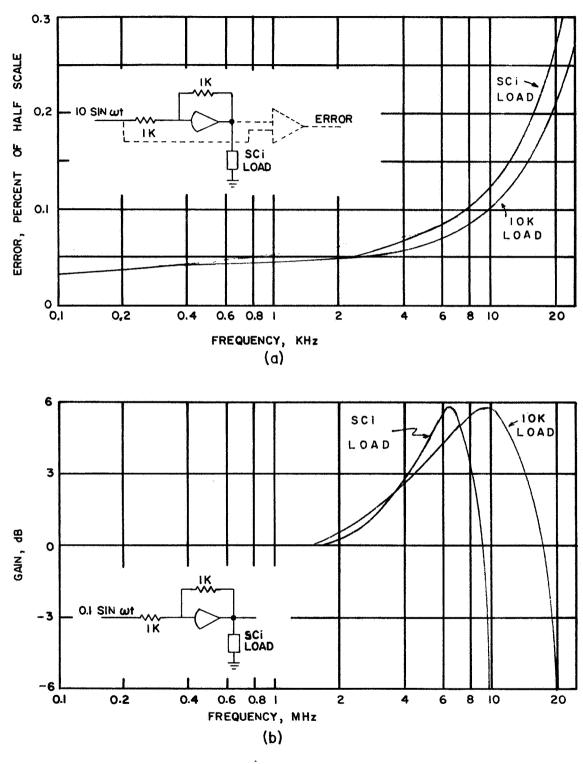

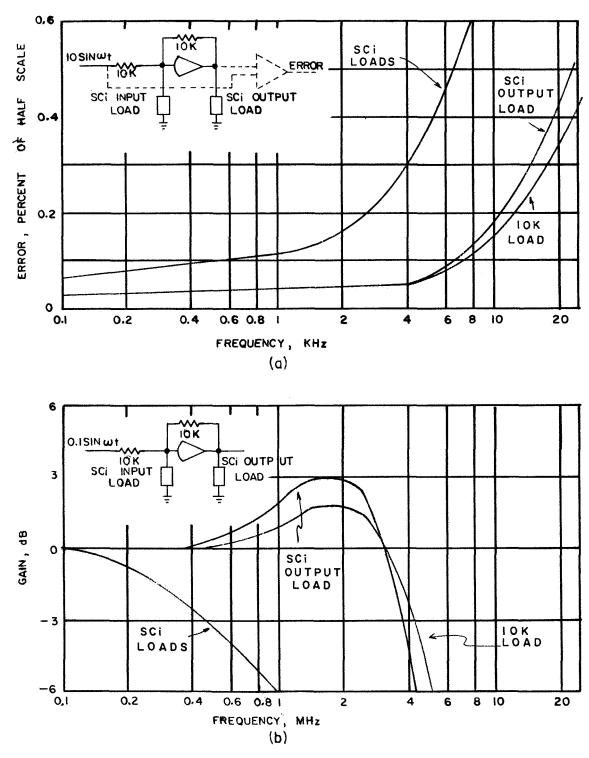

| 4.3    | (a) Unity-gain Phase-inverter Response (1 k $\Omega$ input and feedback resistors) (b) Small-signal Frequency Response                                                                                                             | 55         |

| 4.4    | (a) Unity-gain Phase-inverter Response (10 k $\Omega$ input and feedback resistors) (b) Small-signal Frequency Response                                                                                                            | 56         |

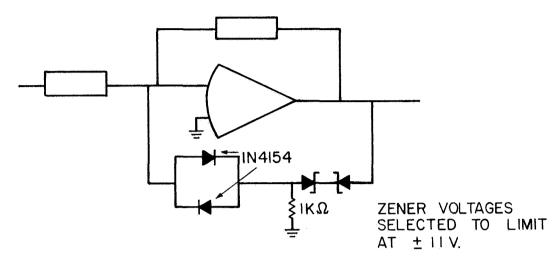

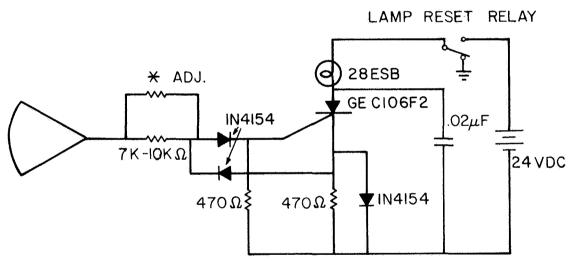

| 4.5    | (a) LOCUST High-speed Limiter Circuit and (b) new<br>LOCUST Overload-indicator Circuit                                                                                                                                             | 58         |

| 4.6    | LOCUST Integrator/Track-hold Circuit Schematic Diagram                                                                                                                                                                             | 60         |

| 4.7    | New LOCUST FET Input-stage Electronic Mode-control Switch<br>Schematic Diagram                                                                                                                                                     | 61         |

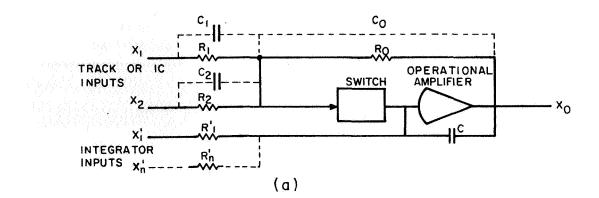

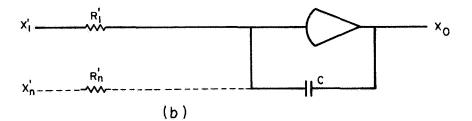

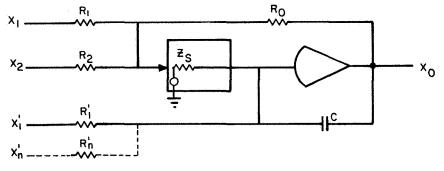

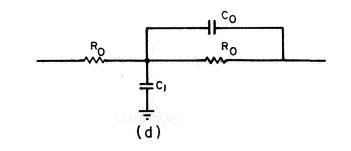

| 4.8    | <ul> <li>(a) Integrator/Track-hold Circuit (b) Equivalent Circuit</li> <li>in HOLD or COMPUTE (c) Equivalent Circuit in TRACK or RESET</li> <li>(d) Modified Feedback Network Replacing Impedance R<sub>0</sub> of (a).</li> </ul> | 62         |

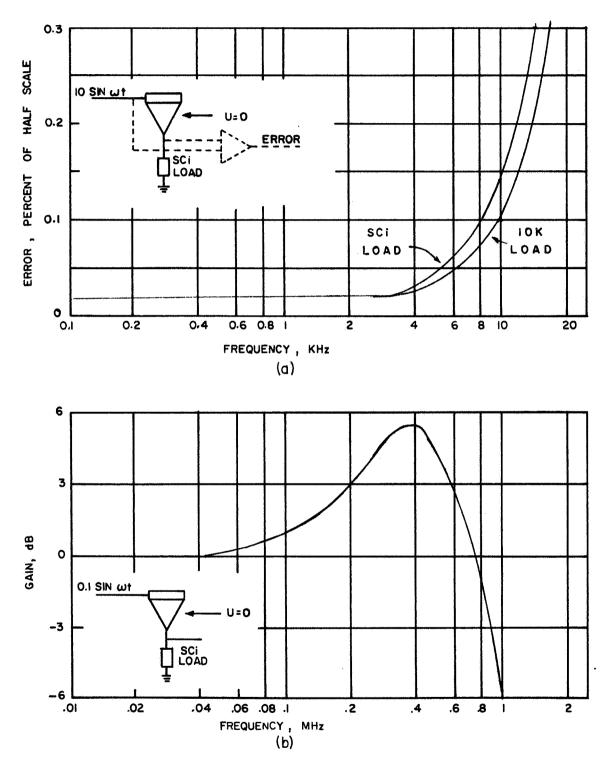

| 4.9    | <ul> <li>(a) Tracking Error of the Integrator/Track-hold Circuit</li> <li>(b) Small-signal Frequency Response in TRACK</li></ul>                                                                                                   | <b>6</b> 6 |

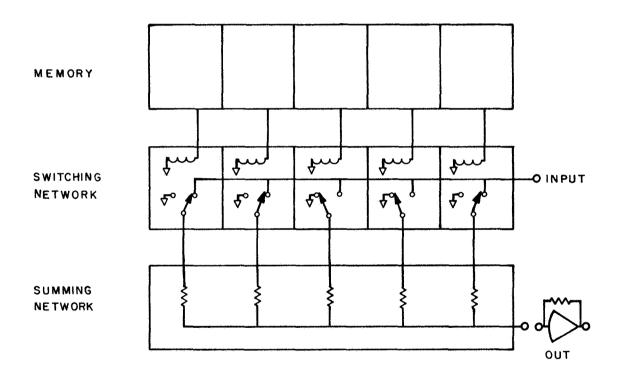

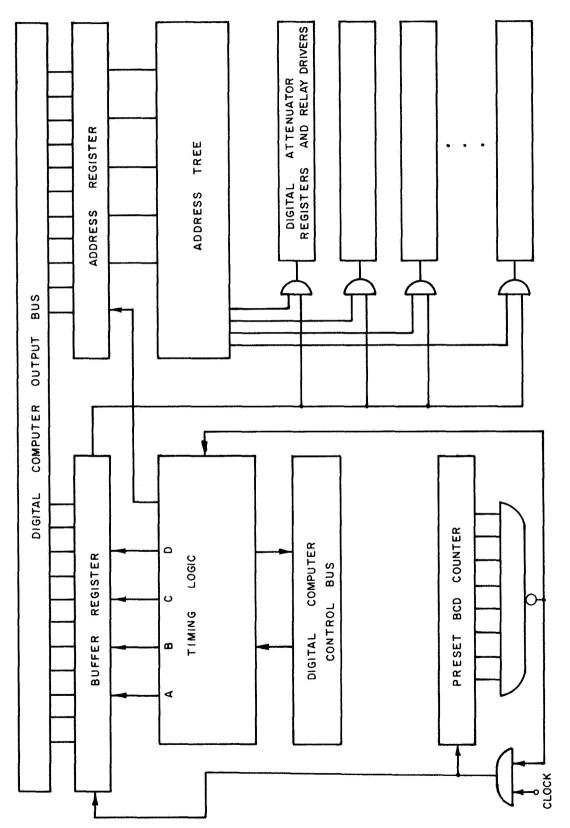

| 4.10   | A Typical Digital Attenuator                                                                                                                                                                                                       | 67         |

| 4.11   | LOCUST Digital Attenuator Control Block Diagram                                                                                                                                                                                    | 69         |

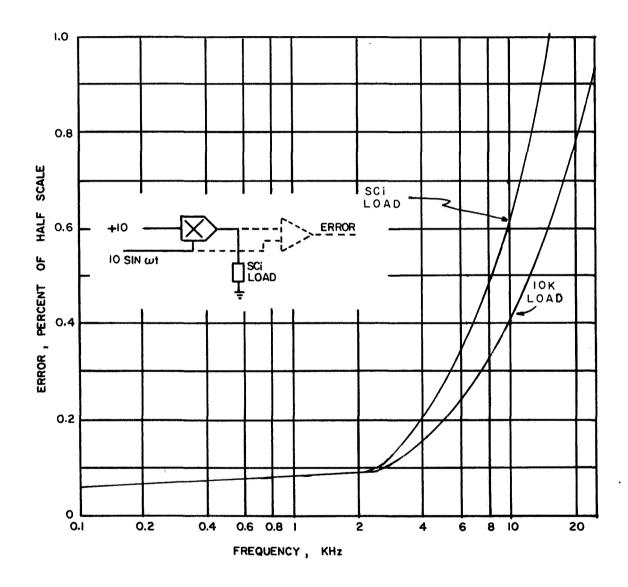

| 4.12   | LOCUST Multiplier Performance                                                                                                                                                                                                      | 71         |

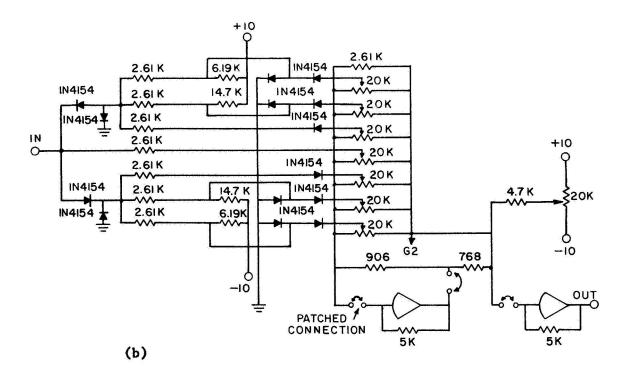

| 4.13   | (a) LOCUST Plug-in Diode Function Generator and (b) its<br>Schematic Diagram                                                                                                                                                       | 73         |

| 4.14   | Circle Test Data                                                                                                                                                                                                                   | 75         |

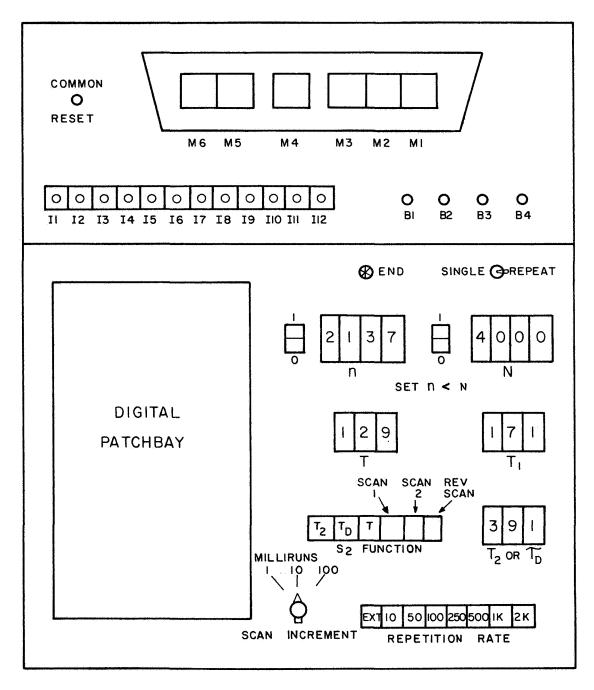

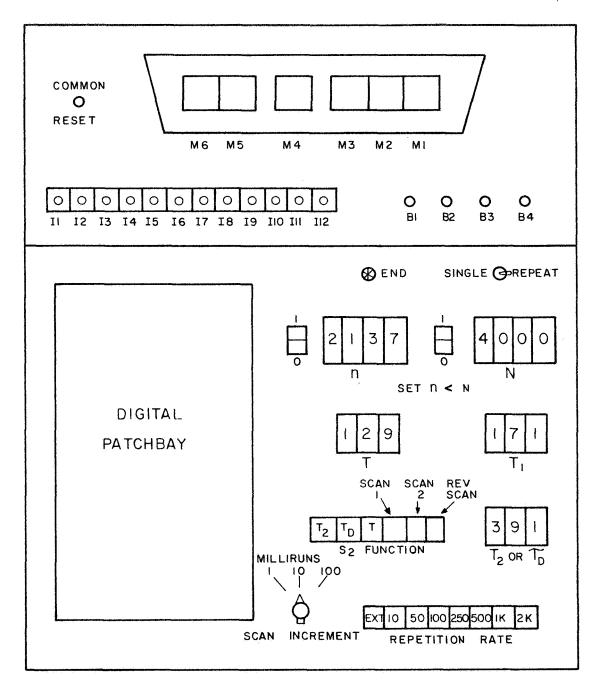

| 5.1    | The LOCUST Digital Control Module                                                                                                                                                                                                  | 77         |

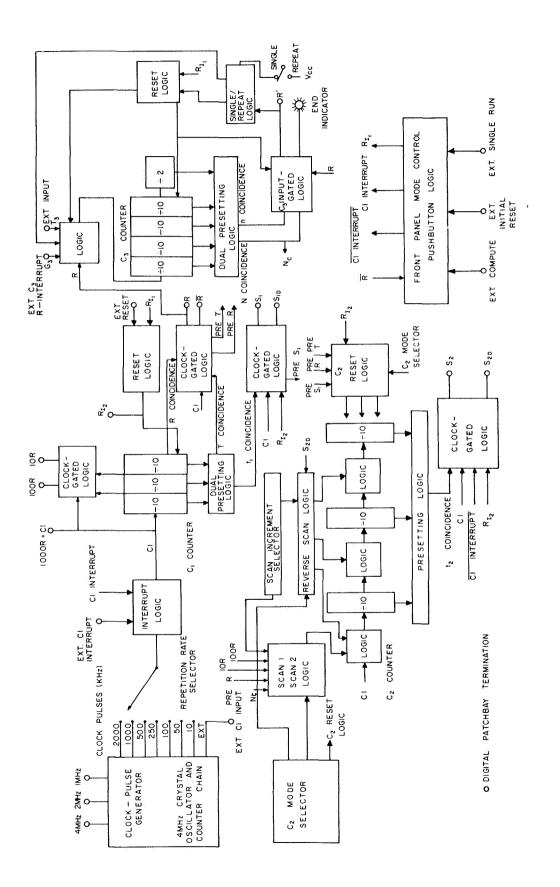

| 5.2    | Block Diagram of the LOCUST Digital Control System                                                                                                                                                                                 | 81         |

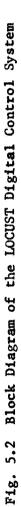

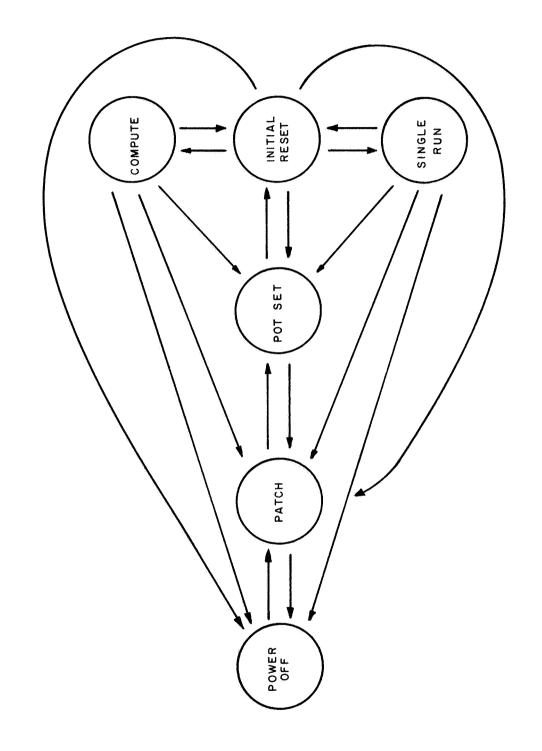

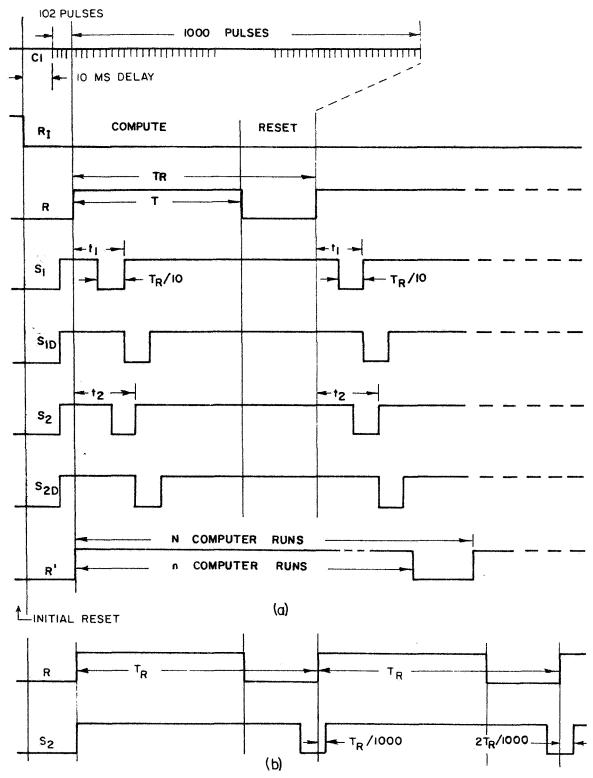

| 5.3    | (a) Timing and Control Signals for Normal Repetitive<br>Operation and (b) Control Signals for SCAN 1 Operation                                                                                                                     | 82         |

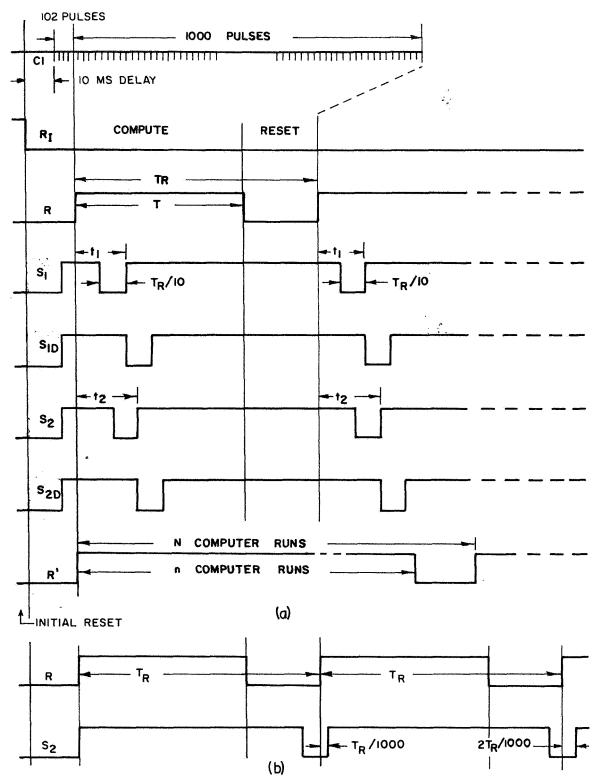

| 5.4    | Random Process Simulation                                                                                                                                                                                                          | 87         |

# List of Illustrations (Continued)

| Figure | I                                                                                                              | Page |

|--------|----------------------------------------------------------------------------------------------------------------|------|

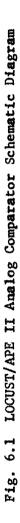

| 6.1    | LOCUST/APE II Analog Comparator Schematic Diagram                                                              | 93   |

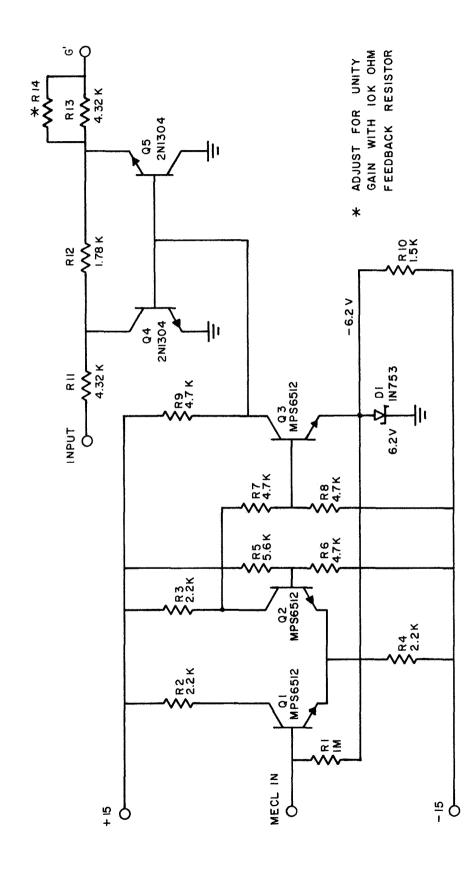

| 6.2    | D/A Dual-transistor Shunt Switch Schematic Diagram                                                             | 94   |

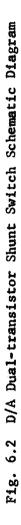

| 6.3    | (a) D/A Switch Dynamic Error (ON state) and (b) Feed-<br>through Error (OFF state)                             | 95   |

| 6.4    | Logic-controlled Relay Switch Schematic Diagram                                                                | 97   |

| 6.5    | LOCUST 6-stage Shift Register Schematic Diagram                                                                | 98   |

| 6.6    | Sampling-type Binary Random-sequence Generator                                                                 | 100  |

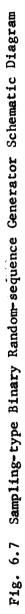

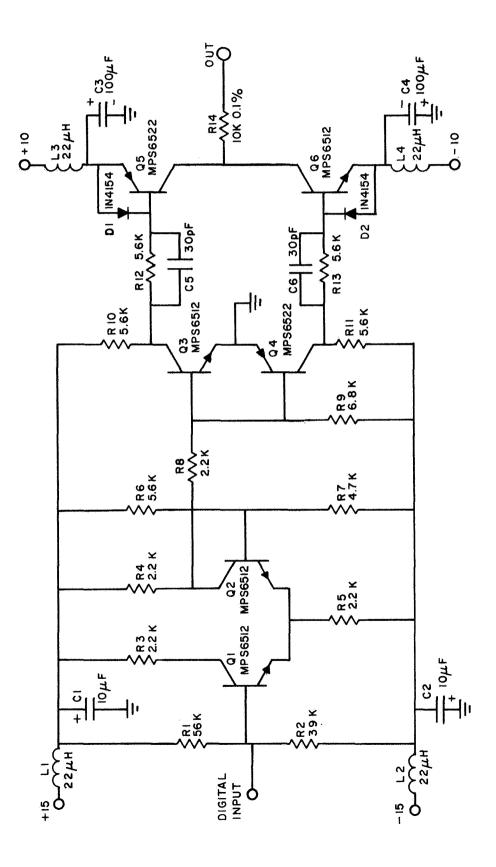

| 6.7    | Sampling-type Binary Random-sequence Generator Schematic<br>Diagram                                            | 101  |

| 6.8    | Noise Driver Schematic Diagram                                                                                 | 103  |

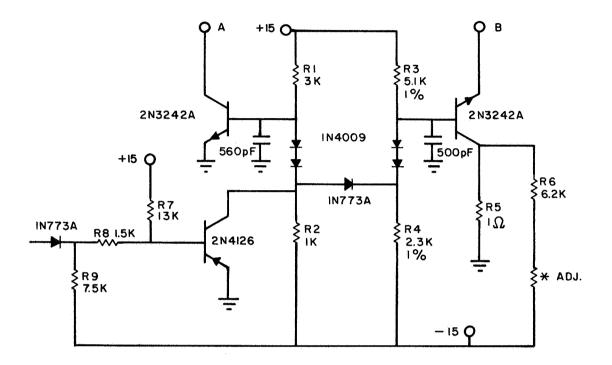

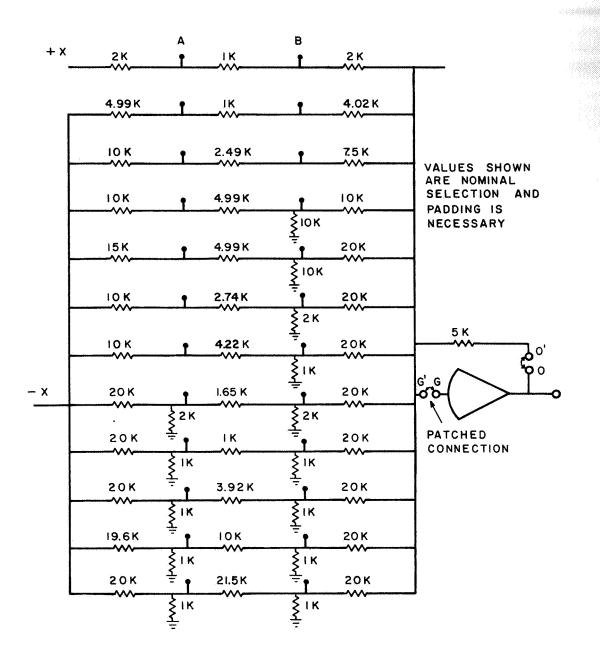

| 6.9    | D/A Multiplier Switch Schematic Diagram                                                                        | 105  |

| 6,10   | 12-bit D/A Multiplier Resistor Network                                                                         | 106  |

| 6.11   | A/D Converter Block Diagram                                                                                    | 107  |

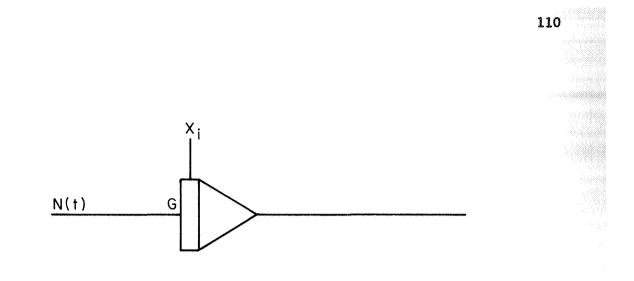

| 7.1    | A Markov Process Generated by Excitation of a First-order<br>System with White Gaussian Noise                  | 110  |

| 7.2    | Hybrid Computer Diagram for Monte Carlo Solution of                                                            | 114  |

|        | Example Problem                                                                                                |      |

| 7.3    | Monte Carlo Solutions of Example Problem                                                                       | 116  |

| 7.4    | Hybrid Computer Diagram for Parameter Optimization Problem .                                                   | 117  |

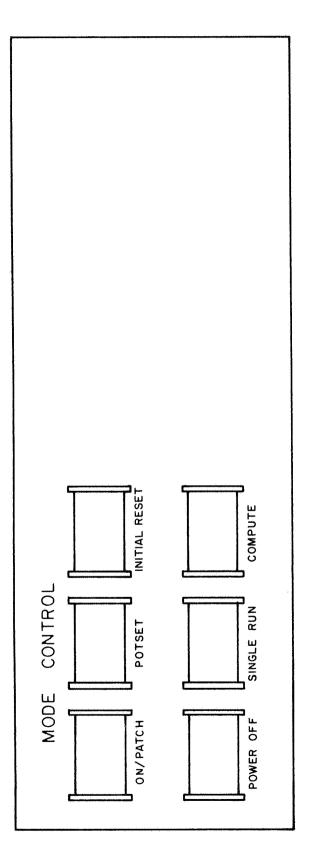

| A.1    | LOCUST Mode Control Panel                                                                                      | 121  |

| A.2    | Mode Control Logic State Diagram                                                                               | 122  |

| A.3    | (a) Timing and Control Signals for Normal Repetitive<br>Operation and (b) Control Signals for SCAN 1 Operation | 125  |

| A.4    | LOCUST Digital Control Module                                                                                  | 127  |

| A.5    | Simplified Block Diagram of LOCUST Digital Control Timers                                                      | 128  |

# List of Illustrations (Continued)

| Figure | ·                                                                                                                                                                | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

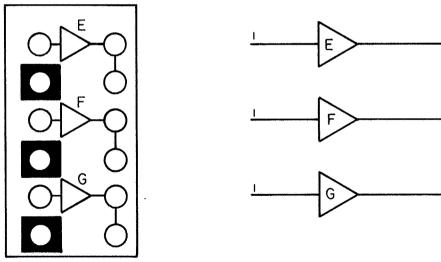

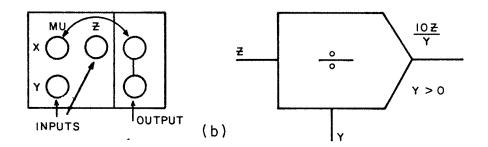

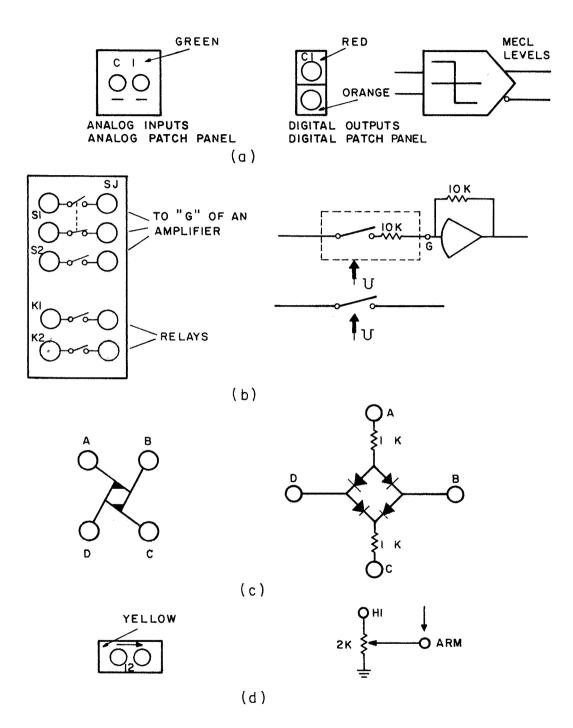

| A.6    | (a) Integrator/Track-hold Patchfields (b) Digital Patch-<br>panel Patching                                                                                       | 133  |

| A.7    | LOCUST Integrator/Track-hold Circuit Schematic Diagram                                                                                                           | 135  |

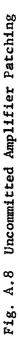

| A.8    | Uncommitted Amplifier Patching                                                                                                                                   | 137  |

| A.9    | (a) 2-input Dual Amplifier Patching (b) Phase Inverter<br>Patching                                                                                               | 138  |

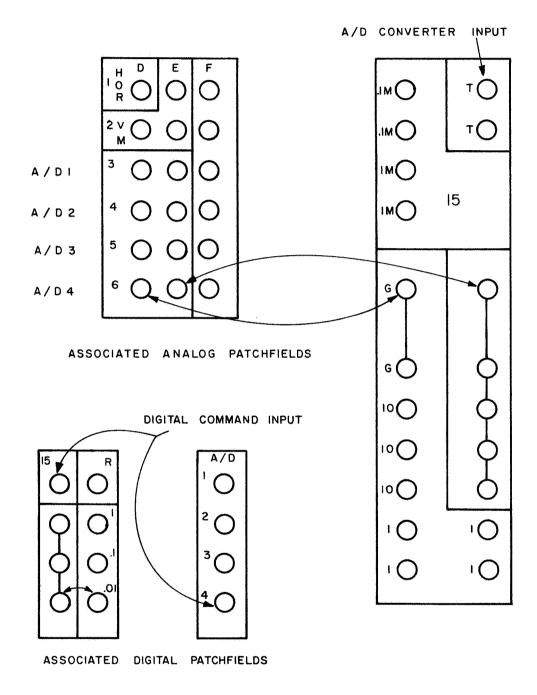

| A.10   | A/D Converter Patching                                                                                                                                           | 139  |

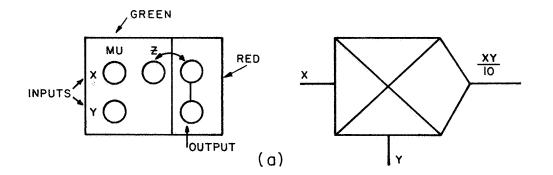

| A.11   | <ul> <li>(a) Analog Multiplier Patching (b) Analog Divider Patching</li> <li>(c) Sine-Function Generator Patching (d) D/A Multiplier</li> <li>Patching</li></ul> | 141  |

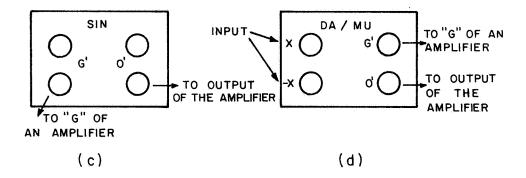

| A.12   | <ul> <li>(a) Analog Comparator Patching (b) D/A Electronic Switch</li> <li>Patching (c) Diode Bridge Patching (d) Potentiometer</li> <li>Patching</li></ul>      | 143  |

| A.13   | (a) Noise Driver Patching (b) Free Diode Patching                                                                                                                | 145  |

| A.14   | Master and Auxiliary Timer Patchfields                                                                                                                           | 147  |

| A.15   | External Control and Subroutine Counter Patchfields                                                                                                              | 148  |

| A.16   | Shift Register and Modulo-2 Adder Patchfields                                                                                                                    | 150  |

| A.17   | Pseudo-random Noise Generator Block Diagram                                                                                                                      | 151  |

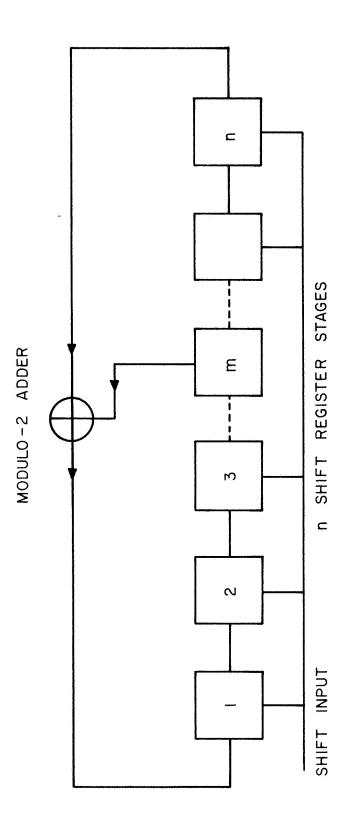

| A.18   | <ul> <li>(a) J-K Flip-flop Patchfield</li> <li>(b) 3-input Gate Patchfield</li> <li>(c) 4-input Gate Patchfield</li> <li></li></ul>                              | 154  |

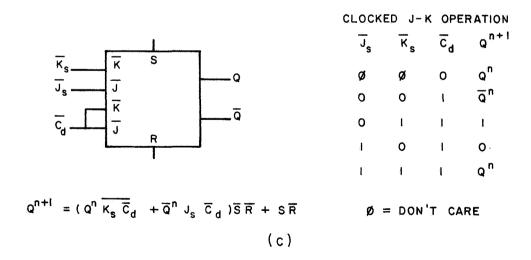

| A.19   | Flip-flop Operation (a) D-c Set and Reset Operation<br>(b) Toggle Operation (c) Clocked J-K Operation                                                            | 156  |

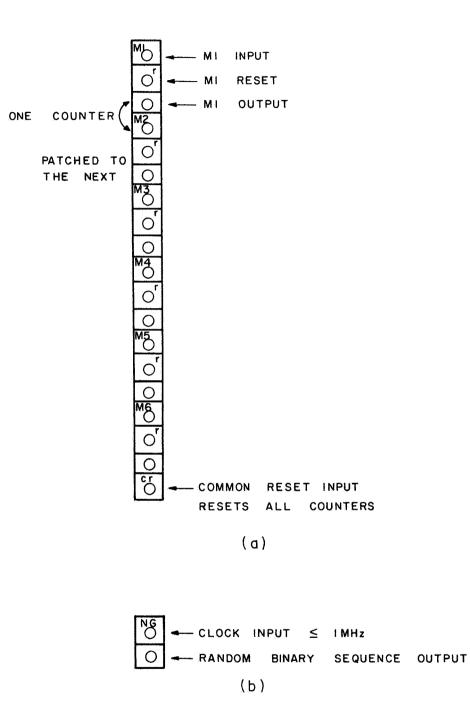

| A.20   | (a) Readout Counter Patchfield (b) Sampling-type Noise<br>Generator Patchfield                                                                                   | 158  |

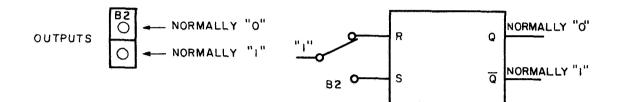

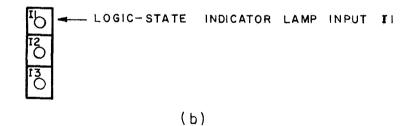

| A.21   | (a) Manual Pushbutton Patchfield (b) Logic-state Indicator<br>Inputs                                                                                             | 161  |

## LIST OF TABLES

| Tab le |                                                    | Page  |

|--------|----------------------------------------------------|-------|

| 1.1    | Student Contributions to APE II and LOCUST         | . 2   |

| 1.2    | Comparative Computer Specifications                | . 10  |

| 2.1    | Suggested APE II Experiments                       | . 15  |

| 3.1    | LOCUST System Equipment Complement                 | . 36  |

| 4.1    | LOCUST d-c Amplifier Performance                   | . 53  |

| 4.2    | LOCUST Integrator/Track-hold Circuit Performance   | . 63  |

| 4.3    | Digital Attenuator Specifications                  | . 68  |

| 4.4    | Multiplier/Divider Specifications                  | . 70  |

| 5.1    | LOCUST Digital System Logic Cards                  | . 78  |

| 6.1    | Analog Comparator Performance Specifications       | . 92  |

| A.1    | Pseudo-random Noise Generator Feedback Connections | . 152 |

| A.2    | LOCUST Flip-flop Truth Table                       | . 153 |

### ABSTRACT

This dissertation describes the third generation of high-speed iterative differential analyzer systems designed and built in the Analog/Hybrid Computer Laboratory at The University of Arizona. The APE II system, a new hybrid computer for laboratory instruction, served as a test vehicle for new shielding and packaging techniques and the use of current-mode integrated-circuit logic for digital control of computer operations.

LOCUST, an all-solid-state iterative differential analyzer employs  $\pm$  10-V, 30-mA amplifiers with 30 MHz unity-gain bandwidth and can operate at iteration rates as high as 2,000 analog computer runs per second as well as in real time. Computing elements are plugged directly into the rear of a modified inexpensive patchbay which has removable patchboards. Subroutines are controlled by a flexible digital control unit as well as by patched digital logic or by an associated digital computer. New linear and digital monolithic integrated circuits along with a novel patchbay shielding system and computing-element packaging techniques have enhanced computer performance and reduced costs.

This description of the LOCUST system includes performance data, circuit diagrams, examples of applications and an instruction manual.

хi

### Chapter 1

### INTRODUCTION

This dissertation describes the design and development of a "third generation" of iterative differential analyzers at the Analog/ Hybrid Computer Laboratory of The University of Arizona. These computers include the APE (Arizona PEdagogical) II system, a small solid state iterative computer for laboratory instruction and the LOCUST (LOw CoST) system, a larger, more sophisticated iterative differential analyzer; both employ integrated circuits.

It is the purpose of the Analog/Hybrid Computer Laboratory to provide students with engineering experience related to their academic work and yet comparable to industrial experience. In accordance with this policy, the writer, as part of his Ph.D. research assignment, coordinated and supervised the development of these two computer systems, which draw on the experience of numerous graduate M.S. theses and student term-paper projects. The M.S. theses and term papers which contributed directly to the APE II and LOCUST projects are listed in Table 1.1. The writer acted as project engineer, under the direction of Professor G. A. Korn, with responsibility for design, construction and testing for the LOCUST system and for much of the APE II project, the supervision of student technicians and of student projects. In addition, a maintenance manual and an instruction manual were prepared.

1

### Table 1.1

Student Contributions to APE II and LOCUST

| Naylor, J. R.,  | "A New High Performance Computer D-C Amplifier,"<br>M.S. Thesis, 1967.                              |

|-----------------|-----------------------------------------------------------------------------------------------------|

| Shick, L.,      | "A Simplified Dual-slope Digital Voltmeter,"<br>M.S. Thesis, 1968.                                  |

| Pracht, C. P.,  | "A New Digital Attenuator System for Hybrid<br>Computers," M.S. Thesis, 1967.                       |

| Belt, J.,       | "An Integrated-circuit Binary Noise Source,"<br>Term paper, 1968.                                   |

| Goltz, J. R.,   | "A New Low-cost Analog-to-digital Converter for<br>Hybrid Computers," Special course project, 1968. |

| Mueller, J. D., | "An Overload Circuit for Iterative Differential<br>Analyzers," Honors project, 1967.                |

### 1.1 Iterative Differential Analyzers

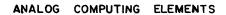

An analog computer with integrator-mode and program switches controlled by sequence-controlling digital clocks, analog-comparator outputs, and/or other digital logic is called an <u>iterative differential</u> <u>analyzer</u> (Eckes and Korn, 1964). Such machines can automatically perform successive analog computer runs utilizing stored results of previous runs and can, therefore, implement iterative computations converging to a desired solution. The automatic programming features have many other applications as well (Korn and Korn, 1964).

Iterative differential analyzers are programmed through a series of subroutines, such as an analog computer run or a number of repetitiveanalog-computer runs. Each subroutine is controlled by its associated digital control variable  $U_i$  (Fig. 1.1). The subroutine proceeds when  $U_i = 1$ ;  $U_i = 0$  "resets" the computing elements (e.g., integrators, counters) for a new subroutine sequence. Note that  $\overline{U}_i$ , the logical complement of  $U_i$ , may also define a subroutine. Subroutines may be "nested", i.e., a subroutine may have component subroutines; branching and loops are possible.

Typical analog-subroutine changes are combinations of the following operations:

- Switching a group of integrators from RESET to COMPUTE, or from RESET (TRACK) to HOLD.

- Switching to new values of parameters or to new initial conditions (e.g., parameter optimization, automatic scale factor changes).

- 3. Switching interconnections to produce computer-setup changes. Subroutines begin and terminate when their corresponding control variables change state as logical functions of (1) external control (switches and/or relays controlled by external devices), (2) the states of timers or event counters, and (3) analog-comparator decisions. Boolean functions of such control inputs are implemented by patched digital logic, or by an associated digital computer.

The interplay of analog and digital variables gives the computer its hybrid structure. Relays, electronic mode-control switches, D/A switches, D/A and A/D converters and analog comparators are the interface elements of the system.

O CONTROL PATCHBAY TERMINATION

# Fig. 1.1 Iterative-differential Analyzer System

The high-speed iterative differential analyzer and the small general purpose digital computer are particularly well suited to operate together (Korn, 1966a). Since most analog-to-digital and digital-toanalog exchanges between the two occur only once or twice per analogcomputer iteration, the digital computer has ample time to perform many logical and computational operations (e.g., memory storage, function generation, statistical computation). The digital computer may also provide timing and mode-control functions and perform housekeeping functions such as setting potentiometers (in modern computers, digital attenuators) and static checks.

### 1.2 Iterative Differential Analyzer Applications

High-speed iterative differential analyzers can implement much more sophisticated models than ordinary analog computers and at the same time still retain much of the intuitive appeal of the familar "slow" analog computer.

The iterative differential analyzer is particularly well suited to the following applications:

- Iterative parameter optimization (Maybach, 1966). The computer varies parameters of a simulated system to improve some performance criterion measured and/or computed in successive computer runs.

- Monte Carlo studies of random processes (Handler, 1967). The computer computes statistics over many computer runs at very fast repetition rates simulating systems with random inputs.

3. Simulation of sampled-data systems. High-speed integrator mode switches and D/A switches with convenient patchable digital control logic permit the simulation of various sampling and data-reconstruction schemes.

High-speed repetitive analog computation is a necessity for Monte Carlo and parameter-optimization studies if computation is to be completed in a reasonable amount of time. An additional feature is that the operator receives practically immediate feedback of the effects of system parameter changes on statistics, and automatic optimization of statistics is possible (Korn, 1966b).

Other interesting applications include:

- 4. Automatic sequencing of computations for plotting families of curves, special displays, etc.

- Introduction of artificial errors into alternate computer runs for purposes of error analysis, sensitivity studies, etc. (0'Grady, 1967).

- 6. Automatic scale-factor changes.

- 7. Special simulation and data processing circuits, e.g., patchbayassembled time-division and sampling multipliers, sampled-datareconstruction units, digital voltmeters, special function generators, etc.

### 1.3 The Impact of Integrated Circuits

The impact of integrated circuits on the design, performance and cost of iterative differential analyzers has been great. Reductions in size and cost afforded by integrated circuits have made it possible to design truly producible high-speed iterative differential analyzers at moderate cost.

The digital control section of a hybrid computer has been most radically affected by integrated circuits. Integrated-circuit flipflops and gates have replaced discrete-component logic cards, resulting in a size reduction of an order of magnitude. Single logic cards now contain complete logic <u>functions</u> such as a master timer, auxiliary timer, subroutine counter, shift registers, binary noise sources and free logic. Small size allows these cards to be <u>plugged directly into the rear of</u> the digital patchbay system, reducing construction costs and eliminating long interconnections, which might radiate digital noise throughout the computer.

Digital integrated circuits, which are ten times faster than their older discrete counterparts, also reduce delay errors, an important consideration in high-speed iterative computers.

Parts costs have been reduced to one-third that of a discrete system by using fast emitter-coupled logic. Costs could be reduced even further if one were willing to accept the noise associated with larger logic-level swings and unbalanced-current operation of RTL, DTL, or TTL logic families.

The impact of integrated circuits on analog computing elements has been less dramatic than that on the digital elements, because the performance of integrated-circuit linear elements cannot yet match that of a discrete-component element. Both performance and cost can be improved, however, by <u>combinations</u> of linear integrated circuits and discrete components.

7

APE II and LOCUST analog comparators utilize commercial integrated-circuit comparators which have been provided with input circuit protection and output logic levels compatible with the digital control logic. These inexpensive analog comparators have only <u>one-tenth</u> the cost of comparable high-speed comparators made from wide-band operational amplifiers.

The LOCUST wide-band operational amplifier also includes two integrated circuit modules plus a discrete-component output stage. The conventional chopper stabilizer is replaced with a novel hot-substrate, integrated-circuit input stage, which provides much better drift performance than a high-quality non-chopper-stabilized amplifier. The midfrequency stage of the amplifier employs an integrated-circuit amplifier, which is an operational amplifier in its own right! Designing high performance amplifiers in this manner eliminates the problems of transistor matching necessary with totally discrete-component amplifiers.

In addition to reduced parts costs and improved performance, integrated circuits reduce construction costs of computer systems; there are by far fewer parts to mount, fewer connectors, less cabling and wiring and less cabinet space required. The cost of separately testing and hand-picking critical components such as input-stage matchedtransistor pairs is completely eliminated.

### 1.4 APE II and LOCUST

The feasibility of really high-speed hybrid computation with realistic accuracy (0.2 percent of half-scale component accuracies up

8

to 10 kHz) was demonstrated by the development and application of The University of Arizona's ASTRAC II (Eckes, 1967). As yet, no computer <u>commercially</u> available has the required mode-control switching speed and low-impedance computing networks. Most computers do not have the required amplifier bandwidth. Development of the APE II and LOCUST iterative differential analyzers was, then, undertaken with the specific objective of demonstrating the design of truly producible high-speed hybrid computers at moderate cost.

Several new design features are of special interest:

- Maximum use of both linear and digital monolithic integrated circuits enhances computer performance and still reduces parts and assembly costs.

- New techniques of mounting printed-circuit cards and shielded components directly to low-cost computer patchbays were developed, as was a new simple technique for shielding low cost unshielded patchbays.

- 3. Low level integrated-circuit, current-mode logic has practically eliminated digital noise in the analog computer.

- 4. The amplifier and mode-control switch designed for LOCUST were substantially improved by the use of new solid state devices.

Table 1.2 shows engineering data for the two new computers and compares them with ASTRAC II and with commercially available hybrid computers.

Chapter 2 contains a description of the APE II system. The LOCUST system design, which includes accuracy requirements, mechanical

| Table | 1.2 | Comparative | Computer | Specifications |

|-------|-----|-------------|----------|----------------|

|                                                  | Commercial<br>Computers<br>1967 | ASTRAC II<br>1965      | APE II<br>1967                    | LOCUST<br>1967                    |

|--------------------------------------------------|---------------------------------|------------------------|-----------------------------------|-----------------------------------|

| D-C AMPLIFIER (+10V)                             | . <del></del>                   |                        | **** #1 #*** #7*****              |                                   |

| Output Current                                   | 25-50 mA                        | 30 mA                  | 20 mA                             | 30 mA                             |

| Max. frequency for full output                   | 50 kHz                          | 1 MHz                  | 1 MHz                             | 5 MHz                             |

| Small-signal OdB<br>bandwidth (1V p-p)           | 100 kHz to<br>10 MHz            | 20 MHz                 | 20 MHz                            | 30 MHz                            |

| Drift vs. temp.                                  | 0.5µV/degC<br>0.05nA/degC*      | 10µV/degC<br>1nA/degC* | 10µV/degC<br>0.2nA at<br>25degC** | 2.5 μV/deg(<br>0.05nA/deg(        |

| INTEGRATOR/TRACK-HOL                             | D SWITCH                        |                        |                                   |                                   |

| Turn-off time                                    | 500 <b>-1</b> 000ns             | 80 ns                  | 200 ns                            | 40 ns                             |

| Differential<br>turn-off time                    | 125-250 ns <sup>µ</sup>         | 20 ns                  | 50 ns                             | 10 ns                             |

| Drift vs. temp.<br>(RESET/TRACK)                 | negligible                      | 50µV/degC<br>30nA/degC | 100µV/degC<br>10nA/degC           | 100µV/degC<br>1 nA at<br>25degC** |

| Drift Current<br>(COMPUTE/HOLD)                  | 0.5 to 0.1nA                    | 1 nA                   | 0.1 nA                            | 0.05 nA                           |

| Turn-off charge                                  | negligible                      | 50 pC                  | 50 pC                             | 10 pC                             |

| Max. frequency for full output                   | 10 kHz <sup>µ</sup>             | 50 kHz                 | 25 kHz                            | 40 kHz                            |

| Small-signal TRACK<br>error at 10 kHz            |                                 | 0.25%                  |                                   | 0.2%                              |

| MULTIPLIER                                       |                                 |                        |                                   |                                   |

| Static error (% of half scale)                   | 0.05                            | 0.1                    | 0.25                              | 0.25                              |

| Freq. for 0.5% of<br>half scale dynamic<br>error | 0.5-2 kHz                       | 10 kHz                 | 10 kHz                            | 10 kHz                            |

| *chopper stabilized                              | **doubles ev                    | ery 10 degC            | " estimated                       |                                   |

layout and shielding, patchbay system and costs, is discussed in Chapter

3. Chapter 4 contains a description of LOCUST analog computing elements, and Chapter 5 describes special-purpose computing elements.

Chapter 6 discusses the LOCUST digital system and digital control of iterative differential analyzers. Applications of the APE II and LOCUST systems are the subject of Chapter 7.

## Chapter 2

### THE APE II SYSTEM

In view of the increasing use of analog computers for teaching at the college sophomore level, a need has developed for introducing more sophisticated analog/hybrid computation and techniques into senior-level analog computer courses. At The University of Arizona, this need led to the development of the APE II (Arizona PEdagogical) system, a small solid state iterative differential analyzer designed for laboratory instruction.

The author carried out the design and development of the APE II digital control module (Conant, 1967) while the analog portion was designed by Professor G. A. Korn (Korn, 1967); the machine was built with the aid of undergraduate student technicians. The APE II system also served as a test vechicle for the digital techniques used in the larger and more advanced LOCUST system.

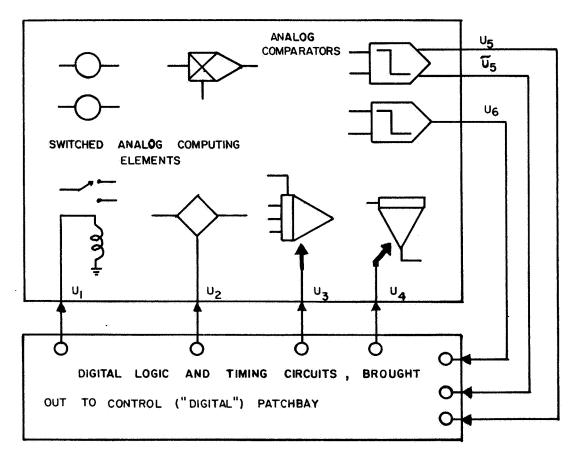

APE II (Fig. 2.1) is comprised of a twelve-amplifier analog computer with track-hold circuits and integrators permitting digital modecontrol and repetitive operation, analog comparators, multipliers, patchable zener-diode limiters and diode bridges. Removable patchboards permit problem storage and efficient machine utilization.

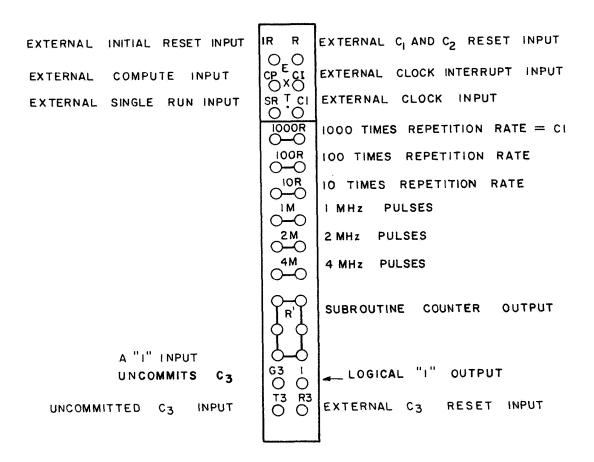

The APE II digital module contains free logic (gates and flipflops) as well as a flexible digital clock and counters capable of controlling analog subroutines. Shift-register modules and modulo-2

12

Fig. 2.1 APE II Front Panel

13

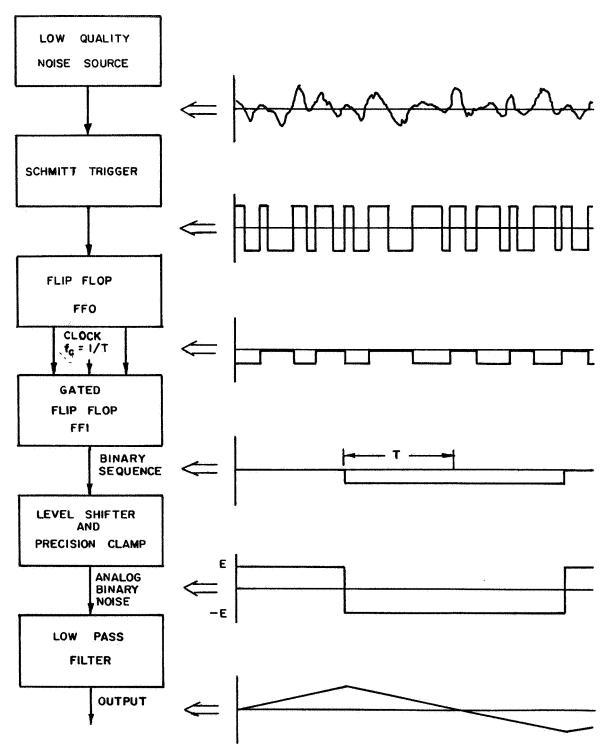

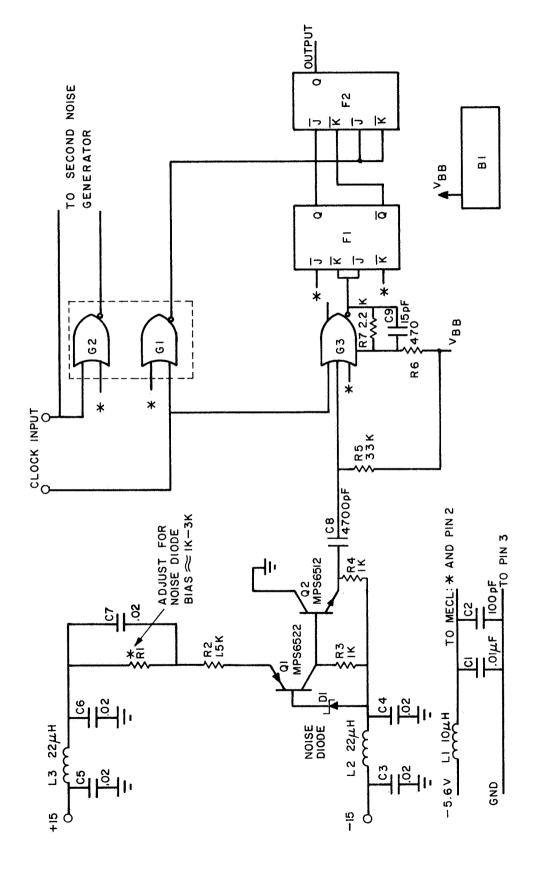

adders (exclusive OR circuits) permit generation of pseudo-random shift register sequences. A sampling-type noise generator provides a clocked digital noise source for Monte Carlo experiments.

These features, when combined with a novel packaging technique, result in a versatile hybrid computer permitting a wide variety of analog and hybrid experiments at minimum cost. A list of suggested APE II experiments is contained in Table 2.1 (Korn, 1967).

### 2.1 Packaging

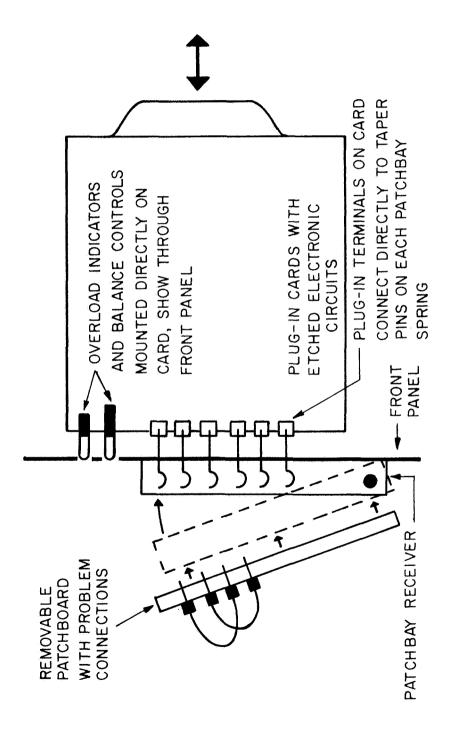

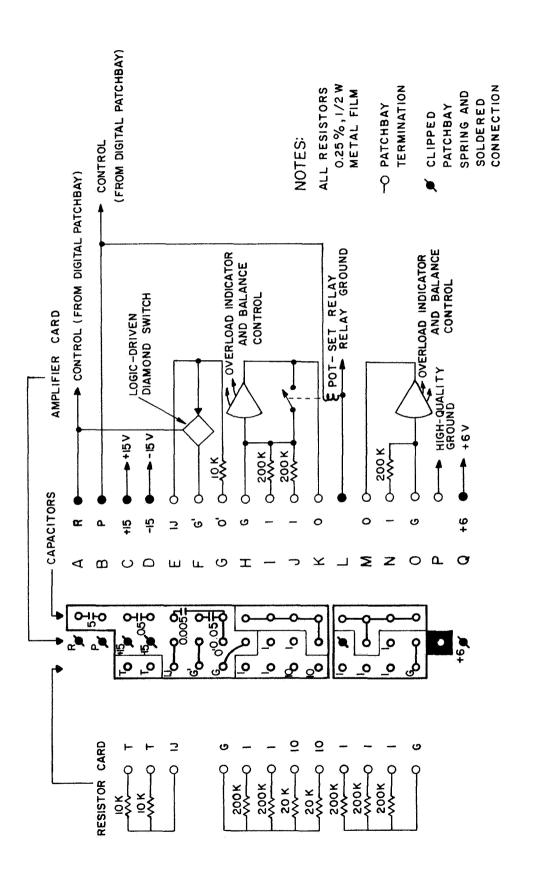

The APE II packaging design (Fig. 2.2) has done away with all signal and power-supply wiring to a card cage. The use of small transistor amplifiers and all-integrated circuit logic has made it possible to plug circuit cards directly into the rear of the inexpensive patchbay receivers. Ground planes on one side of the double-sided printed circuit cards (Fig. 2.3) serve as shields between adjacent cards (Korn, 1967).

Each amplifier card holds two  $\pm$  10-V, 20-mA transistor amplifiers with field-effect transistor input stages (Burr-Brown Model 9877), an electronic mode-control switch (Burr-Brown Model 9580), a potset relay, overload indicators and amplifier balance controls. Power-supply and logic inputs are supplied from the patchbay receiver, which furnishes all electrical connections to the cards. Similar cards hold summing resistors and other computing elements.

The same type of construction also accommodates all digital components in a separate patchbay receiver, with the exception of a set of in-line readout counters, and the front-panel pushbutton control logic.

### Simulation Techniques

- 1. Bouncing-ball Simulation Using Analog Memory

- 2. Study of Steepest-descent Optimization

- (a) Steepest-descent Division

- (b) Linear Regression by Steepest Descent

- (c) Simulation of a Simple Optimizing Servo

- 3. Solution of a Simple Problem in the Calculus of Variations Using Pontryagin's Maximum Principle

- 4. Solution of Difference Equations and Simulation of Digitaldifferential-analyzer Integration with Track-hold Circuits

- 5. Simulation of a Simple Sampled-data Control System

- 6. Automatic Solution of a Two-point Boundary-value Problem by Iteration

- 7. Computation of Parameter-influence Coefficients (Solution of Sensitivity Equations)

- 8. Computation of a Satellite Trajectory of a Simple Perturbation Method

- 9. A Simple Model-matching Experiment

- 10. Study of a Maximum-effort Servo

### Hybrid-computer Hardware Techniques

- 1. Study of Fast Diode Circuits and Precision Limiters

- 2. Study of a Simple Analog-to-digital Converter

- 3. Accurate Signal Generators and Pulse-width Modulators

- 4. Study of Track-hold Operation and First-order Hold Circuits

- 5. Simulation of Combined Analog-digital Computation Error Compensation

Statistical Measurements and Communication/Detection System Simulation

- 1. Statistical Measurements

- (a) Measurement of Continuous and Sampled-data

- (b) Measurement (Estimation) of Correlation Functions

- (c) Measurement (Estimation) of Probability and Probability Density

- 2. Coarse-quantization Measurements; Polarity-coincidence Correlation

- 3. Monte Carlo Computation of a Definite Integral

- 4. Measurement of Mean-square Filter Output and Filter Optimization

- (a) Direct Method

- (b) Modified-adjoint-system Method

- (c) Monte Carlo Method

- 5. Study of Ballistic-trajectory Errors

- 6. Demonstration of Modulation Waveforms with and without Noise

- 7. Simulation of a Superheterodyne Receiver

### Table 2.1 (Continued)

- 8. Simulation of an FM Communication System

- 9. Simulation of a Phase-lock Loop

- Simulation of Matched-filter Detection Using Pseudo-random Signals (Shift-register Sequences)

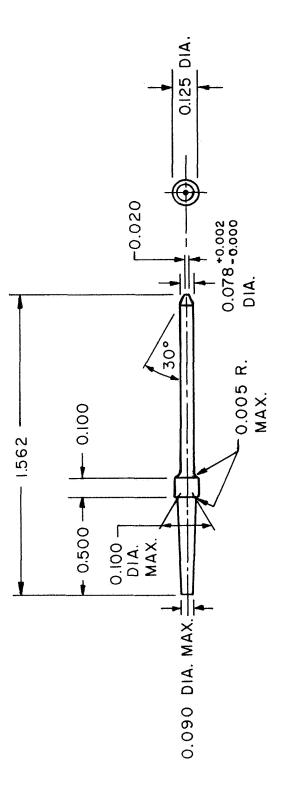

A low-cost MAC PANEL 440 point patchbay receiver having the necessary low-leakage (diallylpthallate) base and gold-plated spring construction was used for both digital and analog patchbays. Direct plug-in connections to the rear of each patchbay are implemented with special screw-machine fabricated, gold-plated taper pins terminated into plugs of standard 0.080 in. test-probe diameter (Fig. 2.4). These plugs mate with inexpensive test-point jacks mounted on the circuit cards. Gold-plated MAC PANEL shorting strips interconnecting patchbay points are inserted and held by the taper pins. All wiring from power supplies, coefficient potentiometers, and between digital and analog patchbays is soldered directly to the taper pins.

### 2.2 The Analog Module

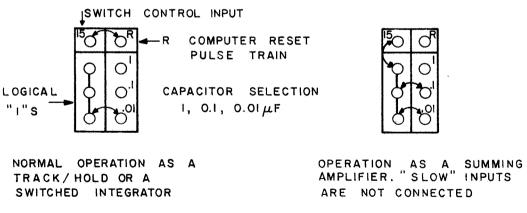

One of the two amplifiers on each amplifier card can be patched as an electronically switched integrator or track-hold circuit as well as a summing amplifier (Fig. 2.5). Integrating capacitances of 5  $\mu$ F, 0.5  $\mu$ F, 0.05  $\mu$ F and 0.005  $\mu$ F are employed together with summing resistors of 200 k $\Omega$  and 20 k $\Omega$  to permit both real-time and repetitive analog computation. A reed-relay, which shorts amplifier output and summing junction under logic control, serves as a POTSET relay and for starting certain iterative procedures. The lower amplifier on each card is

Fig. 2.3 Ground planes on one side of double-sided printed circuit boards serve as a shield between cards.

- MATERIAL: 0.125 DIA. HARD BRASS

- FINISH: 0.00003 HARD GOLD OVER 0.0001 NICKEL

SCALE: 2:1

Fig. 2.4 Specially fabricated taper pins permit direct plug-in connections to the rear of the patchbay.

Fig. 2.5 APE II Switched-Integrator/Summer Module

intended to serve as a simple summing amplifier with only gain-of-one inputs.

The analog module also contains wide-band quarter-square multipliers, diode bridges, analog comparators (with outputs on the digital patchbay), zener-diode limiters, free diodes, and twelve 5 k $\Omega$  co-efficient potentiometers.

#### 2.3 The Digital Module

The digital module consists of the following cards:

- 1. Front-panel pushbutton-logic card.

- Master clock card which provides all computer reset, sampling and timing pulses.

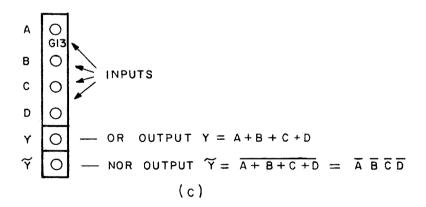

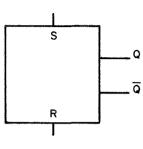

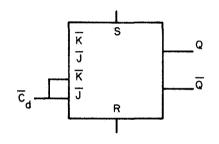

- Five free-logic cards, each containing a J-K type flip-flop and two three-input OR/NOR gates.

- 4. Four shift register cards, each with five stages and special reset/set logic, which can be patched for pattern generation, memory, and pseudo-random shift-register sequences.

- 5. A card containing 4 modulo-2 adders (exclusive OR's) used for pseudo-random sequences, digital correlation and digital comparison, and a sampling-type binary noise generator.

- 6. A counter card with 4 free decade counters intended for additional program timing and statistical experiments.

- 7. A 4-decade readout counter with in-line display for counting events.

Other digital module features include 3 front-panel pushbuttonswitch outputs for manually setting or resetting flip-flops and counters, 6 logic-state lamp inputs for visual determination of the state of any digital logic output, and digital outputs of 2 analog comparators (inputs on the analog patchbay).

The digital-logic cards, designed and constructed at The University of Arizona, are made with 1/16 in., two-sided, 1 oz., copper-clad, glass-epoxy printed-circuit board. To reduce cost, connections from one side of the PC board to the other are made with small wire. The component side of the board is mostly ground plane to reduce radiation and interference.

Motorola MECL integrated-circuit current-mode logic is employed throughout the digital module. The low-level logic swings (0.8V) and the balanced current-mode operation, producing negligible power-supply-line transients during switching times, combine with ground-plane shielding and L-C decoupling of the power supply leads of each card to reduce the digital noise coupled to the analog module. This is a critical factor in view of the wideband analog-computer amplifiers (0 dB at 20 MHz) used in the APE II system.

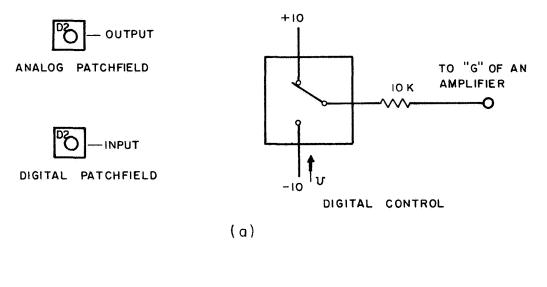

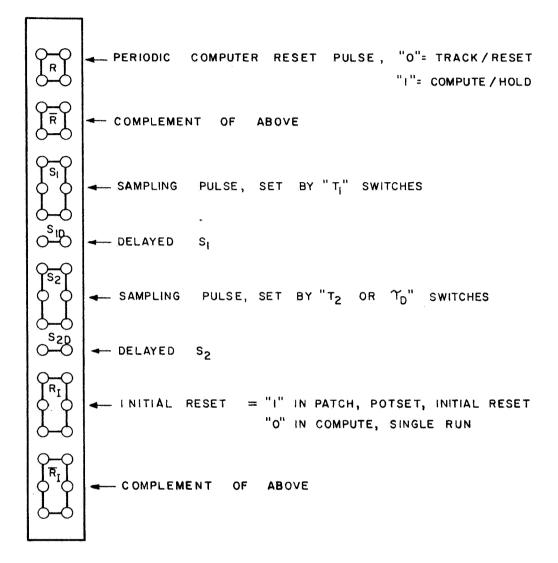

## 2.4 Digital Control of Analog Computer Operations

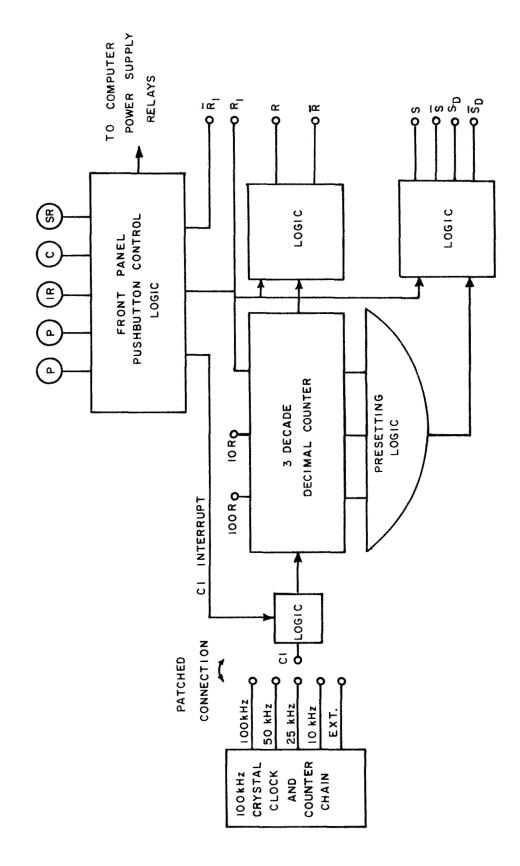

Figure 2.6 illustrates the design of the APE II control unit, which is a simplified and improved version of that used in The University of Arizona's ASTRAC II. A 100 kHz crystal-controlled clock and counter chain provides timing pulses (100 kHz, 50 kHz, 25 kHz and 10 kHz) which are always available on the patchbay for various control and display purposes. The desired computer repetition rate (100, 50, 25, or 10 runs per second) is obtained by patching to the above timing pulses. All

Fig. 2.6 Block Diagram of APE II Control Unit

other timing is performed in terms of these "C1" pulses (1000 per computer run), so that the time scale of all counting and timing operations changes automatically with the repetition rate  $f_R = 1/T_R$ .

The master timing counter  $C_1$  is a three-decade decimal counter with a preset output designed to perform the following timing functions:

- 1. Counts down by 1000 to mark the start of periodic COMPUTE periods.

- 2. Produces timing markers at 10 and 100 times the computer repetition rate  $f_R$  (e.g., for oscilloscope displays).

- 3. Produces sampling pulses S (set by convenient rocker-type thumbwheel decimal switches in steps of  $T_R/1000$ ) at t =  $T_1$  seconds after the start of each COMPUTE period (Fig. 2.7).

In normal repetitive operation (Fig. 2.7), R is "1" (logical one, not voltage) at t (computer time) = 0 and "0" at t = 0.9  $T_R$  to produce periodic reset pulses R, so that COMPUTE periods of length T = 0.9  $T_R$ alternate with RESET periods of length  $T_S = T_R/10$ . The preset output at  $T_1$  feeds a flip-flop timing-logic block to produce periodic sampling pulses S and delayed sampling pulses  $S_D$  of length  $T_S$ . Note that R, S and  $S_D$  (and hence also their complements) are clocked by Cl in order to eliminate timing errors and coincidence-gate output spikes due to ripplethrough delays in  $C_1$ .

The front-panel controls are PATCH, POTSET, INITIAL RESET, COM-PUTE and SINGLE RUN. The master clock is controlled by a pushbuttonlogic card (see state diagram Fig. 2.8). In addition, the COMPUTE button puts the computer into INITIAL RESET when depressed and into

Fig. 2.7 APE II Timing Diagram

COMPUTE when released. The pushbutton-logic card provides an INITIAL RESET pulse  $R_I$  and POTSET pulse P, available on the digital patchbay, a Cl-interrupt pulse which gates the Cl pulses into  $C_1$  and other pulses to front panel pushbutton indicator lights, amplifier, reference and potset-relay power supplies.

## 2.5 Operating Conditions

When the computer is turned on, a special RC delay circuit places the machine into the PATCH mode. In this mode:

1. Amplifier and reference power is OFF.

- 2. Counter C<sub>1</sub> is reset to zero.

- 3. R, S, and  $S_D$  are "0" (RESET/TRACK).

- 4. INITIAL RESET R<sub>I</sub> and POTSET P are "1".

From PATCH, one goes to POTSET, where the following conditions are established:

- Amplifier power is ON, but reference power is still removed from the patchbay.

- 2. Counter  $C_1$  is reset to zero.

- 3. R, S, and  $S_D$  are "0" (RESET/TRACK)

- 4. R<sub>T</sub> and P are "1".

- 5. The digital voltmeter (DVM) is connected to the potentiometer readout bus.

- 6. Amplifier overload lights are reset.

Before one begins to compute, one depresses the INITIAL RESET button to produce the following conditions:

- 1. Amplifier and reference power is ON.

- 2. Counter  $C_1$  is reset to zero.

- 3. R, S, and  $S_D$  are "0" (RESET/TRACK).

- 4. R<sub>I</sub> is "1", P is "0".

- 5. DVM is connected to an analog-patchbay point.

All integrators and track-holds and digital logic are now reset to suitable initial conditions, ready for computation. This state is maintained until one depresses and releases the COMPUTE button. Then  $R_I$  goes to "O", S and  $S_D$  go to "1", and a delay of 10 ms (to allow any special relay circuits to operate), due to a one-shot multivibrator on the pushbutton-logic card, runs out. Then the Cl-interrupt pulse gates Cl pulses into counter  $C_1$  which counts 101 pulses before starting the first COM-PUTE period. The periodic reset pulses R and sampling pulses S and  $S_D$ will then continue on, as illustrated in Fig. 2.7. For single-run operation, one must begin in INITIAL RESET (going from COMPUTE to SINGLE RUN is prevented by the logic design) and depress the SINGLE RUN button. At the end of one run, only the Cl pulses are interrupted, and the computer stands ready for another single run obtained by depressing the SINGLE RUN button again; this permits one to check the progress of iterative routines computer run by computer run.

In normal repetitive operation, the integrators are controlled by R, and selected track-hold circuits can be controlled by S. Track-hold pairs are controlled by R and S, or by S and S<sub>D</sub> by digital readout of solution values x(t) at an accurately present computer sampling time  $t = T_1$ .

Different patching connections can employ R, S and  $S_D$  for flexible memory control, including three-period control (Eckes and Korn, 1964).

### 2.6 Free Logic

The free-logic circuits, namely J-K type flip-flops, OR/NOR gates, modulo-2 adders and decade counters, are of straightforward design and need no detailed description. The APE II shift-registers have some extra features, which are worth explanation.

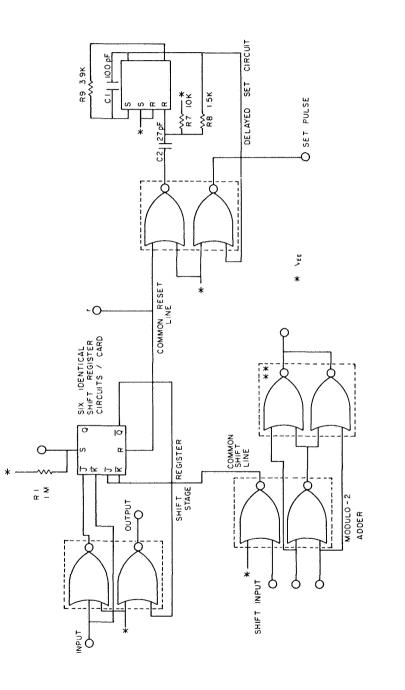

Each shift-register card contains five stages, with each stage conveniently patchable to the following stage by a single connection; this is made possible by an extra input gate for each stage (Fig. 2.9). A one-shot multivibrator (using a MECL R-S flip-flop) provides a delayed set pulse, 100 ns wide, immediately after a reset pulse (usually  $R_I$ ), patched to the common reset line, goes to "0". Each stage patched to this delayed set pulse is, thus, ready for computation. This scheme is especially useful in setting up the shift register for pseudo-noise sequences. The one-shot circuit can also be used by itself as a source of delayed pulses.

Four decimal in-line readout counters have their individual input, reset lines, and outputs available on the digital patchbay. In addition, a RESET button common to all four counters is provided on the front panel near the display unit. Each counter has a forbidden-code gate to prevent the simultaneous appearance of two numbers when the computer is turned on, or when some interference accidentally triggers the counter into an unwanted state.

Fig. 2.9 APE II Shift Register Card Schematic

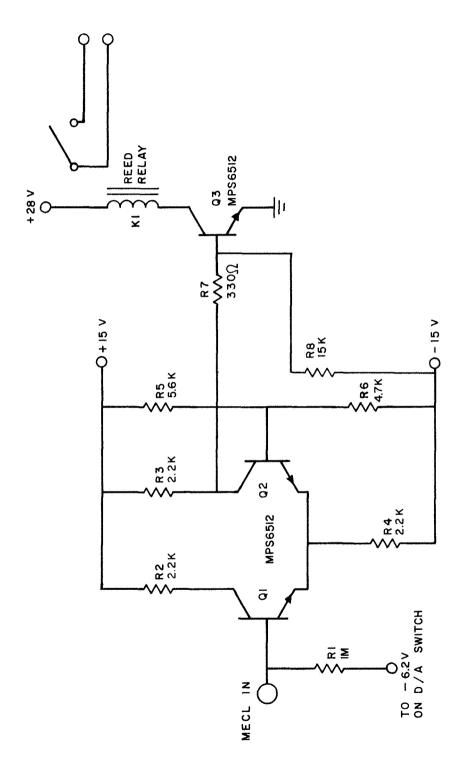

Incandescent lamps in the counter readout display unit (I.E.E., Inc., Series 20), control-panel pushbutton lamps, relays (paralleled by a filter capacitor) and logic-state lamps, are driven by a novel inexpensive driver circuit employing a silicon controlled-rectifier (SCR) actuated directly by MECL logic levels (Fig. 2.10).

# 2.7 Discussion

The new APE II system provides a small flexible differential analyzer intended for laboratory instruction in analog and hybrid computation. Total parts cost is estimated to be \$4,500. Two APE II systems have been in use by students one semester and have worked out quite well. The results of an experiment using APE II are detailed in Chapter 7.

Experience with APE II has demonstrated that the packaging techniques and the use of low-level current-mode logic to be very worthwhile. This provided experience and more confidence for the design of LOCUST.

NOTE: TRANSFORMER SECONDARY WINDING IS APPROXIMATELY AT -1.45 VOLTS WITH RESPECT TO GROUND. SEVERAL CIRCUITS MAY BE CONNECTED TO THE SAME TRANSFORMER AT A AND B. FILTER CAPACITOR IS USED WITH RELAY ONLY.

Fig. 2.10 Indicator Lamp and Relay Driver Circuit

.

#### Chapter 3

### THE LOCUST SYSTEM

The feasibility of really fast hybrid computation was demonstrated by the development and application of The University of Arizona's ASTRAC II (Eckes, 1967). But, as noted earlier, no machine commercially available to date has the required mode-control switching speed and low-impedance computing networks; and most computers do not have the required amplifier bandwidth. The development of the LOCUST system represents an attempt to design a truly producible very fast hybrid computer at moderate cost.

The LOCUST system is an all solid-state iterative-differentialanalyzer making maximum use of integrated circuits (Fig. 3.1). The machine comprises 34 free amplifiers of which 16 can be used as integrator/track-hold circuits, plus 18 amplifiers permanently committed . to 6 high-speed multiplier/dividers, and 4 comparators (56 amplifiers total). It is capable of computation at iteration rates up to 2 kHz; linear-component errors are within 0.2 percent up to 10 kHz. Special "slow" summing networks also permit operation as a slow analog computer. The following design features are of special interest:

Maximum use of both linear and digital monolithic integrated circuits enhances computer performance and still reduces parts and assembly costs.

33

- 2. New mounting and shielding techniques, including a technique for shielding low cost unshielded patchbays, were developed.

- 3. Low-level current-mode digital logic modules have essentially eliminated digital noise in the analog portion of the computer.

- 4. New solid-state devices have substantially improved amplifier and mode-control switch performance.

- 5. Free digital logic has been made more convenient as a result of ASTRAC II experience; and the LOCUST digital-computer linkage is designed as an integral part of the logic-control system.

- New patchpanel design affords exceptional convenience for setup and logic control.

The LOCUST system equipment complement is listed in Table 3.1.

# 3.1 <u>High-speed Computing Requirements</u>

To appreciate the technical problems associated with fast computation, consider the following requirements:

- To obtain a dynamic error (phase-shift error) of 0.1 percent of half scale at 10 kHz in an ordinary phase inverting amplifier, the amplifier gain-bandwidth product must be greater than 10 MHz.

- To prevent dynamic errors due to distributed capacitances, computing resistances (summing resistors in summing amplifiers and integrators) should be low, less than 10 kΩ. Such low impedances require high-current amplifier output stages.

- 3. The voltage rate of change of a 20-volt peak-to-peak 10 kHz sine wave is  $2\pi \times 10^5$  volts per second. To insure a track-hold

# Analog Elements

- 16 Integrator/Track-hold Summing Circuits 4 Summing amplifiers

- 8 2-input summing amplifiers

- 6 Phase inverters

- 6 Quarter-square multipliers

- 4 General-purpose diode function generators

- 4 Sine generators

- 40 Coefficient potentiometers

- 4 Diode bridges

# Digital Elements

- 12 MECL J-K type flip-flops

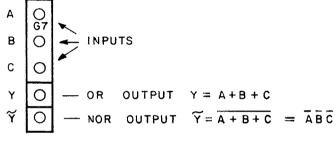

- 12 3-input OR/NOR gates

- 6 4-input OR/NOR gates

- 5 6-stage shift registers with a one-shot multivibrator reset circuit and a modulo-2 adder (exclusive-OR) circuit

- 6 Decade counters with in-line readout

- 12 Logic-state lights

- 1 Digital control module

# Hybrid Elements

- 4 Comparators

- 4 D/A multipliers (to be added later)

- 4 A/D converters

- 4 D/A level changers (noise drivers)

- 6 D/A electronic switches

- 4 D/A relay switches

## Auxiliary Elements

- 1 Electronic Digital Voltmeter

- 1 Oscilloscope

- 1 Power supply balance indicator and control panel

sampling accuracy of 0.1 percent, mode-control and track-hold timing must be within 15 nanoseconds.

When such high-speed computing elements are placed in a hybrid computer system, other considerations become important:

- Added stray capacitance due to wiring and patchbay system can reduce computing bandwidth.

- 2. Crosstalk between computing elements through patchbay capacitances and through the analog power supply can reduce accuracy.

- 3. Wideband analog elements pick up switching noise from modecontrol switches and from the digital control module.

In the LOCUST system all analog computing elements are housed in aluminum cans and plugged directly into the rear of a modified low-cost patchbay system. Analog amplifier and all mode-control switch power supply lines are decoupled with a CLC pi-network filter in each amplifier and switch module.

Digital noise is minimized through the use of Motorola Emitter Coupled Logic (MECL). The low-level logic swing (0.8V) along with the balanced-current nature of the non-saturating current-mode logic serve to reduce radiation and, more importantly, computer ground-system disturbances.

Good computer-system design requires that all ground returns terminate at one point in order to eliminate ground loops which pick up signals and thus cause ground system noise. The LOCUST analog patchbay serves as the common ground point for the system.

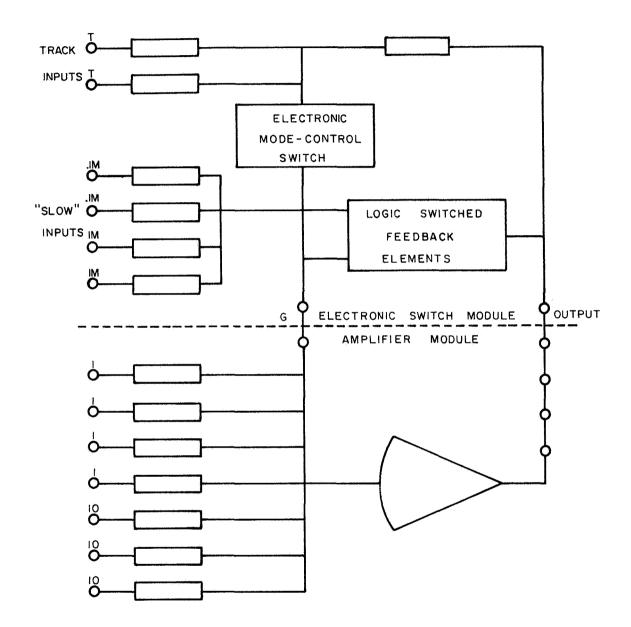

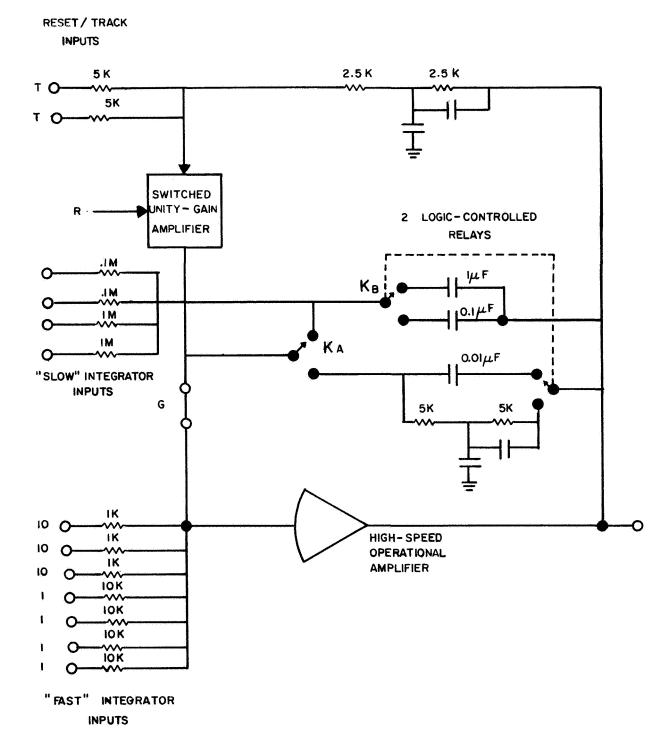

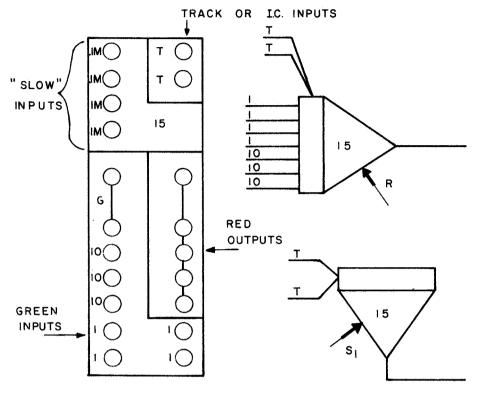

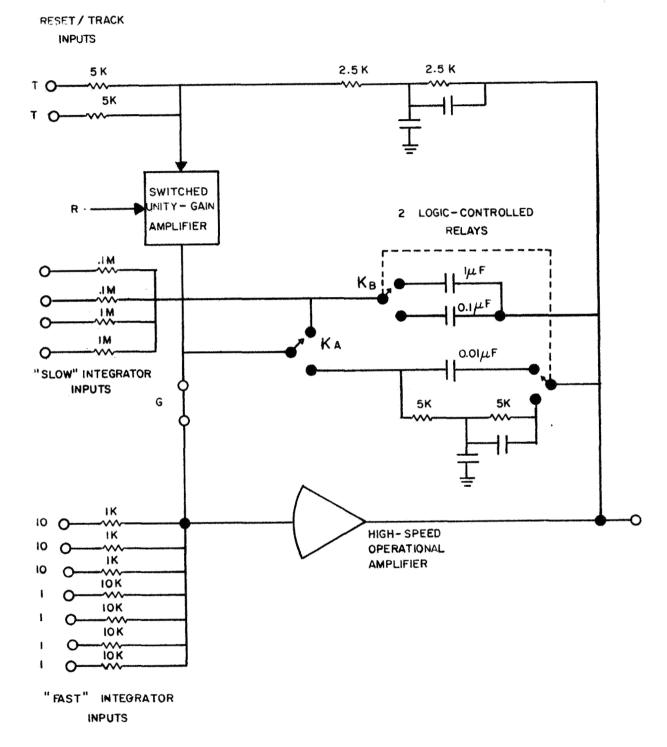

## 3.2 LOCUST Integrator/Track-hold Module

The heart of an iterative differential analyzer is an amplifier/electronic-switch combination, the integrator/track-hold circuit. The LOCUST integrator/track-hold circuit block diagram is illustrated in Fig. 3.2. A single high-speed electronic switch, which is controlled by signals from the digital control module, suffices for each integrator, and the same switched-integrator circuit is used for both integration and track-hold (sample-hold, zero-order hold) operation. A complete description of the circuit and its operation is included in Chapter 4.

The feedback capacitors (0.01, 0.1 and 1.0  $\mu$ F) for integration and track-hold operation, and one feedback resistor (10 kΩ) for summing amplifier or switched-amplifier operation are selected by relays driven by digital logic from the digital patchbay. A "slow" summing network is connected, when the 1.0 and the 0.1  $\mu$ F capacitors are used, to permit real-time integration.

### 3.3 LOCUST Analog Patchbay System

Analog computing elements whose input and output voltages may contain frequency components as high as 10 to 20 kHz make it mandatory to use shielded patchbay systems with shielded patchcords in spite of their added shunt capacitances. Shielded patchbay systems are also needed to reduce leakage when computing-elements impedances are high, say, greater than 100 k $\Omega$ . Low-impedance levels of 1 k $\Omega$  to 10 k $\Omega$  used

Fig. 3.2 Block Diagram of LOCUST Integrator/Track-hold Module

in LOCUST are low enough that surface leakage is a minor problem. Nevertheless, a low-leakage material, such as diallylpthallate, must be used for the patchbay receiver.

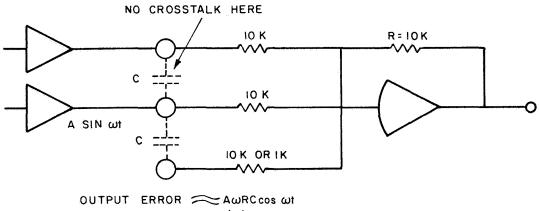

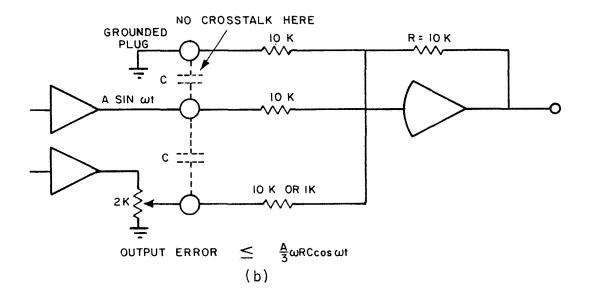

Crosstalk between patchbay terminations can be a major problem in high-speed analog computers. Capacitive coupling between patchbay receiver springs and patchcord-tip combinations cause undesirable coupling between the connected and unconnected inputs of a particular amplifier, and between the output of an amplifier and the inputs of the amplifier located next to it. The capacitance of unshielded patching systems may be as high as 5 to 10 pF between holes, which can cause an error of from 0.3 to 0.6 percent at 10 kHz if the summing resistors are 10 k $\Omega$  (Fig. 3.3).

The price of totally shielded patchbay systems is considerable, \$2,000 to \$4,000 for a system with enough holes (1,000 to 2,000) for a small-to-medium size analog computer. An unshielded patchbay system of the same size costs only about \$350 to \$500.

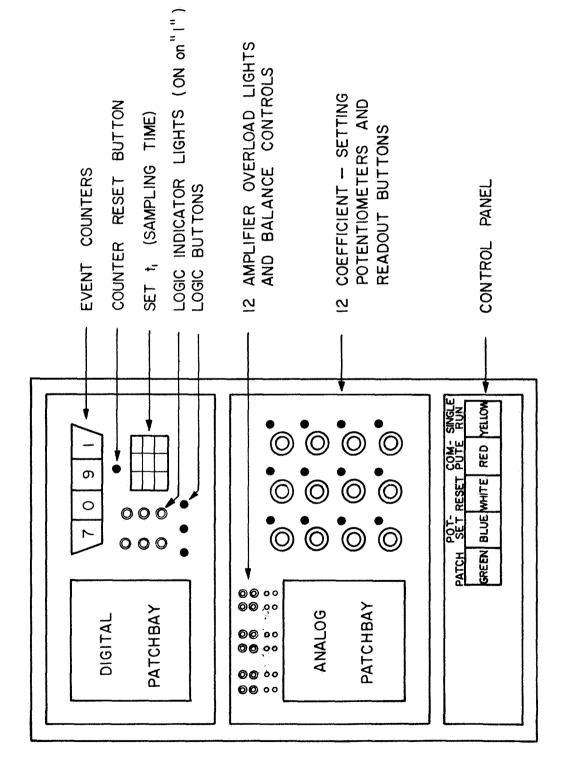

The LOCUST analog patchbay system represents a compromise in terms of crosstalk, leakage and cost. It comprises a low-cost MAC Panel 1,600 hole unshielded patchbay receiver having the necessary diallylpthallate base for low leakage, and gold-plated springs for low contact resistance and corrosion protection.

Suitable rows and columns of patchbay receiver springs are connected to the computer system-ground using gold-plated shorting strips held in by taper pins to provide shielding between analog

(a)

Fig. 3.3 Patchbay capacitances between inputs cause gain errors.

(a) Open inputs contribute ARC  $\omega \cos \omega t$  volts error (0.3% for  $\omega = 2\pi 10^4$ ,  $R = 10^4$ ,  $C = 5 \times 10^{-12}$ ). (b) Grounded gainof-one input eliminates crosstalk to that input at the expense of open-loop gain; grounded gain-of-ten inputs would seriously affect amplifier performance. Potentiometer connection reduces error to at most one-third that of an open input. computing elements (Fig. 3.4). This "wastes" about 400 holes. About 500 other patchbay terminations are used for all power-supply and logic-control wiring for the analog computing elements so that the latter has no other connections whatsoever.

An analog module covers a field as shown in Fig. 3.5. Inputs and outputs are separated as much as possible by locating power supply and control connections in the center column. These low-impedance terminations supply additional shielding between analog terminations.

Amplifiers, mode-control switches, multipliers, D/A switches, phase inverters etc., are housed in aluminum cans plugged directly into the rear of the analog patchbay (Fig. 3.6). These direct plug-in connections are implemented with special screw-machine-fabricated goldplated taper pins terminated into plugs of standard 0.080 in. test-probe diameter. These are a shortened version of those used in APE II (Fig. 2.4). These plugs mate with standard press-fit test-probe jacks on the computing element cans. The cans are held at the rear by simple frames with swing-out bars which permit easy removal for maintenance.

All power supply, digital control, potentiometer, and referencesupply wiring is soldered directly to the patchbay-receiver solder-cup taper pins or to the special taper-pin plugs. As noted earlier, the computing elements do not require rear connectors.

All aluminum patchboards, fabricated at The University of Arizona's Electrical Engineering Shop, replace the plastic patchboards usually provided with unshielded patchbays. The finished aluminum

42

Fig. 3.4 Rows and columns of terminations provide shielding between modules. Power-supply and logic-control wiring is made directly to the patchbay receiver.

POWER AND CONTROL CONNECTIONS IN CENTER COLUMN

Fig. 3.5 LOCUST Analog Module Patchbay Field

(b)

Fig. 3.6 (a) Analog elements are housed in aluminum cans and (b) plugged directly into the rear of the patchbay receiver and held by simple frames. patchboards, which are drilled for standard commercially available Electronic Associates or Virginia Panel shielded patchcords, have patch holes only for the patchbay terminations actually used (Fig. 3.7).

These patchbay-system construction techniques yield a good measure of shielding against crosstalk at relatively low cost. Crosstalk error between amplifiers was measured and found to be less than 0.01 percent for all computing frequencies. This indicates the effectiveness of the inexpensive shielded patchbay system and of the power supply filters in each analog module. Capacitance between adjacent patchbay terminations has been reduced by one-half to about 3pF. Capacitance between adjacent patchcords has been eliminated by using shielded patchcords. Leakage currents through the removable patchboard portion of the system have been eliminated. The total cost has been reduced to one-third to one-half that of a commercial shielded-patchbay system.

### 3.4 Analog-patchpanel Layout

The layout design of a patchpanel is a human-engineering task as well as an electrical and mechanical design task (Fig. 3.7).

The patching of an integrator/track-hold circuit is convenient because there are no bottle plugs required to implement a switched integrator; scale changing and mode control are more conveniently patched on the digital patchpanel. Inputs of computing elements are located on the left of a patchfield and outputs on the right.

The technique of bringing power supply and control lines directly to the patchbay receiver puts additional constraints on layout,

|    |          |     |   |     |     |    |    |                 |          |   |   |     | 3  |     | •  | 0 8 4<br>0 - 4 |     |    |    |    |    | •           |

|----|----------|-----|---|-----|-----|----|----|-----------------|----------|---|---|-----|----|-----|----|----------------|-----|----|----|----|----|-------------|

|    | -        |     | : |     | - 0 |    | :: | -00             |          |   |   | -0  |    |     |    | : ;            | •   |    |    |    | •  | *           |

| 30 |          |     |   | 1   |     | 2  |    | •● <sup>1</sup> |          |   | - | -®' | 6  |     | ,  |                |     | 0  |    | .0 |    | <b>*</b> ., |

|    | <u>.</u> | ě   | ۲ | •   | •   | ٠  |    | • •             | • •      |   |   | •   | •  | •   | •  |                | •   |    | ٠  | •  | ē  |             |

|    | 0        | ie. | • |     |     | :  |    |                 |          |   |   |     | \$ |     | •  |                | :   |    |    |    | ** |             |

|    | -        |     | : |     |     |    |    |                 |          |   |   | •   | Ś  |     | ÷  | 00<br>-        |     |    |    | :  | :  | •           |

| ۲  | i        |     |   |     |     |    |    |                 |          |   |   |     | •  |     |    | 0(             |     |    |    |    |    | •           |

|    | 2        |     |   |     |     |    |    |                 |          |   |   |     |    |     | 9  |                |     |    |    |    | 2  |             |

|    | -        | ž   |   | ្តី |     | 12 |    | - 14            | -0.15    |   |   |     | 16 |     | 7  | ě,             |     | 19 |    | 20 |    |             |

|    |          |     |   |     |     | •  |    |                 | <b>e</b> |   |   | •   | .• | •   | •  |                |     | •  |    |    |    | -           |

|    |          | •   |   |     |     | •  |    |                 |          |   |   | ٠   | •  |     | 2  | èée            |     | •  |    |    |    | •           |

|    |          |     | ě | Ĩ   |     | Ì  |    | - 0             |          |   |   |     | ž  |     | Ŧ. |                |     | Ī  |    |    |    |             |

| 1  |          |     | ŝ | i   |     | Ì  |    |                 |          |   |   |     |    | :   | 3  |                |     |    |    |    |    |             |

| 5  | -        |     |   |     |     |    |    |                 |          | - |   |     |    | ieć |    |                | 160 |    | ě. |    |    |             |

Fig. 3.7 All aluminum patchboards are drilled only for the terminations used and silkscreened and color-coded for identification.

since it could, conceivably, increase the problem of leakage currents from power supply lines causing undesirable voltage offsets at computing element outputs. On the other hand, as mentioned earlier, these low impedance lines in the center column provide added electrostatic shielding between analog inputs and outputs.

Because patchboards have patching holes only for patchbay terminations actually used for patching, they have a relatively wider hole spacing which permits more patching room and presents a much more uncluttered appearance than the original unshielded patchboards.

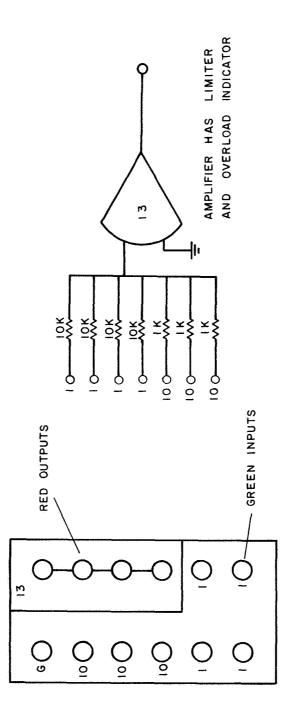

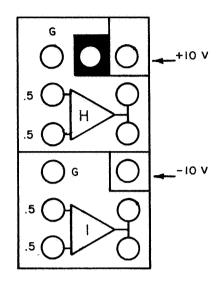

The patchpanel contains, in addition to patchfields for integrator/track-hold computing elements, patch fields for summing amplifiers, comparators, phase inverters, multipliers, sin-generators, D/A multipliers, and D/A switches. Additional patch fields provide connections to interface equipment linking LOCUST to a PDP-9 digital computer and to readout trunk-lines. A number of patching setups are described in the LOCUST instruction manual (Appendix).

Since the analog module cans cover the entire patching field associated with each particular element, coefficient-setting potentiometers and 10-volt reference points are located around the edge of the patchpanel.

The patchboards are silkscreened white with black letters and symbols. Inputs, outputs and potentiometers are color-coded with transparent ink for identification.

# 3.5 Costs

New packaging techniques, the modified patchbay system and the use of integrated circuits have reduced parts and assembly costs of LOCUST to one-half that of ASTRAC II at no sacrifice in performance. The most striking savings were made in the digital section, \$3,000, one-third of ASTRAC II digital-module cost, and the analog patchbay system, about \$1,000, one-half of ASTRAC II patchbay system cost. Total parts cost for the system is about \$13,000.

#### Chapter 4

## LOCUST ANALOG COMPUTING ELEMENTS

To exploit the possibilities of fast iterative computation, wide-band analog computing elements are mandatory. Gain and phase shift of operational amplifiers must be controlled well beyond the actual working frequency range in order to maintain stability and to insure the specified accuracy in operational-amplifier feedback circuits. Impedance levels in analog computing elements are quite low (10 k $\Omega$  or less) to reduce the effects of stray capacitance. Low impedances, in turn, require more current, and so the LOCUST amplifiers are designed to supply 30 mA. The switching times of electronic modecontrol switches, D/A switches, and the comparison delay of analog comparators are designed to be as short as possible.

The resulting design problems are extremely difficult and, for some computing elements, they have never been wholly satisfactorily solved. The Analog/Hybrid Computer Laboratory at The University of Arizona has pioneered in the design of high-speed computing elements, beginning as early as 1961 with ASTRAC I, a 100-volt vacuum tube machine. Significant improvements in speed and timing resulted from the ASTRAC II project, a 10-volt all-solid-state machine. The LOCUST project is an attempt to further refine the design and to exceed the specifications of the ASTRAC II system by utilizing new packaging techniques, new solid state devices, and substantial improvements in the circuit design.

50

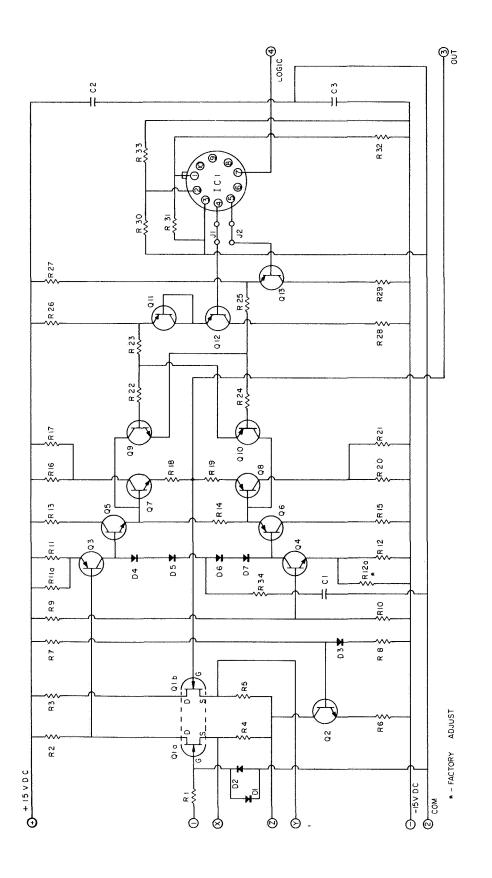

## 4.1 The LOCUST Operational Amplifiers

The LOCUST iterative differential analyzer satisfies the first two requirements of Section 3.1 with the aid of a new high-performance amplifier developed at The University of Arizona as an M.S. thesis project (Naylor, 1967); the reference describes its design in great detail. The performance of the new amplifier is summarized in Table 4.1.

The block diagram of Fig. 4.1(a) illustrates the basic amplifier design, which employs a three-channel feed-forward circuit. Beginning from the amplifier input, the channels are: the high-frequency channel directly to the wide-band class AB output stage, the intermediate-frequency channel through a Motorola MC1433 integrated-circuit operational amplifier, and the low-frequency channel through a Fairchild  $\mu$ A726C hotsubstrate preamplifier.

The bandwidth and output-current limitations of the MC1433 integrated-circuit amplifier are overcome by cascading it with a highcurrent output stage and by feeding forward the high frequency signals directly to the output stage from the summing junction. Because of the low-offset, low-drift properties of a new integrated-circuit hot-substrate differential amplifier, a chopper stabilizer channel is unnecessary.

Figure 4.1(b) illustrates the frequency response of each channel and their combination. Dotted lines show the roll-off of a more conventional 6 dB/octave feed-forward amplifier; the "zero" needed at 40 kHz lowers the gain at 10 kHz. An improvement in the open-loop gain of only

Fig. 4.1 (a) Block diagram showing signal flow through the three channels. (b) Open-loop Bode plot of the three channels and their combination.

| Typical Performance at 25 <sup>0</sup> C |              | Unit           |

|------------------------------------------|--------------|----------------|

| Open-loop Gain                           | 120          | dB             |

| Unity Gain Bandwidth                     | 30           | MHz            |

| Rated Output                             |              |                |