https://ntrs.nasa.gov/search.jsp?R=19680014253 2020-03-12T10:39:25+00:00Z

NASA CR 92101

FINAL REPORT

## AUXILIARY MEMORY FOR APOLLO GUIDANCE COMPUTER

#### CONTRACT NAS 9-5994

R68-4125 Vol. 1 - Sections 1, 2, 3, and 4 11 MARCH 1968 Appendices A, B, C, F, and G

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION MANNED SPACE FLIGHT CENTER Houston, Texas

PREPARED BY

RAYTHEON COMPANY SPACE AND INFORMATION SYSTEMS DIVISION Sudbury, Massachusetts

SPACE AND INFORMATION SYSTEMS DIVISION

### CONTENTS

#### Section

#### Page

| 1. | UNIT  | DESCRIPTION                                            | -1  |

|----|-------|--------------------------------------------------------|-----|

|    | 1.1   | Auxiliary Core Memory                                  | -1  |

|    |       | 1.1.1 Logic                                            | -1  |

|    |       | 1.1.2 Memory System                                    | -7  |

|    |       | 1.1.3 ACM Power Supply                                 | -16 |

|    | 1.2   | Interface Module                                       | -21 |

|    |       | 1.2.1 Electrical Description 1                         | -21 |

|    |       | 1.2.2 Mechanical Description                           | -27 |

|    | 1.3   | Auxiliary Tape Memory                                  | -28 |

|    |       | 1.3.1 Electrical Description 1.                        | -32 |

|    |       | 1.3.2 Mechanical Description 1                         | -42 |

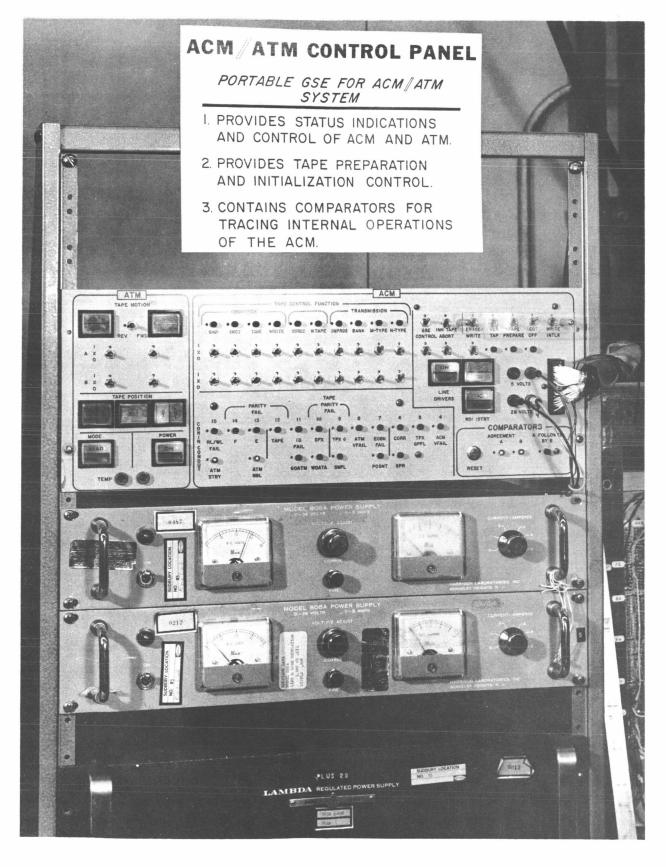

|    | 1.4   | Control Panel                                          | -48 |

|    |       | 1.4.1 Electrical Description 1.                        | -51 |

|    |       | 1.4.2 Mechanical Description 1.                        | -51 |

|    |       | 1.4.3 Controls and Indicators 1.                       | -52 |

| 2. | SYSTI | EM ORGANIZATION                                        | -1  |

|    | 2.1   |                                                        | -1  |

|    |       | 2.1.1 Detailed Description of System Organization . 2- | -3  |

|    | 2.2   | General Information                                    | -7  |

|    |       | 2.2.1 Input-Output Mechanism                           | -7  |

|    |       | 2.2.2 Memory Subsystem                                 | -10 |

|    |       | 2.2.3 Voting and Correcting Philosophy 2.              | -17 |

|    | 2.3   | AGC Memory Extension                                   | -21 |

|    |       | 2.3.1 Memory Address Assignment                        | -21 |

|    |       | 2.3.2 Address Detection Logic                          | -22 |

|    |       | 2.3.3 Data Transfer                                    | -27 |

SPACE AND INFORMATION SYSTEMS DIVISION

CONTENTS (CONTINUED)

RAYTHEON

|    | 2.4  | Tape Og | perations                                     |

|----|------|---------|-----------------------------------------------|

|    |      | 2.4.1   | Read Tape into ACM                            |

|    |      | 2.4.2   | The Search Sequence                           |

|    |      | 2.4.3   | Data Transfers When Reading Program Tape 2-31 |

|    |      | 2.4.4   | Data Transfers When Reading Data Tape 2-35    |

|    |      | 2.4.5   | Writing on the Data Tape                      |

|    |      | 2.4.6   | Position Tape Mode                            |

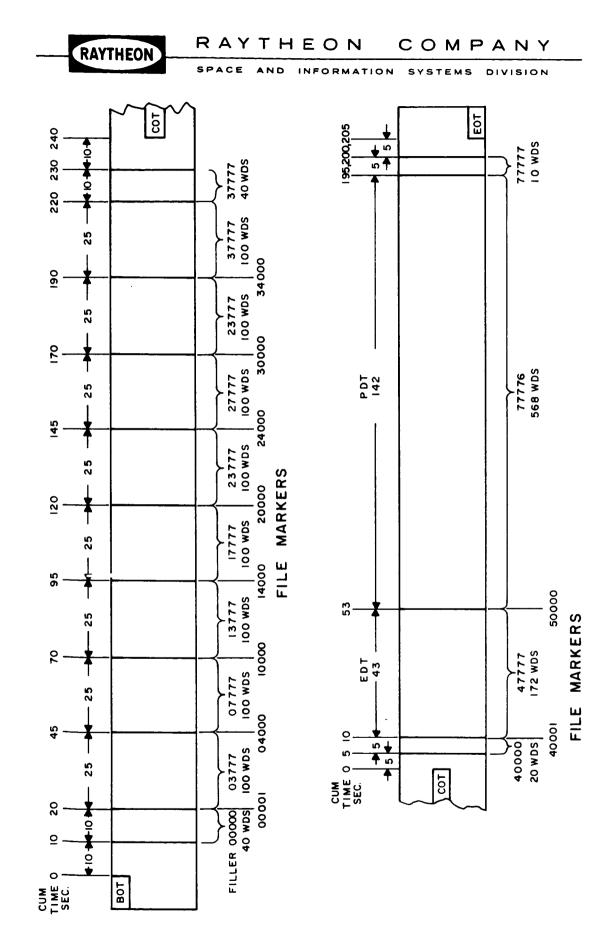

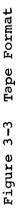

|    |      | 2.4.7   | Tape Format                                   |

|    | 2.5  | Alarms  | and Failure Protection                        |

|    |      | 2.5.1   | ACM Parity Failures                           |

|    |      | 2.5.2   | Tape Parity Failures      2-48                |

|    |      | 2.5.3   | Voltage Failures                              |

|    |      | 2.5.4   | Miscellaneous Failures                        |

|    |      | 2.5.5   | Failure Protection and Self-Amputation 2-52   |

| з. | SOFT | WARE CO | NTROL OF AUXILIARY MEMORY                     |

|    | 3.1  | ACM Co  | ntrol                                         |

|    |      | 3.1.1   | Power Control                                 |

|    |      | 3.1.2   | Addressing                                    |

|    |      | 3.1.3   | Failure Effects                               |

|    | 3.2  | ATM Co  | ntrol                                         |

|    |      | 3.2.1   | Power Control                                 |

|    |      | 3.2.2   | Tape Format and File Size                     |

|    |      | 3.2.3   | MU Addressing                                 |

|    |      | 3.2.4   | SIMPLEX/TRIPLEX                               |

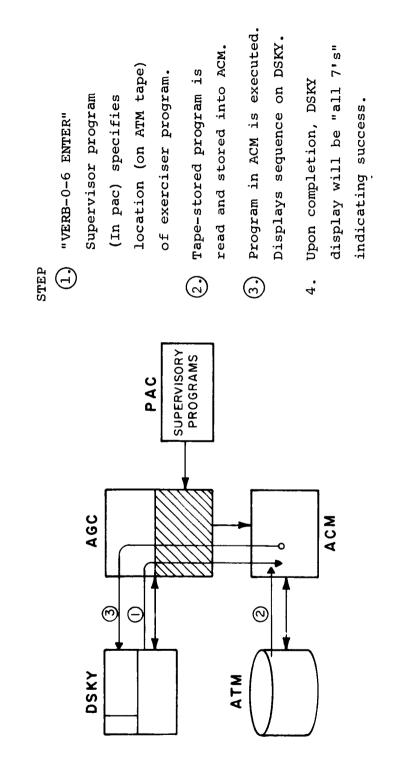

|    |      | 3.2.5   | Transfer Program from Tape to ACM Memory 3-7  |

|    |      | 3.2.6   | Transfer Data from Tape to ACM Memory 3-8     |

|    |      | 3.2.7   | Transfer Data from ACM Memory to Tape 3-8     |

|    |      | 3.2.8   | Transfer Program from ACM Memory to Tape 3-9  |

RAYTHEON

.

Ì

SPACE AND INFORMATION SYSTEMS DIVISION

CONTENTS (CONTINUED)

| 3.         | .2.9       | ID Words .                | • • •   | • •   | • •  | •   | • •   | • •  | • • | • • | •   | • | 3-9           |

|------------|------------|---------------------------|---------|-------|------|-----|-------|------|-----|-----|-----|---|---------------|

| 3.         | .2.10      | Position                  | Таре .  | • • • | • •  | •   | • •   | • •  | • • | • • | •   | • | 3-11          |

| 3.         | •2.11      | Tape Erro                 | ors     | • •   | ••   | •   | • •   | • •  | • • | • • | • • | • | 3-11          |

| 4. DEMONS  | TRATIC     | N TESTS                   |         | • •   | • •  | •   | • •   | • •  | • • | • • | •   | • | 4-1           |

| 4.1 T      | 'est Ob    | j <b>e</b> ctives ,       |         | • •   | • •  | •   | • •   | • •  | • • | • • | •   | • | 4-1           |

| 4          | .1.1       | Power Cont                | trol .  | • •   | • •  | •   | • •   | • •  | • • | • • | • • | • | 4-1           |

| 4          | .1.2       | Program Op                | peratio | ons . | • •  | •   | • •   | • •  | • • | • • | •   | • | 4-1           |

| 4          | .1.3       | Data Opera                | ations  | • •   | • •  | •   | • •   | • •  | •   | • • | • • | • | 4-1           |

| 4.2 T      | est Co     | nfiguratio                | on .    | • • • | • •  | •   | • •   | • •  | • • | • • | •   | • | 4-2           |

| 4.3 D      | escrip     | tion of Te                | ests .  | • • • | • •  | •   | • •   | • •  | • • | •   |     | • | 4-2           |

| 4          | .3.1       | Power Cont                | trol Te | ests  | • •  | •   | ••    | • •  | • • | • • | •   | • | 4-2           |

| 4          | .3.2       | Program Ta                | ape Tes | sts . | • •  | •   | • •   | • •  | • • | •   | • • | • | 4-5           |

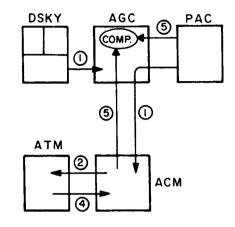

| 4          | .3.3       | Data Tape                 | Tests   | • •   | • •  | •   | • •   | ••   | • • | •   | • • | • | 4-7           |

| 4          | .3.4       | Restart Te                | ests .  | • • • | ••   | •   | •••   | ••   | ••  | •   | • • | • | 4 <b>-</b> 10 |

| APPENDIX A |            | INTERFACE                 |         |       |      |     |       |      |     |     |     | • | A-1           |

| APPENDIX B | 3 - 3      | INTERFACE                 | SIGNAL  | ROUTI | ING  | - v | ol.   | 1.   |     | •   | • • | • | B1            |

| APPENDIX C | - <u>-</u> | TAPE INITI.<br>PREPARATIO |         |       |      |     |       |      | _   |     |     |   | <b>C-</b> 1   |

| APPENDIX D |            | PROGRAM LI                |         |       |      |     |       |      |     |     |     |   | D-1           |

| APPENDIX E |            | ACM SIGNAL                | DICTIC  | ONARY | - v  | ol. | 2     | ••   |     | •   |     | • | E-1           |

| APPENDIX F | _          | JTILITY VE                |         |       |      |     |       |      |     |     |     |   | F-1           |

| APPENDIX G | 6- I       | DISPLAY AN                | D I.D.  | INFOR | RMAI | ION | . – I | /ol. | 1.  | •   |     | • | G <b>-</b> 1  |

RAYTHEON

Figure

RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

#### **ILLUSTRATIONS**

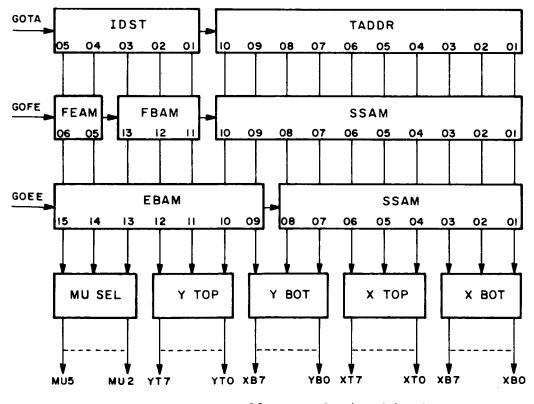

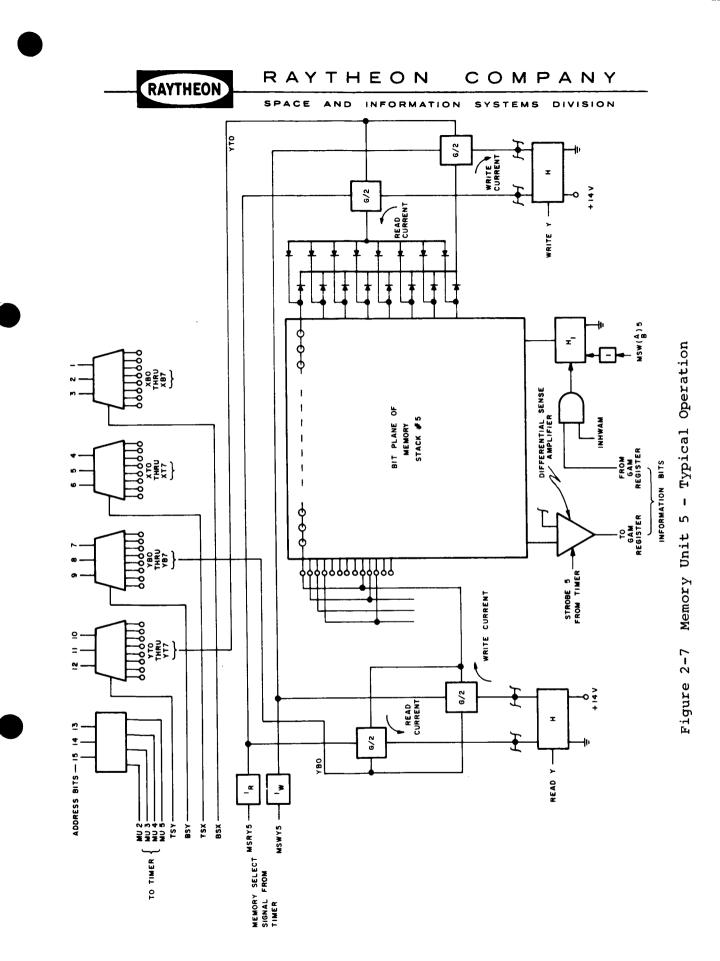

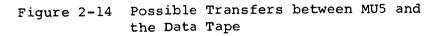

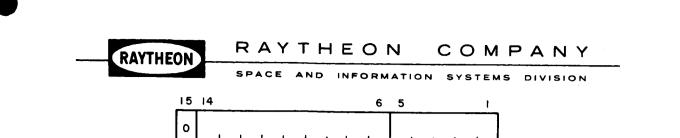

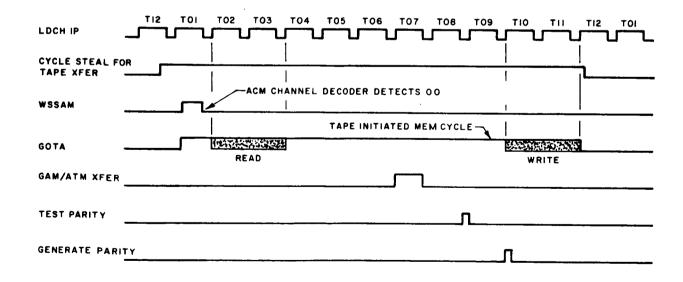

#### Page 2 - 6ACM Address Relationship for Tape, Fixed and Erasable 2 - 132-7 2 - 142-8 2-15 2-9 2 - 182 - 102 - 192-11 2 - 212 - 122 - 302 - 13Possible Transfers from Program Tape to ACM Stack . . . 2 - 342-14 Possible Transfers between MU5 and the Data Tape ... 2 - 362 - 152-38 2-16 2 - 472-17 TAPE/ACM Memory Cycles ..... 2 - 472-18 2 - 512-19 2-57 RL/WL "Ones" Test (Not Implemented in Engineering 2-20 Model).... 2 - 592 - 212-61 2-22 2 - 633-1 3-3 3-2 3-4 3-3 3 - 53 - 43-6 4-1 4-3 4 - 24 - 44-3 Execution of Verb 06 . . . . . . . . . . . . . . . . . 4-6 4-4 Execution of Verb 14 . . . . . . . . . . . . . . . . . . 4 - 9Execution of Verb 22 4-5 4 - 11. . . . . .

RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

#### ILLUSTRATIONS (CONTINUED)

| Figure            |                                                            | Page          |

|-------------------|------------------------------------------------------------|---------------|

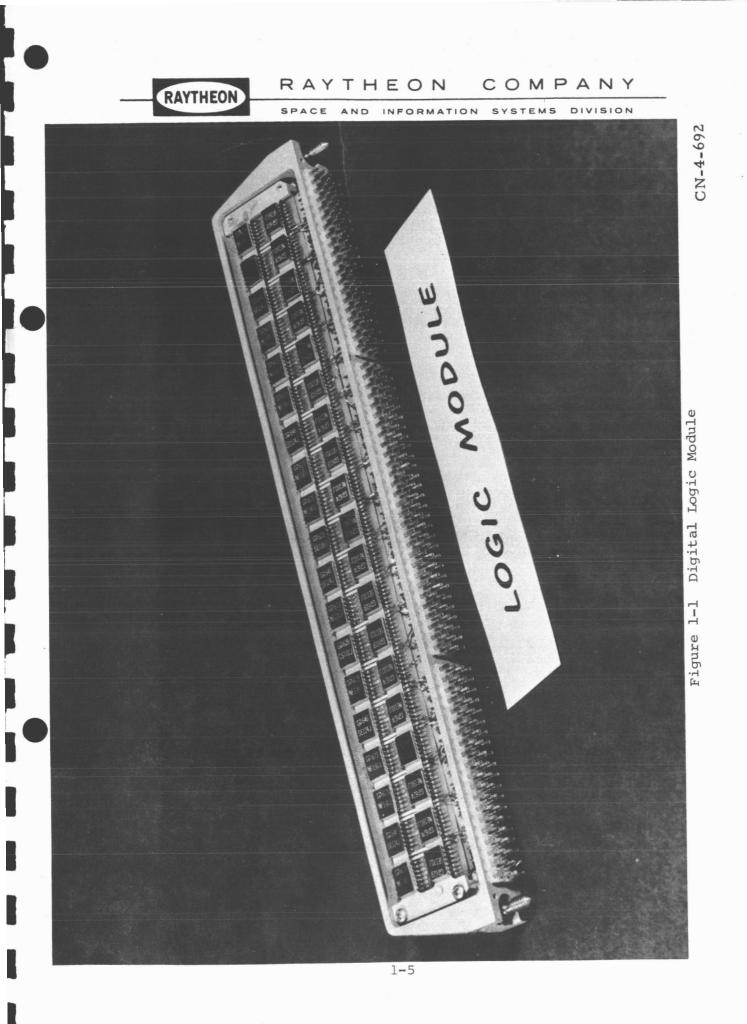

| 1-1               | Digital Logic Module                                       | 1-5           |

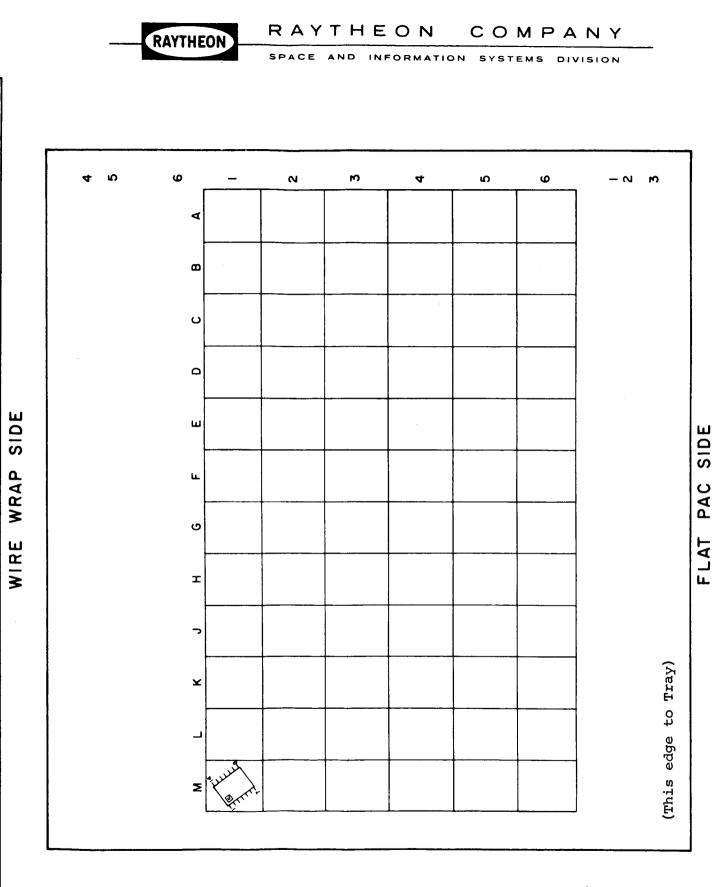

| 1-2               | ACM LHM Breadboard Sideplate Layout                        | 1-8           |

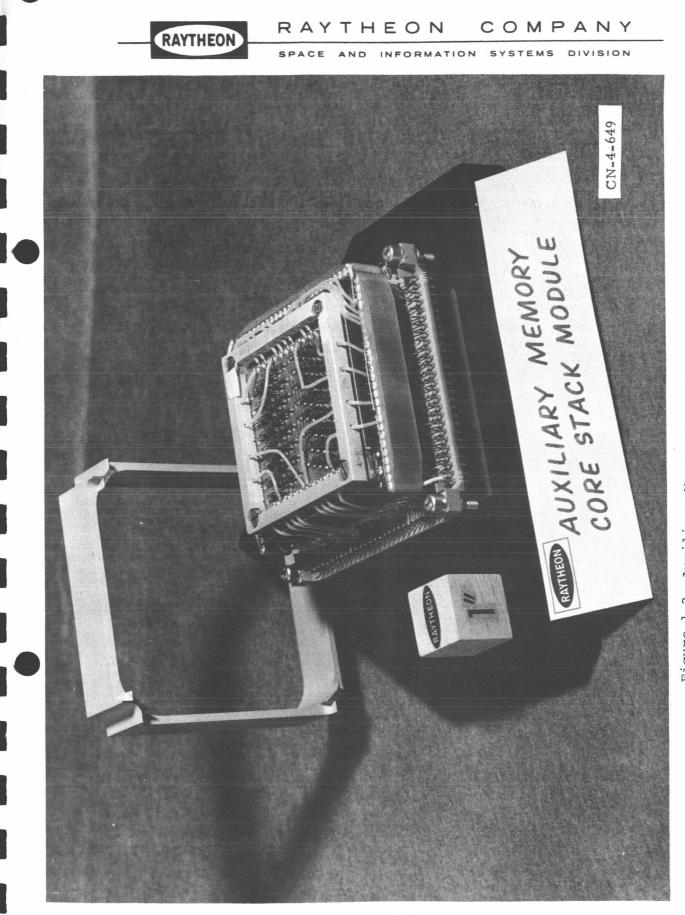

| 1-3               | Auxiliary Memory Core Stack Module                         | 1-9           |

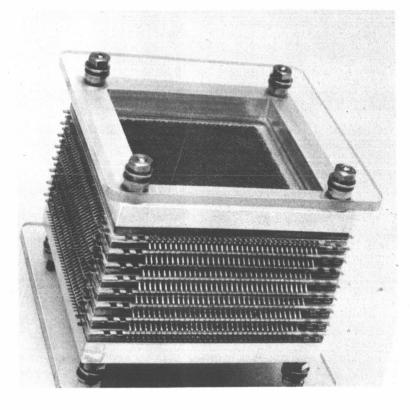

| 1-4               | Militarized Stack for Military/Aerospace Applica-<br>tions | 1-10          |

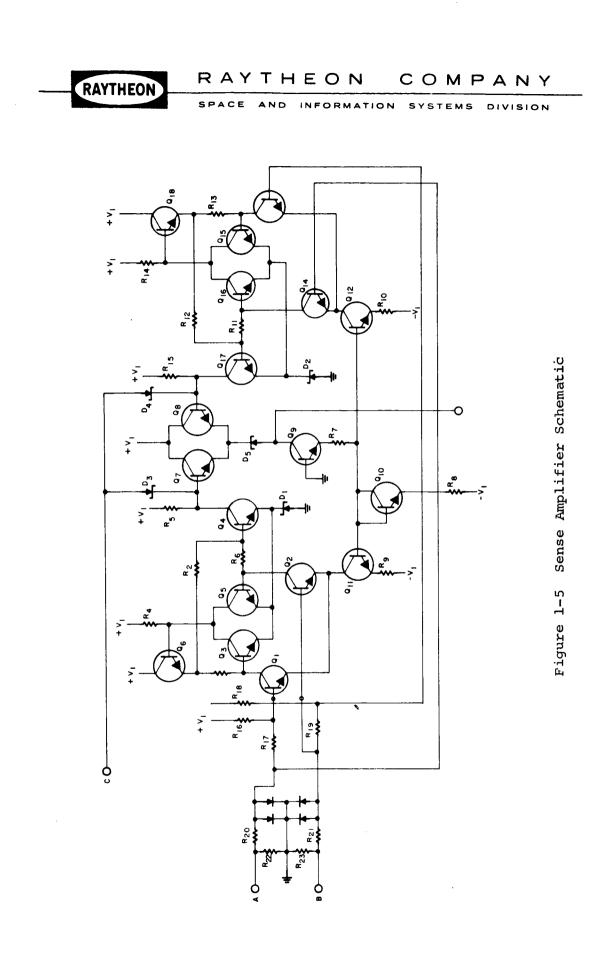

| 1-5               | Sense Amplifier Schematic                                  | 1-12          |

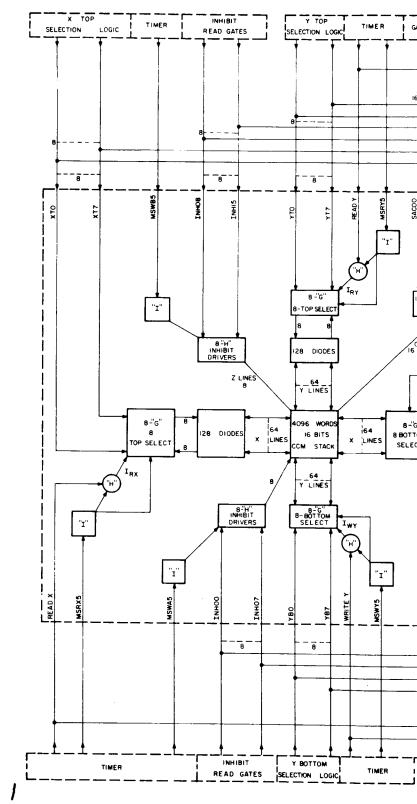

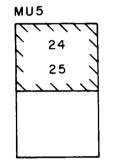

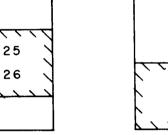

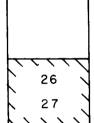

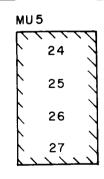

| 1 <b>-</b> 6      | MU System                                                  | 1-13          |

| 1-7               | Discrete Component Module                                  | 1-15          |

| 1-8               | Power Supply Block Diagram                                 | 1-18          |

| 1-9               | Power Supply Characteristics                               | 1-20          |

| 1-10              | ACM Prototype Power Supply, Top View                       | 1-22          |

| 1-11              | ACM Prototype Power Supply, Bottom View                    | 1-23          |

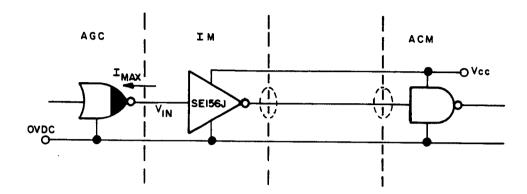

| 1-12              | AGC to ACM Signal Interface                                | 1 <b>-</b> 25 |

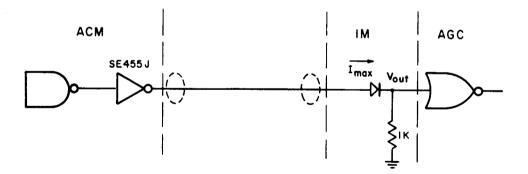

| 1-13              | ACM to AGC Signal Interface                                | 1-25          |

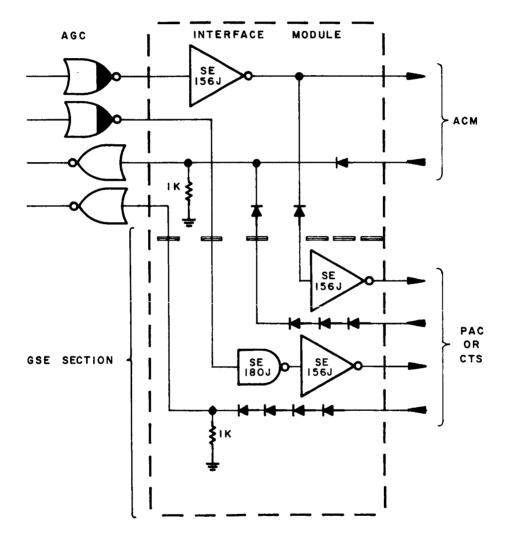

| 1-14              | AGC to GSE Interface Signals                               | 1 <b>-</b> 26 |

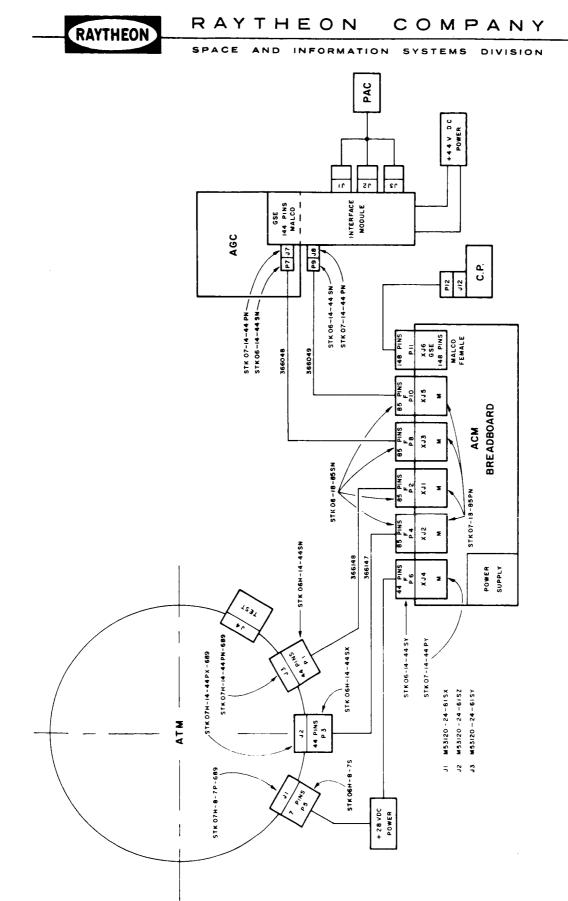

| 1-15              | Wiring Diagram - ACM, ATM, and AGC                         | 1-29          |

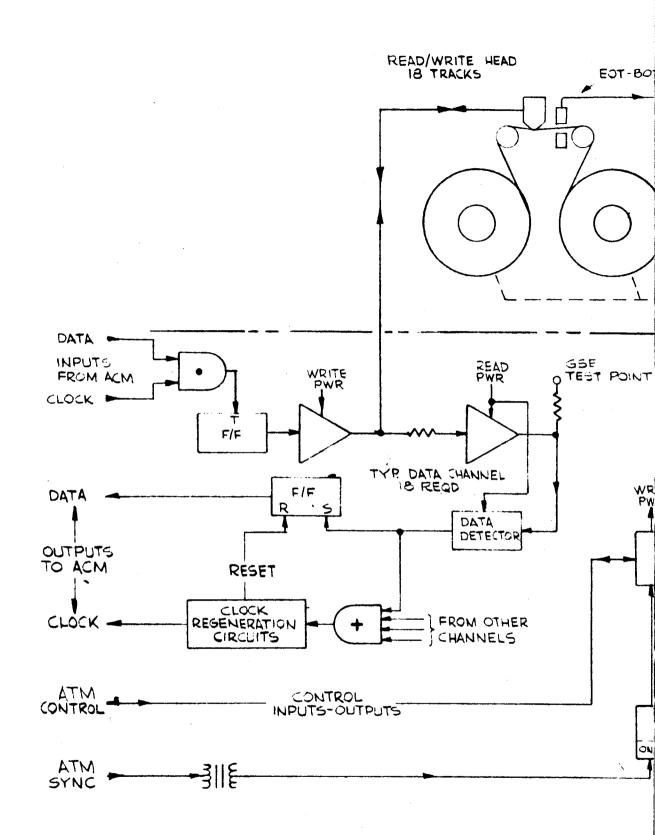

| 1-16              | System Block Diagram: Apollo DVT/ATM                       | 1-30          |

| 1 <del>-</del> 17 | Read/Write Electronics: Apollo DVT/ATM                     | 1-33          |

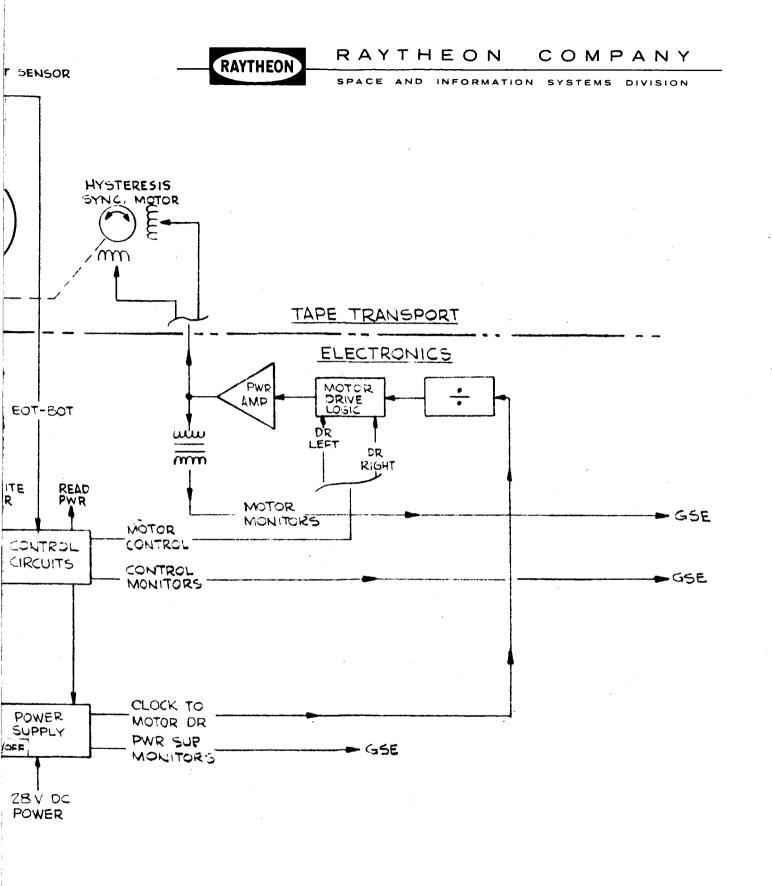

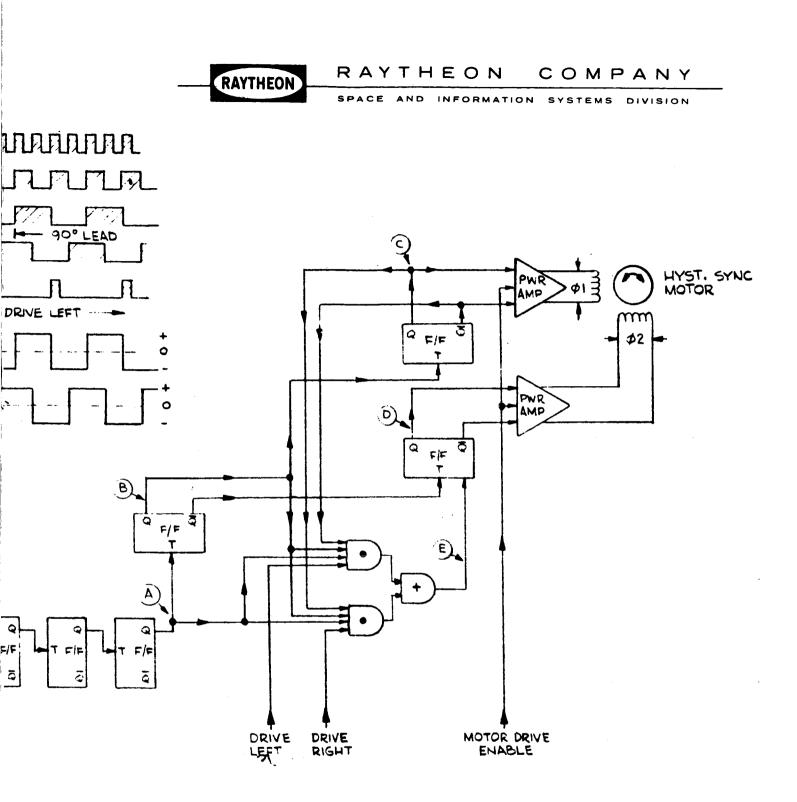

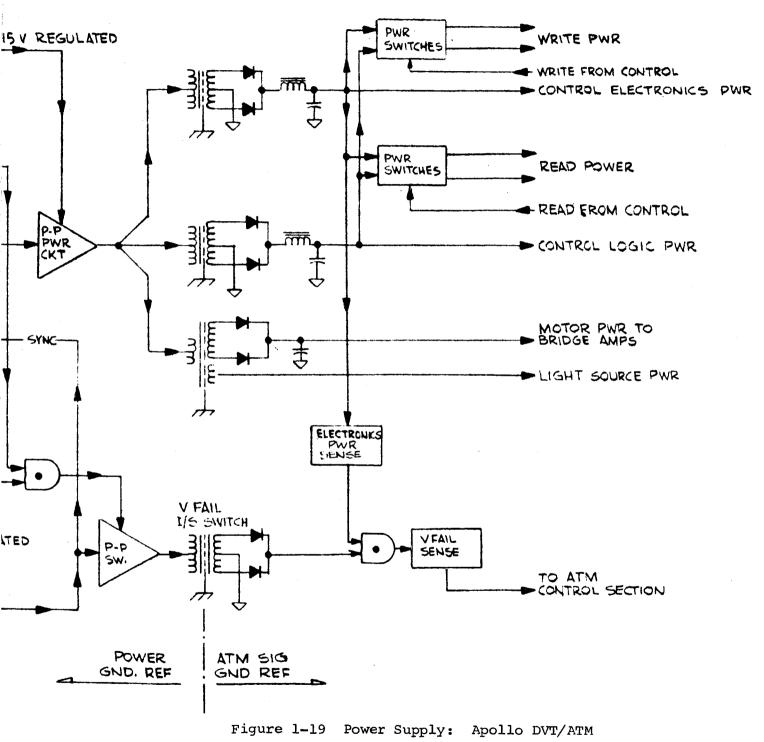

| 1-18              | Motor Drive and Control: Apollo DVT/ATM                    | 1-39          |

| 1-19              | Power Supply: Apollo DVT/ATM                               | 1-40          |

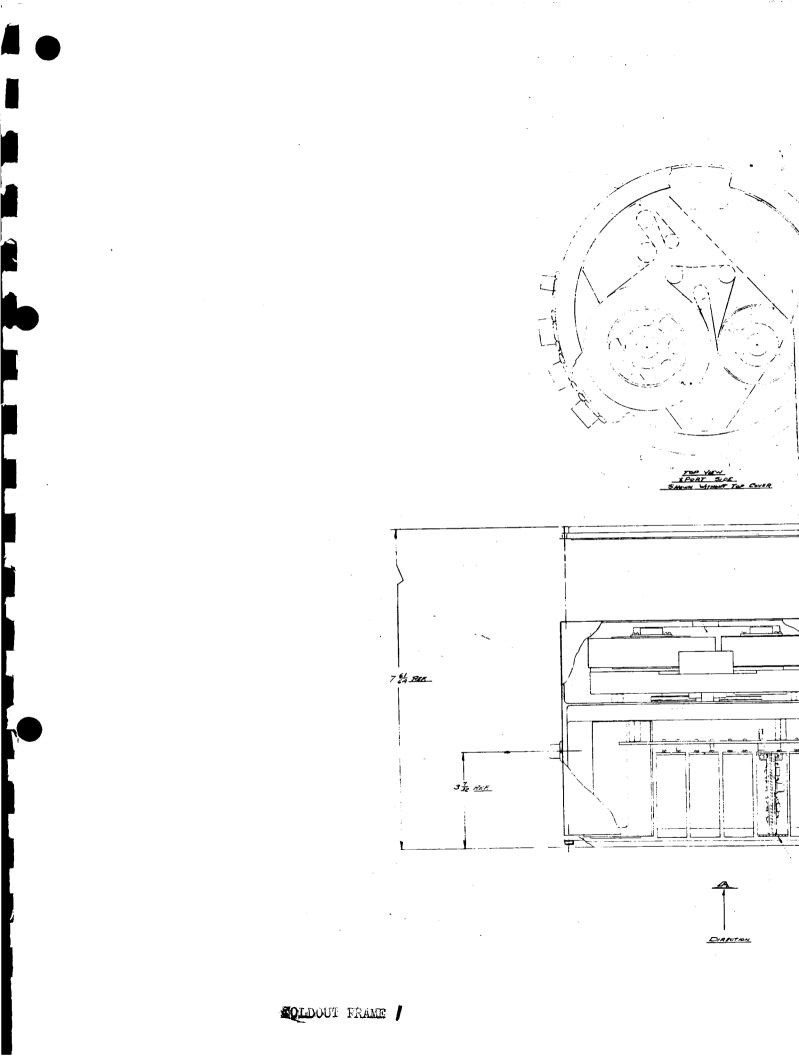

| 1-20              | Outline and Installation: Apollo DVT/ATM                   | 1-43          |

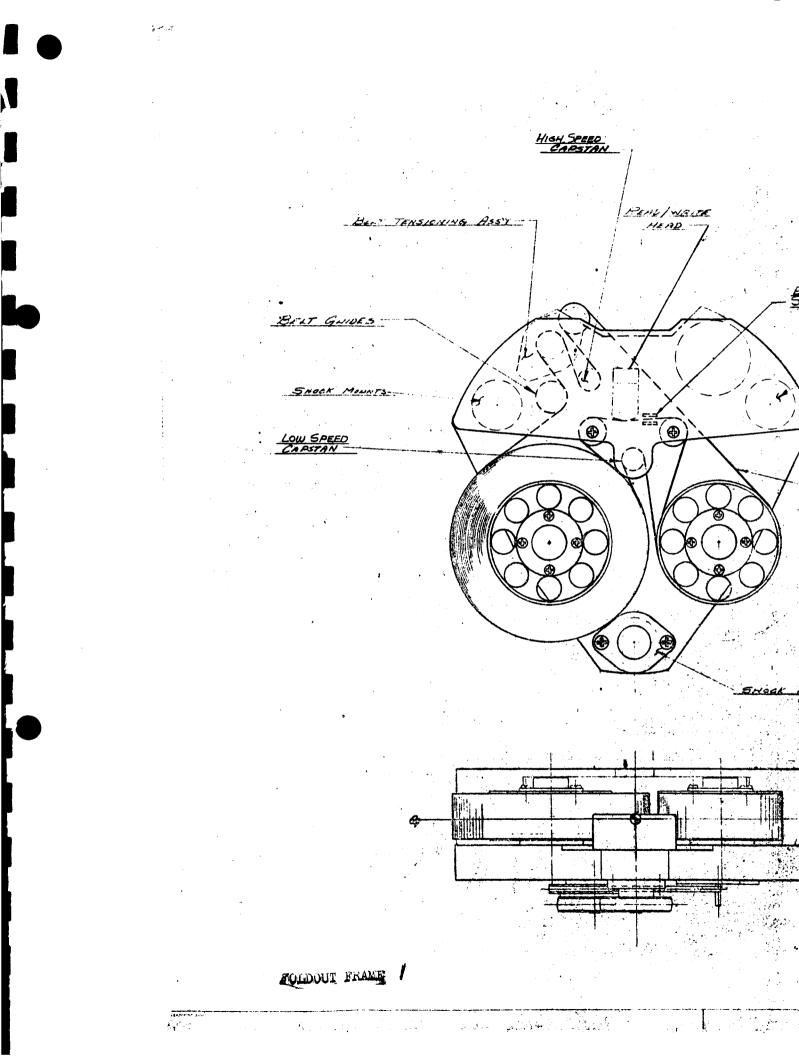

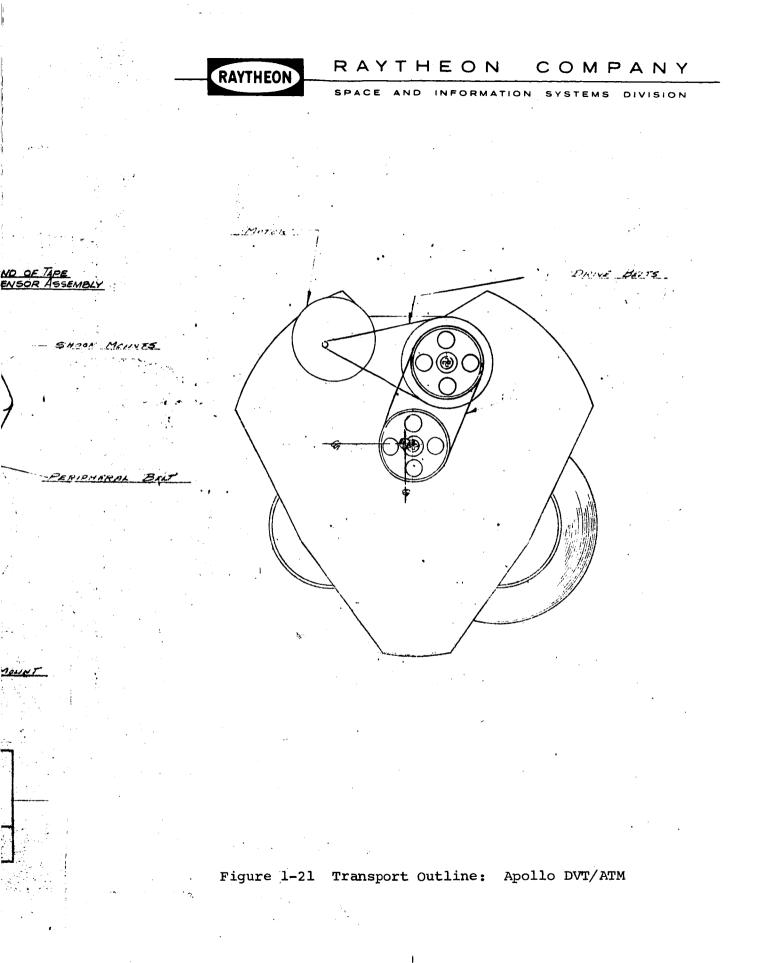

| 1-21              | Transport Outline: Apollo DVT/ATM                          | 1-45          |

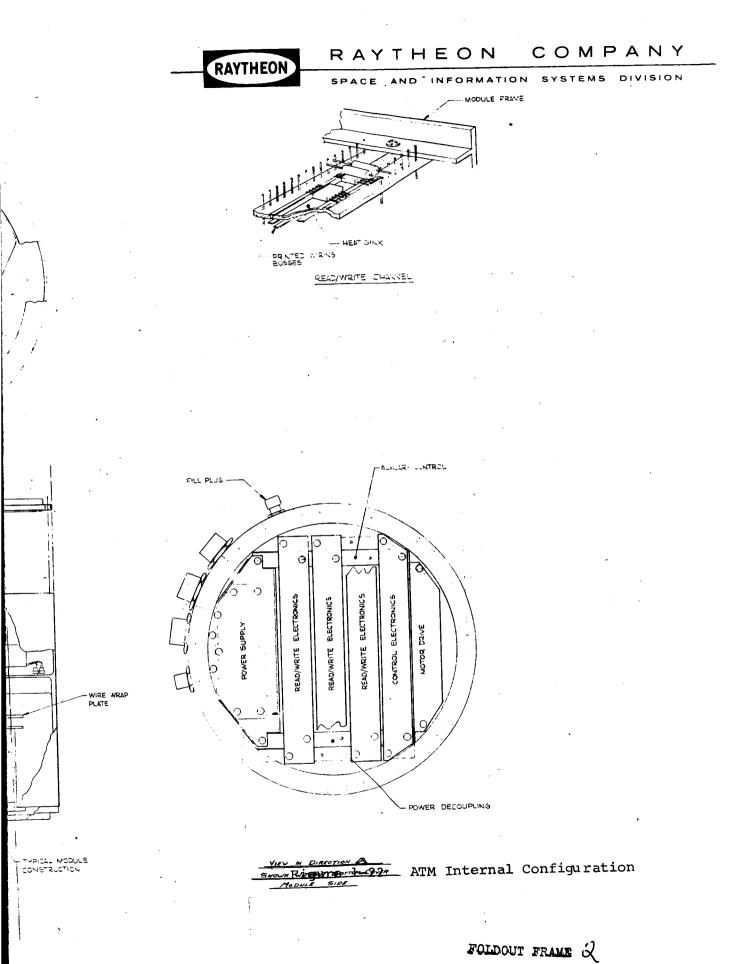

| 1-22              | ATM Internal Configuration                                 | 1-49          |

| 1-23              | Control Panel                                              | 1-50          |

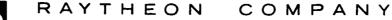

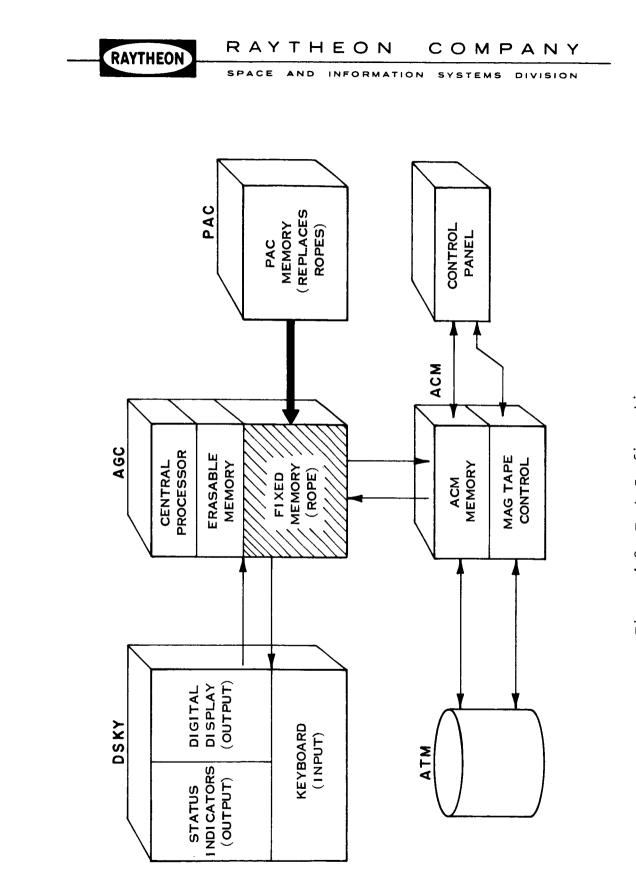

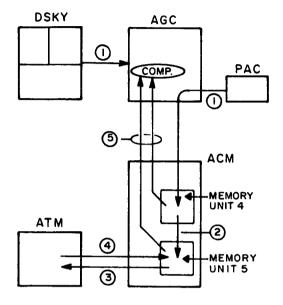

| 2-1               | Functional Block Diagram                                   | 2-2           |

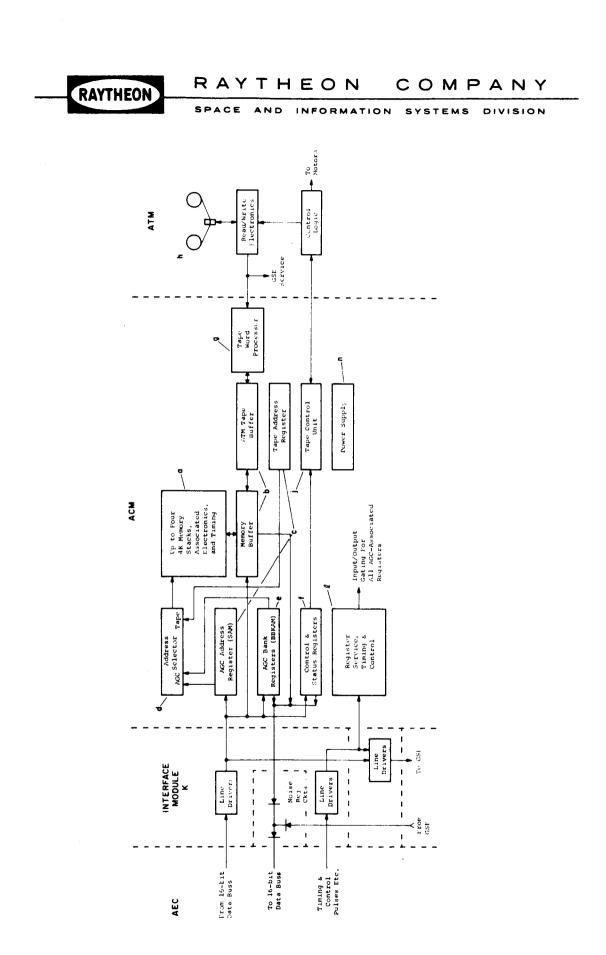

| 2-2               | Detailed System Organization                               | 2-4           |

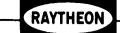

| 2-3               | Bit Assignments when Reading Channels 20 and 21            | 2-10          |

| 2-4               | Auxiliary Memory Sense Amplifier Module                    | 2-11          |

| 2-5               | AM Electronics Module                                      | 2-12          |

RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

#### TABLES

| Number |                                  | Page          |

|--------|----------------------------------|---------------|

| 1-1    | Logic Modules                    | 1-3           |

| 1-2    | IM Printed CKT Board Type        | 1 <b>-</b> 28 |

| 2-1    | ACM Channel Addresses            | 2-9           |

| 2-2    | AGC and AM Addresses             | 2-23          |

| 2-3    | Bits 15 and 14 Under GSE Control | 2-41          |

| 2-4    | ACM Failure Chart                | 2 <b>-</b> 54 |

| 3-1    | Program ID Numbers               | 3-10          |

|        |                                  |               |

PACE AND INFORMATION SYSTEMS DIVISION

#### FOREWORD

This document is the final report submitted in accordance with the requirements of Contract NAS-9-5994.

The program conducted under this contract began as a feasibility exercise to demonstrate that the Apollo Guidance Computer (AGC) could be augmented with additional fixed memory, supplemented by a tape recorder.

Subsequent redirection to configure the system for possible use on an early flight resulted in the Auxiliary Tape Memory (ATM) being fabricated to standards much higher than a feasibility demonstration would require.

As work progressed, additional requirements were imposed on the system, principally the augmentation of AGC erasable memory.

This report contains a description of the hardware designed and developed under this contract, together with a description of the system design leading up to the hardware.

Material has been included which describes the operation of the system from a software point of view; a "programmer's guide" to the AM.

Demonstration of the system was an important contract milestone; the test objectives, configuration, and method of accomplishing the objectives have been incorporated in the report.

Several appendices contain significant supplementary information, including (in a separate volume) complete listings of the demonstration test programs.

viii

SPACE AND INFORMATION SYSTEMS DIVISION

#### **SECTION 1**

#### UNIT DESCRIPTION

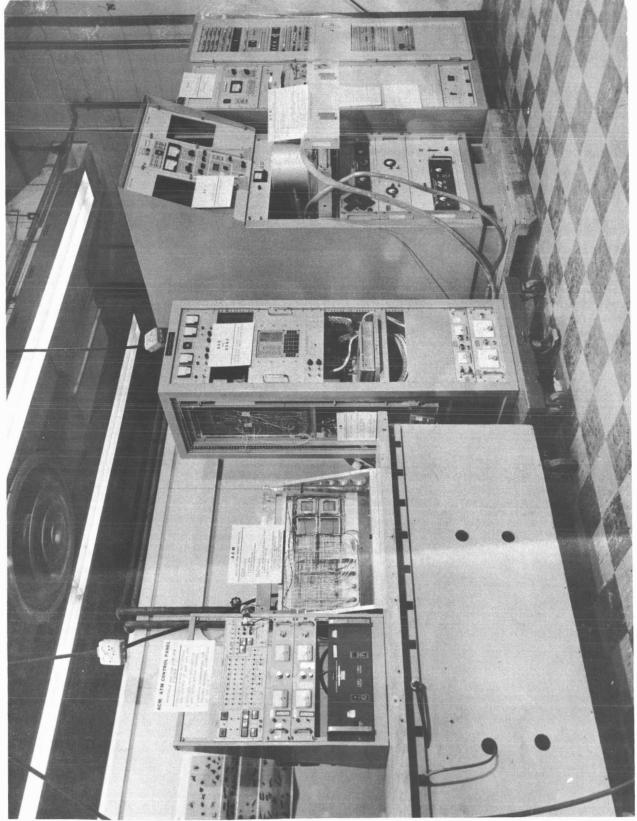

The Auxiliary Memory (AM) system is composed of three units: the Auxiliary Core Memory (ACM), Auxiliary Tape Memory (ATM) and the Interface Module (IM). In addition, a portable control panel is used for monitoring and testing purposes.

The engineering model of the ACM is of brassboard construction with the logic modules, memory electronics modules and the power supply modules mounted on the same tray.

The ATM, supplied by Raymond Engineering Laboratory, Inc., Middletown, Connecticut, includes a magnetic tape transport with motor drive electronics, record/playback electronics and a self-contained power supply.

The IM is of open breadboard construction, although the printed circuit boards incorporated are suitable for flight use. The breadboard version of the IM includes not only circuits to service the ACM in flight, but also the circuits required for operation of GSE; these additional circuits would not be included in flight but would be contained in a separate piggy-back adapter.

The Control Panel (CP) is to be used as a monitoring device, particularly in the area which is inaccessible to the AGC; as a debugging aid; and as a tape preparing device for loading programs and the initial ID words. The panel with its electronics (which are easily removable for maintenance) fits in a suitcase type cabinet ("Transicase").

#### 1.1 AUXILIARY CORE MEMORY

RAYTHEON

#### 1.1.1. LOGIC

The logic elements used in the AM system are composed of a readily available family of Signetics low power (NE 400 series) and medium power (NE 100 series) monolithic integrated circuits. The units

SPACE AND INFORMATION SYSTEMS DIVISION

in the engineering model are a commercial quality and operate over a temperature range of  $0^{\circ}$  to  $70^{\circ}$ C. Over 90 percent of the logic will utilize the NE 100 series while the NE 400 series line driver will be used mainly for ACM to AGC line drivers. The NE 100 series employs diode transistor (DTL) inputs for fan-in expansion capabilities, both active outputs (transistor pull-up) for driving high capacitive loads such as signal layer and multilayer boards, and resistor pull-up outputs for allowing the use of collector logic. The various members of the 100 series offer medium power, high speed and logic flexibility. The NE156 line driver is being used in the IM to interface with the AGC blue-nose gate (1006394) which offers greater speed for the AGC output signals.

RAYTHEON

All digital functions of the ACM are mechanized with integrated circuits. The micro-circuits are packaged in the familiar flat pack unit with 14 connector pins. The flat pack units are organized in three different kinds of modules; the low header, the extended low header, and the Deep Submergence mother-board header. See Table 1-1 for a listing of the logic modules.

The extended header is similar to the low header shown in Fig. 1-1 except that one half of the module has been extended to expose the signal layers on both sides for quick repair. The flat pack units are organized in sub groups of 19, arranged in a single row so that the gates are interconnected with a Signal Layer Matrix. Two rows are arranged on the module side and 276 module connector pins are made available to the 76 flat packs. The flat packs are mounted directly to the heatsink frame with 0.004 inch thick epoxy resin adhesive. The leads are parallel gap soldered to conductor pads on a universal Printed Circuit Board which is mounted to the opposite side of the heatsink frame. The Signal Layer Matrix assemblies are parallel gap soldered to the printed circuit board on the side opposite to the flat packs, and welded jumper wires accomplish the connection from the Printed Circuit Board to the module connector pins. It is essential to high speed computer operation that capacitances are minimized. The largest contributor to

l

## RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

#### TABLE 1-1

#### LOGIC MODULES

| Module<br>No. | Schematic<br>No. | Logic<br>Half<br>Module<br>No. | Туре                | Function                                                                                                                                                     |

|---------------|------------------|--------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A02           | 194858           | 13                             | Extended<br>Header  | Tape Data Transmitter,<br>TW Parity Gen                                                                                                                      |

|               | 366152           | 14                             |                     | GSE Interface Line Drivers                                                                                                                                   |

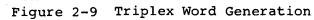

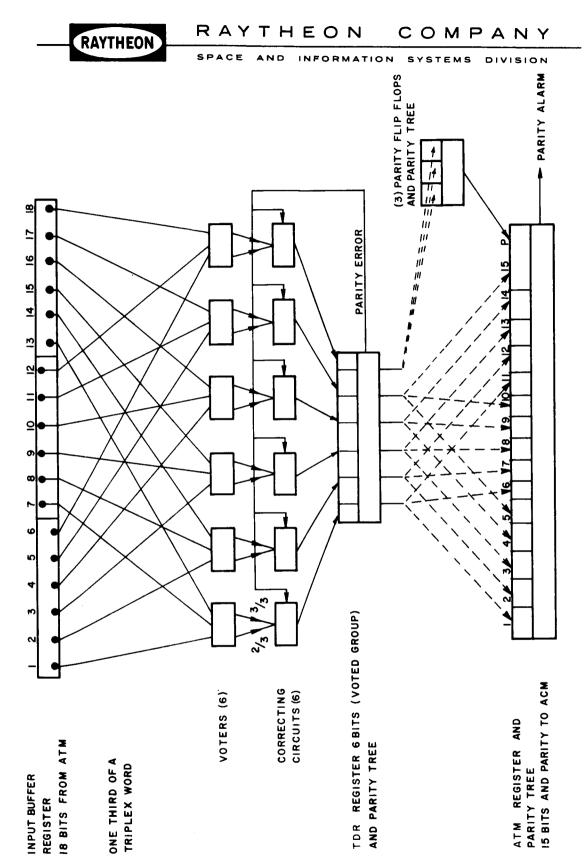

| A03           | 194835           | 11                             | Extended<br>Header  | Tape Data Receiver; Input<br>Buffer                                                                                                                          |

|               | 194982           | 12                             |                     | Tape Data Receiver;<br>Agreement Det.Voters, Out-<br>put Buffer                                                                                              |

| C04           | -                | -                              | DS Mother-<br>board | Control-mastercounter,<br>RATM, WATM, AMLDCH, POWER<br>SUPPLY CONTROL, AMRDCH,<br>MSTRT, COIN04                                                              |

| C05           | -                | -                              | DS Mother-<br>board | Control-CONOUT REG, NBL<br>GAP, IDREC, INST.COUNT.,<br>TIME COUNT, TRNSIP, WRITE-<br>COUNT, TRSN, FF's., GOFWD/<br>REV, READ, WRITE, INCID,<br>END, EOBNKFL. |

| A06           | 194764           | 3                              | Low Header          | IDREAD, IDSTART, IDSTOP,<br>COMPARATOR, STOPWT, STOPRD,<br>RD=ST, WIDST                                                                                      |

|               | 194771           | 4                              |                     | COMPARATOR, CHOOO, IDREAD,<br>IDSTART, IDSTOP, RD ∠ST,<br>AMADDR, WGAMWL                                                                                     |

| A07           | 194553           | 5                              | Extended<br>Header  | RL DRIVERS, RLWLCOMP.<br>COIN 12, 13, 14                                                                                                                     |

|               | 194570           | 6                              |                     | RL DRIVERS, RLWLCOMP.<br>RCH20, 21, 25, 23                                                                                                                   |

| A08           | 365733           | 9                              | Extended<br>Header  | RGAM GENERATION, COIN 5, 6,<br>7,8,9,10,15 SSAM 9-12,<br>WGAMATM, NBLATMFLI, RCHAM                                                                           |

|               | 194459           | 10                             |                     | ATM, TADDR, TW PARITY GEN.                                                                                                                                   |

| A09           | 194467           | 1                              | Extended<br>Header  | GAM,GAM PARITY,WCHAM,SAM,<br>EBAM,FBAM, FEAM, CHANNEL                                                                                                        |

|               | 365322           | 2                              |                     | ADDRESS DECODER                                                                                                                                              |

.....

## RAYTHEON COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

## TABLE 1-1 (Continued)

LOGIC MODULES

| Module<br>No. | Schematic<br>No. | Logic<br>Half<br>Module<br>No. | Туре                | Function                                                                                 |

|---------------|------------------|--------------------------------|---------------------|------------------------------------------------------------------------------------------|

| T10           | -                | -                              | DS Mother-<br>Board | MEMORY TIMING, PH1, PH2,<br>& 12.8 kHz frequency<br>generation. Tape Deskewing<br>Logic. |

| All           | 194635           | 7                              | Low<br>Header       | MEMORY ADDRESS DECODERS,<br>INHIBIT DRIVERS                                              |

|               | 194679           | 8                              |                     | MEMORY ADDRESS DECODERS,<br>INHIBIT DRIVERS                                              |

SPACE AND INFORMATION SYSTEMS DIVISION

the total capacitance on any one signal is the path length, a function of how the flat packs are connected. Signal Interconnections within the module are incorporated with a Signal Layer Matrix and a universal Printed Circuit Board. The matrix assembly consists of "signal layers" of nickel, machine stamped from nickel strip to the required network configuration. The strips are positioned as layers in a plastic case or envelope and insulated from each other with mylar tape. Studies and worst case analysis tests evaluated the capacitances of a Signal Layer Matrix assembly as under the limit required for high speed operation of the logic devices selected. The signal paths from the flat pack connector pins and the module connector pins to the Signal Layer Matrix are accomplished with a universal, etched nickel, double sided Printed Circuit Board utilizing plated through holes. This item is simple in construction, uses generally standard fabrication techniques, can be inspected easily and is reliable and inexpensive.

RAYTHEON

The universal module mounting frame is a magnesium alloy structural member which supports heat transfer by conduction and holds the 276 module connector pins. Captive jacking screws, one at each end, mount the module to the chassis forcing engagement of the module connector pins with mating connector pins in the chassis. A high-dielectric coating is applied to all parts of the frame requiring electrical isolation from the electronic and signal carrying components. All electronic components receive a 15 mil thick conformal coating to provide environmental protection. It is apparent that all connections are readily accessible, a prime factor in diagnosis, repair, and replacement producing a low cost and highly reliable Digital Module design.

For a detailed description of the pin and flat pack configuration on the low and extended header logic modules see ACM dwg. 189623.

Control Modules CO4, CO5, and the ACM Timer Tl0 were built on a mother board side plate and mounted to an ACM header. Twelve printed circuit boards each containing 6 flat packs are soldered to one side of the side plate; interconnections are made on the reverse side with wire

# SPACE AND INFORMATION SYSTEMS DIVISION

wrap connections. The flat pack layout and pin configuration of these modules is shown in Fig. 1-2.

#### 1.1.2 MEMORY SYSTEM

The Memory System consists of two Core Stack Modules, two Sense Amplifier Modules, and four Memory Electronics Modules. Expansion of the Memory System to twice its current capacity is possible by doubling the above complement of modules. The memory system is capable of receiving or returning data to the GAM register as instructed by Auxiliary Memory logic.

#### 1.1.2.1 Core Stack Module

The Core Stack Module consists of a magnesium header shaped as a square box, in which the memory Core Stack is contained. The sides of the header are stepped, and on three sides resistor blocks containing a total of sixty-four resistors are located within the step. The stack also includes diode boards mounted on top and bottom containing a total of 256 diodes. The module is mounted on the ACM tray, making contact only at the four corner points of the step in the module header.

The cores selected for use in this array are 30-mil lithium ferrite with fast switching time, wide temperature range ( $-55^{\circ}C$  to  $+100^{\circ}C$ ), and low temperature coefficient.

Each core stack contains 4096 16-bit words (see figure 1-3). This stack is organized as a 3-D coincident current, 4-wire (x, y, sense & inhibit) memory. The array is configured as a 64 x 64 x 16 matrix mounted on eight double-sided planes. Each plane provides two word-bits of storage with a given side containing a single word bit for the entire 4096 words.

The basic stack configuration is packaged in a 4 inch x 4 inch frame to which mount two mats of 4096 cores, one mat per side. Eight frames are stacked vertically along with a top and bottom end frame (Figure 1-4). The device is then sandwiched together with four tie bolts, one in each corner. The required diode decoding matrices are mounted on

FOLDOUT FRAME

|   |            | •        |          |                | 1     |            |            |                | 1                                                |            |     | 1           |        |     | ,             |   |        |     | 1              |          |            |          |        |

|---|------------|----------|----------|----------------|-------|------------|------------|----------------|--------------------------------------------------|------------|-----|-------------|--------|-----|---------------|---|--------|-----|----------------|----------|------------|----------|--------|

|   | <b>N</b> O | 0        | 0        | ≌0%0%+¥        | +::+  | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | +   +         | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | 0        | 0        | 20             | - 2+  | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | +              |          |            |          | +      |

| Σ | mΟ         | 0        | 0        | -              |       |            | 12         |                |                                                  | Σ          |     |             | Δ<br>4 |     |               |   | Σ      |     |                |          | <b>M</b> 6 |          |        |

|   | ∾ 0        | 0        | 0        | ≊o ≊           | °2+   | +          | Σ          | +              | +                                                | ~          | +   | +           | ~      |     | +   +         |   | ~      | +   | +              |          | ~          |          | +      |

|   | - 0        | 0        | 0        | =0505+4        | +ត+   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | +   +         | + | +      | + + | +              | +        | +          | +        | +      |

|   | ົດ         | 0        | Ó        | 00+            | + +   | + +        | +          | + +            | + +                                              | • +        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | 0        | 0        | 0              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | +              |          |            |          | +      |

| L | mΟ         | 0        | 0        | _              |       |            | 2          |                |                                                  | ر<br>د     |     |             | 4      |     |               |   | г<br>2 |     |                |          | 9          |          |        |

|   | N 0        | 0        | 0        | •              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   | _      | +   | +              |          | -          |          | +      |

|   | - o        | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | +   +         | + | +      | + + | +              | +        | +          | ÷        | +      |

|   | 50         | Ö        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | 0        | 0        | 0              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | +              |          |            |          | +      |

| ¥ | юO         | 0        | 0        | -<br>¥         |       |            | K2         |                |                                                  | N<br>X     |     |             | Х<br>4 |     |               |   | Υ<br>Ω |     |                |          | ¥6         |          |        |

|   | N 0        | 0        | 0        | o —            | +     | +          | _          | +              | +                                                | _          | +   | +           | -      |     | +   +         |   | -      | +   | +              |          |            |          | +      |

|   | - 0        | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | +   +         | + | +      | + + | +              | +        | +          | +        | +      |

|   | 50         | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | 0        | 0        | 0              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | +              |          |            |          | +      |

| 7 | юo         | o        | 0        |                |       |            | JZ         |                | 1                                                | M          |     |             | 4      |     |               |   | 15     |     |                |          | J6         |          |        |

|   | ~ 0        | 0        | 0        | ^ ۲            | +     | +          | ,          | +              | +                                                | r          | +   | +           | ,      |     | +   +         |   | 1      | +   | +              |          | ,          |          | +      |

|   | - 0        | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    |     | +   +         | + | +      | + + | 1              | +        | +          | +        | +      |

|   | 50         | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | +          | + + | +           | + +    | +   | +   +         | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | o        | o        | 0              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | +              |          |            |          | +      |

| I | mО         | o        | 0        | -              |       |            | ₽          |                | 1                                                | n          |     |             | 4      |     |               |   | 5      |     | Ľ              |          | 9          |          |        |

|   | NO         | o        | 0        | ₀≖             | +     | +          | I          | +              | +                                                | I          | +   | +           | I      |     | +   +         |   | I      | +   | +              |          | I          |          | +      |

|   | - 0        | o        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    |     | + +           | + | +      | + + | 1              | +        | +          | +        | +      |

|   | 50         | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | 0        | 0        | o              | +     | +          |            | +              | +                                                |            | +   | +           |        |     | +   +         |   |        | +   | 1+             |          |            |          | +      |

| 9 | mо         | 0        | 0        | -              |       |            | 2          |                |                                                  | M          |     |             | 4      |     |               |   | ŝ      |     |                |          | 9          |          |        |

| _ | NO         | 0        | 0        | ്റ             | +     | +          | U          | +              | +                                                | G          | +   | +           | G      |     | +   +         |   | c      | +   | 1.             |          | G          |          | +      |

|   | - 0        | 0        | ō        | 00+            | + +   | + +        | +          | + +            | + +                                              | +          | + + | ļ.          | + +    |     | + +           | + | +      | + + |                | +        | +          | +        | +      |

|   | 00         | 0        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | • •        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | <u>,</u> |            | +        | •<br>• |

|   | 40         | 0        | ō        | 0              | +     | +          |            | +              | +                                                | •          | •   | ļ.          | • •    | •   | • +           | • | •      |     | 1              |          | Ŧ          | •        | ,<br>, |

| L | юo         | 0        | 0        | -              |       |            | 2          | •              | 1                                                | m          |     | Ľ           | 4      |     | Ϊ.            |   | ŝ      |     | 1              |          | 9          |          | *      |

|   | NO         | 0        | 0        | ۰ <sup>۱</sup> | +     | +          | <b>L</b> . | +              | +                                                | L.         | +   | ↓           | Ľ.     |     | +   +         |   | LL.    |     |                |          | ш          |          |        |

|   | - 0        | 0        | 0        | 00+            | + +   | • •        | +          | + +            | ļ                                                |            |     | L.          | + +    |     | +   +         |   | ÷.     | + + |                | -        |            | -        | •<br>• |

|   | <u>v 0</u> | 0        |          | 00+            | + +   | + +        | +          | + +            | + -                                              | + +        | + + | <u>†</u> ∔  | + +    |     | $\frac{1}{1}$ |   | +      | + + | +              |          | +          | <u>+</u> | +<br>+ |

|   | 40         | 0        | 0        | 0              | +     | +          |            | · +            | +                                                |            | • • | ļ.          | •••    |     | +   +         | • | •      | . + | 1              |          | •          | •        | -<br>- |

| ц | mО         | 0        | 0        | -              |       |            | 2          |                | 1                                                | ъ          | •   | Ľ           | 4      |     | 1.            |   | ŝ      | •   | Ľ              |          | 9          |          | Ŧ      |

|   | NO         | 0        | 0        | ы<br>О         | +     | +          | ш          | +              | 1                                                | ш          | +   | 1+          | ш      |     | +   +         |   | ш      | +   | 1              |          | ш          |          |        |

|   | - 0        | õ        | 0        | 00+            | + +   | + +        | +          | + +            | + +                                              | + +        | + + | <b> </b>    | + +    |     | +   +         | + | +      | + + |                | ÷        | +          | Ŧ        | +<br>+ |

|   | 50         | 0        | 0        | 00+            | + +   | + +        | +          | + +            | +                                                | +          | + + | t÷          | + +    |     |               |   | +      | + + | +              | -        | -          | +        | +      |

|   | 40         | 0        | 0        | 0              | +     | +          | •          | + +            | +                                                |            | + + | I.          |        | ÷.  | []]           | ٣ | Ŧ '    |     | 1.             | *        | -          | т        | ≁<br>1 |

|   | мО         | 0        | 0        | _              | •     | Ŧ          | 2          | *              | ľ                                                | ю          | -   | 1           | 4      |     | + +           |   | ŝ      | +   | +              |          | 9          |          | +      |

|   | NO         | 0        | 0        | ° 0            | _     |            | ٥          |                | 1.                                               | ö          |     |             | Ó      |     | .   .         |   | ۵      |     | 1.             |          | õ          |          |        |

|   | -0         | 0        | 0        | 00+            |       | <b>.</b> . | ,          | т т<br>т       | II.                                              |            | +   | IT.         |        |     | []*           |   |        | +   | 1              |          |            |          | +      |

|   | -0-        | 0        | 0        |                |       | + +        | +          | <del>* *</del> |                                                  | · +        | + + | <b> </b> ⁺  | + +    | +   | +             | + | +      | + + | +              | +        | +          | +        | +      |

|   | 40         | -        | 0        | 00+            | + + + | + + +      | +          | * *            | IT 1                                             | •          | + + | 11          | + +    | +   | []†           | + | +      | + + | 1              | +        | +          | +        | +      |

|   |            | 0        |          | 0              | •     | Ŧ          | N          | +              | *                                                | ю          | +   | *           | 4      |     | +   +         |   | ŝ      | +   | 1              |          | 9          |          | +      |

|   | m 0        | 0        | 0<br>0   | ຸບ             | _     |            | ö          |                | Ι.                                               | ö          |     | ١.          | ပိ     |     |               |   | ö      |     |                |          | ő          |          |        |

|   | N 0        | 0        |          |                | +     | т<br>      | ,          | +              | 1.                                               |            | . * | 1           |        |     | * +           |   |        | +   |                |          |            |          | +      |

|   | - 0        | <u> </u> | <u> </u> | 00+            |       | + +        | +          | + +            | + - 1                                            | + +        | + + | <u> </u> ⁺. | + +    | + · | +++           | + | + ·    | + + | ++             | +        | +          | +        | +      |

|   | 50<br>110  | 0        | 0        |                | + +   | + +        | +          | + +            | 1. 1                                             | +          | + + | 1*          | + +    | + · | * +           | + | +      | + + | 1*             | +        | +          | + ·      | +      |

|   | 40         | 0        | 0        | ° _            | +     | +          | 2          | +              | 1                                                | ю          | +   | 1*          | 4      | •   | + +           |   | ŝ      | +   | 1+             |          | 9          |          | +      |

|   | mo         | 0        | 0        | 0              |       |            | ä          |                | Ι.                                               | 6          |     | 1.          | à      |     |               |   | 60     |     | 1              |          | ã          |          |        |

|   | N 0        | 0        | 0        | 0              | +     | +          |            | . +            | 1.                                               |            | . + | 1*          |        |     | •   +         |   |        | +   | 1              |          |            |          | +      |

|   | - 0        | 0        | 0        | 00+            |       | + +        | +          | + +            | <del>+                                    </del> | +          | + + | <u> +</u>   | + +    | + · | + +           | + |        | + + | - <b>h</b> im- | +        | +          | +        | +      |

|   | <b>n</b> O | 0        | 0        |                |       | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | + - | + +           | + | +      | + + |                | +        | +          | + ·      | +      |

|   | 40         | 0        | 0        | ±0 _           | 2+    | +          | <u>.</u> . | +              | +                                                |            | +   | +           | -      |     | + +           |   |        | +   | +              |          |            |          | +      |

|   | рo         | 0        | 0        | -<br>-         |       |            | A2         |                | I                                                | <b>A</b> 3 |     | 1           | A 4    |     |               |   | A 5    |     | 1              |          | A 6        |          |        |

|   | N 0        | 0        | 0        |                | \$;+  |            |            | +              | +                                                | ,          | +   | +           | -      |     | +   +         |   | -      | +   | +              |          | •          |          | +      |

|   | - 0        | 0        | 0        | =0202+4        | + 5+  | + +        | +          | + +            | + +                                              | + +        | + + | +           | + +    | +   | + +           | + | +      | + + | +              | +        | +          | +        | +      |

|   | 4          | ŝ        | 9        |                |       |            |            |                | •                                                |            |     | 1           |        |     | 1             |   |        |     | 1              |          |            |          |        |

+ + + + + - - 2 4 5

+ 50

+ 10

+ + + + 5 + + 2 +

+ 4 + 10 + 10 + 10 + 10 + 10 + 10

> + 10 + 2 + -+ -+ 5

> > + 4

+---++-0

17 + 17 (1) + 10

+ 💊

+ 4 1 + 10

+ N

+ 4

+ 0 + 10 + + 4

> + ~ + -

₩ + ₩ + ₩ + + + ₩

+

+ I + m + + ∾

Figure 1-2 ACM LHM Breadboard Sideplate Layout

Figure 1-3 Auxiliary Memory Core Stack Module

Militarized Stack for Military/Aerospace Applications

Figure 1-4 Militarized Stack for Military/Aerospace Applications

SPACE AND INFORMATION SYSTEMS DIVISION

printed circuit boards within the top and bottom end frames respectively.

#### 1.1.2.2 <u>Sense Amplifier Module</u>

This module contains sixteen amplifier circuits and a voltage regulator circuit. The electronic parts are staked into the cavities of a magnesium header with RTV-11 epoxy.

The sense amplifier circuit shown in Fig. 1-5 discriminates between "ones" and "zeros" read from the storage array. It uses a dual differential amplifier, threshold-detector combination. This approach has the advantage of eliminating many of the tolerance problems encountered in the design of a sense amplifier. The sense amplifier threshold is determined by external resistors and is practically independent of integrated circuit characteristics. The dual comparator (uA711) is an integrated circuit manufactured by Fairchild. External strobing of the sense amplifier is accomplished in the memory timing logic.

The output of the dual comparator is designed so that a number of them can be wire-OR'ed to provide a common data path from the memory to the GAM buffer register. Up to eight devices can be OR'ed, yet the outputs will still be compatible with the memory buffer logic. In order to make this OR'ing capability possible and hold the device dissipation to satisfactory levels, the sink current of the comparator must be reduced. As a result, at least four devices must be OR'ed before they can provide for a DTL fan-out of one. Two resistive termination blocks are provided in the ACM for reduction of sink current due to the absence of sense amplifier modules for Memory Units 2 and 3.

#### 1.1.2.3 <u>Memory Electronics Module</u>

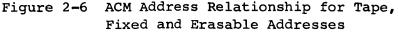

This module contains sixteen selection switch circuits (8 top, 8 bottom), two read/write drivers, eight inhibit drivers, three memory select circuits and two filter circuits. The electrical parts of this module are staked into the cavities of a magnesium header with RTV-11 epoxy. The relation of these circuits to an MU system is shown in Figure 1-6.

COLDOUT FRAME

- . \_

1.1.2.4 <u>Mechanical Description of Sense Amp and Memory Electronics</u> <u>Modules</u>

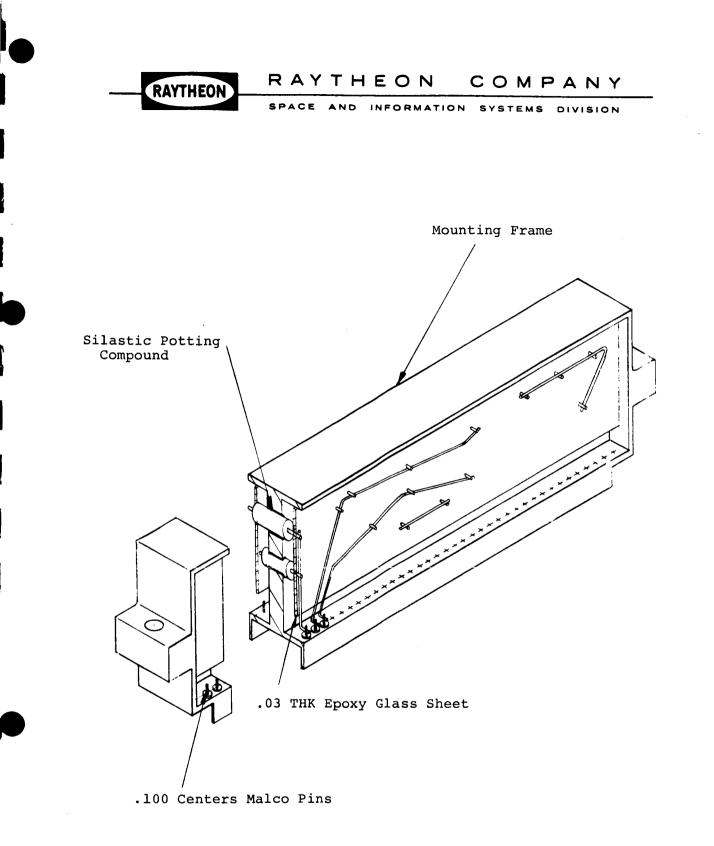

Discrete component modules do not lend themselves to the same kind of mechanized interconnection approach as do the digital type because of the random physical nature of electronic parts and their interconnection; therefore, a greater degree of design flexibility exists. This flexibility is limited somewhat by the size and shape of the digital module which was established in consideration of the many factors involved in packaging high speed, high power, integrated circuits.

The packaging design for the discrete component modules is an adaptation of the welded "cordwood" construction technique, a design governed by thermal considerations and the requirements of high density packaging of non-uniform discrete components. Figure 1-7 is an explanatory sketch of welded "cordwood" construction techniques applied to the Auxiliary Memory Sense Amplifier Module (Figure 2-4) and the Memory Electronics Module (Figure 2-5) manufactured by Raytheon. The component carrying frame is a magnesium alloy structural member that supports heat transfer by conduction. In essence the frame is of I beam construction with a web thickness determined by the thermal dissipation requirements. The frame is C. G. mounted with restraint on 3 edges, and features a high stiffness to weight ratio with resultant high natural frequency. Captive jacking screws, one at each end, mount the module frame to the chassis, forcing engagement of the module connector pins with mating connector pins on the chassis, and providing the necessary bearing pressure required to dissipate the heat to the heatsink.

The components are mounted in machined cavities in the web and the remaining volume is filled with a silastic potting compound to insure minimum thermal resistances between component and frame. This compound surrounds the component on all surfaces contiguous to the frame cavity surfaces. Electrical components having critical operating temperatures are positioned as near as possible to the heat sink. In most cases, signal interconnections are accomplished with two layers of

Figure 1-7 Discrete Component Module

Î

SPACE AND INFORMATION SYSTEMS DIVISION

point to point welded nickel wire interconnections on each side of the module. This technique has a considerable history of use on analog electronics designed and manufactured by Raytheon for the Apollo, Poseidon, and Polaris Guidance systems. Mylar sheets with photographically imprinted signal wiring patterns are used to position the leads of the components for welding and compensate for the random component lengths.

Nickel ribbon welded connections are made from the required circuit points directly to the module connector pins which are identical for all modules.

1.1.3 ACM POWER SUPPLY

RAYTHEON

The power supply consists of two magnetic amplifier controlled dc to dc Converter-Regulators, and three series regulators. It also includes the turn on-off circuitry (OUTCOM-4VSW), 28 Vdc Alarm circuit, ACMON (4.4Vdc logic detect circuit), and the 4.4 V Line Driver turn off circuit. The regulators furnish power to the ACM logic, line drivers, memory, and control functions.

Technical specifications and special features of the power supply include the following:

a. Regulated output voltage over a minimum input voltage range of +19 Vdc to 36 Vdc.

b. Current limiting on the +4.4 Vdc logic and +12 Vdc power supplies. Short circuit protection on the 4.4 Vdc, and +14 Vdc power supplies.

c. High impedance isolation between input and signal ground.

d. Output voltages and regulator specifications are as

follows: Maximum Maximum Average Output Current Ripple Power Voltage Regulation 8 amperes 5% 22 watts +4.4 Vdc (Logic) ± 5% 2.5 amperes 5% 17 watts +12.0 Vdc ± 5%

| RAYTHEON             | RAYTH     | HEON CO          | MPANY        |    |

|----------------------|-----------|------------------|--------------|----|

|                      | SPACE AND | INFORMATION SYST | EMS DIVISION |    |

| + 4.4 Vdc (Line Driv | ver)± 5%  | 0.4 watts        | 0.1 amperes  | 5% |

| +14.0 Vdc            | ± 5%      | 28 watts         | 3.0 amperes  | 5% |

| -5 Vdc               | ± 2%      | 1.9 watts        | 0.7 amperes  | 2% |

The power supply consists of two multivibrators which generate the driving square waves at a frequency of approximately 10 kHz. The multivibrators operate in a free running mode during power turn on and until such time as the ACM logic furnishes the necessary sync pulses. The multivibrator is then synchronized to 12.5 kHz, a countdown frequency of the 1.024 MHz frequency from the AGC. The multivibrator design features low power consumption and minimum change in frequency during variations of the 28 Vdc input.

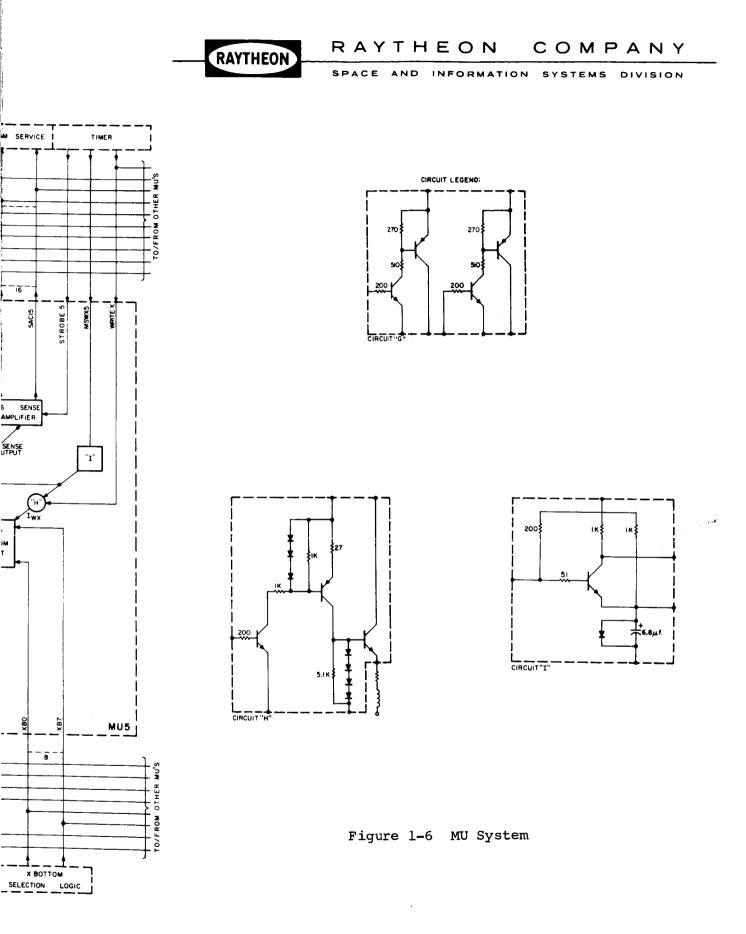

A block diagram of the ACM power supply is shown in Figure 1-8.

With the exception of the magnetic amplifier circuitry, series regulators, and control circuits, the supply circuit configuration is that of a square wave driven dc to dc transformer coupled converter. Line and load regulation for 4.4 Vdc and 14 Vdc supplies is accomplished by generating a symmetrical pulsewidth control signal proportional to the difference between the output voltage (which is converted to current by a precision resistor) and the reference source.

The voltage control magnetic amplifier shunt modulates the base drive of the power amplifier stage, providing the pulsewidth control and summing function for regulation. Short circuit protection is achieved by a series limiting the base drive to the power amplifier stage with a magnetic amplifier which senses the output current.

This magnetic amplifier is normally saturated and has little effect on circuit operation except in the event of an overload condition. In an overload condition the magnetic amplifier regulates the pulsewidth to limit the base drive.

Regulation for the + 4.4 Vdc (Line Drivers), +12V and -5V

RAYTHEON SPACE AND INFORMATION SYSTEMS DIVISION +4.4 VLD +4.4 VDC -5.0000 + 14 VDC ACMON No C Q q Q Q LINE DRIVER SERIES REGULATOR REGULATOR REGULATOR SERIES SERIES Ţ 1 • RECTIFIER FILTER RECTIFIER RECTIFIER B FILTER ACM ON CIRCUIT 6 ALARM REF. VOLTAGE . Ā STANDBY POWER RENSFORMER RANSCRMER ¥ Ă AMPLIFIER AMPLIFIER POWER POWER TO TURN OFFS & INHIBITS STANDBY POWER VOLTAGE LIMIT MAG AMP VOL TAGE Reg Mas Amp 28 VF IND ALARM Ą ¥ FROM CURRENT LIMIT MAG AMP 4 CURRENT LIMIT MAG AMP (FE) -lı -lÞ +28V ALARM MULTIVIBRATOR MULTIVIBRATOR TURN ON-OFF CIRCUIT **A 4** . INPUT SYNC SYNC 0 12.5 KHz OUTCOM 0 28 RET +4VSW < 0 Q ∞ó

ł

RAYTHEON

COMPANY

SPACE AND INFORMATION SYSTEMS DIVISION

supplies is achieved by means of series type regulators. The transformers used to furnish the +4.4 VDC and +14 VDC also provide the necessary AC signals, which after rectification and filtering provide the power for the -5 VDC, +4.4 VDC and +14 VDC regulators. Some regulation for line changes is obtained by the magnetic amplifiers used to regulate the +4.4 VDC and +14 VDC supplies.

The input filter provides transient attenuation, power line isolation, and energy storage capability to furnish power to the ACM regulators during a short power failure. A failure period of 300  $\mu$  sec can be tolerated with the filter design.

The turn on-off circuit (OUTCOM, +4SW) restricts the operation of the ACM power supply, and therefore the ACM, to only those periods when both a +4 SW and OUTCOM signal are present. The lack of either one or both signals turns off the power supply. A delay of approximately one hundred milliseconds is provided within the circuit for continuous operation of ACM power supply during short transients in the OUTCOM signal.

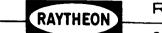

A 28V Alarm Circuit monitors the 28 VDC (at the input of the filter). The Power Supply is turned off by the alarm circuit when the 28 VDC line is reduced to a level of 19.9 VDC or less. A filter delay is provided to prevent premature alarms due to a transient loss of the input voltage. The circuit will also detect an increase in line level above 35.5 VDC and then turn off the power supply. An ACMON circuit is also utilized as a monitor and controlling circuit, regulating turn off timing between the 4.4 volt logic supply and the 4.4 volt line driver supply. It also monitors the 4.4 VDC (logic) for proper level.

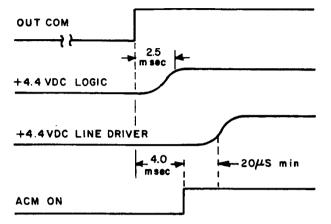

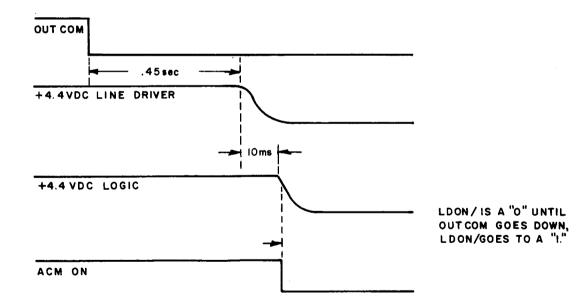

Figure 1-9 shows the relative timing of ACMON with respect to the signal OUTCOM. This assumes LDON/ is controlled by the logic.

RAYTHEON COMPANY SPACE AND INFORMATION SYSTEMS DIVISION

NOTES: ASSUMES 28 VOLTS IS ON, +4V SW ON, LD ON/ IS A "O"

TURN ON

#### Figure 1-9 Power Supply Characteristics

SPACE AND INFORMATION SYSTEMS DIVISION

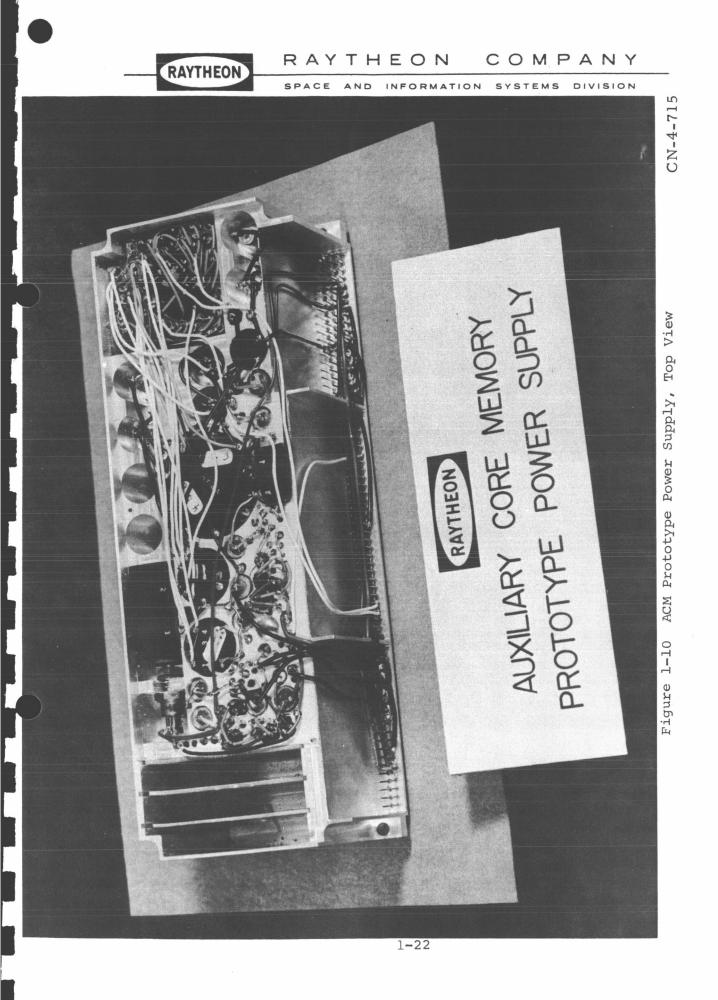

The ACM power supply module which mounts in position  $A \not 01$  on the ACM Tray is shown in Figures 1-10 and 1-11. This supply exhibits an overall efficiency in excess of 75%. The output voltages are +4.4 VDC, +12 VDC, +14.0 VDC, and -5 VDC. Power output capability for this power supply was a total of 76 watts. Regulation was better than  $\pm$  3% for all voltages.

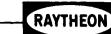

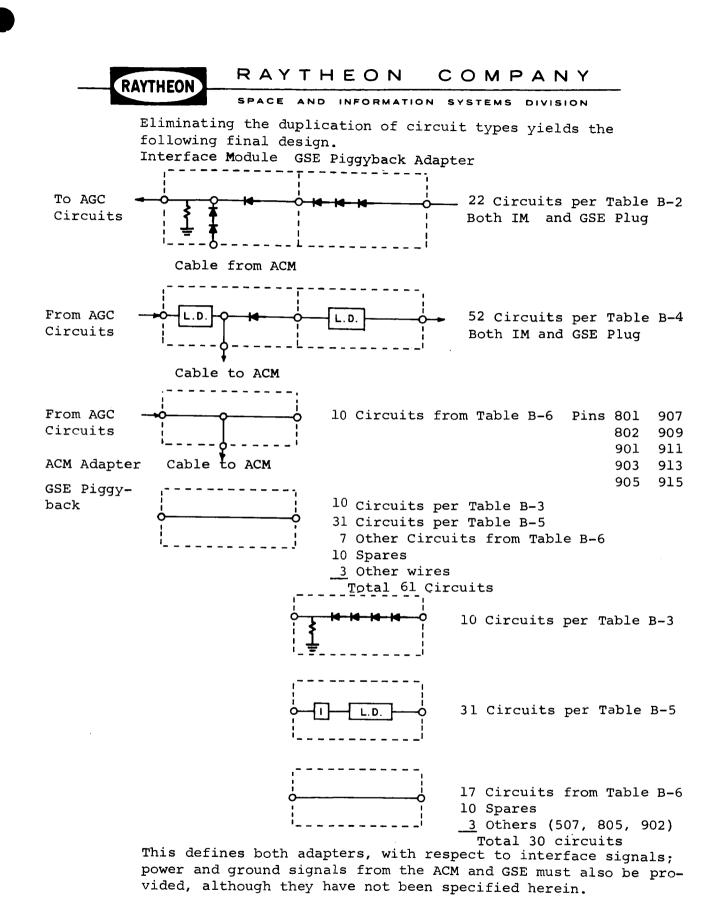

#### 1.2 INTERFACE MODULE

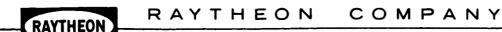

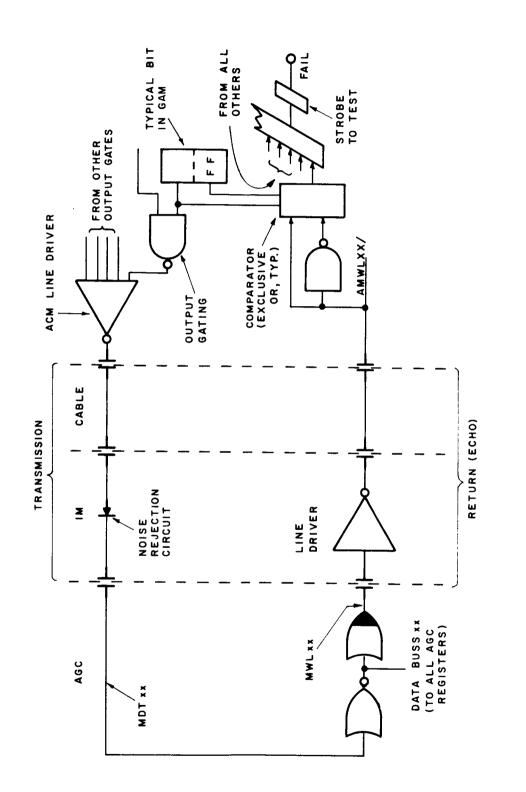

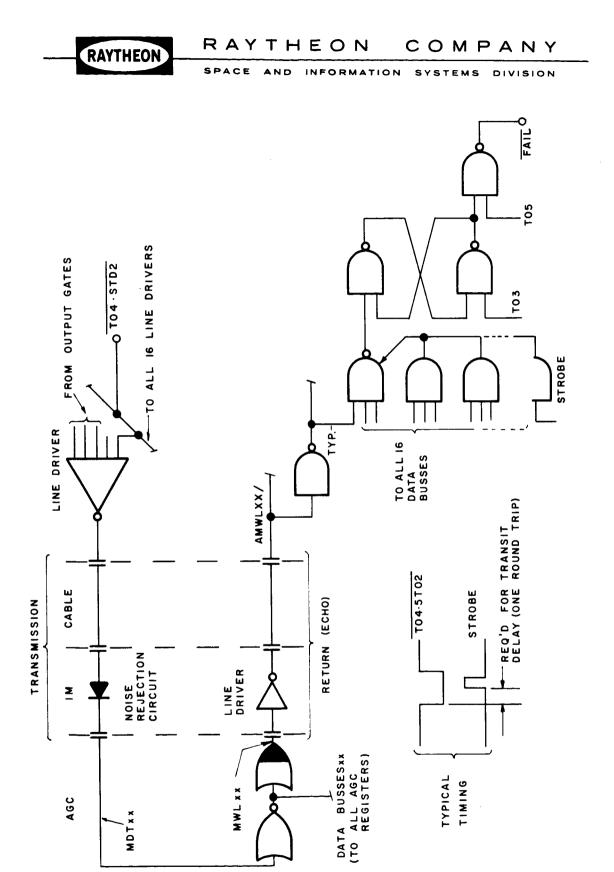

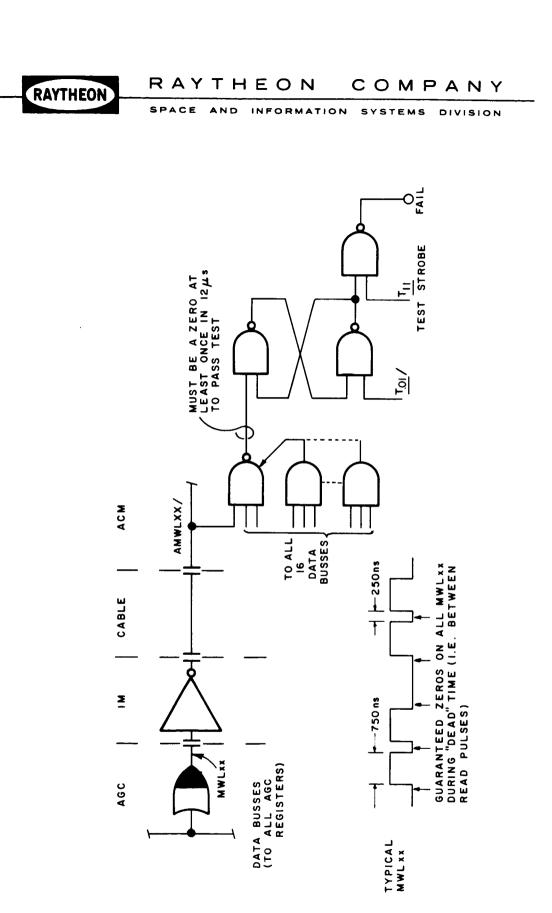

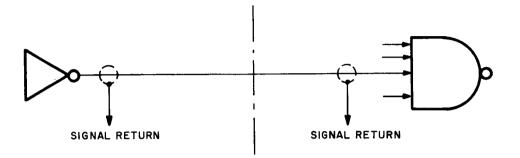

The IM provides buffering for AGC outputs and noise rejection for AGC inputs at the test connector. The major problem in interfacing the ACM with the AGC is the time delay and pulse waveform degradation resulting from the length of the connecting cable and its associated capacitance. The negate these effects, line drivers located in the IM and ACM are provided for each of the interfacing signal lines.

The IM is placed as close as possible to the AGC by plugging the IM directly into the AGC A52 connector to minimize cable effects.

AGC signals destined for the ACM are processed in the IM by Signetics type SE156J Line Drivers. These are low source impedance (100 ohms) devices with transistor pull-up and are capable of driving reasonably high capacitance loads.

The input current supplied from the line driver to the collector of the AGC Nor gate will not exceed 2 ma under all conditions of temperature and voltage. The IM line drivers for the ACM signals and GSE signals are powered separately. The GSE supplies +10 VDC power for the +4.4v zener diode supply which powers the GSE line drivers within the IM. External +4.4 VDC power must be supplied separately for powering the ACM line drivers within the IM.

#### 1.2.1 ELECTRICAL DESCRIPTION

A total of 92 line drivers are provided for the AGC signals; sixty are shared by the ACM and GSE, including spares, while 32 are exclusively used by the GSE.

A total of 40 noise rejection circuits protect AGC input lines

RAYTHEON COMPANY

from noise introduced in the cables from the ACM and the GSE. The routing of wires through the connector and the isolating components are shown in Appendix C.

#### 1.2.1.1 AGC-IM-ACM Interface

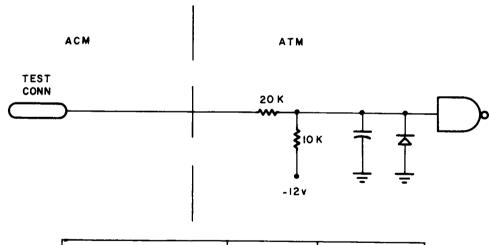

The configuration shown in Figure 1-12 is used for all AGC outputs. The cable length was maintained at five feet to minimize the delay between the AGC and the ACM.

Two AGC output signals, OJTCOM and the 4.4v SWITCHED, are not serviced by line drivers: OJTCOM is handled as a wire connection and 4.4v SWITCHED is wired with a series current limiting resistor to protect the AGC.

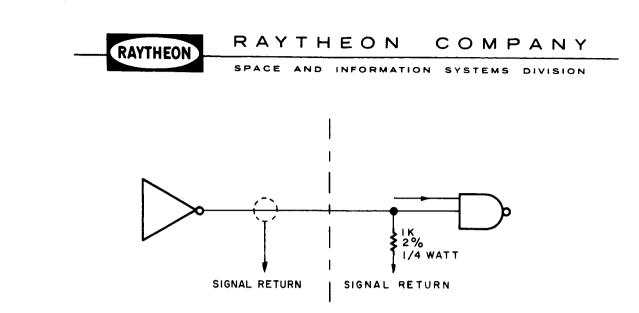

Signals to the AGC from the ACM require noise rejection in the IM to provide noise immunity for the sensitive inputs of the AGC NOR gates. Each signal from the ACM as shown in Figure 1-13 passes through a diode for noise rejection. A resistor to ground provides a bleed path for the base current of the AGC NOR gate when it is turning off. Although the output impedance of the SE 455J line driver (200 ohms) is higher than the SE 156J, resulting in a slight reduction of speed, it has been chosen to provide output levels which will not be above 0.2 volts at the input to the AGC in the event of an ACM power failure.

The cable harness from the IM to the ACM includes individual shielded wires to minimize cross talk between signals, and an outer shield to provide RFI interference protection.

#### 1.2.1.2 AGC-IM-GSE Interface

The present interface between the AGC and GSE is maintained by including a GSE section in the Interface Module (Figure 1-14).

|     |         | MAX     | MIN   |

|-----|---------|---------|-------|

|     | IMAX    | 2.0 m a |       |

| VIN | LOGIC I | 6 V     | 4.0 V |

| VIN | LOGIC O | 0. 2 V  | 0.0V  |

Figure 1-12 AGC to ACM Signal Interface

|                          | MAX       | MIN         |

|--------------------------|-----------|-------------|

| Imax                     | 2.0 ma    |             |

| Vout LOGIC I             | 3.0 volts | 0.825 volts |

| V <sub>out</sub> LOGIC O | 0.2 volts | 0.0 volts   |

Figure 1-13 ACM to AGC Signal Interface

Figure 1-14 AGC to GSE Interface Signals

SPACE AND INFORMATION SYSTEMS DIVISION

This technique replaces the present Buffer Circuit Assembly and its short cable (2 feet) between the AGC and the Buffer Circuits of the Program Analyzer Console (PAC) or Computer Test Set (CTS) when the AM system is installed. The GSE cables connect to the GSE section which mounts to the buffer circuit bracket assembly for strain relief. The current interface to the Program Analyzer Console (PAC), or the Computer Test Set (CTS) is preserved. The PAC, which has similar time delay problems as the ACM, achieves a significant reduction in delays now caused by the cable between the AGC blue nose and the buffer circuit.

## 1.2.2 MECHANICAL DESCRIPTION

The Interface Module (IM) is designed to be mounted to the AGC test connector, A52, by means of its own captive hardware. On top of the IM are connector receptacles for the GSE and ACM cables. The IM also provides those functions which are found on a GSE buffer circuit assembly such as: the ALGA switch, the STRT1/STRT2 switch and BNC connectors for MTHI and MTLO. There is no provision for exercising the self-test feature of the GSE with the Interface Module installed, because the GSE section is an integral part of the IM.

The IM consists of 24 printed circuit boards of seven types mounted in a common frame. The printed circuit boards are listed by type in Table 1-2.

The two cables between the IM and the ACM (See Figure 1-15) are connected by Deutsch connectors (44 pin connector on the ACM side and an 85 pin connector on the IM side; reference drawings 366048 and 366049. Low capacitance coaxial cable is used in the cables with each coax shield terminated at logic ground at each end. An outer electrostatic shield is also provided for RFI protection, with the termination made on the outer shield of the connectors at each end.

SPACE AND INFORMATION SYSTEMS DIVISION

| TABLE | 1-2 |

|-------|-----|

|-------|-----|

IM PRINTED CKT BOARD TYPE

| TYPE           | QUANTITY | FUNCTION            |

|----------------|----------|---------------------|

| А              | 4        | AGC to GSE          |

| B <sub>1</sub> | 2        | ACM & GSE to AGC    |

| B <sub>2</sub> | 2        | GSE to AGC          |

| с              | 4        | GSE diodes only     |

| Dl             | 5        | AGC to ACM & GSE    |

| D <sub>2</sub> | 5        | GSE LD only         |

| Е              | 2        | Discrete Components |

## 1.3 AUXILIARY TAPE MEMORY

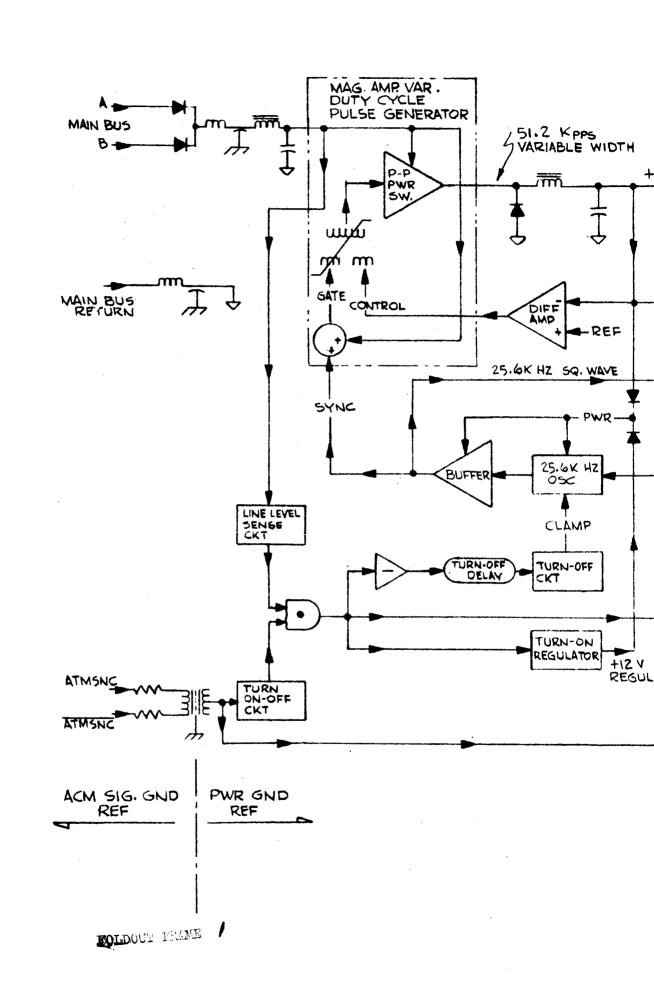

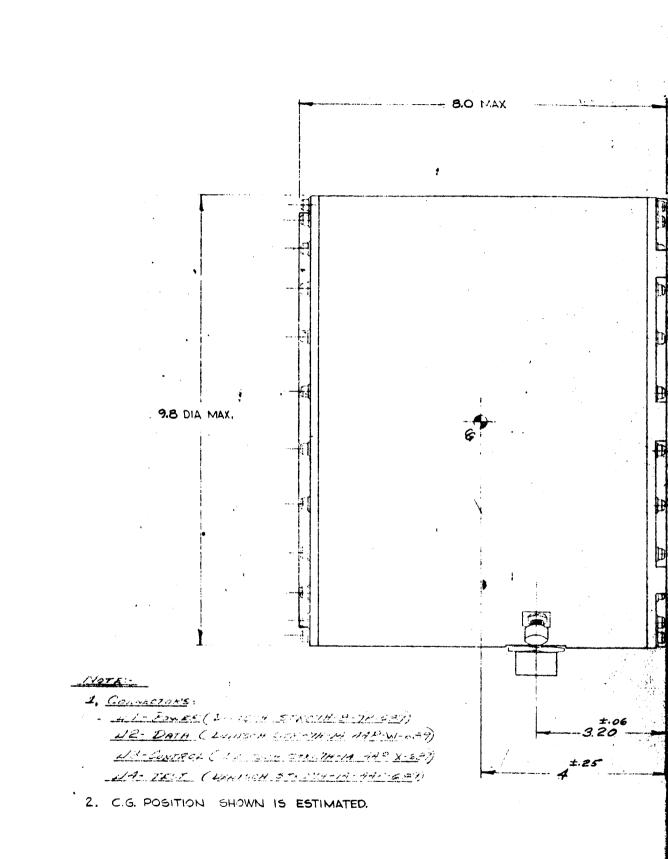

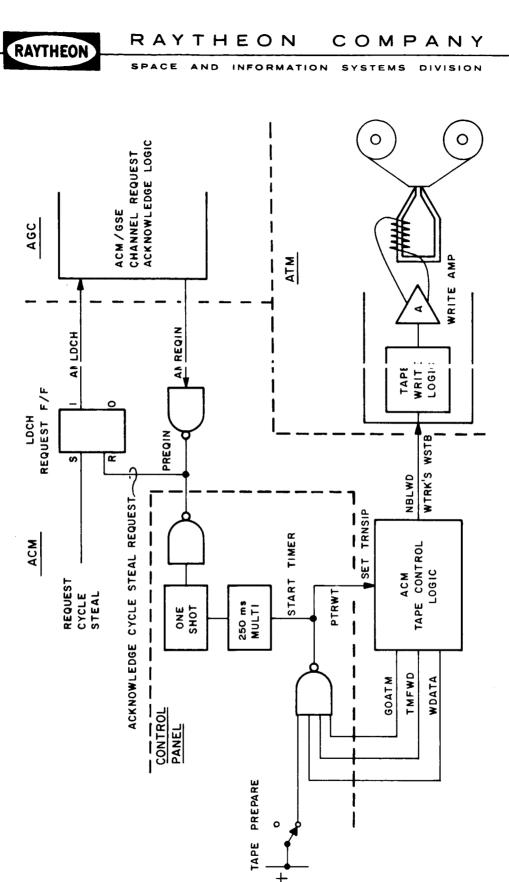

A simplified block diagram of the auxiliary tape memory is shown in Figure 1-16. The unit is a complete digital recorder system which contains all sections necessary for operation of the unit. This includes tape transport, read and write electronics, control logic, motor drive circuits, and power supply.

The recorder is an eighteen channel unit designed to record and reproduce digital information in parallel at 12.8 kiloframes per second. Five hundred-fifty feet of one inch heavy duty instrumentation tape yield a total information capacity of approximately  $1 \times 10^8$  bits. The tape speed is fifteen inches per second and the digital packing density is 853 frames per inch or 853 bits per channel-inch.

Accurate tape speed is maintained by use of a hysteresis synchronous motor slaved, ultimately, to the guidance computer master clock. A photo-electric sensing mechanism limits tape travel, and provides end of tape information to the control circuit.

Figure 1-15 Wiring Diagram - ACM, ATM, and AGC

FOLDOUT FRAME

Figure 1-16 System Block Diagram: Apollo DVT/ATM

SPACE AND INFORMATION SYSTEMS DIVISION

Control of the recorder is established by hybrid (logic element - discrete component) circuits especially designed to protect recordings from accidental erasure, prevent damage to components and interface with the ACM control section.

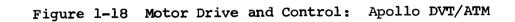

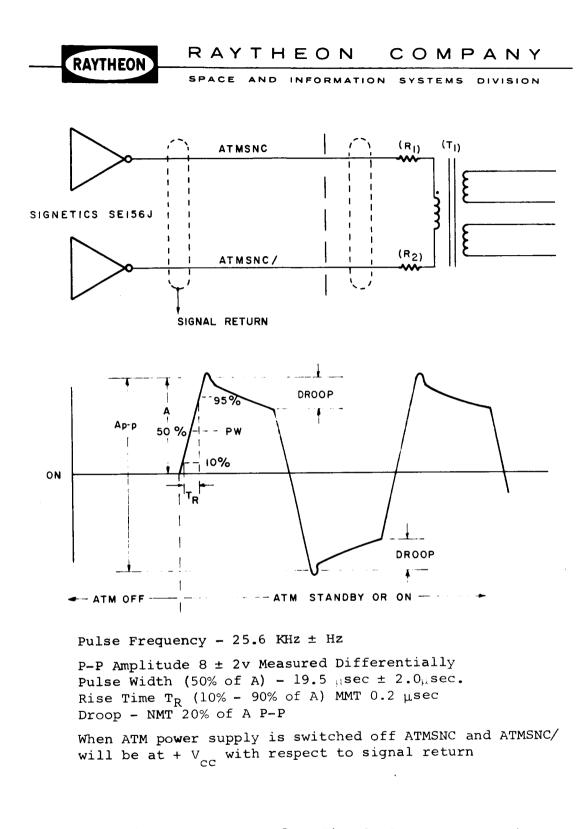

An integral power supply furnishes the various voltages used throughout the system. The power supply operates from the 28 VDC main bus. On-off control is achieved by sensing the presence or absence of a 25.6 KHz synchronizing signal from the ACM. A dc to ac power inverter and constant efficiency chopper regulator are each phase-locked to the ACM signal to assure stable operation and reduce line noise effects on the overall system. Because the power supply is synchronized to a frequency stable source, it is convenient to control the tape transport speed by dividing down the 25.6 KHz power supply signal to derive ac drive to the synchronous motor.

Various test points are provided to verify proper operation and to aid in locating trouble spots. Test connector outputs are provided for monitoring major parameters, including power supply outputs and amplified playback signals.

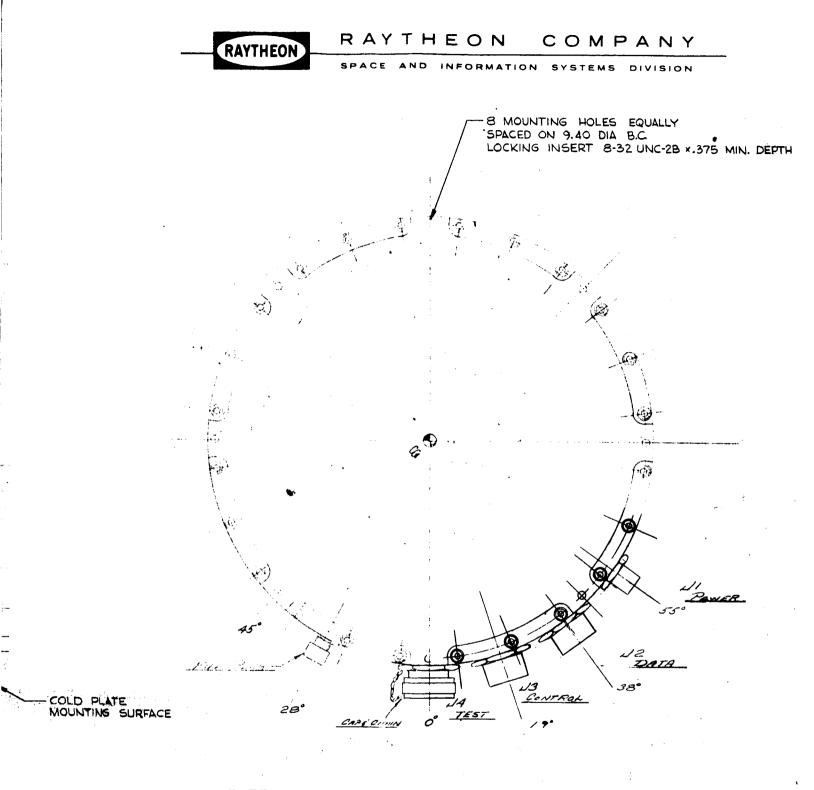

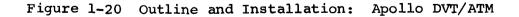

Characterists of the ATM-DVT system are:

| a. | Form Factor   | -Cylindrical, 9.8 inches maximum diameter x<br>8.0 inches maximum height                |

|----|---------------|-----------------------------------------------------------------------------------------|

| b. | Weight        | -Approximately 18 pounds.                                                               |

| c. | Power         | -28 VDC, 20 watts. Less than 20 watts in worst case operation mode.                     |

| đ. | Data Capacity | -18 channels, 5.6 x $10^6$ bits per channel or 1 x $10^8$ bits total.                   |

| e. | Bit Density   | -853 bits per inch per track.                                                           |

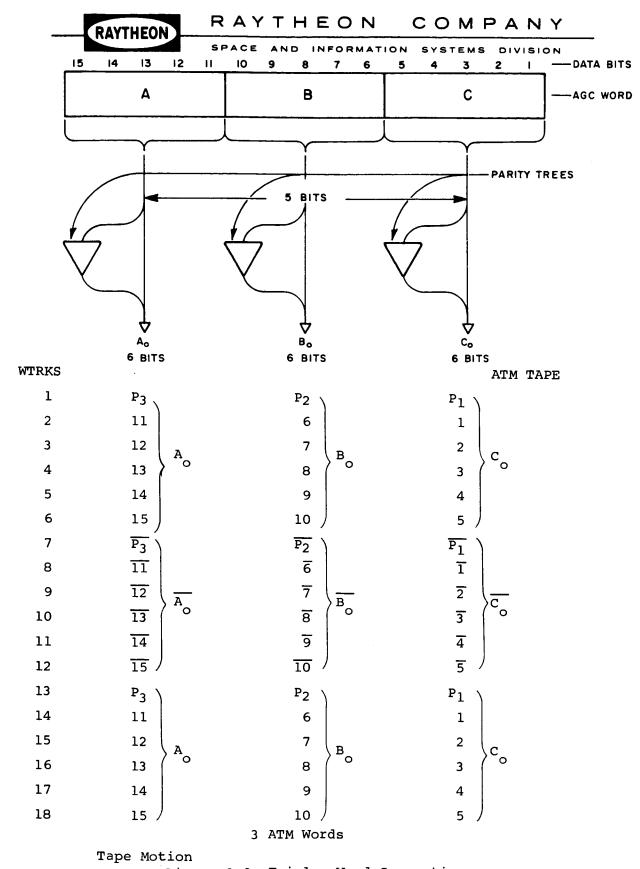

| f. | Code Format   | -18 channel parallel format, channels arranged in three sets of six channels each. Each |

1-31

set has five data channels plus odd parity.

| RAYTHEON            | RAYTHEON COMPANY                       |

|---------------------|----------------------------------------|

|                     | SPACE AND INFORMATION SYSTEMS DIVISION |

| g. Data Rate        | -12.8 KBPS per channel.                |

| h. Tape Speed       | - 15 ips.                              |

| i. Tape Length      | -550 feet.                             |

| 1.3.1 ELECTRICAL DE | ESCRIPTION                             |

## 1.3.1.1 <u>Read/Write Electronics</u>

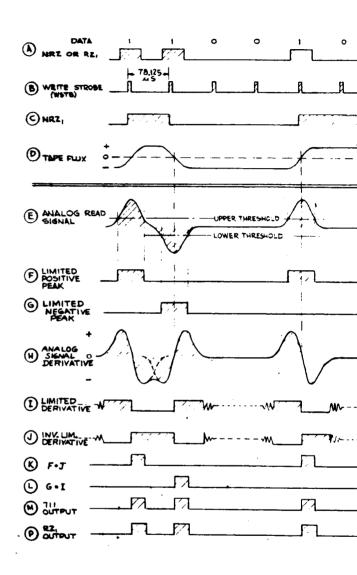

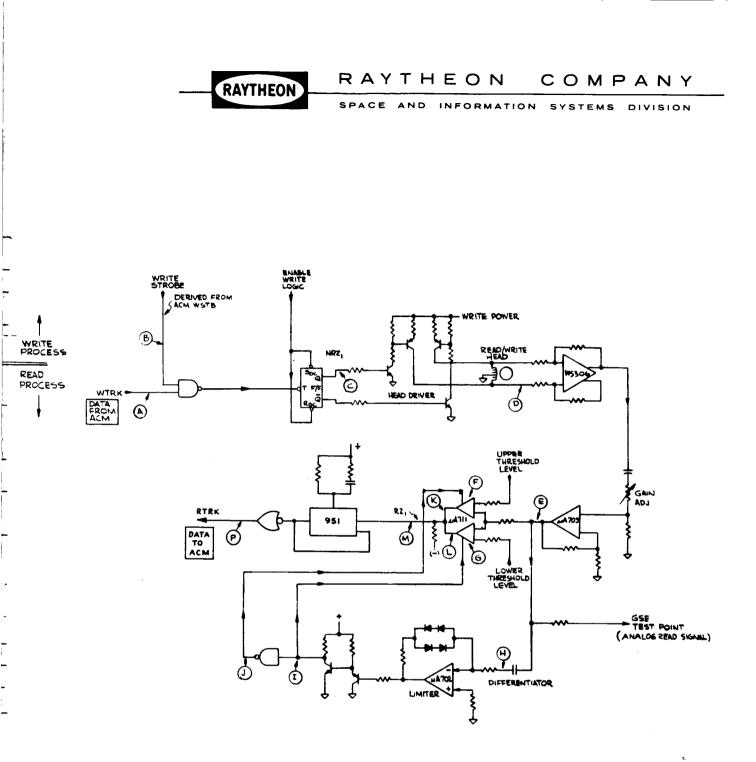

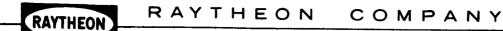

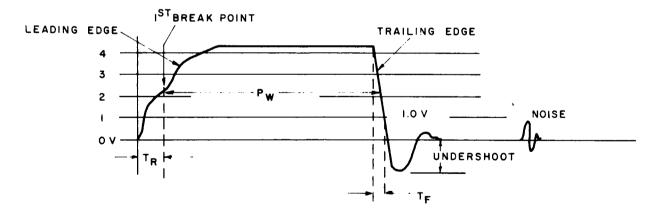

Figure 1-17 depicts a hybrid diagram and waveform chart for a typical read/write channel. Eighteen channels, identical to that shown, are provided.

Operation of the circuit may be best explained by considering the recording method. The code format selected for use in this system is NRZ<sub>1</sub> (sometimes referred to as NRZ1 or NRZ-MARK). This format is defined as a change-of-state or inversion of tape flux for each logical "one" to be recorded. Saturation recording is used, with overdrive sufficient to completely erase or rewrite previous recordings. The coding format, by definition, implies a system where only flux transitions are of importance; thus the direction of the tape flux is not controlled. It is important to consider that application and removal of head power, during the course of making a recording, will introduce flux transitions in an unpredictable manner because the flux state of both the previous and new recording is unknown and uncontrolled.

Because of this, the head power programming circuit was developed to prevent readable marks from appearing on the tape when record power was switched on or off. The circuit was set to provide a ramp increase/ decrease of "write" voltage with a nominal transition time of 2.5 msec.

During the writing process, a direct current is applied to one or the other winding of the read/write head. The head driver is designed to be a constant current source to the head. The output of a T type flip-flop determines which head winding is receiving current. When a logical "one" is to be written, a pulse appears on the WTRK line, strobed in the center by a clock pulse, (write Strobe), which toggles the flipflop to its complementary state. The head driver is disabled during

TOLDOUT FRAME

Figure 1-17 Read/Write Electronics: Apollo DVT/ATM

Ē

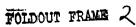

FOLDOUT FRAME 2

SPACE AND INFORMATION SYSTEMS DIVISION

read operations by removal of write power and application of both a dc Set and a dc Reset to the flip-flop, causing both outputs to rise to an "up" level and saturate the NPN stages of the head driver. This precaution is taken to assure that noise pulses on the write lines will not couple through to the read amplifiers during tape reading operations.

The writing process results in the tape's saturation, approximately as shown in the waveform chart. The relatively poor flux transition definition is a characteristic of the tape itself, related to the oxide thickness and formulation. It is not affected by head current rise time provided that adequate design margins are used.

Once a recording has been made, the head, when passed by an NRZ<sub>1</sub> transition, will produce a push-pull analog signal which approximates the time derivative of the flux transition seen by the head gap. We use the term "approximate" because the head actually responds to the rate of change of the average flux seen by the gap. This fact is used to advantage in limiting the bandwidth of the head tape combination to the optimum point by increasing the gap dimension to the point of incipient pulse crowding at maximum packing density. In this system maximum packing density on any channel occurs when a series of logical ones is written.

The read amplifier consists of a differential preamp to ensure noise immunity, followed by a single-ended stage with gain adjustment provisions. Both stages are integrated circuit operational amplifiers adapted to the application by the addition of appropriate discrete components. Sufficient gain is thus available to allow for read-write head variations and to provide some design flexibility. The analog output signal is applied to a peak detector circuit for conversion to digital form.

Peak detection is accomplished by logically ANDing the selected amplitude limited peaks of the read signal with the appropriate (in phase or inverted) amplitude limited derivative of the same signal.

PACE AND INFORMATION SYSTEMS DIVISION

Pulses must exceed the threshold levels before detection can occur. The results of the ANDing processes are ORed together and appear at the output of the dual voltage comparator ( $\mu$ A711). The amplitude limited derivative of the analog tape signal is produced by means of a passive R-C differentiator followed by a symmetrical limiter and dc restorer. The waveform appearing at the output of the dc restorer is a standard logic signal compatible with the other logic elements. AND and OR functions occur within the dual voltage comparator and are not observed in actual practice. An additional AND function separates positive pulse and negative pulse outputs for application to the voltage comparator. The output of the comparator drives a one-shot which reproduces the waveform introduced to the head driver during the writing process.

### 1.3.1.2 Control and Signal Electronics

RAYTHEON

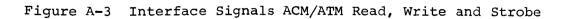

A functional description of each signal control interface between the ACM and the ATM follows to illustrate the features of ATM control. For a more detailed electrical description see Appendix A.

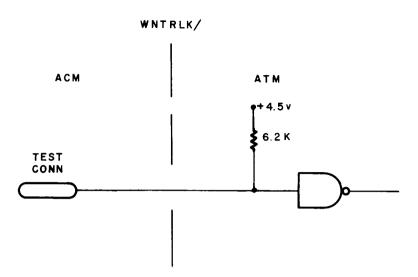

#### WNTRLK-Write Interlock

This line is provided so that the writing capability of the recorder may be inhibited, as the AM system requires, to improve operational reliability. Such a step might be taken where software or hardware confidence is not high and maximum protection of any programs stored in the ATM is desired. A switch on the control panel jumps the signal to ground to inhibit the write function and is left open for normal operation.

## NBLWP, NBLWD-Enable Write

Write head power is applied when NBLWP or NBLWD is brought to an up level, provided other conditions are met. First, the ATM Enable Timer must have run down to produce a "1" at its output. Second, the

SPACE AND INFORMATION SYSTEMS DIVISION

tape must be at operating speed, i.e., a forward tape motion command must be present and the One Second Timer must have run down. Third, there must be no read command present.

#### WOVRYD-Write Over-Ride

It is quite often necessary to completely erase sections of the tape which is difficult due to interlocking control features. Write override is a highly noise immune test input which can force head power on regardless of whether the tape is in motion. The use of this function is restricted to GSE operations and a switch provides this function on the control panel.

### RTAPE-Read Tape

The read tape line, when up, applies power to the read electronics. It is interlocked with the OR of the tape motion commands to conserve power when the tape is not being used and with the write override command to prevent overloading the power supply with both read and write electives on at the same time.

## TMREV, TMFWD - Tape Moving

The output of the One Second Timer is sent to the ACM to indicate when a tape motion command has been received and acted upon. The timer is enabled when the ATM Enable Timer has run down and when either tape motion command is present.

## EOT, BOT, COT - End-of-Tape, Beginning-of-Tape, Center-of-Tape

Whenever an end-of-tape or center-of-tape window is over its associated light sensor, the corresponding output to the ACM is at an up level.

### GOFWD, GOREV - Go Forward, Go Reverse

These lines are the tape motion command lines for the ATM. The logic is arranged so that the system will respond to only one command at a time. Commands which would tend to drive the tape off of the

SPACE AND INFORMATION SYSTEMS DIVISION

reels are inhibited by the end-of-tape circuits. A small delay is incorporated in each command line to allow the One Second Timer to reset in the event that a rapid change of command occurs.

## ATMON-ATM Not On

An output status signal will be at "O" whenever the ATM is ready to provide and accept control signals. Otherwise the signal is at a "1" when the ATM is off, where the voltage is supplied to this circuit by the ACM.

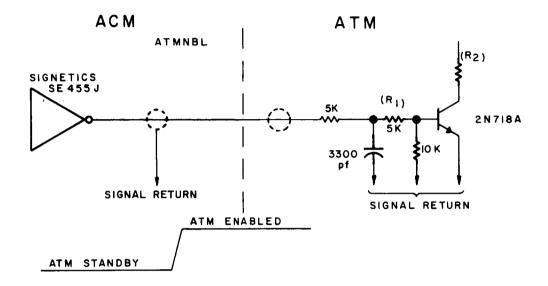

## ATMNBL-ATM Enable

The ACM may enable or disable the ATM by means of the ATM Enable line. In the event a rapid shutdown of the system is desired, a down level at the ATM Enable line will disable the ATM within a few microseconds. Enabling the system is delayed by the rundown of the ATM Enable Timer.

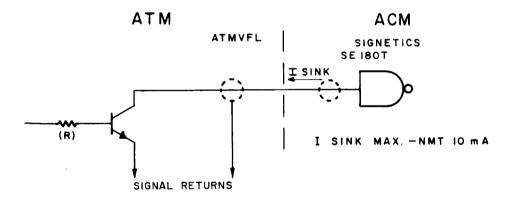

## ATMVFL-ATM Voltage Failure

Qualitative ATM power supply status is conveyed to the ACM by means of the ATM Voltage Failure line. When the system is operating, an up level serves to warn the ACM that a disabling power interruption has occurred and that ATM self-shutdown is imminent.

#### ATMSNC & ATMSNC/ - ATM Synchronization

A dual polarity 25.6 Hz square wave input provides a synchronizing signal to the power supply and acts as the normal turn on-off function of the ATM.

#### WSTB-Write Strobe

An ATM input which strobes the incoming data (WTRK's) to the ATM.

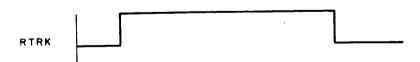

### RTRK01-18 Read Tracks

A parallel arrangement of 18 pulse output signals represents information read from the 18 separate tape track positions.

SPACE AND INFORMATION SYSTEMS DIVISION

## WTRK01-18 Write Tracks

A parallel arrangement of 18 pulse input signals will record in NRZ-1 format on 18 separate tape track positions. Each track will have corresponding read and write lines: WTRK01 corresponds to RTRK01, etc. The input data is strobed into the ATM via a pulse (WSTB) located central to the incoming data pulse.

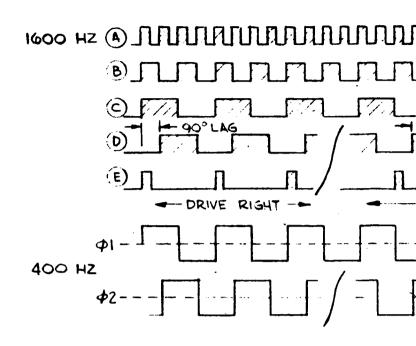

## 1.3.1.3 Motor Drive

A block diagram encompassing the essentials of the motor drive and control electronics is shown in Figure 1-18.