## **General Disclaimer**

## One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

Frederick Dordon 7/6

| SPO PRICE     | \$    |

|---------------|-------|

| SFTI PRICE(S) | S     |

| Hard cony (H( | )     |

| Microfiche (M | × ~ - |

т 653 шт у 65

THRU)

OR TMX OR AD NUMBER

(NASA CR

THE INTERRELATION OF PROCESS TECHNIQUES AND SPACE RADIATION EFFECTS IN METAL-INSULATOR-SEMICONDUCTOR STRUCTURES

FINAL REPORT

21 APRIL 1966 THROUGH 31 JULY 1967

CONTRACT NO. NASS-10177

#### Prepared by

A. G. HOLMES-SIEDLE and W. J. DENNEHY RCA ASTRO-ELECTRONICS DIVISION DEFENSE ELECTRONIC PRODUCTS PRINCETON, NEW JERSEY 08540

and

K. H. ZAININGER RCA LABORATORIES DAVID SARNOFF RESEARCH CENTER PRINCETON, NEW JERSEY 08540

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND 20771 FINAL REPORT

# THE INTERRELATION OF PROCESS TECHNIQUES

# AND SPACE RADIATION EFFECTS IN

# METAL-INSULATOR-SEMICONDUCTOR STRUCTURES

21 APRIL 1966 THROUGH 31 JULY 1967

CONTRACT NO. NAS5-10177

Prepared by

A. G. HOLMES-SIEDLE and W. J. DENNEHY RCA ASTRO-ELECTRONICS DIVISION DEFENSE ELECTRONIC PRODUCTS PRINCETON, NEW JERSEY 08540

and

K. H. ZAININGER RCA LABORATORIES DAVID SARNOFF RESEARCH CENTER PRINCETON, NEW JERSEY 08540

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND 20771

### PREFACE

This project was carried out at the David Sarnoff Research Center under the supervision of Mr. Martin Wolf, Manager, Physical Research Laboratory of the RCA Astro-Electronics Divisior, with assistance from Mr. Paul Rappaport, Associate Director, Materials Research Laboratory of RCA Laboratories. Technical supervision for NASA was by Messrs. Phillip Newman and Harry Wannemacher, Jr. (Technical Project Monitor) of the Radiation Effects Group, NASA Goddard Space Flight Center (Manager, Mr. Frederick Gordon). Other RCA personnel whose assistance is acknowledged are Mr. H. Harmon of Reliability Engineering, RCA Astro-Electronics Division, Hightstown, New Jersey (Manager, Mr. J. Kimmel) who assisted with some measurements; Messrs. C. Hanchett and P. Gardner of the Advanced Devices Group, RCA Electronic Components, Somerville, New Jersey, (Manager, Dr. R. Glicksman), who supplied samples of developmental ("Pattern 7") transistors and oxidized silicon wafers; Mr. T. Athanas, of Semiconductor Components Applications (MOS) of the same division (Manager, Dr. H. Veloric), who supplied samples of production transistors; and Dr. W. Kern and Mr. W. Schilp of the Process Research and Development Laboratory, RCA Laboratories (Director, Mr. G. Herzog), who supplied samples of chemically deposited insulators.

### ABSTRACT

To find out how to minimize radiation sensitivity in MOS transistors, a study was made on the interrelation between sensitivity to space radiation in MOS devices and the method of fabricating the gate oxide film of these devices. Both MOS capacitors and transistors were studied using automatic plotting of capacitance-voltage and channel current-gate voltage characteristics. For both types of device, the oxides studied were fabricated under varied but closely controlled conditions. Both special laboratory furnaces and production types of furnace were used for oxide growth. A key item in the work was a controlled experiment in which the addition of phosphorus to the MOS insulator layer led to a true "radiation hardening". Radiation sensitivity is manifested as a negative shift in C-V and I-V characteristics. The main conclusions of the project were as follows:

- The gate oxide process technique used can change the sensitivity of MOS structures to high-energy radiation by an order of magnitude.

- (2) The reproducibility of the degree of sensitivity to radiation is greater when steam-growth of oxides is used, rather than dry-oxygen growth.

- (3) In general, the nearer the pre-irradiation C-V characteristic of an MIS insulator is to the ideal (charge-free) characteristic, the less sensitive is the MIS device to radiation.

- (4) The coating of thermal oxides with a phosphosilicate layer appears to affect favorab y the sensitivity of the resultant MOS device to radiation. This result can be described as a true "radiation-hardening".

- (5) Several other process parameters can be ruled out as to their influence on radiation sensitivity.

- (6) The present levels of radiation sensitivity in massproduced devices can be improved by changes in process technique.

# PRECEDING PAGE BLANK NOT FILMED.

## TABLE OF CONTENTS

| Sectior |                                |                          |         |        |       |      |      |      |      |    |   | Page     |

|---------|--------------------------------|--------------------------|---------|--------|-------|------|------|------|------|----|---|----------|

| PREFACE |                                |                          |         |        |       |      |      |      | •    |    |   | ii       |

| ABSTRAC | т                              |                          |         |        |       |      |      | •    | • •  | •  | • | iii      |

| LIST OF | ILLUSTRATIONS                  |                          |         |        |       |      |      | •    |      |    | • | vi       |

| 1.      | INTRODUCTION .                 |                          |         |        |       |      | •••  | • •  | • •  | •  | • | 1        |

|         | A. General .<br>B. Brief Chron | 0.                       |         |        |       |      |      |      |      | •  | • | 1        |

|         | MIS Devices                    |                          |         |        |       |      |      |      |      |    |   | 2        |

|         | C. Relation of                 |                          |         |        |       |      |      |      |      |    |   | 3<br>4   |

|         | D. Space Radia                 | ation Leve               | ls      |        | •••   | •••  | •••  | • •  | • •  | •  | • | 4        |

| II.     | PHYSICS OF THE                 | MIS SYSTE                | M AND M | EASURI | EMENI | CON  | SID  | ERAT | 101  | ١S | • | 6        |

|         | A. General Con                 |                          |         |        |       |      |      |      |      |    |   | 6        |

|         | B. Charge Rela                 |                          |         |        |       |      |      |      |      |    |   | 7        |

|         | C. Measurement                 |                          |         |        |       |      |      |      |      |    |   | 8<br>8.  |

|         |                                | gh-Frequen<br>6 Conducta |         |        |       |      |      |      |      |    |   | 10       |

|         |                                | annel Condu              |         |        |       |      |      |      |      |    |   | 10       |

|         | D. Mechanisms                  | of Radiat                | ion-Ind | uced ( | Charg | e Pr | oduo | tio  | on . |    |   | 11       |

|         | 1. "Fixed"                     | 'Oxide Ch                | arge .  |        |       | · .  |      |      |      |    |   | 11       |

|         | 2. Interfa                     | ace States               |         |        |       |      |      | •    |      |    |   | 15       |

| 111.    | APPROACH IN PRI                | ESENT PROJ               | ECT .   |        |       |      |      |      |      |    |   | 17       |

|         | A. General App                 | oroach                   |         |        |       |      |      |      |      |    |   | 17       |

|         | B. Devices Stu                 |                          |         |        |       |      |      |      |      |    |   | 19       |

|         | C. MIS Capaci                  | tor Select:              | ion .   |        |       |      |      | •    |      |    |   | 19       |

|         | D. MIS Transis                 |                          |         |        |       |      |      |      | • •  | •  | • | 20       |

|         | E. Relevancy of                | -                        |         |        |       |      |      |      |      |    |   |          |

|         | Problem .<br>F. Special Exp    | · · · · ·                |         |        |       |      |      |      |      | •  | • | 21<br>21 |

|         | r. Special Exp                 | periments                |         |        | • •   | • •  | •••  | •    | •••  | •  | • | 21       |

| IV.     | EXPERIMENTAL D                 | ETAILS                   |         |        |       | •••  |      | •    | •••  | •  |   | 23       |

|         | A. Irradiation                 |                          |         |        |       |      |      |      |      |    |   | 23       |

|         |                                | Van de Gra               |         |        |       |      |      |      |      |    |   | 23       |

|         |                                | -60 Gamma                |         |        |       |      |      |      |      |    |   | 23       |

|         | B. Test Equips<br>1. Automat   | nent<br>tic C-V Pl       |         |        |       |      |      |      |      |    |   | 23<br>23 |

|         | 2. Automa                      |                          |         |        |       |      |      |      |      |    |   | 25       |

# TABLE OF CONTENTS (Cont'd.)

· det Mittel .....

HARRIS R. LAW

| Section | n                                               | Page |

|---------|-------------------------------------------------|------|

| v.      | EXPERIMENTAL RESULTS                            | 27   |

|         | A. Criteria of Radiation Sensitivity            | 27   |

|         | B. Dependence of Radiation Sensitivity on Oxide |      |

|         | Growth Conditions                               | 29   |

|         | 1. General                                      | 29   |

|         | 2. Oxides Grown in Dry Oxygen                   | 29   |

|         | C. Oxides Grown in Steam                        | 37   |

|         | D. Post-Oxidation Annealing                     | 38   |

|         | 1. Annealing in an Inert Atmosphere             | 38   |

|         | 2. Annealing in Hydrogen                        | 39   |

|         | E. Nonthermal Oxidation Procedures              | 40   |

|         | 1. Anodic Oxides                                | 40   |

|         | 2. Pyrolytically Deposited Oxides               | 41   |

|         | 3. Composite Insulator Layers                   | 44   |

|         | F. Production-Line Transistors                  | 48   |

|         | 1. TA 2578 Transistors                          | 48   |

|         | 2. Semi-Integrated "Pattern 7" Transistors      | 53   |

|         | 3. Complementary Integrated Circuits            | 54   |

|         | G. Special Experiments                          | 54   |

|         | 1. Crystallographic Orientation                 | 54   |

|         | 2. Oxide Thickness Effects                      | 54   |

|         | 3. Stepwise Etch Dissolution Experiments        | 55   |

| VI.     | DISCUSSION                                      | 62   |

|         | A. Variation in Sensitivity                     | 62   |

|         | B. Dose Dependence of Radiation Sensitivity     | 67   |

|         | C. Methods of Reducing Radiation Sensitivity    | 67   |

|         | D. Recommendations for Hardening of MOS Devices | 68   |

| VII.    | CONCLUSIONS                                     | 70   |

| VIII.   | REFERENCES                                      | 73   |

# LIST OF ILLUSTRATIONS

,0

| Figure |                                                                                                                                                                                                                                | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.     | Changes in operating region of MOS device which are produced by ionizing radiation in the 10 <sup>4</sup> to 10 <sup>6</sup> rad absorbed dose region                                                                          | 1    |

| 2.     | Typical MIS capacitance vs. bias characteristics for<br>10 ohm-cm p-type silicon with 0.010-in. nickel gates<br>deposited on a 0.1-um grown silicon dioxide film                                                               | 9    |

| 3.     | General form of shift in MIS characteristics as a function of integrated irradiation level                                                                                                                                     | 12   |

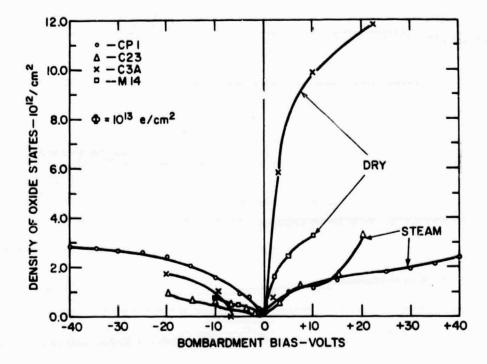

| 4.     | Radiation-induced shifts in MOS capacitor characteristics<br>vs. irradiation bias, $V_I$ , at a fluence of $10^{13}$ 1-MeV<br>electrons/cm <sup>2</sup> (approx. 3 x $10^5$ rads), for four different<br>preparations of oxide | 13   |

| 5.     | Model for the effect of high-energy radiation on MIS structures                                                                                                                                                                | 14   |

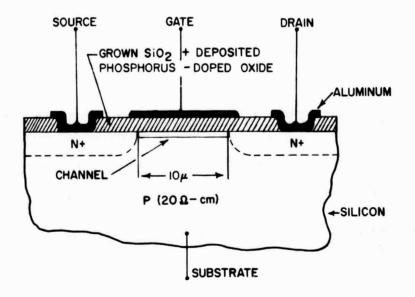

| 6.     | Structure of a typical high-performance MOS transistor                                                                                                                                                                         | 18   |

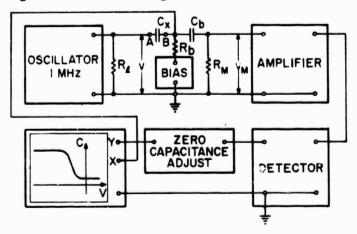

| 7.     | Simplified schematic of the C-V measuring apparatus                                                                                                                                                                            | 25   |

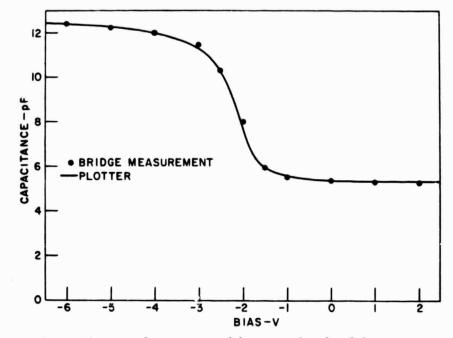

| 8.     | MIS capacitance vs. bias as obtained by measurement<br>with the automatic plotting equipment and with a<br>Boonton Electronics 75 A Capacitance Bridge                                                                         | 25   |

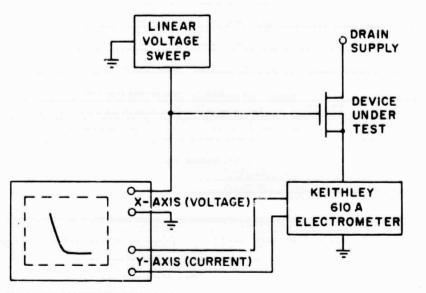

| 9.     | Simplified schematic of MOS transistor transfer characteristic measuring apparatus                                                                                                                                             | 26   |

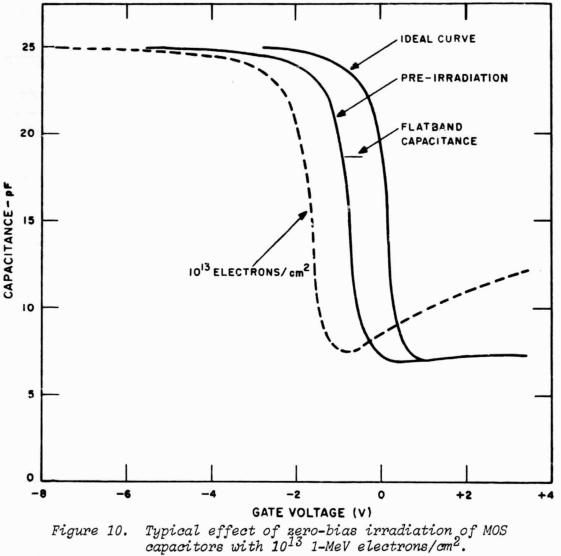

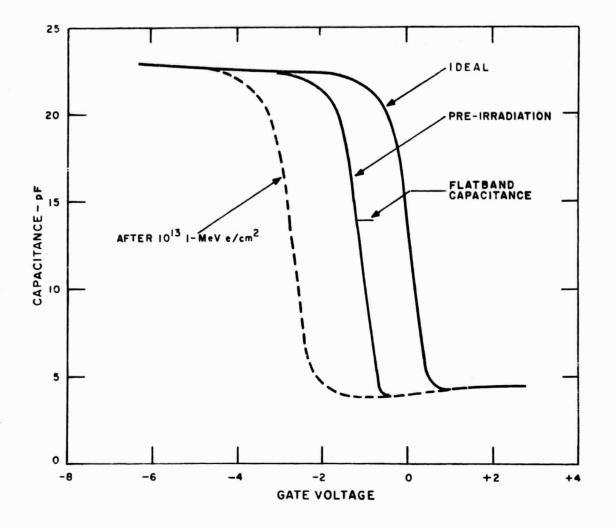

| 10.    | Typical effect of zero-bias irradiation of MOS capacitors with $10^{13}$ 1-MeV electrons/cm <sup>2</sup>                                                                                                                       | 30   |

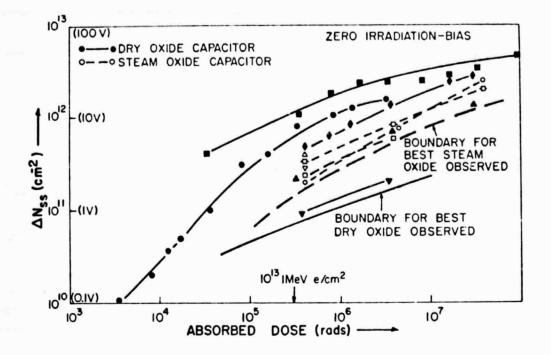

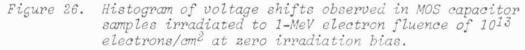

| 11.    | Collected data on 1-MeV electron irradiation of MOS capacitors made from steam-grown and dry-grown oxides                                                                                                                      | 34   |

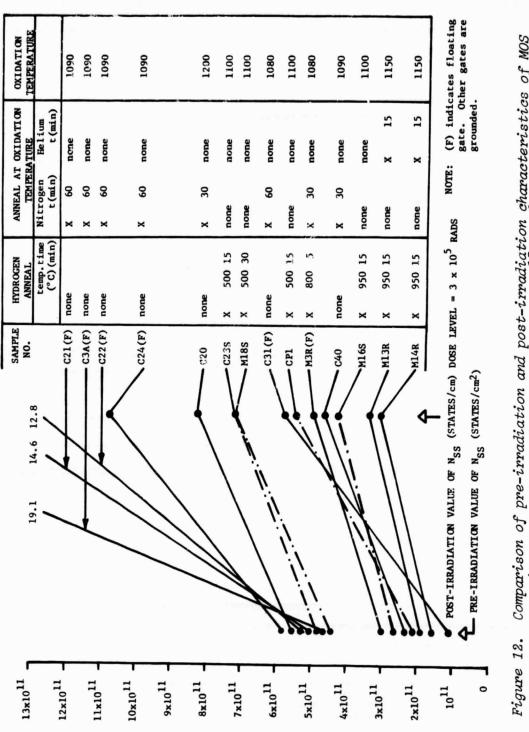

| 12.    | Comparison of pre-irradiation and post-irradiation characteristics of MOS capacitors at a 1-MeV tron fluence of $10^{13} \text{ e/cm}^2 \dots \dots \dots \dots \dots \dots \dots$                                             | 35   |

| 13.    | Effect of irradiation on anodic-oxide capacitor at a 1-MeV fluence of $10^{13}$ e/cm $^2$ and with gate floating                                                                                                               | 41   |

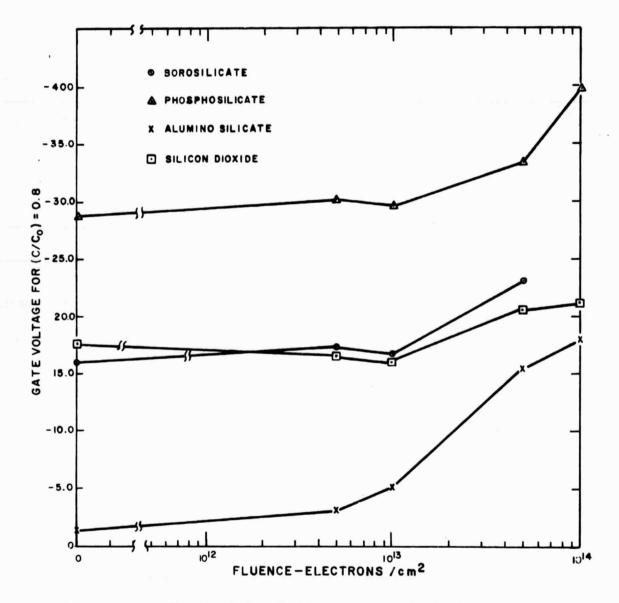

| 14.    | Radiation-induced shifts for pyrolytically deposited<br>layers derived from mixtures of oxygen, silane, and<br>hydrides of silicon, phosphorus, boron, and aluminum.<br>"Silicon dioxide" indicates use of unmixed silane      |      |

|        | with oxygen                                                                                                                                                                                                                    | 43   |

# LIST OF ILLUSTRATIONS (Cont'd.)

三人の思いたので、

Property and the second second

時間においていた。

| Figure |                                                                                                                                                                                                          | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

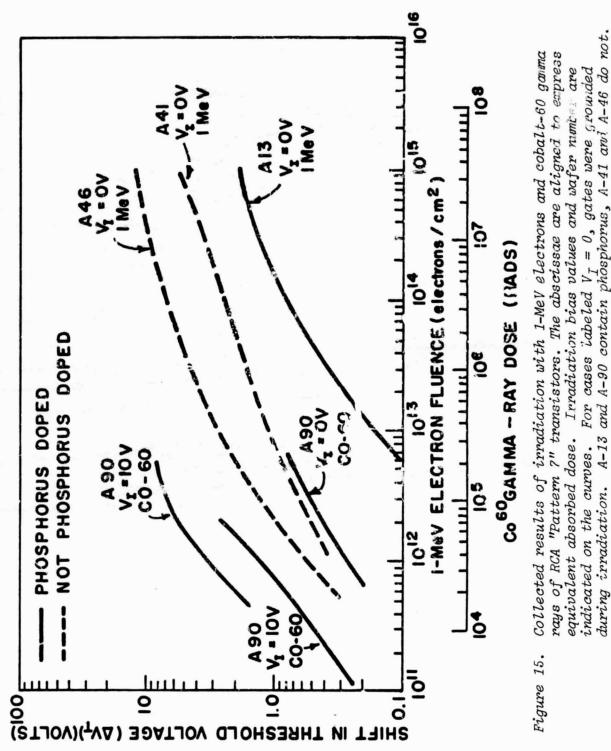

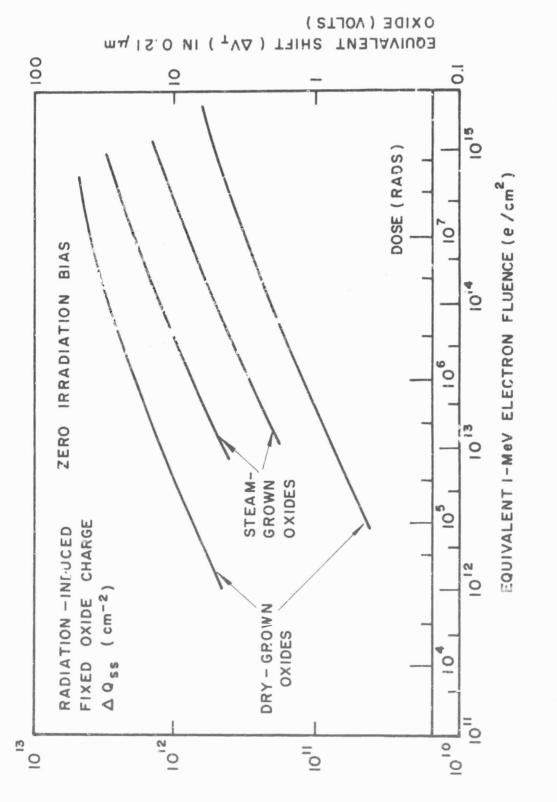

| 15.    | Collected results of irradiation with 1-MeV elec-<br>trons and Cobalt-60 gamma rays of RCA "Pattern 7"<br>transistors                                                                                    | 45   |

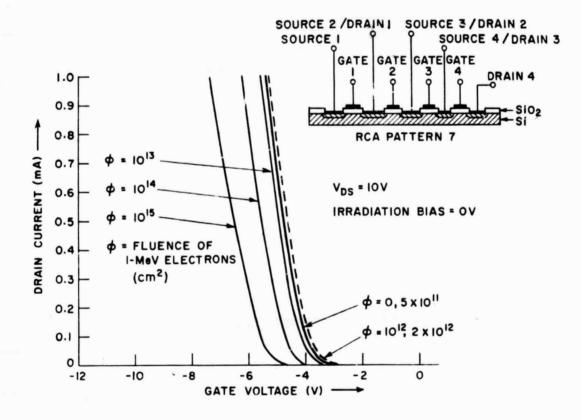

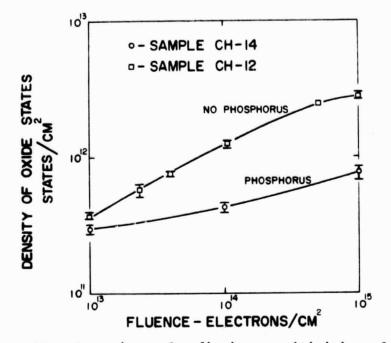

| 16.    | Typical changes in transfer characteristics of a<br>"Pattern 7" transistor under zero irradiation bias                                                                                                   | 47   |

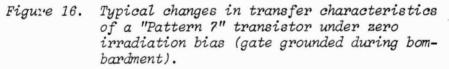

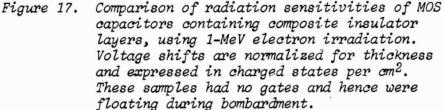

| 17.    | Comparison of radiation sensitivities of MOS<br>capacitors containing composite insulator layers,<br>using 1-MeV electron irradiation                                                                    | 48   |

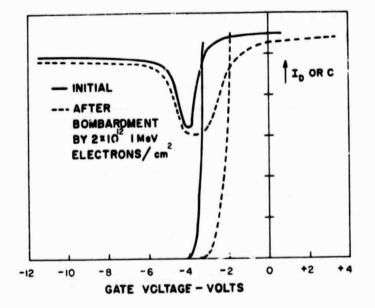

| 18.    | Correlated C-V and I <sub>d</sub> -V <sub>g</sub> characteristics of TA 2578<br>transistor before and after irradiation at zero<br>irradiation-bias                                                      | 50   |

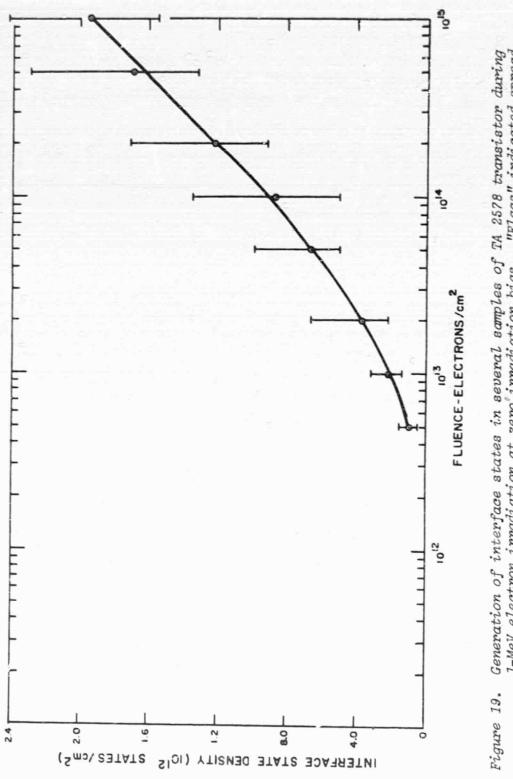

| 19.    | Generation of interface states in several samples of<br>TA 2578 transistor during 1-MeV electron irradiation<br>at zero irradiation bias                                                                 | 51   |

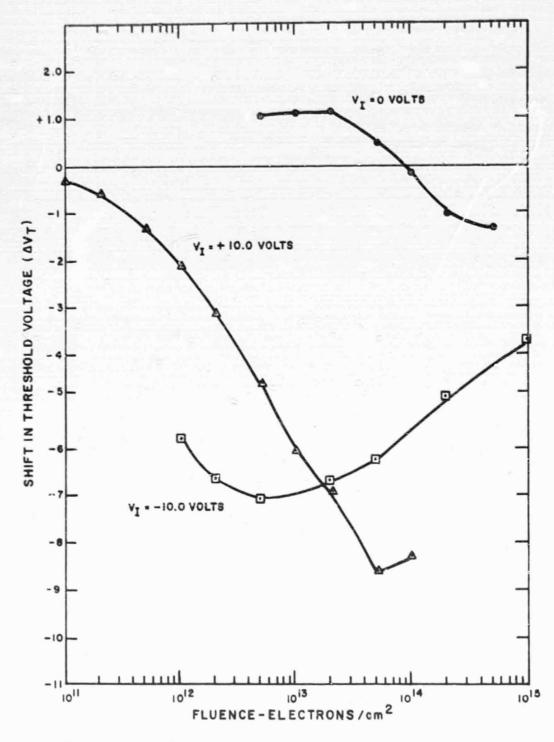

| 20.    | Radiation-induced shift in threshold voltage (gate<br>voltage for $I_D = 2 \times 10^{-5}$ A) vs. 1-MeV electron<br>fluence for three irradiation-bias conditions<br>(TA 2578 transistor)                | 52   |

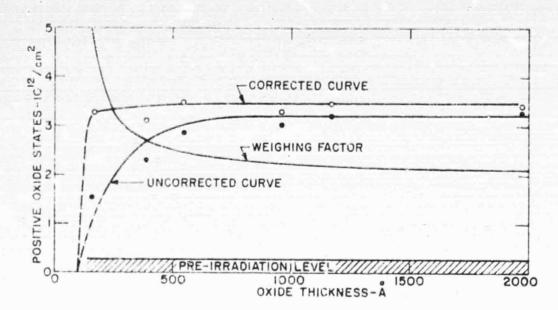

| 21.    | Spatial location of fixed oxide charge within dry-<br>oxygen grown oxide irradiated with $10^{13}$ 1-MeV elec-<br>trons/cm <sup>2</sup> under zero irradiation bias                                      | 56   |

| 22.    | Spatial location of fixed oxide charge within steam-grown oxide irradiated with 10 <sup>13</sup> 1-MeV electrons/cm <sup>2</sup> at an irradiation bias of +5 volts. Correction factors as for Figure 21 | 58   |

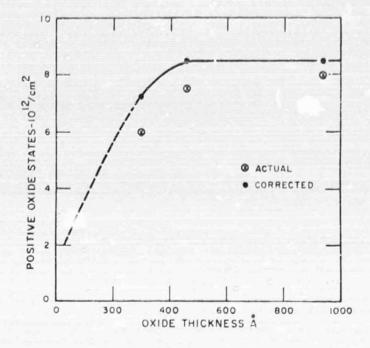

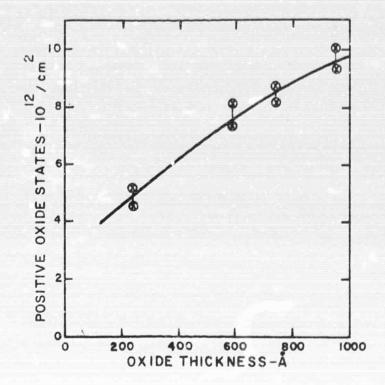

| 23.    | Spatial location of fixed oxide charge within steam-<br>grown oxide irradiated to a fluence of $10^{15}$ 1-MeV electrons/cm <sup>2</sup> at an irradiation bias of -10 volts                             | 59   |

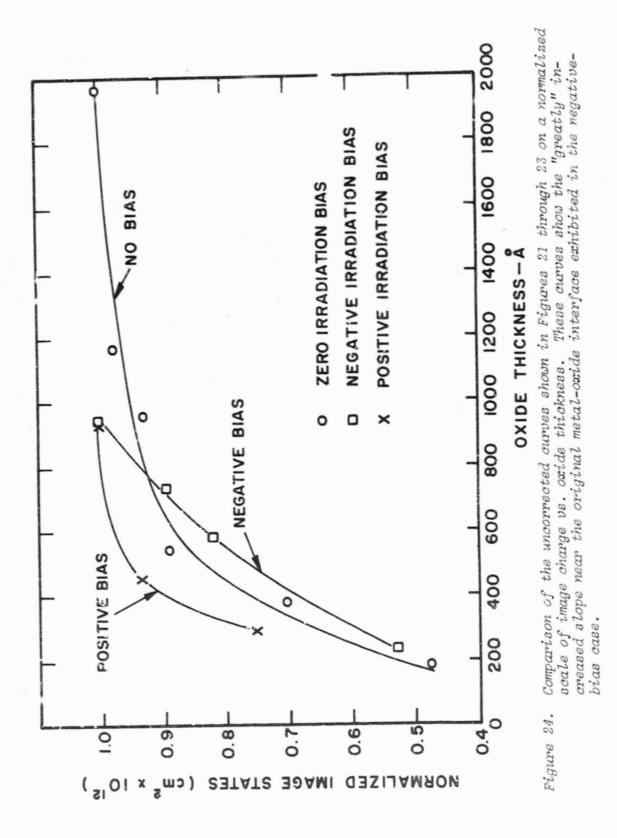

| 24.    | Comparison of the uncorrected curves shown in Figures 21<br>through 23 on a normalized scale of image charge vs.<br>oxide thickness                                                                      | 61   |

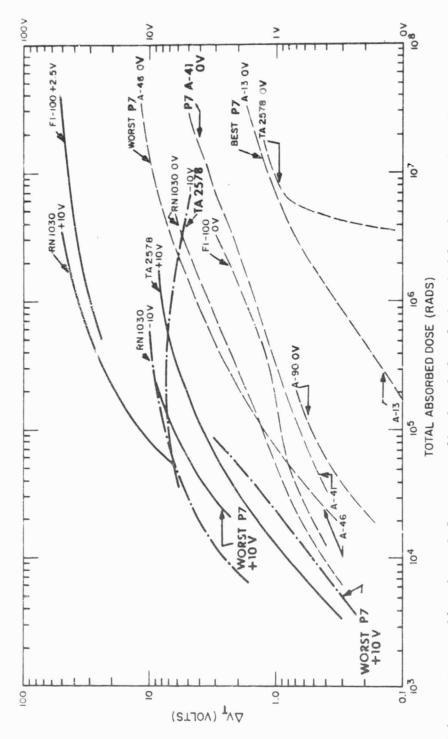

| 25.    | Collection of data on radiation-induced threshold<br>voltage shifts in commercially available, mass produced<br>MOS devices                                                                              | 63   |

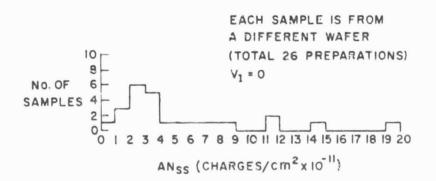

| 26.    | Histogram of voltage shifts observed in MOS capacitor samples irradiated to 1-MeV electron fluence of $10^{13}$ electrons/cm <sup>2</sup> at zero irradiation bias                                       | 65   |

| 27.    |                                                                                                                                                                                                          | 72   |

## I. INTRODUCTION

#### A. GENERAL

With increasing use of metal-oxide-semiconducto: (MOS) transistors in satellite electronics, concern has arisen over the fact that virtually all the available varieties of MOS devices show a strong sensitivity to radiation arising from radiation-induced charges in the thin gate oxide layer[1]. In attempting to minimize this effect of radiation, it is clearly necessary to study first the basic character of the effect and, secondly, whether it can be minimized by some change in the oxide fabrication procedure or in the conditions under which the device is operated in satellite electronics.

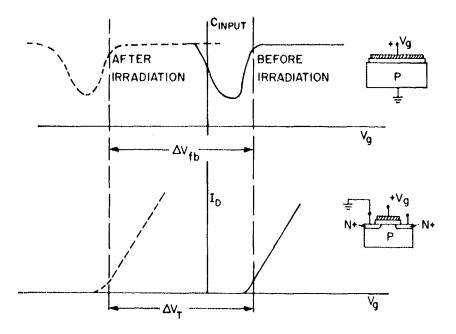

The effect which is invariably observed in MOS devices when subjected to ionizing radiation is a shift in the capacitance-voltage  $(C-V_g)$  characteristic and/or the channel current-gate voltage  $(I_d-V_g)$ characteristic, along the voltage axis in the negative direction (Figure 1). This effect can be interpreted in terms of the trapping

Figure 1. Changes in operating region of MOS device which are produced by ionizing radiation in the  $10^4$  to  $10^6$  rad absorbed dose region.

of holes (loss of electrons) in the insulator layer[2-4]. Thus, the degree of sensitivity of MOS devices to radiation should depend very strongly upon the defect structure of the oxide. The defect structure, in turn, should be strongly affected by the conditions under which the oxide is fabricated. For example, in the case of conventional MOS insulator layers, which are grown directly from the silicon by oxidation, it is to be expected that such variables as oxide growth rate, growth temperature, water-vapor concentration in the growth atmosphere, post-oxidation annealing temperatures, and annealing atmosphere should all be important in establishing the defect structure of the oxide.

The authors have thus undertaken a systematic investigation of the character of the radiation effect in MOS insulators and its variation throughout a wide range of fabrication conditions. At the same time, these conditions have been carefully characterized and have embraced the conditions likely to be found in practical high-performance MOS transistors used in space missions. Thus, the investigation has included not only tests of laboratory-grown oxides, where growth and contamination conditions can be varied at will, but also tests of oxides grown under device-development laboratory conditions and under MOS transistor production-line conditions.

#### B. BRIEF CHRONOLOGY OF RADIATION EFFECTS IN MOS AND MIS DEVICES

The effect of radiation on MOS devices was first noted by Hughes and Giroux[5]. This observation removed the earlier impression that, because surface-channel devices would not be affected by the production of minority-carrier recombination centers in the bulk silicon, they would be radiation resistant. Even though radiation-induced charge-trapping had long been recognized as the source of "color center" formation[6] in bulk silica and other insulators, it was not appreciated that similar effects would strongly influence the performance of MIS devices.

In early 1964, at about the same time that the MOS device data were obtained, unusual degradation effects were also observed in planar bipolar transistors under irradiation. Factual reports of this effect were made by Peden[7] and Peck and Schmid[8] in 1964. Clarifying experiments on the effect were made in late 1964 by Green et al.[9] and by Brucker, Dennehy, and Holmes-Siedle[10,11], which indicated that charge-trapping effects in the oxide were almost certainly the cause of the phenomena observed. These phenomena were strong changes in dc current gain and collector-base leakage current under ionizing radiation. It could be shown that the effect was a surface effect because it was produced by x-rays and by electrons of energy below the minimum needed for bulk silicon damage and because of the strong regular dependence of the gain degradation on injection level[11]. During 1965, Szedon and Sandor[12], Speth and Fang[13], Messenger et al.[14], Kooi[15], and Hughes[16] produced data on MOS devices which indicated that oxide charge buildup was clearly involved in radiation effects in grown oxides and that fields in the oxide during irradiation were vitally important in determining the amount of charge trapped. Zaininger's publication[17] of capacitor measurements gave the first evidence that a well-defined holetrapping effect was involved and was accompanied by variable amounts of interface state production[18].

In 1966, Snow and coworkers[19] and Kooi[20] published confirmatory capacitor data; evidence was produced for strong interface state production in transistors by Dennehy and coworkers[21]; and studies of the practical aspects of the use of MIS devices under radiation were made by Gordon and Wannemacher[22] and Barry and Page[23]. New aspects of bias dependence of radiation-induced shifts on MOS and MIS devices were reported by Stanley[24]. At present, several more profound studies of mechanisms and process effects are in progress, with new techniques such as measurement of oxide charging currents[25,26], probing with fine electron beams of varied energy[27], and preparation and irradiation of high-purity samples of MOS structures, as in the project to be reported here.

The overall conclusion is that the production of significant amounts of trapped charge in the oxide is universal, while other effects, such as interface-state production, instability, and leakage, may or may not occur, depending on oxide structure.

#### C. RELATION OF OXIDE CHORGE AND VOLTAGE SHIFT

A relation which is used very extensively in this report will be explained briefly here. In an MOS device, either capacitor or transistor, the trapping of fixed charge in the oxide leads to a parallel shift in the drain-current vs. gate voltage or capacitance vs. gate voltage characteristic which is proportional to the amount of charge deposited. Thick oxides give larger shifts than thin oxides, the effect being inversely proportional to oxide thickness d<sub>1</sub>. The following relation may be used to calculate charge density  $\Delta N_{SS}$  from voltage shift ( $\Delta V$ ):

$$\Delta N_{ss} = 2.11 \times 10^{10} \left(\frac{\Delta V}{d_i}\right) \tag{1}$$

where  $d_i$  is in microns. It is thus seen that, for d = 0.211 micron or 2110 Å, a fairly common thickness, a negative 1-V shift corresponds to

a positive charge density of  $10^{11}/cm^2$ , 10 V correspond to  $10^{12}/cm^2$ , etc. Two factors may modify this simple relation of fixed charge to shift; (1) If the charge is not within a few hundred angstroms of the silicon; (2) if the charge can exchange with the silicon, i.e., lies in interface states.

#### D. SPACE RADIATION LEVELS

The radiation conditions under which active semiconductors usually have to operate in space is very low-rate particle and Bremsstrahlung irradiation. For most orbits of importance, integrated dose levels are usually less than a megarad in magnitude. The only exceptions would be circular orbits matched precisely with the heart of the inner Van Allen belts, i.e., 1500 to 2500 miles altitude at low inclination to the plane of the geomagnetic equator. These orbits are not of strong operational interest.

A typical heavily used orbit with fairly high radiation fluxes is that being used by operational weather satellites, e.g., ESSA II and TIROS M (a 750 naut. mile altitude circular orbit of inclination 82° to the geographic equator).

Electronic devices such as transistors will usually be enclosed by the equivalent of 0.1 in. of aluminum or more. Estimates for ESSA II in the 1968-75 era are that, with the anticipated thicknesses of structural elements and packages, annual particle fluxes inside electronic packages will not impart ionization doses of more than  $3 \times 10^5$ rads in the more exposed locations. A repetition of the enhancements in trapped electron flux experienced after the "Starfish" hydrogen bomb explosion could, of course, increase these ionization doses by a large factor and require extra shielding thicknesses (say 0.2 in. aluminum) to keep ionization doses in the ranges now anticipated.

It is thus assumed that the important radiation levels which should be considered in a study of the usefulness of MOS devices in space are  $10^3$  to  $10^6$  rads. It seems certain from all work to date that atom displacement damage does not play a major part in degrading MOS devices at the particle flux-levels anticipated; and, hence, all particles can be equated by normalizing factors which convert particle fluence to absorbed dose (e.g.,  $3 \times 10^7$  1-MeV electrons/cm<sup>2</sup>  $\equiv$  1 rad (SiO<sub>2</sub>)  $\equiv$  10<sup>6</sup> 10-MeV protons/cm<sup>2</sup>).

Some assumptions are made in this report about the significance of dose rate when attempting to simulate space radiation effects in the laboratory. Several workers have determined that, for a wide variety of MOS device types, most of the positive charge deposited

remains firmly trapped in the oxide for months or years. Although no definitive experiments have been performed at a typical operational space dose rate, (usually less 10 rads per hour), no strong dose-rate dependence of the radiation effect has yet been observed in the laboratory. On the other hand, in a few types of device, a partial recovery of radiation-induced shifts is observed within a few weeks of the irradiation of an MOS transistor. In these latter cases, measurement of the device immediately after irradiation at a dose rate several thousand times that encountered in space would give a somewhat pessimistic answer as to the performance of that device in orbit after the same total dosage level had been reached. It still appears, however, that the major hazard to MOS devices in space radiation is the permanently induced, firmly "frozen" charge buildup which would not be subject to dose rate effects. Thus, in a study such as the present one, which has the main purposes of placing various process variables in order of merit in producing radiation resistance it is considered valid to perform irradiations at the usual laboratory rates (104 rad/sec or higher) which are, in any case, demanded by the time constraints of the project. An experiment which had the objective of accurate prediction of shifts to be encountered for a given device in a given orbit might, on the other hand, requires slower irradiation rates.

### II. PHYSICS OF THE MIS SYSTEM AND MEASUREMENT CONSIDERATIONS

## A. GENERAL COMMENTS ON SOLID-SOLID INTERFACES

An MIS structure consists of a semiconductor substrate covered by an insulator layer (between 50 Å and 5000 Å thick) upon which a metal electrode (gate) is deposited. Early work on semiconductor surfaces was mainly concerned with the semiconductor-vacuum and semiconductor-gas systems[28]. In the latter, fortuitous room-temperature air oxidation normally produced a 30 to 50-Å-thick oxide film that was considered part of the surface region. This could thus be regarded as a narrow region of discontinuity between the two media. The physics of such surfaces was reasonably well understood, and the localized electronic states associated with the surface region were called surface states. A distinction was made between fast and slow surface states, i.e., between states that could exchange charge with the semiconductor space-charge region rapidly or slowly, respectively. The slow states were generally thought to be at the outside of the oxide film, and the fast ones right at the boundary between the semiconductor and the oxide layer.

MIS physics is a natural extension of semiconductor surface physics into a system of two solid-solid interfaces separated by an insulating film whose thickness is no longer negligible. Because of the presence of this film and its two surface space-charge regions, MIS physics is more complicated than semiconductor surface physics[29]. Depending on the ratio of the insulator thickness to the extent of the space-charge regions, three different situations may arise.

(1) If this ratio is very large, then there is no interaction between the metal-insulator and insulator-semiconductor interface regions, and the voltage drops linearly across the oxide except in the two (relatively small) surface space-charge regions. This is the condition usually assumed but rarely justified in device calculations.

(2) If the ratio is in the order of unity, then the two surface regions in the oxide begin to interact. In this case the two interfaces cannot be separated, and the voltage profile is a complicated function of all the parameters involved.

(3) For a ratio much smaller than unity, the integrated space charge in the oxide can be neglected with respect to the surface charge in the metal, resulting in a linear voltage variation through the oxide film. The silicon surface potential in this case is essentially determined by the interaction between the metal and the silicon, and by the density of states at the interface. The concepts and terminology used are mostly inherited from semiconductor surface physics dealing with a semiconductor-gas system. Thus, for example, the simple distinction between fast and slow surface states is not applicable in an MIS system. However, because of the widespread use of the term "surface states" we have retained this expression, but use it in an operational manner. In this usage, the term "effective surface states" lumps together the effect of work-function difference and both the charge configurations that can be defined for the MIS system, namely, interface states and oxide charge.

#### B. CHARGE RELATIONS IN THE MIS SYSTEM

The charge neutrality of an MIS system is frequently expressed as

$$Q_{ss} + Q_{sc} + Q_{M} = 0,$$

(2)

where Qss, Qsc, and QM indicate charges in the effective surface states, semiconductor space-charge region, and metal electrode, respectively. In reality these quantities represent effective charges with considerable complexity as regards their distribution and energetics of formation[30]. Charge-exchange equilibria exist between each region, and several different types of charge can be distinguished within the insulator phase itself. A clear experimental separation of the charge in the effective surface states into its components, including their polarity, is difficult. Each measurement method can only distinguish between certain kinds of charge and, thus, classifications depend to a large extent on the method of measurement employed. Since high-frequency ( $\sim 1$  MHz) C-V measurements are relatively easily and rapidly carried out[31], and since it has been shown[32-33] that they can yield interesting, meaningful results if the proper experimental conditions are established and if care is taken in their interpretation, it is advantageous to classify the surface states in the MIS system on the basis of this measurement method. Thus, we have the following two categories.

(1) Interface states are stationary electronic states located right at the (Gibbsian) plane separating the semiconductor from the insulator. Interface states are analogous to the fast surface states mentioned above. Because the insulator has a wide forbidden gap, the energy levels of interface states can lie either within or outside the forbidden gap of the semiconductor. This will determine whether or not they change their charge state when a field is applied between metal and semiconductor.

(2) Oxide charge is charge that is trapped in the space-charge region of the insulator film and cannot communicate with the semiconductor surface. There are two forms of this charge, namely, mobile and immobile.

The immobile species is mainly held in traps that are part of the intrinsic defect structure of the insulator; the mobile charge is mostly due to ions that are capable of migrating through the insulator, especially during conditions of high field and elevated temperature.

#### C. MEASUREMENT METHODS

Several measurement methods are available that give certain distinctions between the various types of charge in the MIS system.

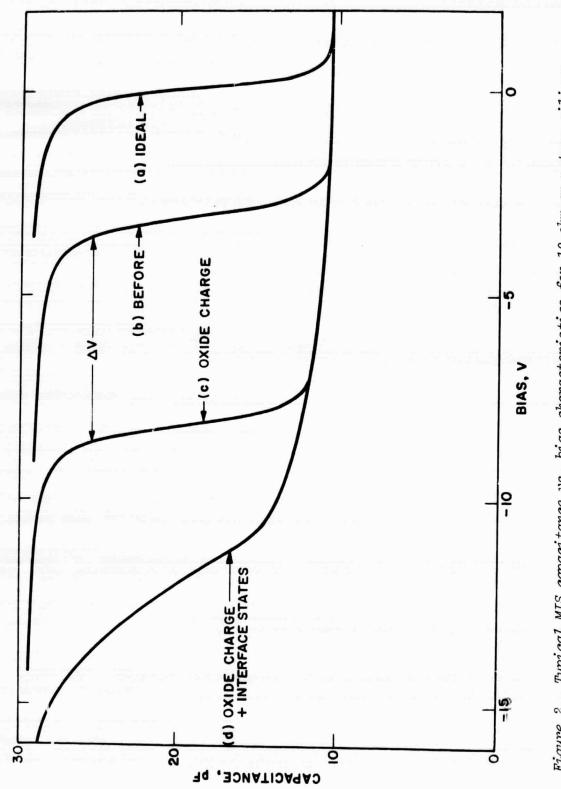

#### The High-Frequency MIS Capacitance (C-V) Method

The small-signal differential admittance of an ideal MIS capacitor with no surface states consists of the insulator capacitance, Ci, in series with the surface space-charge layer capacitance, C<sub>sc</sub>[34-38]. C<sub>i</sub> is independent of frequency. Csc also is independent of frequency in the accumulation and depletion regimes (up to 10<sup>11</sup> Hz), but in the inversion regime, C<sub>sc</sub> takes on different forms depending on whether or not the minority carriers can follow the applied ac signal and/or bias. The dependence of this ideal MIS capacitance on effective bias is shown in Figure 2(a) for the case of a metal -SiO<sub>2</sub> - Si structure. In all cases, this capacitance is uniquely determined by the semiconductor surface potential,  $\psi_s$ . For an actual MIS diode in which surface states are present but in which loss mechanisms are neglected, the above equivalent circuit is modified by adding the surface state capacitance,  $C_{ss}$ , in parallel with  $C_{sc}$ . The dependence of  $C_{ss}$  on frequency and surface potential is a function of the density of surface states and their spatial and energy distribution[39]. Since this is, in general, not known, little information about the physical properties of the interface can be obtained from an analysis of the MIS C-V characteristics obtained at an arbitrary frequency. However, if the measurement frequency is sufficiently high so that surface states cannot follow, then the surface-state capacitance becomes zero and the MIS capacitance reduces to its high-frequency form, i.e., the series combination of C<sub>i</sub> and C<sub>sc</sub>. When this condition is satisfied, the MIS capacitance is unambiguously related to the semiconductor surface potential. However, there is a difference between an experimentally determined high-frequency C-V characteristic and one computed for an identical structure without surface states, and this is the voltage due to the total charge in surface states. By finding the difference,  $\Delta V$ , between the measured voltage for a given capacitance value, say the "flat-band" capacitance, and its "ideal" value, one can determine the total charge that is trapped in surface states as a function of surface potential. The density of effective surface states for any particular value of capacitance, as reflected to the insulator-semiconductor interface, N<sub>ss</sub>, is then given by

$$\Delta N_{ss} = \frac{C_{ox}}{q} \Delta V = \frac{\varepsilon_{o}K_{i}}{q d_{i}} \Delta V$$

(3)

where  $C_{ox}$  is the insulator capacitance per unit area, q is the elementary electronic charge,  $\Delta V$  is the shift in the C-V characteristic along the voltage axis,  $\varepsilon_o$  is the free space permittivity, and  $K_i$  and  $d_i$  are the dielectric constant and thickness of the insulator, respectively. For grown silicon dioxide layers, this equation has constants as follows

$\Delta N_{ce}$  (states/cm<sup>2</sup>) = 2.11 × 10<sup>10</sup>  $\Delta V/d_1$  (micrometers)

If the experimental C-V curve is to the left of the ideal curve, the charge in surface states is positive; if it is to the right, the charge is negative.

2. The MIS Conductance (G-V) Method

The small-signal differential ac conductance, G, of an MIS diode is essentially due to the exchange of charge between interface states and the bulk semiconductor. If this conductance is measured as a function of bias and frequency, information concerning the density distribution, timeconstants, and capture cross section of the interface states present can be obtained[40].

3. The Channel Conductivity  $(I_d - V_a)$  Method

The property of MIS devices most commonly made use of in electronics is the modulation of channel conductivity g by gate bias  $V_g$ . Drain-to-source current  $I_d$  is, of course, controlled by g,

$$g = \frac{I_d}{V_{ds}} = \frac{W_{\mu}C}{L} \left( V_g - V_T - \frac{V_{ds}}{2} \right) , \qquad (4)$$

where  $V_{ds}$  is the drain-to-source voltage,  $V_g$  is gate voltage,  $V_T$  is "pinchoff" or threshold voltage (here taken as a negative quantity as in n-channel depletion devices),  $\mu$  is the carrier mobility, C is the gate-to-substrate capacitance per unit area, L is the channel length (i.e., source-drain separation), and W is the channel width. As "pinch-off" is a gradual phenomenon, the definition of  $V_T$  must include a statement as to the channel current or conductivity value chosen to represent the threshold between the turned-on and pinched-off conditions.

Under certain conditions, measurements of the shift in threshold voltage ( $\Delta V_T$ ) induced in an MIS transistor by radiation can be used to determine the density of charge  $\Delta Q$  newly introduced into the oxide. The introduction of positive charge into oxide states and interface states induces a balancing increase of negative conduction electrons in the channel. The product of C and  $\Delta V_T$  represents the amount of electronic charge that must be suppressed in the channel in order to bring the conductivity back to the defined threshold level.

Particular care is needed, however, in interpreting such data. Gatesource capacitance must be eliminated from C; it must be assumed that semiconductor doping is not changed by the irradiation; and  $V_{\rm ds}$  must be small enough to be insignificant in Eq. (4). If new interface states are generated by the irradiation (and several experiments discussed later suggest that they frequently are), the shape of the  $I_{\rm d}$ -V<sub>g</sub> characteristic will be affected, since changing the bias may now cause emptying or filling of these states. Thus, the calculated value of fixed oxide charge density from  $I_{\rm d}$ -V<sub>g</sub> characteristics will contain an uncertainty equal to the density of interface states created. Despite these limitations, the  $I_{\rm d}$ -V<sub>g</sub> characteristic is of use for studying the inversion regime, while the C-V characteristic gives more unambiguous data concerning the accumulation and depletion regime.

#### D. MECHANISMS OF RADIATION-INDUCED CHARGE PRODUCTION

I. "Fixed" Oxide Charge

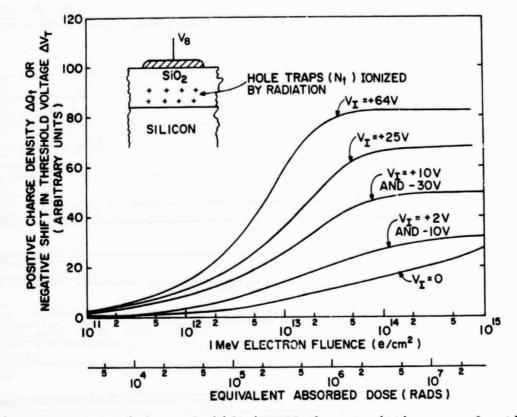

The parallel shift in electrical characteristics that occurs in MIS devices under radiation appears to be the most significant effect as well as the most amenable to analysis by virtue of the static nature of the charge configuration. The degree of parallel shift observed in MIS devices varies very widely with the nature of the insulator film. Indeed, for the normal-grown silicon dioxide layers, it will be seen that there is a striking dependence on the conditions used for the growth process. The degree of parallel shift is also very strongly dependent on the field applied across the oxide during the particle irradiation. In this report, the applied field is usually given in terms of the bias applied to the metallic gate of the device during irradiation, and is called the *irradiation bias*,  $V_I$ . Figure 3 is a generalized form of the behavior of those MIS devices that undergo virtually parallel shifts. The form shown is common to most of the data published and encourages the view that a common process occurs in most MIS devices.

Several features are worth noting. There is a strong dependence of the threshold-voltage shift  $(V_T)$  on irradiation bias, negative bias having a smaller effect than positive bias. At certain dose levels, saturation occurs, and this saturation level is higher under high bias. These features indicate that bias must have a strong effect on the permanent space-charge region produced in the oxide. The variability of this bias effect is indicated in Figure 4, which shows the dependence of voltage shift (converted to radiation-induced oxide charge density) on irradiation bias for four samples of oxide, which were grown at different times and in different

Figure 3. General form of shift in MIS characteristics as a function of integrated irradiation level. Gate bias during irradiation  $(V_I)$  is the parameter. The irradiation level is given in electron fluence and the equivalent dose in rads, absorbed from electrons.

atmospheres; and irradiated to  $10^{13}$  1-MeV electrons/cm<sup>2</sup>. While the shapes of both quadrants are, in all cases, roughly parabolic, it appears that strong individual differences exist in the profile of space-charge per Å vs. depth in these oxides. In other words, the charge-trapping capabilities of the regions near each interface in which charge is trapped by radiation are, in some way, different in each oxide.

The fact that, at zero bias, positive charge is built up in the oxide despite the absence of field is of considerable interest. If the features of this radiation-sensitivity vs. dose characteristic can be interpreted correctly and are found to bear a predictable relation to the sensitivity of the same oxide irradiated under bias, then a very simple sensitivity test of oxides will be possible. It will be possible to test oxide layers for radiation-sensitivity without the previous deposition of a metal electrode (which brings with it possibilities of contamination and other oxide

Figure 4. Radiation-induced shifts in MOS capacitor characteristics vs. irradiation bias,  $V_I$ , at a fluence of  $10^{13}$  1-MeV electrons/cm<sup>2</sup> (approx. 3 x  $10^5$  rads), for four different preparations of oxide. Shifts are normalized for thickness and expressed as oxide charge per cm<sup>2</sup>.

stresses), while the need for the arrangement of biasing contact during irradiation, always inconvenient, will be removed.

Etching studies have thrown some light on the form of zero-irradiation bias characteristic. After zero-bias irradiation, almost all the positive charge is found within 100 Å of the Si-SiO<sub>2</sub> interface. This probably corresponds to the region from which radiation-excited electrons can diffuse from the oxide even in the absence of an applied bias.

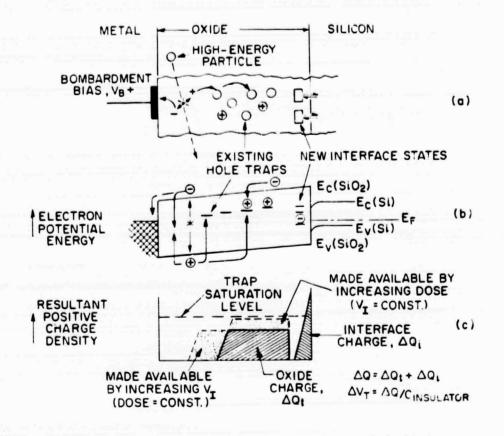

The above observations have led to the physical model for fixed oxide charge production shown in Figure 5[1]. Radiation generates electron-hole pairs in the insulator which subsequently interact with trapping sites within the insulating film. The radiation-generated electrons either recombine with the holes or move out of the insulator. The radiation-generated holes may diffuse in the insulator, but are less mobile than the electrons; many stationary hole traps are also present. The result is the net positive charge profile shown on this model. The influence of irradiation bias on

Figure 5. Model for the effect of high-energy radiation on MIS structures: (a) device cross section, (b) energy-band picture, and (c) oxide charge distribution.

the amount and location of the radiation-induced space charge is clear. If there is no electric field present in the insulator during irradiation, the major effect will be electron-hole recombination; only a relatively small number of holes will be trapped. If there is an electric field present, the electrons will readily move out of the insulator film, and the trapping of holes becomes significantly enhanced. Thus, a significant positive space-charge layer is built up at the insulator-semiconductor interface and moves into the insulator with continued irradiation. Most of this charge will be imaged in the semiconductor surface, and MIS measurements will show a large voltage shift.

If the gate is negative during irradiation, then in the simplest approximation one would expect the positive space-charge layer to be formed at the metal-insulator interface and to move into the insulator with continued irradiation. Most of the charge is imaged in the gate, and MIS measurements will not show an effect until the width of the space-charge layer is a significant portion of the insulator film. This may account for the flat minimum seen in Figure 4 at low negative irradiation biases.

If, in addition to the capture of holes, a significant trapping of electrons takes place, or if the insulator is somewhat conductive (as is most probably the case for certain silicon nitride films), then no significant net space charge will be built up.

#### 2. Interface States

The change in shape due to interface states shown in Figure 2(d) can be important in its effect on transistor operation, since a similar change in shape in the  $I_d-V_g$  characteristic corresponds to a reduction in gain. The generation of interface states by radiation is not well understood and varies from sample to sample less predictably than for fixed oxide charge.

The usual form, as shown in Figure 2(d), is the generation of a wide distribution of energy states throughout the silicon bandgap. This produces a smooth change in shape of the C-V or  $I_d-V_g$  characteristic. Occasionally, however, cases have been observed in which a defect is present that gives rise to a predominance of states concentrated around a single energy level. The states at this level appear to be enhanced by irradiation over and above the general background of other interface states at other energy levels. This leads to an unusual "stepped" characteristic which could cause unusual transistor characteristics[3].

In the early work on MOS capacitors, it was observed that the state of the silicon oxide interface before bombardment has a strong influence on the number of interface states produced by irradiation. A result like that of Figure 2(c) is produced if the degree of perfection of the interface is high. If, on the other hand, the original interface already has a high density of interface states, these states are usually enhanced. Most irradiations of mass-produced transistors involve some generation of distributed interface states, which are manifested as a change in the shape of the  $I_d-V_g$  curve and an increase in surface recombination velocity. In one experiment[21], a very strong generation of interface states actually reversed the direction of shift of the transfer characteristic of an nchannel transistor. In the experiment, the room-temperature transfer characteristic also became unstable under gate bias. The direction of the instability is such that if positive voltage is applied to the gate, the characteristic shifts toward more positive voltage; if negative voltage is applied, the shift is toward negative voltage. These shifts are opposite in direction to the temperature-bias instabilities observed in some devices, which are attributed to the motion of ionic species in the

oxide and occur only at elevated temperatures. The effect has, however, also been observed in unirradiated devices with large densities of interface states, such as many metal-silicon-nitride-silicon (MNS) devices. Kooi[15] also reported, but did not discuss, a slight instability of this kind in wet-oxygen-grown oxides irradiated by x-rays.

### III. APPROACH IN PRESENT PROJECT

#### A. GENERAL APPROACH

The objective of the present work was to elucidate, by investigation of well-characterized metal-oxide-semiconductor (MOS) or other metalcharacterized metal-insulator-semiconductor (MIS) devices, the reason for the degradation of MOS transistors under high-energy radiation such as that found in space; and to determine, in particular, how changes in the fabrication techniques used could affect this degradation. It was already well appreciated that another factor played an important role in the degree of degradation of MOS devices under radiation, namely the electric field strength and field direction in the oxide during irradiation. Since a satellite would be operating for all of its lifetime under low-rate radiation, the mode of operation of the device (enhancement vs. depletion, n- vs. p-channel, high vs. low logic voltages) during that time was also important in determining the best type of MIS device to use in satellite electronics.

It was realized that mass-produced MOS transistors were not ideal test vehicles for two reasons:

- (1) Such devices are usually not well-defined as material systems; in mass-production semiconductor processing, little attention is paid to exact material compositions, especially with regard to trace impurities, so long as satisfactory device performance is achieved; in addition, the crucial gate insulator is frequently a layered structure.

- (2) The presence of source and drain contacts, usually in geometrically complex configurations (see Figure 6, for example), introduces complexity in analyzing any electric-field effects observed and may also introduce extra impurities into the gate oxide region.

With this in mind, it was decided that, while it was important to evaluate the present state of the art in mass-production oxide technology and device geometry, detailed conclusions on the physics of radiation effects on MIS devices could only be obtained in cases where the investigators had full control over every step in the fabrication of the device. This is not a new situation in radiation effects research but the condition probably holds more strongly in the present case than in any known case to date. A close and truly analogous case is that of glasses, where small changes in composition and processing can affect the colorations produced by irradiation. There is, indeed, some likelihood that the effect of radiation on glasses and MOS insulators arises from the same

Figure 6. Structure of a typical high-performance MOS transistor.

cause, namely from positive charges (holes) trapped at interband defect levels between the valence and conduction band of the oxide structure.

It was thus accepted that there was a considerable gulf between the devices actually used in satellites and the ideal test device for physical studies, and it was decided that both classes of device would be studied and special efforts be made to bridge the gap between them. The basic list of devices given below was decided upon.

It should again be emphasized here that the data on oxide condition, which can be derived from C-V<sub>g</sub> and  $I_d$ -V<sub>g</sub> characteristics, are complementary. C-V data can be used to calculate interface state densities in the accumulation and depletion regions. In these regions, the channel is pinched off, and hence no information can be obtained from  $I_d$ -V<sub>g</sub> characteristics. Conversely, the C-V technique is not useful in the inversion region because the frequency response of the inverted semiconductor space charge layer[41] is not simply determined; in this region, the MIS transistor is conducting and the variation of this channel conductance with bias can now be used to study interface states in the inversion region. Hence, the two methods can be combined to give information on the interface states throughout the bandgap. A particular example of this is discussed in the experimental section.

#### B. DEVICES STUDIED

1. Simple oxide films produced in steam and dry-oxygen furnaces used by RCA Laboratories' Electronic Research Laboratory or in other apparatus producing special insulating films, such as chemical vapor deposition reactors and anodizing chambers.

2. RCA "Pattern 7" transistors, a semi-integrated device of bar geometry suitable for the development of logic circuit designs, including complementary designs (see, for example, the recently released RCA TA 5361 complementary NOR gate and inverter combination). In this device, gate-substrate capacitance is small to allow for fast switching. The device is produced in a variety of forms as a part of the developmental work by RCA Electronic Components\*. Complete details were available on small batches produced by this activity in very wellcontrolled furnaces.

3. Simple oxide films produced in the same furnaces as the abovementioned two devices under the same processing conditions and passed on to the experimenters without further treatment for evaluation by the C-V technique.

4. Commercially available RCA TA 2578 transistors, which are designed for use in low-frequency amplification circuits. This device has a large gate-substrate capacitance and channel area and, hence, is suitable for comparative C-V and  $I_d$ -V<sub>g</sub> measurements. Also, the gate is an enclosed structure and, hence, leakage effects should be minimized.

5. Other MOS transistors and arrays which had special properties likely to add information to the study (e.g., complementary MOS logic arrays and large-geometry transistors). The ability to evaluate unmodified films by the C-V technique and to obtain these from several different facilities was regarded as very important in the attempt to discover the important processing steps in determining radiation resistance.

#### C. MIS CAPACITOR SELECTION

One of the ways in which MOS capacitor study is particularly convenient is in the ability to study samples with known initial interfacestate density. Oxides are grown on silicon wafers in conditions which give rise to very low interface-state density. Since the oxide thickness may be measured accurately by ellipsometry, the "ideal" C-V characteristic can be calculated and the interface-state density estimated by noting the deviation of shape from the ideal. In the present study, samples with high interface-state density rejected.

\* Located at Somerville, N. J.

Preliminary observations[3] showed that samples with low interfacestate density developed fewer additional interface-states under radiation. Thus, it was possible to find many samples in which interface-state production under irradiation could be neglected by comparison with the number of bulk oxide charges produced. This situation made it possible effectively to isolate, and to concentrate upon, the problem of bulk oxide charge in the present study.

The main processing parameters of the capacitor gate insulators to be varied were: crystallographic orientation of substrate, oxide growth atmosphere, growth temperature, post oxidation annealing temperature and atmosphere, and oxide thickness. As well as varying the above parameters for simple thermal silicon dioxide layers, some deposited insulators containing large amounts of dopant impurity were also to be studied for gross impurity effects.

#### D. MIS TRANSISTOR TEST VEHICLE CONSIDERATIONS

The MIS transistor is essentially an MIS capacitor in which contact to the semiconductor surface channel has been effected. "Active" operation of the device consists of control of the electric field at the surface of the semiconductor and consequent control of the density of charged carriers (electrons or holes) at this surface. It is, of course, still possible to measure capacitances, although with less accuracy than in a large-area capacitor. Figure 6 shows the construction of a typical high-performance device. For the device shown (n-channel) the starting material is a slab of p-type semiconductor into which n<sup>+</sup> regions are diffused (source and drain regions) forming two  $p-n^+$  junctions with the substrate. An insulator is then placed between the two junctions and a metal electrode (the gate) is placed on top of the insulator. In operation the source and substrate are grounded and a voltage is applied to the gate in such a manner as to have the two p-n junctions back-biased. For the case shown in Figure 6, a positive voltage applied to the gate causes the semiconductor surface to become electron-rich. Consequently, the two n<sup>+</sup> regions are connected by a surface channel and conduction occurs. The exact value of the gate voltage at which conduction begins is determined by such factors as the insulator thickness, the doping density of the substrate and the density of oxide charge and interface states. Since the dependence of device parameters on insulator thickness and substrate doping density can be calculated, the gate voltage at which conduction begins in an MIS transistor can be used to characterize the surface states. Hence, an analysis of the transfer characteristic, drain current vs. gate voltage  $(I_d - V_g)$ , of an MIS transistor is a convenient way to characterize the effects of space radiation.

Figure 1 shows a plot of the C-V and transfer characteristics of an MOS transistor with no surface states (solid line) and the shift one sees in these characteristics when a fixed positive charge is introduced in the insulator (dashed line). The introduction of this fixed positive charge is typical of what happens in a radiation environment. As can be seen in the illustration, both characteristics shift by the same voltage, and either can be used to characterize the surface states.

The density of interface states can be calculated by measuring the widening of the C-V characteristic. This is accomplished by taking the difference between the shift in flat-band voltage and the shift in the gate voltage for, say,  $I_d = 1 \times 10^{-5}$  A, and making appropriate normalizing corrections.

#### E. RELEVANCY OF MOS CAPACITOR DATA TO TRANSISTOR PROBLEM

It has been stated earlier that the MOS transistor is not an ideal vehicle for determining the basic principles of charge buildup in the gate oxide of the MOS structure. It must likewise be stated that the simple MOS capacitor cannot simulate all the conditions present in an MOS transistor. The most important of these is probably the asymmetry of the electric fields in the gate oxide of an operating MOS transistor. If the device is "off," then different fields exist between the gate and the source and drain electrodes. Also, the source and drain diffusions in the oxide may cause an unintentional doping of the gate oxide (which is usually grown after source-drain diffusion).

Summarizing, the gate oxide of a practical MOS transistor device may contain several complexities, in lateral fields, lateral doping profiles, and stratification of the insulator which complicate the analysis of radiation effects in the gate oxide. However, the basic oxide structure is the same in MOS capacitors and transistors, and many conclusions on capacitors can be transferred to the transistor case.

#### F. SPECIAL EXPERIMENTS

In addition to varying materials and processes to determine the influence of fabrication parameters on radiation sensitivity there are some special, but important experiments that will help in confirming and extending the existing physical model for the effect of ionizing radiation on MIS structures.

Experiments of type 1, below, formed a part of the present project. Experiments of types 2 and 3 were not performed but data from earlier tests[3] provided general guidance in analyzing the data produced during this project. It is suggested that experiments of the latter types should also form a part of future work and they are cited below to indicate their relation and importance to the present study.

(1) The spatial location of the charge induced by the radiation in the insulator is of particular interest and can be ascertained by a so-called dissolution experiment. This can be achieved by a stepwise removal of an insulator layer, subsequent thickness determination by ellipsometry, and measurement of the remaining charge by the C-V technique.

(2) Temperature annealing of the radiation-induced damage can provide additional information concerning the physics of the mechanism of degradation. The annealing of radiation damage is usually complicated and not well understood, and in many cases it does not appear that annealing is the reverse of irradiation. Nevertheless, in a basic study of the radiation physics, annealing experiments cannot be neglected.

(3) Energy-level spectroscopy is the study, by means of optical absorption, of the energy distribution of the radiation-induced defect levels within the forbidden gap of the insulator. Again, this type of investigation can shed considerable light on the nature of the defects and thus on the process of radiation damage.

## IV. EXPERIMENTAL DETAILS

### A. IRRADIATION SOURCES

#### I. I-MeV Van de Graaff Generator

The most frequently used source of radiation in this study was the RCA Laboratories' Van de Graaff generator. Bare MOS devices were irradiated in air at the exit window of the accelerator beam tube. The devices were removed at various intervals in the exposure and their characteristics were recorded. The beam current was checked at the beginning of the exposure and at various intervals during the exposure with a vacuum Faraday cup. In almost all exposures the electron beam energy was kept at 1 MeV. It has previously been shown[2,3,10] that such conditions produced essentially the same results as irradiation to the same ionizing dose under vacuum or in typical transistor encapsulant atmospheres (dry nitrogen, etc.). The electron beam current was measured with a vacuum Faraday cup. The irradiation was interrupted at various fluence levels, and the characteristics of the MOS device were measured.

#### 2. Cobalt-60 Gamma Ray Source

Experiments requiring low dose rates were performed in a 3000-curie Cobalt-60 chamber located at Evans Signal Corp. Laboratories, Belmar, New Jersey. Various dose rates were obtained by placing the sample at different distances from the source. Calibration of the source was accomplished by means of a Victoreen chamber. As in the case of the Van de Graaff experiments, the exposure was interrupted at various intervals and the characteristics of the device were recorded.

#### B. TEST EQUIPMENT

#### I. Automatic C-V Plotter

C-V measurements are normally carried out on a point-by-point basis using a capacitance bridge. Then the data have to be plotted. Such a procedure is extremely cumbersome, time-consuming, and subject to frequent error. To eliminate this problem an experimental arrangement has been developed\* which allows the automatic and rapid measurement of C-V characteristics of MIS structures at 1 MHz over a wide

\*Funded by RCA.

range of bias and sweep speed and under a variety of experimental conditions. The apparatus consists of standard laboratory equipment, provides a graphical output, and makes possible the rapid study of certain problems in MIS physics. For the comparison between experimental and theoretical C-V curves a computer program in FORTRAN has been developed. A detailed description of the measuring circuit and a discussion of the various applications have been published elsewhere[31]. We shall outline here only the principle of operation of this apparatus and its main applications.

In this circuit, the actual quantity measured is an impedance. Hence, the need for a phase-sensitive detector is eliminated. A sawtooth voltage is applied to the MIS capacitor to provide a smoothly varying bias, and a 1-MHz oscillator is used as the signal source. The basic measuring circuit is shown in Figure 7. If the conditions

$$R_{M} \ll 1/\omega C_{x} \text{ and } C_{b} \gg C_{x}$$

(5)

are satisfied, the magnitude of the ac voltage appearing across the measuring resistor  ${\rm R}_{\rm M}$  is

$$|\mathbf{v}_{\mathbf{M}}| = |\mathbf{v}| \ \omega \ \mathbf{R}_{\mathbf{M}} \mathbf{C}_{\mathbf{x}}.$$

Here,  $C_x$  is the MIS capacitance,  $C_b$  a blocking capacitor, and  $\omega$  the frequency of operation. The magnitude of the ac signal from the oscillator is |v|, and it is adjusted so that the signal across  $C_x$  is never larger than 20 mV. If the reactance of the capacitor is much larger than 50 ohms, then |v| is essentially constant and  $|v_M|$  is proportional to  $C_x$  and can be used as a measure of  $C_x$ . Bias is applied to the MIS capacitor through a parallel branch which is ac-shorted by the series combination of  $C_b$  and  $R_M$ . If  $v_M$  is displayed as a function of the applied bias, then the envelope of the resulting curve is the C-V characteristic. Since  $|v_M|$  is only about 0.2 mV, amplification is necessary. This is achieved by the amplifier indicated, which has a gain of about 100 dB. The amplified signal is detected and the dc voltage, which is proportional to capacitance, can then be exhibited as a function of the applied bias on either an x-y recorder or x-y oscilloscope, depending on the rate of change of bias.

This apparatus allows the so-called three-terminal measurement of a capacitor. In this circuit, neither terminal of the test capacitor,  $C_x$ , is at ground potential. Shunting to ground by lead capacitance and other stray capacitances that may exist to other parts of the diode structure is thereby eliminated. The losses associated with the MOS device may introduce an error in the measured capacitance. However, these can be kept below 5 percent if the Q of the device is somewhat better than 3. Using present-day silicon dioxide technology, such low loss levels are easily obtained. The range of measurable capacitance is 100 pF/inch to 0.1 pF/inch and the maximum accuracy is 2 percent. The excellent agreement with bridge measurements is shown in Figure 8.

Figure 7. Simplified schematic of the C-V measuring apparatus.  $R_1 = 50$  ohms,  $R_b = 10$  kilohms and  $C_b = 0.01$  µF.

Figure 8. MIS capacitance vs. bias as obtained by measurement with the automatic plotting equipment and with a Boonton Electronics 75 A Capacitance Bridge.

## 2. Automatic I d-V Characteristic Plotter

A schematic diagram of the basic circuit used for the measurement of the transfer characteristic is shown in Figure 9. The gate bias sweep circuit consists of the positive sweep from an oscilloscope being driven

Figure 9. Simplified schematic of MOS transistor transfer characteristic measuring apparatus.

against a battery supply and associated potentiometer so that the voltage could be trimmed to the proper magnitude. The ammeter was a Keithley 610 A electrometer which has an output suitable for driving an x-y recorder. The electrometer was operated in a mode so that the voltage drop across the instrument never exceeded 0.1 V. The drain supply was fixed at 10 V.

## V. EXPERIMENTAL RESULTS

#### A. CRITERIA OF RADIATION SENSITIVITY

It has been stated earlier (see Section II) that  $\Delta N_{ss}$ , the change in number of "surface states" produced in the cxide by a given process is, as defined here, a quantity in which fixed bulk oxide charge and bias-dependent interface charge may both be included. This is so because it is derived simply from  $\Delta V_{fb}$ , the change in flat-band voltage of the C-V characteristic. If a large number of interface states are present in the oxide,  $\Delta V_{fb}$  is thus not a good measure of the fixed oxide charge produced by radiation, although it may still serve as a gross characterization of the sensitivity of an oxide to radiation.

In this report it can be assumed that, unless otherwise indicated, the shifts in flat-band voltage ( $\Delta V_{\rm fb}$ ) were taken for samples which exhibited a near-parallel shift of the whole C-V or I-V characteristic. Hence, the  $\Delta N_{\rm SS}$  values consist largely of fixed oxide charge and not bias-dependent interface charge. The error in  $\Delta N_{\rm SS}$  introduced by this assumption will not be greater than 10% and frequently less, since the preparation of the oxides was carried out by methods which allowed only very small quantities of interface states to form; and samples for which the C-V characteristic indicated an appreciable concentration of bias-dependent interface states after fabrication and before irradiation were rejected for most analyses made here.  $V_{\rm fb}$  was calculated from C-V plots as follows: The flat-band voltage ( $V_{\rm fb}$ ) of an MOS capacitor is that gate voltage for which

$$\frac{c}{c_{o}} = \frac{1}{1 + c_{o} \left(\frac{kTq}{\epsilon_{s}q N}\right)^{1/2}}$$

(6)

where C = measured capacitance

- $C_0 = oxide capacitance$

- $\varepsilon_s$  = dielectric constant of semiconductor

- q = elementary electronic charge

- N = semiconductor doping density

- k = Boltzmann constant

- T = temperature in degrees Kelvin.

This fraction is sometimes called normalized flat-band capacitance value  $C_{\rm fb}/C_{\rm O}$ . If the experimenter is analyzing a C-V curve without the benefit of data on doping density, N, this can be calculated from the ratio of the minimum capacitance to the oxide capacitance,  $C_{\rm min}/C_{\rm O}$ . Curves for rapid

calculation of this quantity are presented in a series of graphs in reference 31.  $C_{\rm fb}/C_0$  can then be read conveniently from another curve in this reference. For example, for a p-type semiconductor with a 1000 Å-thick oxide, if the measured  $(C_{\rm min}/C_0) = 0.25$ , then the doping density can be found from the curves to be  $N_a = 10^{15}/\text{cm}$  (about 13 ohm-cm). Using this as input data for another curve the normalized flat-band capacitance can be found; in this example,  $C_{\rm fb}/C_0 = 0.7$ .

Irradiation conditions used were determined by several considerations. Firstly, although the importance of irradiation bias (bias during irradiation) on radiation effects in MOS devices was realized, it was decided to survey first a wide range of oxides without irradiation bias, since as wide a survey as possible in the time available was thought preferable to more information on bias effects over a narrower range of devices\*. Bias effect studies were limited to a few series of oxides. Secondly, "saturation" of the radiation effect was not sought, as in some other studies [19,42], since the effects of radiation levels likely to be reached in operating satellites will not eve. approach saturation (105 in space vs. 10<sup>9</sup> rads for good saturation). The radiation levels of most interest in space applications were considered to be  $10^{11}$  to  $10^{15}$  e/cm<sup>2</sup> (approximately equivalent to  $3 \times 10^3 - 3 \times 10^6$  rads). Thirdly, other studies[10,18] indicated that any source of ionizing radiation could be used for the work and that bulk displacement damage in the silicon did not have to be considered when studying oxide effects. Thus, results obtained using 0.1- to 1-MeV electrons, x-rays, Cobalt-60 or reactor gamma-rays could be regarded as interchangeable, so long as the amount of ionization in the oxide (expressed as ergs/gm or rads absorbed) was used as the criterion of comparison.

Note added after submission. Recent rapid 1-MeV electron irradiations by P. Newman (private communication) indicate that significant differences exist between  $\Delta V_T$  shifts observed when gates are grounded to substrate as opposed to when gates are left floating. The probable reason is a buildup of negative charge on the gate and hence a buildup of oxide field during irradiation. The result is a difference in the  $\Delta V_{T}$  vs. flux curves which do not saturate as early in the "floating" case as in the "grounded" case. Above fluences of about  $10^{12}$  e/cm<sup>2</sup>, the curves thus separate. At the reference fluence of  $10^{13} \text{ e/cm}^2$ , separation is of the order of 1 volt. Early in the experiments recorded in this report, MOS capacitors were irradiated without any form of contact to the metal islands which were thus floating. Later, spring-loaded tungsten probes were used to contact at least three islands per chip irradiated. In all experiments with MOS transistors the chips were mounted and wire-bonded and gates were routinely grounded. Throughout the tabulations given here, the electrical state of the gate is noted. It is not thought that the possible buildup of charge during the above survey experiments invalidates the comparison of different oxide processes since the irradiation rates and other conditions were the same in most cases.

### B. DEPENDENCE OF RADIATION SENSITIVITY ON OXIDE GROWTH CONDITIONS

### I. General

Since the silicon dioxide layer of MOS devices is usually formed by diffusion-limited inward growth, it is to be expected that the defect structure of the oxide (hence, its radiation sensitivity) will be strongly affected by variations in growth rate and the components of the oxidation atmosphere. Thus, it is not surprising that some significant differences in sensitivity appear to exist between films grown in dry oxygen and in steam, when irradiated either with or without an applied field during the bombardment. The results of these experiments on very pure laboratory-grown dry oxides and steam-grown oxides will now be discussed.

### 2. Oxides Grown in Dry Oxygen

a. Preparation - Insulator films of thicknesses ranging from 800 to 2000 Å were prepared by diffusion-limited oxidation or "growth" in an rf (radio-frequency-heated) furnace. The furnace consisted of a vertical vitreous silica tube which was cooled by a stream of forced air passing through an outer jacket. The silicon specimens to be treated were supported by a graphite pedestal on a silica holder coated with silicon carbide. The pedestal acted as a susceptor, or energy-absorber, for the rf energy that was provided by an inductively coupled generator wound around the outside of the tube. Very pure inert or reactive gases could le passed up the silica tube and over the pedestal. By this arrangement, evaporated impurities were carred away by the flowing gas or trapped on the cold tube wall.

Temperature was controlled automatically be means of the signal from an infrared detector which viewed the silicon sample through an optically flat silica plate in the top of the furnace. Most oxidations were carried out by passing pure dry oxygen over the samples at temperatures varying from 900 to 1200°C. Post-oxidation annealing was conducted in helium, nitrogen, or hydrogen.

After oxidation, the samples were provided with a large-area back nickel contact to the silicon and with nickel dots ("gates") on top of the oxide. The contacts were evaporated in a vacuum system operating in the  $10^{-6}$  Torr range. The thickness of the evaporated nickel gates was  $0.1 \mu$  as estimated from a previous calibration of the evaporator. The gates were formed either by evaporation through a mask or by conventional photoresist etching from a continuous metal film. The size of the dots was usually 0.012 in. in diameter. No difference in the radiationsensitivity was observed for the two methods of gate deposition.