AC-F-3065-3 1 JULY 1967

**FINAL REPORT** VOLUME II

Prepared for

# INSTRUMENTATIONS AND COMMUNICATIONS DIVISION ASTRIONICS LABORATORY GEORGE C. MARSHALL SPACE FLIGHT CENTER Huntsville, Alabama

Approved by <u>L. W. Porter</u>

K. W. Porter, Chief Engineer Telecommunications Laboratory

AROD TEST MODEL HARDWARE **FINAL REPORT** CONTRACT NO. NAS8-11835

AROD SYSTEM FINAL REPORT AC-F-3065-3

#### ABBREVIATED TABLE OF CONTENTS

#### VOLUME I

Section I. Introduction

Section II. AROD Concept

Section III. Program History

Section IV. Program Results

REFERENCES

APPENDICES

A. Developmental Vibration Test

B. Pressure Test of AROD Base Plate

C. Results of Thermal Mock-up Test for the Vehicle-Borne AROD Unit

D. Thermal Test of a Typical AROD Cordwood Module

E. AROD Vehicle Borne Equipment, Reliability Analysis

F. AROD Ground Station Equipment, Reliability Analysis

VOLUME II

Section V. Vehicle-Borne Equipment

VOLUME III

Section VI. Transponder Station

Section VII. AROD Vehicle Checkout Equipment

Section VIII. Transponder Checkout Equipment

## TABLE OF CONTENTS

ľ

| Section  |            |         |           | Title                          | Р   | age   |

|----------|------------|---------|-----------|--------------------------------|-----|-------|

| SECTION  | <b>I</b> . | INTROI  | DUCTION   |                                | VOL | . I   |

| SECTION  | II         | AROD C  | CONCEPT   |                                | VOL | . I   |

| SECTION  | III        | PROGR   | M HISTOP  | RY                             | VOL | . I   |

| SECTION  | IV         | PROGR   | AM RESULT | TS                             | VOL | . I   |

| REFERENC | CES        |         |           |                                | VOL | . I   |

| APPENDIC | CES A      | Through | ı F       |                                | VOL | . I   |

| v        |            | VEHICI  | LE-BORNE  | EQUIPMENT                      | 5   | 5-1   |

|          |            | 5.1     |           | nstruction                     | 5   | 5-2   |

|          |            | 5.2     |           | Control Transmitter            |     | 5-22  |

|          |            |         | 5.2.1     | Technical Approach             | 5   | 5-25  |

|          |            |         | 5.2.2     | Circuit Descriptions           | 5   | 5-27  |

|          |            |         | 5.2.3     | Test Results                   |     | 5-32  |

|          |            | 5.3     | Control   | Data Modulator                 | 5   | 5-32  |

|          |            |         | 5.3.1     | Technical Approach             | E   | 5-32  |

|          |            |         | 5.3.2     | Logic Description              | . 5 | 5-37  |

|          |            |         | 5.3.3     | Output Filter Description. :   | . : | 5-37  |

|          |            |         | 5.3.4     | Test Results                   | , ; | 5-40  |

|          |            | 5.4     | Tracking  | g Transmitter                  | . ! | 5-40  |

|          |            |         | 5.4.1     | Technical Approach             |     | 5-42  |

|          |            |         | 5.4.2     | Functional Description         |     | 5-42  |

|          |            |         | 5.4.3     | Test Results                   | •   | 5-48  |

|          |            | 5.5     | Test Res  | sults                          | •   | 5-48  |

|          |            |         | 5.5.1     | AROD Frequency Converters      | •   | 5-48  |

|          |            |         | 5.5.2     | Tracking Subsection            | •   | 5-62  |

|          |            |         | 5.5.3     | Vehicle Receiver Code Control. | •   | 5-129 |

|          |            | 5.6     | Frequen   | cy Synthesizer                 | •   | 5-154 |

|          |            |         | 5.6.1     | Technical Approach             | •   | 5-156 |

|          |            |         | 5.6.2     | Circuit Descriptions           |     | 5-164 |

|          |            |         | 5.6.3     | Physical Description           |     | 5-174 |

|          |            |         | 5.6.4     | Performance Deviations         |     | 5-178 |

|          |            |         | 5.6.5     | Conclusion and Results         |     | 5-179 |

#### TABLE OF CONTENTS (Cont)

#### Section Title Page v VEHICLE-BORNE EQUIPMENT (cont) Data Measurements Subgroup. . . . . . . . 5.7 5 - 1805.7.1 5-181 Data Readout System . . . . . . . . . 5.7.2 5 - 195Velocity Extraction Unit. . . . . . 5.7.3 5-217 Range Extraction Unit . . . . . . . 5.7.4 5 - 2245.8 5 - 2405.8.1 System Philosophy and Requirements. . 5-242 5.8.2 Detailed Functional Description 5-242 5.8.3 5 - 2555.8.4 5 - 2685.8.5 5-272 5.9 5-273 5.9.1 5-273 5.9.2 Technical Approach. . . . . . . . . . . 5 - 2745.9.3 5 - 274Breadboard Test Results . . . . . . 5.9.4 5-281 5.9.5 5 - 2835.9.6 5 - 288Conclusions . . . . . . . . . . . . . . . . 5.9.7 5-288 5.10 Vehicle Transmitter Code Control. . . . . . 5 - 2895.10.1 Subsystem Requirements 5-289 . . . . . . . Functional Logic Description. . . . 5.10.2 5-290 Discrete Component Circuits . . . . 5.10.3 5 - 2965.10.4 5-297 SECTION VI TRANSPONDER STATION VOL. III SECTION VII AROD VEHICLE CHECKOUT EQUIPMENT VOL. III SECTION VIII TRANSPONDER CHECKOUT EQUIPMENT VOL. III

## LIST OF ILLUSTRATIONS

## Figure

## Title

Page

| 5-1  | Vehicle-Borne Equipment Functional Block Diagram                        | 5-3  |

|------|-------------------------------------------------------------------------|------|

| 5-2  | Case l Top View                                                         | 5-4  |

| 5-3  | Case 2 Top View                                                         | 5-5  |

| 5-4  | AROD Vehicle-Borne Equipment                                            | 5-7  |

| 5-5  | Station Control Transmitter.                                            | 5-8  |

| 5-6  | Vehicle Tracking Transmitter                                            | 5-9  |

| 5-7  | Bi-Phase Mod/Mult. X2                                                   | 5-11 |

| 5-8  | R-F Converter                                                           | 5-13 |

| 5-9  | Vehicle Tracking Receiver                                               | 5-14 |

| 5-10 | Typical R-F Cordwood Module                                             | 5-15 |

| 5-11 | Micro Matrix Technique                                                  | 5-16 |

| 5-12 | Digital Integrated Circuit Module                                       | 5-17 |

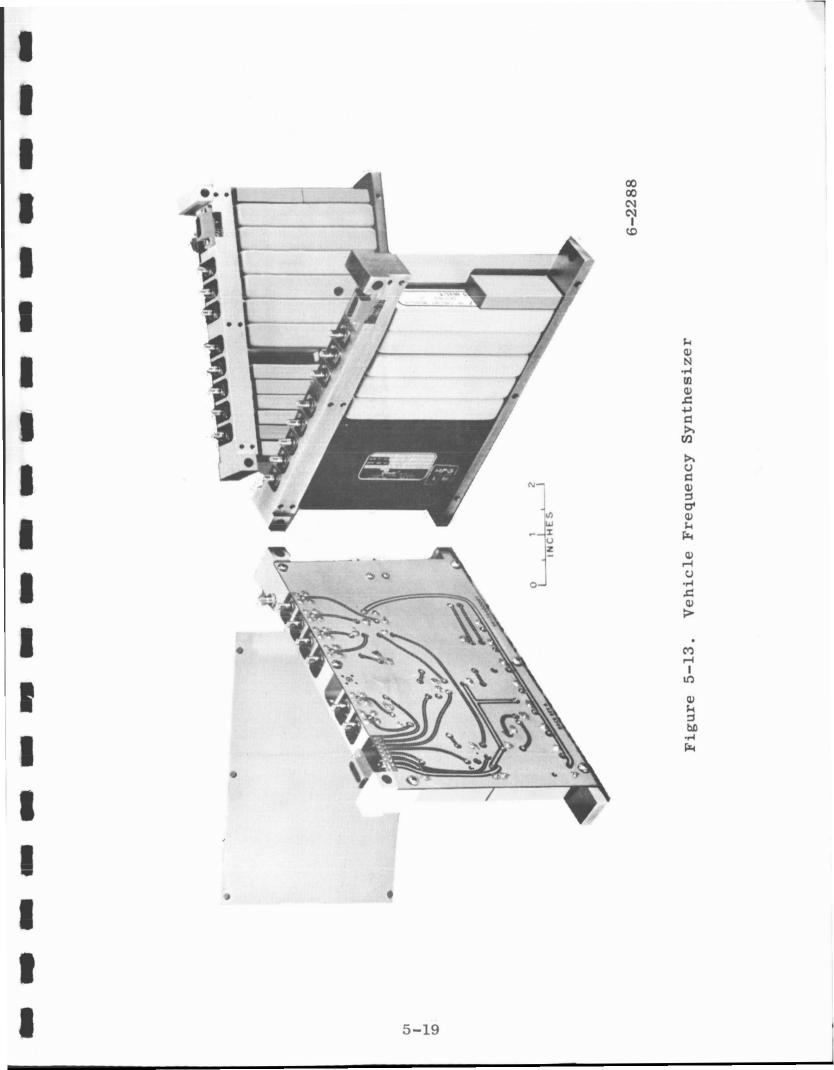

| 5-13 | Vehicle Frequency Synthesizer                                           | 5-19 |

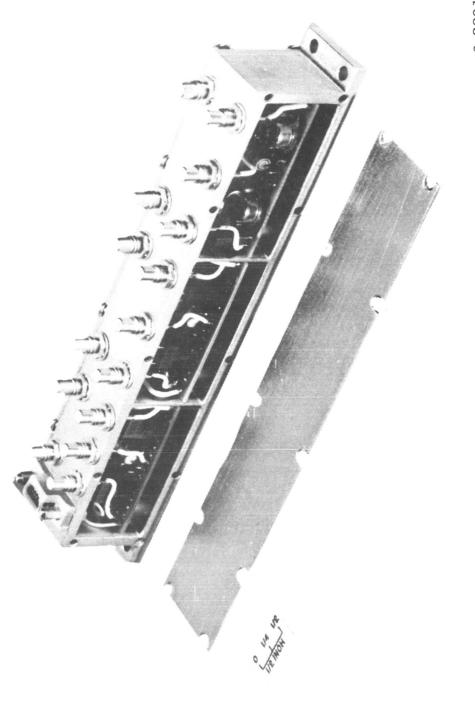

| 5-14 | Distribution Amplifier                                                  | 5-20 |

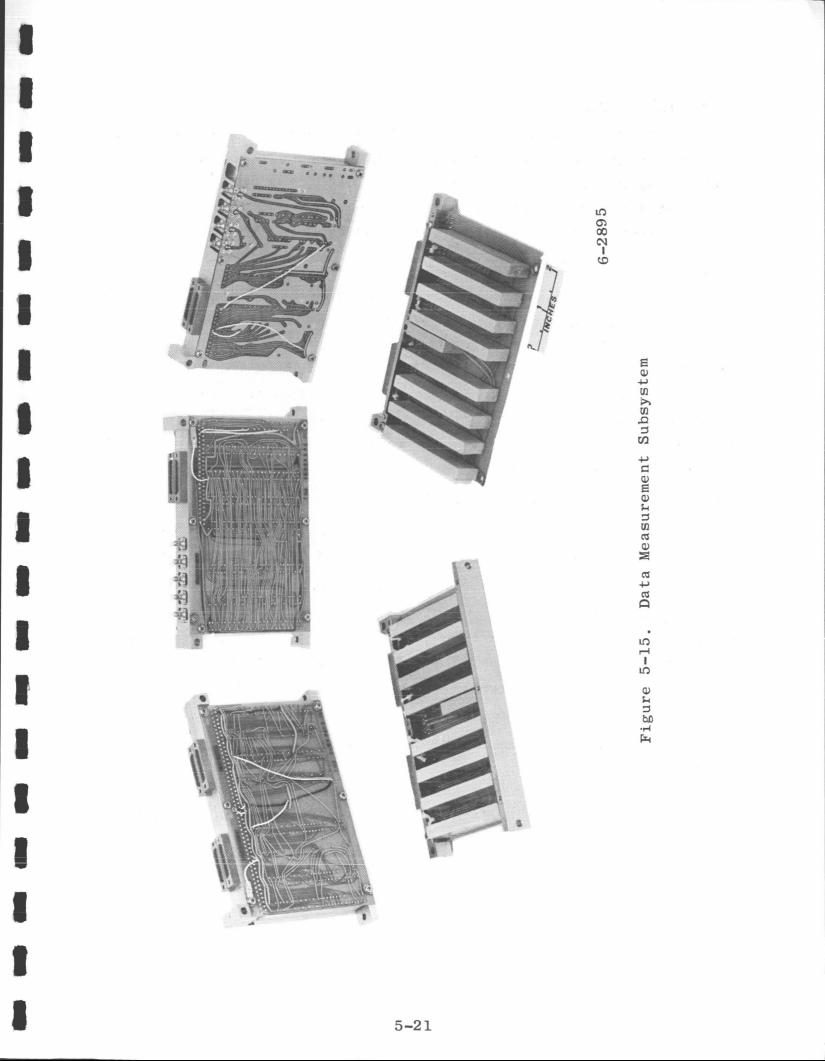

| 5-15 | Data Measurement Subsystem                                              | 5-21 |

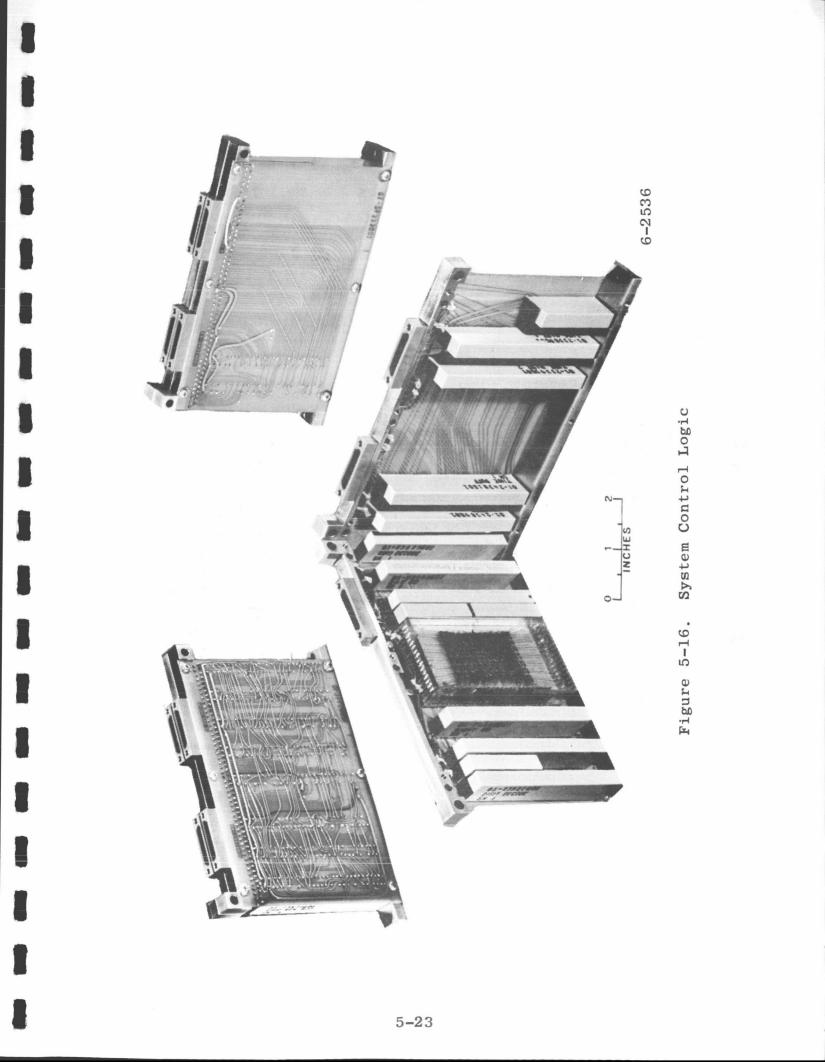

| 5-16 | System Control Logic                                                    | 5-23 |

| 5-17 | Vehicle Power Converter                                                 | 5-24 |

| 5-18 | Station Control Transmitter, Block Diagram                              | 5-26 |

| 5-19 | Station Control Transmitter, Schematic Diagram                          | 5-28 |

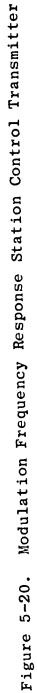

| 5-20 | Modulation Frequency Response Station Control<br>Transmitter            | 5-34 |

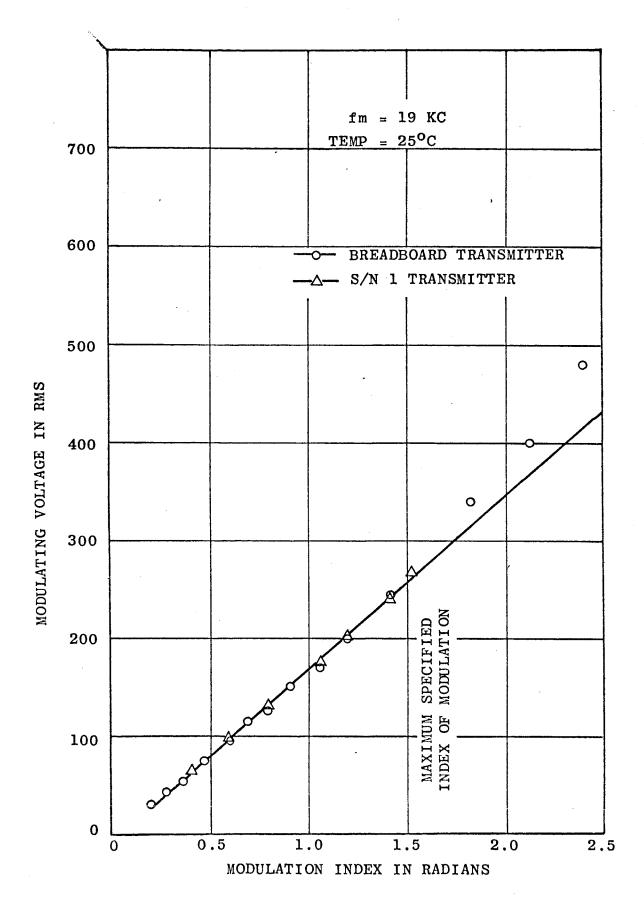

| 5-21 | Modulation Linearity Station Control Transmitter                        | 5-35 |

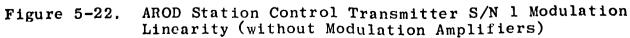

| 5-22 | AROD Station Control Transmitter S/N l Modulation                       |      |

|      | Linearity (without Modulation Amplifiers)                               | 5-36 |

| 5-23 | Station Control Transmitter, Motherboard Schematic<br>Diagram           | 5-38 |

| 5-24 | Station Control Transmitter, I/C Module Logic Diagram                   | 5-39 |

| 5-25 | Phase Modulation and Power Amplifier of Vehicle<br>Tracking Transmitter | 5-41 |

| 5-26 | Vehicle Tracking Transmitter, Block Diagram                             | 5-43 |

| 5-27 | TWTA Waveforms                                                          | 5-49 |

| 5-28 | Vehicle Tracking Transmitter, Schematic Diagram                         | 5-50 |

|      |                                                                         |      |

## LIST OF ILLUSTRATIONS (Cont)

| Figure | Title                                                                                         | Page  |

|--------|-----------------------------------------------------------------------------------------------|-------|

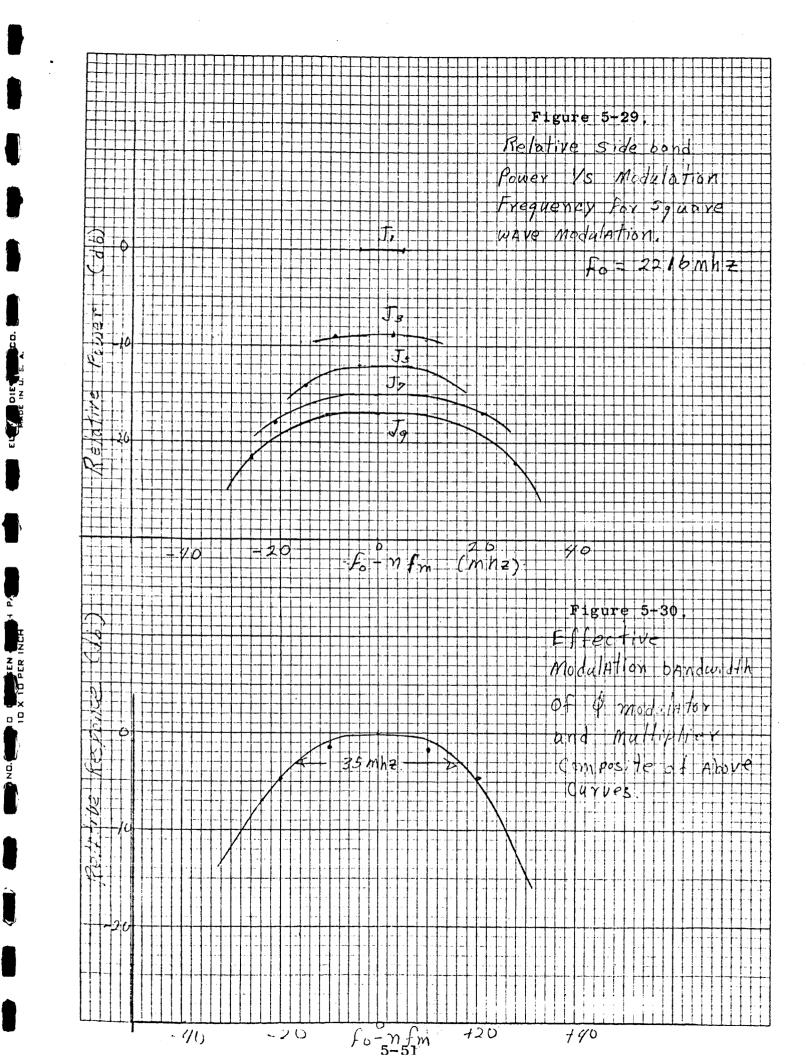

| 5-29   | Relative Sideband Power vs Modulation Frequency for Square Wave Modulation                    | 5-51  |

| 5-30   | Effective Modulation Bandwidth of Phase Modulator<br>and Multiplier Composite of Above Curves | 5-51  |

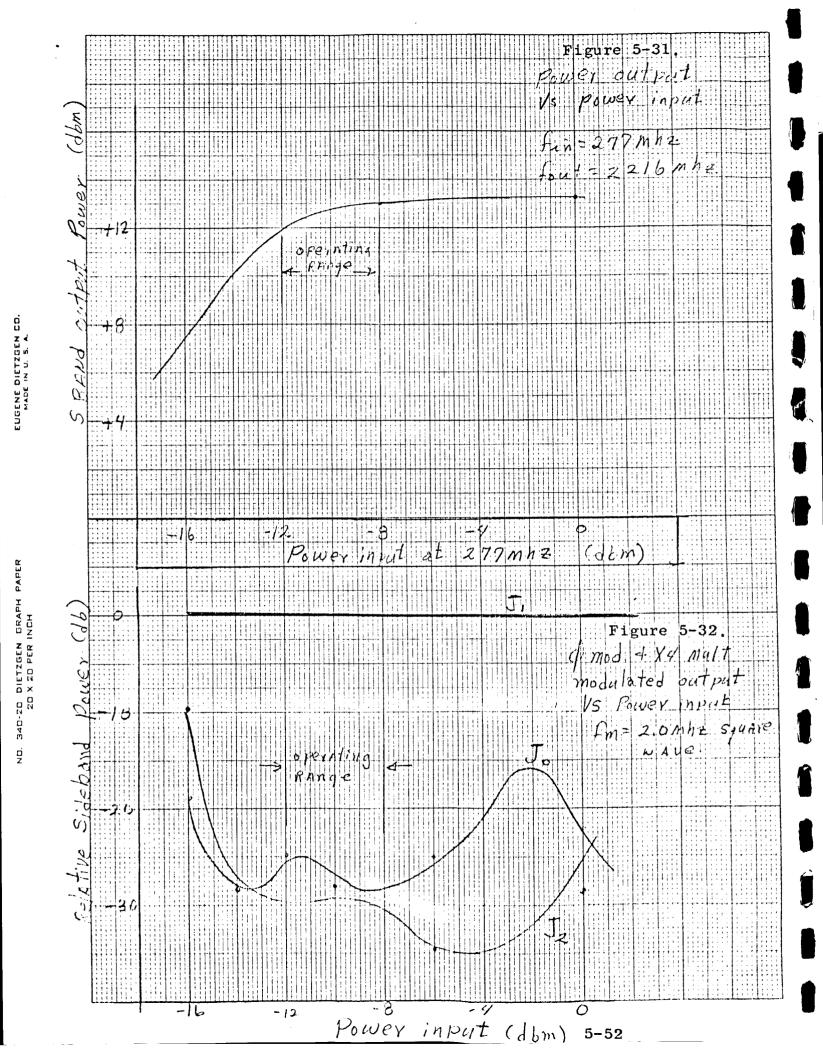

| 5-31   | Power Output vs Power Input                                                                   | 5-52  |

| 5-32   | Phase Modulator and X4 Multiplier Modulated Output vs Power Input                             | 5-52  |

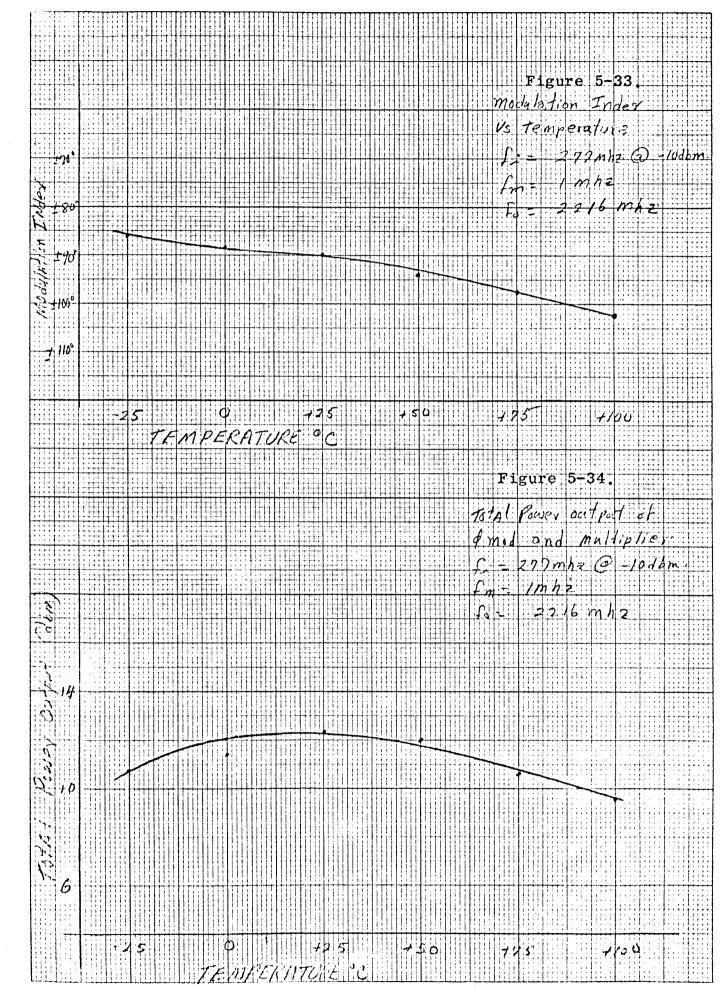

| 5-33   | Modulation Index vs Temperature                                                               | 5-53  |

| 5-34   | Total Power Output of Phase Modulator and Multiplier                                          | 5-53  |

| 5-35   | Vehicle TWTA Assembly                                                                         | 5-54  |

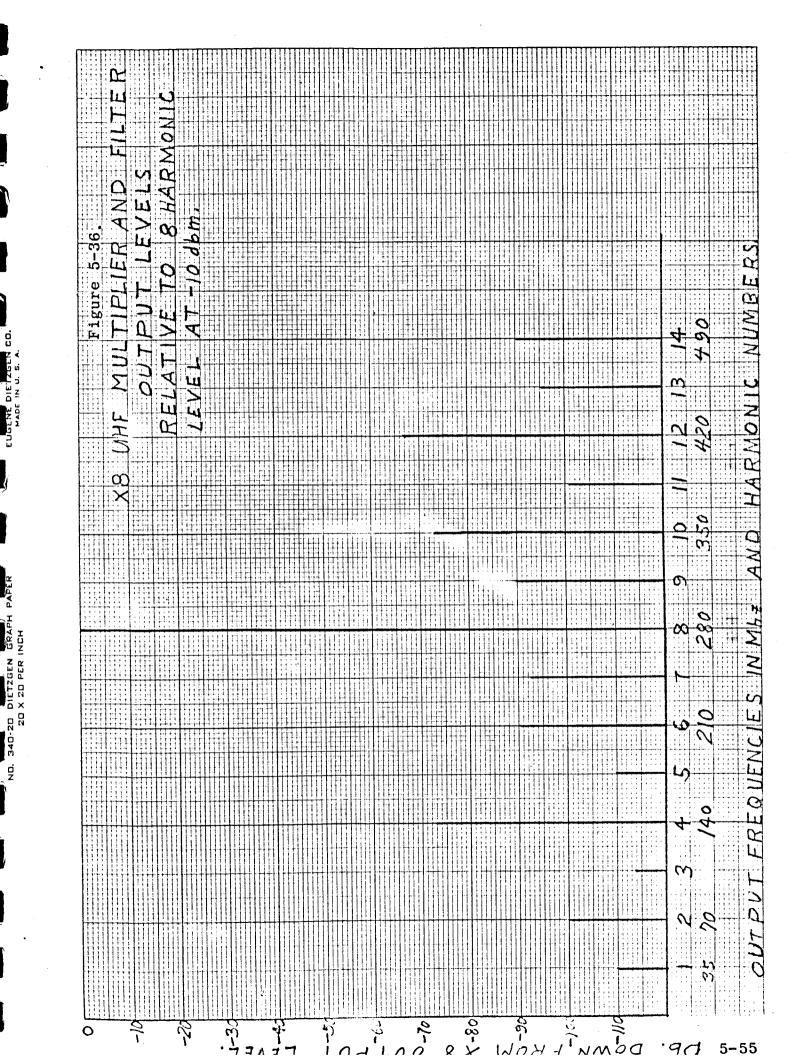

| 5-36   | X8 UHF Multiplier and Filter Output Levels Relative<br>to 8 Harmonic Level at -10 dbm         | 5-55  |

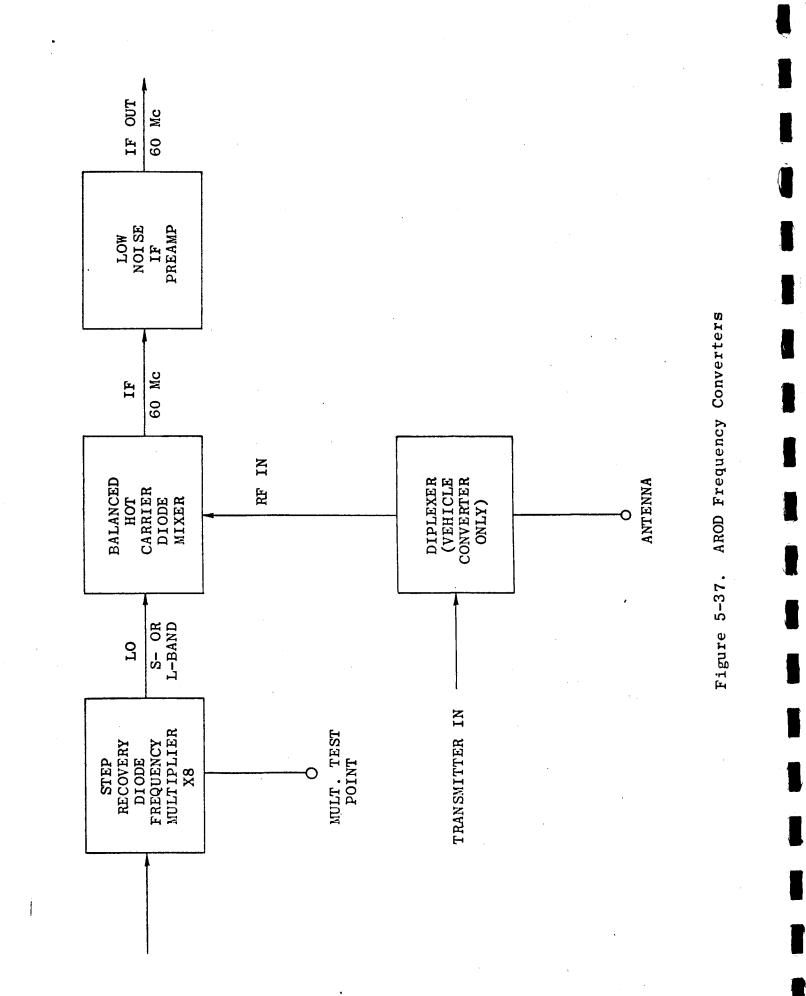

| 5-37   | AROD Frequency Converters.                                                                    | 5-60  |

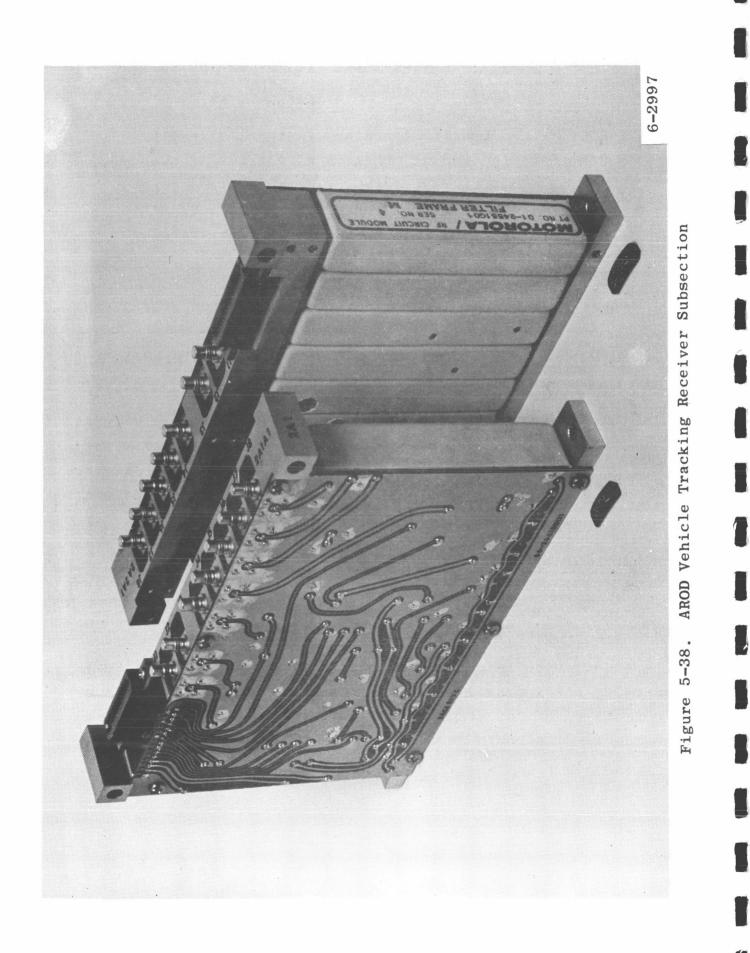

| 5-38   | AROD Vehicle Tracking Receiver Subsection                                                     | 5-66  |

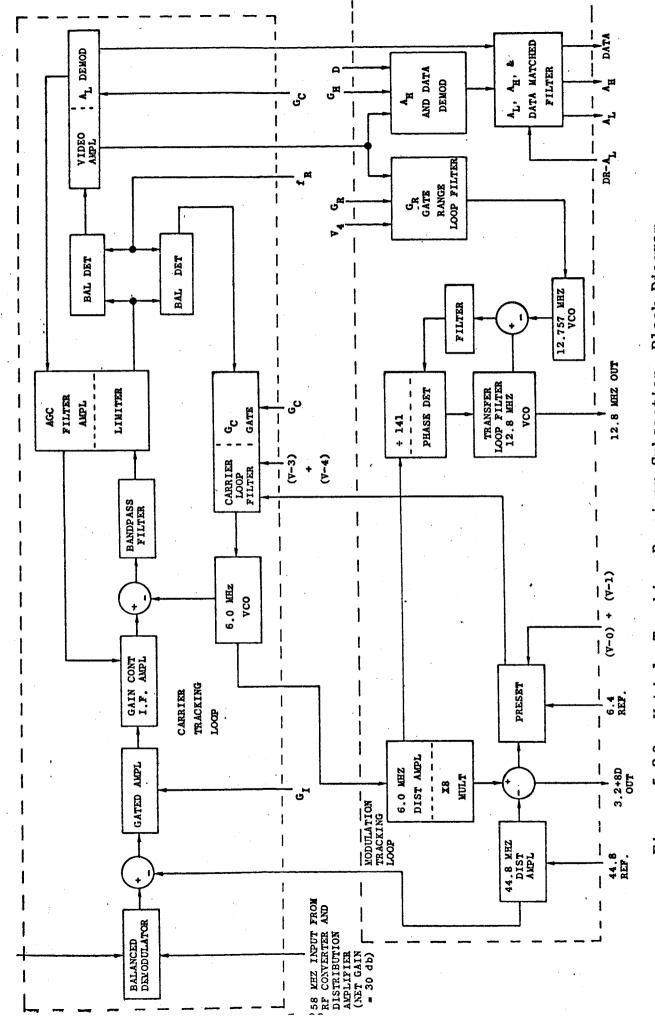

| 5-39   | Vehicle Tracking Receiver Subsection, Block Diagram.                                          | 5-69  |

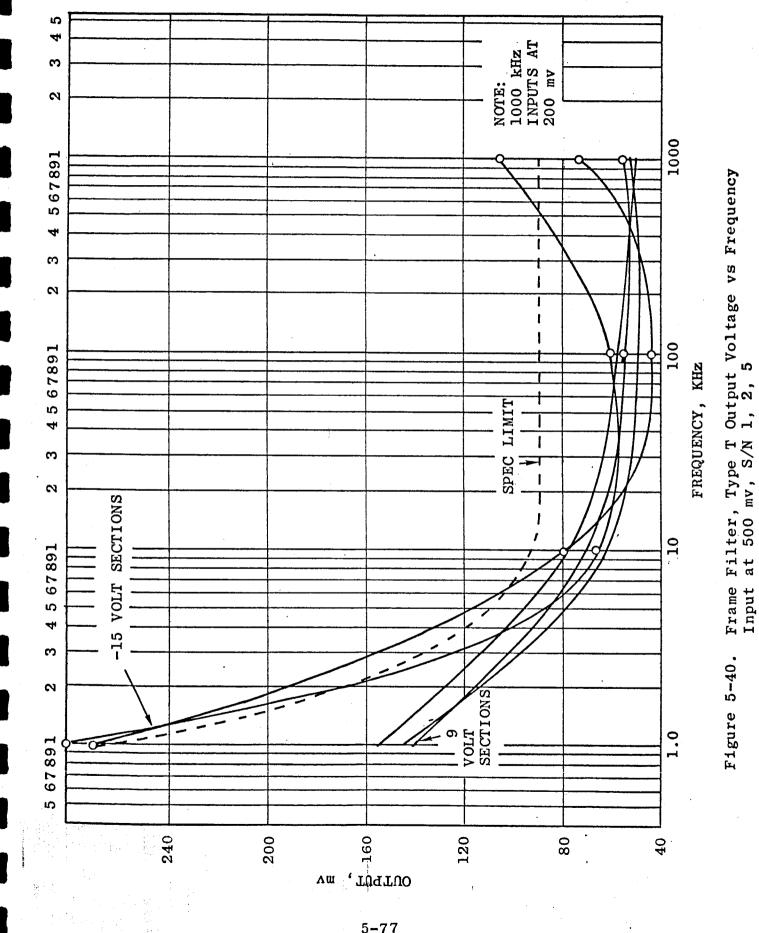

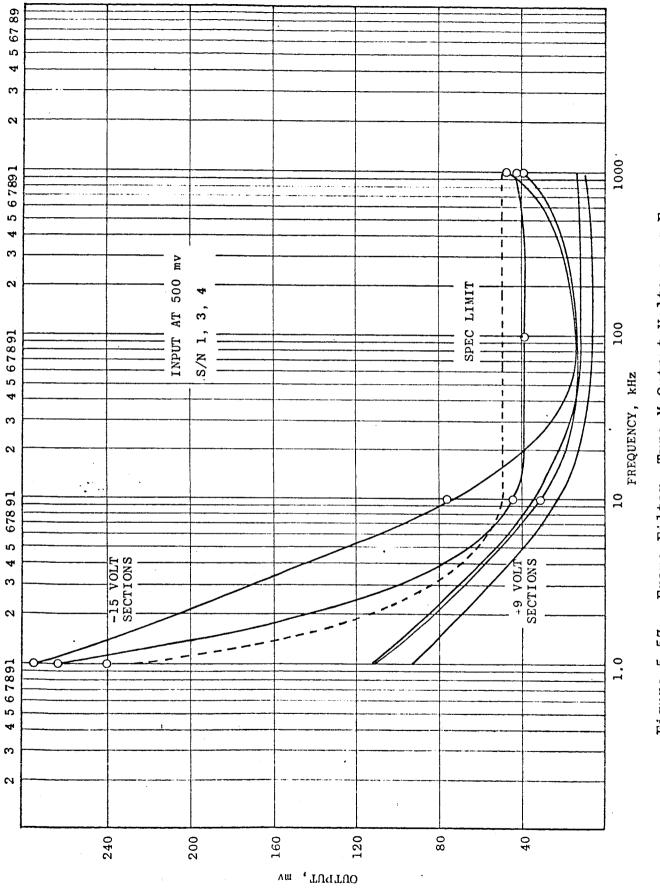

| 5-40   | Frame Filter, Type T Output Voltage vs Frequency<br>Input at 500 mv, S/N 1, 2, 5              | 5-77  |

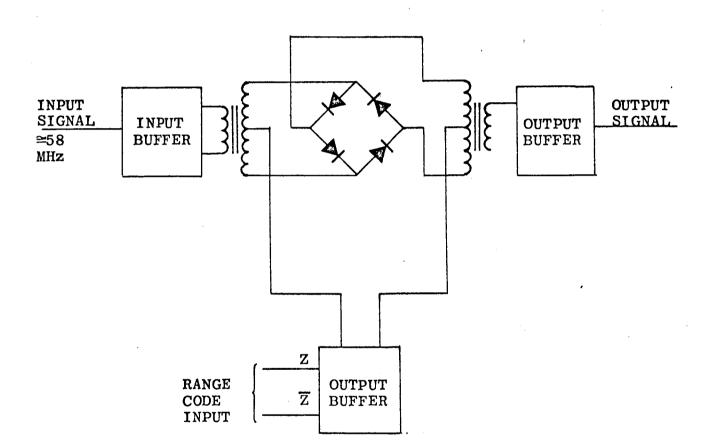

| 5-41   | Balanced Phase Demodulator Circuit                                                            | 5-78  |

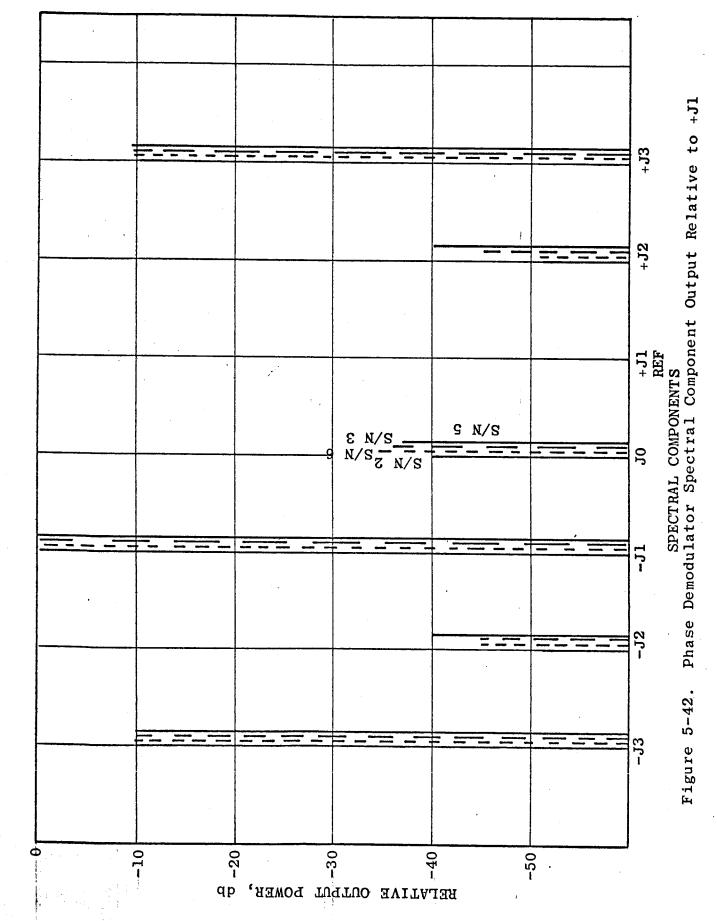

| 5-42   | Phase Demodulator Spectral Component Output Relative to +Jl                                   | 5-79  |

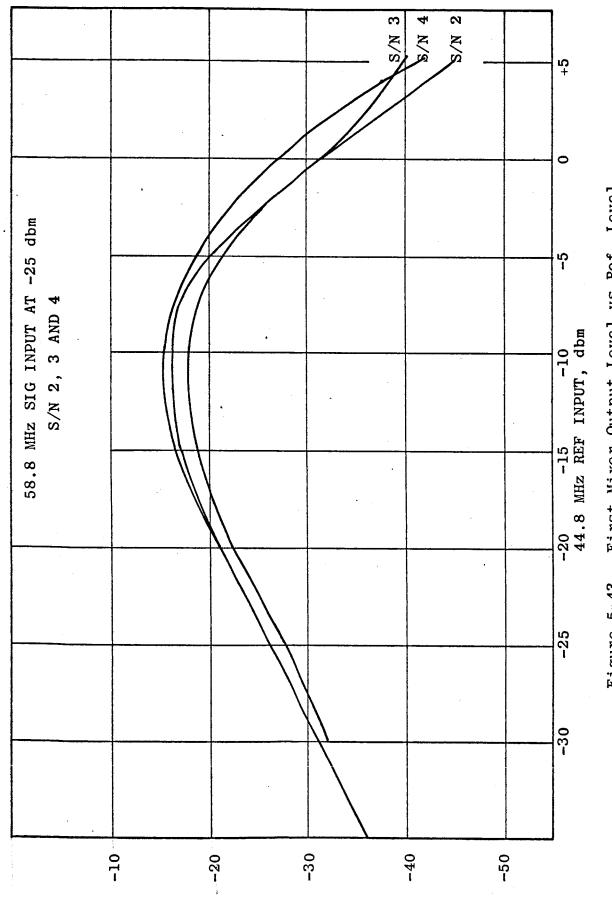

| 5-43   | First Mixer Output Level vs Ref. Level                                                        | 5-81  |

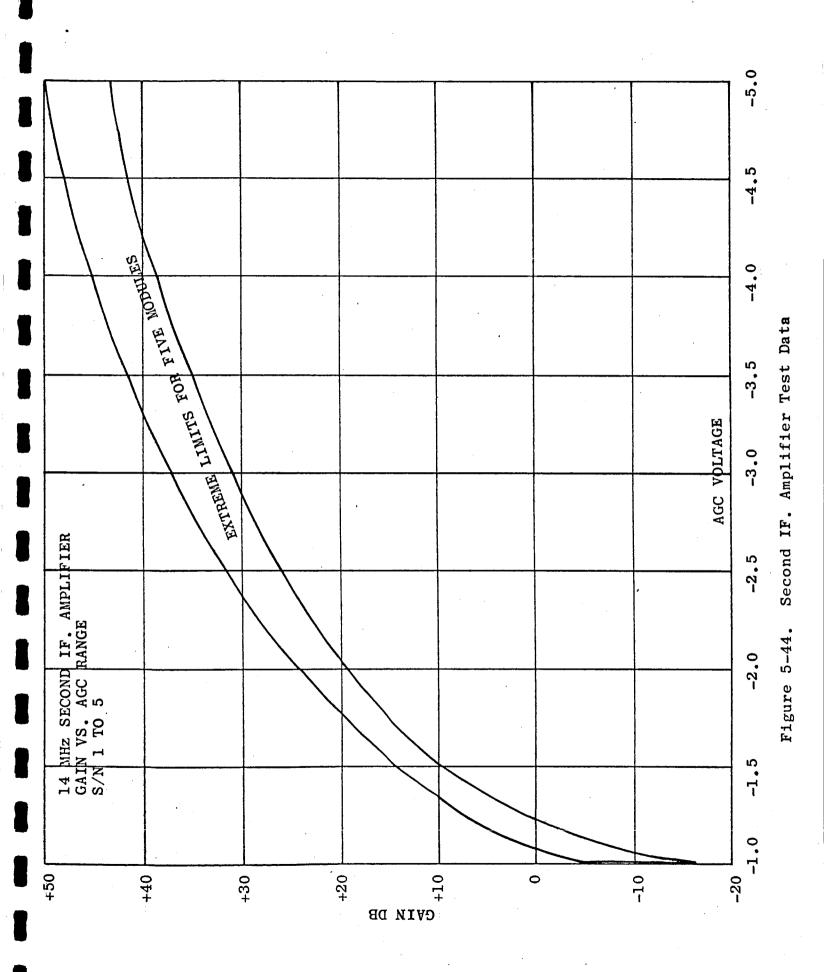

| 5-44   | Second IF. Amplifier Test Data                                                                | 5-83  |

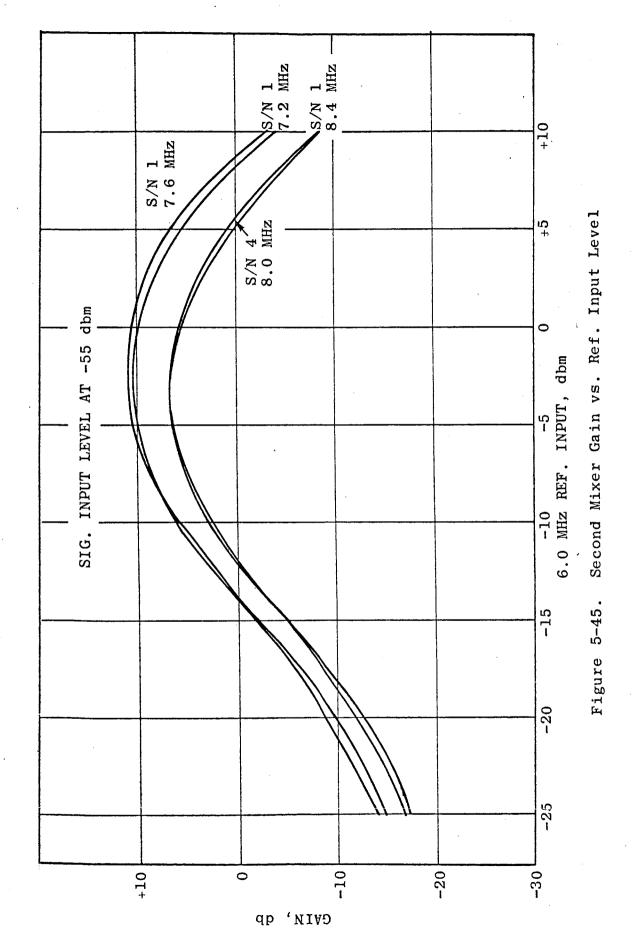

| 5-45   | Second Mixer Gain vs Ref. Input Level                                                         | 5-85  |

| 5-46   | Predetection Channel Filter                                                                   | 5-84  |

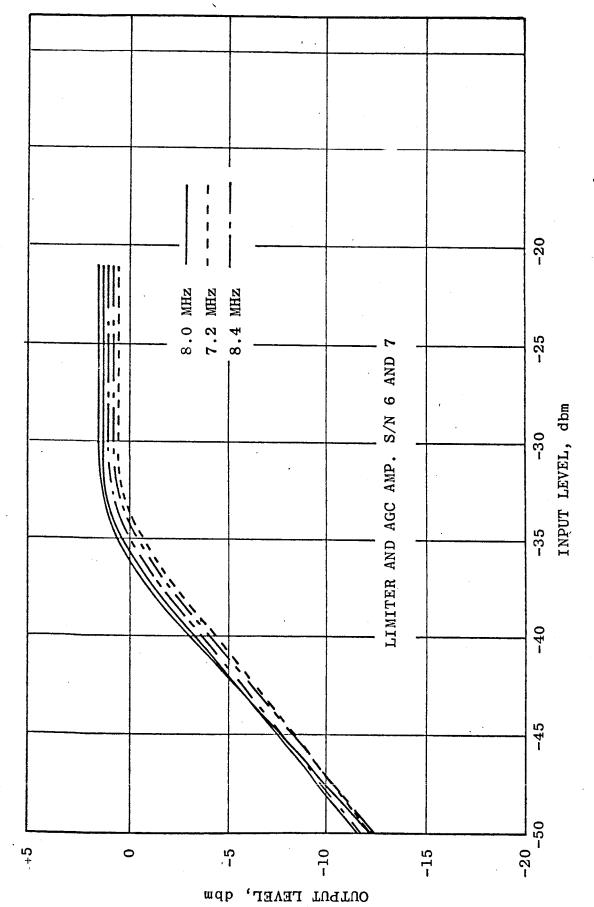

| 5-47   | Limiter Gain                                                                                  | 5-87  |

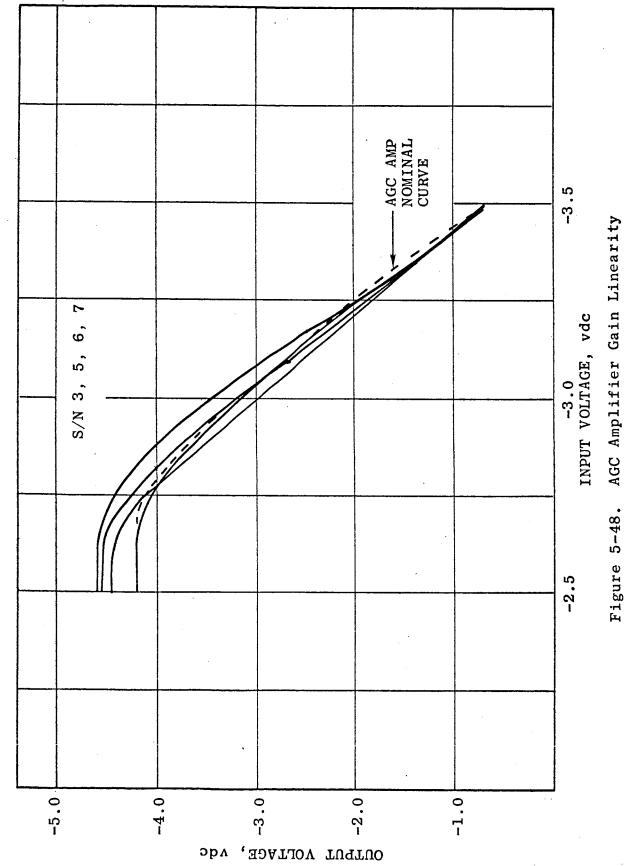

| 5-48   | AGC Amplifier Gain Linearity                                                                  | 5-89  |

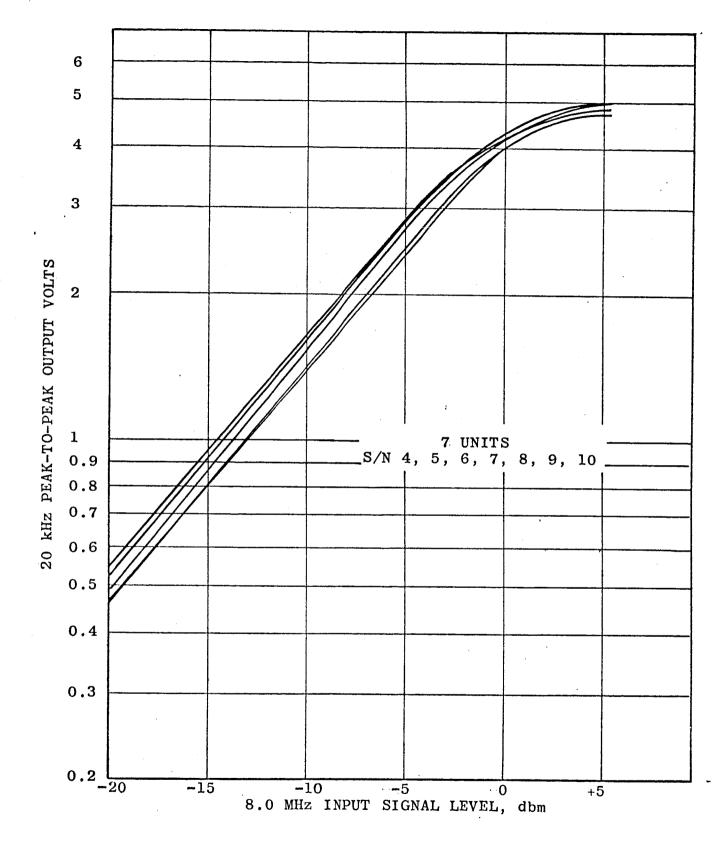

| 5-49   | 8 MHz Balanced Detector 20 kHz Gain and Linearity<br>Curves                                   | 5-91  |

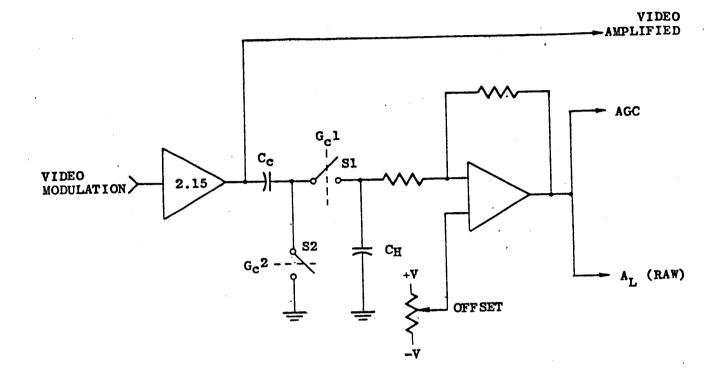

| 5-50   | Amplifier and A <sub>L</sub> Demodulator                                                      | 5-92  |

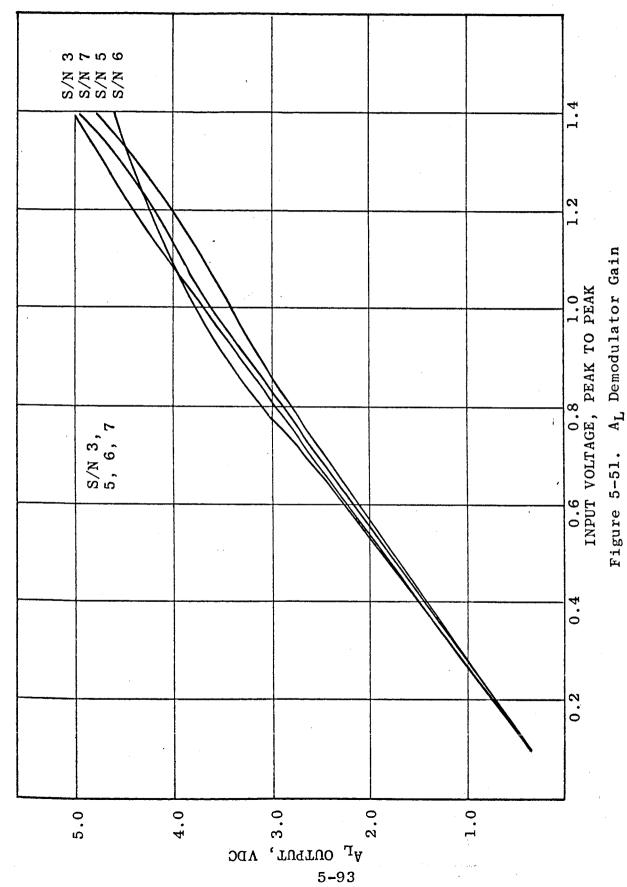

| 5-51   | A, Demodulator Gain                                                                           | 5-93  |

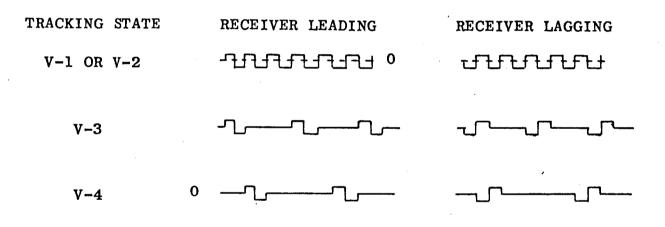

| 5-52   | Carrier Loop Filter Input Signal                                                              | 5-94  |

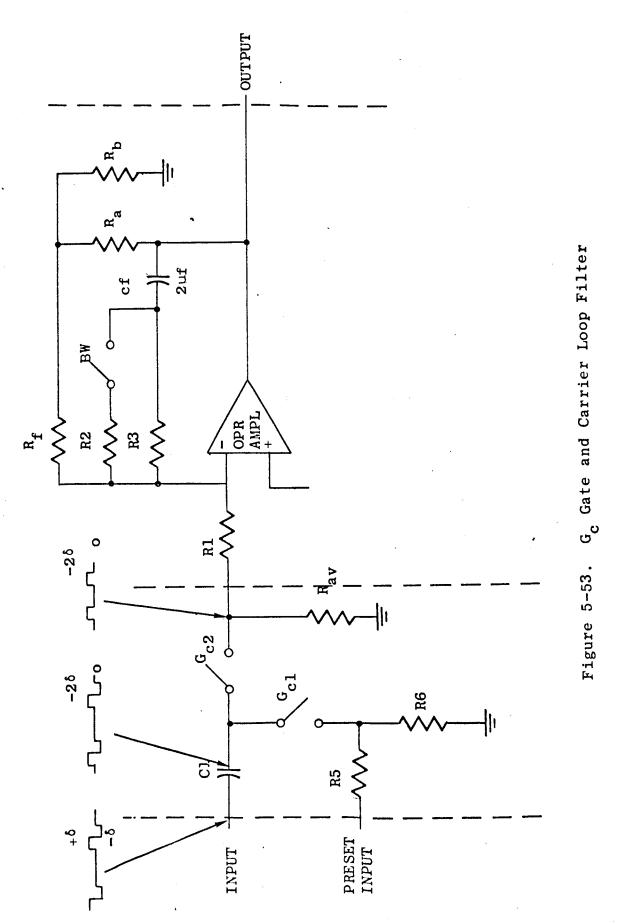

| 5-53   | G Gate and Carrier Loop Filter                                                                | 5-96  |

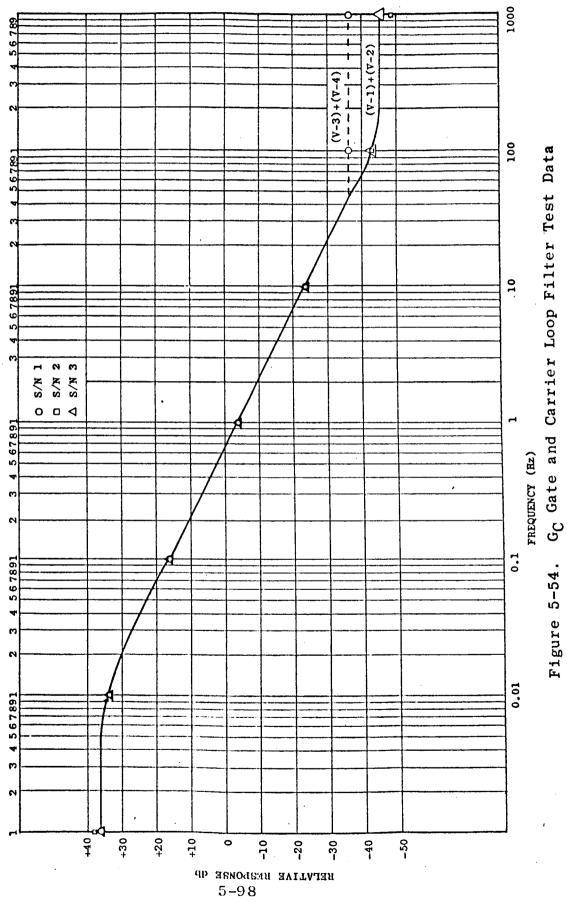

| 5-54   | $G_{C}$ Gate and Carrier Loop Filter Test Date                                                | 5-98  |

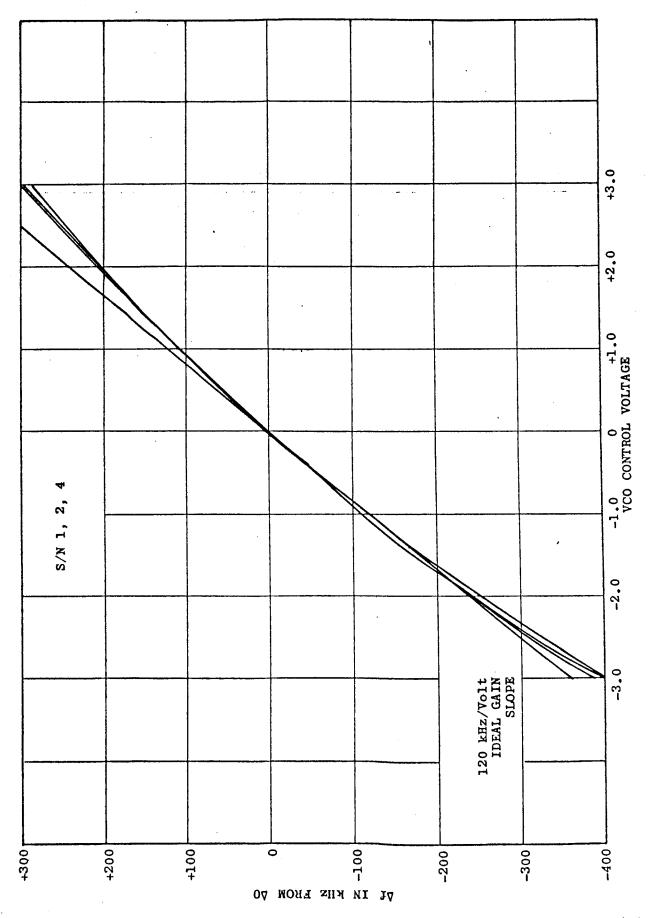

| 5-55   | 6.0 MHz VCO Gain                                                                              | 5-100 |

.

V

## LIST OF ILLUSTRATIONS (Cont)

| Figure | Title                                                                                                                               | Page  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5-56   | 6 MHz VCO Test Data                                                                                                                 | 5-101 |

| 5-57   | Frame Filter, Type M Output Voltage vs Frequency                                                                                    | 5-103 |

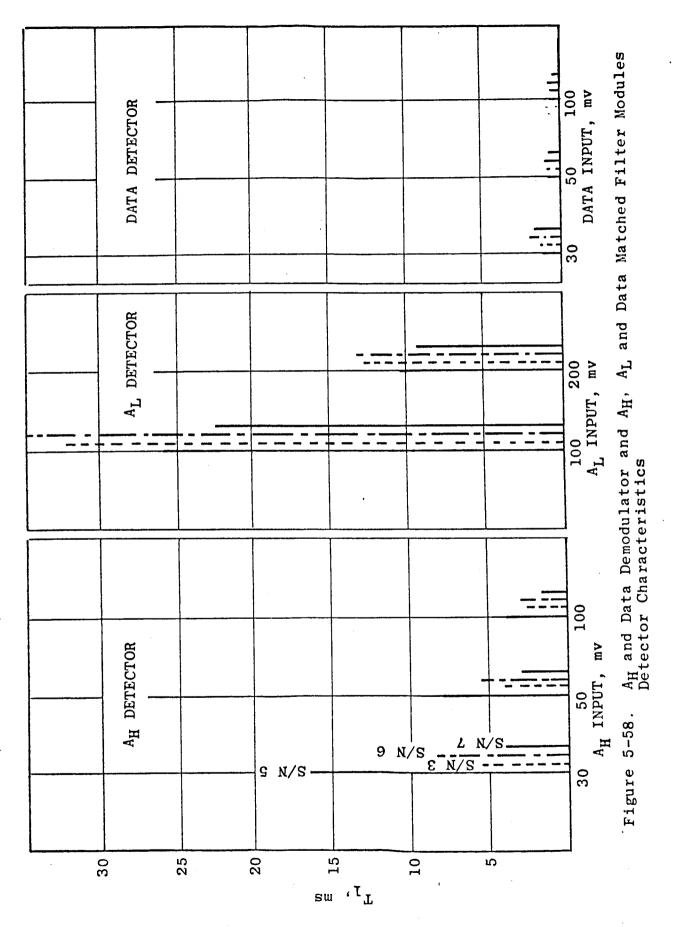

| 5-58   | A <sub>H</sub> and Data Demodulator and A <sub>H</sub> , A <sub>L</sub> and Data Matched<br>Filter Modules Detector Characteristics | 5-104 |

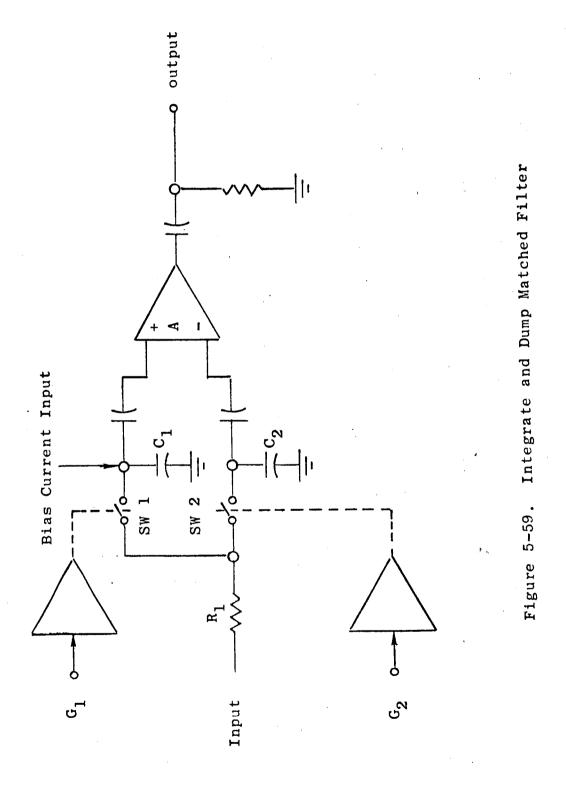

| 5-59   | Integrate and Dump Matched Filter                                                                                                   | 5-106 |

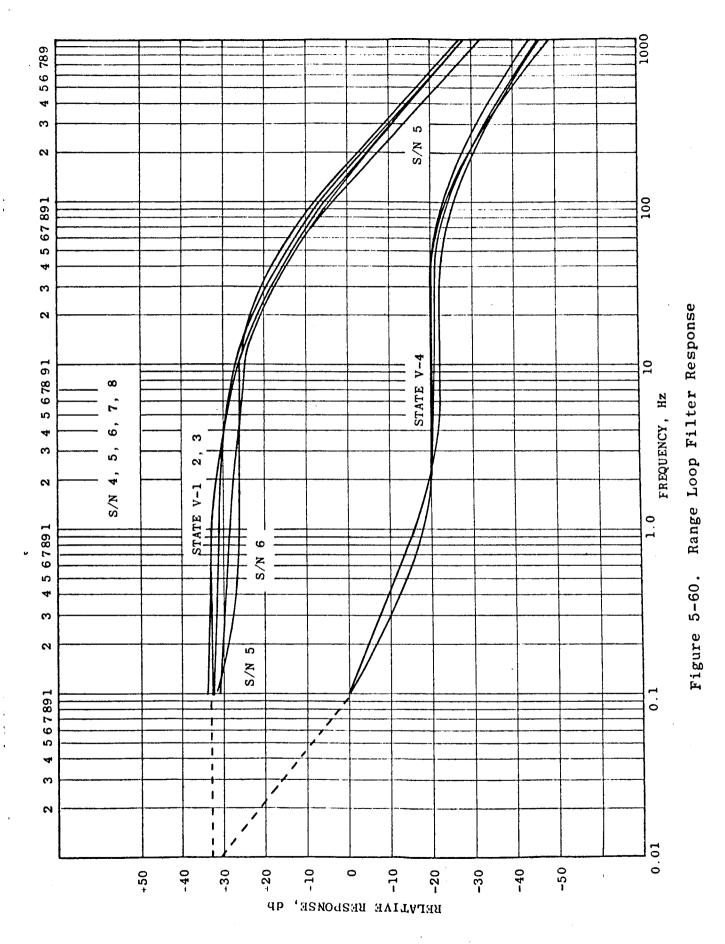

| 5-60   | Range Loop Filter Response                                                                                                          | 5-108 |

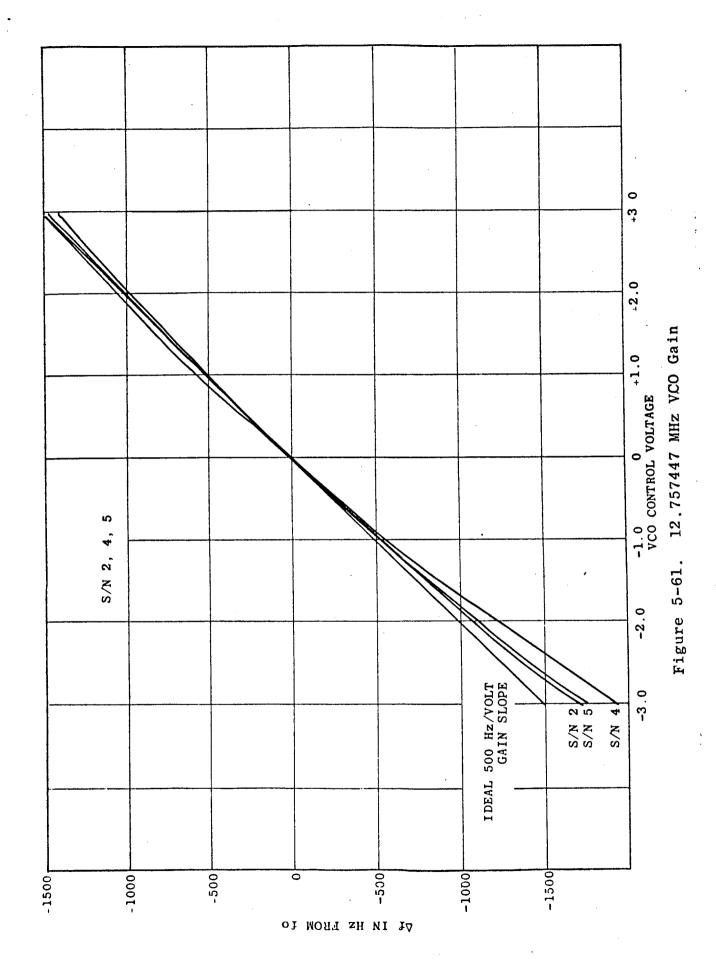

| 5-61   | 12.757447 MHz VCO Gain                                                                                                              | 5-110 |

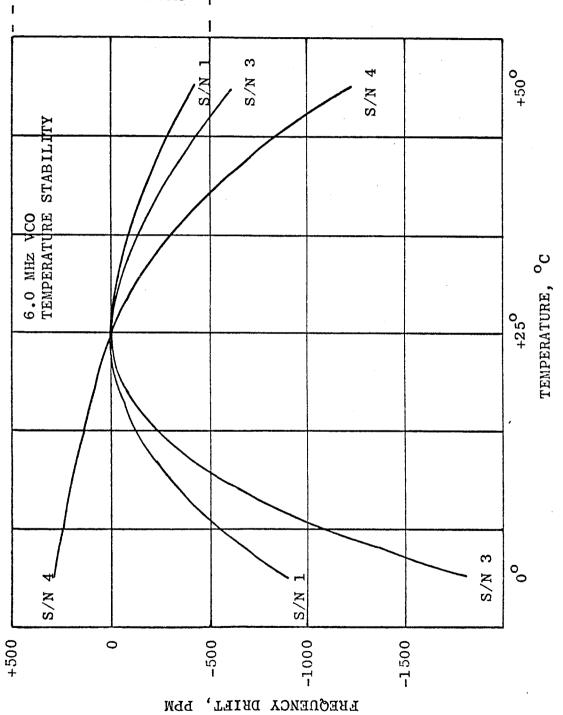

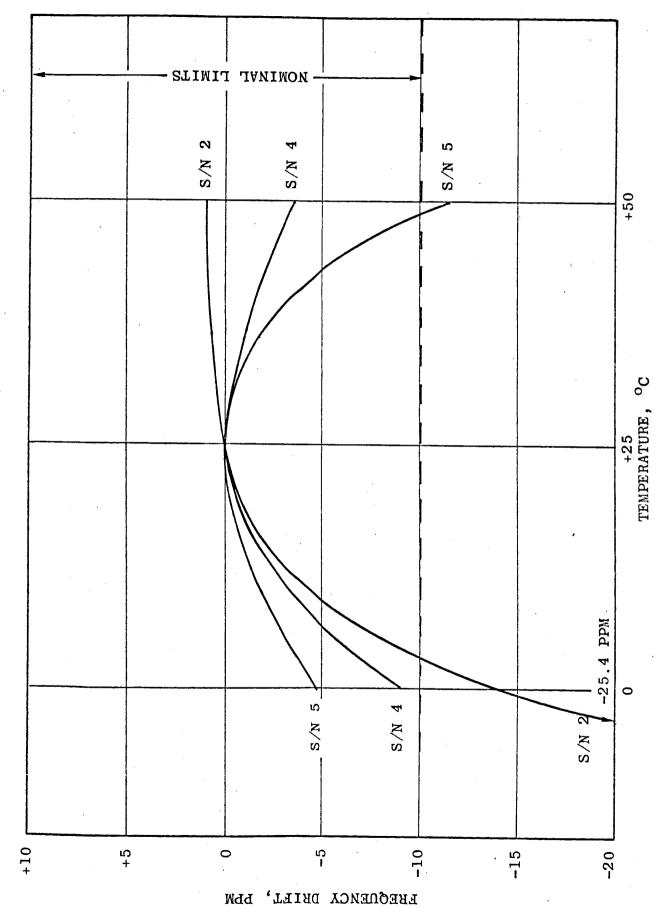

| 5-62   | 12-757447 MHz VCO Temperature Stability                                                                                             | 5-111 |

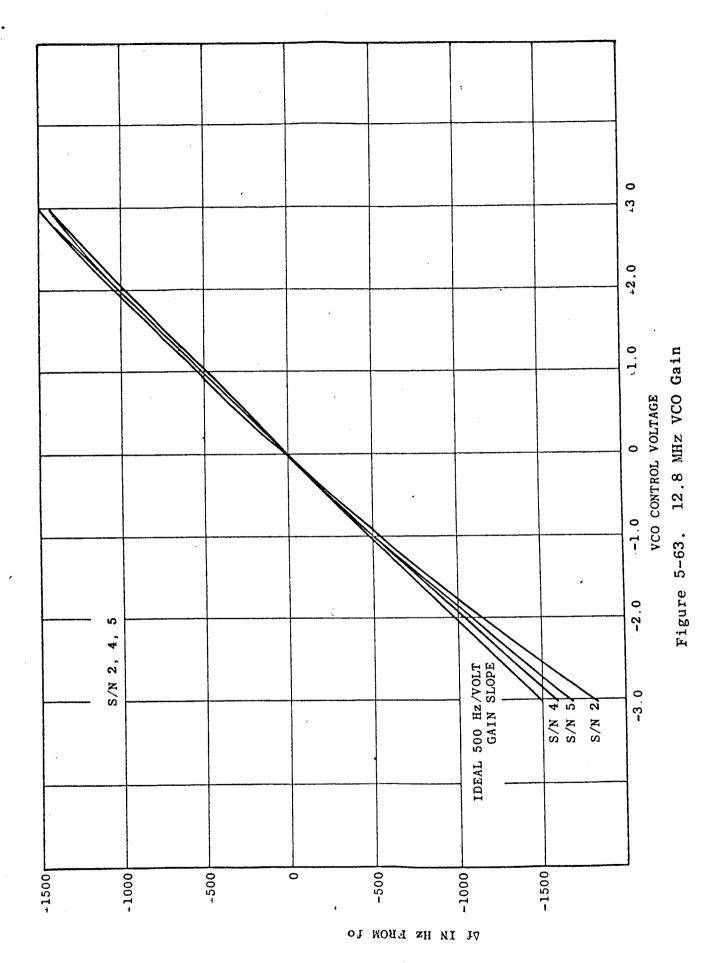

| 5-63   | 12.8 MHz VCO Gain                                                                                                                   | 5-114 |

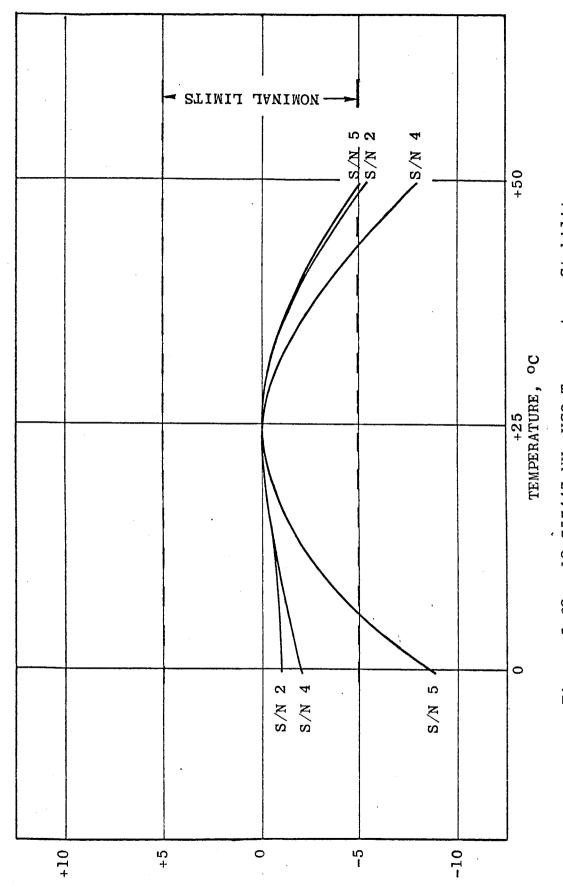

| 5-64   | 12.8 MHz VCO Temperature Stability                                                                                                  | 5-115 |

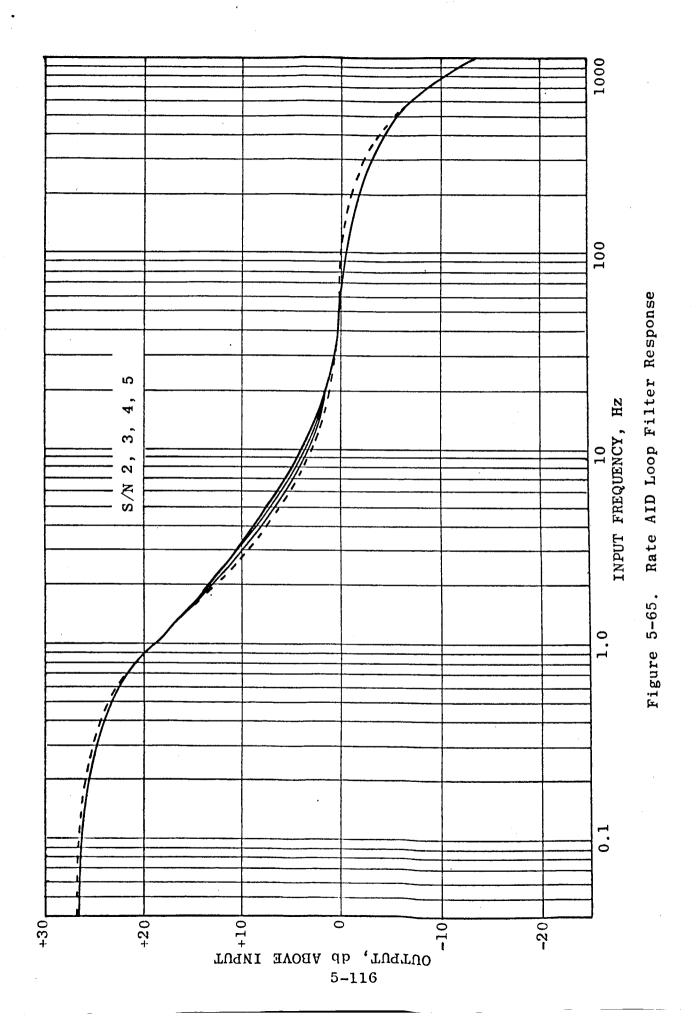

| 5-65   | Rate AID Loop Filter Response                                                                                                       | 5-116 |

| 5-66   | Carrier Loop Frequency Preset                                                                                                       | 5-118 |

| 5-67   | Frequency Comparison - Preset Discriminator                                                                                         | 5-120 |

| 5-68   | Frequency Comparison - Preset Discriminator                                                                                         | 5-121 |

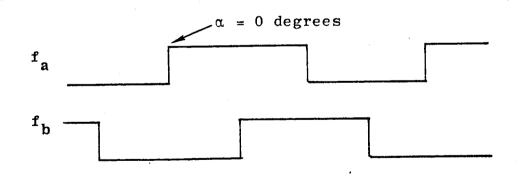

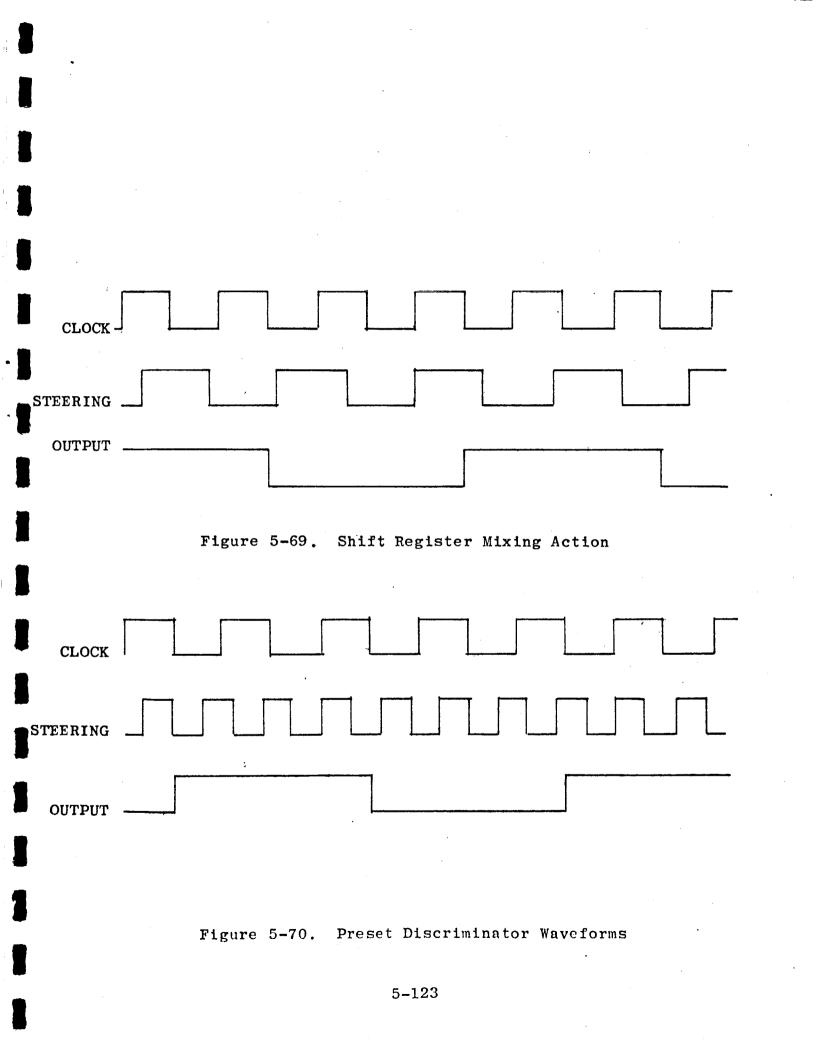

| 5-69   | Shift Register Mixing Action                                                                                                        | 5-123 |

| 5-70   | Preset Discriminator Waveforms                                                                                                      | 5-123 |

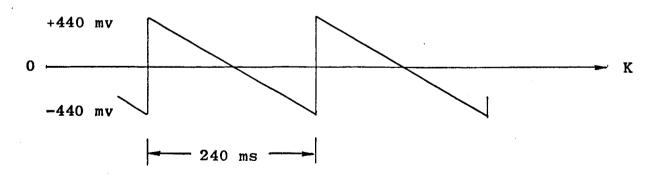

| 5-71   | H-Code Search Sweep Waveform                                                                                                        | 5-124 |

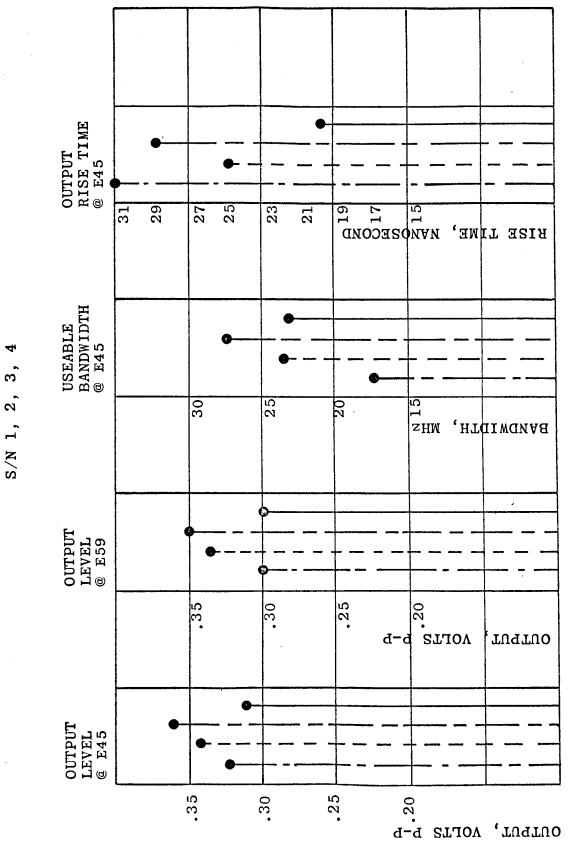

| 5-72   | Doppler Mixer Test Data                                                                                                             | 5-126 |

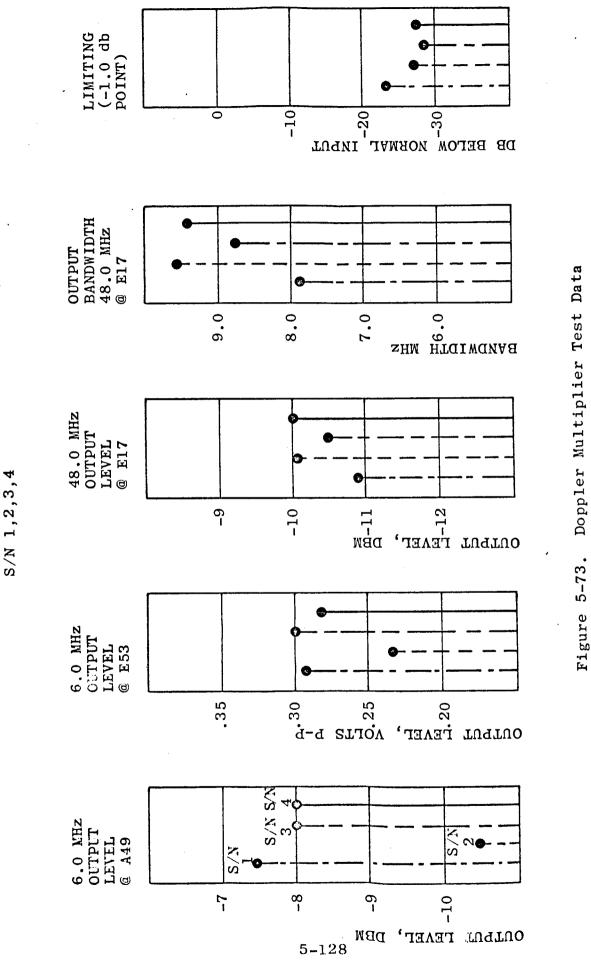

| 5-73   | Doppler Multiplier Test Data                                                                                                        | 5-128 |

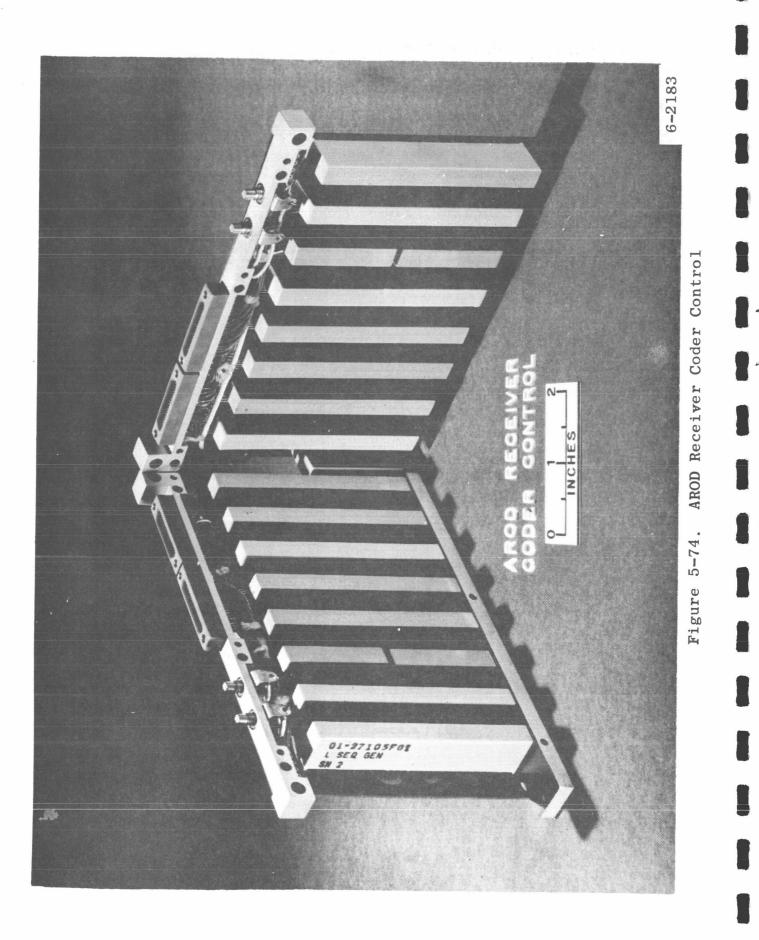

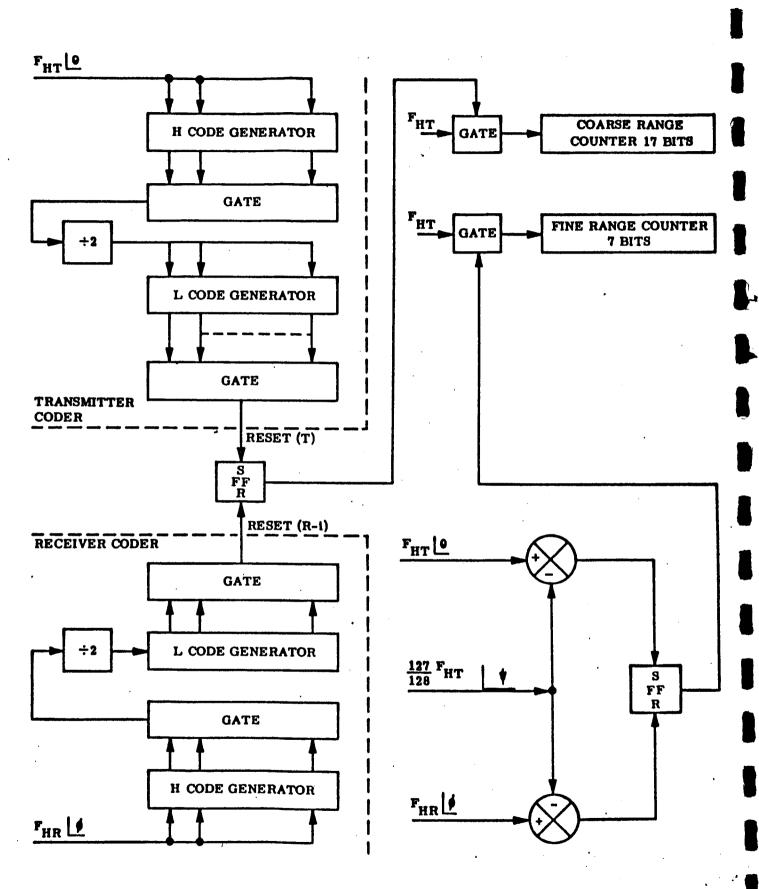

| 5-74   | AROD Receiver Coder Control                                                                                                         | 5-130 |

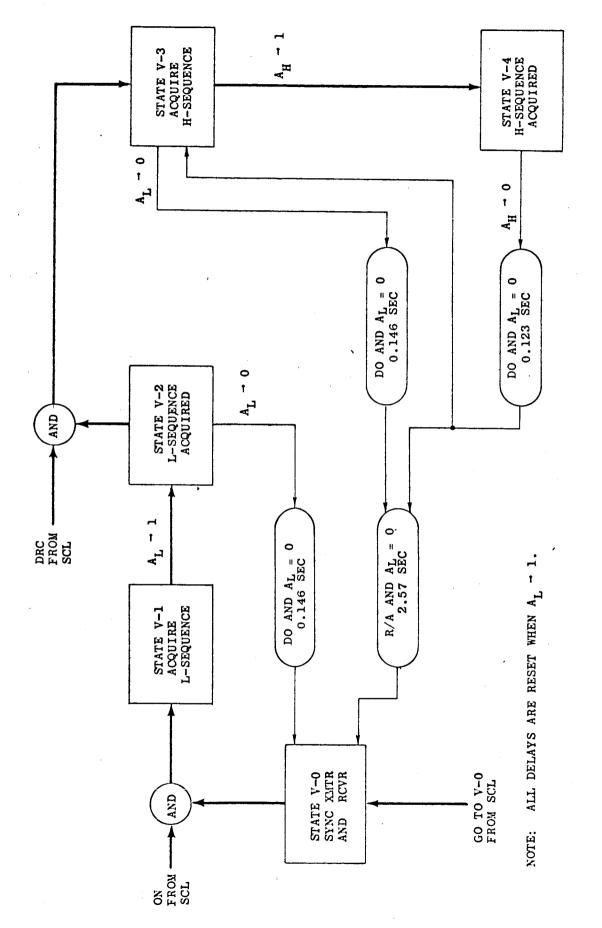

| 5-75   | Vehicle Code Control States (Program Sequence)                                                                                      | 5-133 |

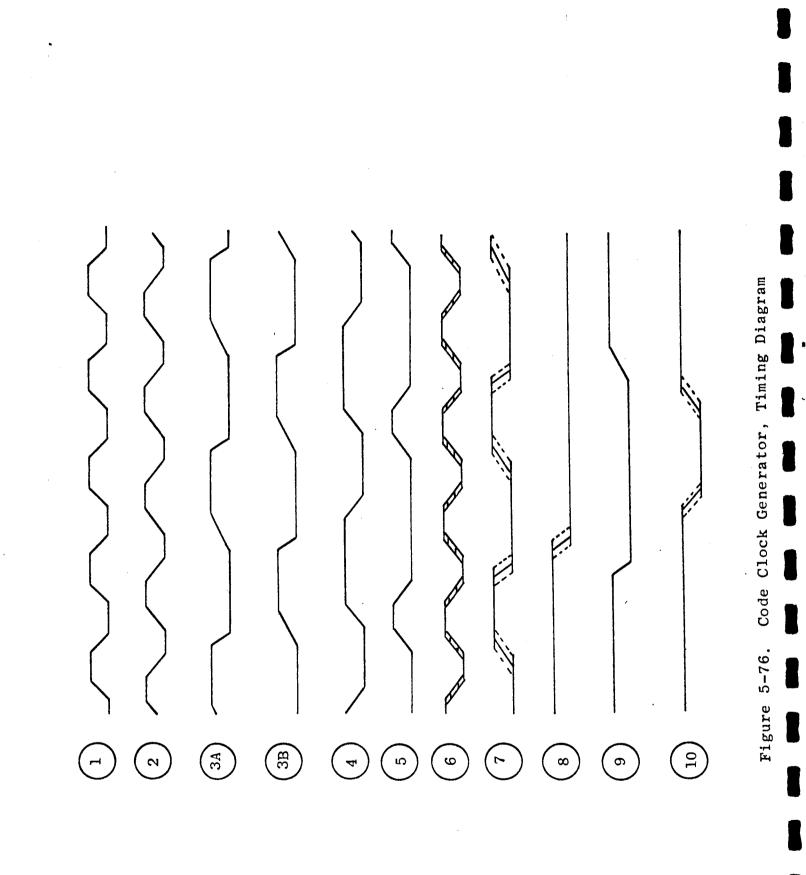

| 5-76   | Code Clock Generator, Timing Diagram                                                                                                | 5-136 |

| 5-77   | Timing Pulses                                                                                                                       | 5-139 |

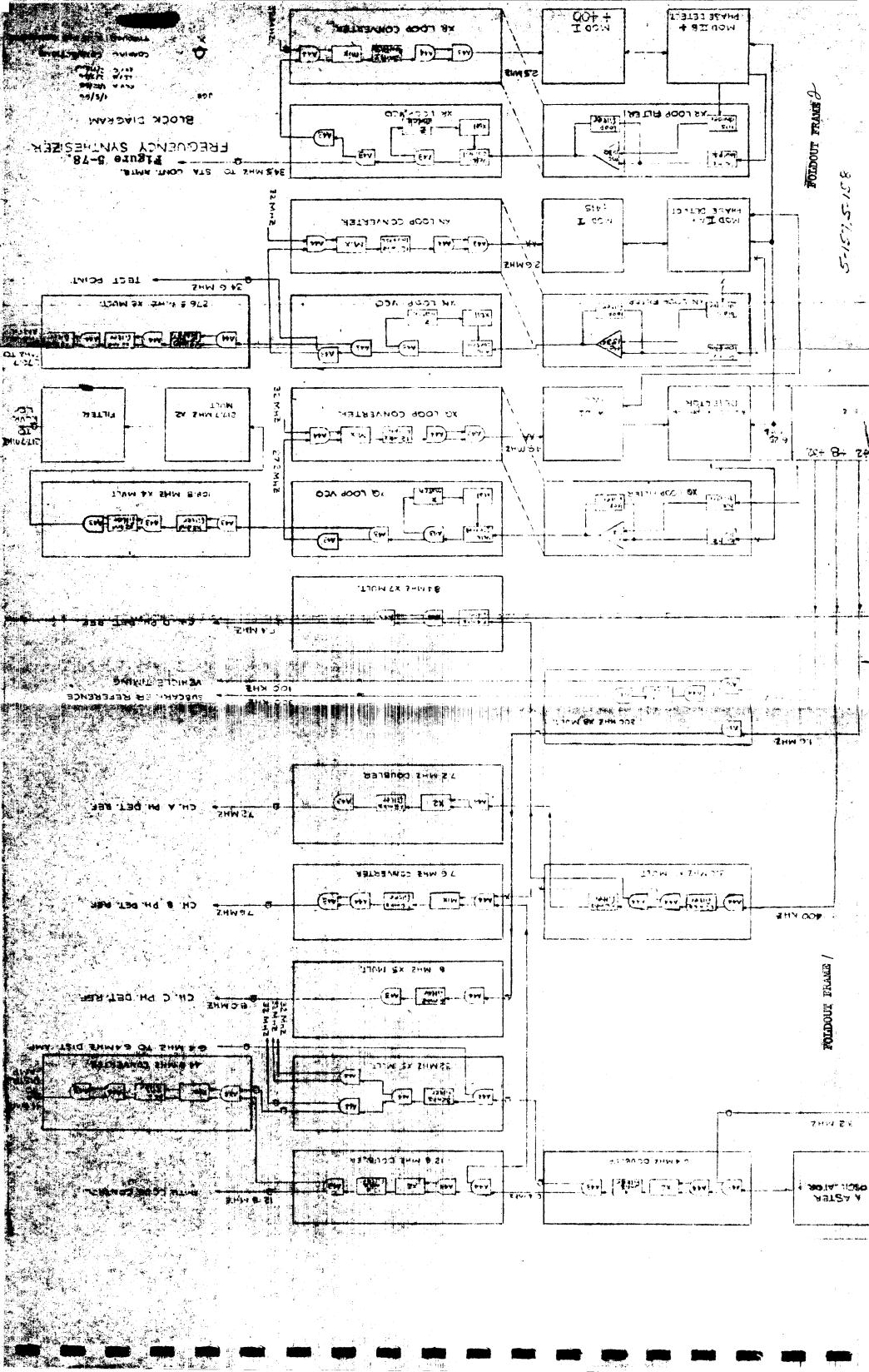

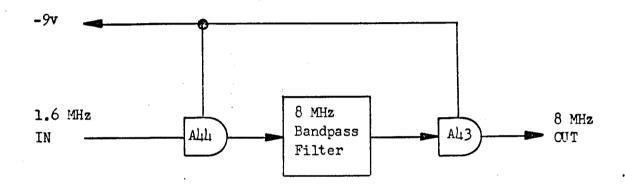

| 5-78   | Frequency Synthesizer, Block Diagram                                                                                                | 5-157 |

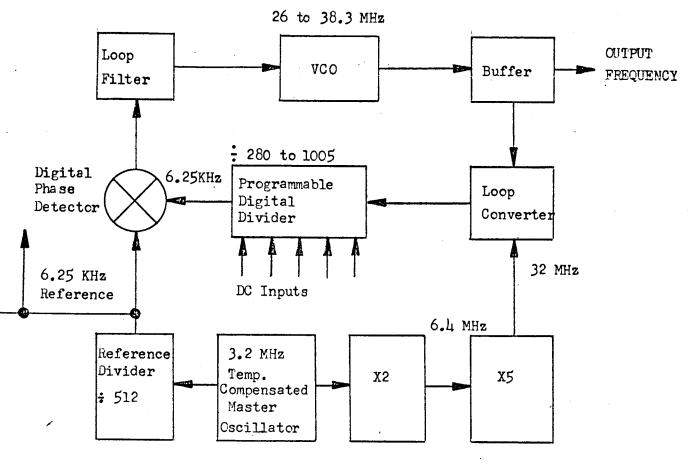

| 5-79   | Phase Locked Loop Synthesis Technique                                                                                               | 5-161 |

| 5-80   | 8 MHz X5 Multiplier Filter                                                                                                          |       |

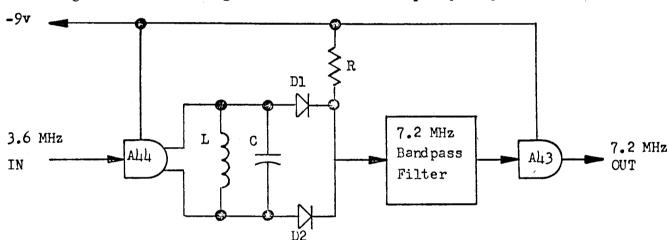

| 5-81   | 7.2 MHz Doppler                                                                                                                     |       |

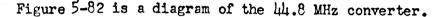

| 5-82   | 44.8 MHz Converter                                                                                                                  |       |

| 5-83   | 8 MHz X5 Multiplier                                                                                                                 |       |

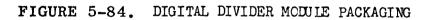

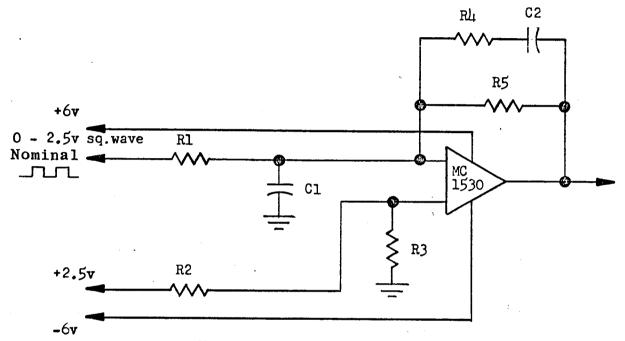

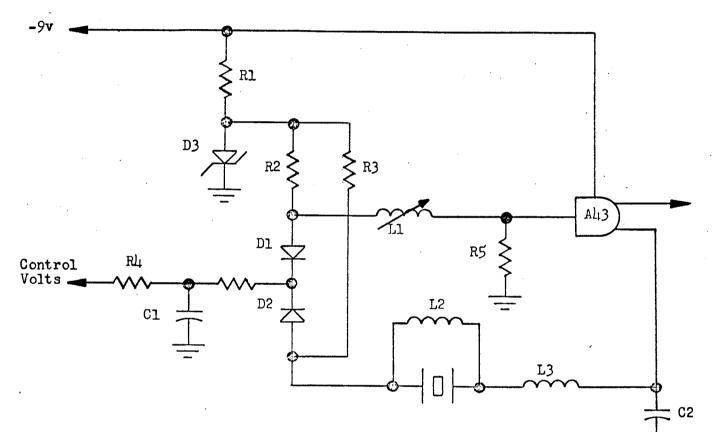

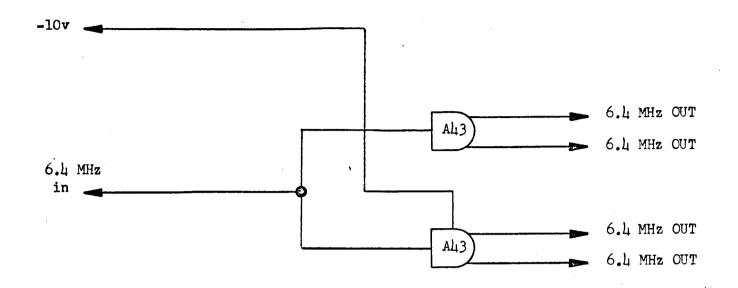

| 5-84   | Digital Divider Module Packaging                                                                                                    |       |

| 5-85   | Loop Filter                                                                                                                         | 5-171 |

vi

5

Ĩ

## LIST OF ILLUSTRATIONS (cont)

| Figure | Title                                                           | Page  |

|--------|-----------------------------------------------------------------|-------|

| 5-86   | vco                                                             | 5-172 |

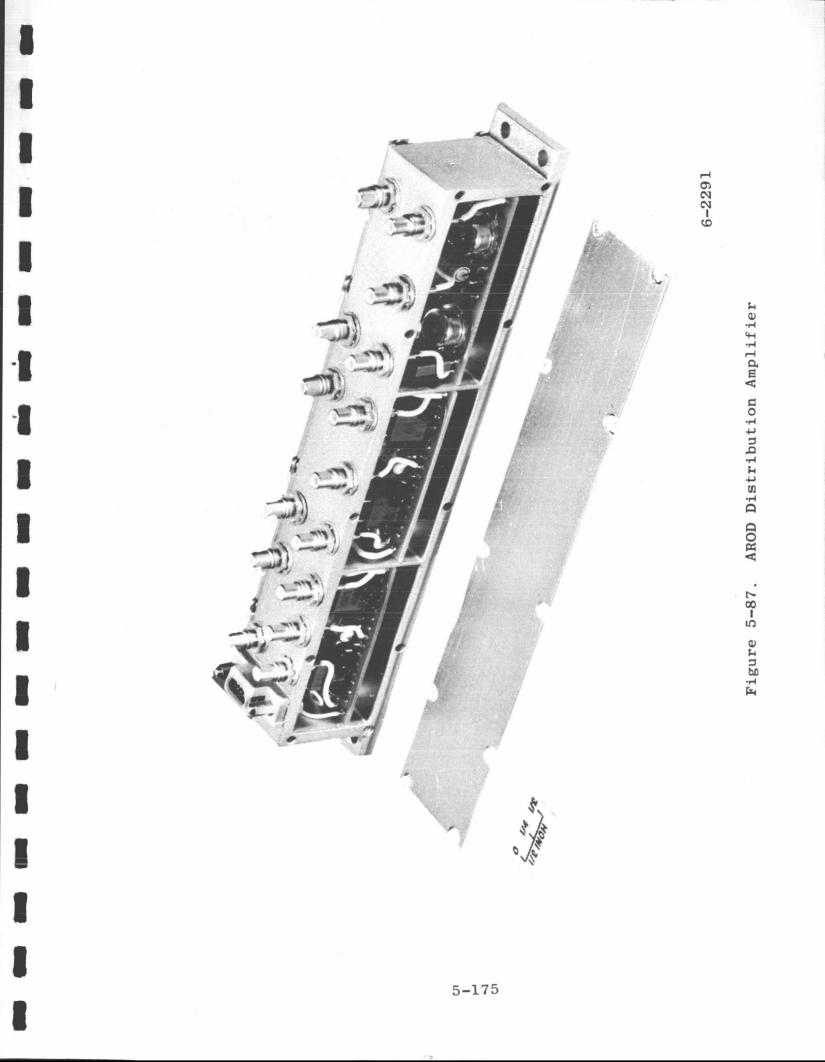

| 5-87   | AROD Distribution Amplifier.                                    | 5-175 |

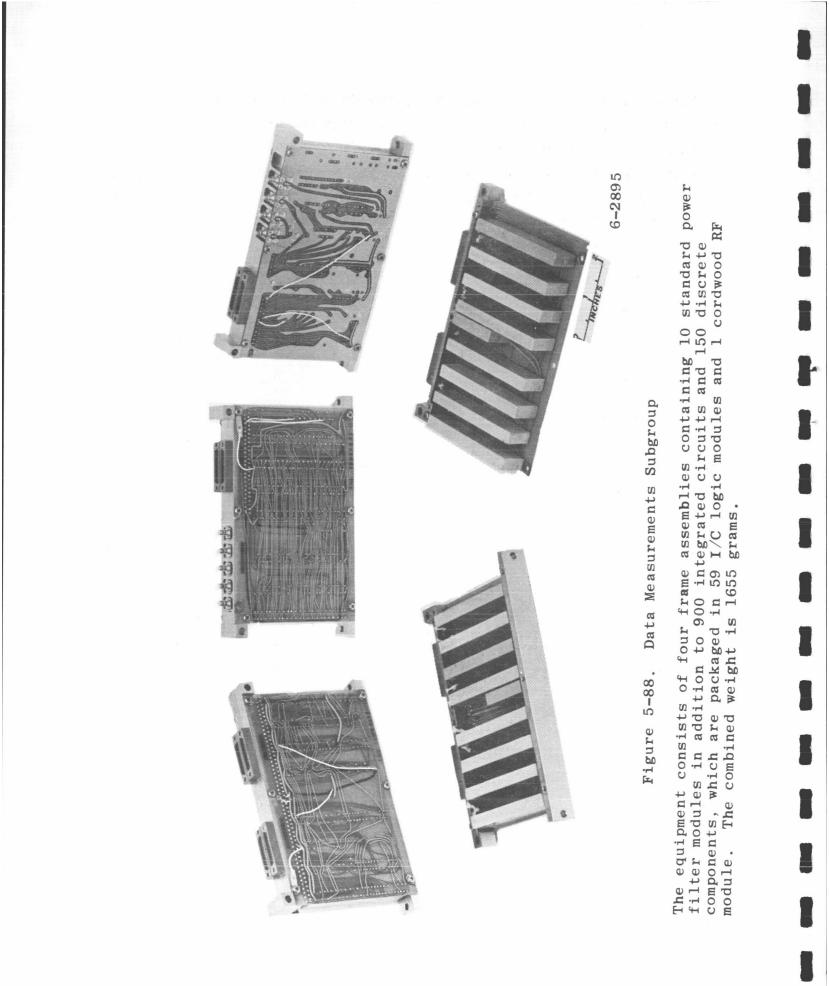

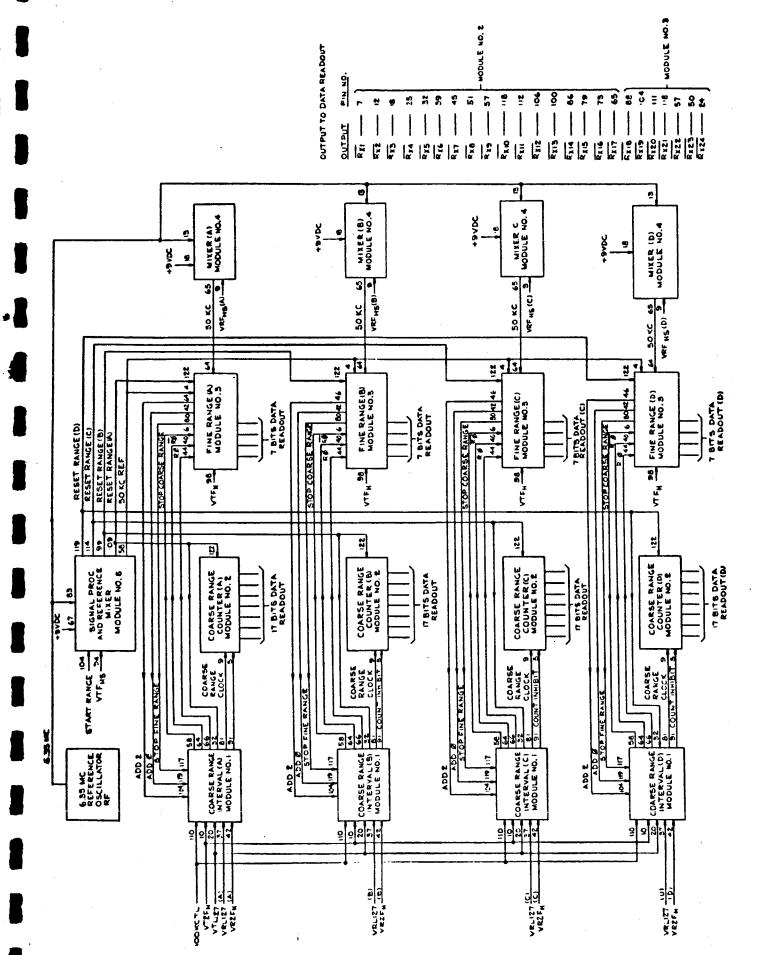

| 5-88   | Data Measurements Subgroup                                      | 5-182 |

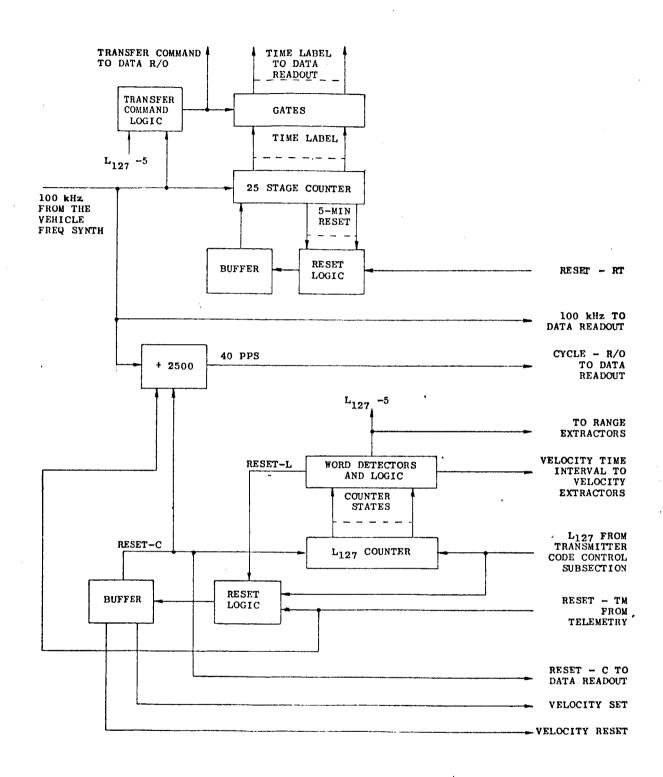

| 5-89   | Vehicle Timing Unit                                             | 5-184 |

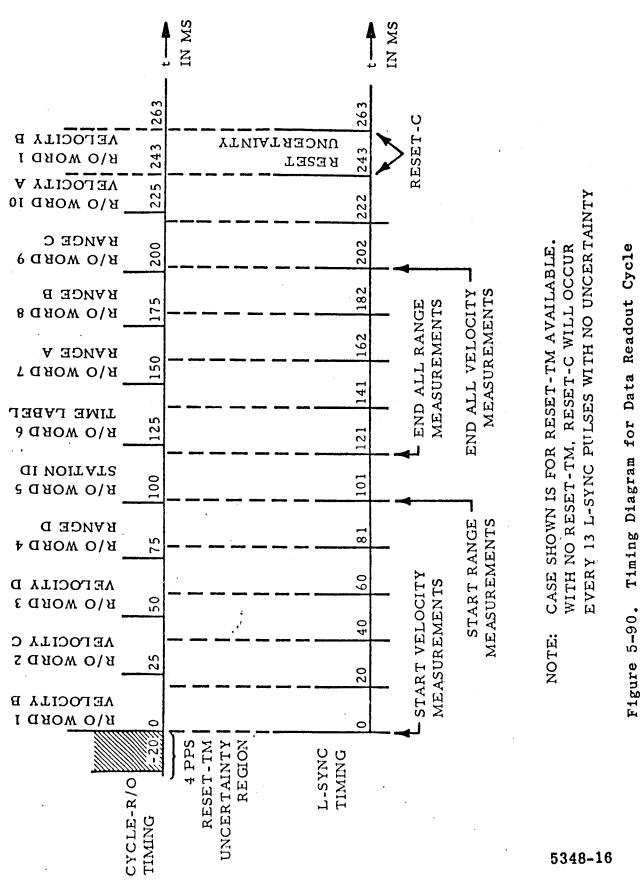

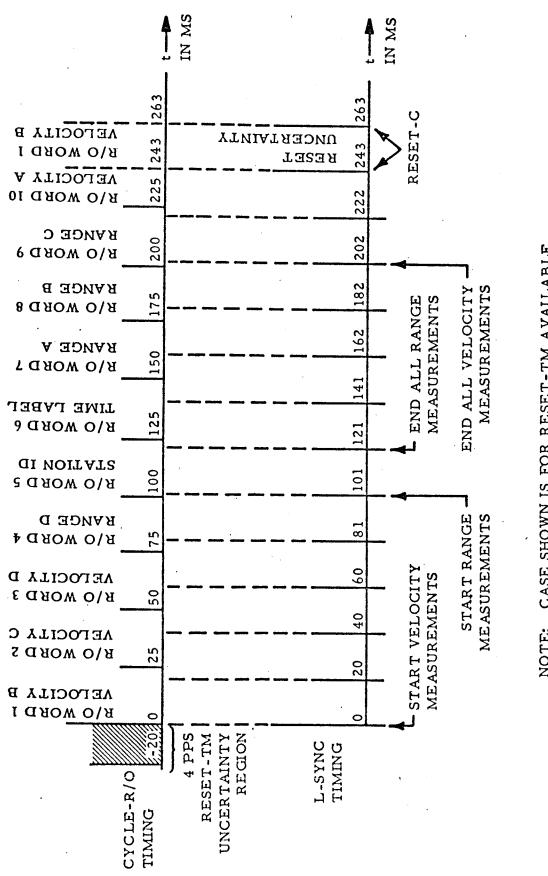

| 5-90   | Timing Diagram for Data Readout Cycle                           | 5-186 |

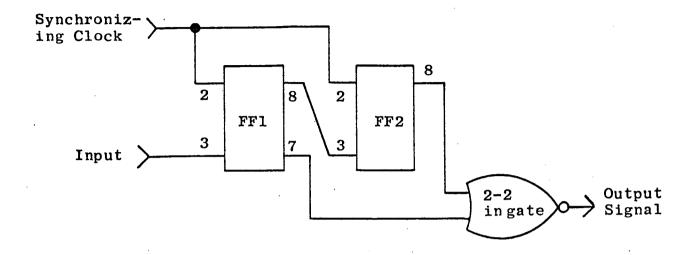

| 5-91   | Synchronous Monostable Multivibrator                            | 5-188 |

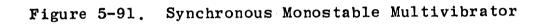

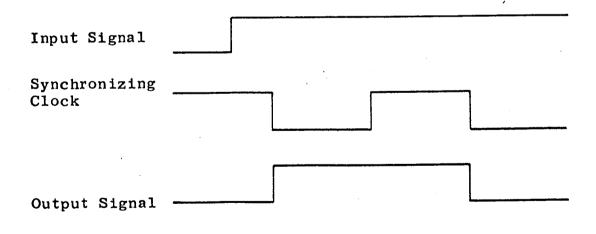

| 5-92   | Timing Diagram for the Synchronous Monostable<br>Multivibrator  | 5-188 |

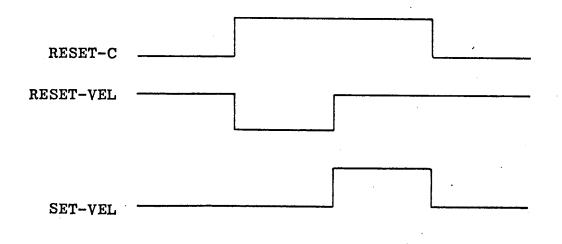

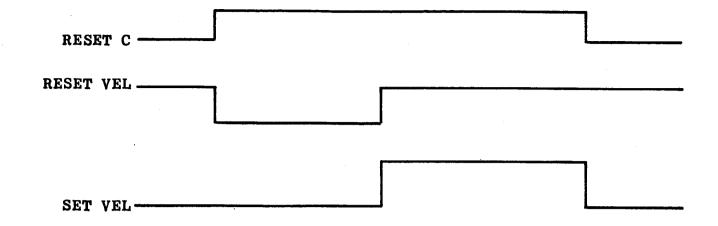

| 5-93   | Timing Diagram of the Velocity Preset Signals                   | 5-191 |

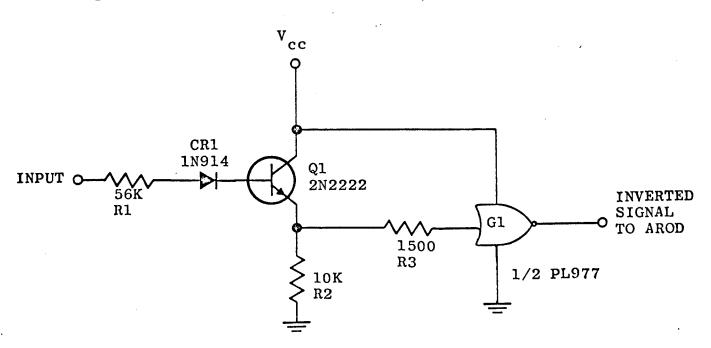

| 5-94   | Interface Circuit for Telemetry to AROD Interfacing             | 5-192 |

| 5-95   | Data Readout Unit - Block Diagram                               | 5-196 |

| 5-96   | Timing Diagram for Data Readout Cycle                           | 5-203 |

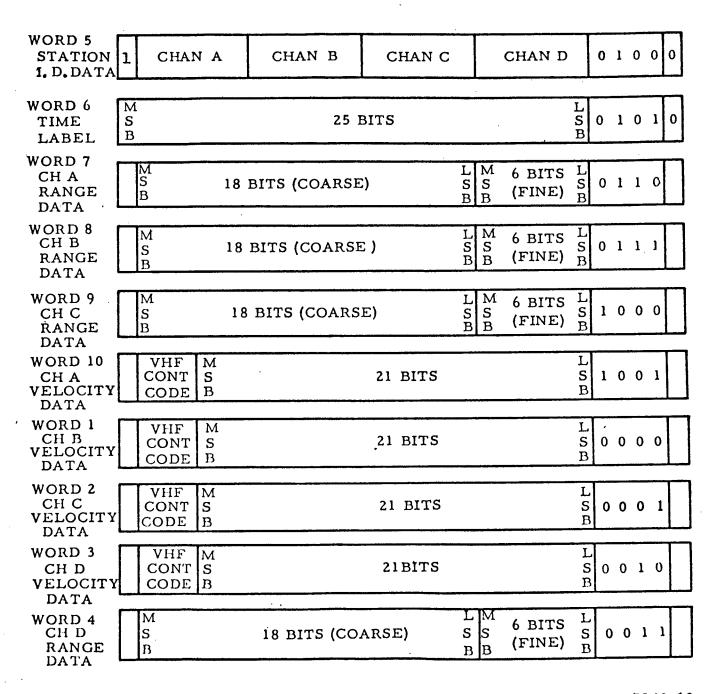

| 5-97   | Word Order and Format                                           | 5-204 |

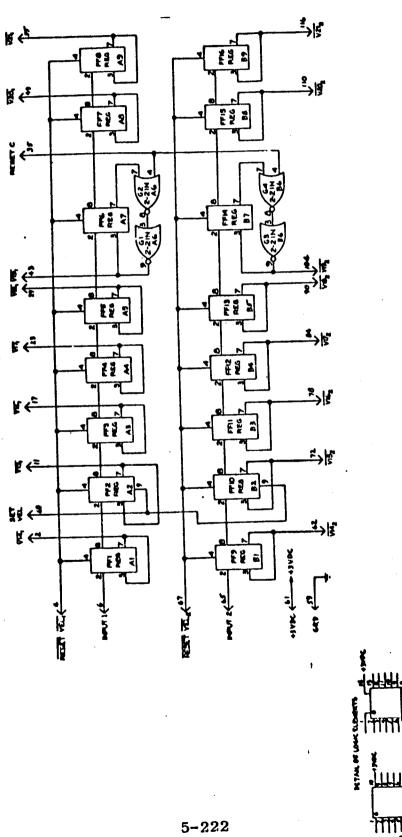

| 5-98   | Timing Diagram for the Generation of the Gated<br>Clock Signals | 5-208 |

| 5-99   | +5.6 VDC Power Source                                           | 5-214 |

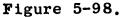

| 5-100  | Velocity Extraction Unit, Block Diagram                         | 5-220 |

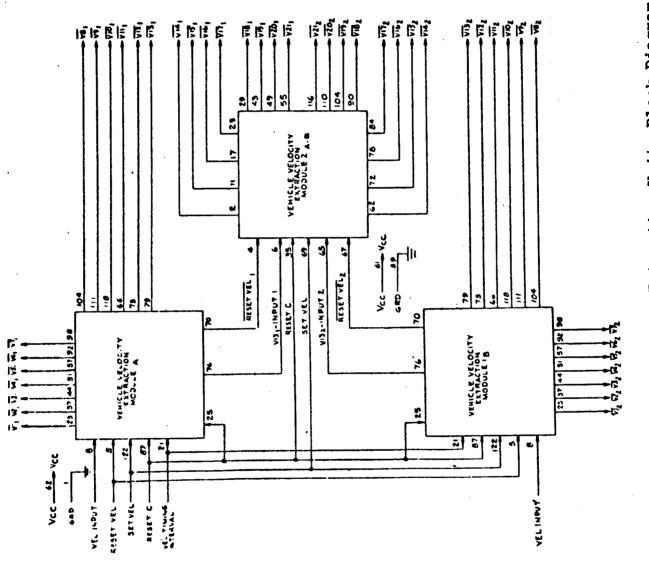

| 5-101  | Vehicle Velocity Extraction Module 1, Logic Diagram             | 5-221 |

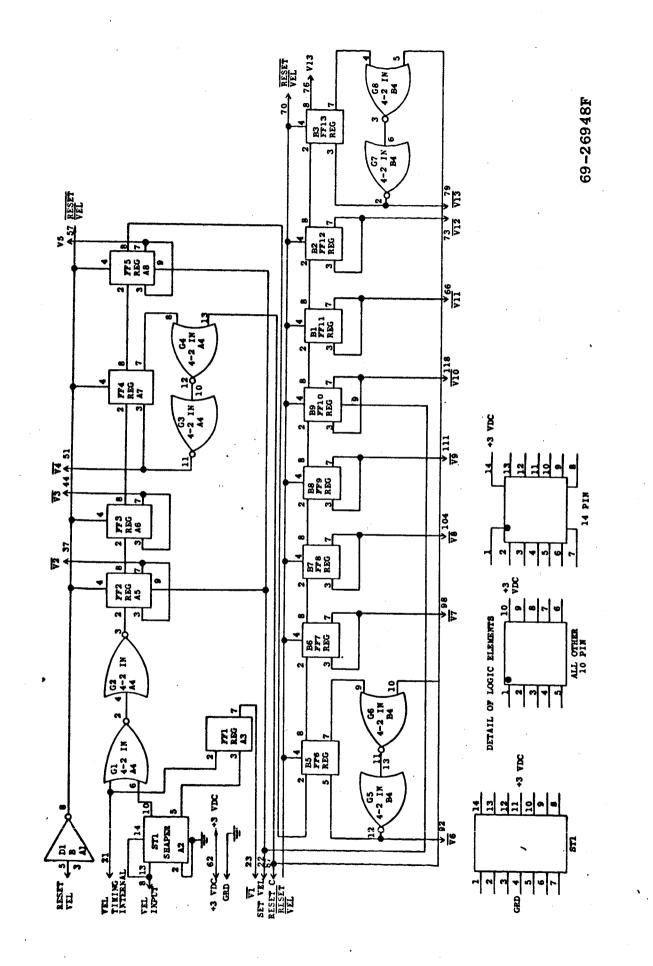

| 5-102  | Vehicle Velocity Extraction, Module 2                           | 5-222 |

| 5-103  | Timing Signals                                                  | 5-223 |

| 5-104  | Functional Block Diagram of the Range Extraction<br>Unit        | 5-226 |

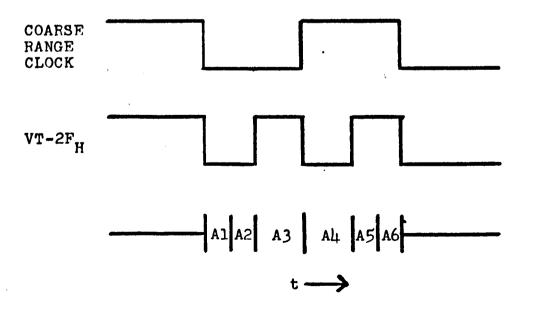

| 5-105  | VT-2F <sub>H</sub> Signal Timing                                | 5-228 |

| 5-106  | Range Extraction Unit, Block Diagram                            | 5-233 |

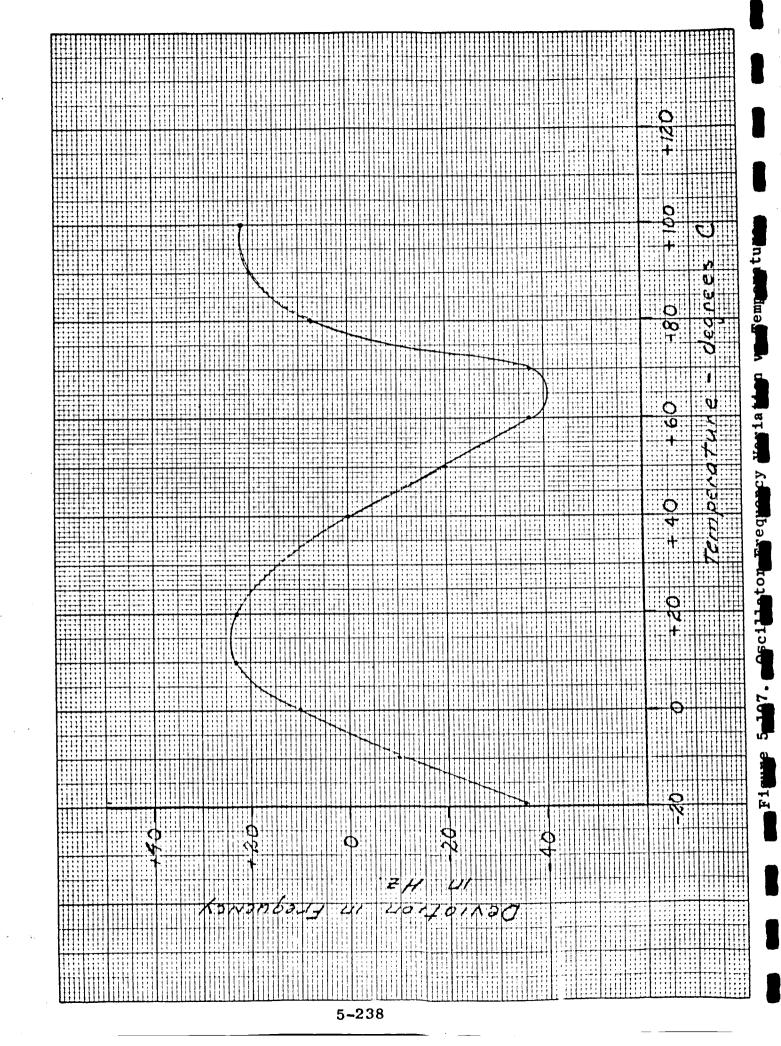

| 5-107  | Oscillator Frequency Variation vs Temperature                   | 5-238 |

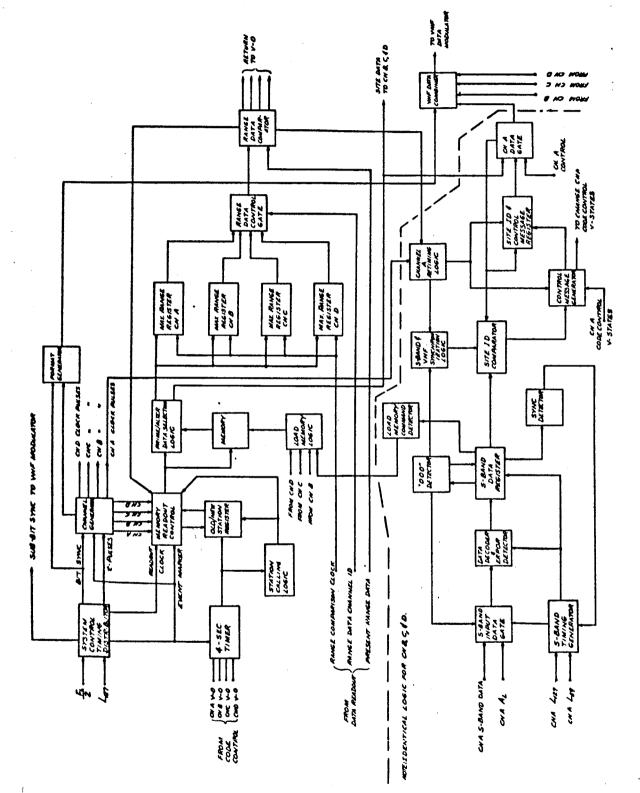

| 5-108  | AROD System Control Logic Block Diagram                         | 5-241 |

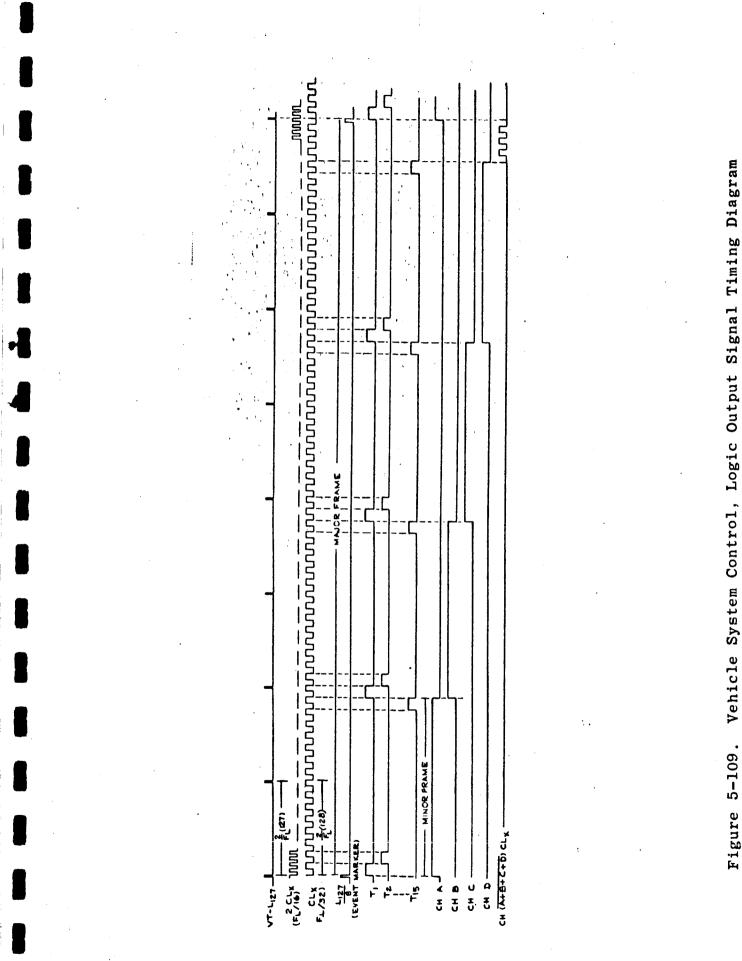

| 5-109  | Vehicle System Control, Logic Output Signal Timing<br>Diagram   | 5-243 |

| 5-110  | VHF Data Format                                                 | 5-244 |

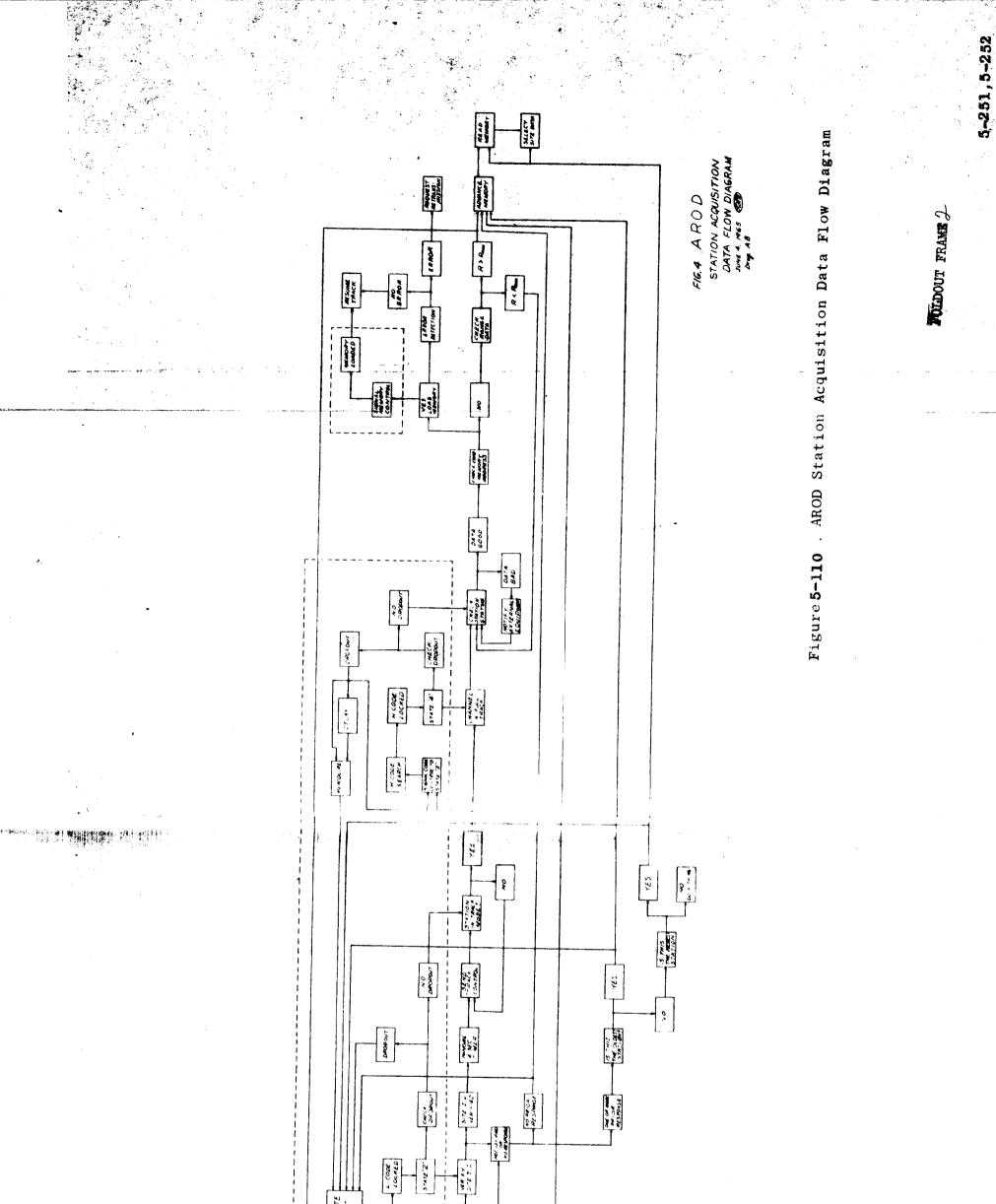

| 5-110A | AROD Station Acquisition Data Flow Diagram                      | 5-251 |

| 5-111  | Load Memory Address                                             | 5-267 |

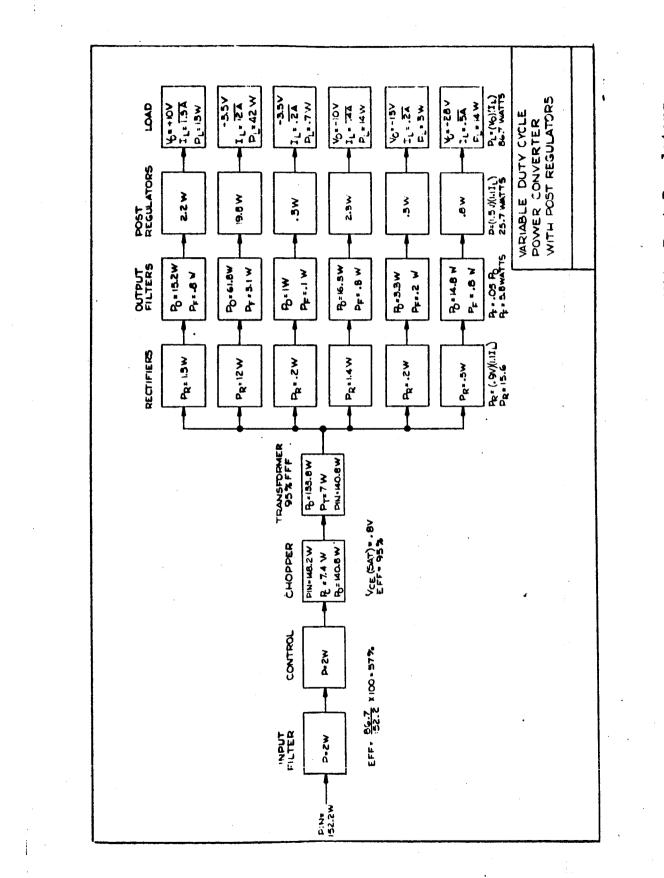

| 5-112  | Variable Duty Cycle Power Converter With Post<br>Regulators     | 5-275 |

## LIST OF ILLUSTRATIONS (cont)

| Figure | Title                                                                                        | Page  |

|--------|----------------------------------------------------------------------------------------------|-------|

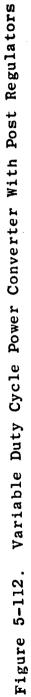

| 5-113  | Variable Duty Cycle Pre-Regulator with Series<br>Regulator and DC-DC Converter               | 5-276 |

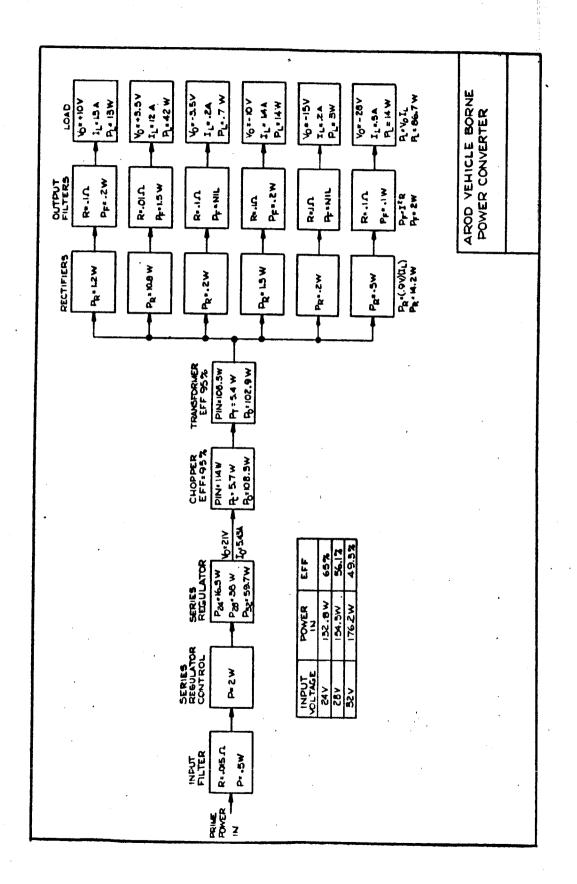

| 5-114  | AROD Vehicle-Borne Power Converter                                                           | 5-277 |

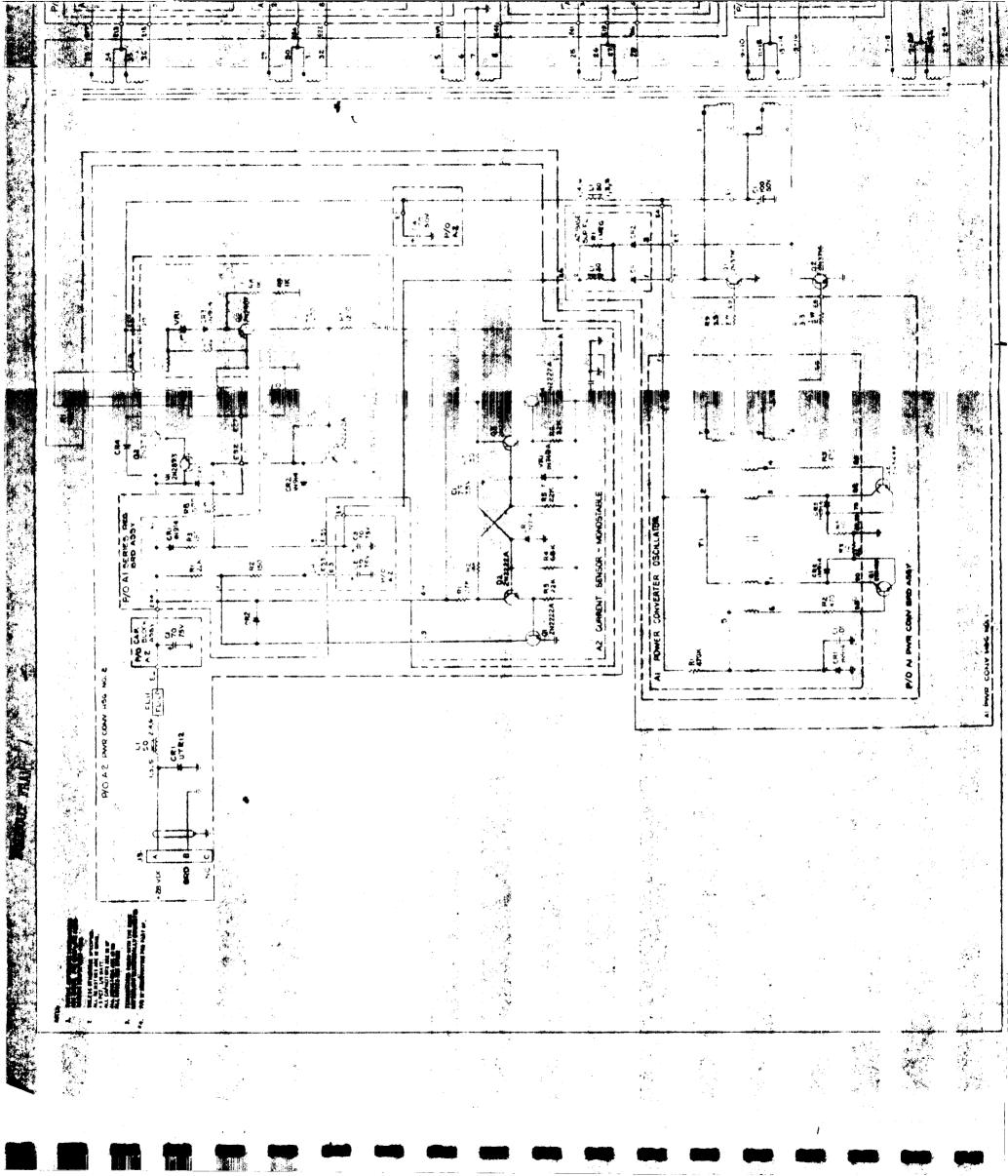

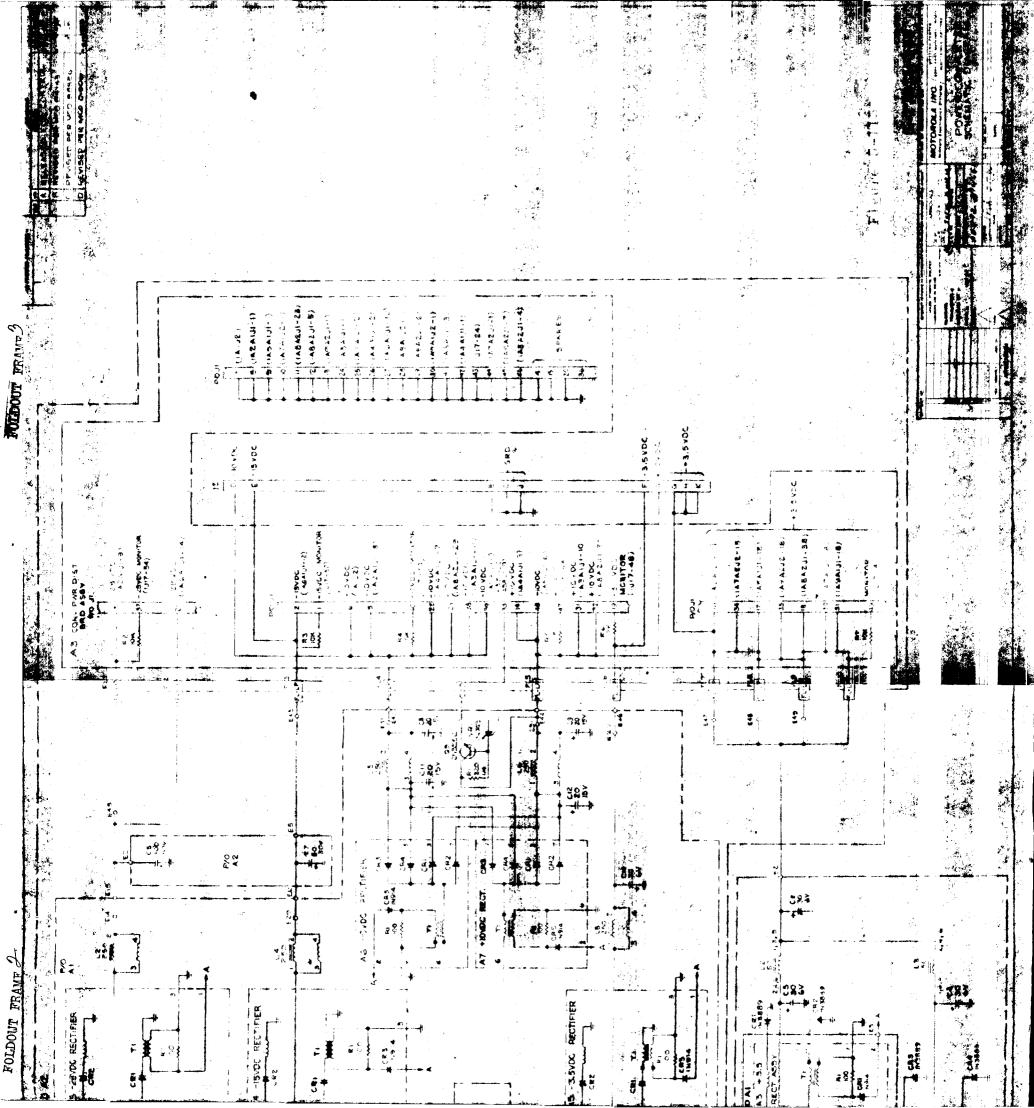

| 5-115  | Power Converter, Schematic Diagram                                                           | 5-279 |

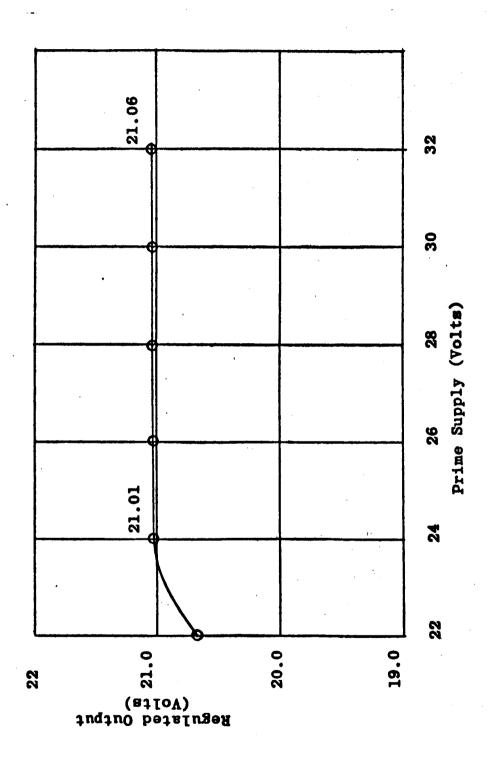

| 5-116  | Regulation of Breadboard Series Regulator                                                    | 5-282 |

| 5-117  | Output Impedance of Power Amplifier Used for Audio<br>Susceptibility When Loaded With 2 Ohms | 5-286 |

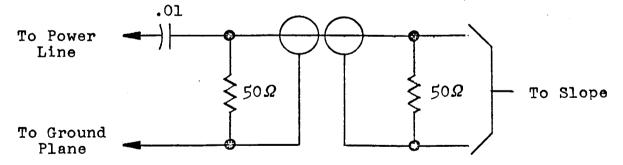

| 5-118  | Conducted Interference Using LSN (CW)                                                        | 5-287 |

## LIST OF TABLES

| Table | Title                                                                | Page  |

|-------|----------------------------------------------------------------------|-------|

| 5-1   | Performance of S/N l Station Control Transmitter                     | 5-33  |

| 5-2   | AROD Vehicle Receiver Code and Gate Equations                        | 5-131 |

| 5-3A  | Frequency Synthesizer Output Signals                                 | 5-154 |

| 5-3B  | Temperature Compensated Master Oscillator Specifica-<br>tion Summary | 5-160 |

| 5-4   | Phase Locked Loop Parameters                                         | 5-168 |

| 5-5   | Package Configurations                                               | 5-176 |

| 5-6   | Frequency Synthesizer Power and Weight Requirements.                 | 5-177 |

| 5-7   | Deviations From Specified Performance                                | 5-178 |

| 5-8   | Performance Deviations of Master Oscillator                          | 5-179 |

| 5-9   | Summarization of the Data Measurements Subgroup<br>Documentation     | 5-180 |

| 5-10  | Fine Range Counter Output.                                           | 5-229 |

| 5-11  | Q1 Output                                                            | 5-229 |

| 5-12  | Control and Information Messages                                     | 5-245 |

| 5-13  | Channel-Frequency Assignments.                                       | 5-245 |

| 5-14  | Transponder Responses at the End of 4 Seconds.                       | 5-247 |

| 5-15  | Station Sequence Registers                                           | 5-261 |

|       |                                                                      |       |

#### SECTION V

#### 5. VEHICLE-BORNE EQUIPMENT

Since the AROD system is primarily a vehicle-based system, the functions of timing, control, station selection, and data extraction are all performed in the vehicle equipment.

The vehicle equipment will operate with up to four stations simultaneously. Two radio frequency links are used to accomplish the functions of station control, acquisition aid, and the determination of the relative range and velocity to each station. The relative range is derived from the two-way time delay of a ranging modulation on the S-band transmission, and the relative velocity is derived from the two-way Doppler shift of the S-band carrier from the vehicle to the station and back.

The system is fully coherent in the tracking mode, for all radio frequency carriers as well as the ranging modulation are derived from a common source.

The vehicle-borne equipment performs all of the functions normally assigned to a ground tracking station in a "turnaround" manner. The vehicle-borne equipment originates the control and tracking signals and acts as the measurement and data collection point.

The vehicle range relative to a ground station is derived from the time delay between originating the ranging signal and correlating the returned signal at the vehicle. The range measurement is instrumented with a resolution of 0.183 meter over an unambiguous range of 3042 kilometers.

The vehicle velocity relative to a ground station is derived from the Doppler frequency shift on the returned signal and is measured with a resolution of 0.026 meter/second over a span from 0 to  $\pm 13,500$  meters/second.

A time label is made with an accuracy of  $\pm 0.1$  milliseconds of real time referenced to the vehicle oscillator with a resolution

of 10 microseconds over a 5-minute period. The time label references the time all measurements commenced for every 250-millisecond period.

At an approximate rate of four times per second (to telemetry or external source) the vehicle equipment is capable of reading out simultaneously four range measurements, four velocity measurements, and the time label.

The data readout is compatible with either an on-board computer or a telemetry system, or both, simultaneously.

The terminal equipment which eventually receives the data determines the actual position and velocity vector of the vehicle by processing the measured data and the known location of the ground stations.

General information regarding the requirements and characteristics for the vehicle equipment subsystems can be found in references 1 and 12. The following sections provide further detail of the subsystem design characteristics.

The AROD vehicle borne equipment is packaged in two cases. Within the cases, the subsystems are roughtly divided into frames. The circuitry within the frames is then packaged, mainly, in modules with some exceptions where the components are mounted directly to open boards.

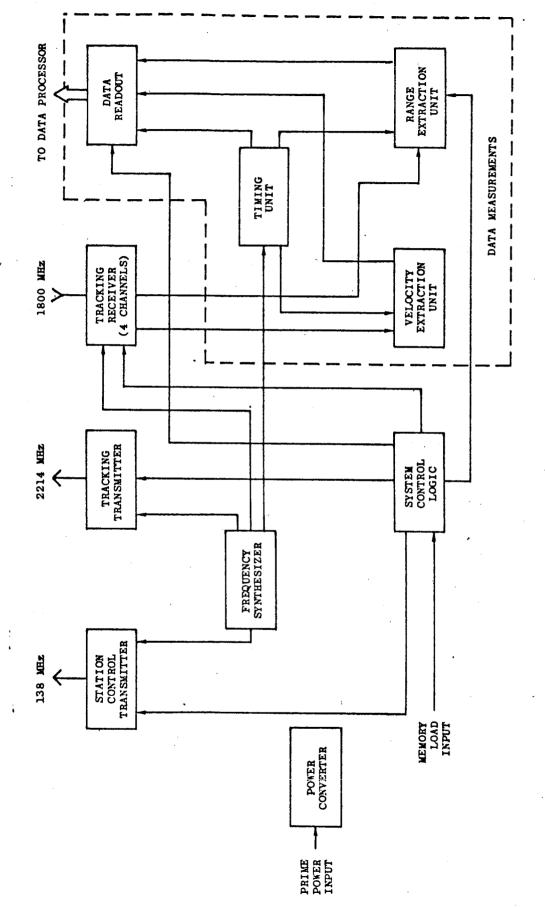

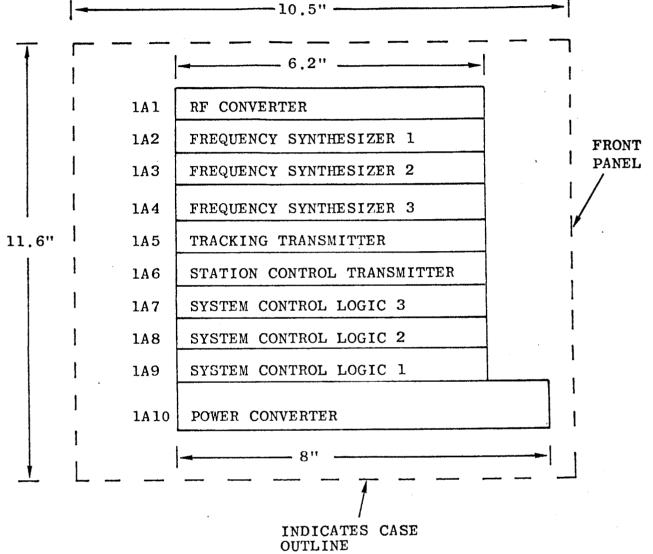

Figure 5-1 is a functional block diagram of the major subsystems of the vehicle borne equipment. Reference designations for the subassemblies and the physical location within the cases is shown in Figures 5-2 and 5-3.

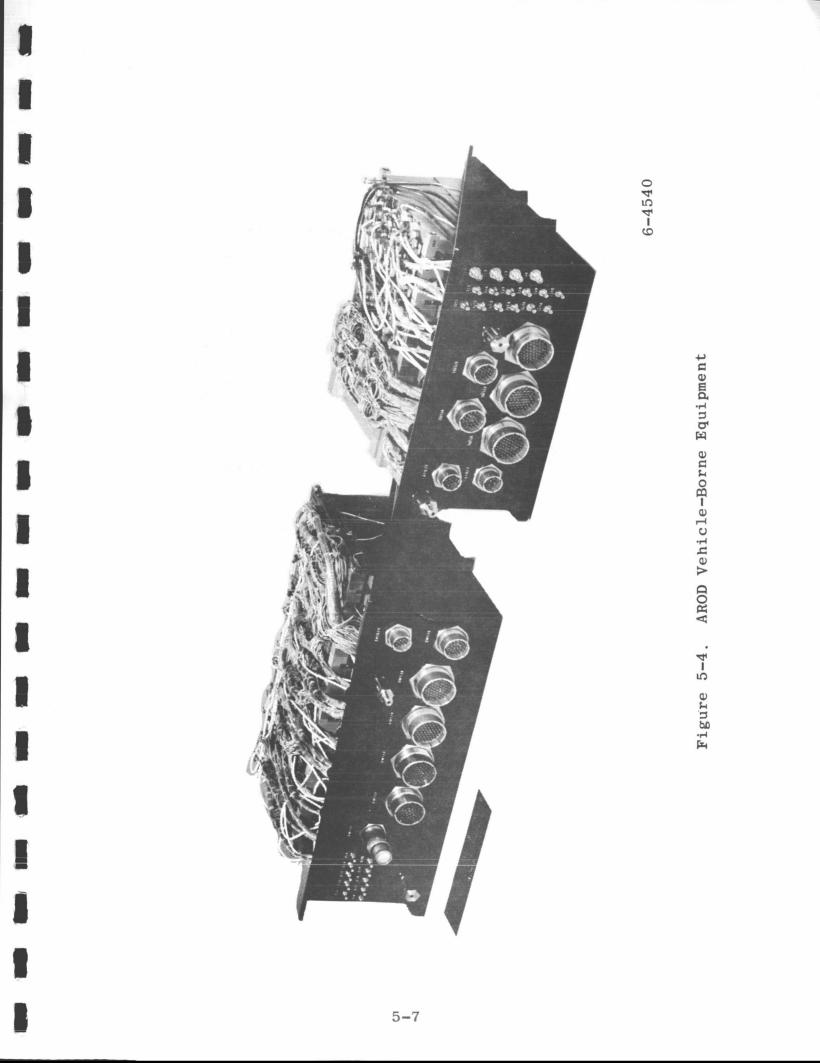

The AROD vehicle-borne system is divided into two cases to provide improved r-f isolation and to provide greater ease in handling. The angled case, see Figure 4-4, is used to permit easy removal of modules or frames, while still retaining a rigid connector mounting panel. The two cases are designed for mounting upon a thermal conditioning panel within the space vehicle or to the "cold plate" in the laboratory (see Figure 1-1) to maintain the base plate at approximately room temperature.

#### 5.1 TYPE CONSTRUCTION

The lower half of the angle case consists of a thick aluminum base plate to which sheet aluminum sides have been dip-brazed.

Vehicle-Borne Equipment Functional Block Diagram Figure 5-1.

Figure 5-2. Case 1 Top View

10.5"

6.2"

DATA MEASUREMENTS

DATA MEASUREMENTS

DATA MEASUREMENTS

DATA MEASUREMENTS

DATA MEASUREMENTS

BATA MEASUREMENTS

ATA MEASUREMENTS

Gata MEASUREMENTS

DATA MEASUREMENTS

BATA MEASUREM

FRONT

PANEL

2A12 2A11 CARRIER TRACKING LOOP 2A10 CHANNEL D 16.2" RECEIVER CODE CONTROL 2A9 CHANNEL C 2A8 MODULATION TRACKING LOOP CHANNEL C 2A7 CARRIER TRACKING LOOP CHANNEL C RECEIVER CODE CONTROL 2A6 CHANNEL B MODULATION TRACKING LOOP 2A5 CHANNEL B CARRIER TRACKING LOOP CHANNEL B 2A4. RECEIVER CODE CONTROL 2A3 CHANNEL A 2A2 MODULATION TRACKING LOOP CHANNEL A CARRIER TRACKING LOOP CHANNEL A 2A1

2A16

2A15

2A14

2A13

/ INDICATES CASE OUTLINE

Figure 5-3. Case 2 Top View

Stiffening members have been brazed to the side panels. The high side serves as the case front panel and is used, therefore, as the connector mounting panel. The upper half of the case is fashioned in a similar manner -- of sheet aluminum with stiffening ribs added by dip-brazing.

#### Mechanical Features

Each case is provided with an inlet and a purging value so that the case, when sealed, may be filled and pressurized with an inert gas. The cases and the internal module frame structures are designed to withstand the environmental conditions.

The interframe wiring harness is designed around prewired, prepotted, miniature multipin connectors. The angled case as shown in Figure 5-4 provides good accessibility to the modules, to the wiring harness, and to the connectors.

#### Dimensions and Weight

The total volume of Case 1 and Case 2 is approximately 1700 cubic inches and the total weight is approximately 51 pounds, including interconnecting cables.

#### Frame Assemblies

All frame assemblies, 10 in Case 1 and 16 in Case 2, except for the d-c power converter, have common dimensions -- 0.9 x 4 x 6.2 inches. The method of securing the frames to the base plate is also identical from frame to frame and consists of a cap screw in each end. There are three basic types of module construction utilized -- integrated circuit "microharness" modules, cordwood style, and point-to-point style.

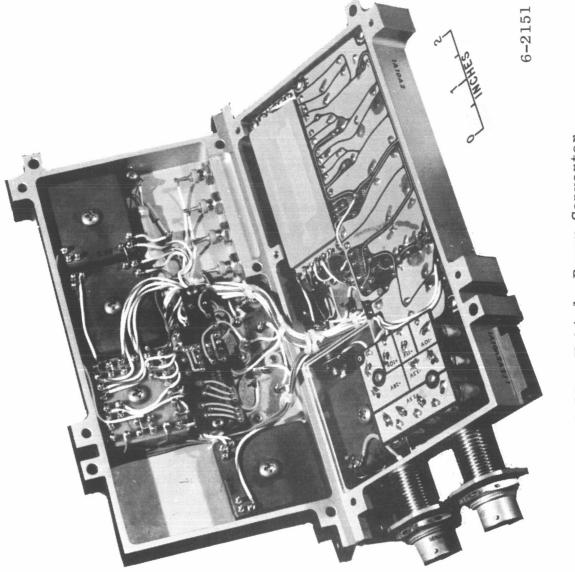

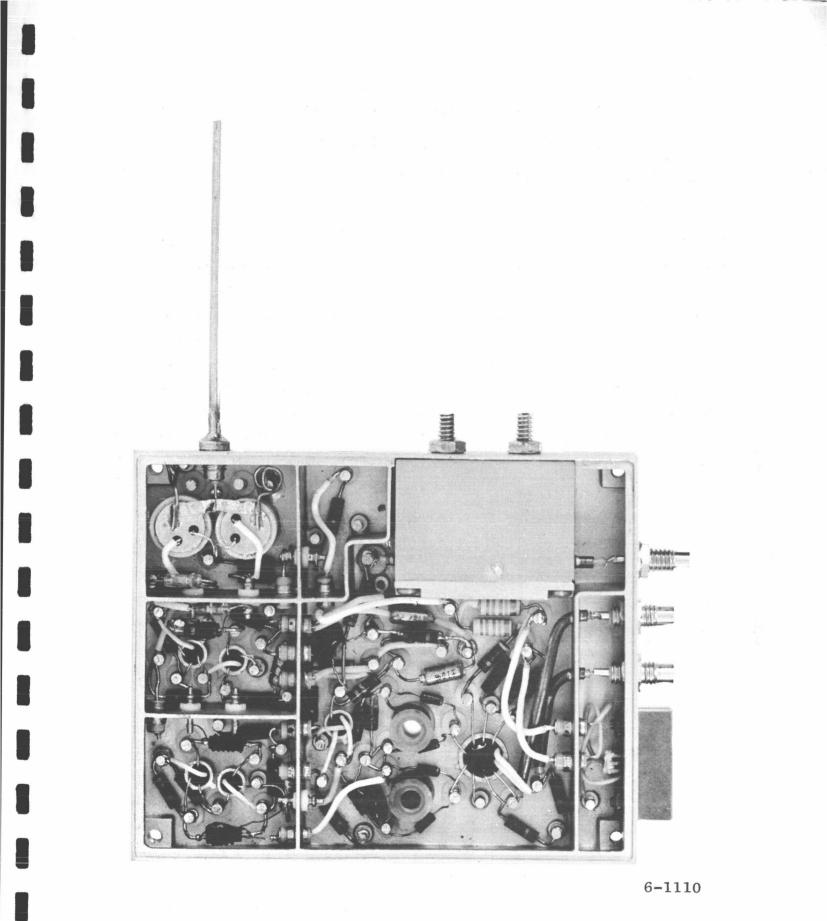

#### Station Control Transmitter

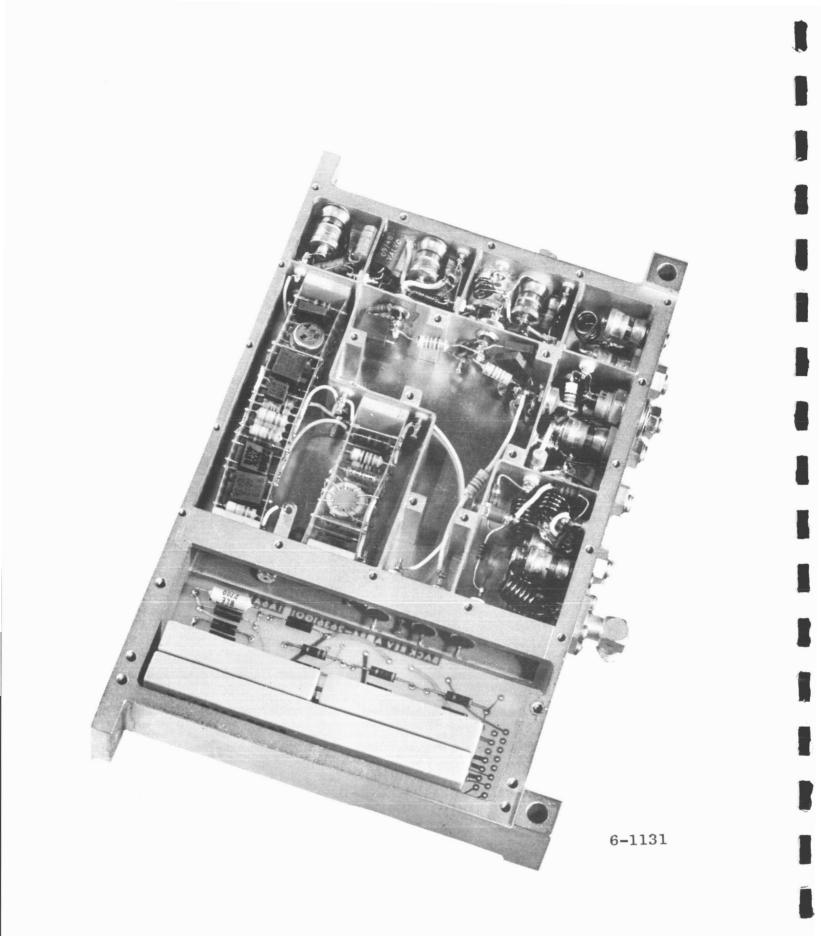

The station control transmitter is of standard dimensions and weighs 434 grams. The assembly is a combination of point-to-point wiring, r-f cordwood, and integrated circuit digital modules. A photograph of the transmitter is shown in Figure 5-5.

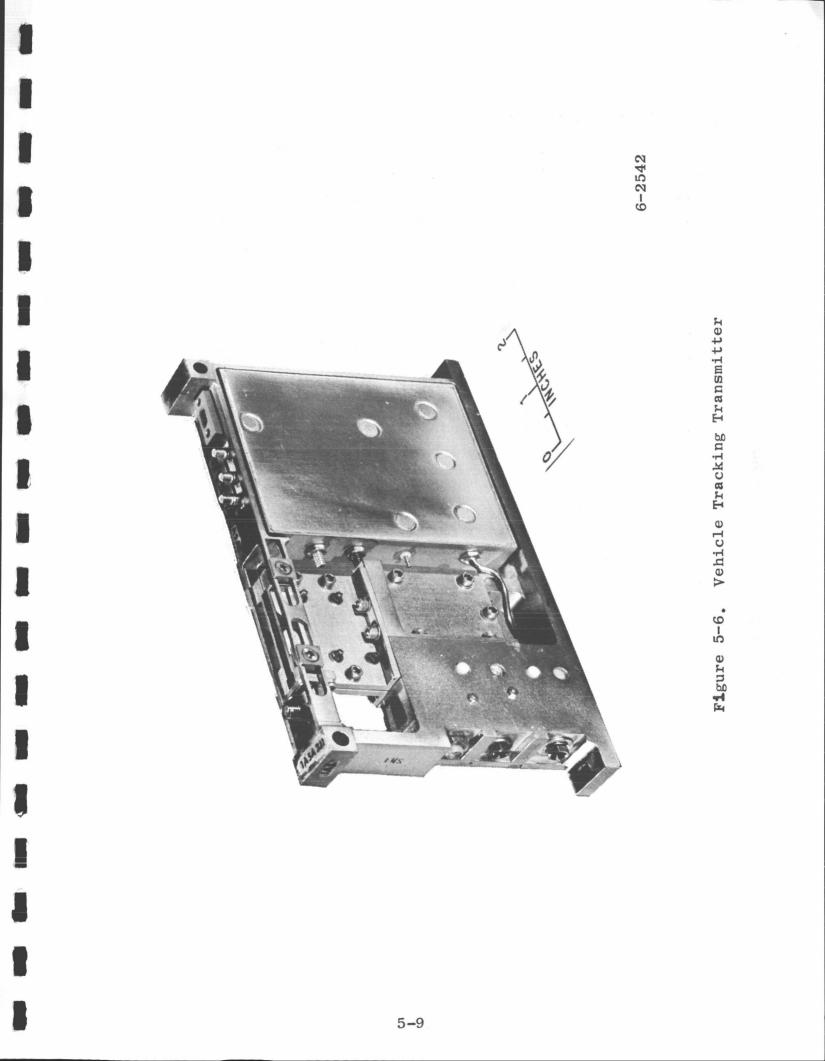

The Control Data Modulator, located at one end in Figure 5-6 uses digital integrated circuit modules attached to a printed motherboard along with a few discrete components. The modulator and first r-f stages utilize cordwood type construction while the later r-f stages, being more critical as to lead length and component placement utilize point-to-point wiring. The entire assembly is potted with epoxy-glass foam for shock and vibration considerations.

Figure 5-5. Station Control Transmitter

#### Vehicle Tracking Transmitter

The vehicle tracking transmitter is built around the S-band X4 multiplier (see Figure 5-6), which occupies the left half of the frame. The entire housing is milled from a solid block of aluminum, with the X4 multiplier input circuitry located in a cavity at the lower left corner. Provision is made to accommodate the sliding adjustment on the output filter, upper left.

The bi-phase modulator/multiplier X4 subassembly is installed in the right half of the frame. For r-f shielding and ease of assembly, the d-c power connector and the coaxial input fittings are integral to the subassembly. A slot is provided in the frame through which they are inserted during assembly. This subassembly is completely hand-wired, point-to-point wiring, see Figure 5-7. The semi-rigid coaxial output is cut to fit at assembly with the S-band X4 multiplier.

After assembly and alignment, both the S-band X4 multiplier and the bi-phase mod/mult X2 are filled with an epoxy-glass form, Scotchcast #XR5068, to secure all components in position. The assembled unit is of standard dimensions and weighs 399 grams.

6-1110

Figure 5-7. Bi-Phase Mod/Mult. X2

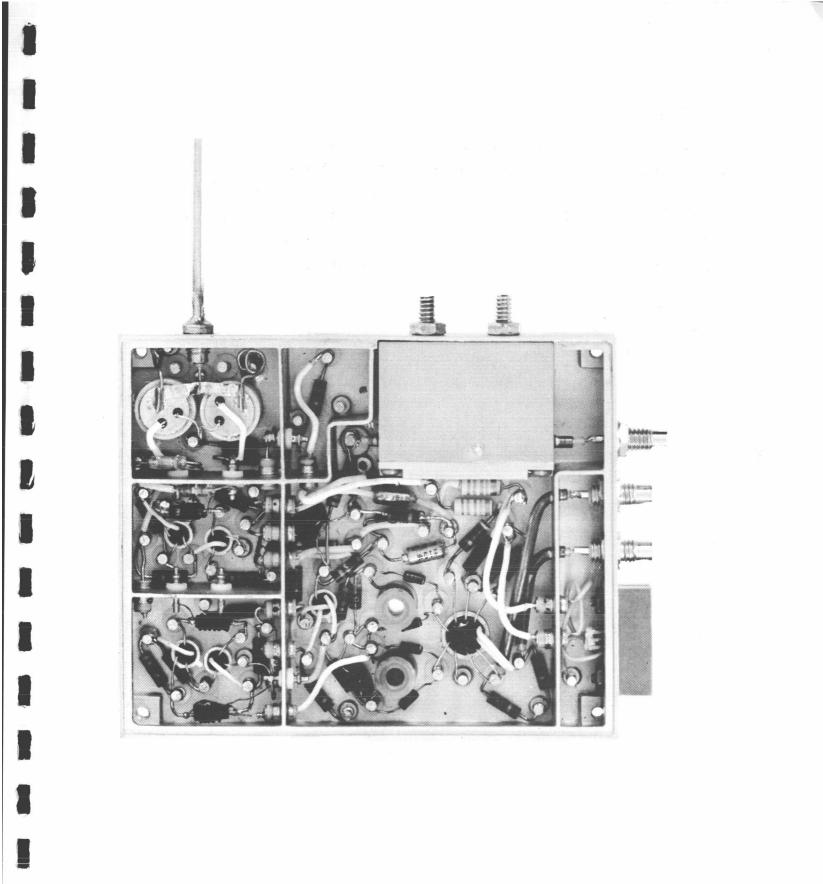

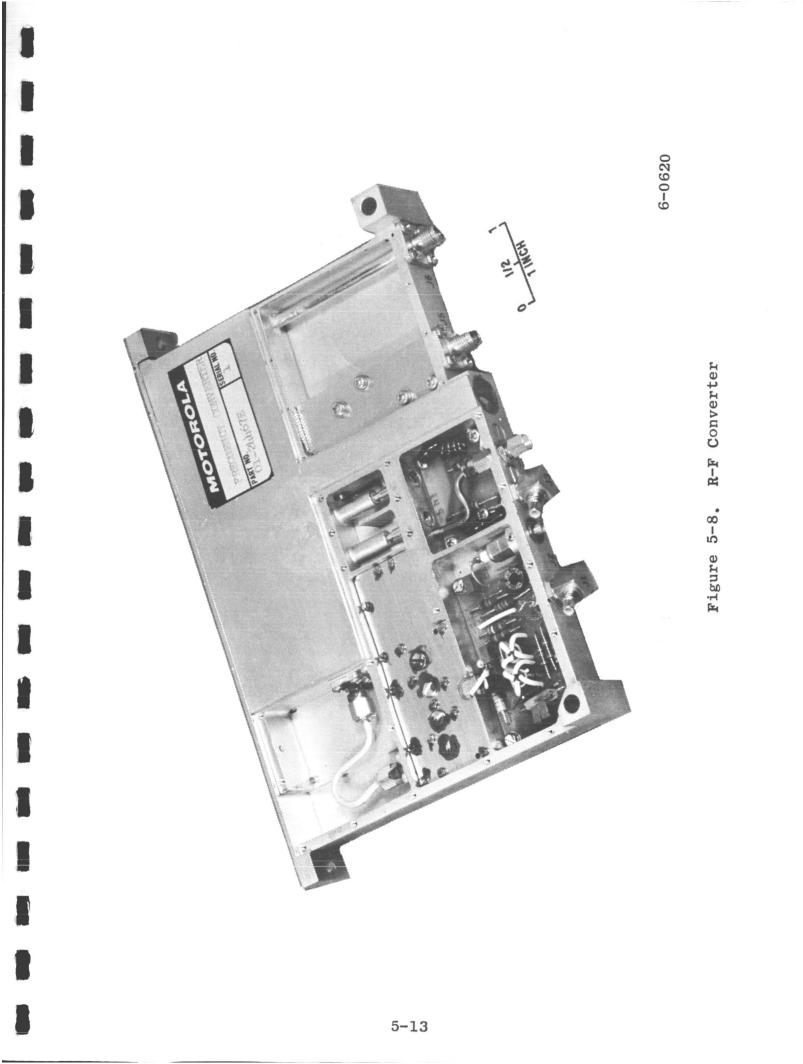

#### **R-F** Converter

The r-f converter assembly is shown in Figure 5-8 (with the covers removed). The S-band diplexer is located in the upper side (under the nameplate). The mixer is located in the left center portion with the low-noise i-f stage and local oscillator multiplier just below. This assembly utilizes the point-to-point wiring style. This subassembly weighs 411 grams.

#### Vehicle Tracking Receivers

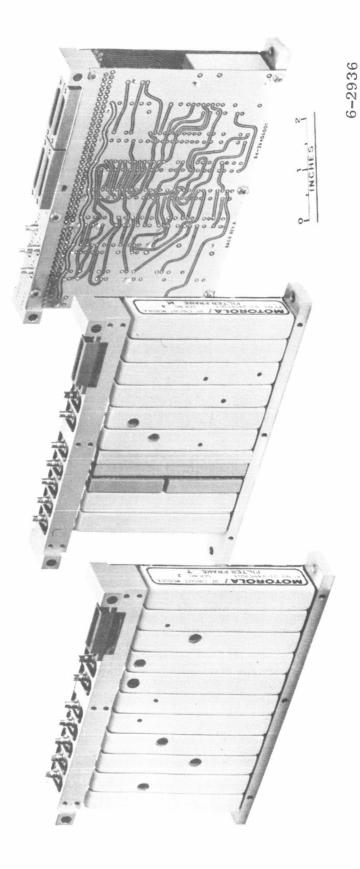

Each of the four vehicle tracking receivers utilizes three frames of Case 2. One frame, the carrier tracking loop, utilizes all r-f cordwood modules, the receiver code control frame is a double motherboard using all digital integrated circuit modules, while the third frame, the modulation tracking loop, uses a mixture of r-f cordwood and digital modules. A photograph of the three frames, which weigh approximately 1440 grams, is given as Figure 5-9.

#### RF Cordwood Modules

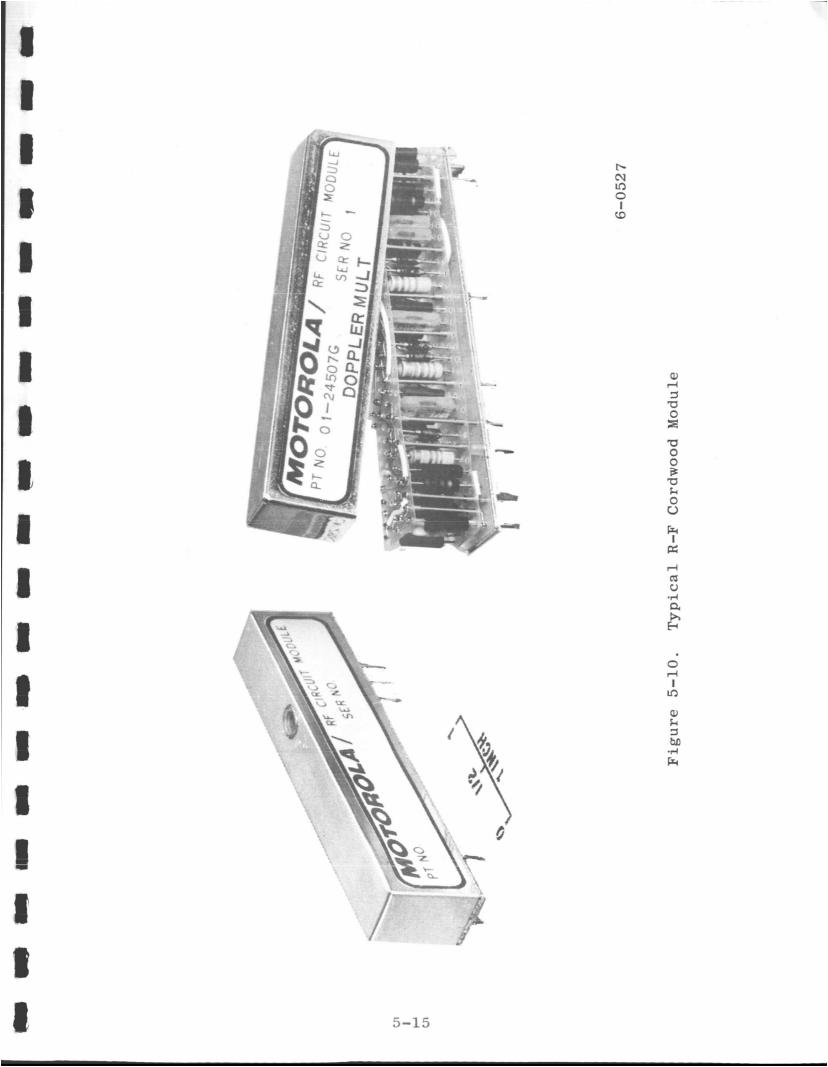

A typical r-f cordwood module is shown in Figure 5-10. The dimensions are 3.15 in. long x 0.55 in. wide x 0.7 in. high. After component assembly, the module is tested and aligned, if necessary, and the metal cover is sealed to the header. The assembly is then potted using epoxy-glass foam.

#### Digital Integrated Modules

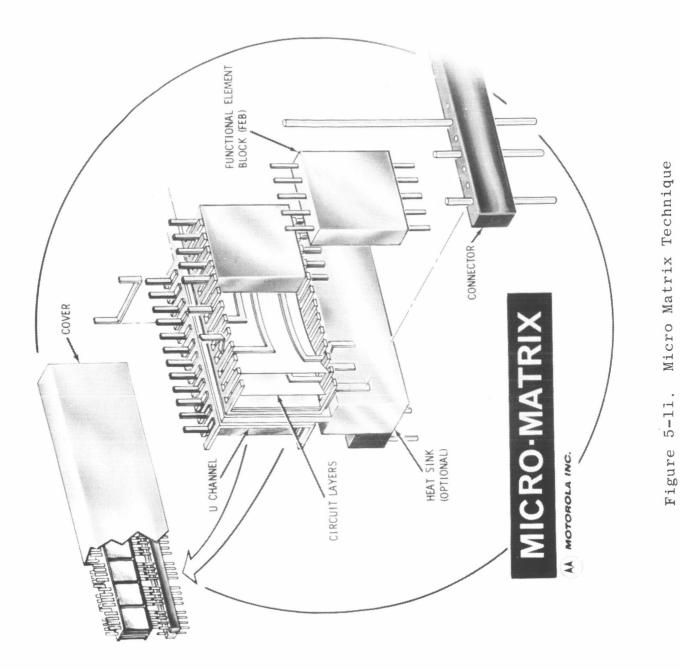

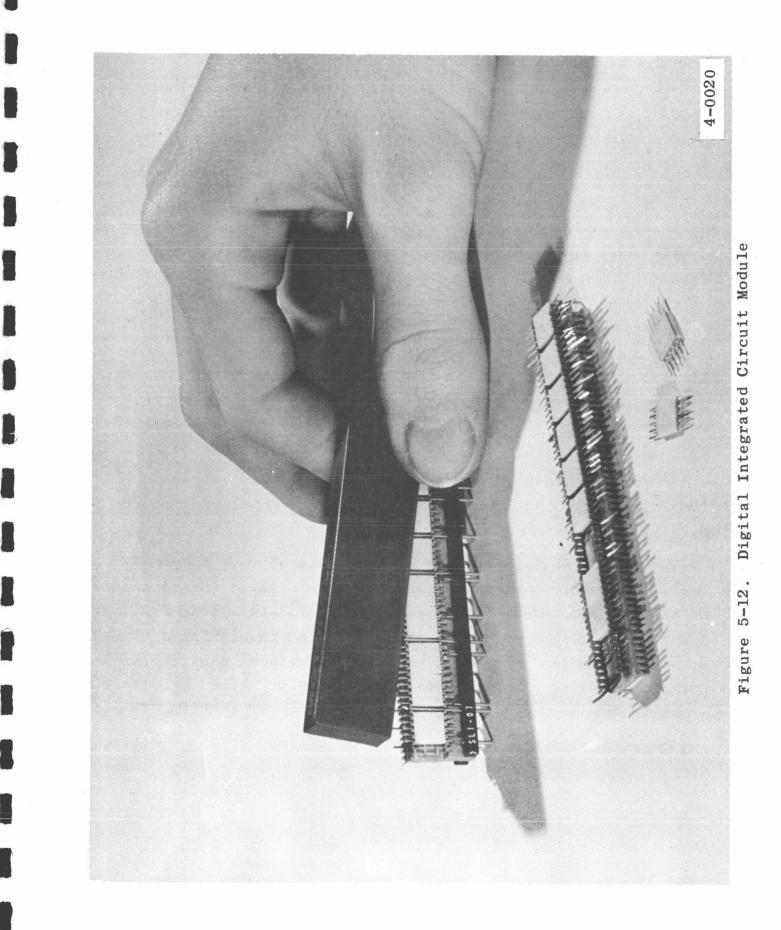

Figure 5-11 shows the technique used in AROD for packaging "flat-pack" integrated circuit elements. Up to 20 flat packs are mounted in a module, 10 in each "U-Channel". Electrical interconnections are made by the circuit layers, which consist of thin (0.004 in.) "Kovar" clad mylar sheets, separated by 0.002 in thick plain mylar sheets. Connections between flatpacks and header pins are made by resistance welding. The resulting package, after test, is then encapsulated with stycast to form the completed module which is 3.15 in. long x 0.35 in. wide x 0.7 in. high. Figure 5-12 is a photograph of a typical module.

Figure 5-9. Vehicle Tracking Receiver

4 - 0480

#### Frequency Synthesizer

The AROD frequency synthesizer consists of three frames, as shown in Figure 5-13, having a total weight of 1445 grams. It uses a combination of RF and cordwood modules. In addition, the 3.2 MHz frequency standard is installed on the center frame.

#### Distribution Amplifier

The AROD distribution amplifier, shown in Figure 5-14, is constructed differently from other portions of AROD. It is mounted on the base of Case 2 just below the coaxial connectors 2J1-2J10. The distribution amplifier accepts three r-f

signal inputs from Case 1 and distributes them to their proper location in Case 2. Within the distribution amplifier, the three signals are buffered providing isolated outputs to each of the four receivers. The small  $(0.9 \times 1 \times 6 \text{ inch})$  case is divided into three isolated compartments with the components mounted on printed circuit boards within the compartments. The total weight is 131 grams.

#### Data Measurements

The data measurements subgroup consists of four frames of digital integrated circuits (Figure 5-15). These frames consist of two motherboards, with up to nine I/C modules per board. The I/C modules are spaced so they sandwich together. The method provides the added printed circuit paths without sacrificing packaging density, and results in an extremely strong, rigid assembly.

The subgroup includes the timing unit, four velocity extraction units, four range extraction units, the transmitter code control, and the data readout subsystem. This consolidation into a subgroup was made to alleviate the requirements of the interconnection harness. The four frames have a combined weight of 1635 grams.

Figure 5-14. Distribution Amplifier

6-2291

1

#### System Control Logic

The AROD System Control Logic (Figure 5-16) consists of three frames of digital integrated circuits packaged with the double motherboard concept described above. One frame of the system control logic contains the magnetic memory. The three frames of the system control logic weigh 1152 grams.

#### D-C Power Converter

The d-c power converter is the largest  $(1.75 \times 4 \times 8 \text{ in.})$  and the heaviest 1545 grams) of all the subsystem frames. It is constructed in two halves (see Figure 5-17) which then sandwich together to form a closed frame. The enclosures are milled from solid aluminum stock with the base left quite heavy to serve as a heat sink for the power diodes and transistors. Power input leads and Case 2 power leads are shielded within metallic bellows to allow for dimensional tolerances.

#### 5.2 STATION CONTROL TRANSMITTER

This section is the final Engineering Report on the Station Control Transmitter designed and developed for the AROD System.

The transmitter (Figure 5-5) is the space vehicle portion of the VHF link between the vehicle and the ground station. Information is transmitted on this link to control the state of the ground stations. The link also provides a coherent carrier which is used for coarse acquisition and antenna tracking prior to lockon to the S-band link.

The output frequency of the transmitter is 138 MHz at a power level of 6 watts. The carrier is phase modulated to a nominal index of 1.2 radians. Modulation linearity is  $\pm 5\%$  of the best straight line for modulation indexes up to 1.5 radians. Complete specifications on the transmitter can be found in Document No. 12-25562J, Electrical Performance Requirements for the Station Control Transmitter.

Figure 5-17. Vehicle Power Converter

1

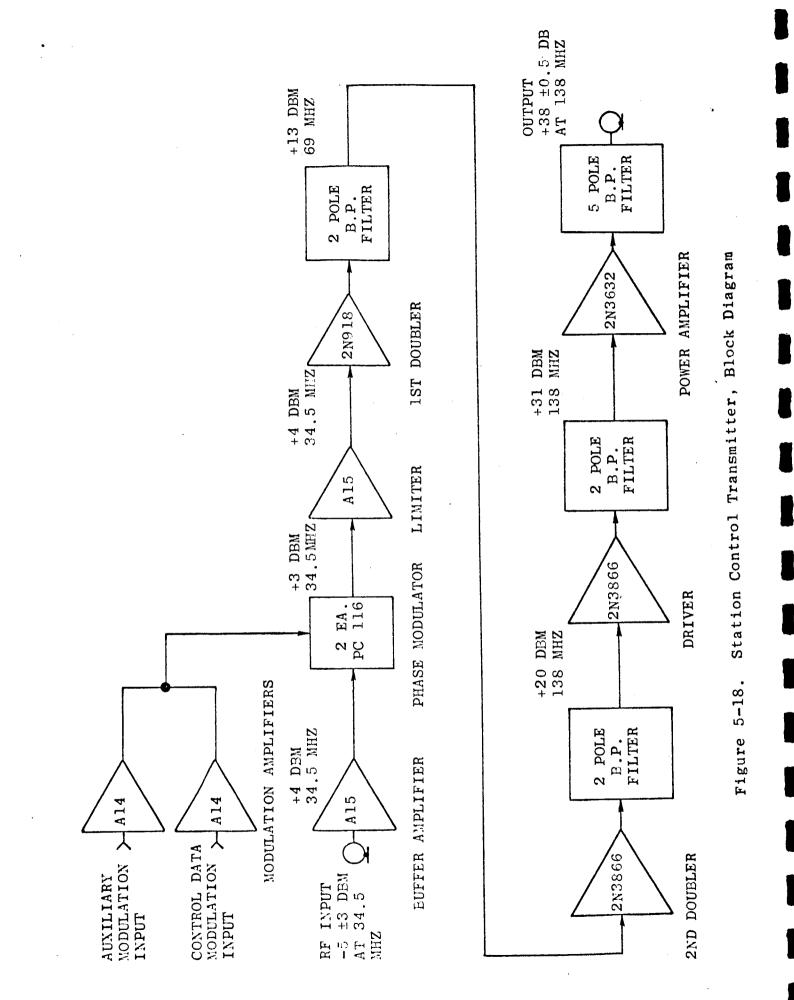

#### 5.2.1 Technical Approach

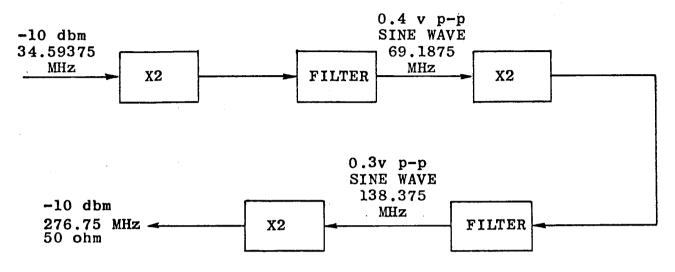

Figure 5-18 is a block diagram of the Station Control Transmitter. This section presents very briefly some of the technical considerations which resulted in the configuration shown in Figure 5-18.

The VCO carrier frequency reference for the Station Control Transmitter is at a frequency of 34.5 MHz. This requires that the transmitter provide a multiplication of 4 to obtain the proper output frequency of 138 MHz. This presents many implementation possibilities such as a varactor X4, a transistor X4, two varactor doublers, two transistor doublers, or a varactor doubler and a transistor doubler combination. Since present day transistors can multiply by two or four and still provide gain at these frequencies, active multipliers were selected as being more economical in both size and cost. The reduced number of components also results in better reliability.

Because of the stringent specifications on antenna conducted spurious emissions, two doublers were selected rather than a single X4 so that filtering could be provided between the multipliers. This greatly facilitates reducing the spurs occurring 34.5 MHz above and below the carrier to the specified 88 db down from the carrier level.

The phase modulation is applied prior to the multiplication so the index of modulation is multiplied also. This makes it easier to obtain large modulation indexes linearly. The phase modulator is followed by a limiter to strip off any unwanted amplitude modulation.

The modulation amplifiers, the buffer amplifier and the limiter all utilize hybrid integrated circuit differential amplifiers which had already been designed and developed for other uses on the project. This was done to minimize design time and conserve space.

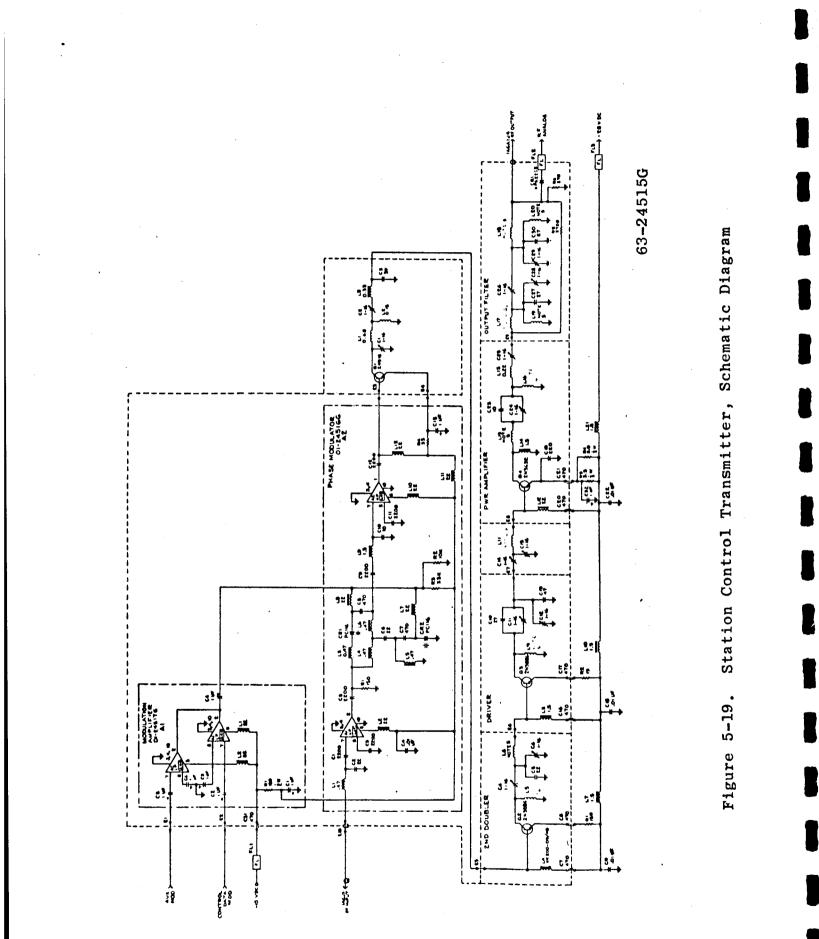

# 5.2.2 Circuit Descriptions

A schematic diagram of the Station Control Transmitter is shown in Figure 5-19. A discussion of each of the stages shown in the schematic follows.

### 5.2.2.1 Phase Modulator Assembly

The Phase Modulator Assembly is a cordwood assembly containing the Buffer Amplifier, Phase Modulator and Limiter plus the base return, emitter by-pass and emitter resistor for the First Doubler. Cordwood construction techniques were used to conserve space.

#### Buffer Amplifier

The Buffer Amplifier is a hybrid differential amplifier. It has a saturated output power level of approximately +4 dbm with a gain of 23 db. The input signal to the Buffer Amplifier is nominally -5 dbm at 34.5 MHz. Matching to the 50 ohm line is accomplished by Ll and C2 while DC decoupling is provided by Cl, C3, and C5. This stage draws approximately 19 ma at -9 vdc.

#### Phase Modulator

The Phase Modulator is a bridged-T network in which CRl is a voltage variable capacitor and CR2 is made to look like a voltage variable inductor through a quarter wave transmission line. Phase shift through the network then becomes a function of the bias voltage on CRl and CR2. In the transmitter, the diodes are DC biased at -2 volts and the modulating voltage is AC coupled to them. The DC bias is to prevent the diodes from becoming forward biased when modulation voltage is applied.

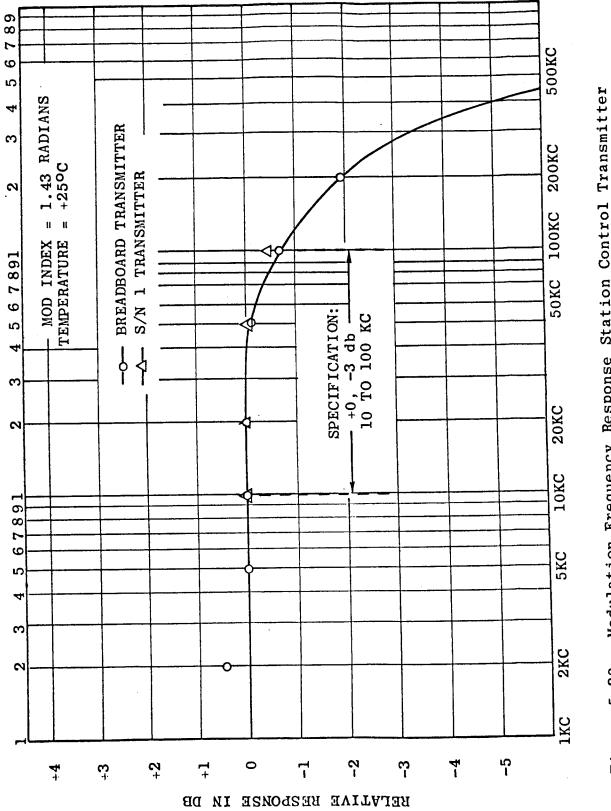

A bridged-T network was selected as the phase shifter because of its ability to provide large phase shifts linearly while introducing a minimum of amplitude modulation. This circuit is capable of modulating the transmitter output to an index of greater than 4 radians linearly when driven directly. (See Figure 5-20) However, when used with the Modulation Amplifiers the capability for linear modulation drops to approximately 1.5 radians because

of the limiting action of the amplifiers. A modulation index of 1.5 radians is more than adequate for this application.

Complete details on the design and operation of this type of phase modulator can be found in NASA Technical Report, Constant Amplitude, Variable Phase Filters, by L. J. Rogers and D. S. Helper.

#### Limiter

A hybrid integrated circuit differential amplifier was selected for the limiter stage because of its excellent limiting characteristic as well as for its ability to save space and design effort. The amplifier is operated deep into saturation to strip off any residual amplitude modulation and to provide a temperature stable signal source for the first doubler.

The saturated output of the limiter is approximately +4 dbm with a gain of about 23 db. The input level from the Phase Modulator is approximately +3 dbm putting the stage well into limiting.

Current drain of the limiter is about 19 ma at -9 vdc. The impedance match from the Phase Modulator to the Limiter is made by L4 and Cl0. DC isolation is provided by C9, Cl1, and Cl2. Ll2, R4, and Cl3 although packaged in the Phase Modulator Assembly are respectively the base return, emitter resistor and emitter by-pass for the first doubler stage.

5.2.2.2 Modulation Amplifier Assembly

The Modulation Amplifier Assembly consists of two identical amplifier stages. The two amplifiers provide the transmitter with two isolated modulation inputs. Low power hybrid integrated circuits are used in the two stages. Each amplifier has an output to input isolation of 40 db resulting in an isolation of greater than 80 db between modulation inputs.

Modulation voltage sensitivity of the transmitter is set by selecting resistors in voltage divider networks at the inputs of the amplifiers. The divider networks are located on the Printed Circuit Board Assembly (01-26360G01). The two amplifiers operate on -15 vdc and draw approximately 7 ma each.

Resistor R1 in the Modulation Amplifier Assembly is simply a dropping resistor to reduce the -15 vdc to -9 vdc for use in the Phase Modulator Assembly. C1 provides filtering between the Modulation Amplifier Assembly and the Phase Modulator Assembly on the power supply line.

The hybrid integrated circuit differential amplifiers were selected for use as the modulation amplifiers because of their high output to input isolation, broad frequency response, and small size. However, because of their limiting action, the voltage swing into the Phase Modulator is limited which limits the modulation index at the transmitter output to about 1.5 radians if good linearity is to be maintained.

5.2.2.3 Multipliers and Power Amplifier

The First and Second Doublers, the Driver and the Power Amplifier utilize point-to-point wiring techniques because of the frequencies and power levels involved. All of the active elements are mounted directly to the chassis providing a heat sink to minimize the junction temperature rise. High Q components such as air core inductors are used to reduce losses in the high power stages.

# First Doubler

The First Doubler is a 2N918 transistor driven in class C operation to produce harmonics. The two pole filter following the doubler selects the desired harmonic and makes the necessary impedance transformation into the following stage.

Input to the doubler is about +4 dbm at 34.5 MHz from the Limiter. The output of the doubler is +14 dbm at 69 MHz for a conversion gain of 10 db. Collector efficiency of the stage is approximately 16%, thus requiring a current of 15 ma at -9 vdc.

# Second Doubler

This stage uses a 2N3866 transistor operated as a class C doubler having an output frequency of 138 MHz at a power level of +21 dbm. As originally designed, this stage had a conversion gain of 13 db, however, the output level of +27 dbm placed the driver stage too far into a power saturated condition resulting in inefficient operation and a high junction temperature. The emitter resistor of the doubler was, therefore, increased to 150 ohms to decrease the doubler output power to +21 dbm. The stage now draws approximately 11 ma at -28 vdc for a collector efficiency of 42%. A two-pole bandpass filter follows the doubler and provides the necessary impedance transformation to the driver stage.

A ferrite choke was used as the base return in the Second Doubler to improve the stability of the stage.

### Driver

The Driver is a class C RF amplifier which provides slightly over 10 db of gain at 138 MHz. The output level is about +31dbm (1.25 watts) and the stage draws 70 ma at -28 vdc. The active device is a 2N3866 transistor.

To ease design and test problems, the impedance transformation from the Driver to the Power Amplifier is made in two discrete steps. The first step is down to 50 ohms and the second step is down to the input impedance of the Power Amplifier (about 6 ohms). The two transformation steps also provide two poles of bandpass filtering between the stages.

#### Power Amplifier

The Power Amplifier is a class C amplifier using a 2N3632 transistor. This stage develops approximately 8 watts of power at a collector efficiency of 66% through the two pole filter and matching network formed by Ll3, Ll5, and Ll6 and C23, C24, and C25 into a 50 ohm load. However, the spurious outputs at this point were too high to meet the EMI specification, so an additional three poles of filtering had to be added to the output.

The three pole filter has an insertion loss of approximately 1 db at center frequency which reduces the transmitter output power to the required +38 dbm (6.3 watts).

Multiple emitter by-passing is used on the Power Amplifier to insure its stability and to improve the gain. The stage draws about 445 ma at -28 vdc which requires the use of two  $\frac{1}{2}$  watt resistors in parallel in the emitter.

A monitor of the transmitter output power is provided by the detector circuit formed by R5, R6, CR1 and FL2. The detector circuit was placed at the front end of the output filter rather than at the output connector so the harmonics generated by the detector diode must pass through the output filter. With a transmitter output of 6 watts the detector circuit develops an RF analog voltage of approximately +3 vdc into a 1 K load.

# 5.2.3 Test Results

Table 5-1 and Figures 5-20 to 5-22 compare the performance of SN-1 Station Control Transmitter with the design specifications and with the Breadboard Transmitter performance.

# 5.3 CONTROL DATA MODULATOR

The Control Data Modulator uses the Control Data input and the sub-bit input to phase modulate a subcarrier of 18.75 kHz. The subcarrier is modulated in a manner such that an output data "1" level is represented by 18.75 kHz at -90 degrees for the first-half bit and 18.75 kHz at 0 degrees for the secondhalf bit. A data "0" level is represented by 18.75 kHz at +90 degrees for the first-half bit and 18.75 kHz at 0 degrees for the second-half bit.

# 5.3.1 Technical Approach

The digital portion of the Control Data Modulator is packaged in a standard AROD I/C module and an output filter section is mounted on the motherboard assembly. The motherboard assembly

Performance of S/N 1 Station Control Transmitter TABLE 5-1.

|                    |               |              |                           |                |              |        |                  |            | _          |            |            |            |            | -          |            |            | <br>_ | _ |   |   |

|--------------------|---------------|--------------|---------------------------|----------------|--------------|--------|------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------|---|---|---|

| +52°C              | S/N 1         | +37.25 dbm   | 6 MHZ                     | 50 <b>5</b> ma | 63.5 ma      |        |                  | -81 db     | -88 db     | -76 db     | -72 db     | -90 db     | -95 db     | -92 db     | -93 db     | >−96 db    |       |   |   |   |

|                    | B/B           | +37.6 dbm    | 5 MHZ                     | 470 ma         | 58<br>ma     |        |                  | -96 db     | -90 db     | -96 db     | >−96 db    | db ∂9-<    | db ∂9-<    | >-96 db    | -96 db     | db 39<     |       |   |   |   |

| °c                 | S/N 1         | +37.6 dbm    | 6 MHz                     | 525 ma         | 64 ma        |        |                  | -96 db     | >-96 db    | -76 db     | -72 db     | -90 db     | -95 db     | -91 db     | -93 db     | >-96 db    |       |   | · |   |

| +25 <sup>o</sup> C | B/B           | +38.2 dbm    | 5 MHZ                     | 495 ma         | 58 ma        |        |                  | -94 db     | -88 db     | db 99-<    | db 99<     | >−96 db    | db 99-<    | db 99<     | -96 db     | db 99<     |       |   |   |   |

| 0                  | I N/S         | +38.26 dbm   | 6 MHz                     | 520 ma         | 64 ma        | •<br>• |                  | -96 db     | >-96 db    | -76 db     | -72 db     | -92 db     | -95 db     | -92 db     | -93 db     | −96 db     |       |   |   |   |

| 0°C                | B/B           | +38.2 dbm    | 5 MHz                     | 485 ma         | 56 ma        |        |                  | db 99<     | -88 db     | >-96 db    | 96 db      | db ∂b-<    | db ∂9-<    | >96 db     | >-96 db    | >−96 db    |       |   |   |   |

|                    | Specification | +38 ±0.5 dbm | 2 MHz min                 | 550 ma min     | 80 ша шах    |        |                  | -88 db min | -88 db min | -60 db min | -60 db min | -88 db min |       |   |   | • |

|                    | Parameter     | Power Output | Dynamic 3 db<br>Bandwidth | -28v Current   | -15v Current | :      | Spurious Outputs | 103.5 MHz  | 172.5 MHz  | 276.0 MHz  | 414.0 MHz  | 552 MHZ    | 690 MHZ    | 828 MHZ    | 966 MHz    | All Others |       |   |   |   |

5-35

X

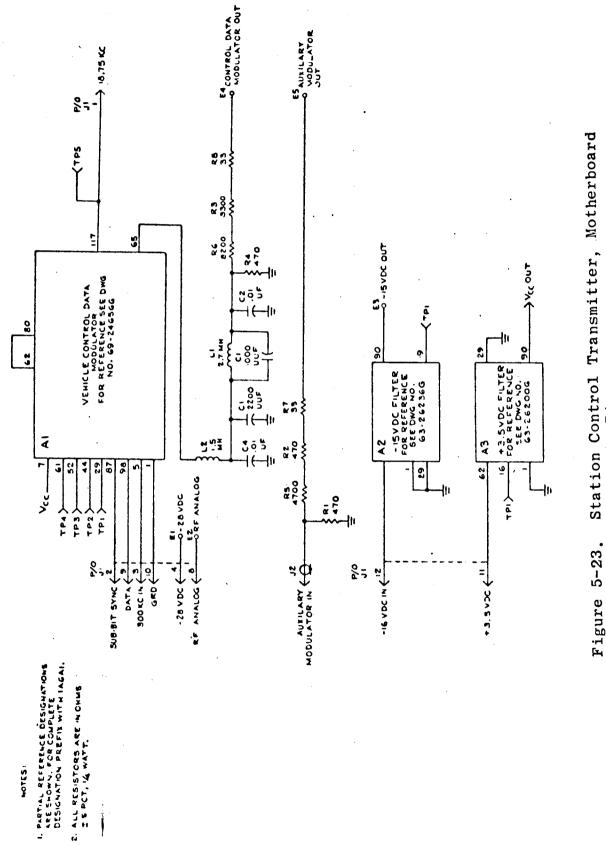

schematic diagram is shown in Figure 5-23 and the logic diagram for the I/C module is shown in Figure 5-24.

The digital logic portion of the Control Data Modulator was well defined and presented no design problems. The output filter section specifications were a delay time of 11  $\mu$ s ±2  $\mu$ s at 18.75 kHz and given attenuations at each of the first five harmonics of 18.75 kHz.

In the design effort both active and passive symmetrical bandpass filters were evaluated. These proved unsatisfactory because of the large variation in time delay with respect to small changes in component values. An inductor-input,  $\pi$ -section, low pass filter was chosen because of its relatively insensitive time delay at all frequencies less than the cutoff frequency and its non-critical component values.

## 5.3.2 Logic Description

The 300 kc signal from the Frequency Synthesizer is shaped by a hybrid interface circuit and is divided by 16 to form 18.75 kHz at 0 degrees (B) and shifted to form 18.75 kHz at +90 degrees (A) and 18.75 kHz at -90 degrees (C). These signals are then gated by the data input (D) and the sub-bit clock (SB) to form the subcarrier output modulation.

Output =  $A \cdot \overline{SB} \cdot D + B \cdot SB + C \cdot \overline{SB} \cdot \overline{D}$

This output is capacitively coupled through a 510 ohm resistor to the output filter. The 510 ohm resistor provides the proper source resistance for the output filter.

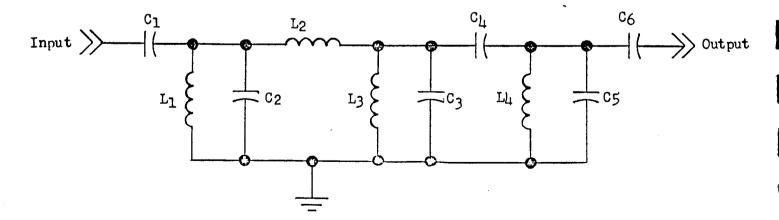

# 5.3.3 Output Filter Description

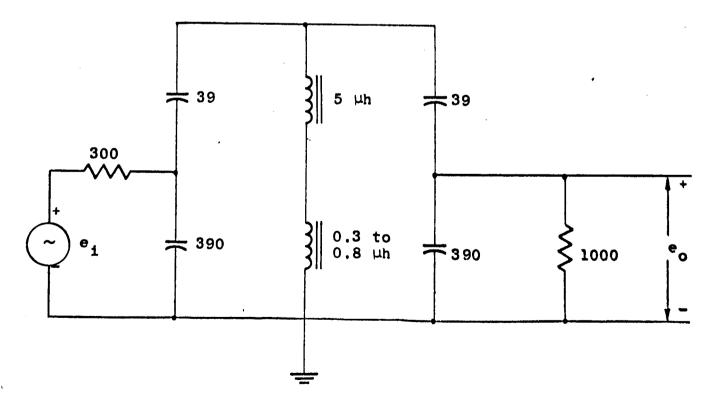

The output filter section is made up of L2, C4, C1, L1, C3, C2, and R4. The input section to the filter, L2, C1, and C4, provide the first roll off frequency at 42 kHz while L1 and C3 provide a notch at 94 kHz and L1 and C2 maintain the attenuation above the notch frequency. Resistor R4 is the filter termination while resistors R6, R3, and R8 are selected to provide the proper modulation voltage sensitivity of the transmitter.

5-38

Schematic Diagram

COM OUT -P.C. F = 4 859 89 1 PES P Station Control Transmitter, I/C Module Logic Diagram 10 A 4 AB 1 V 2 R2 2 NOTE 5 3231 -FFI REG Q n ž ŭ 8 2 4 Å DETAIL OF LOCIC ELEMENTS **\***\*\* 2-1-1 ₿-₹ ॶॖॖॖ॒ढ़१ ऻ(—|। तन्तन्त-ट्र Figure 5-24. ----ÿ 5 § §: 10 2014 NI4 01 2003 巾 -मनन ह DATA 496 J SUB BIT SYNC (87 300KC IN <del>€5</del> ن لار + ĝ ÿ

# 5.3.4 Test Results

The digital portion of the Control Data Modulator imposes no speed or loading problems for the logic family and is easily implemented as shown in Figure 5-24.

Original calculations on the output filter did not show that the third harmonic of 56 kHz required additional attenuation above its attenuated component in the square wave itself. Subsequent calculations have shown that the 56 kHz component requires 21 db of attenuation. This is approximately 10 db greater than the present filter provides.

Evaluation by the System Analyst resulted in the decision that this particular discrepancy did not warrant redesign at this time.

The Control Data Modulator requires 155 mw of power out of the 3.5 vdc supply.

# 5.4 TRACKING TRANSMITTER

The transmitter is the space vehicle portion of the S-band link between the vehicle and ground stations. The modulation on this link is the range modulation signal to be demodulated by all ground stations which have been acquired during that orbital pass.

The transmitter is capable of operating over the entire output frequency range of 2200 MHz to 2450 MHz. The output frequency is varied by changing the input carrier frequency reference and by retuning where necessary. The input frequency can be varied in steps of 6.25 kHz and the output frequency which is the 64th harmonic of the input frequency is varied in steps of 400 kHz. This provides approximately 625 separate channels.

The output frequency designated for the transmitter is 2214 MHz at a power level of 10 watts. The carrier is biphase modulated  $(\pm 11.25^{\circ})$  with the PN range code at 277 MHz and multiplied times eight to 2214 MHz with  $\pm 90^{\circ}$  phase modulation. Figures 5-6 and 5-25 are photographs of the AROD Vehicle Tracking Transmitter.

Figure 5-25. Phase Modulation and Power Amplifier of Vehicle Tracking Transmitter

The transmitter was developed as three separate entities:

1. Phase Modulator and Power Amplifier

- 2. X8 S-Band Frequency Multiplier

- 3. TWTA.

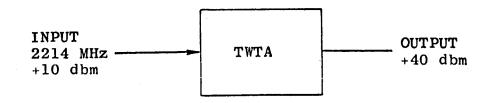

The transmitter (with the exception of the TWTA) is packaged in a frame assembly physically located in Case 1 of the vehicleborne equipment. The outside dimensions of the frame are  $0.9" \times$ 4" x 6.2" and the weight is 399 grams. The 2214 MHz signal is amplified to +10 dbm in the frame assembly and then delivered to the TWTA assembly which is a separate package where the signal is amplified to +40 dbm. The frame assembly operates from the system supply voltages (-10 v at 90 ma and +10 v at 40 ma) consuming a total power of 1.3 watts. The Hughes TWTA has its own separate power supply which operates from 60 cps AC at 110 volts.

Complete specifications of the transmitter can be found in Document No. 12-25564F, Electrical Performance Requirements for the Vehicle Tracking Transmitter.

The Hughes TWTA is an interim device for the present AROD configuration and was a subcontracted item.

## 5.4.1 Technical Approach

The Vehicle Tracking Transmitter performs the following functions:

- 1. Multiplies the output frequency of a VHF VCO up to S-band

- 2. Provides biphase modulation of the carrier, and

- 3. Amplifies the modulated signal up to a level of approximately 10 watts.

Figure 5-26 is the basic block diagram of the transmitter.

### 5.4.2 Functional Description

The following are brief functional descriptions of each of the major divisions of the Vehicle Tracking Transmitter in order of the serial signal flow. The divisions consist of the X8 UHF

MODULATOR LIMITER BUFFER AMP N N BUFFER MULTIPLIER RANGE CODE INPUT X2 +20 dbm 553.5 MHz FILTER 275.75 MHz 2214 MHz +40 dbm MULTIPLIER X4 -10 dbm 276.75 MHz . X8 UHF MULTIPLIER FREQUENCY SYNTHESIZER 2214 MHz FILTER TWTA 2214 MHz +10 dbm 34.59375 NHz - 10 INPUT

Figure 5-26. Vehicle Tracking Transmitter, Block Diagram

5-43

LOCATED IN

VCO

ďbm

Multiplier, Phase Modulator, Limiter Amplifier, X2 Multiplier, X4 Multiplier, and Traveling Wave Tube Amplifier.

5.4.2.1 X8 UHF Multiplier (Located in the Frequency Synthesizer)

The functional breakdown of the multiplier is given below.

This multiplier is a broad band multiplier utilizing the Differential Amplifiers (A-44) and a pair of diodes to function as a full wave rectifier. This technique provides for a broad band frequency multiplication requiring a minimum of filtering. Additional filtering of the output signal is provided in the phase modulator section with a two pole helical resonator.

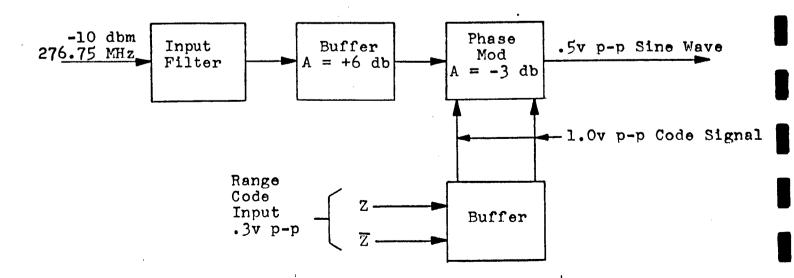

5.4.2.2 Phase Modulator

The phase modulator input circuit includes a two pole helical resonator filter and a buffer stage before the phase modulation. The input filter is required to improve the spectral purity of the incoming signal from the X8 UHF Multiplier. The required phase modulation at this point is  $\pm 11.25^{\circ}$ . This modulation index gives the desired  $\pm 90^{\circ}$  after a multiplication factor of eight as required to increase the frequency to S-band.

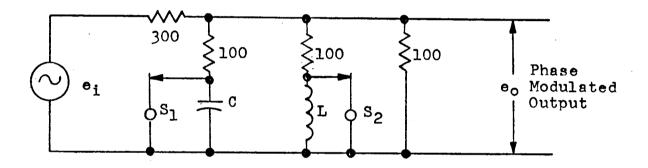

The basic technique employed for the biphase modulation is given below. The impedances are approximate values that appear in the actual circuit.

$S_1$  and  $S_2$  are hot carrier diode switches operated such that one switch is open while the other switch is closed.  $S_1$  and  $S_2$ are operated such that the switching transient resulting in the abrupt change in current in the diodes is essentially cancelled out minimizing the distortion caused by the switching transient. The values of L and C are chosen to give the required phase modulation index with a minimum of amplitude components.

This technique of modulating at a low frequency and at a low power level is fairly easy to implement and the required stability and speed are easily achieved. As of mid-1965, no technique existed for modulation at a higher power level and at a higher frequency so that the required switching speed could be accomplished.

If it has been possible to perform the modulation at this higher power and frequency, the signal handling after modulation

would have been only a minor problem. With the technique employed the modulation was relatively simple but the signal handling after modulation became difficult. The problems arise from the fact that a modulation bandwidth of greater than 40 MHz must be preserved through a two-stage amplifier, a X2 transistor multiplier and a X4 diode multiplier. The bandwidth of this signal processing chain must be such that the spectral distortion is very low over the required information bandwidth.

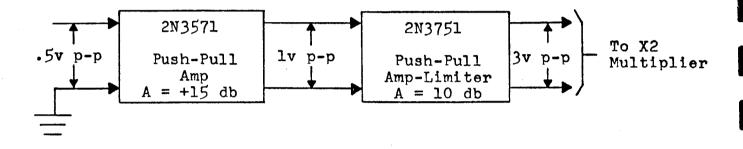

5.4.2.3 Limiter Amplifier

This section consists of a two-stage push-pull amplifier. The push-pull arrangement is used to give a very broad band amplifier with low distortion limiting characteristics. The actual gain of the two stages when operated in the linear mode is approximately 35 db.

The limiter is required to insure that no amplitude distortion is present on the input to the step recovery diode. The amplitude distortion occurs during the time the phase is changing from the one state to the zero state (or zero to one) due to the finite bandwidth of the input matching network.

5.4.2.4 X2 Multiplier

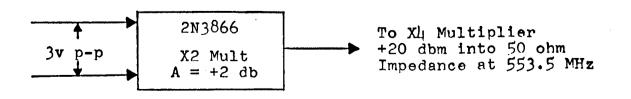

This multiplier is a broad band push-push doubler. The pushpush arrangement provides an output with the major component of power at the second harmonic of the input frequency. The fundamental component appearing on the output is approximately 30 db below the desired harmonic.

5.4.2.5 X4 Multiplier

The input matching network consists of a two-pole, low pass filter with a cut off frequency of approximately 700 MHz followed by a  $\pi$ -section matching network. The overall bandwidth of the matching network and input filter is approximately 20% of the center frequency.

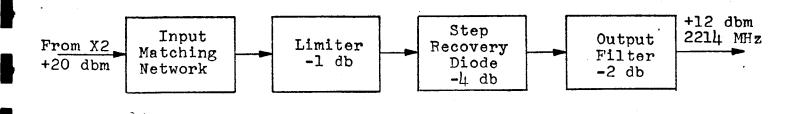

The frequency multiplication is accomplished with a HPA 0241 step recovery diode with self bias. The desired harmonic (4th) is selected with a 4-pole, strip-line filter with approximately 4% bandwidth. The strip line filter elements are capacitive loaded on the high impedance end to suppress odd order modes and to provide for tuning of the filter to the desired center frequency.

5.4.2.6 Traveling Wave Tube Amplifier

This amplifier is a broad band traveling-wave tube amplifier having a linear gain of over 30 db and a bandwidth of greater than

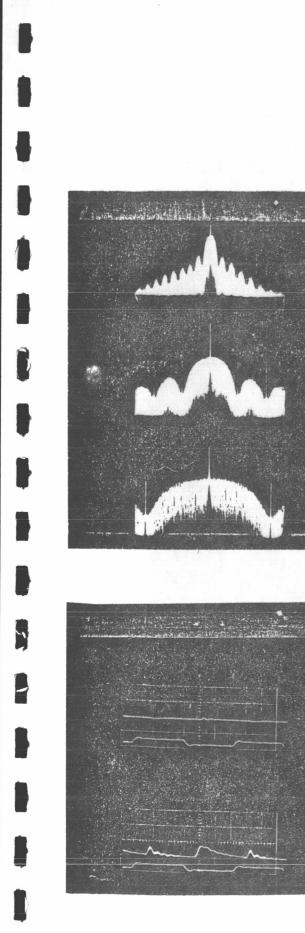

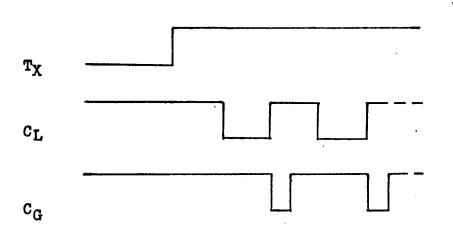

100 MHz. The +10 dbm input signal to the TWTA from the X4 Multiplier is sufficient to drive the amplifier into limiting; the small amount of residual AM occurring during the phase modulation switching is removed by the limiting action of the TWTA. The amplitude wave form is shown in Figure 5-27.

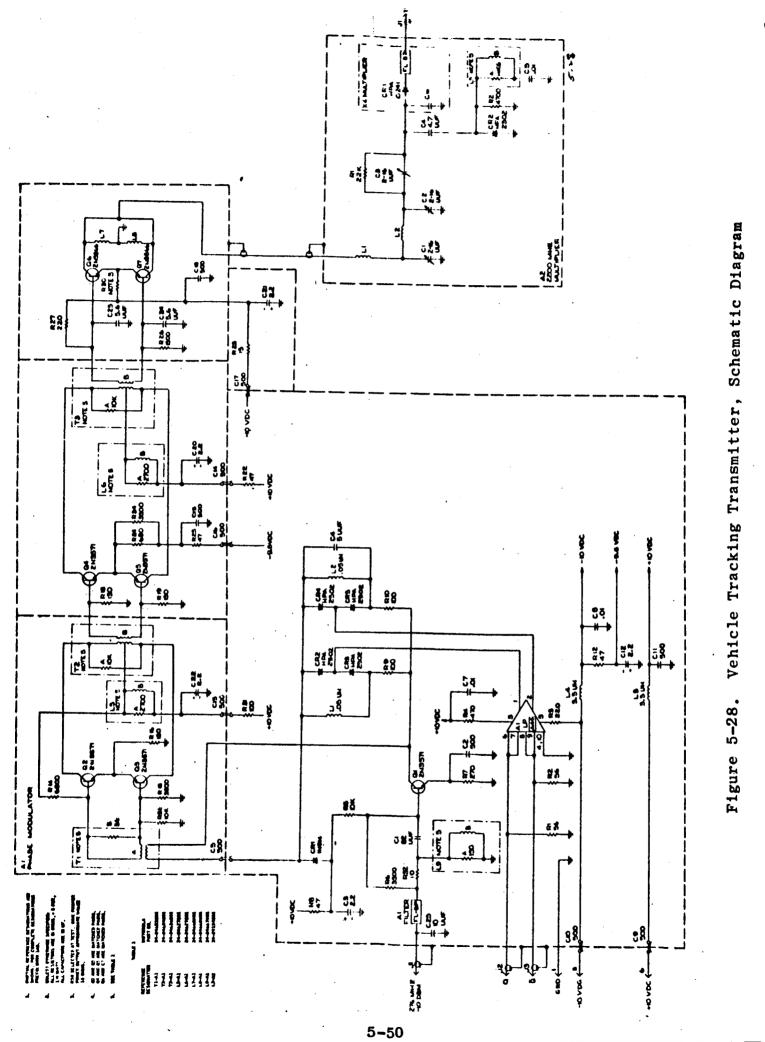

Figure 5-28 is an electrical schematic diagram of the Vehicle Tracking Transmitter.

# 5.4.3 Test Results

Figures 5-29 through 5-36 give a comparison of the Vehicle Tracking Transmitter performance versus the design specifications and with the breadboard transmitter performance. The Electrical Test Procedure for the Vehicle Tracking Transmitter is contained in Document No. 12-24602G.

### 5.5 VEHICLE TRACKING RECEIVER

The Vehicle Tracking Receiver is composed of four subdivisions described in the following sections. These are:

1. Frequency Converter, common to all channels

2. Carrier Tracking Loop

3. Modulation Tracking Loop

4. Receiver Code Control.

Items 2 and 3 are described under the common heading of Tracking Subsection.

Reference 6 provides a comprehensive report on the design and evaluation of the prototype Vehicle Tracking Receiver. The reader should refer to that report for the overall receiver design information.

### 5.5.1 AROD Frequency Converters

X

This section is a final summary of design, fabrication and testing of both the vehicle and transponder frequency converters.<sup>1</sup> It contains the initial project objectives, what was accomplished,

FINAL OUTPUT OF PHASE MODULATOR AND TWTA WITH PN RANGE CODE MODULATION

Horizontal = 100 MHz Full Scale Vertical = 70 db Full Scale

Horizontal = 30 MHz Full Scale Vertical = 70 db Full Scale

Horizontal = 16 MHz Full Scale Vertical = 70 db Full Scale

AMPLITUDE MODULATION - TOP TRACE MODULATION INPUT - BOTTOM TRACE

Amplitude modulation on output of TWTA (1 db/division vertical, 50 nanoseconds/division horizontal)

Amplitude modulation on output of phase modulator and X8 multiplier (Same scale as above)

Figure 5-27. TWTA Waveforms

,

ZO X ZÖ PER INCH

ALAE 12 214 5-35. Ŷ G VENTEL TIM P 4 D: EUGENE DIETZGEN CO. Made in U. S. A. :11 [iiii 111 114 in l 441 340-20 DIETZGEN GRAPH PAPER 20 X 20 PER INCH 111 ci z 2-02 3 ¢ 37 4) 3 15 7.11.100 (W80) DOMER

ΞH

ê

-0

\$

7

0

Ðo

ś

4

0

111111

Ĩ Ø

J D H

the conclusions to be drawn, and finally recommendations directed toward possible future work in this area.

# 5.5.1.1 Objectives

The objective was to design, develop, fabricate, test, and deliver, complete with documentation and drawings, one vehicle (L-band) and three station (S-band) engineering model RF converters for the AROD system. The main objectives were low noise figures, wide bandwidth, good linearity, and minimum size and weight. Some of the more important initial objectives were:

| 1.  | Frequency:                           | Vehicle 1800 MHz<br>Station 2214 MHz                                                                                                                   |  |  |  |  |  |  |  |

|-----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 2.  | Local Oscillator<br>Input Frequency: | Vehicle 217.7 MHz<br>Station 268.8 MHz                                                                                                                 |  |  |  |  |  |  |  |

| 3.  | Intermediate<br>Frequency:           | Vehicle 58 MHz<br>Station 63.6 MHz                                                                                                                     |  |  |  |  |  |  |  |

| 4.  | IF Bandwidth (3 db):                 | 30 MHz minimum, 50 MHz maximum                                                                                                                         |  |  |  |  |  |  |  |

| 5.  | Conversion Gain:                     | +22 db $\pm$ 2 db (includes preselector loss in vehicle converter).                                                                                    |  |  |  |  |  |  |  |

| 6.  | Dynamic Range:                       | -130 dbm to -60 dbm                                                                                                                                    |  |  |  |  |  |  |  |

| 7.  | Intermodulation:                     | $2f_1 - f_2$ and $2f_2 - f_1 > 70$ db below<br>$f_1$ or $f_2$ where $f_1$ and $f_2$ are in the<br>passband and have a power level of<br>$\leq -60$ dbm |  |  |  |  |  |  |  |

| 8.  | Noise Figure:                        | 8.5 db with 0.5 db preselector<br>insertion loss included (objective<br>6.5 db)                                                                        |  |  |  |  |  |  |  |

| 9.  | Signal Input VSWR:                   | 1.2:1 maximum                                                                                                                                          |  |  |  |  |  |  |  |

| 10. | Local Oscillator<br>Leakage:         | -20 dbm maximum                                                                                                                                        |  |  |  |  |  |  |  |

- 11. Local Oscillator +16 dbm ±3 db

Input Power:

- 12. Local Oscillator 1.5:1 maximum Input VSWR:

13. IF Output Impedance: 50 ±10 ±j10 ohms

14. IF Output Linearity: Linear ±1 db up to -15 dbm power output

5.5.1.2 Design and Development

Individual circuits for both the vehicle and station converters were independently designed, breadboarded, and tested. Following completion of these design phases the individual circuits were assembled into breadboard converters. The breadboard converters were also tested and delivered to the project. The deliverable converters were built as integrated units using these breadboards as models. No intermediate prototypes were constructed in the interest of both time and cost.

# Single Stage Step Recovery Diode Multiplier

The frequency multiplier was designed to use a Microwave Associates MA4752 step recovery diode. A number of different HPA and Microwave Associates' step recovery diodes were tested and the MA4752 chosen as the most efficient. Conventional varactor diodes were not considered because of the multiplier size limitation and their poor high order multiplication efficiency. The design of the output bandpass filter and input low pass filter both emphasized small size. The multipliers were designed to deliver a nominal 4 to 5 mw as recommended by the mixer diode manufacturer. A small lumped constant circuit on the input was determined to be necessary to assure satisfactory operation when operated with a bandpass filter connected to the multiplier input rather than a 50 ohm generator.

# Balanced Hot Carrier Diode Mixer

Both a rat race and a directional coupler hybrid were considered in the mixer design. A 3 db directional coupler was selected since this hybrid is approximately 6 times smaller than a rat race hybrid.

The directional coupler hybrid assures a good impedance match to the diode but requires tuning screws to improve the isolation. A rat race hybrid would assure good isolation but require tuning screws for a good impedance match. Since both a good impedance match and high isolation was required, the directional coupler hybrid was chosen.

Hot carrier diodes were selected as the mixer diode because of their extremely low noise properties and low conversion loss. Optimum noise figure is obtained with about 2 to 3 mw LO drive per diode. At the time the design was done, only one hot carrier diode was available (the HPA 2350). This diode proved satisfactory and is therefore used in the AROD converters. Texas Instruments has since come out with a hot carrier diode designated the Al024 which should be interchangeable with the HPA 2350. Data was taken on several 2350 diodes at various LO drive levels over a frequency range of 1600-2400 MHz. The mixer hybrid and diode mounts were designed to give broadband operation from 1600-2400 MHz.

# Low Noise Transistor IF Preamp

Both cascade and cascode circuits were studied for the IF preamp. The cascode configuration was chosen mainly because of its superior stability as a function of the operating temperature range. The initial design used Motorola 2N3783 transistors with a rated noise figure of 2.2 db maximum. However a problem developed with delivery of these units and the design was modified to use the KMC 2021 with a rated noise figure of 1.5 db maximum. Considerable effort was necessary to achieve gain stability in the small package size required. The wide bandwidth was finally achieved by use of a ferrite core transformer on the IF input to match the mixer impedance (approx. 50  $\Omega$ ) to the required impedance for best IF noise figure (approx. 400  $\Omega$ ). A powdered iron

core was used in the IF output to match approximately 3K ohms to 50 ohms. The design uses a KMC 2021 in the first half of the cascode circuit and a 2N918 in the second half.

# 5.5.1.3 Final Results

Three station converters and one vehicle converter were fabricated. The performance data on the three station converters is very similar and the vehicle converter data is quite similar to the station converter data. However, during the development of these converters it became apparent that certain of the initial converter specifications should be changed for one reason or another. A revised converter specification was written and released. The delivered converters meet these specifications with the exception of two areas. First, the converter conversion gain is typically a little low (1 dB), and the vehicle converter LO leakage is as much as 8 dB higher than the revised specification although it is still 7 dB better than the initial specification. In other words, the present specifications represent realistic values for the existing converters except for the conversion gain specification which should be reduced to  $21 \text{ dB} \pm 2 \text{ dB}$  and the vehicle converter LO leakage specification which should be changed to specify a level of less than -25 dbm. With'the exceptions noted above, the delivered converters meet all the present specifications. However certain discrepancies do exist in the diplexer performance. Primarily, the receive channel VSWR on the vehicle converter diplexer is high. This could be improved by a slight redesign of the diplexer printed circuit board. However the cost to modify this unit was not considered to be worth the performance improvement.

5.5.1.4 Theory of Operation

Figure 5-37 shows a general block diagram for both the station and vehicle converters. The two converters are basically very similar except the vehicle converter has a diplexer as part of the unit while the station converter does not. The VHF LO input signal frequency is multiplied eight times by a single stage step recovery

5-60

ł

diode multiplier, whereupon it is then used as the LO drive signal to a balanced hot carrier diode mixer. Multiplier power output is a nominal 4 mw and the mixer output is connected to a low noise (1.5 dB NF) wideband (30 Mc min.) IF preamplifier. The IF center frequency is approximately 60 Mc. This mixer-IF preamp combination provides a nominal 7 dB noise figure excluding the diplexer insertion loss. Overall conversion gain from the RF signal input to the IF output is approximately 20 dB. The vehicle converter diplexer allows the antenna to be used by both receiver and transmitter simultaneously. It provides the receive channel with more than 100 dB isolation from the transmitter channel and the transmitter channel with more than 50 dB isolation from the receiver channel.

The converters can be checked for proper operation by a number of different measurements, however, they are all rather complicated and somewhat inconclusive individually. Probably the two most meaningful measurements are converter noise figure, which should be 6.5 to 8.5 dB, and overall conversion gain, which should be 21 dB ±2 dB. The step recovery diode frequency multiplier can be checked independently by sampling the multiplier output on a spectrum analyzer through the multiplier test point connector. No spurious responses should be visible, however care should be taken to insure that what appears to be spurious frequencies of the multiplier are in fact spurious frequencies of the multiplier and not spurious responses of the spectrum analyzer or frequency related harmonics of the multiplier output. If for any reason a converter should ever perform improperly no attempt should be made to either realign or repair the unit. The unit should be returned to its source for proper repair and alignment.

5.5.1.5 Conclusions

Three station and one vehicle frequency converter have been designed, developed, and fabricated for delivery to NASA. They are smaller and lighter weight than any previously known units.

The vehicle converter weighs approximately 15 oz. and the station converters approximately  $9\frac{1}{2}$  oz. The converters make use of state of the art semiconductors such as the step recovery diode, hot carrier diode, and low noise transistors along with advanced miniaturization techniques. However, these units are difficult to assemble. A few minor design changes and modifications would greatly improve their ease of reproducibility and assembly time. The design has been well documented and with some design improvements would enable production of an advanced miniaturized, low noise converter assembly.

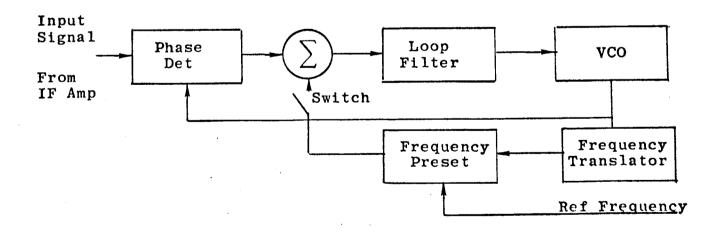

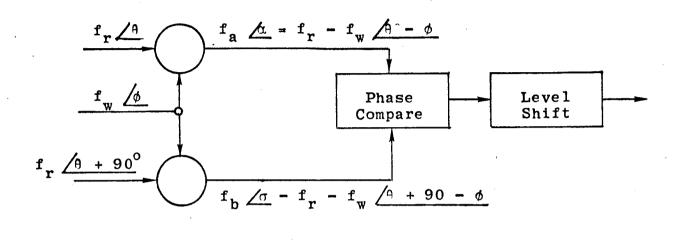

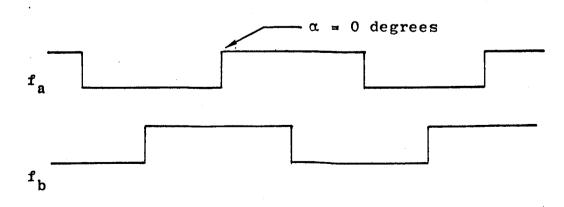

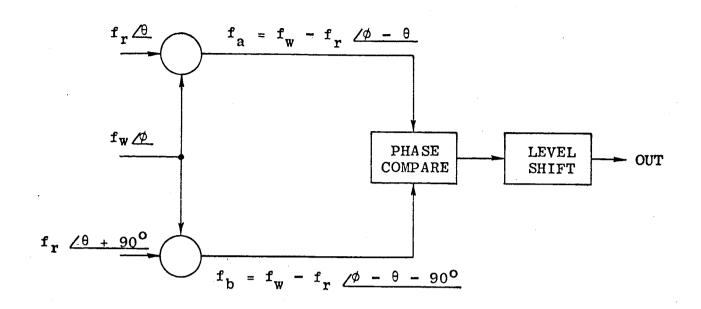

### 5.5.2 Tracking Subsection

This section describes the implementation of the Vehicle Tracking Subsection which is part of the Vehicle Tracking Receiver in the Airborne Range and Orbit Determination (AROD) system. The purpose of this report is to complement reference 6 AROD Vehicle Tracking Receiver Design. This is a final engineering report which delineates system constraints imposed on the receiver design and presents the functional implementation, salient design features, and module test results.

The Vehicle Tracking Receiver is the on-board terminal of the S-band up-link. Its function is to communicate simultaneously with up to four transponder ground stations.

The receiver has a common RF converter and distribution amplifier followed by four Vehicle Tracking Subsections operating in parallel. Each Tracking Subsection is identical in implementation with the exception of the predetection filter center frequency. Channel offsetting is done with four different coherent reference frequencies.

Each Tracking Subsection interfaces with a receiver code control subsection that provides the demodulation signals and programmed operational commands. All four Tracking Subsections, or receiver channels as also referred to, interface with a common vehicle frequency synthesizer subsystem that provides coherent reference signals.

A Vehicle Tracking Subsection consists of two module frame subassemblies located in Case 2 of the airborne equipment. The two frame subassemblies have been named Carrier Tracking Loop (CTL) and Modulation Tracking Loop (MTL) for the respective subsystem functions performed.

In this report, a functional block diagram is discussed in Section 5.5.2.3 to assist in determining the location and usage of circuits which are packaged in modules on a subsection frame assembly. Sections 5.5.2.5 and 5.5.2.6 contain the theory of operation, on a module basis, defining circuit operation and design goals with references to the circuit schematic diagrams. Following each module description, test data is presented in graphical form with data superimposed from several modules of the same type to show normal production tolerances. This data was obtained following the test procedures outlined in the referenced documents test specifications.

5.5.2.1 Tracking Subsection Function and Requirements

The Tracking Subsection provides amplification, demodulation and coherent tracking of the receiver input signal. The receiver signal is a balanced-modulated, pseudo-noise coded, suppressed carrier spectrum. This spectrum is centered at approximately 58 MHz at the Tracking Subsection input and the signal level varies between -100 dbm to -40 dbm. Both acquisition and tracking are performed over this dynamic range.

The pseudo-noise (PN) sequence is a combination of a high and a low speed code. The high speed code is called H-code and the low speed code is called L-code. There are two main phaselocked loops used to acquire coherent tracking in minimum time. These loops are called the Carrier Tracking Loop and the Modulation Tracking Loop or Range Loop. When locked to the transmitted signal, the Tracking Subsection provides the following outputs for use by other subsections of the AROD system.

| Output Signal | Function Provided |

|---------------|-------------------|

|               |                   |

| 3.2 MHz ±8D              | Doppler Signal for Velocity Measurement |

|--------------------------|-----------------------------------------|

| 12.8 MHz                 | Clock for PN Code Generator             |

| $A_L$ Amplified          | Low Speed Code Lock Indication          |

| A <sub>H</sub> Amplified | High Speed Code Lock Indication         |

| Data                     | Binary Data Output                      |

To provide the tracking and demodulation function, the subsection requires the following input signals.

| Input Signal   | Source                           | Usage                              |

|----------------|----------------------------------|------------------------------------|

| Signal Input   | 58 MHz Distribution Amplifier    | Carrier and Range<br>tracking      |

| GI             | Vehicle Receiver Code<br>Control | Inhibit carrier loop               |

| G <sub>C</sub> | Vehicle Receiver Code<br>Control | Carrier loop<br>demodulator gating |

| V-0 + V-1      | Vehicle Receiver Code<br>Control | Carrier preset inhibit             |