# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

NASA CR-73262 Available to the Public

**RESEARCH REPORT**

MULTIPAC, A MULTIPLE POOL PROCESSOR AND COMPUTER FOR A SPACECRAFT CENTRAL DATA SYSTEM

> By E. Cohler T. Baker

G. Cummings

R. South

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

MARCH - 1969

Prepared under Contract No. NAS2-3255 by APPLIED RESEARCH LABORATORY SYLVANIA ELECTRONIC SYSTEMS An Operating Group of Sylvania Electric Products, Inc. 40 Sylvan Road, Waltham, Massachusetts 02154

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION AMES RESEARCH CENTER MOFFETT FIELD, CALIFORNIA 94035

NASA CR-73262 Available to the Public

#### **RESEARCH REPORT**

# MULTIPAC, A MULTIPLE PGOL PROCESSOR AND COMPUTER FOR A SPACECRAFT CENTRAL DATA SYSTEM

- By E. Cohler

- T. Baker

- G. Cummings

- R. South

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

,

ł

MARCH- 1969

Prepared under Contract No. NAS2-3255 by APPLIED RESEARCH LABORATORY SYLVANIA ELECTRONIC SYSTEMS An Operating Group of Sylvania Electric Products, Inc. 40 Sylvan Road, Waltham, Massachusetts 02154

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION AMES RESEARCH CENTER MOFFETT FIELD, CALIFORNIA 94035

# PRECEDING PAGE BLANK NOT FILMED.

## TABLE OF CONTENTS

| Secti | ion                                                              | <u>Page</u>  |

|-------|------------------------------------------------------------------|--------------|

|       | SUMMARY                                                          |              |

| 1.0   | INTRODUCTION                                                     |              |

| 2.0   | THE MULTIPAC CONCEPT AND ITS EVOLUTION                           |              |

| 3.0   | SYSTEM DESCRIPTION                                               |              |

|       | 3.1 Data Flow                                                    |              |

|       | 3.1.1 Address switching                                          |              |

|       | 3.1.2 The I/O system                                             | .15          |

|       | 3.1.3 Telemetry Output                                           | .22          |

|       | 3.1.4 Command inputs                                             |              |

|       | 3.2 Control Functions                                            |              |

|       | 3.2.1 Program selection                                          |              |

|       | 3.2.2 Instruction list                                           |              |

|       | 3.2.3 Command link override                                      |              |

|       | 3.2.4 Interrupts                                                 | .32          |

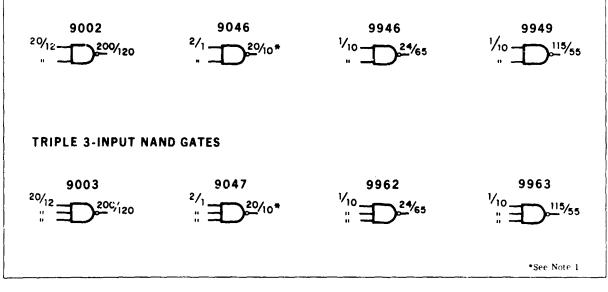

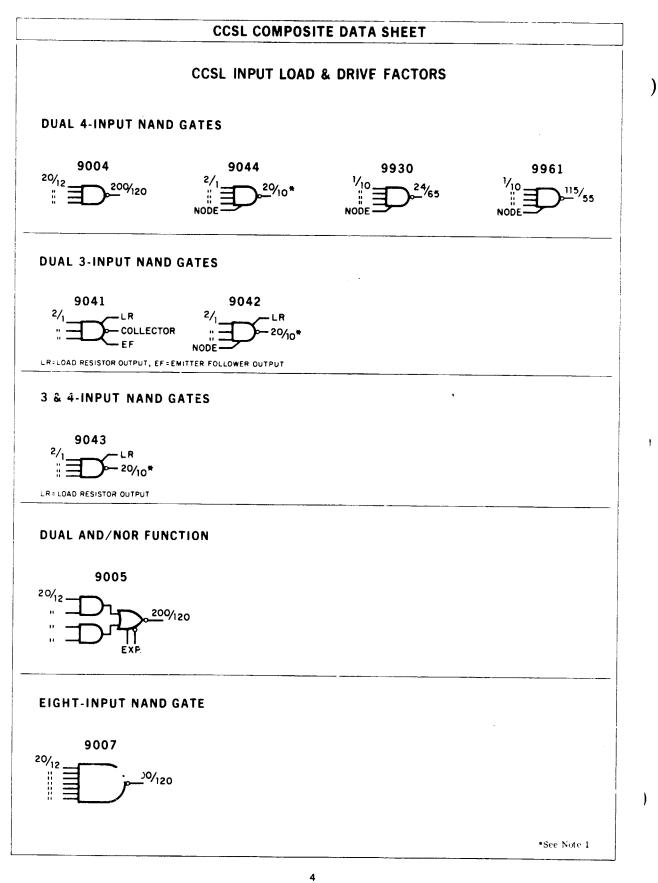

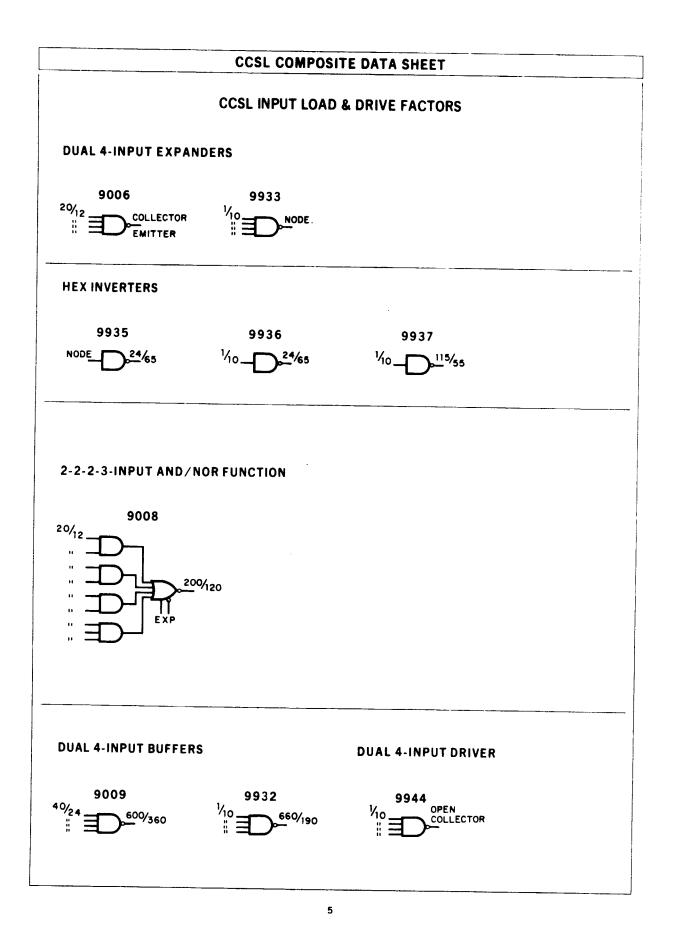

| 4.0   | DESCRIPTION OF THE MULTIPAC INTEGRATED CIRCUIT LOGIC DESIGN      | .34          |

|       | 4.1 Circuitry                                                    | .34          |

|       | 4.1.1 Logic circuits                                             | .34          |

|       | 4.1.2 Memory circuits                                            | • <b>3</b> 0 |

|       | 4.1.3         Special circuits           4.2         Parts Count | . 30         |

|       | 4.2 Parts Count                                                  |              |

|       | 4.3 weight                                                       |              |

|       | 4.5 Power                                                        |              |

|       | 4.6 Speed                                                        |              |

| 5.0   | RELIABILITY                                                      |              |

| 0.0   | 5.1 Individual Module Reliability                                |              |

|       | 5.2 Reliability of Groups of Interchangeable Modules             |              |

|       | 5.3 Reliability of the I/O, Telemetry and Command Interfaces     |              |

|       | 5.4 System Reliability                                           |              |

| 6.0   | PROGRAMMING                                                      |              |

|       | 6.1 Timing                                                       |              |

|       | 6.2 Multiplication                                               |              |

|       | 6.3 Subroutine Call                                              |              |

|       | 6.4 Program Modification                                         |              |

|       | 6.5 Addressable Registers                                        |              |

|       | 6.6 Ground Software                                              | .69          |

| 7.0   | REPROGRAMMING AROUND FAILURES                                    | .70          |

|       | 7.1 Complete Failure of a Register                               | .70          |

|       | 7.2 Complete Failure of a Logic Unit                             |              |

|       | 7.3 Memory Failures                                              |              |

|       | 7.3.1 Complete failure                                           |              |

|       | 7.3.2 Partial failures                                           | .73          |

# TABLE OF CONTENTS --- Continued

2

.

.

-

| Section | <u>n</u>                         |                                                                                                                                                                                                                                   | Page                                                        |

|---------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 7.      | 7.4.1                            | ramming Methods<br>Diagnostic tests<br>Timing                                                                                                                                                                                     | 74                                                          |

| 8.0 C   |                                  | AND RECOMMENDATIONS FOR FUTURE IMPLEMENTATION                                                                                                                                                                                     |                                                             |

|         | 8.1.1<br>8.1.2<br>8.1.3<br>8.1.4 | sions<br>Speed and power<br>Weight and volume<br>Reliability<br>Programming<br>ended Changes<br>Use of macroinstructions<br>Elimination of base registers and two-level<br>switching<br>System operation with recommended changes | · .77<br>· .77<br>· .77<br>· .78<br>· .78<br>· .78<br>· .78 |

|         |                                  |                                                                                                                                                                                                                                   |                                                             |

### Appendix

| Α | DESCRIPTION OF LOGIC BY MODULE            |

|---|-------------------------------------------|

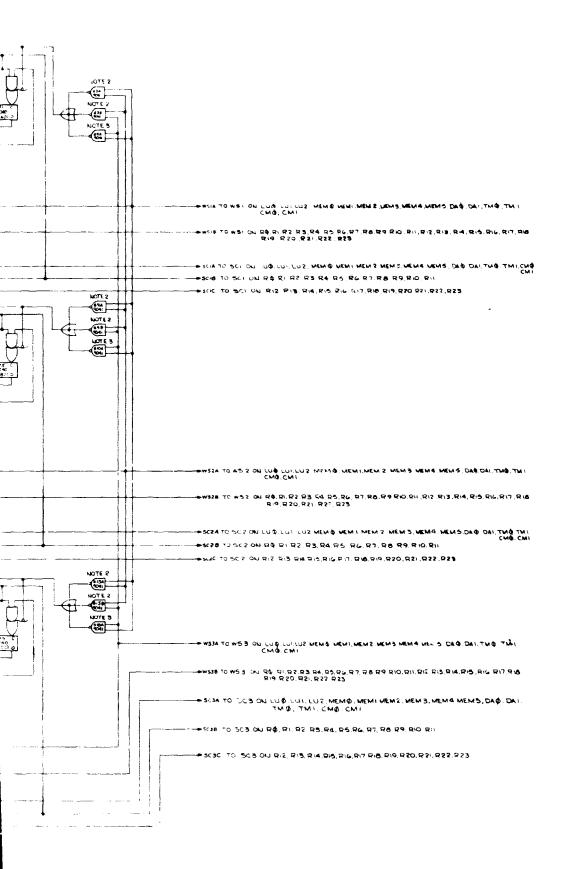

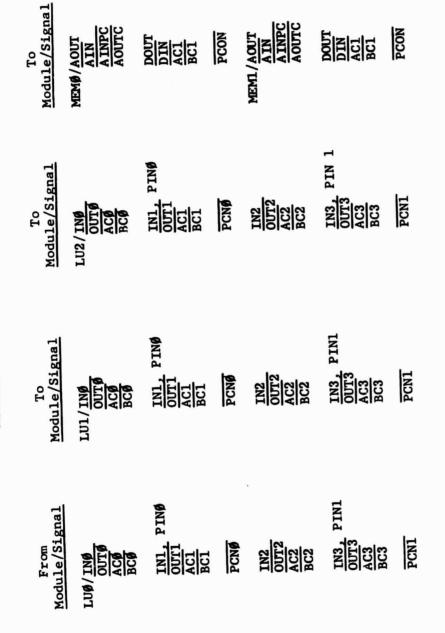

| В | SYSTEM INTERCONNECTION OF MODULES         |

| С | SPECIFICATIONS FOR INTEGRATED CIRCUITS157 |

|   | REFERENCES                                |

## LIST OF ILLUSTRATIONS

.

| Figure     |                                                               | Page |

|------------|---------------------------------------------------------------|------|

| 1          | Simplified Block Diagram of MULTIPAC                          | 4    |

| 2          | Original MULTIPAC Concept                                     | 7    |

| 3          | Data Flow in Original MULTIPAC Concept                        | 8    |

| 4          | MULTIPAC Block Diagram                                        | 13   |

| 5          | MULTIPAC Address Allocations                                  | 16   |

| 6          | MULTIPAC Telemetry and Command Interface                      | 23   |

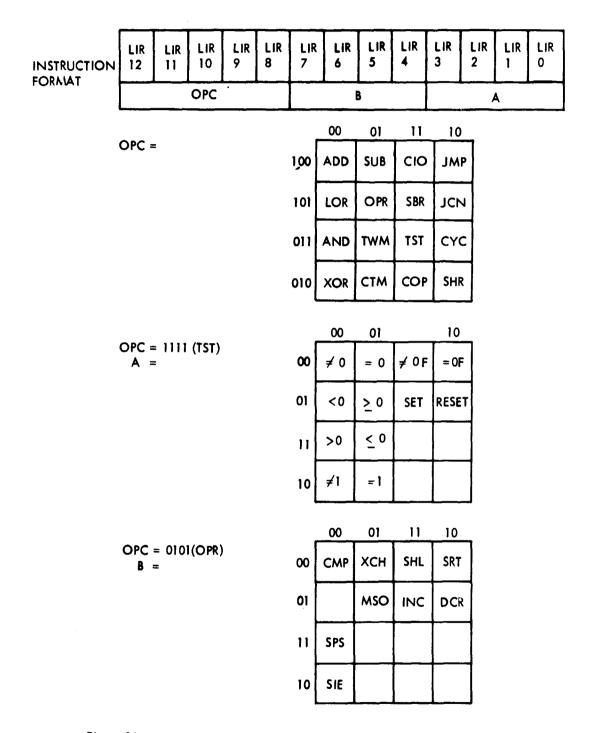

| 7          | Instruction Format                                            | 29   |

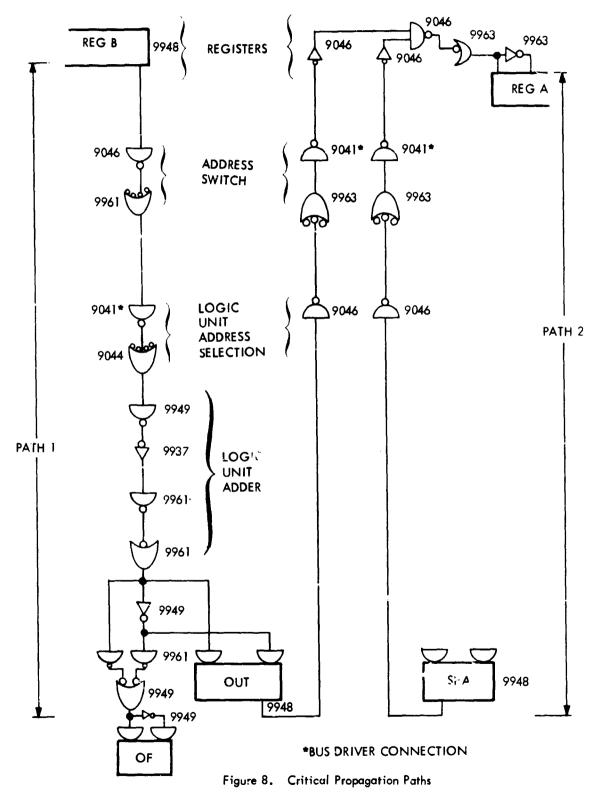

| 8          | Critical Propagation Paths                                    | 39   |

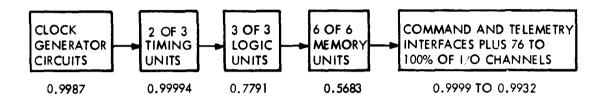

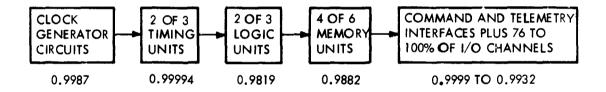

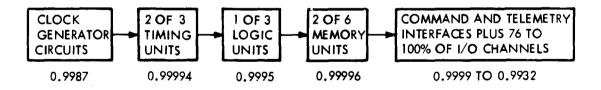

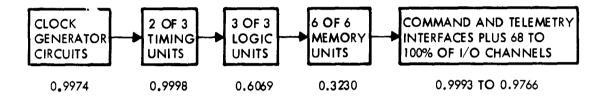

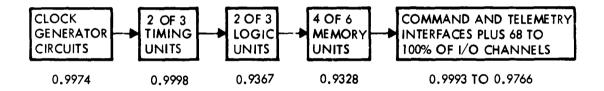

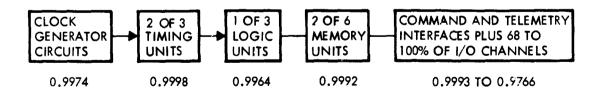

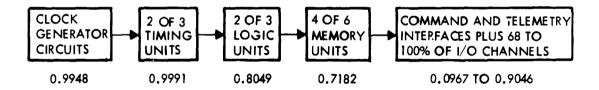

| 9          | Six-Month System Reliability Models                           | 45   |

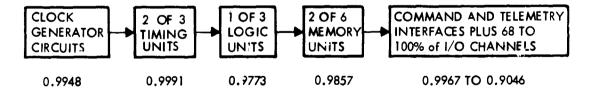

| 10         | Twelve-Month System Reliability Models                        | 46   |

| 11         | Twenty-Four Month System Reliability Models                   | 47   |

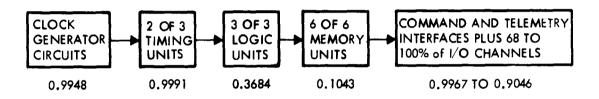

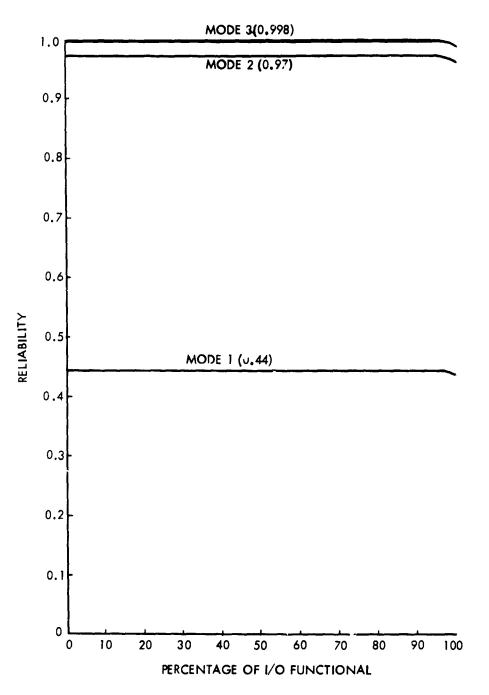

| 1 <b>2</b> | Six-Month System Reliability                                  | 48   |

| 13         | Twelve-Month System Reliability                               | 49   |

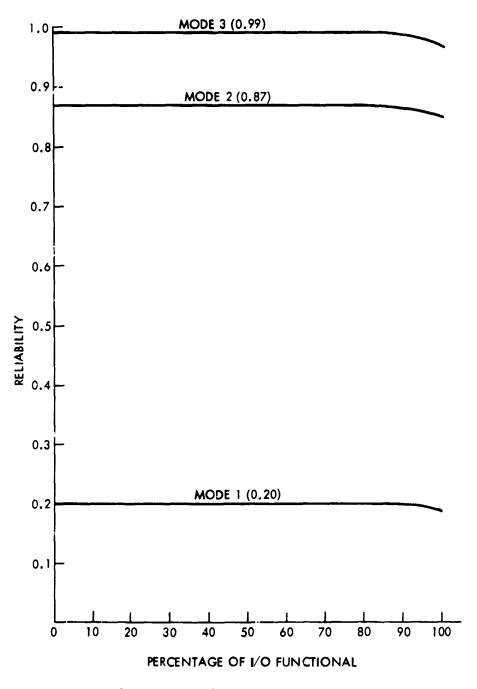

| 14         | Twenty-Four Month System Reliability                          | 50   |

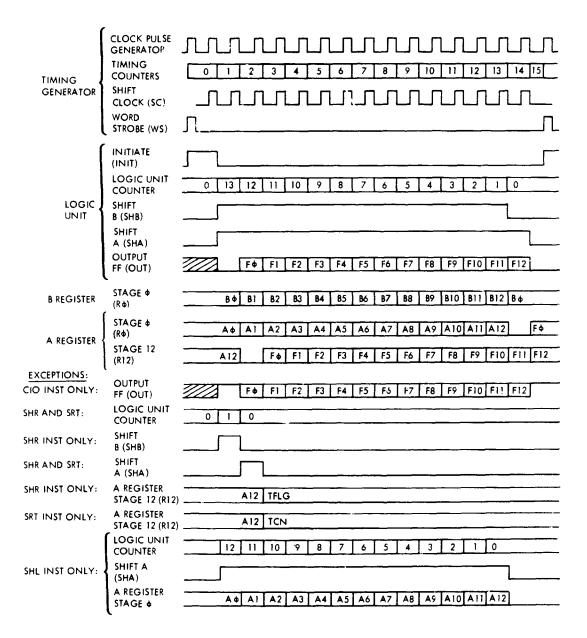

| 15         | MULTIPAC Timing Diagram                                       | 86   |

| 16         | Instruction Format and Karnaugh Mapping of Instruction Coding | 87   |

# PRECEDING PAGE BLANK NOT FILMED.

## LIST OF TABLES

| <u>Table</u> |                                                                               | Page       |

|--------------|-------------------------------------------------------------------------------|------------|

| 1            | SCIENCE INTERFACE LINES                                                       | 1 <b>7</b> |

| 2            | ENGINEERING INTERFACE LINES                                                   | 18         |

| 3            | I/O CHANNELS REQUIRED                                                         | 19         |

| 4            | MULTIPAC INSTRUCTION LIST                                                     | 25         |

| 5            | MAXIMUM CIRCUIT PROPAGATION DELAYS                                            | 41         |

| 6            | WORST CASE PROPAGATION DELAYS FOR CRITICAL PATHS                              | 42         |

| 7            | MODULE RELIABILITY                                                            | 5 <b>2</b> |

| 8            | RELIABILITY FIGURES FOR GROUPS OF INTERCHANGEABLE<br>MODULES                  | 53         |

| 9            | CRITERIA FOR SUCCESS OF THE I/O, TELEMETRY, AND COMMAND INTERFACES            | 56         |

| 10           | MONTE CARLO RELIABILITY OF I/O, TELEMETRY, AND COMMAND INTERFACES (6 MONTHS)  | 57         |

| 11           | MONTE CARLO RELIABILITY OF I/O, TELEMETRY, AND COMMAND INTERFACES (12 MONTHS) | 58         |

| 12           | MONTE CARLO RELIABILITY OF I/O, TELEMETRY, AND COMMAND INTERFACES (24 MONTHS) | 59         |

| 13           | A/D CONVERSION ROUTINE                                                        | 61         |

| 14           | INPUTTING ROUTINE                                                             | 62         |

| 15           | OUTPUTTING ROUTINE                                                            | 64         |

| 16           | LIST OF MACROINSTRUCTIONS                                                     | 83         |

| 17           | EQUATIONS OF LOGIC UNIT OUTPUT                                                | 90         |

| 18           | TRUTH TABLE OF LOGIC UNIT CONTROL SIGNALS                                     | 92         |

## LIST OF TABLES. -- Continued

| <u>Table</u> |                                  | Page |

|--------------|----------------------------------|------|

| 19           | JUMP AND INTERRUPT SEQUENCES     | 96   |

| 20           | MULTIPAC MODULE INTERCONNECTIONS | 124  |

2

.

÷

#### LIST OF ABBREVIATIONS

| ANAMP       | Analog amplifier                 |

|-------------|----------------------------------|

| ANSW        | Analog switch                    |

| BMIC        | Bipolar-to-MOS interface circuit |

| BRA, BRB    | Base register A and B            |

| CDS         | Central data system              |

| CIR         | Command input                    |

| CMD         | Command module                   |

| DTL         | Diode-transistor logic           |

| IEN         | Interrupt enable                 |

| INC         | Incrementing carry (flip-flop)   |

| LIR         | Logic instruction register       |

| LSI         | Large-scale integration          |

| LSR         | Logic shifting register          |

| LU (or LUR) | Logic unit (register)            |

| MA          | Memory address (register)        |

| MBIC        | MOS-to-bipolar interface circuit |

| MD          | Memory data (register)           |

| MOS         | Metal oxide semiconductor        |

| MR          | Module reliability               |

| OPC         | Operation code                   |

| PC          | Program counter                  |

| PSR         | Program switch register          |

| RD          | Read (flip-flop)                 |

| SC          | Shift clock                      |

| TCLK        | Transfer clock                   |

| TFF         | Test flip-flop                   |

| ТМ          | Telemetry module                 |

| TOF         | Telemetry output flip-flop       |

|             |                                  |

## LIST OF ABBREVIATIONS. -- Continued

| TOR | Telemetry output register |

|-----|---------------------------|

| TTL | Triode-transistor logic   |

| WR  | Write (flip-flop)         |

| WS  | Word strobe               |

#### RESEARCH REPORT

#### MULTIPAC, A MULTIPLE POOL PROCESSOR AND COMPUTER

#### FOR A SPACECRAFT CENTRAL DATA SYSTEM

- By E. Cohler

- T. Baker

- G. Cummings

- R. South

#### SUMMARY

A computer has been designed for use as a central data system on deep space probes. This computer has the unusual characteristic that it may be repaired during flight through the command and telemetry link by reprogramming around the failed unit. This computer organization uses pools of identical modules which the program organizes into one or more computers. In the event of a failure, new programs are entered which reorganize the central data system. The only effect of such reorganization is to reduce the total processing capability aboard the spacecraft, and therefore some low priority process may have to be eliminated.

This report contains a detailed description of this design including logic diagrams of all modules and interconnection lists for these modules. Further implementation of this design is now proceeding using large-scale integrated circuits (LSI). A section containing recommendations for improving the system organization when reimplementing this design is included in this report.

# PRECEDING PAGE BLANK NOT FILMED.

#### 1.0 INTRODUCTION

MULTIPAC is a spacecraft central processor whose modular organization permits reprogramming around failed modules. Machine reorganization may be accomplished by program changes to utilize surviving modules optimally, thus effecting a gradual degradation of processing capability as additional modules fail in the course of a long mission. Since there is an inverse relationship between the processing capacity of such reorganizations and their probability of survival, the probability that at least some minimal mode of operating the spacecraft can be sustained throughout very long missions is quite high.

The present report describes a conventional integrated circuit implementation of the system which indicates its feasibility and provides a base line for the evolution of the final LSI design.

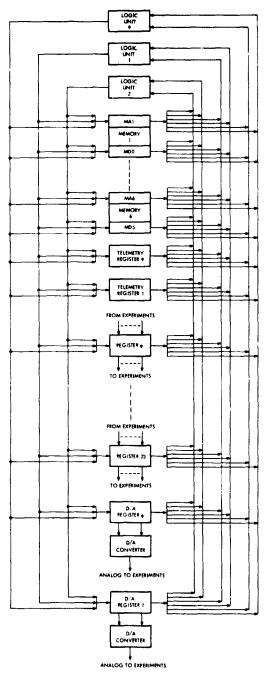

The general block diagram of the present MULTIPAC system is shown in Figure 1. (This diagram is a simplification showing the data flow paths only.) The system consists basically of from 2 to 24 of each of seven different types of modules which are interconnected by data busses. The module types are:

- (1) Logic Unit

- (2) Address Switch

- (3) Register

- (4) D/A Register(5) Memory

- (6) Telemetry and Command Interface Unit

- (7) Timing Generator

The control-arithmetic-logi(al module is called a logic unit. Each logic unit has two input and one or .put data busses and the data flow, which is a 13-bit serial transfer, is controlled by them. Each of the logic units can operate on the output from two other modules through its two input data busses and return the result to one of the two through its output data bus. The logic unit selects the connections on its own input and output busses.

The second type of module, the address switch, is an extension of the logic unit input and output bus structure and further expands their address switching by providing a second level of selection. These are not shown separately in Figure 1.

Figure 1. Simplified Block Diagram of MULTIPAC

.

.

The third type of module is the register. This module acts as a general purpose quick access storage register and also provides I/O interfaces to the rest of the spacecraft and the experiments. Each register may have 13 inputs and 12 outputs attached to it, and if an input or output command is given to this register, it may either take in 13 bits or put out 12 bits to the experiments. There are 24 of these registers, allowing up to 312 inputs and 288 outputs to the experiments and engineering subsystems.

In addition to the above 24 register modules, there are two more register modules with D/A converters attached to their outputs. The analog output is distributed through isolating amplifiers to the experiments to be used in conjunction with A/D conversion.

The fifth type of module is a 2048-word, 13-bit memory. There are six of these which are used for program store as well as data store. When used for program store, their address registers increment each machine cycle, thus serving as program counters.

The sixth type of module is for the telemetry and command interface. It is basically two register modules interfaced to the telemetry transmitter and command receiver with the additional capability of obtaining control over logic units via the command link. There are two of these modules for redundancy purposes.

The seventh type of module is a timing generator which supplies synchronizing clock pulses to the rest of the MULTIPAC system. It is not shown in Figure 1.

The three logic units, in conjunction with the six memories, provide for three possible processors. These would divide the processing load, such as one handling inputting and outputting of data to and from the experiments, one handling data reduction routines, and one doing the formatting and outputting to the telemetry. Data can be exchanged between such processors by simply exchanging their data memories, each processor updating certain tables. Communication between the processors is necessary to assure that the timing of such transferring is mutually agreeable. Under the graceful degradation concept, these three independent processors would have to absorb one another's tasks if equipment failures caused a reconfiguration to two processors or one. The processing load and telemetry rate would have to be adjusted as necessary to keep each such combined processor working within real time.

#### 2.0 THE MULTIPAC CONCEPT AND ITS EVOLUTION

The MULTIPAC system was originally proposed as a computer organization which would make the versatility of a programable central processor available on long space flights without making the spacecraft dependent on the poor reliability of a conventional computer in which any failure normally makes the entire system useless. The solution then envisioned, shown in Figure 2, was a very simple processor organized from modules selected from pools of three basic module types (logic units, memories, and general-purpose registers) which would be assigned to their functional roles by software methods. Should a failure occur, the faulty module could be replaced by assigning another to fulfill its function. Moreover, spares would not have to be assigned as such but could be used insofar as possible to enlarge the initial capacities of the processor. Failures would simply cause a gradual degradation of processing capability so long as sufficient modules remained from which to construct the minimal processor.

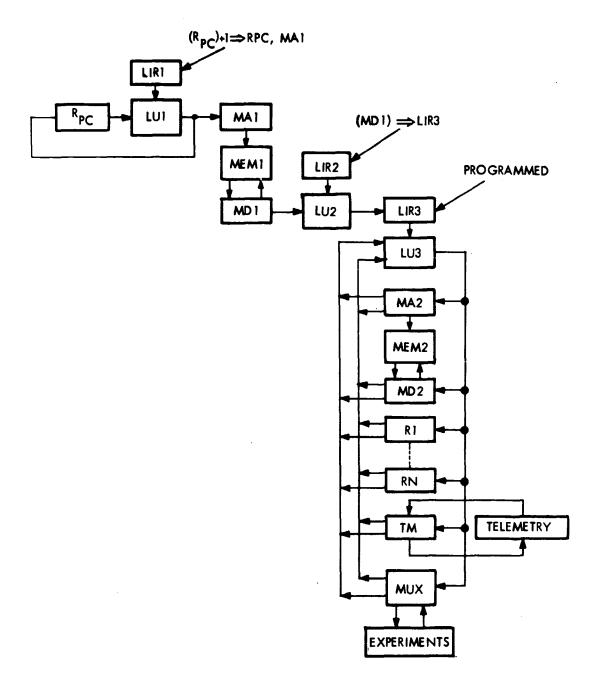

As originally envisioned, a processor could be constructed from three logic units, two memories and several registers, plus a multiplexer to provide I/O to the spacecraft experiments and modules to interface with the command and telemetry links. The logic units perform all transfers in the machine as dictated by their individual instruction registers (LIR's). The memories automatically output to their data registers (MD) the contents of the location specified by their address registers (MA) or write in that location any data word transferred into their MD registers.

The data flow, which is programmed, is typically as shown in Figure 3. LIR1, the instruction register of Logic Unit 1, is initially loaded with an instruction causing the contents of a register  $(R_{pc})$ , used as the program counter, to be incremented and passed to the address register (MA1) of the memory containing the program.

A second logic unit (LU2) is also initially programmed causing it to continuously transfer the contents of the program memory data register into the instruction register of a third logic unit (LU3) which actually executes the program. It, in turn, operates on several registers which may be used as accumulators, index registers, counters, and scratch storage, and upon a second memory used for data storage. If the memory address is set in MA2 by the logic unit, one machine cycle later the contents of the location may be read from the memory data register (MD2).

The following table illustrates the overlapping timing with which the program counter is advanced, the instructions delivered into the instruction

ns) a Caran

Figure 2. Original MULTIPAC Concept

.

.

Figure 3. Data Flow in Original MULTIPAC Concept

register and, as an example, how an add from memory into the accumulator  $(R_{ACC})$  is executed. Operation codes used are copy (COP), no operation (NOP), and add (ADD).

| R pc | MA1 | MD1 | LIR3                   | MA2  | MD2    | RACC     |

|------|-----|-----|------------------------|------|--------|----------|

| 0    | 0   |     |                        |      |        | А        |

| 1    | 1   | (0) |                        |      |        | A        |

| 2    | 2   | (1) | (0)=COP MD1, MA2       |      |        | А        |

|      |     | (2) | (1)=NOP ADDR           | ADDR |        | A        |

|      |     |     | (2)=ADD MD2, $R_{ACC}$ | ADDR | (ADDR) | Α        |

|      |     |     |                        |      |        | A+(ADDR) |

The original machine was to have used a 16-bit word having a 4-bit operation code and three 4-bit addresses. Addresses were 12 bits long and the operation code field contained all zeroes, defined as a no operation (NOP) instruction. Addresses were buried in the program stream in what were essentially two-word instructions and prevented from acting as instructions when they reached LIR3 by their NOP coding.

Three factors have proved troublesome in the practical design of the machine. First, there is a great deal of switching interconnecting all the modules in order that they may all be interchangeable. Second, the power limits set upon the design constrain the choice of circuitry to the lowest-powered (and lowest speed) logic families. Third, the real-time data processing requirement, initially assumed to consist of low-rate data formatting, has grown quite large, enough to tax a modern general-purpose computer, let alone the simple micro-ordered set of trivial modules originally envisioned.

These three factors have influenced the evolution of the design. The choice between a serial or parallel machine was resolved in favor of a serial one, largely in order to minimize the amount of switching logic between modules. Also involved in this decision was the question of speed versus power. Investigation indicated that a parallel machine would have been too large, considering the switching logic, and would exceed the power budget even with very low powered logic. The serial system was smaller and could stay within the power budget if constructed from very low powered logic. However, it would be an order of magnitude slower, which would have

an adverse effect upon the ability of the machine to handle the processing load. This was alleviated to some extent by the use of a small percentage of higher powered, and thus faster, logic in the critical data paths.

The power budget was also responsible for the decision to reduce the machine word size to thirteen bits. Three-address instructions were eliminated, which not only disposed of one 4-bit address field, but also prohibited instructions designating two locations in which the result should be stored. This permitted the simplification of the switching logic to include only one output data bus instead of two. One extra bit (the thirteenth) had to be added to distinguish data from instructions. The machine is now coded so that all instructions have the twelfth and thirteenth bit dissimilar, whereas for two's complement data the thirteenth bit acts as an extended sign bit, making it always the same as the sign, or twelfth bit.

Considering the speed that could be attained with such a serial machine (initially estimated at about 8-microsecond instruction times but later increased to 16 microseconds), it became necessary to consider a multiprocessing system having two or three independent processors in order to fulfill the real-time requirements. This, in turn, increased the number of modules required and the size of the switching matrix. At this point, it became necessary to depart from the generality of the Figure 2 arrangement, which had standard logic unit modules doing such simple tasks as incrementing the program counter and transferring the output of the program memory into the instruction registers. The logic units used for these simple tasks were eliminated. Now, self-incrementing logic is built into the memory address register and the program selection switch is built into the logic unit. The number of logic units was reduced by two thirds. Since logic units were no longer addressable devices, a secondary bus structure was created for the transfer of instructions. In essence, some of the simplicity and generality of the original concept had to be specialized to meet the demands of speed and efficiency.

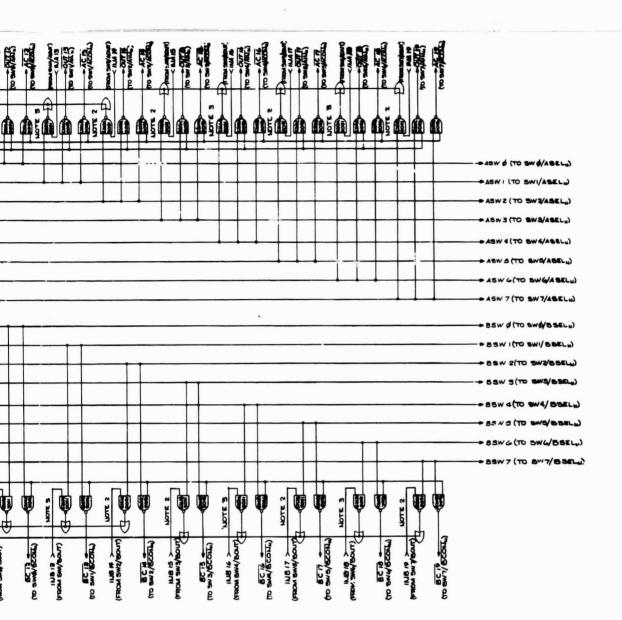

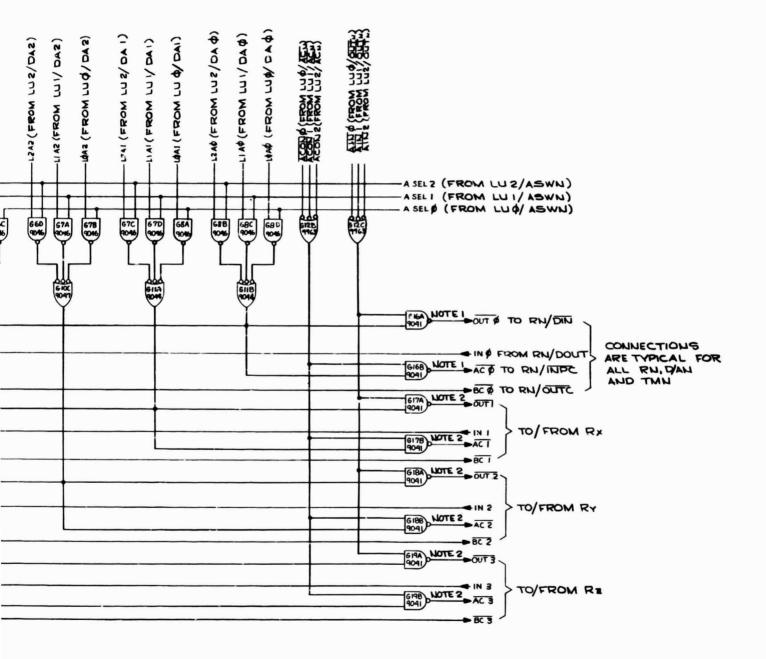

In the course of designing the I/O devices, it was found that the multiplexer had switching problems very similar to those of the logic units. At least 200 I/O channels had to be provided, which called for something like four modules, each containing addressable 64-way switching of in, out, and control signals. This problem was solved by combining the multiplexer with the general-purpose registers and providing special instructions to use each bit of each register as an I/O channel. The number of channels required was essentially divided by 13 and the multiplex switching was moved back into the main address switching. With the exclusion of logic units as addressable devices but the inclusion of 24 registers (which would provide 312 input and 288 output channels) and the number of processors set at three, the system has 40 addressable devices. This overtaxed the 4-bit address field, and therefore 3-bit base registers were incorporated in the logic unit addressing structure. Furthermore, to move a portion of the address switching outside of the logic unit, a second level of switching was incorporated which forms a common extension of the address switching of all the logic units. This is used to address the I/O registers and, in essence, constitutes the multiplexer switch, controlled by the logic unit base registers. Since this second level of address switching is common to all logic units, programming restrictions must be imposed to prevent different processors from interfering with each other.

Another step taken to increase the efficiency of the processing routines was the improvement of the A/D conversion method. The original concept called for analog-to-pulse-width converters at the experiments, the duration of whose output levels would be counted by the processor. This proved unworkable, since the processor would have had to devote itself to each conversion for about 50 milliseconds in a tight loop to achieve the required 8-bit accuracy. To solve the problem, a new module was created, a register which has a D/A ladder network on its outputs. This provides an analog reference signal to the experiments, and each of the latter now must have an analog comparator which returns a signal level to the processor I/O indicating whether their output signal is greater or less than the reference signal supplied. This makes possible the successive approximation method of conversion whose algorithm runs much faster, i.e., about 1.4 milliseconds for the maximum length (8-bit) conversion.

The instruction set was then enlarged from simple two-argument logical and arithmetic instructions and test commands to include the bit manipulating and I/O instructions necessary to make the I/O registers and the A/D algorithm operate efficiently.

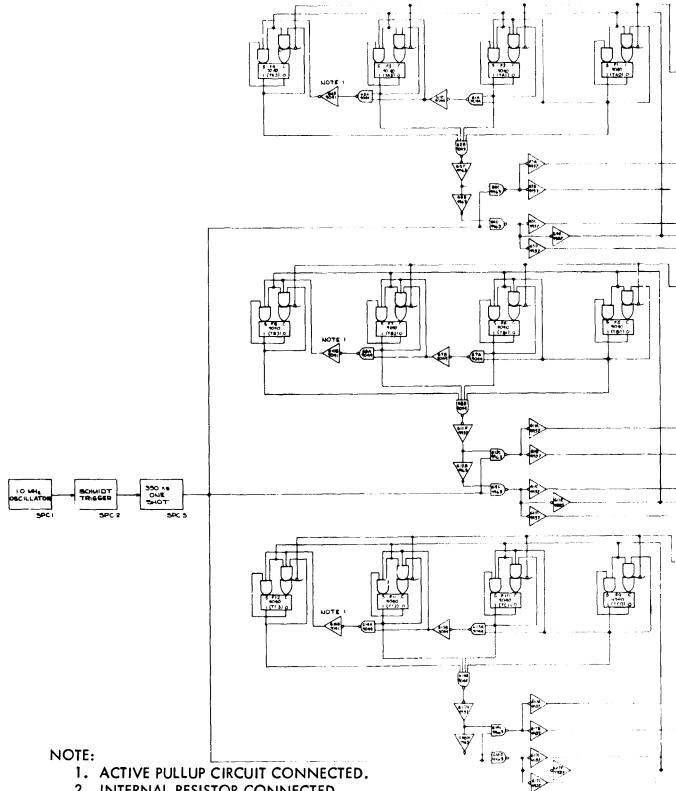

Finally, the clock signals, the one set of signals which were common to all modules, were made less susceptible to failure by triplicating the buses and putting majority voting gates at each module interface.

At this point the external specifications and features of the MULTIPAC design were frozen in order that a detailed IC logic design could be done. The iteration of the design for LSI will offer opportunities for further improvements. Section 8 contains recommendations for such improvements as can presently be foreseen.

#### 3.0 SYSTEM DESCRIPTION

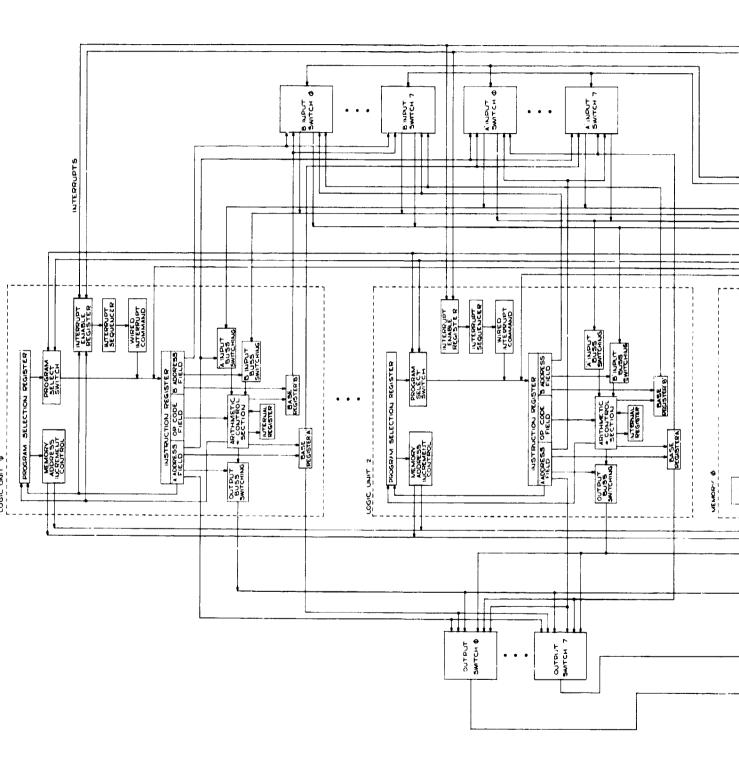

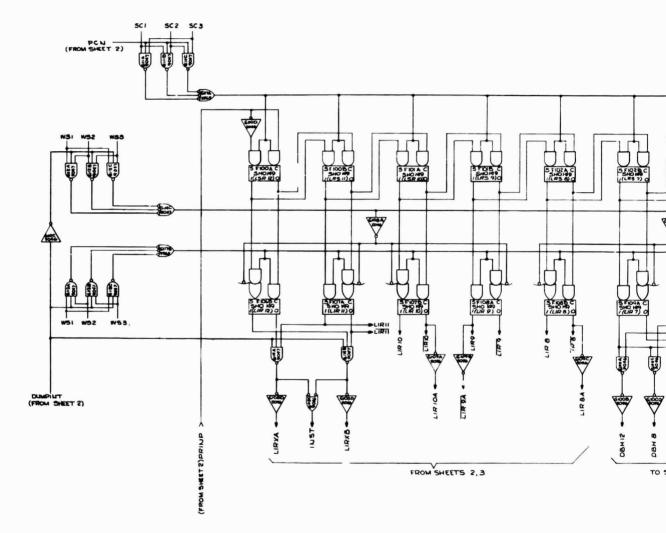

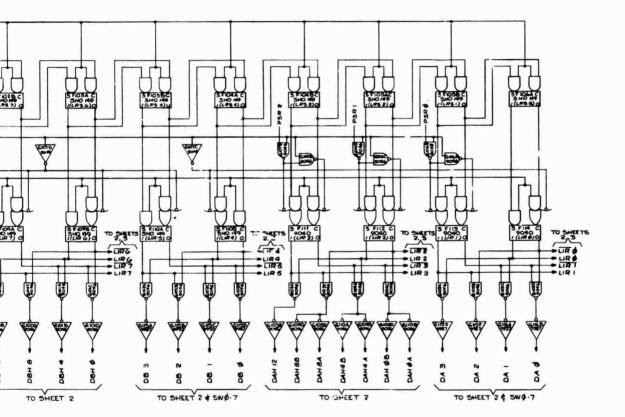

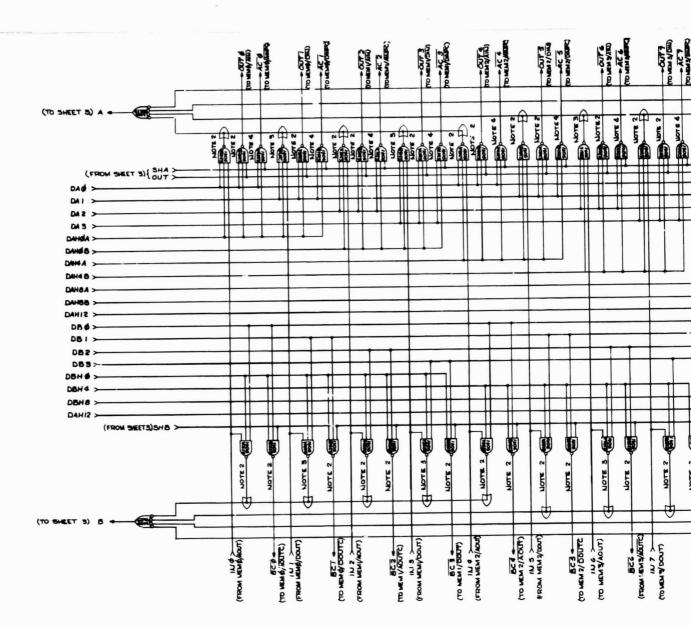

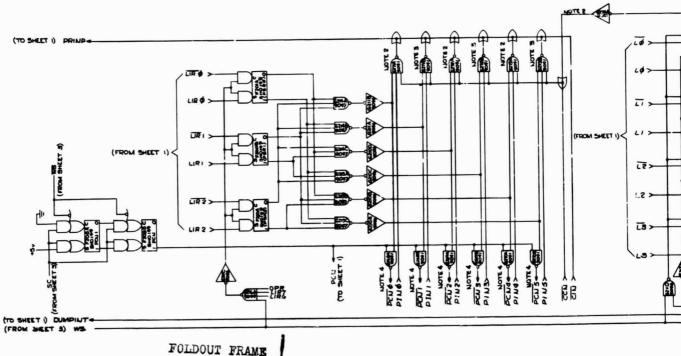

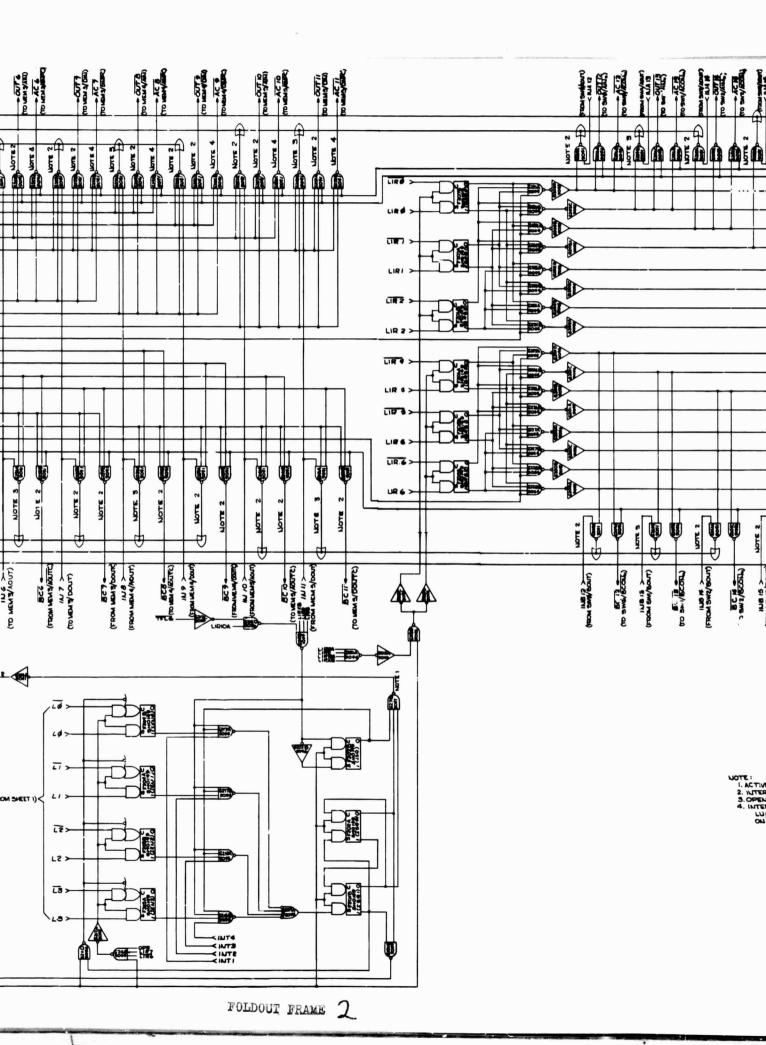

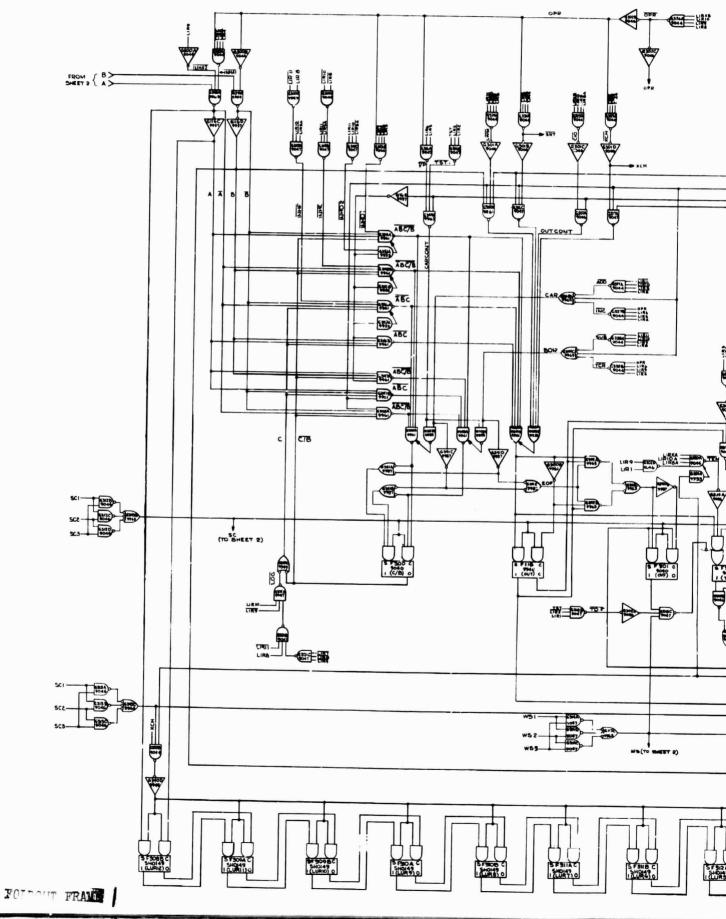

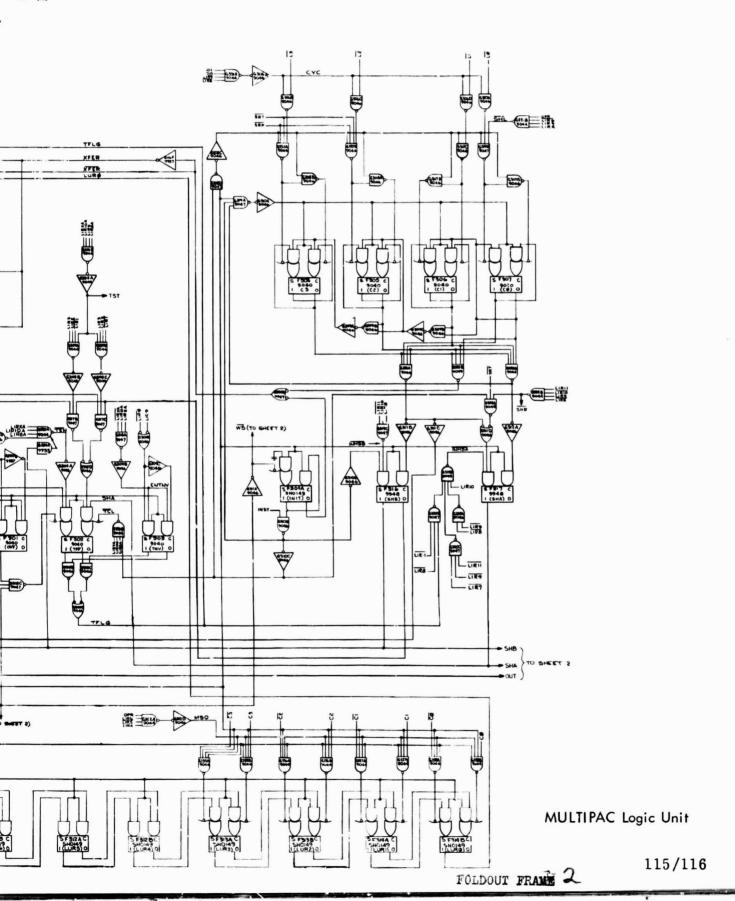

The detailed block diagram of the MULTIPAC IC design is shown in Figure 4. This includes the control functions and details of data switching which were omitted from the simplified diagram of Figure 1.

#### 3.1 Data Flow

Data flow takes place only under the control of one of the three logic units. Each of these communicate directly with six memories, 24 general purpose registers also serving as I/O interfaces, two D/A registers, two command registers, and two telemetry registers.

The memories themselves each contain two addressable registers, the address register (MA) and the data register (MD). Except for the automatic incrementing of the MA, which will be considered under control functions, the memories operate entirely on the basis of transfers to and from these registers. When data is transferred into the MA, a read cycle is automatically initiated to read out the contents of the new location into the MD one cycle later. When data is transferred into the MD, a write cycle is initiated to store it in the location specified by the MA.

Each of the 24 general purpose registers has connections for 13 bilevel inputs and 12 bilevel (dc) outputs which may be accessed by a special I/O instruction. Thus, they provide 338 inputs (counting the D/A registers) and 288 outputs to the rest of the spacecraft and the instruments.

The D/A registers are very similar to the general purpose registers, having the same number of input channels, but the output channels are not present. Instead, a D/A ladder network is connected to provide an analog signal proportional to the arithmetic value of the register contents which is used by the experiments as a reference voltage in the successive approximation A/D conversion process.

The telemetry and command registers share a common address. Instructions operating on such an address will connect one of the command registers to its input bus and/or one of the telemetry registers to its output bus. Since these are normally addressed by simple copy instructions, they copy to the telemetry register or from the command register.

Figure 4.

BE1

Figure 4. MULTIPAC Block Diagram

**\$**/14

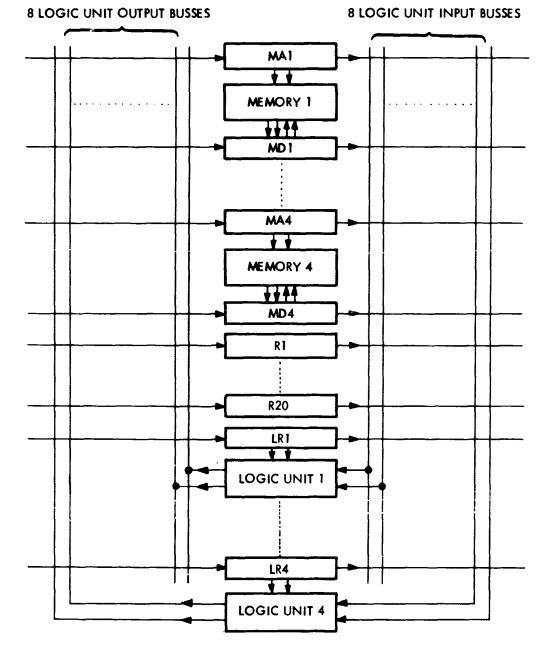

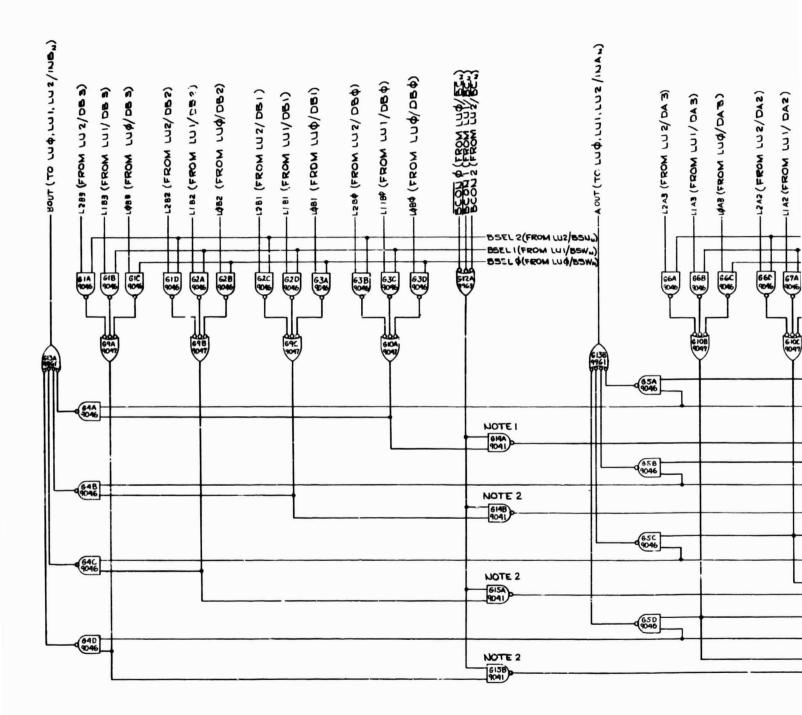

3.1.1 Address switching.-- Address selection is determined both by the address fields of the instruction and by the setting of base registers in the logic unit and is actually performed in two parts by the bus switching logic in the logic unit and by the external switching module operating on levels supplied to it from the logic unit. Each logic unit has 16 addresses directly addressable from each 4-bit field in the instruction word. Twelve of these directly address six memories. The other four addresses are passed on to the eight second-level switches where one of the four outputs of the switch is thus directly addressable by the instruction address field. The selection of a switch by a logic unit is controlled by the contents of a 3-bit base register which may be loaded by a special instruction. There are two such base registers per logic unit, one for each of the address fields in the instruction word. Each base register acts independently of the other register. There are three logic units, all connected similarly to the same switches. Figure 5 shows these address allocations. The 12 addresses of the six memories, which are common to all the logic units, plus the 32 outputs of the eight switches provide 44 total addresses.

The second-level switching arrangement introduces a programming restriction. Two logic units operating through the same second-level switch will have their input data busses ORed together, thus creating meaningless data. Therefore, separate programs running in separate logic units must not have their base registers set to the same value.

The intercommunication between processors, which is necessary to prevent their mutually interfering with one another, can be accomplished by connecting certain input and output channels located on different base register settings to one another, providing flags from one processor to the other.

3.1.2 <u>The I/O system.--</u> The I/O interface of the central processor, as described in the Final Report of Phase 1 of this project, is summarized in Tables 1, 2, and 3.

There are 191 input channels and 126 output channels required. The science input lines are doubled in order to be connected through two different registers for path redundancy. Also, there is one output channel added for each serial digital input and each serial command output since these must have additional signals to control the serial transfer.

The multiplexing system which has been devised employs each bit in each of the registers of the machine as a bilevel input channel as well as a bilevel output channel. The use of a special I/O instruction at the time

| STER<br>                 |    | 0    | -     | •        | 3   | r   | 4           | S     | \$   | ~    |                               |

|--------------------------|----|------|-------|----------|-----|-----|-------------|-------|------|------|-------------------------------|

| BASE REGISTER<br>SETTING | 17 | R2   | 4     | <u>}</u> | R 8 | L Z | R14         | R17   | R 20 | RZ   |                               |

| BA                       | 91 | R2   | 1 7 8 |          | R7  | R10 | <b>R</b> 13 | RI&   | R19  | R 22 |                               |

|                          | 15 | RØ   | 4     | 2        | R6  | R9  | R12         | R 15, | R 18 | R 21 |                               |

|                          | 4  | DΑφ  | DAd   |          | DAI | DAI | ŢMģ         | ŢΜ∳   | TMI  | TM2  |                               |

|                          | 13 | MD5  |       |          |     |     |             |       |      |      | ations                        |

|                          | 12 | MA5  |       |          |     |     |             |       |      |      | MULTIPAC Address All ocations |

| DRESS                    | [  | MD4  |       |          |     |     |             |       |      |      | ,C Addre                      |

| ON AD                    | 01 | MA 4 |       |          |     |     |             |       |      |      | IULTIPA                       |

| INSTRUCTION ADDRESS      | 07 | MD3  |       |          |     |     |             |       |      |      |                               |

| INS                      | 96 | MA3  |       |          |     |     |             |       |      |      | Figure 5.                     |

|                          | 05 | MD 2 |       |          |     |     |             |       |      |      |                               |

|                          | 8  | MA 2 |       |          |     |     |             |       |      |      |                               |

|                          | 03 | ; dw |       |          |     |     |             |       |      |      | •                             |

|                          | 02 | MA 1 |       |          |     |     |             |       |      |      |                               |

|                          | 10 | Ø QW |       |          |     |     |             |       |      |      |                               |

|                          | 8  | MAØ  |       |          |     |     |             |       |      |      |                               |

## SCIENCE INTERFACE LINES

| Magnetometer:            | 3 Analog Inputs          |

|--------------------------|--------------------------|

|                          | 2 Serial Commands        |

|                          | 2 Bilevel Commands       |

| Cosmic Ray Telescope:    | 4 Analog Inputs          |

|                          | 5 Serial Inputs          |

|                          | 1 Bilevel Input          |

|                          | 4 Bilevel Commands       |

| Plasma Probe:            | 11 Analog Inputs         |

|                          | 1 Serial Command         |

|                          | 1 Bilevel Command        |

| Radio Propagation:       | 5 Analog Inputs          |

|                          | 1 Serial Input           |

|                          | 1 Bilevel Command        |

| Neutron Detector:        | 19 Serial Inputs         |

|                          | 2 Bilevel Commands       |

| VLF Experiments:         | 6 Analog Inputs          |

| • -                      | 1 Serial Command         |

|                          | 1 Bilevel Command        |

| Micrometeorite Detector: | 2 Analog Inputs          |

|                          | 3 Serial Inputs          |

|                          | 3 Bilevel Inputs         |

|                          | 4 Bilevel Commands       |

|                          |                          |

| Totals:                  | <b>31</b> Analog Inputs  |

|                          | 28 Serial Digital Inputs |

|                          | 4 Bilevel Inputs         |

|                          | 4 Serial Commands        |

|                          | 15 Bilevel Commands      |

\_

.

-

Ĭ

17

the second second second

### ENGINEERING INTERFACE LINES

| Orientation Subsystem:        | 5 Analog Inputs        |

|-------------------------------|------------------------|

| -                             | 5 Bilevel Inputs       |

|                               | 10 Bilevel Commands    |

| Power Subsystem:              | 14 Analog Inputs       |

|                               | 1 Bilevel Input        |

|                               | 11 Bilevel Commands    |

| RF Subsystem:                 | 15 Analog Inputs       |

| •                             | 9 Bilevel Inputs       |

|                               | 10 Bilevel Commands    |

| S/C Support Subsystem:        | 6 Analog Inputs        |

|                               | 2 Bilevel Inputs       |

|                               | 2 Bilevel Commands     |

| Central Data Engr. Subsystem: | 5 Analog Inputs        |

|                               | 3 Bilevel Commands     |

| Other Subsystems:             | l Serial Input         |

| ·                             | 2 Bilevel Inputs       |

|                               | 3 Serial Commands      |

|                               | 4 Bilevel Commands     |

|                               |                        |

| Totals:                       | 45 Analog Inputs       |

|                               | 1 Serial Digital Input |

|                               | 19 Bilevel Inputs      |

|                               | 3 Serial Commands      |

|                               | 40 Bilevel Commands    |

18

1

-

4. . .

# I/O CHANNELS REQUIRED

•

.

.

-

.....

1

| Inputs (Science lines doubled): |   |                                      |                           |                  |  |

|---------------------------------|---|--------------------------------------|---------------------------|------------------|--|

| Analog                          | - | Science<br>Engineering               | 62<br><u>45</u><br>107    | 107              |  |

| Serial                          | - | Science<br>Engineering               | 56<br><u>1</u><br>57      | 57               |  |

| Bilevel                         | - | Science<br>Engineering               | 8<br><u>19</u><br>27      | $\frac{27}{191}$ |  |

| Outputs                         |   |                                      |                           |                  |  |

| Serial Commands                 | - | Science<br>Engineering               | <b>4</b><br><u>3</u><br>7 | 7                |  |

| Bilevel Commands                | - | Science<br>Engineering               | 15<br><u>40</u><br>55     | 55               |  |

|                                 |   | Control Lines for<br>Serial Inputs   | 57                        | 57               |  |

|                                 |   | Control Lines for<br>Serial Commands | 7                         | $\frac{7}{126}$  |  |

that serial word transfer has ceased affects the data line differently from the other instructions. For all other instructions, the data line will be forced to zero after each data transfer. After an I/O instruction, the data line will be forced to a one after the data transfer and will gate the word strobe which either inputs data to a register or outputs data from it, depending on the contents of the data that was transferred. If the data word transferred to a register by an I/O instruction contains a ONE in the high order bit, the data will be dumped to an output register. If the data word contains all ZEROES, the I/O instruction will serve as an input command and the data from the input interface lines will be dumped into the address register to be read by the next instruction. I/O instructions will also cause interface shift pulses to be generated at the register, from which they are distributed to the peripheral devices connected to that register. These, in conjunction with enabling levels, are used to transfer serial data to and from the experiments.

The I/O interfaces fall into the following categories, and the methods for handling each of them is discussed in detail below.

Inputs:

| Bilevel inputs: | Two-state signals which are sampled asychronously at the interface                            |

|-----------------|-----------------------------------------------------------------------------------------------|

| Serial inputs:  | 2- to 17-bit words to be transferred serially into the machine                                |

| Analog inputs:  | 0- to 5-volt analog levels to be converted<br>into digital words with up to 8-bit<br>accuracy |

| uts:            |                                                                                               |

#### Outputs:

| Bilevel commands: | Single-bit commands which are held<br>indefinitely as levels at the inter-<br>face. Pulsed reset signals are also<br>included here, but they are set, then<br>cleared, by the program. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial commands:  | Commands of two to five bits which are<br>transferred serially to the peripheral<br>device                                                                                             |

3.1.2.1 Bilevel inputs:-- These are simply levels which must be read by the processor. They are present at inputs to individual stages of the I/O registers and are transferred into the registers by an input instruction addressed to the register. The operation is a clear-set in which the input instruction performs the clear by transferring a data word of all ZEROES into the register. The whole word is then read from the register by the processor executing a "test with mask" (TWM) instruction. This AND's the contents of the I/O register with a masking register which contains a ONE in the bit to be tested and sets the Test flip-flop if the result produces a ONE. The Test flip-flop in the logic unit is thus set to the state of the input bit, and the program can pack such bits into words as necessary. These inputs require only one input channel each, and no output channel.

3.1.2.2 Serial inputs: -- Serial data will appear as sequential bilevel inputs to one stage of an I/O register, but there must also be output signals to synchronize shifting of the data with reading it into the register. A channel will be allocated to each such input which will be used to gate the peripheral device into its outputting mode. It will then respond to shift pulses from the register which occur each time an I/O instruction is addressed to the register.

3.1.2.3 Analog inputs: -- A/D conversion is accomplished by the successive approximation method, where processor software is used for the customarily hard-wired conversion logic. Two addressable registers are equipped as D/A converters. Their outputs are fed into a ladder network and the resultant analog signals distributed through isolating amplifiers to all devices requiring A/D signal conversion. Each such analog signal will be connected to its own comparator, which will also receive the distributed reference signal from the D/A output. The output of the comparator will then be treated as a birevel input to one stage of an I/O register.

To accomplish the conversion, the program sets a ONE in the high order end of theD/A converter, which is a digital number one-half the number range of the register, and produces an analog output equal to one-half of the analog signal range. The comparator response indicates by its output which signal is larger. This is detected by the program through testing the input channel, and the high order bit in the D/A register is left at ONE or set to ZERO according to whether the analog signal is greater or less than half the signal range. The next highest bit is then set to ONE, and the process is repeated to see whether the analog value is greater or less than 1/4 or 3/4, depending on what the first bit was, and so on. After all bits are thus determined, the converter value is read out of the D/A converter. The interface required, apart from the distribution of the D/A converter outputs, consists of one input channel per analog signal. 3.1.2.4 Bilevel command outputs:-- The register module includes an output buffer register which is loaded in parallel from the shifting register using the word clock timing. This is a typical structure throughout the machine. In this case, however, the buffer register will be loaded only upon receipt of an output command. The outputs of this buffer register constitute the bilevel output channels. This arrangement provides both an input and an output channel for each stage of the I/O register, and since the number of each is approximately equal, it effectively doubles the multiplexing.

Since there is no way of outputting data to one channel without affecting others, and no way of transferring the contents of the output buffer register back into the processor to regenerate the bits which should not be changed, it is intended that a command table of 24 locations be kept in memory. Command routines would operate on the appropriate word in memory to alter the appropriate bits, using masking instructions that leave the other bits unaffected. Then the updated word would be transferred to the register by an I/O instruction.

3.1.2.5 Serial command outputs: -- Two bilevel channels are required for serial commands, one to switch the peripheral device to its input mode and the second to provide data levels. A shift pulse from the register will be provided each time it receives an I/O instruction.

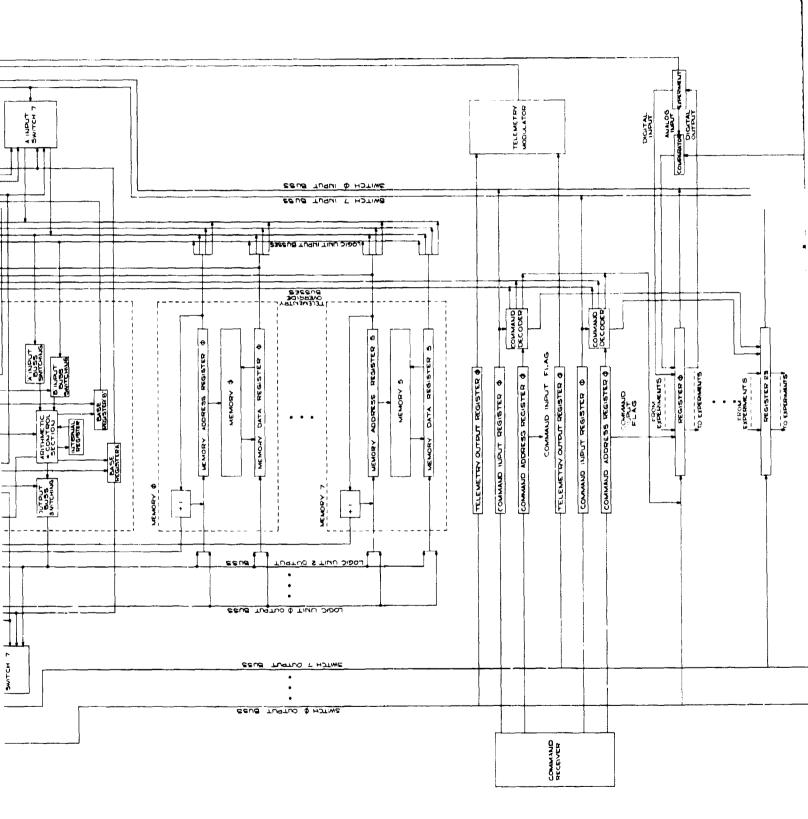

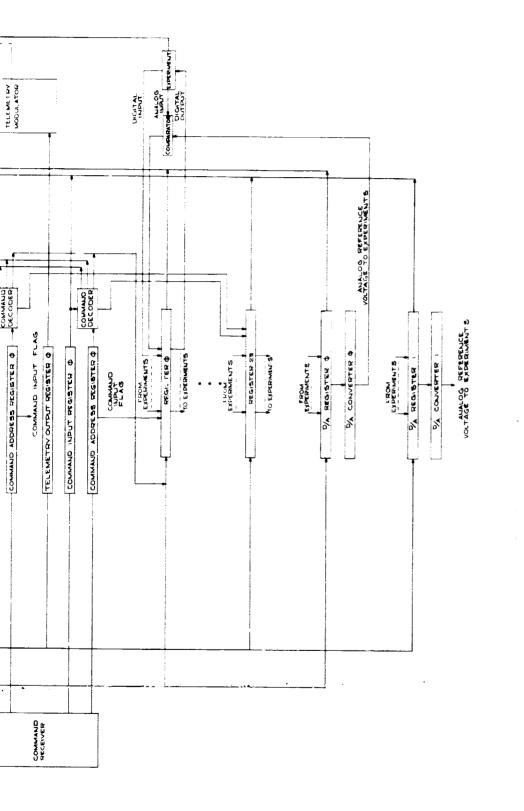

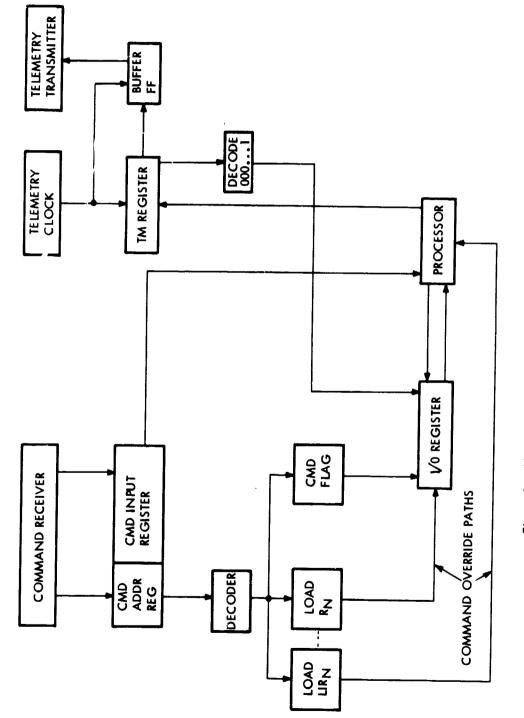

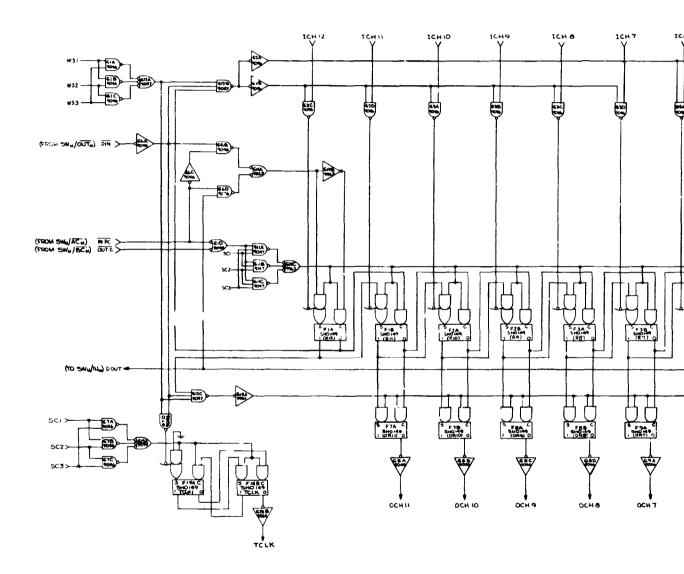

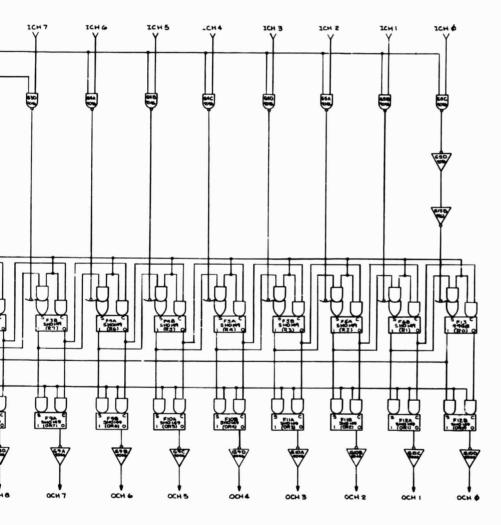

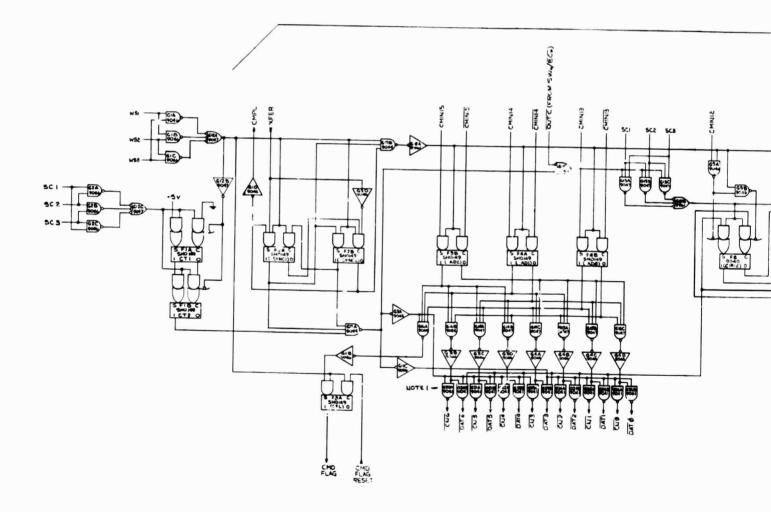

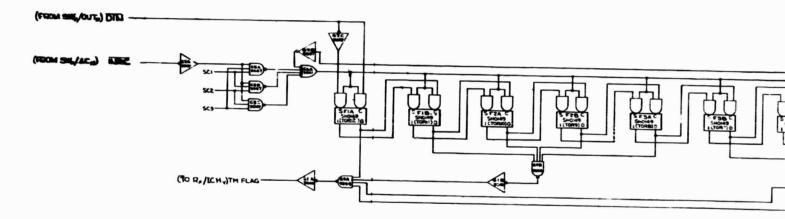

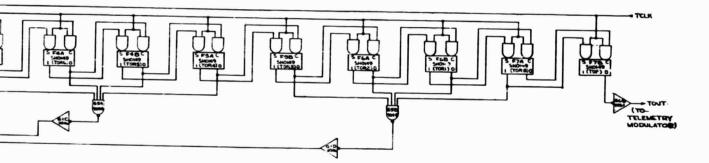

3.1.3 Telemetry output.-- Figure 6 is a block diagram of the telemetry and command interfaces. Data to be output to the telemetry modulator is transferred in maximum word lengths of twelve bits to the telemetry register. The next higher order bit, to the left of the data word, must always be a ONE because the output operation requires it. The telemetry register will shift right, with each pulse of an external telemetry clock delivered to it, outputting the contents of the register serially into a 1-bit buffer flip-flop whose output may be used to directly modulate the telemetry transmitter. The telemetry register is filled from the left with ZEROES as it shifts so that when the last bit of data has been shifted into the buffer, it contains a ONE in the low order bit and otherwise all ZEROES. This condition is detected by a decoder whose cutput is sensed by the processor which, in turn, causes the next output word to be transferred into the telemetry register. It must act within one bit time of the telemetry rate in order that the next data bit can be transferred into the output buffer when required. The decoder output may be connected to one of the I/O input channels to be sensed by the processor, but the response time required at a high telemetry rate could require checking the flag frequently enough to prevent the processor from doing other unrelated tasks efficiently. The normal mission configuration, therefore, should be to connect the decoder output onto one of the interrupt lines.

.

Ì

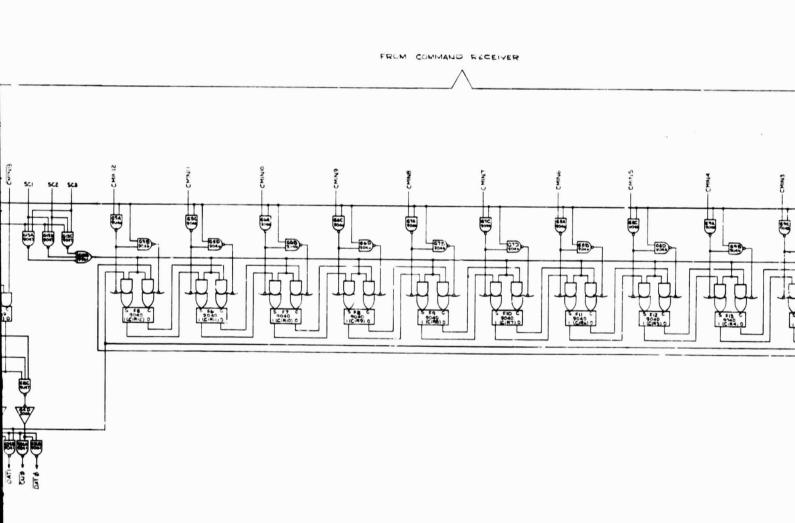

3.1.4 <u>Command inputs.--</u> Normal commands received from the command transmitter, i.e., those which do not attempt to override the processor, are loaded into the data register of the command input module and a flag sensed by the processor is set. The processor then reads out the contents of the command register under program control. Although this sensing could be accomplished by interrupt, as described above for the telemetry output control signal, it is anticipated that the up-link data rate will be slow enough to permit periodically sampling the flag level connected through one of the normal input channels.

The different operations caused by commands which override the program in order to acquire control of the processor are explained in paragraph 3.2.3 below.

#### 3.2 Control Functions

The paths for program flow in the MULTIPAC are separate from the data flow and are determined by the program switch in each logic unit described below. In addition to this software control, there is provision for interrupting and an overriding input to each logic unit from the telemetry registers which permits the command link to acquire control of the system at any time.

3.2.1 <u>Program selection.--</u> Program sources for each logic unit are selected by a switch in the logic unit itself. This switch, in turn, is controlled by the contents of the 3-bit program selection register. This register is addressable only by the logic unit of which it is a part, and its contents are entered by a special instruction. The switch addresses any one of the six memories. When a memory is thus selected, a control line from the logic unit causes the memory address to increment at each word time and the memory data register to shift out its contents into the instruction register (LIR) of the logic unit. From there, these instructions are dumped into the buffer register on each word pulse, where they are decoded to control the operation of the logic unit.

3.2.2 <u>Instruction list.</u>-- Each logic unit in the MULTIPAC system performs the instruction set listed in Table 4 using the instruction format shown in Figure 7.

Programming of MULTIPAC is accomplished through groups of machine microinstructions which actually constitute multiple word macroinstructions and must take into account the MULTIPAC machine timing for their

# MULTIPAC INSTRUCTION LIST

|      | Mnemonics   | Operation | Operation                                                                                                                       |

|------|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| (1)  | ADD, R1, R2 | 20        | Add the contents of R1 to R2<br>and put the result in R2.                                                                       |

| (2)  | SUB, R1, R2 | 21        | Subtract the contents of R1 from R2 and put the result in R2.                                                                   |

| (3)  | COP, R1, R2 | 13        | Move the contents of R1 to R2.                                                                                                  |

| (4)  | JMP, R1, R2 | 22        | Copy R1 into R2 and blank the second instruction which follows.                                                                 |

| (5)  | JCN, R1, R2 | 26        | If the Test flip-flop is a ONE,<br>copy Rl into R2 and blank the<br>second instruction which follows;<br>otherwise, do nothing. |

| (6)  | XOR, R1, R2 | 10        | Perform a bit-by-bit logical ex-<br>clusive or between the contents<br>of R1 and R2, potting the result<br>in R2.               |

| (7)  | LOR, R1, R2 | 24        | Perform a bit-by-bit logical OR<br>of R1 and R2, putting the result<br>in R2.                                                   |

| (8)  | AND, R1, R2 | 14        | Perform a bit-by-bit logical AND<br>of the contents of Rl and R2,<br>putting the result in R2.                                  |

| (9)  | SBR, N, M   | 27        | Set Base Register 1 to literal M;<br>set Base Register 2 to literal N.                                                          |

| (10) | SHR, R1, R2 | 12        | Cycle Rl one bit to the right;<br>shift R2 one bit to the right,<br>replacing the high order bit with<br>the bit cycled in Rl.  |

.

ł

-2-

25

-

## TABLE 4.-- Continued

## MULTIPAC INSTRUCTION LIST

|      | Mnemonics         | Operation<br>Code | Operation                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (11) | CYC, R1, N        | 16                | Cycle the contents of R1 N bits to the right, where $1 \le N \le 12$                                                                                                                                                                                                                                                                                                      |

| (12) | TWM, R1, R2       | 15                | Test the bit-by-bit logical AND<br>function of Rl and R2 and set<br>the Test flip-flop (TFF) to ONE<br>if the result is nonzero.<br>Otherwise, clear this flip-flop.                                                                                                                                                                                                      |

| (13) | CWM, R1, R2       | 11                | Copy the value of the Test flip-<br>flop into the bits in R2 not<br>masked by zeros in R1.                                                                                                                                                                                                                                                                                |

| (14) | CIO, R1, R2       | 23                | Copy the contents of R1 into R2.<br>If the high order bit of R2 = 0<br>after the transfer, load the<br>input interface signals into R2.<br>If the high order bit of R2 $\neq$ 0<br>after the transfer, load the<br>contents of R2 into the output<br>register of R2. Then transmit<br>an interface transfer pulse<br>(TCLK) from R2.                                      |

| (15) | TST, R <b>,</b> X | 17                | Test the register R for condi-<br>tions specified by X and set the<br>Test flip-flop (TFF), if the<br>condition is met:<br>X = 01 equal to zero<br>00 not equal to zero<br>04 less than zero<br>14 greater than zero<br>15 less than or equal to zero<br>05 greater than or equal to zero<br>11 equal to one<br>10 not equal to one<br>07 Unconditionally set TFF to ONE. |

<u>76</u>

## TABLE 4.-- Continued

## MULTIPAC INSTRUCTION LIST

|      | Mnemonics                        | Operation<br>Code | Operation                                                                                                                 |  |

|------|----------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| (15) | TST, R <b>,</b> X<br>(continued) | 17                | X = C6 Unconditionally set<br>TFF equal to ZERO.                                                                          |  |

|      |                                  |                   | <pre>02 Set TFF equal to the<br/>overflow flip-flop<br/>(OVF).</pre>                                                      |  |

|      |                                  |                   | 03 Set TFF not equal to<br>the overflow flip-flop<br>(OVF).                                                               |  |

| (16) | OPR, X, R                        | 25                | <b>Perform the operation specified<br/>by the X field on R as follows:</b>                                                |  |

|      |                                  |                   | X = 07 INC R - Increment the contents of R.                                                                               |  |

|      |                                  |                   | 06 DCR R - Decrement the contents of R.                                                                                   |  |

|      |                                  |                   | 00 CMP R - Perform the one'<br>complement of R, putting<br>the result in R.                                               |  |

|      |                                  |                   | 02 SRT R - Shift right the<br>contents of R, filling<br>the high order bit with<br>the contents of the Test<br>flip-flop. |  |

|      |                                  |                   | 03 SHL R - Shift left the<br>contents of R, filling<br>the low order bit with<br>zero.                                    |  |

|      |                                  |                   | 01 XCH R - Exchange the con<br>tents of R with the con-<br>tents of the LU register                                       |  |

|      |                                  |                   |                                                                                                                           |  |

1

1.1

### TABLE 4.-- Concluded

## MULTIPAC INSTRUCTION LIST

¥

|      | Mnemonics                | Operation<br>Code | Operation                                                                                                    |

|------|--------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|

| (16) | OPR, X, R<br>(continued) | 25                | 05 MSO R - Copy a number in<br>the LU register which is<br>two larger than the most<br>significant one in R. |

|      |                          |                   | 14 SPS N - Set the Logic Unit<br>Program Switch to literal N.                                                |

|      |                          |                   | 10 SIE N - Set the Interrupt<br>Enable Register to literal N.                                                |

•

-

| BITS   | BITS  | BITS  |  |

|--------|-------|-------|--|

| 8 - 12 | 4 − 7 | 0 - 3 |  |

| OPC    | A     | В     |  |

| OPC (bits 8-12) | = | Operation Code<br>(Bits 12 and 11 are different<br>for instructions, identical for data) |

|-----------------|---|------------------------------------------------------------------------------------------|

| A (bits 4-7)    | = | Register Address Field 1                                                                 |

| B (bits 0-3)    | = | Register Address Field 2                                                                 |

proper operation. When programming, care must be taken in: (1) copying addresses or literal data from the program stream, where they are imbedded in what are essentially the address fields of multiple word instructions, and (2) allowing for the timing of the memory read or write cycles initiated by transferring data into the address or data registers respectively.

The example below of adding to a register R, used as an accumulator, for memory shows both these aspects of machine timing. Memory No. 1 is used as the program memory and Memory No. 2 is used as the data memory. MA and MD refer to the memory address register and memory data register, respectively. The LIR is the instruction register from which instructions are decoded in the logic unit.

Starting in location 0, consider the following three instructions in Memory No. 1:

| Location | Instruction  |

|----------|--------------|

| 0        | COP MD1, MA2 |

| 1        | ADDR         |

| 2        | ADD MD2, R   |

This leads to the following machine timing, where each entry in the list represents the execution time of one microinstruction.

| Contents<br>of MA1 | Contents<br>of MD1 | Contents<br>of LIR  | Contents<br>of MA2 | Contents<br>of MD2 | Contents<br>of R |

|--------------------|--------------------|---------------------|--------------------|--------------------|------------------|

| 0                  |                    |                     |                    |                    | (R)              |

| 1                  | ( 0)               |                     |                    |                    | (R)              |

| 2                  | (1) =ADDR          | (0)=COP MD1,<br>MA2 |                    |                    | (R)              |

|                    | (2)                | (1) = ADDR          | ADDR               |                    | (R)              |

|                    |                    | (2)=ADD MD2,<br>R   | ADDR               | (ADDR)             | (R)              |

|                    |                    |                     | ADDR               | (ADDR)             | (R) + (ADDR)     |

Note that the instruction sequencing permits: (1) the COP instruction to be executed in LIR while ADDR is in MD1, and (2) the ADD instruction is executed in LIR after the memory cycle has loaded (ADDR) in MD2.

ADDR also appears in LIR and is thus treated as an instruction. The thirteenth bit of the machine, however, is coded to distinguish instructions and data. The operation field of all executable instructions is coded with the  $12^{th}$  and  $13^{th}$  bits dissimilar. Data words and addresses are limited to 12 bits in length and have the  $13^{th}$  bit the same as the  $12^{th}$  bit. Thus, the arithmetic unit can treat the  $13^{th}$  bit as any other, but a difference between the  $12^{th}$  and  $13^{th}$  represents an overflowed condition. Data and addresses which are not overflowed can safely be imbedded in the program since they will be decoded by the LIR as non-executable as instructions.

Jumping is accomplished through the data flow paths (shown in Figures 4 and  $\beta$ ) by the following instruction sequence.

| Contents<br>of MA1 | Contents<br>of MD1 | Contents<br>of LIR |

|--------------------|--------------------|--------------------|

| 0                  |                    |                    |

| 1                  | (0)                |                    |

| 2                  | (1) = JMPADR       | (0) =COPY MD, MA   |

| JMPADR             | (2)                | (1) =JMPADR        |

| JMPADR+1           | (JMPADR)           | (2) =NOP           |

| JMPADR+2           | (JMPADF.+1)        | ( JMPADR)          |

The data flow path has a hard-wired priority over the program control function which increments the address register and thus overrides it as it shifts in the jump address.

3.2.3 <u>Command link override</u>.-- The command module inputs to the program switch exercise hardwired priority over the source dictated by the register setting, and this overriding control is used to take over the MULTIPAC system for reprogramming. An instruction from the telemetry unit will replace any instructions from the normal program stream. The first reprogramming instruction to each logic unit causes the latter to reset its program switch to a blank input where it reads only zeroes.

This is interpreted as a series of no operation (NOP) instructions and the logic unit is effectively disabled. Since only the logic unit itself can address its own program switch, there is no danger of another processor which is still active interfering and restarting it. During the relatively long period while each instruction of the reprogramming bootstrap loader is being received on the command link, the logic units are disabled, but when an instruction has been assembled in the command receiver and transferred to the MULTIPAC command register, it is inserted in the stream of NOP's at the normal instruction rate.

Figure 6 shows the block diagram of the command interface. The command receiver must assemble a digital word of data, and load this word into one of the two CMD registers in the CDS.

The transfer signal dumps the CMD address and CMD data into the proper registers of the CMD module, the data going into the register which is addressable by the processor. The decoding logic addresses one of seven devices in the MULTIPAC system and transfers the data word into one of them, or on decoding the eighth address, sets a flag which is sensed by the program. The latter is the normal method of command input (see paragraph 3.1.4 above).

The seven devices which are addressed are the instruction registers of the three logic units and four of the general purpose registers. These are used for taking control of the MULTIPAC system for reprogramming. The signals from the command receiver to the logic units override those from the program selection switch contained in each logic unit, and the first three instructions in a reprogramming sequence direct each logic unit to set its program select switch to a blank position where only NOP's will be read. Thus, there will be no program action from the logic units except when a telemetry word is directed to one of them. Each word of a bootstrap loader is then read into one of the general purpose registers, followed by an instruction to one of the logic units to store it in one of the memories. Instructions setting and incrementing the memory address are also directed to the logic unit. Once the bootstrap loader has been stored in memory, an instruction is directed to a logic unit to set its program control switch to that memory. From then on the operational program is read in through the usual command input. The loader program detects each new word when it is ready in the CMD register, stores it, and increments memory address. Finally, the override must be employed again to set the program selection switch of each logic unit to the memory into which its program has been loaded.

3.2.4 <u>Interrupts.--</u> Each logic unit has four interrupts which are connected in parallel with those from the other logic units. A 4-bit masking register in each logic unit, called the interrupt enable register, is loaded by special instruction and sensitizes that particular logic unit to the interrupts corresponding to the stages in which it contains ONES. Upon responding to one of the interrupts, the logic unit breaks off the program stream and executes a wired instruction to exchange the contents of the program memory address register with the contents of its own internal register. The latter must initially contain the address of the interrupt routine and afterward will hold the return address. Actually, the contents of the register will be greater by three than the correct return address owing to the overlapping timing and the inhibiting of instruction execution as soon as the interrupt begins. The return address must therefore be corrected before the return to the main program can be accomplished. The program sequence is given below.

| Contents<br>of MA1 | Contents<br>of MD1 | Contents<br>of LIR        | Contents<br>of INTR | Contents<br>of R1 | Interrupt<br>in Process |

|--------------------|--------------------|---------------------------|---------------------|-------------------|-------------------------|

| 100                |                    | ••                        | INTA.DR             |                   | 0                       |

| 101                | (100)              |                           | INTADR              |                   | 0                       |

| 102                | (101)              | (100) LAST EXECUTED INSTR | INTADR              |                   | 0                       |

| 103                | (102)              | (101)                     | INTADR              |                   | 1                       |

| 104                | (103)              | (102) XCH MA1             |                     |                   | 1                       |

| INTADR             | (104)              | (103)                     | 104                 |                   | 1                       |

| INTADR+1           | (INTADR)           | (104)                     | 104                 |                   | 1                       |

|                    | (INTADR+1)         | (INTADR)                  | 104                 |                   | 0                       |

|                    | į                  | (INTADR+1)                | 104                 |                   | 0                       |

|                    |                    | INTERRUPT SUBROUTINE      |                     |                   |                         |

The interrupt lines must also appear as bilevel inputs to the I/O interface in order that they can be tested by the program to see which one occurred. The interrupt routine is also responsible for storing any data which it may destroy.

Since a second interrupt during the interrupt subroutine would destroy the return address, the interrupt enable register is cleared at the start of each interrupt and must be reloaded from a memory image to re-enable the proper interrupts immediately before returning to the main program.

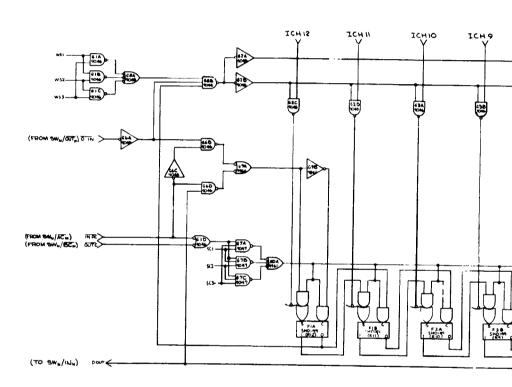

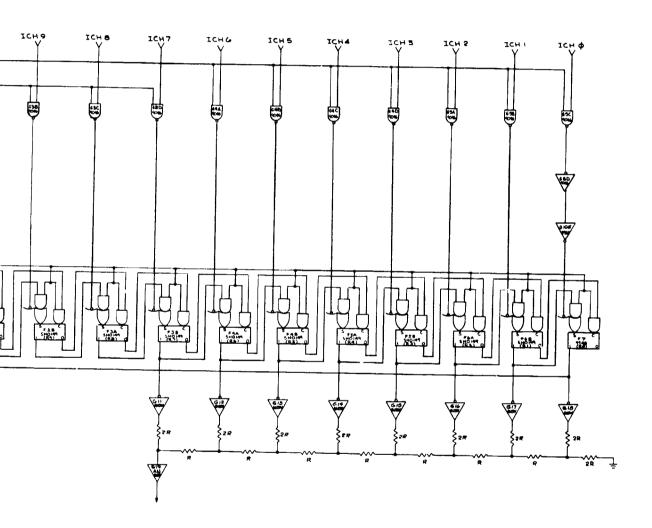

### 4.0 DESCRIPTION OF THE MULTIPAC INTEGRATED CIRCUIT LOGIC DESIGN

In October 1967 a baseline system was established for the detailed logic design and documentation of MULTIPAC in integrated circuit form. It was initially intended to constitute the final MULTIPAC design. However, the increasing development of practical LSI technology together with system improvements discovered in the course of working out the present design, have made it desirable to consider the integrated circuit design reported here as a feasibility study to guide subsequent LSI implementation. This report is, therefore, written as a Research Report on the integrated circuit work rather than a Final Design Report.

#### 4.1 Circuitry

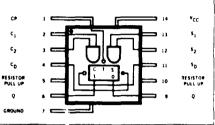

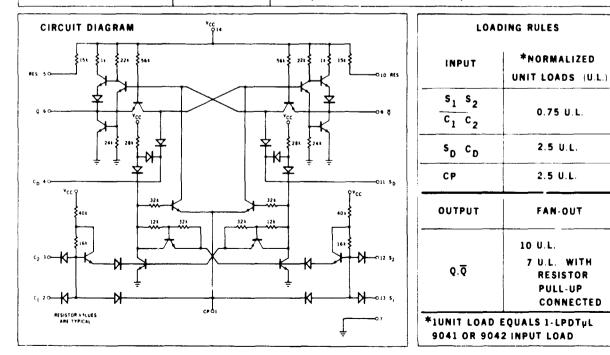

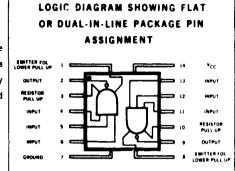

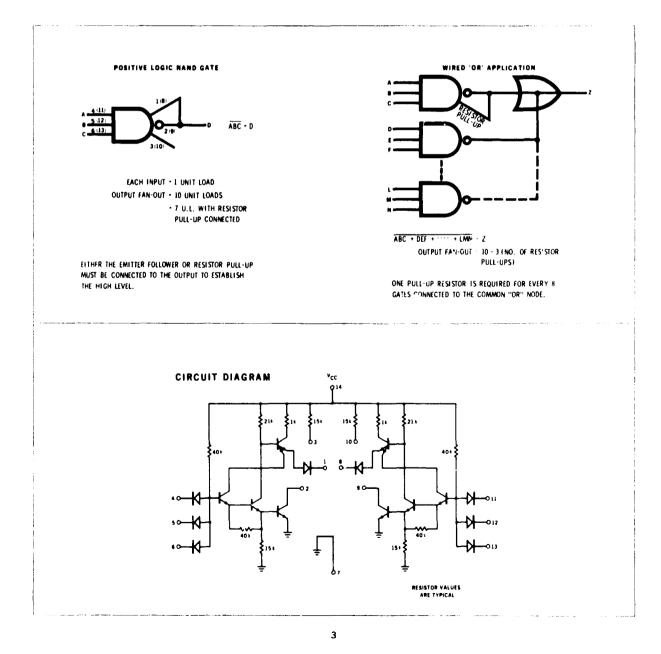

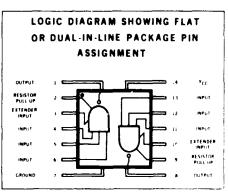

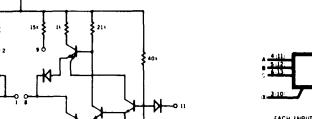

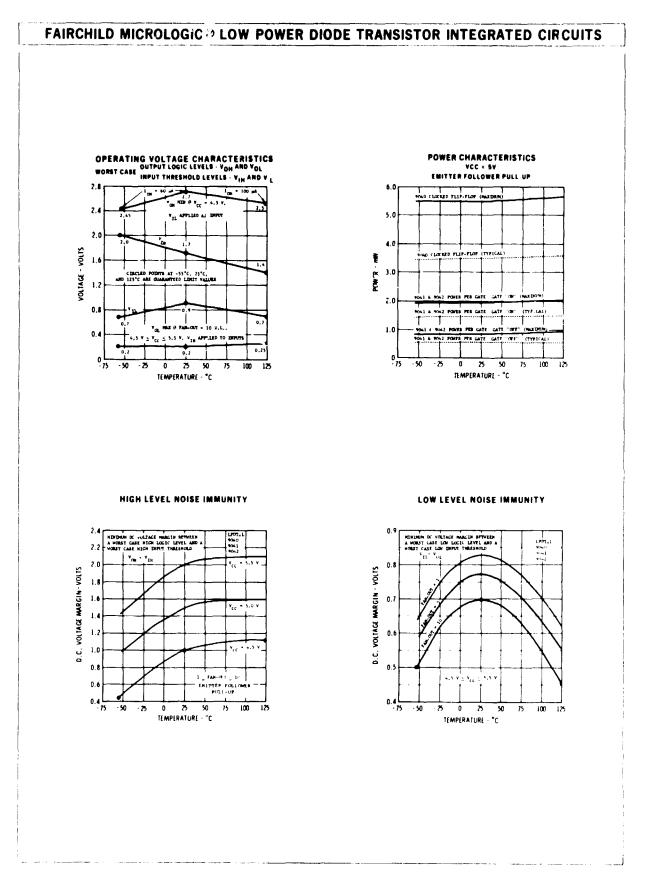

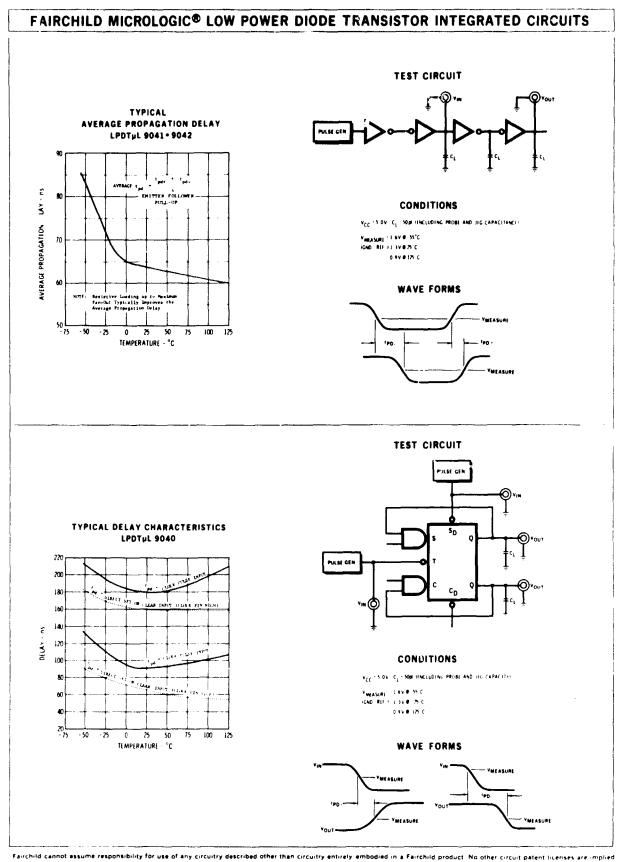

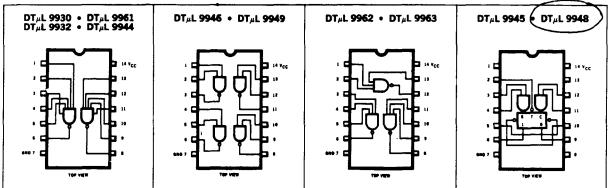

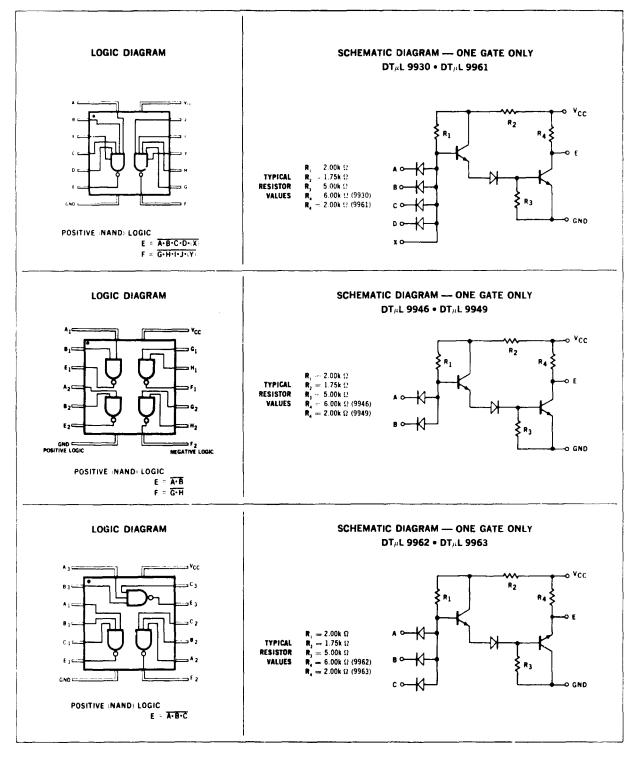

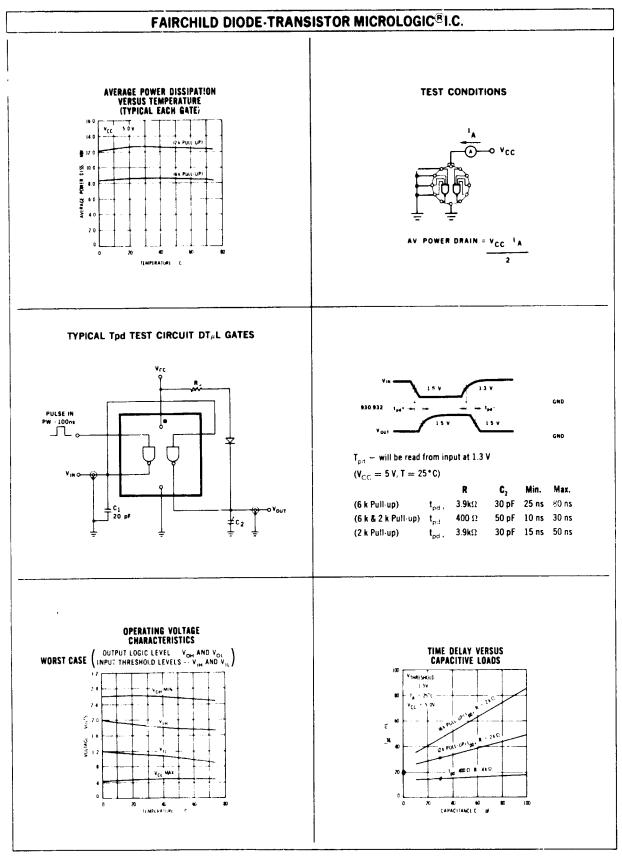

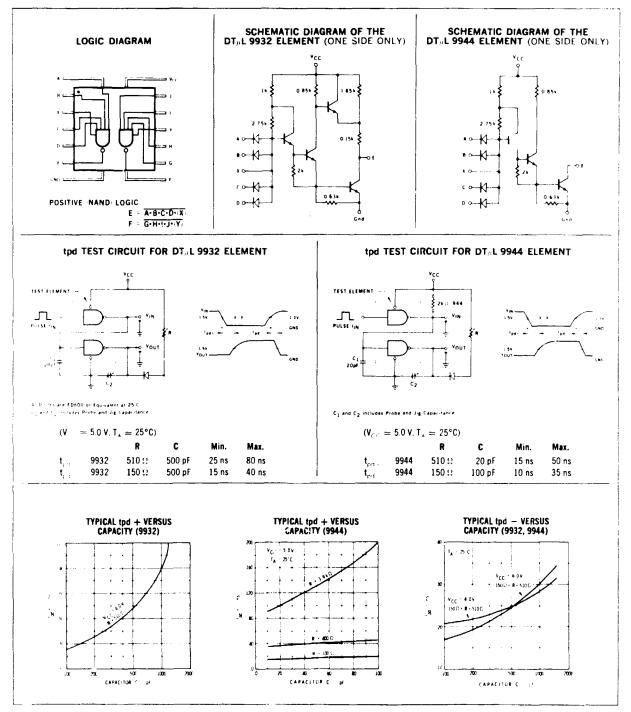

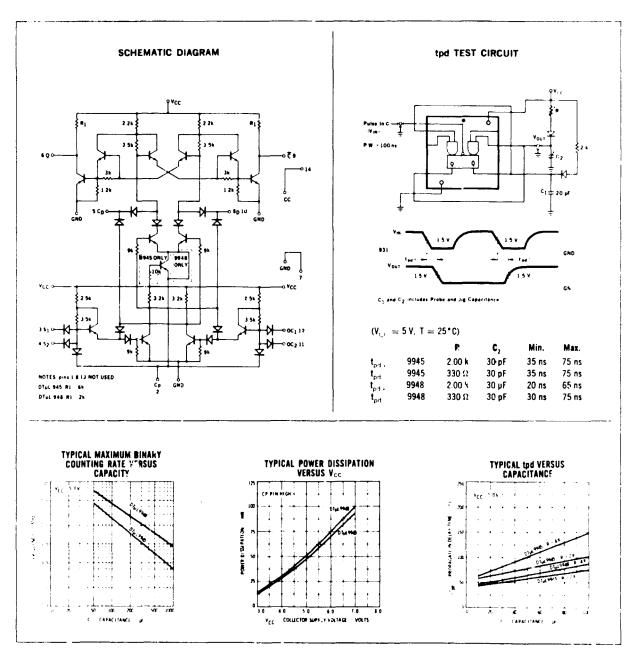

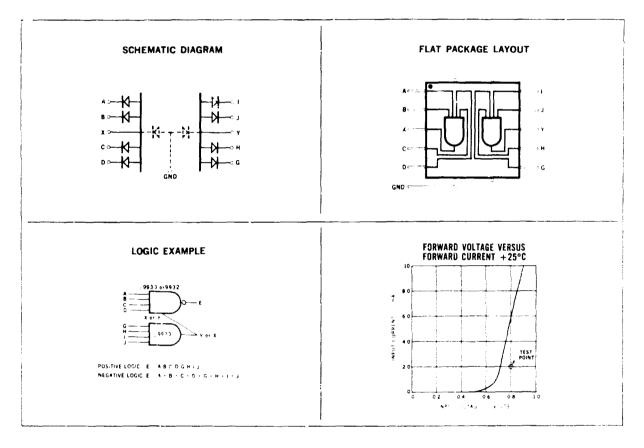

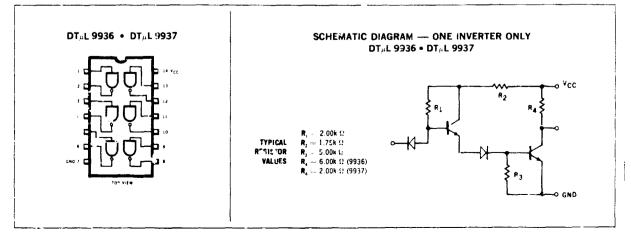

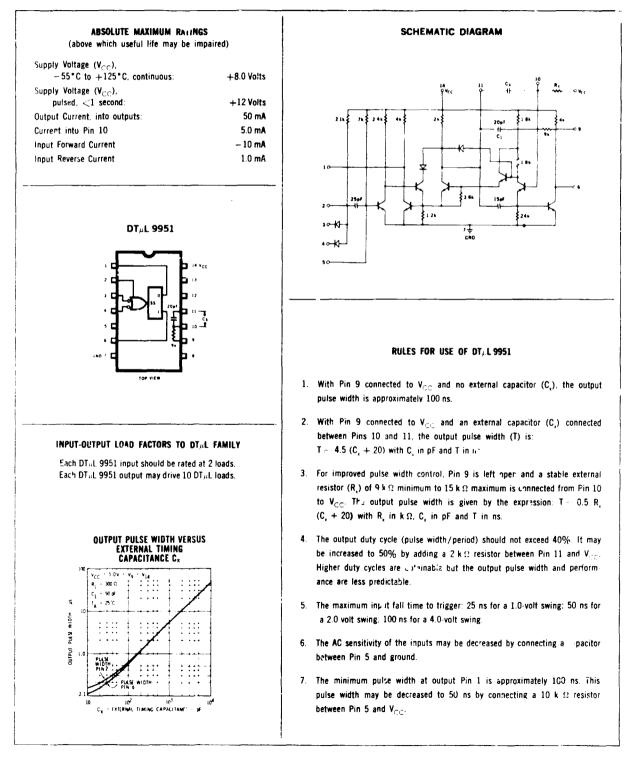

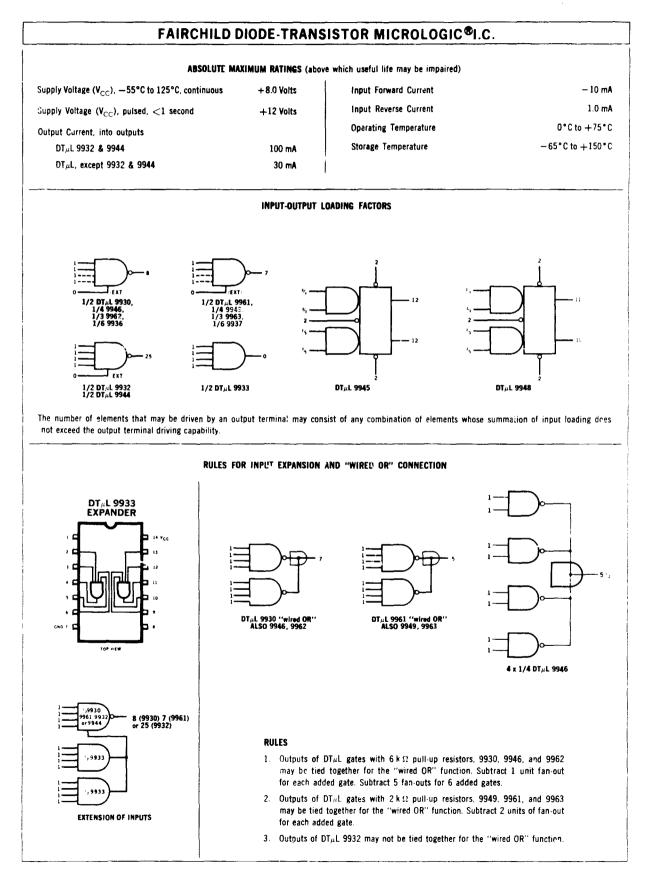

4.1.1 Logic circuits. -- The chief constraint on the choice of integrated circuits for logic was the extremely low power consumption demanded. The Fairchild LPDTµL line was chosen as having the features best suited to the design among the logic families available in the required speed-power class at the time the choice was made.<sup>1</sup> The manufacturer's specifications for those circuits used in the design are included as Appendix C. Other logic families considered were Philco MEL, RCA LPDTL, Amelco 500 Series TTL, Signetics 400 Series TTL, and the several manufacturers' families deriving from Fairchild MWبت. Chief considerations in the selection were 1) lowpower (approximately 1 mw per gate) operation; 2) circuit delay less than 100 nanoseconds; 3) availability of collector-ORed bus drivers; 4) availability of a compatible higher powered, higher speed logic family; and 5) maximum fan-in and fan-out. The Fairchild circuits required the least power of those considered except for the Philco MEL or the lowest powered of the Amelco circuits, and additionally met the remaining criteria better than the latter two. The Amelco circuits which were competitive in power levels with the Fairchild were significantly slower. The Philco family, while exhibiting the best speed/power ratio in the group, included only a very restricted choice of circuits with limited fan-in and fan-out capability. The Fairchild circuits were also in more widespread use, thus offering better statistical data. Two drawbacks of the Fairchild circuits for the MULTIPAC design were noted: 1) The flip-flops required a relatively long clock pulse width which takes in data on the rising edge and outputs on the falling edge. This pulse width must be added as delay into all propagation paths. 2) There is a fan-out of only one when the low-speed circuits drive the high-speed family.

The above matters should all be considered in the choice of LSI ciruitry. However, they should not present the problems in tailored LSI circuitry that they do in working with a standard off-the-shelf family of integrated circuits.

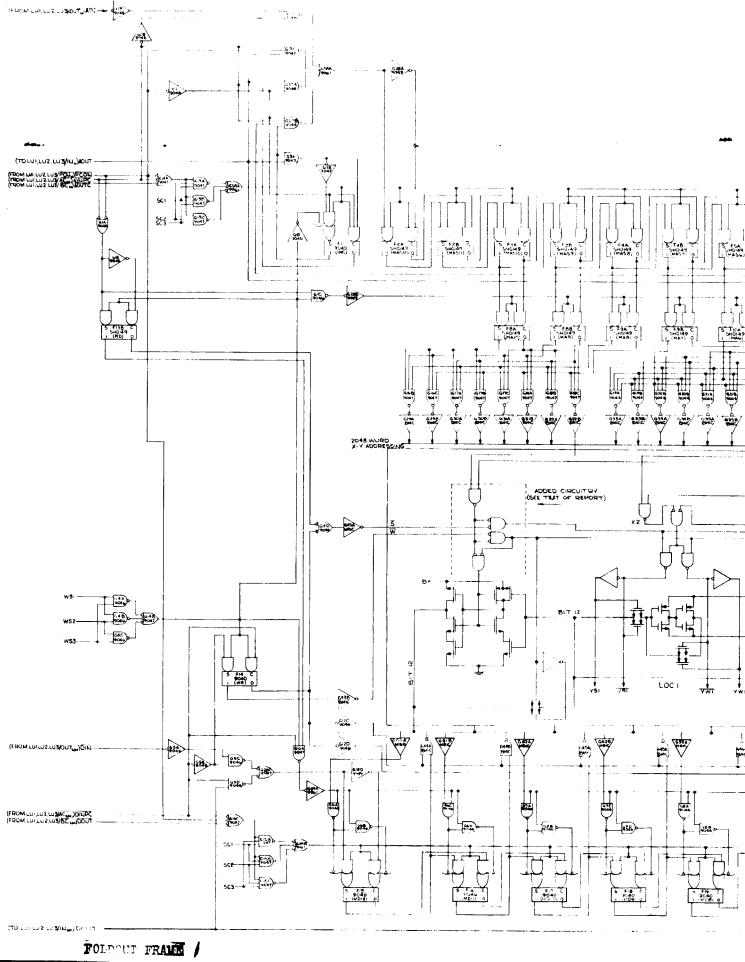

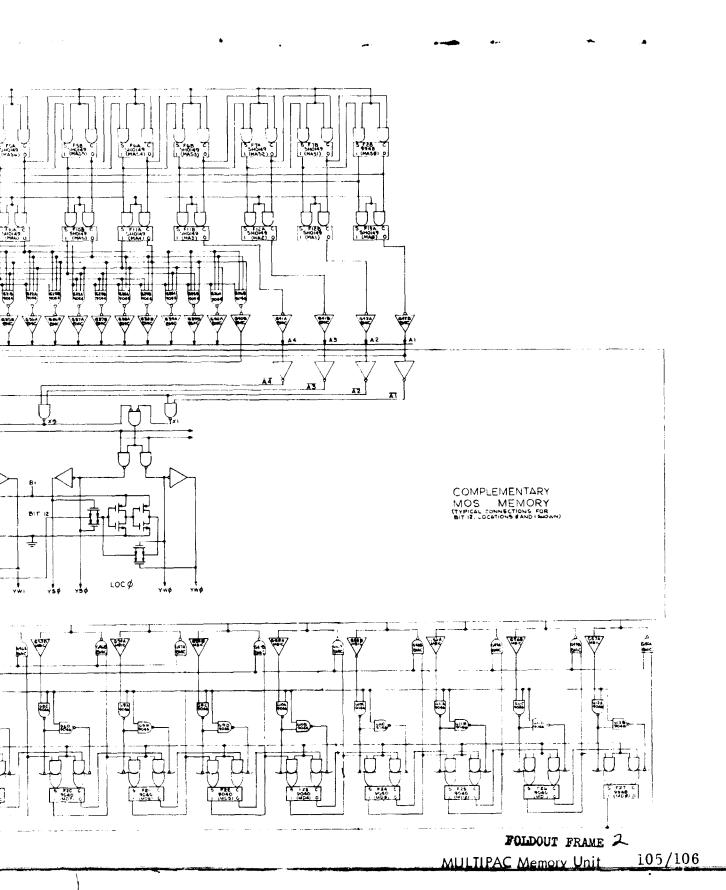

4.1.2 Memory circuits. -- The memory storage medium postulated is a modification of the 256-bit complementary MOS memory ship under development for NASA by Westinghouse on contract No. NAS-5-10243.<sup>2</sup> As with the integrated circuits, the chief reason for this choice was the low power drain of this medium. In a flip-flop memory, one important consideration is the power required to maintain the memory contents under dc conditions. Standby power required for this MOS circuitry is reported as typically less than one nanowatt per cell, which would be approximately .026 milliwatts for a 2048-word, 13-bit memory. This is negligible compared to the operating power of the one chip in the memory selected by the addressing logic, which is reported as 30 milliwatts for the present device containing 16 words of 16 bits each when cycled at a 0.5-MHz rate. If this were scaled to a 13-bit word with a 16-microsecond cycle time, the indications are that the 2048-word memory would consume on the order of 3 milliwatts. This power is, in turn, negligible compared to that required by the bipolar portions of the memory module, especially the circuits interfacing the MOS chip. These would probably require special design to minimize their power consumption.