# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

**Final Report**

# DEVELOP MENT OF A MICROELECTRONIC MODULE

By H. Strack, F. Doerbeck, E. Harp, and E. Mehal

November 1968

DISTRIBUTION OF THIS REPORT IS PROVIDED IN THE INTEREST OF INFORMATION EXCHANGE AND SHOULD NOT BE CONSTRUED AS ENDORSEMENT BY NASA OF THE MATERIAL PRESENTED. RESPONSIBILITY FOR THE CONTENTS RESIDES WITH THE ORGANIZATION THAT PREPARED IT.

Prepared under Contract No. NAS 12-537 by

TEXAS INSTRUMENTS INCORPORATED Components Group Dallas, Texas

?

for

**Electronics Research Center**

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

| 5   | N69-2409                      | 3          |

|-----|-------------------------------|------------|

| ž   | (ACCESSION NUMBER)            | (THRU)     |

| 101 | /04                           |            |

| Ē   | (PAGES)                       | (CODE      |

| PAC | $CR^{-}\lambda U144$          |            |

|     | INASA CR OR TMX OR AD NUMBERI | (CATEGORY) |

**Final Report**

# DEVELOPMENT OF A MICROELECTRONIC MODULE

ŀ

-

ς,

By H. Strack, F. Doerbeck, E. Harp, and E. Mehal

November 1968

DISTRIBUTION OF THIS REPORT IS PROVIDED IN THE INTEREST OF INFORMATION EXCHANGE AND SHOULD NOT BE CONSTRUED AS ENDORSEMENT BY NASA OF THE MATERIAL PRESENTED. RESPONSIBILITY FOR THE CONTENTS RESIDES WITH THE ORGANIZATION THAT PREPARED IT.

Prepared under Contract No. NAS 12-537 by

TEXAS INSTRUMENTS INCORPORATED Components Group Dallas, Texas

for

**Electronics Research Center**

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# FOREWORD

| Contract No.           | NAS 12-537                                                                                          |

|------------------------|-----------------------------------------------------------------------------------------------------|

| Agency:                | National Aeronautics and<br>Space Administration<br>Electronics Research Center<br>Cambridge, Mass. |

| Contractor:            | Texas Instruments Incorporated<br>Components Group<br>P.O. Box 5012<br>Dallas, Texas 75222          |

| Technical Monitor:     | Dr. K. Haq                                                                                          |

| Report Period:         | 1 April 1967 through 30 September 1968                                                              |

| Date Submitted:        | November 1968                                                                                       |

| Contractors Report No: | 03-68-80                                                                                            |

,

:

## TABLE OF CONTENTS

| SECTION | TITLE                                                                                                | PAGE |

|---------|------------------------------------------------------------------------------------------------------|------|

| I.      | INTRODUCTION                                                                                         | 1    |

|         | MATERIAL PREPARATION                                                                                 | 3    |

|         | A. General                                                                                           | 3    |

|         | B. Vapor Phase Epitaxial GaAs                                                                        | 3    |

|         | 1. Halide Transport System (Sn-Doping)                                                               | 3    |

|         | 2. Halide Transport System (S-Doping)                                                                | 7    |

|         | 3. Water Vapor Transport System (Undoped)                                                            | 7    |

|         | 4. Elemental Source System (Ge-Doping)                                                               | 7    |

|         | C. Solution Epitaxial GaAs                                                                           | 10   |

|         | D. Bulk Material                                                                                     | 12   |

| III.    | CATHODOLUMINESCENCE STUDIES ON GaAs                                                                  | 15   |

|         | A. General                                                                                           | 15   |

|         | B. Theory                                                                                            | 15   |

|         | C. Experimental Arrangement                                                                          | 23   |

|         | D. Results $\ldots$ | 26   |

|         | 1. Comparison of Epitaxial Materials Used for Device Fabrication                                     | 27   |

|         | 2. Studies on the Spatial Distribution of Cathodoluminescent Light                                   | 30   |

|         | 3. Dependence of Materials Parameter on the Ga: As Ratio                                             | 32   |

| IV.     | DEVICE FABRICATION                                                                                   | 35   |

|         | A. General                                                                                           | 35   |

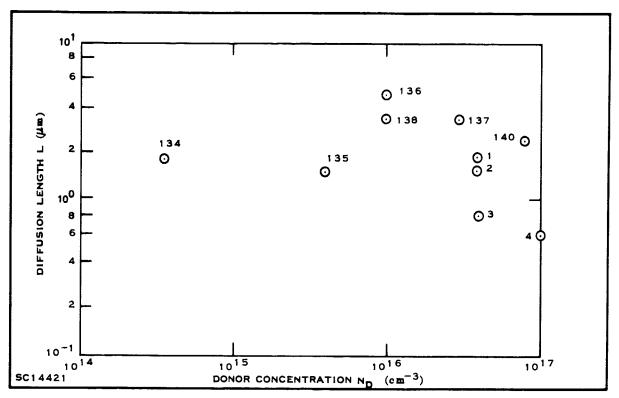

|         | B. The Fabrication of NPN Mesa Transistors by Standard Process                                       | 35   |

|         | 1. Base Formation                                                                                    | 35   |

|         | 2. Emitter Diffusion                                                                                 | 37   |

|         | 3. Metal Contacts                                                                                    | 37   |

|         | 4. Final Processing                                                                                  | 38   |

|         | C. Special Fabrication Runs                                                                          | 38   |

|         | 1. Passivated Transistors (Planar).                                                                  | 38   |

|         | 2. Transistors with Zinc-Doped Base Region                                                           | 38   |

|         | 3. Transistors with Zinc Added to the Emitter                                                        | 39   |

|         | 4. Experiments Using Si-Doped Bulk GaAs Slices and Double                                            |      |

|         | Oxide Techniques                                                                                     | 39   |

|         | 5. Experiments with S Plus Cd-Doped Epitaxial Layers                                                 | 39   |

|         | 6. Fabrication of PNP Transistors                                                                    | 40   |

|         | D. Fabrication of Diodes                                                                             | 40   |

|         | 1. Diodes in P-Type GaAs                                                                             | 40   |

|         | 2. Diodes in N-Type GaAs                                                                             | 40   |

# TABLE OF CONTENTS (Continued)

# SECTION

# TITLE

# PAGE

:

•"

|       | E.  | Field Effect Transistors    41        |

|-------|-----|---------------------------------------|

| V.    | DE  | VICE MEASUREMENTS                     |

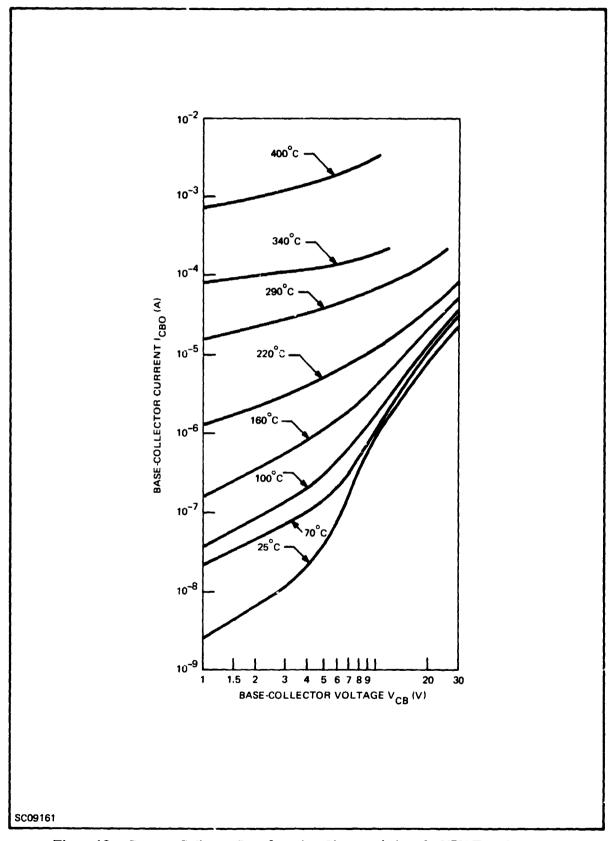

|       | A.  | Reverse Leakage Currents    43        |

|       |     | 1. Transistor Junctions               |

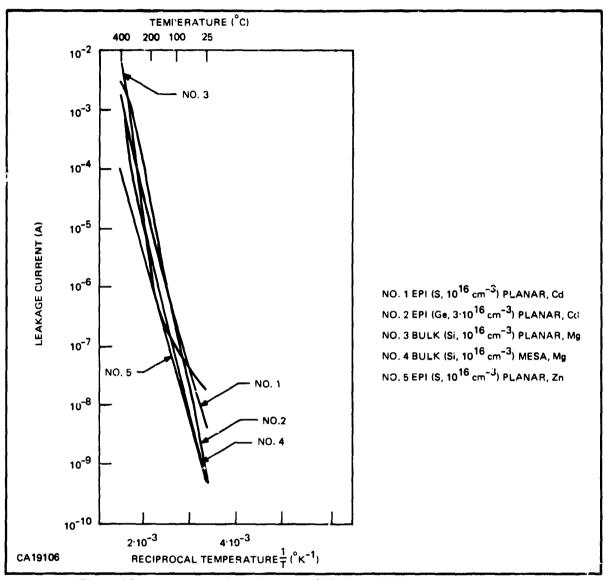

|       |     | 2. Diffused Diode Junctions           |

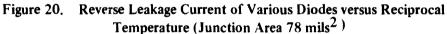

|       |     | 3. Solution-Grown Junctions           |

|       | B.  | DC Characteristics of NPN Transistors |

|       | C.  | DC Characteristics of PNP Transistors |

|       | D.  | Large Signal Characteristics    62    |

|       | Ε.  | Field-Effect Transistors    66        |

|       | F.  | Silicon Transistors                   |

| VI.   | DE  | VICE STABILITY                        |

|       | Α.  | Basic Limitations on Stability        |

|       | В.  | Device Stability                      |

| VII.  | CIR | CUITS                                 |

|       | Α.  | General                               |

|       | B.  | Thick-Film Circuits    81             |

|       |     | 1. Circuit Description                |

|       |     | 2. Circuit Design and Operation       |

|       |     | 3. Circuit Tests                      |

|       | C.  | Thin-Film Circuits    86              |

|       |     | 1. Circuit Description         86     |

|       |     | 2. Circuit Design and Operation       |

|       |     | 3. Circuit Tests                      |

| VIII. | SUN | MMARY                                 |

| IX.   | RE  | FERENCES                              |

# LIST OF ILLUSTRATIONS

:

;

ł

•

| FIGURE | TITLE                                                                   |   |   |   | PAGE |

|--------|-------------------------------------------------------------------------|---|---|---|------|

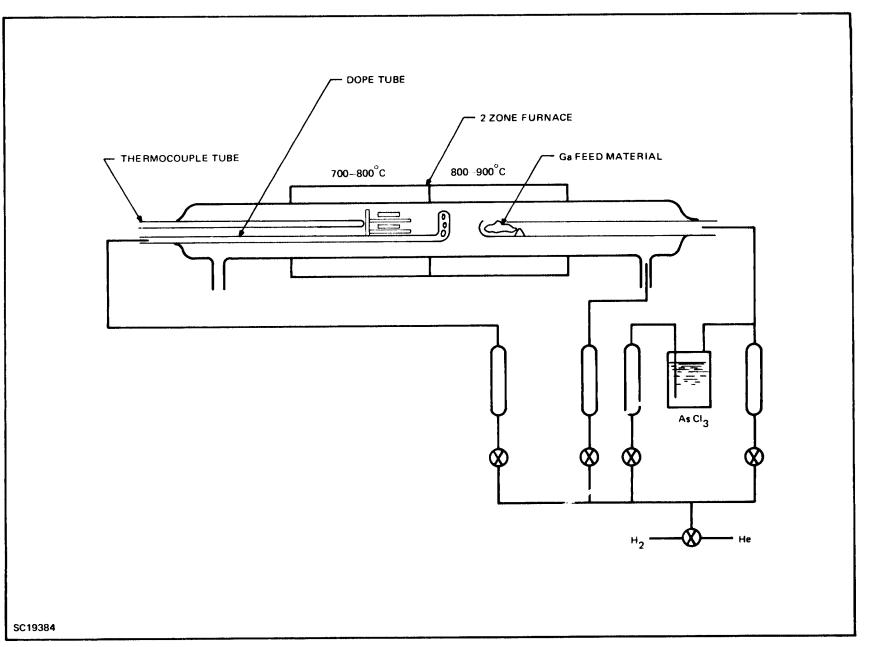

| 1.     | Epitaxial Reactor                                                       |   |   |   | 5    |

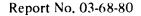

| 2.     | Diffusion Cell Used for Tin Doping                                      |   |   |   | 6    |

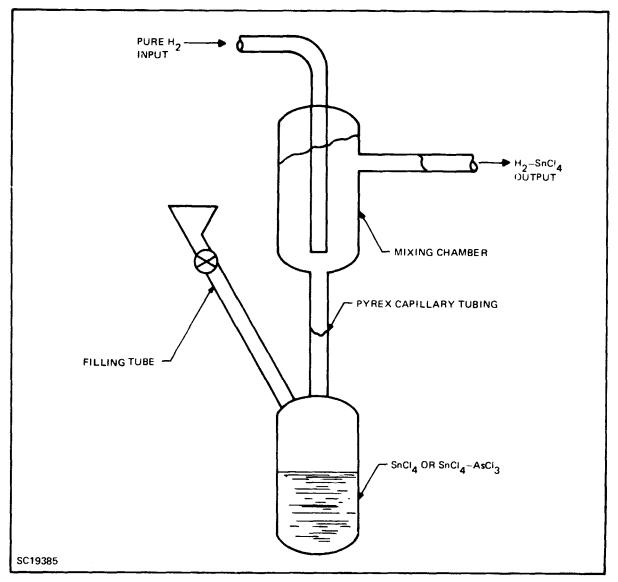

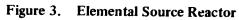

| 3.     | Elemental Source Reactor                                                |   |   |   | 8    |

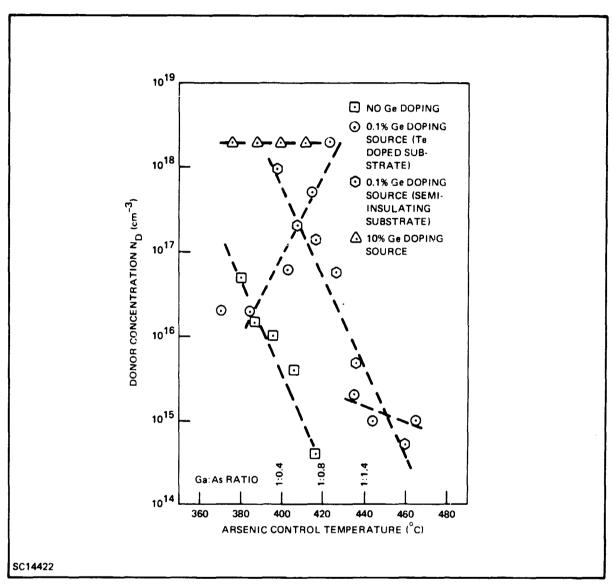

| 4.     | Donor Concentration versus Arsenic Control Temperature                  |   |   |   | 10   |

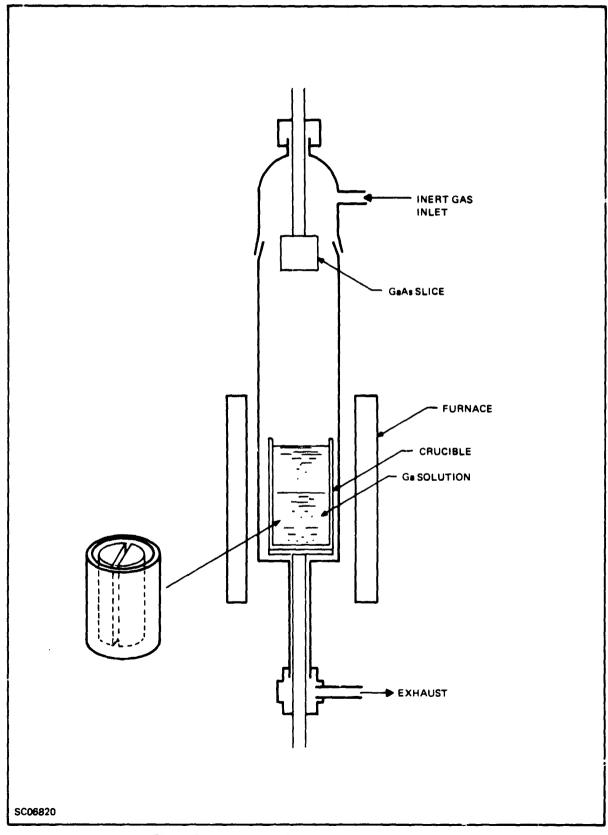

| 5.     | Apparatus for Solution Growth of GaAs                                   |   |   |   | 11   |

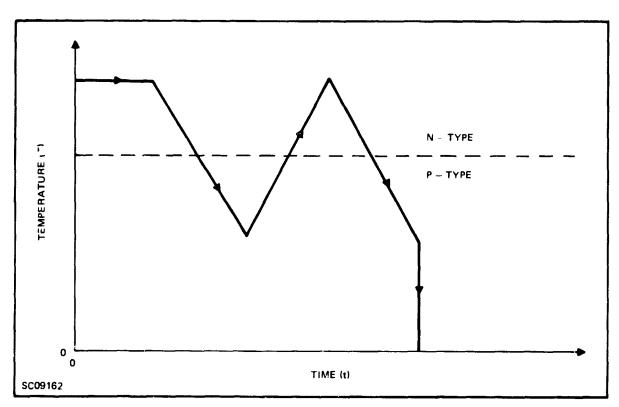

| 6,     | Growth Cycle for Fabrication on P-N-P-N Layers                          |   |   |   | 12   |

| 7.     | Electron Concentration as a Function of the Tin Concentration           |   |   |   |      |

|        | in (111) and (100) Grown GaAs                                           |   |   |   | 14   |

| 8.     | Electron-Beam Penetration in GaAs                                       |   |   |   | 18   |

| 9.     | Normalized Cathodoluminescence Intensity as a Function of               |   |   |   |      |

|        | the Electron. bsorption Constant Multiplied by the                      |   |   |   |      |

|        | Diffusion Length                                                        |   |   |   | 20   |

| 10.    | Logarithmic Derivation of the Cathodoluminescence Intensity             |   |   |   |      |

|        | as a Function of the Electron-Absorption Constant                       |   |   |   |      |

|        | Multiplied by the Diffusion Length                                      |   |   |   | 22   |

| 11.    | Diagram of the Electron Microprobe                                      |   |   |   | 24   |

| 12.    | Intensity of Cathodoluminescence as a Function of                       |   |   |   |      |

|        | Accelerating Voltage (Epitaxial Material)                               |   | • |   | 28   |

| 13.    | Logarithmic Derivation of the Cathodoluminescence Intensity             |   |   |   |      |

|        | as a Function of the Square of the Reciprocal Voltage                   |   |   |   |      |

|        | (Epitaxial Material)                                                    |   |   |   | 29   |

| 14.    | Spatial Distribution of Cathodoluminescence Light                       | • | • | • | .31  |

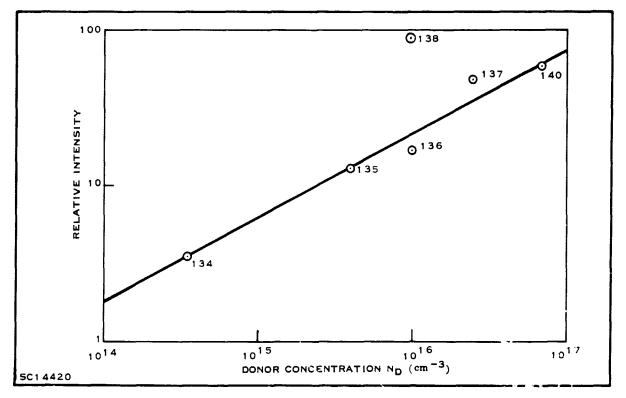

| 15.    | Cathodoluminescence Intensity versus Donor Concentration                |   |   |   | 32   |

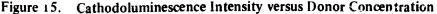

| 16.    | Diffusion Length versus Donor Concentration                             |   |   |   | 34   |

| 17.    | Cross-Section Views of GaAs Transistors                                 | • | • | • | 36   |

| 18.    | GaAs FET Structure (Gate Length $10 \mu$ m, Length to Width             |   |   |   |      |

|        | Ratio 275)                                                              | • | • | • | 41   |

| 19.    | Reverse Collector-Base Junction Characteristics of a NPN                |   |   |   |      |

|        | Transistor at Various Temperatures (Junction Area 90 mil <sup>2</sup> ) | • | • | • | 44   |

| 20.    | Reverse Leakage Current of Various Diodes versus Reciprocal             |   |   |   |      |

|        | Temperature (Junction Area 78 mils <sup>2</sup> )                       | • | • | • | 47   |

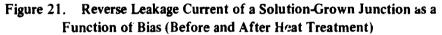

| 21.    | Reverse Leakage Current of a Solution Grown Junction as a               |   |   |   |      |

|        | Function of Bias (Before and After Heat Treatment)                      | · | • | • | 48   |

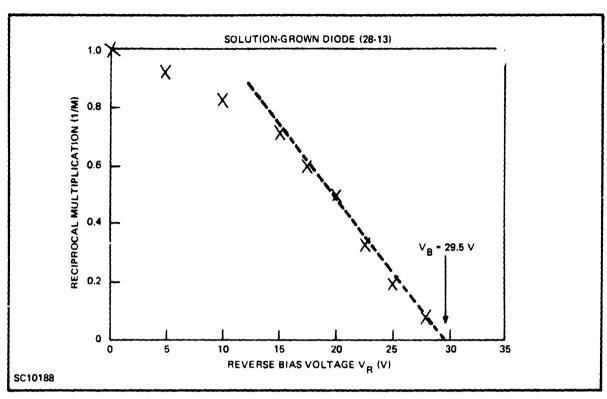

| 22.    | Reciprocal Multiplication as a Function of the Reverse Bias             |   |   |   |      |

|        | for a Solution Grown Diode                                              |   | • |   | 49   |

# LIST OF ILLUSTRATIONS (Continued)

# FIGURE

# TITLE

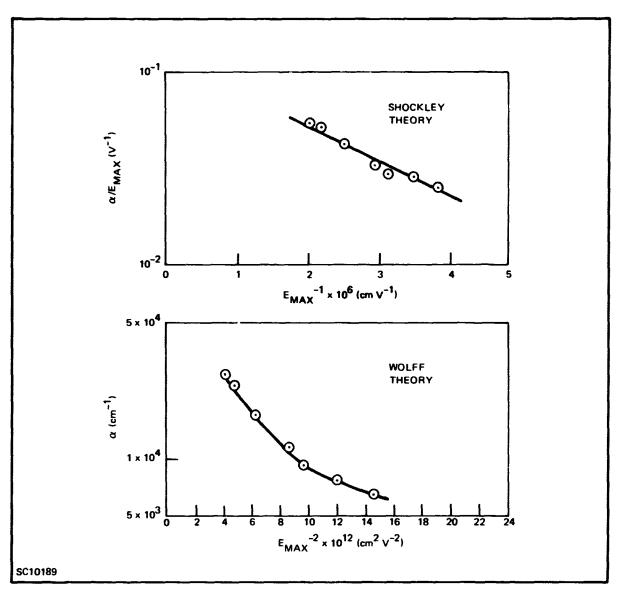

| 23. | Ionization Coefficient for GaAs as a Function of the Electron Field                                         |    |

|-----|-------------------------------------------------------------------------------------------------------------|----|

|     | According to Shockley's and Wolff's Theory                                                                  | 50 |

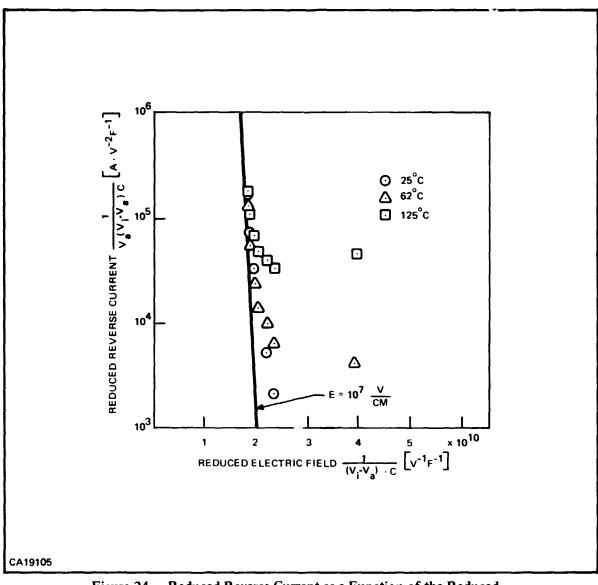

| 24. | Reduced Reverse Current as a Function of the Reduced Electron Field                                         |    |

|     | for a Solution Grown Diode                                                                                  | 51 |

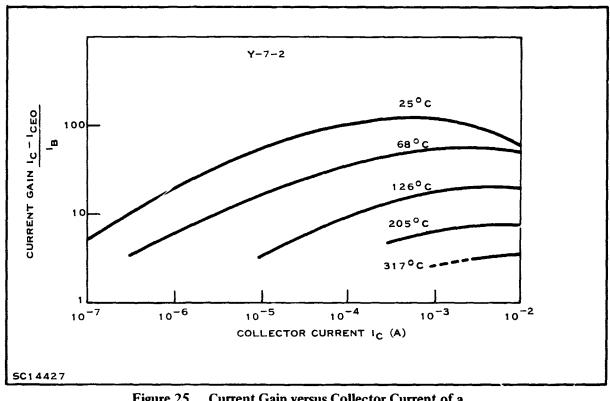

| 25: | Current Gain versus Collector Current for a NPN GaAs Transistor at                                          |    |

|     | Various Temperatures                                                                                        | 53 |

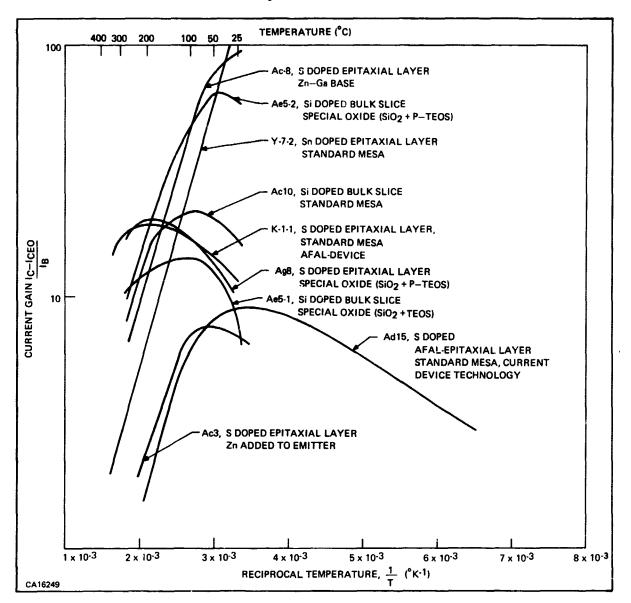

| 26. | Current Gain versus Reciprocal Temperature of Various NPN GaAs Transistors                                  |    |

|     | Using Different Crystal Materials and Technologies                                                          | 54 |

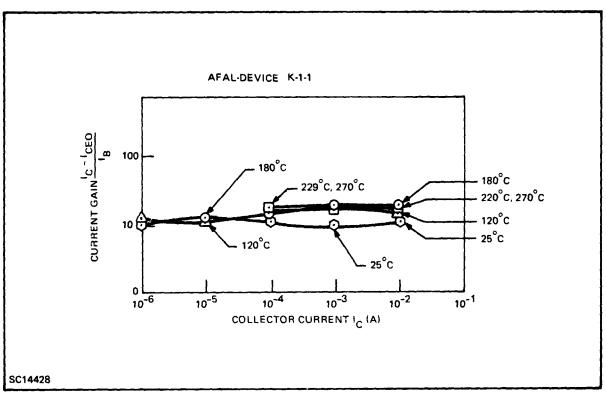

| 27. | Current Gain versus Collector Current of a NPN GaAs Transistor                                              |    |

|     | (AFAL-Device)                                                                                               | 55 |

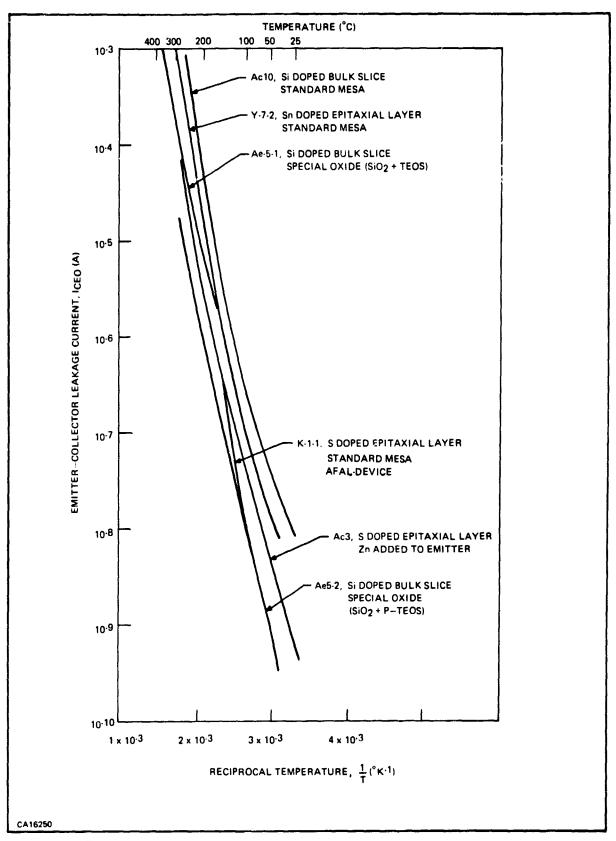

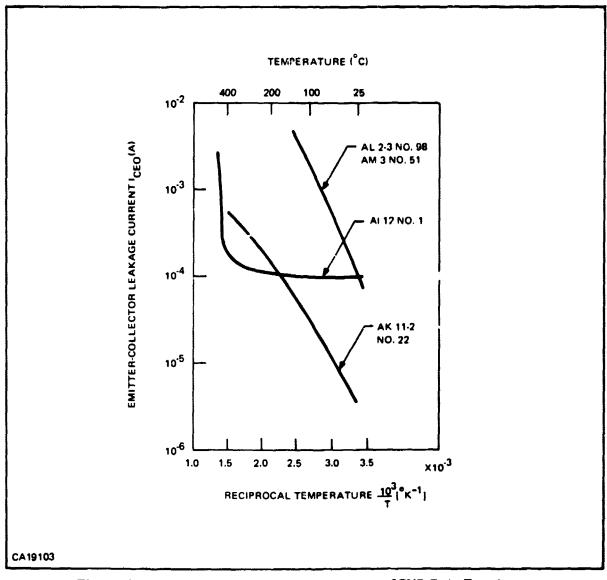

| 28. | I <sub>CEO</sub> versus Reciprocal Temperature for various GaAs NPN Transistors using                       |    |

|     | Different Crystal Materials and Technologies. (The Collector-Junction                                       |    |

|     | Area is 90 mils <sup>2</sup> for Device Y-7-2 and 56 mils <sup>2</sup> for all other Devices). $\therefore$ | 57 |

| 29. | ICEOversus Reciprocal Temperatures of PNP GaAs Transistors                                                  |    |

|     | (Collector Junction area 56 mils <sup>2</sup> )                                                             | 59 |

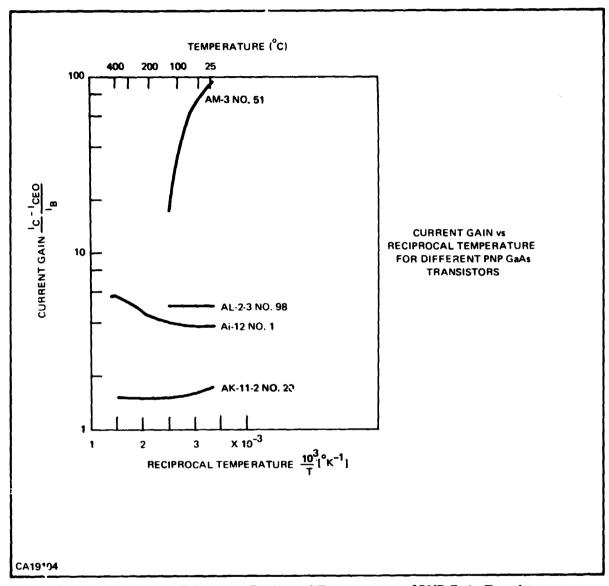

| 30. | Current Gain versus Reciprocal Temperatures of PNP GaAs Transistors                                         | 60 |

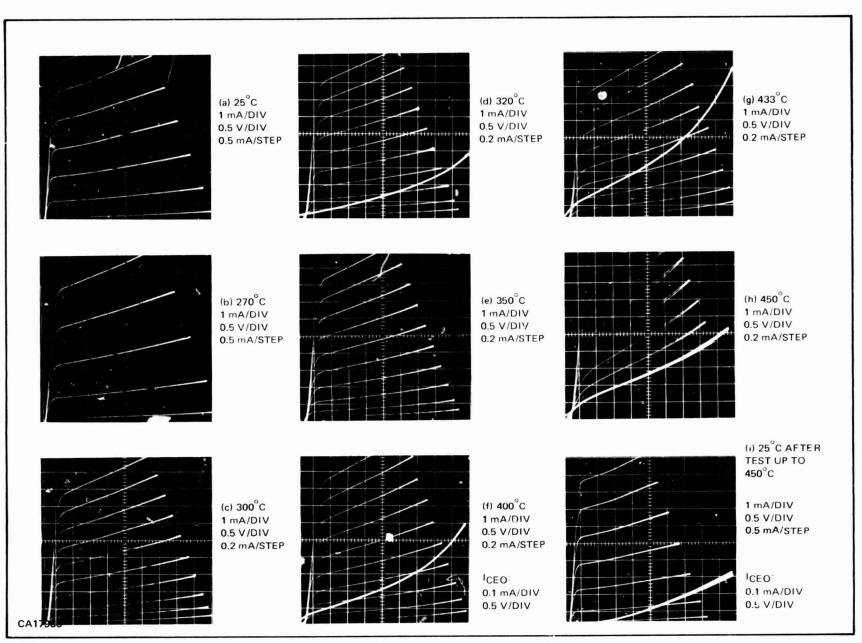

| 31. | Performance of a PNP GaAs Transistor at Different Temperatures                                              | 61 |

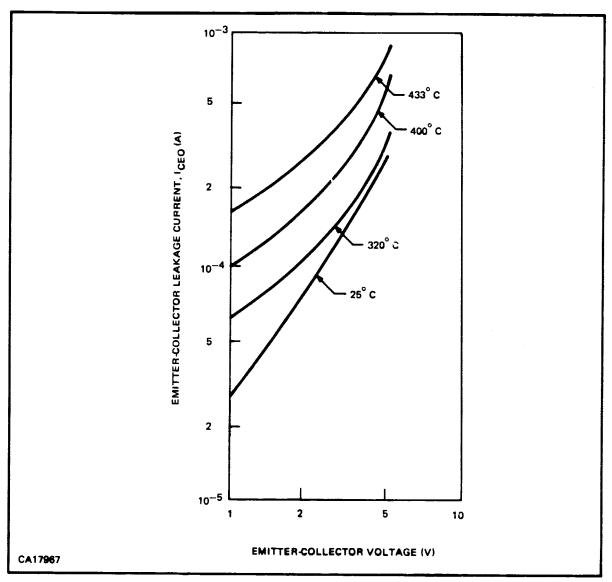

| 32. | Emitter-Collector Leakage versus Emitter-Collector Voltage of a PNP GaAs                                    |    |

|     | Transistor at Different Temperatures (Collector-Base Junction Area                                          |    |

|     | 56 mils <sup>2</sup> )                                                                                      | 62 |

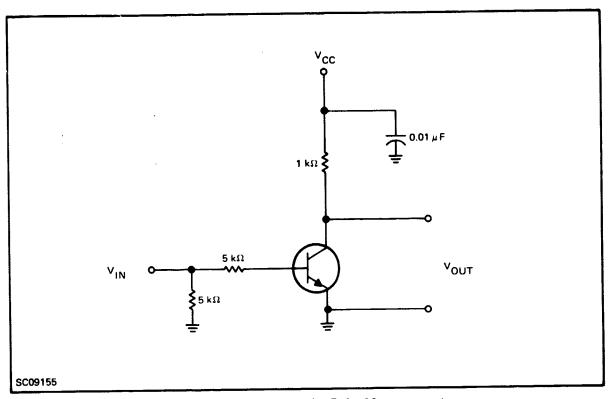

| 33. | Test Circuit for Pulse Measurements                                                                         | 63 |

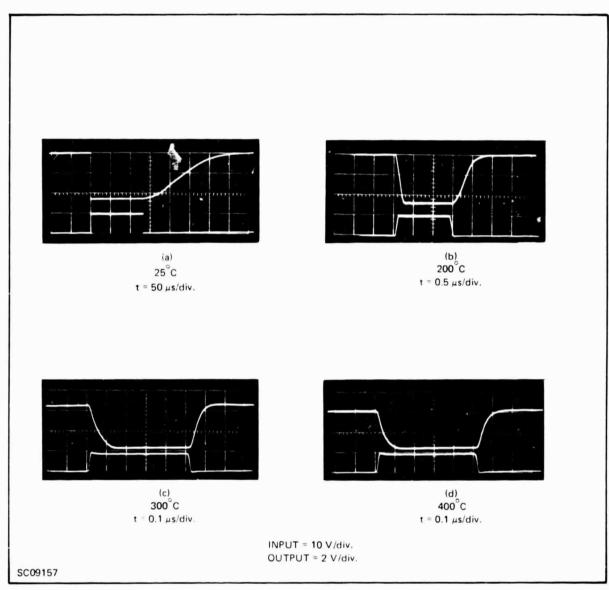

| 34. | Common-Emitter Pulse Measurements at Various Temperatures                                                   | 65 |

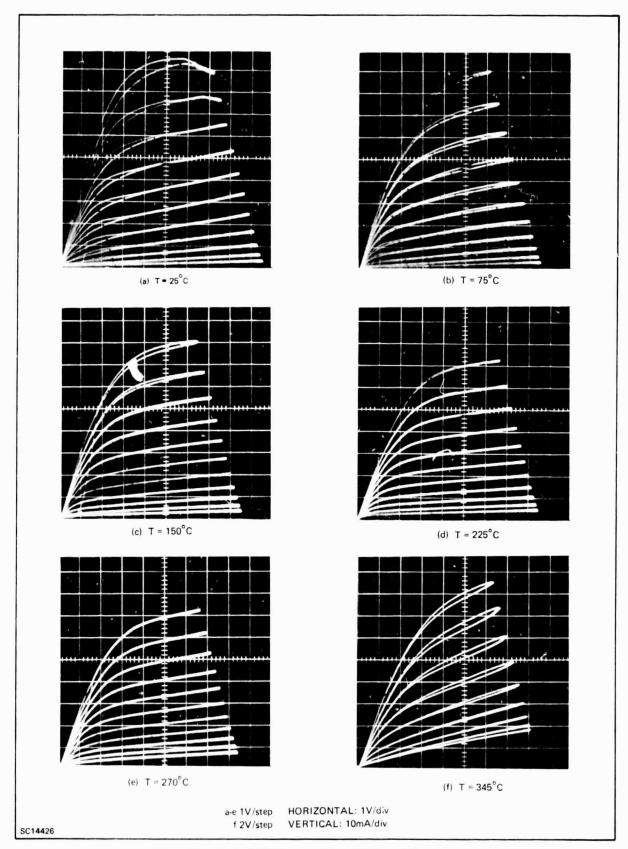

| 35. | GaAs FET Characteristics at Different Temperatures                                                          | 67 |

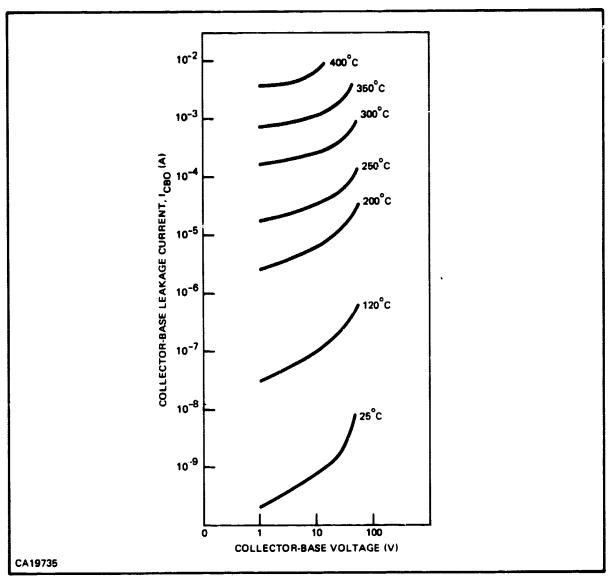

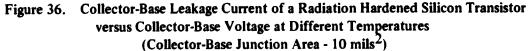

| 36. | Collector-Base Leakage Current of a Radiation Hardened Silicon Transistor                                   |    |

|     | versus Collector-Base Voltage at Different Temperatures (Collector-Base                                     |    |

|     | Junction Area - 10 mils <sup>2</sup> )                                                                      | 70 |

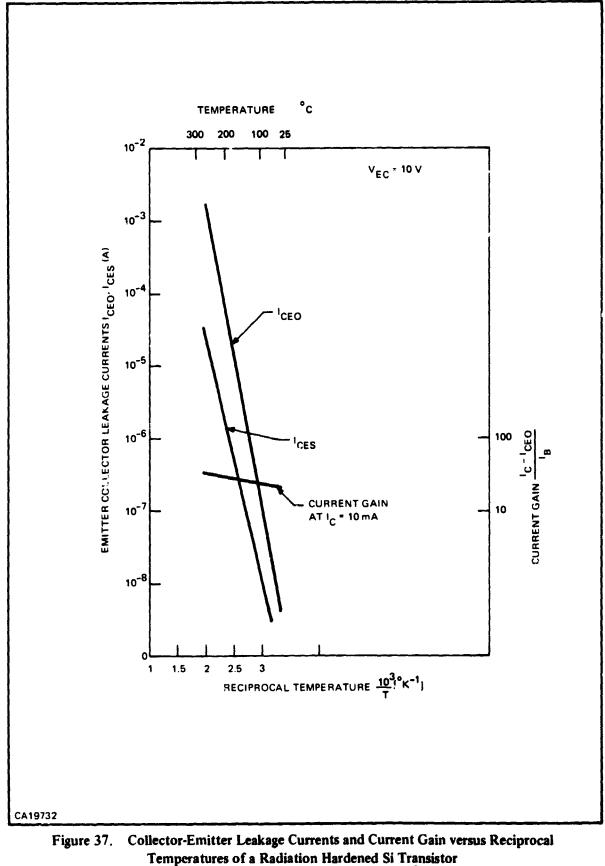

| 37. | Collector-Emitter Leakage Currents and Current Gain versus Reciprocal                                       |    |

|     | Temperatures of a Radiation Hardened Si Transistor (Collector-Base                                          |    |

|     | Junction Area - 10 mils <sup>2</sup> )                                                                      | 71 |

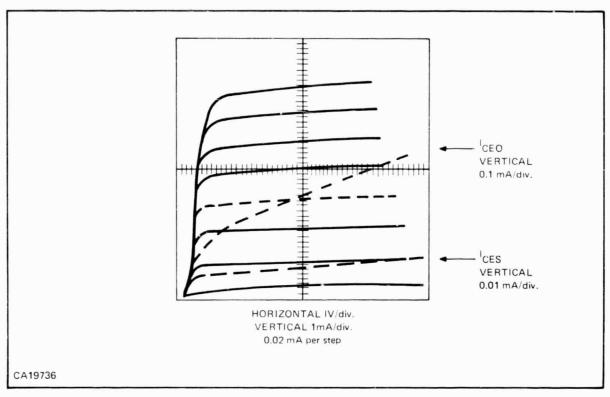

| 38. | Transistor Characteristics of a Radiation Hardened Si Transistor at 230°C                                   | 72 |

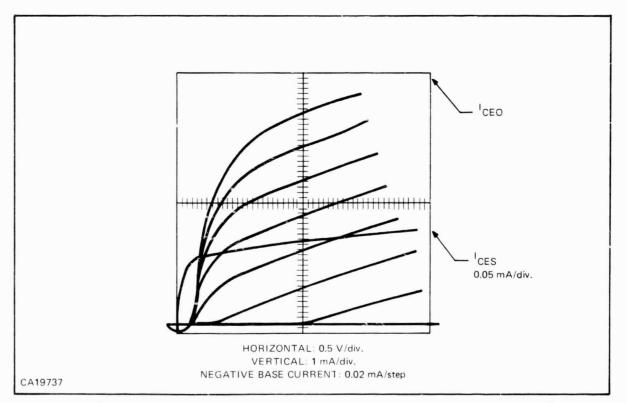

| 39. | Transistor Characteristics of a Radiation Hardened Si Transistor at 300°C                                   | 72 |

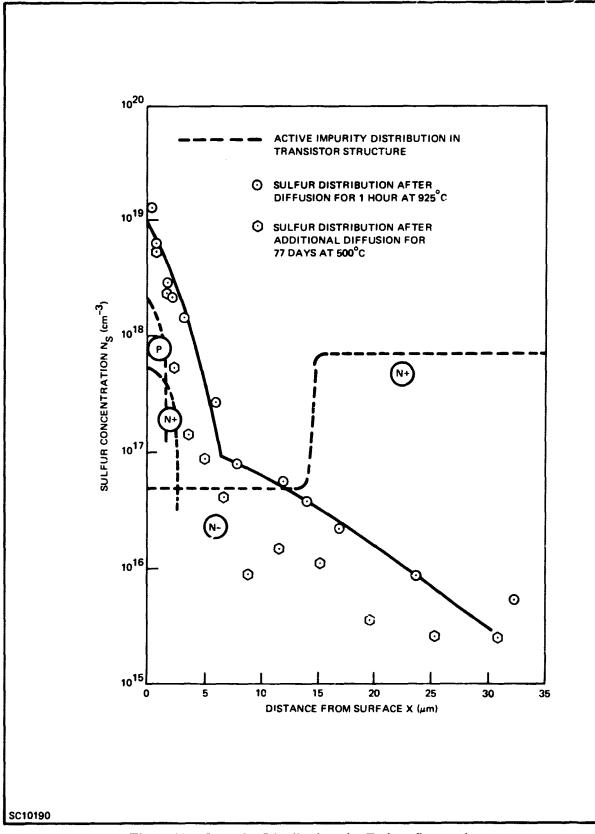

| 40. | Inpurity Distribution for Emitter-Base and Collector Dopants in NPN                                         |    |

|     | GaAs Transistors                                                                                            | 74 |

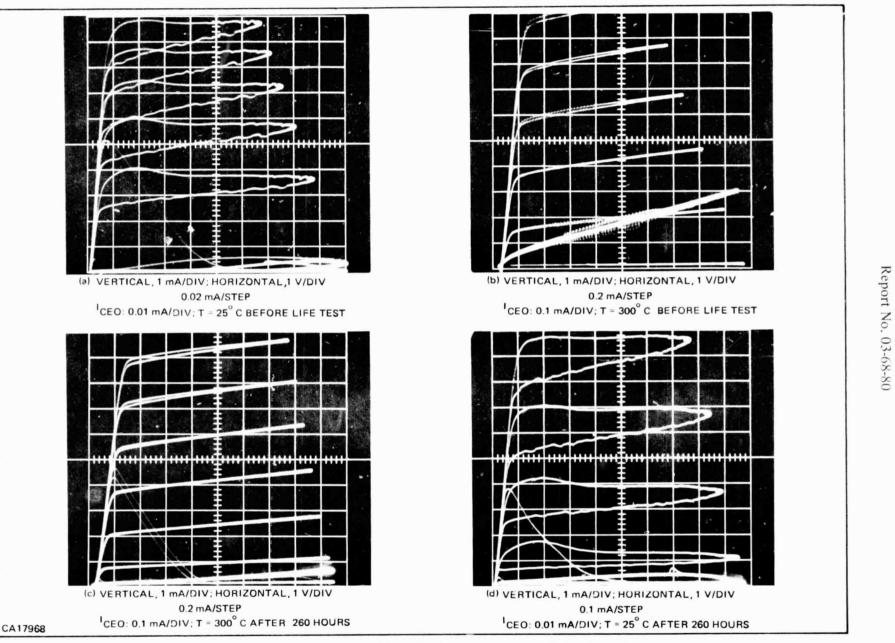

| 41. | Performance of NPN GaAs Transistor at 20°C and 300°C Before and After                                       |    |

|     | Life Test at 300°C for 260 Hours                                                                            | 77 |

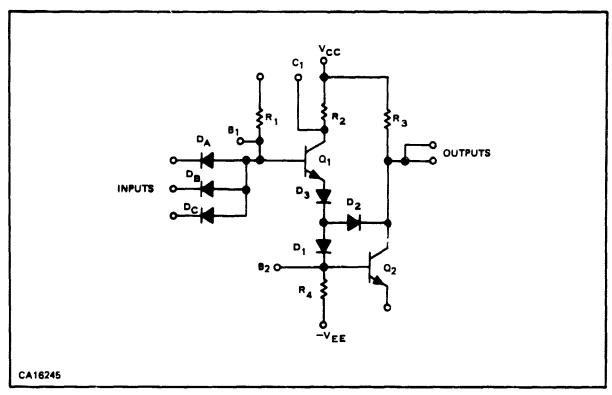

| 42. | Basic NAND Gate Circuit                                                                                     | 82 |

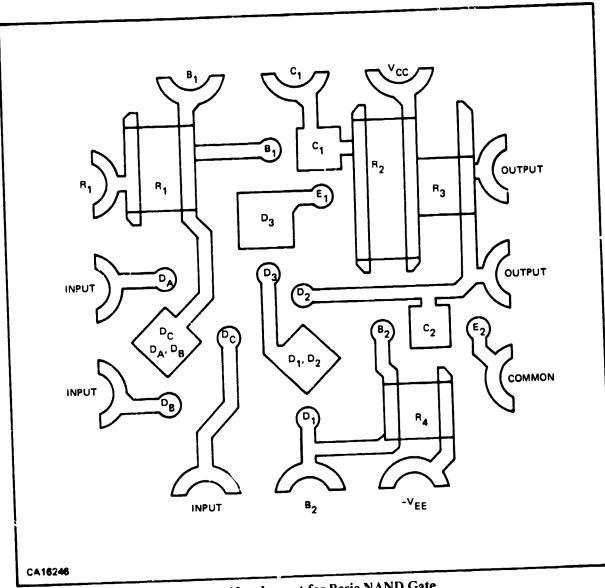

| 43. | Layout for Basic NAND Gate                                                                                  | 83 |

| 44. | Characteristics of Modified NAND Gate                                                                       | 87 |

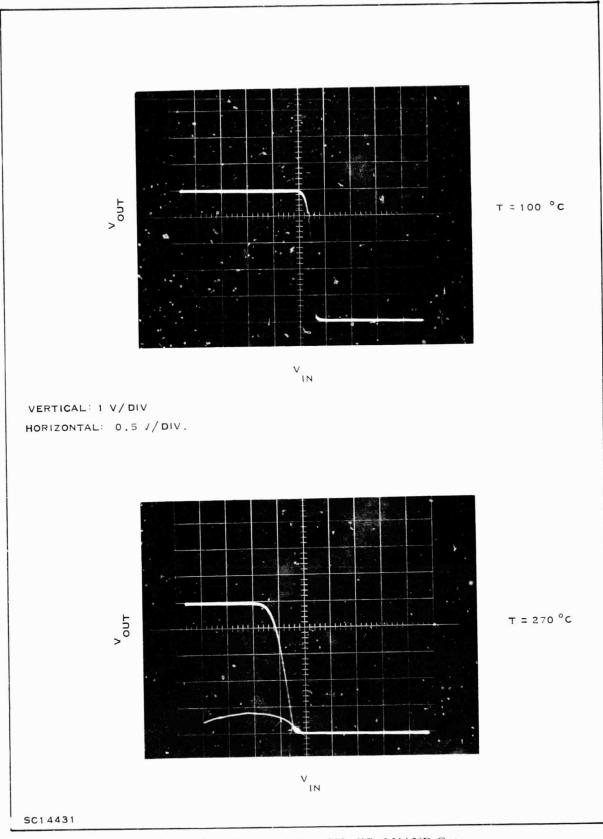

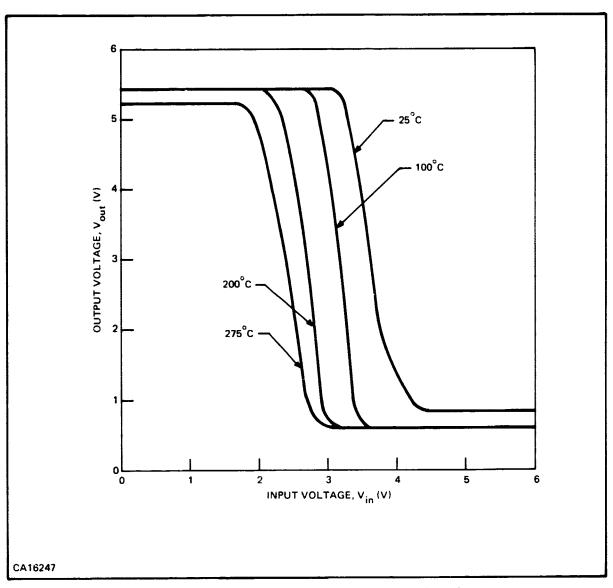

| 45. | NAND Gate Transfer Characteristics as a Function of Temperature                                             | 88 |

# LIST OF ILLUSTRATIONS (Continued)

# FIGURE

}

;

č

•

.

# TITLE

# PAGE

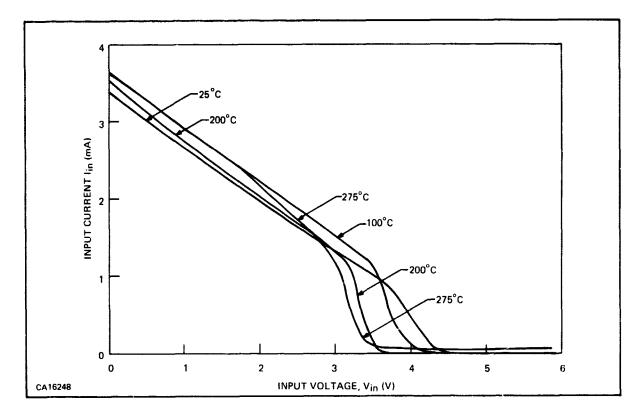

| 46. | NAND Gate Input Characteristics as a Function of Temperature           | 89 |

|-----|------------------------------------------------------------------------|----|

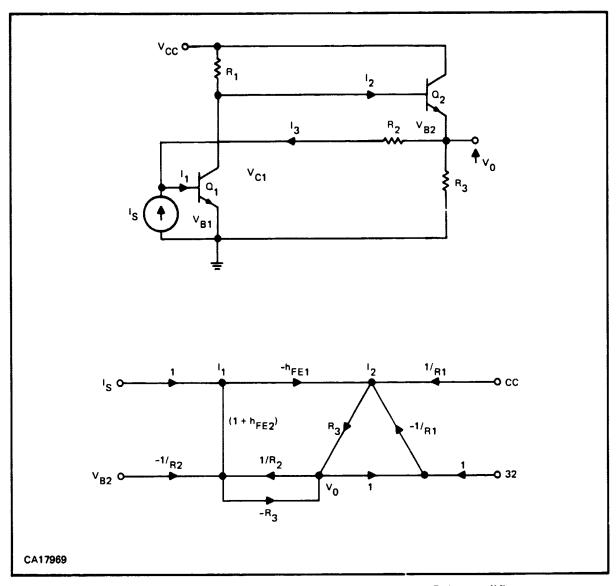

| 47. | Circuit and Signal Flowgraph for Feedback-Pair Amplifier               | 90 |

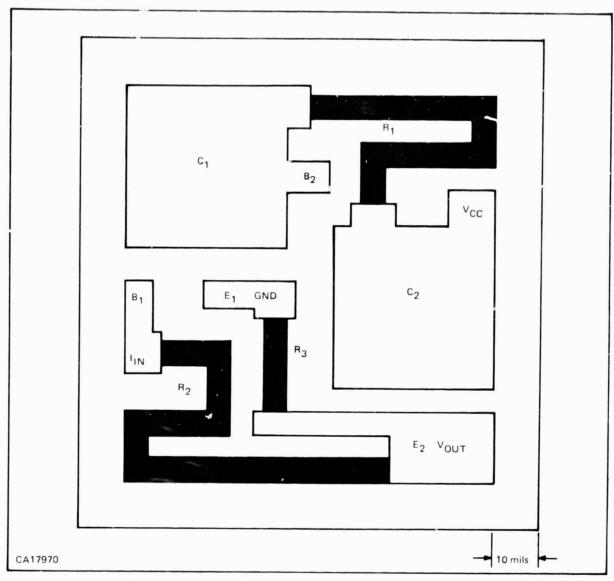

| 48. | Thin-Film Layout for Feedback-Pair Amplifier                           | 93 |

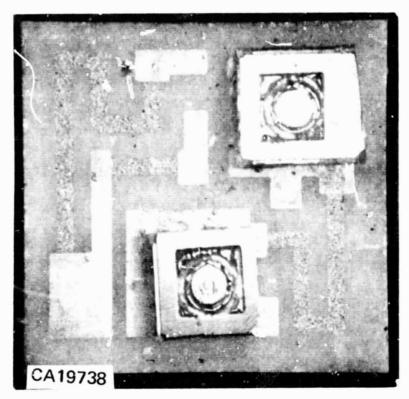

| 49. | Photograph of the Thin-Film Circuit with 2 GaAs Transistors            |    |

|     | (Before Wire-Bonding).                                                 | 94 |

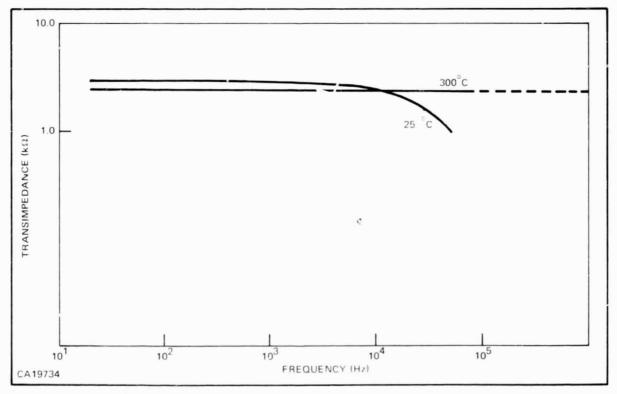

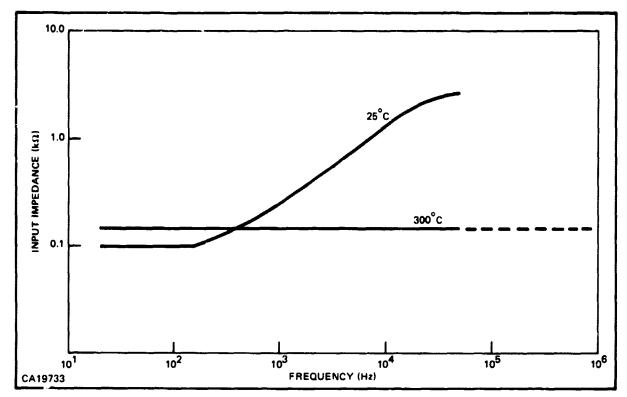

| 50. | Transimpedance versus Frequency of a Thin-Film Feedback Pair Amplifier |    |

|     | at 25°C and 300°C                                                      | 94 |

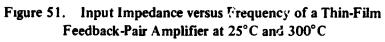

| 51. | Input Impedance versus Frequency of a Thin-Film Feedback-Pair          |    |

|     | Amplifier at 25°C and 300°C                                            | 95 |

# PRECEDING PAGE DLANK NOT HLMLD

# LIST OF TABLES

# TABLE

,

•

|:

.

-

# TITLE

# PAGE

| I.    | Comparison of Material and Device Properties                  |   |   |   |   | 30 |

|-------|---------------------------------------------------------------|---|---|---|---|----|

| П.    | Properties of Vapor-Phase Epitaxial GaAs (No Doping Source) . | • |   |   |   | 33 |

| III.  | Typical dc Characteristics of Good 25°C-GaAs Transistors      | • |   |   | • | 53 |

| IV.   | Performance Data of GaAs Transistors at 400°C                 |   |   |   | • | 58 |

| V.    | Performance of a GaAs Transistor as a Function of Temperature |   |   |   | • | 58 |

| VI.   | GaAs Transistor Switching Times Versus Temperature            |   | • | • | • | 64 |

| VII.  | Life-Test Data of NPN Transistors                             | • |   |   |   | 78 |

| VIII. | Life-Test Data of Diodes from Different Fabrication Runs      |   |   |   | • | 79 |

| IX.   | Fan-Out Factor "N"                                            |   |   |   |   | 85 |

### SECTION I

### INTRODUCTION

The upper temperature at which transistors can be operated depends on the bandgap of the semiconductor material. Based on an operating temperature of 100°C for germanium, silicon transistors can be predicted to operate up to a temperature of 250°C, gallium arsenide transistors up to 450°C, and gallium phosphide or silicon carbide transistors at 1000°C and higher. No technology is presently available to fabricate gallium phosphide or silicon carbide transistors. Common silicon transistors are specified for a temperature range of about -60°C to 180°C case temperature and 200°C junction temperature. Gallium arsenide transistors have been operated at the theoretical limit of 450°C; however, the studies in this report show that the performance and stability of devices at this temperature are generally poor. Because of the much lower thermal conductivity of gallium arsenide, the difference between the maximum safe ambient temperature and the maximum junction temperature is larger than that for silicon. Based on our findings, we believe that a junction temperature of 350°C and an ambient temperature of 300°C are more appropriate maximum safe temperatures than the theoretical limit given above. These theoretical considerations are based on idealized assumptions of the thermal generation of carriers and do not take into account mechanisms for the generation of excess leakage currents prevailing in gallium arsenide transistors. The main limitation is indeed not the magnitude of the current gain but the excessive leakage current and the stability of the leakage current. This means that field-effect transistors, such as those described in this report, cannot be considered alternatives because of the high gate leakage current, though the transconductance stays fairly constant as expected based on the temperature variation of the majority carrier mobility. The leakage current, in turn, is related to the surface properties of gallium arsenide, which are quite different from those of silicon. It is therefore the inherent property of the material that limits the fabrication of devices which can be operated safely at temperatures near the theoretical limit. Surface problems in gallium arsenide also make it very difficult to fabricate MIS devices and are the major reason for the instability of other gallium arsenide devices such as light emitters.

Stability of passive components is determined by the type of chemical reaction that takes place between the resistor material and the ambient gas. Pyrolytically deposited carbon resistors encapsulated in glass perform well in the range where gallium arsenide transistors can be safely operated. They cannot be used easily, however, in microelectronic circuits. Thick-film palladium oxide resistors can be integrated but are not as stable. Thin-film resistors changed less than 10% during 500 hours of operation at 400°C and typically 1% during 1000 hours at 300°C.

Encapsulation techniques for present day semiconductor devices work satisfactorily at higher temperatures although can leakage occasionally was found to be the cause of device failure. Testing of devices and circuits at 400°C is difficult because of the oxidation of leads and circuit parts and because of the lack of suitable sockets and connectors. One conclusion of this report is that high-temperature electronics requires not only new technologies for active devices but also improved technologies for passive components, encapsulations, circuit fabrication and testing.

#### **SECTION II**

### MATERIAL PREPARATION

### A. GENERAL

Previous work on GaAs transistors has shown that device performance is affected by the material fabrication technique, by the type of impurity used for doping the substrate and the epitaxial layer, and by the doping level. Theoretical considerations, supported by experimental results obtained from GaAs devices (such as transistors, Gunn oscillators, and electro-optical devices) have shown that Group IV donors, such as tin, germanium or silicon, are preferred over Group VI donors, with the exception of sulfur. Therefore, a process was developed for the work on this program to deposit reproducibly Sn-doped epitaxial layers on Sn-doped, (100)-oriented substrates. The epitaxial deposition system was of the halide transport type. Other systems such as the water vapor transport reactor, the elemental source reactor, and solution growth techniques were also employed to find the most suitable material fabrication process. The different fabrication techniques are described in the following paragraphs. In addition to epitaxial GaAs, bulk material was used for device fabrication.

### B. VAPOR PHASE EPITAXIAL GaAs

#### 1. Halide Transport System (Sn-Doping)

The material used in this work is provided in the form of vapor-phase epitaxially deposited layers of GaAs that are grown in a system referred to as the automatic reactor. This TI-built system consists of all of the temperature controllers, furnaces, flow meters, and plumbing necessary to perform standard epitaxial processes. Temperature sensing devices, timers, electrical switches and relays, and solenoid-operated valves are controlled by an Acton programmer, which may be set up for several different types of operations. For a particular operation, such as a normal deposition run, the programmer automatically steps through the various operations involved, each time producing the prescribed conditions for a given function. Aside from occasional adjustments in the system, the only operator-dependent step in the preparation process is the predeposition clean-up of the substrate material.

GaAs slices from tin-doped crystals having carrier concentrations in the range of 4 to  $8 \times 10^{17}$  cm<sup>-3</sup> are routinely used for substrates. These slices are cut in the (100) orientation and receive a chemical polish with hypochlorite solution. To prepare a substrate for deposition, degreasing with a suitable solvent such as methanol or trichloroethylene removes any traces of wax left after the sawing and polishing. A short chemical etch with 5:1:1 (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O) etch is then used to remove any remaining surface damage. Immediately after the slice is dried in a stream of nitrogen gas, it is placed in the reactor under a flush flow of helium.

Epitaxial crystal growth is accomplished in a quartz reactor of the open-tube, gas-flow design, using "arsenided" gallium (gallium saturated with GaAs) as the feed material and  $AsCl_3$  as the transporting agent. This system is described in more detail by others<sup>1,2,3</sup> and is shown schematically in Figure 1. The purity of the deposits obtained depends quite strongly on the starting materials which are: metallic gallium (99.9999+ %); AsCl<sub>3</sub>, which is fractionally distilled in our laboratories (exact purity value unknown); and hydrogen (as a carrier gas), which is purified by means of a palladium diffusion process. Before the system can be used to grow epitaxial deposits, it is necessary to saturate the gallium feed source with arsenic. This "arseniding" step is performed by passing AsCl<sub>3</sub>-saturated H<sub>2</sub> over the gallium boat, which is maintained at normal depositing temperature (900°C). After saturation, a film of arsenic can be seen to form at the exhaust end of the reactor, and the system is ready for use. Precompounded GaAs used with metallic gallium can also serve as feed material, reducing the time required for arseniding, but this approach also sacrifices to some extent the level of purity attainable in the deposited layers. Typical run conditions consist of temperatures of 900°C and 775°C for the feed and substrate, respectively, and a total gas flow of about 500 cc/min is maintained through the reactor. Of this total, 190 cc/min of carrier gas pass through the AsCl<sub>3</sub> bubbler. With these conditions, deposition rates of 5 to  $7 \,\mu$ m/hr were observed. Recently, the reactor was modified by changing from a flat, fixed-position substrate holder (as illustrated in Figure 1) to one with an inclined holder at about 45° from horizontal. This new holder has a plate that measures about 1 inch by 2 inches and has improved flexibility over the previous design, in that the position of the substrate in the reactor can easily be changed. With this modification, growth rates ranging from 9 to  $18 \,\mu$ m/hr have been achieved.

The epitaxial layers are tin-doped by using a diffusion cell which may be filled with anhydrous stannic chloride or mixtures of  $SnCl_4$  and  $AsCl_3$ . The cell, depicted in Figure 2, consists of a chamber for the volatile liquid connected to the mixing chamber with a 1-mm-diameter and 10 cm long capillary tube. The doping mixture is then carried to the substrate zone of the reactor by sweeping out the mixing chamber with a stream of purified H<sub>2</sub>. Doping levels obtained by this system depend on the concentration of the solution used and its temperature. In the present work, a 10 percent (volume) mixture of  $SnCl_4$  in  $AsCl_3$  is used. By maintaining the temperature of the reservoir at about 20°C, doping levels in the mid-10<sup>16</sup> range are obtained on a reasonably reproducible basis.

The approach to the materials aspect of this program has been to attempt to develop the preparation process to a point that a reasonable consistency in the quality of the epitaxial layers can be achieved. Although the doping levels of the deposits have been found to be extremely sensitive to such factors as changes in total AsCl<sub>3</sub> flow rates and the temperature of the diffusion cell, the use of the automatic system serves to regulate these factors, keeping the doping levels reasonably consistent. Determination of the electrical properties of the layers has been limited to a simple point-contact reverse breakdown (PCRB) voltage measurement, and the layers deposited for the work typically exhibit breakdowns on the order of 30 to 40 volts. A sample of epitaxial material grown on a semi-insulating substrate has been evaluated by means of Hall measurements. This tin-doped slice, which exhibited 20 to 25 V (PCRB) was found to have a carrier concentration of  $2.2 \times 10^{17}$  cm<sup>-3</sup> and a room temperature mobility of about 4100 cm<sup>2</sup>/V<sub>sec</sub>.

. .

. •

Report No. 03-68-80

Figure 1. Epitaxial Reactor

S

. .

Figure 2. Diffusion Cell used for Tin Doping

Deposit thicknesses, which are not critical above a minimum value of 10 to  $12 \mu m$ , have not achieved the run-to-run reproducibility desired. Thickness measurements are made by bevel-lapping a small piece of the deposited slice at a known angle (usually 5°) and using an electroless gold-plate solution to stain the lower resistivity substrate. By means of a calibrated microscope eyepiece and the appropriate calculations, the layer thickness is determined. For a given deposition time, successive runs may result in layers that differ in thickness by as much as  $10 \mu m$ . Although the level of feed material in the source boat and the amount of extraneous deposition on the reactor walls probably affect growth rates, no consistent pattern has been observed to account for the difference in thicknesses. Very large area substrates generally exhibit a tapering effect, with a 5  $\mu m$  thickness variation over the slice not uncommon.

#### 2. Halide Transport System (S-Doping)

In order to obtain sulfur-doped deposits, the diffusion cell was filled with a solution of 0.5 percent (vol.) sulfur monochloride in  $AsCl_3$ . After several runs with the solution temperature maintained at 0°C, it was found that the doping level achieved was higher than the desired value, as indicated by point-contact reverse-breakdown (PCRB) measurements of 10 to 15 V. Further dilution of this solution to a value of 0.25 percent  $S_2Cl_2$  was then made with  $AsCl_3$ . The epitaxial material prepared with this dopant concentration (again maintained at 0°C) has consistently yielded breakdown measurements of 20 to 30 V.

Since it was thought that material fabricated under a previous contract (AFAL-TR-66-361) and used here for manufacturing high temperature transistors was contaminated with Cd, a series of runs was made to produce Cd-compensated epitaxial slices. Cd was introduced by adding 50 mg of 1  $\times 10^{17}$  cm<sup>-3</sup> Cd-doped bulk GaAs to the feed material. Donor doping was accomplished with S<sub>2</sub>Cl<sub>2</sub>. Carrier concentrations in these compensated slices ranged from 2 to 20  $\times 10^{15}$  cm<sup>-3</sup>.

### 3. Water Vapor Transport System (Undoped)

In addition to the material produced in the automatic reactor chloride transport system, slices have been obtained from two other reactor sources. These slices make possible the relative evaluation of variables, such as substrate dopants, orientation, and layer doping levels, as well as the obvicus comparison of the reactor systems themselves. The reactor used in the water-vapor transport system closely resembles that of the automatic reactor (see Figure 1), except that no modifications for doping are made with this method. Several major differences in operation are required by this process. Precompounded GaAs is used as a feed source, and by selecting the doping of the bulk feed material, the doping levels of the epitaxial layers can be controlled. As the name indicates, water is used as a transporting agent, replacing the AsCl3 used in the automatic reactor system, but the method of introduction is the same, namely, saturating a stream of carrier gas  $(H_2)$ with the transporting agent by passing it through a bubbler. Although no extensive studies have been made to evaluate the effect of the purity of the water used, de-ionized water has been found to be satisfactory for use in this reactor system. Probably the most critical difference inherent in this method is the fact that substantially higher reactor temperatures must be used. Typically, the feed temperatures employed are on the order of 950°C to 1050°C with the substrates maintained at a temperature 50°C to 100°C lower than the feed.

#### 4. Elemental Source System (Ge-Doping)

The elemental source method requires a modified reactor design (see Figure 3). High purity (99.9999+%) gallium and arsenic, used as starting materials for the system, allow variation in the vapor phase stoichiometry. The arsenic content of the vapor stream is controlled by varying the temperature of the arsenic source boat, which determines the vapor pressure of the solid material. Purified H<sub>2</sub> sweeps the arsenic vapors down the reactor where it is mixed with the gallium species. The gallium is transported with HCl, which is generated from purified AsCl<sub>3</sub> by passing AsCl<sub>3</sub>-saturated H<sub>2</sub> through a quartz reduction tube filled with crushed quartz and heated to 900°C. The arsenic produced by this reduction condenses out of the stream at the cold end of the

00

. .

reduction furnace and does not enter the reactor system. The amount of gallium transported by this process is controlled by the flow rate of the carrier gas through the  $AsCl_3$  and the temperature (vapor pressure) of the  $AsCl_3$  reservoir. Typical operating temperatures are shown in the schematic drawing, Figure 3, of this reactor system.

In the following section, it will become apparent that epitaxial GaAs prepared in the "AsCl<sub>3</sub>-Ga" reactor, or in the "elemental" reactor system, was superior to GaAs produced by "water vapor" transport. Both the "AsCl<sub>3</sub>-Ga" and "water vapor" transport systems are fixed gas composition systems; the "elemental" s, stem can utilize variable gas-phase compositions, e.g., various Ga:As, or Ga:Cl gas-phase compositions. This system was thus selected to determine what effect gas-phase composition had on materials' properties as reflected by cathodoluminescence and device performance.

A series of samples was prepared with varying Ga:As ratios in the gas phase. Substrates were (100)-oriented and heavily doped N-type. No intentional dopant was added to the gas phase. These samples had apparent donor concentrations which varied depending upon the Ga:As ratio in the gas phase (see Figure 4). They were then used in the cathodoluminescence study.

A second set of samples was prepared in which GeCl<sub>4</sub> was added as a dopant to the gas phase. The dopant source was 10 percent GeCl<sub>4</sub>-AsCl<sub>3</sub> in a diffusion cell. The dopant was added so that it mixed with the reactants in the zone immediately before deposition. These runs produced epitaxial layers which had carrier concentrations of ~ 1 to  $5 \times 10^{18}$  cm<sup>-3</sup>. This concentration did not vary with Ga:As ratio over the range investigated.

The next series that was prepared used a 0.1 percent GeCl<sub>4</sub>-AsCl<sub>3</sub> dopant source. The results obtained are also shown in Figure 4. Carrier concentrations in these samples vary depending upon the Ga:As ratio. However, over most of the range investigated, the dependence is opposite to that seen with no intentional doping. This effect could be due to the dopants in each instance. It is suspected that with no intentional doping, the background is caused by a Group VI element, which could be introduced either from the elemental arsenic source (the AsCl<sub>3</sub> used as the HCl source) or the N-type substrate. Germanium, being a Group IV element, is incorporated differently from a Group VI element. Increasing arsenic concentration would tend to reduce the Group VI element solubility, while it would favor Group IV element solubility on gallium sites (donor sites for germanium). This means the yet unexplained portions of the curves are those with decreasing donor concentration at higher arsenic temperature when doped with germanium. It was also found that the growth rate increased with increasing Ga:As ratio, thus enhancing the probability for a dopant atom to be incorporated into the lattice.

To study the effect of the substrate, runs were repeated with Cr-doped, semi-insulating substrates, using a 0.1 percent  $\text{GeCl}_4\text{-AsCl}_3$  dopant source. This time, the concentration of donors in the deposit decreased with arsenic temperature as shown in Figure 4. So far, only (100)-oriented substrates have been used. Other orientations might give different results. The standard starting material for transistor fabrication was prepared in the halide transport reactor. This system has a Ga:As ratio of about 2 if the Ga solution is not yet completely saturated with As. This ratio decreases with increasing degree of saturation.

Report No. 03-68-80

Figure 4. Donor Concentration versus Arsenic Control Temperature

Considering Figure 4 again, it is recognized that small changes in the concentration of dopant source and small changes in the Ga:As ratio can affect the electrical properties of the deposit considerably. Also, the element used for substrate doping and the substrate orientation have an influence.

# C. SOLUTION EPITAXIAL GaAs

Solution growth of GaAs has developed into a technology that allows fabrication of high-quality material for many different devices such as Gunn oscillators<sup>4</sup> and light emitting diodes<sup>5</sup>. Recently, solution-grown GaAs P-N junctions have been formed that were doped amphoterically with silicon.<sup>6</sup> We have applied this technique to make materials for transistor fabrication. The apparatus is shown in Figure 5. The gap shown in the center of the crucible serves the purpose of providing growth boundaries. It was found empirically that such an arrangement yields better surfaces.

Report No. 03-68-80

•

Figure 5. Apparatus for Solution Growth of GaAs

Solution-grown P-N-P-N layers were formed by inserting an N-type substrate into a gallium melt saturated at 860°C with GaAs. Silicon was added as a dopant, preferentially occupying donor sites at temperatures below 840°C. Upon cooling from 860°C, an N-P layer is grown on the N-type substrate. After reheating and cooling again, a second N-P junction is formed. The growth cycle is shown schematically in Figure 6. Solution-grown material is used for fabrication because of the long diffusion length observed in this material. A common-base current gain of 0.6 was observed for a 25- $\mu$ m-thick base layer using a conventional sulfur-diffused emitter. This corresponds to a diffusion length of at least 20  $\mu$ m, about one order of magnitude higher than in non-solution-grown GaAs. This property was also confirmed by cathodoluminescence measurements, the technique of which is described in Section III. The transistors were made by etching off the top P-layer and mesa-etching the emitter. All transistors had low gain because of the wide base layer and were not used in high temperature tests.

### D. BULK MATERIAL

Though attempts have been made earlier in this laboratory and elsewhere to use bulk material for device fabrication, transistors were always inferior to those made on epitaxial GaAs. Recently, silicon-doped bulk GaAs pulled in a sealed system became available.\* This material has properties

<sup>\*</sup>Source: Bell & Howell, Pasadena, California

Figure 6. Growth Cycle for Fabrication on P-N-P-N Layers

similar to those of the epitaxial GaAs used for device fabrication, namely a donce concentration  $N_D = 5 \times 10^{16}$  cm<sup>-3</sup> and an electron mobility of  $\mu_e = 5000$  cm<sup>2</sup>/V sec. Some runs on this material were very successful. If bulk material could be used for transistor fabrication, an increase in reproducibility and a reduction in cost could be expected. However the problem with Si-doped material is that it is obviously more difficult to grow. Many slices are not sufficiently uniform for a base diffusion. They show an irregular diffusion front and too low sheet resistance after etchback to the proper base-layer thickness. Only a small number of devices could be built.

For fabrication of PNP transistors, bulk GaAs doped with cadmium to  $1 \times 10^{17}$  cm<sup>-3</sup> was used. Best results were obtained from a crystal which exhibited a very high hole mobility of  $\mu_{\rm h} = 680$  cm<sup>2</sup>/V sec.

Heavily doped bulk material  $(2 \times 10^{17} \text{ to } 10^{12} \text{ donors/cm}^3)$  was used as substrate for the vapor phase deposition of epitaxial GaAs. During the present work, a conversion problem was encountered that prevented for some time fabrication of transistors. The N-epitaxial collector region converted into P-type material after either the magnesium diffusion or the sulfur diffusion. This behavior could be traced back to the growth direction of the Czochralski pulled crystal. More than 70 percent of slices that came from (100)-grown material did not convert, while more than 60 percent of slices grown from (111) crystals converted. The substrates were doped with Sn in all cases. Earlier studies<sup>7</sup> on Te-doped material showed that the probability of conversion was higher on (100)-grown material than on (111)-grown substrate–opposite to our present findings with tin doping. One possible explanation is given in connection with the low-temperature diffusion data, in Section VI of this report.

At this point, some stated possibilities may be ruled out. Quite often, copper diffusion is given as a reason for the conversion. Though this was a possibility, we found that conversion also occurred when care was taken to remove any contamination due to copper-e.g., by rinsing slices and ampoules in KCN and employing Spectrosil instead of standard GE-quartz. Also, when a slice from one crystal that gave frequent conversions was diffused with a slice from another crystal that was not likely to convert, conversion occurred in the first slice and not in the latter. After many subsequent conversions of slices from one (111)-grown Sn-doped crystal, conversion stopped when a slice from a (100)-grown, tin-doped or a (111)-grown, Te-doped crystal was used.

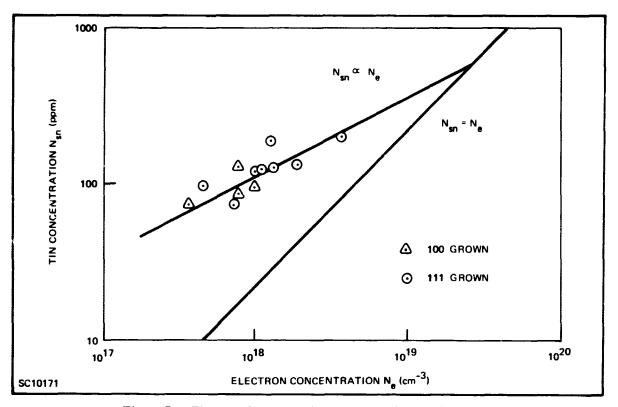

Te-doped crystals showed the peculiar behavior that the Te concentration in (100)-grown crystals, as determined by mass spectroscopy, was generally lower than the electron concentration.<sup>7</sup> To find out whether this observation is related to the probability of conversion for tin-doped crystals, samples were analyzed for tin by an emission spectrography. In Figure 7, the tin concentration expressed in parts per million (ppm) is plotted versus the electron concentration found by Hall measurements. The solid line shows the 1 electron for 1 tin atom line. The tin concentration was found to be higher than electron concentration in all crystals, both (100)-grown and (111)-grown. Though there is not a very good correlation between tin concentration and electron concentration or the tin concentration in the crystal with the tin concentration in the melt is not as good. Other than growth direction, no crystal property could be found that related to the frequency of conversion of epitaxial layers. (111)-grown Te-doped crystals or (100)-grown Sn-doped crystals were finally specified for substrate material.

Report No. 03-68-80

### **SECTION III**

### CATHODOLUMINESCENCE STUDIES ON GaAs

### A. GENERAL

Transistor fabrication requires, besides the two diffusion steps, many other fabrication steps that are likely to contribute to the wide spread in transistor performance. This makes it difficult to separate the effects of the starting material from those introduced during fabrication. The three types of vapor phase epitaxial starting materials used were prepared by one of the methods described in Section II:

- 1) Material from the automatic reactor (A-material).

- 2) Material produced by the water-vapor transport technique (W-material).

- 3) Material from the elemental reaction (E-material).

Most good transistors made so far were fabricated on A-material. Transistors on E-material were marginal, and no good transistors were obtained on W-material. Thus, it was decided to use only A-material for device fabrication when epitaxial GaAs was called for.

Breakdown voltage, mobility dislocation density, or appearance of materials have given no criteria by which material can be selected. Cathodoluminescence experiments, then, were performed on all types of material to find out if measurements of the minority carrier properties in the materials indicate any differences.

### **B. THEORY**

Cathodoluminescence is defined as light emission stimulated by electron bombardment of semiconducting materials. The theory was worked out by Wittry.<sup>8</sup> To obtain quantities such as the ratio of surface recombination velocity (s) to diffusion velocity ( $v_D$ ), or the diffusion length of minority carriers (L), the cathodoluminescence intensity is measured as a function of the electron beam voltage for constant beam power. By curve fitting techniques, these quantities can be determined. The methods of calculation used by Wittry and the form of the distribution of primary electrons in the materials give a satisfactory description of the experimental results. For a first order estimate of the expected dependence of the intensity as a function of beam voltage, we will use a much simplified treatment which has the advantage of giving a clear picture of the process and a very simple form of the solution.

In a typical cathodoluminescence experiment, an electron beam is focused on an area, the diameter of which is large compared with the sum of electron penetration depth and electron diffusion length. The problem of calculating the light intensity is then reduced to a one-dimensional case. Since the energy for producing electron-hole pairs is in the order of a few times the bandgap, the electron-hole pair generation follows the primary electron distribution. In N-type GaAs (similar arguments apply to the excess electron concentration in P-type material), excess holes can recombine either radiatively, giving rise to the cathodoluminescence effect, or recombine nonradiatively. The balance equation for holes under steady-state condition is given by

$$Dp'' - \frac{p}{\tau} + g(x, V) = 0$$

(1)

where

p = hole concentration

D = hole diffusion constant

τ = hole lifetime

x = distance from surface

g(x, V) = generation function for holes

The first term gives the flux of holes due to diffusion into a given volume element per unit time, the second describes the loss of holes, and the third one stands for the number of holes generated by the incident electrons per unit volume per unit time. For a first order calculation, we will assume an exponential distribution of electrons so that the generation function is given by Lenard's law

$$g(x, V) = constant e^{-\alpha(V)x}$$

(2)

where the voltage dependent parameter  $\alpha$  is defined  $\therefore$  analogy to the photoluminescence case as an "electron absorption constant." The constant is determined by the experimental condition that the total number of holes generated in the sample-per-unit time F, be constant. Equation (2) then assumes the form

$$g(x, V) = \alpha F e^{-\alpha X}$$

(3)

The hole distribution is obtained by integrating Equation (1) subject to appropriate boundary conditions. For infinitely long samples, the hole concentration zero at  $x = \infty$ , i.e.,

$$p_{(x = \infty)} = 0 \tag{4}$$

At the surface, holes recombine at a rate determined by the surface recombination velocity, S, and the diffusion constant for holes. The recombination rate-per-unit are per-unit time at the surface can be expressed as

$$Dp'(x = 0) \stackrel{= s - p}{=} (x = 0)$$

(5)

The solution of Equation (1) subject to the boundary conditions (4) and (5) is

$$p = \frac{\alpha F \tau}{1 - \alpha^2 L^2} \left[ e^{-\alpha x} - \frac{\alpha L + S}{S + 1} e^{-\frac{x}{L}} \right]$$

(6)

where we have defined

$$S = \frac{s}{v_D} = \frac{s}{D/L}$$

and

$$L = \sqrt{D\tau}$$

Equation (6) is of the same form used by Vilms<sup>9</sup> et. al., for the photoluminescence case except for the different meaning of  $\alpha$ . The light intensity is proportional to the number of radiative transitions of holes and is given by

$$I = \kappa \int \frac{p}{\tau_{\rm r}} e^{-\beta x} dx$$

(7)

where

$$r = radiative$$

hole lifetime

$\beta$  = absorption constant for light generated in the sample

$\kappa$  = constant depending on the optical properties of the light exit surface

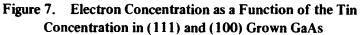

Light absorption effects can be neglected for our first order calculation since the electron penetration depth is not larger than about  $5 \,\mu m$  for 40 keV electrons (see Figure 8), while a typical absorption length for band edge light in GaAs is in order of 30  $\mu m$  except for very lightly doped material, where the absorption length is shorter. Integration of Equation (7) leads to

$$I = \kappa \frac{\tau}{\tau_{\rm r}} \frac{S + 1 + L\alpha}{(1 + \alpha L)(S + 1)}$$

(8)

or in normalized form

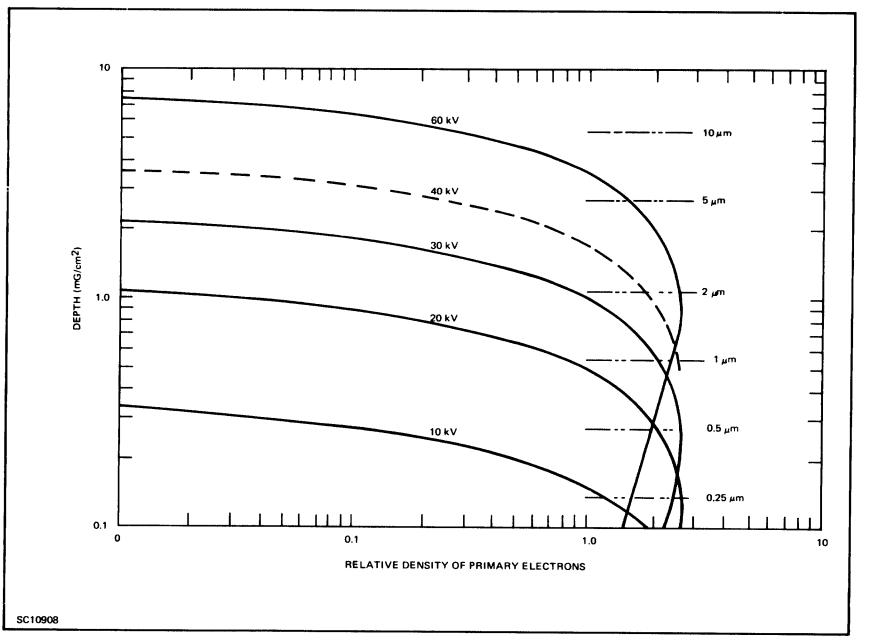

$$I_n = 1 - \frac{S}{S+1} \frac{\alpha L}{\alpha L+1}$$

(9)

Figure 8. Electron-Beam Penetration in GaAs

- **-**

۰.

Report No. 03-68-80

where the normalization factor is

## $\kappa \tau / \tau_{\rm r}$

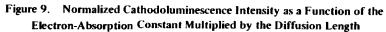

Equation (9) is plotted in Figure 9 (solid lines) as function of the dimensionless quantity  $L\alpha$  for various values of the parameter S. As can be seen by inspection of Equation (9), the intensity is not a strong function of either S or  $L\alpha$ , which makes it difficult to determine one of these quantities by curve-fitting techniques. The voltage dependence of  $\alpha$  will be taken to be that given by Cosslett and Thomas<sup>10</sup>

$$\alpha = 1.9 \times 10^{11} \ (\rho Z)^{1/2} \ V^{-2} = 574/V^2 \tag{10}$$

when  $\alpha$  is measured in  $\mu m^{-1}$  and V in kV. A comparison with the data presented in Figure 8 shows that the absorption constant is reasonably well represented in Equation (10). For a voltage of 20 kV, the absorption length is 0.7  $\mu m$  which agrees with a decrease of about a factor 2.7 of the electron concentration over that distance. Small values of L $\alpha$  correspond to large voltages and large penetration depths. For large penetration depths, Equation (8) asymptotically approaches the value

$$I = \kappa \frac{\tau}{\tau_{r}}$$

(11)

Expressing the total lifetime  $\alpha$  as

$$\frac{1}{\tau} = \frac{1}{\tau_{\rm r}} + \frac{1}{\tau_{\rm nr}} \tag{12}$$

where  $\tau_{nr}$  is the non-radiative lifetime, we obtain

$$1 = \kappa \frac{\tau_{\rm nr}}{\tau_{\rm nr} + \tau_{\rm r}} \approx \kappa \frac{\tau_{\rm nr}}{\tau_{\rm r}}$$

(13)

In GaAs, typical non-radiative lifetimes are in the order of  $10^{-9}$  to  $10^{-10}$  sec and radiative lifetimes are in the order of  $10^{-8}$  sec so that the intensity at high voltages is proportional to the ratio of non-radiative to radiative lifetime. If we compare materials of the same donor concentration, which means roughly the same radiative lifetime, high cathodoluminescence intensity means long non-radiative lifetime. Light emitters require starting material with long non-radiative lifetimes in order to favor electron injection into the P-type region, from which almost all light is emitted. We will, therefore, consider material with a high cathodoluminescence intensity superior to material of lower intensity.

.

.

20

•

٠

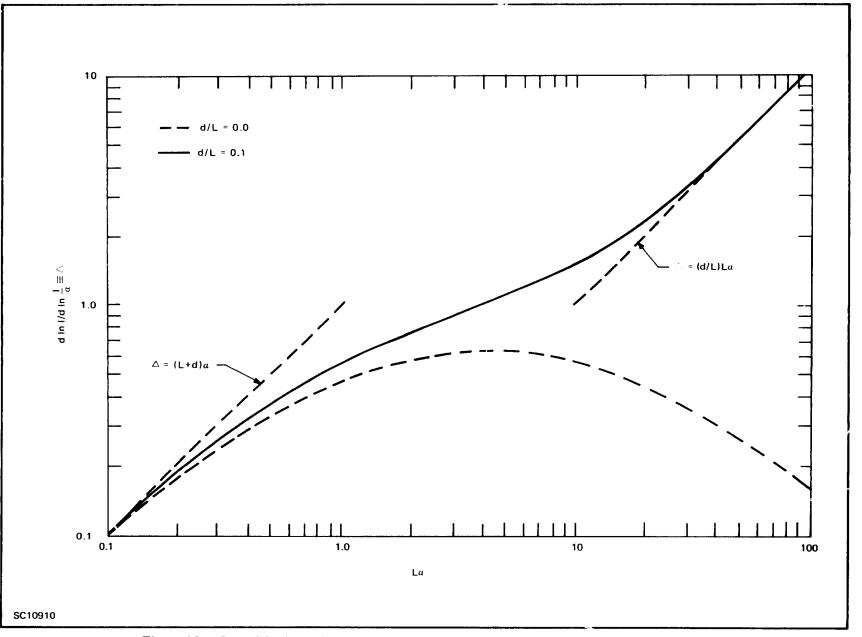

Another quantity of interest and related to the total intensity is the minority carrier diffusion length. We will describe a simple technique that allows us to determine graphically the diffusion length. For this purpose, the following expression is derived from Equation (8)

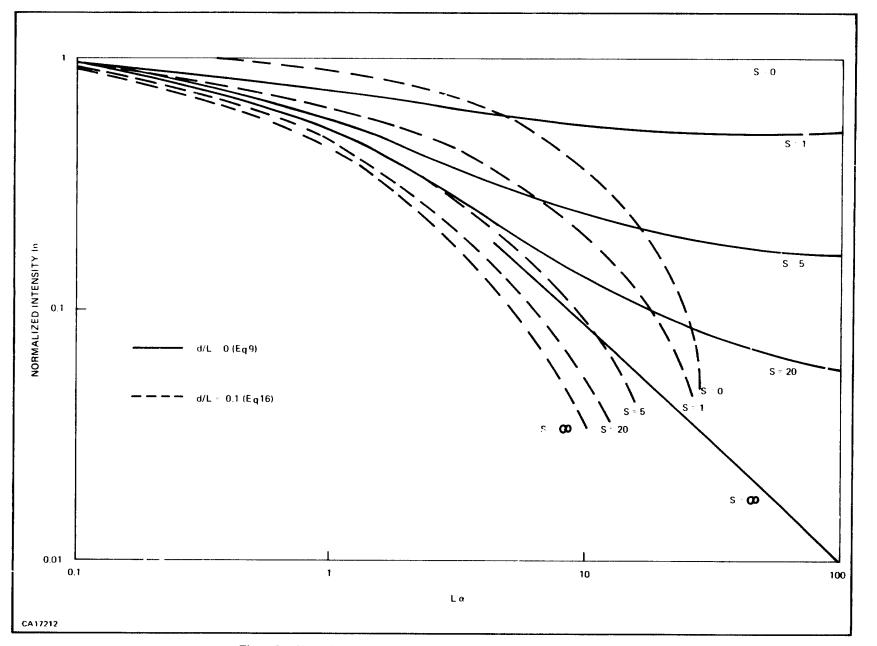

$$\Delta = \frac{d(\ln 1)}{d(\ln 1/\alpha)} = -\frac{L\alpha}{(S+1) + L\alpha} + \frac{L\alpha}{1 + L\alpha}$$

(14)

For small values of L $\alpha$  and large values of S so that  $L\alpha \ll 1 \ll S,\Delta$  increases as L $\alpha$ . One can then obtain L from the slope of a plot of  $\Delta$  versus  $\alpha$ . At values of L $\alpha$ , so that  $S \gg L\alpha \gg 1, \Delta$  decreases as  $1-L\alpha/S$ . At  $L\alpha_m = \sqrt{S+1}$ , the quantity  $\Delta$  reaches a maximum value

$$\Delta_{\rm m} = (1 + \frac{S}{1 + \sqrt{S + 1}})/(S + 1) \tag{15}$$

In N-type GaAs, a typical value for (S + 1) is 20. In Figure 10, the dependence of  $\Delta$  on L $\alpha$  for S + 1 = 20 is shown (dotted line). Though we have used only a rough approximation for the generation function, we expect that by plotting the experimental data in the manner suggested by Equation (14), it is possible to separate materials of different diffusion lengths.

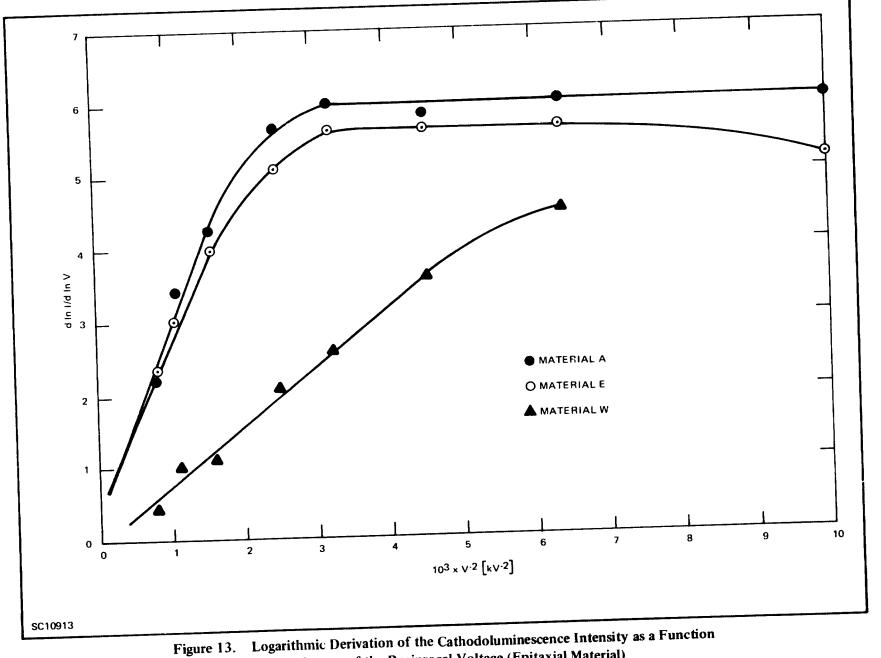

To arrive at a value for the diffusion length from a presentation of experimental data, one first obtains the quantity  $d(\ln I)/d(\ln V)$  by graphical differentiation. This quantity is then plotted versus (voltage)<sup>-2</sup>. The slope of the linear portion of that curve at high voltages is then related to the diffusion length by

$$L = \left(\frac{d\ln I}{d\ln V}\right) \frac{1}{1150}$$

(16)

where we have combined Equations (10) and (14). The diffusion length is obtained in  $\mu$ m when the voltage is expressed in kV. Though the value thus obtained for L is achieved under the simplifying assumption that the electron distribution can be represented by an exponential function, we expect that a material with a longer diffusion length also exhibits a larger value of the quantity derived in Equation (16).

The other quantity of interest, S, could be obtained similarly from the slope of a plot of  $\Delta$  versus V for small voltages. For small voltages (close to the surface), the intensity is expected to change only weakly with bias, as can be seen in Figure 9. Wittry has observed that the intensity even

22

· · ·

Report No. 03-68-80

at small voltages continues to drop. He explains this behavior with the existence of a "dead" layer in which no radiatve recombination takes place. We can modify Equations (8) and (14) to take account of the presence of a "dead" layer by writing

$$I = I_0 e^{-\alpha L(d/L)}$$

(17)

$$\Delta = \Delta_0 + \alpha L \ (d/L) \tag{18}$$

where the subscript "o" refers to the case without surface layer and d is the thickness of the dead layer. Modifying Equations (8) and (14) is equivalent to shifting the boundary of Equation (5) from x = 0 to x = d and by integrating Equation (7) from x = d instead of from x = 0. The solid line in Figure (10) is calculated for S + 1 = 20 and d/L = 0.1. We notice that the curves are about the same for  $L\alpha < 1$  but that  $\Delta$  increases with  $(d/L)L\alpha$  rather than decreases as  $1/L\alpha$ . We expect therefore, depending on the magnitude of d/L, that for large values of  $\alpha$  the quantity  $\Delta$  either increases, stays about constant or decreases with  $L\alpha$ .

The term "surface effects" and "bulk properties" can now be defined more properly. We will consider the range in L $\alpha$  below the maximum of Equation (14) (see Figure 10) as dominated by bulk properties, the range in L $\alpha$  above the maximum as dominated by surface properties. That means the boundary between surface and bulk effects in our definition lies at L $\alpha_m = \sqrt{S+1}$ . For the typical values of (S + 1) = 20, we find L $\alpha_m = 4.5$ . For a diffusion length of 1.5  $\mu$ m, we obtain  $\alpha$  = 3  $\mu$ m<sup>-1</sup> and from Equation (10) a voltage of 15 kV. The voltage range for standard electron microprobes is 10 to 45 kV, thus covering the transition range from surface-dominated to bulk-dominated properties for typical GaAs samples.

### C. EXPERIMENTAL ARRANGEMENT

In order to observe the cathodoluminescence output from a gallium arsenide target as a function of the depth at which the excitation occurred, the intensity of radiation is measured at several different beam accelerating voltages. As the accelerating voltage is increased, the excitation is produced at greater depths in the sample. Thus, we must measure both the intensity of the infrared radiation and the accelerating voltage. Further, we must monitor the current in the beam to maintain constant power. (The constant power requirement is essential for the derivation of Equation (8) in dimensionless quantities.) At constant beam power, the curves for intensity versus beam voltage should show an initial increase in intensity as the voltage increases. At very high voltages, the curve should level out because the surface no longer is a factor in the recombination process (see Figure 9).

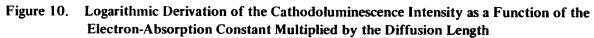

The cathodoluminescence measurements were made on a Materials Analysis Company Model 400 Electron Microprobe Analyzer. The equipment is illustrated in Figure 11. A photomultiplier was fitted to the third eyepiece of the microscope on this microprobe. The radiation emitted from the sample was thereby focused onto the face of the photomultiplier. The output pulses were amplified

Report No. 03-68-80

Figure 11. Diagram of the Electron Microprobe

and analyzed by a pulse height analyzer. The output pulses from the pulse height analyzer were counted and printed out. Instead of placing the photomultiplier directly on the microscope, a monochromator can be put between the microscope and the photomultiplier. This allows a study of the spectral distribution of the cathodoluminescence radiation. Experimental modifications of this type for microprobes and electron scanning microscopes are common  $^{11-16}$ ; therefore, we will not describe the instrumentation in detail. However, the need for careful experimental procedures is critical and should be elaborated.

The high voltage power supply was checked at the electron gun with an electrostatic voltmeter, and a correction curve was made to correct the meter readings. This correction was quite small throughout the voltage range

As the electron beam bombards the target, a contamination film deposits at the points of impact. This film is composed primarily of carbon, caused by the decomposition of vacuum grease and pump oil. It attenuates the cathodoluminescence output appreciably; therefore, the measurements must be made at the lowest possible sample currents and with the minimum time for bombardment. Two methods have been suggested for retarding the growth of the contamination film; one is by placing a cold finger just above the specimen surface, and another is by directing a jet of air or other gas at the point of impact. We did not use these methods because we found that this contamination film did not appear until the sample was bombarded for several minutes; the actual measurements require a total bombardment time of much less than a minute.

The surface recombination velocity and possibly the nature of the "dead layer" are very sensitive to the surface conditions. The exact effects of the initial electron beam bombardment and deposition of the contamination layer are unknown. It is not unreasonable to expect that a great change in surface properties can be initiated by a few seconds of electron beam bombardment. This is a matter for further investigation. On the other hand, permanent changes in the bulk semiconductor properties should not be expected at the beam energies we used.<sup>17</sup> However, studies on semiconductor devices by electron scanning microscopes have been shown to alter the device characteristics for short periods of time, but it has not been illustrated that this is due to a change in the bulk properties.

The measurements were all made at constant beam power, that is  $iV_0 = constant$ . This assures that the same amount of energy loss occurs at each accelerating voltage provided that i truly relates to the total power dissipation. The absorbed current can be carefully measured and printed out with the intensity data, but the effect of backscattered and secondary electron loss should be considered. The electrons striking the target are not all absorbed; some electrons dissipate energy in the target and are then backscattered. This is generally not a problem since the portion backscattered, and its energy distribution is not dependent on the accelerating voltage; thus, the backscattering always represents the same amount of power loss. Secondary electron emission from the sample is, however, dependent on the accelerating voltage. At voltages beyond a few kV, there exists an inverse relationship between secondary electron emission and beam acceleration potential. As secondary electrons are lost, the measured current becomes lower than the actual current. We therefore produce some ionizations, creating positive holes, which are not recorded by the current measurement. To compensate for this, one would increase the total beam current, but this would only compound the error. In order to reduce this error, we biased the sample at +67 volts to hold the majority of the secondary electrons in the sample.

The electron beam can heat the sample at the point of impact, thereby reducing output intensity; it can also create an electrical charge in a poor conducting sample, thereby distorting the distribution of excitation. The heating effect in gallium arsenide is not large, and when constant beam power is maintained, this effect should not be a source of error<sup>11</sup>. Maximum power level was 4 mW, at a current density of  $5 \times 10^{-2}$  A/cm<sup>2</sup>. Charging in this semiconductor has also been shown to be mincr.<sup>18</sup>

Before each experimental determination, an examination of the signal output as a function of absorbed current was made. Generally, this is a linear relationship, and the range of linearity of these determinations defined the experimental conditions for obtaining good data. By examining these data, the limitations imposed by dead time, poor pulse-height analyzer settings, current saturation, heating effects, etc., could be detected. Strictly speaking, the intensity should not be linear with current. Actually, we observed a very slight nonlinearity. These effects have been discussed by other workers.<sup>12, 19</sup> However, within the range of our normal measurements, the current and intensity are essentially linear.

We did not use a monochromator to separate the spectral distribution of the emitted light since at least with a low resolution instrument, this radiation appeared as a single, sharp spectral peak. The benefits derived by spectral selection would therefore be small; furthermore, the integrated radiation was much more intense than that which was transmitted through a light pipe and a monochromator.

The measurements were made at several random 3-mil diameter spots on each sample at each accelerating potential. The 3-mil spot size was reproduced after each change in potential. Other workers used a 5- $\mu$ m diameter spot for their measurements; further, they made all observations at the same point. However, the major purpose of our study has been to develop a means for quickly evaluating bulk material. For an "on-line" evaluation, a 3-mil spot is much more realistic than a 5-micron spot. We also found that the integrating effect of the larger spot gave us more meaningful data than a smaller spot, because the samples that we studied were generally quite heterogeneous in cathode-luminescence output as far as areas in the order of several square  $\mu$ m are concerned. Furthermore, by observing several spots on each sample at each potential, the effects of carbon contamination buildup were held to a minimum.

### D. RESULTS

GaAs samples were obtained from materials with a known device history. This means that the performance of devices from these materials is known for at least several hundred units. No attempt was made to relate the performance of one single device to the specific chip of material from which it was made. The purpose of these experiments was to determine if differences in material preparation or differences among one type of crystal are reflected in the performance of devices. Studies were made on N-type epitaxial material and on bulk material used for transistor fabrication.

# 1. Comparison of Epitaxial Materials Used for Device Fabrication

GaAs vapor phase epitaxial N-type GaAs was fabricated using three different reactors. The concentration was in the mid  $10^{16}$  cm<sup>-3</sup> range. Material A was grown in an automatic deposition reactor employing the halide transport technique. Material W was produced in the water vapor transport reactor and material E in the elemental source reactor. A detailed description of the three fabrication processes is given in Section II. Transistors fabricated on type A-material had gains up to 300 and were superior to those fabricated on the other materials. Transistors fabricated on type E-material had current gains up to 10, while no transistors with gains higher than 1 were fabricated on type W-material.

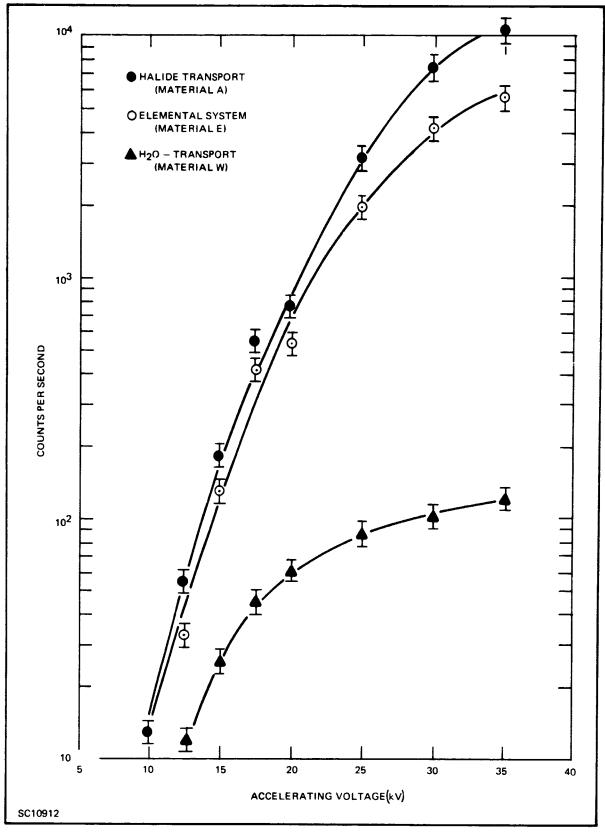

The cathodoluminescence intensity of these three materials is shown in Figure 12, as a function of the beam voltage. The vertical lines on each of the measurement points indicate the spread obtained when data were taken in 10 different spots. The spread is small, indicating that there are no gross nonuniformities over a 3-mil diameter in all three materials. We notice that the best material for fabrication of transistors also had the highest intensity, followed by the type E and type W material. In this experiment, all three samples were mounted on a quartz slide and received the same surface clean-up. Graphical differentiation of the curves in Figure 12 yielded the quantity  $d(\ln I)/d(\ln V)$ , which is plotted in Figure 13 as a function of V<sup>-2</sup> as suggested by Equation (16). As expected, all curves follow a straight line at high voltages and then level off (except material W, for which the sensitivity in the low voltage range was too small). The magnitude of the slopes of the straight line portions of the curves follow in the same order as the absolute intensities. In Table I, a description of the materials and the diffusion length derived from the curves using Equation (15) are given. We notice that the best transistor material also has the highest minority carrier diffusion and the highest ratio of nonradiative to radiative lifetime, while the worst transistor material exhibits the lowest such values. It should be noted that the data for the best material (L =  $2.2 \,\mu$ m) agree with these obtained by Wittry, et al.<sup>18</sup> (L =  $3 \mu m$ ) and Biard, et al.<sup>20</sup> (L = 3.5) who made measurements on bulk GaAs in the same concentration range used here.

At low voltages, the curves in Figure 13, level off as can be expected from inspection of Figure 10. Values for the surface depletion layer thickness d or the reduced surface recombination velocity S cannot be obtained. It can, however, be said that the ratio d/L must be very small. A rough estimate for S can be obtained as follows: The knee in the curves of Figure 13corresponds roughly to the point where  $L_M = \sqrt{S+1}$ . Using Equation (10) and rearranging the equation, S can be calculated from

$$S = 3.35 \times 10^5 \left(\frac{L}{V_M^2}\right)^2 - 1$$

(19)

Report No. 03-68-80

Figure 12. Intensity of Cathodoluminescence as a Function of Accelerating Voltage (Epitaxial Material)

•

Report No. 03-68-80

٠

29

•

| Material   | Description                                  | Dopant  | Concentration                                | Device              | Diffusion<br>Length | Relative<br>Intensity<br>(V→∞) | S   |

|------------|----------------------------------------------|---------|----------------------------------------------|---------------------|---------------------|--------------------------------|-----|

| Material A | Vapor Phase Epitaxy<br>Halide Transport      | Sn      | $\sim$ 5 x 10 <sup>16</sup> cm <sup>-3</sup> | Transistors         | 2.2 µm              | 107                            | ~10 |

| Material E | Vapor Phase Epitaxy<br>Elemental Sources     | Unknown | $\sim$ 5 x 10 <sup>16</sup> cm <sup>-3</sup> | Transistors         | 1.8µm               | 57                             | ~10 |

| Materisi W | Vapor Phase Epitaxy<br>Water Vapor Transport | Sn      | $\sim$ 5 x 10 <sup>16</sup> cm <sup>-3</sup> | Transisto <b>rs</b> | 0.7µm               | 1                              | ~10 |

Table I.

Comparison of Material and Device Properties

For all three samples, this leads to values for S of about 10. Wittry obtained for a similar material d/L = 0.05 and S ~ 20, while Biard finds S ~ 14. The surface recombination velocity is estimated to be  $4 \times 10^5$  cm<sup>2</sup>/sec using a hole mobility of 200 cm<sup>2</sup>/V sec and the experimentally determined values of S = 10 and L = 2.2  $\mu$ m. The importance of the type of analysis performed here is not as much the yield of quantitative results as the fact that materials can be selected by cathodoluminescence measurements. It further means that the minority carrier diffusion length of the starting material is a meaningful parameter that relates to device performance. Because of the involvement of many parameters, the method described here will not easily yield information about comparable materials but will have merits in separating material that can be used for device fabrication, e.g., material A and E from material that is unsuitable for this purpose, e.g., material W.

#### 2. Studies on the Spatial Distribution of Cathodoluminescent Light

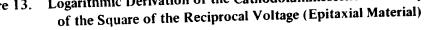

A comparison of four types of transistor grade materials was made by studying the spatial distribution and the intensity of the cathodoluminescent light. The relative intensities are shown in Figure 14 over an area comparable in size to a transistor mesa. The four types of materials were

- a) S-doped epitaxial material (grown under contract AFAL-TR-66-361), probably contaminated with Cd ( $N_D = 5 \times 10^{15} \text{ cm}^{-3}$ ).

- b) Standard epitaxial material grown under this contract (N<sub>D</sub> =  $5 \times 10^{16}$  cm<sup>-3</sup>).

- c) S-doped epitaxial material, counterdoped with Cd (N<sub>D</sub> =  $5 \times 10^{15}$  cm<sup>-3</sup>).

- d) Si-doped bulk material (N<sub>D</sub> =  $2 \times 10^{16}$  cm<sup>-3</sup>).

The absolute intensity measured on sample (b) was highest probably due to the higher donor concentration. Next followed the intensity of samples (a) and (c) both of comparable value. The lowest intensity by far was measured on sample (d).

A detailed analysis indicates a similarity between material (a) and (c) as far as the uniformity and intensity of the cathodoluminescence output is concerned, though the diffusion length of material (a) was somewhat larger. The bulk material showed an erratic behavior caused by gross nonuniformities in the material, though portions of this material might be superior to the epitaxial materials. This was borne out by the fact the good transistors on bulk material were distributed at random over the slice. Also, the base distributed on front shows irregularities.

Figure 14. Spatial Distribution of Cathodoluminescence Light

Figure 14 shows that, in many cases, the substrate material is not uniform even over the extension of a single transistor. Adding a compensating impurity such as Cd seems to improve the uniformity.

## 3. Dependence of Materials Parameter on the Ga:As Ratio

Experiments described in Section II show that for a given fabrication method, the properties of the material vary widely with small change in the growth conditions. Cathodoluminescence measurements were performed to characterize the deposited layer. The only other information that can be obtained is the breakdown voltage measurements which give an estimate of the donor concentration. Hall measurements are not possible because of the N<sup>+</sup> substrate, while deposits on semi-insulation material are not representative because the influence of the substrate materials is neglected. Though earlier experiments have shown that material from the elemental source reactor is somewhat inferior from the device point of view, this epitaxial deposition system is the only one that allows studying the effect of growth conditions on growth rate and quality of the deposit.

In Figure 15, the maximum cathodoluminescence intensity (at high beam voltage) is plotted versus the donor concentration. Donor concentration was obtained by measuring the point breakdown voltage in several regions. The average breakdown voltage was used to determine the donor concentration from published charts.<sup>21</sup> The numbers next to the measurement points are

referred to in Table II. Accuracy of the donor concentration is not better than  $\pm 50$  percent. Nevertheless, the quantum efficiency increases monotonically with the exception of sample 138. So far, no explanation has been found for the high efficiency of run 138. It is of interest, however, to note that the growth rate decreases monotonically with decreasing arsenic control temperature while the donor concentration increases. But this also is with the exception of run 138.

| Run<br>No. | Substrate<br>Doping | Orientation | Breakdown<br>Voitage<br>(V) | Net Donor<br>Concentration<br>(cm <sup>-3</sup> ) | Growth<br>Rate<br>(µm/h) | Arsenic<br>Control<br>Temperature<br>(°C) | Relative<br>Quantum<br>Efficiency | Diffusion<br>Length<br>(µm) |

|------------|---------------------|-------------|-----------------------------|---------------------------------------------------|--------------------------|-------------------------------------------|-----------------------------------|-----------------------------|

| 134        | Sn                  | (100)       | 150                         | 3.5 x 10 <sup>14</sup>                            | 27.0                     | 416                                       | 35.5                              | 1.8                         |

| 135        | Те                  | (100)       | 60                          | $4.0 \times 10^{15}$                              | 15.0                     | 406                                       | 130.0                             | 1.5                         |

| 136        | Те                  | (100)       | 40                          | 1.0 x 10 <sup>10</sup>                            | 12.0                     | 396                                       | 170.0                             | 4.7                         |

| 137        | Te                  | (100)       | 30                          | 2.5 x 10 <sup>10</sup>                            | 6.0                      | 387                                       | 480.0                             | 2.3                         |

| 138        | Te                  | (100)       | 40                          | 1.0 x 10 <sup>10</sup>                            | 6.8                      | 387                                       | 920.0                             | 3.3                         |