https://ntrs.nasa.gov/search.jsp?R=19690022836 2020-03-12T05:06:37+00:00Z

# PROCESS TECHNIQUES STUDY OF INTEGRATED CIRCUITS INTERIM SCIENTIFIC REPORT NO. 2

By J.V. Brandewie and P.H. Eisenberg

June 1969.

Prepared under Contract No. NAS 12-4 by NORTH AMERICAN ROCKWELL CORPORATION Anaheim, California

Electronics Research Center NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# PROCESS TECHNIQUES STUDY OF INTEGRATED CIRCUITS INTERIM SCIENTIFIC REPORT NO. 2

By J.V. Brandewie and P.H. Eisenberg

June 1969

Prepared under Contract No. NAS 12-4 by NORTH AMERICAN ROCKWELL CORPORATION Anaheim, California

Electronics Research Center NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

ij

# CONTENTS

|                                                                                                                                                                                                                                      | Page                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Introduction                                                                                                                                                                                                                         | 1                                            |

| Summary                                                                                                                                                                                                                              | 5                                            |

| Mechanism Research                                                                                                                                                                                                                   | 7                                            |

| Effects of Oxide Thickness and Stress<br>Silicon Surface and Initial Oxidation Aspects<br>Nonoxidative vs Oxidative Cleaning<br>HCl Wafer Pretreatment<br>Dielectric Defects – Vendor Survey<br>Dielectric Defects – Pilot Line Test | 7<br>8<br>10<br>13<br>18<br>19               |

| Bibliography on Silicon Surface Passivation                                                                                                                                                                                          | 25                                           |

| Preparation of Oxide Layers<br>Other Passivation Techniques<br>Passivation Layer Mechanical Aspects<br>Passivation Layer Properties and Evaluation Techniques                                                                        | 25<br>26<br>26<br>28                         |

| References                                                                                                                                                                                                                           | 29                                           |

| Appendix A. Oxide Defect Test Procedure                                                                                                                                                                                              | 33                                           |

| Scope                                                                                                                                                                                                                                | 33<br>33<br>34<br>34<br>37<br>37<br>37<br>37 |

| Appendix B. Summary - Factors Influencing Dielectric Defects in<br>Silicon Oxide Layers By P. J. Besser, J. E. Meinhard, and<br>P. H. Eisenberg                                                                                      | 39                                           |

| Abstract                                                                                                                                                                                                                             | 39<br>41                                     |

| Appendix C. Evidence of Mechanical Stress as a Cause of<br>Dielectric Defects in Silicon Dioxide Layers                                                                                                                              | 45                                           |

| References                                                                                                                                                                                                                           | 48                                           |

# **CONTENTS (Cont)**

|                                                                                          | Page |

|------------------------------------------------------------------------------------------|------|

| Appendix D. Measurement of Compressive Stress in Oxide Layers                            | 49   |

| Appendix E. Wafer Oxide Defect Data<br>(Autonetics M & P Laboratory Experimental Wafers) | 51   |

| Appendix F. Wafer Oxide Defect Data<br>(Vendor Wafers)                                   | 65   |

| Appendix G.Wafer Oxide Defect DataAutonetics MOS Device Pilot Line                       | 69   |

# **ILLUSTRATIONS**

| Figure |                                                                  | Page      |

|--------|------------------------------------------------------------------|-----------|

| 1.     | Oxide Defect Dependence on Processing                            | 6         |

| 2.     | Defects as a Function of Oxide Thickness for                     |           |

|        | Various Stress Conditions                                        | 9         |

| 3.     | Comparison of Oxidative Precleaning with Nonoxidative            |           |

|        | Precleaning Plus Initial Slow Growth                             | 12        |

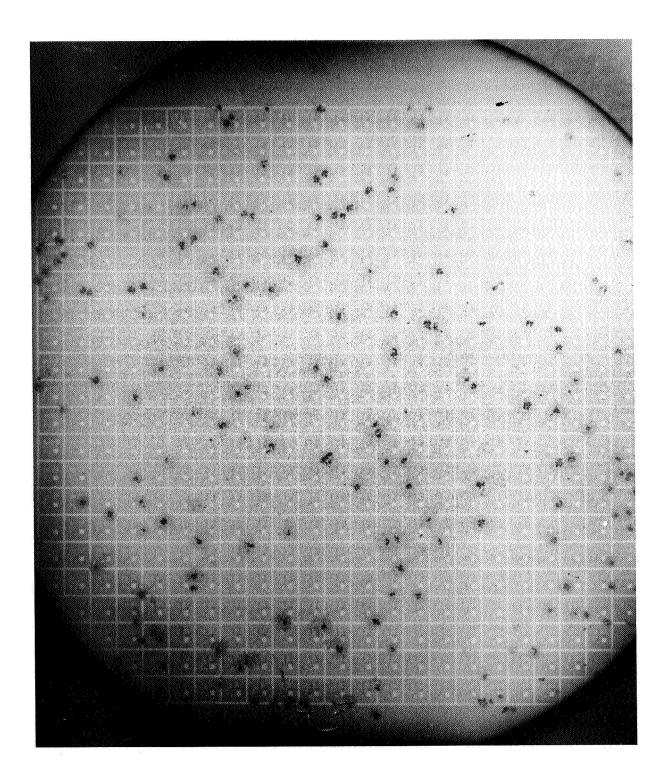

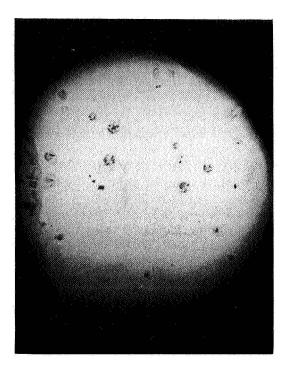

| 4.     | Test Wafer Showing Random Distribution of Dielectric Defects     | <b>21</b> |

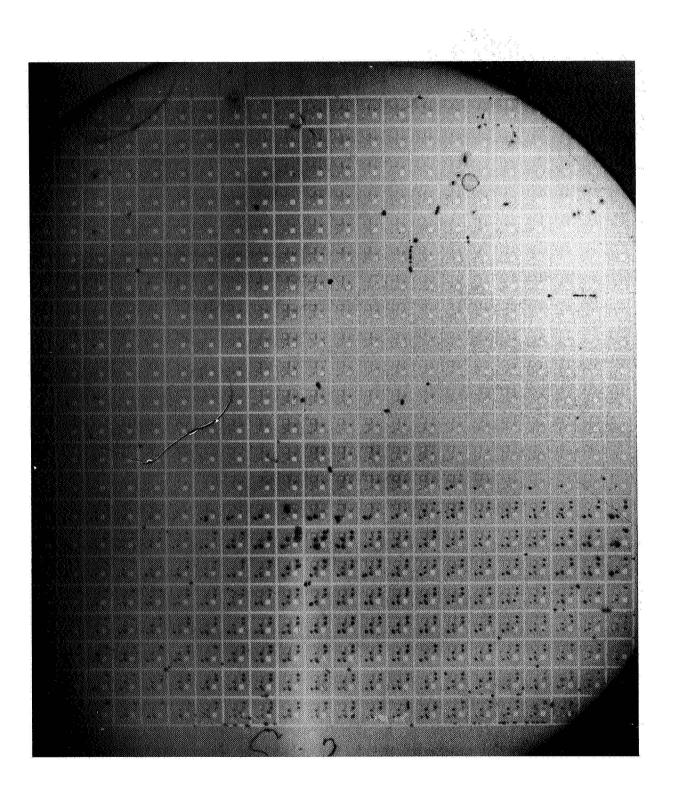

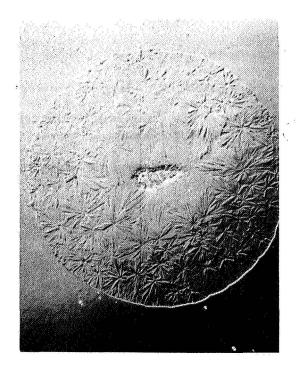

| 5.     | Test Wafer Showing Non-Random Distribution of Dielectric Defects | 22        |

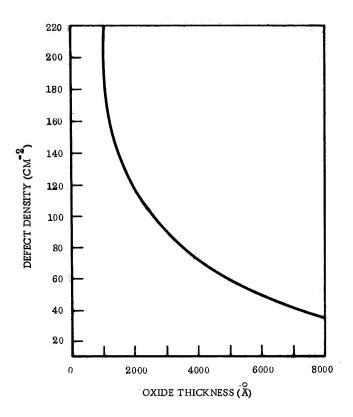

| B-1.   | Defect Density Variation in Virgin Thermal Oxide                 | 40        |

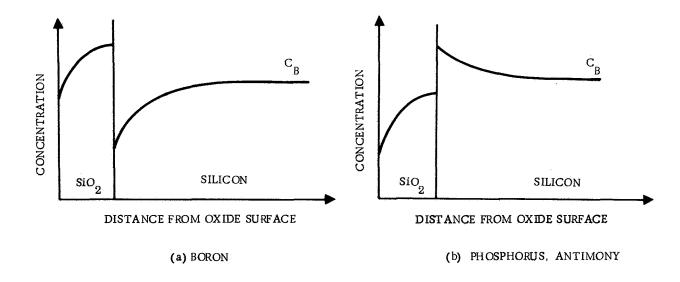

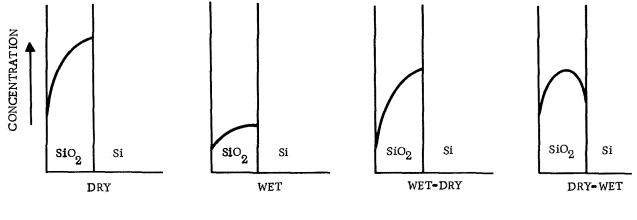

| B-2.   | Impurity Profiles in Oxidized Silicon Wafers.                    |           |

|        | CB Denoted Bulk Impurity Concentration (From Grove, et al,       |           |

|        | Reference 20)                                                    | 42        |

| B-3.   | Postulated Boron Distributions in Thermally Grown Oxides         | <b>43</b> |

| C-1.   | Oxide Defect Decorations on Silicon Wafer Specimen No. 4 of      |           |

|        | Table C-1 (Outer Diameter 2.3 cm.)                               | 46        |

| C-2.   | Etch Pit in Silicon (Center) and Surrounding                     |           |

|        | Structure (Outer Diameter $600 \mu$ )                            | 47        |

# TABLES

### <u>Table</u>

| I<br>II ··· | Correlation of Defect Densities With Various Stress Conditions<br>Defect Densities as a Function of Pretreatments and Growth Rate | 8<br>1 <b>1</b> |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|

| ÎII         | Effect of HCl Pre-etching on Subsequent Oxide Defect Densities                                                                    | 14              |

| IV          | High Temperature Heat-Soak Effects on Subsequent Defect                                                                           |                 |

|             | Densities                                                                                                                         | 15              |

| V           | Effects of HCl Pretreatment and Heat-Soak on Defects                                                                              | 16              |

| VI          | Oxide Defects as a Function of Previously Introduced Etch Pits                                                                    | 17              |

| VII         | Defect Levels in 10,000 Å Oxides From Various Sources                                                                             | 18              |

| VIII        | Variation of Defect Densities With Processing and Pretreatments                                                                   | <b>20</b>       |

| C-1         | Oxide Dielectric Defects Located by Electrophoretic Decoration                                                                    | <b>46</b>       |

| D-1         | Correlation of Defect Densities With Oxidation and Stress                                                                         | 49              |

| E-1         | Defect Densities as a Function of Wafer Stress                                                                                    | 52              |

| E-2         | Defect Densities as a Function of Preoxidation Treatment and                                                                      |                 |

|             | Initial Oxidation Rate                                                                                                            | 54              |

| E-3         | HCl Pre-Etch Data                                                                                                                 | 57              |

| E-4         | High Temperature Soak Data                                                                                                        | 59              |

| E-5         | HCl Pretreatment Data                                                                                                             | 62              |

### INTRODUCTION

This Second Interim Scientific Report prepared under NASA Contract No. NAS 12-4 describes the program effort for the period May 1968 to February 1969. The objectives of this effort were to discover why structural defects are produced in thermally grown oxides and to learn how they may be prevented. In order to reach these objectives it was first necessary to develop a tool (described in Appendix A) for the reliable location and identification of oxide defects. This technique was then successfully utilized to isolate those process and structural considerations which contribute significantly to increased defect densities. Early program results confirmed that the inherent thermal mismatch between silicon and silicon dioxide was a significant cause of oxide defects and provided a lower limit of defects which could not be reduced by processing changes. It was later determined that one of the most critical process related factors is the initial condition of the silicon surface in terms of cleanliness and smoothness. As a result, an improved surface preparation technique was developed which significantly reduced defect densities. At least two major semiconductor manufacturers are presently using the defect detection technique developed on this program.

One of the most frustrating and widespread problems in planar technology is that caused by dielectric defects, or "pinholes," in oxide layers. The characteristic failure mode introduced by oxide defects is an electrical discharge through the defect from an overlying metallization to the substrate. The metallization need not fill the hole for failure to occur; plasma breakdown can occur in the intervening space. In the case of very small diameter holes, the discharge current may not be large enough initially to constitute a failure. But redistribution of metallization throughout the hole as a result of prolonged plasma discharge ultimately may create a much more highly conductive path and a clearly defined failure. This supports the fact that not all pinhole failures are recognized as such at initial burn-in or early systems test stages but show up later as long term effects in the field. The importance of eliminating this processing problem is clearly evident, not only for high reliability guidance systems, but also for increasing component yields, particularly in the case of LSI and MOSFET gate oxides.

Although numerous remedial innovations in materials and process techniques have been attempted, no reliable solution to this problem has yet been found. Because of the general convenience and superiority of thermally grown oxides for most masking and passivating purposes, and because this application of silicon dioxide has been successfully optimized in most other respects, it seems important to take full advantage of these characteristics by determining the process requirements needed to remove this remaining major problem in its use.

Initial activity on this program sought to relate the origin of dielectric defects to various process factors and structural considerations. These results may be summarized as follows:

- 1. Factors tending to increase dielectric defects.

- a. Extended processing (generally)

- b. Higher compressive stress in the oxide

- c. Embedded lapping grains in the substrate

- d. Superficial HF etching

- e. Abrupt oxide steps

- f. Thermal cycling

- g. Mechanical wiping

- h. Removal of back oxide layers

- 2. Factors tending to decrease dielectric defects.

- a. Growth of oxide to higher thicknesses

- b. Chemical etch of initial wafer

- c. Pyrolytic oxide, uniformly applied and properly densified

- d. Additives tending to reduce bond strain in silica glass

- e. Addition of steam to oxidation process gas

The results noted above are consistent with a compressive stress model as the principle source of dielectric defects in oxide layers. The compressive stress in the oxide layer is introduced during cooling from the oxidation temperature as a result of an approximately tenfold mismatch in thermal expansion coefficients between substrate and dielectric. This model was confirmed in a number of subsequent experimental observations. Replicate electron microscopy of a known defect revealed oxide outcroppings suggestive of a compressive stress relief process. Measurements of the compressive stress gave values of the order of  $4 \times 10^4$  psi. Quantitative comparison of oxide defect densities before and after cooling to room temperature demonstrated that the bulk of the defects (90 to 98 percent) were introduced during the cooling process. Removal of one oxide layer from a wafer introduced a significant warping of the wafer which resulted in an increase in the measured defect population in the remaining oxide layer.

A tool developed on this program for locating and identifying oxide defects is based on a functional test originated by James Lytle of Westinghouse. This test, known as "Electrophoretic Decoration," is particularly applicable to wafers in the beginning stages of manufacture. The test utilizes the oxidation of a metal anode to form positively charged colloidal particles which are propelled through an organic electrolyte toward cathodic sites on an oxide coated silicon wafer situated below the anode. The accumulation and discharge of the colloidal salt particles around oxide defect sites occurs as a result of electron transfer through the defects from the negatively charged silicon wafer. Thus the functional mode of the test is identified with the failure mode sought. The accumulated insoluble matter surrounding each defect serves as a many-fold magnification of the defect location which, for documentary purposes, is readily photographed at low magnification. (A detailed description of the test developed is given in Appendix A.) The following report indicates that this technique has been used successfully on two kinds of investigations. The first investigation is an evaluation of oxides from various sources for silicon wafer lots oxidized to 10,000 Å by three different processors. The second investigation assesses the effect of various wafer pretreatments, reflecting various methods of preparing the wafer prior to oxidation and yielding thereby essential process control information.

Appendixes B, C, and D have been repeated from Interim Scientific Report No. 1 as a convenience to the reader for reference purposes.

This page intentionally left blank.

### SUMMARY

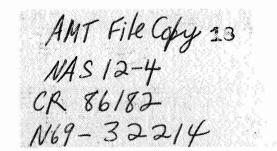

Several experiments were conducted to more clearly define the origin of oxide defects in terms of processes and to ascertain the dependence of oxide defects on various process steps. Figure 1 is a summary of the results obtained, indicating the defect decay curves as a function of oxide thickness for four basic processes. Curve A represents initial wafer treatments as grown early in the program. Curves B and C are subsequent improvements in terms of reduced oxide defects (at low thicknesses) vs wafer surface pretreatments. From these mechanistic studies it was postulated that the primary local cause of dielectric defects is physical promontories in the silicon substrate which result in stress concentrations on the grown oxide after cooling to room temperature. The shear component of these stresses is believed to result in the defect occurrence at these sites. A recommended optimum oxide growth process for minimizing dielectric defect densities in thin oxide regions was defined. Utilization devices especially with the advent of thin MOS capacitor regions.

A series of wafers were obtained from three different vendors for comparison purposes. The defects are indicated in the graph at the 10,000 A level. It is believed that the superiority of vendor A is due to the utilization of a wafer pretreatment similar to that developed on curve C (HCl vapor etch).

A special program was also performed to test the developed wafer pretreatment in an actual pilot line operation. The standard pilot line process was compared with two process modifications. The effect of wafer pretreatment on the final oxide integrity was also evaluated. The data obtained at two oxide thicknesses (1400 and 14,000 Å) using a test pattern are also shown in Figure 1. The 14,000 Å data is obviously much higher than any of the other results obtained when extrapolated to comparable thicknesses. These data are comparable, it is felt, since the oxide has been through several thermal cycles which will cause additional defects as determined previously on this program.

The 1400 Å thickness, however, is a regrown area and has seen fewer thermal excursions. These data appear to be comparable with the vendor oxide data except for Vendor A, which is clearly superior. (In this comparison it is necessary to extrapolate using the same decay constant as either curve B or C.)

Further experiments are recommended to implement the developed process modifications on actual production devices. Also other reliability testing is needed to ensure that other problems are not introduced as a result of the changes made.

Figure 1. Oxide Defect Dependence on Processing

### MECHANISM RESEARCH

A series of experiments were conducted in an attempt to determine the mechanism and thus the origin of oxide dielectric defects. As previously discussed, tests conducted in this laboratory and confirmed by other work established beyond reasonable doubt that the origin of physical forces were due to the thermal mismatch compressive stress in the coated oxide. However, no direct indication of the local factors contributing to their formation was known.

#### Effects of Oxide Thickness and Stress

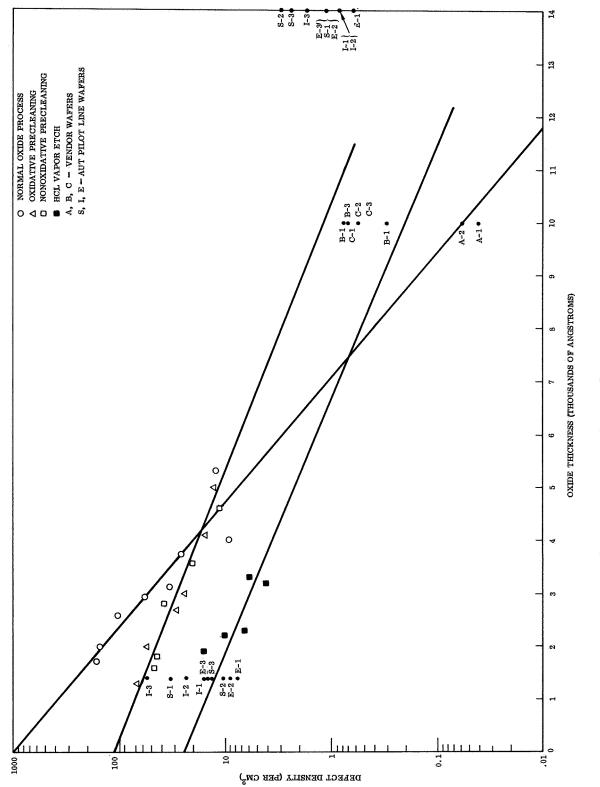

Additional experiments were undertaken to examine in detail the kinetics of the oxidation process. Investigations were conducted to compare defect densities at no stress (before cooling), at full stress (after cooling), and at partial stress relief (after removal of the back oxide layer). These data are listed in Table I Appendix A), and Figure 2 for a series of oxide thicknesses. Conventional oxide growth technique was used (N<sub>2</sub>:245 cc/min; O<sub>2</sub>:245 cc/min passed through water at slightly less than 100 C; temperature: 1180 C) followed by HC $\ell$ -He etching before removal from the growth zone. Defect densities were evaluated by standard etch pit and decoration counts. The exponential decrease in the number of defects with oxide growth is apparent from Figure 2. Decay of this number, N, may be expressed in terms of layer thickness

$$N = N_{z} e^{-\phi z}$$

(1)

where  $N_Z$  is the preexponential factor (ordinate intercept) and  $\phi$  is the decay factor. Decay factors appropriate to Figure 2 are 2.22, 1.08 and 0.83 respectively for no stress, full stress, and partial stress.

The decay factors followed an exponential law and were largest prior to wafer cooling (unstressed condition) and smallest after warping the wafer by removal of one oxide layer. The general nature of these results indicated the existence of latent defects in the oxide prior to cooling which were progressively strengthened and rendered less vulnerable to rupture as oxide thickness was increased. The assumed presence of such latent defects, however, implied the existence of structural or distributional irregularities in the oxide-substrate system introduced either before or during the oxidation process.

The existence of a virtual defect density (N of Eq 1) of the order of  $10^3/\text{cm}^2$  is significant. However, one must still assume a very large defect density at some small t > 0 which increases exponentially with thinner oxides. This problem is especially critical to MOSFET technology where gate oxides of 1000 Å, or less, are generally required. It seems more important, therefore, to understand the physical basis for the virtual defect density, so that it can be manipulated downwards, rather than attempting to increase defect decay factors.

|                        |         | Oxidation                               |           | Def                            | ects: Per cm               | 2 *                           |

|------------------------|---------|-----------------------------------------|-----------|--------------------------------|----------------------------|-------------------------------|

| Oxide (Å)<br>Thickness | Run No. | 1 · · · · · · · · · · · · · · · · · · · | $t^{1/2}$ | No Stress<br>(vapor etch pits) | Full Stress<br>(decorated) | Partial Stress<br>(decorated) |

| 1720                   | ·A      | 5                                       | 2.24      | 39                             | 161                        | 292                           |

| 1995                   | B**     | 10                                      | 3.16      | 10                             | 151                        | 190                           |

| 2590                   | C       | 15                                      | 3.87      | 3.0                            | 101                        | 142                           |

| 3125                   | D       | 20                                      | 4.47      | 1.5                            | 33                         | 43                            |

| 2945                   | EJ      | 25                                      | 5.00      | 1.2                            | 55                         | 93                            |

| 3760                   | I       | 25                                      | 5.00      | 1.2                            | 26                         | 40                            |

| 4010                   | F**     | 40                                      | 6.32      | 0.3                            | 9                          | 42                            |

| 5325                   | G       | 60                                      | 7.81      | 0                              | 12                         | 29                            |

TABLE I CORRELATION OF DEFECT DENSITIES WITH VARIOUS STRESS CONDITIONS

\*All entries represent an average of four wafers – data in Appendix E-1 \*\*Runs selected for initial Proficorder study

#### Silicon Surface and Initial Oxidation Aspects

Further investigation revealed that a kinetic anomaly in oxide growth rate existed at the beginning of oxidation (during the first 300 to 600 Å) after which a square root law characteristic of a diffusion controlled process was followed. Attention, therefore, was focused on the beginning phase of oxidation in the expectation that moderation of the reaction kinetics at this point might remove an assumed distributional irregularity in the oxide and thereby reduce the latent defect density. Such a moderation was achieved (and kinetically demonstrated) by application of an oxidative pretreatment (using hot nitric acid) which developed a very thin oxide layer on the wafers prior to high temperature oxidation. A significant drop in the latent defect density (extrapolated to oxidation time zero) was observed as a result of this treatment.

Accordingly, wafers were pretreated in a manner designed to produce diffusion attenuation layers on the surfaces. These layers consist primarily of silicon dioxide in the 200 Å or less thickness range produced by a wet chemical method consisting of treating the wafers with HF (to remove old oxide), KOH solution (to remove residual fluoride), and hot concentrated nitric acid (to remove residual KOH and initiate uniform oxidation). Each step was followed by thorough rinsing with distilled water. The exact nature of the layers so produced still is unknown. Boundaries in such layers

.....

Figure 2. Defects as a Function of Oxide Thickness For Various Stress Conditions

produced by controlled (masked) HF etching are readily revealed by moisture condensation from a humid environment. Attempts to measure the thickness of the layers by Proficorder and Tally-Surf tracing, and by interferometry, however, failed. Although the layers are suspected of being a porous and partly hydrated silicon dioxide, the possibility of a small component of nitride cannot be ruled out.

High temperature oxide defect densities on wafers so treated (termed hereinafter "oxidative precleaning") were found to be practically nonexistent, even for oxidation time as short as 2.5 min. Room temperature decorated defects, however, were significant. The corresponding defects densities are shown as Set A in Table II.

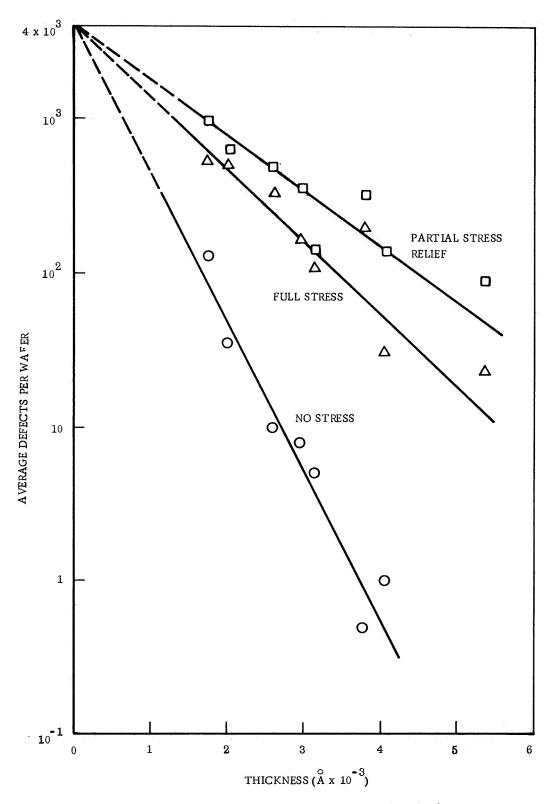

#### Nonoxidative vs Oxidative Cleaning

It was not clear from these results whether the decrease in defect density was due solely to the initial oxidative attack on the substrate or to an additional "cleansing effect" caused by the nitric acid treatment. Therefore a "nonoxidative" precleaning technique was developed. In this case the wafers were "nonoxidatively" precleaned using a swabbing technique with HF, preceded and followed by water and alcohol rinses.

Slow oxide growth was achieved by limiting the oxygen to 4 percent of the process gas composition and by reducing the temperature of the water reservoir. The oxidation temperature, however, remained at 1180 C.

All data were taken as a function of oxide thickness grown, as measured (in most cases) by Proficorder tracing. All defect readings are recorded on a  $\rm cm^{-2}$  basis. In addition the ratio of etch pits (high temperature defects) to decorations (room temperature defects) were computed for each series, where applicable, as a further test of internal consistency. The "nonoxidative" results are shown as Set B in Table II.

Comparison of Sets A and B in Table II plotted against oxide thickness (Figure 3) indicates that there may be little or no difference in how the initial oxidation rate is moderated. The effect of both on the virtual defect density appears to be significant. Compared with earlier results, which yield a virtual defect density of  $-4 \times 10^3$  per wafer ("Full Stress" curve, Figure 2), or  $>10^3$  cm<sup>-2</sup>, the present treatments yield an order of magnitude improvement ( $-1.1 \times 10^2$  cm<sup>-2</sup>). Although the defect decay rate is somewhat smaller than that applicable to Figure 2, this potential modification in process technique may have important implication for thin oxide applications, such as MOS gates. At 1000 Å oxide thickness, for example, Figure 2 yields a density of 410 defects cm<sup>-2</sup> (taking the wafer area as 3.2 cm<sup>2</sup>) while Figure 3 yields a density of 70 cm<sup>-2</sup>.

This result was taken as potential confirmation that the assumed initial inhomogeneities associated with latent defect densities were, in fact, related to the observed kinetic anomaly at the beginning of oxidation. Further attention was given, therefore, to the effects of the various process parameters on defect densities in the first few hundred Angstroms of growth. It was shown that the nonoxidative precleaning treatment was superior to the oxidative treatment in reducing defect densities in this

|                                                                 |                                              |             |       |         |       |      |                                           |         |                 | -       |         |         |

|-----------------------------------------------------------------|----------------------------------------------|-------------|-------|---------|-------|------|-------------------------------------------|---------|-----------------|---------|---------|---------|

|                                                                 | Etch-Pits/<br>Decorations                    | -<br>-<br>- |       |         |       |      |                                           |         | 0.0018          |         | 0.004   |         |

| KUWTH KATE                                                      | Decoration<br>Density<br>(cm <sup>-2</sup> ) | 67. 0       | 54. 0 | 27.6    | 23. 5 | 15.7 | 12.6                                      | 47.4    | 43.6            | 37. 7   | 20. 0   | 11.3    |

| ENTS AND G                                                      | Etch-Pit<br>Density<br>(cm <sup>-2</sup> )   |             |       |         |       |      | ann - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | o       | 0.079           | 0       | 0.079   | 0       |

| F FRETREATM                                                     | Oxide<br>Thickness<br>(Angstroms)            | 1300        | 2000  | 2700    | 3000  | 4100 | 5000                                      | 1600    | 1800            | 2800    | 3600    | 4600    |

| A FUNCTION U                                                    | Oxide<br>Growth Rate                         | Normal      |       |         |       |      |                                           | Slow to | 400 Å<br>then   | Normal  |         |         |

| DEFECT DENSITIES AS A FUNCTION OF PRETREATMENTS AND GROWTH RATE | Water<br>Temperature<br>(Deg C)              | 95          |       | <u></u> |       |      |                                           | 34-35   | )<br>)<br> <br> |         |         |         |

| DEFEU                                                           | Wafer<br>Precleaning                         | Ox.         | Ox.   | Ox.     | Ox.   | Ox.  | Ox.                                       | Non-Ox  | Non-Ox.         | Non-Ox. | Non-Ox. | Non-Ox. |

|                                                                 | Set                                          | A           |       |         |       |      |                                           | д       | )               |         |         |         |

TABLE II DEFECT DENSITIES AS A FUNCTION OF PRETREATMENTS AND GROWTH RATE

Data in Appendix E-2

11

Figure 3. Comparison of Oxidative Precleaning With Nonoxidative Precleaning Plus Initial Slow Growth

12

region. It also was shown that initial slow thermal oxidation after the nonoxidation precleaning produced additional oxide improvement if dry, rather than wet, oxygen was used. It was possible at this point, therefore, to formulate a tentative set of optimum process conditions for oxide growth. These included an initial nonoxidative precleaning of the wafers (using a wiping technique with HF, as previously described) and an extremely slow initial growth of thermal oxide using dry oxygen, followed by conventional growth with moist oxygen.

In attempting to adduce a physical basis for the effects described above, it became evident that the controlling process parameter might be one of equilibration rather than of oxygen diffusion attenuation. That is, the inhomogeneities determining defect loci might as well be purely structural instead of being confined to the result of kinetic irregularities in the initial oxide distribution. In either case, then, the initial slow oxidation might provide the necessary conditions for the equilibrium distribution of either oxide or substrate material, whereas oxygen diffusion attenuation alone would affect only the oxide distribution. The participating physical irregularities of the oxide-substrate system, regardless of origin, would be in the submicron range; e.g., a significant fraction of the oxide layer thickness and several orders of magnitude greater than the substrate lattice parameter. The appearance of a defect in the oxide layer (after cooling) then would become a function of the particular local stress conditions associated with the radius of curvature of the presumed structural irregularity. As more oxide is grown the ratio of the radius of curvature to the oxide thickness will decrease exponentially with oxide thickness, thus accommodating the corresponding disappearance of dielectric defects. In addition to accounting for the localization of oxide defects a model of this type is more susceptible to physical verification.

The nitric acid pretreatment would be expected to attack microscopic promontories on the silicon surface more rapidly than surrounding smooth areas, thus reducing their effectiveness in creating localized stress anomalies in the subsequent oxide layers. Reconsideration of the "nonoxidative" pretreatment discloses that the opportunity for limited oxidation occurs here, too, because the HF wiping procedure is done in the presence of air. In other words, the treatment is nonoxidative only in the sense that it leaves no additional oxide layer on the silicon surface. The wiping process therefore can be regarded as a chemical lapping in which promontories are more susceptible to erosion than surrounding flat areas. The HF serves the familiar function of removing silicon dioxide as it is formed.

#### HCl Wafer Pretreatment

The above concept was subjected to further test by applying an HC $\ell$  vapor etch to wafers (four sets of four each) immediately prior to oxidation. \* This idea is not novel, as it has been recently learned that Semimetals (q. v., below) employs the

<sup>\*</sup>This treatment differs from one investigated earlier at the Qualification and Standards Laboratory, NASA-ERC, where HC $\ell$  was admitted <u>during</u> oxidation in an attempt to modify the composition and structure of the oxide layers as they were grown.

same treatment prior to wafer oxidation. The decoration densities resulting from the inclusion of this treatment are compared in Table III with a similar set in which the HCl pretreatment was omitted. It is clear than an improvement was thereby achieved (in the 500 Å thickness range) even though both sets of wafers also were pretreated by the chemical lapping ("nonoxidative") method.

Continuing further with the equilibration approach, tests were designed to maximize the redistribution of assumed structural irregularities both in "bare" silicon and in very thin initial oxide layers using various heat-soak periods at the oxidation temperature (1180 C). Because this temperature is well above the set temperature of silica (1000 C) it was felt that the oxide would be sufficiently plastic to conform to any interfacial energy-reducing material migrations. In consideration of the number of process variables of interest a simple matrix was designed in which the normal oxidation periods were given only two values (5 min and 20 min, Table IV). These process variables included a comparison of the effects of initial oxide layers produced by oxidative precleaning technique with those produced by initial thermal oxidation (using 4 percent dry  $O_2$  diluted with helium) (sets C and D), time of heat soak in nitrogen (two values) (sets E and F), and comparison of dynamic with essentially static nitrogen flow during heat-soak (sets D and E). A control omitting the major variable was included with each run. Each charge consisted of four wafers whose etch-pit and decoration counts were averaged to yield the data in the last two columns of Table IV.

| Set | Wafer<br>Precleaning | HCl Pre-<br>treatment | Water<br>Temperature<br>(Deg C) | Oxygen<br>Conc.<br>(Percent) | Oxide<br>Thickness<br>(Angstroms) | Decoration<br>Density<br>(cm <sup>-2</sup> ) |

|-----|----------------------|-----------------------|---------------------------------|------------------------------|-----------------------------------|----------------------------------------------|

| A   | Non-Ox               | None                  | 50                              | 4                            | 470                               | 860                                          |

|     | Non-Ox               | None                  | 50                              | 4                            | 480                               | 390                                          |

|     | Non-Ox               | None                  | 50                              | 4                            | 600                               | 314                                          |

|     | Non-Ox               | None                  | 50                              | 4                            | 650                               | 121                                          |

| в   | Non-Ox               | 1 min                 | 50                              | 4                            | 500                               | 201                                          |

|     | Non-Ox               | 1 min                 | 50                              | 4                            | 500                               | 144                                          |

|     | Non-Ox               | 1 min                 | 50                              | 4                            | 510                               | 278                                          |

|     | Non-Ox               | 1 min                 | 50                              | 4                            | 560                               | 46                                           |

TABLE III \*EFFECT OF HCl PRE-ETCHING ON SUBSEQUENT OXIDE DEFECT DENSITIES

\*Data in Appendix E-3

| ×                                                                  | Defect<br>Decorations<br>(cm <sup>-2</sup> ) | 161  | 61       | 29   | 12       | 37     | 31       | - 19   | 4.4      | 17     | 15       | 15     | 9.4      | 10.3   | 82       | 5.7    | 15.7      |

|--------------------------------------------------------------------|----------------------------------------------|------|----------|------|----------|--------|----------|--------|----------|--------|----------|--------|----------|--------|----------|--------|-----------|

| DENSITIES                                                          | Etch-Pits<br>(cm <sup>-2</sup> )             | 9.4  | 9.3      | 2.5  | 3.1      | 0.63   | 8, 06    | 0      | 0.08     | 0.63   |          | 1.57   | 0.24     | 1.8    | 18.3     | 0      | 0.6       |

| UENT DEFECT                                                        | Oxide<br>Thickness<br>(Ängstroms)            | 1400 | 1400     | 3000 | 3100     | 1300   | 1550     | 3200   | 2900     | 1700   | 1400     | 3000   | 3100     | 2200   | 1200     | 3300   | 2700      |

| ON SUBSEQ                                                          | Normal<br>Oxidation<br>(Min)                 | ວ    | 21       | 20   | 20       | വ      | 2        | 20     | 20       | 2      | വ        | 20     | 20       | QJ     | ß        | 20     | 20        |

| EFFECTS                                                            | N2 Flow<br>(cc/min)                          | 480  | 480      | 480  | 480      | 480    | 480      | 480    | 480      | 10     | 10       | 10     | 10       | 10     | 10       | 10     | 10        |

| HEAT-SOAK                                                          | Heat-Soak<br>in N2<br>(Hrs)                  | 5    | 61       | 63   | 7        | 5      | C3       | 01     | 73       | 5      | 7        | 01     | 7        | 16     | 16       | 16     | 16        |

| HIGH TEMPERATURE HEAT-SOAK EFFECTS ON SUBSEQUENT DEFECT DENSITIES* | Thermal Pre-<br>Oxidation<br>(Min)           | None | None     | None | None     | Ω      | None     | QI     | None     | ດາ     | None     | ດາ     | None     | ດາ     | None     | ວ      | None      |

| HIGH                                                               | Wafer<br>Precleaning                         | Ox   | Non-Ox** | Ox   | Non-Ox** | Non-Ox | Non-Ox ** |

|                                                                    | Set                                          | c    |          |      |          | A      |          |        |          | ы      |          |        |          | ۲щ     |          |        |           |

|                                                                    |                                              |      |          |      |          |        |          |        |          |        |          | A      |          |        |          |        |           |

TABLE IV HIGH TEMPERATURE HEAT-SOAK EFFECTS ON SUBSEQUENT DEFECT DENSITIES\*

15

<sup>\*</sup>Data in Appendix E-4 \*\*Control: Initial thin oxide omitted

The results obtained are generally superior to the best data previously obtained by HNO<sub>3</sub> treatment (Figure 3), with the exception of the first value of set C. In sets C, D, and E the controls (in which the introduction of a first thin oxide laver was omitted) consistently vielded lower defect densities, whereas the reverse is true for set F in which the heat-soak period was increased to 16 hrs. These results appear to indicate a substrate surface redistribution process at 1180 C which is hindered by the presence of a thin oxide layer unless sufficient time is allowed for the highly viscous accommodation by the oxide. In comparing the results of sets C and D the oxidative precleaning again is shown to be inferior to the HF lapping and appears to be sufficient reason for abandoning further work with the nitric acid pretreatment. Analysis of sets E and F shows a slight improvement from a prolonged heat-soak, set F being superior to all previous runs. Comparison of sets D and E indicate that a slow nitrogen flow rate results in fewer defects than the normal flow rates used throughout the bulk of these investigations. An unidentified component of the nitrogen source may contribute to this effect. The relatively high defect densities from the control runs of set F, where the heat-soak was relatively prolonged, further suggests this possibility. In conclusion, it appears that treatments tending to promote greater smoothness of the substrate surfaces, as well as prolonged periods of equilibration to enhance initial oxide uniformity, may have an important bearing on the reduction of oxide defects.

In continuing experiments all wafers were precleaned by HF wiping, as described previously, and all were exposed to a five-minute treatment with four percent dry  $O_2$  immediately prior to a 16-hour heat-soak in nitrogen. Process variables and resulting defect counts are summarized in Table V.

| HC <b>l</b> Pre-<br>treatment<br>(Min) | N <sub>2</sub> Heat-<br>Soak<br>(Hrs) | Normal<br>Oxidation<br>(Min) | Oxide<br>Thickness<br>(Ångstroms) | Defects<br>(cm <sup>-2</sup> ) |

|----------------------------------------|---------------------------------------|------------------------------|-----------------------------------|--------------------------------|

| None                                   | 16                                    | 10                           | 2600                              | 12, 3                          |

| None                                   | 16                                    | 40                           | 4500                              | 6.0                            |

| None                                   | 16                                    | 80                           | 6100                              | 3.7                            |

| 1                                      | 16                                    | 5                            | 1900                              | 15.8                           |

| 1                                      | 16                                    | 20                           | 3300                              | 5.7                            |

| 2                                      | 16                                    | 5                            | 2300                              | 6.4                            |

| 2                                      | 16                                    | 20                           | 3200                              | 4.0                            |

TABLE V

EFFECTS OF HC! PRETREATMENT AND HEAT-SOAK ON DEFECTS\*

\*See Appendix A-5

A log plot of the first three defect counts yields approximately 1 defect/cm<sup>2</sup> when extrapolated to 10,000 Å, which compares with results from Vendors B and C wafers grown to 10,000 Å (see below). The second set of data, which includes a oneminute HCl treatment prior to the dry O<sub>2</sub> preoxidation, when similarly plotted yields less than 0.1 defects/cm<sup>2</sup> at 10,000 Å. The effect of the HCl appears to be to cause a significantly higher defect decay rate with oxide thickness as a result of reducing initial wafer surface irregularities. Increasing the HCl treatment to two minutes produced a further reduction of defect densities as shown in Table V.

The results are clearly superior to those obtained with a shorter HC $\ell$  pretreatment. Extrapolation to 10,000 Å again yields a defect density of the order of 0.  $1/cm^2$ .

This HCl pretreatment, however, was distinctly less than optimum because it introduced clearly visible (at 100 X) etch pits in the wafers. Etch pit sizes lay in the micron and submicron range. A comparison of etch pit counts with defect counts revealed a distinct correlation as shown in Table VI.

The only anomalous results in this progression are the ones starred. This is the first known direct evidence that depressions in the silicon surface, in the micron and submicron range, give rise to subsequently grown oxide irregularities which are incapable of withstanding the compressive stress introduced on cooling from the oxidation temperature. It is well known that vitreous silica is remarkably resistant to compressive stress but yields readily to tension and shear. The abrupt changes in oxide curvature caused by the etch pits introduce tension and shear vectors as resultants of the existing compressive stress.

| ·                                       |                                    |

|-----------------------------------------|------------------------------------|

| HC <b>l</b><br>Etch Pits<br>(per wafer) | Ultimate<br>Defects<br>(per wafer) |

| 72                                      | 20                                 |

| 77                                      | 45*                                |

| 82                                      | 27                                 |

| 98                                      | 34                                 |

| 116                                     | 16*                                |

| 125                                     | 40                                 |

| 174                                     | 58                                 |

| 233                                     | 115                                |

TABLE VI

OXIDE DEFECTS AS A FUNCTION OF PREVIOUSLY INTRODUCED ETCH PITS

#### **Dielectric Defects - Vendor Survey**

Defect analyses of 10,000 Å oxides prepared by three manufacturers was performed for comparison with the Autonetics laboratory results obtained. The results obtained are summarized in Table VII.

The superiority of the Vendor A product is clearly evident with 80 percent of the wafers having no defects at all. A Vendor Representative indicated to Autonetics that its oxidations were preceded by an HC $\ell$  etch; no other vendor made this claim. In view of the results tabulated in the preceding section of this report it seems likely that neither Vendor B nor Vendor C employ a pre-etch with HC $\ell$ . The defect levels of the latter two manufacturers are characteristic of those obtained on this program prior to the use of an HC $\ell$  etch.

Also of interest is the variation represented by Vendor C's lot number 3, indicating a lot-to-lot control problem. This is common to the entire lot, with a standard deviation of  $\pm 1.64$  defects/cm<sup>2</sup> ( $\pm 46$  percent). NASA centers would be well advised to require a test wafer for defect analysis after the first oxidation prior to purchasing planar devices from a given lot. It also would seem prudent for manufacturers to adopt some embodiment of the electrophoretic decoration test (as described in Appendix A of this report) not only to inform themselves of lot-to-lot control problems but also of their standing with the oxide quality of other vendors.

| Company  | Number<br>of<br>Wafers | Average<br>Defects<br>(cm <sup>-2</sup> ) | Wafers<br>With Zero<br>Defects (%) | Maximum<br>Count<br>(wafer <sup>-1</sup> ) |

|----------|------------------------|-------------------------------------------|------------------------------------|--------------------------------------------|

| Vendor A |                        |                                           |                                    | ······································     |

| Lot 1    | 10                     | 0.040                                     | 80                                 | 1                                          |

| Lot 2    | 28                     | 0.057                                     | 79                                 | 2                                          |

| Vendor B |                        |                                           |                                    |                                            |

| Lot 1    | 10                     | 0.29                                      | 30                                 | 9                                          |

| Lot 2    | 10                     | 0.69                                      | 0                                  | 19                                         |

| Lot 3    | 10                     | 0.72                                      | 10                                 | 13                                         |

| Vendor C |                        |                                           |                                    |                                            |

| Lot 1    | 30                     | 0.73                                      | 3.3                                | 11                                         |

| Lot 2    | 10                     | 0.55                                      | 20                                 | 10                                         |

| Lot 3    | 10                     | 3.55                                      | 0                                  | 41                                         |

TABLE VIIDEFECT LEVELS IN 10,000Å OXIDES FROM VARIOUS SOURCES\*

\*See Appendix F for data

#### Dielectric Defects - Pilot Line Test

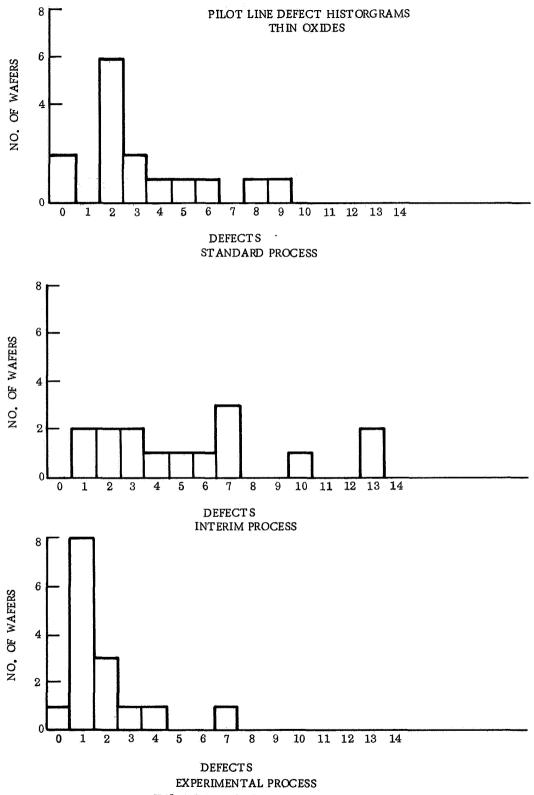

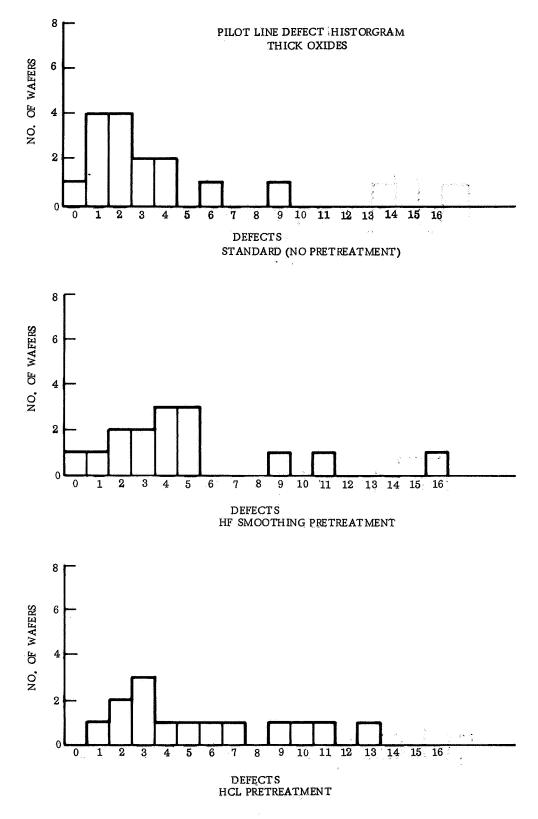

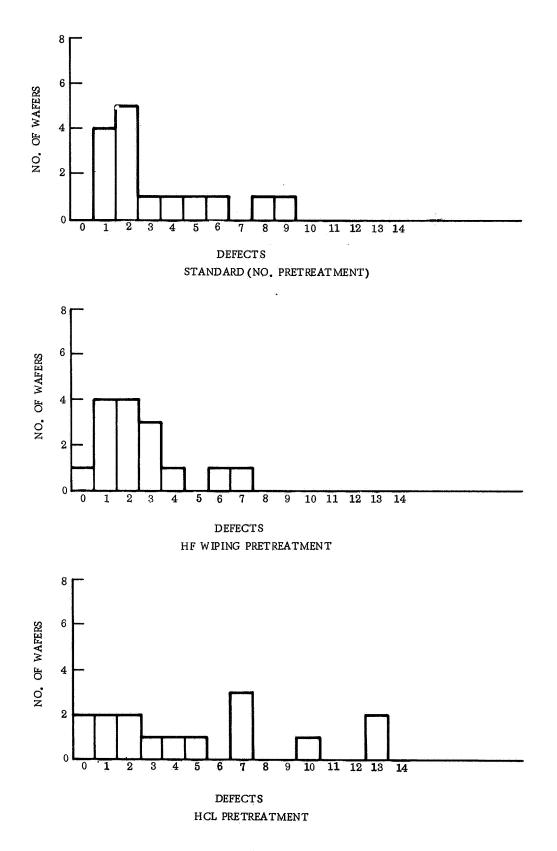

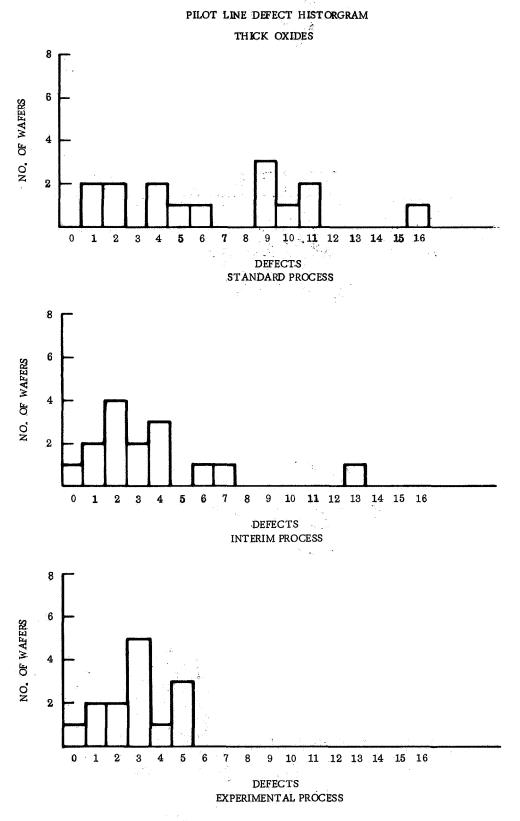

Standard Rel-chip wafers were fabricated on the Autonetics pilot line by three process modifications designated as "Standard," "Interim," and "Experimental." Each modification was represented by 18 wafers which additionally were divided into three pretreatment subgroups of six each comprising standard pretreatment, HF wiping, and HCl pre-etching. Final window opening and metallization was omitted in five out of each set of six wafers and were defect counted by electrophoretic decoration. The sixth wafer was carried through metallization and electrically tested for dielectric breakdown in the capacitor area which was 0.008 in. x 0.008 in. x 1400 Å thick. The wafers contained an average of 435 Rel-chip integrated circuits; all of the IC's on each of the five wafers of each group were defect counted. The results for each process modification and each wafer pretreatment are summarized in Table VIII.

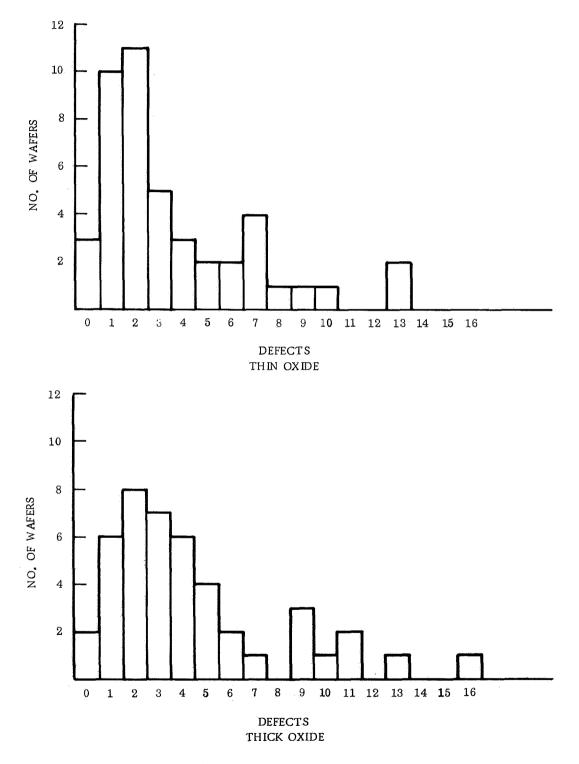

Histograms of the data are presented in Appendix G. The information summarized in the first histograms indicates a "tighter" distribution for the thin oxides of all wafers with a mode of 2 defects per wafer. The thick oxides show a greater spread on the average with a mode also at 2 defects per wafer. (The thick oxide area is of course much larger than the thin oxide layer.) Other histograms in Appendix G show the data for thin and thick oxides as a function of process and pretreatment. The thin oxide distribution by process show a considerable spread for the interim process and thus a possible out-of-control situation. There was also a considerable spread in all of the thick oxide data.

The data summary (average values) shown in Table VIII indicate no significant trends in thick or thin oxide defect density as a function of the variables examined. The additional pretreatments appear to have produced some improvement in the thin (1400 Å) oxide produced by the ''Standard'' process but this relationship was reversed on the Interim and Experimental process. Both of the pretreatments were accompanied by increased defects on the thick oxides. It appears that more data are needed in order to arrive at statistically significant conclusions. Other factors appeared to be present which confounded the data obtained. This is indicated in Figures 4 and 5 which show respectively a random and nonrandom distribution of defects on two wafers examined.

An attempt was made to compare these data with those previously obtained on this program for three vendor oxides. It was necessary to extrapolate the data since the pilot line oxides were 1400 and 14,000 Å while the vendor oxides were 10,000 Å. By use of the decay constants (slopes) for curves B or C in Figure 1 extrapolation would reveal that the pilot line thin oxides are comparable with Vendors B and C while Vendor A is an order of magnitude better. Also the pilot line oxides were subjected to several thermal excursions not represented in the sample growth of the vendor oxide.

The above results were substantiated by electrical tests on the metallized wafers. Among all capacitors tested not a single electrical breakdown was induced under an applied potential of 100 v. In the present case this amounts to a field of 0.07 v/Å which is about 70 percent of the breakdown strength of sound oxide and considerably higher than fields sustained in normal operation.

#### TABLE VIII VARIATION OF DEFECT DENSITIES WITH PROCESSING AND PRETREATMENTS\*

|                                                     | Pretreatment |                                                                                                                      |              |  |  |  |  |

|-----------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| Process                                             | Standard     | HF Wiping                                                                                                            | HCl Pre-etch |  |  |  |  |

| Standard                                            |              |                                                                                                                      | <u></u>      |  |  |  |  |

| Thick oxide** (cm <sup><math>-2</math></sup> )      | 1.1          | 2.9                                                                                                                  | 2.3          |  |  |  |  |

| Capacitor *** (cm <sup>-2</sup> )                   | 32.4         | 10.2                                                                                                                 | 13.1         |  |  |  |  |

| Oxide step (cm <sup>-1</sup> )                      | 0.10         | 0.09                                                                                                                 | 0.09         |  |  |  |  |

| Interim                                             |              |                                                                                                                      |              |  |  |  |  |

| Thick oxide (cm <sup><math>-2</math></sup> )        | 0.9          | 0.8                                                                                                                  | 1.7          |  |  |  |  |

| Capacitor ( $cm^{-2}$ )                             | 14.8         | 23.5                                                                                                                 | 52.5         |  |  |  |  |

| Oxide step (cm <sup>-1</sup> )                      | 0.06         | 0.15                                                                                                                 | 0.16         |  |  |  |  |

| Experimental                                        |              |                                                                                                                      |              |  |  |  |  |

| Thick oxide (cm <sup>-2</sup> )                     | 0.6          | 1.0                                                                                                                  | 1.1          |  |  |  |  |

| Capacitor ( $cm^{-2}$ )                             | 7.5          | 8,9                                                                                                                  | 14.2         |  |  |  |  |

| Oxide step (cm <sup>-1</sup> )                      | 0.02         | 0.02                                                                                                                 | 0.07         |  |  |  |  |

| *See data in Appendix G<br>**14,000 Å<br>***1,400 Å | L            |                                                                                                                      |              |  |  |  |  |

| Terms Used in Table                                 |              |                                                                                                                      |              |  |  |  |  |

| Standard Pretreatment                               | to initial   | Standard Pilot Line cleansing of wafers prior<br>to initial oxidation. (Solvent, HF "rinse" 10<br>percent dilution.) |              |  |  |  |  |

| HF Wiping Pretreatment                              |              | HF experimental technique. (HF swabbing in transverse directions prior to initial oxidation.)                        |              |  |  |  |  |

| HCl Pre-etch Pretreatmen                            | nt HClexpe   | HCl experimental technique. (Pre-clean                                                                               |              |  |  |  |  |

HCl experimental technique. (Pre-clean No. 1 followed by HCl etching of wafer at oxidation temperature followed by immediate initial oxidation in same furnace.)

Figure 4. Test Wafer Showing Random Distribution of Dielectric Defects

Figure 5. Test Wafer Showing Non-Random Distribution of Dielectric Defects

As observed in the past, a substantial proportion (greater than 50 percent) of the total defects were situated along oxide steps. The linear densities given in Table VII were derived only from the peripheries of the large capacitor regions. It was not determined whether these defects were actually on the step or possibly in a trough of extremely thin oxide believed to be at the base of the step. No vendor step data is currently available for comparison. This page intentionally left blank.

## **BIBLIOGRAPHY ON SILICON SURFACE PASSIVATION**

This program has been directed toward an understanding of the interrelationship of semiconductor device processing and the resultant reliability. Specifically, the role of surface passivation and related process variables has been studied.

In conjunction with the research carried out on this program, a continual literature review was made, with a goal of relating other findings to the results of this program. Also searched for were improved passivation techniques which might reduce or eliminate the problems defined for currently used  $Si-SiO_2$  systems. The following is a synopsis of some of the pertinent information which is applicable to the research performed. The information is presented in several related sections.

#### Preparation of Oxide Layers

A comprehensive report on the process parameters for oxidized silicon was prepared by the Research Triangle Corporation (Ref 1). A more detailed analysis of the kinetics of the growth process has been presented in several articles by Deal (Ref 2) and Burkhardt and Gregor (Ref 3). The parabolic growth rate constants as a function of various process variables was explored by Ainger (Ref 4). The oxidation kinetics of silicon were studied by Law (Ref 5) at temperatures from 1000 to 1300K and pressures from  $10^{-3}$  to  $5 \times 10^{-2}$  mm. This information confirmed the parabolic growth rate, with the rate constant being markedly pressure dependent.

It has been demonstrated that hydroxyl groups can be introduced into silica by high temperature exposure to water vapor (Ref 6), that oxides grown in steam or wet ambients contain measurable amounts of hydrogen (Ref 7, 8, 9), and that thermally grown oxides incorporate varying amounts of the substrate dopant into the oxide structure (Ref 10, 11). Investigators have shown that the growing oxide has an affinity for boron but rejects phosphorus and antimony (Ref 11).

Nossibian and Whiting (Ref 12) showed that particulate contaminations on the oxide surface act as loci for the formation of high concentration regions of  $P_2O_5$  during a deposition of phosphorus. In the subsequent diffusion, the phosphorus is considered to penetrate the oxide preferentially beneath these high concentration sources, doping the silicon substrate in localized regions under the oxide.

Several low temperature techniques have been proposed for forming silicon oxide films. These methods are of special interest in that they reduce the thermal stress problem possibilities.

Thin oxide films were formed by dilute HNO<sub>3</sub> and studied (Ref 13). The formation of SiO<sub>2</sub> films by the low temperature (750 C) decomposition of tetraethoxysilane in an evacuated system was studied (Ref 14). The performance of the system was investigated and the film characteristics evaluated. Most of the properties of the deposited oxides were similar to those of thermally grown oxides after a thermal treatment. Hennisch (Ref 15) devised a closed tube method for deposition of SiO<sub>2</sub> via decomposition of tetraethoxysilane.

The growth of  $SiO_2$  in a microwave discharge was investigated by Kraitchman (Ref 16). This technique provided rapidly oxidized silicon at temperatures estimated to be 500 C or lower.

Ing and Davern (Ref 17) described a process for the formation of silicon oxide thin films by the low temperature decomposition of tetraethoxysilane in an a-c glow discharge. It was shown that films produced in this manner can be used effectively as the dielectric in thin film capacitors. The resultant capacitors have low dielectric losses and are very stable under various life test conditions.

#### Other Passivation Techniques

Several other materials or combinations of materials have been investigated in an attempt to eliminate some of the objectionable problems detected for the Si-SiO<sub>2</sub> system.

Aboaf (Ref 18) experimented with amorphous aluminum oxide films deposited at 420 C by thermal decomposition of an aluminum alkoxide. The dielectric and moisture resistance properties were favorable when compared with conventional SiO<sub>2</sub>.

MOS transistors with aluminum oxide gate dielectric were fabricated and tested by Waxman and Zaininger (Ref 19). Their films are formed by anodizing aluminum in an oxygen plasma. The radiation resistance of these devices appeared excellent.

The most promising substitute and the one with extensive work involves various types of silicon nitride films. Typically silicon nitride films have been deposited on silicon by reacting SiCl<sub>4</sub> and NH<sub>3</sub> at 550 - 1250 C (Ref 20). One important finding is that the deposited films are extremely effective diffusion masks for sodium.

Amorphous silicon nitride films have been deposited in a gas flow system by the ammonolysis of silicon tetrachloride and the nitridation of silane with ammonia (Ref 21, 22). The substrate temperature during the deposition process appeared to have the most significant influence on the film properties. It has been shown that such amorphous nitride films can be converted to anodic SiO<sub>2</sub> (Ref 23).

Amorphous films of silicon nitride-silicon dioxide mixtures were deposited and evaluated by Chu and coworkers at Westinghouse (Ref 24). The technique utilized was the pyrolysis of silane in ammonia-oxygen mixtures in a gas flow system. Heat treatment of silicon nitride films (Ref 25) was found to result in severe structural changes resulting in fractured layers.

#### Passivation Layer Mechanical Aspects

Mechanical rupturing of the oxide film has been related in this report and by others (Ref 26) to the difference in coefficient of thermal expansion between silicon and the passivation layers utilized. The evidence as reported (Ref 27, 28) indicates that dielectric failures are a result primarily of actual physical openings in the insulating layer rather than regions of enhanced conductivity in uniformly thick oxide.

The silicon-silicon oxide stress has been experimentally measured (Ref 27, 29) and was found to be in the range from 30,000 to 60,000 psi. The expansion characteristics of silicon apparently exhibit unusual behavior (Ref 30) above ~ 1000 C.

The effect of structural defects such as hydroxl groups and network forming or other modifications is to alter the silica structure producing a less rigid network. This alteration is reflected in changed physical and electrical properties. For example, the introduction of either boron (Ref 31) or hydroxl (Ref 32) into the SiO<sub>2</sub> structure increases the thermal expansion coefficient and decreases the viscosity of the modified material relative to the intrinsic oxide. Strains at the Si-SiO<sub>2</sub> interface were measured by Joecodine and Schlegel (Ref 33) and Whelan (Ref 34). Besser and Eisenberg (Ref 35) and Lopez (Ref 36) studied the factors that affect the density of defects in SiO<sub>2</sub> films. Lane (Ref 37) has recently correlated stress in the Si-SiO<sub>2</sub> interface to surface state density.

Lopez (Ref 38) found that defect density for a particular thickness was greater for the thinned oxide than for the unaltered oxide.

It has been shown that mechanical polishing results in a certain amount of structural damage to the silicon surface and may leave particles of the polishing compound embedded in the polished surface. This was recently confirmed (Ref 39) by electron microprobe analysis performed by Cocca and Carroll at NASA-ERC. This may be the origin of the somewhat higher defect density in the oxide grown on such wafers.

Fisher and Amick (Ref 40) detected defect structures on silicon surfaces after oxidation which were partially due to stresses induced by the oxidation processes. Slip in Si crystals has also been suggested. Recently Drum and Rand reported (Ref 41) a method of reducing stress by using a silicon oxide-silicon nitride combination. Stresses of the order of  $10^7$  dynes/cm<sup>2</sup> were obtained which is 2 to 3 orders of magnitude lower than usually obtained.

Techniques utilized by other investigators were evaluated for use on this program for the detection of dielectric defects. Techniques such as a high temperature HCletch (Ref 42) or Cl etching around 900 C (Ref 43, 44) were found to be not conveniently applicable. The results obtained earlier on this contract have been reported (Ref 27) and two techniques which were found to be suitable, electrophoretic decoration and electrochemical autograph, were utilized in this study for the observation of oxide defects.

#### Passivation Layer Properties and Evaluation Techniques

Techniques for the physical and chemical evaluation of silicon oxide films formed by a wide variety of techniques have been developed (Ref 45). Silicon oxide films were characterized on the basis of refractive index, etch rate, infrared spectra, stoichiometry, passivation efficiency and thermal densification. It was found that films formed by low temperature techniques generally had properties inferior to oxides formed by conventional high temperature techniques.

Worthing (Ref 46) and Klein (Ref 47) made evaluations of dielectric breakdown in thin oxide films. At positive silicon potentials, Worthing found that dielectric breakdown occurred abruptly with no detectable conduction at lower voltages. At negative silicon potentials, conduction in the nanoamp range and time dependence of dielectric breakdown was detected. Klein confirmed that breakdown starts on electric field induced thermal instability at flaws in the dielectric resulting in a hole through the oxide.

The properties of silicon nitride-silicon oxide mixtures were obtained by Chu, Szedon, and Lee (Ref 24).

The electrical properties of both silicon nitride and silicon oxide were investigated by Deal, Fleming and Castro (Ref 48). As contrasted to the thermal oxides, the silicon nitride films are characterized by polarization and room temperature trapping instabilities, relatively high conductance, and high surface state charge densities. The vapor-deposited oxides were found to resemble the nitrides in those properties which were associated with the silicon-dielectric interface, but the bulk properties where more like those of thermal oxides. The properties of a  $SI_xO_yN_z$  film on Si was investigated by Brown and others at G. E. Research, Schenectady (Ref 49). These films were formed by the pyrolysis of various mixtures of SiH<sub>4</sub>, NH<sub>3</sub>, and NO.

Several investigators have utilized the MOS test structure as a means for electrical evaluation of silicon oxide films. Typical reviews by Fairchild personnel describe impurity distributions of oxidized silicon and ion migration kinetics (Ref 50, 51).

A method of doping the oxide film with (DEP) diethylphosphate-nitrate-tetrahydrofuryl alcohol alcohol was studied for use in device diffusion of phosphorus (Ref 52). The fabrication of simple device structures by controlled out-diffusion of phosphorous from the oxide was evaluated.

#### References

- 1. R.P. Donavon, "Oxidation," Integrated Silicon Device Technology Ser. Vol. 7, Research Triangle Inst. Durham, N.C., Report No. ASD-TDR-63-316, DDC-AD-618-704, 1965.

- B. E. Deal, "The Oxidation of Silicon in Dry Oxygen, Wet Oxygen, and Steam," J. Electrochem. Soc, Vol. 110, 1963, pp 527-533.

- 3. P.J. Burkhardt and L.V. Gregor, "Kinetics of the Thermal Oxidation of Silicon in Dry Oxygen," Trans. Met. Soc, AIME, Vol. 236, 1966, pp 299-305.

- 4. F.W. Ainger, "The Formation and Devitrification of Oxides of Silicon," Journal of Materials Science 1 (1966).

- 5. J.T. Law. "The High Temperature Oxidation of Silicon, "Journal of Physical Chemistry, Vol. (61).

- 6. R.W. Lee, Physics and Chemistry of Glasses, 5, 35 (1964).

- 7. J.E. Meinhard, Electrochemical Society Spring Meeting, 1966, Cleveland, Ohio, Recent News Paper No. 19.

- 8. T.E. Burgess and F.M. Fowkes, Extended Abstracts of the Electronics Division of the Electrochemical Society <u>15</u>, No. 1, 110 (1966).

- 9. P.J. Burkhardt, Electrochemical Society Spring Meeting, 1966, Clevelend, Ohio, Recent News Paper No. 18.

- 10. M. M. Atalla and E. Tannebaum, Bell Systems Techn. J. 39, 933 (1960).

- 11. A.S. Grove, O. Leistiko, Jr., and C.T. Sak, J. Appl. Phys. 35, 2695 (1964).

- 12. A.G. Nossibian and G. Whiting, Solid State Electronics, 7, (1964).

- W. B. Glendinning, S. Marshall, A. Mark, "Thin Films Grown on Silicon Surfaces by Excess Nitric Acid Process," J. Electrochem. Soc., 112, No. 12, (1965).

- 14. J. Orashnik and J. Kraitchman, "Pyrolytic Deposition of Silicon Dioxide in an Evacuated System," J. Electrochem. Soc. Vol 115, No. 6 (1968).

- G.W. Hennisch, "Closed Tube Apparatus for the Deposition of Silicon Oxide," J. Electrochem. Soc., Vol. 114, No. 6, (1967).

- 16. J. Kraitchman, J. Appl. Physics, V. 38 (1967).

- 17. S.W. Ing, Jr. and W. Davern, "Glow Discharge Formation of Silicon Oxide and the Deposition of Silicon Oxide Thin Film Capacitors by Glow Discharge Techniques, "J. Electrochem. Soc., V. 1112, (1965).

- J.A. Aboaf, 'Deposition and Properties of Aluminum Oxide Obtained by Pyrolytic Decomposition of an Aluminum Alkoxide, "J. Electrochem. Soc., Vol. 114 (1967).

- 19. A. Waxman and K.H. Zaininger, "Al<sub>2</sub>O<sub>3</sub> Silicon Insulated Gate Field Effect Transistors," Applied Physics Letters, Vol. 12, No. 3 (1968).

- M.J. Grieco, F.L. Worthing, and B. Schwartz, "Silicon Nitride Thin Films from SiCl<sub>4</sub> Plus NH<sub>3</sub>; Preparation and Properties, "J. Electrochem. Soc., Vol. 115 (1968).

- T.L. Chu, C.H. Lee, and G.A. Gruber, "The Preparation and Properties of Amorphous Silicon Nitride Films," J. Electrochem. Soc., Vol. 114, No. 7, (1967).

- 22. T. Sugano, K. Hirai, K. Kuroiwa, and K. Hoh, 'Vapor Deposition of Silicon Nitride Film on Silicon and Properties of MNS Diodes."

- 23. P.F. Schmidt and D.R. Wonsidler, J. Electrochem. Soc., Vol. 114, No. 6 (1967).

- 24. T. L. Chu, J. R. Zedon, and C. H. Lee, "Films of Silicon Nitride-Silicon Dioxide Mixtures," J. Electrochem. Soc., Vol. 115, No. 3 (1968).

- 25. D.J.D. Thomas, "The Effect of Heat Treatment on Silicon Nitride Layers on Silicon," Physica Status Solidi, Vol. 20, No. 1-2 (1967).

- 26. A.N. Saxena and O. Tkal, J. Electrochem. Soc., Vol. 115, No. 2 (1968).

- 27. P.J. Besser and J.E. Meinhard, Proceedings of Symposium on Manufacturing In-Process Control and Measuring Techniques for Semiconductors, Phoenix, Arizona, March 1966, Vol. II.

- 28. R.L. Nolder, "Defects in Silicon Oxide Films on Integrated Circuits," 1966 Fall Meeting of Electrochem Soc., Philadelphia, Pa., Abstract 179.

- 29. S.S. Baird, Annals New York Academy of Sciences, 101 (1963).

- 30. H.A. Robinson, Jr., Phys, Chem. Solids 26 (1965).

- 31. Corning Glass Works, "Properties of Selected Commercial Glasses," pp 8-83, Corning, New York (1961).

- 32. G. Hetherington and K. H. Jack, Phys, Chem. Glasses, 5, 35 (1964).

- 33. R.S. Joccodine and W.A. Schlegel, "Measurement of Strains at Si-SiO<sub>2</sub> Interface," J. Appl. Phys., Vol. 37 (1966).

- 34. M.U. Whelan, A.H. Goemans, L.M.C. Goossens, "Residual Stress at an Oxide-Silicon Interface," Appl. Phys. Lett., Vol. 10 (1967).

- 35. P.J. Besser and P.H. Eisenberg, 'Factors Influencing Dielectric Defects in Silicon Oxide Layers," 1966 Fall Meeting of Electrochem. Soc., Philadelphia, Pa., Abstract 178.

- A.D. Lopez, "Fast Etching Imperfections in Silicon Dioxide Films," J. Electrochem Soc., Vol. 113 (1966).

- 37. C.H. Lane, 'Stress at the Si-SiO<sub>2</sub> Interface and its Relationship to Interface States, "IEEE Transactions on Electron Devices, Vol. ED-15, No. 12 (1968).

- 38. A.D. Lopez, J. Electrochem. Soc., 113 (1966).

- 39. F.J. Cocca and K.G. Carroll, "Electron Microprobe Analysis of Impurity Heterogeneities in Thermally Grown Silicon Oxide," IEEE Transactions on Electron Devices, Vol. ED-15, No. 12 (1968).

- 40. A.W. Fisher and J.A. Amick, 'Defect Structure on Silicon Surfaces After Thermal Oxidation, "J. Electrochem. Soc., Vol. 113, No. 10 (1966).

- 41. C.W. Drum and M.H. Rand, "A Low-Stress Insulating Film on Silicon by Chemical Vapor Deposition," J. of Applied Physics, Vol. 39, No. 9 (1968).

- 42. "Manufacturing In-Process Control and Measuring Techniques for Integral Electronics, "No. 4, IR-8-140(IV), Motorola, Inc., Jan. 1965 <u>1</u> 97.

- 43. E.F. Duffek, E.A. Benjamini, and C. Mylroie, Electrochem Tech. <u>3</u>, 75 (1965).

- 44. S.W. Ing, R.E. Morrison, and J.E. Sandor, J. Electrochem, Soc., <u>109</u>, 222 (1962).

- 45. W.A. Pliskin and H.S. Lehman, "Structural Evaluation of Silicon Oxide Films," J. Electrochem. Soc., Vol. 112, No. 10 (1965).

- 46. F.L. Worthing, "D.-C. Dielectric Breakdown of Amorphous Silicon Dioxide Films at Room Temperature, "J. Electrochem. Soc., Vol. 115, No. 1, (1968).

- 47. N. Klein, "The Mechanism of Self-Healing Electrical Breakdown in MOS Structures," IEEE Transactions on Electron Devices, Vol. ED-13, No. 11 (1966).

- 48. B. E. Deal, P. J. Fleming, and P. L. Castro, "Electrical Properties of Vapor-Deposited Silicon Nitride and Silicon Oxide Films on Silicon," J. Electrochem. Soc., Vol. 115, No. 3 (1968).