#### **General Disclaimer**

### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

Final Report

For

Task 6 - Development of MNOS Technology

NAS 9-6636

WEC GO HS - 51431

March 20, 1970

### Prepared by

WESTINGHOUSE DEFENSE AND SPACE CENTER Systems Development Division Baltimore, Maryland 21203

For

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

Manned Spacecraft Center

Houston, Texas 77058

# Aerospace Division—

### Table of Contents

|                                                                  | Page   |

|------------------------------------------------------------------|--------|

| 1.0 Introduction and Summary                                     | 1-1    |

| 2.0 Technical Discussion                                         | 2-1    |

| 2.1 Theory and Physical Models                                   | 2-1    |

| 2.1.1 Charge Storage in MNOS Devices                             | 2-1    |

| 2.1.2 Limiting Cases                                             | 2-1    |

| 2.1.3 Basic Model and Theory                                     | 2-4    |

| 2.1.4 Charging Time Analysis                                     | 2-8    |

| 2.2 Experiments and Results                                      | 2-10   |

| 2.2.1 Silicon Oxidation Techniques                               | 2-10   |

| 2.2.2 Characterization of MNOS Devices                           | 2-11   |

| 2.2.3 Charging and Retention Time Response                       | 2-19   |

| 2.2.4 Nitride-Oxide Passivation                                  | 2-28   |

| 2.2.5 Processing Manual for Pyrolytic Silicon Nitride Deposition | n 2-31 |

| 2.3 MNOS Transistor Memory System                                | 2-31   |

| 3.0 Conclusions                                                  | 3-1    |

Aerospace Division—

| Figure No. | <u>Caption</u>                                                                                                                                                      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.         | Schematic Band Diagram for Tunneling Trapping in MNOS Structures.                                                                                                   |

| 2.         | Circuit Model for Transient Analysis                                                                                                                                |

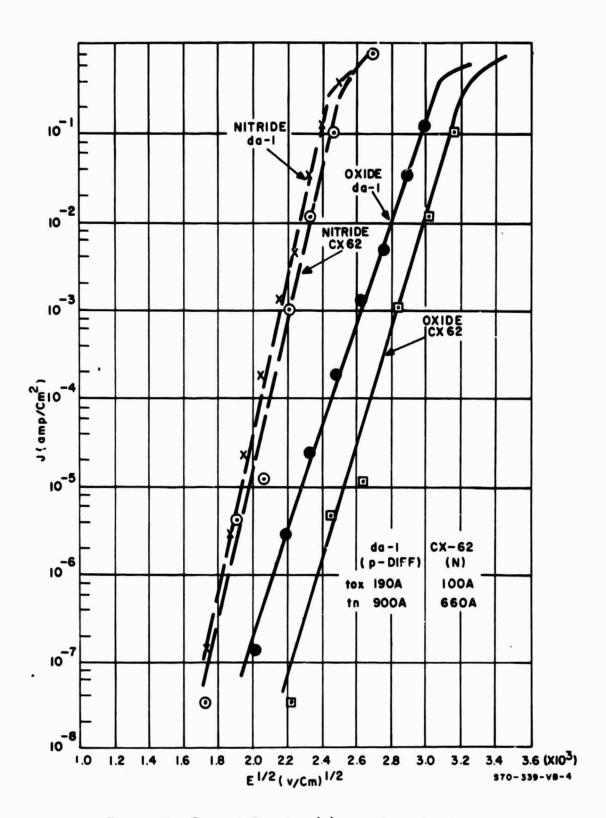

| 3.         | Insulator Current Density (J) vs. Electric Field ( $\mathbb{E}^{\frac{1}{2}}$ ) for Separate Oxide and Nitride Films                                                |

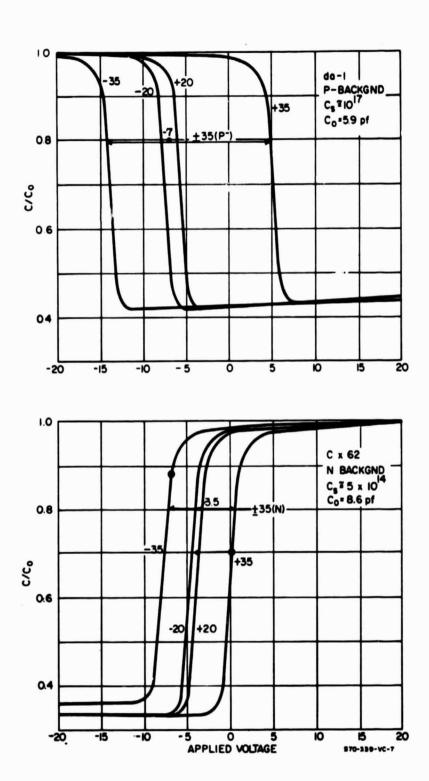

| 4.         | C-V Curves for Thermally Oxidized N and P Type Wafers                                                                                                               |

| 5.         | Current Density (J) vs. Electric Field ( $\mathbb{E}^{\frac{1}{2}}$ ) for MNOS Capacitors                                                                           |

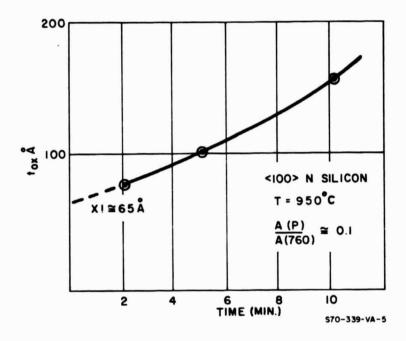

| 6.         | Thin Thermal Oxide Thickness vs. Oxidation Time (low partial $0_2$ pressure)                                                                                        |

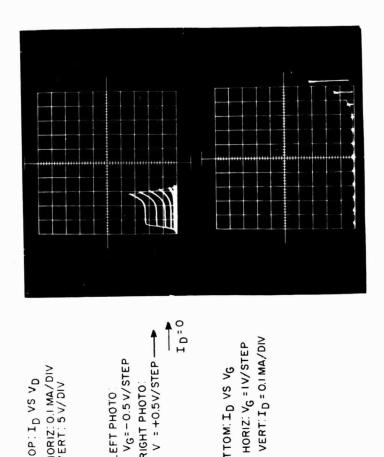

| 7.         | MNOS Transistor Drain Current vs. Drain Voltage and Gate Voltage Showing Threshold Voltage Shift                                                                    |

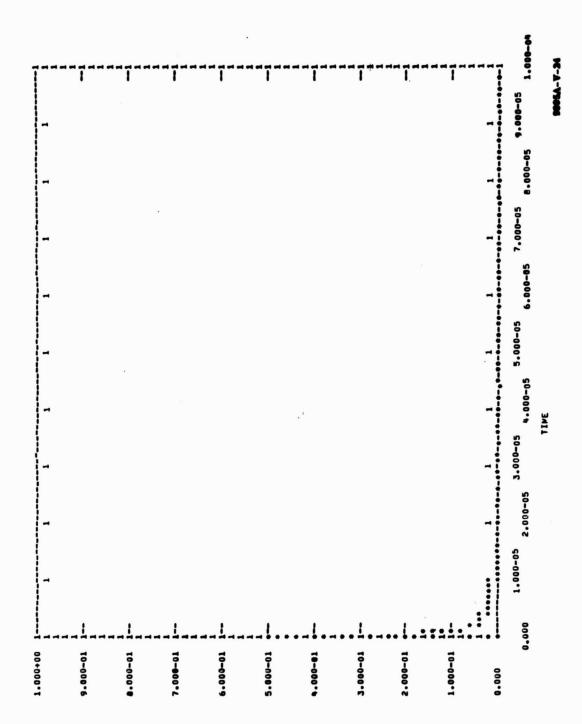

| 8.         | Computer Print Out of $J_G$ vs t                                                                                                                                    |

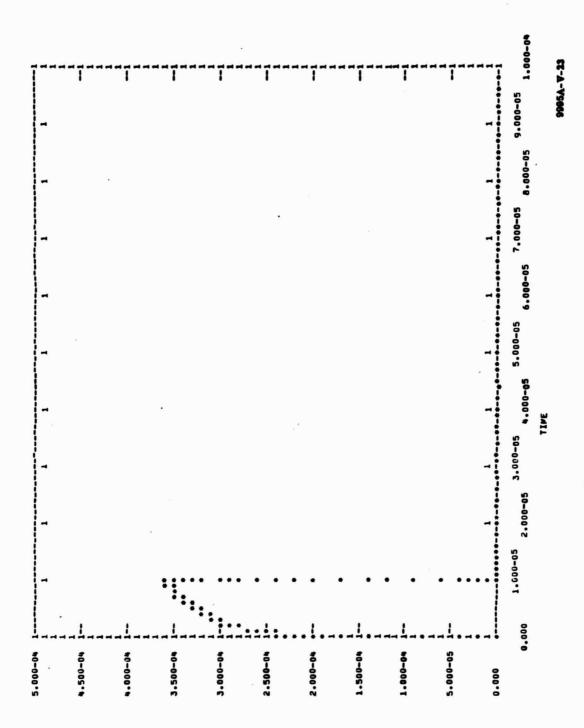

| 9.         | Computer Print Out of $J_{\mathrm{N}}$ vs t                                                                                                                         |

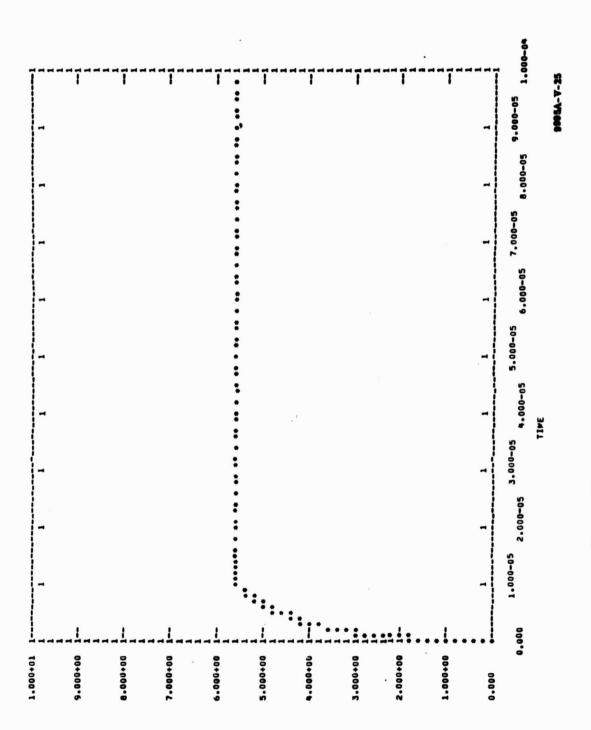

| 10.        | Computer Print Out of VFB vs t                                                                                                                                      |

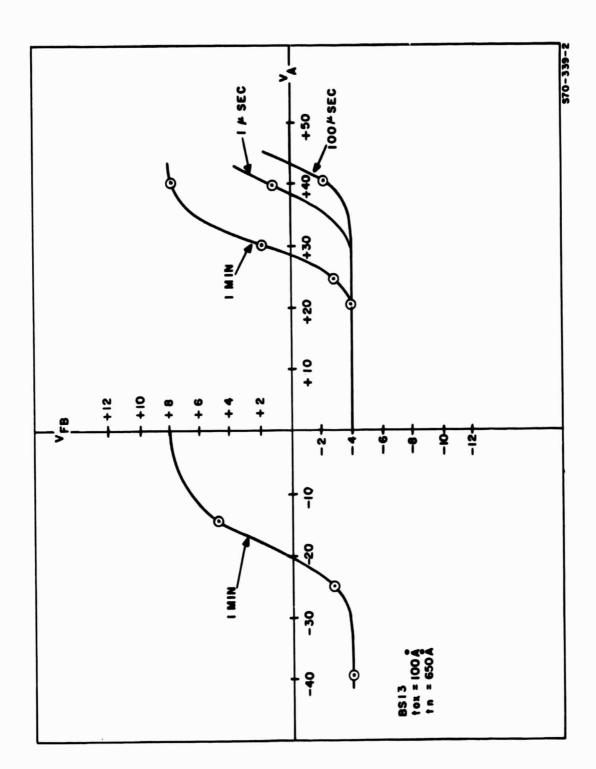

| 11.        | Flatband Voltage vs. Applied Voltage for Different Times                                                                                                            |

| 12.        | Retention of Charge                                                                                                                                                 |

| 13.        | C-V Curve Showing N Channel Transistor Flatband Voltage<br>Shift for 100 Nanosec Pulses                                                                             |

| 14.        | MNOS Transistor Curves for Temperature Bias Stress ( $V_A = \pm 20v$ and $E_N \simeq \pm 0.8 \times 10^6 \text{ v/cm}$ , EG $\simeq 1.3 \times 10^6 \text{ v/cm}$ ) |

| 15.        | Gate to Source Polarization (Channel Shielding) Modes of Operation                                                                                                  |

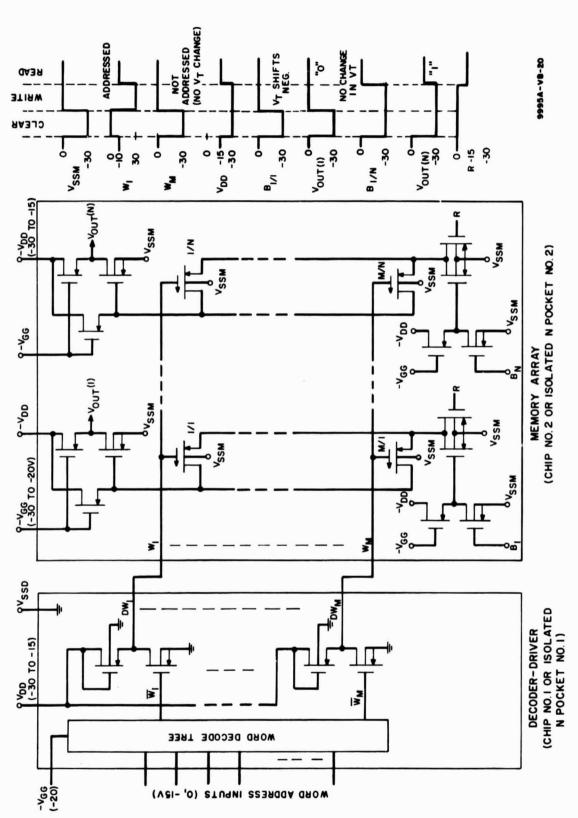

| 16.        | Array Schematic Diagram and Waveforms                                                                                                                               |

#### 1.0 Introduction and Summary

The objective of this task was to develop pyrolytic silicon nitrideon-silicon dioxide technology and to correlate the deposition parameters with physical and electrical characteristics of metal-nitride-oxide-semiconductor (MNOS) structures (amplifying and memory).

The theory and physical models of charge storage in MNOS structures is described in terms of the Fowler-Nordheim tunneling currents, Poole-Frenkel field enhanced thermal currents, ohmic currents and ionic currents. Two limiting cases based on the presence or absence of deep traps at the nitride-oxide interface are shown to have significant effects on the magnitude of the flatband shift and charge retention.

The experiments are all limited to thermally grown silicon dioxide in oxygen with temperature and partial pressures as variables. It has been shown that on  $\langle 100 \rangle$  silicon that the data extrapolates to an initial oxide thickness  $X_i$  of 65 Å. The most significant experiments showed that there are large differences in both oxidation rate and conductivity caused by the presence of diffused boron regions. The conclusion is that then thermal oxides should not be used on p channel MNOS transistors because of the anomolous behavior produced.

From the transient analysis and computer aided calculations it has been shown that the charging time and retention is a predictable and reproducible phenomena. Flatband shifts of about 8 volts for ±55 volts,10 microsec pulses have been achieved on n channel transistors and correlated with the theory. Retention decay rates of 0.3 to 0.5 v/decade have been measured which indicate that the retention is poorer than for other oxide types. To show that much faster charging times may be achieved, thin oxide - thin nitride n channel structures,

Aerospace Division—

were built that exhibited a 2 volt shift with  $\pm$  20 volt, 100 nanosec pulses.

From a consideration of the optimum conditions for nitride-oxide passivated structures it has been determined that thin oxides with thicker nitrides provide maximum transconductance and minimum flatband voltage shifts if precautions are taken to limit the applied fields to less than  $2 \times 10^{6}$ v/cm. Other more conservative combinations are possible that permit larger fields to be applied.

The use of MNOS transistors in memory systems is described. A four bit breadboard was delivered to demonstrate the memory operation.

- Aerospace Division-

#### 2.0 TECHNICAL DISCUSSION

### 2.1 Theory and Physical Models

#### 2.1.1 Charge Storage in MNOS Devices

The storage of charge within Metal-Nitride-Oxide-Semiconductor (MNOS) structures is dependent on the difference in current density of the two insulators. The oxide current density has been shown to be mainly governed by tunneling (Fowler-Nordheim effect)<sup>1,2</sup> at the silicon-oxide or nitride-oxide interface while the nitride current density has been shown to be mainly governed by field enhanced thermal exitation of charge trapped within the bulk of the material.<sup>3</sup> (Poole-Frenkel effect)

### 2.1.2 Limiting Cases

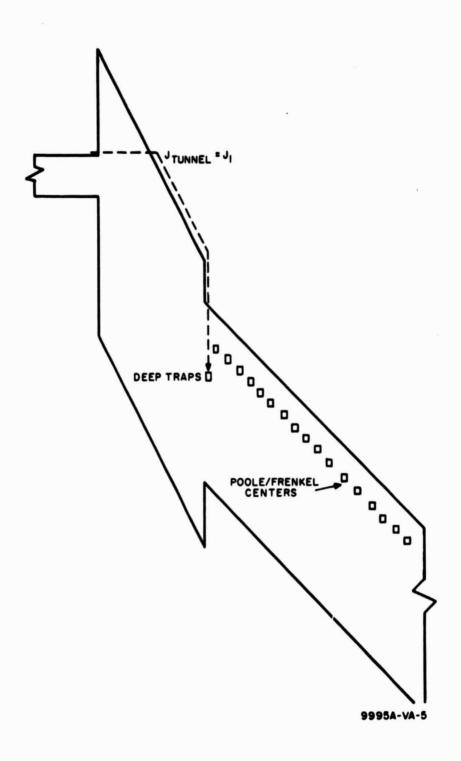

Two limiting-case physical models have been presented in the literature to explain the observed features of MNOS charge storage memory devices. In the first<sup>4,5</sup>, the current through the insulators is affected by deep traps located near the nitride-oxide interface as shown by the schematic band diagram shown in figure 1. In the second<sup>6,7</sup>, the deep traps are assumed to be negligable in density such that they have little affect on the insulator currents.

To illustrate these differences several simplified extreme cases are listed in Table 1 for applied electric fields less than the point at which the flatband voltage saturates.

Figure 1. Schematic Band Diagram for Tunneling Trapping in MNOS Structures.

- Aerospace Division-

Table 1

| Dominant<br>Current                | Deep Trap<br>Assumption | J Sensitivity<br>to Field Direction | Direction of $\Delta V_{FB}/E_A$ | Relative Shift $\Delta V_{FB} \; (E_A)$    |

|------------------------------------|-------------------------|-------------------------------------|----------------------------------|--------------------------------------------|

| 1) J <sub>N</sub> > J <sub>G</sub> | no                      | $J_{N}(+) \simeq J_{N}(-)$          | -                                | $\Delta V_{FB}(+) \simeq \Delta V_{FB}(-)$ |

| 2) $J_G > J_N$                     | no                      | $J_G(+) \simeq J_G(-)$              | +                                | $\Delta V_{FB}(+) \simeq \Delta V_{FB}(-)$ |

| 3) $J_N > J_G$                     | yes                     | $J_{N}(+) < J_{N}(-)$               | -                                | $\Delta V_{FB}(+) < \Delta V_{FB}(-)$      |

| 4) $J_G > J_N$                     | yes                     | $J_{G}(+) > J_{G}(-)$               | +                                | $\Delta V_{FB}(+) > \Delta V_{FB}(-)$      |

In case 1, the nitride current density  $J_N$  is assumed to be much greater than the oxide current density  $J_G$ , and that no deep traps at the nitride-oxide interface are present. The nitride current density for a given electric field is not very different for positive and negative applied electric fields. Note that for a positive applied field, the flatband voltage shift is negative. The shift from the flatband condition is about equal for positive and negative fields. The charge retention is determined only from the bulk nitride current term for the given field conditions.

In the fourth case, it is assumed that the oxide current is much greater than the nitride current and that deep traps are present at the oxide-nitride interface. By assumption, all the charge tunneled from the silicon into the oxide conduction band under positive bias is trapped in relatively deep centers. Because of the energy level of the deep traps the oxide current density for negative oxide field is much less than for a positive oxide field. The direction of flatband shift is positive with an applied positive field. Also the flatband shift for positive applied fields is larger than for negative applied fields because of the polarity sensitivity of the current term. The

- Aerospace Division-

retention of charge stored for this case can be far greater than for a structure such as example 1 if the traps are sufficiently deep to have negligable low rates of emission into either the nitride Poole-Frenkel centers or the oxide conduction band.

### 2.1.3 Basic Model and Theory

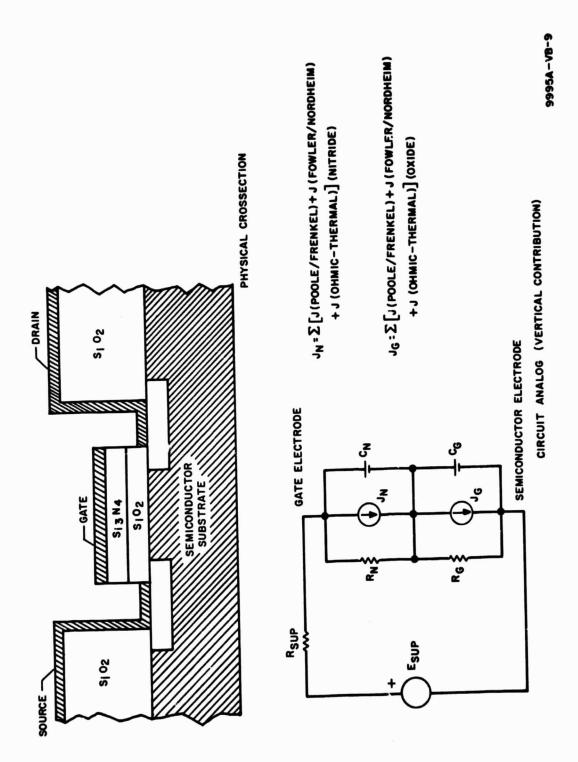

A simplified schematic representing the basic structure of the analytical model used to study the MNOST characteristics is shown in figure 2 together with a physical cross-section of a typical MNOST included for reference. This model is used to analyze the vertical components of the electrical phenomena taking place in the MNOST. Therefore, fields and currents that appertain to the structural sequence proceeding from the gate metal electrode, through the nitride. through the oxide, and to the semiconductor substrate electrode, are analyzed while the activity proceeding from the source to drain terminals is not treated explicitly, but is related to the analysis through the treatment of the flatband voltage. The model is established on a per unit area basis in order to lend flexibility in its utilization and in the interpretation and correlation of the results. It consists in the assignment of a capacitance per unit area  $(C_M)$ to the nitride layer corresponding to determinations made as to the relative dielectric constant  $(\epsilon_N)$  of this material and to the thickness  $(X_N)$  of this material & a capacitance per unit area (CG) to the oxide layer and its corresponding dielectric constant ( $\epsilon_G$ ) and thickness ( $X_G$ ). A voltage controlled conductance for high-field conditions is represented by the current generator  $(J_N)$ ; and a low-field conductance represented by the resistor  $(R_N)$ . Similar circuit elements are also assigned to the portion of the model representing the oxide layer. The model is completed by the inclusion of a voltage generator

Figure 2. Circuit Model for Transient Analysis

$(V_{\sup} = V_A)$  which provides the applied voltage to the metal electrode and a resistor  $(R_{\sup})$  to represent the output impedance of this driver. The value of this resistor  $(R_{\sup})$  is adjusted so as to obtain a time constant of approximately 10 nsec for the pulse driver for the computer aided transient analysis. The capacitive elements  $(C_N \text{ and } C_G)$  in the model provide for the storage of electrical energy within their respective layers of material and, furthermore, specifically serve to establish the presence of charge at their interface by considering the discontinuity in the dielectric displacement vectors. The current generators  $(J_N \text{ and } J_G)$  are multi-functional conductance elements which serve to characterize the field dependent conductivities of their respective layers at high values of electric field intensity. Conduction mechanisms specifically considered in the analysis include:

a) Field enhanced thermal excitation with trapping centers (Poole-Frenkel effect)

$$J = C_1 \times \exp \left(-\frac{q}{kT}\right) \left[\phi_{PF} - \left(q \times \pi_{e_0} \varepsilon\right)^{\frac{1}{2}}\right]$$

b) Charge carrier tunneling (Fowler-Nordheim effect)

$$J = C_2 E^2 \exp (-E_2/E)$$

c) Thermally excited charge carrier conduction (ohmic effect)

$$J = C_3 E \exp (-q \phi_3 kT)$$

d) Thermally excited ionic conduction

$$J = (C_{\perp} E/T) \exp (-q \phi_{\perp} kT)$$

The theory of the MNOS charge storage and retention is based on the integrity of the summation of electric potential, the charge/dielectric displacement continuity and the conduction current continuity. These are expressed as:

$$X_G E_G + X_N E_N = V_A$$

(Electric potential summation) (2-1)

$$\epsilon_{o}(\epsilon_{G} E_{G} - \epsilon_{N} E_{N}) = Q$$

(charge/dielectric displacement continuity) (2-2)

$$Q = \int_{0}^{t} (J_{N} - J_{G}) dt \qquad (current continuity) \qquad (2-3)$$

Equations 2-1 and 2-2 may be solved for the electric field intensity pertaining to each material layer to obtain

$$E_{G} = \frac{\epsilon N}{\alpha} V_{A} + \frac{X_{N}}{\epsilon_{O} \alpha} Q_{I}$$

(oxide field intensity) (2-4)

$$E_{N} = \frac{\epsilon_{G}}{\alpha} V_{A} - \frac{X_{G}}{\epsilon_{O} \alpha} Q_{I}$$

(nitride field intensity) (2-5)

where

$$\alpha = (\epsilon_{C} X_{N} + \epsilon_{N} X_{C}). \tag{2-6}$$

Since the flatband condition ( $E_{\rm si}=0$ ) is achieved in the semiconductor when the oxide field is zero, the flatband voltage  $V_{\rm FB}$  may be written in terms of the effective sheet of charge per unit area stored at the oxide-nitride interface  $Q_{\rm I}$  from equation 2-4 as

$$V_{A} = V_{FB} = -\frac{x_{N}}{c_{O}} Q_{I}$$

$$= -\frac{Q_{I}}{c_{N}} . \qquad (2-7)$$

Where a net effective surface state charge  $(Q_{SS})$  exists at the siliconsilicon dioxide interface

$$\epsilon_{o} \epsilon_{G} E_{G} = \epsilon_{o} \epsilon_{si} E_{si} - Q_{ss}.$$

(2-8)

Then for  $E_{si}=0$ ,  $V_{FB}=V_A$  and  $E_G=\frac{Q_{ss}}{\varepsilon_0\varepsilon_G}$  from equation (2-4) flatband voltage is

$$V_{FB} = - \begin{bmatrix} X_{N} & Q_{I} + \frac{\alpha}{\varepsilon_{O} \varepsilon_{N} \varepsilon_{G}} & Q_{SS} \end{bmatrix}$$

$$= - \begin{bmatrix} Q_{I} & Q_{SS} & Q_{SS} \\ \hline C_{N} & C_{T} \end{bmatrix}$$

(2-9)

where  $C_{\mathrm{T}}$  is the total effective series capacitance per unit area of the oxide and nitride layers.

### 2.1.4 Charging Time Analysis

Solutions for the charging time for the cases where the nitride current is dominant have been derived from the relationship

$$t_c = c_N \int_0^{V_{FB}} \frac{1}{J_N - J_G} dV_{FB}$$

(2-10)

For the nitride current dominant 8

$$J_{N} - J_{G} \simeq J_{N} = J_{O} \exp G E_{N}^{\frac{1}{2}}$$

(2-11)

and

For the oxide current dominant where tunnelling is the principal mechanism

$$J_{N} - J_{G} \simeq -J_{G} = -C_{3} E_{G}^{2} \exp \frac{-C_{L}}{|E_{G}|}$$

(2-13)

--- Aerospace Division-

The charging time then for this case is

$$t_{c} = \frac{\beta_{2}}{\gamma_{2}} \left[ \exp \left( \frac{\gamma_{2}}{V_{A} - V_{FB}} \right) - \exp \left( \frac{\gamma_{2}}{V_{A}} \right) \right]$$

(2-14)

where

$$\beta_2 = \frac{\epsilon_0 \alpha^2}{\epsilon_N X_N C_3}$$

$$\gamma_2 = \frac{c_4 \alpha}{\epsilon_N}$$

$$\alpha = \varepsilon_G^{\phantom{C}X}_{\phantom{C}N} + \varepsilon_N^{\phantom{C}X}_{\phantom{C}G}$$

For some thermal oxide cases, it has been found empirically that for pulse conditions the oxide current has a form

$$J_{G} = C_{1} \exp C_{2} E_{G}^{\frac{1}{2}}.$$

(2-15)

The charging time then for the case for this type of dominant oxide current

is

$$t_{c} = \frac{2A}{B^{2}} \left[ \frac{B (V_{A} - V_{FB})^{\frac{1}{2}} + 1}{\exp B (V_{A} - V_{FB})^{\frac{1}{2}}} - \frac{B (V_{A})^{\frac{1}{2}} + 1}{\exp B (V_{A})^{\frac{1}{2}}} \right]$$

(2-16)

where

$$A = \frac{\epsilon_{0} \epsilon_{N}}{X_{N} c_{1}}$$

$$B = \frac{c_{2} \epsilon_{N}}{\alpha^{2}}$$

$$\alpha = X_{N} \epsilon_{G} + X_{G} \epsilon_{N}.$$

### 2.2 Experiments and Results

#### 2.2.1 Silicon Oxidation Techniques

There are several types of silicon dioxide films such as thermally grown from steam; thermally grown from oxygen; thermally grown from nitrious oxide and by the pyrolytic decomposition of silane that have been used in combination with silicon nitride. In this study the experiments were restricted to thermally grown silicon dioxide from oxygen. Several variations of this type of thermally grown oxide were studied to determine the effect of oxygen partial pressure and silicon dopant concentrations on the characteristics of MNOS devices.

The oxidation rates of silicon have been shown to be dependent on the oxygen partial pressure, the crystal orientation and the concentration and type of dopant elements in the silicon at the surface.

For example, it has been shown that the linear oxidation rate constant A is not affected, but the parabolic rate constant B is linearly proportional to the equilibrium concentration of the oxidant in the oxide which in turn is related to the partial pressure of the oxidant gas.

On the other hand, it has been shown that the linear oxidation rate constant A is increased for  $\langle 100 \rangle$  oriented silicon as compared to  $\langle 111 \rangle$  oriented silicon while the parabolic rate is not changed much. Further, it has been shown that for heavily doped silicon (C >  $10^{18}$ ) for either phosphorous or boron that the parabolic rate constant B can be increased by a factor of 1.5. The effect of temperature and time has also been determined 0. Of particular importance is the approximation for short time oxidations which is

$$X_G = \frac{B}{A} t + X_1$$

The oxide thickness  $X_G$  for thermally oxidized silicon with oxygen gas as the oxidant is linearly dependent on time; however, the silicon initially appears to oxidize very rapidly such that the linear extrapolation of data yields an initial oxide thickness  $X_i$  at t=0. This has been reported to be typically 200 Å for  $\langle lll \rangle$  silicon.

Since the understanding of the thin oxide case is of primary importance for the fabrication of polarizable MNOS transistors and generally for the fabrication of oxides with low surface state density  $Q_{SS}$ , several experiments were carried out to further characterize this case. First, it was decided that the possibility of an initial oxide,  $X_i$ , would be minimized by elimination of chemically formed surface oxides by a final HF rinse leaving the surface hydropholic. The silicon wafers are then reduced in  $H_2$  in the oxidization system (reactor or furnace) to minimize the effect of fluorine retention on the silicon surface. The silicon material used was primarily  $\langle 100 \rangle$  2 to 8 ohm N type phosphorous doped and the same type of  $\langle 100 \rangle$  crystal diffused with boron to yield a P type surface concentration of 5 x  $10^{16}$  to 2 x  $10^{17}$  per cm<sup>3</sup>. Oxidation on P+ and N+ diffusions were also carried out. The oxidations were either in 100%  $0_2$  or with the oxygen flow reduced to about 10% of the nitrogen carrier gas flow.

The silicon nitride was formed by the pyrolytic decomposition of silane (SiH<sub>4</sub>) in ammonia (NH<sub>3</sub>) premarily at 900°C with nitrogen as a carrier gas. The ammonia/silane ratio was greater than 200 for all experiments.

#### 2.2.2 Characterization of MNOS Devices

Electrical measurements of the current density (J) vs electric field (E) relationship, capacitance-voltage measurements (C-V) under temperature bias stress and N and P channel transistor drain current ( $I_d$ ) vs applied voltage ( $V_A$ ) have

been used to characterize the nitride-oxide films fabricated. Also optical and physical measurements of film thicknesses have been used with the capacitance measurements to determine the dielectric constants.

The first type of measurements that were made were to characterize the grown silicon diocide films and the deposited silicon nitride films individually. The typical dielectric constants measured were  $\epsilon_{\rm N}=6.5$  and  $\epsilon_{\rm G}=3.9$ . The dielectric constant of the very thin oxide films is uncertain because of the difficulty in measuring the oxide thickness; however, reasonably good agreement of the capacitance and current-field relationships for different thicknesses in the same range (100-200 Å) was obtained by using the dielectric constant of the thicker oxide films.

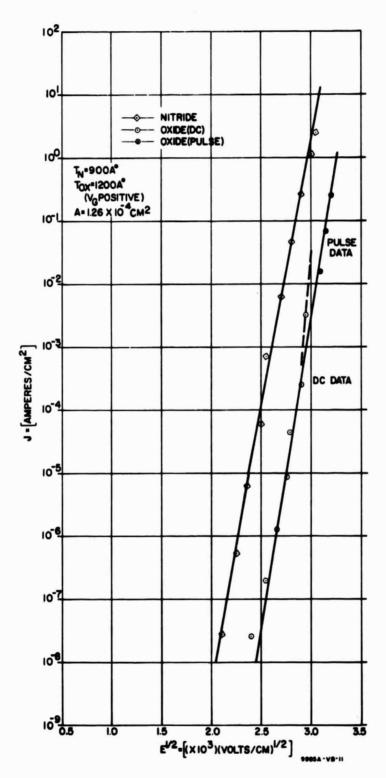

Typical silicon nitride and thermally grown silicon dioxide single layer current density vs electric field relationships are shown in figure 3. The current measurements were made down to  $10^{-14}$  amperes. Comparison of these characteristics with the double layer nitride-oxide films provides some insight into the interaction of the nitride deposition conditions on the oxide formation and vice versa.

The most significant MNOS device experiment performed involved the simultaneous fabrication of N and P channel MNOS transistors and capacitors. The C-V measurements of the two types of capacitors are shown in figure 4. It should be noted that while the thermal oxidations were performed simultaneously the nitride depositions for these samples were done in two different runs to accommodate other test wafers used in the experiment. The measured thicknesses for the samples were:

|       | x <sub>N</sub> | X <sub>G</sub> | Cmax                                |

|-------|----------------|----------------|-------------------------------------|

| da-l  | 900            | 190            | 5.91 pf (P- Diff & N+<br>Diffusion) |

| CX 62 | 660            | 100            | 8.65 pf (N type and P+<br>Diffusion |

Figure 3. Insulator Current Density (J) vs. Electric Field ( $\mathbb{E}^{\frac{1}{2}}$ ) for Separate Oxide and Nitride Films.

Figure 4. C-V Curves for Thermally Oxidized N and P Type Wafers.

|       | x <sub>N</sub> | X <sub>G</sub> | C <sub>max</sub>           |

|-------|----------------|----------------|----------------------------|

| BS 13 | 660            | 100            | - (N type Capacitors only) |

It can be seen from the C-V curves of figure 4 that the  $\Delta V_{FB}$  for a given applied dc voltage  $(V_A)$  is much greater for da-1 than for CX 62 even though the field in the oxide of da-1 is much less than for CX 62. It is concluded that not only is the oxidation rate of the P- diffusion (da-1) almost twice that of the N wafer, but also the conductivity of the thicker film on the P- wafer must also be greater than for the N wafer. Note also that the  $\Delta V_{FB}$  for  $\pm$   $V_A$  is almost symetrical indicating that deep traps are not significant for these oxidation conditions.

The J vs  $E^{\frac{1}{2}}$  relationships shown in figure 5 for the oxide and nitride films on these two wafers were calculated from the measured current through the composite MNOS capacitor and the fact that

$$J_{N} (E_{N}) = J_{G} (E_{G})$$

in equilibrium. The equations 2-4 and 2-5 were used to calculate  $E_N$  and  $E_G$ .

It can be seen that the nitride J vs E characteristics for the two films are nearly the same as should be, but that the current density for the oxide film on the P- diffused wafer is much greater than for the oxide on the N type wafer as predicted from the C-V measurements, i.e.,

$$J_C$$

(da-1) >  $J_C$  (CX 62)

for a given field.

An additional factor observed is that the oxide - J vs E - relationship does not seem to be like Fowler-Nordheim tunneling. The presence of other field

Figure 5. Current Density (J) vs. Electric Field (E2) for MNOS Capacitors.

dependent currents is probably masking the pure tunneling characteristic.

Finally the initial value of  $V_{FB}$  for the samples that included the MNOS transistors (CX 62 and da-1) was much greater than for the capacitor only wafer BS13. This indicates some contribution to  $Q_{SS}$  from the previous processing steps. The efficacy of the hydrogen reduction step was proven by the fact that BS13 and other similarly processed wafers had initial flatband voltages of about 1 volt indicating low net effective  $Q_{SS}$ . If it is assumed that the initial interface charge  $Q_T$  is zero, then from equation 2

$$N_{ss} = \frac{c_T}{q} \left[ \Delta V_{FB} - \emptyset_{ms} \right]$$

$$N_{ss} \simeq 2 \times 10^{11} \text{ cm}^{-2}$$

This represents about the lowest limit of N<sub>SS</sub> for the thermally oxidized samples measured. Also there were no significant differences between the oxides thermally grown in the reactor and the oxides thermally grown in the resistance heated furnaces.

The oxide thickness for thermally oxidized N type  $\langle 100 \rangle$  control wafers fabricated along with da-1, CX 62 and the others where the partial pressure of  $0_2$  was about 0.1 of atmospheric is shown in figure 6. Note that  $X_i = 65$  Å for these conditions is much less than that reported previously  $(X_i = 200 \text{ Å})^{12}$ . The oxidation rate ratio (B/A) calculated from this data is lower by a factor of two as compared to the oxidation theory and previously determined rate constants for thicker oxides  $^{9}$ ,  $^{10}$ ,  $^{11}$ ,  $^{12}$ . The uncertaintly in the thin oxide measurements may be contributing to this error.

N channel MNOS transistors made on wafer da-1 were tested and shown to have characteristics very similar to the capacitors on the same wafer. The drain

Figure 6. Thin Thermal Oxide Thickness vs. Oxidation Time (low partial  $O_2$  pressure)

2-18

Aerospace Division-

current vs drain voltage ( $I_d$  vs  $V_d$ ) and drain current vs gate voltage ( $I_d$  vs  $V_g$ ) characteristics are shown in figure 7. The P channel MNOS transistors on CS 62; however, exhibited anomolous behavior. It was found that at low electric field for long periods of time some correlation between the MNOS transistors and capacitors was obtained. At higher fields, however, the direction of the transistor threshold voltage,  $V_{\mathrm{T}}$ , shift was reversed compared to the capacitors. Since P channel transistors require a P+ source and drain diffusion and it has been shown that the oxides over boron diffused (P type) regions are much more conductive, it is believed that the reversal of the direction of  $\Delta V_{\rm T}$  is caused by a larger and opposite polarity of charge being stored near the source junction as compared to the charge stored over the N type material where the channel is formed. This points to the conclusion that thermally grown thin oxide for MNOS P channel transistors is undesirable.

#### 2.2.3 Charging and Retention Time Response

In addition to the simplified solutions to the charging response time of MNOS devices listed in section 2.1, computer aided transient analysis using Sceptre has been used. The basic circuit transient analysis program has been modified to include a number of defined functions which are used to describe the conduction mechanisms in the nitride and oxide layers based on empirically derived data. The model of figure 2 is the basic circuit model used for the transient analyses. The simulation of the N channel transistor case described in the previous section has been accomplished and the results are shown in figures 8, 9 and 10. The correlation with the measurements is reasonably good. Figure 8 depicts the waveshape corresponding to the conduction current density through the oxide, and it can be seen that it is three orders of magnitude greater at its

VG=-0.5 V/STEP

A-LEFT PHOTO

P = O I

RIGHT PHOTO:

HORIZ: 0.1 MA/DIV VERT: 5 V/DIV

TOP: ID VS VD

+ \

0

و ا

9995A-VA-12

AFTER +55 V, 10 USEC VT (SAT) = +6V V<sub>T</sub> = +4

and Gate Voltage Showing Threshold Voltage Shift

Figure 7. MNOS Transistor Drain Current vs. Drain Voltage

BOTTOM: ID VS VG

0

ا ۸<sub>G</sub>

۰ ۲

AFTER -55V, 10 µSTC

VT (SAT) = -9V VT = -4V

2-20

Figure 8. Computer Print Out of J<sub>G</sub> vs. t

Figure 9. Computer Print Out of  $J_N$  vs. t

Figure 10. Computer Print Out of VFB vs. t

peak in relation to the peak nitride current density shown in figure 9. The waveshape of  $J_{\rm N}$  clearly defines the turnoff for the 55 volt driving pulse of 10 microseconds width. The flatband voltage waveshape is shown in figure 10. This is seen to reach 5.6v within 10 microsec and is seen to persist after the driving pulse has been turned off.

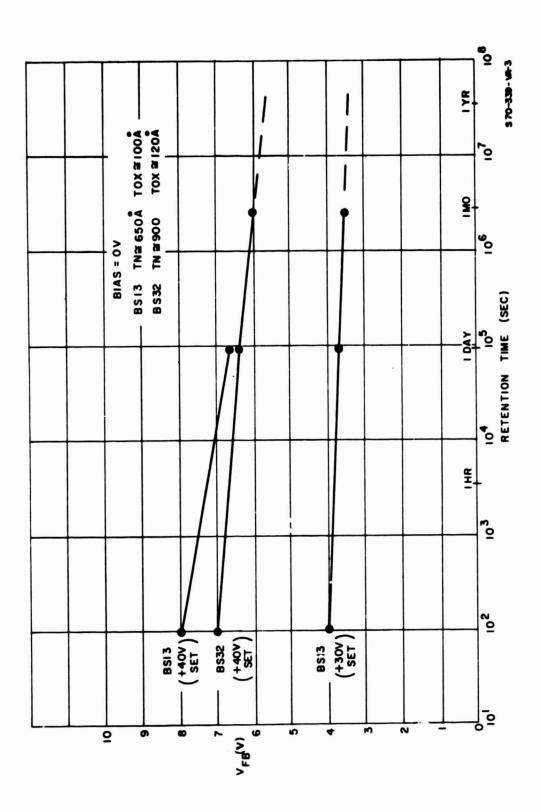

The P channel capacitors formed on wafer BS13 which are similar to those on CS 62 were also pulse tested to determine the flatband voltage shift vs the applied voltage and pulse width. The data is shown in figure 11. Note that the flatband voltage shift is nearly symetrical for negative and positive applied fields taking into account the effect of  $V_{FB}$  on the fields. This indicates that deep electron traps at the interface of the insulators are not present in any large amount. The retention time for this type of MNOS device was measured at  $V_A = 0v$  and is shown in figure 12. The rate of decay is a function of the total  $V_{FB}$  shift. The decay is logrithmic and a characteristic rate of decay is 0.3 to 0.5 v/decade from saturation. This is not as good as measured for samples that have been shown to have deep traps where the rate of decay is less than 0.1 v/decade.

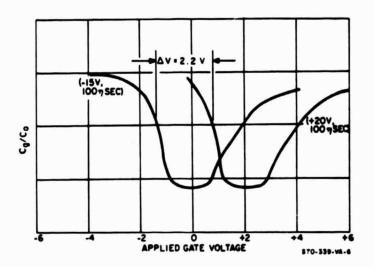

To illustrate the high switching speed limits for thermally oxidized MNOS transistors, N channel MNOS transistors were fabricated with a thermal oxide grown at  $850^{\circ}$ C in a partial pressure of oxygen and with a nitride film of about 350 Å. The C-V curve of the gate capacitance which gives a low frequency characteristic is shown in figure 13. The curves illustrate that a 2.2 volt  $V_{FB}$  shift is possible with a +20 and a -15 v, 100 nanosec pulse. The decay rate was typical of the thermally grown oxides previously discussed.

Figure 11, Flatband Voltage vs. Applied Voltage for Different Times

Figure 12. Retention of Charge

2-26 UNCLASSIFIED

Figure 13. C-V Curve Showing N Channel Transistor Flatband Voltage Shift for 100 Nanosec Pulses.

2-27

#### 2.2.4 Nitride-Oxide Passivation

The factors involved in optimizing nitride passivated devices are the initial level of  $Q_{\rm I}$  and  $Q_{\rm ss}$  that can be achieved, the long term accumulation of  $Q_{\rm I}$  at the operating fields, the change in  $Q_{\rm I}$  and  $Q_{\rm ss}$  for a given temperature bias stress, the maximum electric field protection provided and finally the extent to which the MNOS transistor transconductance (where  $g_{\rm m} \sim C_{\rm T}$ ) is to be maximized. Where shielding is not provided radiation sensitivity is also a factor to be considered.

To illustrate the range of possibilities consider the following list of cases where the total effective series capacitance per unit area  $C_{\rm T}$  is kept constant. The flatband voltage is derived from equation 2-9, i.e.,

$$v_{FB} = \frac{1}{c_T} \quad \begin{bmatrix} c_T \\ \hline c_N \end{bmatrix} \quad c_I \quad + \quad c_{SS} \quad .$$

| Case | Relative<br>Thicknesses | Relative<br>Capacitance | $\Delta V_{\mathbf{FB}}$                                        |

|------|-------------------------|-------------------------|-----------------------------------------------------------------|

| 1    | $x_{G} < x_{N}$         | $c_N \cong c_T$         | $-\frac{1}{C_{\mathrm{T}}}$ [Q <sub>I</sub> + Q <sub>ss</sub> ] |

| 2    | $x_G = x_N$             | $c_{N} \cong 2.7 c_{T}$ | $-\frac{1}{C_{\rm T}}$ [0.37 $Q_{\rm I} + Q_{\rm ss}$ ]         |

| 3    | $x_G > x_N$             | $c_N > c_T$             | $-rac{1}{C_{ m T}}$ [Q $_{ m ss}$ ]                            |

Therefore, to minimize the effect of Q<sub>I</sub> build up, it appears at a first glance that the nitride thickness should be minimized. There are, however, two additional factors that must be considered. One is that the masking ability of the Si<sub>3</sub>N<sub>4</sub> tends to decrease as its thickness is decreased. Second, but more important, is the consideration of a dipole electric moment

— Aerospace Division—

that has been observed in  $SiO_2$  after the  $Si_3N_4$  deposition. It is suspected that the dipole is caused by the presence of hydrogen during the  $Si_3N_4$  deposition. A similar list of cases for thick and thin nitride films again where  $C_T$  is a constant and where  $\Delta V_{FB}$  is also a function of the dipole charge  $Q_P(V_A)$  in the oxide in this manner,

$$\Delta V_{FB} = -\frac{1}{C_{T}} \qquad \boxed{\frac{C_{T}}{C_{N}}} \quad (Q_{I} - Q_{P}) + (Q_{ss} + Q_{P})$$

is shown below:

| Case | Relative<br>Thickness             | Relative<br>Capacitance | ΔV <sub>FB</sub>                                                                           |

|------|-----------------------------------|-------------------------|--------------------------------------------------------------------------------------------|

| 1    | $x_{G} < x_{N}$                   | $c_N \cong c_T$         | $-\frac{1}{C_{\mathrm{T}}} [Q_{\mathrm{I}} + Q_{\mathrm{ss}}]$                             |

| 2    | $\vec{x}^{G} = \vec{x}^{\Lambda}$ | $c_N \cong 2.7 c_T$     | $-\frac{1}{C_{\rm T}}\left[.37 \; (Q_{\rm I} - Q_{\rm P}) + Q_{\rm ss} + Q_{\rm P}\right]$ |

| 3    | $x_G > x_N$                       | $C_N > C_T$             | $-\frac{1}{C_{\mathrm{T}}} \left[Q_{\mathrm{ss}} + Q_{\mathrm{P}}\right]$                  |

The result is that the dipole charge effect can be minimized for a given  $C_T$  with a thin oxide. This reduction of the dipole effect has been observed for thinner oxides. Also the magnitude of  $Q_P$  can be affected somewhat by the total amount of  $NH_3$  present during the nitride deposition.

Another hysteresis effect that has been observed which has the opposite sense to hysteresis caused by dipole moments is caused by interface charge transport across either the nitride-metal interface, the nitride-oxide interface or the oxide semiconductor interface. For any of these cases a space charge tends to remain at the interface after the applied bias because of the interface barrier.

— Aerospace Division—

This space charge is then imaged in the scmiconductor producing a flatband voltage shift. The significant aspect of this interface charge transport affect is that the direction of  $V_{FB}$  shift is positive for a positive applied voltage. Note that either ionic drift or dipole moments in the insulators always produce a negative  $V_{FB}$  shift for a positive applied voltage and therefore, may be separated from the hysteresis caused by interface charge transport. This space charge effect is minimized by increasing the total effective capacitance  $C_T$ . The magnitude of  $\Delta V_{FB}$  for samples with 900 Å of nitride and 100 Å of oxide is about  $\pm$  .2v for  $\pm$  15v bias.

The conclusion based on the above factors is that for fields of less than 2 x  $10^6$  v/cm that the case where  $\rm X_G < \rm X_N$  is the preferred and more stable case since at low fields  $\rm Q_I$  remains small,  $\rm Q_P$  is minimized, and the maximum  $\rm C_T$  can be obtained for a given nitride thickness.

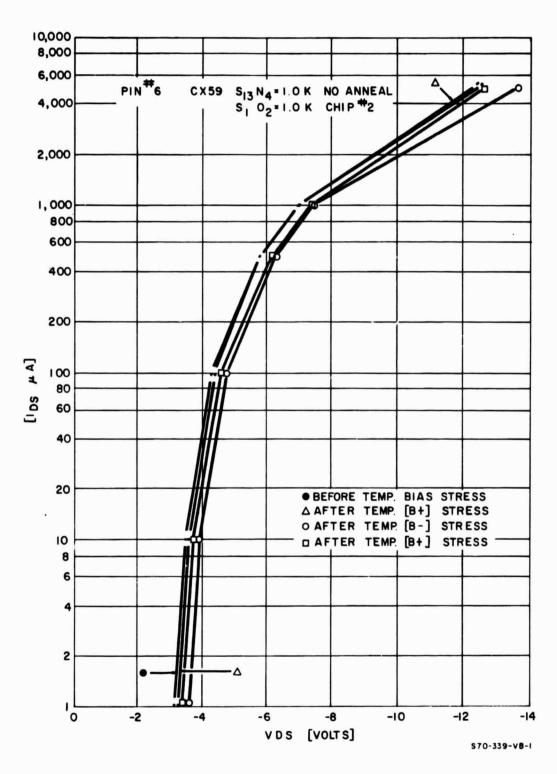

A very conservative case of where both a thick oxide and thick nitride of equal thicknesses are used to minimize the magnitude of the electric fields is shown in figure 14. A bias of  $\pm$  20 volts was used giving fields of less than 2 x  $10^6$  v/cm in both the nitride and oxide films. The temperature of the test was  $150^{\circ}\text{C}$  and the time was 16 hours for each bias. The initial threshold voltage at 1 micro-amp was about -3.1v. Note that for a positive bias little shift occured, but for a negative bias about a -0.6v shift occured. A shift of +0.4v occured after the positive bias was occured leaving a net shift of -0.2v. The direction of the shift with bias (+  $\Delta V$  with +  $V_A$ ) is indicative of the interface charge transport and the net - $\Delta V$  shift is indicative of either redistribution of ionic charge in the oxide or some nitride conduction resulting in an increase of positive insulator interface charge  $Q_T$ .

### 2.2.5 Processing Manual for Pyrolytic Silicon Nitride Deposition

A manual describing the nitride processing details used for this task entitled "Pyrolytic Silicon Nitride Deposition" has been delivered under separate cover.

### 2.3 MNOS Transistor Memory System

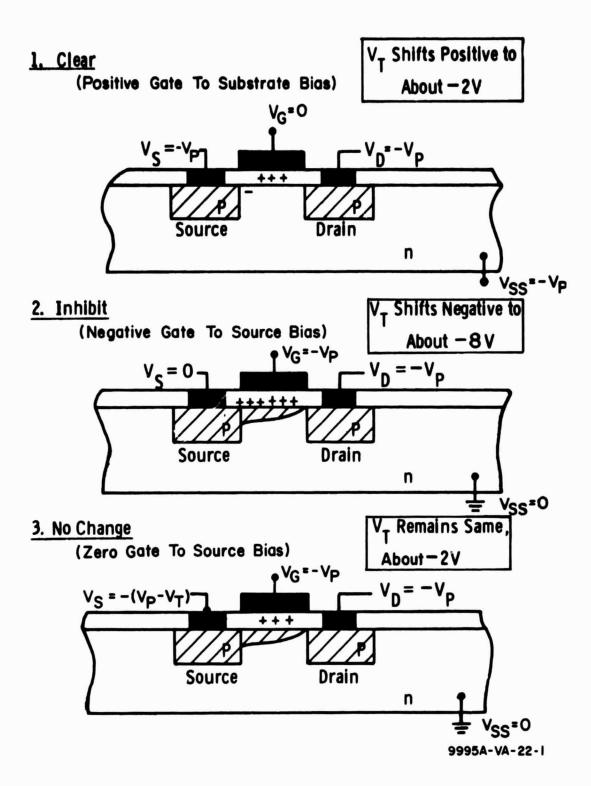

A memory array using MNOS transistors has been designed. The memory operation depends on gate-to-source biasing for polarization or inhibiting of polarization. This is also known as channel shielding. The three modes of operation of the polarizable MIS transistor for gate-to-source polarization which is required in clear (erase)—write systems are shown in figure 15.

In the clear mode, a sufficiently large negative bias  $(V_{SS} = -V_p)$  applied to the n-type pocket provides a positive gate-to-source bias which shifts the threshold voltage positive. In the inhibit mode, a negative bias

Figure 14. MNOS Transistor Curves for Temperature Bias Stress (V<sub>A</sub> =  $\pm$  20v and E<sub>N</sub>  $\simeq$   $\pm$  0.8 x 10<sup>6</sup> v/cm, E<sub>G</sub>  $\simeq$  1.3 x 10<sup>6</sup> v/cm)

2-32 UNCLASSIFIED

Figure 15. Gate to Source Polorization (Channel Shielding) Modes of Operation.

is applied  $(V_G = -V_P)$  with respect to the source  $(V_S = 0)$ . Under this condition, notice that the p-channel MIS transistor is turned on such that a p-type surface channel exists. In the inhibit mode, the threshold voltage is made to shift negative. If the threshold voltage is made more negative than the read sense voltage, then the device will not turn on during the read operation. In the last mode of operation, shown in figure 15 the source voltage is made about equal to  $-V_P$  when the gate polarizing voltage  $(V_G = -V_P)$  is applied. Since the gate-to-channel voltage is only about a threshold voltage  $V_T$ , the device is not polarized and the threshold voltage  $V_T$  remains the same.

A breadboard of a 4 bit read/write memory array has been fabricated, and delivered for this task. The operation of the breadboard memory is based on a memory word clear (erase) period followed by a write period. A schematic of a Westinghouse read/write MNOS memory system including timing waveforms is shown in figure 16. The breadboard memory represents a four bit segment of this type of memory. The addressing and read/write logic is achieved with switches in the breadboard. Four transistors are bonded together in each package to form the MNOS memory.

The timing and voltage waveforms for operation of the decoder/driver and memory array sections are also shown on the memory schematic, figure 16. The basic drain supply voltage  $V_{DD}$  common to both decoder/driver and memory array varies between -30V during the clear (erase) and write periods and -15V during the read period. The inverter-load-device gate supply voltage  $V_{gg}$  varies between -30V during the clear and write periods and -20V during the read period to provide maximum current drive and thus faster response times. Also, the output voltage of the memory output drivers is then the full value of the  $V_{DD}$  supply voltage since  $|V_{gg} - V_{T}| \geq |V_{DD}|$  The nominal logic levels

Figure 16. Array Schematic Diagram and Waveforms

2 35 UNCLASSIFIED

for the address inputs, address decoder, bit-line inputs and memory outputs are "1" = -15V and "0" = 0 V, thus all of the input/output levels are compatible with p-channel logic design. Internally, the logic levels for the word lines  $W_1$  through  $W_M$  are 0 or -30V during the clear and write periods and are 0 V and  $-(15V-V_T) \cong -10V$  during the read period.

The most significant feature of this array design is that the positive clear (earse) bias of the gate with respect to the substrate is achieved by pulsing the memory array substrate (V<sub>SSM</sub>) to -30V while grounding the word line that is to be cleared (erased). The nonaddressed words have the word line voltage also at -30V to prevent loss of stored charge. These cases are illustrated in the timing diagram in figure 16. The advantages of this approach is that the word driver and all of the associated address decoder is not required to switch between +3- and -30V and all of the input/output voltage levels remain compatible. Also, no junction or gate ever sees more than a 30V bias.

When the bit line is a logical "O" = OV during the write period such as for  $B_{1/1}$  in the timing diagram, the source of each memory device on bit line 1 also goes to OV. Thus, since word line 1,  $W_{1}$  is at -30V, the gate-to-chennel bias is nearly O V and no threshold voltage shift occurs. The non-addressed memory devices ( $W_{N}$  =0) remain in the off condition, the gate-to-substrate bias is O V, and no threshold voltage shift occurs.

During the read period, the read signal R is biased to -15v; thus, the source of each memory device is essentially at ground potential. In the case of memory device 1/1, assume the threshold voltage has been shifted to a negative value of about -10v. When the word line  $W_1$  for the read period is -10v the memory device is off making the memory device drain voltage negative which in turn makes  $V_{\rm OUT}$  (1) = 0 V. It is easy to adjust the read (or sense) value 2-36

— Aerospace Division—

of W<sub>1</sub> to be about the value of the most negative threshold voltage of the memory devices to make this case valid.

In the case of N<sup>th</sup> bit of word one, the threshold voltage has been shifted to its most positive value, but not to depletion mode for the values of supply voltage shown. If the devices are shifted to the depletion mode, then the substrate voltage of the decoder (V<sub>DSS</sub>) called the offset voltage and the logical "O" voltage level of all of the address inputs must be shifted from O to a slightly more positive voltage; (i.e., from O to +4 V). This is possible because the substrate of the decoder/driver is isolated from the memory array. It has been observed that oxides thermally grown on p channel MNOS transistors exhibit a lower gate breakdown voltage than capacitors on the same wafer. This is attributed to different oxide characteristics for the oxide over the P+ diffused source and drain regions. N channel transistors; however, do not exhibit the same problem. The lower gate breakdown of the p channel transistors limits the switching speed that can be achieved with thermally grown oxides.

---- Aerospace Division-

#### 3.0 Conclusions

Experiments have shown that thermally grown oxides with reduced 0, partial pressure are capable of producing oxides less than 100 A thick. These thin thermal oxide nitride structures do not appear to have deep traps at the insulator interface, and thus have poorer retention than comparable deposited oxide structures. Because of the higher conductivity of the oxide, however, it is possible to achieve switching and storage with 20v. 100 nanosec pulses. N channel transistors are the preferred type using the thin thermal oxide because of the anomolous behavior exhibited by the p channel MNOS transistors which is related to the conductivity of the thermal oxide over the P+ source and drain diffusions. Passivated MNOS devices are optimized with respect to maximum trans-conductance and stability when the oxide is much less than the nitride thickness provided the voltages applied do not produce fields greater than  $2 \times 10^6$  v/cm. Other, more conservative options that trade off transconductance for lower fields are possible. These processes are predictable and reproducable; and therefore, the MNOS devices may be readily used in nitride passivated arrays or charge storage memory arrays.

- Aerospace Division-

#### REFERENCES

- 1. J. R. Szedon and T. L. Chu. "Tunnel Injection and Trapping of Electrons in Al-Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub> Silicon (MNOS) Capacitors," IEEE Solid State Device Research Conference, Santa Barbara, Calif., June 1967.

- 2. M. Lenzlinger and E. H. Snow. "Fowler-Nordheim Tunneling into Thermally Grown SiO2," Journal Appl. Phys., Vol. 40, p. 278, Jan. 1969.

- 3. S. M. Sze. "Current Transport and Maximum Dielectric Strength of Silicon Nitride Films," Journal Appl. Phys., Vol. 38, p. 295, June, 1967.

- 4. T. L. Chu, J. R. Szedon, and C. H. Lee. "The Preparation and C-V Characteristics of Si-Si3N<sub>4</sub> and Si-SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub> Structures," Solid State Electronics, X, (1967), p. 897-905.

- 5. J. R. Szedon and T. L. Chu, Ibid.

- 6. F. A. Sewel, Jr., H. A. R. Wegener, and E. T. Lewis. "Charge Storage Model for Variable Threshold FET Memory Element," Appl. Phys. Letters, Vol. 14, p. 45, 15 Jan. 1969.

- 7. D. Frohman-Bentchkowsky and M. Lenzlinger. "Charge Transport and Storage in Metal-Nitride-Oxide-Silicon (MNOS) Structures," Journal Appl. Phys., Vol. 40, No. 8, July 1969, pp. 3307-3319.

- 8. H. A. R. Wegener, F. A. Sewell, Jr., "MIS Transistor for Use as a Non-volatile Digital Storage Element," AFAL-TR-69-187, July 1969, p. 12.

- 9. B. E. Deal and A.S. Grove, Journal Appl. Phys., 36, 3370, (1965).

- 10. W. A. Pliskin, E.B.M. Journal, 10, 198, (1966).

- 11. B. E. Deal and M. Sklar, J. El. Chem. Soc., 112, 430, (1965).

- 12. B. E. Deal and A. S. Grove, SAP 36, 3770, (1965).

- 13. SCEPTRE, AFWL-TR-67-124.