https://ntrs.nasa.gov/search.jsp?R=19700026403 2020-03-11T23:36:59+00:00Z

Los - Etha

NASA CR. 72725

GE NO. 70SD4256

No. 170-35719

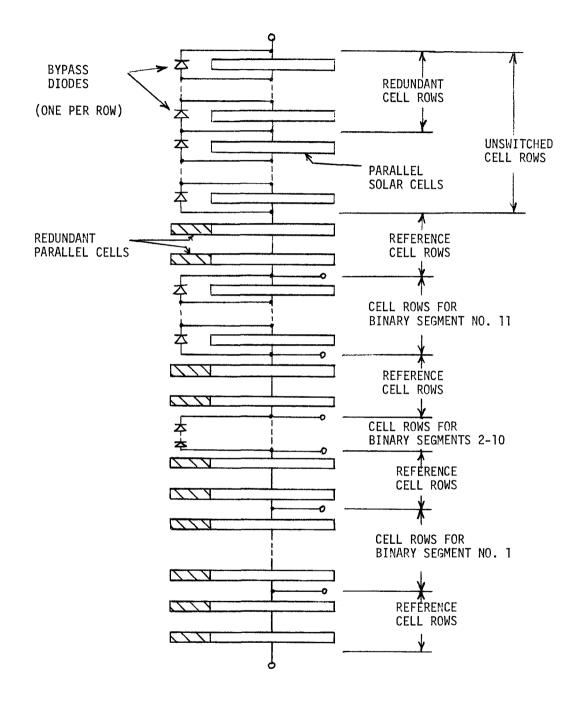

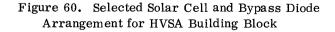

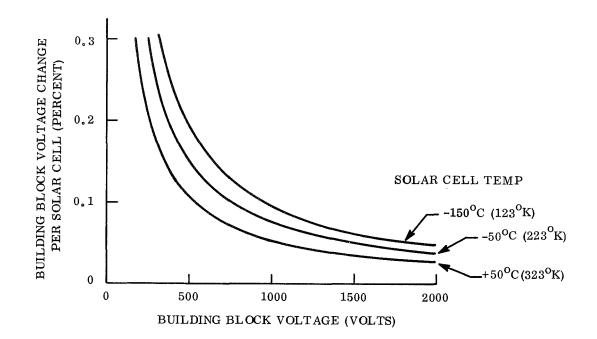

# STUDY OF HIGH VOLTAGE SOLAR ARRAY CONFIGURATIONS WITH INTEGRATED POWER CONTROL ELECTRONICS

by

T. Ebersole, J.H. Hayden, R. Rasmussen, and P. Wiener

GENERAL ELECTRIC COMPANY

prepated for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION June 1970 Contract No. NAS 3-8997 NASA Lewis Research Center

Bernard L. Sater, Project Manager

# NOTICE This report was prepared as an account of Government-sponsored work. Neither the United States, nor the National Aeronautics and Space Administration (NASA), nor any person acting on behalf of NASA: A.) Makes any warranty or representation, expressed or implied, with respect to the accuracy, completeness, or usefulness of the information contained in this report, or that the use of any information, apparatus, method, or process disclosed in this report may not infringe privately-owned rights; or B.) Assumes any liabilities with respect to the use of, or for damages resulting from the use of, any information, apparatus, method or process disclosed in this report. As used above, "person acting on behalf of NASA" includes any employee or contractor of NASA, or employee of such contractor, to the extent that such employee or contractor of NASA or employee of such contractor prepares, disseminates, or provides access to any information pursuant to his employment or contract with NASA, or his employment with such contractor. E. Requests for copies of this report should be referred to National Aeroanutics and Space Administration Scientific and Technical Information Facility P.O. Box 33 College Park, Md. 20740

# Final Report STUDY OF HIGH VOLTAGE SOLAR ARRAY CONFIGURATIONS WITH INTEGRATED POWER CONTROL ELECTRONICS

by

R. Rasmussen - Systems Analyst P. Wiener - Program Manager

prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION June 1970 Contract No. NAS 3-8997 NASA Lewis Research Center Cleveland , Ohio

> Bernard L. Sater, Project Manager Spacecraft Technology Division

SPACE SYSTEMS ORGANIZATION Valley Forge Space Center P. O. Box 8555 • Philadelphia, Penna. 19101

# TABLE OF CONTENTS

| Section  |               |       |              |      |            |      |         |         |     |         |         |      |          |          |         |      |         |          |          |          |     |          |        |   |   |   | Page |

|----------|---------------|-------|--------------|------|------------|------|---------|---------|-----|---------|---------|------|----------|----------|---------|------|---------|----------|----------|----------|-----|----------|--------|---|---|---|------|

| 1        | SUI           | MMAI  | RY .         | • •  | •          | •    | •       | •       | •   | •       | •       | •    | •        | •        | •       | •    | •       | •        | •        | •        | ۰   | •        | •      | • | ۰ | ٥ | 1    |

| 2        | INT           | ROD   | UCTI         | ION  | •          | •    | •       | •       | •   | •       | •       | •    | •        | •        | •       | •    | •       | ٠        | •        | •        | •   | •        | ø      | • | • | • | 2    |

| 3        | RE            | QUIR  | EME          | NTS  | , DI       | ESI  | GN      | GC      | )AI | ĽS A    | ANI     | DG   | UI       | DE       | LIN     | VES  | •       | •        | •        | •        | •   | •        | •      | • | • | • | 4    |

| 4        | EN            | VIRO  | NME          | NT ( | CON        | ISII | DEF     | la 1    | ГЮ  | NS      | •       | •    | •        | •        | •       |      | •       | •        | •        | •        | •   | •        | •      | • | • | • | 7    |

| 5        | TE            | CHNI  | CAL          | ANA  | LY         | SES  | 5       | •       | •   | •       | •       | •    | •        | •        |         | •    | •       | •        | •        | •        | •   | •        |        | • | • | • | 13   |

| 6        | SEI           | LECI  | ED S         | SYSI | ΈM         | СС   | ONF     | FIG     | UR  | АТ      | IOI     | NS   | •        | •        | •       | •    | •       | •        | •        | •        | •   | •        | •      | • | • | • | 88   |

| 7        | SYS           | STEM  | [ PEI        | RFO  | RMA        | ANC  | CE :    | ES'     | TIN | /IA ]   | res     | 5    | •        | •        | •       | ٠    | •       | •        | •        | •        | ٠   | •        | •      | • | • | • | 100  |

| 8        | $\mathbf{RE}$ | LIA B | ILIT         | Y Al | <b>NAL</b> | YS   | ES      | •       | •   |         | •       | •    |          | •        |         | •    | •       |          | •        | •        | •   | •        | •      | • | • | • | 107  |

| 9        | RE            | LATI  | ED A         | NAL  | YSE        | s A  | NI      | c c     | ON  | SIL     | )EF     | RA . | ГЮ       | NS       | • .     | •    | •       | •        | •        | •        | •   | •        | •      | • |   | • | 131  |

| 10       | $\mathbf{PR}$ | OBLI  | EMS .        | •••  | •          | •    | •       | •       | •   | •       | •       | •    |          |          | •       | •    | •       | •        | ٠        |          |     | •        | • .    | • | • | • | 155  |

| 11       | $\mathbf{FU}$ | TURI  | e wo         | RK   | •          | •    | •       | ٠       | •   | •       | •       | •    | •        | •        | •       | •    | •       | •        | •        | •        | •   | •        | •      | • | • | • | 161  |

| 12       | co            | NCLU  | JSIOI        | NS.  |            | •    | •       | •       | •   | •       | •       | •    | •        | •        | •       | •    | •       | •        | •        | •        | •   | •        | •      | • | • | • | 167  |

| APPENDIX | <b>A</b> :    |       | TERN<br>MPEI |      |            |      | OF<br>• | MI<br>• | CR  | OE<br>• | LE<br>• | ст   | rrc<br>• | NIO<br>• | cs<br>• | SU:  | BST.    | rrA<br>• | \ТІ<br>• | E .      | •   |          | •      | • | • | • | 171  |

| APPENDIX | С В:          |       | FECT<br>SA W |      |            |      |         |         |     | AN      | D I     | BA ( | CK       | SHI<br>• | EL      | DII. | ٩G<br>• | тн<br>•  | ICI<br>• | KNI<br>• | ESS | 101<br>• | ۲<br>• | • | • | o | 176  |

| APPENDIX | C:            | NEV   | N TE         | CHN  | 10L        | 0G   | Y       |         | •   |         |         |      |          | •        | •       |      | •       |          |          | •        |     | •        | •      |   |   | • | 178  |

#### ABSTRACT

This study defined solar array electrical configurations which regulate and reconfigure, by switching, a 16 KV, 15 KW array with electronics integrally mounted to the array substrate. A hypothetical mission included load requirements of: 1 KV to 16 KV, milliamperes to amperes,  $\pm 0.1\%$  voltage regulation, and array switching to supply alternate load configurations. Voltage regulation is by a binary-coded digital switching system, which short-circuits series connected solar cell groups. Minimal total power dissipation and high power transfer efficiency are system characteristics. A general case solution and specific optimized systems were derived. Performance estimates show significant weight savings compared to conventional power conditioning. Problem areas include charged particle radiation and thermal transient effects, and high local power dissipation in semiconductor switches and electronics packaging. Future work requires high voltage switch and isolator development, resolution of environmental problems and breadboard regulator tests.

#### SECTION 1

#### SUMMARY

The purpose of the subject effort was to study electrical configurations for a high voltage solar array (HVSA) which would provide regulated D.C. power directly to spacecraft loads. Primary goals included definition of (1) conceptual designs of electrical configurations for HVSA systems with integral power conditioning, i.e., where all power control functions are array mounted, (2) problems (particularly with switches) associated with HVSA power system development, and (3) future effort to resolve problems identified.

A representative mission was hypothesized where the HVSA (1) supplies power to ion thrusters to raise a spacecraft from low orbit to synchronous altitude orbit in a 90 day period and (2) switches the power to high frequency high voltage electron tubes for broadcast purposes for a period of 5 years.

Definition of generalized load requirements was made in an attempt to define HVSA configurations having applicability to a wide range of loads. Requirements included: (1) voltage range from 1 Kv to 16 Kv, (2) regulated load power of 15 Kw at 16 Kv and alternately 15 Kw total at six or more voltage levels, (3) load current from milliamperes to amperes, (4) system regulation tolerance of  $\pm 0.1\%$ , and (5) provision for HVSA reconfiguration to supply alternate load systems.

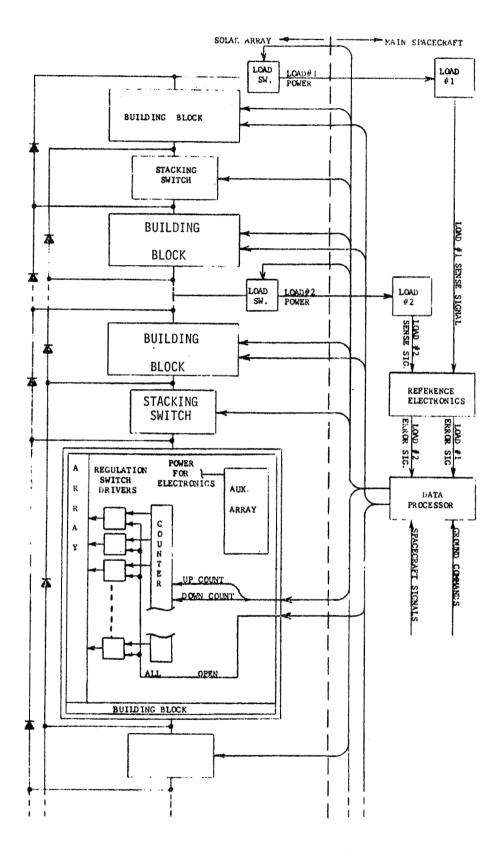

The requirement to perform many and varied switching functions is fundamental to the HVSA. Switching is necessary to (1) arrange HVSA building blocks (power modules) in alternate series-parallel system configurations, (2) connect and disconnect loads from the power sources, (3) establish the voltage reference point, and (4) provide protection for loads and the array. Switches for functions (2) and (3) must block up to 16 Kv, which presently exceeds semiconductor device capability. System tradeoffs show building blocks should be designed for maximum output voltage; 1500 volt transistors are feasible and also satisfy the remaining switch functions.

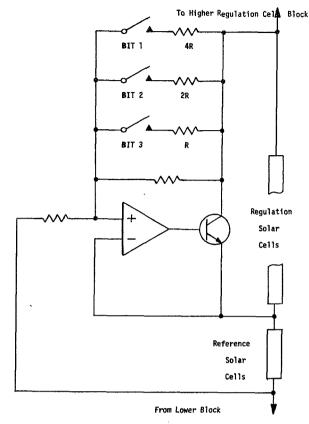

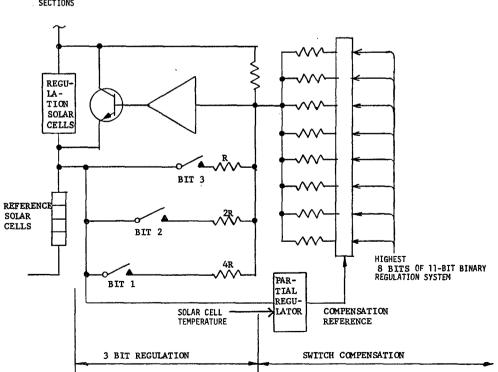

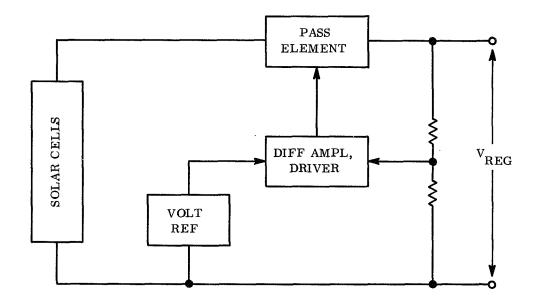

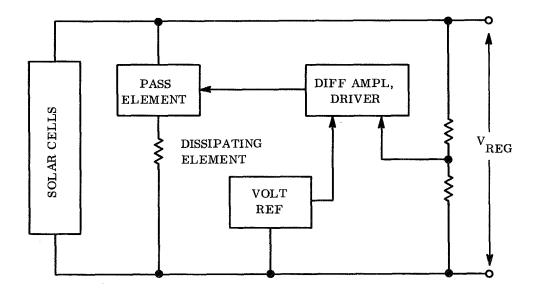

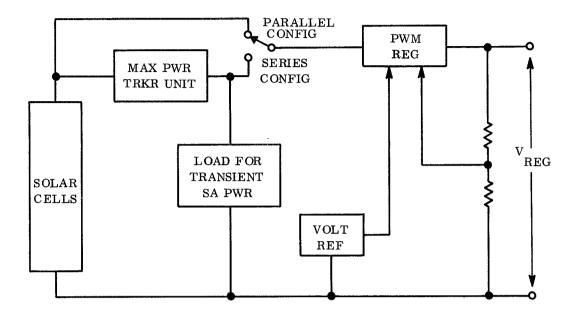

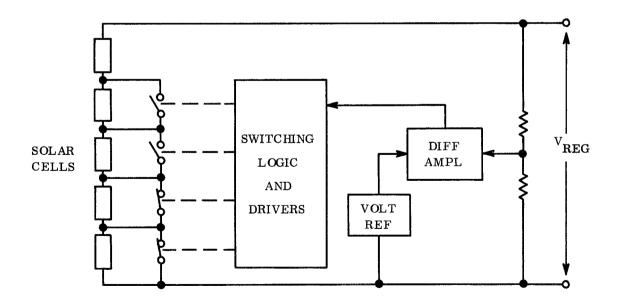

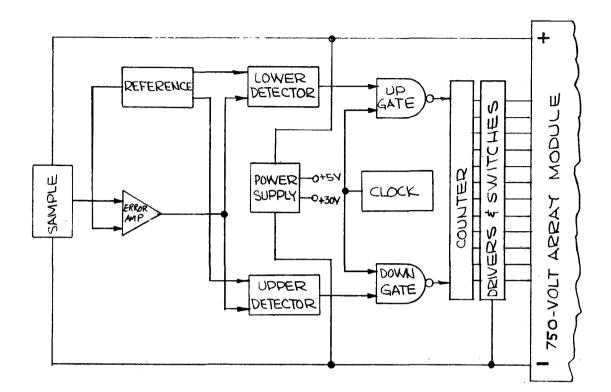

Systems tradeoff studies have eliminated conventional series and shunt regulator systems and maximum power tracker systems in comparison to a system which achieves regulation by a binary-coded switching system. The selected discrete switching system (1) appropriately short circuits series connected solar cell groups to achieve voltage regulation and (2) reduces problems of rejecting excess array power and unneeded array power (when loads are off) by operating the solar cells in a shorted mode, which produces considerably less total heat dissipation than other techniques.

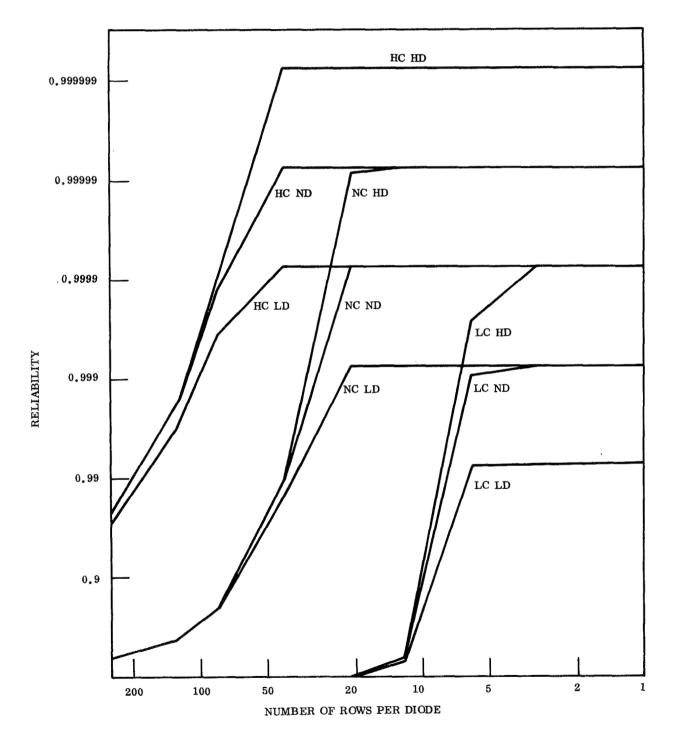

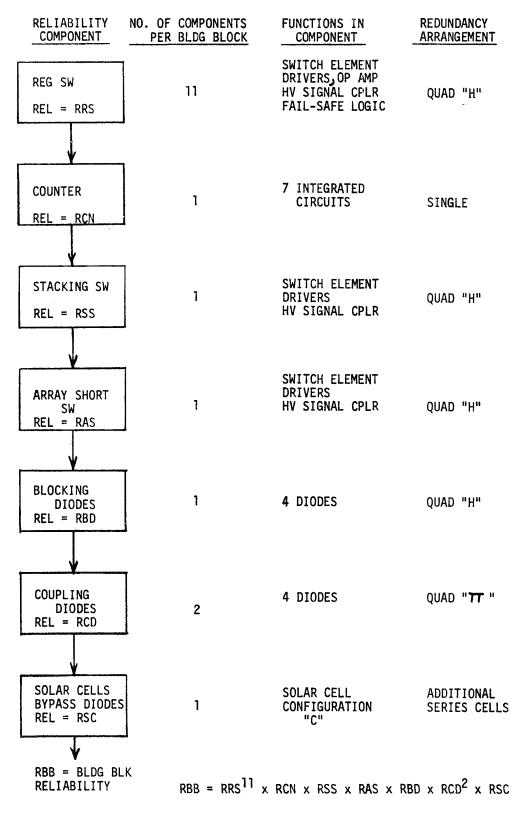

Reliability analyses resulted in selection of an optimum array configuration to minimize effects of cell failures and shadows. Tradeoff studies demonstrate that on the basis of efficiency considerations it is desirable to minimize the number of building blocks, and to design for highest building block voltage and current that satisfies the alternate loads when the HVSA is reconfigured.

Study goals for the HVSA configuration were the attainment of 108 watts/m<sup>2</sup> and 66 watts/Kg. System performance calculations demonstrate a typical 1.5 KV HVSA building block is capable of delivering 117 watts/ m<sup>2</sup> and 70.5 watts/Kg when delivering regulated power. An optimized representative system of building blocks delivers 24.6 Kw of regulated power with a total system weight of 381 Kg.

Major conclusions are that the HVSA concept is feasible, but several major problems must be resolved. These include: severe radiation damage in the transfer orbit, minimization of synchronous altitude radiation damage in the transfer orbit, minimization of synchronous altitude radiation effects on array mounted electronics, developing and qualifying a solar cell module/electronics package capable of surviving thermal cycling, developing a 16 Kv load switch (semiconductor or lightweight/small volume relay), development of a high blocking voltage low level signal coupler, electronic device characterization at low HVSA temperatures, and high local heat dissipation in semiconductor switches.

Future work recommended includes high voltage device development, breadboard binary regulator fabrication and test, comprehensive power systems analyses, design and development of a typical HVSA building block, and resolution of aforementioned problems.

#### **SECTION 2**

#### INTRODUCTION

This is the Final Report of the "High Voltage Solar Array Electrical Configuration Study" performed by the Space Systems Organization of the General Electric Co. for the NASA – Lewis Research Center under Contract Number NAS 3-8997. Briefly, the purpose of this effort was to define solar array electrical configurations which condition high voltage, high power solar arrays with all power control electronics integral with the array. Parallel studies have been conducted for NASA Lewis Research Center under Contracts Number NAS 3-8995 and NAS 3-8996.

The anticipated advent of satellites incorporating ion thrustors and high frequency electron tubes (Klystrons, etc.) has created a need for D.C. power supplies with 2,000 to 16,000 volt outputs. The present thrustors require from 2,000 to 5,000 volts D.C. at the accelerator electrodes. The near future tubes may require up to 16,000 volts D.C.

The D.C. power required for the thrustors and tubes is expected to be derived from solar arrays. It is further expected that for many satellites where thrustors and tubes are involved, a major portion of the total solar array power will be used by these systems and used at relatively constant power levels during steady state operations.

Conventional solar arrays are wired to deliver their D.C. power at less than 100 volts. For the present low voltage solar arrays to meet the high voltage requirements noted above, it is necessary to transform the low voltage into a higher voltage through the use of heavy and complex power conditioning equipment. Typically, each one kilowatt of regulated power is delivered with 15-30 pounds (6.8-13.6 Kg) of conditioning equipment.

In light of the system needs described above, a departure from the conventional method of developing solar array power may be desirable. In this regard, it appears desirable and feasible to:

- 1. Develop solar array power at the voltage levels required by the major using loads.

- 2. Provide on the array itself, the power conditioning required by the major using D.C. loads.

Such a high voltage solar array (with integrated D.C. power conditioning equipment and capable of delivering discrete voltage levels from 2,000 to 16,000 volts to the using load) should reduce the complexity and weight and increase the overall reliability of the total power system.

The information necessary to design the high voltage solar array described above must be determined. To obtain the information to design such arrays, research and development effort is necessary in the areas of (1) operating high voltage solar arrays, (2) providing power conditioning and switching integral with the array (3) developing deployable large area array configurations. Studies of the first of these areas has been conducted under Contracts NAS 3-11534 and NAS 3-11535. The subject contract and this report are concerned with the second of these areas.

The subject effort is significant because it demonstrates that regulation on the array can be performed with high efficiency and minimum total power dissipation compared to conventional series and shunt regulated power systems. Regulated load power can be delivered with a penalty of only 0.33 pounds/Kw (0.15 Kg/Kw) including all electronic devices (with quad redundancy), heat sinks and radiation shielding.

Array reconfiguration, necessary to provide for supplying power to alternate load configurations, can be performed with transistors that are readily available or need minimal development.

Load switching on the array requires 16Kv silicon controlled rectifiers which are unavailable and may not be feasible. Relays may be a more successful approach. Voltage isolation (16 Kv) between signal circuits and high voltage sections is required and can be achieved using light emitting diodes – fiber optics – and photosensitive devices, which are feasible.

The HVSA concept is shown herein to be feasible, but the device problems described previously and radiation, thermal cycling, and packaging design problems must be resolved.

#### **SECTION 3**

#### REQUIREMENTS, DESIGN GOALS AND GUIDELINES

#### 3.1 GENERAL

This section presents the contractual and technical bases for the subject study. Requirements and Design Goals established in the Statement of Work are discussed in Section 3.2. Section 3.3 establishes Guidelines derived from the Statement of Work and during the Mid-Term Oral Presentation.

#### 3.2 REQUIREMENTS

#### 3.2.1 SCOPE

The Statement of Work defines the scope of the subject effort to be a study of electrical configurations for a High Voltage Solar Array (HVSA) which would provide conditioned D. C. power directly to a using load and define:

- 1. Conceptual designs of electrical configurations for high voltage solar arrays with integral power conditioning.

- 2. The problems, and in particular the switch problems, associated with developing such electrical systems.

- 3. The efforts required to resolve the problems defined by the study.

#### 3.2.2 TECHNICAL REQUIREMENTS

The possible applications of a switchable HVSA are many and varied. A single applications, hopefully representative of the general scope of problems, was defined to provide direction to the study.

The array application envisioned (1) supplied power to ion thrustors to raise a spacecraft from low orbit to a synchronous orbit and then (2) switched the power to high frequency electron tubes for broadcast purposes.

The array must be capable of providing power for the following periods:

- 1. Produce 15,000 watts of power divided between up to six (6) different voltage and power level combinations for a period of three months while traversing from a 100 N. M. (185 Km) to a synchronous altitude orbit.

- 2. Produce 15,000 watts of power at 16,000 volts at the end of a period of five (5) years at synchronous altitude.

General requirements for the HVSA study are:

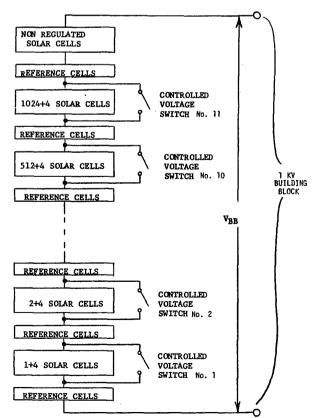

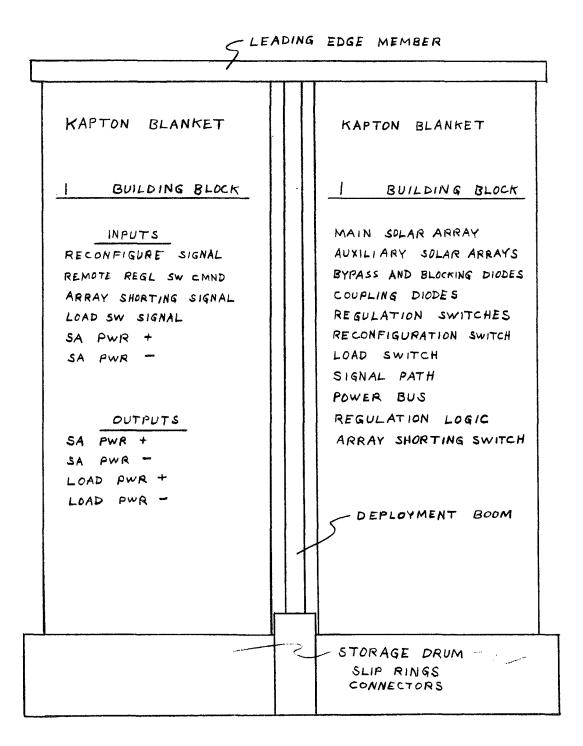

- 1. Use switchable building blocks to comprise the array configuration. A building block (BB) is defined as a combination of solar cells, power conditioning, and switches capable of (1) delivering regulated load power at an output voltage,  $V_{BB}$ , and (2) being switched in series and parallel with other BB.

- 2. Load Power Requirements 15 Kw @ 16 Kv and up to 15 Kw at several (> 6) voltages in the range from approximately 1 to 16 Kv.

- 3. Provide capability to reconfigure the solar array to any electrical series-parallel arrangement in the supply voltage range by command.

- 4. Provide floating output voltages or locate ground to obtain voltages up to + 16 Kv to ground.

- 5. Provide capability to connect and disconnect any load.

- 6. Provide automatic protection against open circuit and short circuit failures.

- 7. Regulate load voltage to  $\pm 0.1\%$  zero to full load current.

- 8. Provide voltage isolation between signal (command) circuits and high voltage circuits on the HVSA.

- 9. The array must be capable of operating with either a negative or a positive bias relative to the space plasma potential.

- 10. The array must be capable of operating in the space environment from 100 N.M. (185 Km) to synchronous altitudes.

- 11. The array's ability to perform its mission function must not be negated (except for loss of power in the earth's shadow) by operation in eclipse orbits. The HVSA must servive the eclipse and provide protection to the power electronics and loads during the eclipse transients.

- 12. The array must have adequate safeguards for personnel protection during ground handling operations.

- 13. The array should be capable of producing 66 watts/kilogram (30 watts/lb) and 108 watts/sq. meter (10 watts/ft<sup>2</sup>).

- 14. The reliability after array deployment is a 0.99 probability of design power at the end of 5 years with a 90% confidence level.

#### 3.3 GUIDELINES AND GROUND RULES

- 1. The study was to concentrate on determining the feasibility of using microelectronic packaging techniques to implement power conditioning and switching functions integral with the array substrate. Because of the requirement to consider light weight solar arrays of relatively thin substrate cross section, conventional discrete electronic components are ruled out by virtue of their large size. The results of the investigations pursued shall be applicable to most array configurations or deployment techniques.

- 2. A major goal of this study was to identify the need for new devices, such as switches. On the basis of a survey of semiconductor device manufacturers, it was assumed that high voltage (16 Kv) silicon controlled rectifiers (SCR) and high voltage (1500 volt transistors) could be developed. This assumption permitted electrical configuration studies to proceed on the basis that device characteristics were not the limiting considerations.

- 3. The HVSA building block (BB) is to possess a maximum of flexibility i.e., the capability of delivering power to the load over the widest practical range of voltage and current. The current range was from mA to amperes and the voltage range from hundreds of volts to non-integral multiples of 1 Kv, with an upper limit of 1500 volts established by semiconductor maximum voltage capability.

- 4. The technique of deployment and construction that shall be assumed for design estimates, as to weight and size, is that given in Feasibility Study 30 Watts Per Pound Roll-Up Solar Array Final Report No. 68SD4301, dated June 21, 1968, JPL Contract No. 951970 with General Electric Company, Missile and Space Division.

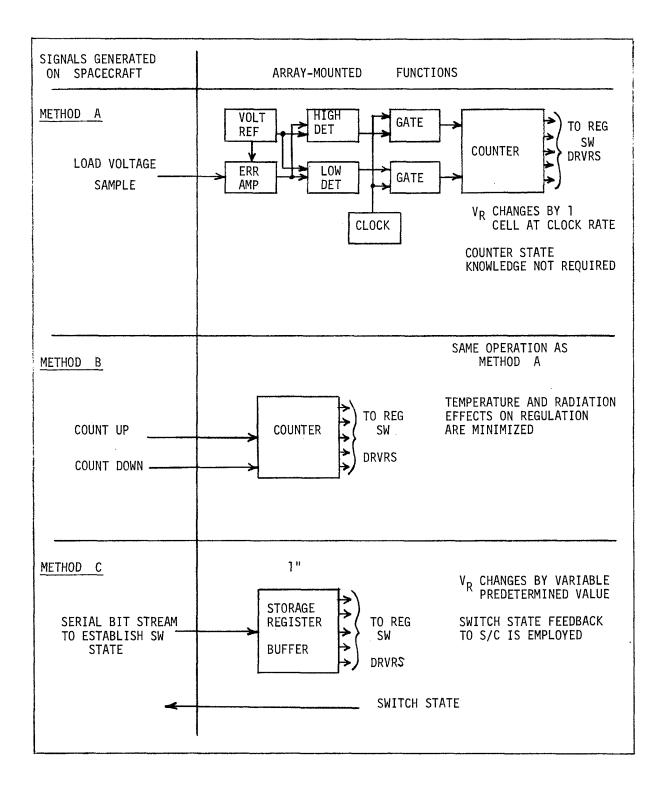

- 5. It was an early conclusion of this study that post-eclipse solar array substrate temperatures much below -55°C (+218° K) will occur at syncrhonous altitudes and that state-of-the-art voltage references cannot maintain ± 0.1% regulation over the anticipated temperature range. Therefore, a ground rule was established that the voltage reference and voltage sampling and error detection functions would be performed by a computer function on-board the spacecraft.

- 6. Additionally, a ground rule was established that power conditioning (voltage regulation) was not necessary at HVSA temperatures below -55°C (+218° K). This was important because little or no data exists for electronic device performance at temperatures below -55°C (+218° K). This ground rule did not preclude future requirements to raise or lower the "cold" array temperature at which the voltage regulation function would be initiated following spacecraft emergence from the earth's shadow.

Solar cells, power conditioning, switch functions and spacecraft loads must all survive and be protected from the potentially deleterious affects associated with eclipse orbit low temperature excursions.

- 7. Electrical configuration studies will not be based upon specific load characteristics for the ion thruster and transmitter. Array and power conditioning configurations shall provide for maximum utilization of array power for all loads at all voltage levels. Ground rules were established concerning the spacecraft loads in order to maintain the study results general in nature:

- a. Loads require no power during the HVSA warmup interval following eclipse. Therefore, regulated voltage need not be made available under "cold" array conditions.

- b. Loads may not be used to hold down array voltage during post-eclipse warmup; certain loads may be damaged by exposure to increasing supply voltages.

- c. Loads do not require power during array reconfiguration. It is therefore possible to disconnect the load(s) when in the process of array reconfiguration.

- d. Loads may not be disconnected by slowly decreasing the array voltage certain loads may be damaged when exposed to slowly decreasing supply voltages.

- 8. A major goal of this study was that requirements for new or modified devices be identified and justified. Recommendations for device development must be accompanied by justification that device development is feasible.

- 9. The preferred technique for voltage regulation uses switches to effect discrete or incremental voltage changes; however, other electrical systems concepts were to be considered.

- 10. Analyses conducted early in the study demonstrated significant (charged particle) radiation induced performance degradation of the HVSA occurred during the transfer period from parking orbit to synchronous altitude. Therefore, in order to avoid excessive array penalties which could not contribute to the study goals, this degradation mechanism was omitted. Recommendations were made for future analyses to consider various approaches to minimize the impact of radiation damage on the spacecraft and HVSA.

#### SECTION 4

#### ENVIRONMENT CONSIDERATIONS

#### 4.1 GENERAL

The hypothetical mission described in Section 3 for the HVSA includes a range of earth orbits and an environment in which many spacecraft have successfully operated. However, the long duration ascent trajectory from parking out to synchronous altitude, low thermal mass and low radiation shielding properties of the rollup solar array, and requirements for high local heat dissipation capability combine to present unique environmental challenges to the HVSA. These environmental factors have been analyzed and the results are presented in this section. A separate program, the "High Voltage Solar Array Study," is being conducted for NASA (Contracts NAS3-11534 and NAS3-11535) to consider the problems of operating a high voltage (16 kv) solar array in the space environment.

#### 4.2 HVSA ENVIRONMENT FACTORS

#### 4.2.1 THERMAL CYCLING

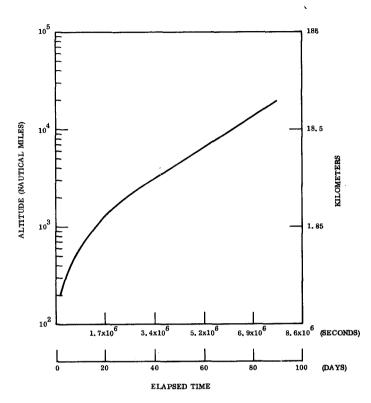

The HVSA is to operate for five years in an equatorial 24-hour synchronous orbit which is achieved by a spiraling transfer orbit from the 100 NM (185 Km) circular parking orbit to the 19,300 (35,800 Km) synchronous orbit over a period of 90 days. Assuming the vehicle is constrained to fly a very nearly circular orbit while acted upon by a nearly tangential thrust, modulated so that the thrust to mass ratio remains a constant, an equation relating spacecraft altitude with time has been developed and is presented in Section 9.1, Radia-tion Environment and Effects Predictions, and is accompanied by a plot of the altitude vs time.

An approximation of the number of thermal cycles (day-night transitions) encountered during the 90-day transition is obtained by assuming a constant altitude during a 24-hour period, computing the resulting number of passes, up-dating the value of the altitude for the succeeding 24-hour period, computing the resulting number of passes, etc. summing thte total passes as this iteration is performed 90 times. The number of thermal cycles thus computed is 585. It can be shown that the maximum error is no greater than the number of passes during the first 24-hour period (16). This number (585) assumes that the transition orbiting occurs in the earth equatorial plane with each revolution yielding an eclipse period.

Eclipse periods in the synchronous equatorial orbit are encountered when the sun declination with respect to the equatorial plane is in the range of  $\pm$  8.3 degrees, which results in 90 eclipse periods per year, or about 450 thermal cycles during the 5-year mission at synchronous altitude.

The total number of thermal cycles incurred during the ascent and synchronous orbits is computed to be approximately 1035.

The occurrance of thermal cycling is significant for several reasons:

- Experience with solar arrays has demonstrated that I-V curve degradation (softening of the knee of the I-V curve) and open circuits (associated with solar cell fractures and interconnection tab fatigue arising from repetitive working) are dependent upon (1) the number of thermal cycles,

(2) rates of array temperature change, (3) maximum illuminated temperature, and (4) the "low" or "cold" eclipse temperature. For purposes of this study, it is sufficient to identify the thermal cycling environment as a potential cause of array mechanical and performance degradation - a discussion appears in Section 10, Problems Identified.

- 2. Another aspect of the array thermal cycling environment is the impact upon power conditioning and switching. Influence of temperature transients and array "cold" temperatures are discussed in Section 5, Technical Analyses, for the switching, regulation, and array functions of the HVSA.

- 3. Section 4.2.3 presents the array temperature profile predicted for the HVSA and the bases for the resulting calculations.

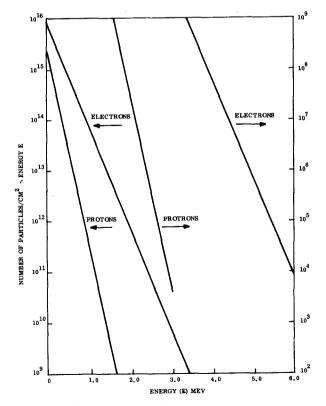

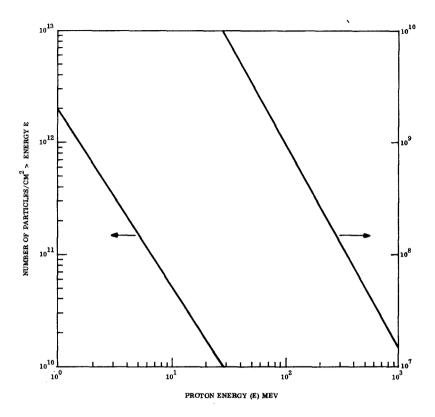

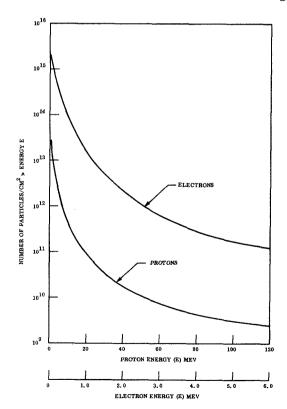

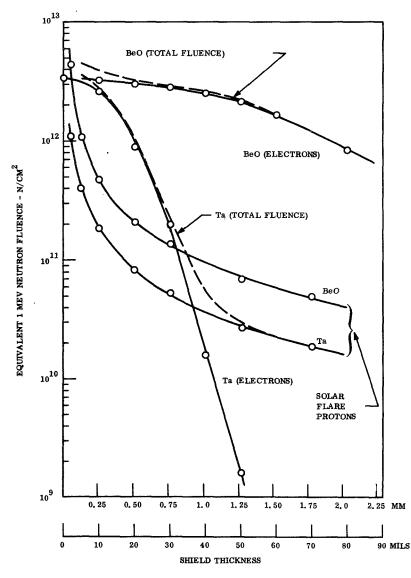

# 4.2.2 CHARGED PARTICLE ENVIRONMENT

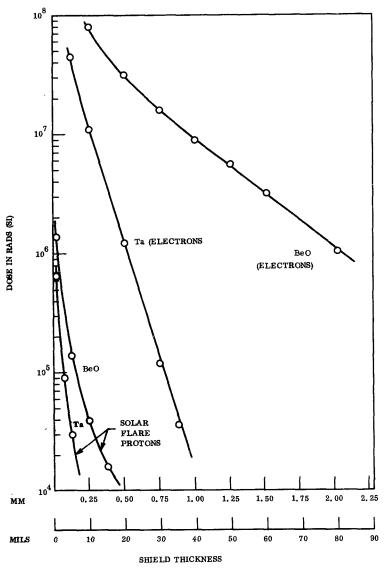

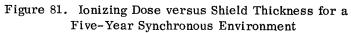

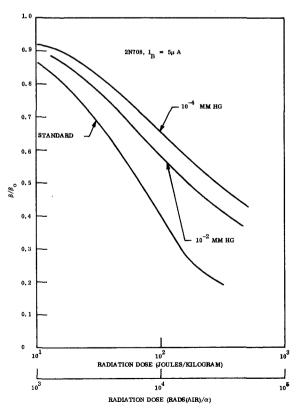

An estimate of the electron and proton fluxes in the transition and synchronous orbits and the protons in a solar flare model is presented in Section 9.1, Radiation Environment and Effects Predictions. Radiation damage investigations reported in Section 5.3 show an intolerably large amount of solar cell power degradation caused by the ascent orbits passing through the dense regions of the Van Allen Belts. In order to proceed further in this study, it was assumed that this transition damage is protected against (perhaps by heavier solar cell shielding than that provided by the referenced rollup solar array, (see Section 3) by altering the flight path to synchronous altitude, or by deploying only that portion of the total array needed to power the ion thrustor.

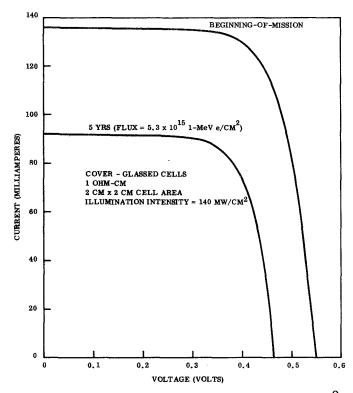

The solar flare model produces about four times as much damage-equivalent, normally-incident 1-MeV electron flux as the synchronous trapped electrons and protons, such that about 28 percent solar cell power loss is predicted for five years if no flare is considered, and about 41 percent power loss if the solar flare flux is included in the damage assessment.

A possible enhancement to mission performance is the concept of retracting the rollup solar array in advance when a severe solar flare is expected. The referenced rollup array design readily accommodates this feature, requiring approximately 20 watts for less than 5 minutes per 250 ft<sup>2</sup> array section to perform the deployment or retraction operation. It is noted that intense flare activity can be present in the synchronous orbit for periods of time up to one or two days in duration, indicating the need for electrical energy storage to maintain spacecraft orientation and to allow access to ground commands as well as to re-deploy the rollup array sections.

The impact of the charged particle environment upon semiconductor device performance and array design is significant and is discussed at length in Section 9.1, Radiation Environment and Effects Prediction.

Sizing of the solar array for the HVSA systems considered in this study is based upon solar cell radiation damage due to the trapped particles at synchronous altitude and the predicted solar flare particles.

#### 4.2.3 SOLAR ARRAY TEMPERATURE-TIME PROFILES

An estimate of the temperature versus time relationship for the HVSA was made for the 100 NM (185 Km) parking orbit and for the 19,300 NM (35,800 Km) synchronous orbit because these altitude extremes represent conditions which cause the highest and lowest array temperatures in the hypothetical mission established for this study.

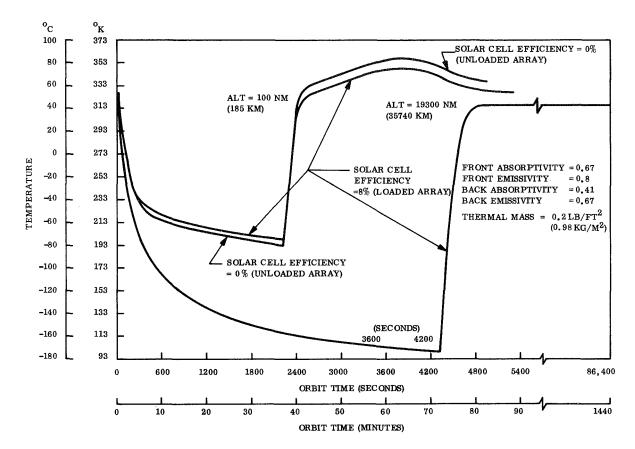

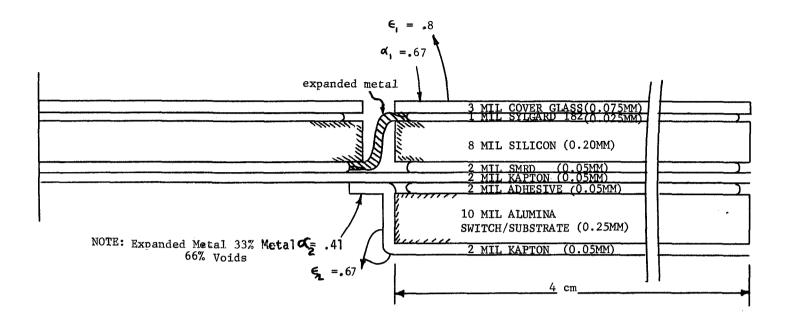

It was assumed that the solar array is maintained perpendicular to the earth-sun line during the entire orbit. Array thermal mass is  $0.2 \text{ lbs/ft}^{2*}$  ( $0.98 \text{ Kg/m}^2$ ), with a specific heat of  $380 \text{ W-sec/lb}^{-0}\text{K}$ . Values of illuminated side absorptivity and emissivity of 0.67 and 0.8, respectively, were used with back side (Kapton) average values of 0.41 and 0.67 for absorptivity and emissivity. Heat transfer by radiation only was considered. A typical solar cell conversion efficiency of 8% was used for the temperature calculations of a normally loaded array and 0% for an unloaded array. The latter case defines the maximum array temperature used for heat sink area and semiconductor device temperature calculations (Section 4.2.4).

Figure 1 presents the temperature vs time profiles for the solar array for the two extreme orbits. The synchronous altitude profile is negligibly influenced by albedo and ranges from a low temperature of about  $-173^{\circ}$ C (100°K) to a steady-state high temperature of about  $+43^{\circ}$ C ( $+316^{\circ}$ K). The significant albedo influence in the 100 NM (185 Km) orbit produces about a 20°C (20°K) increase in temperature when the array is above the subsolar point, which disappears as the array moves behind the earth terminator. Infrared radiation from the earth surface limits the cold temperature extreme in the low-altitude orbit to about  $-80^{\circ}$ C (193°K) at the end of the eclipsed portion of the orbit. A high temperature of about  $+83^{\circ}$ C (356°K) is predicted for the 100 NM (185 Km) orbit, unloaded (efficiency = 0) solar array.

<sup>\*</sup>Value based upon characteristics of the referenced Rollup Array.

Based on available information, the expected cold temperature of  $-173^{\circ}C$  (100<sup>°</sup>K) is beyond the range for which a rollup solar array has been qualified.

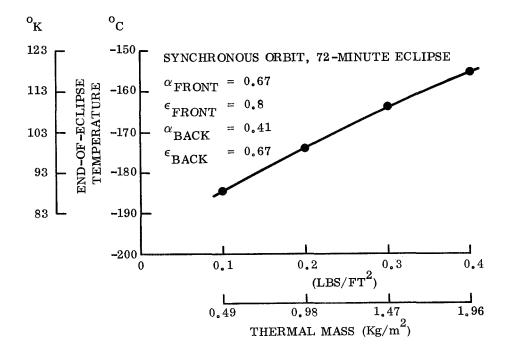

End-of-Eclipse temperatures have been calculated to demonstrate the impact of thermal mass and Kapton emissivity ( $\epsilon$ ) variations. Figure 2 relates end-of-eclipse temperature to thermal mass and shows a 10<sup>o</sup>C (10<sup>o</sup>K) increase in temperature for each 0.1 pound/foot<sup>2</sup> (0.49 KG/m<sup>2</sup>) increase in mass. Since the mass of the referenced rollup array blanket assembly is 0.2 pounds/foot<sup>2</sup> (0.98 Kg/M<sup>2</sup>) the penalty for increasing eclipse temperature by only 10<sup>o</sup>C (10<sup>o</sup>K) from -174<sup>o</sup>C (+99<sup>o</sup>K) to -164<sup>o</sup>C (+109<sup>o</sup>K) is 50% in blanket weight and 30% total array weight. Thermal mass changes do not affect steady-state high temperature (and array power output).

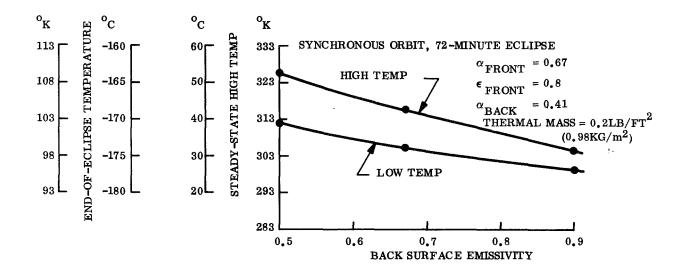

The wide variations reported for kapton  $\epsilon^*$  have prompted the need for the curves in Figure 3. Steady state (illuminated) and end-of-eclipse temperature are both affected by kapton  $\epsilon$  variations but to differing degrees. Decreasing Kapton  $\epsilon$  from a value of 0.67 to 0.5 increases "LOW TEMP" by only 3.5°C (3.5°K) and "HIGH TEMP" by 10°C (10°K) resulting in a 5% array power loss. This is a severe power penalty for a relatively small increase in eclipse temperature. The same increase in temperature can also be achieved by increasing thermal mass to ~ 0.235 pounds/ft<sup>2</sup> (1.15 Kg/M<sup>2</sup>) which increases array blanket weight by 17%.

The conclusion is that increasing mass or reducing kapton  $\epsilon$  to raise the eclipse temperature results in small temperature improvements with large penalties in weight and area. Therefore, future array thermal cycling qualification criteria will be insignificantly affected if temperature limits are based on minimum weight and area designs. Furthermore, measurements are required to provide considerably more statistical confidence in Kapton  $\epsilon$  since  $\epsilon$  variations affect array power sig ificantly.

Array sizing and performance estimates presented in Section 7, System Performance Estimates, are based upon a steady-state synchronous altitude orbit temperature of  $+43^{\circ}C$  ( $+316^{\circ}K$ ). Further discussion appears in Section 5.3, Solar Cells and Array.

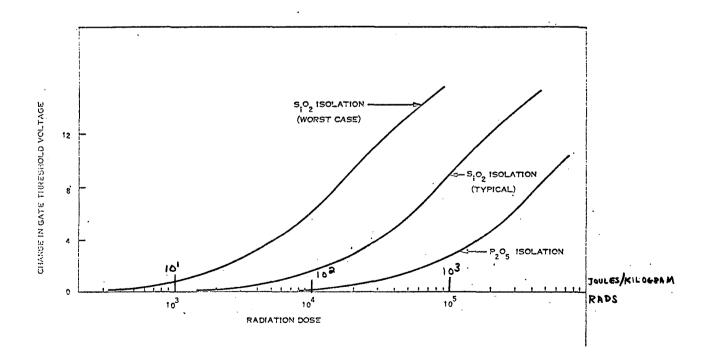

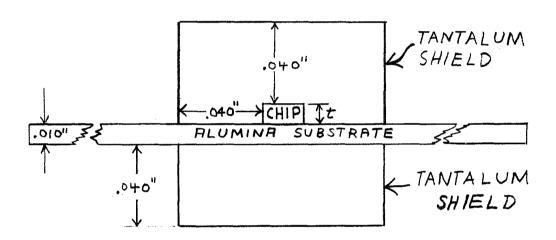

#### 4.2.4 TEMPERATURE OF MICROELECTRONIC SWITCHES

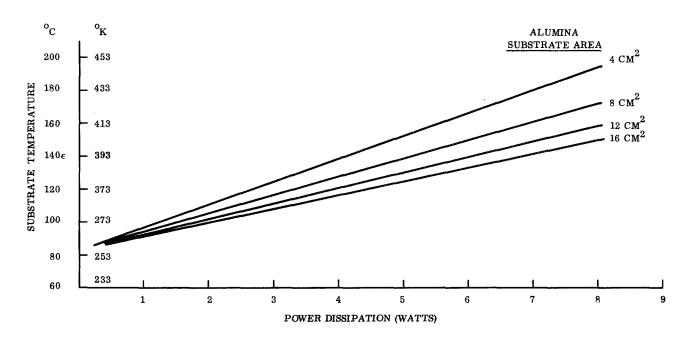

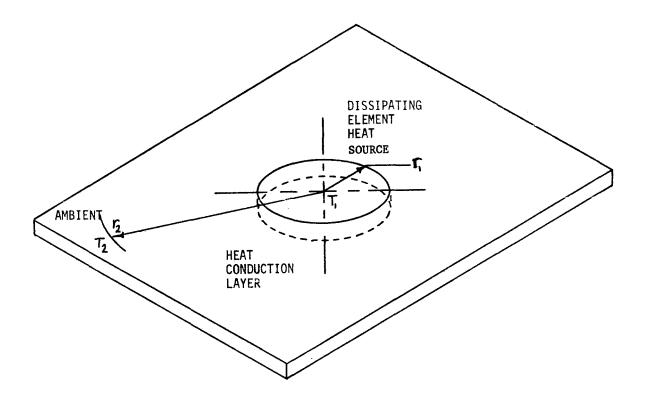

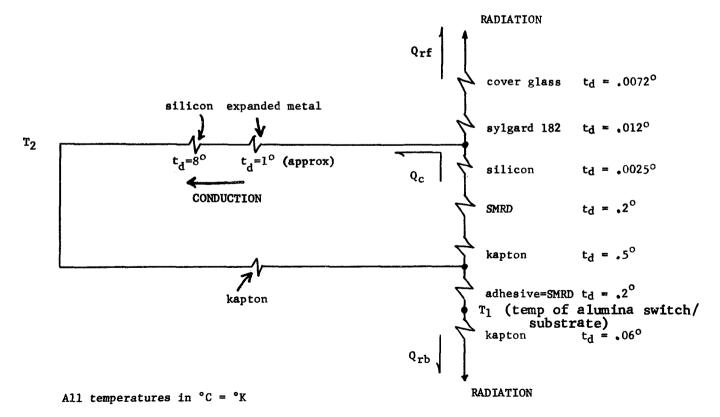

It has been shown in Section 4.2.3 that the temperature of the rollup solar array can be as high as  $+83^{\circ}$ C (356<sup>o</sup>K) with incident solar energy, albedo and earth "blackbody" radiation as the only heat inputs. Power dissipation in the regulation switches and the inter-building block switches will increase the array temperature locally to values greater than shown in the array temperature-time profiles. A worst-case thermal analysis was performed to estimate the maximum operating temperature of a semiconductor chip (switch) bonded to an alumina substrate, which in turn is bonded to the back side of the kapton array blanket with epoxy adhesive. It is assumed for this analysis that conduction between the actual semiconductor switch and its alumina substrate is ideal, i.e., they represent an isothermal mass. The choice of alumina as a microcircuit substrate has not been finalized, but it does appear as a representative candidate.

Appendix A presents the details of the thermal analysis. Starting with the rollup array and micro-circuit substrate, a much simpler but thermally equivalent model is developed. Iterative solution of conduction equation and a radiation equation yields the steady-state temperature for the microcircuit substrate, which is conservative (higher than actual) because of the worst-case assumptions made in the development of the thermal model.

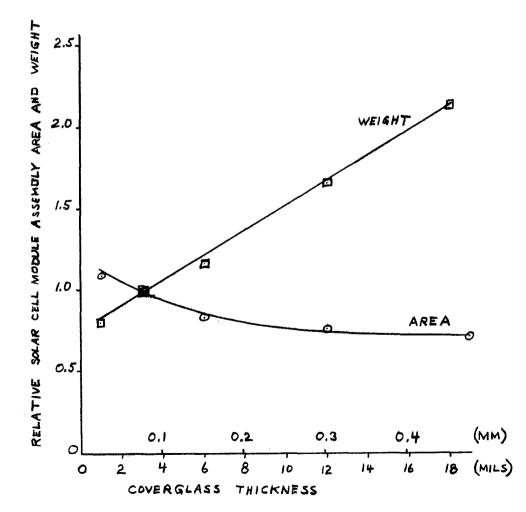

This method has been mechanized, and a computer program used to determine temperatures for semiconductor substrates dissipating from 1 to 8 watts, with substrate areas of 4, 8, 12 and 16 cm<sup>2</sup>. The results are plotted in Figure 4. The worst-case assumption of an array temperature of  $+83^{\circ}C = +356^{\circ}K$  (equator crossing at 100 NM (185 Km) altitude with maximum solar intensity) was employed to emphasize the possible high-temperature conditions. Values of power dissipated in the various semiconductor devices employed in the HVSA design are presented in Section 5. 1. 11.

<sup>\*</sup>Emissivity values in the literature range from 0.65 to 0.89; an average value of 0.67 has been determined for this study.

The thermal model incorporated in the temperature calculation process is inadequate to analyze the effect of the very high SCR power dissipation (16 to 80 watts). A possible approach to reducing the dissipation in the SCR conducting mode (80 W for an 8A load) might be to employ several parallel devices for this purpose. However, the load sharing problem with parallel SCR's is apparently very complex. It is also noted that, even with parallel SCR's, the power dissipation due to leakage when blocking high voltage is not reduced for each SCR, and in fact may be even greater than the dissipation in the conducting state, since vendors have indicated that leakage currents as high as 20 mA may occur when blocking 16 Kv.

#### 4.2.5 ULTRAVIOLET RADIATION ENVIRONMENT

UV radiation has been reported (Reference 1) to cause some degradation in solar array power output. While of significance to the array designer this factor is not significant to the subject study.

#### 4.3 SUMMARY

The HVSA environment, in sufficient detail to quantitatively assess the most significant effects, has been defined. Reference is made to other sections of this report where the effect of the environment is considered. Temperature cycling, charged particle radiation, and the thermal environments are considered as significant environmental factors.

Figure 1. HVSA Temperature versus Time Profiles

Figure 2. Effect of HVSA Thermal Mass on Temperature

Figure 3. Effect of Back Surface Emissivity on HVSA Temperature

Figure 4. Microelectronic Substrate Temperature versus Power Dissipation and Substrate Area

#### SECTION 5

#### TECHNICAL ANALYSES

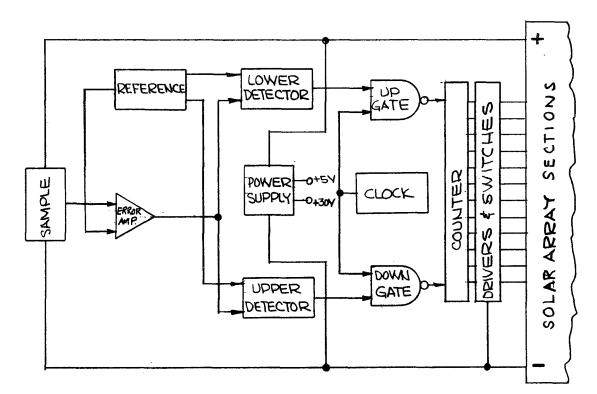

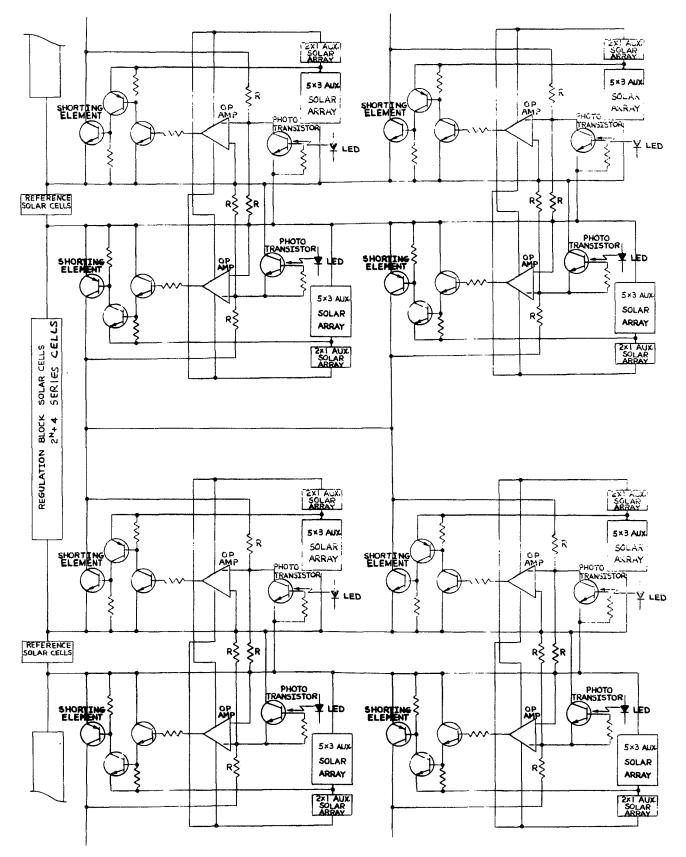

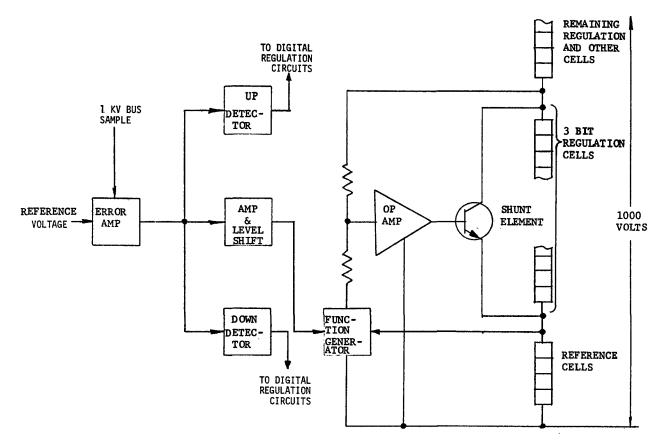

This section provides detailed discussion of switching, solar array, power conditioning and various system tradeoff considerations. Development of a recommended system switching configuration is presented, and alternate approaches to regulation by discrete switching are described. Circuit schematics for the various switching and regulation functions are introduced and the spacecraft/solar array signal interface is defined for a selected method of system regulation. Comparison of alternate power system block diagrams and solar cell connection arrangements is made. The impact of a wide range of building block voltage and current capability on total system sizing is discussed, resulting in definition of a general building block design criterion.

#### 5.1 SWITCHING FUNCTIONS

#### 5.1.1 GENERAL

The requirement to perform many and varied switching functions is fundamental to the concept of a HVSA. Switching is necessary to rearrange building blocks in alternate series-parallel system configurations, connect and disconnect loads from their power sources, establish the voltage reference point, provide protection for the loads and power source and to implement the discrete voltage change technique of load voltage regulation. Regulation switching is discussed in Section 5.2; this section presents considerations of the remaining switching functions.

A definition of each switching function is made here, and will apply to the use of these terms throughout this report.

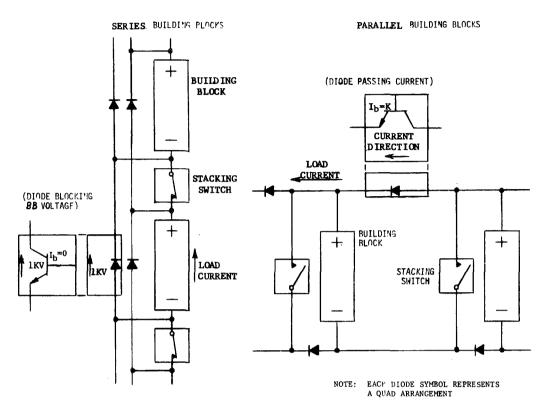

- 1. <u>Stacking Switch</u> Connects a building block electrically in series with another building block when in the "ON" (closed) state.

- 2. <u>Coupling Diodes</u> Connect the positive and negative terminals of a building block electrically in parallel with the respective output terminals of another building block when the stacking switch between the two blocks is in the "OFF" (open) state.

- 3. <u>Array Shorting Switch Short-circuits the entire output-power-generating solar cell complement of</u> an individual building block when in the "ON" (closed) state.

- 4. <u>Load Switch Connects the regulated solar array output to the "hot" terminal of an individual load,</u> permitting load current, when in the "ON" (closed) state.

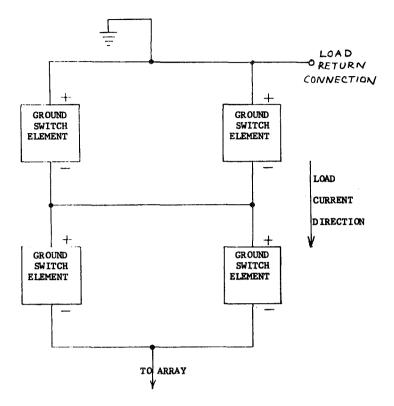

- 5. Load Return/Array Ground Switch Connects the spacecraft ground, or reference, point and/or the common load return to the solar array when in the "ON" (closed) state.

Each of the above switch functions can be maintained in either the "ON" or "OFF" mode for steady-state operation; blocking diodes are automatically reverse-biased (OFF) when the associated stacking switch is ON. Operation of any switch function is independent of other switches, although a particular switching sequence may be necessary or preferred. Signals governing operation of the switch functions are received from the spacecraft via high voltage signal couplers (see Section 5.2); signals may originate from ground commands or from on-board spacecraft logic functions.

Effort during this study has been directed toward the use of array substrate-mounted microelectronic components, which has precluded the investigation of more conventional, bulky components, such as packaged relays for switching functions. However, the question of the feasibility of a high-voltage semi-conductor load switch remains, and a severe design problem exists in providing adequate heat sink capability on the array for such a device. Future effort to include feasibility determination of a high voltage semiconductor switch and development of a high voltage relay for the load switching function is recommended in Section 11.

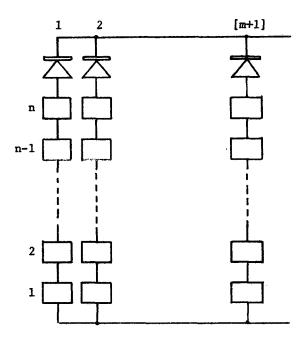

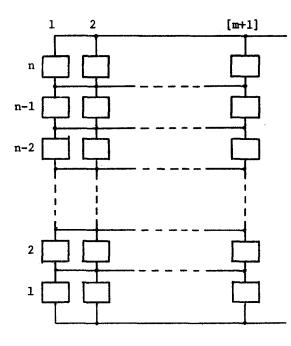

#### 5.1.2 GENERAL CASE SYSTEM SWITCHING CONFIGURATIONS

The goals to be attempted when selecting a general purpose switching configuration for a HVSA system are:

- 1. Compatiblity with the electrical requirements established in Section 3.

- 2. Flexibility in structuring the building block series-parallel arrangements.

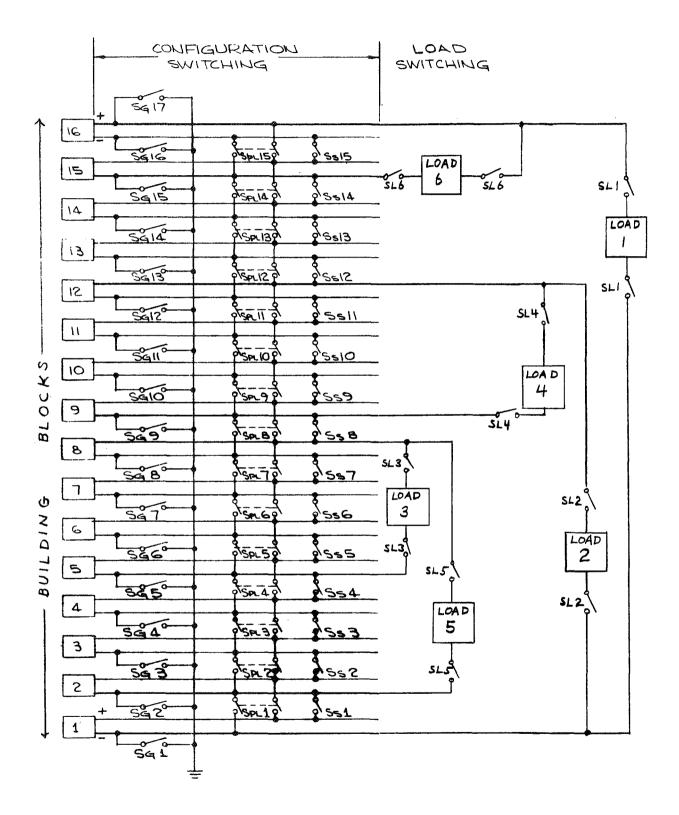

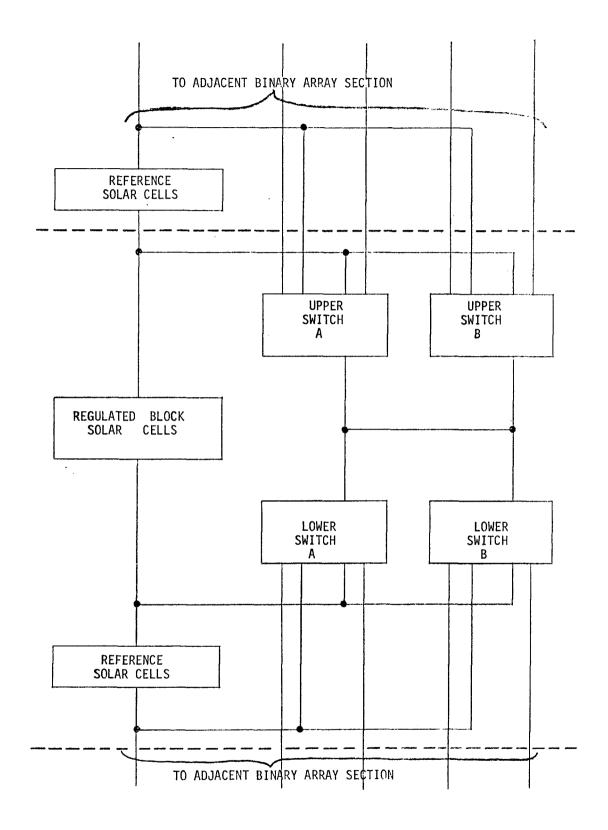

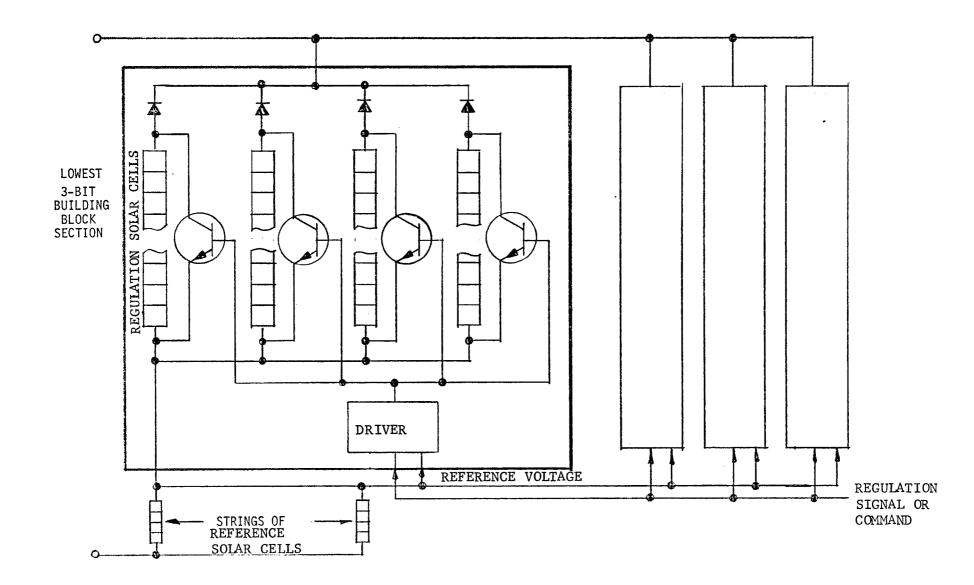

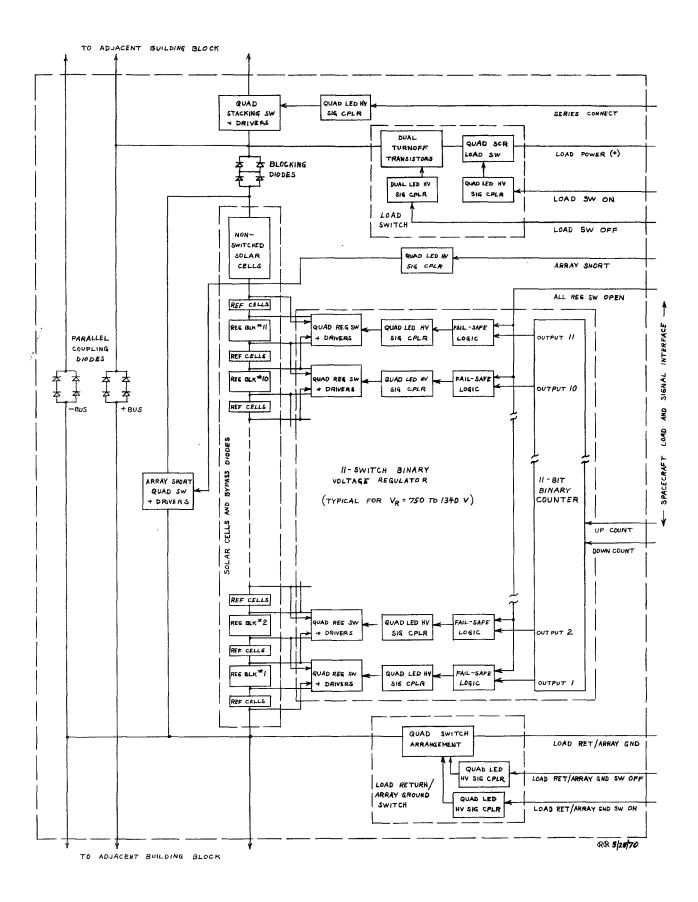

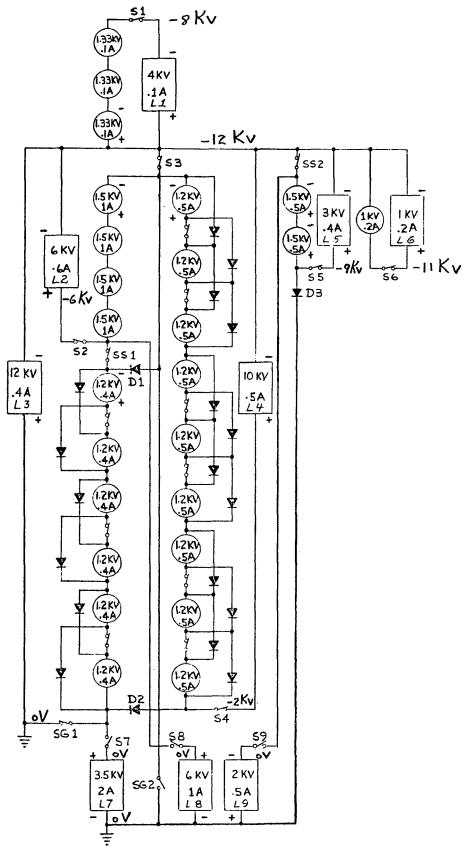

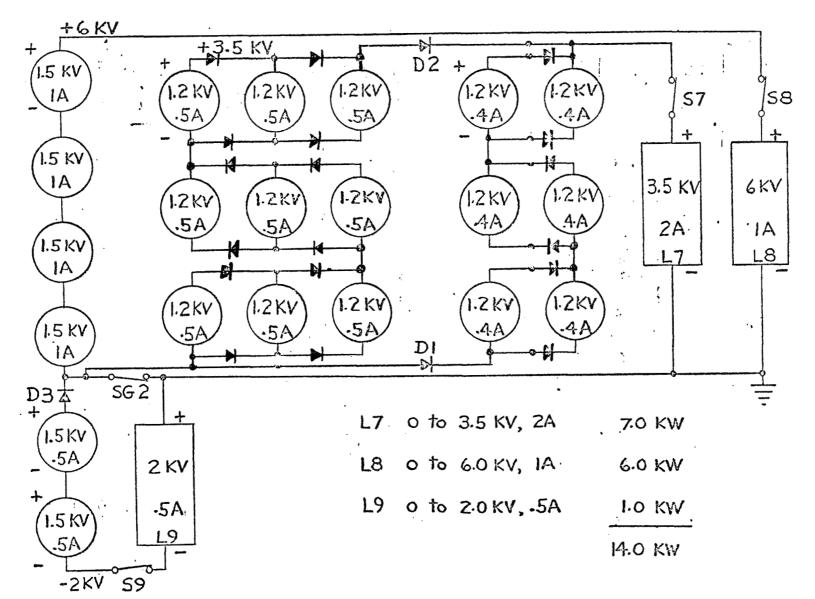

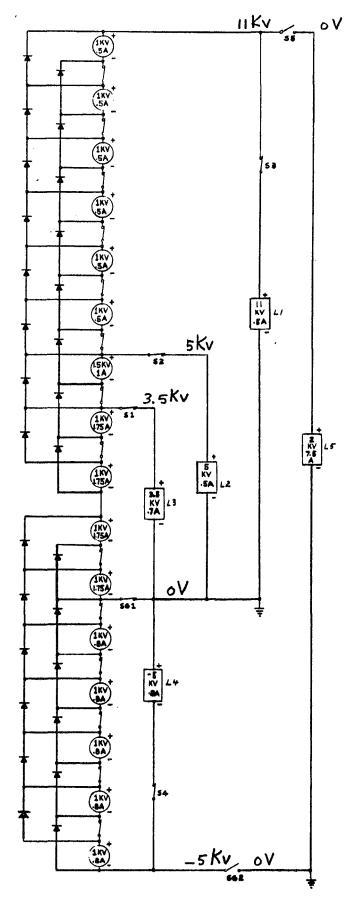

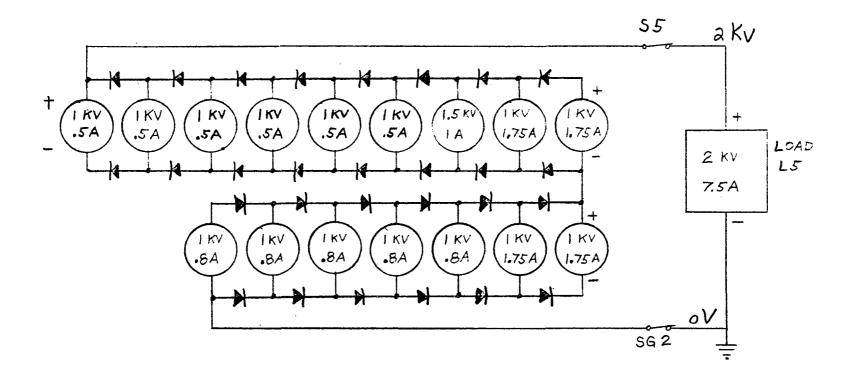

A switchable block concept that would fulfill these requirements is shown in Figure 5. The system is arbitrarily powered by 16 1Kv building blocks and is supplying 6 different loads having various current and voltage requirements. There are 15 switches for connecting the 16 array building blocks in series,  $S_{\rm S1}$ - $S_{\rm S15}$ , and 15 switches for paralleling the blocks,  $S_{\rm PL1}$ - $S_{\rm PL15}$ . With this switch arrangement, a group of one to 16 blocks can be connected in series or parallel or a combination of both, independent and isolated from those blocks which were not switched. This scheme does not allow arbitrary placement of a block in parallel with or in series with any other block, but does permit all combinations of electrical series/parallel arrangements possible with 16 blocks. The scheme also provides 17 switches,  $S_{\rm G1}$ - $S_{\rm G17}$ , for "grounding" the array at any point. The loads are connected at whatever electrical output tap represents the correct voltage for the loads.

The paralleling switches for this scheme require two poles, and therefore would be realized by two solid state switches. Thus a total of 62 switch functions are required to meet the most general electrical requirements established as a starting point for the switching concept developments, not including load switching.

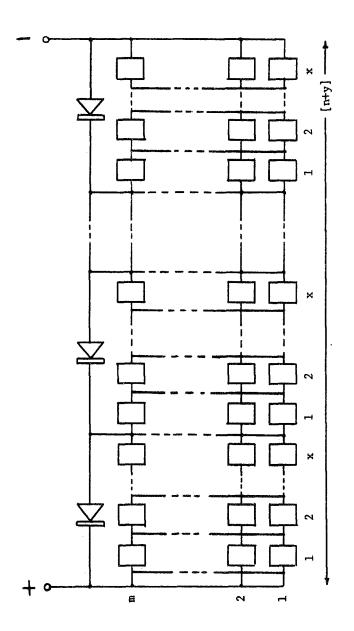

A considerable simplification in the number of switches and in command requirements can be realized by eliminating the electrical isolation requirement on the array switching configuration. All electrical series/ parallel combinations of 1-Kv building blocks are still available, but loads will be at some definite potential with respect to all other loads and the ground connection. The electrical position of the ground in the 16 Kv range is still arbitrary with this simpler switching arrangement. The switches in Figure 5 which were used to connect the building blocks electrically in parallel ( $S_{PL1}$ - $S_{PL15}$ ) are essentially replaced by diodes in the simplified configuration, which is presented in Figure 6.

In Figure 6, there are 15 switches controlling the series parallel arrangement, and 17 switches to select the arbitrary ground point, totaling 32 switches for this configuration (excluding load switches). The ground point could be determined merely by the loads being connected; that is, the return for the ground referenced load is connected to the array, and hence determines the array ground point if that return is grounded at the load. This would reduce the array configuration switching to 15 switches, each of which need only sustain the open circuit voltage of one building block.

The load switches SL1-SL6 in Figure 5 provide for a connect/disconnect function at each terminal of the individual load. Economy of load switching can be achieved by using a common switch in the return paths of several loads and also by allowing this switch to establish the array ground point. Examples of the significant reduction in the number of stacking, ground and load switches that can be achieved when optimizing the general switching provisions of Figure 5 for a specific system design are discussed in Section 6. In Section 6, two representative HVSA systems are optimized for the purpose of providing a base for performance estimates.

## 5.1.3 SWITCH VOLTAGE AND CURRENT REQUIREMENTS

The maximum voltage that a switch must block when in the open state, the polarity of the blocking voltage, and the maximum current that must be accommodated with the switch in the closed state are of course determined by the specific system design requirements. Representative requirements applied to this study are (1) load switch blocking voltages up to 16 Kv, either plus or minus, since the ground point can be located at any tap point on the string of building blocks comprising the system, and (2) maximum steady-state switch current of 7.5 amperes, since up to 15 Kw must be supplied at voltages in the range of 2Kv to 16 Kv. Determination of the maximum current and blocking voltage capability required of the various switch functions is discussed below.

- 1. <u>Stacking Switch</u> This switch is employed between two building blocks which are either in series (when the stacking switch is closed) or in parallel (when the stacking switch is open and coupling diodes parallel the two blocks). As a result, the stacking switch need only block the output voltage of the building block. If the paralleled blocks are of unequal design voltages, the switch must accommodate the higher of the two voltages. The highest current in a stacking switch would occur in a minimum voltage, full power system configuration (7.5A at 2 Kv in this study). As seen in Figure 6, the top 8 building blocks would be paralleled with coupling diodes, the bottom 8 building blocks would also be paralleled with coupling diodes, and the series connection between the two 1 Kv, 7.5A building block arrangements would be made by stacking switch SS8, which must pass the maximum 7.5A.

- 2. <u>Coupling Diodes</u> When a stacking switch between two building blocks is closed, the coupling diodes are reverse biased by the building block voltage, which is the maximum voltage that they must accommodate. With several or more building blocks paralleled by coupling diodes to provide sufficient load current, the maximum current through any one coupling diode will approach the value of load current, since the output current of the parallel block to which the load is connected does not pass through a coupling diode.

- 3. <u>Array Shorting Switch</u> This switch must be capable of blocking the output voltage of the building block to which it is connected. The maximum current through this switch is the short-circuit current of the solar array associated with the single building block.

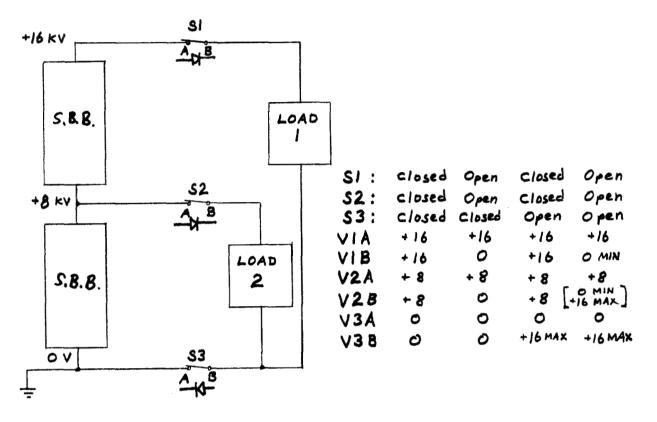

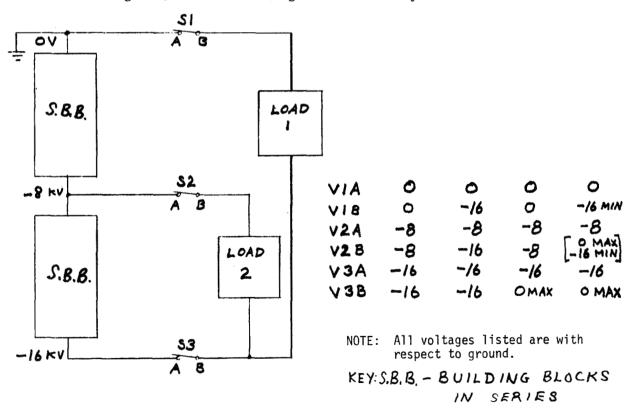

- 4. Load Switch In the high voltage solar array configuration, the switches that must accommodate the greatest voltage difference across its terminals in the "open" condition are the load switches. The sum of the voltages which must be blocked in the forward plus the reverse directions never exceeds 16 Kv, as can be seen in Figure 7 and 8. Figure 7 shows a particular arrangement with the solar array grounded at the bottom of the lowest voltage building block, thereby supplying only positive voltages from the array to whatever loads may be connected. Switch S1 connects Load 1 to the +16 Kv potential, S2 connects Load 2 to the +8 Kv potential, and S3 provides the return path from the loads to the OV, or ground, potential. The table of load switch voltages in Figure 7 lists the range of possible voltages that can be obtained across the terminals of each switch for the given ground point of connection. It is seen that S1 must block +16 Kv at terminal A with respect to terminal B; S3 must block +16 Kv at terminal B with respect to terminal A; and switch S2 must block up to +8 Kv at terminal A with respect to B, or up to +8 Kv at terminal B with respect to terminal A.

Figure 8 illustrates a situation where the ground connection is made at the opposite end of the array from that shown in Figure 7, thereby providing only negative voltages to the system. As can be seen from the table of load switch voltages in Figure 8, each switch (S1, S2 and S3) still must block the <u>same</u> voltages at one terminal with respect to the other terminal. Thus, any given load switch must be able to block either +16 Kv in one direction and OV in the other, or +15 Kv in one direction and only +1 Kv in the other, or +8 Kv in one direction and +8 Kv in the other, etc., but never more than a combined sum of forward and reverse blocking voltages of 16 Kv.

Figure 7 shows a diode representation of forward-biased, "closed" SCR load switches; in the case shown, the loads are obviously powered by positive voltages only. Note that with the array grounded at either end, switches 1 and 3 must be able to block 16 Kv in the forward direction only; there is no requirement to block voltages in the reverse direction at these two switch locations. Switch 2, however, must be able to block 8 Kv in the reverse direction also. Table 1 shows the value of forward blocking voltage and the corresponding value of reverse blocking voltage the SCR load switch must be capable of blocking, depending on where in the array the load connection is made.

The conclusion to be drawn from the preceding discussion is that if a single, general-purpose load switch device were to be developed to accommodate all load point connections, it must be capable of blocking 16 Kv in the forward direction and 16 Kv in the reverse direction. If this development were not feasible, however, two devices could be used to accomplish all the desired load switching. One device must block 16 Kv in the forward direction and 8 Kv in the reverse direction, while the second device must block 8 Kv in the forward direction and 16 Kv in the reverse direction.

The maximum load current that a load switch must pass is 7.5A for the ground rules imposed on this study.

5. Load Return/Array Ground Switch - The maximum forward and reverse blocking voltages and maximum current that the load return and/or solar array ground switch must accommodate are identical to those for the "hot" side load switch: 16 Kv and 7.5A. Additionally, this switch must be able to function as a switch in the closed state with no current through it from the source or load, as described further in Section 5.1.9.

#### 5.1.4 BUILDING BLOCK COUPLING DIODES

Connection of building blocks in a parallel electrical arrangement is required when reconfiguring the HVSA system to supply load currents which exceed the current capability of a single building block. Figure 5 presented a switching diagram showing that a double-pole, single throw switch function is needed to place a block in parallel with the block below it. A subsequent switch diagram (Figure 6) showed the replace-ment of each switch with two diodes to accomplish the paralleling function.

The electrical requirements on the coupling device to perform the parallel building block connection function are, basically, that it must be capable of blocking the maximum building block output voltage when the blocks are connected in series, and must be capable of passing the maximum load current required from the parallel building block connection (almost 8 amperes).

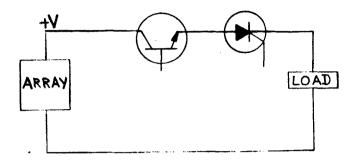

A transistor switch was considered as an alternate to the use of a diode for the coupling device. In the 8A coupling device application, a quad transistor switch would require about 1100 2 x 2 cm solar cells for operation, including drive power and cells necessary to overcome the series voltage drop. The use of a quad diode arrangement requires only 84 extra cells in a typical 1 Kw building block to overcome the series voltage drop. Additionally, drive circuitry and a command function would be required for the transistor switch. Figure 9 shows the application of both a diode and a transistor for the parallel block coupling function. The requirement for one emitter connection in the coupling device blocking mode and the opposite emitter connection in the paralleling mode show that the transistor cannot perform both functions. The simplicity and minimum power loss associated with use of the diode for this function, plus the conclusion that a transistor cannot function in the required two modes of operation, result in the specification of a diode (or quad diode arrangement) to perform the parallel building block connection function.

#### 5.1.5 SERIES AND PARALLEL CONNECTION OF BUILDING BLOCKS

The semiconductor devices employed as switches and coupling devices introduce small voltage drops in the HVSA system configurations which must be accounted for a sizing the required solar array area.

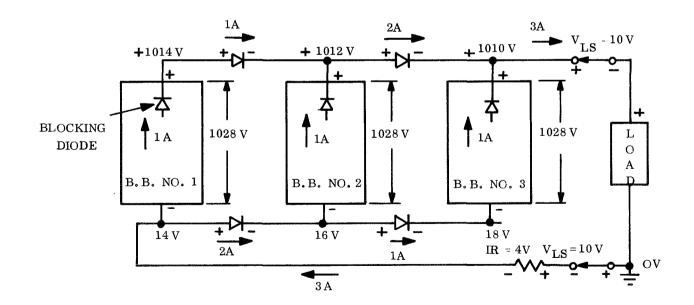

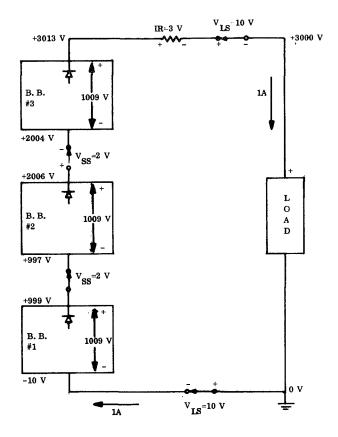

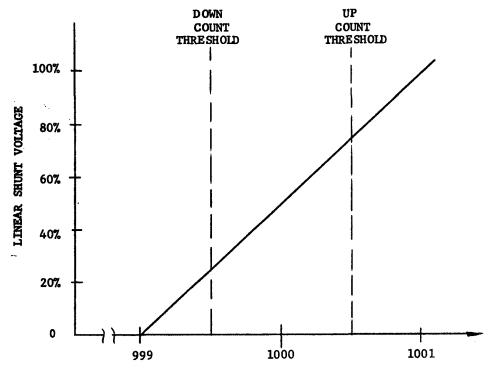

Figure 10 presents a functional diagram of a portion of the switchable system showing parallel connection of 3 building blocks to supply a load. An arbitrary building block voltage and current of about 1 Kv and 1A have been selected for an example. The components contributing to significant voltage losses between the building blocks and the load are seen to be the load switches, a lumped "IR" loss, coupling diode losses, and blocking diode losses. Each building block will supply the same magnitude of voltage, but the voltage of each block is at a slightly different reference value. This effect is not detrimental, and is rather easily overcome by the system regulation logic scheme proposed in Section 5.2 of this report, which regulates by sensing voltage at the load.

Figure 11 shows a comparable diagram for a load supplied by a series connection of three building blocks. In this figure, the voltage drops are due to the load switches, stacking switches, lumped IR losses, and blocking diodes. As with the parallel connection of building blocks, each block operates at the same voltage magnitude but with each having a different reference point. The selected "up-down" regulation scheme readily accommodates this type of building block configuration, also. A more detailed description of the voltage and power losses associated with each switching function is included in Section 5.1.11.

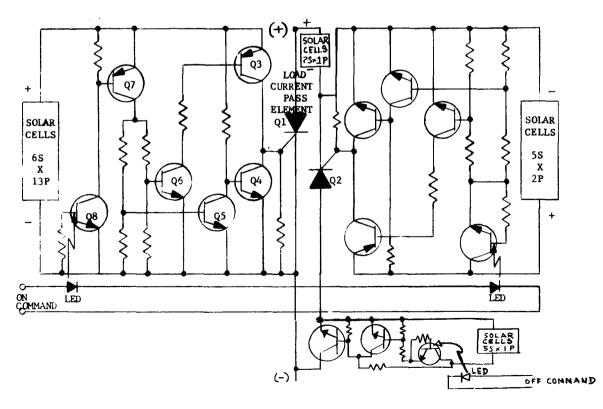

#### 5.1.6 STACKING SWITCH

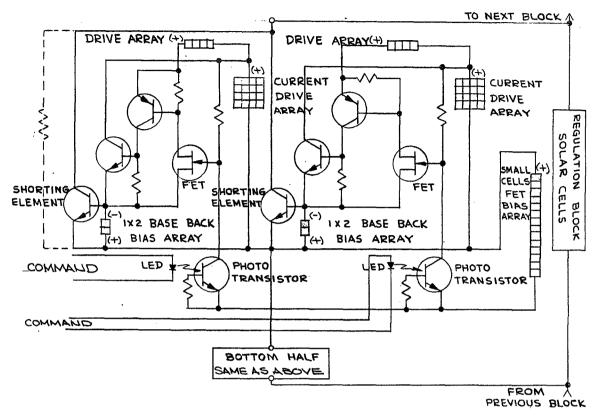

Stacking switch current requirements for building block arrangements considered during this study range from less than 1 to almost 8 amperes. The difference in design of a 1 and 8 amp switch is in the number of driver stages and number of solar cells required for drive power. The reliability goal for the HVSA requires the use of a "quad H" arrangement of switch elements to ensure protection against failure.

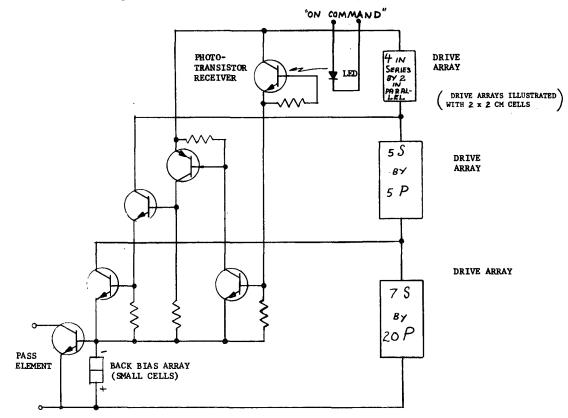

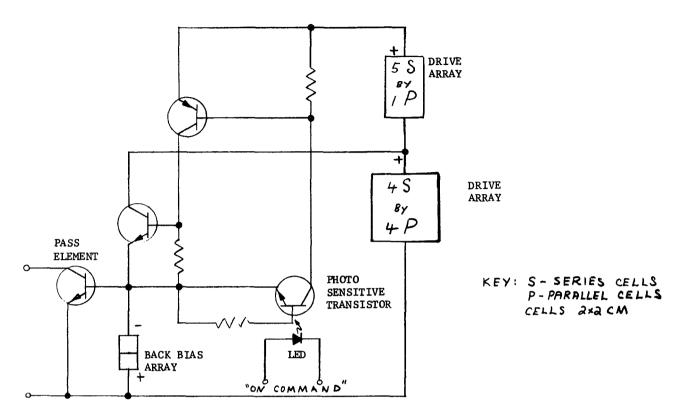

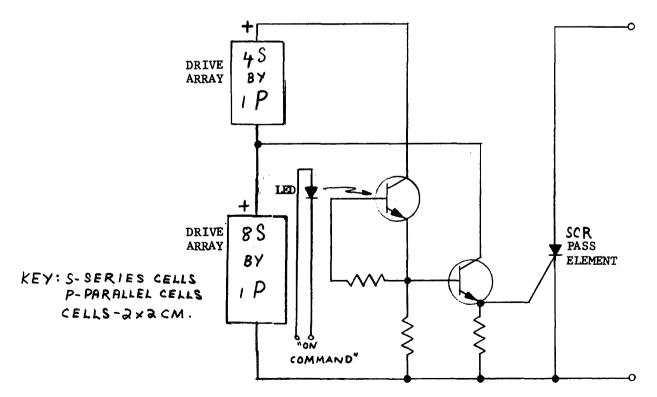

Figure 12 presents a schematic diagram for one of the four elements of a quad 8-amp stacking switch. The base of the high voltage transistor is back biased by 1 x 2 cm cells and four switches are used in a quad arrangement. A conventional transistor arrangement is used here because it is most desirable for this switch to be normally "OFF", that is, requiring a positive signal to close the switch and thereby connect building blocks in series. An FET-type receiver may be required, however, depending upon the current capability of the LED/Photo transistor combination which is used as the high voltage signal coupler for the switch "ON" command from the spacecraft.

From investigation of typical power transistor parameters, a gain of 3 to 5 provides minimum power dissipation between the sum of  $V_{ce \ sat} X$  pass current and base drive power. Accordingly, the stacking switch designs shown provide a base drive of greater than 1.6 amps for the 8 amp stacking switch.

Figure 13 presents a schematic diagram for one element of a 1-amp quad stacking switch arrangement.

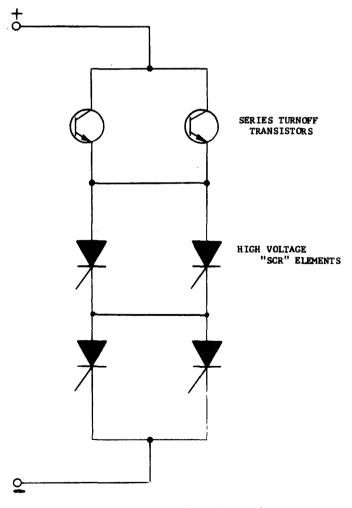

A possible SCR switch for stacking is shown in Figure 14. The SCR stacking switch requires less auxiliary array for drive current, but will require more array in the power path due to its higher voltage drop. Another significant problem with the SCR stacking switch is turn-off. It seems quite unlikely that capacitive or inductive commutation circuits could be put on the array for stacking switch SCR turn-off, hence array shorting will have to be used to turn off the stacking SCR by reducing its forward voltage to zero.

The problem of possible SCR turn-on due to dv/dt from regulation or load transients exists, which might result in operational difficulty when building blocks are paralleled and the stacking switch is in the open state.

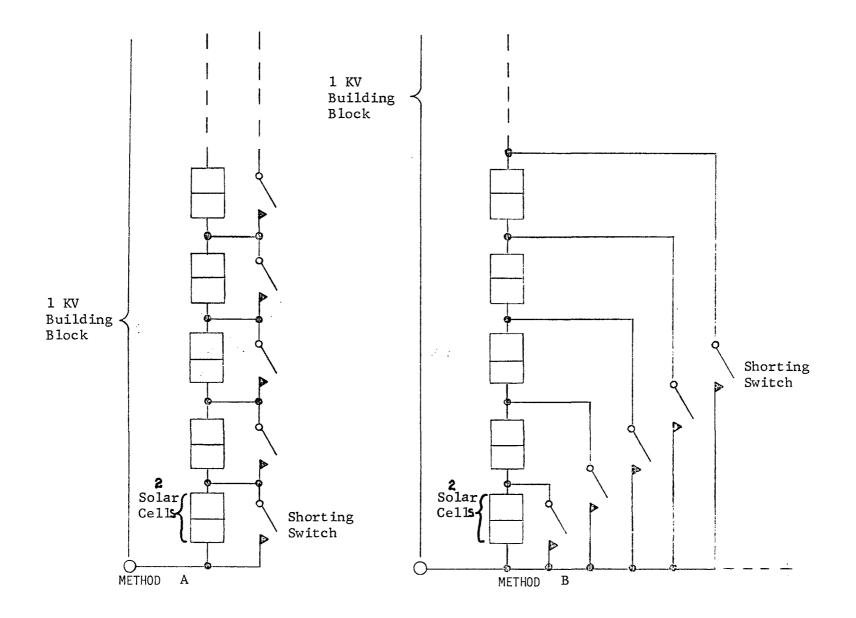

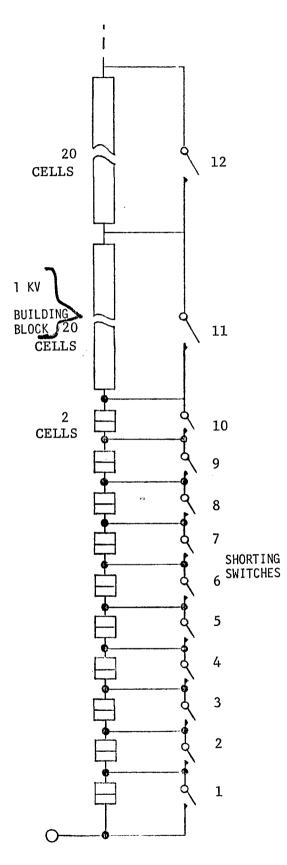

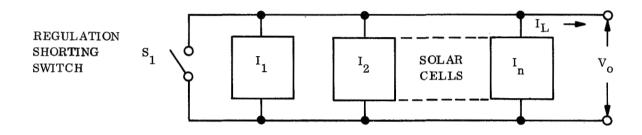

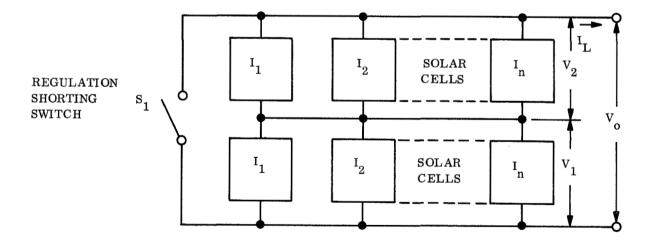

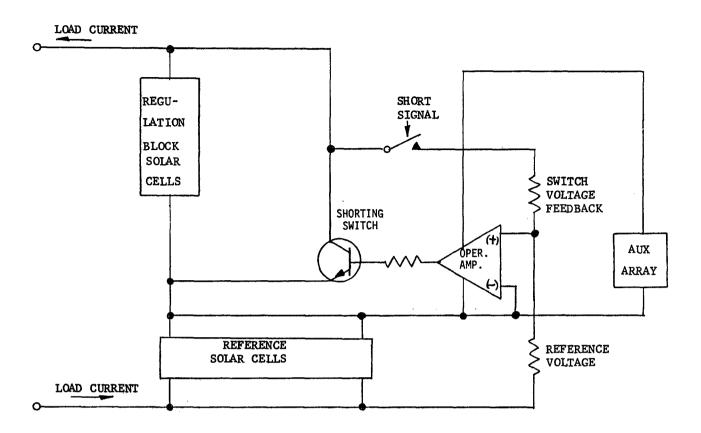

#### 5.1.7 ARRAY SHORTING SWITCH

The array shorting switch reduces building block voltage to zero for load protection during reconfiguration, load switching, and emergence from eclipse when the possibility of high array voltages exists before regulation can be established. During normal operation of the building block, the array shorting switch is in the open state, and must withstand the maximum output voltage of the building block. The current that the switch must pass is the short-circuit current of the main array in the building block, which has a maximum value of 2.7 amps for the range of building block currents considered during this study. Consequently, the stacking switch described in the previous paragraph will accommodate the array shorting switch requirements and the same quad circuit arrangement is specified.

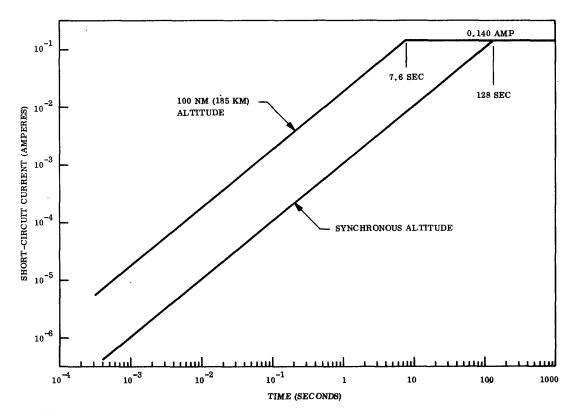

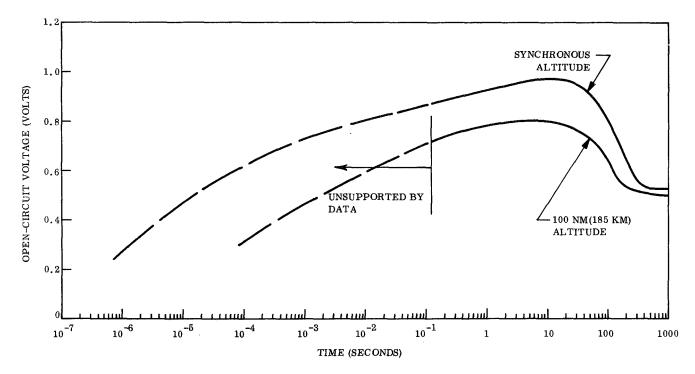

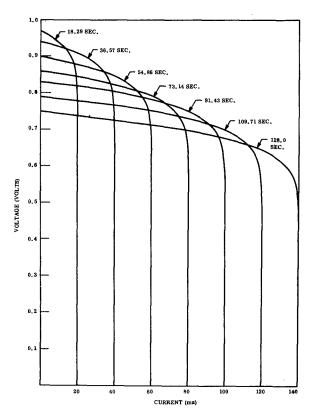

An estimate of the solar cell open-circuit voltage and short-circuit current as a function of time on emerging from earth shadow is presented in Section 5.3. It will be shown in a following section of this report that rated building block voltage is achieved at a per-cell operating voltage of 0.358 volt, with no regulation switches closed. This voltage may be present in as short a period of time as 2 to 3 microseconds, which requires that the array shorting switch be activated and effectively short the array within this time. Based on the solar cell voltage versus time estimates, the rate of voltage rise at the building block output terminals may be well in excess of  $10^6$  volts per second. Therefore, the array shorting switch must not only protect the array components from a higher-than-building-block voltage condition, but must also prevent undesirable premature turn-on of the SCR load switches due to a possible excessive dv/dt condition. Since the drive power for the array shorting switch is supplied by a small auxiliary array having the same relative voltage and current buildup as the main array, a possibly severe design problem exists in that insufficient drive current may be available to activate the array shorting switch before high solar cell voltages are present. The ability of a transistor array shorting switch to safely accommodate this problem is uncertain, and must be established by test to verify the feasibility of a semiconductor switch for this function. The critical nature of this problem may result in the specification of a relay for the array shorting switch function.

#### 5.1.8 LOAD SWITCH

Load switching is an extremely critical function in the HVSA system because of the need to isolate loads until regulated voltage from the source is achieved.

The extremely high voltages (up to 16 Kv) which must be switched is the most significant problem. Load voltages in excess of 2000 volts well exceed present transistor capability and even expected future development.

The semiconductor device which presently seems more capable of this function is the SCR. Application of transistor switching would be relatively simple and represent no serious problems from the turn on/turn off standpoint, but the SCR load switch presents several problems in this respect.

Turn on of the SCR does not appear difficult, although a continuous gating signal may be required if the value of load current is less than the minimum SCR holding current. The LED-fiber optics-photosensitive transistor receiver combination proposed as the HV signal coupler in Section 5.2 would provide the turn-on signal, but prevention of unwanted triggering must be carefully considered. The dv/dt on an output due to regulation switching and especially configuration switching must not exceed the SCR anode dv/dt capability. No large effect on triggering circuit noise problems is foreseen just due to the high voltage presence, al-though distributed capacitance on the array substrate and the space plasma effects presently represent an area of uncertain interaction with the semiconductor switching functions. Turn-off of the SCR load switch presents a problem. Several possibilities exist which depend upon the acceptability of voltage transients to the load to accomplish turn-off.

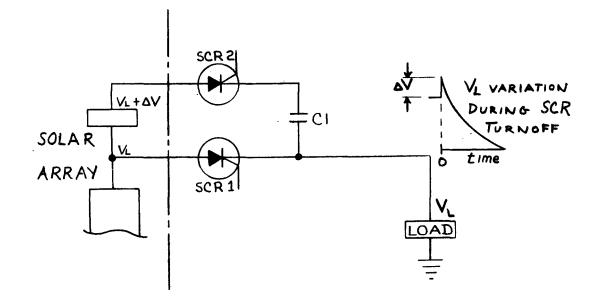

- 1. <u>Capacitive</u> Figure 15 presents a capacitive SCR turn-off technique. SCR 1, supplying load current, is turned off by the turn-on of SCR 2, which provides a back bias for SCR 1 while the capacitor C1 charges. The load voltage at turn-off is also shown in Figure 15.

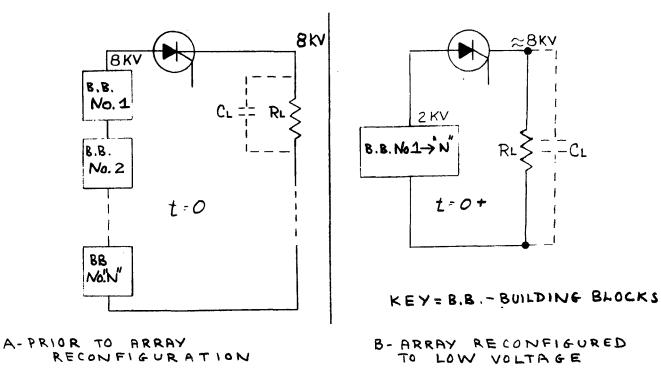

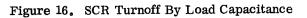

- 2. Load Capacitance If there is capacitance at the load, and its value can be ascertained, the load switch SCR may be turned off by reconfiguring the array to a lower voltage so that the voltage on the SCR anode drops rapidly, thereby back biasing the SCR due to the load capacitance. This method of SCR turn off is shown in Figure 16. The load capacitance  $C_L$  required for a 100 usec time constant is only 0.025 mfd  $\leftarrow$  This may be true only at 16 Kv; i.e., sensitive to voltages.

- 3. <u>Series Transistor</u> A transistor switch in series with the SCR interrupts the current for a sufficient time so the SCR will block when voltage is reapplied. This turn off must be done with the array configured to a low voltage to be within the transistor specifications. The transistor must be turned on again after the SCR is off so the SCR blocks the high voltage when the array is reconfigured. This technique is illustrated in Figure 17.

The technique of method (1) is subject to a serious drawback. A lightweight high-voltage capacitor suitable for mounting on the solar array is presently beyond the state-of-the-art. A consideration for method (2) is that the unknown magnitude of solar cell and substrate to ground capacitances on the array side of the SCR load switch may be comparable to the load capacitance, rendering this method ineffective.

Method (3) appears to be the most feasible approach to configuring the load switch. Use of the array shorting switches to reduce the source voltage to zero would result in a relatively short duration load turn-off time, with an excellent backup to ensure SCR turn-off being provided by the zero-voltage source. This method is proposed for the load switch, with appropriate redundancy to achieve reliability.

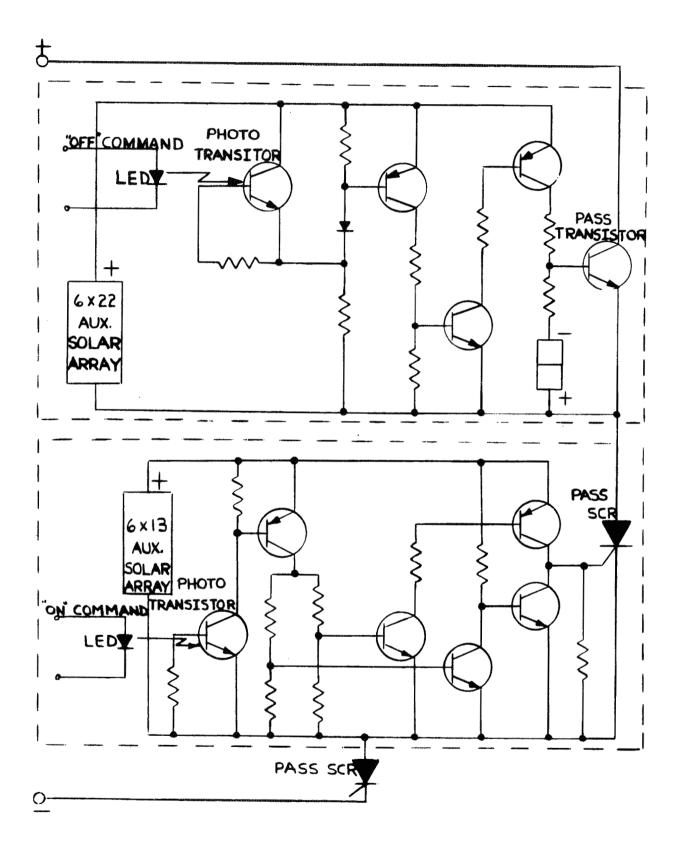

Figure 18 presents a block diagram of the redundant load switch arrangement. The switch redundancy features are:

- 1. Redundant to "close" by the parallel transistors and SCRs.

- 2. Redundant to "turn off", either by the turn off transistors in series with the SCRs, or by reduction of voltage by means of the array shorting switch located in the building block, both of which cause the SCRs to turn off by loss of holding current, and

- 3. Redundant to remain "open" by the series connection of the quad SCRs.

A schematic arrangement for an 8-ampere load switch is shown in Figure 19 and a 1-ampere load switch circuit is illustrated in Figure 20.

The transistor gate to the cathode in the "SCRs" provides maximum dv/dt capability of the SCR, to reduce the possibility of spurious turn-on due to regulation switching and reconfiguration voltage transients. The series transistors could be eliminated if knowledge of both the load and "SCR" can assure that the load current will be less than the "SCR" holding current, in which case SCR turn-off would be accomplished by merely removing the cathode gate. The series transistor circuit allows the transistor to be normally on, and the current interrupt function is initiated by the temporary presence of the LED-coupled "OFF" command. The SCR "ON" command is required to provide the gate current for the SCR to ensure conduction if the load current is less than the device holding current.

## 5.1.9 LOAD RETURN/ARRAY GROUND SWITCH

The block diagram in Figure 5 shows that 17 ground switches (SG1 - SG17) would be required in order to have the capability of placing the ground point at any 1 Kv voltage increment on a representative HVSA sytem having 16 Kv building blocks. Since the loads are returned to the system side of the grounding switch, a critical design problem would exist in that there may be no current through the switch when it is commanded closed, due to the absence of a return to the array from the ground side of the switch. The impact of this condition is that no collector current would exist for a transistor switch and no holding current would exist for a SCR type switch. It can be shown that transistor circuitry can be designed to overcome this problem, but of course the need for the ground switch to accommodate up to 16 Kv across it in the open configuration precludes the use of any present transistor.

While the array could be grounded at 17 different points with the arrangement shown in Figure 5, provided a suitable switching device were available, the final design would probably not require this many ground points, and only those ground switches necessary would be included. Therefore, another approach which could be used is to determine the ground point of the array by the loads connected to it. A switch would be required in the power return lines which are grounded at the load, and this switch may be in a common return line for several loads. An SCR or "gate turn-off switch" would probably be used, since this switch must block both polarities of voltage but pass current only in one direction.

The establishment of a ground reference point for the HVSA requires that a switch function connect spacecraft ground to a particular tap point on the array before the array shorting switches are opened and before the high voltage is applied to the loads.

It is proposed to accomplish the array grounding function and provide load return current with a single switch function, but since the loads are not powered at the time this switch function, a unique requirement on this switch is that it must operate when no load current exists.

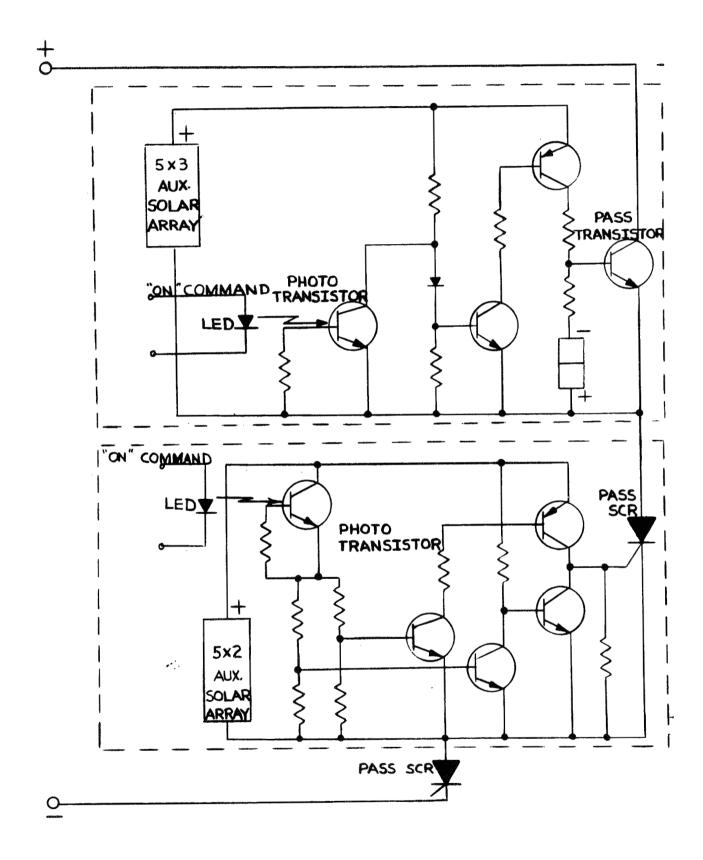

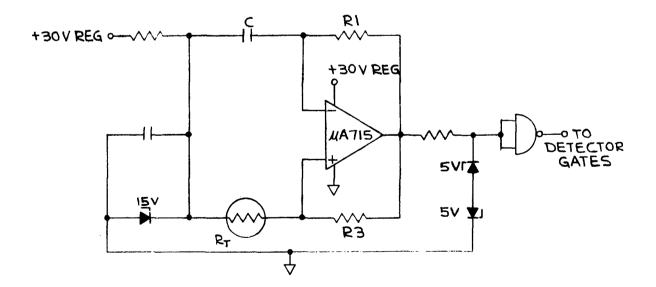

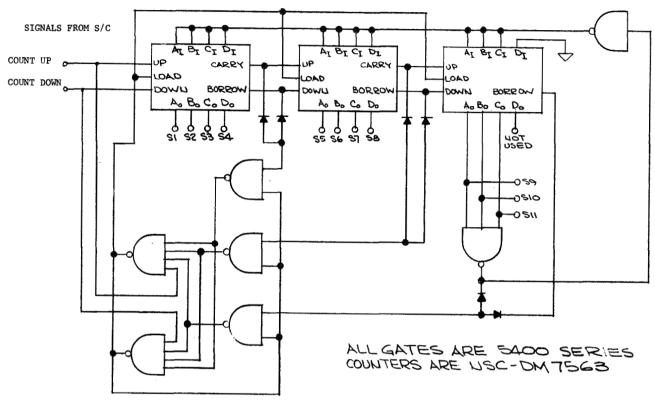

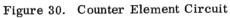

Figure 21 presents a functional diagram of a "quad H" arrangement of the load return/array ground switch elements. The redundancy ensures that no single short or open failure will impair the switching function. The load return would be connected at the same terminals of the switch where the ground is shown. A schematic arrangement of one of the quad ground switch elements is shown in Figure 22. The SCR device Q2 and the group of solar cells between Q1 and Q2 provide a current path and sufficient voltage to ensure conduction for the main switch element, Q1, when the gate signal from the "ON" command is present, even with the absence of a current path external to the switch terminals. The transistor in series with Q1 and Q2 ensures cutoff of the main switch element, Q1, by reducing its current to zero with the presence of the OFF command signal. A light-emitting diode is employed as the signal isolator for both the ON and OFF commands from the spacecraft.

#### 5.1.10 HIGH VOLTAGE STACKING SWITCH AND COUPLING DIODE FUNCTIONS

The stacking switches and coupling diode functions considered during the study have had the purpose of connecting a building block electrically in series or parallel, respectively, with another (adjacent) building block. In this application, each device must be capable of blocking the output voltage of one building block only.

In the design of a specific HVSA system, as evidenced by the optimized system configurations discussed in Section 6, it may be advantageous to retain several building blocks connected in series for more than one switchable system configuration. In this case it may be necessary to switch the string of building blocks, requiring stacking switches and coupling diodes which must block voltages higher than the output voltage from a single building block.

The stacking switch and coupling diode voltage requirements therefore exceed the operating ratings (1500 V) for the devices shown for these functions in the single building block applications. Section 5.4 presents the considerations in selecting switch voltage ratings. Consequently, such stacking switches will be a direct adaption of the SCR load switch design, which readily accommodates the higher blocking voltage requirements. The higher voltage coupling diode functions can be implemented by a series connection of several lower-voltage diodes, which is a common practice for obtaining high voltage blocking capability. Of course the SCR load switch design could also be used for this "coupling diode" function, but the complexity and auxiliary array penalty involved with the SCR switch makes the stacked diodes appear to be a better selection. The coupling diode function would be configured as the parallel connection of two stacked diode strings, each diode string having N diodes connected in series. The parallel redundancy protects against open-circuit failure. The number of series-connected diodes, N, will permit possible diode short-circuit failures without exceeding the breakdown rating of the remaining diodes. For the diode total failure rate employed in this study (0.005 x 10<sup>-6</sup> failures per hour) and a 9 to 1 short versus open failure rate, the following tabulation presents the total number of series-connected diodes, N, needed to achieve .999999 reliability.

| No. of Diodes Needed for<br>Voltage Capability | No. of Additional<br>Diodes for Rel. | Total No. of Series<br>Diodes, N |

|------------------------------------------------|--------------------------------------|----------------------------------|

| 2                                              | 1                                    | 3                                |

| 4                                              | 1                                    | 5                                |

| 6                                              | 2                                    | 8                                |

| 8                                              | 2                                    | 10                               |

| 10                                             | 2                                    | 12                               |

| 12                                             | 2                                    | 14                               |

### 5.1.11 SWITCHING FUNCTIONS SUMMARY

The following list defines the semiconductor device type and circuit redundancy arrangement recommended for each of the switching functions described in this section.

| Function                                  | Implementation                                                                                                                            |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Parallel Connection of<br>Building Blocks | Quad Configuration of HV Diodes                                                                                                           |

| Stacking Switch                           | Quad Configuration of HV Transistors (normally OFF).<br>Figure 12.                                                                        |

| Array Shorting Switch                     | Quad Configuration of HV Transistors (normally OFF).<br>Figure 12.                                                                        |

| Load Switch                               | Quad Configuration of SCR devices (normally OFF) and Dual<br>Configuration of Turn-off Transistors (normally ON).<br>Figures 18, 19.      |

| Load Return/Array Ground<br>Switch        | Quad Configuration of Elements, each having SCR device<br>(normally OFF) and series Turn-off Transistor (normally<br>ON). Figures 21, 22. |

Table 2 presents the fundamental electrical operating requirements for each of the switching functions, as well as the maximum power dissipation in the devices. The maximum values apply to the application in the two representative optimized systems described in Section 6.

| p                                       |                       |                         |

|-----------------------------------------|-----------------------|-------------------------|

| Load No. 2<br><u>Connection at (KV)</u> | Switch No. 2 Blocking | Voltage Capability (KV) |

|                                         | Forward               | Reverse                 |

| 0                                       | 0                     | 16                      |

| + 1                                     | 1                     | 15                      |

| + 2                                     | 2                     | 414                     |

| + 3                                     | 3                     | 13                      |

| + 4                                     | 4                     | 12                      |

| + 5                                     | 5                     | 11                      |

| + 6                                     | 6                     | 10                      |

| + 7                                     | 7                     | 9                       |

| + 8                                     | 8                     | 8                       |

| + 9                                     | 9                     | 7                       |

| +10                                     | 10                    | 6                       |

| +11                                     | 11                    | 5                       |

| +12                                     | 12                    | 4                       |

| +13                                     | 13                    | 3                       |

| +14                                     | 14                    | 2                       |

| +15                                     | 15                    | 1                       |

| +16                                     | 16                    | 0                       |

|                                         |                       |                         |

Table 1. Forward and Reverse Blocking Voltage Combination for Load Switch

Table 2. Switching Function Voltages and Currents

| FUNCTION                               | MAX. BLOCKING<br>VOLTAGE | MAX. OPERATING<br>VOLTAGE | MAX, STEADY-STATE<br>CURRENT | MAX. POWER<br>DISSIPATION* |

|----------------------------------------|--------------------------|---------------------------|------------------------------|----------------------------|

| Stacking Switch                        | 1500 V                   | י ר                       | 8 A                          | 8 W                        |

| Array Shorting Switch                  | 1500 V                   | 1 V                       | 2.7 A                        | 2.7 W                      |

| Coupling Diode                         | 1500 V                   | 1 V                       | 8 A                          | 8 W                        |

| Load Switch SCR                        | 16 KW                    | 10 V                      | 8 A                          | 80 W**                     |

| Load Switch Turnoff<br>Transistor      | 1500 V                   | 1 V                       | 8 A                          | 8 W                        |

| Load Return/Array<br>Ground Switch SCR | 16 KV                    | 10 V                      | 8 A                          | 80 W**                     |

\* Per device

\*\* SCR power dissipation when blocking 16 KV may range from 16 to 320 W, based on estimated leakage current of 1 to 20 milliampere.

Figure 5. General Case System Switching Block Diagram

| CONFIGURA | TION SWI            | TCHING |   | LOAD<br>WITCHING |

|-----------|---------------------|--------|---|------------------|

| 5617      | BUILDIN G<br>BLOCKS |        |   |                  |

| SGIG      | 16                  |        | * |                  |

| SG15      | [15]                | 5615   |   |                  |

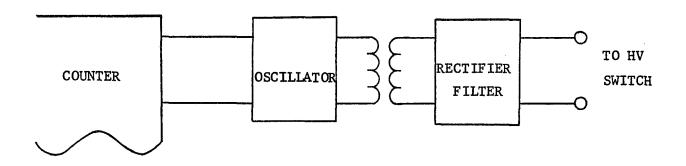

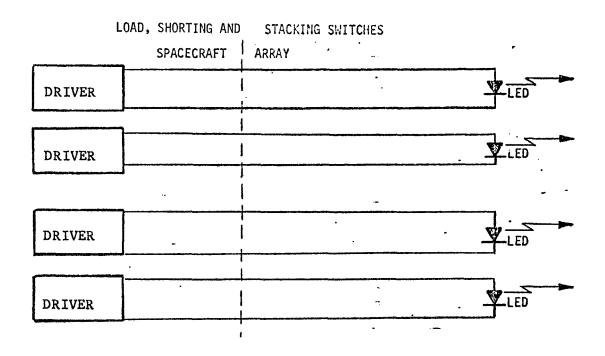

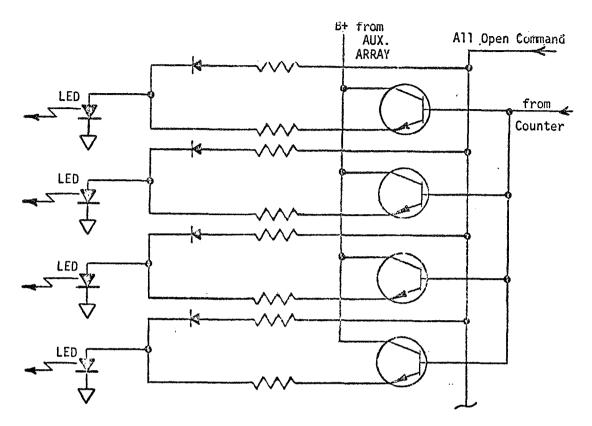

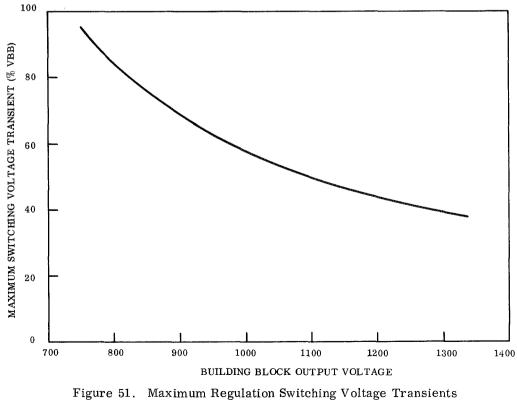

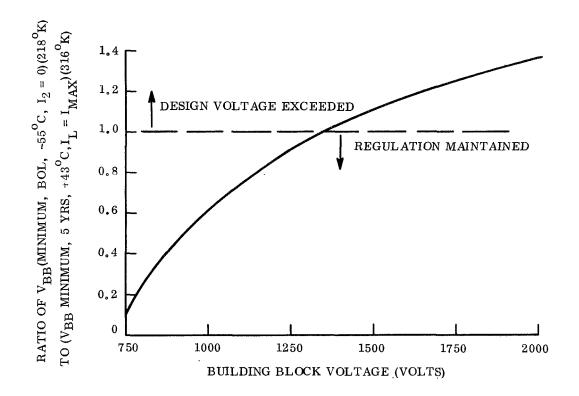

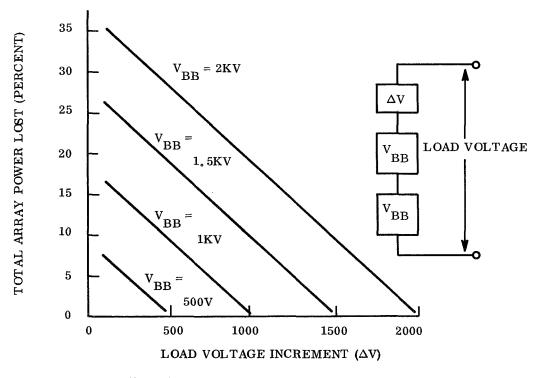

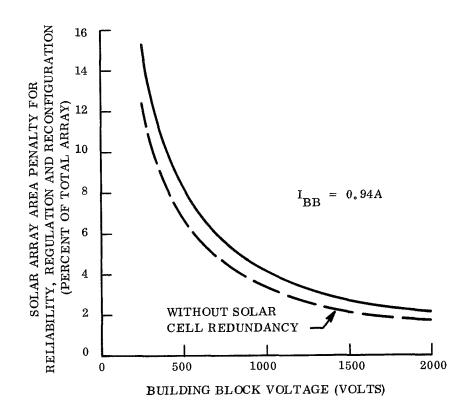

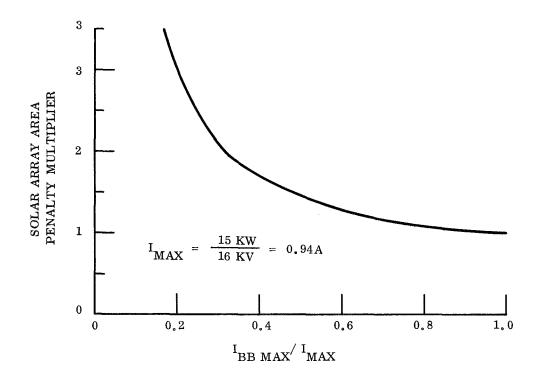

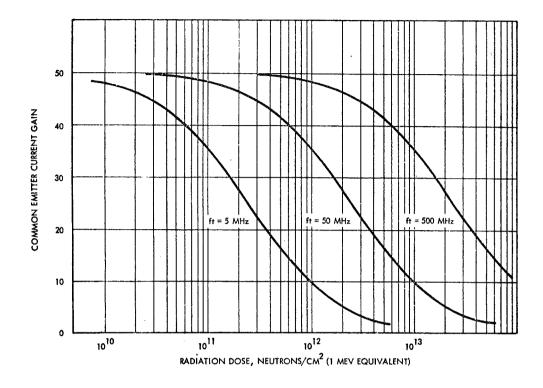

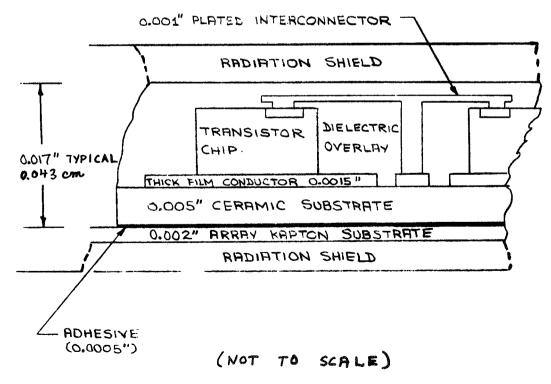

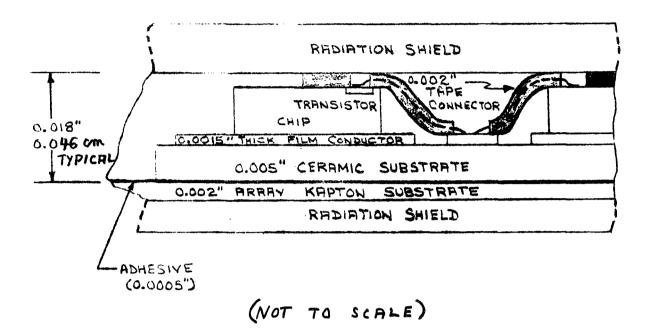

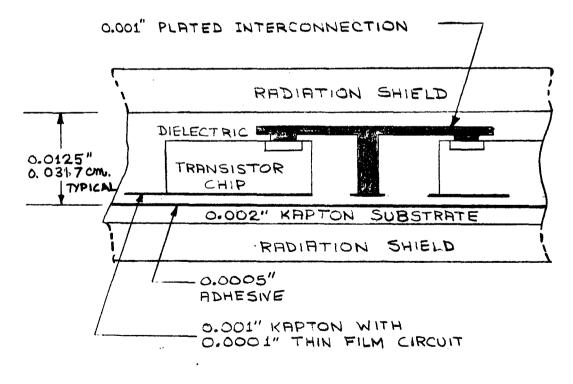

| 3G14      | 14                  | 5514   |   |                  |