#### **General Disclaimer**

## One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

The University of Arizona

Engineering College

Department of Electrical Engineering

Computer Science Research Laboratory

(gr print)

CSRL Memo No. 208

A Solid-state Crossbar Switch

for Automatic Analcy-computer Patching

by

A. Yagi (Electrotechmical Laboratory, Tokyo, Japan)

## Abstract

An all-electronic crossbar switch consisting of FET seriesshunt switches inside the feedback loops of monolithic operational amplifiers was designed and constructed.

As the application, time-shared solution of five different differential equations was obtained by using four integrators on ASTRAC II, with a new solution being generated 250 times per second.

(ACCESSION NUMBER)

(PAGES)

(PAGES)

(PAGES)

(PAGES)

(PAGES)

(PAGES)

(PAGES)

(CODE)

(CATEGORY)

(CATEGORY)

ACILII T FORM 60;

NGR-03-002-U24

# Introduction

Among current problems relating to analog and hybrid computers, one of the most interesting is that of automatic analog-computer patching, which will replace the conventional analog patch board. A set of 20 to 50 relatively small (4 X 4 to 6 X 8) crossbar switches, which change the connections of analog some would permit not only the automatic patching or storage of analog programs, but also the time sharing of analog computers. (5) From the viewpoint of hardware, low-cost integrated circuit switches and operational amplifiers will provide the means of constructing such a crossbar switch.

This paper describes the design and construction of a 4 x 4 crossbar switch and its application to analog patching. The crossbar switch consisting of monolithic operational amplifiers employs series—shunt switches in—side feedback loops of operational amplifiers; therefore high accuracy is ensured. Each crossbar matrix consists of four multiplexers, which can change the connections of analog computing elements. The solutions of five differential equations are obtained by using four integrators. This scheme was successfully tried on ASTRAC II. a very fast iterative analog computer.

# The Design of the, Analog-patching Crossbar Switch Configuration Selection of the Multiplexer

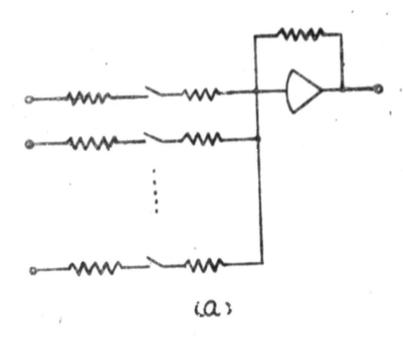

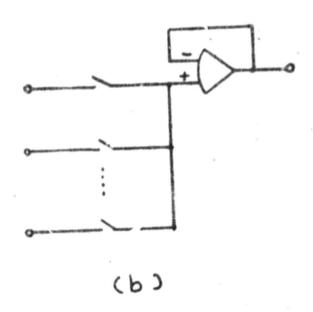

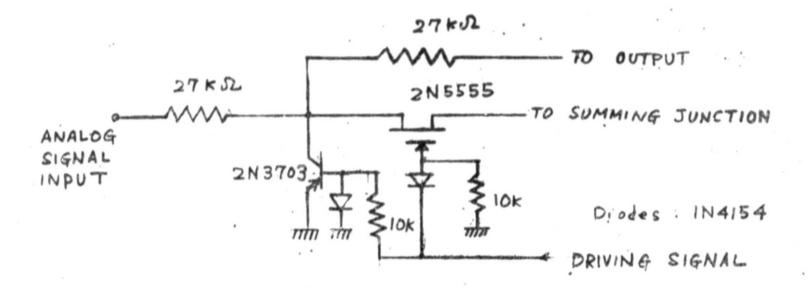

There are various methods of multiplexing analog signals. One method is to switch analog signals by switches placed in the input computing resistors of an operational amplifier as in Fig. 1 (a). The disadvantage of this method lies in the fact that the ON resistance of the switch causes computing errors. Adjustment of network resistances will improve the accuracy, but this is cumbersome and expensive.

If the operational amplifier is used as a voltagefollower as in Fig. 1 (b), the ON resistance of the switch

tends to be negligible compared to the very high-input follower impedance. However, no more than one switch must be

ON at any one time.

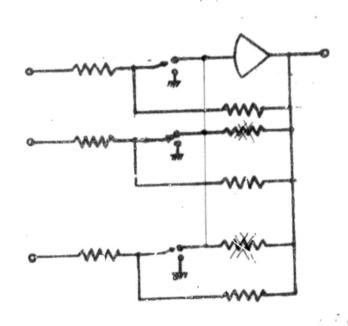

A better method is to place the switches in the feedback loop of the operational amplifier to eliminate the effect of the ON resistance. (Fig. 1 (c)). It has the advantage that the number of operational amplifiers required is one and more than one switch is allowed to close at a time.

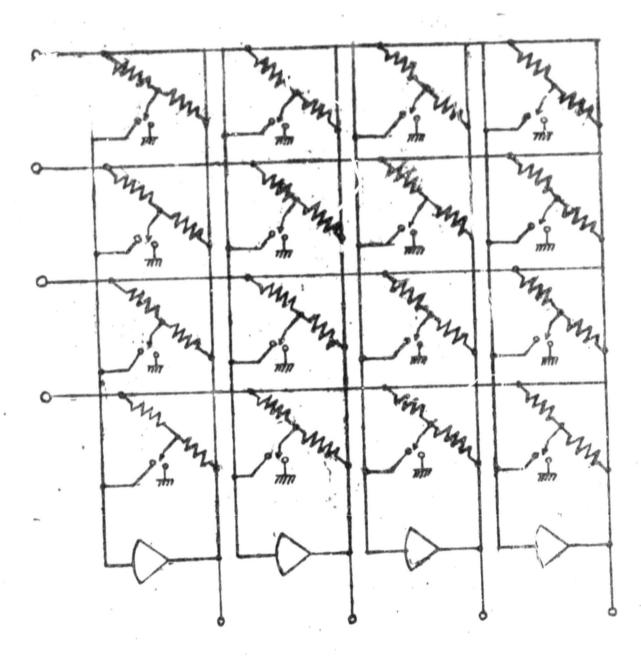

Considering these points, the last method was adopted for an analog-patching multiplexer. For this purpose, the 4 X 4 matrix switch shown in Fig. 2 was designed and tested.

# Analog Switch

Although this multiplexer does not require switches

with low ON resistance, it does require low offset-voltage. Therefore FET series-shunt switches (Fig. 3) are desirable. When the FET is OFF, and the transistor is ON, the collector voltage of the transistor is small (less than 50 mV), so this shunt transistor makes analog signal current flow to ground and the switched node is disconnected to the summing junction. When the FET is ON and the transistor is OFF, the node is connected to the summing junction. The gate leakage current or the ON FET is not the problem, because the gate to source voltage of JFET is kept at O V by a resistor (Fig. 3). The OFF shunt transistor produces leakage current which flows into the summing junction, but this effect is within 0.1% of half scale, if a silicon transistor is used and proper value of computing resistors of the operational amplifier is selected.

N channel junction FET 2N5555 and PNP silicon transistor 2N3703 were selected for the reason of availability and low cost. The ON resistance of the FET (OV gate voltage) is about 140 ohms, and the leakage current of the OFF transistor is specified to be less than 100nA and the resistance of the ON transistor is less than 20 ohms. In order to ensure the operation of this series-shunt switch, a driving signal swing between -9 volts and 3 volts is required.

### Switch Driver

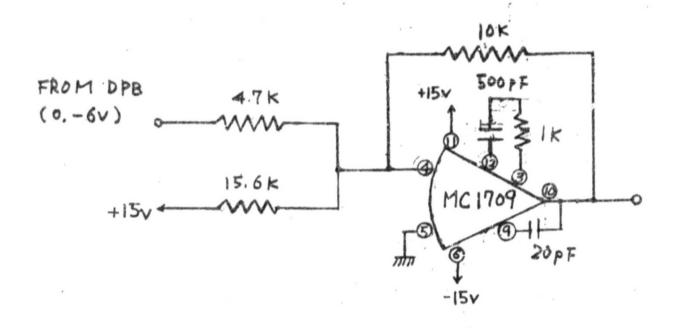

For use with our particular analog computer, the switch

on the ASTRAC II digital patch bay to the -9 volts to +3 volts levels. Among various kinds of circuits available, monolithic operational amplifier MC 1709 (±10 V output voltage swing) was selected (in Fig. 4), because it costs less than commercially available FET drivers, and save construction; a sufficiently large output swing is easily obtained, and especially fast switching is not required for automatic patching, which always takes place between analog-computer runs.

The amplifier is equalized so that the maximum frequency for rated output is more than 35 KHz and the amplifier is stable.

## Output Operational Amplifier

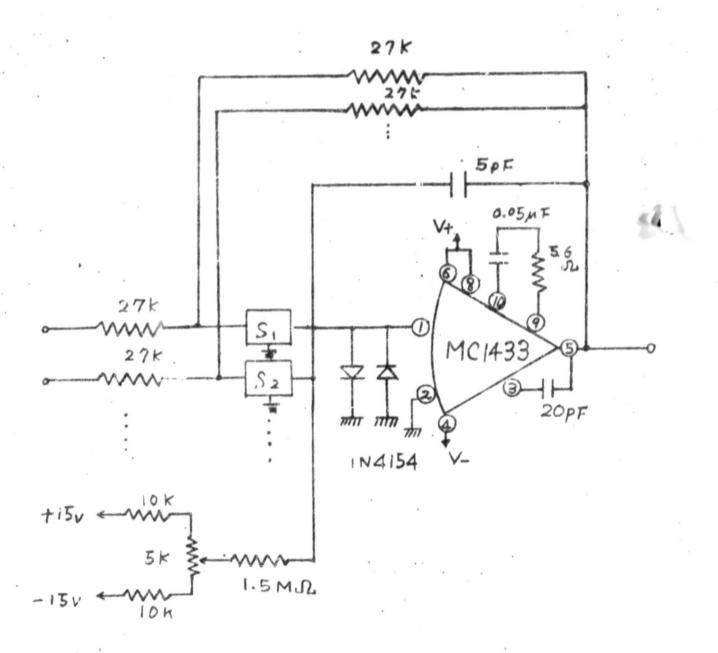

As for the output operational amplifier, the monolithic operational amplifier MC 1433 (±10 V output voltage swing) was selected for simplicity of circuit construction and low cost. For higher accuracy, a chopper-stabilized discrete circuit would be substituted. The circuit diagram is as in Fig. 5. The diodes at the input terminal protect the operational amplifier if the summing-junction voltage should rise because of a damaged switch. All computing resistors are selected to be 27 KΩ.

Because of stray capacitances associated with the

switching circuit, the operational amplifier had to be equalized for stability so that the maximum frequency for rated output is about 35 KHz, and the noise is within 0.05% of half scale.

# Construction and Results

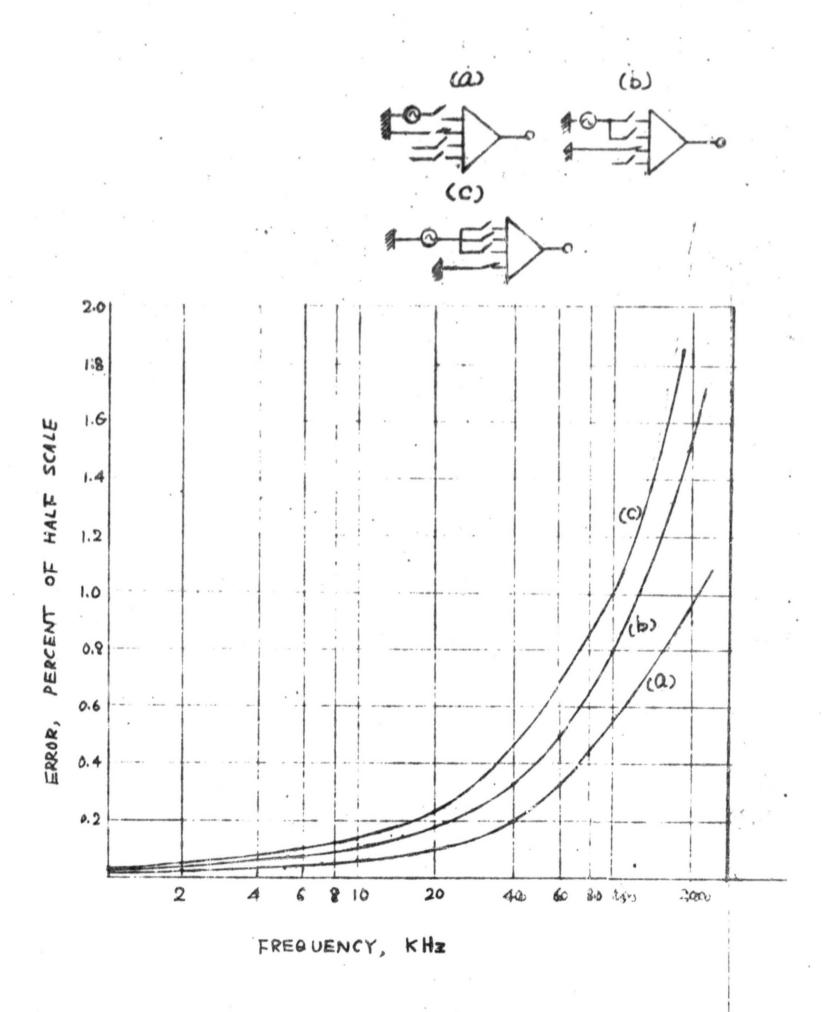

The 4 X 4 crossbar circuit and switch drivers were constructed on an 3.5 in. X 17 in. perf board sheet. The most serious problem is that of crosstalk which affects the accuracy of the multiplexer. In the construction of the circuit, attention is paid to good short ground connections.

The crosstalk characteristics are shown in Fig. 6. The curve (a) shows the case where the input sine wave signal (20  $V_{\rm pp}$ ) is applied to one of the OFF state analog inputs, and curve (b), (c) shows the case of two and three of the OFF state analog inputs respectively. It is also shown that the circuit will work with two switches ON and the crosstalk becomes smaller because the feedback resistance is the half (13.5  $K\Omega$ ); this connection could be used to compute one-half the sum of two inputs, if desired.

# The Application of the Crossbar Switch

# Statement of Problem

By using this multiplexer, we can change the connections of analog computing elements in a short time. In a

large automatic patching system several crossbar switches would be used as "telephone exchanges". Here, as a demonstration of the operation of the multiplexer, the iterative patching of five setups is tried on ASTRAC II. The problem is to generate five solutions of five different differential equations at a rate of 250 per second for each problem.

These problems are:

- (1) First order differential equation,  $\dot{x} + a_1 x = 0$

- (2) Harmonic oscillation,  $\ddot{x} + a_2 x = 0$

- (3) Damped harmonic oscillation,  $\ddot{x} + a_3 \dot{x} + b_3 = 0$

- (4) Mathieu's equation,  $\ddot{x} + a_4 (1-\cos \omega_m t) \pi = 0$

- (5) Vandder Pol's equation,  $\ddot{x} + a_5(x^2-1)\dot{x} + x = 0$

The 4 X 4 matrix switch (Fig. 2) is not sufficient to connect each computing element independently. Therefore some fixed connections and tricks must be employed to overcome this restriction.

## Method of Solution

Analog Computer Setup. In general, one would change coefficient (digital attenuator settings as well as patching connections for each problem in order to set the proper value of time scale, amplitude scale and initial conditions. For simplicity, however, settings of potentiometers are kept constant for each problem, so time scale and amplitude scale must be compromised.

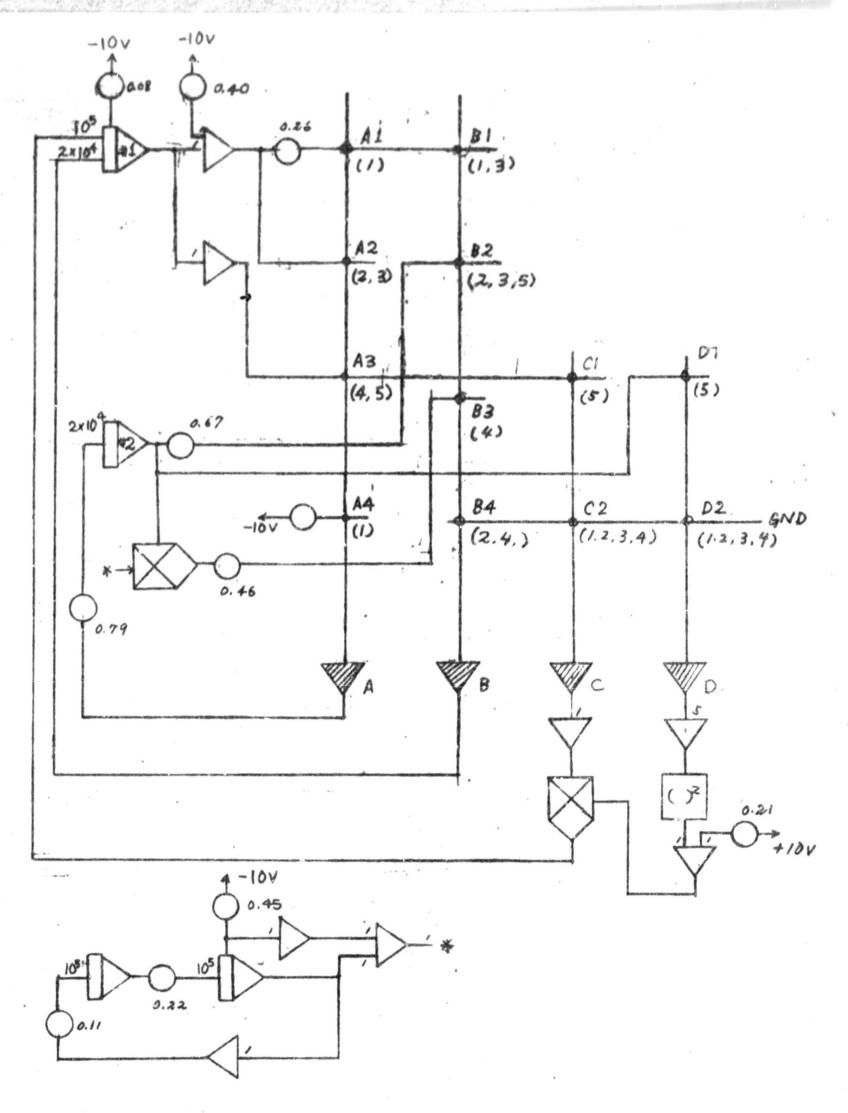

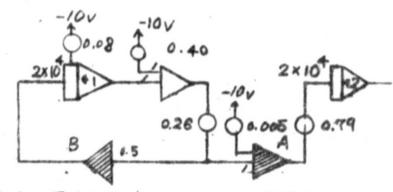

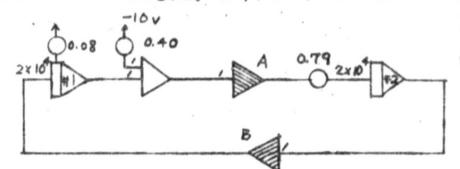

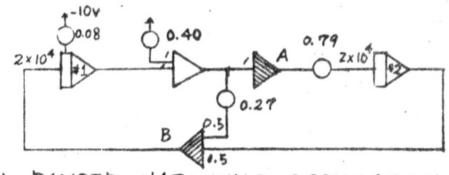

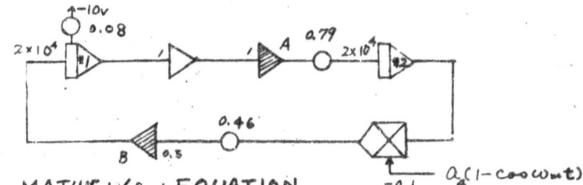

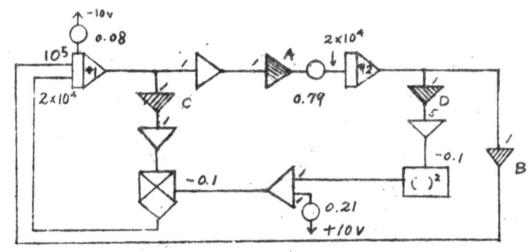

The setup diagram is shown in Fig. 7. Each switch is denoted as Al, A2, Bl, B2 etc. The number near the switches [(1), (2), ...] shows that each switch closes only at the computing time corresponding to the problem [(1), (2) ...] and opens at other computing time.

Each problem setup is shown in Fig. 8, where the shaded amplifiers A, B, C, D are the output amplifiers of the crossbar switch. As the output to CRT is taken from the output of integrator \$2, the solution shown for problem (1) (first-order differential equation) is the integral of X (Fig. 8(a)). As described earlier, it is allowed that two switches of a multiplexer become ON at a time, but the gain of the multiplexer is 1/2 (Fig. 8). Initial conditions for linear differential equations are large, but those for nonlinear equations are small. A constant initial-condition voltage is added with a summer in the case of linear equations.

# Control Signals for Multiplexer Switches

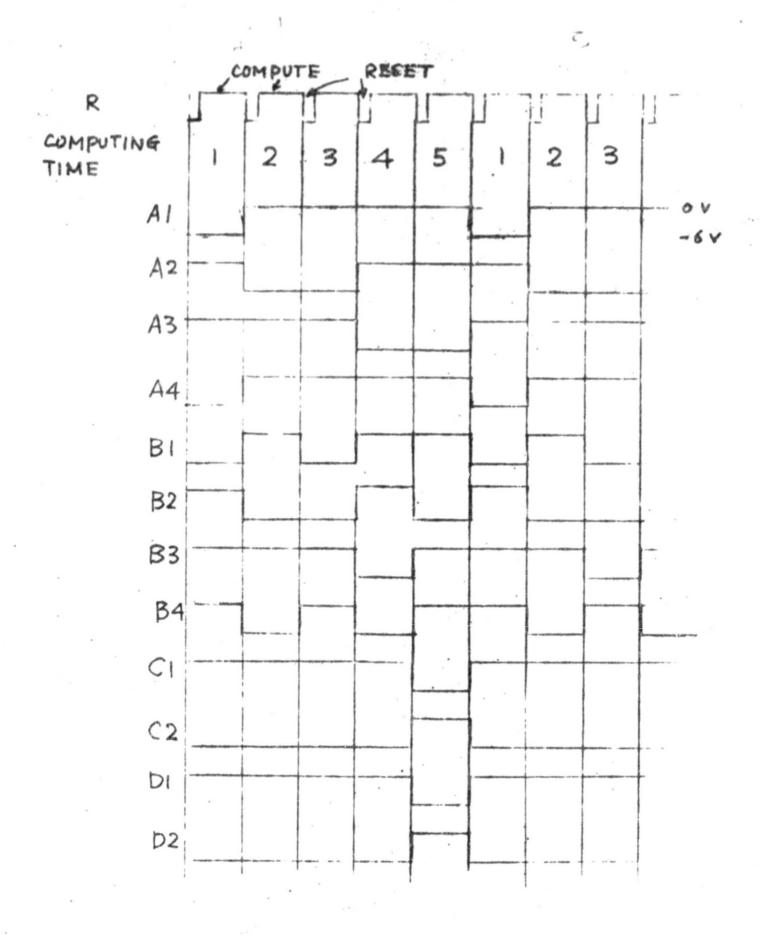

In order to set up five differential equations successively, each multiplexer switch must be furnished with a proper control signal. Referring to Fig. 7, these control signals become those in Fig. 9 (ON and OFF levels, -6v O V). The transition of the signals must take place at the end of the COMPUTE period of ASTRAC II.

There are two methods for generating such pattern signals.

One is to use ASTRAC II logic elements; the alternative is to use the digital computer (PDP-9).

# Pattern Generation by ASTRAC II Logic Elements

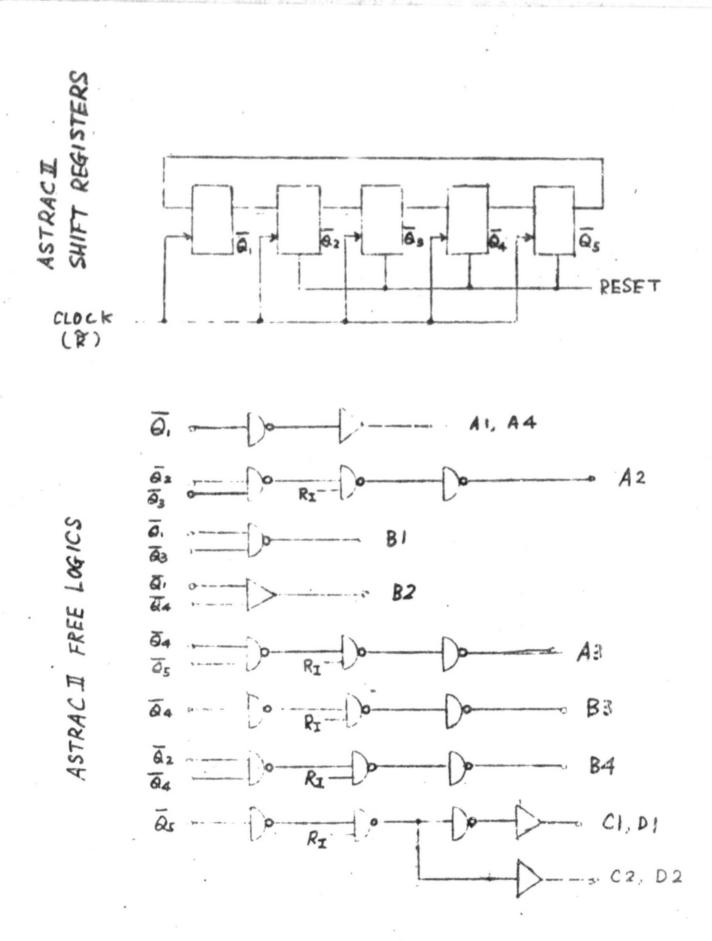

Shift registers on ASTRAC II are available to compose a five-bit ring counter. It operates at the ASTRAC II reset rate (in this case 250 Hz) and produces a periodic pulse sequence whose period is 5 times of the compute/reset period of ASTRAC II (20 ms). By combining the shift-register outputs properly, the pattern signals of Fig. 9 are obtained (Fig. 10).

When ASTRAC II is in INITIAL RESET mode, the multiplexer switches produce the connection corresponding to

problem (1) with the aid of the INITIAL RESET level obtained

to the ASTRAC II digital patch bay.

## Pattern Generation by PDP-9

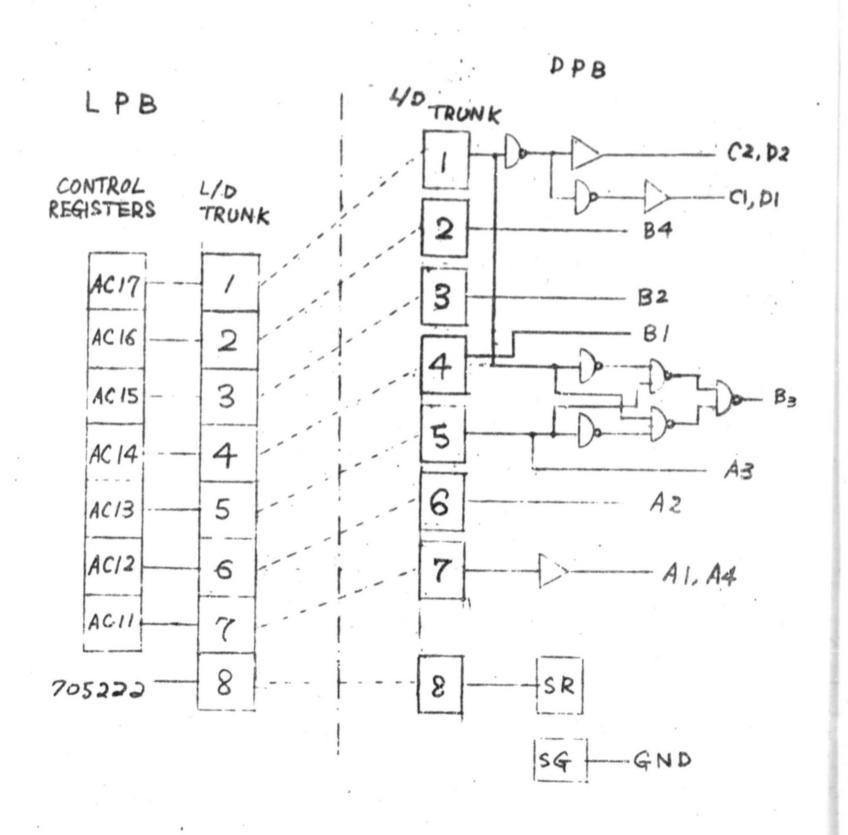

In this case, ASTRAC II is placed in SINGLE RUN mode, and control registers on the linkage patch bay are loaded from the PDP-9 accumulator, which contains the number corresponding to one of the problem connections. After that, one of the free IOT pulses on the LPB initiates SINGLE RUN.

Fig. 11 shows the necessary patch connections on digital and linkage patch bays. Because there are only eight trunk lines from LPB to DPB, some free logic on DPB is needed. (The signals on LPB (0,-3 V logic) can be used,

however, it is noisy).

Seven control signals (Al, A2, A3, B1, B2, B4, C1) out of twelve redundant signals (Fig. 9) correspond to the bits of AC11 through AC17. Because the inverter is in the trunk line (LPB to DPB), the number for each problem's connection is as follows.

| Problem | (1) | 0110111 | (67)  |

|---------|-----|---------|-------|

| Problem | (2) | 1011001 | (131) |

| Problem | (3) | 1010011 | (133) |

| Problem | (4) | 1101101 | (155) |

| Problem | (5) | 1101010 | (152) |

The PDP-9 program is listed in Table 1. When ASTRAC II is in the RESET mode, the program is waiting at CLOCK FLAG

TEST and the crossbar-switch power is on. The program starts when the compute push button on ASTRAC II is depressed.

## Results

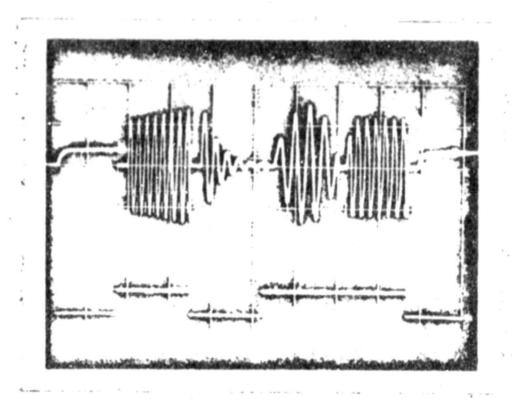

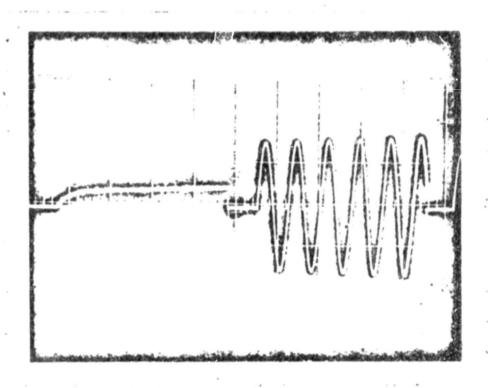

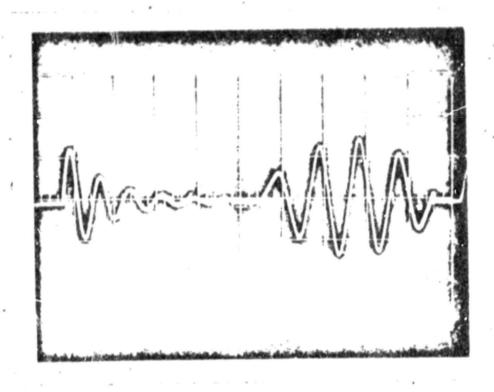

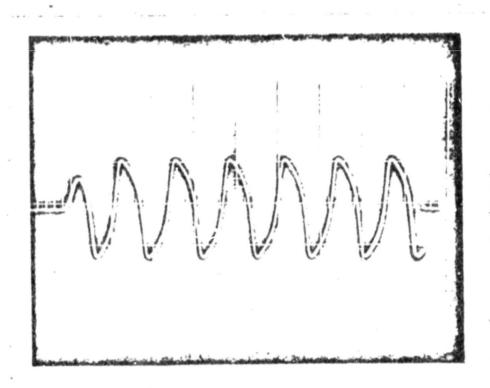

Fig. 2(a) shows the five kinds of waveforms and one of the control signals (Bl). The expanded waveforms are in Fig. 12 (b) - (d).

The number of computing elements of ASTRAC II is as follows.

Integrator ; 4 (2 for function generation)

Summer ; 14 (6 for multipliers)

Multiplier ; 3

Potentiometer ; 11

Figure 1. Multiplexer Configuration

Figure 2. 4 x 4 Matrix + Multiplexer

Figure 3. FET Series-Shunt Switch

Figure 4. Schematic Diagram of Switch Driver

Figure 5. Schematic Diagram of Output Operational Amplifier

Figure 6. Crosstalk Characteristics of the Multiplexer

Figure 7. Setup Diagram of Five Differential Equations

(1) FIRST ORDER DIFFENTIAL EQUATION

(2) HARMONIC OSCILLATON

(3) DAMPED-HARMONIC OSCILLATION

(4) MATHIEU'S EQUATION

(5) VAN DER POL'S EQUATION

Figure 8. Setup Diagrams of Each Equation

Figure 9. Control Signals to Multiplexer Switches

Figure 10. Pattern Generation by Shift

Registers and Free Logics

Figure 11. Patch Connections on LPB and DPB

```

/AY-6 JULY 2,1979

/ITERALVE PATCHING

(FIRST-1

LAC

BGN

223023

30730

(18)

DAC*

260724

20221

CONST

LAC

277 14

000:2

COUNT

DAC

C47115

22533

10

LOOP

LAC*

22711

02724

/LOAD C.R WITH A.C

785284

725224

77775

/TEST CLOCK FLAC

785521

775:21

77776

.-1

JMP

677766

02707

/MAKE SINGLE RUN

705222

00013

715222

COUNT

ISZ

22211

447015

LOOP

J MP

623224

00012

BGN

JMP

62727

27013

CONST

777773

00014

COUNT

8

00015

230300

/PLOPLEM. 1

FIRST

Ø67

000° S7

20016

/PLOPLEM. 2

131

232131

03017

/PLOFLEM. 3

123

3 1123

00023

/PLODIEM. 4

155

333155

20021

/PLOPLEM.5

152

200152

CC322

. END

BGN

000730

P *LIT

030015

00023

A * LIT

65.616

03024

NO ELFOR LINES

```

PAGE

AY-6

(a) Solution of 5 Differential Equations

CONTROL SIGNAL BI

VERTICAL SCALE 5V/CM

HORIZONTAL SCALE 2.4 MS/CM

(b) Problem (1) and (2)

VERTICAL SCALE 5V/cm HORIZONTAL SCAL IMS/cm

(C) Problem (3) and (4)

VERTICAL SCALE 5 1/cm

HORIZONTAL SCALE IMS/cm

(d) Problem (5)

VERTICAL SCALE 5 V/cm

HORIZONTAL SCALE 0.5 ms/cm

Figure 12. Waveforms of the Solution of 5 Differential Equation

## ACKNOWLEDGEMENTS

The writer is grateful to Professor Korn for his suggestions and guidance. He is also grateful to Dr. R. H. Mattson, Head, Electrical Engineering Department. This project was supported by the NASA Awes Research Center under Grant NGR-03-002-024.

## REFERENCES

- 1. Korn, G. A. and T. M. Korn: Electronic Analog and Hybrid Computers. McGraw-Hill, 1964.

- 2. PDP-user Handbook. Digital Equipment Corporation.

- 3. Eckes, H. R.: Design, Test and Application of Highspeed Iterative Differential Analyzer. Ph.D. Dissertation, Electrical Engineering, University of Arizona, 1967.

- 4. O'Grady, E. P.: Design, Test and Application of a

Hybrid Computer Interface. Ph. D. Dissertation,

Electrical Engineering, University of Arizona,

1969.

- 5. Hannauer, G.: Automatic Patching for Analog and Hybrid Computers, Simulation, May, 1969.