CR 73486 AVAILABLE TO THE PUBLIC

# **VOLUME I**

# FINAL ENGINEERING REPORT for PLASMA PROBE C, D&E

N71-12768

(ACCESSION NUMBER)

(PAGES)

(PAGES)

(NASA CR OR TMX OR AD NUMBER)

(CATEGORY)

prepared for

NASA/AMES RESEARCH CENTER (Contract No. NAS 2 3374)

#### FINAL ENGINEERING REPORT

# PLASMA PROBE C, D & E

#### CONTRACT NUMBER NAS 2-3374

# Prepared By

Members of the Technical Staff:

Dean A alami

Dean Aalami

Rene Evelyn-Veere

Approved By

George Mohler

Manager, Aerospace Division

Robert Kobayashi

Chief Engineer

#### ABSTRACT

The Plasma Probe instrument was designed by Marshall Laboratories (now Time-Zero Corporation) for the Pioneer C, D and E spacecraft. The instrument is designed to measure ion and electron density and angular distribution in outer space.

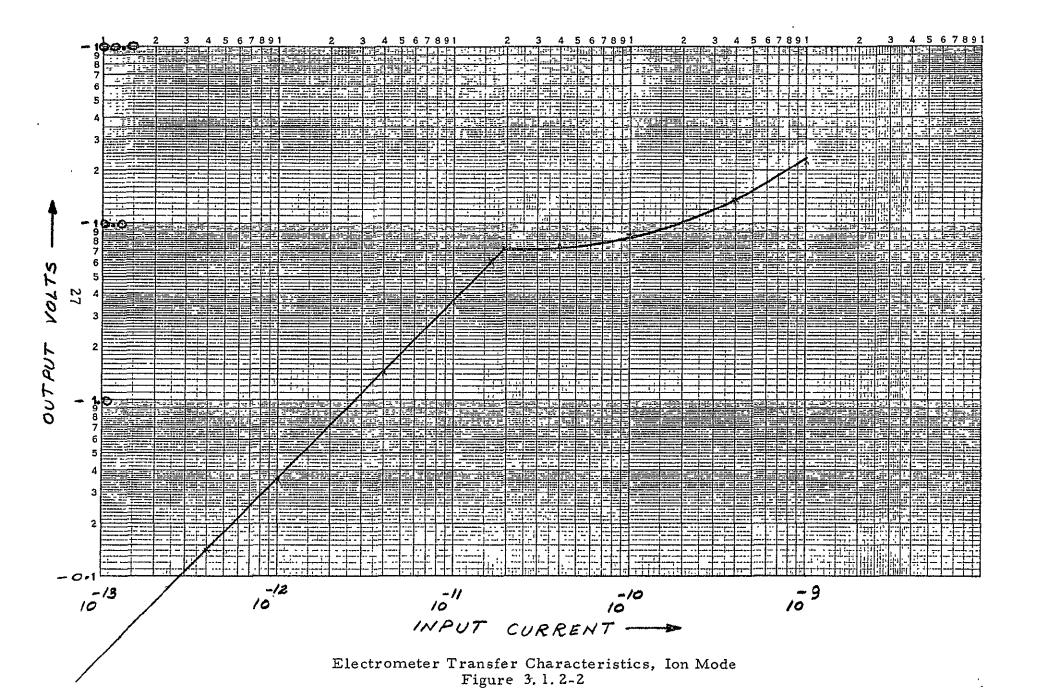

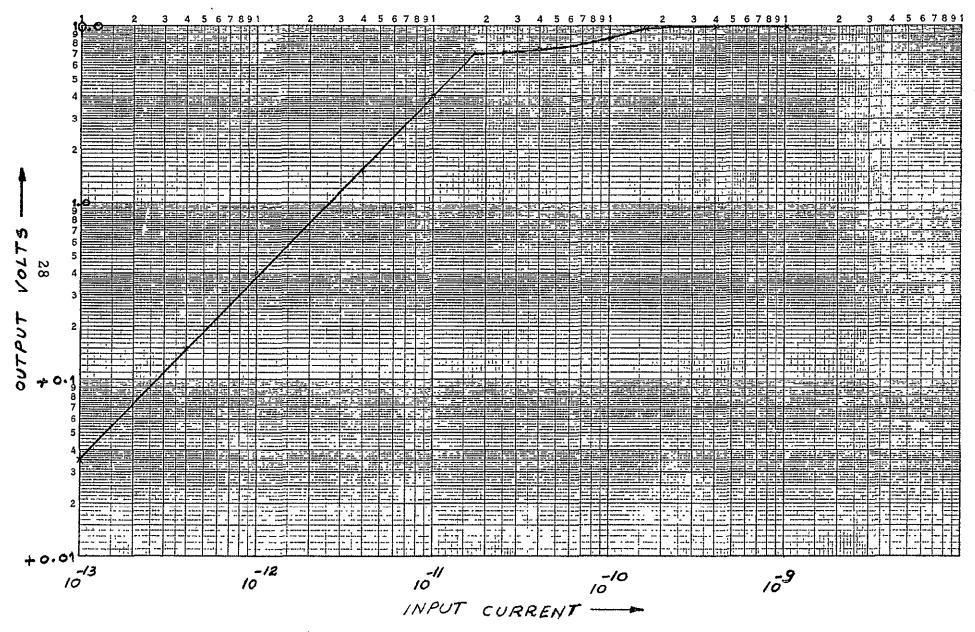

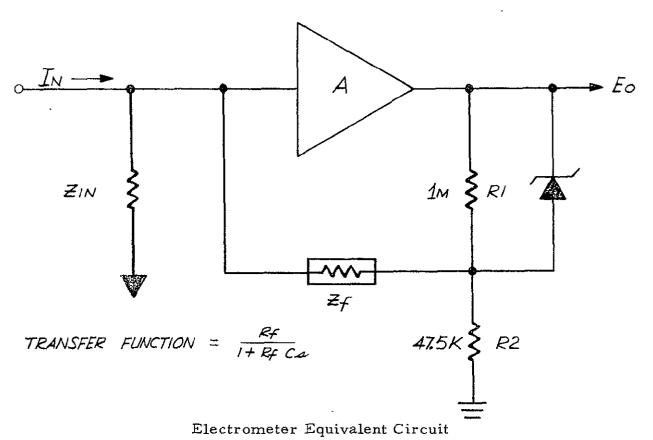

An Electrometer Amplifier converts the negative and positive ion flux collected on its target to a bipolar signal proportional to the energy per unit charge as determined by the optic electro-static potential, solar wind flux, and direction. The output is dc-compressed at 2/3 of full scale input to keep the output swing to a reasonable value in measuring 5 magnitudes of signal range. Output is 3.2 millivolts for  $1 \times 10^{-14}$  amperes, approximately 7 volts for  $2 \times 10^{-11}$  amperes, and 21.5 volts for  $10^{-9}$  amperes. The output is positive for negative particles (limited to  $10^{-10}$  amperes) and negative for positive ions.

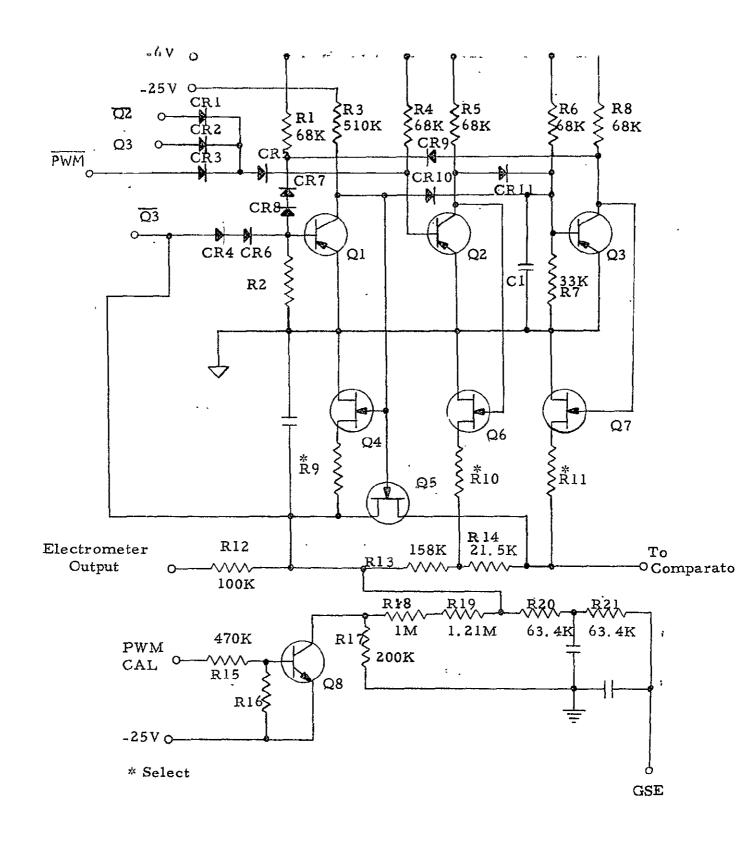

A Compression and Pulse Width Modulator performs a linear logarithmic compression on the piece-wise linear output of the electrometer amplifier. The output of this section is a pulse width modulated signal logarithmically proportional to the input flux. Maximum pulse width is equal to minimum flux and minimum pulse width is equal to maximum flux.

An A/D converter converts the pulse width modulated signal into a 7 bit binary word. It also converts the High Voltage Analog into a logarithmically compressed 7 bit binary number.

The Target Programmer logically controls the 3 targets and related information into other subsystems.

The Sector Programmer's primary function is to divide the spacecraft revolution into 128 (7bit) equal segments. It also furnishes section timing signals to other subsystems.

The Timing and Control section provides all central timing, control and mode signals for the instrument.

The Buffer Storage subsection provides temporary storage of input data to meet the telemetry readout rate.

The High Voltage Programmer controls the High Voltage Power Supply and provides 7 cycles of 30 ion reference steps and one cycle of 15 electron reference steps. It also programs the suppression voltage requirements.

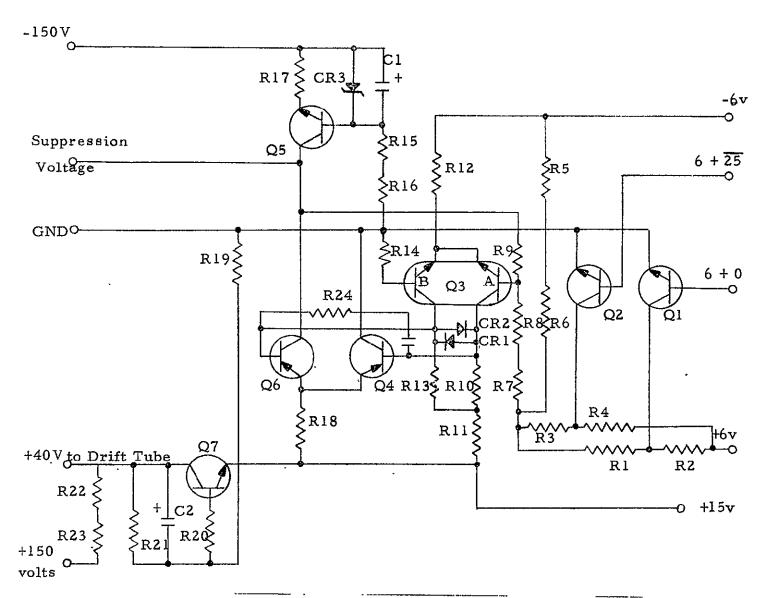

The High Voltage Power Supply generates the balanced stepping high voltage for the analyzer plates in the optics section. It also provides all suppression and related voltages.

The Low Voltage Power Supply converts the spacecraft 28 volts into the required instrument voltages.

Ground Support Equipment (GSE) has been designed to stimulate the spacecraft electronics normally interfacing with the Plasma Probe Instrument. The GSE provides the stimulus, timing signals, and power necessary to operate and test the flight hardware. The GSE also provides a readout capability which is synchronized to the stimulation of the sensor for measuring and recording system inputs, outputs, and performance parameters.

|         |                                      | Page |

|---------|--------------------------------------|------|

| 1.0     | INTRODUCTION                         | 1    |

| 1.1     | Scope                                | i    |

| 1.2     | Delivered Units                      | 2    |

| 2.0     | GENERAL DESCRIPTION                  | 2    |

| 2.1     | Subsystems General Description       | 10   |

| 2.1.1   | Electrometer Amplifier               | 15   |

| 2.1.1.1 | Optics                               | 15   |

| 2.1.1.2 | Electrometer .                       | 15 . |

| 2.1.1.3 | Attenuator and Pulse Width Modulator | 15   |

| 2.1.2   | Logic                                | 15   |

| 2.1.2.1 | Timing and Control                   | 15   |

| 2.1.2.2 | Sector Programmer                    | 16   |

| 2.1.2.3 | Target Programmer                    | 16   |

| 2.1.2.4 | High Voltage Programmer              | 16   |

| 2.1.2.5 | High Voltage A/D Converter           | 16   |

| 2.1.2.6 | Commutator                           | 17   |

| 2.1.2.7 | Status Decoder                       | 17   |

| 2.1.2.8 | Calibrate and Sector Delay Mode      | 17   |

| 2.1.2.9 | Temperature Sensor                   | 17   |

| 2.1.3   | Buffer Storage                       | 17   |

| 2.1.4   | Power Supplies                       | 18   |

| 2.1.4.1 | Low Voltage Power Supply             | 18   |

| 2.1.4.2 | High Voltage Power Supply            | 18   |

| 3.0     | ELECTRICAL SYSTEM DESCRIPTION        | 19   |

| 3.1     | Electrometer Amplifier and Optics    | 19   |

| 3.1.1   | Optics                               | 19   |

| 3.1.2   | Electrometer                         | 23   |

| 3.1.3   | Attenuator and Pulse Width Modulator | 32   |

| 3.1.4   | Pulse Width Modulator Programmer     | 32   |

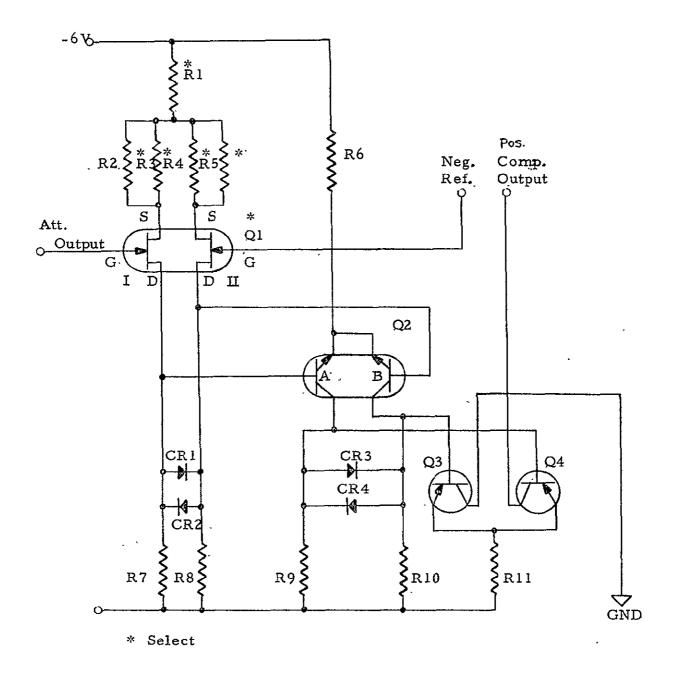

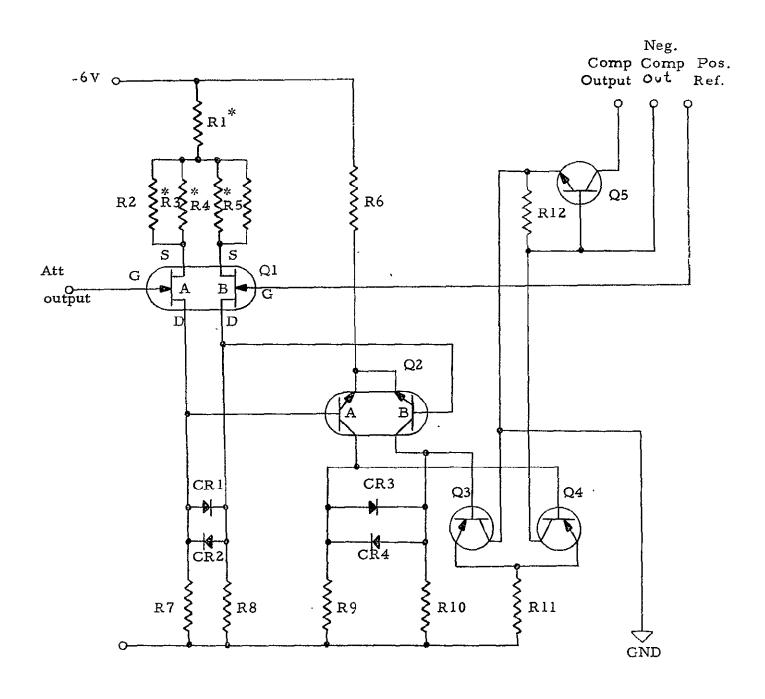

| 3.1.5   | Comparators                          | 36   |

| 3.1.6   | Reference Generator Network          | 36   |

| 3.1.7   | Suppression Circuit                  | 40   |

|          |                                             | Page     |    |

|----------|---------------------------------------------|----------|----|

| 3,2      | Buffer Logic                                | 40       |    |

| 3.2.1    | Timing and Control                          | 40       |    |

| 3.2.1.1  | Voltage Controlled Oscillator               | 43       |    |

| 3.2.1.2  | A/D Clock                                   | 43       |    |

| 3.2.1.3  | Sun Pulse Delay                             | 43       |    |

| 3.2.1.4  | Spoke Generator                             | 45       |    |

| 3.2.1.5  | Sector Detector                             | 47       |    |

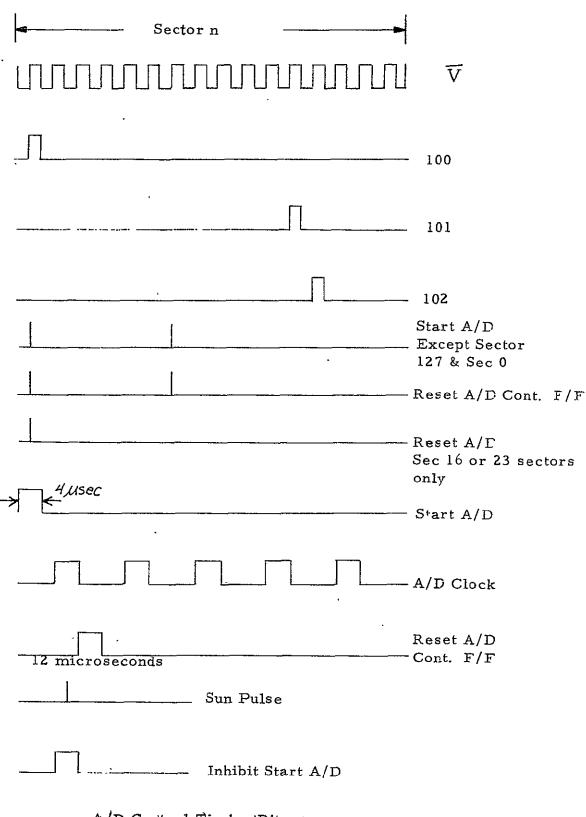

| 3.2.1.6  | A/D Control                                 | 47       |    |

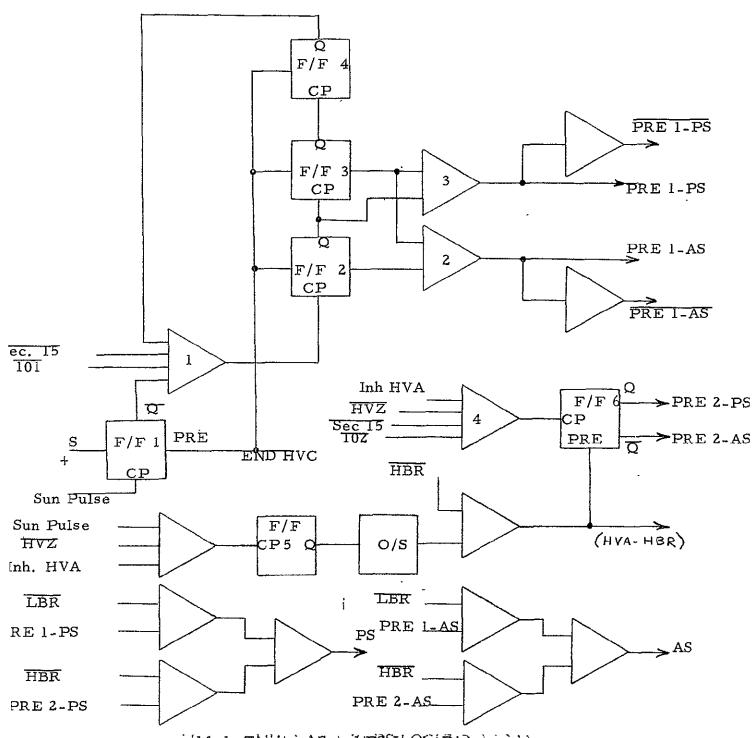

| 3.2.1.7  | Mode Timing                                 | 62       |    |

| 3.2.2    | Target Programmer                           | 68       |    |

| 3.2.3    | Digital Comparator and Long Term Storage    | Register | 71 |

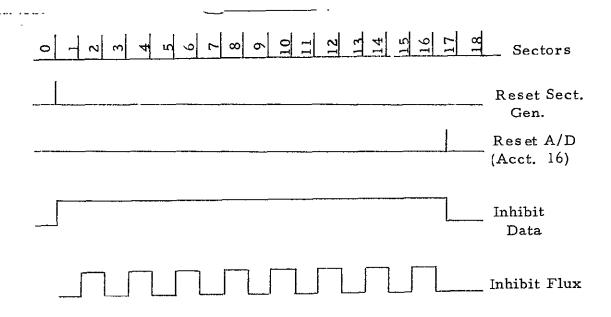

| 3.2.4    | Sector Programmer                           | 75       |    |

| 3.2.5    | High Voltage Programmer                     | 77       |    |

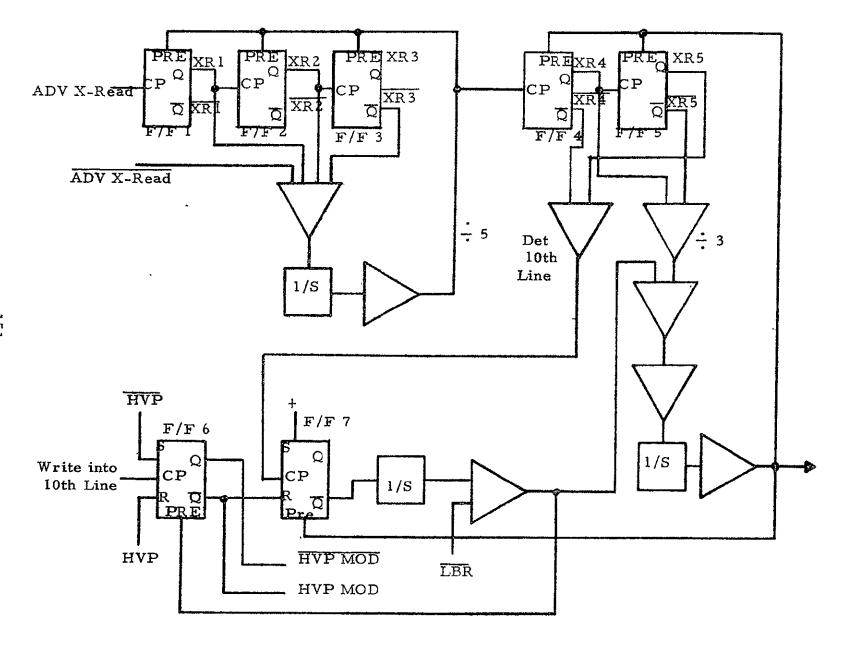

| 3.2.5.1  | High Voltage Advance                        | 81       |    |

| 3.2.5.2  | Inhibit Step Logic                          | 81       |    |

| 3.2.5.3  | Step Counter                                | 81       |    |

| 3.2.5.4  | Force High Voltage Zero Logic               | 86       |    |

| 3.2.5.5  | End-of-Cycle Logic                          | 86       |    |

| 3.2.5.6  | Reset Logic                                 | 86       |    |

| 3.2.5.7  | Step Register                               | 86       |    |

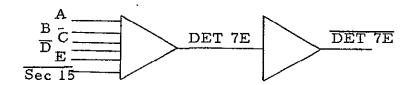

| 3.2.5.8  | Detect 7E Logic                             | 92       |    |

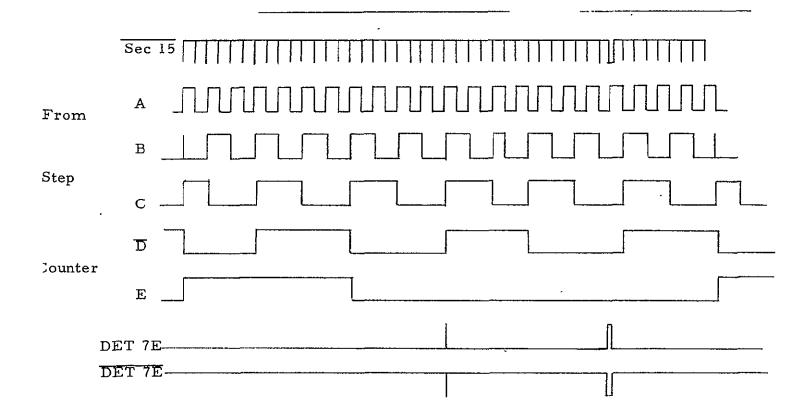

| 3.2.5.9  | Transfer Logic                              | 92       |    |

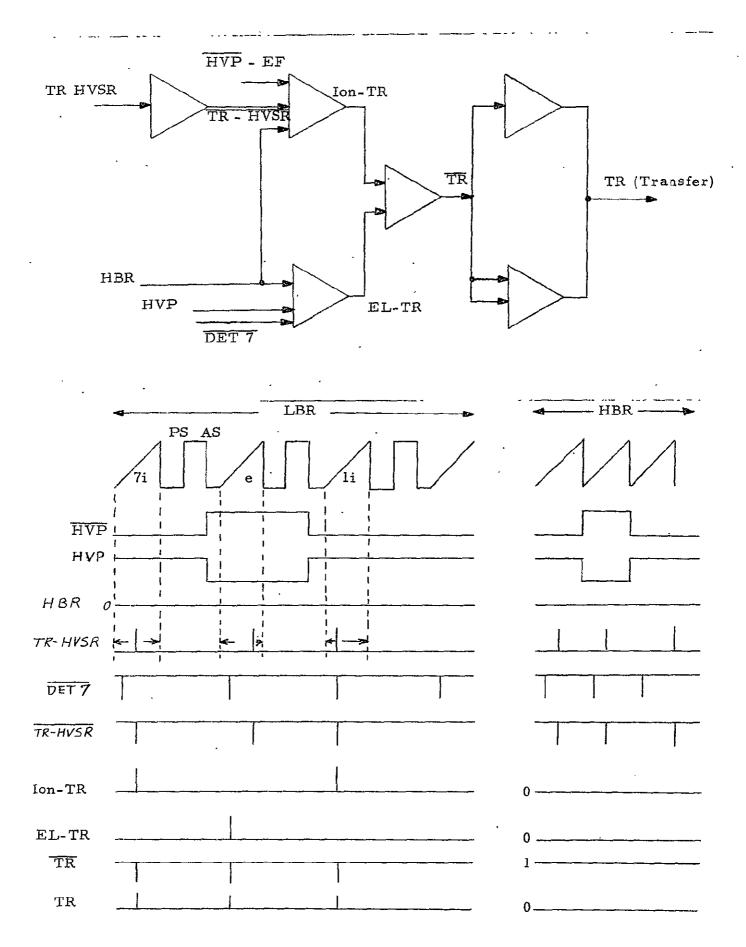

| 3.2.5.10 | Ramp Gate                                   | 92       |    |

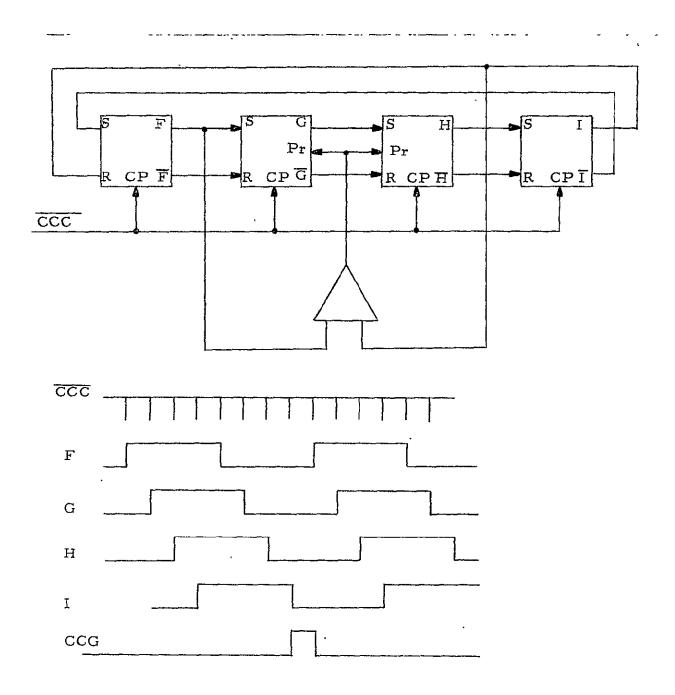

| 3.2.5.11 | Cycle Counter Clock                         | 92       |    |

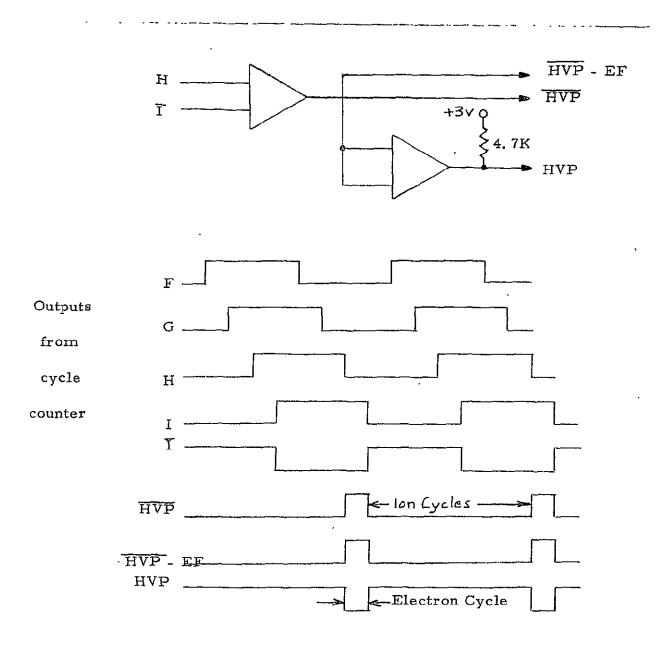

| 3.2.5.12 | Polarity Logic                              | 98       |    |

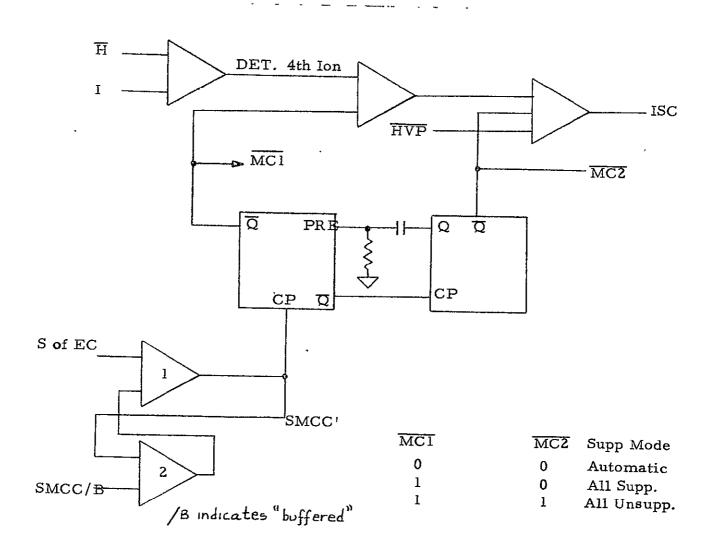

| 3.2.5.13 | Ion Suppression Logic                       | 98       |    |

| 3.2.5.14 | Electron Suppression Logic                  | 98       |    |

| 3.2.5.15 | Suppressed Identification Logic             | 104      |    |

| 3.2.5.16 | Initiate Suppressed Mode Logic              | 104      |    |

| 3.2.5.17 | Suppressed Voltage Logic                    | 104      |    |

| 3.2.6    | High Voltage Zero and Stabilization Control | 107      |    |

| 3.2.7    | High Voltage A/D                            | 111      |    |

| 3.2.8    | Commutator and Intermediate Storage Regis   | ster 113 |    |

| 3.2.9    | Write Pulse Generator                       | 115      |    |

| 3.2.10   | Shift Pulse Generator                       | 122      |    |

| 3.2.11   | Calibration                                 | 125      |    |

| 3, 2, 12 | Status Decoder                              | 127      |    |

|         |                                                              | Page |

|---------|--------------------------------------------------------------|------|

| 3.3     | Buffer Storage                                               | 13 Į |

| 3.3.1   | Core Plane Memory                                            | 136  |

| 3.3.1.1 | Memory Organization                                          | 136  |

| 3.3.1.2 | Memory Operation                                             | 142  |

| 3.3.2   | Buffer Interfaces                                            | 147  |

| 3.3.3   | Y Counters                                                   | 147  |

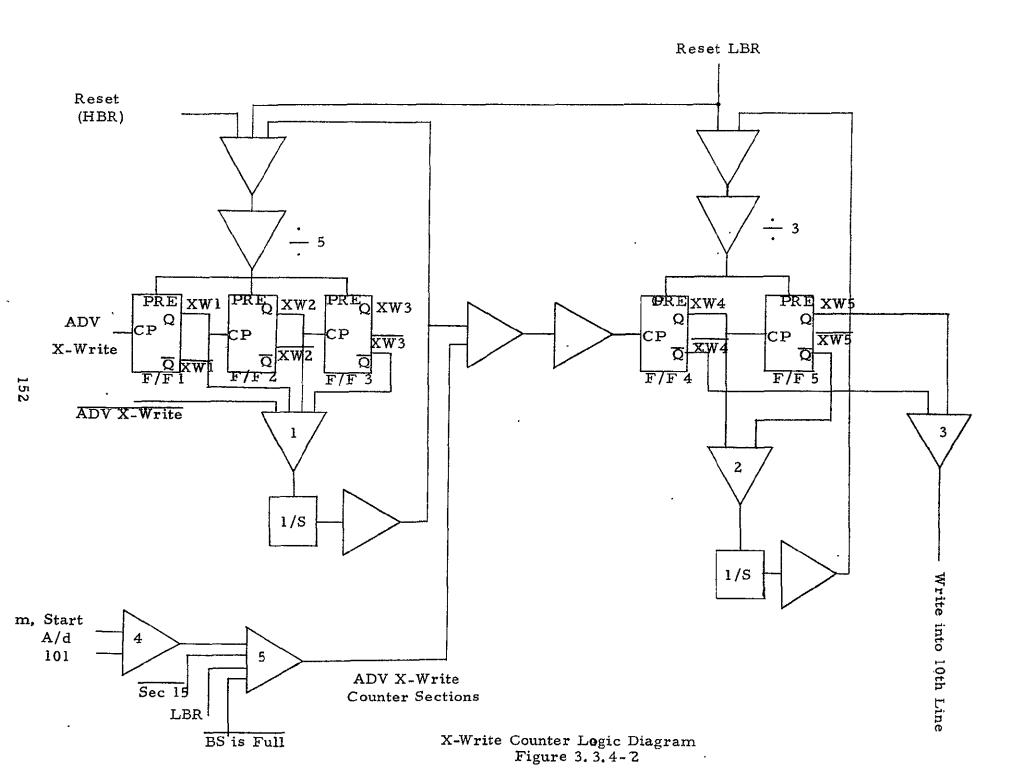

| 3.3.4   | X Counters                                                   | 150  |

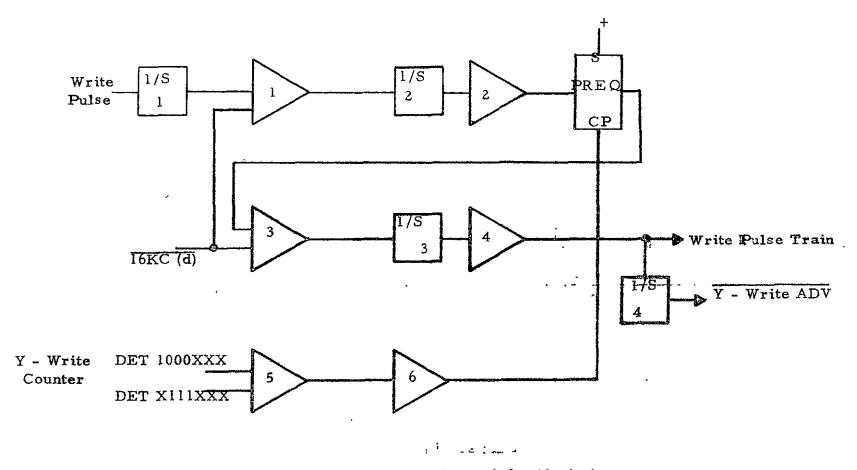

| 3.3.5   | Write Pulse Train Generator                                  | 156  |

| 3.3.6   | Frame ID Counter                                             | 156  |

| 3.3.7   | Inhibit Read-Write                                           | 161  |

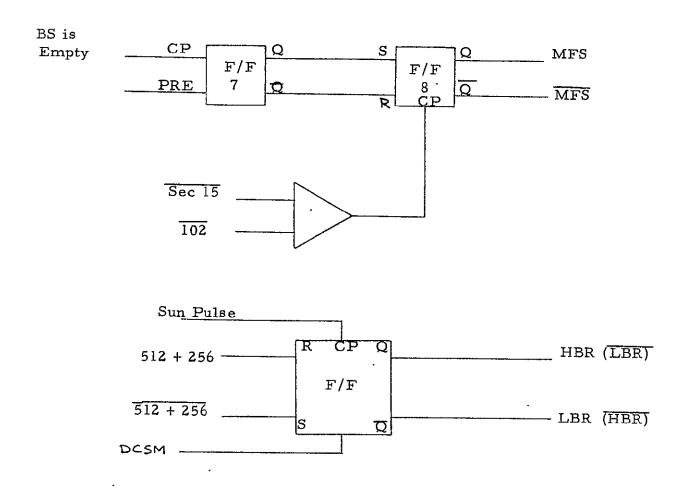

| 3.3.8   | BS is Empty                                                  | 165  |

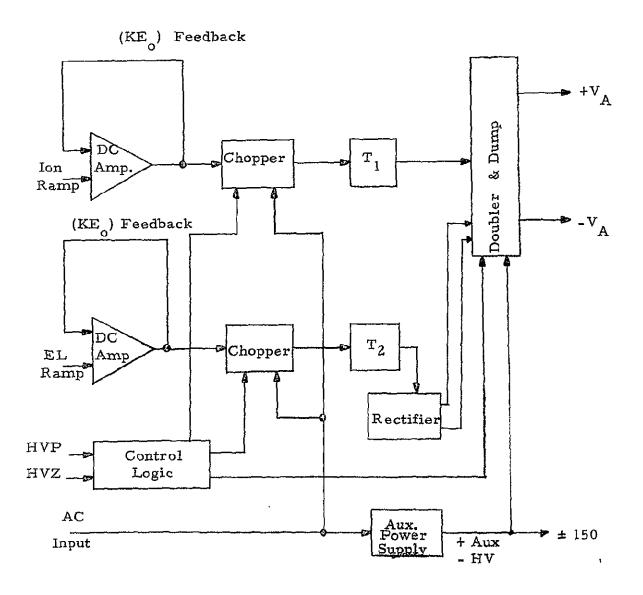

| 3.4     | High Voltage Power Supply                                    | 168  |

| 3.4.1   | Input's and Outputs                                          | 168  |

| 3.4.2   | Operation                                                    | 168  |

| 3.4.2.1 | Slewing Capacitor                                            | 174  |

| 3.4.2.2 | Chopper                                                      | 174  |

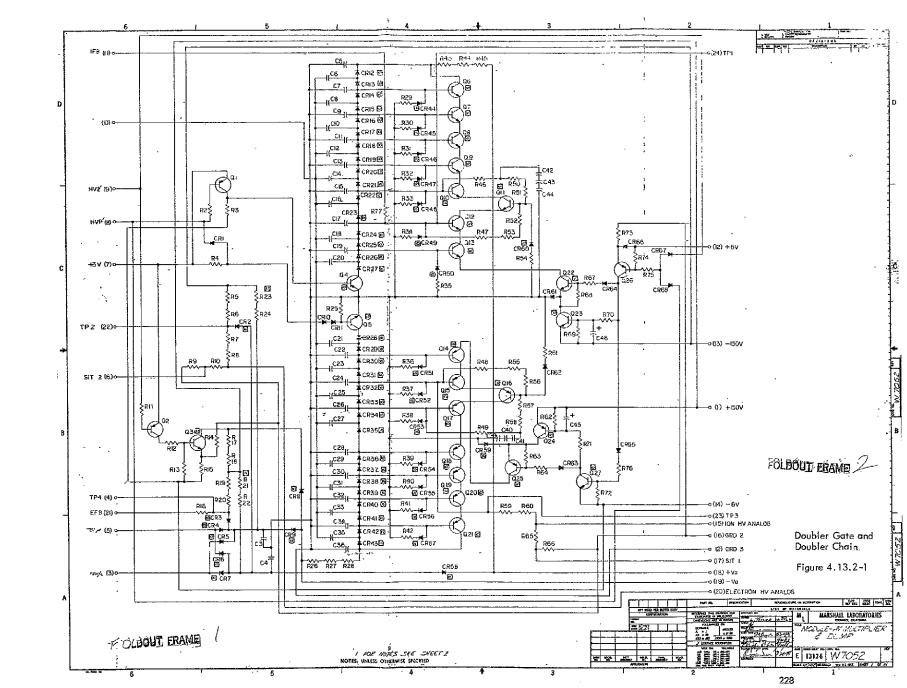

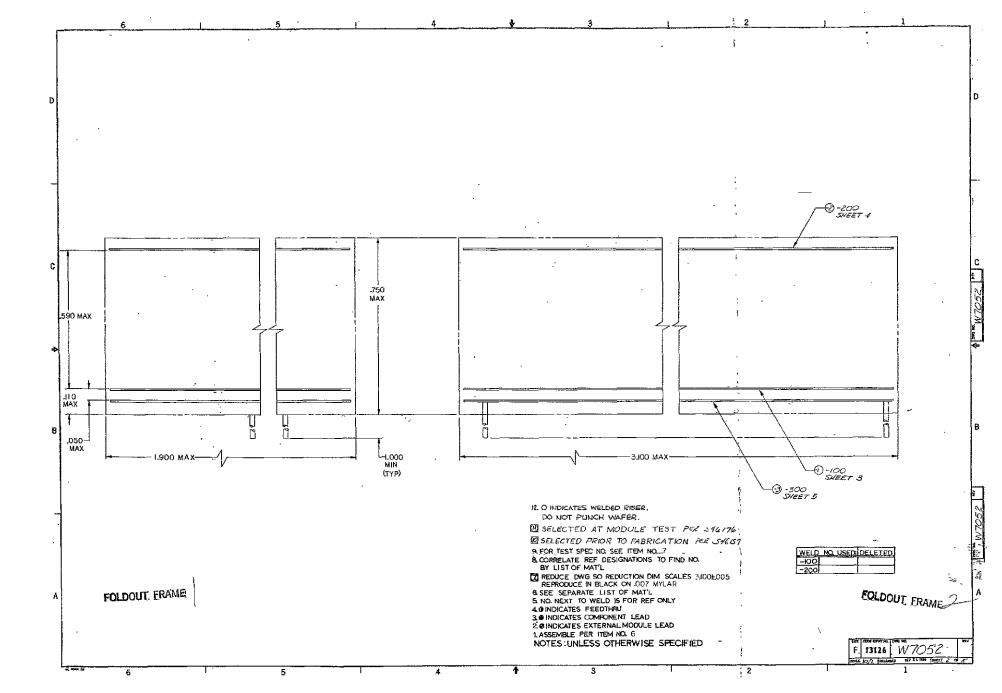

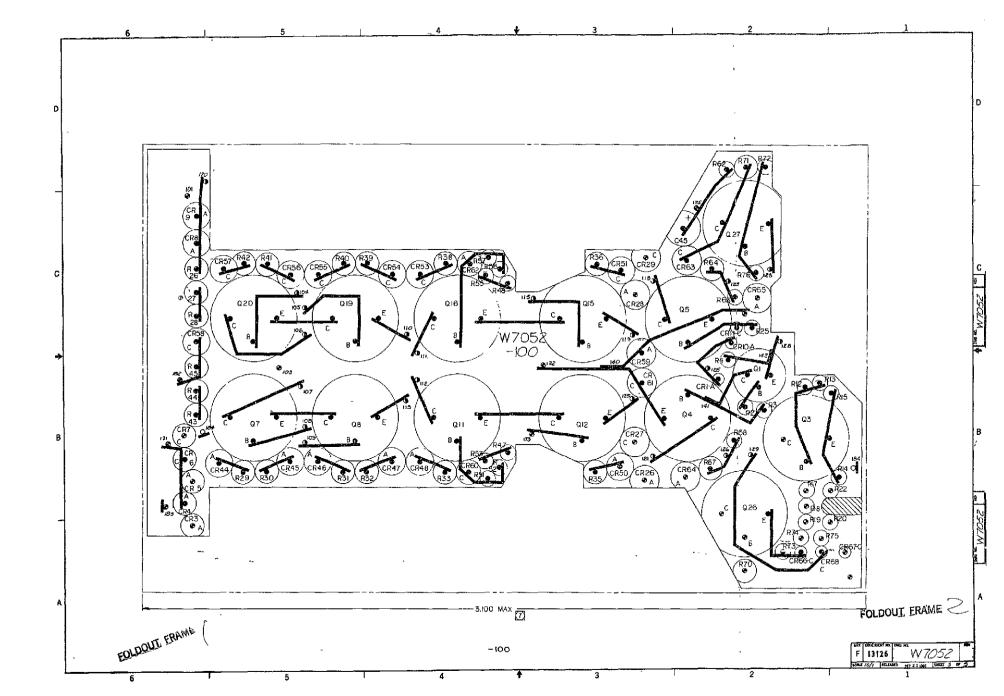

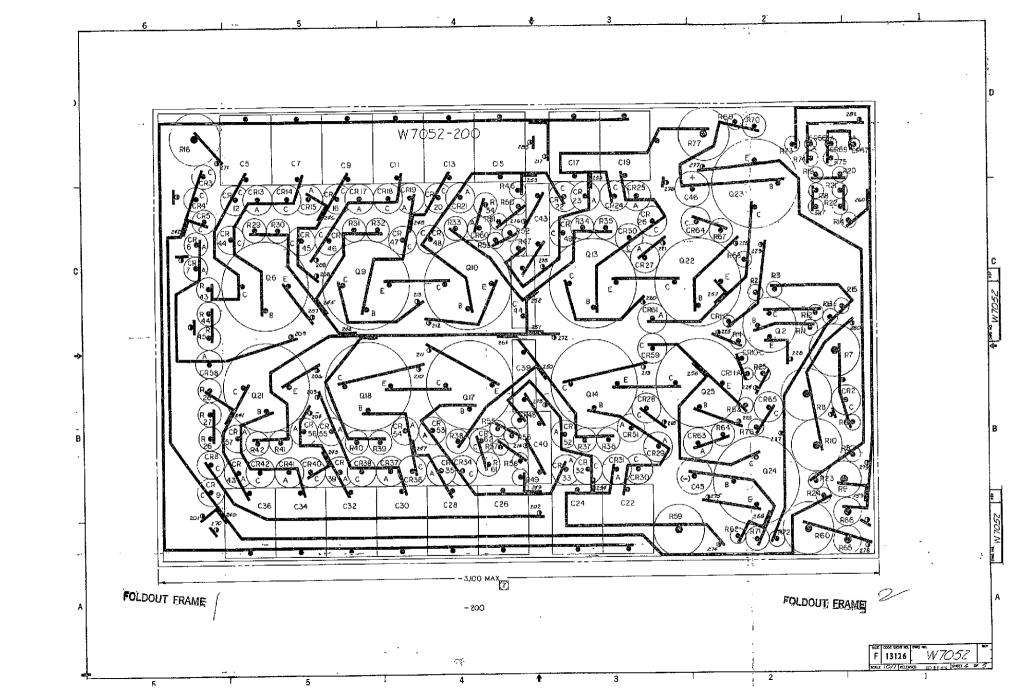

| 3.4.2.3 | Doubler Gate and Doubler Chain                               | 174  |

| 3.4.2.4 | Dump Circuitry                                               | 175  |

| 3.4.2.5 | Control Logic                                                | 175  |

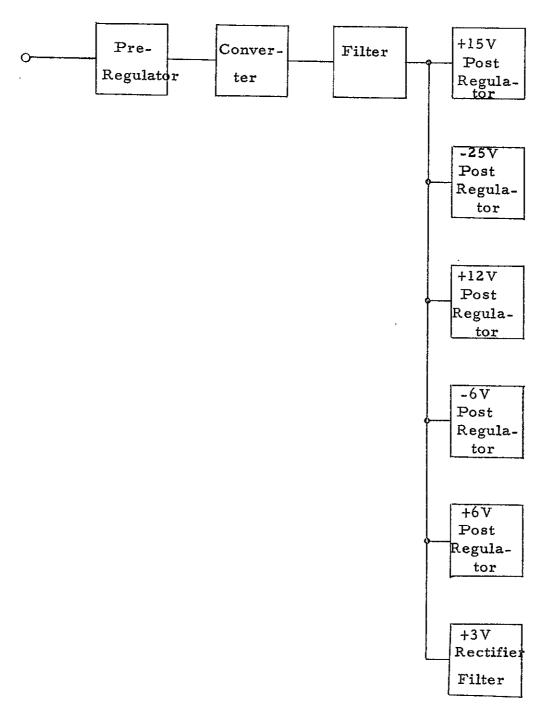

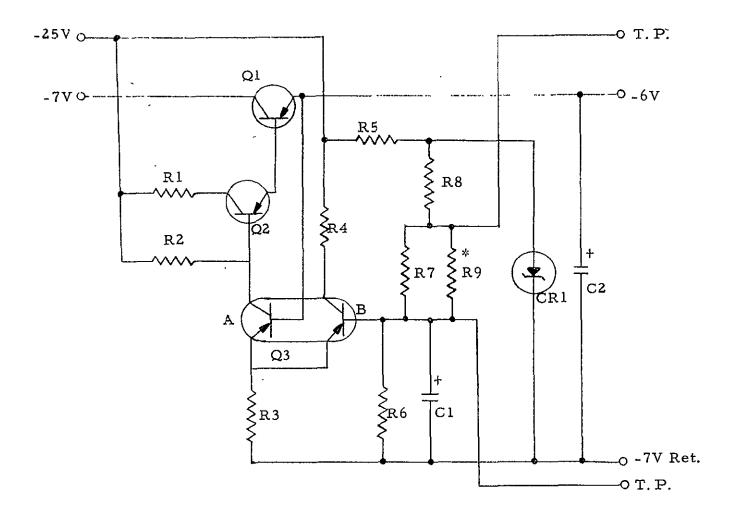

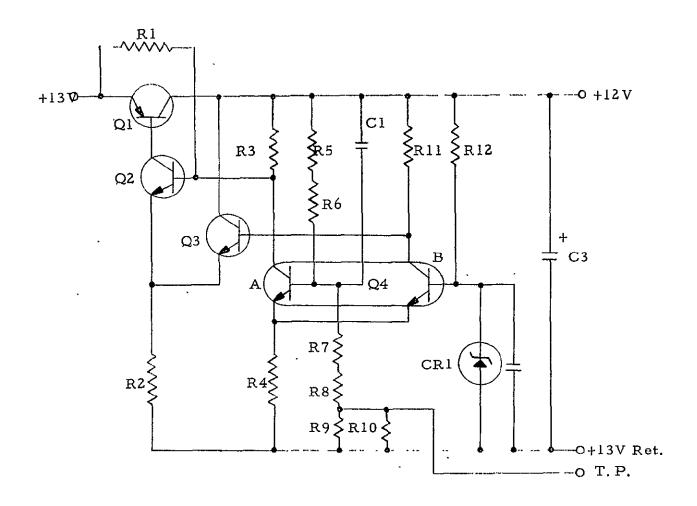

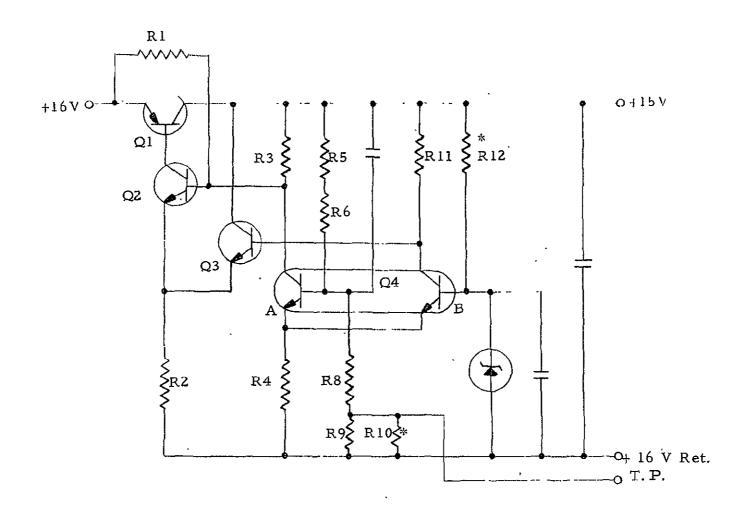

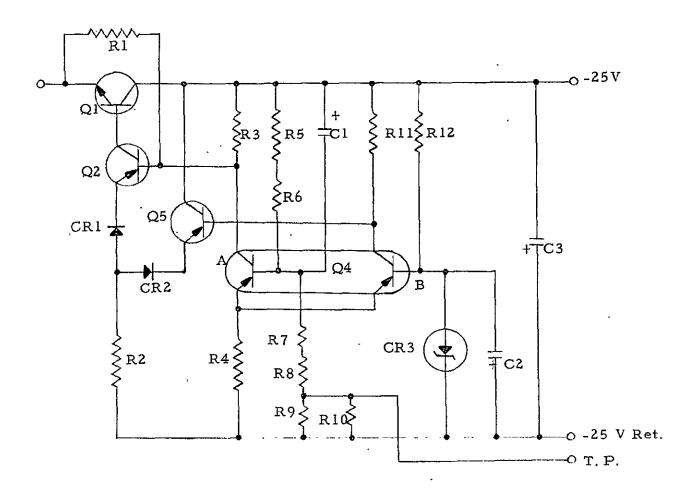

| 3,5     | Low Voltage Power Supply                                     | 175  |

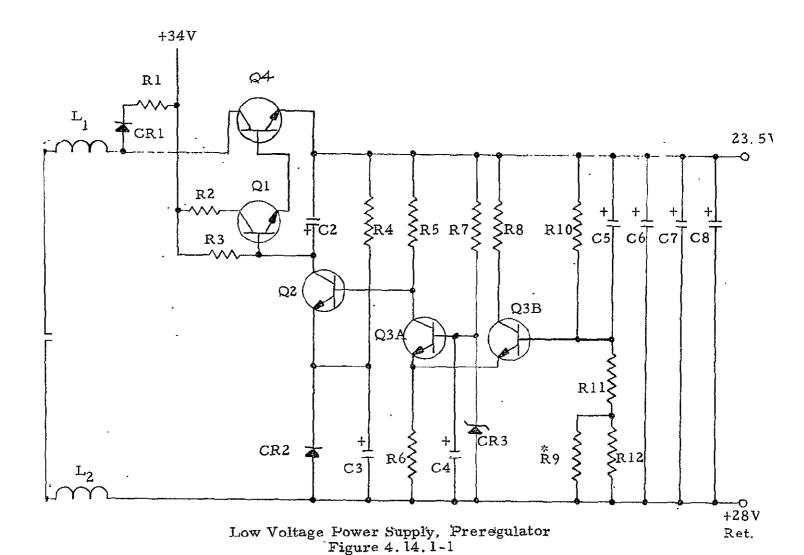

| 3.5.1   | Pre-regulator                                                | 177  |

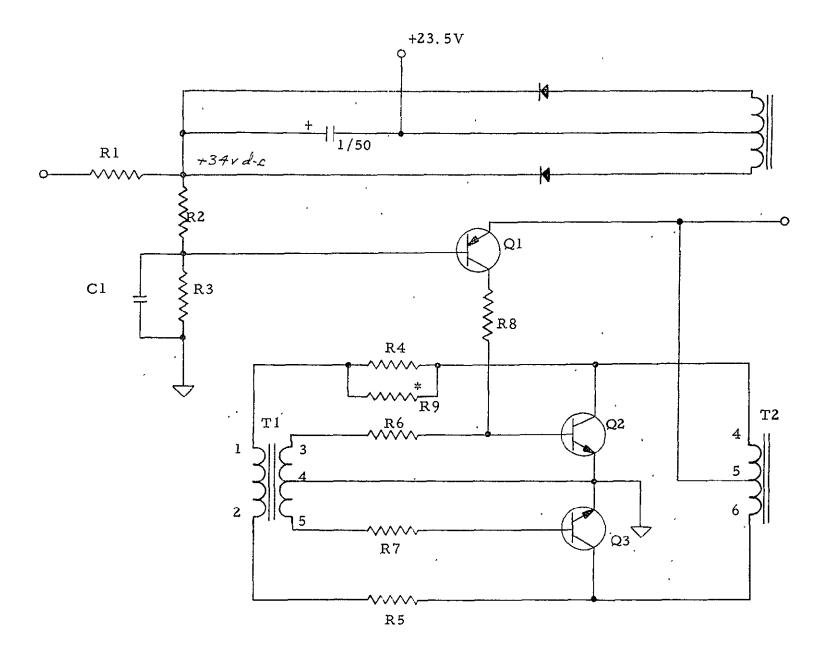

| 3.5.2   | Chopper                                                      | 177  |

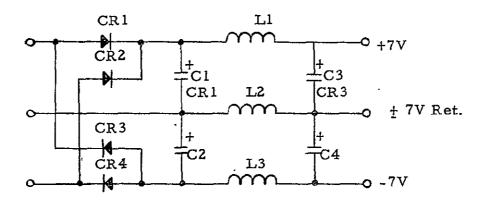

| 3.5.3   | Rectifier Filter                                             | 177  |

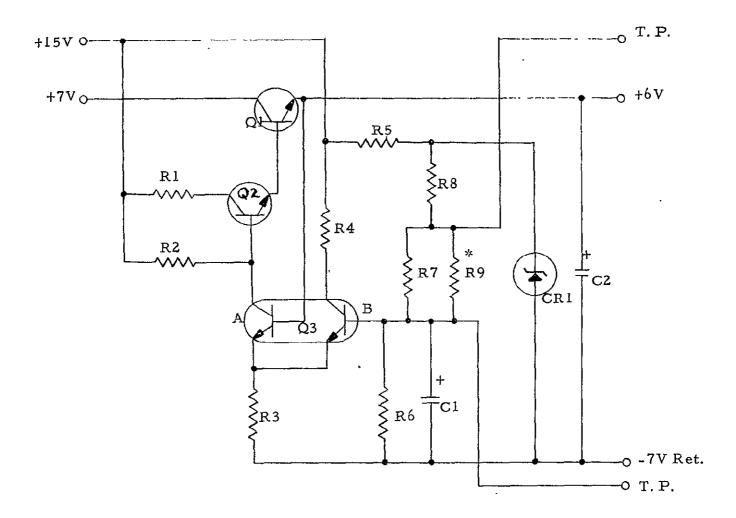

| 3.5.4   | Post Regulator                                               | 177  |

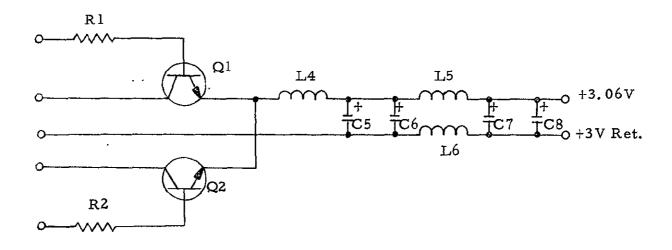

| 3.5.5   | Filament Power Supply                                        | 179  |

| 4.0     | CIRCUIT DESCRIPTIONS                                         | 179  |

| 4.1     | Electrometer Amplifier                                       | 179  |

| 4.1.1   | Stabilization Buffer                                         | 179  |

| 4.1.2   | Stabilization Amplifier                                      | 179  |

| 4.1.3   | Stabilization Storage                                        | 182  |

| 4.1.4   | Electrometer                                                 | 184  |

| 4.1.5   | Attenuator Driver and Attenuate and Calibrate                | 186  |

| 4.1.6   | Suppression Circuit                                          | 188  |

| 4.1.7   | Positive and Negative Comparators                            | 190  |

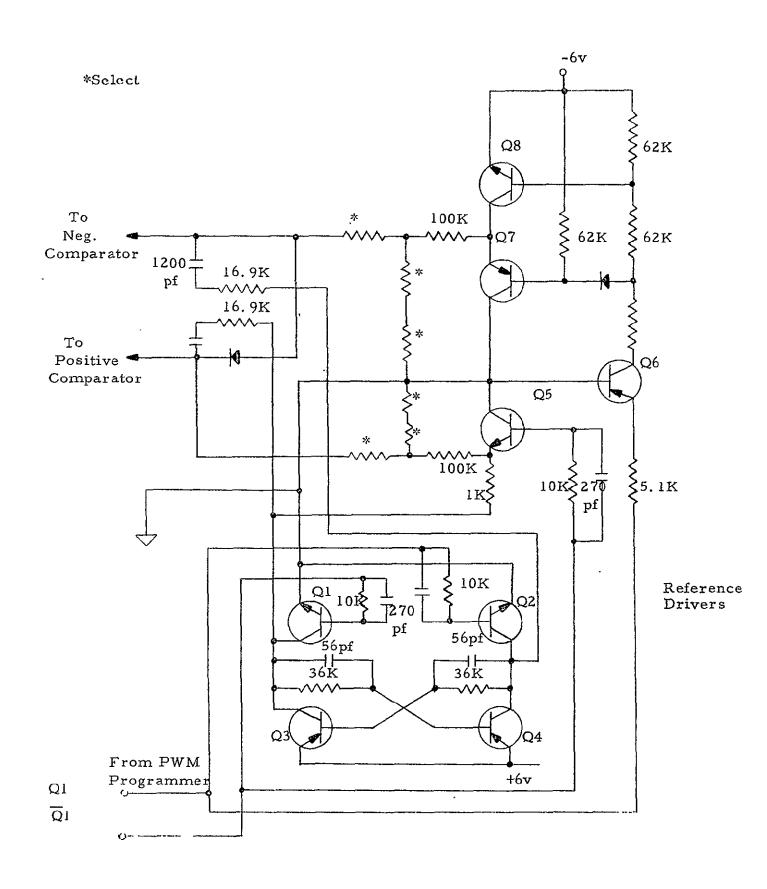

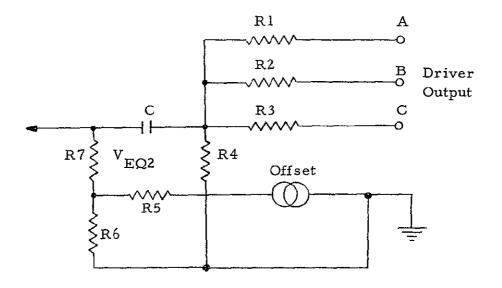

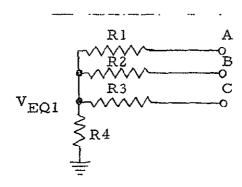

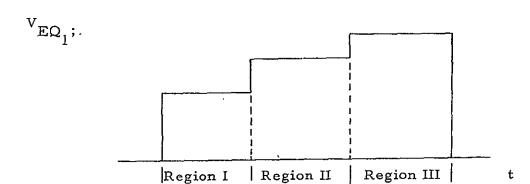

| 4.1.8   | Reference Generator, Offset Generator, and Reference Drivers | 193  |

| 4 1 8 1 | Reference Generator and Offset Generator                     | 196  |

|        |                                  | $\underline{\text{Page}}$ |

|--------|----------------------------------|---------------------------|

| 4.2    | High Voltage Comparator          | . 203                     |

| 4.3    | Temperature Sensor               | 206                       |

| 4.4    | Current Switches                 | 207                       |

| 4.5    | Current Drivers                  | 211                       |

| 4.6    | Gate Switch                      | 213                       |

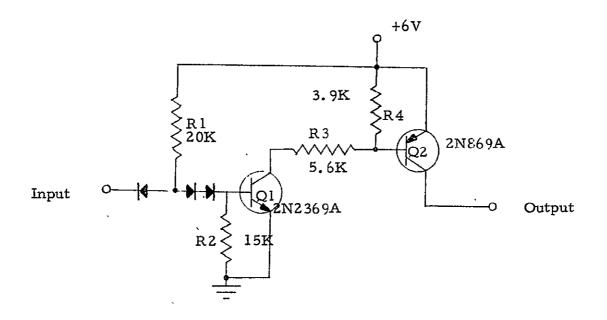

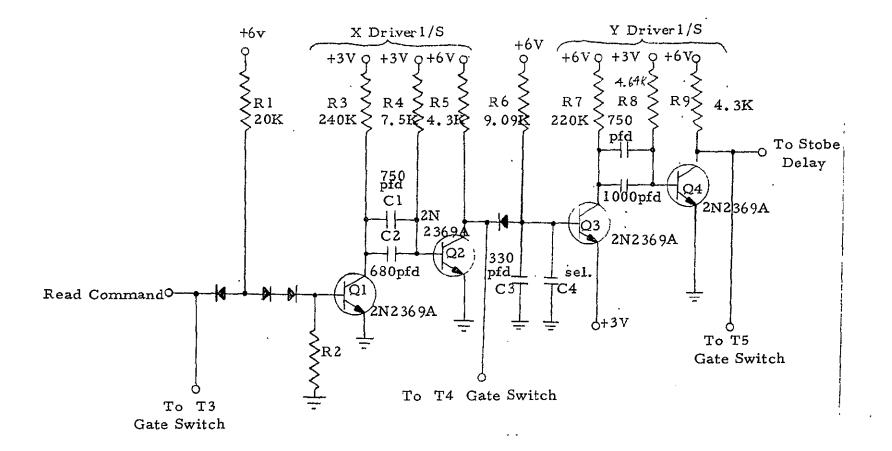

| 4.7    | Read Timing Circuit              | 215                       |

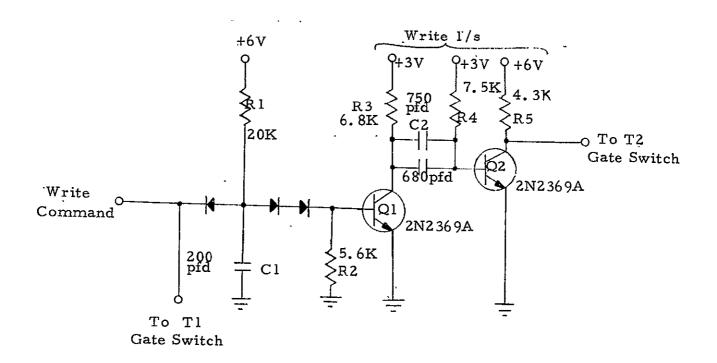

| 4.8    | Write Timing Circuit             | 217                       |

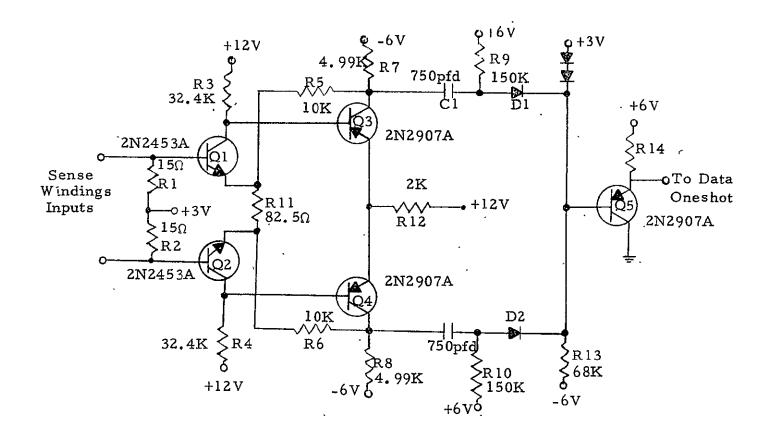

| 4.9    | Sense Amplifier                  | 219                       |

| 4.10   | Strobe Delay and Data One-Shot   | 221                       |

| 4.11   | Frame ID Driver                  | 223                       |

| 4.12   | Ion D-C Amplifier                | 223                       |

| 4.13   | High Voltage Power Supply        | 226                       |

| 4.13.1 | Chopper                          | 226                       |

| 4.13.2 | Doubler Gate and Doubler Chain   | 226                       |

| 4.13.3 | Dump Circuitry                   | 229                       |

| 4.14   | Low Voltage Power Supply         | 230                       |

| 4.14.1 | Pre-regulator                    | 230                       |

| 4.14.2 | Chopper                          | 232                       |

| 4.14.3 | Post Regulators                  | 234                       |

| 4.14.4 | Filament Power Supply            | 234                       |

| 4.15   | Reliability Analysis             | 241                       |

| 5.0    | NEW TECHNOLOGY                   | 241                       |

| 6.0    | MECHANICAL AND THERMAL DESIGN    | 254                       |

| 6.1    | Optics Assembly Design           | 254                       |

| 6.2    | Electronics Packaging            | 263                       |

| 6.3    | Environmental Testing            | 272                       |

| 6.4    | Mechanical and Thermal Interface | 276                       |

| 7.0    | GROUND SUPPORT EQUIPMENT (GSE)   | 278                       |

| 7.1    | Function                         | 278                       |

| 7.2    | Environmental Range of Operation | 278                       |

| 7.3    | Delivered Items                  | 278                       |

| 7.4    | Performance Features             | 279                       |

| 7.5    | Interface                        | 280                       |

| 7.5.1  | System Inputs Provided by GSE    | 280                       |

| 7.5.2  | System Outputs Processed by GSE  | 282                       |

|                               |                                                                     | Page              |     |

|-------------------------------|---------------------------------------------------------------------|-------------------|-----|

| 7.6                           | Functional Description                                              | 282               |     |

| 7.6.1                         | Simulator Unit                                                      | 282               |     |

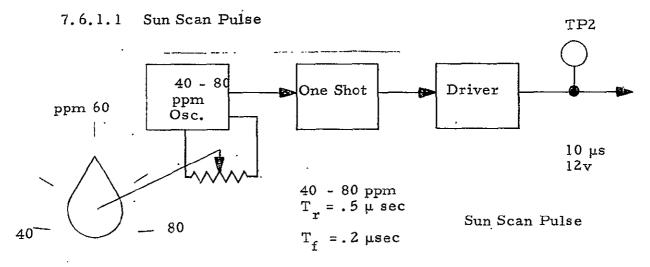

| 7.6.1.1                       | Sun Scan Pulse                                                      | 282               |     |

| 7.6.1.2                       | Commands                                                            | 284               |     |

| 7.6.1.3                       | Mode Select                                                         | 285               |     |

| 7.6.1.4                       | Word Gate Logic                                                     | 286               |     |

| 7.6.1.5                       | Power                                                               | 287               |     |

| 7.6.1.6                       | Miscellaneous Outputs                                               | 288               |     |

| 7.6.2                         | Print Cycle Calculations                                            | 290               |     |

| 7.6.3                         | Monitor and Control Unit                                            | 292               |     |

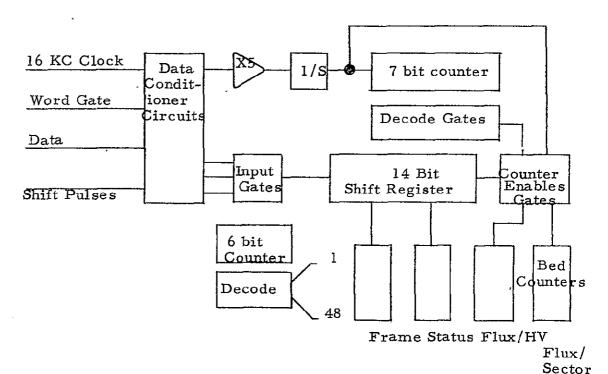

| 7.6.3.1                       | Input Data Encoding                                                 | 292               |     |

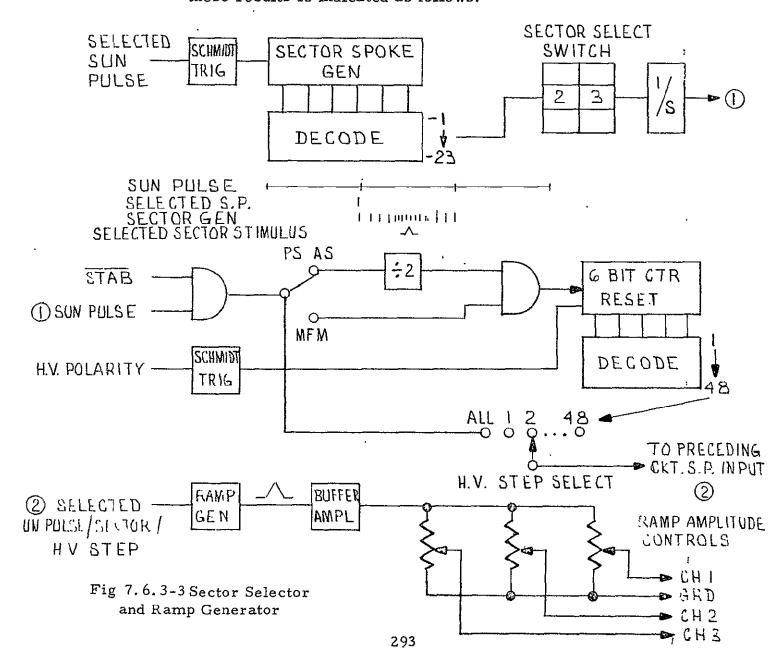

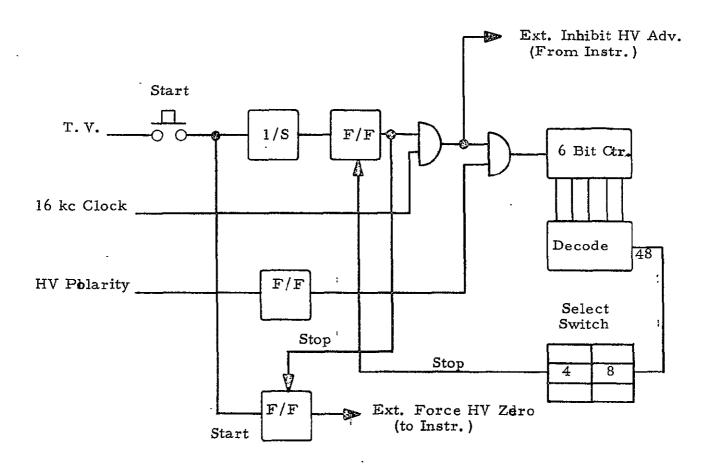

| 7.6.3.2                       | High Voltage Programmer Control                                     | 294               |     |

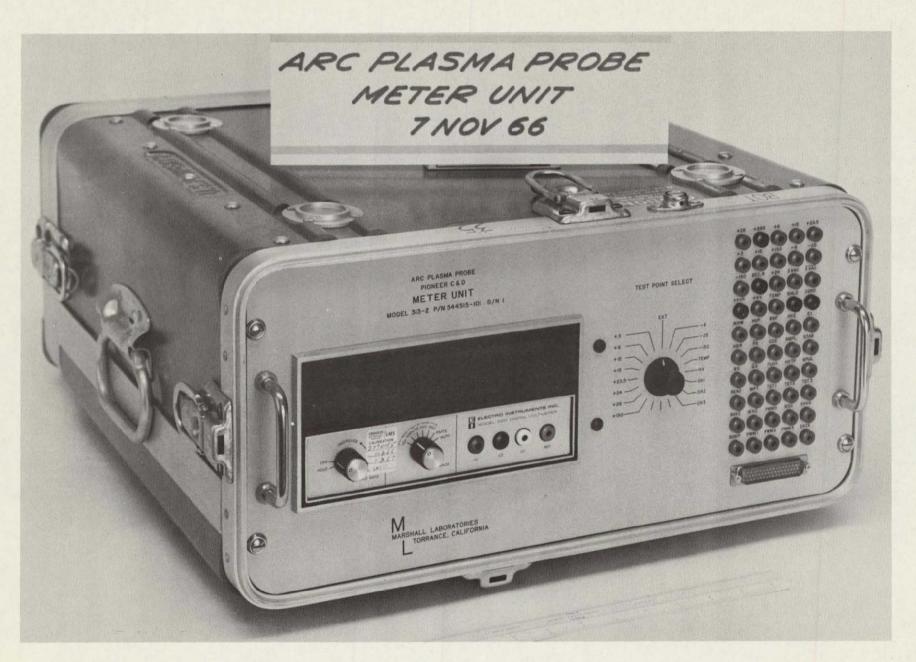

| 7.6.4                         | Meter Unit                                                          | 295               |     |

| 7.6.5                         | Printer Unit                                                        | 295               |     |

| 7.6.6                         | Current Probe Unit                                                  | 295               |     |

| 7.6.7                         | Demodulator                                                         | 300               |     |

| 8.0                           | PROBLEM AREAS AND SOLUTIONS; RECOMM                                 | MENDATIONS.       | 304 |

| 8.1<br>8.2<br>8.3<br>APPENDIX | Electromer Tube<br>Suppression Voltage Noise<br>High Voltage Corona | 304<br>304<br>305 |     |

| A                             | IC Logic                                                            |                   |     |

| В                             | Master Drawing List                                                 |                   |     |

|                               | Operational Test Specification                                      |                   |     |

|                               | Flight Acceptance Specification                                     |                   |     |

| С                             | Flight Acceptance Test Report                                       |                   |     |

| D                             | Memory Specification                                                |                   |     |

| E                             | Instrument Circuit Worst Case Analysis                              |                   |     |

| F                             | Reliability Analysis                                                |                   |     |

| G                             | Mechanical Stress Analysis                                          |                   |     |

| H                             | Shroud Heating Analysis                                             |                   |     |

| I                             | GSE Circuit and Worst Case Analysis                                 |                   |     |

# ILLUSTRATIONS

| Figure No. |                                                             | Page |

|------------|-------------------------------------------------------------|------|

| 2, 0-1     | Data Format                                                 | ` 3  |

| 2.0-2      | Azimuthal Scan Diagram                                      | 6    |

| 2.0-3      | HV Stepping Sequence, LBR                                   | 8    |

| 2.0-4      | HV Stepping Sequence, HBR                                   | 8    |

| 2.0-5      | Electrical Interface Wiring Diagram                         | 11   |

| 2.1-1      | Functional Block Diagram - Plasma Probe                     | 13   |

| 2.1-2      | Interconnect Schematic                                      | 14   |

| 3.1.1-1    | Optics Configuration                                        | 20   |

| 3, 1, 1-2  | Boundary Conditions at Entrance Aperture                    | 22   |

| 3.1.2-1    | Electrometer Simplified Block Diagram                       | 24   |

| 3.1.2-2    | Electrometer Transfer Characteristics, Ion Mode             | 27   |

| 3.1.2-3    | Electrometer Transfer Characteristics,<br>Electron Mode     | 28   |

| 3.1.2-4    | Electrometer Equivalent Circuit                             | 29   |

| 3.1.2-5    | Electrometer Feedback Equivalent Network $(Z_f)$            | 29   |

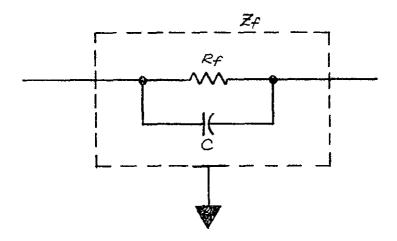

| 3, 1, 2-6  | Electrometer Interconnect Diagram                           | 31   |

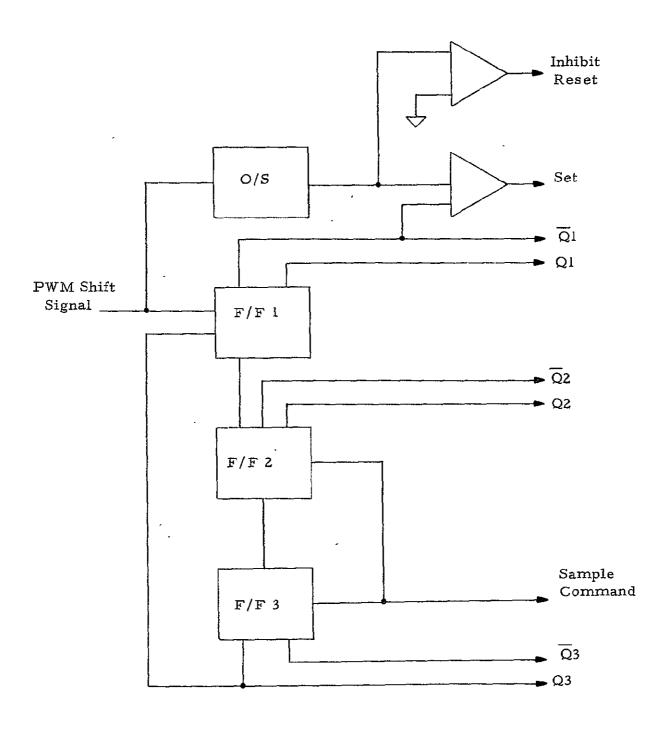

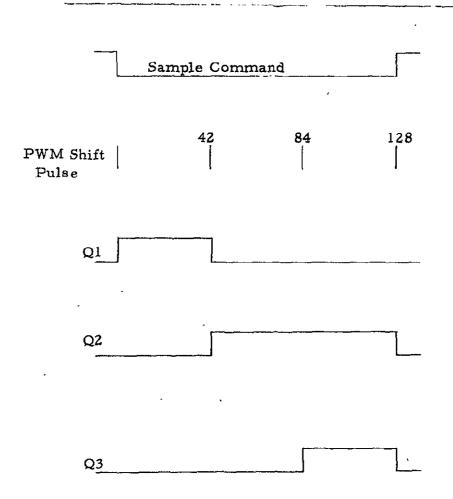

| 3, 1, 3-1  | Pulse Width Modulator Programmer, Block Diagram             | 33   |

| 3.1.4-1    | Pulse Width Modulator and Attenuator<br>Block Diagram       | 34   |

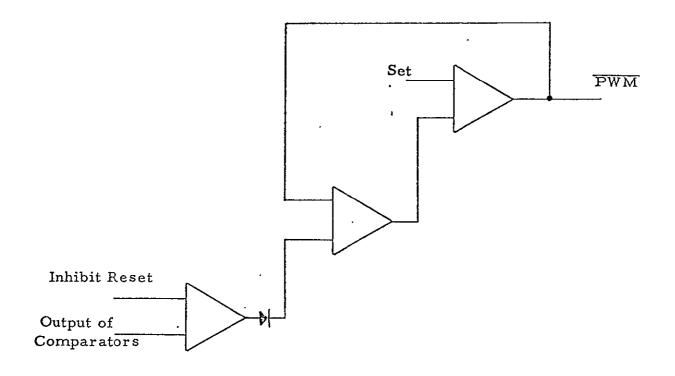

| 3.1.4-2    | Pulse Width Modulator Programmer Input and Output Waveforms | 35   |

| 3.1.4-3    | Logic Programmer Block Diagram                              | 37   |

| 3.1.5-1    | Comparator Block Diagram                                    | 38   |

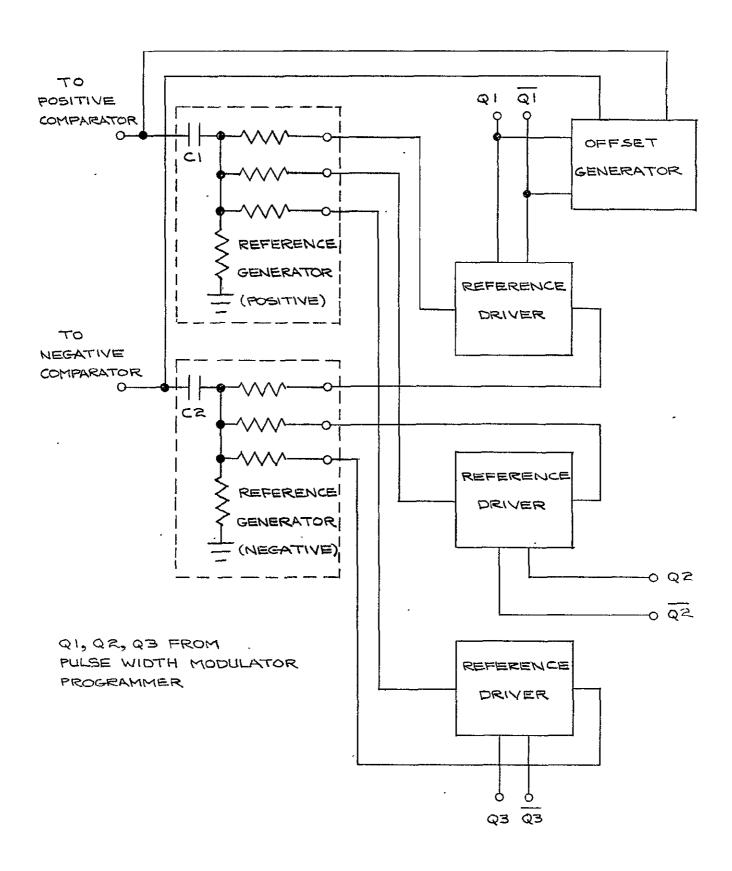

| 3.1.6-1    | Reference Generator Network Block Diagram                   | 39   |

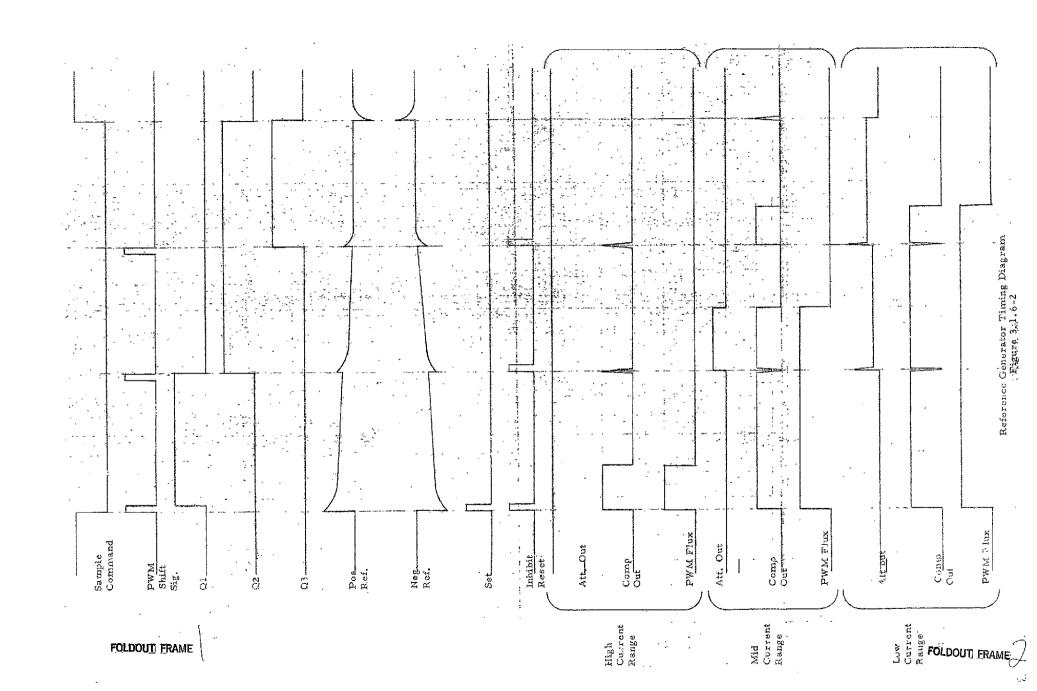

| 3.1.6-2    | Reference Generator Timing Diagram                          | 41   |

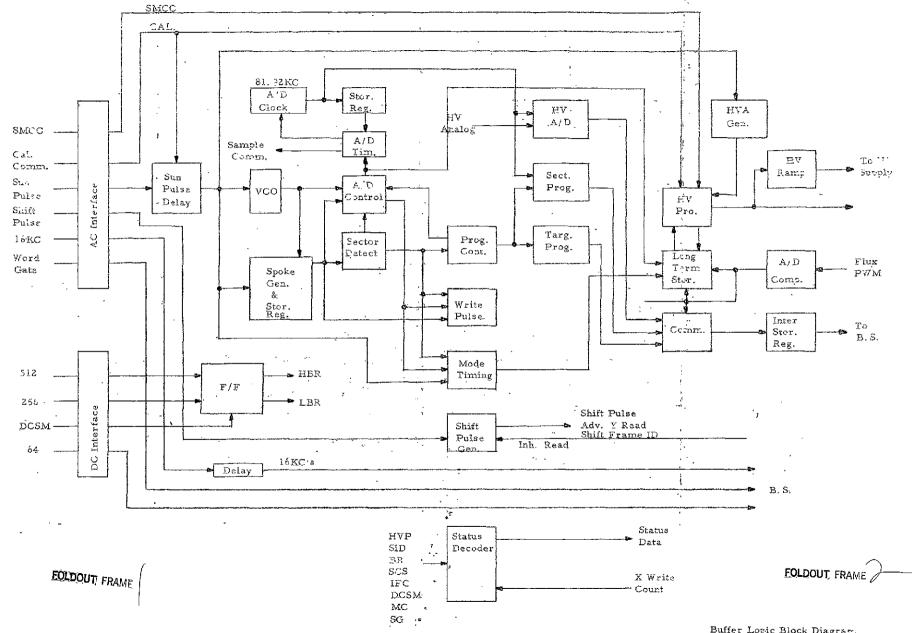

| 3.2-1      | Buffer Logic Block Diagram                                  | 42   |

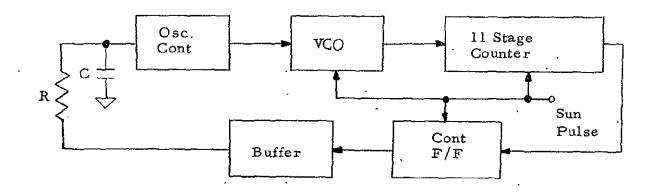

| 3.2.1-1    | Voltage Controlled Oscillator Block Diagram                 | 44   |

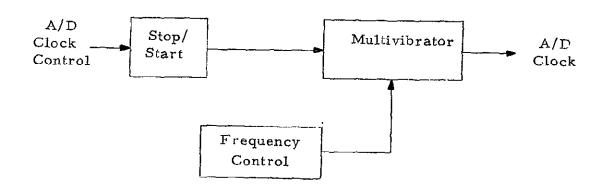

| 3.2.1-2    | A/D Clock Block Diagram                                     | 44   |

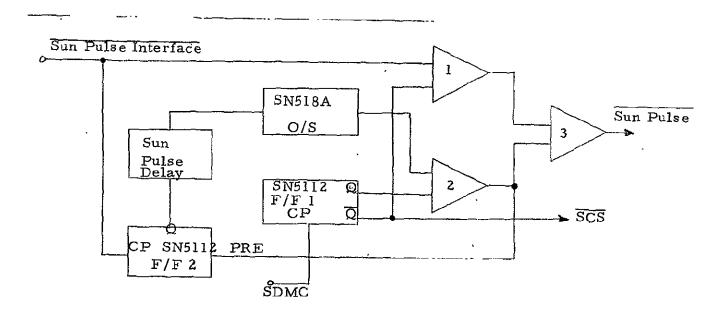

| 3.2.l-3    | Sun Pulse Delay Network Block Diagram                       | 44   |

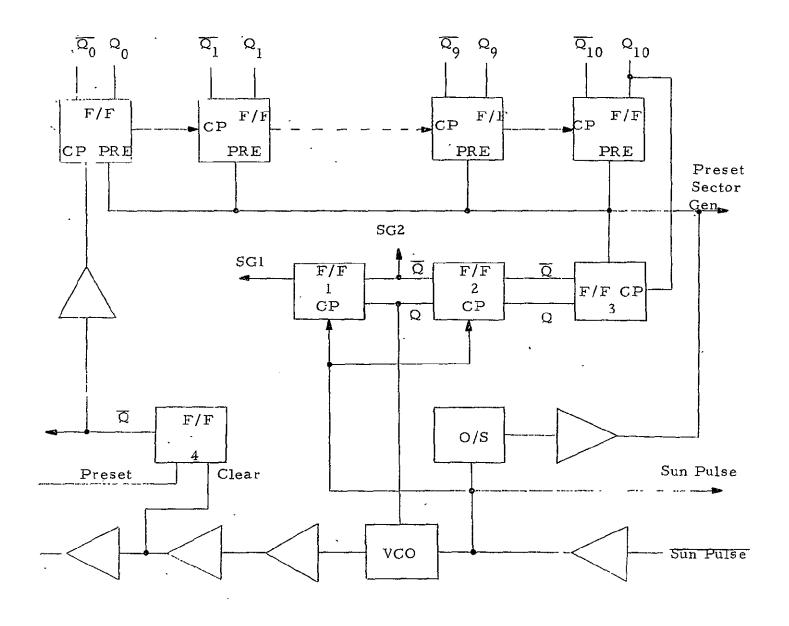

| 3.2.1-4    | Spoke Generator Block Diagram                               | 46   |

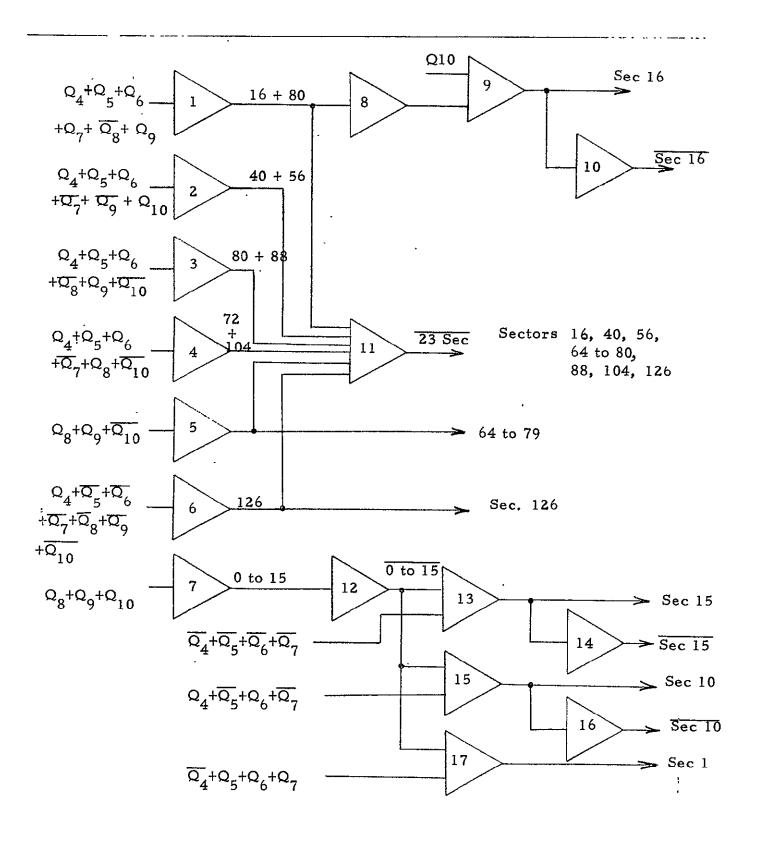

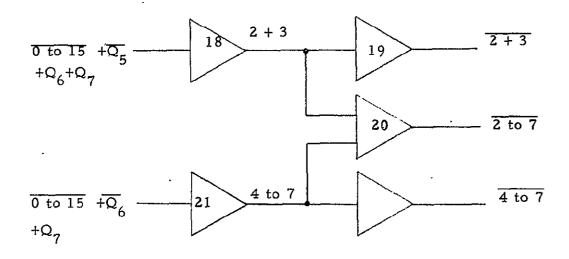

| 3.2.1-5    | Sector Detector Logic Diagram                               | 48   |

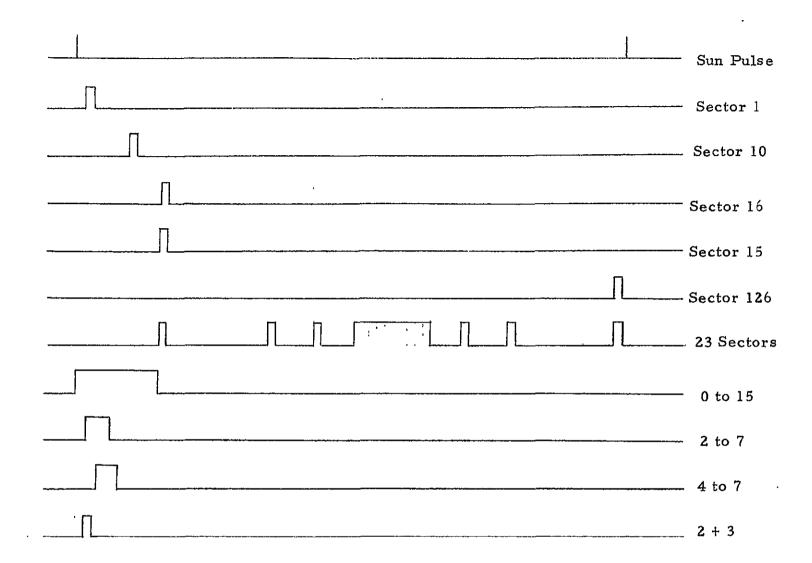

| 3. 2. 1-6  | Sector Detector Timing Diagram                              | 50   |

| Figure No.  |                                                   | Page |

|-------------|---------------------------------------------------|------|

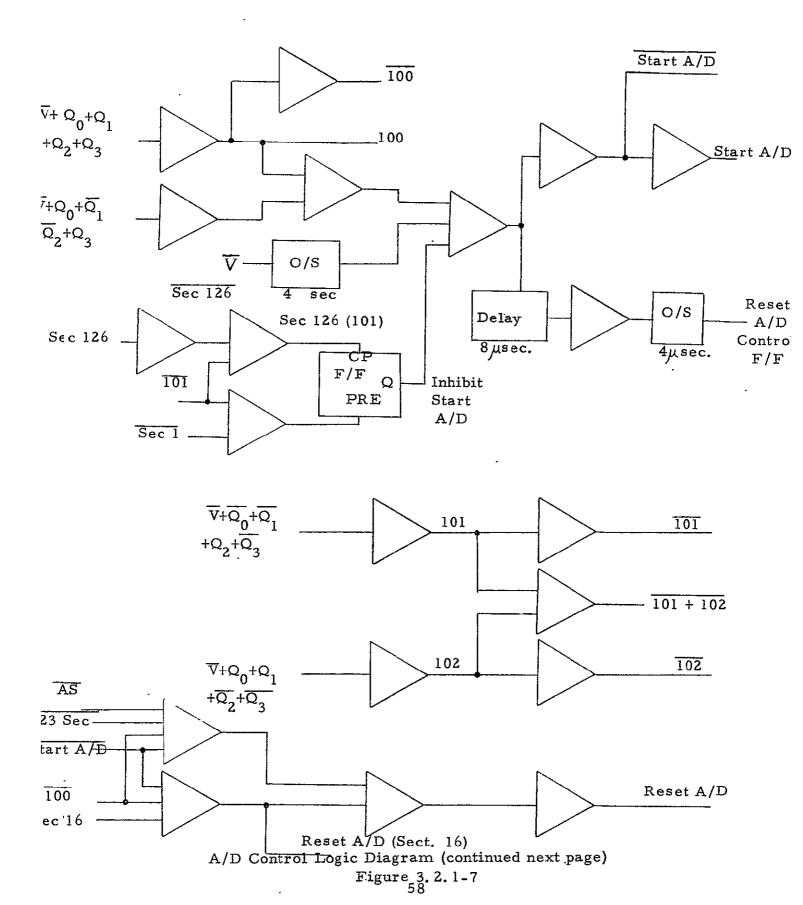

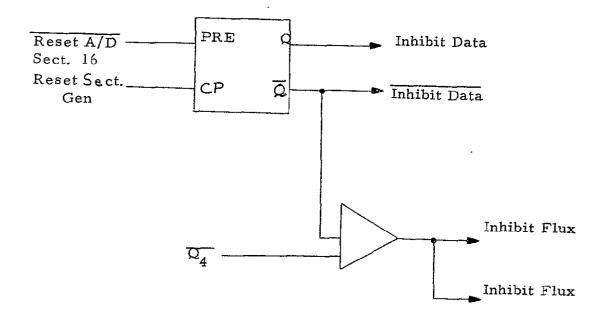

| 3. 2. 1-7   | A/D Control Logic Diagram                         | 58   |

| 3. 2. 1-8   | A/D Control Timing Diagram                        | 60   |

| 3. 2. 1-9   | Mode Timing AS and PS Logic Diagram               | 63   |

| 3. 2. 1-10  | Mode Timing MFS, HBR, LBR, RLTSR<br>Logic Diagram | 64   |

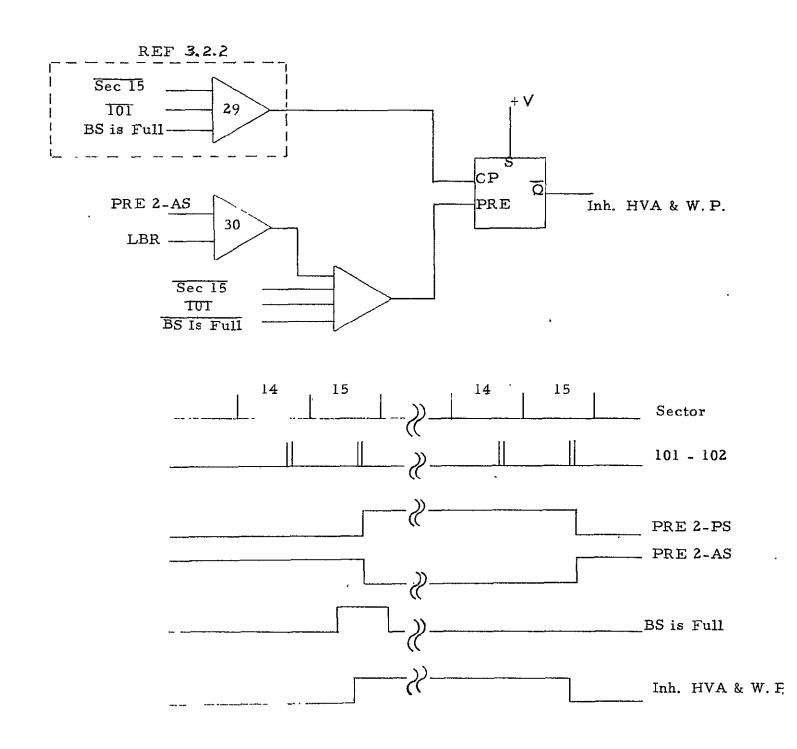

| 3, 2, 1-11  | PRE-2 Timing Diagram `                            | 65   |

| 3, 2, 1-12  | PRE-1 Timing Diagram                              | 66   |

| 3, 2, 2-1   | Target Programmer Logic Diagram                   | 69   |

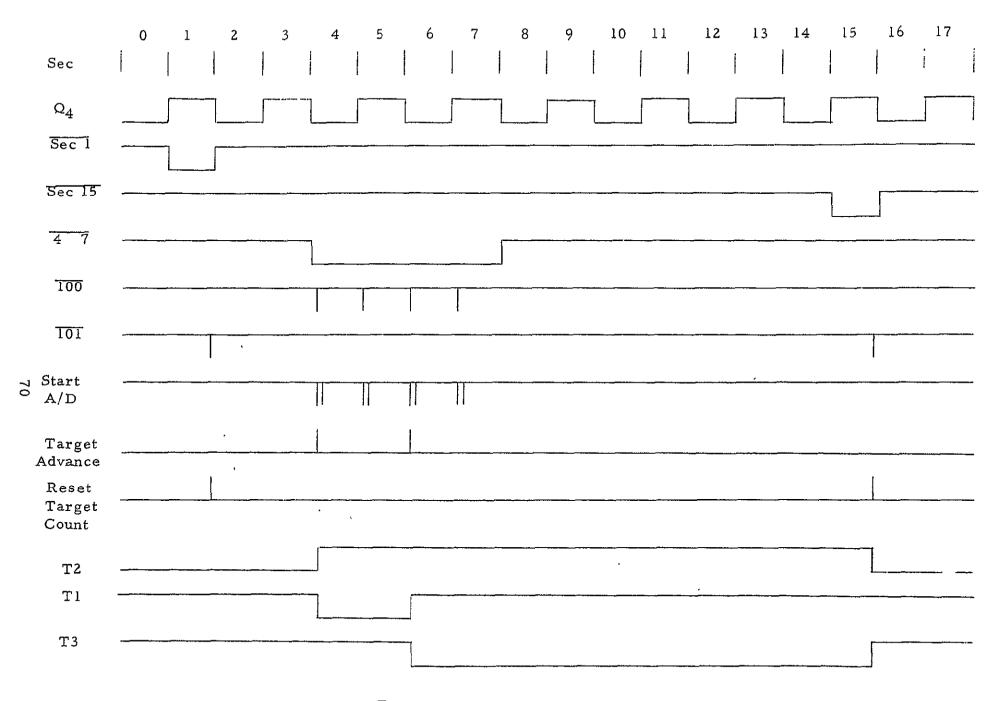

| 3, 2, 2-2   | Target Programmer Timing Diagram                  | 70   |

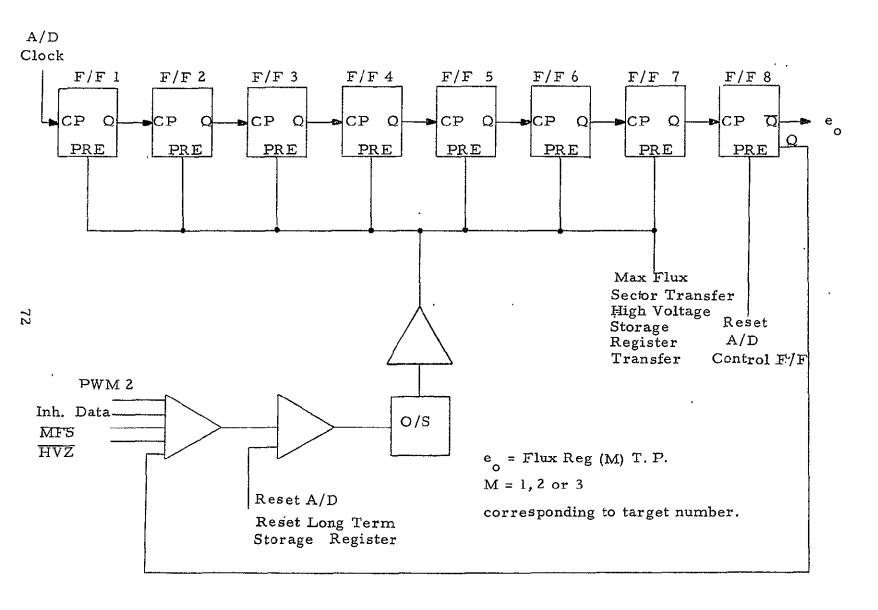

| 3.2.3-1     | Digital Comparator and Long Term Storage Register | 72   |

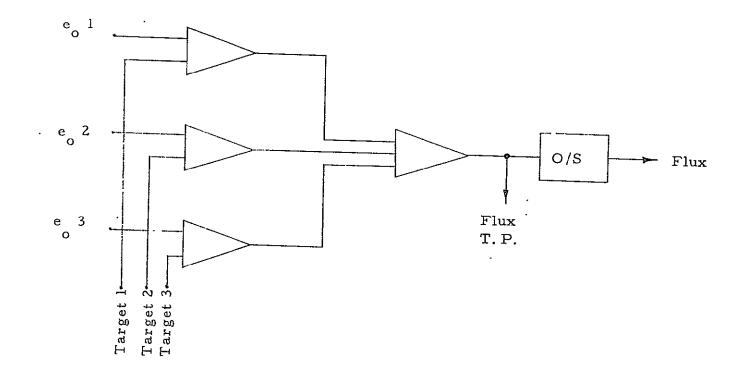

| 3.2.3-2     | Flux Register Commutator                          | 74   |

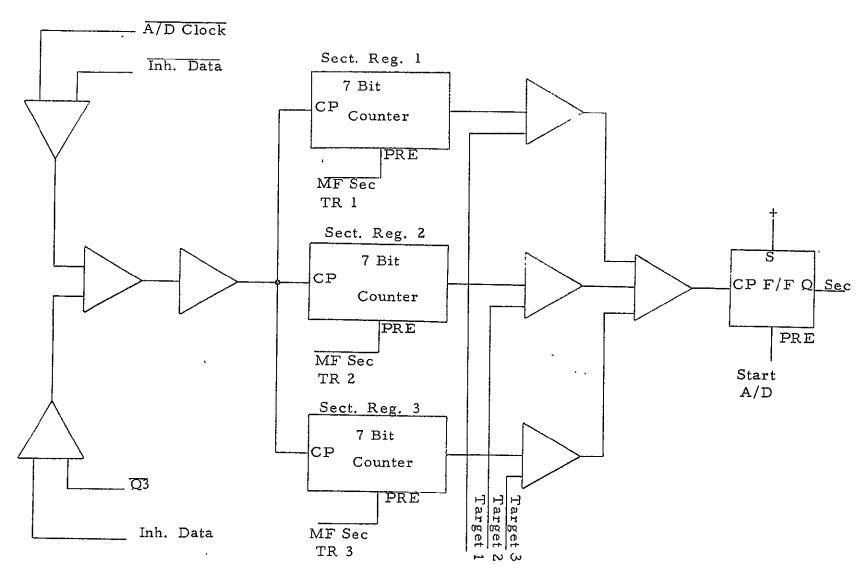

| 3. 2. 4-1   | Sector Programmer Logic Diagram                   | 76   |

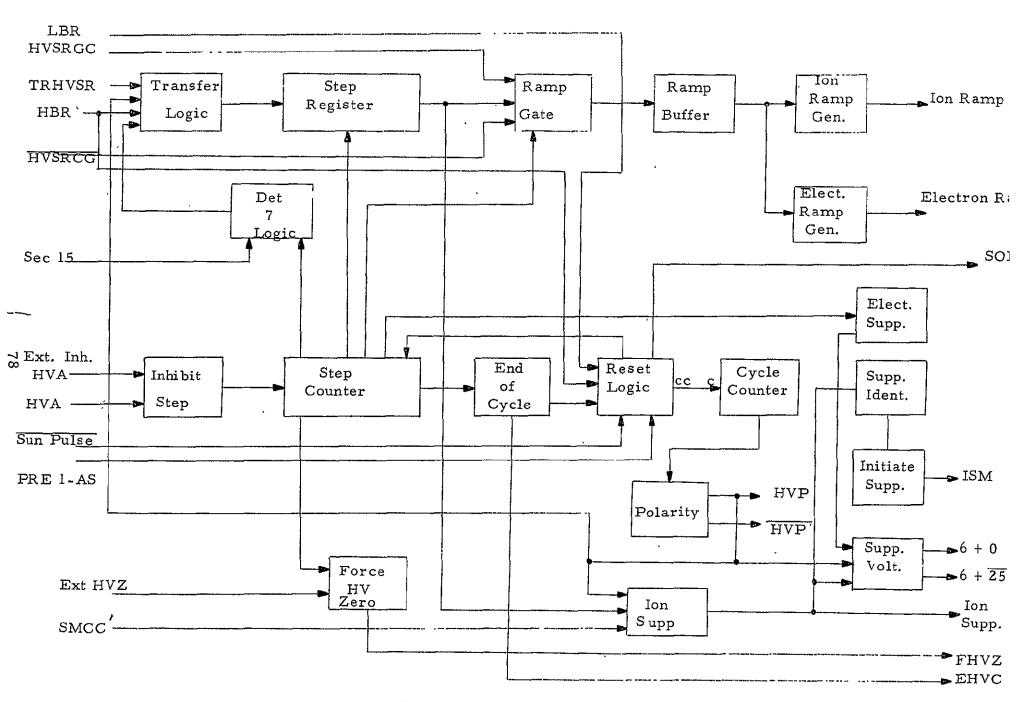

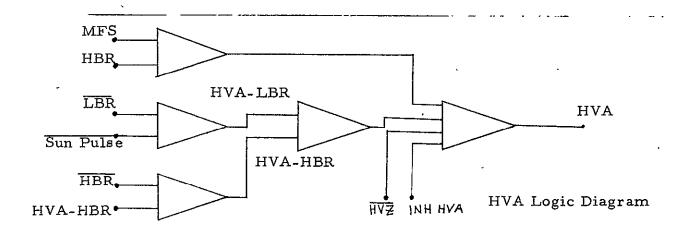

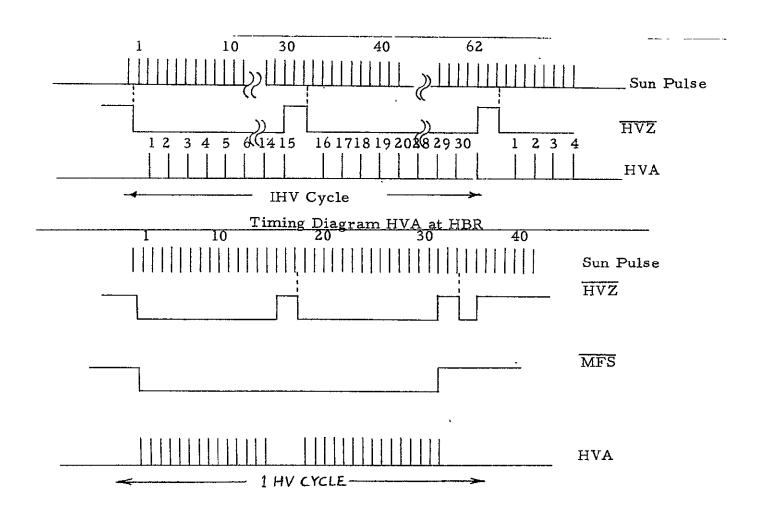

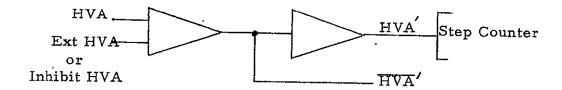

| 3, 2, 5-1   | High Voltage Programmer Block Diagram             | 78   |

| 3.2.5-2     | High Voltage Advance Logic Diagram                | 82   |

| 3.2.5-3     | High Voltage Advance Timing Diagram               | 82   |

| 3. 2. 5-4   | Inhibit Step Logic, Logic and Timing Diagram      | 83   |

| 3, 2, 5-5   | Step Counter Logic and Timing Diagram             | 84   |

| 3. 2. 5-6   | Force High Voltage Zero, Logic and Timing Diagram | 87   |

| 3. 2. 5 - 7 | End-of-Cycle Logic and Timing Diagram             | 88   |

| 3.2.5-8     | Reset Logic Diagram                               | 89   |

| 3. 2. 5-9   | Reset Logic Timing at HBR and LBR                 | 90   |

| 3. 2. 5-10  | Step Register Logic and Timing Diagrams           | 91   |

| 3. 2. 5-11  | Detect 7E Logic and Timing Diagrams               | 93   |

| 3. 2. 5-12  | Transfer Logic and Timing Diagrams                | 94   |

| 3. 2. 5-13  | Ramp Gate Logic and Timing Diagrams               | 95   |

| 3.2.5-14    | Cycle Counter Clock, Logic and Timing<br>Diagrams | 96   |

| Figure No  | <u>).</u>                                                           | Page        |

|------------|---------------------------------------------------------------------|-------------|

| 3.2.5-15   | Polarity Logic and Timing Diagram                                   | 99          |

| 3. 2. 5-16 | Ion Suppression Logic Diagram                                       | 100         |

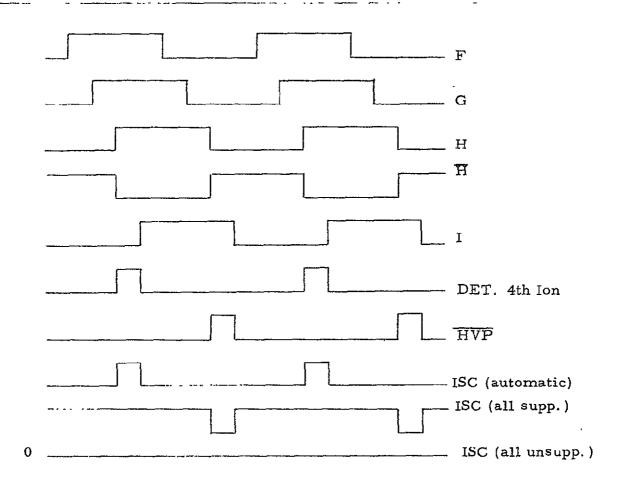

| 3.2.5-17   | ISC Timing Diagram                                                  | 101         |

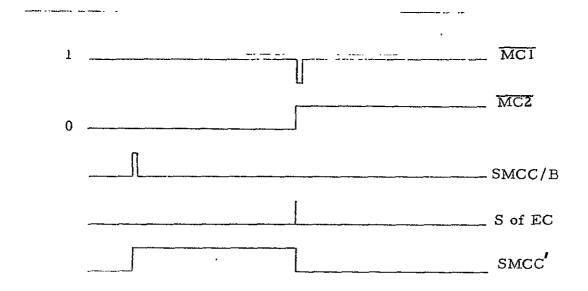

| 3.2.5-18   | MCl and MC2 Timing Diagram                                          | 101         |

| 3. 2. 5-19 | Electron Suppression Logic Diagram                                  | 102         |

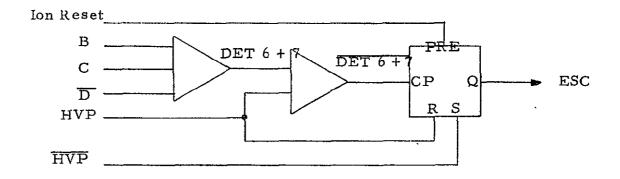

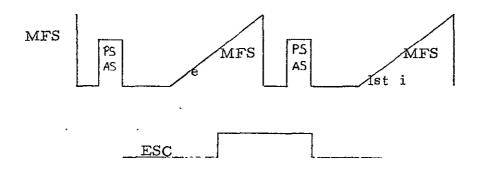

| 3. 2. 5-20 | L.BR and HBR Operation of ESC, Timing Diagram                       | 102         |

| 3. 2. 5-21 | Electron Suppression Logic and Timing Diagram                       | 103         |

| 3. 2. 5-22 | Suppressed Identification Logic and Timing Diagram                  | 105         |

| 3, 2, 5-23 | Initiate Suppressed Mode Logic and Timing Diagram                   | <u>i</u> 05 |

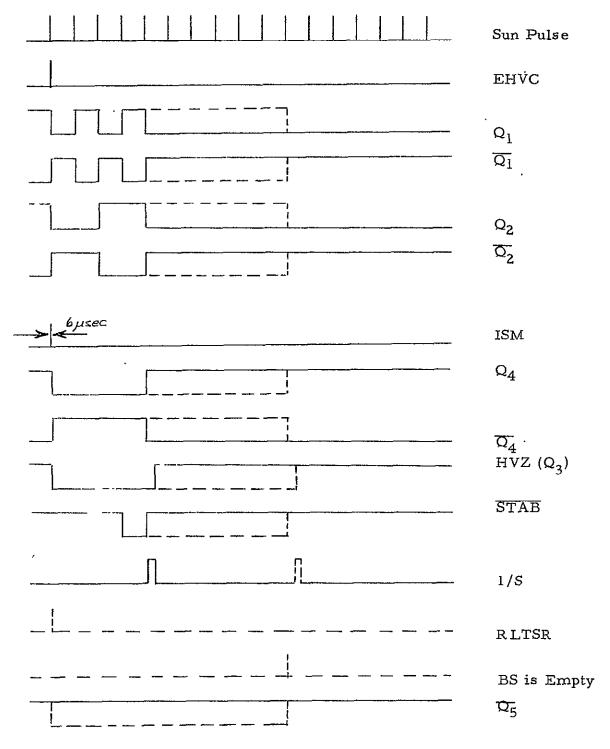

| 3.2.5-24   | Suppressed Voltage Logic Diagram                                    | 106         |

| 3, 2, 5-25 | Suppressed Voltage Logic Truth Table and Timing Diagram             | 106         |

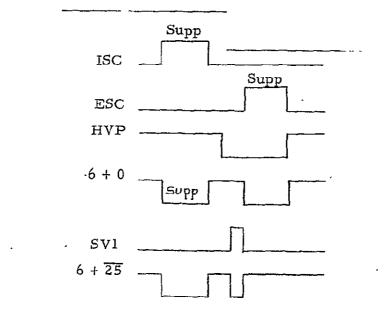

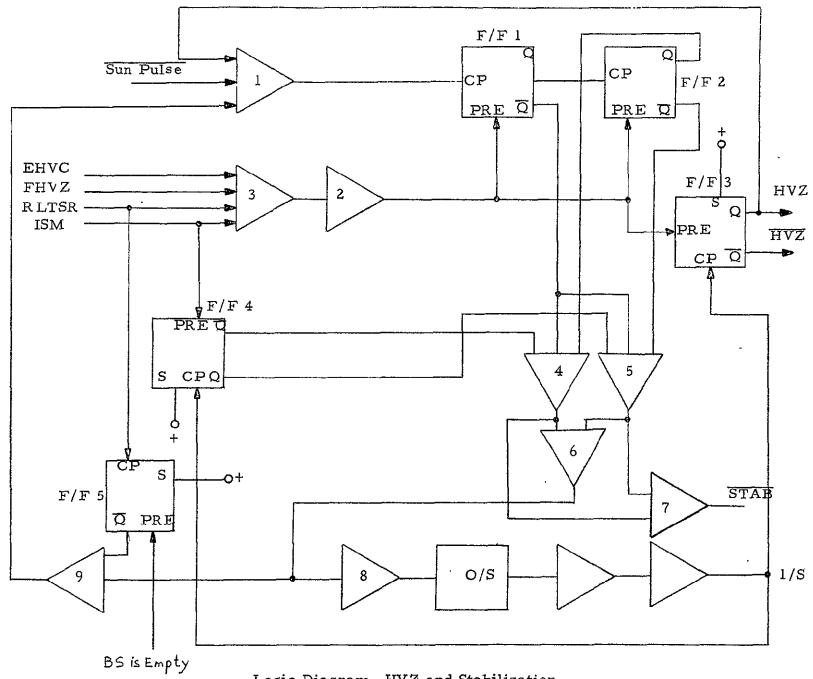

| 3.2.6-1    | HVZ and Stabilization Logic Diagram                                 | 108         |

| 3. 2. 6-2  | HVZ and Stabilization Timing Diagram (Suppression Change at HBR)    | 109         |

| 3. 2. 6-3  | HVZ and Stabilization Timing Diagram (No Suppression Change at HBR) | 110         |

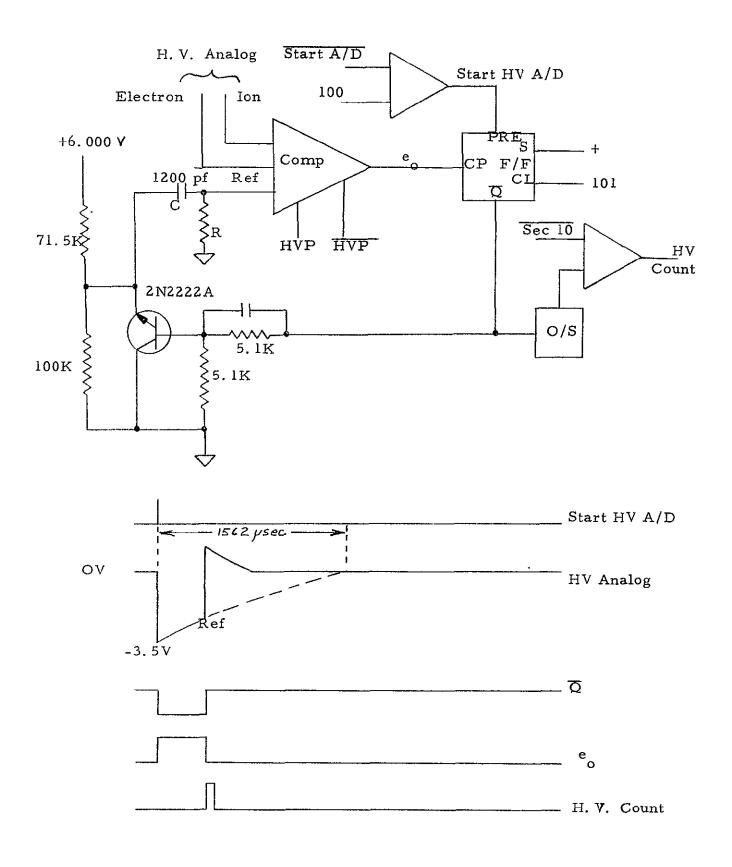

| 3.2.7-1    | High Voltage A/D Block Diagram and Timing                           | 112         |

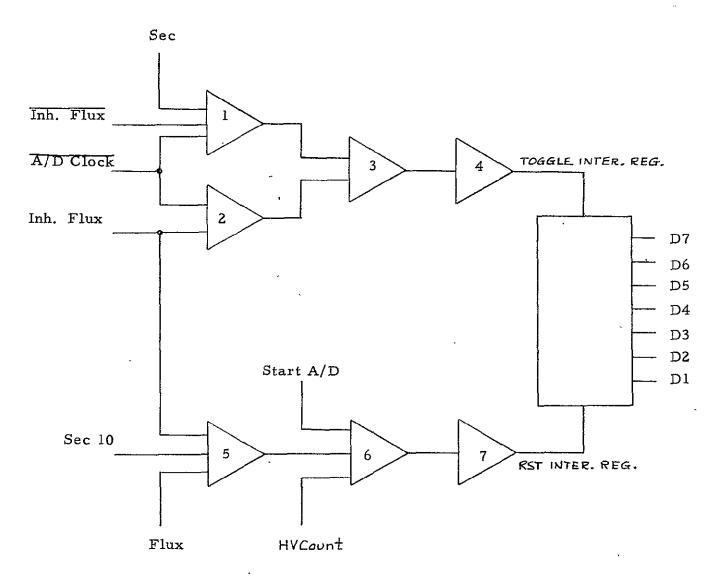

| 3.2.8-1    | Commutator and Intermediate Storage<br>Register Logic Diagram       | 114         |

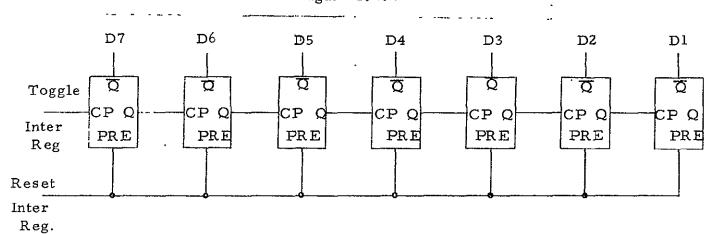

| 3.2.8-2    | Intermediate Storage Register                                       | 114         |

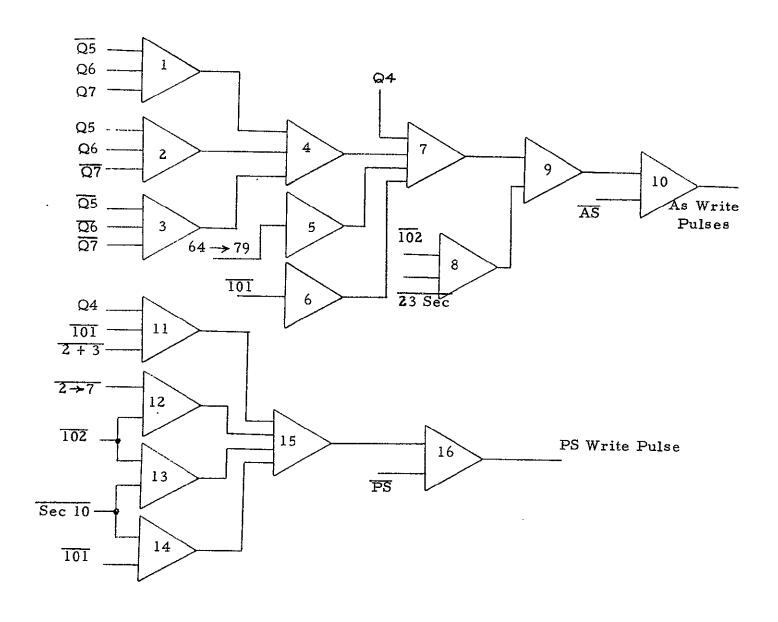

| 3.2.9-1    | AS and PS Write Pulse Logic Diagram                                 | 116         |

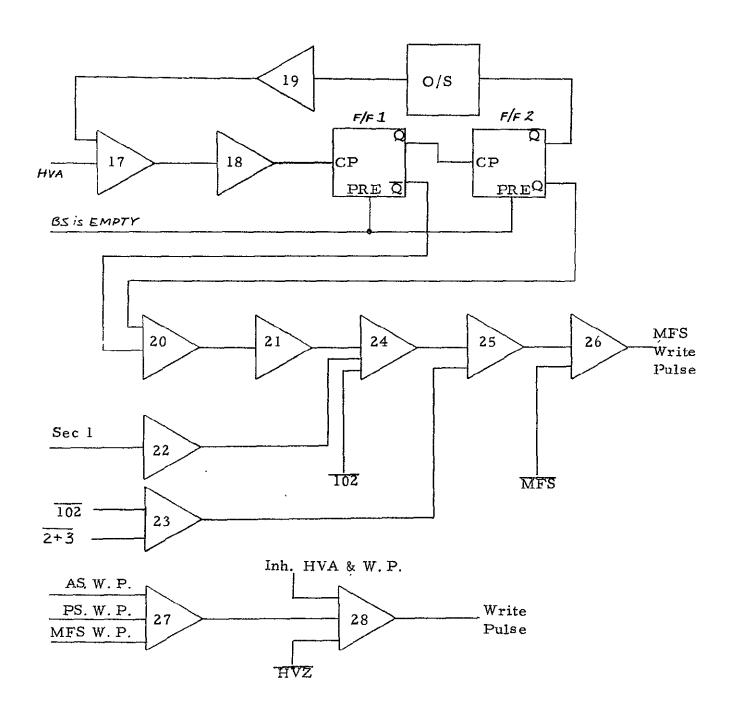

| 3. 2. 9-2  | MFS Write Pulse and Write Pulse Gate<br>Logic Diagram               | 117         |

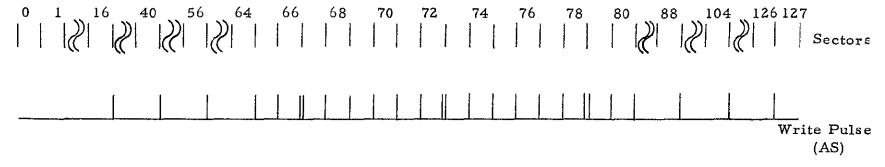

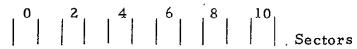

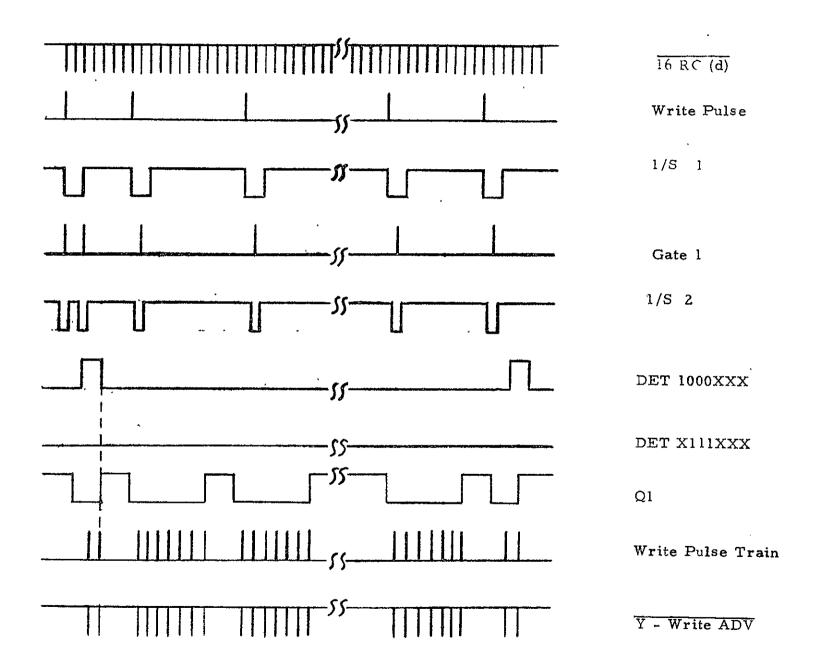

| 3. 2. 9-3  | Write Pulse Timing Diagram                                          | 118         |

| 3, 2, 9-4  | Inhibit HVA and Write Pulse at HBR, Logic and Timing Diagram        | 119         |

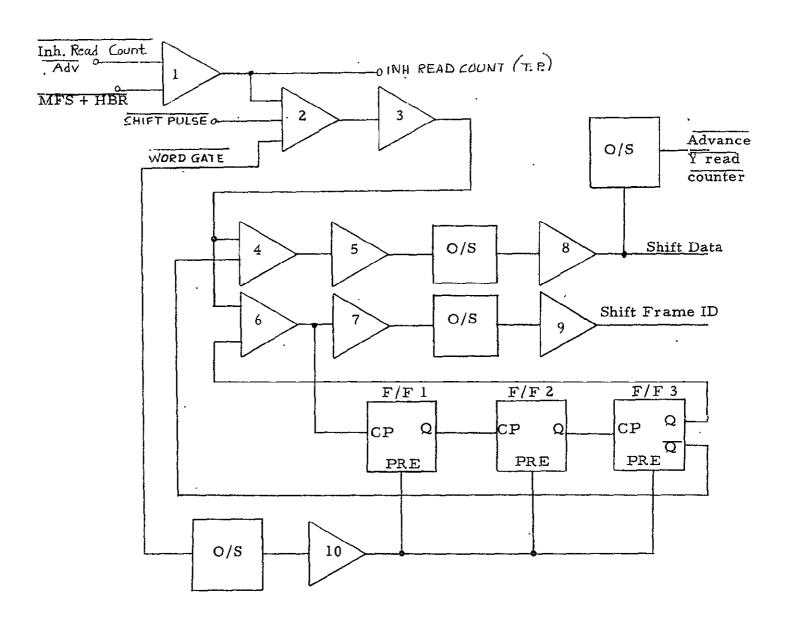

| 3. 2. 10-1 | Shift Pulse Generator Logic Diagram                                 | 123         |

| Figure No. | •                                         | Page |

|------------|-------------------------------------------|------|

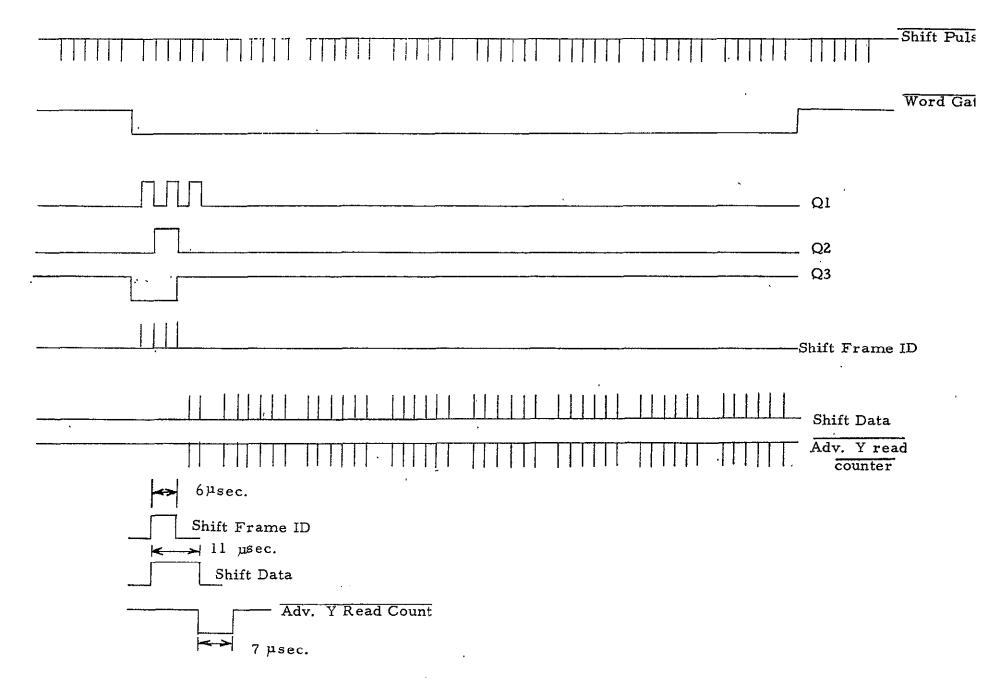

| 3.2.10-2   | Shift Pulse Generator Timing Diagram      | 124  |

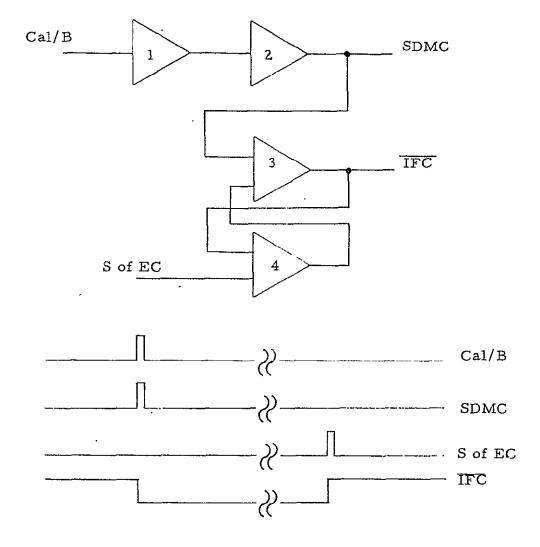

| 3.2.11-1   | Calibration Logic and Timing Diagram      | 126  |

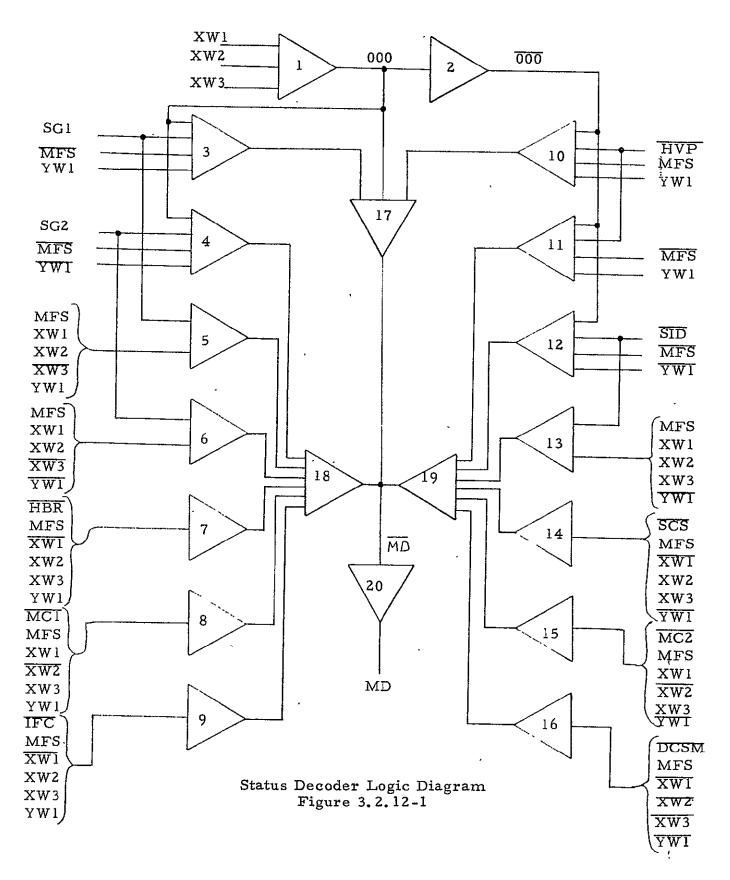

| 3.2.12-1   | Status Decoder Logic Diagram              | 128  |

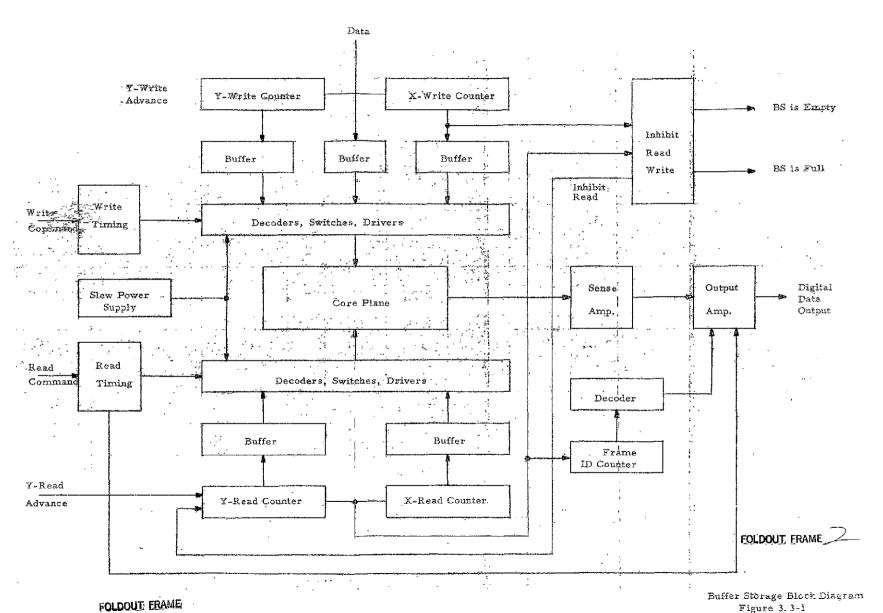

| 3.3-1      | Buffer Storage Block Diagram              | 132  |

| 3.3.1-1    | Memory Block Diagram                      | 137  |

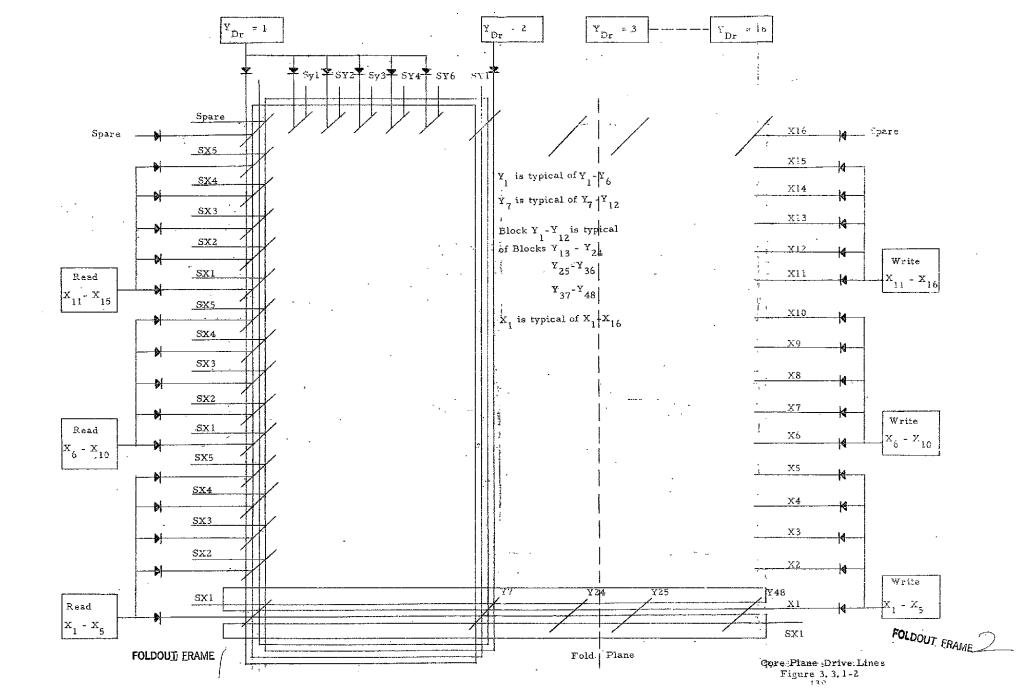

| 3.3.1-2    | Core Plane Drive Lines                    | 139  |

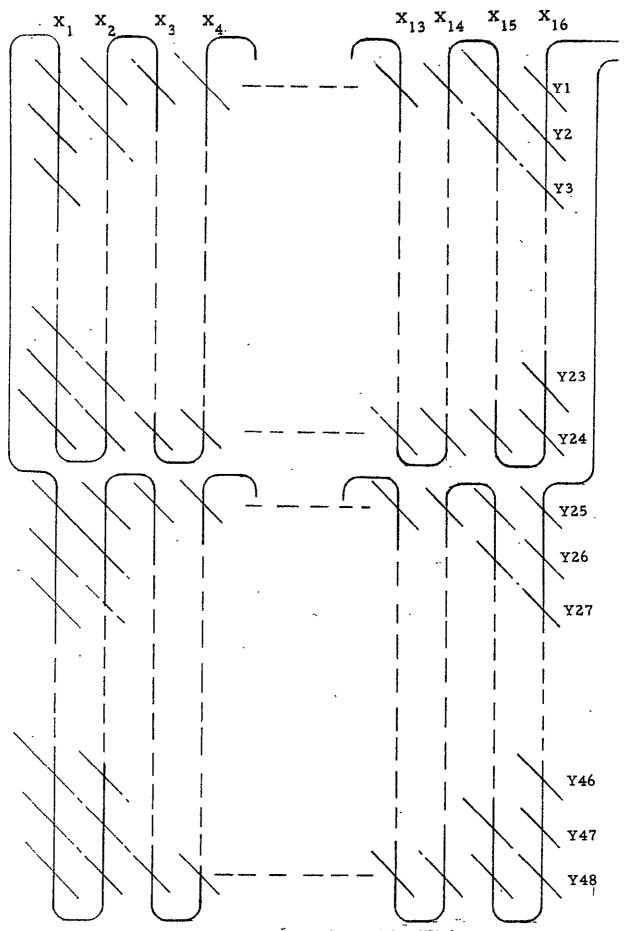

| 3. 3. 1-3  | Sense Line Wiring                         | 140  |

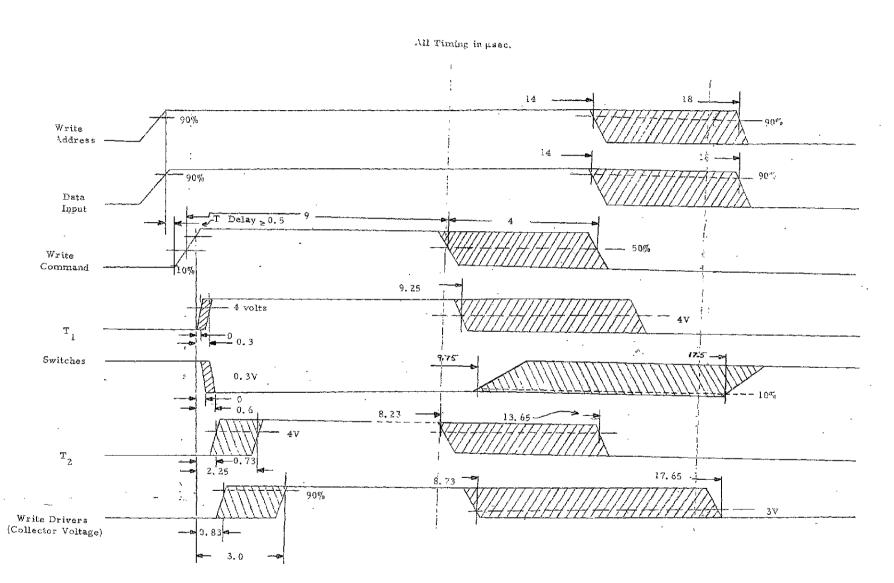

| 3.3.1-4    | Write Cycle Timing Diagram                | 143  |

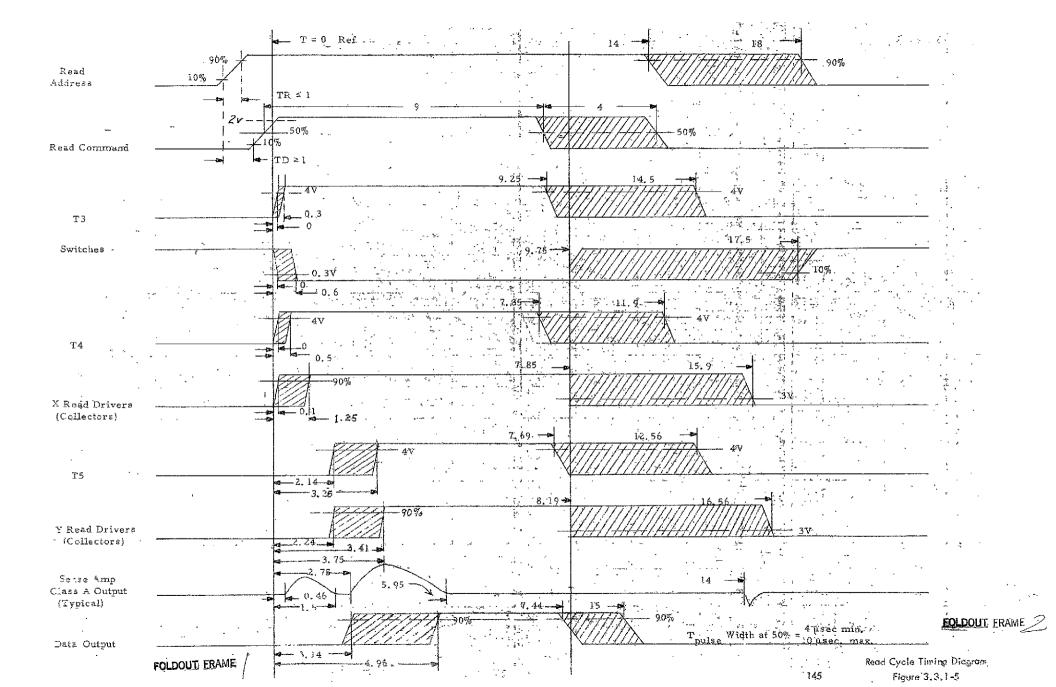

| 3.3.1-5    | Read Cycle Timing Diagram                 | 145  |

| 3, 3, 3-1  | Y-Counters Logic Diagram                  | 148  |

| 3.3.3-2    | Y-Counters Timing Diagram                 | 149  |

| 3. 3. 4-1  | X-Read Counter Logic Diagram              | 151  |

| 3. 3. 4-2  | X-Write Counter Logic Diagram             | 152  |

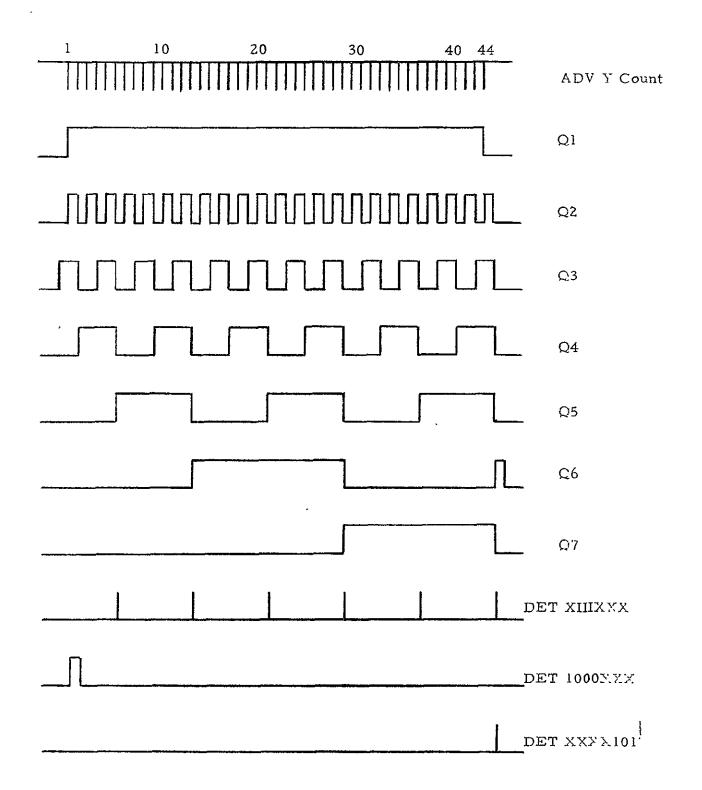

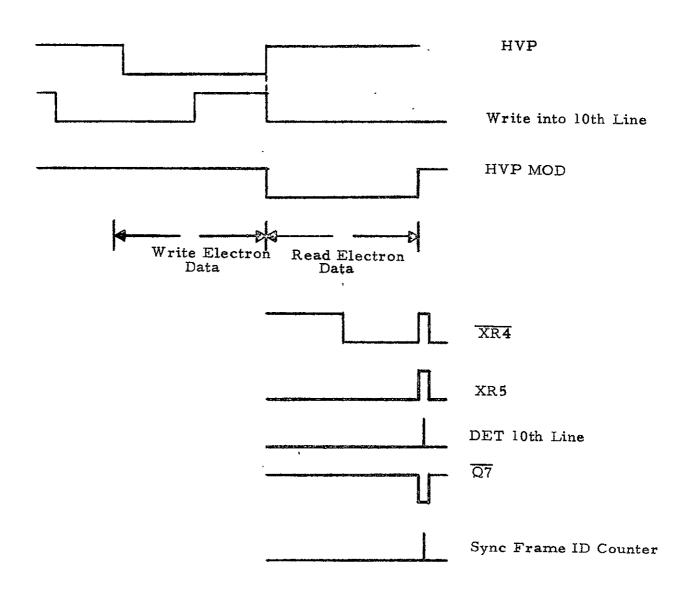

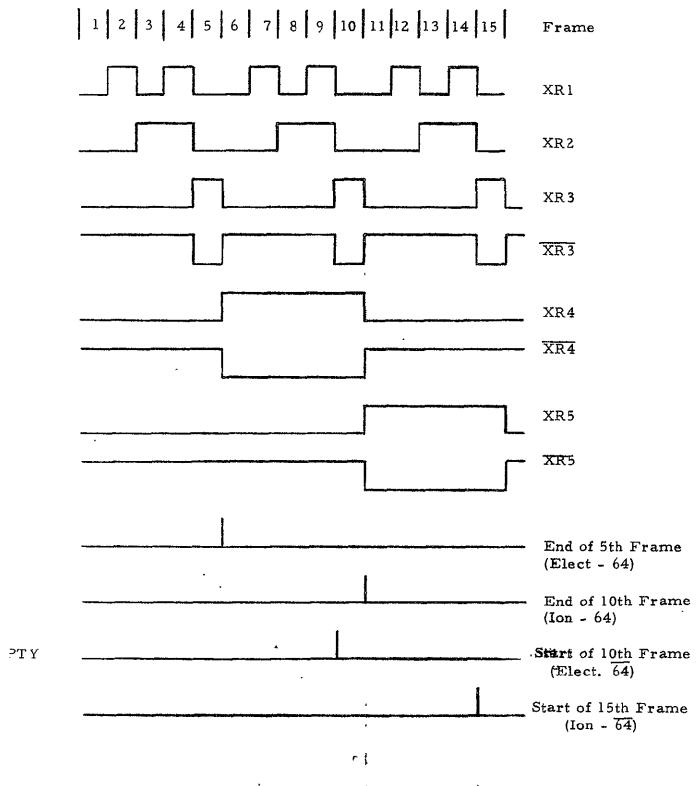

| 3. 3. 4-3  | HVP MOD Timing Diagram                    | 154  |

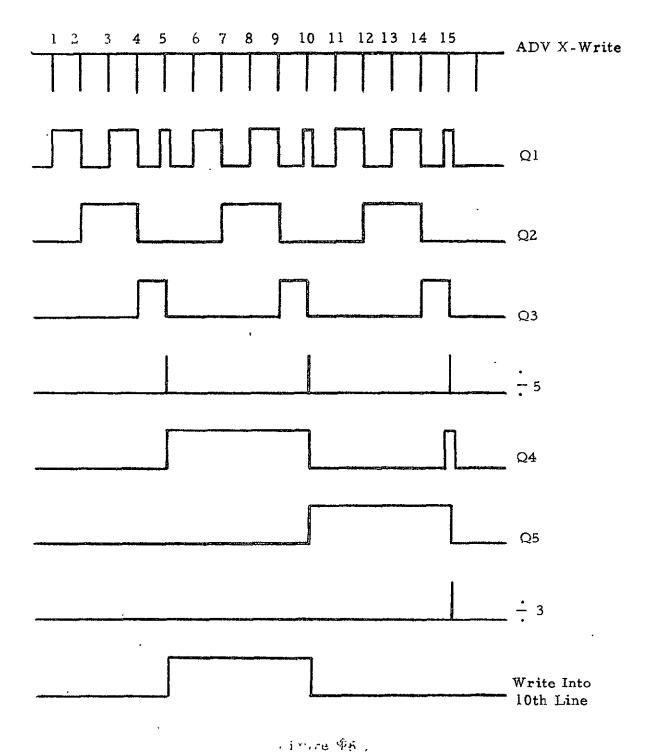

| 3. 3. 4-4  | X-Write Counter Timing Diagram            | 155  |

| 3.3.5-1    | Write Pulse Train Generator Logic Diagram | 157  |

| 3.3.5-2    | Write Pulse Train Timing Diagram          | 158  |

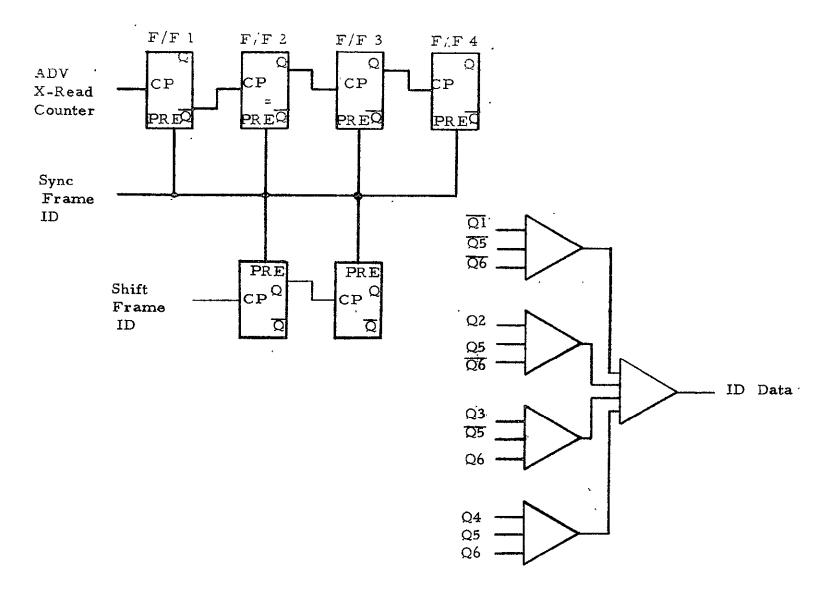

| 3, 3, 6-1  | Frame ID Counter Logic Diagram            | 159  |

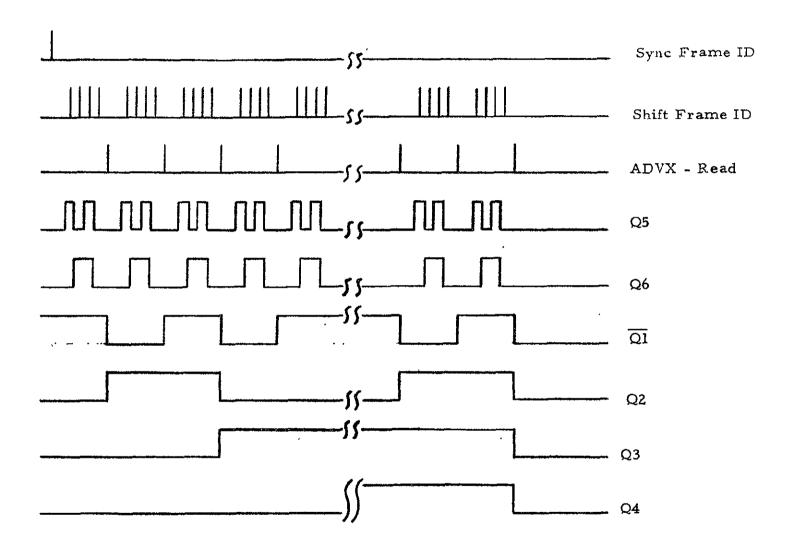

| 3. 3. 6-2  | Frame ID Counter Timing Diagram           | 160  |

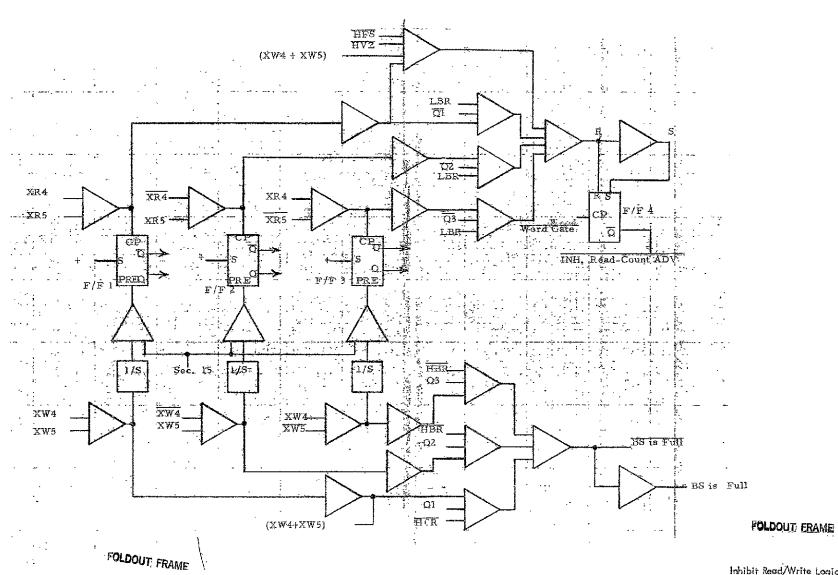

| 3. 3. 7-1  | Inhibit Read/Write Logic Diagram          | 162  |

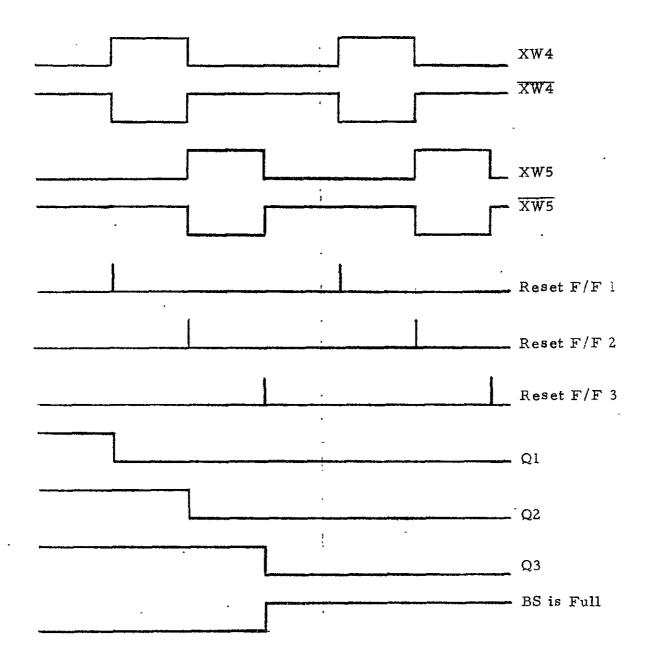

| 3.3.7-2    | BS is Full Timing Diagram                 | 163  |

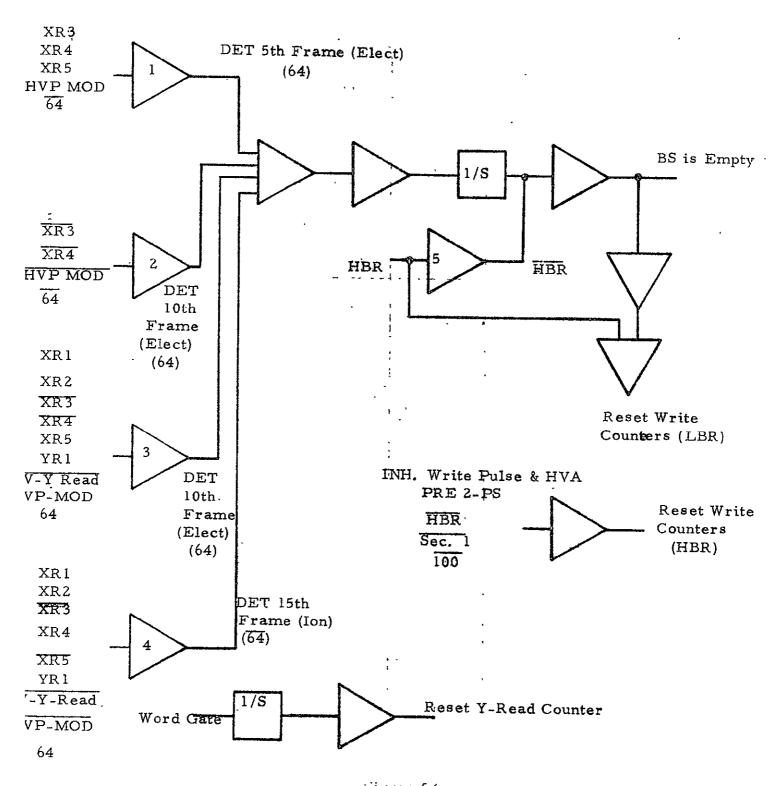

| 3.3.8-1    | BS is Empty Reset Counters Logic Diagram  | 166  |

| 3. 3. 8-2  | BS is Empty Timing Diagram                | 167  |

| 3.4.2-1    | High Voltage Power Supply Block Diagram   | 171  |

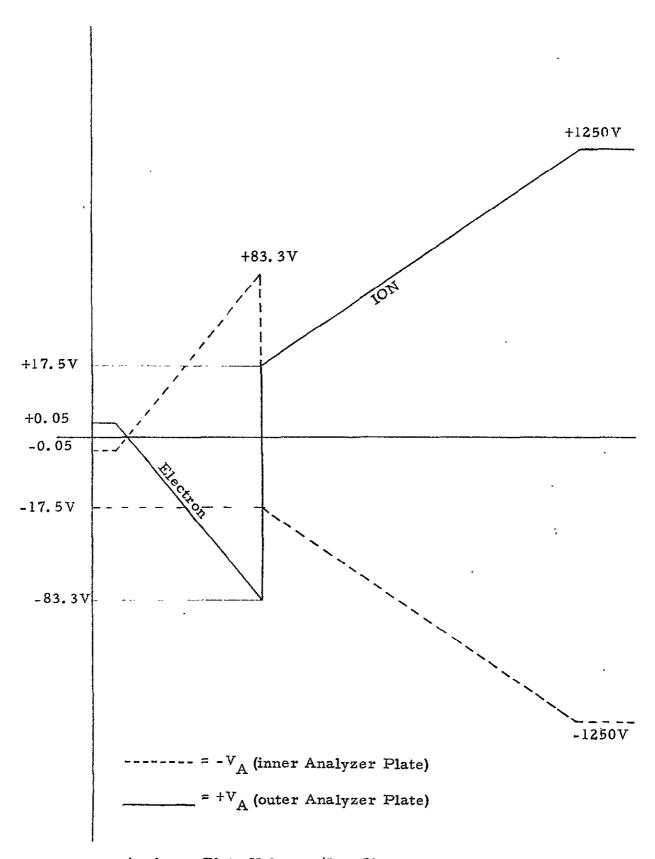

| 3.4.2-2    | Analyzer Plate Voltages/Ion Electron Mode | 173  |

| 3.5-1      | Low Voltage Power Supply Block Diagram    | 176  |

### }.

| Figure No. |                                                                               | Page |

|------------|-------------------------------------------------------------------------------|------|

| 3. 5. 3-1  | Typical Rectifier Filter Configurations                                       | 178  |

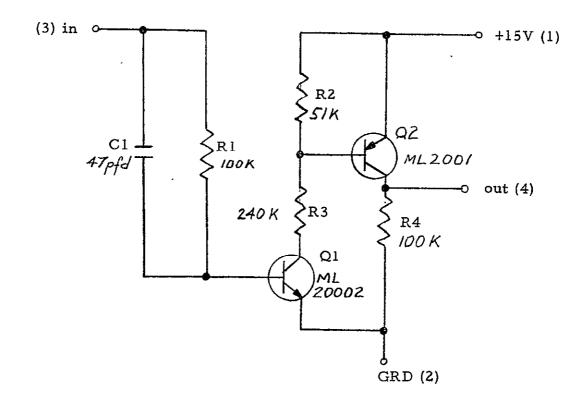

| 4.1.1-1    | Stabilization Buffer Schematic                                                | 180  |

| 4.1.2-1    | Stabilization Amplifier Schematic                                             | 181  |

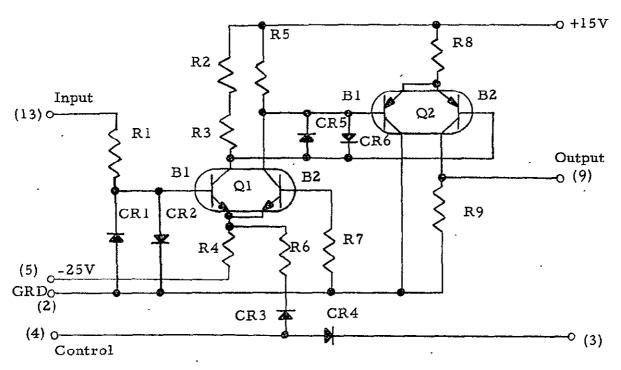

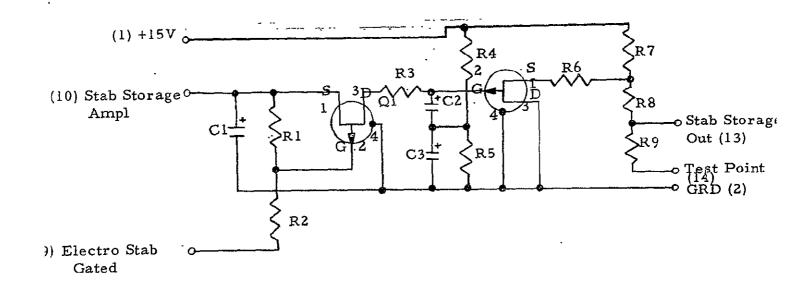

| 4.1.3-1    | Stabilization Storage Schematic                                               | 183  |

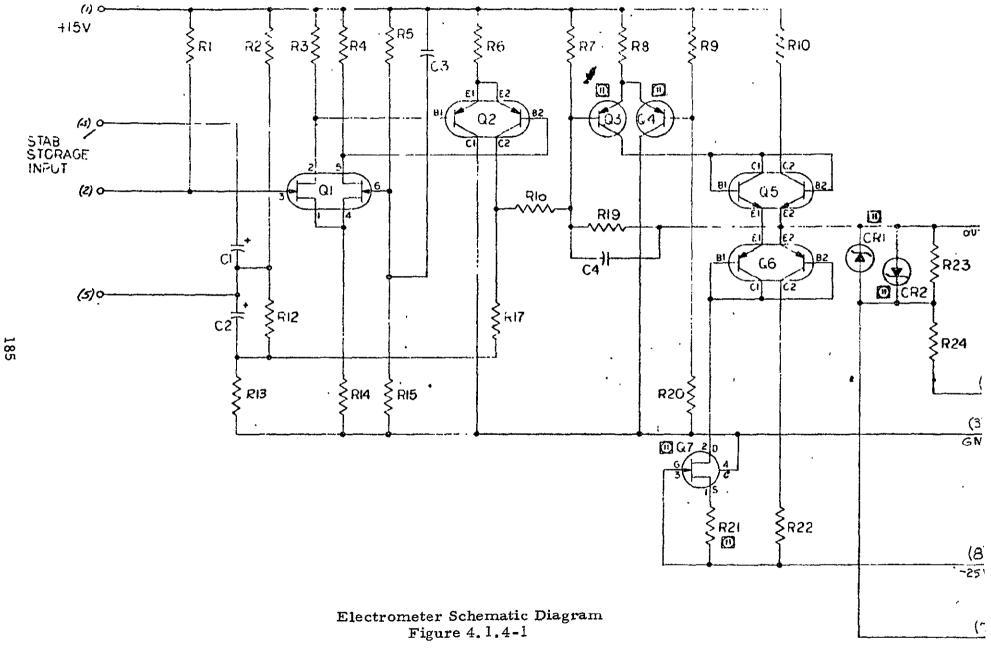

| 4.1.4-1    | Electrometer Schematic Diagram                                                | 185  |

| 4.1.5-1    | Attenuator Driver and Attenuate & Calibrate                                   | 187  |

| 4.1.6-1    | Suppression Circuit Schematic Diagram                                         | 189  |

| 4.1.7-1    | Negative Comparator Schematic Diagram                                         | 191  |

| 4.1.7-2    | Positive Comparator Schematic Diagram                                         | 192  |

| 4.1.8-1    | Reference Generator, Offset Generator, and Reference Driver Schematic Diagram | 194  |

| 4.1.8-2    | Reference Generator and Offset Generator<br>Equivalent Circuit                | 197  |

| 4.1.8-3    | Reference Generator Output Waveforms                                          | 204  |

| 4.2-1      | High Voltage Comparator Simplified Schematic                                  | 205  |

| 4.3-1      | Temperature Sensor Schematic                                                  | 208  |

| 4. 3-2     | Temperature Sensor Output versus Temperature                                  | 209  |

| 4.4-1      | Current Switch Schematic Diagram                                              | 210  |

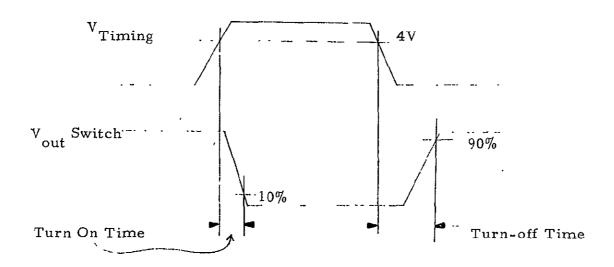

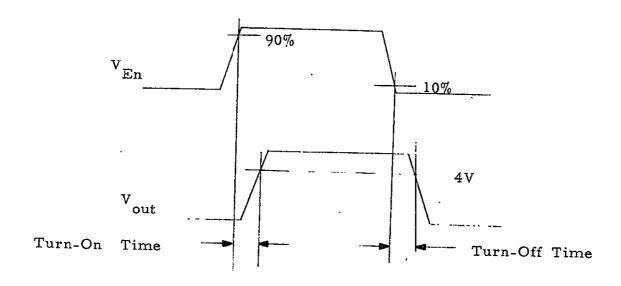

| 4.4-2      | Current Switch Turn-On and Turn-Off Time                                      | 210  |

| 4.5-1      | Current Driver Schematic Diagram                                              | 212  |

| 4.5-2      | Current Driver Turn-On and Turn-Off Time                                      | 212  |

| 4.6-1      | Gate Switch                                                                   | 214  |

| 4.6-2      | Gate Switch Turn-On and Turn-Off Time                                         | 214  |

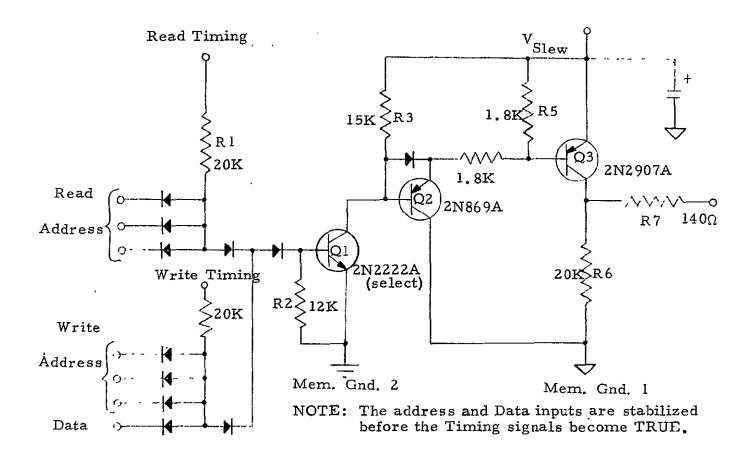

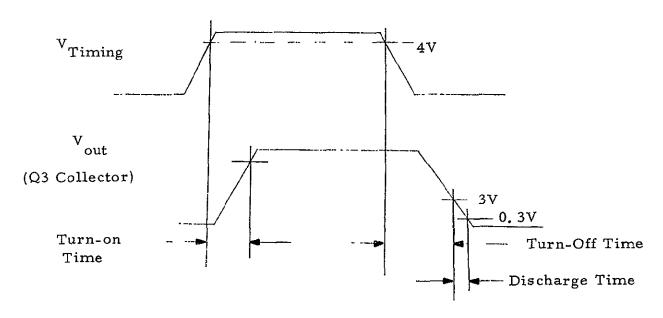

| 4.7-1      | Read Timing Circuit Schematic Diagram                                         | 216  |

| 4.8-1      | Write Timing Circuit Schematic Diagram                                        | 218  |

| 4.9-1      | Sense Amplifier Schematic Diagram                                             | 220  |

| Figure No | •                                        | Page |

|-----------|------------------------------------------|------|

| 4 10 1    | Churcha Dalam and Data One Chat          | 220  |

| 4. 10-1   | Strobe Delay and Data One-Shot           |      |

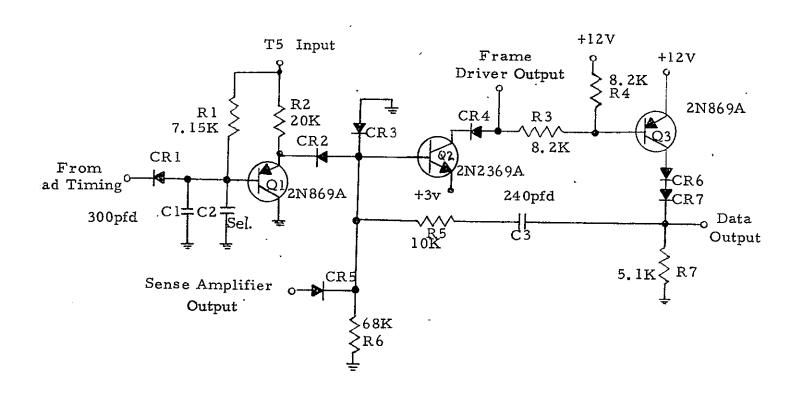

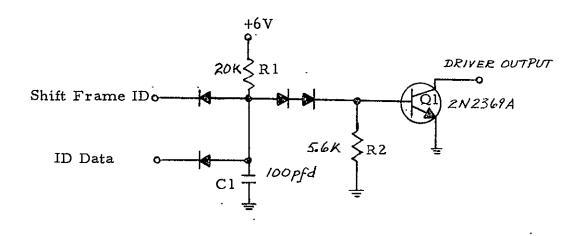

| 4.11-1    | Frame ID Driver                          | 224  |

| 4.12-1    | Ion D-C Amplifier                        | 225  |

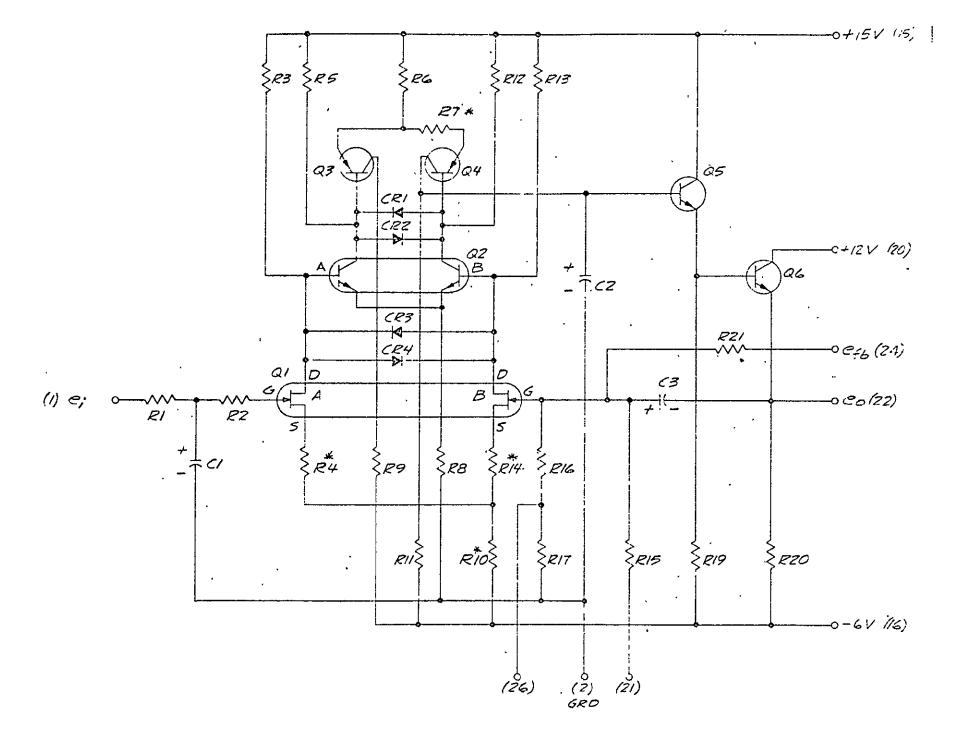

| 4.13.1-1  | Chopper Schematic Diagram                | 227  |

| 4.13.2-1  | Doubler Gate and Doubler Chain           | 228  |

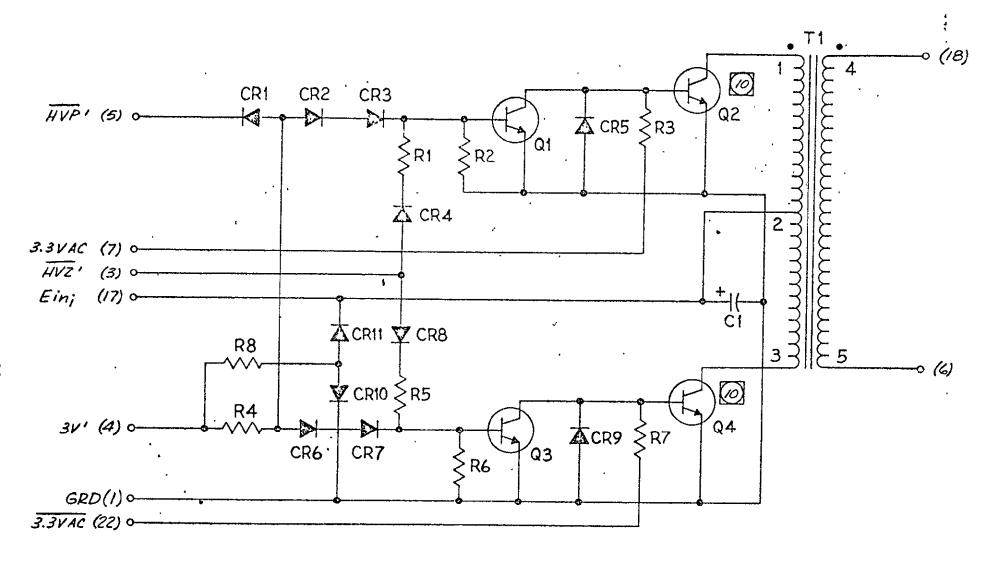

| 4.14.1-1  | Low Voltage Power Supply Pre-Regulator   | 231  |

| 4.14.2-1  | Low Voltage Power Supply Chopper         | 233  |

| 4.14.3-1  | +6V Post-Regulator                       | 235  |

| 4.14.3-2  | -6V Post Regulator                       | 236  |

| 4.14.3-3  | 12V Post-Regulator                       | 237  |

| 4.14.3-4  | .+15V Post-Regulator                     | 238  |

| 4.14.3-5  | -25V Post-Regulator                      | 239  |

| 4.14.4-1  | Filament Power Supply                    | 240  |

|           |                                          |      |

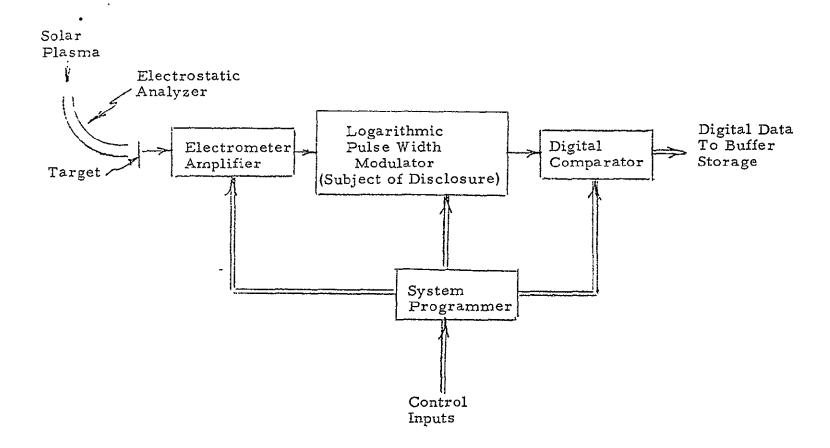

| 5.5-1     | LPWM System Simplified Block Diagram     | 247  |

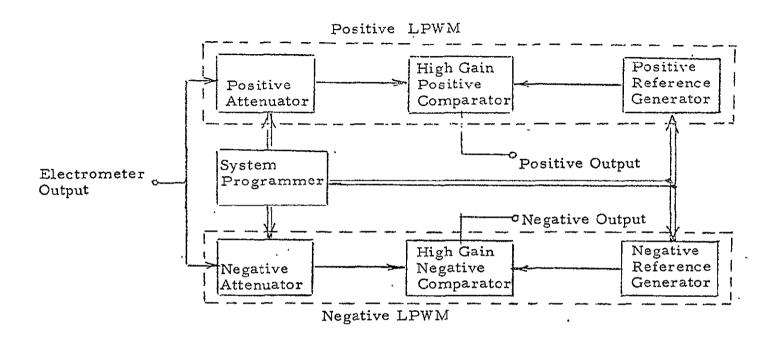

| 5.5-2     | LPWM Simplified Block Diagram            | 248  |

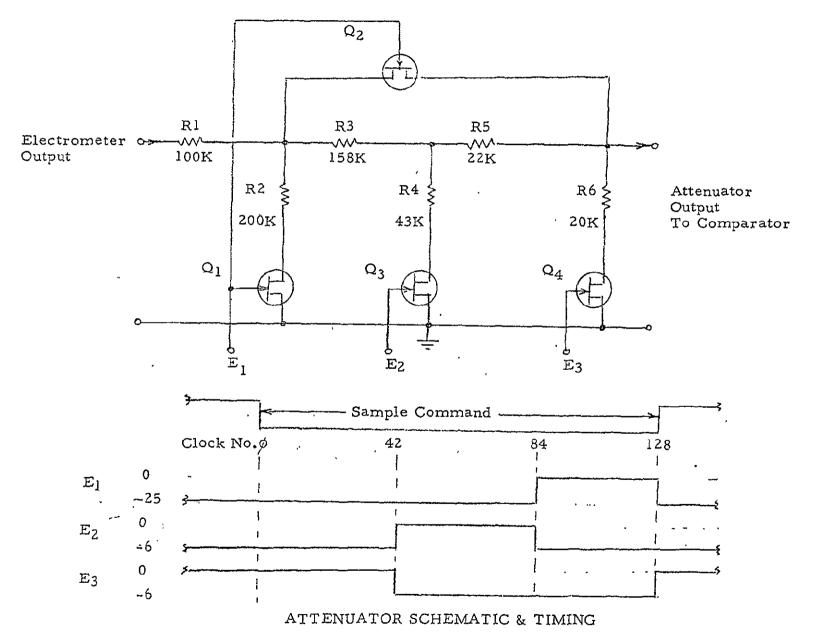

| 5.5-3     | Attenuator Schematic and Timing          | 250  |

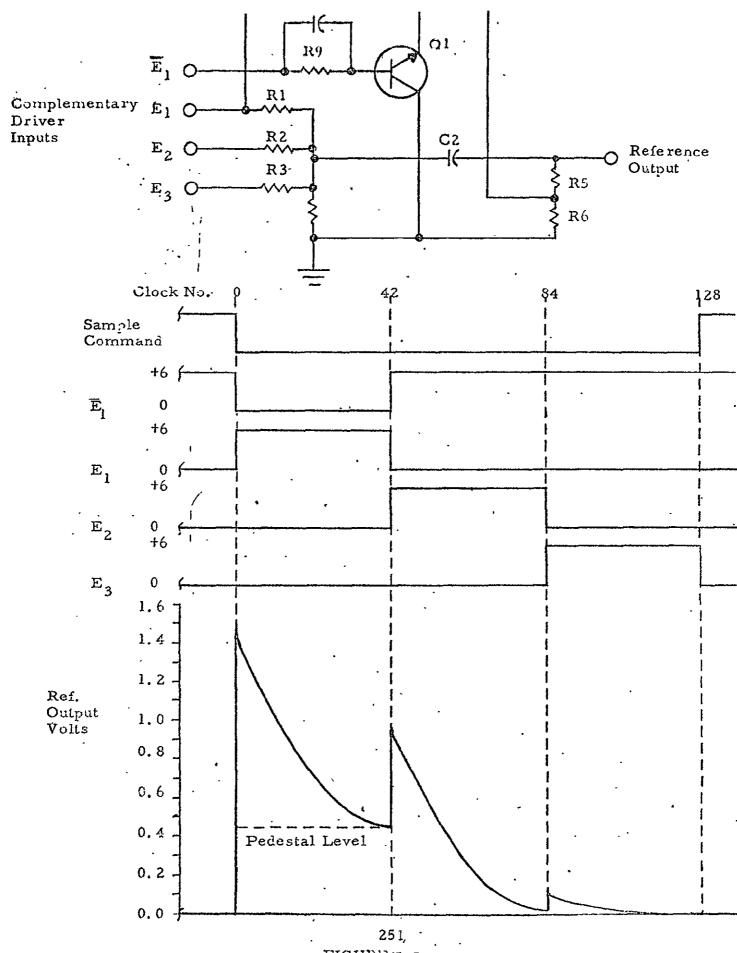

| 5.5-4     | Reference Generator Schematic and Timing | 251  |

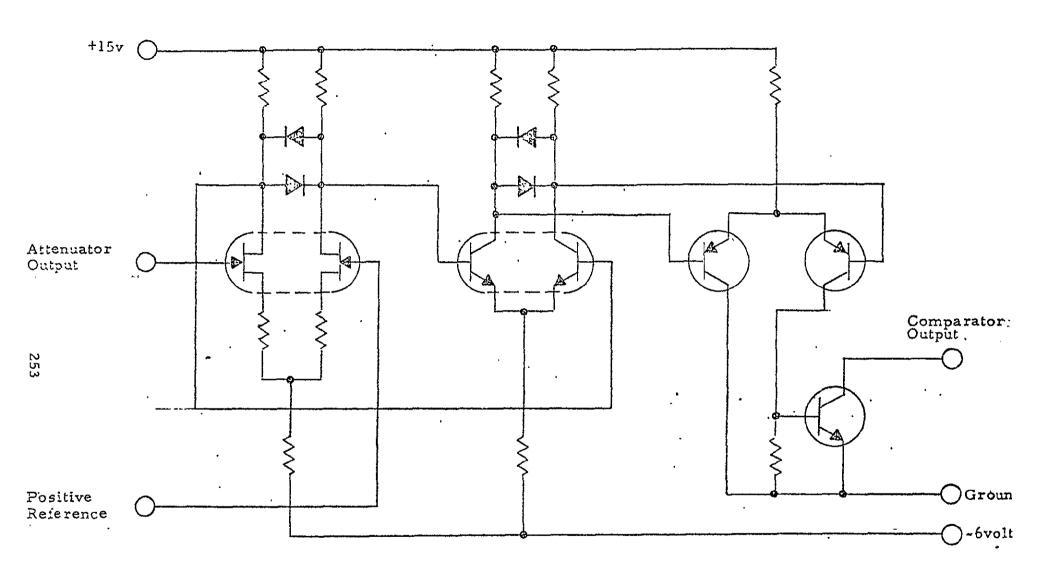

| 5.5-5     | Positive Comparator Simplified Schematic | 253  |

|           |                                          |      |

| 6.1-1     | Instrument Final Assembly                | 255  |

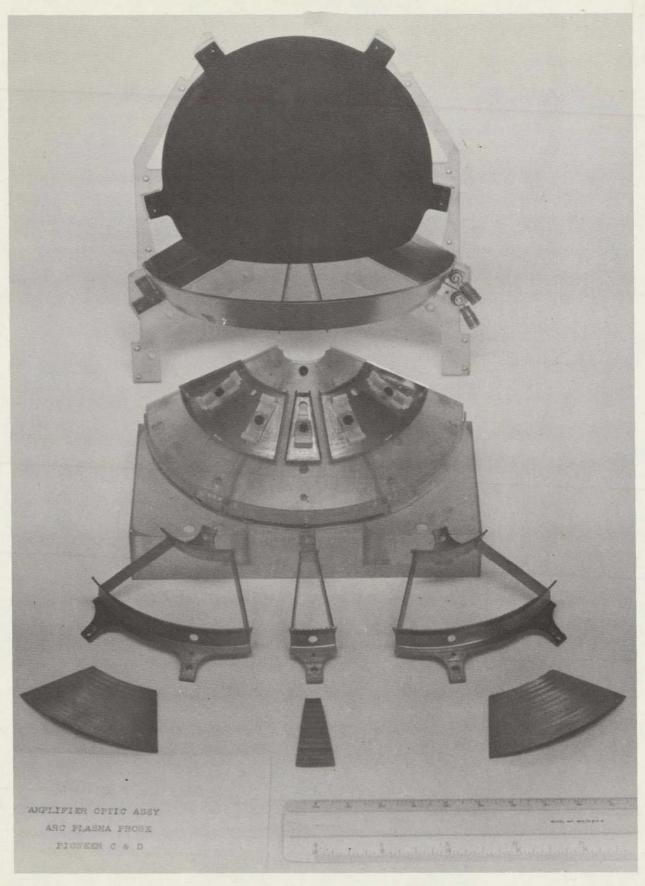

| 6.1-2     | Amplifier and Optics Assembly (photo)    | 256  |

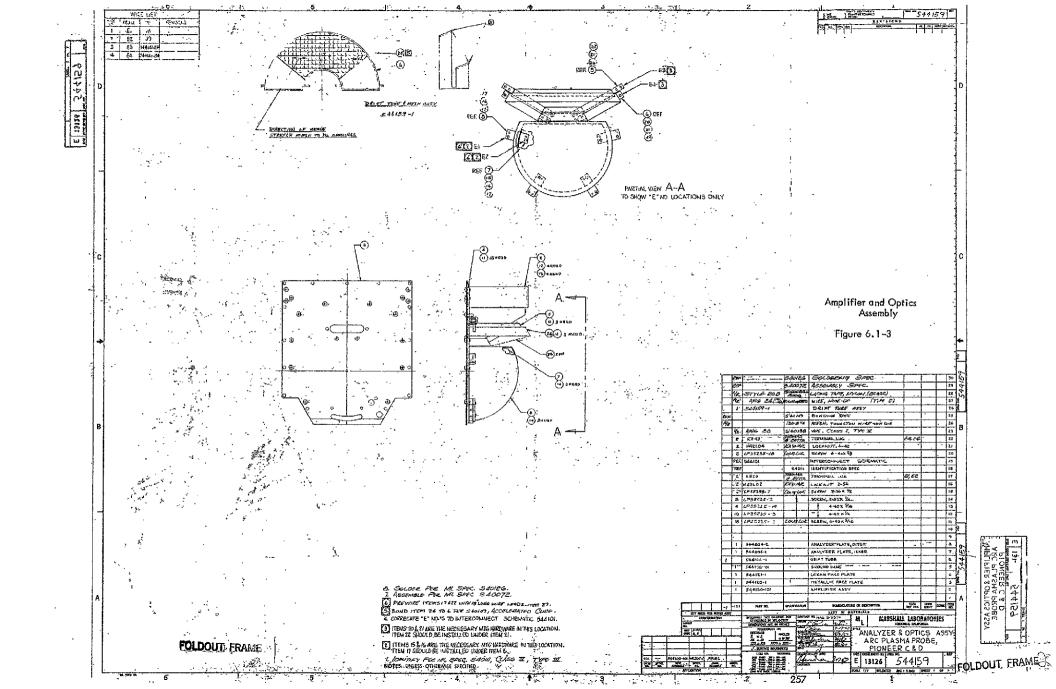

| 6.1-3     | Amplifier and Optics Assembly            | 257  |

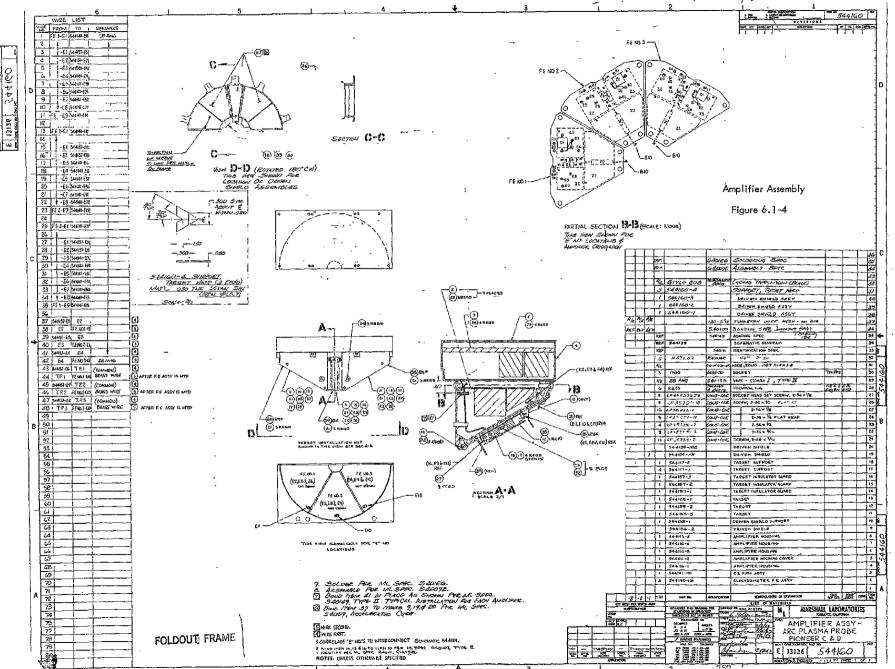

| 6.1-4     | Amplifier Assembly                       | 259  |

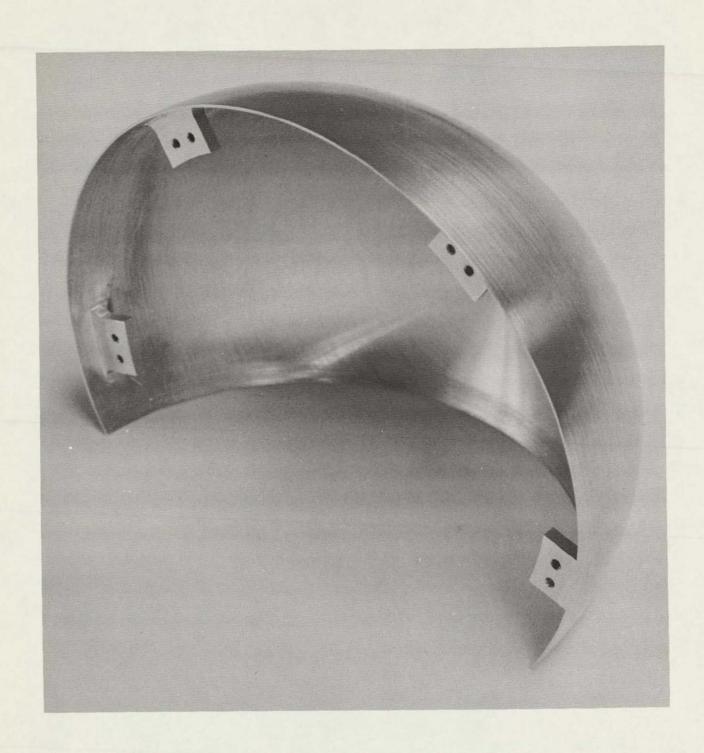

| 6.1-5     | Analyzer Plate-Outer (photo)             | 261  |

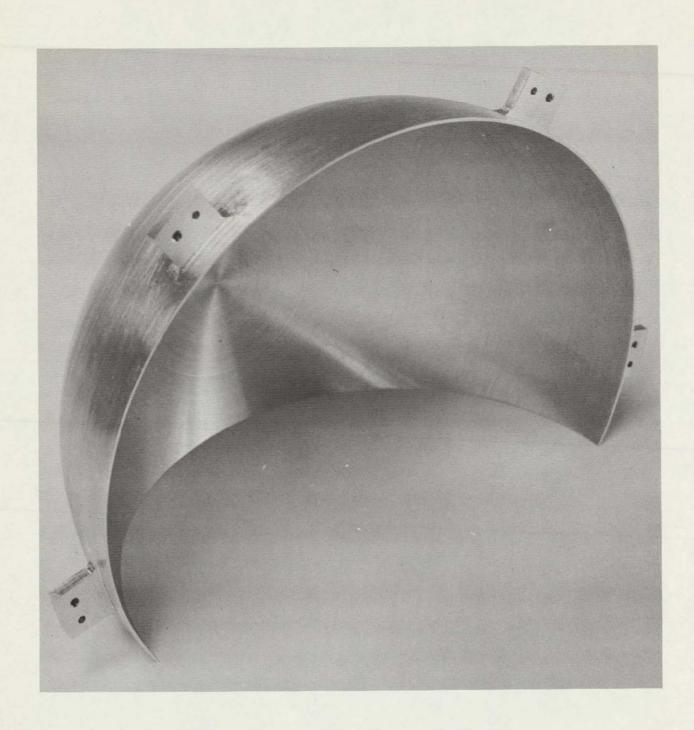

| 6.1-6     | Analyzer Plate-Inner (photo)             | 262  |

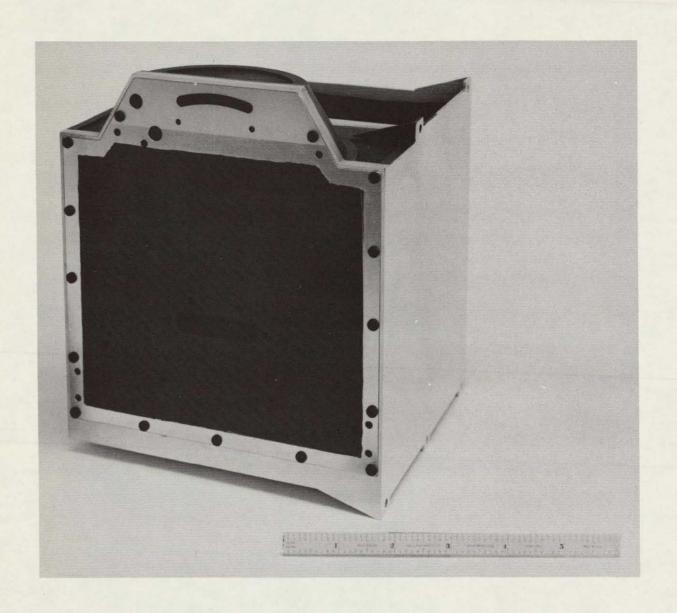

| 6.1-7     | Instrument Housing (photo)               | 264  |

| Figure No. |                                         | Page  |

|------------|-----------------------------------------|-------|

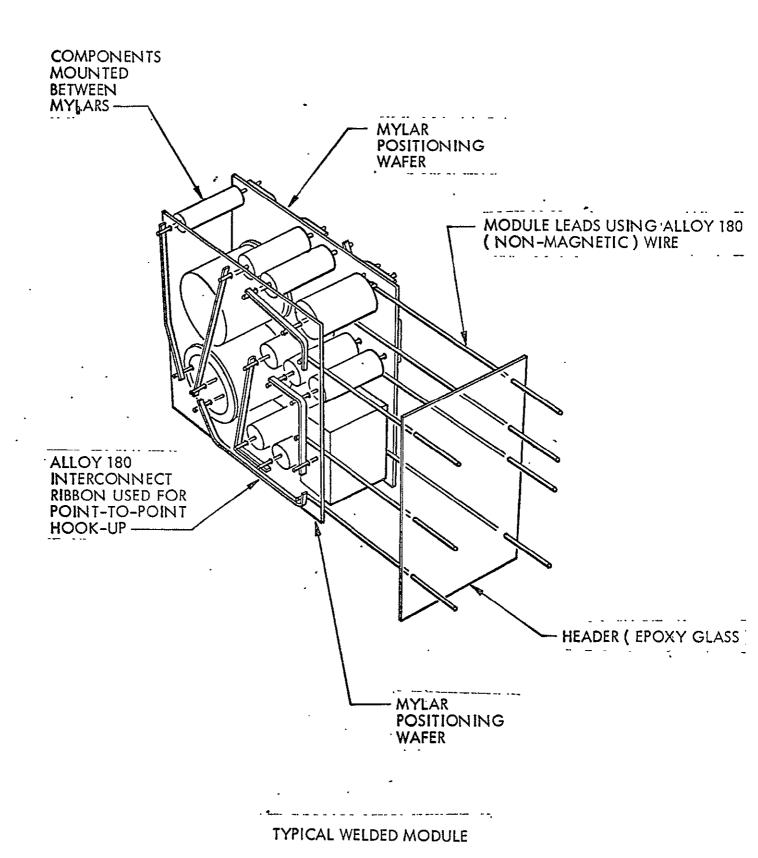

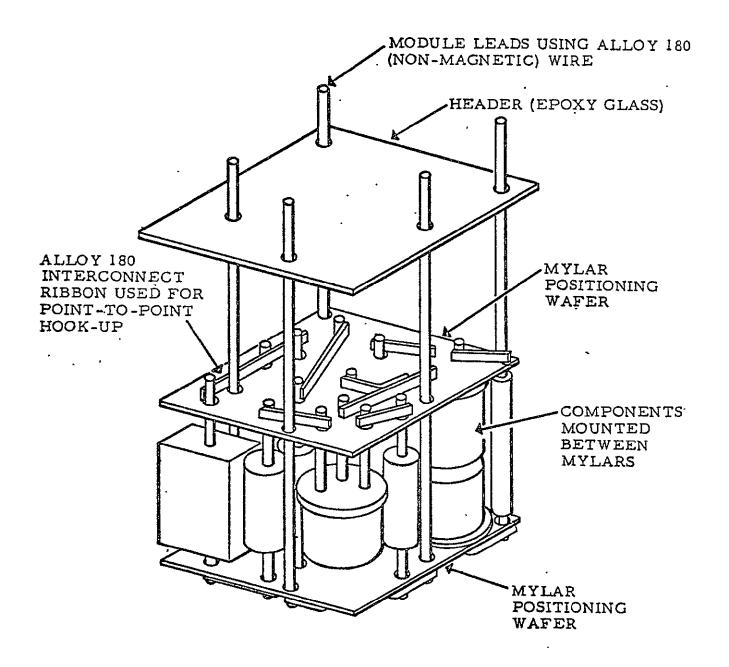

| 6.2-1      | Typical Welded Module                   | 267   |

| 6.2-2      | Welded Module                           | 268   |

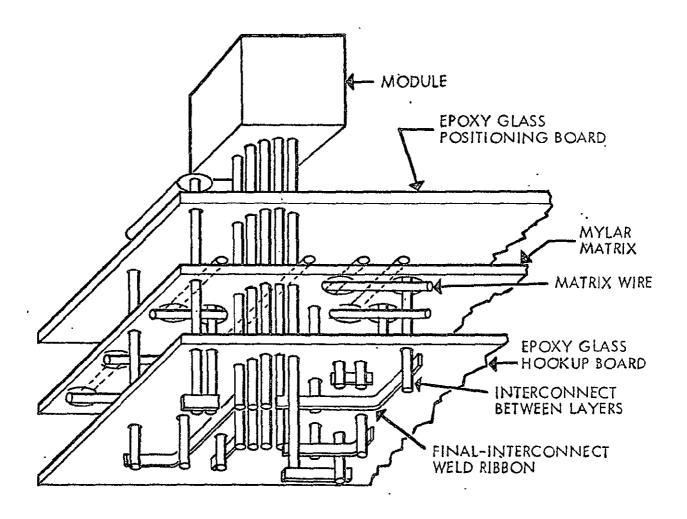

| 6.2-3      | Module Interconnect Matrix              | 270   |

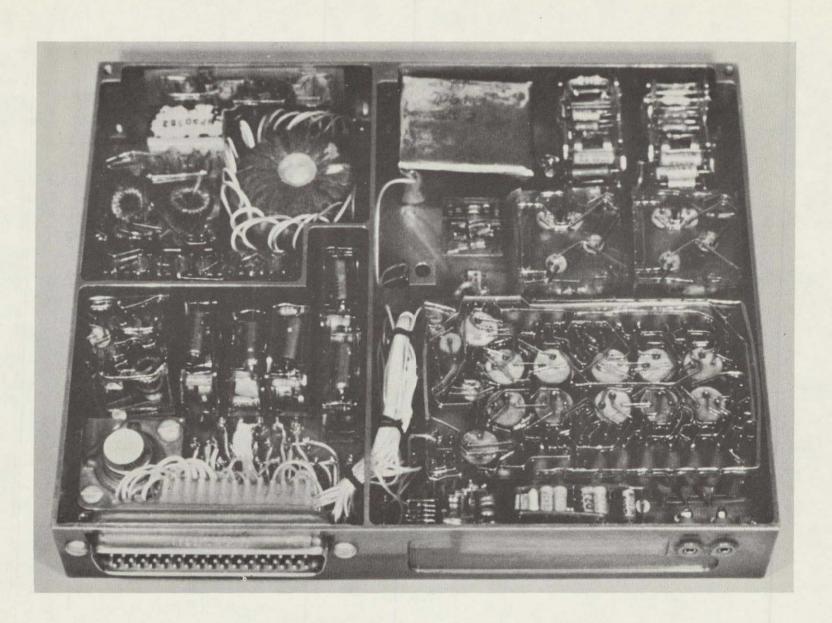

| 6.2-4      | Power Supply Blivet (photo)             | . 273 |

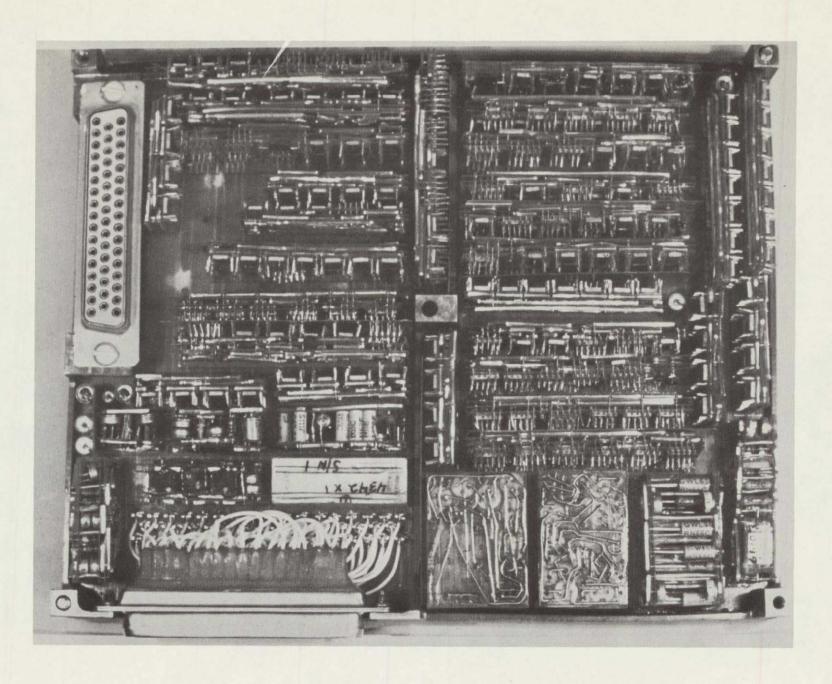

| 6.2-5      | Logic Blivet (photo)                    | 274   |

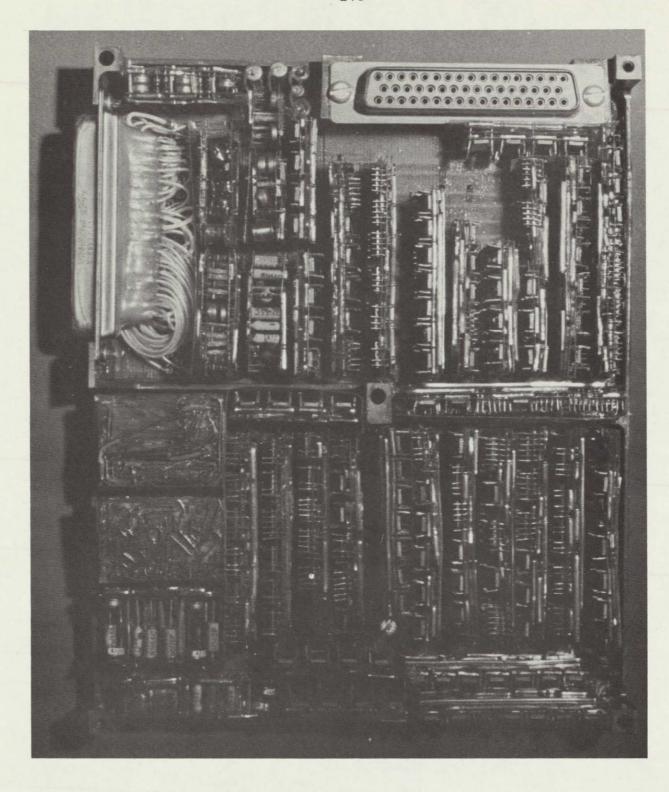

| 6.2-6      | Buffer Storage Blivet (photo)           | 275   |

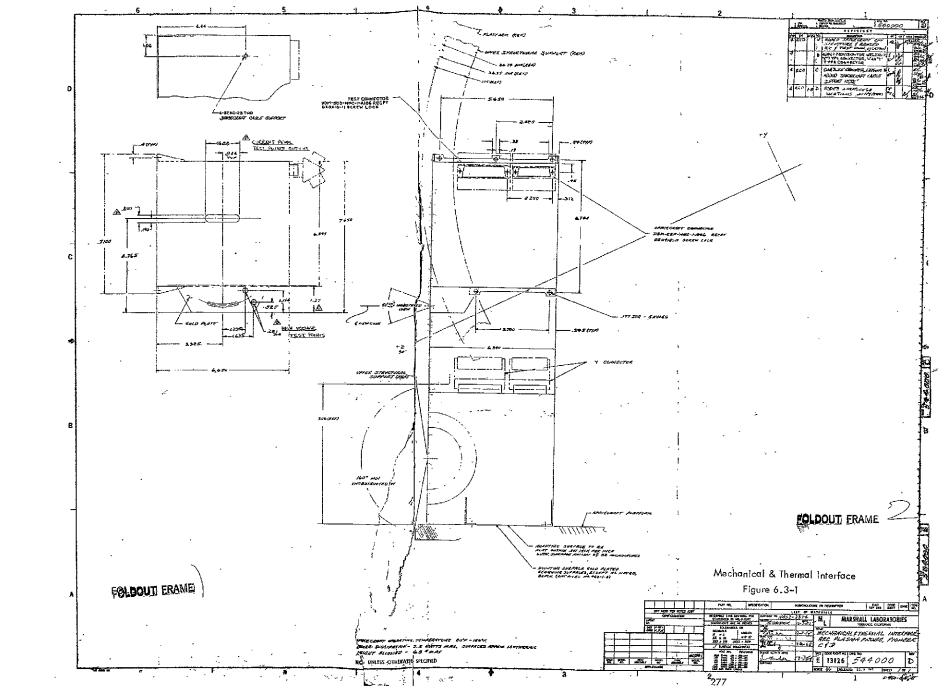

| 6.3-1      | Mechanical & Thermal Interface          | 277   |

|            |                                         |       |

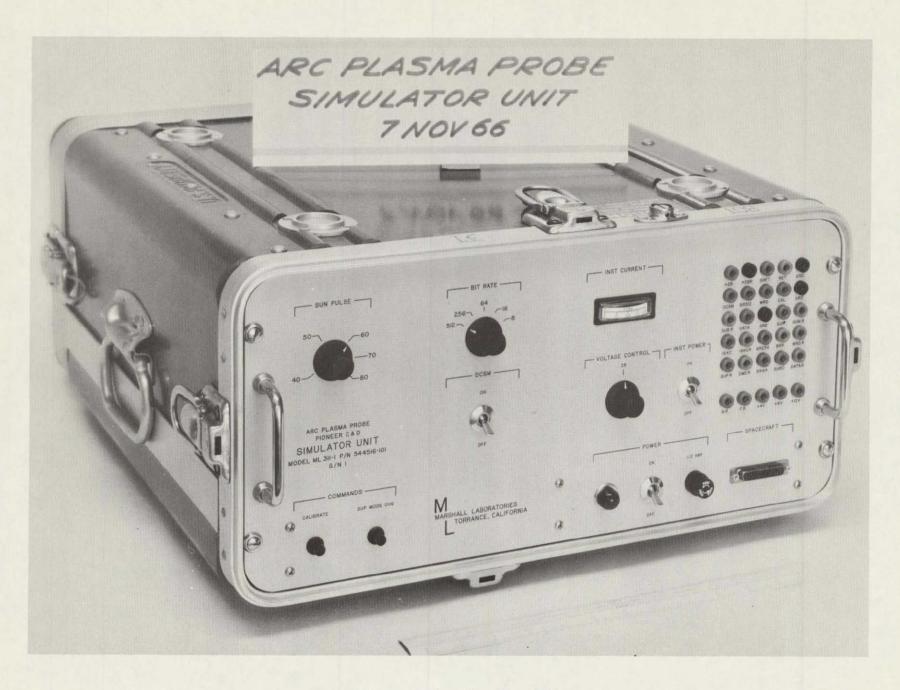

| 7.6.1-1    | Simulator Unit (photo)                  | 283   |

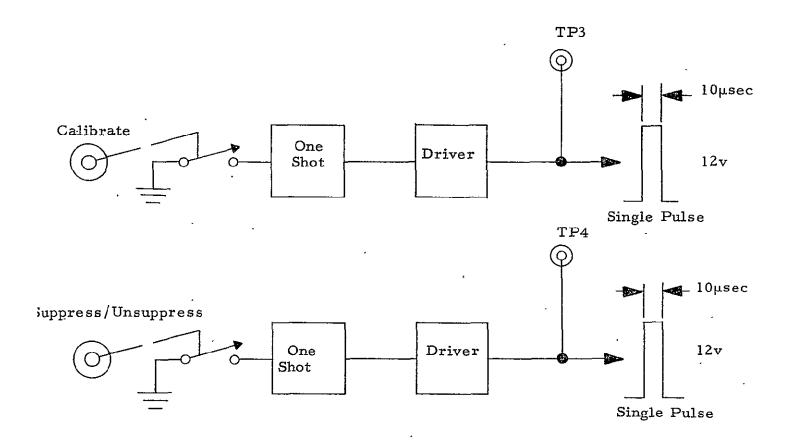

| 7.6.1-2    | Ground Commands, Block Diagram          | 284   |

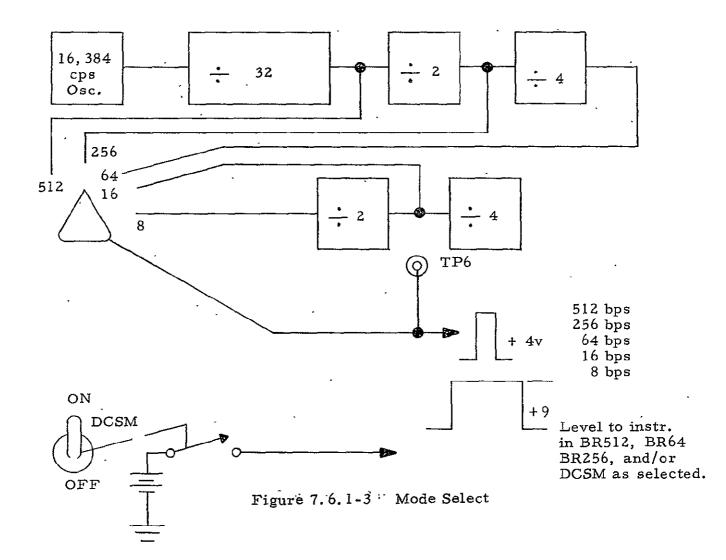

| 7.6.1-3    | Mode Select Block Diagram               | 285   |

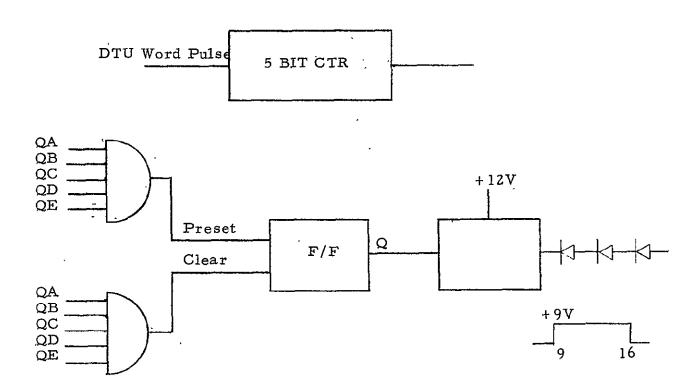

| 7.6.1-4    | GSE Word Gate Logic                     | 286   |

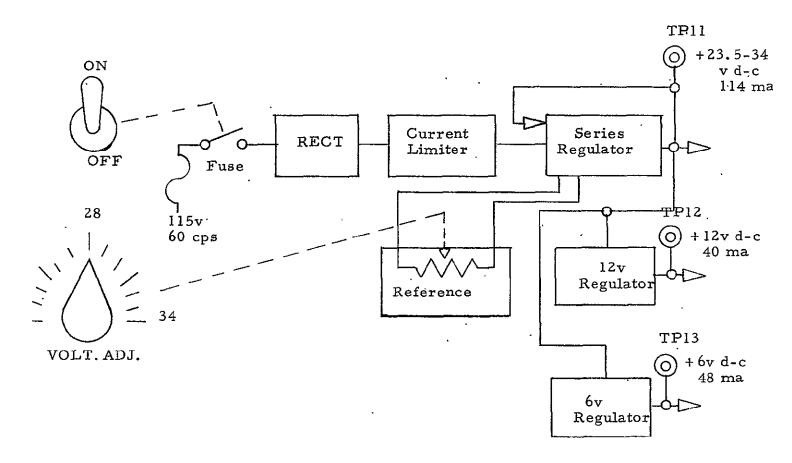

| 7.6.1-5    | GSE Power Supply                        | 287   |

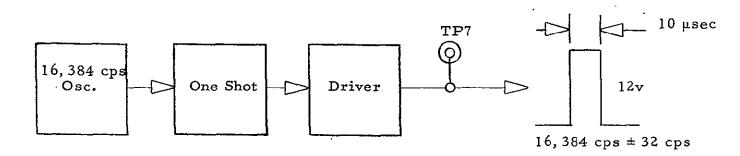

| 7.6.1-6    | GSE Pulse Generator                     | 288   |

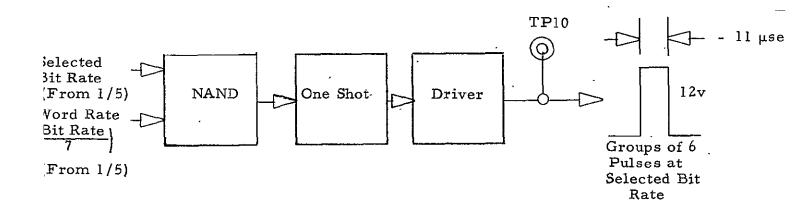

| 7.6.1-7    | GSE Shift Pulse Generator               | 288   |

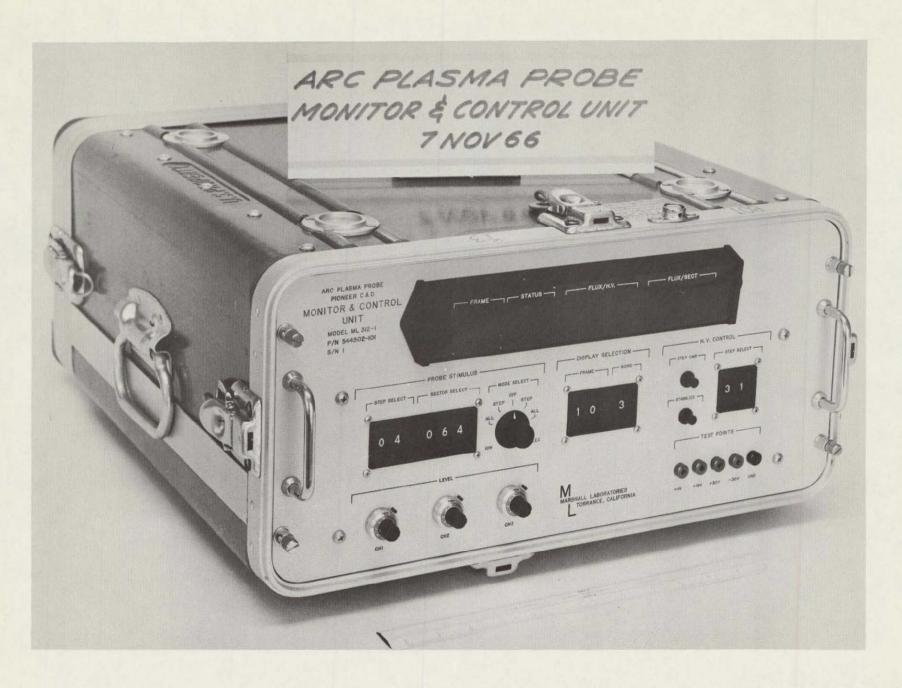

| 7.6.3-1    | Monitor and Control Unit                | 291   |

| 7.6.3-2    | GSE Input Data Encoding Circuit         | 292   |

| 7.6.3-3    | GSE Sector Selector and Ramp Generator  | 293   |

| 7.6.3-4    | GSE High Voltage Programmer Control     | 294   |

| 7.6.4-1    | Meter Unit (photo)                      | 296   |

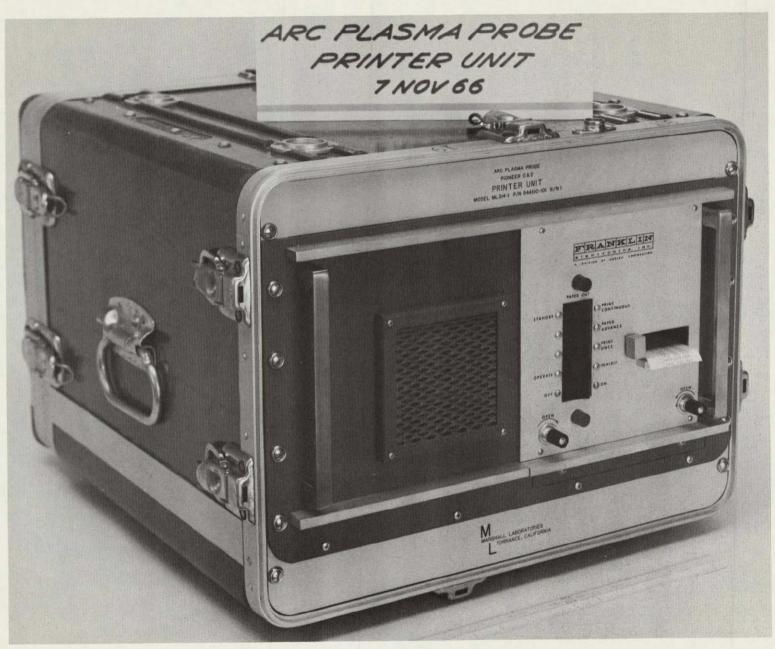

| 7.6.5-1    | Printer Unit (photo)                    | 297   |

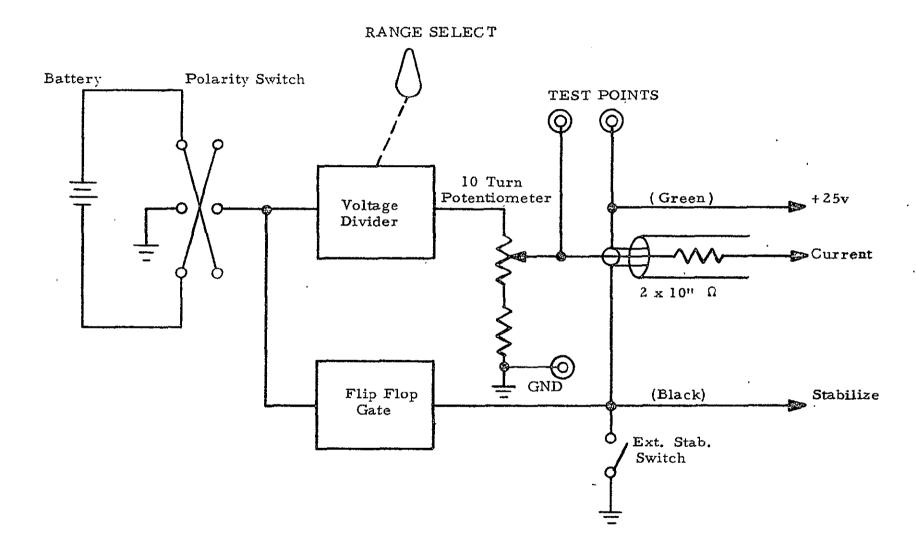

| 7.6.6-1    | Current Probe                           | 298   |

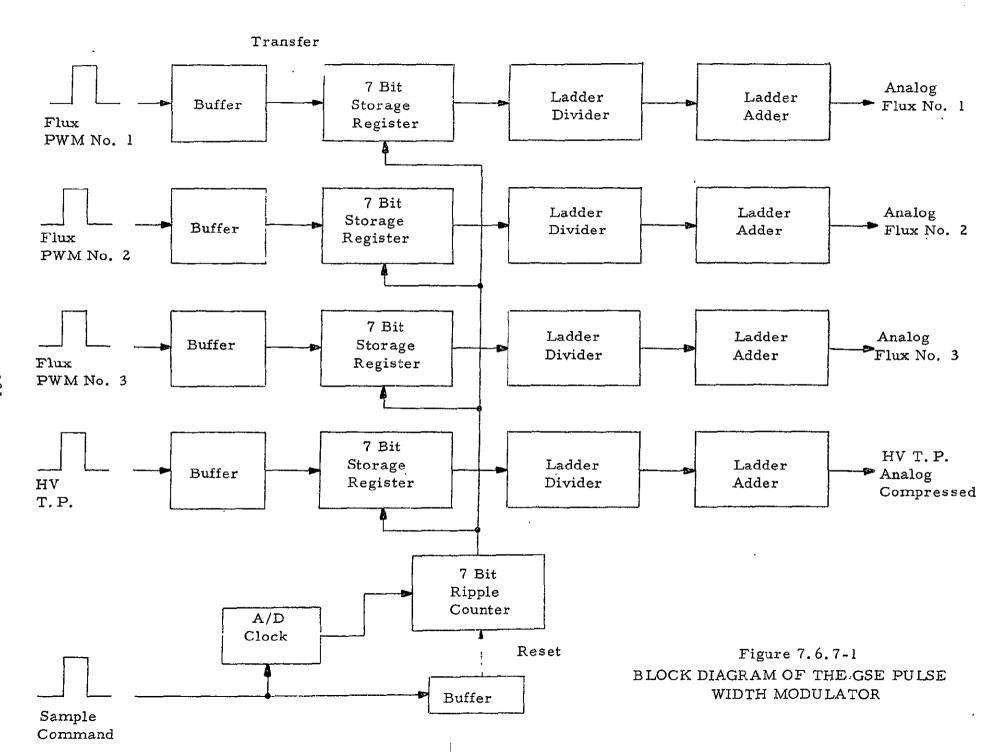

| 7.6.7-1    | (SE Pulse Width Modulator Block Diagram | 301   |

| 7.6.7-2    | Ladder Adder Schematic (GSE)            | 302   |

| 7.6.7-3    | A/D Clock Schematic (GSE)               | 303   |

# TABLES

| Table No. |                                   | Page    |

|-----------|-----------------------------------|---------|

| 3.2.1A    | Register Count and Sector         | 49      |

| 3.2.1B    | Sector Detector Truth Tables      | 51      |

| 3.2.1C    | Sector Detector Truth Tables      | 52      |

| 3.2.1D    | Sector Detector Truth Tables      | 53      |

| 3.2.1E    | Sector Detector Truth Tables      | 54      |

| 3.2.1F    | Sector Detector Truth Tables      | 55      |

| 3.2.1G    | Sector Detector Truth Tables      | 56      |

| 3.2.1H    | Sector Detector Truth Tables      | ·<br>57 |

|           |                                   |         |

| 3.2.5A    | Step Counter Truth Table          | 85      |

| 3.2.5B    | Cycle Counter Clock Truth Table   | 97      |

|           |                                   |         |

| 3.4.1A    | High Voltage Power Supply Inputs  | 169     |

| 3.4.1B    | High Voltage Power Supply Outputs | 170     |

|           | ·                                 |         |

| 4.1.6A    | Suppression Circuit Logic         | 190     |

|           |                                   |         |

| 7.6.1A    | Instrument Readout Format         | 289     |

#### ABBREVIATIONS OF LOGIC SIGNALS

A/D Analog-to-Digital

AS Azimuth Scan

BPS Bits per Second

BS Buffer Storage

CCC Cycle Counter Clock

DCSM Duty Cycle Storage Mode

EHVC End High Voltage Cycle

ESC Electron Suppression Code

FHVZ Force High Voltage Zero

HBR High Bit Rate

HV High Voltage

HVA High Voltage Advance

HVPS High Voltage Power Supply

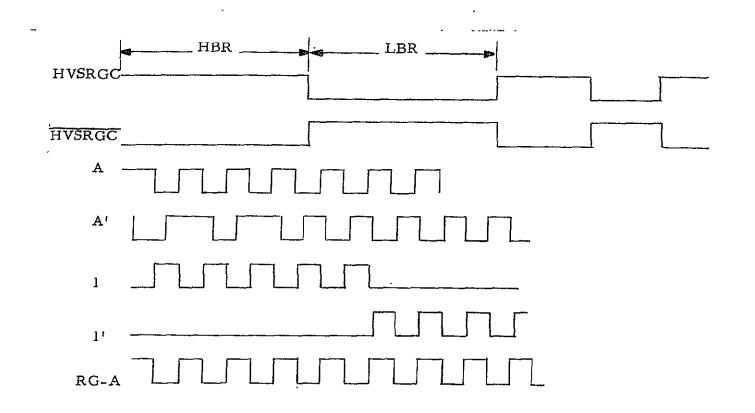

HVSRGC High Voltage Storage Register Gate Control

HVZ High Voltage Zero

ISC Ion Suppression Code

LBR Low Bit Rate

LPWM Logarithmic Pulse Width Modulator

LTSR Long Term Storage Register

MCn Mode Command Status Bit n

MFS Maximum Flux Scan

PS Polar Scan

PWM Pulse Width Modulator

RLTSR Reset Long Term Storage Register

SDMC Sun Pulse Delayed Mode Change

SID Suppressed Identification

S of EC Start of Electron Cycle

#### 1.0 INTRODUCTION

This engineering report describes the Pioneer C, D and E Plasma Probe instrument and associated Ground Support Equipment designed and fabricated by Marshall Laboratories (now Time-Zero Corporation) for Ames Research Center under NASA Contract NAS 2-3374.

The Plasma Probe instrument measures solar plasma charged particles in terms of flux, corresponding to energy level and incident direction of travel. This flux is detected by optical sensors and is converted to analog signals proportional to energy per unit charge.

#### 1.1 Scope

The report covers the electrical, mechanical, and thermal design of the instrument. Also included is the Ground Support Equipment description, new technology, test results, problem areas, and recommendations.

The Appendix contains pertinent stress analysis, worst case design analysis, description of IC logic, and other appropriate supplemental material.

For clarity and convenience, the electrical description portion of this report is divided into three sections:

- a. General Description (Section 2.0)

This section consists of a general discussion of the instrument's main features and interfaces.

- b. System Description (Section 3.0)

This section is primarily concerned with a more detailed description of instrument operation.

This will include logic networks, sensor mechanics, transfer functions, and information flow between circuit "blocks" without going into detailed circuit analysis.

c. Circuit Description (Section 4.0)

Detailed circuit operation is presented in this section.

#### 1.2 Delivered Units

The following units of Plasma Probe Experiment Model Number ML304-1 were designed, fabricated, tested and delivered:

- a. Engineering Prototype, Serial Number 8C05-1

- b. Flight 1 Instrument, Serial Number 8C05-2

- c. Flight 2 Instrument, Serial Number 8C05-3

- d. Flight 3 Instrument, Serial Number 8C05-4

Two sets of Ground Support Equipment were also designed, fabricated, tested and delivered.

#### 2.0 GENERAL DESCRIPTION

The Plasma Probe Instrument is designed to measure ion and electron density and angular distribution in outer space. This: flux is detected by optical targets and converted to analog signals whose amplitudes are proportional to the energy per unit charge as determined by the optics electrostatic potential and the solar wind flux and direction.

The input amplifier capability ranges from  $1 \times 10^{-14}$  amps to  $1 \times 10^{-9}$  amps.

This and other pertinent data is arranged in a particular digital format for transmission to earth. This can be seen in | Figure 2.0-1, Data Format.

| FRAME                                                                            |             | BR 5         | 12 \$ 2                                          | 2.56                                             |             |              |              | BR      | 64,1                                             | 6,8      | ELEC                                             | TRON      | / MOD               | E            |          |           |         |         |              | BR a                                             | 64,16    | ,8       | ION          | MOL                                              | E           |            |           | ,          | CA-COLOMBIA (TAIL)                               | -         |

|----------------------------------------------------------------------------------|-------------|--------------|--------------------------------------------------|--------------------------------------------------|-------------|--------------|--------------|---------|--------------------------------------------------|----------|--------------------------------------------------|-----------|---------------------|--------------|----------|-----------|---------|---------|--------------|--------------------------------------------------|----------|----------|--------------|--------------------------------------------------|-------------|------------|-----------|------------|--------------------------------------------------|-----------|

| BIT 5                                                                            | 1           | 2            | 3                                                | 4                                                | 5           | 1            | 2            | 3       | 4                                                | 5        | 16                                               | 7         | 8                   | 9            | 10       | 1         | 2       | 3       | 4            | 5                                                | 6        | 7        | 8            | 9                                                | 10          | 11         | 12        | /3         | 14                                               | 15        |

| <u> </u>                                                                         | FR'S        | FR'S         | FP'S                                             | FR'S                                             | ED'5        | FR           | FR           | F (2)   | FR                                               | FR       | FR                                               | FR        | FR                  | FR           | FR       | FR        | FR      | FR      | FR           | FR                                               | FR       | FR       | FR           | FR                                               | FR          | FR         | FR        | FR         | FR                                               | FR        |

|                                                                                  | 1,6         | 2,7          | 3,8                                              | 4,9                                              |             | 1            | 2            | FR<br>3 | 4                                                | 5        | 6                                                | 7         | 8                   | 9            | 10       | 1         | 2       | 3       | 4            | 5                                                | 6        | 7        | 8            | 9                                                | 10          | 11         | 12        | /3         | 14                                               | 15        |

|                                                                                  | <i>\$11</i> | £12          | \$13                                             | € 14                                             | £ 15        |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 5 6                                                                              | HVP         | BR<br>SCS    | MCI                                              | IFC<br>DCSM                                      | 561<br>562  | SID          | 56 i         | 56,     | 561<br>562                                       | 561      | HVP                                              | BR<br>SCS | MCI                 | DESM         | 561      | SID       | 561     | 561     | 567          | 56 /<br>562                                      | HVP      | 56 i     | 561          | 193                                              | 561         | HVP<br>51D | BR<br>SCS | MC1        | <i>IFC</i> ,<br>DCSM                             | S61       |

|                                                                                  | 23,2        | 755          | 79102                                            | J. Diri                                          | UUE         |              | 205          | 202     | 202                                              | <u> </u> | روزر ا                                           | 303       | 11111112            | DCDIN        | 202      | 10.0      | 302     | 12.74°  | 2004         |                                                  | ردان     | 802      | 302          | -302                                             | 002         |            | 200       | 111CZ.     | LA DIVI                                          | 1002      |

| 7-m p 20                                                                         |             |              | 1                                                |                                                  |             |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         | ļ            |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 3                                                                                |             | HV           | A5                                               | 12<br>12                                         | 18          |              |              |         |                                                  |          |                                                  | HV        | A5                  | 12<br>12     | A5<br>18 | <u> </u>  | _       |         |              |                                                  |          |          | ļ            |                                                  | <u> </u>    |            | HV        | A.S        | A5<br>12                                         | AS<br>18  |

| 11                                                                               |             | <del> </del> | <u> </u>                                         | 15-                                              | /0          |              |              |         |                                                  |          | <del> </del>                                     |           |                     | 12.          | 10       | r         |         |         |              |                                                  |          |          |              | <del></del>                                      | -           |            |           | φ.         | 1,5                                              | IB        |

| 12<br>13<br>14                                                                   |             |              |                                                  | L                                                |             |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 13                                                                               | P5<br>2     | <u> </u>     |                                                  | <del> </del>                                     |             | MF<br>1      | MF<br>4      | MF<br>7 | MF                                               | MF<br>13 | P5<br>2                                          |           |                     |              |          | MF<br>1   | MF<br>4 | MF<br>7 | MF           |                                                  | MF       |          | MF .<br>22   | MF                                               | MF          | <i>P</i> 5 |           |            | <b></b>                                          |           |

| 15                                                                               | <u> </u>    | -            |                                                  | <u> </u>                                         |             | 1            |              | -       | 10                                               | /_5      | -=-                                              |           |                     | <del> </del> |          | 2         | 7       |         | 10           | 13                                               | 16       | 1.9      | 25           | 25                                               | 28          | ~          |           |            |                                                  |           |

| 16                                                                               |             | A5           |                                                  | A5                                               |             |              |              |         |                                                  |          |                                                  | A5        | AS                  | A5           | A5       |           |         |         |              |                                                  |          |          |              |                                                  |             |            | A5        | A5         | A5                                               | A5        |

| 17                                                                               |             | 1            | 7                                                | /3                                               | 19          | <u> </u>     | ļ            |         |                                                  |          |                                                  | 1         | 7                   | 13°          | 19       |           |         |         |              |                                                  |          | ļ        | ļ            |                                                  |             |            | 1         | 7          | /3                                               | /9        |

| 10                                                                               |             | -            | -                                                |                                                  | -           | $\vdash$     |              |         |                                                  |          | -                                                |           |                     |              | <u> </u> |           |         |         |              | -                                                |          |          |              | <u> </u>                                         |             |            |           |            |                                                  |           |

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25                               |             |              | <b></b>                                          |                                                  |             |              |              |         |                                                  |          | <del> </del>                                     |           |                     | -            |          | <b></b> - |         |         |              |                                                  |          |          | -            |                                                  | ·           |            | -         |            |                                                  | $\Box$    |

| 21                                                                               |             |              |                                                  |                                                  |             |              |              | -       |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 25                                                                               |             | AS           | A5                                               | AS                                               | A5          |              | ļ            |         |                                                  |          | ļ                                                | A5        | A5                  | A5           | AS -     |           |         |         | -            | -                                                |          |          | <u> </u>     |                                                  |             |            | A5        | 10         | A5                                               | AS        |

| 24                                                                               |             | 2            | 8                                                | /4                                               | 20          | <del> </del> |              |         | <del>                                     </del> | -        | <del>                                     </del> | 5         | 8                   | 14           | 20       |           |         |         |              | <del>                                     </del> |          | <u> </u> |              | <del>                                     </del> |             |            | 2         | <i>8</i> 5 | 14                                               | 20 -      |

| 25                                                                               |             |              |                                                  |                                                  |             |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 26                                                                               | Dr.         | <u> </u>     | ļ                                                |                                                  | }           | 145          | 145          | 145     | 14.5                                             | 140      | 00                                               |           |                     | ļ            |          | 14,500    | 26.57   |         | 405          | ,,,,,                                            | 10.5     | 64.5     | 22 7         | 04.5-                                            | 445         | ~          |           |            |                                                  | <b>  </b> |

| <u>∠/</u><br>28:                                                                 | PS<br>1     | <u> </u>     | -                                                |                                                  | -           | MF 2         | MF<br>5      | MF<br>8 | III                                              | MF<br>14 | PS<br>1                                          |           |                     | <b>-</b>     |          | MF 2      | MF<br>5 | MF<br>B | ///          | MF<br>14                                         | MF<br>17 | MF       | <i>Mr</i> 23 | MF<br>26                                         | MF<br>29    |            |           |            | <del>                                     </del> |           |

| 29                                                                               |             |              | <b></b> -                                        |                                                  |             |              |              |         |                                                  |          |                                                  |           |                     |              |          | -         |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 30                                                                               |             | A5           | AS                                               | A5                                               | AS          |              |              |         | ļ                                                |          |                                                  | A5        | A5                  | A5           | A5.      |           |         |         |              |                                                  |          |          |              |                                                  |             |            | AS        | A5         | AS                                               | AS        |

| 32                                                                               |             | 3            | 9                                                | 15                                               | 21          | <del> </del> |              | -       | <del> </del>                                     | <u> </u> | <del> </del>                                     | 3         | 9                   | /5           | 21       |           |         |         |              |                                                  |          |          |              |                                                  |             |            | 3         | 9          | 15                                               | 21        |

| 33                                                                               | ļ. <b>-</b> |              | <b></b>                                          |                                                  |             | -            |              |         | -                                                |          | <b></b>                                          |           |                     |              |          |           |         |         |              |                                                  |          |          | <del></del>  | <u></u>                                          |             |            |           |            |                                                  |           |

| 34                                                                               |             | ļ            |                                                  | L                                                |             |              |              |         |                                                  |          | L                                                |           |                     |              |          |           |         |         |              |                                                  |          |          | ***          |                                                  | ,           |            |           |            |                                                  |           |

| 26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39 |             | -            | <del>                                     </del> |                                                  | <b>-</b>    | ļ            | <del> </del> |         | <u> </u>                                         |          | -                                                | ļ         |                     | <u> </u>     |          |           | <b></b> |         |              |                                                  |          |          |              |                                                  | 1           |            |           |            |                                                  |           |

| 37                                                                               |             | AS           | <i>A</i> 5                                       | AS                                               | A5          |              | +            |         |                                                  |          |                                                  | AS        | AS                  | A5           | AS       |           |         |         |              |                                                  |          |          |              | -                                                |             |            | A5        | A5         | A5                                               | A5        |

| 38                                                                               |             | 4            | 10                                               |                                                  | 22          |              |              |         |                                                  |          |                                                  | 4         | 10                  | 16           | 22       |           |         |         |              |                                                  |          |          |              |                                                  |             |            | 4         | 10         | 16                                               | 22        |

| 39                                                                               | ļ           | <u> </u>     |                                                  |                                                  | ļ. <u>.</u> |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           |            | ļ                                                |           |

| 40<br>41<br>42<br>43                                                             | P5          | -            |                                                  | <del> </del>                                     |             | MF           | MF           | MF      | MF                                               | MF       | P5                                               |           |                     | ·            | <u> </u> | ME"       | МÈ      | AA E    | MF           | MF                                               | MF-      | MF       | MF"          | MF                                               | ME          | . PS       |           |            | j                                                |           |

| 42                                                                               | 3           | <b> </b>     | <b> </b>                                         | <del>                                     </del> |             | 3            | 6            | 9       | 12                                               | 15       | 3                                                |           |                     |              | <u> </u> | 3         | 6       | 9       | 12           | 15                                               | 18       | 21       | 24           | 27                                               | 30          | 3          |           |            | <del>-</del>                                     |           |

| 43                                                                               |             |              |                                                  |                                                  |             |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         | ,       |              |                                                  |          |          |              |                                                  |             |            |           |            |                                                  |           |

| 44                                                                               |             | A5           |                                                  | A5                                               | AS          | ļ            |              | -       |                                                  |          |                                                  | AS        | <i>AS</i>           | 17           | AS       |           |         |         |              |                                                  |          |          |              |                                                  |             |            | AS C      | A5         |                                                  | A5        |

| 45<br>46                                                                         |             | 1-           | H                                                | //                                               | 23          | ļ            | <del> </del> |         |                                                  |          | <u> </u>                                         | 5         | - 1/                | 1/           | 23       |           |         |         |              |                                                  |          |          |              |                                                  |             |            | 5         | _//_       | 17                                               | 23        |

| 47                                                                               |             |              |                                                  |                                                  |             |              | 1            |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  |             |            |           | v          |                                                  |           |

| 48                                                                               |             | I DOUT       | FDARAG                                           |                                                  |             |              |              |         |                                                  |          |                                                  |           | والمستناد والمستراد |              |          |           |         |         | more made as |                                                  |          |          | Marine, re   | ,,re                                             | Arter comme |            | .,]       | 20.50      |                                                  |           |

|                                                                                  | FUL         | DOUT.        | <u>C</u> RAME                                    | - 5                                              |             |              |              |         |                                                  |          |                                                  |           |                     |              |          |           |         |         |              |                                                  |          |          |              |                                                  | -           |            | 1         | .OLDO!     | JT FRA                                           | IVIE      |

#### NOTES to Figure 2.0-1, Data Format:

SCS: Sector Command Status

HVP: High Voltage Polarity

SID: Suppression ID

MCl, 2: Sup. Mode Command Status

IFC: In Flight Cal Status

SG 1, 2: Sector Generator Status

BR: Bit Rate

DCŠM: Duty Cycle Storage Mode

#### ELECTRON MODE:

MF 1 to MF 15 14 Electron steps plus zero step

POSITIVE ION MODE:

MF 1 to MF 30 30 Ion steps

#### **DEFINITIONS:**

DCSM: 1 for DCSM PS 1: Bottom target data

0 for normal operation PS 2: Center target data

HVP: 1 for Ion Mode PS 3: Top target data

0 for Electron Mode

SID: 0 for unsuppressed

1 for suppressed

BR: 1 for High Bit Rate (512 BR, 256 BR)

0 for Low Bit Rate

MC 1, 2: 0 for unsuppressed

0 for suppressed

$\frac{1}{1}$  for Automatic Suppression

IFC: 1 for IFC on

0 for IFC off

SG 1, 2: 1 for Fast (Lead Sun pulse)

0 for Slow (Lag Sun pulse)

SCS: I for normal operation

0 for delayed Sector Gen.

The other data includes High Voltage polarity (to identify positive or negative particle measurement), section information, bit rate (to identify message format), suppression mode, calibration status, and certain other information pertaining to the operation of the instrument.

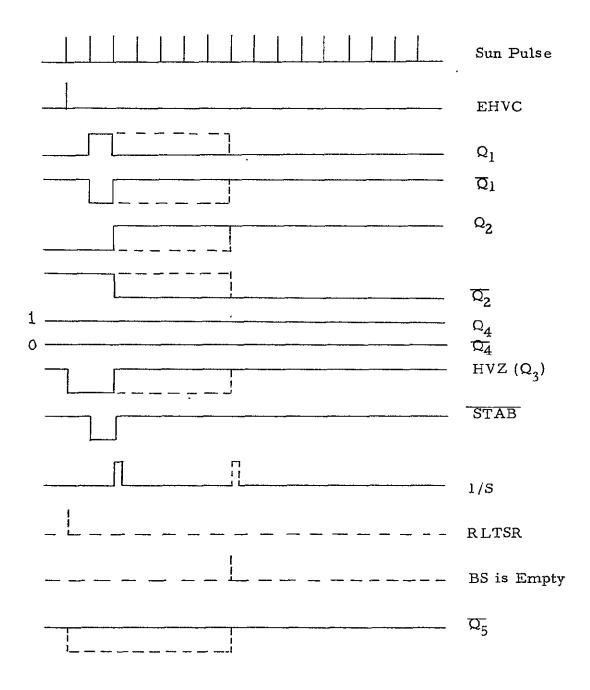

The spacecraft, using a sun sensor, generates a pulse for each revolution of the spacecraft. The Sun Pulse occurs at a nominal rate of 60 ppm, but the rate can range from 54 to 80 ppm. This Sun Pulse is the basic timing signal for the operation of the instrument. Using this Sun Pulse repetition rate, the instrument divides each revolution of the spacecraft into 128 equal angels called Sectors.

Three techniques are used for collecting flux data:

- a. Polar Scan (PS), during which all three targets are used. The instrument detects the sector in which a maximum flux was measured, and the amplitude of this flux at each target.

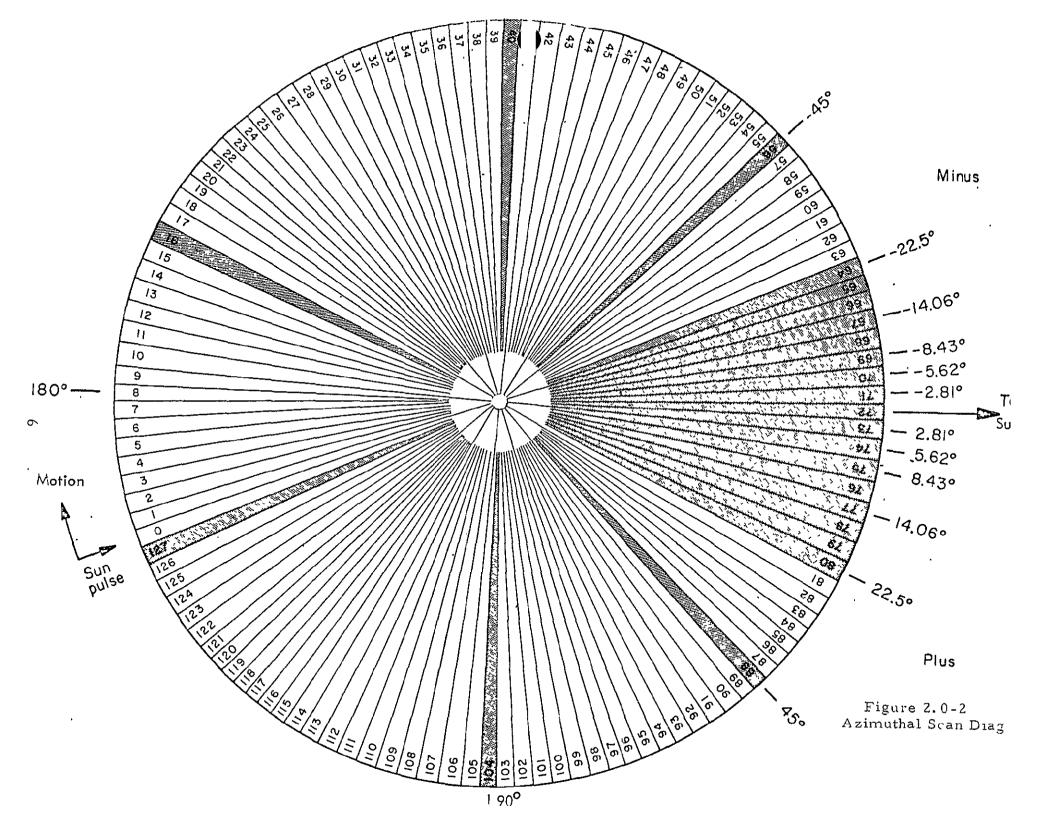

- b. Azimuthal Scan (AS), during which the instrument is programmed to detect the flux collected by the center target at each of 23 particular sectors out of the 128 equal intervals. See Figure 2.0-2 for the Azimuthal Scan Diagram. The shaded areas show the AS Sectors.

- c. Maximum Flux Scan (MFS), which is similar to the Polar Scan. Here, the amplitude of the flux collected only by the center target is measured. The amplitude of the maximum flux during each revolution and the sector in which it occurs are detected.

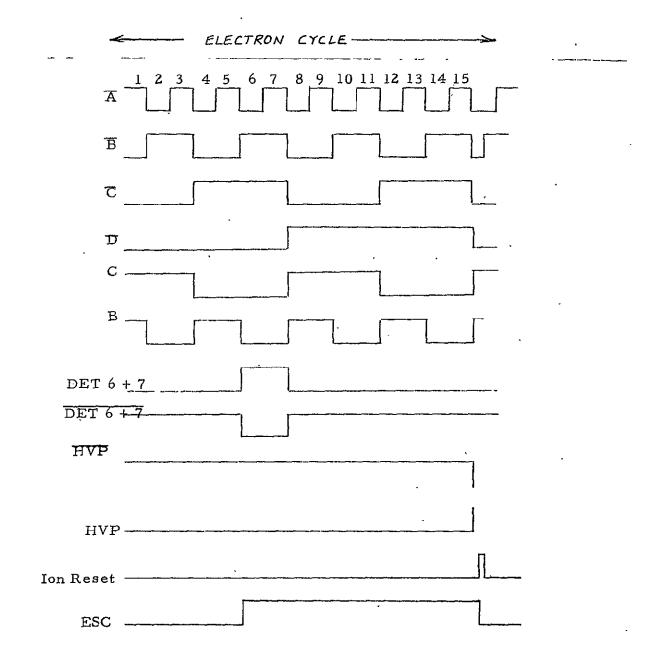

Ion measurements are made at each of thirty levels of analyzer voltage while electrons are measured at each of 15 levels.

When data is transmitted at high bit rates (512 or 256 BPS), one PS and AS is made for each level of high voltage.

At low bit rates (64, 16 or 8 BPS or Duty Cycle Storage Mode-DCSM), one MFS is made for each level of analyzer voltage. After the last voltage step during an Ion cycle, the analyzer voltage is set to that level at which the maximum flux was detected; then one PS and one AS is made.

After the last analyzer voltage step of an Electron cycle, the analyzer voltage is set to the level of the seventh step, and one PS and one AS is made.

Therefore, during high bit rate, in Ion mode, the instrument makes one PS during one revolution and one AS during the next revolution for each of thirty analyzer voltage levels. At a nominal Sun Pulse rate of 60 ppm, 60 seconds are required for one Ion cycle.

During electron mode, the same sequence occurs for each of fifteen levels of high voltage. At the nominal Sun Pulse rate, 30 seconds are required for an electron cycle.

At low bit rates, during Ion mode, the instrument makes one MFS during each revolution for each of thirty analyzer voltage levels, then one PS during an additional revolution and one AS during another revolution. This requires five revolutions minimum for each Ion cycle, which includes three stabilization periods.

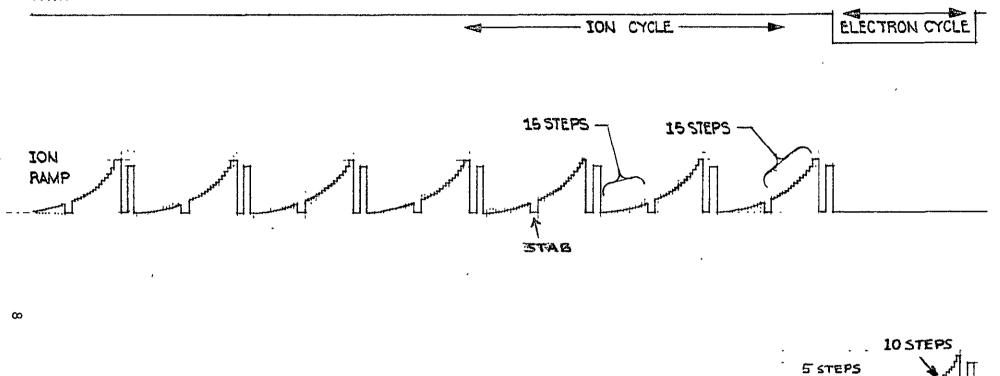

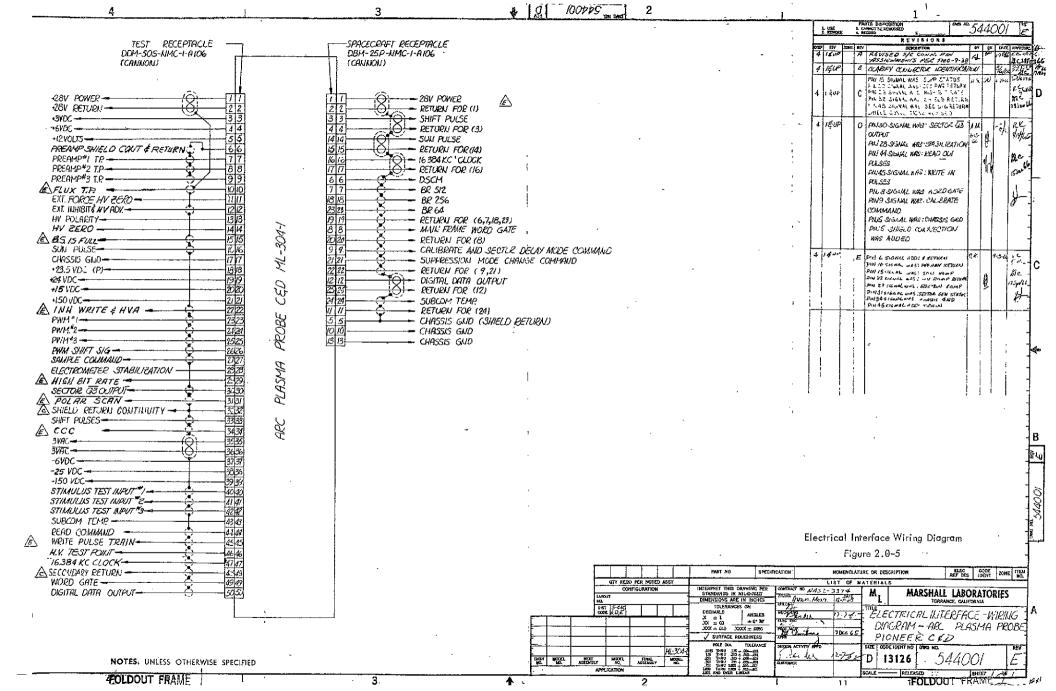

During electron mode, the same sequence occurs for each of fifteen levels of analyzer voltage followed by one PS and one AS. 28 revolutions are required for an electron cycle, which includes two stabilization cycles. See Figures 2.0-3 and 2.0-4 for the HV Stepping Sequence diagrams.

The above statements regarding timing are made for explanatory purposes. Practically, these times are several seconds longer. For instance, midway through an Ion cycle the sequence is stopped and the analyzer voltage reduced to zero for two Sun Pulse periods.

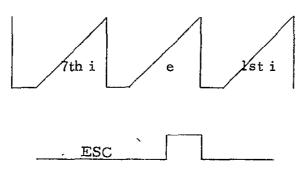

ELECTRON RAMP

Figure 2.0-3, Figh Voltage Stepping Sequence, Low Bit Rate

Figure 2.0-4, High Voltage Stepping Sequence, High Bit Rate

The sequence is also stopped and the analyzer voltage is reduced to zero for four Sun Pulse periods any time the suppression mode is changed, such as occurs between the fifth and sixth analyzer voltage steps of an electron cycle or between an Electron and Ion cycle. These analyzer voltage zero periods are used for stabilizing the Electrometer amplifier.

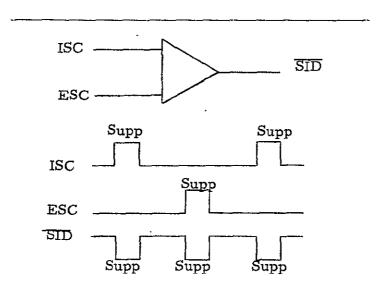

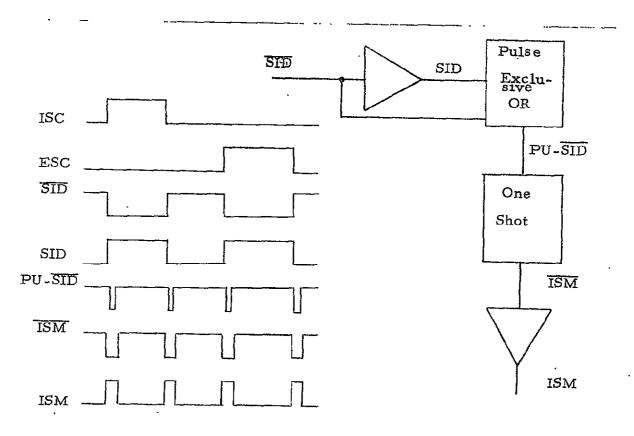

At both high and low bit rates the instrument is sequenced through seven Ion cycles, then through one Electron cycle. For the first five steps of an Electron cycle, the targets are operated with unsuppressed secondary emission and the remaining steps are in a suppressed mode.

During Ion cycles, the instrument operates in one of three suppression modes. These modes are: all unsuppressed, all suppressed, and automatic suppression. During automatic suppression the first three and the last three Ion cycles are unsuppressed and the fourth Ion cycle is suppressed.

The suppression mode can be changed by Earth Command.

This command can be received at any time and stored in the instrument. The command is executed at the start of the next Electron cycle.

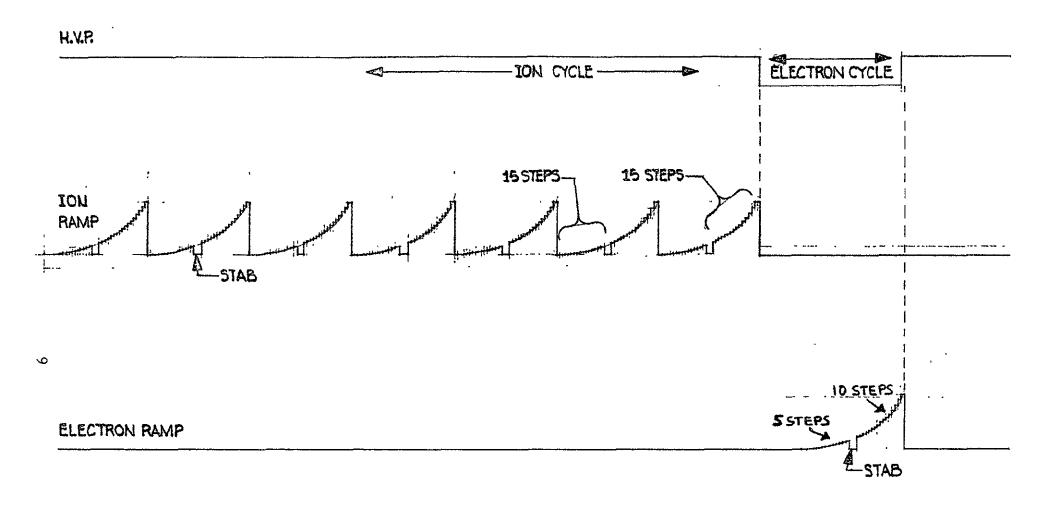

See Figure 2.0-5 for the Electrical Interface Wiring Diagram. Appendix A shows the specification of Integrated Circuit logic used in the system.

#### 2.1 Subsystems General Description

The instrument consists of fourteen electrical subsystems plus the Optics section. These subsections are as follows:

- a. Electrometer Amplifier

- b. Attenuation and Pulse Width Modulator

- c. Timing and Control

- d. Sector Programmer

- e. Target Programmer

- f. High Voltage Programmer

- g. Analog-to-Digital (A/D) Converter

- h. Commutator

- i. Status Decoder

- j. Calibrate and Sector Delay

- k. Buffer Storage

- 1. Temperature Sensor

- m. High Voltage Power Supply .

These sub-systems are arranged into four sub-assemblies:

- a. <u>Electrometer Amplifier</u> contains the Optics, Electrometer Amplifier, and the Attenuation and Pulse Width Modulator.

- b. Logic consists of the Analog-to-Digital (A/D)

Converter, Target Programmer, Sector Programmer,

Timing and Control, Temperature sensor, Status Decoder, Commutator, and High Voltage Programmer.

- c. <u>Buffer Storage</u> contains only the Buffer Storage circuitry.

- d. Power Supply contains the high and low voltage power supplies.

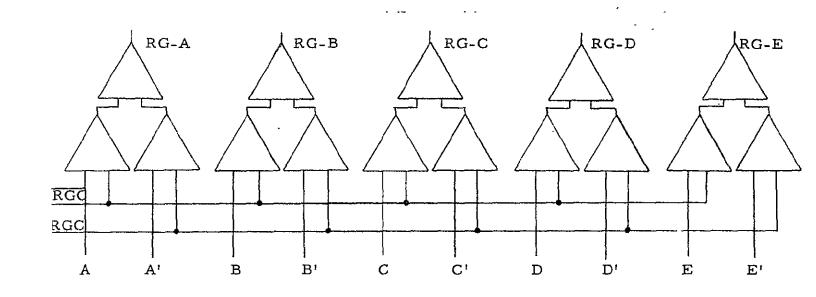

A block diagram of the system is shown in Figure 2.1-1. The Interconnect Schematic can be seen in Figure 2.1-2. See Appendix B for the master drawing list, Operational Test specification, and Flight Acceptance Test Specification. Appendix C shows a typical Flight Acceptance Test Report.

Functional Block Diagram ARC Plasma Probe Figure 2.1-1

#### 2.1.1 Electrometer Amplifier

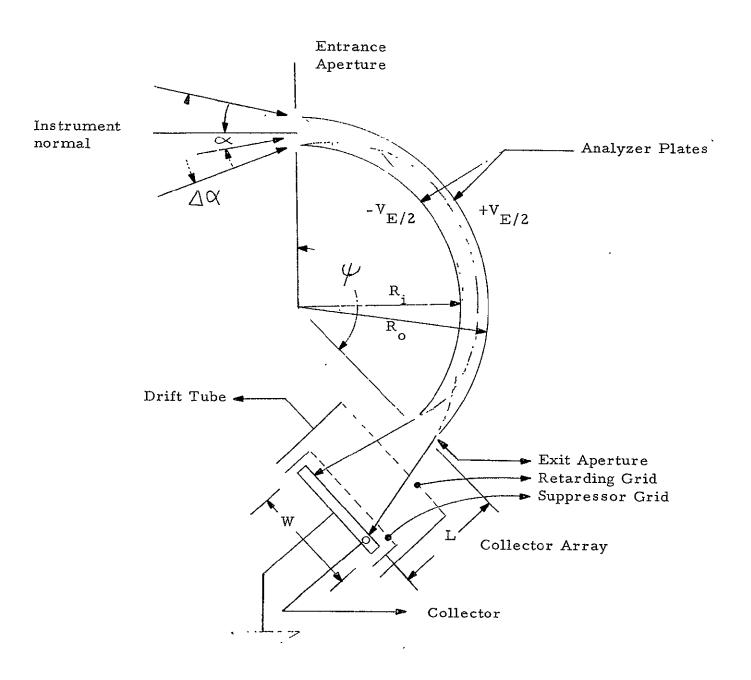

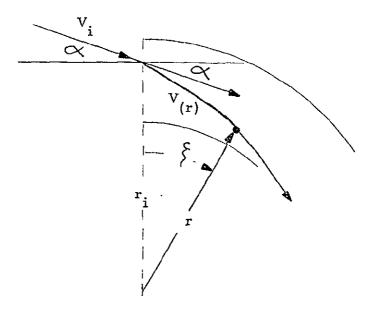

#### 2.1.1.1 Optics

The Optics consist of two concentric spherical analyzer plates that, when properly biased, produce an electrostatic field. Ions entering this field are deflected, and only those having a pre-determined  $\frac{E}{O}$  range can reach the current detectors.

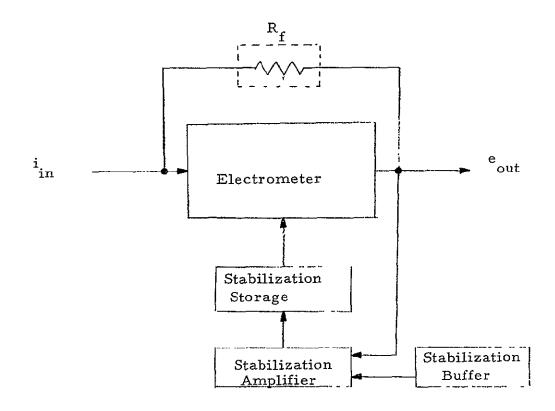

#### 2.1.1.2 Electrometer

Each target is connected to a current amplifier. The amplifier produces a positive output voltage for negative particle inputs, and a negative output voltage for positive particle inputs.

Range of operation is  $1 \times 10^{-14}$  amperes to  $1 \times 10^{-9}$  amperes for the input, and 0.0032 volts to 21.5 volts for the output. The amplifier has been designed to minimize noise, drift, and response time, and to ensure reliable operation for the life of the instrument.

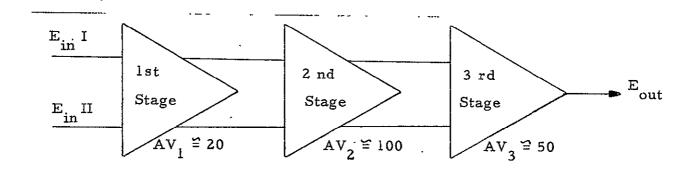

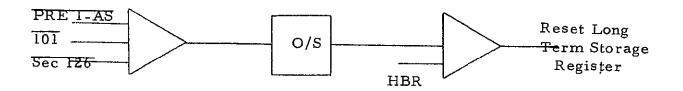

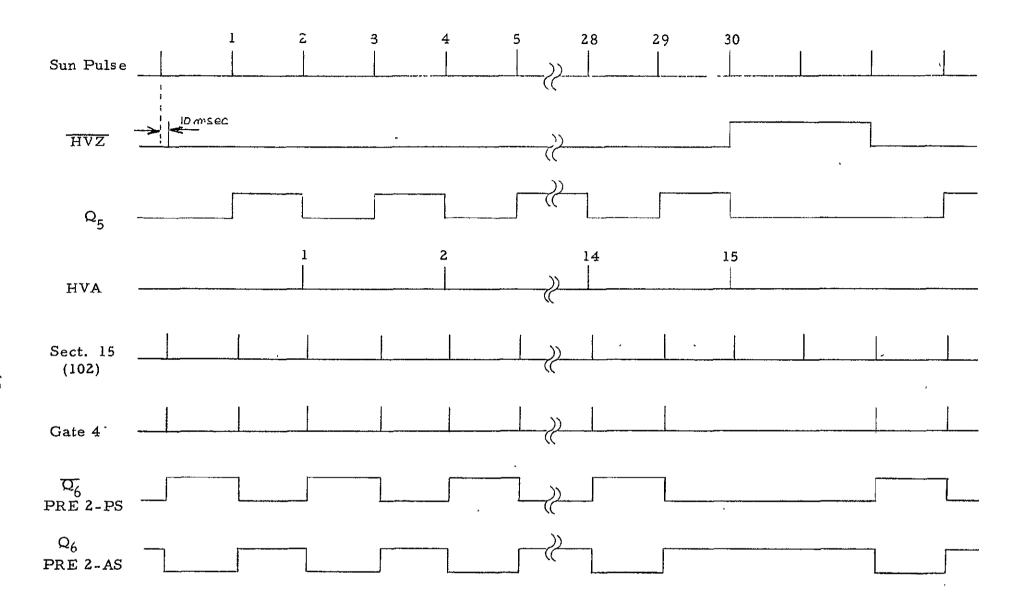

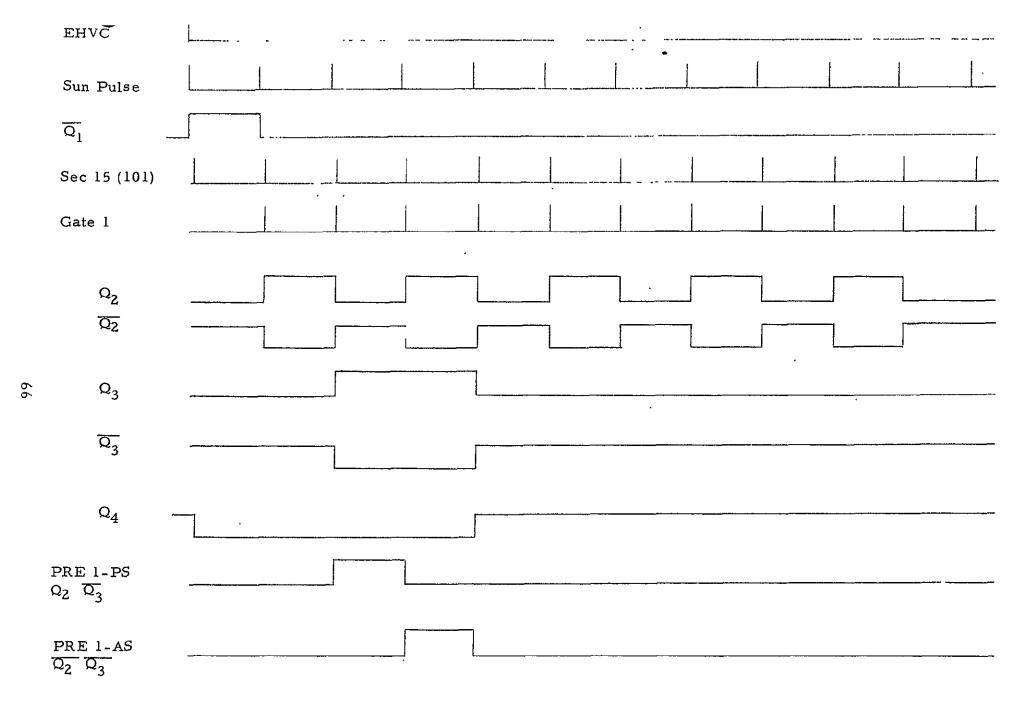

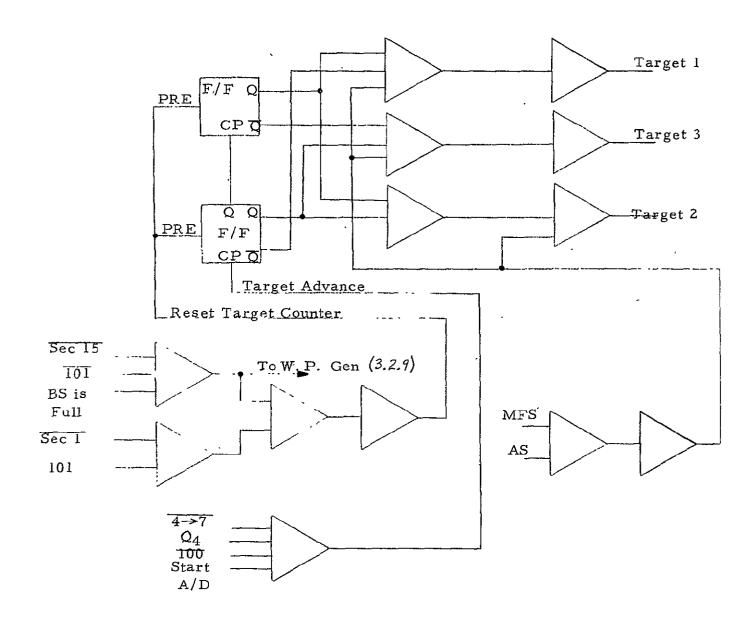

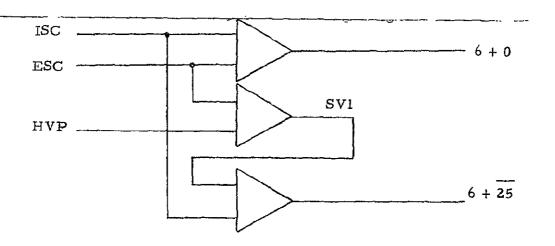

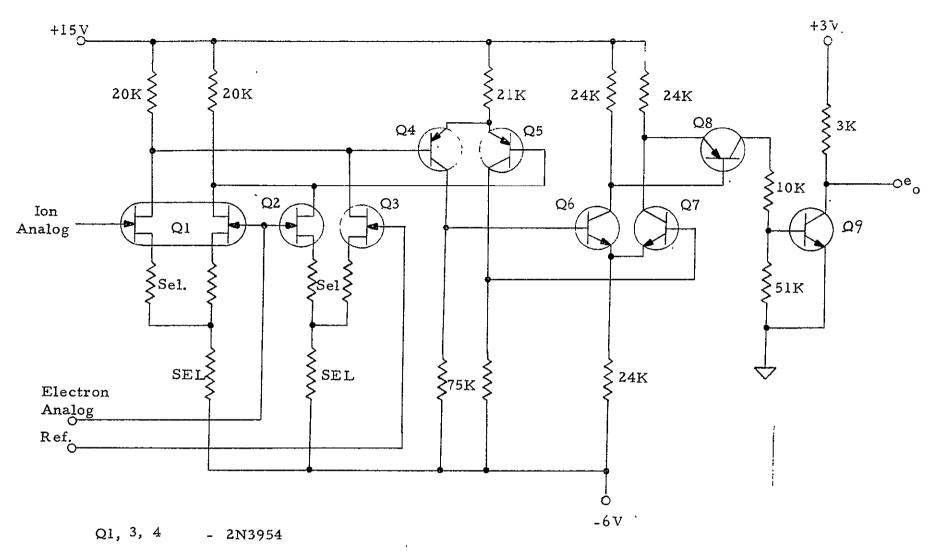

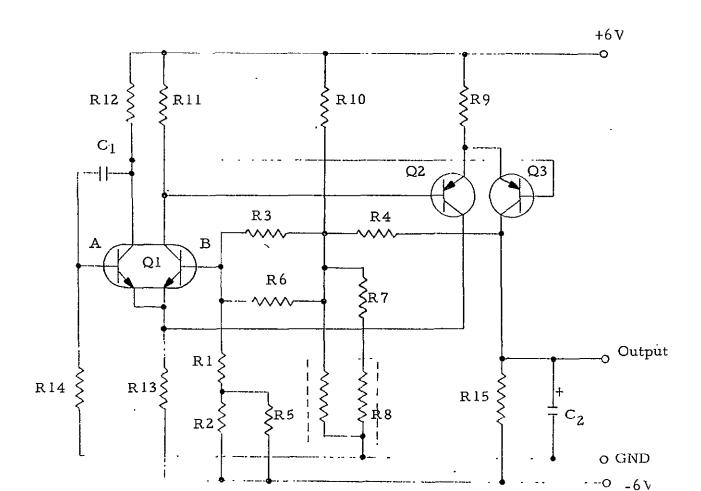

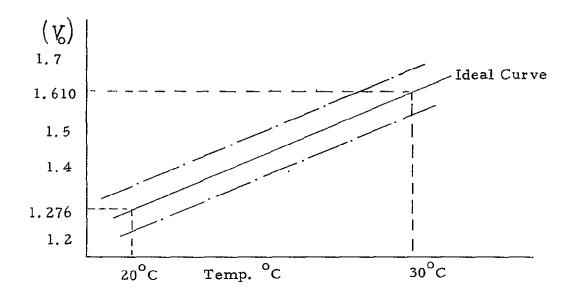

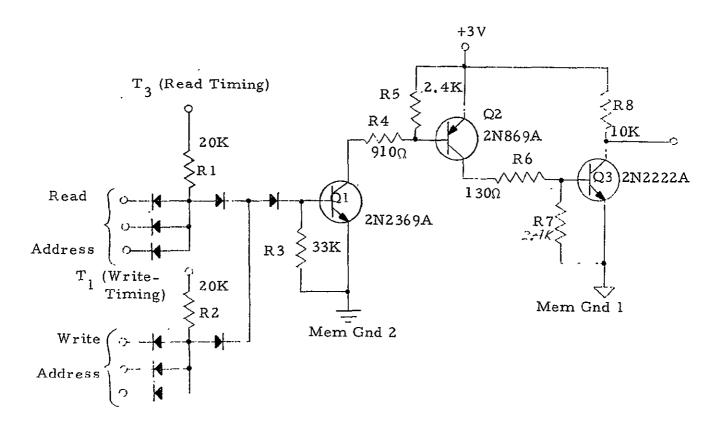

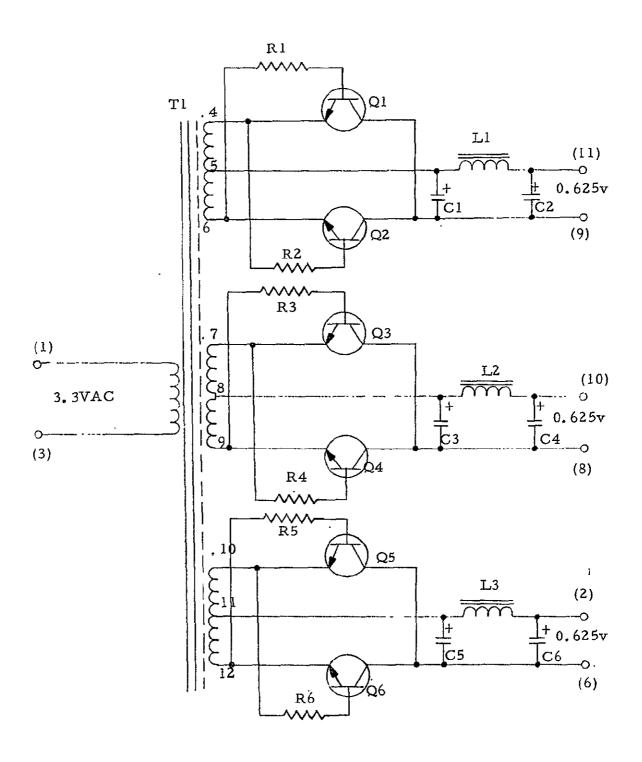

#### 2.1.1.3 Attenuation and Pulse Width Modulation