# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

EDET CASE FILE COPY N71-14723 (ACCESSION NUMBER) ACILITY FORM 602 (THRU) G3 (CODE)  $\frac{206}{(PAGES)}$   $\frac{CR - 108672}{(NASA CR OR TMX OR AD NUMBER)}$ 08 (CATEGORY) INTERMETRICS

Final Report

Engineering Study for A Mass Memory System For Advanced Spacecrafts

By: Alex L. Kosmala, John P. Green, and Fred H. Martin

١

August 1970

Prepared under Addition #1 to Contract NAS 9-9763 by

> INTERMETRICS, INC. 380 Green Street Cambridge, Massachusetts 02139

#### Foreword

This document is the final report of an engineering study of mass memory systems for advanced manned spacecrafts. The work was performed as an extension of a Multiprocessor Computer Systems study, which was previously reported. This effort was sponsored by the National Aeronautics and Space Administration's Manned Spacecraft Center, Houston, Texas under contract NAS 9-9763. It was performed by Intermetrics, Inc., Cambridge, Massachusetts under the technical direction of Alex L. Kosmala.

The study program covered the period from December 1, 1969 through July 1, 1970. The Technical Monitor for the Manned Spacecraft Center was Mr. James P. Ledet.

The publication of this report does not constitute approval by the NASA of the findings or the conclusions contained therein. It is published for the exchange and stimulation of ideas.

١.

- - .

i

# Table of Contents

| Page |

|------|

|      |

| Chapter | 1. Objective and Summary of Study          | 1   |

|---------|--------------------------------------------|-----|

| 1.1     | Introduction                               | 1   |

| 1.2     | Technology Review                          | 2   |

| 1.3     | Memory Requirements                        | 4   |

| 1.4     | Recommendations                            | 5   |

| 1.5     | Final Word                                 | 5   |

| Chapter | 2. Review of Memory Technologies           | 7   |

| 2.1     | Introduction                               | 7   |

| 2.2     | Ferrite Cores                              | 9   |

| 2.3     | Planar Films                               | 28  |

| 2.4     | Plated Wire                                | 44  |

| 2.5     | Block Oriented Magnetic Memory Techniques  | 61  |

| 2.6     | Semiconductor Techniques                   | 76  |

| 2.7     | Beam Accessed Memory Technologies          | 115 |

| 2.8     | Cryogenic Memory Technology                | 143 |

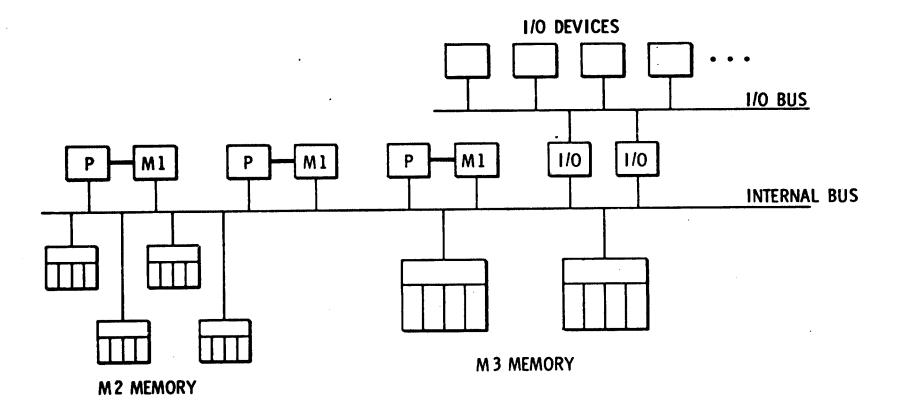

| Chapter | 3. Mass Memory Requirements                | 148 |

| 3.1     | Multiprocessor Design Introduction         | 148 |

| 3.2     | Memory Performance Requirements            | 154 |

| 3.3     | Memory Physical Requirements               | 160 |

| 3.4     | Environmental and Operational Requirements | 166 |

| Chapter | 4. Evaluation and Recommendations          | 179 |

| 4.1     | General Evaluation Criteria                | 179 |

| 4.2     | Evaluation Strategy                        | 182 |

| 4.3     | Comparison of Memory Technologies          | 183 |

| 4.4     | Comparison of Technologies for Ml          | 183 |

| 4.5     | Comparison of Technologies for M2          | 188 |

| 4.6     | Comparison of Technologies for M3          | 193 |

| 4.7     | Summary of Recommendations                 | 200 |

- Warden

Nor International

List of Figures

1

| Figure     |                                          | Page |

|------------|------------------------------------------|------|

| Chapter 2. |                                          |      |

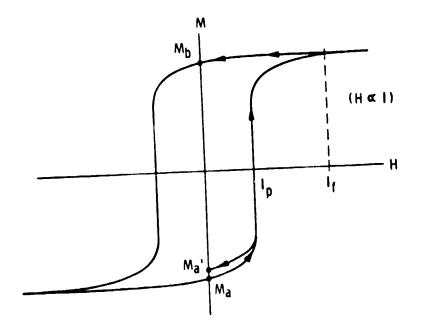

| 2.2.1      | Ferrite Hysteresis Loop                  | 10   |

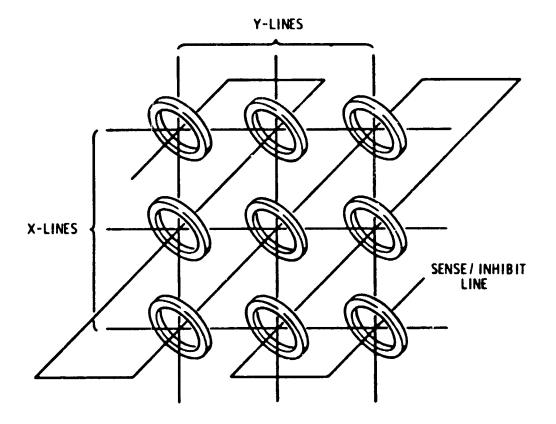

| 2.2.2      | Ferrite Core Array                       | 10   |

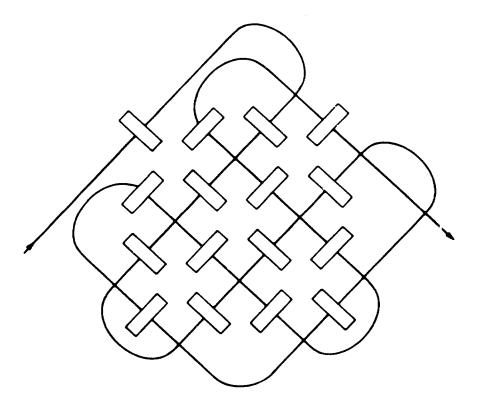

| 2.2.3      | Checkerboard Wiring Pattern              | 12   |

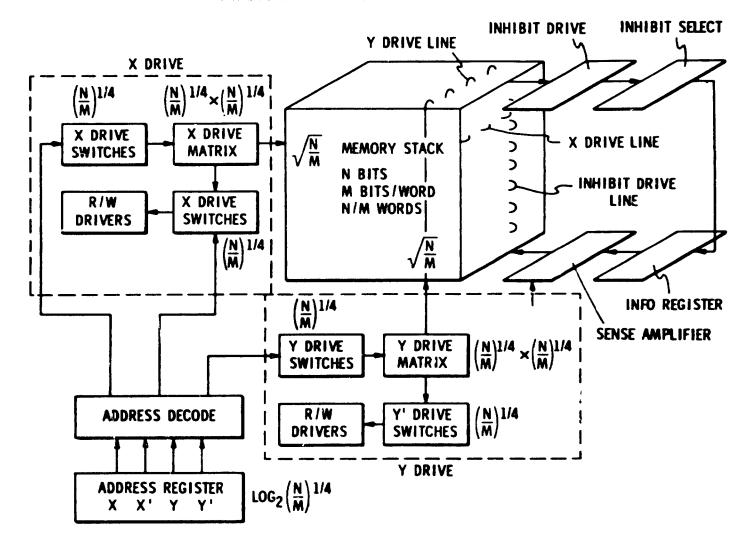

| 2.2.4      | 3-D Ferrite Core Memory Organization     | 14   |

| 2.2.5      | 2-D Ferrite Core Memory Organization     | 16   |

| 2.2.6      | Transition from 2-D to 2½-D Organization | 18   |

| 2.2.7      | 2½-D Ferrite Core Memory Organization    | 19   |

|            |                                          |      |

| 2.3.1      | Thin Film Hysteresis Loop                | 29   |

| 2.3.2      | Thin Film Switching Astroid              | 29   |

| 2.3.3      | Effect of Creep and Skew                 | 32   |

| 2.3.4      | Split Film Memory Element                | 37   |

| 2.3.5      | Mated Film Memory Element                | 38   |

| 2.3.6      | Coupled Film Memory Element              | 39   |

| 2.3.7      | Post and Film Technique                  | 41   |

|            |                                          |      |

| 2.4.1      |                                          | 45   |

| 2.4.2      | · -                                      | 47   |

| 2.4.3      |                                          | 51   |

| 2.4.4      | Plated Wire Tunnel Structure             | 54   |

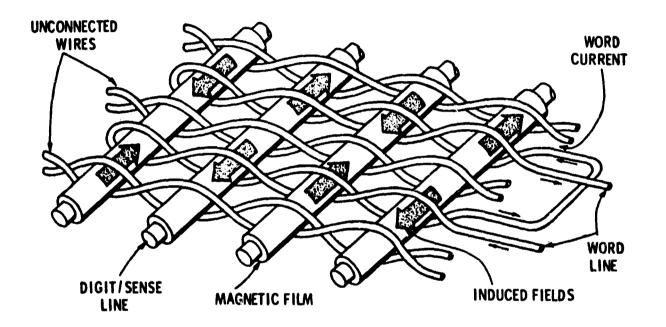

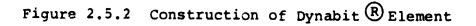

| 2.4.5      | Plated Wire Woven Array                  | 55   |

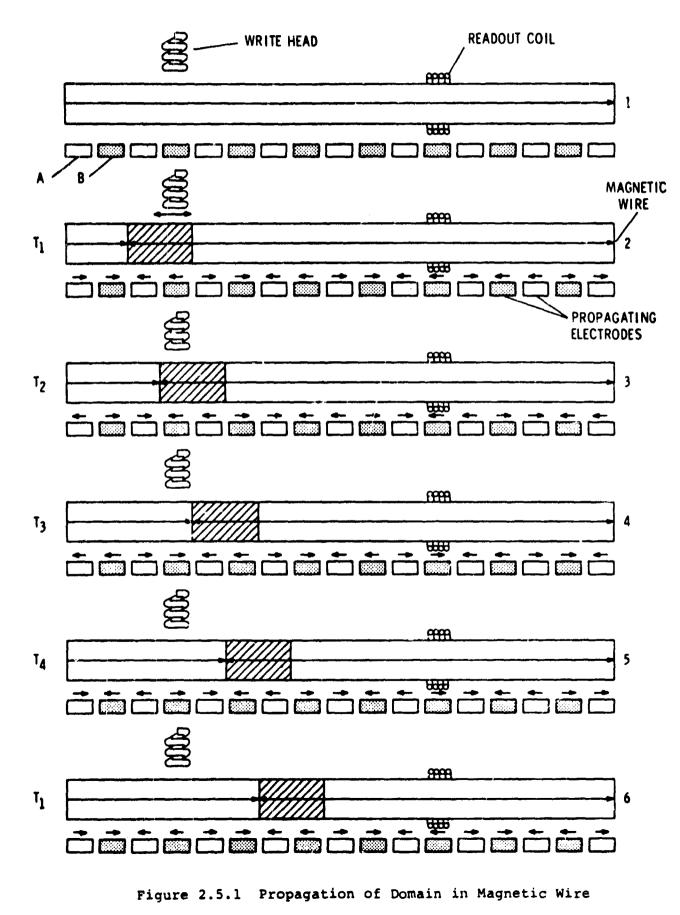

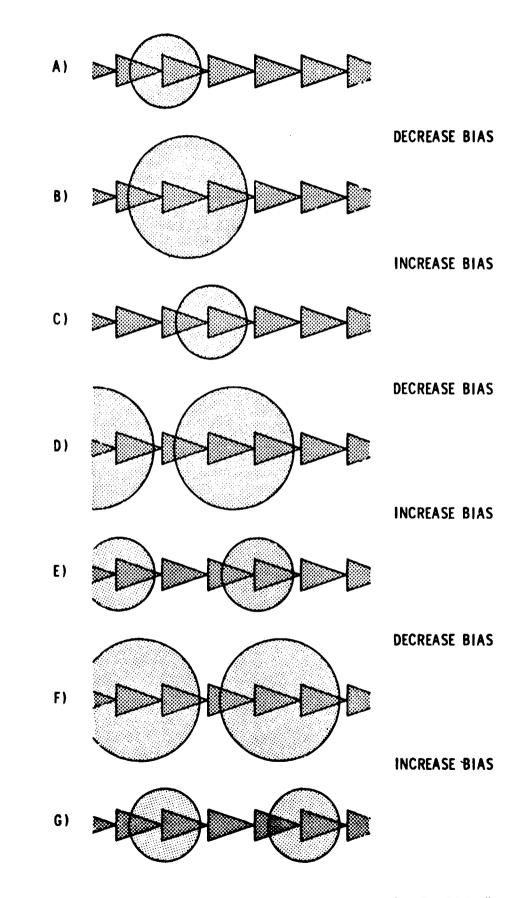

| 2.5.1      | Propagation of Domain in Magnetic Wire   | 63   |

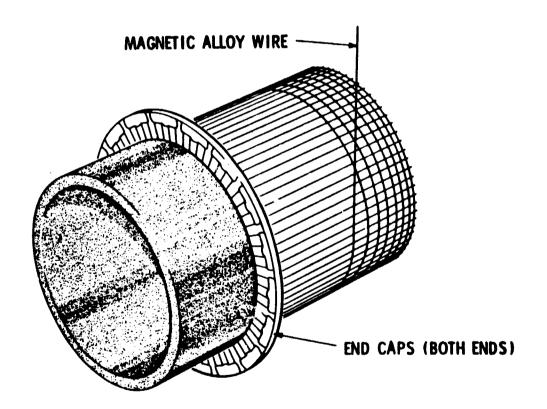

| 2.5.2      | Construction of Dynabit Element          | 64   |

| 2.5.3      | Propagation of Magnetic "Bubble" Domain  | 67   |

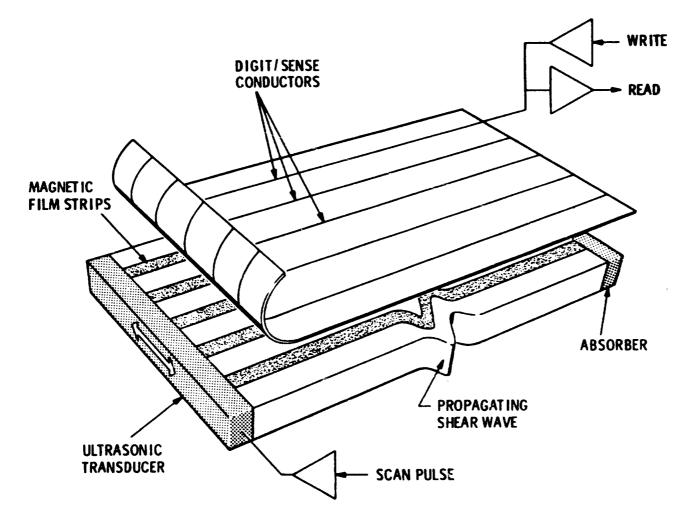

| 2.5.4      | Sonically Scanned Film Memory Schematic  | 71   |

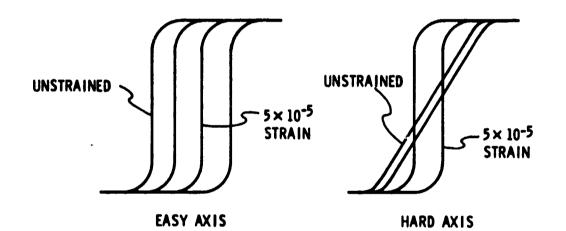

| 2.5.5      | Hysteresis Loop Behavior Under Strain    | 72   |

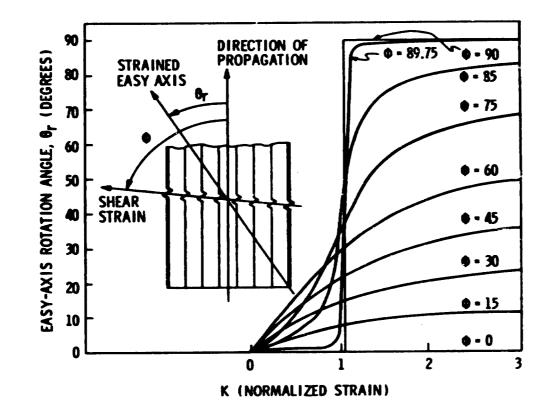

| 2.5.6      | Rotation of Easy Axis Under Strain       | 73   |

a the second day a straight way

Ĵ,

| Figure     |                                                                              | Page |

|------------|------------------------------------------------------------------------------|------|

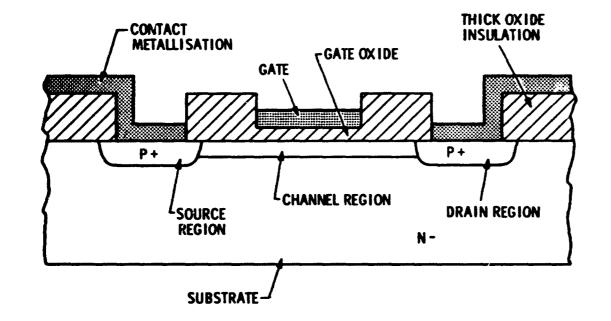

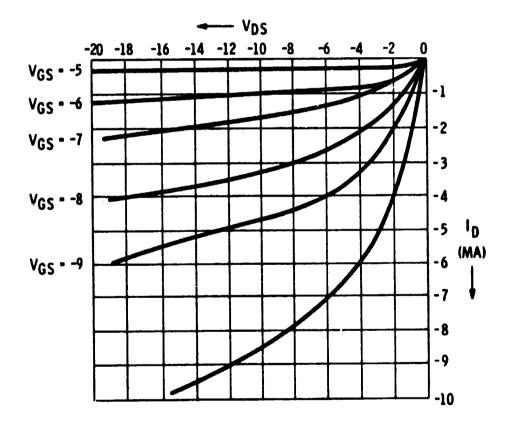

| 2.6.1      | Basic Construction of MOS Transistor                                         | 80   |

| 2.6.2      | Source-to-drain Conductance Characteristics<br>for P-Channel MOS Transistor  | 81   |

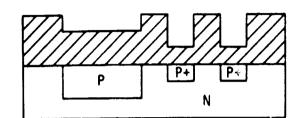

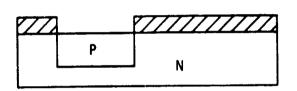

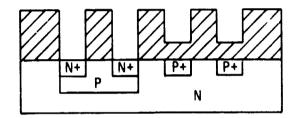

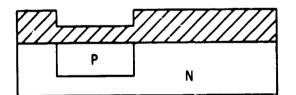

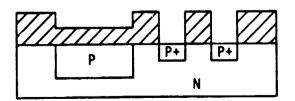

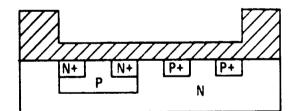

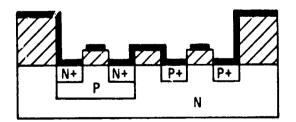

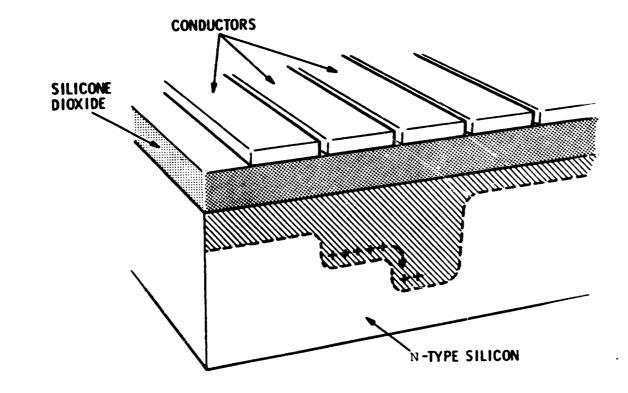

| 2.6.3      | Sequence of Processing Steps for CMOS<br>Integrated Circuit                  | 85   |

| 2.6.4      | Principle of Charge-Coupled Device                                           | 87   |

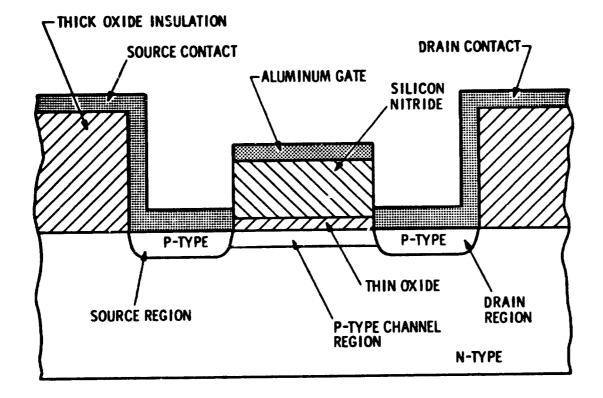

| 2.6.5      | Construction of P-Channel MNOS Transistor                                    | 89   |

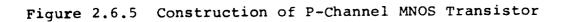

| 2.6.6      | Conductivity of Silicon Oxide and Nitride<br>as a Function of Electric Field | 91   |

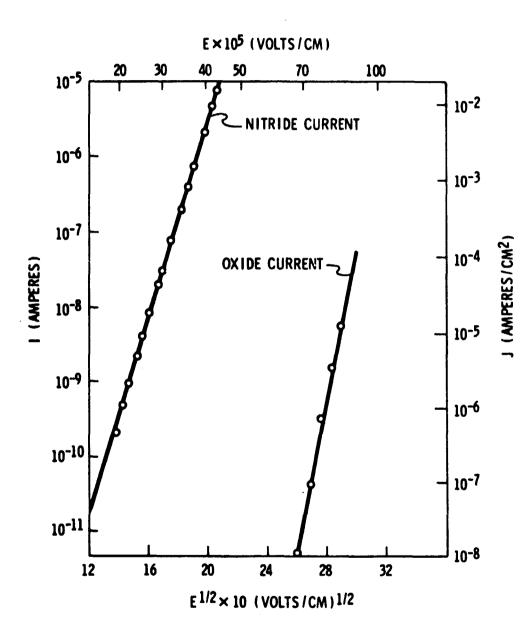

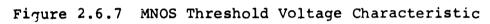

| 2.6.7      | MNOS Threshold Voltage Characteristic                                        | 95   |

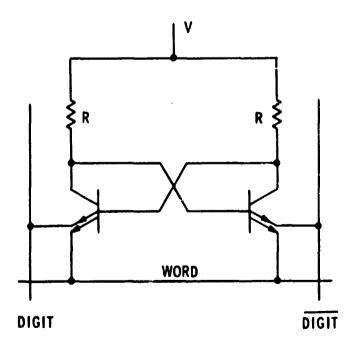

| 2.6.8      | Bipolar Memory Cell                                                          | 95   |

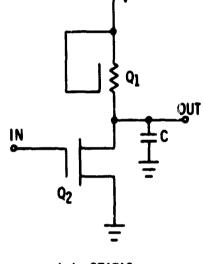

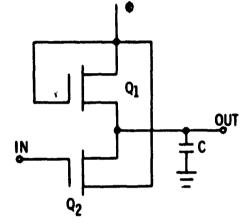

| 2.6.9      | MOS Inverter Circuit                                                         | 97   |

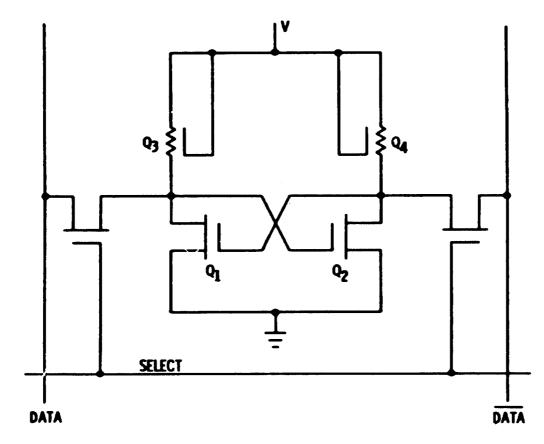

| 2.6.10     | Static MOS Memory Cell                                                       | 98   |

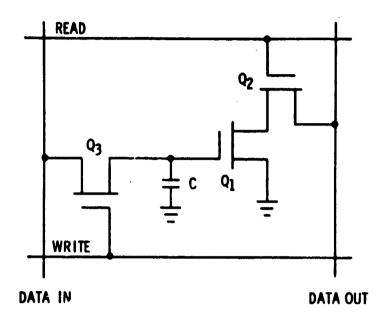

| 2.6.11     | Dynamic MOS Memory Cell                                                      | 100  |

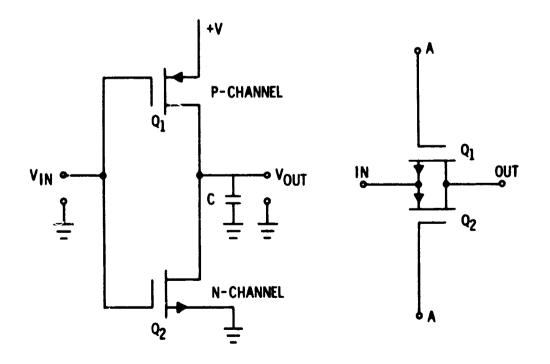

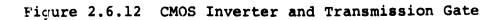

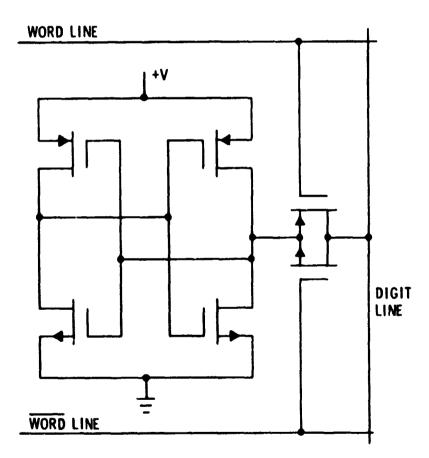

| 2.6.12     | CMOS Inverter and Transmission Gate                                          | 100  |

| 2.6.13     | CMOS Memory Cell                                                             | 101  |

| 2.6.14     | Connections to 1,024 Bit Array                                               | 104  |

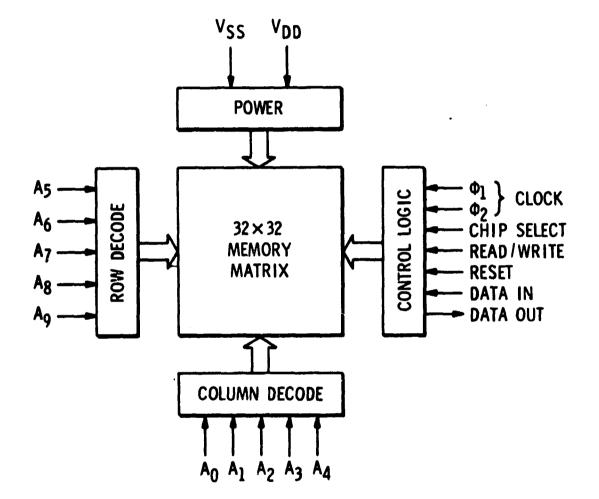

| 2.6.15     | Memory Cost Versus Chip Complexity                                           | 106  |

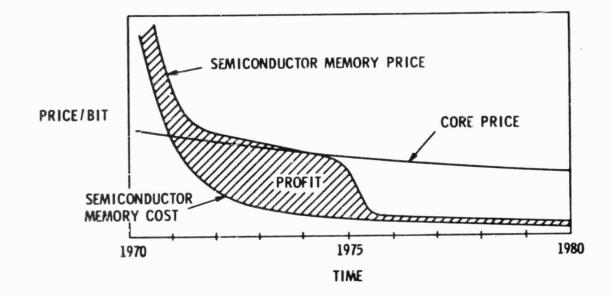

| 2.6.16     | Cost Prediction for Semiconductor Memories                                   | 112  |

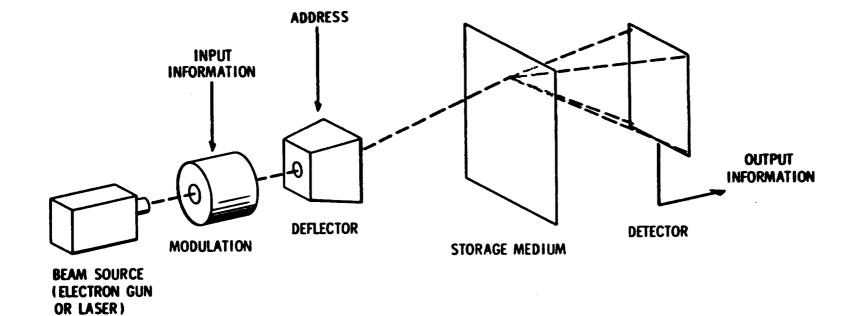

| 2.7.1      | Elements of an Optical Memory System                                         | 117  |

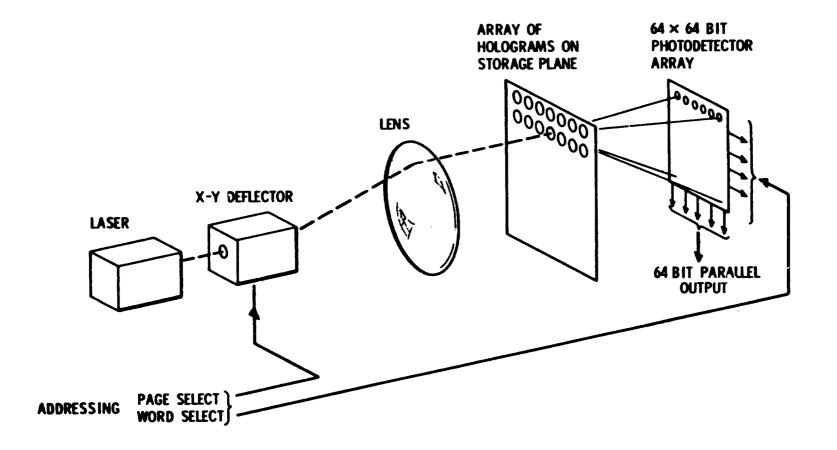

| 2.7.2      | Read-Only Holographic Memory System                                          | 118  |

| 2.7.3      | Mechanical Beam Deflection System                                            | 130  |

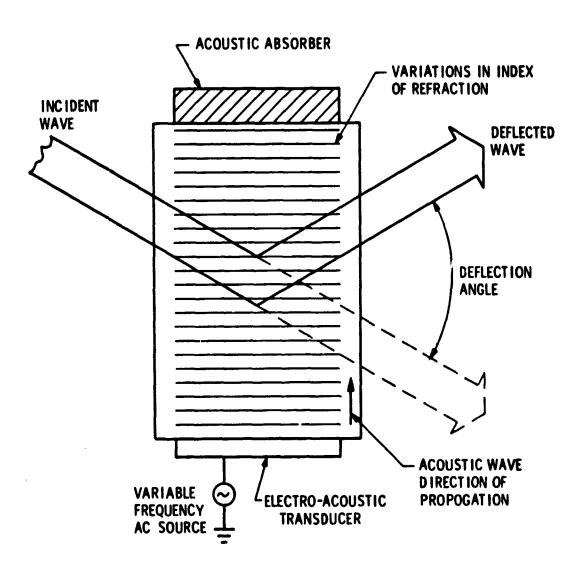

| 2.7.4      | Acoustooptic Deflection System                                               | 131  |

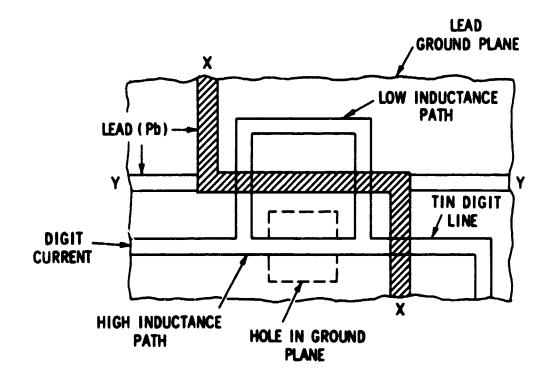

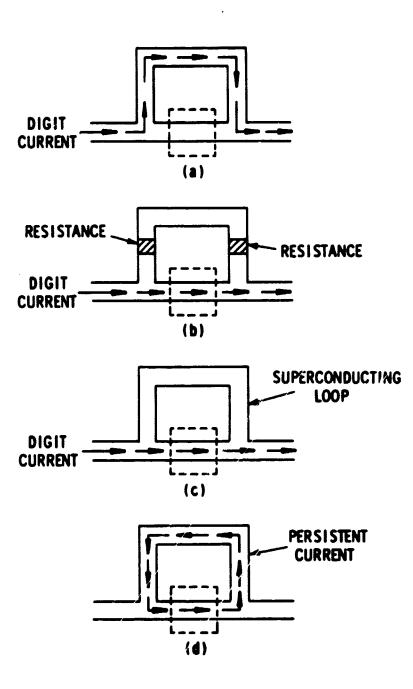

| 2.8.1      | Superconducting Memory Element                                               | 144  |

| 2.8.2      | Writing a 'l' into Superconducting Loop                                      | 145  |

| Chapter 3. |                                                                              |      |

| 2 1        | Intermetrics Multiprocessor Series                                           | 149  |

÷.

| 2.I | intermetiits Maitipiotessor Series                         | 117 |

|-----|------------------------------------------------------------|-----|

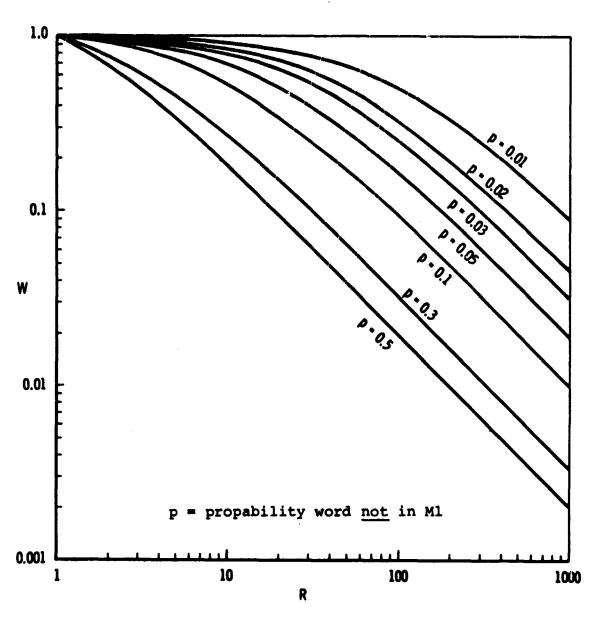

| 3.2 | Normalized Word Rate (W) vs M2/M1 Access<br>Time Ratio (R) | 155 |

iv

List of Tables

# Table

1

Page

计最优的计数

# Chapter 2.

| 2.2.1 | Core Memory Electronics                   | Requirements       | 20  |

|-------|-------------------------------------------|--------------------|-----|

| 2.3.1 | Characteristics of Some                   | Thin Film Memories | 42  |

| 2.4.1 | Characteristics of Some<br>Memory Systems | Plated Wire        | 59  |

| 2.6.1 | Current IC Performance C                  | Characteristics    | 102 |

| 2.7.1 | Characteristics of Recor                  | ding Media         | 127 |

# Chapter 3.

| 3.1 | M2 Access Time (t <sub>2</sub> ) as Function of<br>M1 Access Time (t <sub>1</sub> ) for 1 MIPS | 156 |

|-----|------------------------------------------------------------------------------------------------|-----|

| 3.2 | $t_2$ as a Function of $t_1$ for 10 MIPS                                                       | 159 |

| 3.3 | 1975 Memory Requirements                                                                       | 164 |

| 3.4 | 1980 Memory Requirements                                                                       | 165 |

| 3.5 | Inner Zone Charged Particle Distributions                                                      | 168 |

| 3.6 | Outer Zone Charged Particle Distributions                                                      | 169 |

| 3.7 | Effect of Shielding in Synchronous Orbit                                                       | 170 |

| 3.8 | Absorbed Radiation from Inner Zone Particles                                                   | 172 |

| 3.9 | Absorbed Radiation from Outer Zone Particles                                                   | 172 |

#### Chapter 1

#### Objective and Summary of Study

#### 1.1 Introduction

and a second constant to a solid face and the state of the state of the solid second second

ł.

STREET IS IN BUILDER

Designs for the next generation of manned space vehicles are currently being formulated. They involve advanced computer systems performing comprehensive tasks of guidance, control, navigation, monitoring, data reduction, and communication. The typical aerospace computer that was employed for each of these roles in the past was of modest performance capability and possessed a limited storage facility which was considered to be just sufficient for each function. However, it is expected that the new generation of on-board computing systems will demand the on-line availability of vastly increased storage resources. The chief characteristics of future space missions that will contribute to the need for massive on-board storage facilities are:

- a) The variety and complexity of the systems and the activities which the computing system is expected to service. Examples of these are vehicle control, life support, inventory management, scientific experiments, communications with the crew, with other spacecraft and the ground, etc.

- b) The vast amounts of data that are expected to be generated on-board must be reduced and stored. Estimates of the bulk of data generated by the systems aboard an orbiting space base have been as high as 10<sup>11</sup> bits per day [1].

- c) The long duration of the planned missions of the future will require the computing system to be capable of performing leading roles in a large variety of missions, and of providing support to numerous and varied programs of scientific exploration. These tasks will involve a vast amount of supporting software which must be available on-board.

These aspects have been discussed in the Final Report to the first part of this contract. A computer system was proposed to enable these tasks to be accomplished. A feature of the design was its ability to be gradually improved and enlarged in an orderly fashion to satisfy the increasing computational demands of a developing space program. The

design lefined the necessity for a hierarchy of memory systems to span the conflicting requirements of nanosecond access times and billion bit capacities; it did not seem very likely that these requirements could be met by one memory system based on a single technology, at least in the foreseeable future. It was the purpose of the study summarized by this report to:

- a) determine the characteristics required of each category of memory in the necessary hierarchy to enable it to be implemented by specific technologies;

- b) determine from a detailed search and review which of the existing, or proposed, memory technologies would be the most suitable for implementation of each category;

- c) perform these tasks in order to determine the feasibility of operational memory systems for advanced manned space vehicles for two distinct and separately considered time periods, namely 1975 and 1980.

*.*‡.

This report is presented basically in three parts:

- a) the review of memory technologies;

- b) the derivation of requirements for the various categories of memory;

- c) a comparison of technologies for each category, resulting in recommendations for 1975 and 1980.

Short summaries of the three sections are now given.

#### 1.2 Technology Review

Chapter 2 presents descriptions of a number of technologies that have been used to implement memory systems. The greatest depth of detail has been reserved for those that are considered to show the greatest promise for space vehicle applications, especially in terms of the hierarchical requirements detailed in Chapter 3. The technologies reviewed are summarized below.

- a) Ferrite Cores. This is the predominant technology today, accounting for over 95% of all computer memories.

Despite the existence of a large supporting industry, and continued improvements in density, speed and cost, ferrite cores may lose their dominant position to other techniques at least for space applications, because of basic speed, size and power limitations.

- b) Laminated Ferrites. A batch-oriented ferrite element with promising performance potential, but severe manu-

facturing difficulties.

Ť

- c) Planar Thin Films. A concept with a long history of attention because of its high speed and potential for batch fabrication. Production difficulties with variations on the theme intended to improve density, power and noise levels have discouraged widespread use, except in some military applications.

- d) Plated Wire. A more recently pursued variation of thin film technique, plated wire has been very actively developed by industry and government. Speed, low power and moderate density combined with automated production give this technique a strong potential.

- e) Serial Memories. A collection of thin film and magnetic domain techniques which aim at high densities, low power and low cost at the expense of a block oriented organization. Some show commercial promise on account of low cost, but only the "bubble" domain concept has real promise for future mass storage in space.

- f) Semiconductors. This large field is examined in some detail. Semiconductor integrated circuits will constitute a large proportion of any computing system, but only complementary MOS and the non-volatile variable-threshold MNOS are seen to have mass storage potential. Major problems are yield at the higher chip densities, and substrate interconnection techniques. A wide capacity, speed and power capability is covered by this field, and it is believed to become the major memory technology by the end of the decade.

- g) Beam Technologies. Beam accessing is being investigated for the very large capacity systems of over a billion bits. The principal features are low inertia, high resolution and a departure from the discretely fabricated and interconnected storage medium. There are severe problems in the areas of erasable storage, of deflection systems and in the generation, detection and conversion of optical information. Most designs are at the conceptual rather than implementational stage. They involve considerable overhead equipment such as lasers, optical path control, CRT devices, and therefore must demonstrate high storage densities (up to 10<sup>8</sup> bits/in<sup>2</sup>) to compensate for the otherwise inefficient use of space.

h) Cryogenic Memories. High storage densities and low noise levels are the incentive to superconducting memory cell investigation. Cumbersome overhead equipment and difficult environmental conditions have depressed interest in this field.

#### 1.3 Memory Requirements

From a consideration of performance specifications of 1 million instructions per second (MIPS) for 1975, and 10 MIPS for 1980, the following definitions for three categories of memory are presented in Chapter 3:

a) Ml. A high speed, random access, read and write, buffer memory, addressable to the level of one 30-40 bit word.

|             | 1975                        | 1980                     |

|-------------|-----------------------------|--------------------------|

| Capacity    | 10 <sup>5</sup> bits        | 10 <sup>6</sup> bits     |

| Access time | 100-200 ns                  | 40-60 ns                 |

| Data rate   | 5 xl0 <sup>8</sup> bits/sec | 10 <sup>9</sup> bits/sec |

| Volume      | 300 in <sup>3</sup>         |                          |

| Weight      | 15 pounds                   |                          |

| Power       | 15 wat                      | tts                      |

|             |                             |                          |

b) M2. A large capacity read and write memory, randomly addressable to a 250-400 bit block.

|             | 1975                        |                          |

|-------------|-----------------------------|--------------------------|

| Capacity    | 10 <sup>7</sup> bits        | 10 <sup>8</sup> bits     |

| Access time | 2-4 µs                      | 0.5-1.0 µs               |

| Data rate   | 5 x10 <sup>8</sup> bits/sec | 10 <sup>9</sup> bits/sec |

| Volume      | 1500                        | in <sup>3</sup>          |

| Weight      | 100 pounds                  | 100-200 pounds           |

| Power       | 85 wa                       | atts                     |

c)

M3. A very large capacity, block-oriented read and write memory, addressable to a  $10^4$  to  $10^5$  bit block.

|             | 1975                                      | 1980                     |

|-------------|-------------------------------------------|--------------------------|

| Capacity    | 10 <sup>9</sup> bits                      | 10 <sup>10</sup> bits    |

| Access time | 10-100 ms                                 | 10 ms                    |

| Data rate   | 10 <sup>5</sup> -10 <sup>6</sup> bits/sec | 10 <sup>7</sup> bits/sec |

| Block size  | 10 <sup>4</sup> bits                      | 10 <sup>5</sup> bits     |

| Volume      | 2-4 ft <sup>3</sup>                       |                          |

| Weight      | 200-400 pounds                            |                          |

| Power       | 200-400 watts                             |                          |

The physical and operational requirements imposed by the environment of a space application are also examined in this chapter.

#### 1.4 Recommendations

A category by category evaluation of the technologies reviewed in Chapter 2 is presented in Chapter 4, and recommendations for the two time periods are made. The results are summarized below.

| Category | Year | Technology                            |

|----------|------|---------------------------------------|

| Ml       | 1975 | Plated wire                           |

|          | 1980 | CMOS                                  |

| M2       | 1975 | Plated wire                           |

|          | 1980 | MNOS/CMOS                             |

| МЗ       | 1975 | l. Optical drum<br>2. "Bubble" domain |

|          | 1980 | Holographic                           |

#### 1.5 Final Word

The prediction of technological trends, for even a short journey into the future, must at times take on the aspect of guesswork. For the innocent inquirer there are false signposts along the route pointing in directions that eventually turn into blind alleys. Even researchers in the field have pursued a memory phenomenon for as long as fifteen years before finally concluding that it would, in fact, never yield its promised potential.

The disparity among the estimates for the success of a particular memory technique, even from persons actively engaged in its development, indicates the uncertainty in this game. For example, a number of workers in the plated wire field, when asked in 1968 for their forecasts for 1975, gave estimates for this technology ranging from a 3% to 60% share of the memory market [2].

In our recommendations we have attempted to avoid being misled by the well known tendency among technology forecasters to make their predictions for the near future too optimistic, and for the long term, too conservative.

# References for Chapter 1

a san indak a**ki kura**tang matakan kata san

- Progress Review, Space Station Program: Phase B Definition, Document PDS70-1212, North American Rockwell, February 19, 1970.

- Fedde, G.A. and Chong, C.F., "Plated Wire Memory Present and Future", IEEE Trans. Magnetics, MAG-4, No. 3, September 1969, pp. 313-318.

#### Chapter 2

#### Review of Memory Technologies

#### 2.1 Introduction

This chapter presents a detailed review of the major technologies that have, at one time or another, been investigated for their application to computer memories. No particular regard of the specific mass memory requirements that are presented in Chapter 3 is taken at this time, and no technology trade-offs with respect to these requirements are made until Chapter 4.

Space is devoted to material of a tutorial nature where this helps to promote an understanding of the technology. Several of the technologies are treated in considerable detail. This is sometimes due to their outstanding potential for mass memory implementation and sometimes, as in the case of planar thin film, because the principles and problems of the technology are shared by, and have relevance to, others.

The following technologies are described in this chapter:

Ferrite cores Laminated ferrites Planar thin films Plated wire Serial, block oriented techniques Semiconductors Beam accessed techniques Cryogenic techniques

This list covers all technologies that were considered to have application to the implementation of massive storage systems for space. The complete range of variations on each theme is not always covered, but sufficient indication of the overall potential of each technique is presented. Some technologies are known to have been omitted. Among these are the following:

a filiante su tare.

indens dy strende and a

a) Acoustic Delay Lines. Interest continues to be shown in quartz and glass delay lines as small memories for CRT displays and desk calculators, but the potential for massive storage is considered to be near zero.

- b) Ovonics. Some memory properties are claimed for the amorphous semiconductor, but the apparently very low densities achievable, the early stage of development, and the reluctant general acceptance of its claimed advantages rule it out of consideration. Ovonic devices appear to have great resistance to nuclear radiation, and this property is being studied under government sponsorship.

- c) Magnetic Drum and Disks. This is the traditional mass storage technology. It was felt that the principles, capabilities, and limitations of moving magnetic medium devices were too well known to deserve a detailed technical review in this section. Some reference to the possibilities of space-qualified drums and disks is made in the evaluation of technologies in Chapter 4.

#### 2.2 Ferrite Cores

## 2.2.1 Incroduction

The principle of coincident current selection of the stored magnetization of toroidal ferrites was first patented by MIT in 1956 [1]. Since then the ferrite core has been continuously developed as a storage medium for computers. Its attractive properties have led to its dominance over all other technologies, to the extent that "core" has almost become synonymous with mainframe "memory". Over 95% of all computer memories manufactured today employ ferrite cores, and the capabilities of this technology form the standard against which competing methods must be measured.

Among the reasons for this state of affairs are [2]:

- The ferrite core is an excellent storage device: it can be written into and read out of very rapidly, it is non-volatile and has a near-zero standby power requirement; it has become inexpensive to make with high degrees of reproducibility and uniformity.

- 2) Memory systems have been devised and turned into practical products with no drawn-out development stage.

- 3) Having been first on the scene, the ferrite core has had a comparatively long competition-free maturing phase.

The following sections give a brief description of the principles of operation. Also included is a review of the basic memory organizations that have been developed to address and sense the information from arrays of ferrite cores. These organizations have relevance for all memory techniques that rely on a matrix approach to gain access to desired information.

#### 2.2.2 Principle of Operation

A Margade (and to a

Some ferrites have a magnetization (M v. H) characteristic that is almost "square". This property can provide both memory and logic function. In the absence of a driving current (or field H) two remanent magnetizations of opposite sign  $M_a$ ,  $M_b$  are possible, as in Figure 2.2.1. It is necessary to exceed a critical, or switch current  $I_f$  to cause the magnetization to change sign, say from  $M_a$  to  $M_b$ . A current  $I_p$  is insufficient to switch the magnetization; its only effect is to leave a slightly diminished remanent flux,  $M_a'$ , due to the

Figure 2.2.1 Ferrite Hysteresis Loop

UNITED STORY, NEW CONSTRUCTION

10.00

Figure 2.2.2 Ferrite Core Array

"non-squareness" of the hysteris loop. The material can therefore distinguish between "full" and "partial" select currents.

The ferrite core is normally an annulus, which provides a stored, closed, circumferential flux path. Early cores were over 100 mil O.D. (1 mil = .001 inch), but over the years reductions in size have occurred (to reduce the energy of magnetization) until today memories have been constructed of 12/7 mil (O.D./I.D.) cores [3]. Curiously, each new "standard" size that has been established can almost pass through the hole in its predecessor.

Switching speed is proportional to drive current, if the current is well above the threshold value. It is a complex function of drive current duration, because short pulses involve different magnetic mechanisms in the material than continuous currents. A 20 mil core switches its state in approximately 100 ns when excited by the field from a wire carrying about 1 amp.

Cores are arranged in rectangular arrays, with at least two wires threading each at right angles, as in Figure 2.2.2. The core's property of not switching in response to partial currents is the basis for selective access. The desired core location must be at the intersection of partially driven X and Y lines, a unique location where the fields associated with the currents combine to exceed the switching field. A third wire can be used, threading all cores in an array, to detect the large change in flux through a core as it switches in response to the "coincident" partial select currents. As mentioned before, a consequence of imperfect "squareness" in the B-H characteristic causes each partially selected core to contribute a small flux change, which is detected by the sense wire as noise. To prevent individual cores from additively contributing noise, the cores and sense wire are often arranged in a cancelling "checkerboard" pattern (Figure 2.2.3).

To detect a 'l' a core must be switched from its 'l' state to the '0' state. Information is therefore destroyed on read, and must be restored with an immediate write. To write a 'l' it is necessary to switch the core from its '0' state, with currents of opposite polarity to those required to read a 'l'. Bipolar drive circuits are obviously necessary. To write a '0' the core must be inhibited from changing its '0' state; this can be accomplished by opposing the full write select current with a partial inhibit current. Sometimes this is done with a fourth, inhibit line, and sometimes the sense line is used with additional external logic.

a ......

and the second second

a et a

÷

. . -

Figure 2.2.3 Checkerboard Wiring Pattern

Ì

t i Marcine i S

#### 2.2.3 Memory Organizations

A basic problem is how to get to the desired core locations to read or write information. Three different approaches to addressing core arrays have been devised to serve the conflicting requirements of speed, drive circuit complexity and power.

## 2.2.3.1 3-D Organization

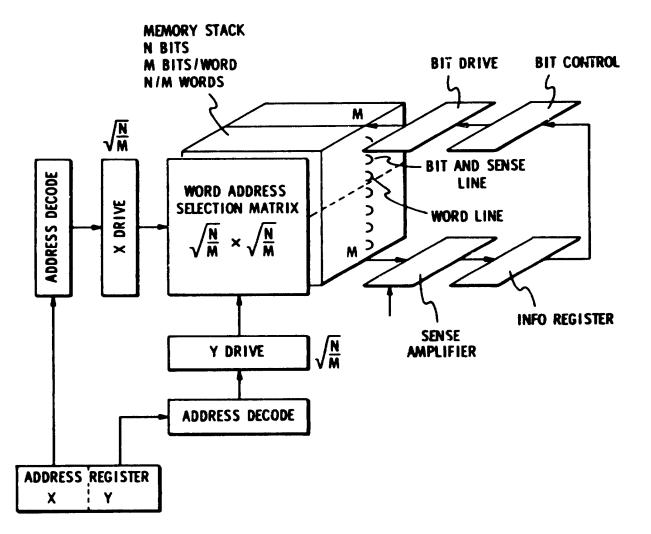

This requires the least amount of address and drive circuitry and for medium performance memories is the most commonly used. The memory is organized into M square planes (where M = bits/word). Plane  $M_1$ , for example, contains bit 1 of all words in the memory (total number of words = N/M, where N = total capacity in bits). Each plane therefore contains N/M cores, and is addressed by X and Y word drive lines, where XY = N/M. Bit 1 of a particular word could be read by selecting the X and Y drive lines of array  $M_1$ that intersect at the location corresponding to the address of the word. Connecting corresponding X and Y lines of each of the M memory planes together allows one X,Y selection to read in parallel all M bits in a particular word. Because it is possible to access an individual bit in one plane, the 3-D approach is sometimes called a bit-organized memory. Other configurations deliver more than one bit at a time from each array. Figure 2.2.4 illustrates a 3-D memory. A selection matrix is shown driving the  $\sqrt{N/M}$  X- and  $\sqrt{N/M}$  Y- lines of the memory. Such an added level of address selection is often used in large memories to reduce the amount of drive circuitry, although each level contributes a delay which slows down overall response. In addition to the X-wire and the Ywire, a sense wire to detect the switching of the selected core during a read operation must be provided. The sense wire can double as the inhibit line during a write cycle, but a fourth wire is sometimes added. Since this wire threads all cores, it is long and resistive. It dissipates heat during the inhibit cycle, when it must carry a half select current, and it is the major cause of delays in the 3-D memory because transients take longer to decay in the inhibitsense line than any other.

The chief properties of the 3-D organization are:

a) Coincident current selection is performed for both read and write: coincidence of current on two wires is required for a read, and on three wires for a write.

Figure 2.2.4 3-D Ferrite Core Memory Organization

- N

14

nemmennen sonstation och

- b) The X,Y drive lines are used only for addressing, and the M (or Z) lines are used only for sensing and/or inhibiting.

- c) Maximum use of the inherent decoding property of partially addressed cores is made to reduce circuit complexity, e.g., total number of XY drive circuits is  $4(N/M)^{\frac{4}{3}}$ , which becomes a really significant factor with large capacity memories (see Figure 2.2.4).

Its drawbacks are:

THE MAN

- a) Relatively tight drive current tolerances are necessary to provide satisfactory core selection throughout the memory by the coincidence principle.

- b) The limit on the switching current imposed by the maximum partial select current does not allow the full speed of the core to be utilized.

- c) The lengthy sense/inhibit line contributes a major portion of the total system delay.

## 2.2.3.2 2-D Organization

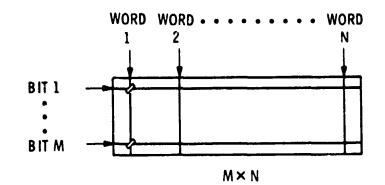

This configuration is dedicated to speed. Cores are arranged in a rectangular plane; one side is length M, the number of bits in a word, and the other is N/M, the number of words. Access to the contents of a word is gained by pulsing one of the N/M word lines with a full select current. All cores on that line that were 'l' switch to '0', inducing corresponding voltages in the bit/sense lines, and all that were '0' stay '0'. As mentioned before, switching speed is proportional tc drive current. In the 2-D (or linear select) memory coincidence is not a requirement on read, and therefore the full potential of the core can be exploited by overdriving the word current. For writing, the word line drive is reversed in polarity, and all uninhibited cores are switched back to 'l'. Those required to stay '0' are inhibited by an opposing coincident current on the appropriate bit/sense line. The chief characteristics of this organization are:

- a) Coincident currents on two wires are required only for writing; for reading, cores are treated purely as storage elements and have no selection function.

- b) Only two wires per core are needed. This allows smaller cores to be used, with further advantages in speed.

-

Figure 2.2.5 2-D Ferrite Core Memory Organization

.

1

ł

and the second second second

and the second loss of the second s

- c) The word lines are used only for addressing and the bit lines are used only for sensing and inhibiting.

- d) The sense wires in a 2-D array thread only one excited core: this means the signal-to-noise ratio in a 2-D memory is inherently better.

The very oblong symmetry of the 2-D organization is disguised by folding the long word side into a rectangular matrix with equal rows and columns of  $(N/M)^{\frac{1}{2}}$  elements, as illustrated in Figure 2.2.5. Address decoding then necessitates only  $2(N/M)^{\frac{1}{2}}$ drive circuits, which is, however, for large m mories, a considerably greater complexity than for the 3-D configuration.

#### 2.2.3.3 2½-D Organization

en die ander die steht die anderse kerken gebeuren die die sone die die steht die stehten die stehten die steht

This organization attempts to combine the better points of both the 3-D and 2-D approaches (hence the name), without incurring any faults of its own. The technique dates from 1954 but was not used as a solution to the performance/complexity problem until IBM revived it for their Large Core Storage.

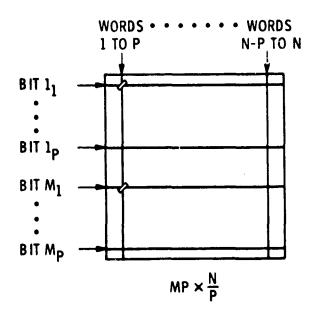

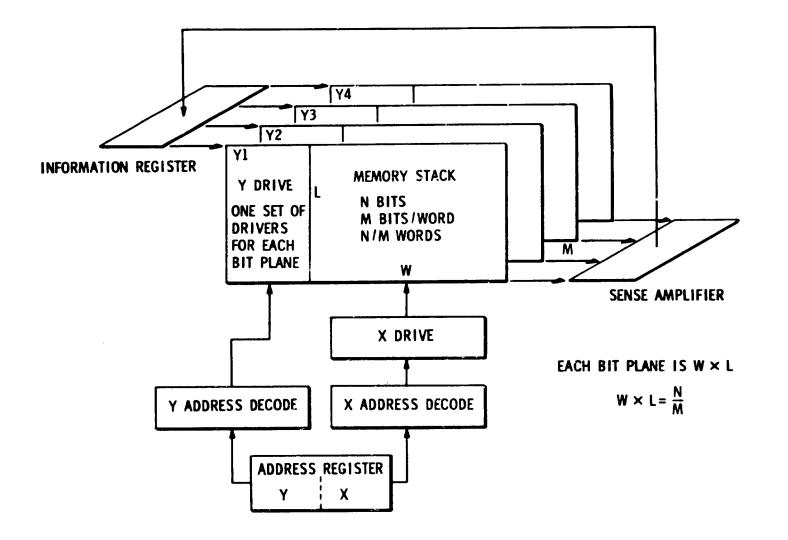

It is essentially a two-dimensional approach, but relieves the drive circuit complexity by "squaring up" the geometry of the pure 2-D. Figure 2.2.6 illustrates the transition. The significant characteristic of the resulting array is that the Y or bit dimension handles both address and data information, unlike the pure 3-D or 2-D. The planar representation of Figure 2.2.6 is "up-ended" for practical reasons, to give the organization of Figure 2.2.7. The memory is organized into M bit planes, each array having an aspect ratio W/L, where WL = N/M.

Reading is accomplished by coincident currents of  $-I_p$  on the appropriate W line and on each of M appropriate L lines. Cores at the M intersection, are set to the '0' state. Effects of flux changes are read out by a sense wire common to all cores on a bit plane; or by the same L line by separating out sensed signals from drive noise. The latter is a slower technique, but allows  $?\frac{1}{2}$ -D, 2-wire construction with its consequent higher packing density, and is the method favored for mass stores where speed is of less essence. The real advantage of the  $2\frac{1}{2}$ -D approach lies in its fast write. There is sufficient circuit redundancy in the y-direction to provide both address selection and data insertion. A word line is pulsed with current  $+I_p$ . The y-address and bit information are logically combined and sent to the y-drivers. To cause a '1' to be stored a  $+I_p$  current is added to the full word

Ĭ.

i distributi Tana ana

a) 2-D schematic

b) 2½-D schematic

Figure 2.2.6 Transition From 2-D to 2½-D Organization

-----

Figure 2.2.7 23-D Ferrite Core Memory Organization

61

#

~

current in the appropriate L line in each bit plane. Intended zeros are left unselected. This provides for faster switching than for the additive half-select currents of the 3-D configuration, because the latter requires built-in delays t ensure "bracketing" of the X and Y pulses by the inhibit pulse.

The 3-D inhibit line recovery problem is eliminated since there is no inhibit line. Of the four states possible by combining X and Y  $\pm I_p$  drives, only two are used: read and write. Practical memories use the other two to effect a x2 word address circuit economy, by a physical rearrangement of the bit planes [5]. Shorter drive and sense lines than for the equivalent 3-D or 2-D memory can be employed.

#### 2.2.3.4 Summary of Drive Electronics

The quantity of drive electronics, for each of the above configurations is summarized in Table 2.2.1. The switch generates the bipolar drive current, and the driver routes the current to the appropriate wire in the memory.

|               | Word                   |           | B:                  | it     |

|---------------|------------------------|-----------|---------------------|--------|

| Configuration | Switch                 | Driver    | Switch              | Driver |

| 2-D           | 2 (N/M) <sup>1</sup> 2 | 2N/M      | м                   | -      |

| 2⅓-D (1)      | $2 W^{\frac{1}{2}}$    | W         | 2M L <sup>*</sup> 2 | ML     |

| 3 <b>-</b> D  | 4 (N/M) 🏅              | 2 (N/M) 🛓 | M(2)                | -      |

Notes: (1) For  $2\frac{1}{2}$ -D: W x L =  $\frac{N}{M}$ N = bits total M = bits/words (2) For 3-D this is an inhibit switch

Table 2.2.1 Core Memory Electronics Requirements

#### 2.2.3.5 Configuration Capabilities

The 3-D organization of ferrite cores is used where performance and/or capacity is not critical, but the cost

associated with electronics is of prime importance. For very high speeds and/or large capacities, high drive currents, small cores and high densities are required, necessitating consideration of the 2-D and 2½-D approaches. 2-D is employed where high speed is paramount and/or where moderate capacity does not pose an impossible penalty in addressing, drive, and sense electronics costs. 2-D memories have most frequently been used as high-speed scratch pad storage of less than a few thousand words. However, an experimental ferrite core memory of 5.9 x 10 bits built to explore the feasibility of very high speeds achieved a 110 ns cycle time using a 2-D, 2 wires per core, 2 cores per bit configuration[3].

The  $2\frac{1}{2}$ -D does not incur the drive electronic expense of the 2-D, nor does it require the careful tolerancing and compensation of drive currents necessary with the 3-D approach. It is therefore popular in the larger system, especially since it allows the use of 2-wire arrays. Some sacrifice in cycle time is inevitable when the third, sense wire is omitted, since delays must be allowed for transients to decay; but for large core storage this is not of prime importance. An example of  $2\frac{1}{2}$ -D core memory organization is the IBM 2361 Large Core Storage which contains 16.8 x 10 bits and operates with cycle times of 8 µs.

#### 2.2.4 Ferrite Core Status and Trend

## 2.2.4.1 Current Status

Cores have steadily decreased in size since their inception. Today's standard sizes as used in commercially available arrays are 22, 20, 18 and 16 mil outside diameter; cores down to 12 mil O.D. and 7.5 mil I.D. have been quantity produced and incorporated in operational memory systems [3].

The trend towards smaller cores is due to the following interrelated reasons:

- Smaller cores can be made to switch faster, without increasing the drive current, because the shorter magnetization path length results in a higher switching field.

- 2) The smaller cross sectional area reduces the inductance of the drive line, because the contributions from individual cores form the major portion of the total inductive load. The result is lower transmission delay, back voltage, and power dissipation.

- 3) The smaller dimensions, coupled with 2) above, enable denser arrays to be constructed. The reduced drive line dimensions compensate in part for the increased resistivity of the smaller diameter lines.

- The increased surface-to-volume ratio of the smaller core improves its ability to dissipate the heat generated during switching.

The overall memory speed is strongly influenced by an improvement in core response, because the core switching time is a large fraction, up to 50% to 75%, of the basic memory cycle. Since core switching is destructive, a full memory read cycle must include a restoration of the destroyed information. The resulting full read cycle is therefore three to four times longer than the core switching time. Small cores present manufacturing problems. The ferrite core owes its popularity to massive automation of the processes of manufacture, testing, and assembly. For smaller cores to become standard practice, this machinery needs to be developed to a higher degree of performance.

The magnesium-manganese ferrite core is fairly temperature sensitive and requires compensation of drive currents for even narrow temperature ranges (25°C - 50°C). Lithium ferrite is now being used, especially in military systems [7]. In this material monovalent lithium displaces the usual trivalent manganese in the complex ferrite molecular system. It has a higher Curie temperature: 400°C versus 150°C to 200°C, and consequently a lower temperature coefficient: -0.16% per °C against -0.36%. In this respect nickeliron memories have an advantage over ferrite core, since permalloy is even less temperature sensitive: about -0.07% per °C.

Drive currents are typically 400 ma to 600 ma, half select. Drive line impedances are about 120 ohms, which means 50-70 volts must be switched. This is outside the scope of integrated circuitry at the present time. Work is being directed at lower switching levels and wider temperature capability, but the penalty is switching time: 4usecs appears to be the limiting speed.

The core/wire assemblies must be supported so as to be capable of:

Surviving the mechanical environmental factors of shock, vibration and acceleration. This requirement is obviously more serious in military and aerospace memories, and has contributed to a reluctance to employ advanced core techniques in these applications.

- 2) Conducting away the heat generated in switching cores and current carrying conductors, and providing a uniform temperature distribution throughout the stack (local hot spots defeat the temperature compensation of drive currents). Some high performance stacks employ a cooling liquid circulating in a hollow frame [3], but conduction and air cooling are the usual mechanisms.

- 3) Allowing the stacking of arrays into a module. Currently planes can be stacked at about 12 to the inch.

#### 2.2.4.2 Ferrite Core Trends

Most of the trends have been indicated already:

- 1) Smaller cores for higher speeds and densities.

- Lower drive currents for IC compatibility and reduced power consumption.

- 3) New materials to achieve higher switching speeds, wider temperature tolerance and easier manufacture [8].

Today's core memory has a barrier at about 500 ns cycle time. Of this 100-200 ns is absorbed by the ferrite core itself, and the remainder is contributed by geometry and circuitry. Exotic techniques, i.e., partial switching of the magnetization by very short, hard pulses, and two cores per bit to improve the signal to noise ratio in a fast, noisy system have been employed to achieve a 110 nanosecond cycle time [3]. But these are expensive devices, which together with the necessary, but electronics-consuming, 2D-2W organization, and cooling problems, are the penalties of higher speeds.

Packing densities in core arrays available today are in the range 1000-3000 bits/sq.in., depending on core size and array organization. Experimental arrays have been built from 12 mil cores spaced at 7.5 mil in the bit direction, and 15 mil in the word direction [3], with a resulting density of 8,500 cores/sq.in. Even though the volumetric efficiency reported in reference [3] deteriorated to 3,900 bits/cu.in. when the plane arrays were assembled, densities in excess of 50,000 bits/cu.in should be realizable if the requirement for very high speed were to be relaxed.

Sec.

The one unavoidable drawback of the simple toroidal core is the destructive nature of the information readout. Significant future developments to obviate this are very unlikely,

because the necessary complex flux linkage must be provided by a multiapertured geometry, exemplified by the Raytheon BIAX, which is difficult to manufacture in a miniaturized form.

#### 2.2.5 Planar Ferrite Technology

#### 2.2.5.1 Introduction

Because of the overwhelming success of the toroidal ferrite core as a memory element, attempts have been made to develop a batch fabrication technique for this technology. The incentive to batch fabrication is common to other technologies, i.e., lowered costs due to a non-discrete manufacturing process, and a higher reliability promised by fewer processing steps and reduced parts counts. However, only one or two attempts have been made to develop a planar ferrite technique to the point where an experimental memory system could be built [9]. Efforts have been directed in two directions, which differ according to the manner in which the word and digit conductors are arranged. The earlier technique provided apertures in the ferrite sheet through which plated wiring could be lead [10], but was not pursued. The other technique is to sandwich orthogonal word and digit lines between laminates of ferrite; this has received considerable attention from at least two manufacturers, and will be described in some detail.

## 2.2.5.2 Laminated Ferrite Technique

Reference [11] describes how a ferrite laminate is The structure consists of two orthogonal sheets of formed. ferrite, each with a pattern of parallel, noble-metal (platinum, palladium, gold) conductors on it, separated by an insulating sheet 0.5 to 1.0 mil thick. The overall thickness of the finished laminate is typically 6-8 mils. Conductor dimensions vary with manufacturing method from 2.4 to 6 mil in width, 0.5 to 1.5 mil in thickness, and are spaced from 10 to 20 mils apart. The conductors are formed in the ferrite either by rolling a ferrite slurry over a conductive paste pattern on a glass substrate and allowing it to dry, or by filling the grooves formed in a ferrite sheet by phonograph record techniques or by embossing, with conductive paste. The laminate is formed by subjecting the ferrite sandwich to a pressure of 2000 p.s.1. at 90°C, after which it is fired for 10 hours at 1260°C. The ferrite system reported in reference [1] was 0.38 MgO-0.19MnO-0.05ZnO-0.38Fe<sub>2</sub>O<sub>3</sub>. This composition was found to possess the best compromise of the several characteristics cited as desirable for low power, high density ferrite memories:

| 1) | Squareness of the hysteresis loop (Br/Bm) | <u>≥</u> 0.9            |

|----|-------------------------------------------|-------------------------|

| 2) | Remanent flux density (magnetization)     | <u>&gt;</u> 1000 gauss  |

| 3) | Coercive force                            | <1.5 oersted            |

| 4) | Curie temperature                         | <u>&gt;</u> 300°C       |

| 5) | Resistivity                               | ≥10 <sup>6</sup> ohm-cm |

| 6) | Grain size                                | <u>&lt;</u> 10 µ        |

Low grain size and high resistivity are desirable in order to achieve minimal conductor widths and spacings, without incurring excessive current leakage between adjacent conductors or unwanted cross-couplings. Unfortunately, grain size and coercivity are related inversely, so that great care must be taken to fire the laminate at the optimum temperature, of which the grain size is a function.

Ferrite sheets formed from a wet slurry shrink in thickness by a factor of about 6 upon drying, and shrink in linear dimensions by a further 20% on firing at high temperature. Neither of these changes can be exactly predicted or controlled, and the latter shrinkage is a limiting factor in the production of laminates. There is a tendency for the conductors to fracture under the action of the differential changes in geometry during firing; the resulting conductor spacings, being variable and non-predictable, make batch-oriented connection techniques for laminated ferrite planes very difficult to implement.

Ferrite sheets cannot be made greater than about one square inch in area, which limits arrays to about 64x64 intersections for a 15 mil conductor spacing. To establish connections the conductors must be bared by air-abrading away the surrounding ferrite at the edges of each sheet, a process which is liable to result in damage and does not lend itself readily to automation.

Formation of ferrite sheets by pressure sintering could minimize the geometry change during firing; this process would also allow the use of solid, prefabricated conductors which could project beyond the edge and would therefore eliminate the airbrasion step of manufacture.

#### 2.2.5.3 Laminated Ferrite Array Performance

The conductors of the laminated ferrite array are about 1 inch in length and have a resistance of about 2.5 ohms. But the heavy inductive and capacitative loading imposed by the onestation of the state of the statement of the

surrounding ferrite causes the line to exhibit a characteristic impedance of about 200 ohms at 10 MHz. The output voltage is of the order of 1-2 millivolts, but the unusually high self inductance and capacitance cause back voltages of up to 20 millivolts per intersection, which poses a problem to the read electronics. However, it is possible to achieve adequate operation with word write/read currents of only 60/100 ma, making operation with MOS I.C.'s feasible. Access times are determined by digit/sense line decay times, which in turn are influenced by data patterns and termination impedances: values between 100 ns and 250 ns have been measured.

Laminated ferrite arrays suffer from a number of performance disadvantages:

- For reliable operation and good signal to noise ratios, two conductor intersections/bit must be used, which diminishes the possible packing density.

- 2) The read out is, like the Coroidal ferrite core, destructive.

- 3) Being basically a 2-wire system, only 2-D operation is possible with a consequent heavy demand (in high capacity systems) for driving and sensing electronics.

- 4) Continuous high speed operation of the same cross-over point causes localized heating and local changes in electrical and magnetic characteristics.

The output signal amplitude and the switching speed can be improved by NRZ digiting (in which only state changes produce current switching), and by partial switching of the ferrite, but both techniques add to the electronic complexity.

# 2.2.5.4 Summary

Laminated ferrite techniques have achieved arrays which exhibit high speed (100-200 ns cycle time), low power (30/100 ma digit/word drive current), and densities between 2000 and 4000 bits/sq. in. The arrays cannot, however, exceed about 4000 bits in capacity because materials difficulties limit the size of ferrite sheets to about a square inch. The feasibility of constructing systems of 10<sup>7</sup> to 10<sup>8</sup> bits, with speeds of 2  $\mu$ s, dissipations of 100 watts, and a volume of 300 cu. in. has been suggested [9], but as yet no system of this size has been implemented.

This technique has one or two significant problems. First, there are severe manufacturing difficulties; there is a strong dependence of the performance characteristics on the control of a large number of processing variables, from preparation of the ferrite compound through to the finished laminated array. Some of the processing steps are tricky, e.g., exposure of electrical connections by airbrasion. Secondly, the poor control that can be exercised over physical dimensions such as conductor spacing, conductor separation at cross-overs, etc., makes mass assembly techniques nearly impossible, reduces yield and maintains a high level of cost. New techniques, such as pressure sintering, have been suggested to alleviate some of these problems, but as yet have not been proved.

# References for Section 2.2

alahiman mentikan gebera meningkan seri

staline en Hallahos egistellerede

- 1. Forrester, J.W., U.S. Patent No. 2,736,880, February, 1956.

- Russel, L.A., et al, "Ferrite Memory Systems", IEEE Trans. Magnetics, MAG-4, June 1968, pp. 134-145.

- 3. Werner, G.E., and Whalen, R.M., et al, "A 110-Nanosecond Ferrite Core Memory", IBM Journal, March 1967, pp. 153-161.

- 4. Brown, J.R., "First-and Second-Order Ferrite Memory Core Characteristics and Their Relationship to System Performance", IEEE Trans. on Electronic Computers EC-15, No. 4, August 1966.

- 5. Gilligan, T.J. and Persons, P.B., "High Speed Ferrite 23-D Memory", Proc. FJCC, Vol. 27, 1965, pp. 1011-1021.

- 6. Brown, J.L., et al, "IBM System/360 Engineering", Proc. FJCC, Vol. 26, 1964, pp. 205-231.

- 7. Rickard, B.W., "Military Masses Its Cores for Battlefield Conditions", Electronics, June 9, 1969, pp. 122-124.

- 8. Agajanian, A.H., "Li-Mn Ferrites for High-Speed Computer Memory Applications", IEEE Trans. Magnetics MAG-6, March 1970, pp. 90-95.

- 9. Shahbender, R., "Laminated Ferrite Memories Review and Evaluation", RCA Review, June 1968, pp. 180-198.

- 10. Rajchman, J.A., "Ferrite Apertured Plate for Random Access Memory", Proc. IRE., Vol. 45, No. 3, 1957, pp. 325-334.

- 11. Gordon, I., et al, "An MOS-Transistor-Driven Laminated Ferrite Memory", RCA Review, June 1968, pp. 199-229.

27

# 2.3 Planar Films

## 2.3.1 Introduction

an (2001) - The Constant of the owner own

The rotational switching of the remanent magnetization of thin anisotropic magnetic films has been investigated since 1955; the main incentive to their development was the achievement of a batch fabrication process that could rival the ferrite core memory in cost. Early core memories were difficult to produce: ferrite toroids were tricky to fabricate and test in large numbers, and wire stringing was not automated to the extent it later became. This motivation changed, because core technology developed to become an industry within the computer industry, and has always maintained a price-performance superiority over all other techniques. Work on films has continued, however, spurred by the promise of a superior performance and the hope of eventual commercial viability.

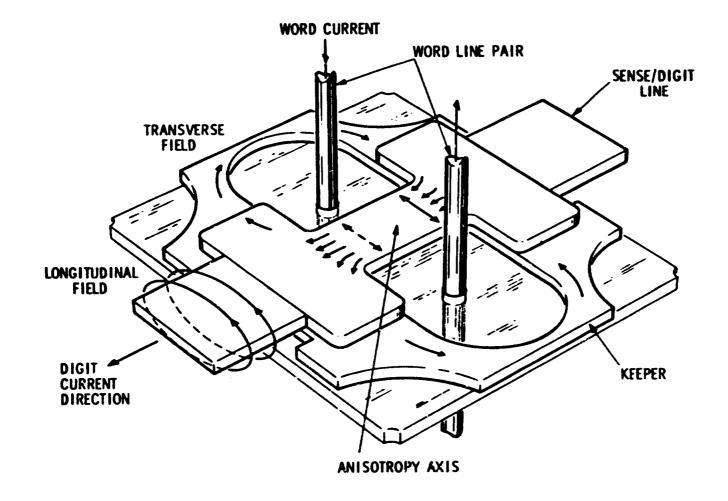

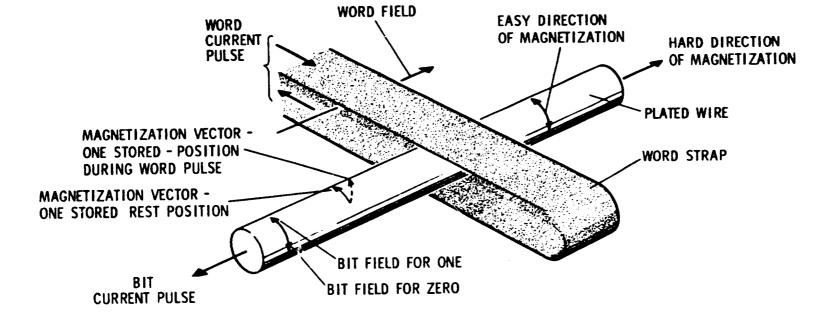

Many of the principles and problems of planar and cylindrical anisotropic magnetic films are similar, so much of the following explanation is applicable to the plated wire technique described in a later section.

# 2.3.2. Basic Principles of Thin Film Memory

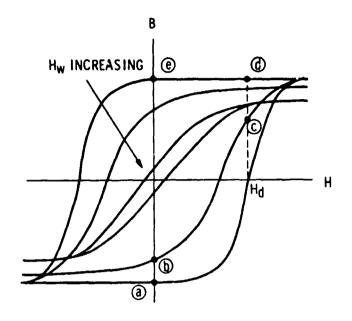

Thin magnetic films can exhibit anisotropic behavior; for example the characteristic B-H hysteresis loop changes as the film is rotated in the applied field. The magnetization in a thin film element has preference for a particular orientation, and this direction is referred to as the "easy" axis, with the "hard" axis being orthogonal to it. The easy axis magnetic properties are affected by the application of hard axis fields. Figure 2.3.1 illustrates the charging behavior of the easy-axis B-H characteristic of a thin film element as an increasing hard-axis field is applied. The variation in the shape of the hysteresis curve represents flux changes which can be used to induce voltage signals in sense windings placed near the element to determine the presence and sign of a remanent magnetization. The hard axis field is usually controlled by word selection logic and the easy axis parameters are associated with the bit or digit organization of a memory, If the element is originally magnetized as at point (a) in Figure 2.3.1, the application of a word field H, decreases the remanent magnetization to point (b). The corresponding change in easy axis magnetization flux will induce a voltage in a sense wire given by Faradays Law:

Figure 2.3.1 Thin Film Hysteresis Loop

A DE ANTANES DE LA COMUNESTION DE LA COMUNESCIA DE LA COMUNESCIA

V. W. Shink and the second second second

हर्ष्विद्यम् - -

Figure 2.3.2 Thin Film Switching Astroid

$$V(t) = -N \frac{d\phi}{dt}$$

Removal of the word field returns the element to point (a). This is an example of a non-destructive readout of information (NDRO). If a digit field  $H_d$  is simultaneously applied, the operating point moves from (a) to (b) to (c). Removal of the word field then shifts the magnetization of the element to (d). Finally, removal of the digit field leaves the remanent magnetization at (e), a situation which corresponds to the writing of a bit into the element, of opposite sign to that originally stored.

Note that the easy axis field necessary to switch an element decreases with increasing hard axis field. The magnitudes of these fields, in the case of an ideal film, are related by:

$$H_e^{2/3} + H_h^{2/3} = H_k^{2/3}$$

where  $H_k$  is defined as the anisotropy field constant. This relationship generates the switching astroid shown in Figure 2.3.2. For a typical 1000 Å Ni-Fe film  $H_k$  is about 5 oersted. If the vector sum of the applied fields exceeds the astroid switching boundary, e.g.  $H_1$  in Figure 2.3.2, the remanent field will align itself with the easy axis field  $H_{e_1}$ , no matter where it was before. If the sum does not exceed the boundary, e.g.  $H_2$ , no switching takes place. A hard axis field that exceeds  $H_k$ , e.g.  $H_3$ , will reduce the remanent field to zero. This last is the destructive read-out case (DRO), which is usually employed for its speed and greater freedom from nonideal film characteristics than NDRO.

The magnetic thin film's main attraction has been its high switching speed. For films less than 3,000 Å the switching mechanism is by magnetization vector rotation rather than domain wall motion, and occurs in 1 to 3 nanoseconds. Actual memory response time is therefore almost totally determined by geometry and drive electronics delays.

The amount of magnetic energy switched is low, approximately  $10^{-10}$  joules; and owing to fairly loose coupling of the flux change into the sense conductors, typical output signal voltages are low, usually 0.5 to 1.5 millivolt. The currents in word and drive currents for the simple, open element geometries are fairly high; 600-1000 ma and 50-100 ma respectively. The word currents are outside the range of today's integrated circuits.

Much research into films is devoted to bringing about integrated circuit compatibility.

A memory is organized by arranging the individual film elements in an array upon some substrate, with orthogonal word and digit conductors intersecting at each bit location. The elements need not be discrete areas of magnetic film, but can be locations in a continuous sheet. Many variations on this theme have been explored, most of them attempts to overcome or circumvent one or more of the problem areas discussed in the next section.

#### 2.3.3 Thin Film Problems

The departure of magnetic thin films from the ideal has been extensively studied and reported on in the literature over the last 15 years.

-#

e en 🙀

- Anterior

A COMPANY AND A

and the spectro set of the second

# 2.3.3.1 Creep

Salahashkali (Alalahan) ana kana kana kana sala salahan samanin masa nasa na

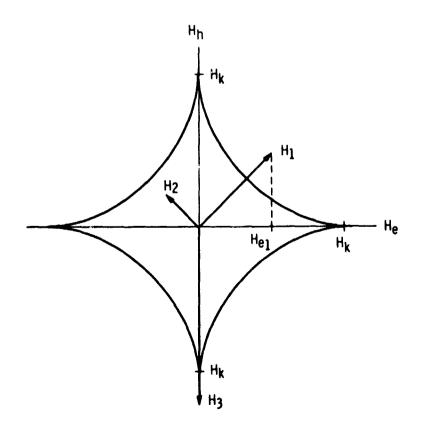

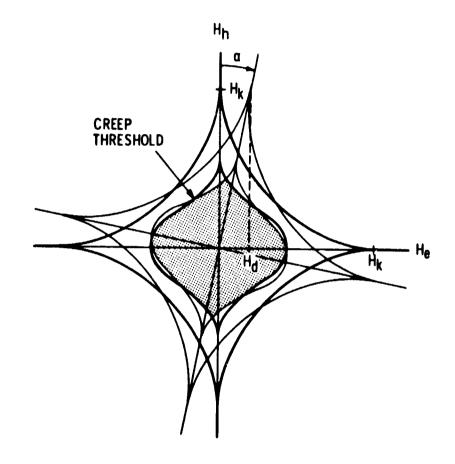

The thin film element does not exhibit homogeneous magnetic properties [1]. When a bit is written into a discrete memory element, the edges of the element do not switch together with the center, unless the same bit is repeatedly written into that location. Microscopic flaws in the film, irregularities in the film edges and in the substrate cause local sensitivity to field disturbances, which then act as nucleation centers for magnetic domain formations. These domains tend to grow and propagate under the influence of varying fields. Repeated switching of an element with the same bit, say a 'l', can therefore change its anisotropic behavior, and unsymmetrical or even erroneous output can be obtained when a '0' is then cycled in the same position. This characteristic is called creep, and is especially serious in continuous film memories as, for example, plated wire, because adjacent bit locations can be encroached upon by the errant domain wall motion under the influence of disturbing fields. The effect of creep is to reduce the boundary for unwanted switching from that of the ideal astroid. This second boundary, termed the creep thresh-old and illustrated in Figure 2.3.3, is the limiting field which, even if applied an infinite number of times, will not cause switching to occur. A good memory design assures that the combined effects of all fields not intended to result in switching i.e.:

1) Unselected bit fields

2) NDRO word fields

# Figure 2.3.3 Effect of Creep and Skew

3) Stray dynamic and static disturbance fields are contained within the creep threshold.

# 2.3.3.2 Skew and Dispersion

The easy axes of an array of elements are only nominally parallel to the geometrical axis, and to each other. The degree of average misalignment of the array is called skew. Figure 2.3.3 illustrates the effect of a skew of  $\alpha$  on the switching boundaries. Since a component of the word field now appears along the element's easy axis, the bit field to switch the element in the presence of skew must exceed:

$$H_{d} > H_{k} \sin \alpha$$

implying increased bit currents, with consequent increase in driver dissipation and disturbance fields.

Dispersion is the variation of the easy axis skew within a discrete element, or over the surface of a continuous sheet. It is usually represented by  $\alpha 90$ , which is defined as the maximum dispersion angle of the individual magnetization contributions from 90% of the area under consideration. Both effects can be considered additive and are due to the polycrystalline nature of the magnetic film and the failure of all the crystals to line up perfectly. Their combined effect is to reduce the area within the effective creep threshold (see shaded portion of Figure 2.3.3) and to reduce the stray field margin. The effects of skew, dispersion, the demagnetizing field and other stray fields combine to set an upper limit This has been discussed at length to the NDRO word field. in Ref. [3]. Briefly, there is a limit to the closeness with which the remanent magnetization may be aligned to the hard-axis during a read operation, beyond which the above effects can combine to prevent the magnetization from relaxing to its previous position.

#### 2.3.3.3 Magnetostriction

Magnetostriction has been quoted as the most serious cause of low yield of planar film arrays [2]. Although the deposited film is closely controlled to yield a zero-magnetostrictive composition, approximately 80% nickel and 20% iron, small deviations from ZMC are very sensitive to mechanical strain. The effect is a large increase in the skew angle with consequent decrease in the disturb threshold. Magnetostriction presents problems for substrate mounting, temperature equalization, and protection against acceleration, shock and vibration.

#### 2.3.3.4 Disturbance Fields

A thin film memory element is subject to a number of disturbing fields:

- 1) The demagnetization field

- 2) Stray fields due to skew, dispersion

- 3) Fields from neighboring elements

- 4) Unaddressed location fields

- 5) Fringe effects from currents in adjacent conductors

- Fields from pulses in word, bit lines induced by adjacent conductors

- 7) Adjacent element switching fields

- 8) The earth's magnetic field

- 9) Eddy currents in ground planes

The summed effect of all these must not exceed the local disturb threshold, or unwanted switching will occur.

Attempts to improve the density and speed of magnetic film memories have always run into problems associated with one or more of these disturbance effects, and different techniques of dealing with them have been developed.

#### 2.3.4 Planar Thin Film Techniques

Thin film memory arrays differ principally in 1) the geometry of the thin film elements, 2) the geometry of the word and digit conductors, and 3) the choice of substrate.

The objective of the element design is usually to reduce the demagnetization field of the simple rectangular thin film segment without diminishing the output signal or increasing the disturb thresholds.

The shape of the magnetic element influences the demagnetization field. Oblong shapes with the easy axis in the longer dimension have lower demagnetization fields; a diamond shape with 3:1 ratio of axes has been used. Domain nucleation centre effects are reduced by tapering the edges of the element. Thinner films have smaller demagnetization fields, but are more difficult to control in manufacture, and yield a smaller output signal when switched. For continuous films sufficient element separation must be assured so that only part of the element area is rotationally switched, thus avoiding problems associated with edge anisotropy and nucleation which would interfere with adjacent locations. The influence of stray fields can be decreased by increasing the disturb threshold of the elements, and by reducing the magnitude of the fields.

The composition of the magnetic film may be altered by the addition of ternary cobalt, copper or manganese [5].  $H_k$ and the coercivity  $H_c$  can be increased and  $\alpha$  90 decreased by an addition of up to 15% cobalt. A higher coercivity provides an increased resistance to unwanted switching, but it also implies higher drive currents, which in turn will aggravate the stray field problem. The inverse approach of lowering  $H_k$  and the switching threshold, so that lower drive currents can be used, has also been considered. Stray fields can be reduced by:

, ÷

on uiththe or A

the group state of the

- 1) Increased separations

- 2) Lowered drive currents

- 3) More sophisticated conductor geometry

- 4) Use of permeable keepers.

Arranging current conductors in complementary pairs, or creating multiple turns for a single conductor can help to concentrate the local magnetic field and attenuate the spread. The former has been used in a thin film array which is described later, and the latter is ideally suited to the plated wire film technique. Both naturally lead to a lower element density, but also to reduced drive currents.

Ferrite or permalloy keepers have been used to surround the elements and the conductors. Their effect locally is to reduce the demagnetizing field and to reduce drive current requirements. Between elements the keeper's low reluctance absorbs the stray fields and inhibits their interaction with adjacent locations. A continuous keeper will also reduce eddy currents in conducting substrates or ground planes, which create disturbing fields and incidentally prolong delays in drive current pulses. Ferrite has the advantage that it is electrically non-conducting, but its permeability decreases with frequency and it loses its effect for sharp current pulses. Permalloy has a wide frequency range, but is effective only for closely spaced, wide conductors.

Several different implementational approaches will now be described.

# 2.3.4.1 Split Film

This arrangement pairs two identical 15 mil x 45 mil film segments on either side of a set of rectangular intersecting word and digit lines. Segments are spaced 20 mil in the word and 50 mil in the sense-digit direction. The assembly is constructed of several substrates. Figure 2.3.4 illustrates the geometry. The magnetization field of the two segments, which are spaced 5 mils, reinforce each other and their distribution is nearer that of a closed flux linkage. Less dependence is placed on element shape and thickness. Burroughs has used this arrangement in the 8.5 x 10<sup>5</sup> bit film memory for the B8500 computer and the 1.3 x 10<sup>5</sup> bit memory for the ILLIAC IV. They claim that demagnetizing fields are reduced 50%. Bit density is 800 bits/sq.in. Manufacture is reasonably straightforward.

# 2.3.4.2 Mated Film

New Providents of the State of

UNIVAC employs multiple depositions on a single substrate. The magnetic material surrounds the digit line (Figure 2.3.5). The complementary word lines, two per element, are orthogonal to the array and pass through holes in successive planes, in the so-called "Solid Stack" assembly. Magnetic keepers are deposited as part of the element to contain the word field. The complex shapes and alignment tolerances restrict the density to 200 bits/sq.in., somewhat defeating the purpose of the sophistication; but UNIVAC claims an increased yield for the process, and relaxed tolerances on creep and sense noise [2]. This technique is applied to the UNIVAC 1832 airborne multiprocessor memory, which is a 10<sup>6</sup> bit, 750 ns cycle time unit.

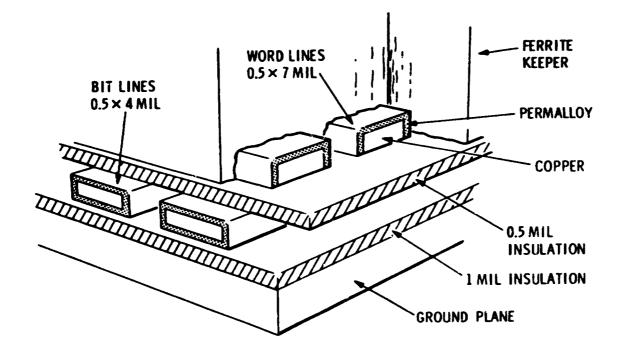

#### 2.3.4.3 Coupled Film

IBM has developed a high density element by depositing a 1000 Å film on rectangular cross section, intersecting word and digit lines (see Figure 2.3.6) [4]. The word-line film provides flux closure for the sense-line film elements. Separations are 0.5 to 1 mil. Packing density is very high: 10<sup>4</sup> bits/sq.in., and word drive currents are low: 200 ma. The manufacturing problems are, however, fairly severe.

ryater H

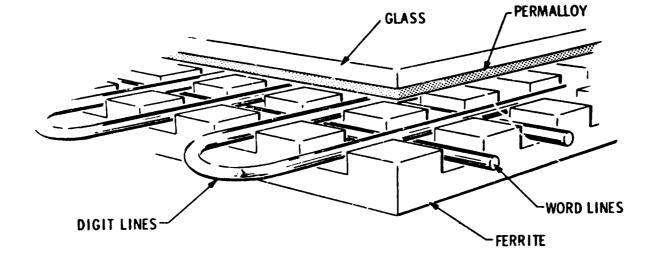

### 2.3.4.4 Post-and-film

This technique uses a continuous permalloy film evaporated onto a glass substrate. The elements are defined at the cross points of orthogonal word and sense lines. The unique feature is that the fields are localized by a continuous

4

Т

an also addressed agains and an address of a subsec

۱.

in de la composition en la composition de la comp

38

ì

、基本的合合化和微量的精制物的传播和描述和描述的描述中描述,但如此的如何的是是一个人的是一个人的。

Figure 2.3.6 Coupled Film Memory Element

١

39

hall

. .

ferrite keeper plane which has been scribed to receive the conductors, leaving an array of mesas or "posts", hence the name (see Figure 2.3.7). Groove spacing is 15 mil, but two interconnections per bit are used, yielding a density of about 2000 bits/sq.in. No etching is done which, proponents claim, boosts the yield. Drive currents are 250 ma and 40 ma for word and digit lines respectively; a 1.3 x  $10^5$  bit memory dissipates 22 watts [7]. A double film version using soft and hard magnetic films can demonstrate NDRO performance without critical drive currents. Variations on this technique, including the "waffle-iron" memory, so-called because of the shape of the ferrite keeper, are being investigated by several manufacturers in the U.S., Europe and Japan. It offers some manufacturing advantages, being batch oriented with few processing steps, but achieves no breakthrough in packing density.

# 2.3.5 Thin Film Memory Application

Although thin film memory development has been pursued for nearly 15 years, adequate manufacturing techniques have not been devised to produce yields which would make this technology commercially attractive. Apart from one or two outstanding exceptions, use of thin films in computer memories has been restricted to laboratory research vehicles, or to special applications requiring high speed or limited capacity, e.g. scratch pad stores and airborne military computer memories.

Thin film techniques are still being very actively investigated in industrial laboratories, although emphasis is now on plated wire research. Some planar memories are still being constructed, but not usually greater than  $10^5$  to  $10^6$  bits. The inherent high speed of the switching mechanism still provides an incentive for continuing effort. A 60 ns cycle time, NDRO, 1.5 x  $10^{5}$  bit thin film memory has been described [6]. This sort of performance is still a challenge to semi-conductors. But activity in the mass storage field above 10<sup>6</sup> bits has been slight. The high per-bit costs, and the problems of integrating large numbers of 2-D arrays with inherent low output and sensitivity to noise, have been the cause. It is significant that a high percentage of operational thin film memories operate in the DRO mode, despite the speed and electronics advantages inherent in NDRO, because DRO requires far less caution regarding thresholds. Of even greater significance to the possible future of planar film mass memories was the decision by Burroughs (which has been committed to film memories for their commercial computers for 10 years), to replace the ILLIAC IV thin film memory with a semiconductor version.

A list of some thin film memory systems that have been assembled is presented in Table 2.3.1.

e 🔪

Figure 2.3.7 Post and Film Technique

1.11

١

gi **k**aran

and the state of the second second

|                        | Capacity<br>(bits)    | Volume<br>(cu.in.) | Weight<br>(1bs) | Access/Cycle      | Power<br>(watts) |

|------------------------|-----------------------|--------------------|-----------------|-------------------|------------------|

| Burroughs<br>B8500     | 8.5 x 10 <sup>5</sup> |                    |                 | 250ns/500ns       | 845              |

| Burroughs<br>ILLIAC IV | 1.3 x 10 <sup>5</sup> |                    |                 | 120ns/240ns       |                  |

| UNIVAC<br>1832         | 5.0 x 10 <sup>5</sup> | 1100               | 49              | 225/500 <b>ns</b> | 190              |

| MIT<br>Lincoln         | 3.6 x 10 <sup>5</sup> |                    |                 |                   | 200              |

and a second second

•

Table 2.3.1 Characteristics of Some Thin Film Memories

- D

•

1

1 1

.

· · · · · ·

### References for Section 2.3

04442116141

. 14. i della i ciardina

- 1. Overn, W.M., "Controlling Creep and Skew in Thin-Film Memories", Electronics, September 15, 1968, pp. 125-128.

- Overn, W.M., "Status of Planar Film Memory", IEEE Trans. Magnetics Mag-4, September 1968, pp. 308-312.

- Logue, C.L., "Effects of Skew and Demagnetizing Fields on NDRO Performance", IEEE Trans. Magnetics MAG-5, March 1969, pp. 10-13.

- Chang, H., "Coupled-Film Memory Elements", J. App. Physics, Vol. 38, No. 3, March 1967, pp. 1203-1204.

- 5. Freedman, J.F., "Soft Magnetic Thin Film Memory Materials", IEEE Trans. Magnetics MAG-5, December 1969, pp. 752-764.

े इ.ज.

a constitution and the second second second second second

- Kohn G., et al, "A Very-High-Speed, Nondestructive Read Magnetic Film Memory", IBM Jour. of Res. and Develop., March 1967, pp. 162-168.

- Veith, R.F., and Womack, C.P., "Post-and-Film Memory Delivers NDRO Capability....", Electronics, January 19, 1970, pp. 102-106.

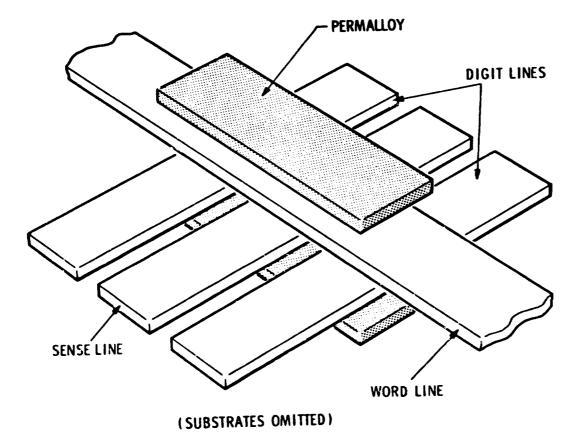

### 2.4 Plated Wire

#### 2.4.1 Introduction

The plated wire memory technique depends on the establishment of an anisotropic magnetic field in a thin, cylindrical film of permalloy, a nickel-iron alloy. It was first suggested as a computer memory element as long ago as 1958 [1], but has not risen to prominence as a competitor to the ferrite core until the last two years or so, due mainly to problems associated with wire production and array manufacture which have rendered the technique uneconomical. That these appear to have been overcome is evidenced by a surge of commercial activity in this field [2].

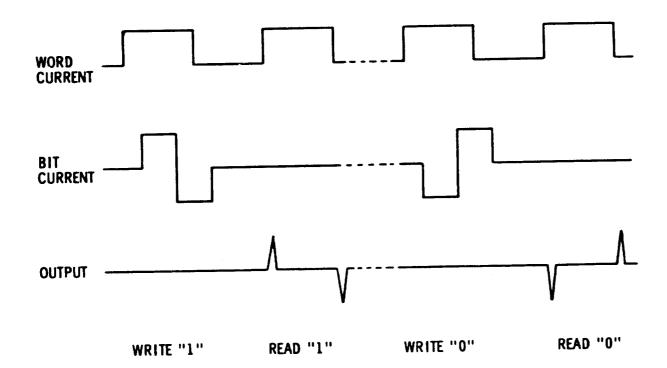

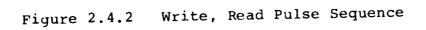

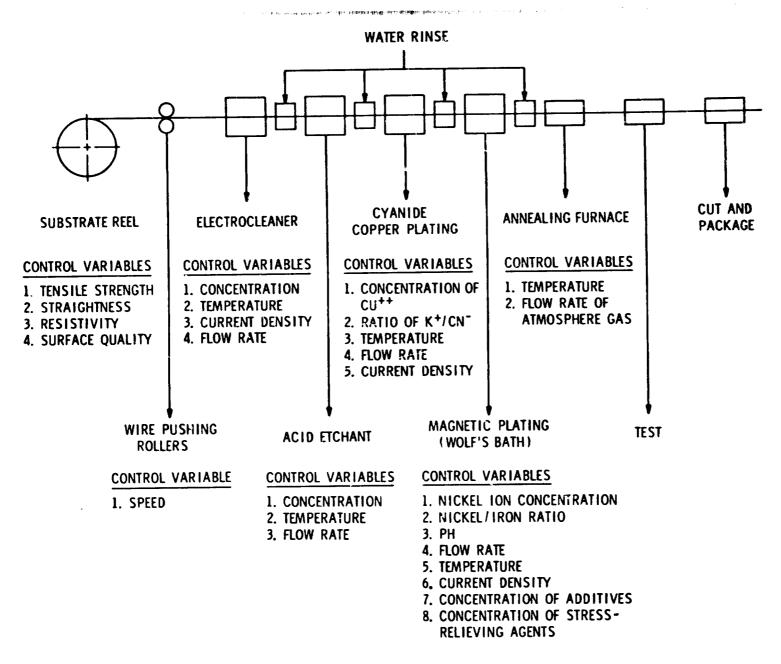

#### 2.4.2 Description of Technique