https://ntrs.nasa.gov/search.jsp?R=19720017581 2020-03-11T18:12:33+00:00Z

MELBOURNE, FLORIDA 32901

1.16 Constraints and the second statements of the statement of the second s

CONTRACT NAS 9-10441 FINAL REPORT

# DATA COMPRESSION/ ERROR CORRECTION DIGITAL TEST SYSTEM

## **APPENDIX 2**

## THEORY OF OPERATION

JANUARY 1972

#### TABLE OF CONTENTS

| Paragraph                                                                                                                                                                                                                                                                           | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| A2-1.0                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                                                                        |

| A2-1.1                                                                                                                                                                                                                                                                              | System Block Diagram Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                                                                                                        |

| A2-2.0 .                                                                                                                                                                                                                                                                            | DETAIL TRANSMITTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                                        |

| A2-2.1<br>A2-2.2<br>A2-2.3<br>A2-2.4<br>A2-2.5<br>A2-2.6<br>A2-2.7<br>A2-2.7.1<br>A2-2.7.2<br>A2-2.8<br>A2-2.8<br>A2-2.8<br>A2-2.8<br>A2-2.8<br>A2-2.10<br>A2-2.10<br>A2-2.11<br>A2-2.12<br>A2-2.12.1<br>A2-2.12.1<br>A2-2.12.2<br>A2-2.12.3<br>A2-2.12.4<br>A2-2.13.1<br>A2-2.13.1 | Filter - FL1.<br>Video Amplitude Shaper - A3 A2 A2<br>Analog-to-Digital Converter - A1<br>Sync Separator - A3A2A1<br>Reducer - A3A1A3<br>Statistical Encoder - A3A5.<br>Transmit Rate Buffer Subsystem - A3A1A4<br>Rate Buffer .<br>Detail Operation .<br>Rate Adaptive Tolerance Generator - A3A1A1<br>Detailed Description.<br>Voice Encoder - A3A3A4<br>Information Rate Timing - A3A2A6<br>Sample Rate Clock - A3A2A6(A7)<br>Time Division Multiplexer - A3A2A1<br>Format<br>Frame Rate Counter .<br>Data Source .<br>Multiplexing Operation<br>Convolution Encoder - A3A3A3<br>Detail Description .<br>Naise Generator - A3A3A2 | 5<br>5<br>11<br>12<br>19<br>26<br>26<br>26<br>29<br>29<br>31<br>33<br>35<br>37<br>37<br>40<br>40<br>41<br>41<br>42<br>44 |

| A2-2.14<br>A2-2.15                                                                                                                                                                                                                                                                  | Noise Generator – A3A3A2<br>Output Buffer Amplifier – A3A3A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44<br>44                                                                                                                 |

| A2-3.0                                                                                                                                                                                                                                                                              | DETAIL RECEIVER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                                       |

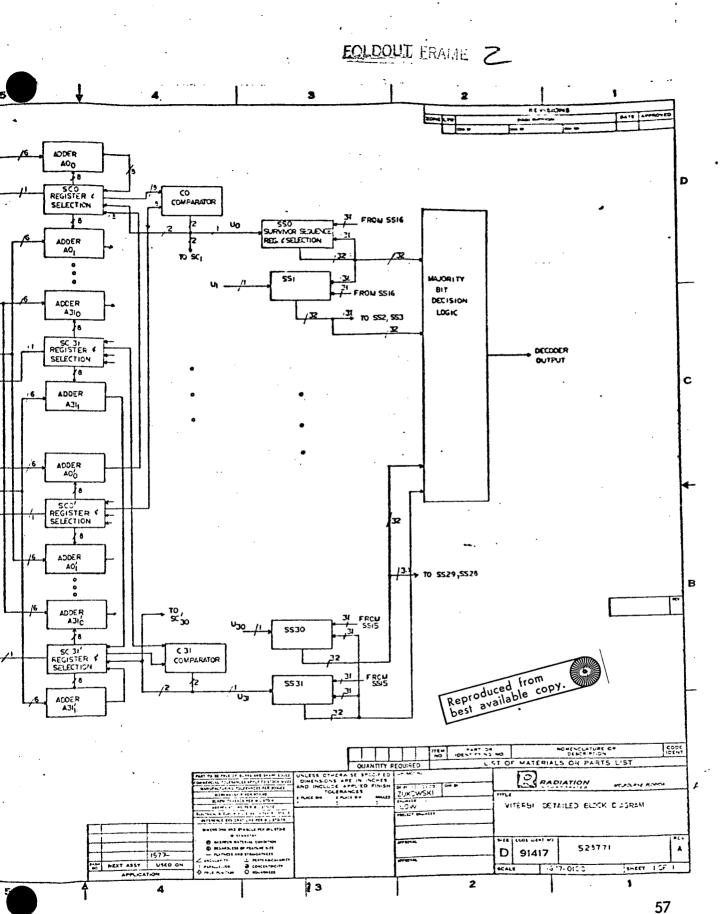

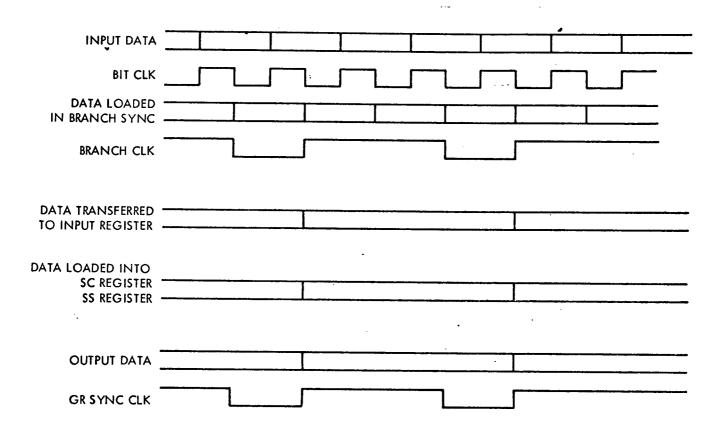

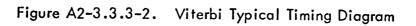

| A2-3.1<br>A2-3.2<br>A2-3.3<br>A2-3.3.1<br>A2-3.3.2<br>A2-3.3.3                                                                                                                                                                                                                      | Bit Sync-Signal Conditioner - Preprocessor - A1(A2)<br>Quadraphase Data Combiner - A9A2<br>Viterbi (Maximum Likelihood) Decoder<br>Review of Decoding Process<br>General Functional Organization of the Decoder<br>Block Diagram Description                                                                                                                                                                                                                                                                                                                                                                                         | 45<br>49<br>50<br>50<br>53<br>56<br>97                                                                                   |

| A2-3.4<br>A2-3.4.1                                                                                                                                                                                                                                                                  | Fano Decoder - A8A1A9 (A13-A22)Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97<br>97                                                                                                                 |

### TABLE OF CONTENTS (Continued)

0

Page

## <u>Title</u>

<u>Paragraph</u>

| A2-3.5    | Group Synchronizer and Demultiplexer – A8A1A2      |

|-----------|----------------------------------------------------|

| A2-3.5.1  | Group Sync Policy                                  |

| A2-3.5.2  | Group Synchronizer Block Diagram                   |

| A2-3.6    | Receiver Rate Buffer (A8A1A1, A8A1A8, and A8A1A11) |

| A2-3.6.1  | Receiver Buffer Operation                          |

| A2-3.6.2. | Buffer Synchronization                             |

| A2-3.7    | TV Data Reconstructor - A8A1A7                     |

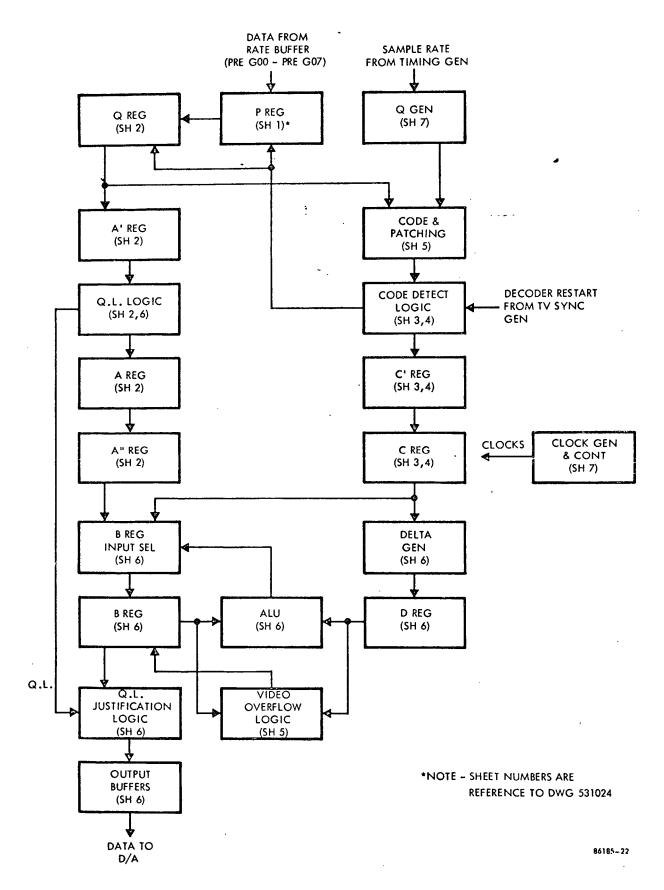

| A2-3.8    | Statistical Decoder – 2A8A6A1 & 2                  |

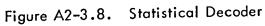

| A2-3.9    | TV Sync Generator – A8A1A10                        |

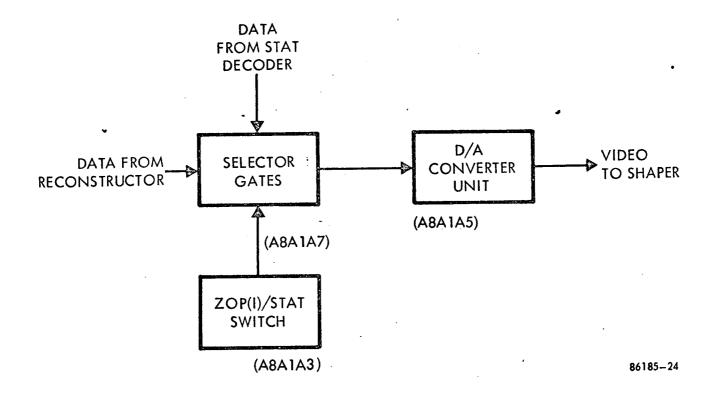

| A2-3.10   | Digital-to-Analog Converter – A8A1A5 and A8A1A7    |

| A2-3.11   | Video Amplitude Shaper (Expander) – A8A1A6         |

| A2-3.12   | Voice Demodulator - A8A1A3                         |

| A2-3.13   | Timing Generator – A8A1A4                          |

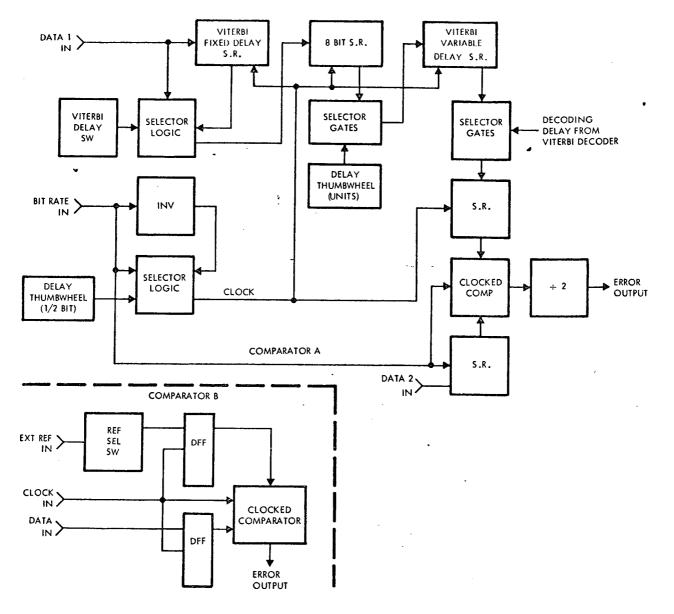

| A2-3.14   | Bit Comparators - A8A9A1                           |

#### APPENDIX 2

. .....

1

### THEORY OF OPERATION

#### A2-1,0 INTRODUCTION

This volume consists of three major sections: a system block diagram description, a description of the units of the Transmitter, and a description of the units of the Receiver.

#### A2-1.1 System Block Diagram Description

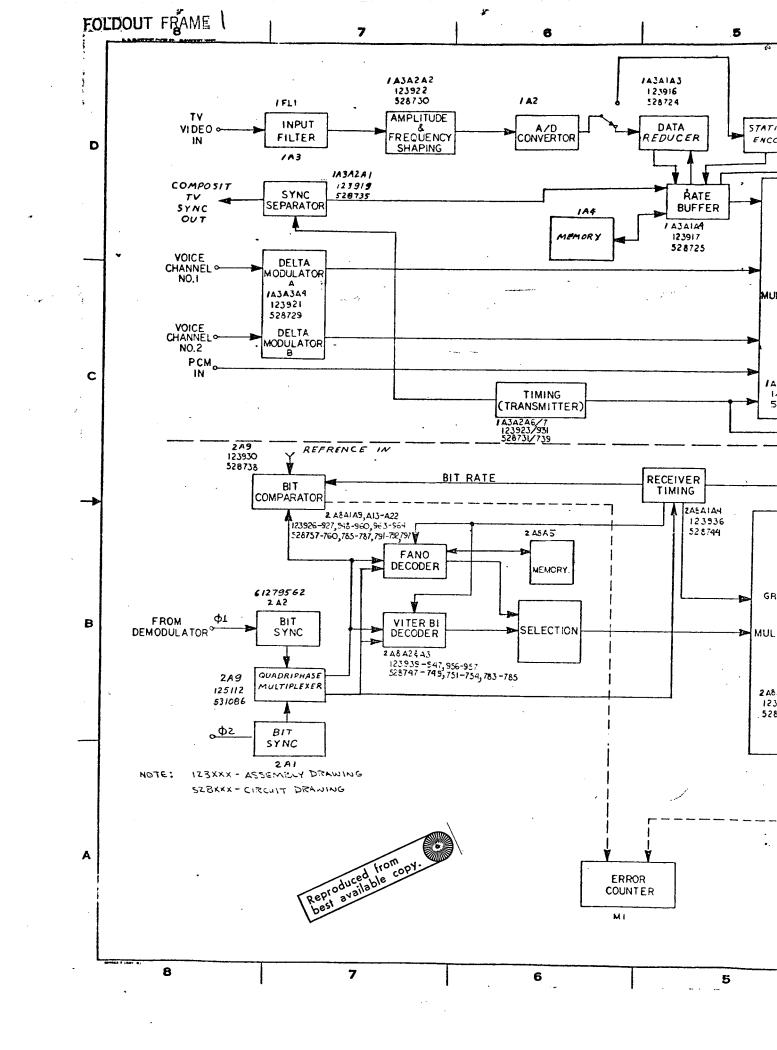

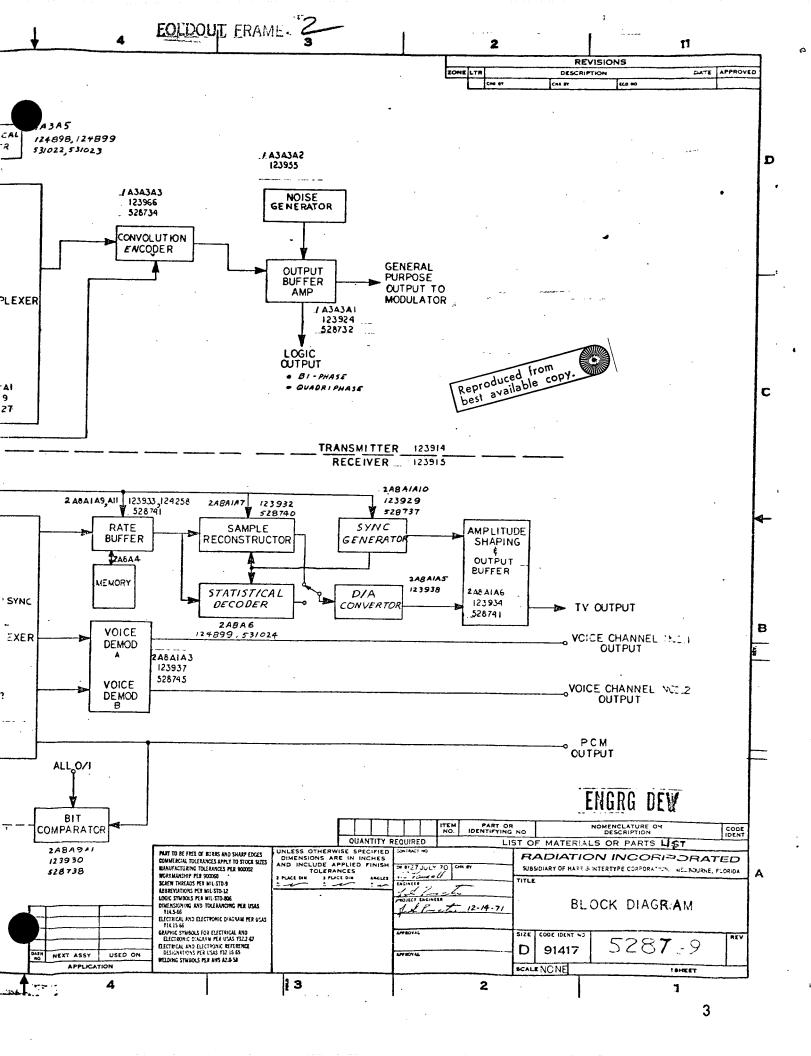

An overall block diagram of the DC/EC Digital System Test is shown in Drawing 528769. The system is divided into two major units, the Transmitter and the Receiver. In operation, the Transmitter and Receiver are connected only by a real or simulated transmission link. The system inputs consist of: 1) Standard format TV video, 2) Two channels of analog voice and 3) One serial PCM bit stream.

Considering first the TV channel, the analog video is supplied from a TV camera in synchronism with the sync separator and routed to the Input Filter. The Sync Separator generates the sync and blanking pulses for the video and produces digital sync words. The unit also produces control signals to the Data Reducer to prevent unnecessary signal processing and transmission during sync and blanking times. The Amplitude Shaping unit processes the analog video so that it may be efficiently sampled and quantized by the Analog to Digital Converter. The digital words from the converter are supplied to the Data Reducer. This unit processes the data to eliminate samples which are unnecessary to the later reconstruction process. These nonredundant samples are fed to the Rate Buffer to allow conversion from their nonuniform rate of occurrence to a uniform transmission rate. Different picture areas contain different numbers of nonredundant samples, so the input rate to the buffer varies. Since the average input and output rates of the buffer must be equal, it is necessary to provide feedback control of the Data Reducer by the Rate Buffer, to avoid uncontrolled overflow or underflow of the Buffer.

An alternate method of reducing the number of transmitted bits per picture may be selected by utilizing the Statistical Encoder. This technique transmits a variable number of bits for code words representing the difference between adjacent A/D samples. The length of the transmitted code words is preprogrammed as a function of the frequency of occurrence of the input differences. Differences which occur most often are presented by the shortest length code words while differences which occur least often are represented by the longest code words. As the code words are generated they are stored in the Rate Buffer prior to transmission.

The Rate Buffer output forms one input to the Multiplexer, which combines this signal with the other three signals. Two of these other signals are from the two Delta Modulators, which convert the analog voice input signals into efficient digital form. The third input is a serial PCM telemetry signal. A sync pattern is also multiplexed with the data to allow synchronization of the receiving equipment. The digital voice and TV data are synchronized with the PCM to allow simple time division multiplexing of the signals to a single bit stream at the output of the multiplexer. The multiplexer output is fed to the Channel Encoder (Convolution Encoder) which inserts redundancy into the bit stream in a form which allows the receiver to efficiently correct transmission errors due to noise. The final bit stream is fed to the Output Buffer Amplifier, which provides flexible gain and offset for interface with a variety of modulators or simulators.

This amplifier also contains provision for mixing noise with the signal to allow link simulation at baseband frequencies. A wideband noise generator with adjustable level is provided. In addition to data, a clock at the transmitted bit rate is provided for use in external equipment.

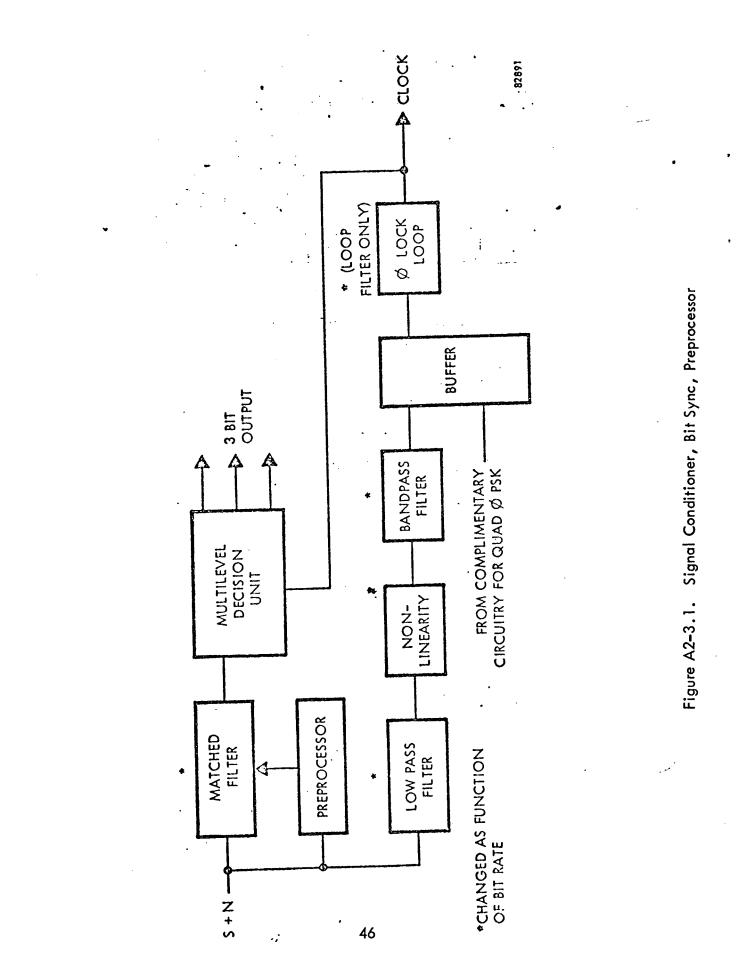

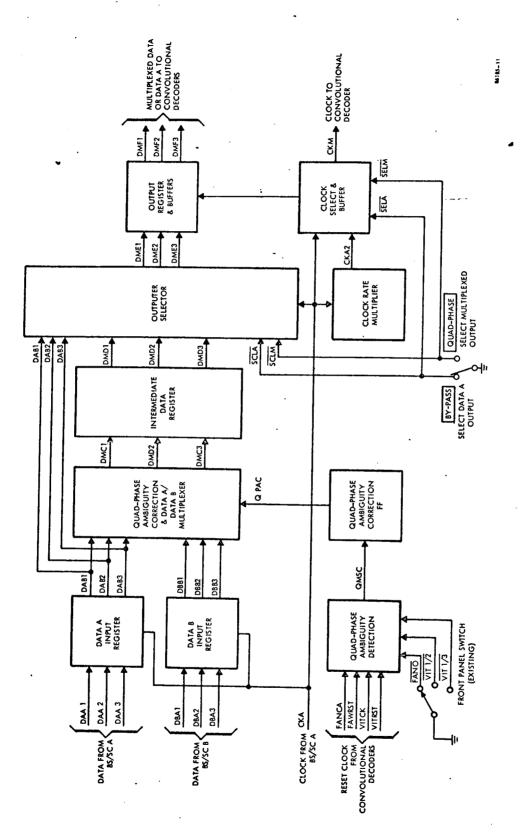

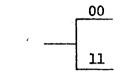

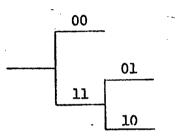

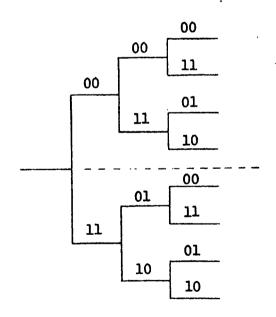

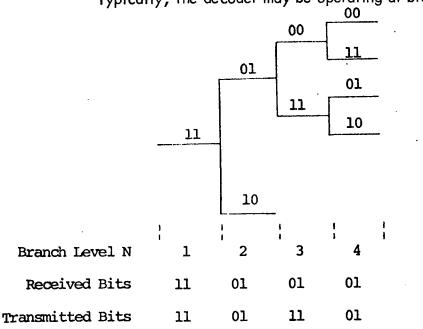

Directing attention to the receiver section, the input signal is applied to the Bit Synchronizer, which synchronizes a bit rate clock to the input and filters the data with a matched filter. The output of the bit detector filter is sampled (by the derived bit rate clock) and quantized to three bit resolution. In the case of Quadriphase signals a second Bit Synchronizer is provided. The output of the two Bit Synchronizers are combined in the Quadriphase Multiplexer. The combined signal, and clock, are fed to the Decoders which operate on the signal to correct transmission errors and reconvert the signal to the form existing at the Encoder input. The Decoders contain circuitry to establish decoding sync, and to resolve demodulator polarity ambiguities. Two Convolution Decoders are provided. One, a parallel processing device implements the Viterbi algorithm and the other, a sequential device, implements the Fano algorithm. The Decoder output is applied to the Group Synchronizer, which locates the sync pattern inserted at the transmitter and synchronizes the demultiplexer.

The Demultiplexer now separates the signal into four individual channels (and deletes the sync pattern). The PCM is outputted directly, while the two voice channels are reconstructed to analog form in the Voice Demodulators and outputted.

The TV channel words are fed at a uniform rate to the Rate Buffer, and are outputted from the buffer as required by the Reconstructor or the Statistical Decoder. TV sync patterns are recognized and used to synchronize the TV Sync generator, which regenerates the standard TV sync signals. The TV video and sync are converted to analog form in the Digital to Analog Converter. The signal is then shaped in the Amplitude Shaping unit to remove the effect of the shaping performed at the transmitter. The final output is standard TV waveform similar to that at the input of the transmitter.

Two bit comparators are provided to monitor the bit error rate at both the input and output of the Convolution Decoders. These units compare the delayed transmitted data or its equivalent to the corresponding receiver data, and generate error pulses. A Counter counts these errors over an adjustable time period and decimally displays the bit error count.

#### A2-2.0 DETAIL TRANSMITTER DESCRIPTION

The following sections describe the individual units of the Transmitter in more detail.

The filter is a bandpass filter, manufactured by Krohn-Hite Corporation, Model #3103R. A list of the primary specifications are provided below:

- Frequency Range: Low-cutoff frequency independently adjustable from 10 Hz to 1 MHz in five bands. High-cutoff frequency independently adjustable from 30 Hz to 3 MHz in five bands.

- 2. Frequency Dials: Separate low-cutoff and high-cutoff dials.

- 3. Bandwidth: Continuously variable within the cutoff frequency limits of 10 Hz to 3 MHz.

- 4. Attenuation Slope: Nominal 24 dB per octave.

- 5. Frequency Response: Standard response is a 4th order Butterworth, maximally flat. A RESPONSE switch on rear of chassis converts to simple RC response optimum for transient-free performance.

- 6. Maximum Input Amplitude: 3 volts rms, decreasing to 2.5 volts at 3 MHz.

- 7. Maximum Output Amplitude: See 6.

- 8. Maximum Output Current: 10 ma rms.

- 9. Connectors: Front panel and rear of chassis, one BNC connector for INPUT and for OUTPUT.

#### A2-2.2 Video Amplitude Shaper - A3 A2 A2

The Transmitter Video Amplitude Shaping Network (Drawing 528730) accepts the composite video input from the system input filter. It amplifies this signal linearly or nonlinearly and provides an output amplitude of 0 to +5 volts to drive the A/D converter. The transfer function of this amplifier is piece wise linear and has up to 3 line segments. The slopes of the line segments are individually adjustable by means of a plug-in resistor module located on the video amplitude shaping board.

A2-2.1 Filter - FL1

The Video Processing Channel consists of amplifiers AR1, AR2, AR3, and AR4 and their associated circuitry. The DC restorer is composed of comparator U1, transistors Q2 and Q3, transformer T1, diodes CR7, CR8, CR10 and CR9 and summing amplifier AR5. Transister Q1, amplifier AR6 and reference diode CR5 form the necessary circuit to establish a precision voltage to reference the break point of the linear segments. Variable resistor R20 establishes the clamping level of the DC restorer, resistor R27 establishes the bias current for diodes CR2 and CR3 and. variable resistors R11 and R14 establish the break points. \$

Amplifier AR1 is used to drive AR2 and the DC restorer circuit. The input video from AR1 is amplified by AR2 (X5) and shaped by amplifier AR3. AR4 is used to drive the 50 ohm input of the A/D converter.

Amplifier AR3 and its associated circuitry perform the shaping function of the input video. The two break points are determined by the resistive combinations of R13, R14, R35, and R12, R11, R34. The circuit is designed to operate on a positive going signal with diode CR1 removing all negative going signals. Thus, using the level adjustment (R20) the incoming signal can be clamped such that only the sync pulse is removed. A brief review of operational amplifier fundamentals is presented to help clarify the discussion of the shaping network.

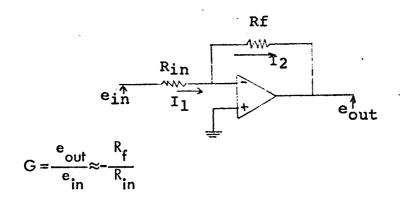

The gain of an operational amplifier is expressed as:

The gain equation is an approximation, but it is reasonably accurate for low frequencies, and provided the amplifier has a large open loop gain. Other approximations to be used in the following discussion are:

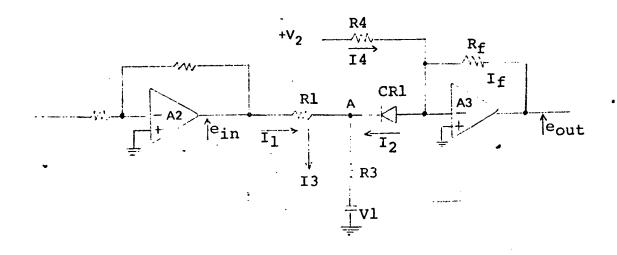

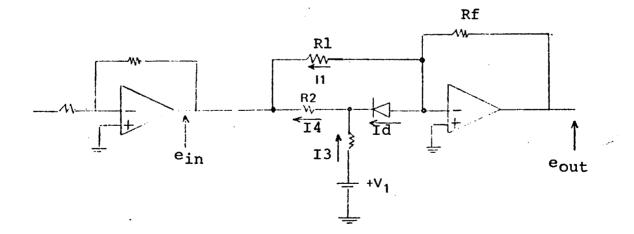

and the summing point for  $I_1$  and  $I_2$  is ground. Therefore, let's consider the following circuit:

For this discussion the break occurs on a positive going signal, as does the actual shaper Figure 3.3-2. The diode CR1 is biased on for 0 volts in. The bias current is determined by V2 and R4. Resistor R3 and V1 are adjusted to sink 12 and 11 plus establish the break point. Since there is a drop across a forward biased diode, amplifier A2 will have to supply enough current for  $e_{in} = 0$ , such that  $1_1 R_1$  is equal to the diode drop. Therefore, for  $e_{in} = e_{out} = 0$  volts. The following conditions exist:

$$I_{f} = 0$$

$I4 = I2 = \frac{V2}{R4}$

$I3 = I1 + I2$

$I1 \approx \frac{.6}{R1}$

As  $e_{in}$  is increased in the positive direction 12 decreases and  $l_f = 14 = 12$ . In this way an output voltage is generated such that

$$l_{f} = \frac{e_{out}}{R_{f}}$$

This will continue until 11 = 13 and 14 = 1f at which time the diode is back biased and a further increase in  $e_i$  will cause no further change in output voltage.

With CR1 biased on, point A will be at a potential of approximately 0.6 volt below ground and this point will remain at the potential until the conduction of the diode is cut off by back bias. If we assume the above statement is true, then the diode can be considered as a constant voltage source with an internal resistance and the gain can be expressed as:

A

$$G = \frac{e_{out}}{e_{in}} \approx \frac{R_f}{R_i^1 + R_d}$$

where  $R_d$  is the dynamic resistance of the diode.

The above gain equation is sufficient for a reasonable approximation of the gain of the circuit while the diode is forward biased and a more detailed analysis will not be presented.

Therefore, with R1 determined by the required gain, the break point can be determined as follows:

$$e_{in} = e_{break}$$

when  $11 = 13$  and  $12 = 0$

Thus:

$$e_{inb} = I_b [R1 + R3] - V1$$

IbR3= $e_{inb} + V1 - IbR1$

assume that for 12 = 0:

$$e_{inb} = I_d R I$$

then:

$$R3 = \frac{e_{inb} + \sqrt{1 - l_b R1}}{\frac{e_{inb}}{R1}}$$

$$R3 = \frac{\sqrt{1}}{e_{inb}} R1$$

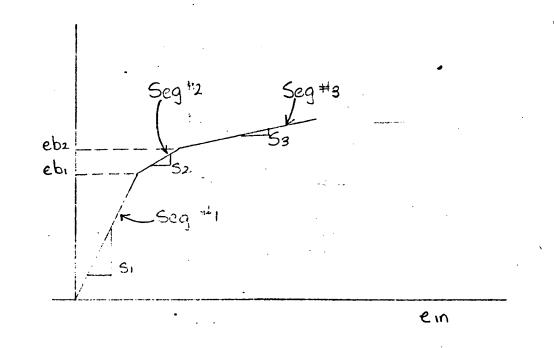

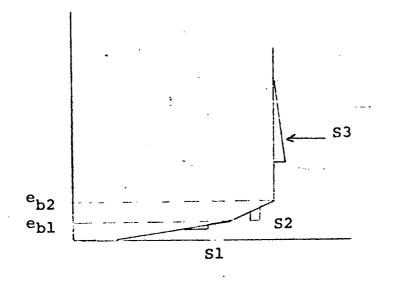

Using the equations just derived, the circuit parameters for the three line segments shown below can be calculated:

There are four different transfer functions provided. These are:

1. Linear,  $e_{out} = e_{in}$  (Function A).

:

- 2. A transfer function where segment #1 has a greater slope than the slope of the equal perceptibility curve (Function B).  $S1 \approx 10$ ,  $S2 \approx 1$  and  $S3 \approx 1/3$ .

- 3. A transfer function where segment #1 has a slope that is less than the slope of the equal perceptibility curve (Function C).  $S1 \approx 4$   $S2 \approx 1$  and  $S3 \approx 1/3$ .

- 4. A two segment transfer function selected to complement the camera nonlinearity,  $S_1 \approx 2$ ,  $S_2 \approx 0.8$ .

From Drawing 528730 the components that determine the different slopes are contained on plug-ins and are: R9, R10, R11, R12, R13, and R14. Variable resistors R27, R34, and R35 are used for the initial setup and for periodic alignments.

It should be understood that the following equations for the break points and slopes are approximations and the actual desired parameters were determined or confirmed empirically. For Function A:

$$S_1 \approx \frac{R16}{R9} = 1$$

where:

$$R10 = \infty$$

$$R11 = \infty$$

$$R12 = \infty$$

$$R13 = \alpha$$

$$R14 = \infty$$

For Functions B and C:

Assume diode resistance  $Rd \approx 40$  ohms

•

$$Ra = \frac{(R9) (R12 + Rd)}{R9 + R12 + Rd)}$$

$$Rb = \frac{(Ra)(R13 + Rd)}{(Ra + R13 + Rd)}$$

then:

$$S_{1} = \frac{R16}{Rb}$$

(Slope of Segment No. 1)

$$S_{2} = \frac{R16}{Ra}$$

(Slope of Segment No. 2)

$$S_{3} = \frac{R16}{R9}$$

(Slope of Segment No. 3)

$$e_{b1} = \frac{3.3 R16}{R14 + R35}$$

(Voltage for break point No. 1)

$$e_{b2} = \frac{3.3 R16}{R11 + R34}$$

(Voltage for break point No. 2)

Ģ

The diode bridge comprised of diodes CR7, 8, 10, and 9 is turned on during the composite sync time. This allows the capacitor C20 to be charged to a positive level equal to the peak voltage of the sync pulse contained in the video signal. The voltage is positive because the video signal has been inverted by AR1. Utilizing Amplifier AR5, this positive voltage is compared with a negative voltage determined by the position of R20. Thus, the delta voltage is added to the video waveform by AR2. In this manner, the sync pulse is clamped to a voltage level determined by R20. Comparator UI shapes the sync pulse and transistors Q2 and Q3 supply the necessary current to drive the transformer T1 to turn the diode bridge on and off.

The resistive network, comprised of R37 and R40, establishes a voltage level (1.65 volts) for the comparator to reference the input sync with and change levels if the sync pulse is of greater amplitude than the reference level. Resistors R30 and R36 cause the comparator to have hysteresis effect, thus preventing oscillation when the comparator changes state.

Zener diode CR5 establishes a voltage reference for Amplifier AR6 and the current drive Q1. This voltage reference is used to set the levels for the line segment break points.

#### A2-2.3 Analog-to-Digital Converter - A1

The Analog-to-Digital Converter is manufactured by Inter-Computer Electronics, Inc., Model IAD-1206. A list of the primary specifications are provided below. For this application, the sample and hold has been bypassed to allow operation at variable sampling rates.

| 1. | Input Voltage          | 0 to 5 volt full scale                                                                                                                                                  |

|----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Input Impedance        | 50 ohms nominal                                                                                                                                                         |

| 3. | Conversion Rate        | 6 bit binary conversion at ten megahertz rate<br>from internal clock                                                                                                    |

| 4. | Overall Accuracy       | $\pm 1\%$ of FS $\pm 1/2$ least significant bit                                                                                                                         |

| 5. | Linearity              | ±1 least significant bit                                                                                                                                                |

| 6. | Digital Output         | Parallel output straight binary. Logic one "1" is<br>2.4 (full load) to 5 volts (unloaded). Logic<br>zero (0) is 0 volts +0.5 volt. TTL compatible<br>drive capability. |

| 7. | Convert Complete Pulse | Pulse is a logic "one" 20 nanoseconds wide that<br>will be available 20 nanoseconds after conver-<br>sion is completed.                                                 |

#### 8. External Convert Command

For synchronous drive from an external signal source, pulse should be greater than 4 volts with a minimum width of 20 nanose conds and a maximum width of 50 nanose conds. Rise time 10 nanose conds. Fall time 10 nanoseconds. Nominal input impedance 50 ohms. Conversion triggerable from an external source at rates from DC to 10 megahertz. 3

Environmental

10. Power

9.

Temperature 0° to 50° C

115 VAC ± 10% 60 Hz 45 watts

#### A2-2.4 Sync Separator – A3A2A1

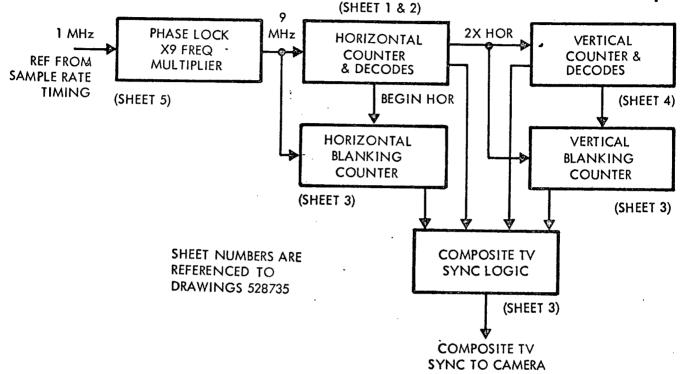

The function of the sync separator is to generate a composite TV synchronization signal to synchronize the TV camera to the system timing. The Sync Separator also provides a blanking signal to control the operation of the Reducer.

A block diagram of the Sync Separator is shown in Figure A2-2.4. The timing is derived from a one Megahertz reference signal from the Sample Rate timing circuitry. This signal is frequency multiplied by a phase lock multiplier to produce a 9 Megahertz signal which is coherent with the sample rate. This 9 Megahertz is used by the Horizontal Counter and Decodes to produce a twice horizontal rate signal, a "begin horizontal blanking" signal, and the horizontally related components of the composite sync signal. Horizontal blanking is generated by a separate counter, from the 9 Megahertz and the "begin horizontal" signal. In a similar manner, the vertically related timing signals are produced from the twice horizontal rate by the Vertical Counter, Decodes and the Vertical Blanking Counter. The Composite TV Sync Logic combines the various horizontal and vertical timing signals to produce the output Composite TV Sync Signal.

#### A2-2.5 Reducer - A3A1A3

There are two redundancy reduction techniques implemented in the reducer. These are the Zero-Order-Predictor (ZOP) and the Zero-Order-Interpolator (ZOI). The reducer subsystem will process the 6 bit A/D parallel output at a rate (1 to 9 MHz) selected from a thumbwheel on the front panel. The reducer tolerance will be a four bit number that can be selected as a fixed value or rate-adaptive. In the rate-adaptive tolerance mode, tolerance is controlled by the transmission buffer fill rate.

86185-3

Figure A2-2.4. Sync Separator

Flexibility of parameter choice is supplied by allowing transmission of a 6 bit sample and 4 bit time tag, a 5 bit sample and 5 bit time tag, or a 4 bit sample and 6 bit time tag. These combinations restrict the transmitted nonredundant word to 10 bits allowing simplification of the multiplexing scheme. When 4 bit timing is selected, the 6 bit nonredundant samples chosen by the reducer are transmitted as is. A choice of 5 bit timing causes the first 5 MSB of the nonredundant sample to be combined with the time word for buffer insertion. This is accomplished by gating the MSB of the 5 bit time count into the position normally occupied by the LSB of the 6 bit samples. The 6 bit time word, in a similar manner, combines the first 4 MSB of the nonredundant sample with the 6 bit time for buffer insertion. In this case gating on the first two MSB of the time count is required. Gating is controlled by the sample/time word size selection on the front panel. ø

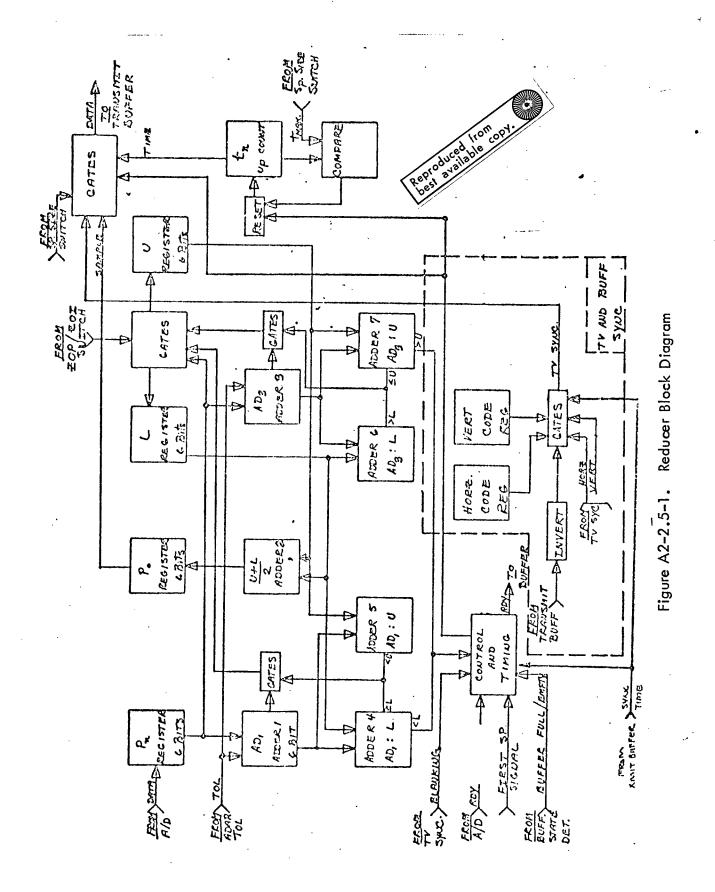

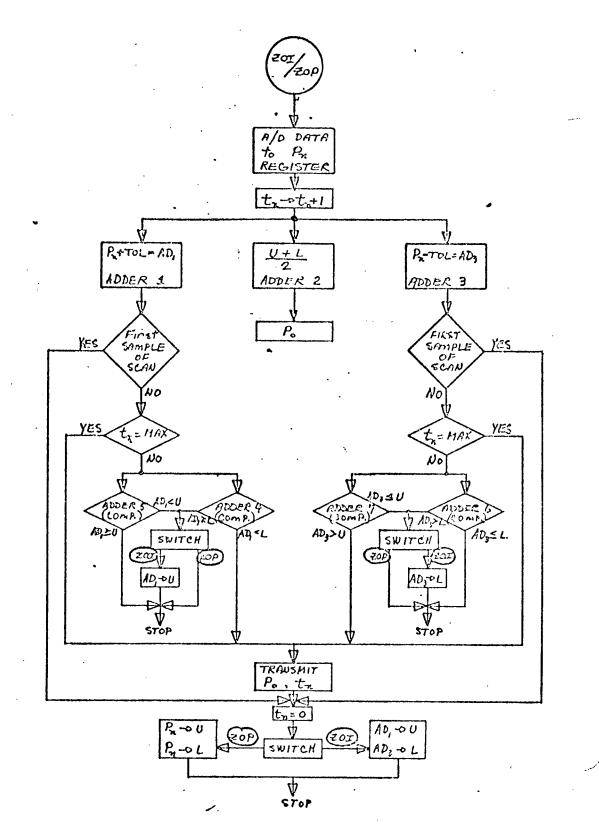

Both reduction algorithms require arithmetic operations and various storage elements to perform a reduction operation. Due to the high speed required (9 MHz sample rate) it was necessary to limit a reduction operation to an arithmetic operation (add or subtract) followed by a comparison. The reducer is therefore constructed to perform these operations in such a manner that both reduction techniques use the same circuitry and associated storage elements with only minor changes in register gating (ZOP - ZOI switch in Figure A2-2.5-1) required to differentiate between ZOI and ZOP modes.

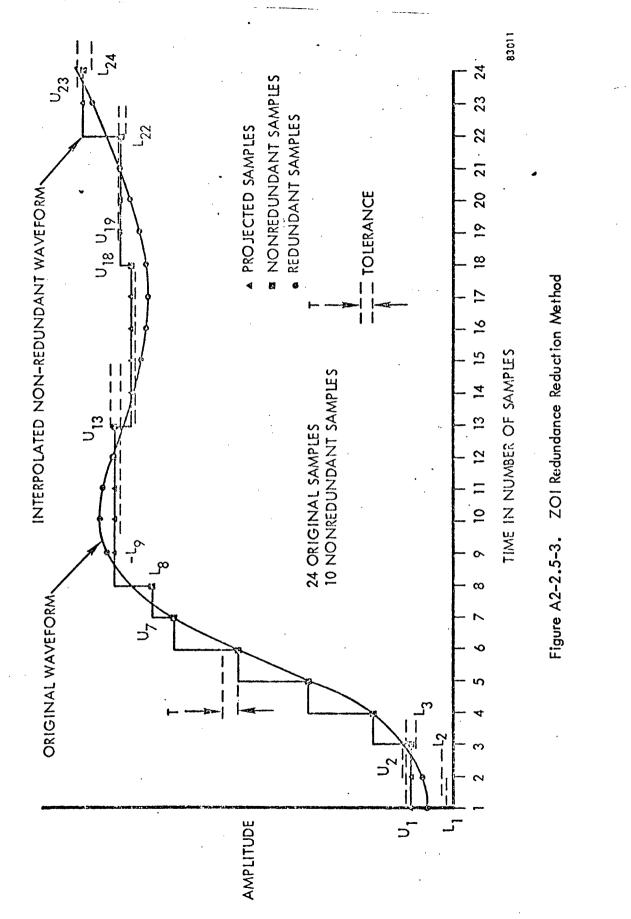

In the ZOI Mode, reducer logic operation satisfies the criteria for redundancy removal shown in Figure A2-2.5-2, a flow diagram of ZOI/ZOP operation, and Figure A2-2.5-3, an illustration of ZOI reduction and reconstruction. ZOI operation is accomplished in Figure A2-2.5.1 when the ZOI/ZOP switch is in the ZOI state. This allows  $AD_1$  to be gated to U when necessary and AD3 to be gated to L when necessary. As shown, the occurrence of a nonredundant sample requires that a new tolerance corridor be established by drawing horizontal lines (U and L) through the limits of the tolerance range placed around the nonredundant sample. This is accomplished by gating AD1 into U and AD3 into L after a nonredundant sample is chosen. If a tolerance range (AD1 and AD3) corridor placed around a subsequent sample  $(P_n)$  overlaps the previous corridor (comparisons made in adders 4-7),  $P_n$  is considered redundant and is discarded and  $t_n$ (the time tag) is incremented by one in preparation for the next sample check. Each successive redundant sample modifies the corridor extended to the next sample. The new corridor consists of that part of the previous corridor which is overlapped by the tolerance range placed about the redundant sample. In other words, the upper range, either AD1 or U, and the lower range, either AD3 or L, forming the most restrictive corridor are saved. If the tolerance range placed about a subsequent sample does not overlap the corridor extended to the sample, this sample is considered nonredundant, and the mid-point of the previous corridor, (U+L)/2, is transmitted along with a time tag  $t_n$  showing the number of times (U+L)/2 must be repeated in the reconstructor. If no nonredundant sample occurs for 14 sample periods (4 bit time), 30 sample periods (5 bit time), or 62 sample periods (6 bit time), the present sample being checked is considered nonredundant.

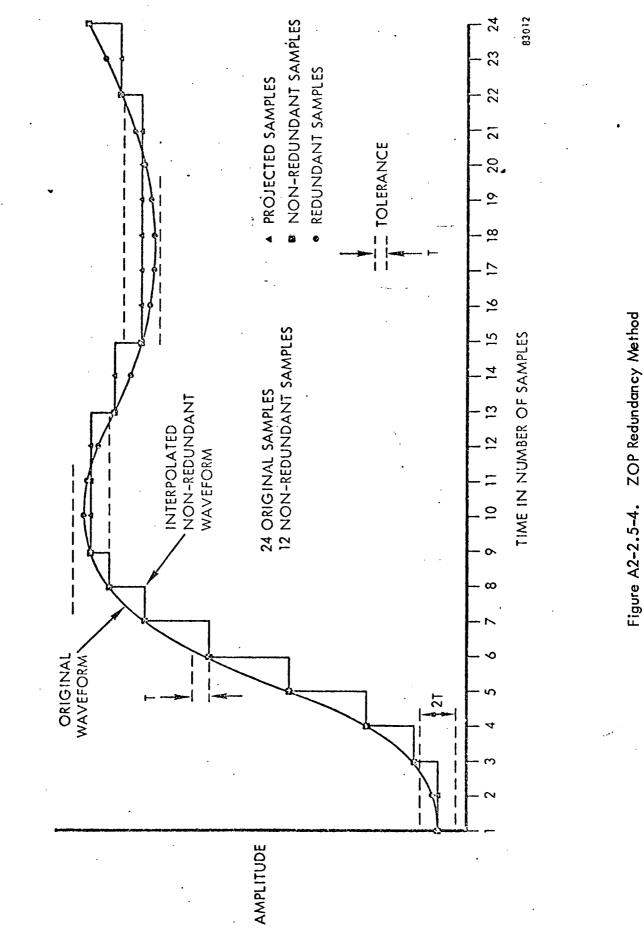

In the ZOP mode, reducer operation satisfies the redundancy removal criteria shown in Figure A2-2.5-2 with the ZOI/ZOP switches in the ZOP state, and Figure A2-2.5-4, an illustration of ZOP reduction and reconstruction. The basic ZOP operation sets tolerance ranges about a nonredundant sample and then checks successive samples to determine if they are within the corridor formed by the ranges mentioned above. When a sample falls outside this corridor it

ø

Figure A2-2.5-2. Reducer Flow Diagram

is considered nonredundant and the previous nonredundant sample that formed the corridor is transmitted along with the time tag. ZOP operation in the test set accomplishes the same result but in a different manner. In order to simplify sequencing and control, ZOP reduction occurs by performing exactly the same operations as in ZO1 except  $P_n$  instead of AD1 and AD3 will be gated into both U and L after every nonredundant sample decision (see Figures. A2-2.5-1 and A2-2.5-2 with the ZO1/ZOP switch in the ZOP state). A tolerance range is placed around successive samples (AD1 and AD3) forming a corridor which is compared to the previous corridor formed by U and L, where both are equal to the starting nonredundant sample. This check is identical to placing the tolerance range about the starting sample.  $P_n$  is considered redundant if the corridors overlap (U and L inside the new corridor), but U and L are not updated by AD1 and AD3 due to the gating of the ZO1/ZOP switch. If the AD1 and AD3 corridor does not overlap the U-L corridor ( $P_0$ ),  $P_n$  is considered nonredundant, and the previous nonredundant sample (U+L)/2 is transmitted along with a time tag showing the number of times it should be repeated in the reconstructor. The sample size-time size choice is identical to ZO1 operation.

c

During TV blanking, when sync information is present in the TV signal, the reducer receives a blanking signal from the sync separator causing the present reduction process to be completed by forcing P<sub>n</sub> to be nonredundant and then suspending reducer operation until the blanking pulse is removed. During blanking the only data placed in the transmitter buffer is a special sync code which tells the reconstructor what type of TV sync should occur (horizontal or vertical) at that point in the signal and a buffer sync word which is not presently used. The particular sync word is determined by the type of blanking that is present. When the transmitter buffer is ready to accept data it signals the reducer to insert the proper TV sync word and operates the loading process with its own clock. After TV sync loading is completed the buffer sync word is loaded into memory. The words for horizontal and vertical sync information are made up of a 6 bit zero "time tag" to distinguish them from TV video data and a 4 bit amplitude. This format makes the sync words independent of sample-time word size.

Buffer underflow during TV data processing results in a signal being sent to the reducer forcing it to consider the present sample being processed as nonredundant and inserting it into the buffer. A special operation mode occurs at the resumption of reducer operation after blanking. In order to eliminate the transmission of incorrect data at the beginning of each active TV scan a flip-flop is used to detect the first sample of a TV scan. The normal reducer operation will be bypassed and the U and L registers will be set up with the proper data depending on the reducer mode. Subsequent samples will be processed in the normal manner.

#### A2-2.6 Statistical Encoder – A3A5

The Statistical Encoder/Decoder system transmits information dependent upon the statistical nature of the sequential data words and the rate of channel activity (encoder memory usage).

Basically the Encoder generates code words that indicate the value difference (delta) in subsequent data words. These codes are chosen to reduce the total amount of data bits transferred across the PCM link. A

The data to be encoded is a six bit binary word equal to the intensity of the TV picture at a point in time. The data is positive true with zero data indicating black.

Sample Rate and Data Rate are selected at the front panel and are chosen dependent upon the picture complexity so that the Transmitter memory does not overflow and for the desired picture quality as determined by Sample Rate.

To maintain a constant serial data flow, automatic quantization varies the rate of memory fill by adjusting the number of significant data bits within a range of 4 to 6 bits. These quantization levels, referred to as QL, are automatic submodes and will be detailed in the block diagram description.

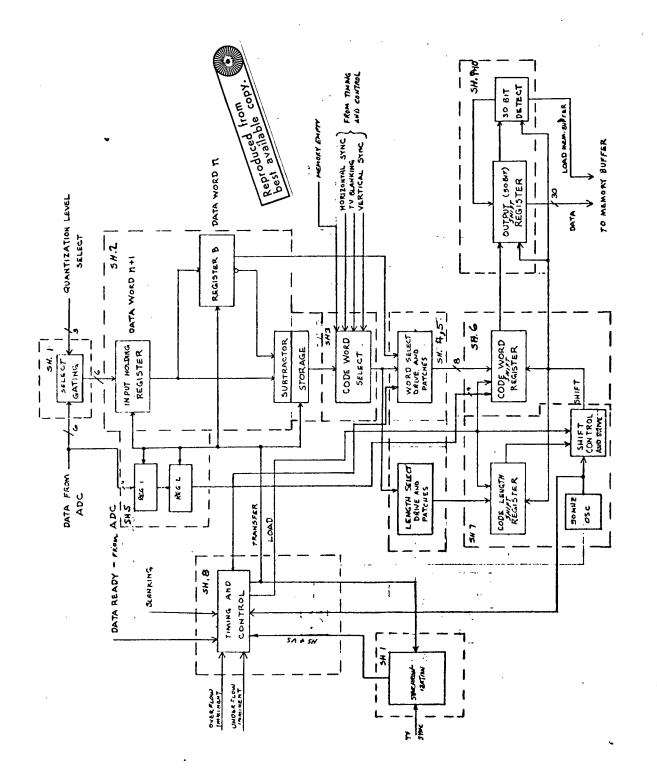

The following detailed description of the Statistical Encoder is referenced to the Encoder Block Diagram (Figure A2–2.6–1) and to the Logic Diagrams 531022 and 531023.

Video data from the A/D is provided to the Encoder in the form of a six bit binary data word each Sample Rate time. This video data word is adjusted for quantization at the Select Gate. Quantization Level (QL) 6 enables all 6 bits. QL5 shift selects the 5 MSB bits down one bit to the 5 LSB outputs and provides a filler '1' bit in location 6. QL4 shift selects the 4 MSB bits down 2 bits and provides '1' filler bits in locations 5 and 6. This shifting of data will reduce the number of video levels transmitted but maintains the more significant picture data. An opposite QL operation in the Statistical Decoder restores the proper bit location.

The Input Holding Register and Register B hold two subsequent data words which shift at Transfer time. The data in these two registers is subtracted from one another with the resultant answer as the difference or Delta of the two words. This Delta is updated each Sample time. The Delta is stored as a six bit word and sign, which is presented to the Code Word Select generator.

The Code Word selector compares the Delta word and selects the next code to be generated. The various codes available are:

Delta0provides no change in informationDelta +1provides increase of 1 bitDelta +2provides increase of 2 bitsDelta +3provides increase of 3 bitsDelta -1provides decrease of 1 bitDelta -2provides decrease of 2 bitsDelta -3provides decrease of 3 bits

Remainder transmits four MSB bits as new data.

Figure A2-2.6-1. Statistical Encoder Block Diagram

¢

The Word Selector is inhibited during TV Sync and Blanking time and is controlled to some extent when the memory is nearly empty by forcing all Remainder codes during this time, which provides the maximum memory fill rate. ø

The output of the Code Word Selector is buffered and provided to the Word and Length Patch Selectors. The code word and its bit length is variable by means of plug-in patch modules. Only one code type is active at any one time and is patched to the Code Length and Code Word Registers. These registers are enabled each Transfer time.

The Code Length register operates directly with the Shift Control to produce a discrete amount of clock pulses after each Transfer time. Each Sample Rate produces a Transfer pulse which in turn enables a Load pulse which initiates the Code Generation sequence. The Load pulse loads the current code word information into the Code Length shift register. This code word information is a single '1' bit placed into one of eight stages. All other stages are cleared. The Load pulse also sets the Start flip-flop and inhibits the 50 MHz Clock until the trailing end of the Load pulse. At the end of the Load pulse the clock is released to shift the register until the '1' bit reaches the start flip-flop to turn off the clock. This permits generation of one to eight clock pulses depending on the Code Word length.

The Shift Control also contains buffer drivers to provide clocks to the Code Word and Output Registers.

The Code Word register is loaded at the same time as the Code Length register but with data information instead of length information. This data is programmable by means of plug-in patch modules or may be actual data in the case of Remainder or Absolute Value code words. The Code Word register is shifted from the Shift Control clock to produce a code data word each Sample Rate.

The Output Shift Register accumulates Data Code Words from the Code Word Register until it has thirty bits of data. At this time, it parallel transfers the thirty bit word into a memory buffer register. The Output Shift register is shifted from the Shift Control clock which is a burst of one to eight clock pulses at a 50 MHz rate.

Parallel transfer of the 30 bit word is accomplished by setting bit 0 of the register to a 'l' bit. When this tag bit arrives at the end of the register, it creates a "Load Memory Buffer" pulse to the Memory Interface Buffer. This Load Buffer pulse also clears the Output Shift register and sets the tag bit 0 for the next 30 bit word.

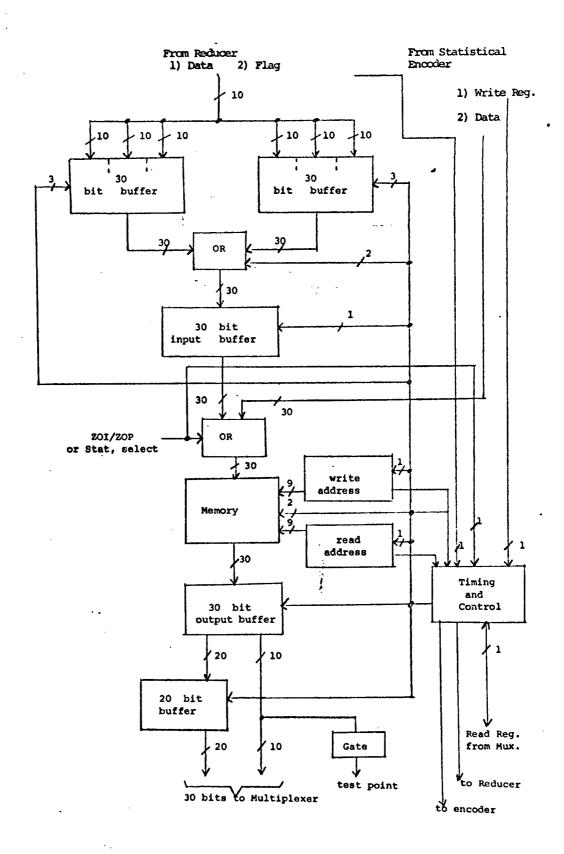

The Memory Interface Buffer (see Figure A2-2.6-2) receives the 30 bit word and sets the Load 30 flip-flop to request a memory Write access of the Memory Control Circuitry. The Memory Interface Buffer provides statistical data to the Data Select gates of the Memory Interface. The other input is ZOP/I data and is selected by a front panel mode select switch. Buffer Drivers are used to interface the 30 bit data word with the memory input.

Figure A2.2.6-2. Statistical Encoder Rate Buffer Block Diagram

ø

TV Sync signals are provided from the Transmitter Timing and are synchronized to the Encoder Timing using the Transfer rate signal.

At sample rates of 1, 2, 3 and 4 MHz, Encoder Timing is controlled by Sample Rate which is synchronized to the 50 MHz oscillator and creates a 'Ready Load' and a 'Transfer' timing pulses using a Shift Register. At 5 MHz Sample Rate, to avoid synchronization problems, the sample rate is generated by dividing the 50 MHz oscillator by 10, and routing this 5 MHz to the sample rate circuitry for use in the Statistical Mode only.

TV Synchronization begins at the start of the Vertical Blanking time. The TV Sync signals received are Vertical and Horizontal Blanking signals. These blanking signals are used to inhibit the generation of code data words for the duration of Blanking.

At the end of Vertical Blanking, the Timing and Control section starts a shift register at Transfer rate. This shift register controls the generation of four code words used to control the Decoder start time. The first word is a 30 bit Time Code Word generated in four segments. This code is a fixed pattern of

#### 0000010000001000000100000001

The next three code words are eight bits each and are the Vertical Sync code, Buffer Word and the Absolute Value word.

The Vertical Sync code is used by the Decoder to start the decoding process. The Buffer word is a spare 8-bit word of all zeros. The Absolute Value word is comprised of two bits of Quantization Level information indicating level 4, 5, 6 to be used for the current horizontal line only. The remaining six bits are a real data value used by the Decoder as a video level starting point.

Horizontal Synchronization occurs at the end of Horizontal Blanking and generates three 8-bit code words which are the Horizontal Sync code, Buffer word, and Absolute Value word identical to those of the Vertical Sync time with the exception of the bit code of the Horizontal Sync word.

The Operation of the Timing and Control is as follows: The T & C receives four timing signals, 1) A 50 MHz clock, 1) Sample Rate, 3) Horizontal Sync (blanking), 4) Vertical Sync (blanking).

As each Sample Rate is received, it is synchronized to the 50 MHz internal clock and placed in a shift register to generate two timing pulses, the Ready Load and the Transfer. The Ready Load is used to setup and strobe the T & C logic and to generate the Load Command to the code generator. The Transfer pulse occurs immediately after the Ready Load and causes the transfer of data in the various parallel registers to update for the next sample rate time. These two pulses operate continuously at the Sample Rate. Vertical and Horizontal Sync signals inhibit the generation of code words for the duration of either signal (that is, the blanking time). This is accomplished by a second shift register which synchronously inhibits Load pulses following the first Load pulse after the start of blanking. Upon the end of blanking, either Horizontal or Vertical, the Load pulses are enabled to start the next video line. The first words of the Video line are the Time Word and sync words in the case of Vertical sync or just the three sync words in the case of Horizontal sync. The remainder of the line generates a code data word for each sample rate until blanking occurs.

õ

Automatic Quantization avoids uncontrolled overflow or underflow of the Transmitter Buffer. Since the Code Word is variable length, one bit to eight bits, the 30 bit word rate out of the Encoder to the buffer varies. The average input and output of the buffer must be equal and therefore it is necessary to provide feedback control of the encoder.

The Quantization is controlled by the Rate Buffer and is readjusted each Horizontal Word time. The Buffer fill rate is determined by an Up/Down Counter which contains the current fill rate at the end of each Horizontal line. This rate may be positive or negative since the counter is preset to 128. The resultant count is compared to two fixed numbers each of which may be one of two values selected by the Memory fill function.

The two numbers are compared against the Rate Buffer counter and fixes the QL of the next line at one of three values depending whether the rate is positive, negative, or average. The three QL values are 4, 5, and 6. The Video resolution is reduced from 6 to 5 or 4 bits as the QL goes to 5 or 4. A low rate selects QL6, an average rate selects QL5, and a high positive rate selects QL4 to reduce the rate of Buffer fill.

Once the Quantization level has been selected for the next horizontal line, the QL shifts the input Video data down zero, one, or two bits creating a six, five, or four bit resolution. The lower the resolution, the fewer large picture value changes take place and more 'no change' or one to three bit changes occur. This transfers the work load from 8-bit Remainder codes to one-bit Delta zero and three-bit Delta one codes which cause a lower fill rate.

The shifting of the Video data words to 5 or 4 bits is compensated for in the Decoder by storing the current QL value of the Absolute Value word and reverse shifting the reconstructed Video data word to produce a six-bit output of the Decoder.

The Transmitter Buffer memory has a buffer empty signal (four words left) which forces the Code Word Selector to produce a series of eight-bit Remainder code words to generate a positive fill function to keep the memory from becoming empty. This may happen at any time during the code generation time.

#### A2-2.7 Transmit Rate Buffer Subsystem - A3A1A4

#### A2-2.7.1 Rate Buffer

The transmit rate buffer accepts data from the data compressor or statistical encoder, assembles it into 30-bit words, and writes the assembled word into memory. It reads 30-bit words and sends them to the multiplexer when required. The buffer subsystem also formats the input TV and buffer synchronization words and calculates the buffer sync word. Blanking fill words are inserted into the multiplexer when required.

-----

۵

#### A2-2.7.2 Detail Operation

The Transmitter Rate Buffer is a 512-word, 30-bit per word high speed memory. This buffer is based on analysis which shows that a larger buffer does not improve system performance.

TV video has active periods of a specific time duration (active portion of a line) and completely inactive periods also with a specific time duration (blanking). During active periods, data is going into and out of the buffer; thus, buffer fill may increase or decrease. Since only buffer output occurs during blanking, buffer fill will decrease at a rate determined by the transmission rate while horizontal or vertical blanking occurs. Due to the distributed nature of horizontal blanking in a field, buffer fill during a field will roughly resemble a sawtooth waveform at line rate, superimposed on a larger sawtooth at field rate.

TV frame activity changes slowly enough that a sequence of many fields will have approximately equal activity. If significant increase in buffer fill occurs over a complete field (including blanking), any feasible size buffer would overflow before the activity could be expected to decrease. For example, assume that data activity does not change significantly over 100 fields (about 1.7 seconds); the net buffer fill per field can only be 1/100 of the total buffer size. Even for a 3,000-word buffer, this is only 30 words per field. At a transmission rate of 9 megabits there are 15,000 10-bit words per field (9 x 10<sup>6</sup> bits/sec x 1/60 sec/field/10 bits/ word). Thus, the extra 30 words per field are a small fraction (0.2 percent) of the total words, and would not significantly improve the picture. Therefore, the buffer may as well be sized so that it can be emptied during vertical blanking. For a vertical blanking time of 1250 µsec and a maximum transmission rate of 9 x 10<sup>6</sup> bits/sec or 0.9 x 10<sup>6</sup> words/sec, the maximum buffer size required in the DC/EC Test System is 1250 (0.9 x 10<sup>6</sup>) = 1125 words. The buffer size provided is 512(3) = 1536 words. Lower transmission rates have a smaller buffer requirement.

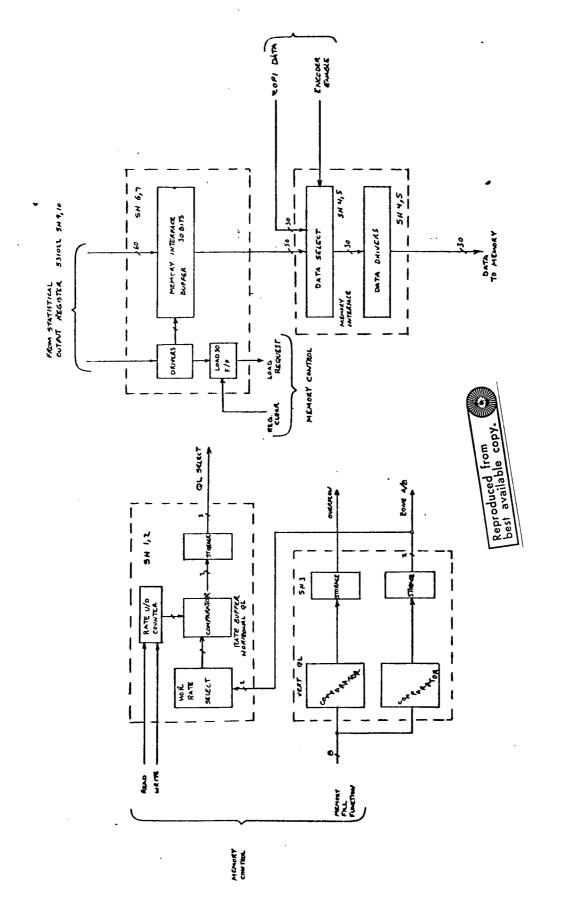

The transmit rate buffer consists of the random access memory and the buffer control logic shown in Figure A2-2.7.2.

The transmit buffer has two sources of input data. Consider first the reception of data from the Reducer. The 10 data lines from that source are updated each sample time. When the data present represents a nonredundant sample, a signal (Flag XX) is sent to the timing and

P

Figure A2-2.7.2. Transmitter Rate Buffer Block Diagram

control (T&C); there it is gated to one of six 10-bit sections in two 30-bit buffers and causes the selected section to accept the data. The same signal then updates a Mod-6 counter in the T&C and qualifies the selection of the next 10-bit section.

The Mod-6 counter is decoded so that when one of the 30-bit buffers is filled, a write request is generated. Coincidentally, unless a prior request is still pending, the data in the filled 30-bit buffer is transferred to the 30-bit input buffer. Under worst-case conditions, 4 of the 6 available 10-bit sections will be filled before a transfer can be made to the 30-bit input buffer. This happens when:

- 1. The reducer finds nonredundant samples in 8 adjacent sample periods, and

- 2. The sample rate is 9 MHz, and

- 3. The write request decoded from the Mod-6 counter occurs at the beginning of a memory read cycle.

Data from the 30-bit input buffer is routed to the statistical decoder logic where it is qualified by a mode selection switch before being gated to the memory.

When the T&C recognizes the write request, the mode line to the memory is set low and a cycle initiate command (MRQ) issued. (Requests for memory service are handled on a priority basis so that if read and write requests occur coincidentally, the write request will be serviced first.) Once the write cycle is completed, the T&C increments the write address counter by 1 count.

If the Statistical Encoder unit is selected, operation is as follows. 30 bits of data are supplied to the memory inputs through a set of gates. Write requests decoded from the Mod-6 counter are inhibited and in their place write requests from the encoder are serviced. Thirty bits from the encoder require more than 3 sample periods to accumulate and the highest encoder sample rate is 5 MHz; so, input buffering at the transmit buffer is unnecessary.

Output service can now be considered. Data readout of the memory is in response to link demands. 30 bits are made available to the demultiplexer (demux). When the first 10 of these are accepted from the 30-bit output buffer, the remaining 20 to be used are transferred from the output buffer to the 20-bit buffer.

The demux signals its acceptance of the first 10 bits when it sends a read request (TV3) to the T&C. While the demux uses the remaining 20 bits, the T&C services the request and loads a new 30-bit word into the output buffer. When the read cycle finishes, the read address counter is incremented by 1 count.

Bits 1 through 10 of the output buffer are decoded in an "and" gate to provide a test point. In the ZOI/ZOP mode the point should sense vertical sync.

Next, consider generation of special words such as buffer sync and TV sync. At the beginning of a horizontal line blanking period, the T&C will command the reducer to output

a horizontal sync word. If one of the two sections of a 30-bit buffer are filled with samples, the T&C will enter a TV sync word in each remaining section and store the data. In the next 30-bit buffer's first two sections, the T&C will enter a TV sync word and then a buffer sync word. This format was selected so that each TV line is represented by some whole number of memory words, and so that the buffer sync word is always located in the middle slot next to a TV sync word. The buffer synchronization scheme utilized in the Receiver buffer does not require this formatting procedure, but no attempt was made to remove the generating logic from the transmit buffer. Ô

The buffer sync word, used in the statistical encoder, is calculated by subtracting the address difference (write-read), from the maximum buffer size selected.

At vertical blanking time the same sequence is used as at horizontal blanking time. The important difference, however, is that the sequence is started at about 1 µsec before the end of vertical blanking.

Fill words are generated when the memory is empty and TV blanking time is occurring. Generation is carried out in two ways. When the ZOI/ZOP mode is used, the T&C commands the reducer to generate fillwords. These are then passed through memory in the normal manner. In the statistical encoder mode, the T&C answers demux requests by loading fillwords directly in the 30-bit output register.

#### A2-2.8 Rate Adaptive Tolerance Generator - A3A1A1

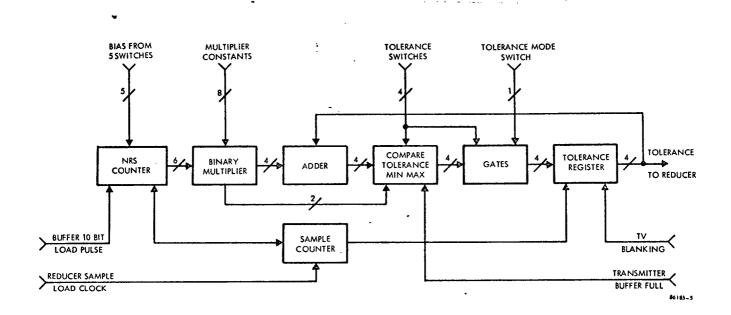

The tolerance generator produces a 4-bit tolerance that is a function of the actual buffer fill rate and the desired fill rate. A minimum tolerance is switch selectable along with the desired buffer fill rate. A fixed tolerance mode is provided that outputs a switch selectable fixed tolerance to the data compressor.

#### A2-2.8.1 Detailed Description

The tolerance generator makes use of the average rate of buffer fill in determining tolerance. This provides feedback to the data compressor as a control on buffer fill. This control is accomplished by increasing tolerance when the buffer fill rate increases and decreasing tolerance as fill rate decreases. This control makes use of the general rule that increasing tolerance decreases the average rate of occurrence of nonredundant samples thus decreasing buffer fill rate. Figure A2-2.8.1 is a block diagram of the tolerance generator.

Two counters are used to determine the average rate of buffer fill, to compare this rate to a desired fill rate, and to generate an error signal which is used to modify tolerance. One counter, the NRS counter, starts from a preset negative bias obtained from 5 bias switches, and counts the 10-bit words that are loaded into the transmitter buffer. The other 5-bit counter counts the samples that are loaded into the data compressor. Every 32 input samples this last counter interrogates the NRS counter and presets it to the selected bias and another counting cycle begins. The value of the NRS counter when sampled is equal to the difference between

A

Figure A2-2.8.1. Tolerance Generator Block Diagram

the desired number of nonredundant samples (represented by the bias) and the actual number of nonredundant samples that have occurred during 32 input sample times. In other words, the counter sample is a measure of the difference between actual and desired buffer fill rates and is a suitable error signal for the buffer fill rate control loop. The desired buffer fill rate can be shown to be a function of the transmitted information rate and the input sample rate. The bias is thus programmed as a function of these two parameters. ø

The NRS counter value observed at the end of each 32 sample period is processed by a binary multiplier. The switch selectable multiplication factors are 4, 2, 1, 1/2, and 1/4 and may be selected independently for positive and negative NRS counter results. The resulting number is used as a tolerance modifier ( $\Delta TOL$ ).  $\Delta TOL$  is the error signal of the control loop. If it is positive, the actual buffer fill rate is greater than the desired fill rate, and tolerance is increased in an attempt to reduce the actual fill rate. Tolerance reduction results when the actual fill rate is less than the desired value. This is accomplished by adding  $\Delta TOL$  to the previous tolerance which is stored in the 4-bit tolerance register.

The new tolerance is now compared with the minimum and maximum tolerance values. Maximum tolerance is 15 due to 4-bit tolerance. Minimum tolerance, which is required due to noise on the input A/D signal, is determined by 4 tolerance switches. When the transmitter buffer fills up, the nonredundant sample rate changes to the transmitted 10-bit word rate. Since this rate may force the tolerance generator to reduce tolerance at a time when tolerance should be large, the buffer full signal from the transmitter buffer is used to force tolerance to its maximum value.

The 4 tolerance switches mentioned above are used to set fixed tolerance when the tolerance generator is in the fixed tolerance mode. In this mode rate adaptive tolerance continues to be generated, but the tolerance switch values are gated into the tolerance register instead of the adaptive tolerance.

#### A2-2.9 Voice Encoder - A3A3A4

The Voice Encoder digitizes an audio signal to a 20 K bit data stream. Analog amplitude compression is available at the voice encoder input. The digitizing technique is high information or variable slope delta modulation, a method which has been demonstrated to be somewhat superior to other digitizing methods at low bit rates.

The voice compressor consists of an operational amplifier with a diode break type nonlinear feedback circuit. When the voice input is 50 mV, the current in the feedback network is low, and all the diodes are reverse biased. Thus, the equivalent feedback resistance is about 32 K ohms, giving a small signal gain of 30 dB. As the input voltage increases to a maximum of 5 V (60 dB over 50 mV) the diodes successively turn on, giving a small signal gain of 0 dB at 5 V input. Thus, the output range is 30 dB for a 60 dB input range, giving a compression ratio of 2:1. The voice compressor may be bypassed. In the bypass mode, the audio input signal must be less than 5 V peak-to-peak maximum. The Voice Encoder (Drawing 528729) contains a voice compressor, which compresses the normal 60 dB voice range into 30 dB, and a high information delta modulator, which encodes the voice output into a digital data stream. Input impedance may be selected to be 600 or 50 ohms. ය

The high information delta modulator has a modulator and a demodulator. The modulator encodes the voice information from the compressor into a serial data stream. The demodulator generates a feedback signal which is used as an error indication in the modulator.

The audio is fed to one input of a comparator, and the demodulated signal from the demodulator is fed to the other input. The comparator operates a transistor driver stage, and is powered by  $\pm 15$  volts power regulated to  $\pm 12$  and -6 volts by zener diodes. When the incoming voice signal is larger than the feedback signal, the transistor is switched on and the comparator output is a logic zero. When the voice input is smaller than the demodulated feedback signal, a one is generated.

The comparator output is sampled at a 20 kHz rate on the clock high going transition by a D flip-flop. The flip-flop output drives the input of a 2-bit shift register. Decoding circuitry on the outputs of this shift register operates commands to a 4-bit shift left/shift right (SLSR) register in accordance with the following table.

#### A follows B follows C

| A≠B≠C          | Shift Left  |

|----------------|-------------|

| $A \neq B = C$ | Shift Left  |

| $A = B \neq C$ | Hold        |

| A = B = C      | Shift Right |

The low going transition of the clock strobes the shift left, shift right, and hold commands into two flip-flops. One of these controls the "mode" input of the SLSR, which determines the shift direction. The other flip-flop disables the clock to the SLSR for one bit period when a hold command is present at its input.

The SLSR shifts ones in from the left and zeroes in from the right. Four "exclusive-OR" gates on the SLSR outputs compare the outputs with the comparator output to generate a 5-bit ones complement output code. The "exclusive-OR" gates and comparator output operate transistor drivers. The comparator output, which is used as the sign bit, is buffered for the modulated voice output.

The outputs of the transistor drivers go to a resistor network at the input of the demodulator. The demodulator consists of an op amp integrator. The input network is designed so that when the SLSR shifts right the output slope of the integrator is doubled. When the SLSR shifts left the slope is halved. When the SLSR state is all zeroes, the normalized slope of the

integrator is +1 when the sign bit is a one, and -1 when the sign bit is a zero. Thus, as the SLSR shifts right, slopes achieved will be 1, 2, 4, 8 and 16.

a

From the table, it is seen that if the previous three bits were identical, indicating a large error between the voice signal and the demodulator output, the SLSR shifts right and the demodulator slope is doubled to help the demodulator "catch up" to the voice input. If the demodulator "catches up" at a time when its slope is large, the sign bit changes, resulting in a polarity reversal of the demodulator slope, and the slope is halved. For step inputs this results in an underdamped characteristic, but for most audio signals, reproduction will be better than with other voice encoding methods.

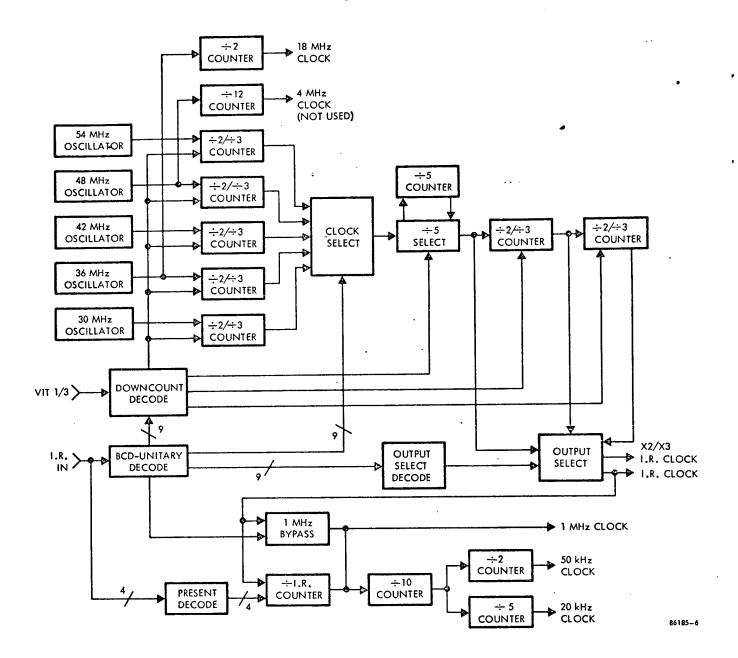

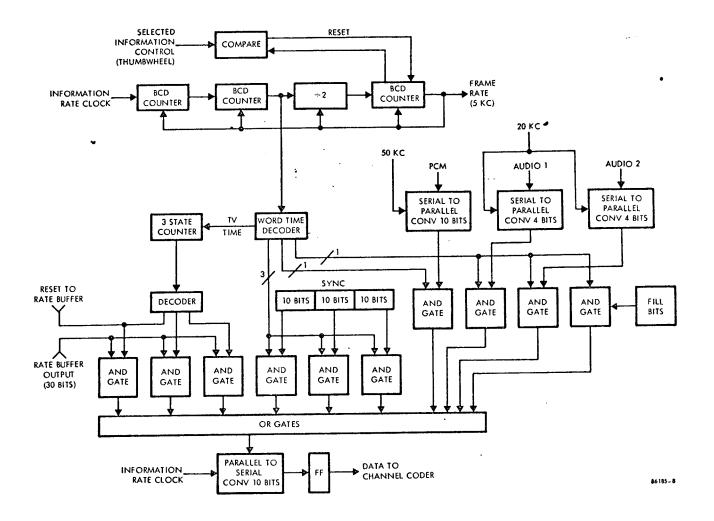

# A2-2.10 Information Rate Timing – A3A2A6

The transmitter information rate timing circuit (Figure A2-2.10) generates clock signals at frequencies of 1 through 9 MHz variable in steps of 1 MHz. Depending upon the coding technique used, a clock (bit rate) of either two times or three times the information rate, synchronous with the information rate, is also generated. Other clocks that are generated for use elsewhere in the system are at frequencies of 18 MHz, 1 MHz, 50 kHz, and 20 kHz. The 18 MHz clock is used in the transmitter rate buffer. The 1 MHz clock is used as a reference to generate the sample rate clock and the coherent 9 MHz for the TV Sync Separator. The 50 kHz clock is used in the multiplexer, while the 20 kHz clock is used by the voice encoders.

The transmitter information rate timing circuit has five digital clocks operating at frequencies of 30 MHz, 36 MHz, 42 MHz, 48 MHz, and 54 MHz. These clocks are divided down to the desired information rate, and two times or three times information rate frequencies by means of a programmable counter circuit and appropriate switching circuitry. The positions of the information rate code switches on the front panel are decoded to determine the mode of operation of the information rate to 1 MHz. Additional down counters reduce the 1 MHz signal to 50 kHz and 20 kHz clocks. An 18 MHz clock is produced by dividing the 36 MHz clock oscillator output by two.

The outputs of these clocks are buffered by high speed Shottky logic gates and go immediately into programmable divide-by-two or divide-by-three counters. The output of the divide-by-two/divide-by-three counter is at 1/3 the frequency of the input signal when the program line is a logic "1." The output is 1/2 the input frequency when the program line is a logic "0." The clock frequencies are thus immediately divided by either two or three to obtain frequencies which can be more easily handled by the clock switching circuitry. The switching circuitry consists of five Shottky gates with enabling lines and an 8-input high speed gate. The highest frequency that will be seen by the 8-input gate is 27 MHz. Folowing the clock switching circuitry is a programmable divide-by-5 gate which may be used to obtain some information rate frequencies. After the switchable divide-by-5 circuit, there are two more divide-by-two/divide-by-three circuits, whose outputs go to the switching circuit. It is at the

0

t

Figure A2-2.10. Transmitter Information Rate Timing Block Diagram

output of these switching circuits that the information rate and two or three times the information rate clocks are taken.

To illustrate the operations of the decoding circuitry and information rate down counters, let us assume it is desired to obtain a 3 MHz information rate with a code 1/3. The information rate switch on the front panel will be set to 3, and the code switch on the front panel will be set to Viterbi 1/3. The VIT 1/3 input of the transmitter information rate timing circuit will be a logic "O," and the IR 2 and IR 1 lines from the information rate switch will also be at ground. The BCD to decimal decoder in the decoding circuitry will interpret the BCD input from the information rate switch and its output in conjunction with the VIT 1/3 line will be decoded to enable the proper circuitry to obtain an information rate of 3 MHz. The clock signals will all be divided by 3. The 54 MHz clock will be selected so that the input to the rest of the down counting circuitry is at a frequency of 18 MHz. The divide-by-5 counter will not be used, and thus the signal will go to the second divide-by-two/divide-by-three counter stage. This counter stage will be set to divide-by-two to obtain a frequency of 9 MHz, and its output will be selected to be the times 3 information rate clock. The final divide-by-two/divide-bythree counter stage will be set to divide by three to obtain a 3 MHz signal. Its output will be selected to be the information rate clock. In a like manner, any other required combination of information rate and two or three times information rate can be generated from one of the clock oscillators.

An 18 MHz clock signal is generated for use in the transmitter rate buffer by dividing the output of the 36 MHz clock oscillator by two. This is done by a flip-flop.

To generate the one MHz clock the BCD input from the information rate switch on the front panel is applied to one set of inputs of a 4-bit adder. The other inputs are hardwired to a count of 10. Since the BCD input from the information rate switch is inverted, the output of the 4-bit adder will be 10 minus the information rate. This is applied to the data inputs of a 4-bit synchronous decade counter. The carry output of the counter is connected back to the load input by an inverter. Thus, when the counter reaches its full count, it will load 10 minus the information rate into the counter. Since the counter is run from the information rate signal, the signal at the carry output will be at a frequency equal to the information rate clock divided by the information rate, or one MHz. When the information rate is set to 1 MHz, the synchronous counter is disabled and the information rate is routed directly to the 1 MHz output.

To generate the 50 kHz and 20 kHz clock signals, the 1 MHz clock is first divided by 10 by a decade counter. This generates a 100 kHz clock which is divided by two to obtain the 50 kHz clock and by five to obtain the 20 kHz clock.

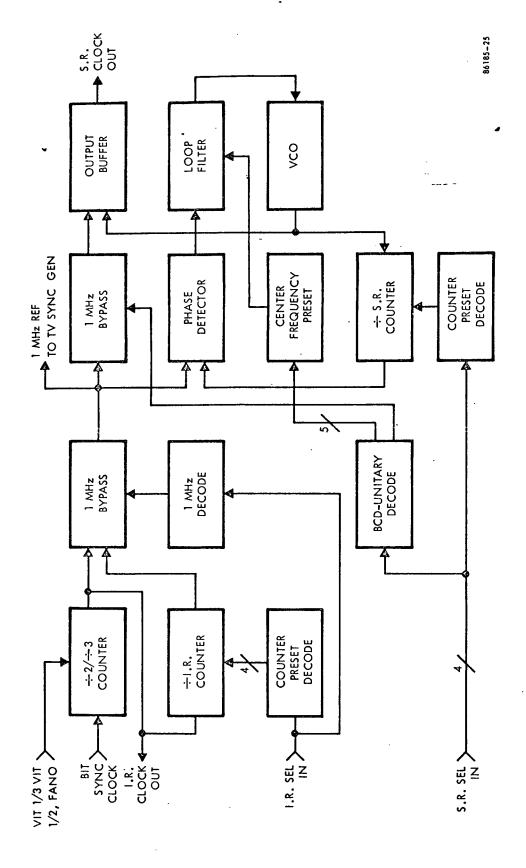

### A2-2.11 Sample Rate Clock - A3A2A6(A7)

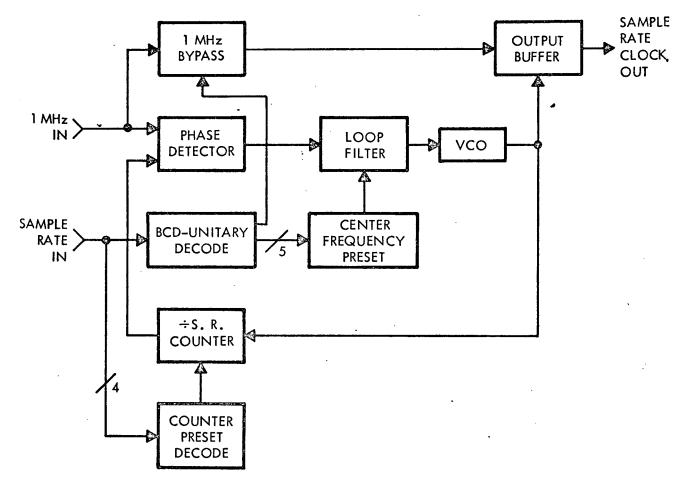

The transmitter sample rate circuitry (Figure A2-2.11) generates a programmable clock from 1 to 9 MHz phase locked with the information rate clock.

#### 86185-7

ø

To generate the programmable 1 to 9 MHz clock output, a phase-lock loop is employed which phase locks this clock output to the one MHz reference output of the information rate timing circuits. The center frequency of the phase-lock loop is selected by the sample rate selector switch on the front panel. a

The one MHz reference signal is applied to a phase detector and is compared with a one MHz feedback signal from the phase-lock loop. Phase lead, or lag, is detected and filtered by a loop filter. The output of the loop filter drives a voltage-controlled oscillator. For a sample rate of one MHz, the one MHz reference input is routed directly to the output.

The sample rate output frequency is divided down to one MHz by a presettable synchronous down counter, and this signal is applied to the phase detector to be compared with the reference input. The center frequency of the voltage-controlled oscillator is selected by varying the dc offset of the loop filter output. This is accomplished by means of five relays, each one of which switches a different offset voltage at the output of the loop filter. The relays are selected by a decoding circuit.

The synchronous upcounter is preset to a count which is equal to 10 minus the sample rate selected on the front panel switch. This number is derived by adding the inverse of the sample rate in BCD to a fixed count of 10. This is accomplished using a 4-bit binary full adder. The outputs of the binary full adder are applied to the data inputs of the synchronous upcounter. When the upcounter reaches a full count, its carry output is routed to its load input so that the number generated by the binary full adder is loaded into the counter on the next clock pulse. Thus, instead of starting at 0, the counter will start at a number which is equal to 10 minus the inverse of the sample rate. Thus, the frequency of the output of the synchronous upcounter will be equal to the sample rate clock divided by the sample rate, or one MHz.

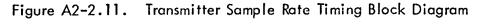

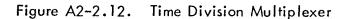

### A2-2.12 Time Division Multiplexer - A3A2A1

The function of the Time Division Multiplexer is to generate a serial stream of continuous bits in the proper format and at the selected rate to the Channel Encoder.

The data from the audio sources, the PCM source and the TV data from the Rate Buffer are time division multiplexed in a predetermined format sequence. A predetermined sequence of 30 bits for frame synchronization is generated at the beginning of each frame in order for the demultiplexer in the receiver to identify the start of each frame. The multiplexer (Figure A2-2.12) is designed such that the frame rate remains constant for different selections of information bit rate. If, for example, the information bit rate is changed from 4 MHz to 8 MHz, the number of bits in the frame are doubled such that the frame rate does not change.

# A2-2.12.1 Format

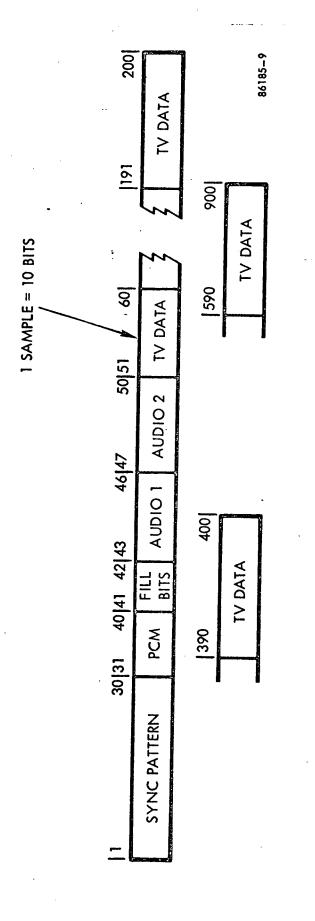

The format of the data frames is as follows (see Figure A2-2.12.1): The first 30 bits of the frame are devoted to the sync pattern. Bits 31 through 34 are for Audio 1 source.

۵

. مىر.

Figure A2-2.12.1. Time Division Multiplexer Format

•.

ര

Bits 35 through 38 for Audio 2 source. Bits 39 and 40 are fill bits. Bits 41 through 50 are for the PCM source The remaining bits (150) are for TV data. Each data sample and associated time tag occupies 10 bits. Thus, an information bit rate of 1 MHz has a frame length of 200 bits. If the information bit rate was 2 MHz, the frame length would increase to 400 bits. The first 50 bits of the frame would remain the same as the 200 frame length case, but 200 bits of TV data would be added to the frame length. This procedure continues and for the case of 9 MHz selected information rate, the frame length would be 1800 bits. Thus, the frame rate remains constant at 5 kHz for any selected bit rate. 0

# A2-2.12.2 Frame Rate Counter

The overall timing for the multiplexer is derived from the information rate clock and the selected information rate control. The information rate clock comes from the transmitter clock subsystem and covers a range from 1 MHz to 9 MHz in 1 MHz increments. The selected information rate control is four lines of BCD information from the front panel. Since the frame rate remains at a constant 5 kHz for any selected information rate, the selected control represents the multiple of 200 bits in a frame. The frame rate counter consists of 3 decade counters and a divide-by-2 counter. At the start of a frame the counters are reset and start from a count of zero. The counter is incremented by the information rate clock. The third decade counter is compared with the BCD number for the selected rate control and is allowed to increment until the count equals the BCD number from the selection rate control. Thus, the third decade counter is being reset at a rate equivalent to some multiple of 200 bits.

# A2-2.12.3 Data Source

There are four sources of data which comprise the Time Division Multiplex format:

#### a. Sync Pattern

The sync pattern 3564622552 (octal) is inserted in each frame of the format. These sync bits are hard-wired to the inputs of the multiplexing gates.

### b. Audio Channels

The multiplexer interfaces with two sources of 20 kHz digital audio data. A continuous 20 kHz clock is presented along with the audio data to the multiplexer. Since the frame rate is 5 kHz, four bits of audio data are generated from two channels during each frame. A four-bit serial-to-parallel converter is provided for each of the audio channels and the input data is shifted into these registers at the constant rate of 20 kHz.

### c. PCM Data

The multiplexer interfaces with a 50 kHz serial PCM channel. A continuous 50 kHz clock rate is also presented from the multiplexer to the external unit. The 50 kHz clock shifts the PCM data into a 10-bit serial-to-parallel converter, composed of 2 5-bit shift registers.

a

### d. Rate Buffer Output

The multiplexer interfaces with the 30 parallel data bits of the output of the rate buffer. The 30 bits are transferred into the multiplexer 10 parallel bits at a time. After the last 10 bits are transferred into the multiplexer, the multiplexer generates a reset pulse to the rate buffer which enables the rate buffer to access the next memory location and provides the next 30-bit word to the multiplexer.

# A2-2.12.4 Multiplexing Operation

A three-stage counter provides a 0-7 count to the 10 MSI multiplexers. These multiplexers decode the count and individually enable the data inputs. The counter is incremented every 10 bits by the output of the first BCD counter in the Frame Counter. At the start of the frame (with the 3-stage counter at zero) the first 10 bits of the sync pattern are transferred into the output register. A bit count of 9 is detected, disabling the serial operation of the output register and enabling the parallel input of the next 10 bits of the sync word. The serial data flow is uninterrupted due to the output flip-flop which holds the tenth bit during the load time. Continuing in this manner, the third set of 10 bits from the sync pattern is generated, followed by the PCM and audio data.

After the first 50 bits have been multiplexed, TV data will be inserted into the bit stream in 10-bit groups for the balance of the frame. This occurs on counts 5, 6 and 7 of the 3-stage counter. The counter will recirculate on these three counts until the end of the frame, at which time the state of the counter is stored in two D flip-flops. The 3-stage counter will be reset and the frame counter will start at zero, stepping the 3-stage counter every 10 bits as before. However, after the first 50 bits have been generated into the bit stream the 3-stage counter will step to the count it was in at the end of the previous frame, thus preventing loss of continuity in the TV data.

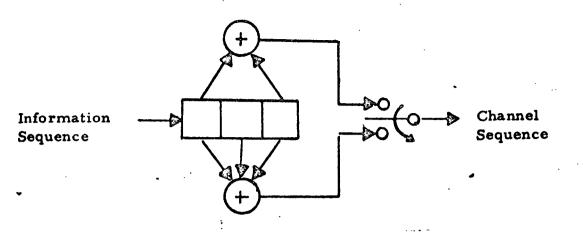

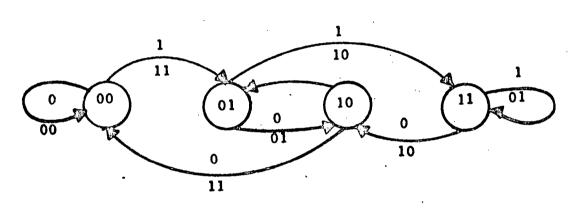

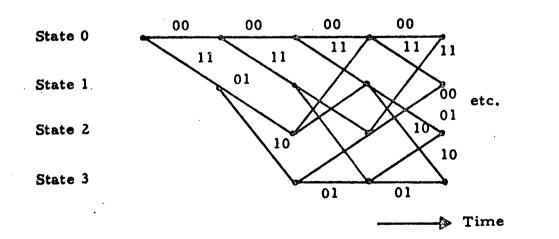

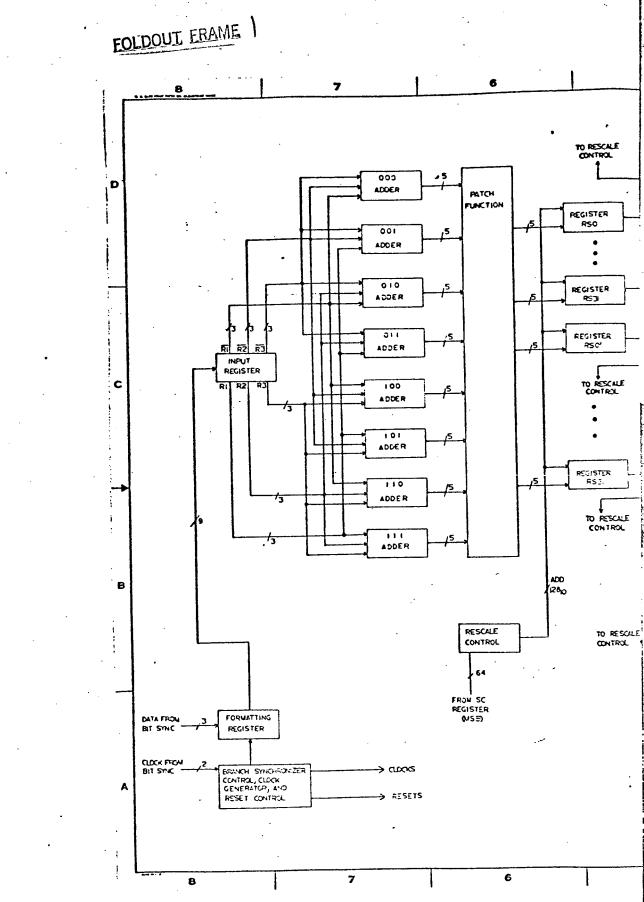

### A2-2.13 Convolution Encoder - A3A3A3

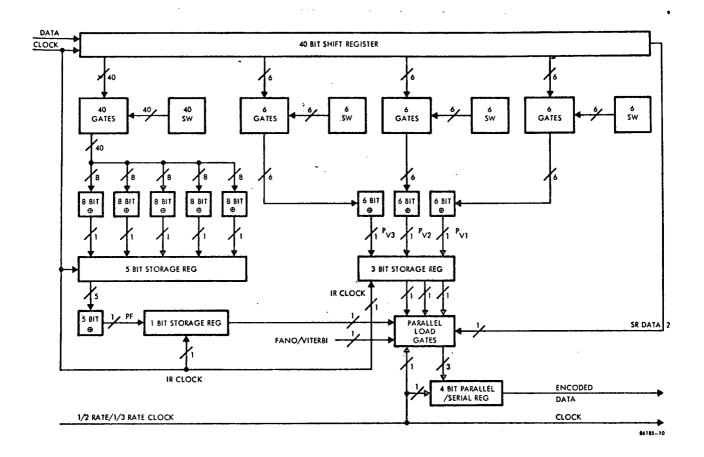

The functions of this unit are as follows:

- a. Accepts serial data and clock (to 9 MHz) from multiplexer.

- b. Accepts 1/2 rate or 1/3 rate clock from timing generator.

- c. Accepts Fano/Viterbi enable from control panel.

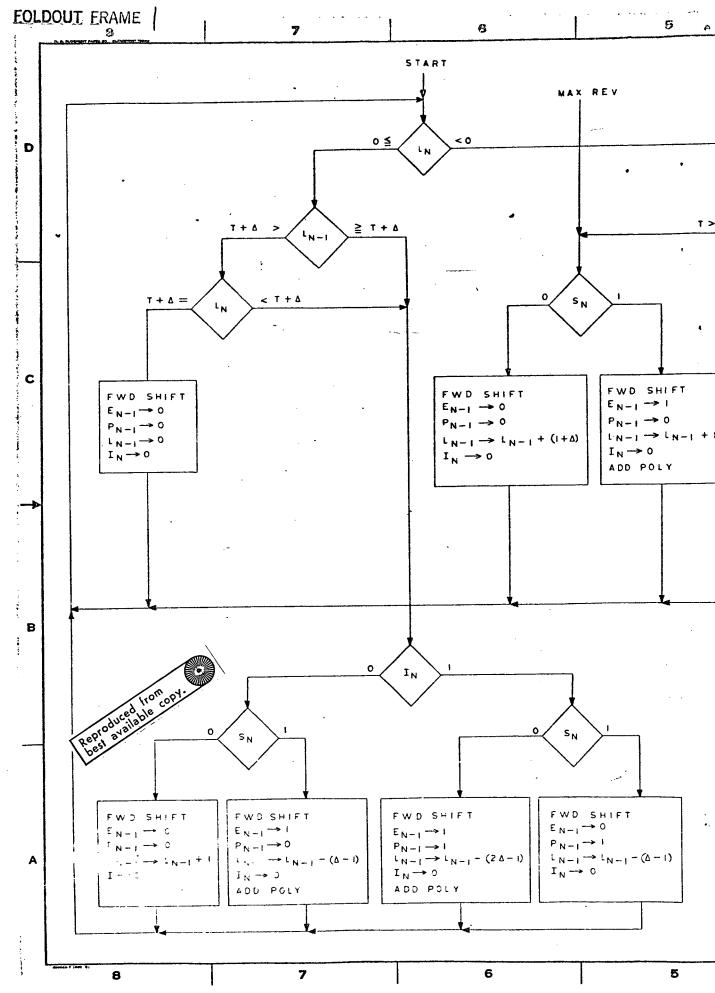

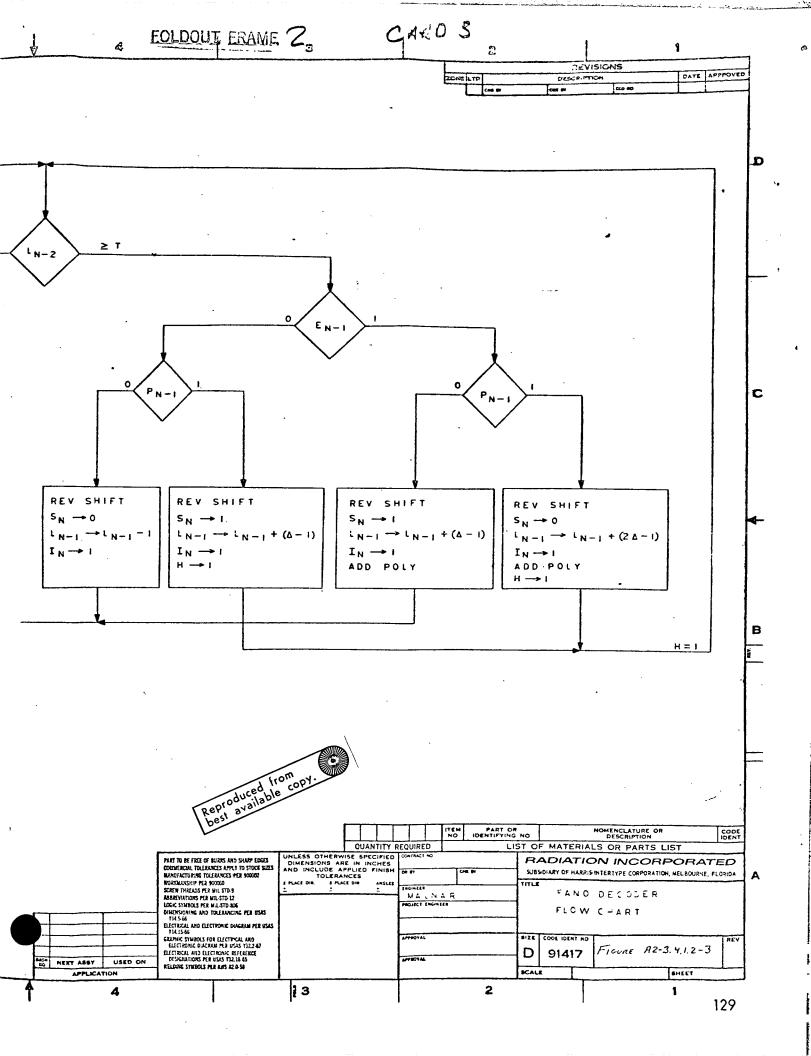

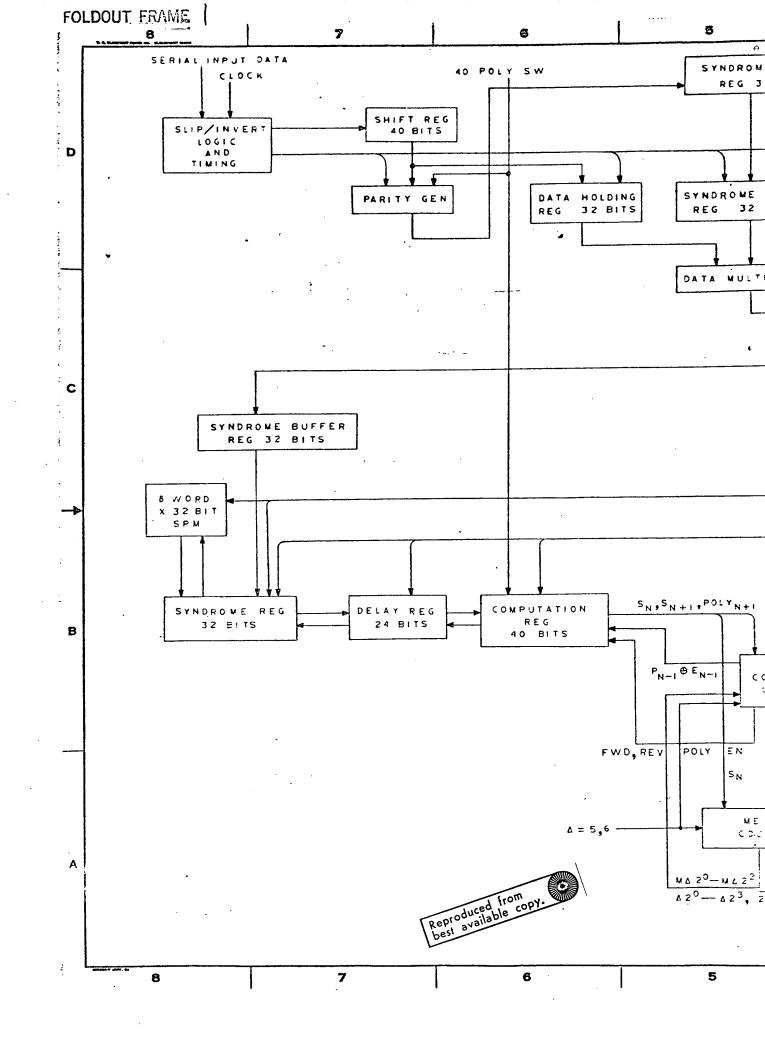

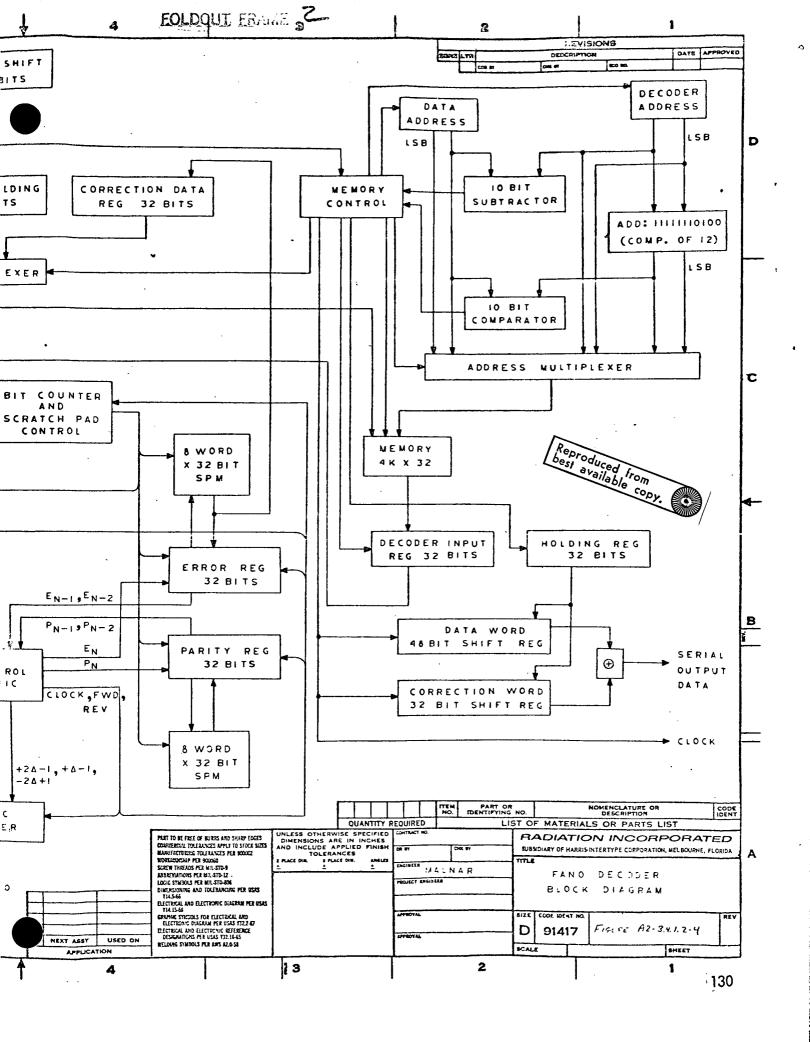

- d. With Fano enable and 1/2 rate clock it generates systematic codes with constraint length up to 40 and polynomial terms up to 40 (switch selectable) at input data rates to 9 MHz (i.e., output to 18 MHz).