https://ntrs.nasa.gov/search.jsp?R=19720023578 2020-03-11T19:30:13+00:00Z

CR-128513

1

2137475

2(mix)

(NASA-CR-128513) ADVANCED DATA MANAGEMENT /SYSTEM ANALYSIS TECHNIQUES STUDY Final Report (Intermetrics, Inc.) 30 Jul. 1972 36.2 CSCL 09B Unclas G3/08 39632

Reproduced by NATIONAL TECHNICAL INFORMATION SERVICE U S Department of Commerce Springfield VA 22151

## FINAL REPORT

### CONTRACT NAS-9-12119

## ADVANCED DATA MANAGEMENT SYSTEM ANALYSIS TECHNIQUES STUDY

30 JULY 1972

Submitted to:

National Aeronautics and Space Administration Manned Spacecraft Center Houston, Texas 77058

Submitted by:

Intermetrics, Inc. 701 Concord Avenue Cambridge, Massachusetts 02138

EB-6 2291

Note: The Project Manager for NASA was Dr. William J. B. Oldham, Information Systems Directorate, MSC. The Project Manager for Intermetrics initially was Mr. Joseph Saponaro, who was succeeded by Mr. Edward Copps.

.1

# ACKNOWLEDGEMENTS

Intermetrics personnel contributing to this study were:

| Neal A. Carlson, Ph.D. | - | Chapter 3                                                              |

|------------------------|---|------------------------------------------------------------------------|

| Edward M. Copps        | - | Chapters 2, 5, 6, 7, 8, 13                                             |

| James T. Pepe, Ph.D.   | - | Chapters 1, 4, 9, 10, 11, 12,<br>14, 16, 17, 19,<br>Appendices A and B |

Ŷ

Joseph A. Saponaro - Chapters 15, 18

hi

## TABLE OF CONTENTS

# Section

# Page

# PART I: INTRODUCTION

| 1. | INTR                     | ODUCTION TO SYSTEM ANALYSIS                                                         | 3                                |

|----|--------------------------|-------------------------------------------------------------------------------------|----------------------------------|

|    | 2.0                      | Introduction<br>Content of Study<br>A Step Toward Unity                             | 3<br>4<br>5                      |

|    |                          | <pre>3.1 Statement of Problem 3.2 Discussion of Problem</pre>                       | 5<br>6                           |

|    | 4.0                      | Summary                                                                             | 8                                |

|    |                          | PART II: ANALYTIC TECHNIQUES                                                        |                                  |

| 2. | RELI                     | ABILI <b>TY ANAL</b> YSIS                                                           | 13                               |

|    | 2.0                      | Introduction<br>Derivation<br>Conclusions                                           | 13<br>13<br>18                   |

| 3. | REDUI                    | NDANT COMPONENT FAILURE ANALYSIS                                                    | 19                               |

|    | 2.0<br>3.0<br>4.0<br>5.0 |                                                                                     | 19<br>19<br>22<br>24<br>37<br>40 |

| 4. | COST                     | CONSTRAINED RELIABILITY ANALYSIS                                                    | 43                               |

|    | 1.0<br>2.0               | Introduction<br>General Redundancy Considerations                                   | 43<br>43                         |

|    |                          | 2.1 Reliability Equations                                                           | 44                               |

|    | 3.0<br>4.0               | The Cost Constraint Problem<br>Non-Linear Programming Solution                      | 47<br>48                         |

|    |                          | 4.1 Construction of the Dominating Sequence 4.2 Computation of $\overline{m}^\circ$ | 49<br>50                         |

|    | 5.0<br>6.0               | Numerical Example<br>Maximum Principle Procedure                                    | 50<br>53                         |

|    |                          | 6.1 Regula Falsi Iteration                                                          | 56                               |

|    | 7.0                      | Example                                                                             | 58                               |

| Sec | ction                                                                   |                                                                                                                                              | Page                                               |  |  |  |  |

|-----|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| 5.  | QUEU                                                                    | EING THEORY                                                                                                                                  | 61                                                 |  |  |  |  |

|     | <pre>1.0 Discussion 2.0 Erlang's Model 3.0 Measures of Congestion</pre> |                                                                                                                                              |                                                    |  |  |  |  |

|     |                                                                         | 3.1 Queueing Time                                                                                                                            | 66                                                 |  |  |  |  |

|     | 4.0                                                                     | More Complex Models                                                                                                                          | 67                                                 |  |  |  |  |

|     |                                                                         | <ul> <li>4.1 Random Arrivals/General Service</li> <li>4.2 Erlang - m Distribution</li> <li>4.3 The Effect of Queueing Disciplines</li> </ul> | 67<br>67<br>68                                     |  |  |  |  |

|     | 6.0<br>7.0                                                              | Priority<br>Networks of Que <b>ues</b><br>Finite Queues<br>Summary                                                                           | 71<br>72<br>74<br>74                               |  |  |  |  |

| 6.  | MACR                                                                    | OSIMULATION                                                                                                                                  | 77                                                 |  |  |  |  |

|     |                                                                         | Introduction<br>Example<br>Computer Simulators                                                                                               | 77<br>79<br>82                                     |  |  |  |  |

|     |                                                                         | 3.1 CSS II<br>3.2 IMSIM                                                                                                                      | 83<br>83                                           |  |  |  |  |

|     | 4.0                                                                     | Summary                                                                                                                                      | 83                                                 |  |  |  |  |

| 7.  | MARK                                                                    | OV ANALYSIS AS AN ALTERNATIVE TO MACROSIMULATION                                                                                             | 87                                                 |  |  |  |  |

|     |                                                                         | Equilibrium Solutions<br>Comparison with Macro-Simulation<br>Speed of Solution                                                               | 87<br>88<br>88<br>89<br>90<br>92<br>93<br>94<br>94 |  |  |  |  |

| 8.  | DISC                                                                    | RETE MARKOV TECHNIQUES IN COMPUTER ANALYSIS                                                                                                  | 97                                                 |  |  |  |  |

|     | 1.0<br>2.0<br>3.0<br>4.0<br>5.0                                         | Comments on the Examples<br>Characteristic Functions                                                                                         | 97<br>100<br>103<br>104<br>105                     |  |  |  |  |

iv

Section

# PART III: HARDWARE TECHNIQUES

| 9.  | AERO              | SPACE COMPUTER ARCHITECTURE                                                                                                          | 109                                                  |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|     | 3.0<br>4.0<br>5.0 | Structural Levels<br>HOL Architecture<br>Reliability<br>Modularity<br>Microprogramming<br>Multiprocessor Networks                    | 109<br>109<br>110<br>111<br>111<br>115<br>115<br>116 |

| 10. | SYST              | EM PERFORMANCE MONITORING TO AID OPTIMIZATION                                                                                        | 121                                                  |

|     |                   | Introduction<br>Design Issues<br>Two Approaches to Monitoring                                                                        | 121<br>121<br>122                                    |

|     |                   | 3.1 An Example of Hardware Monitoring<br>3.2 An Example of Software Monitoring                                                       | 123<br>125                                           |

|     | 4.0               | Further Examples                                                                                                                     | 125                                                  |

|     | ·                 | 4.1 Time - Sharing Performance Monitoring 4.2 Opcode Utilization                                                                     | 127<br>127                                           |

|     | 5.0               | Summary                                                                                                                              | 127                                                  |

| 11. | FAIL              | URE DETECTION TECHNIQUES                                                                                                             | 129                                                  |

|     |                   | Introduction<br>Diagnosing Sequences for Finite State Automata<br>Diagnosis Using Augmented Hardware<br>Additional Detection Methods | 129<br>130<br>138<br>145                             |

|     |                   | 4.1 Voting                                                                                                                           | 145                                                  |

|     |                   | 4.1.1 Detection Level                                                                                                                | 148                                                  |

|     |                   | 4.2 Path Sensitizing                                                                                                                 | 148                                                  |

|     | 5.0               | Correction Techniques                                                                                                                | 149                                                  |

|     |                   | 5.1 Error Correcting Codes                                                                                                           | 149                                                  |

|     |                   | 5.1.1 Distance Codes<br>5.1.2 Binary Cyclic Codes                                                                                    | 150<br>151                                           |

|     |                   | 5.2 Quadded Logic 5.3 Reconfiguration 5.4 Software Restart                                                                           | 154<br>154<br>154                                    |

Page

# Section

|     |            | 5.4.1 Apollo Restart<br>5.4.2 Single Instruction Restart                                           | 155<br>156        |

|-----|------------|----------------------------------------------------------------------------------------------------|-------------------|

|     | 6.0        | Additional Applications and Other Topics                                                           | 156               |

|     |            | 6.1 Error Propagation                                                                              | 156               |

|     |            | 6.1.1 Error Correction in High-Speed<br>Arithmetic                                                 | 157               |

|     |            | 6.2 Intermittent Failures<br>6.3 The STAR Computer                                                 | 157<br>157        |

| 12. | INFO       | ORMATION TRANSMISSION BY ORTHOGONAL FUNCTIONS                                                      | 161               |

|     |            | Introduction<br>Communication Channels                                                             | 161<br>162        |

|     |            | 2.1 Entropy<br>2.2 Noisy Channels                                                                  | 163<br>164        |

|     | 3.0<br>4.0 |                                                                                                    | 165<br>168        |

|     |            | 4.1 Orthogonalization<br>4.2 Representation by Orthogonal Functions                                | 170<br>170        |

|     | 5.0        | Fourier Transforms                                                                                 | 172               |

|     |            | 5.1 Fast Fourier Transforms                                                                        | 173               |

|     |            | 5.1.1 Computational Savings<br>5.1.2 Hardware Implementation                                       | 174<br>175        |

|     |            | 5.2 Video Information                                                                              | 175               |

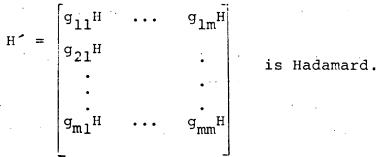

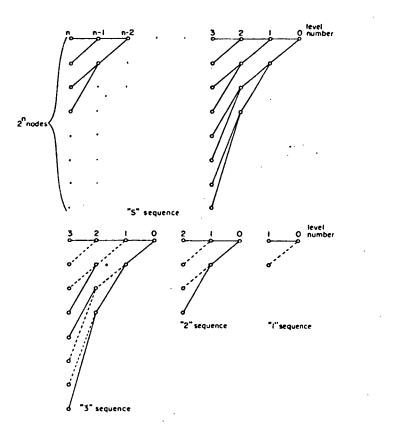

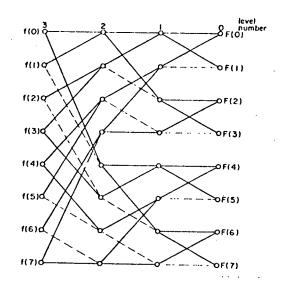

|     | 6.0        | Hadamard Matrices                                                                                  | 176               |

|     |            | <ul><li>6.1 Hadamard Transforms</li><li>6.2 Sequency</li><li>6.3 Fast Hadamard Transform</li></ul> | 177<br>178<br>179 |

|     |            | 6.3.1 Computational Savings                                                                        | 181               |

|     | 7.0        | Advantages and Disadvantages of Orthogonal<br>Transforms                                           | 181               |

|     |            | <ul><li>7.1 Bandwidth Compression</li><li>7.2 Quantization</li><li>7.3 Channel Noise</li></ul>     | 182<br>182<br>183 |

|     |            |                                                                                                    |                   |

ŶĨ

| Sect | ion                      |                                                                                                                                                                                  | Page                                   |  |  |  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| 13.  | SAMPLED DATA ANALYSIS    |                                                                                                                                                                                  |                                        |  |  |  |

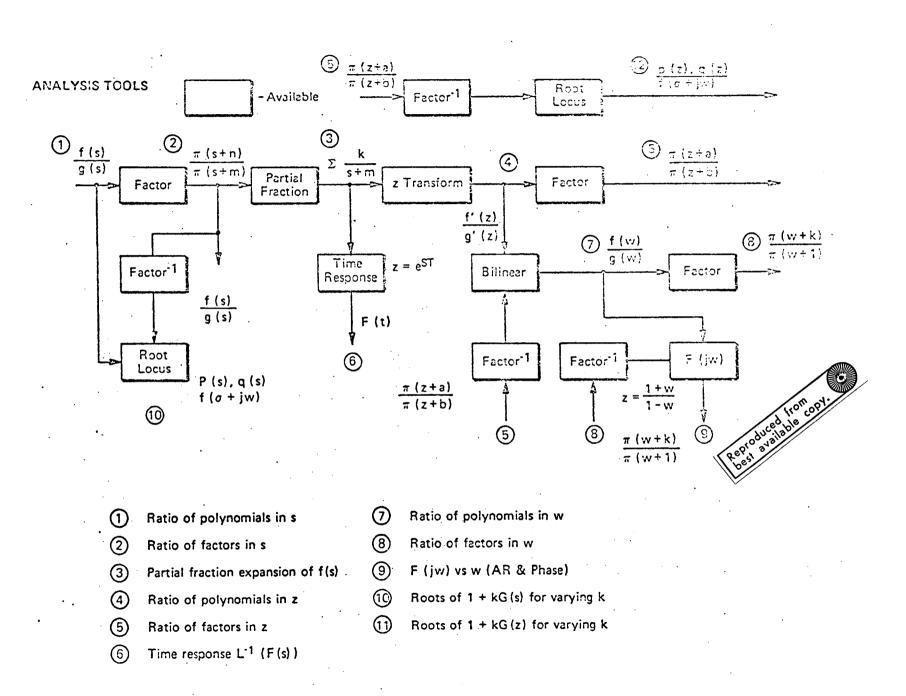

|      | 2.0<br>3.0<br>4.0<br>5.0 | Introduction<br>The Sampling Process<br>Reconstruction of the Unmodulated Signal<br>Basic Theorem of Sampling<br>Noise Into a Sampler<br>Analysis of Linear Sampled Data Systems | 187<br>187<br>189<br>192<br>192<br>193 |  |  |  |

|      |                          | <ul> <li>6.1 Difference Equations, z and w Transforms</li> <li>6.2 Conditions for Stability of the Equations</li> <li>6.3 w Transforms</li> </ul>                                | 194<br>195<br>195                      |  |  |  |

|      | 7.0                      | Sampled Continuous Systems                                                                                                                                                       | 196                                    |  |  |  |

|      |                          | 7.1 An Example 7.2 Design of the Compensation                                                                                                                                    | 198<br>203                             |  |  |  |

|      | 8.0                      | Design Tools                                                                                                                                                                     | 203                                    |  |  |  |

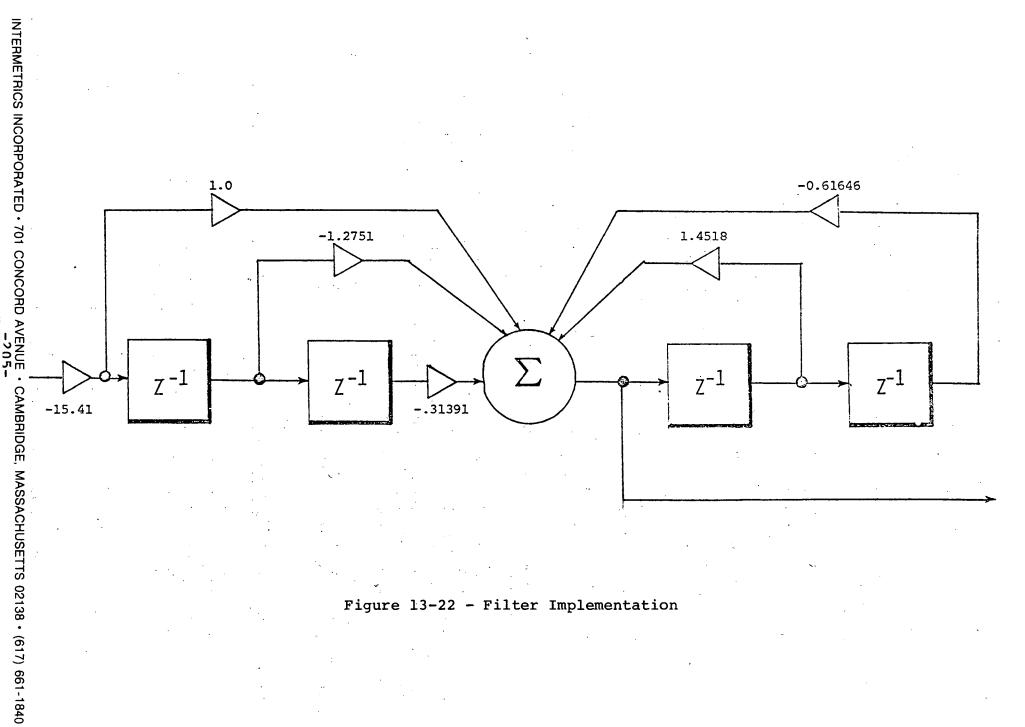

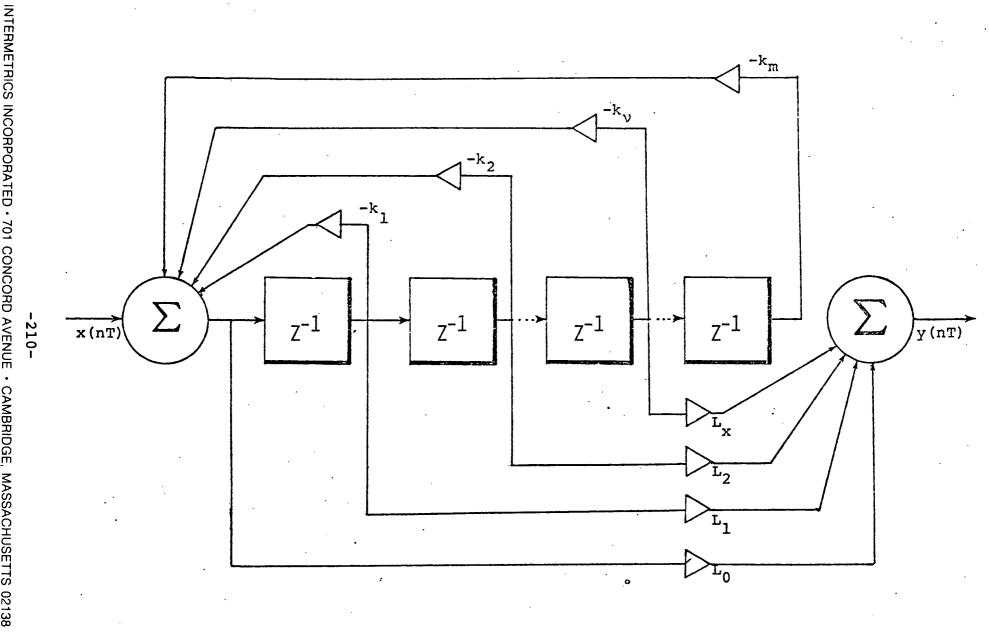

|      | 9.0                      | Practical Considerations in Realization of<br>Discrete Filters                                                                                                                   | 206                                    |  |  |  |

|      |                          | <ul><li>9.1 Stability and Coefficient Accuracy</li><li>9.2 Canonical Forms</li><li>9.3 Noise Analysis</li></ul>                                                                  | 206<br>208<br>209                      |  |  |  |

| -    | 10.0                     | Summary                                                                                                                                                                          | 212                                    |  |  |  |

|      |                          | PART IV: SOFTWARE TECHNIQUES                                                                                                                                                     |                                        |  |  |  |

| 14.  | DATA                     | ORGANIZATION AND HANDLING                                                                                                                                                        | 217                                    |  |  |  |

|      | 1.0<br>2.0<br>3.0<br>4.0 | Introduction<br>Data Types<br>Data Organization<br>Data Handling                                                                                                                 | 217<br>217<br>219<br>222               |  |  |  |

|      |                          | 4.1 Searching<br>4.2 Sorting                                                                                                                                                     | 222<br>223                             |  |  |  |

|      |                          | 4.2.1 Interchange Sort<br>4.2.2 Shell Sort<br>4.2.3 Radix Sort<br>4.2.4 Conclusions                                                                                              | 223<br>225<br>225<br>225<br>225        |  |  |  |

|      | 5.0                      | Data Set Organization                                                                                                                                                            | 228                                    |  |  |  |

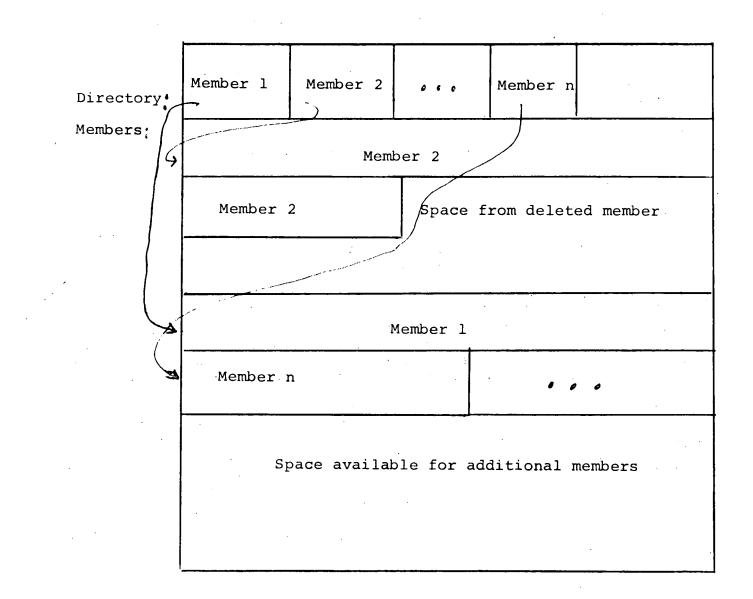

|      |                          | 5.1 Sequential Organization 5.2 Partitioned Organization 5.3 Indexed Sequential Organization 5.4 Direct Organization 5.5 Volume Structure 5.6 Conclusions VII                    | 228<br>228<br>230<br>230<br>230        |  |  |  |

|     | 6.0         | Spec          | cial Data Handling Languages                                                                                                                                                                                            | 231                             |

|-----|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|     |             | 6.1           | SNOBOL                                                                                                                                                                                                                  | 231                             |

|     |             |               | 6.1.1 Examples of String Manipulation<br>within SNOBOL                                                                                                                                                                  | 231                             |

|     |             |               | FILLIP<br>Extensible Languages                                                                                                                                                                                          | 232<br>232                      |

| 15. | THE<br>IN A | ROLE<br>EROSF | OF HIGHER ORDER LANGUAGE PROGRAMMING<br>ACE COMPUTERS                                                                                                                                                                   | 235                             |

|     | 1.0<br>2.0  |               | oduction<br>wages Needed for Advanced Space Flights                                                                                                                                                                     | 235<br>236                      |

|     |             | 2.2           | Role of the Crew Language<br>Crew Language Requirements<br>Role of the Software Development Language                                                                                                                    | 236<br>237<br>238               |

|     | 3.0         |               | ification for Using a Higher Order<br>ramming Language                                                                                                                                                                  | 238                             |

|     |             | 3.1           | Higher Order Programming Language<br>Experience                                                                                                                                                                         | 240                             |

|     | 4.0         | Sing          | le Compiler Approach                                                                                                                                                                                                    | 241                             |

|     |             | 4.1           | Systems Programming                                                                                                                                                                                                     | 242                             |

|     |             |               | 4.1.1 Approach to Systems Programming                                                                                                                                                                                   | 243                             |

|     | 5.0         | Adva<br>Soft  | ntages of the HOL and Compiler to<br>ware Modularity                                                                                                                                                                    | 245                             |

|     |             |               | Apollo Experience<br>Software Modularity                                                                                                                                                                                | 245<br>245                      |

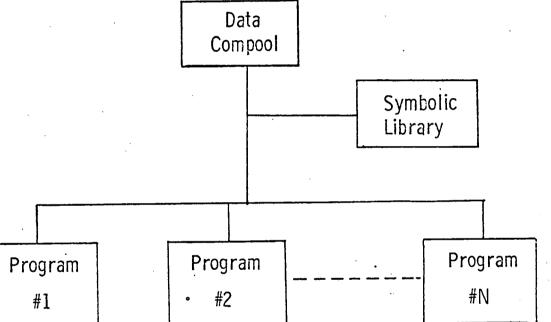

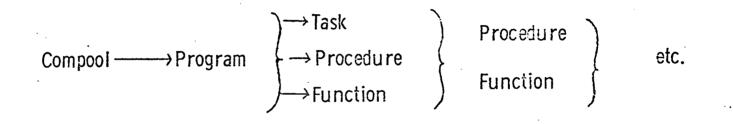

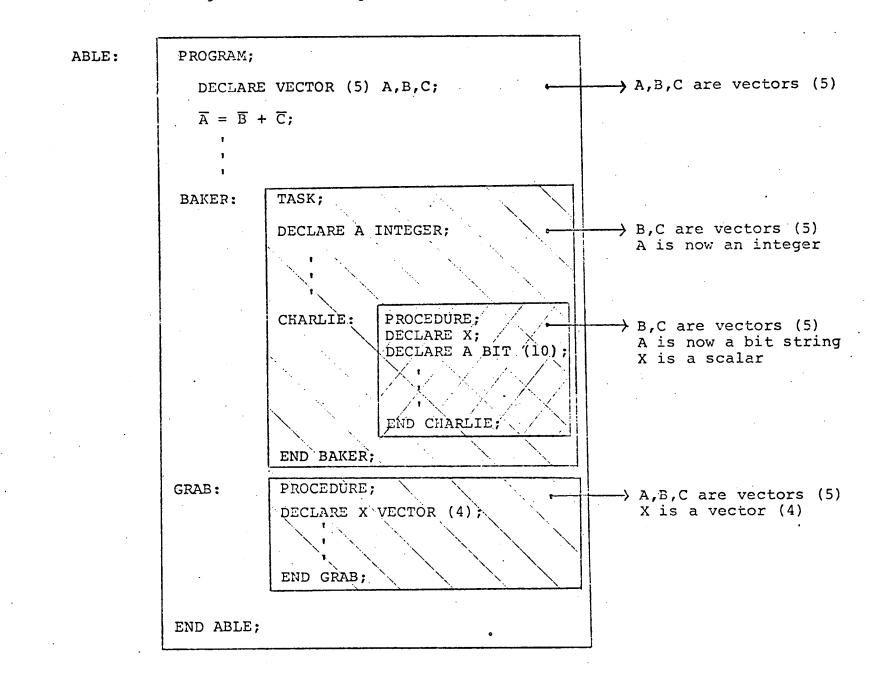

|     |             |               | <ul> <li>5.2.1 Independent Compilation and the<br/>Compool</li> <li>5.2.2 Blocks Structure (Name Scope)</li> <li>5.2.3 Control of Shared Data</li> <li>5.2.4 Access Rights</li> <li>5.2.5 Automatic Checking</li> </ul> | 245<br>246<br>250<br>250<br>250 |

|     |             | 5.3           | Additional Advantages of the HOL Approach                                                                                                                                                                               | 253                             |

|     |             |               | <ul><li>5.3.1 Management</li><li>5.3.2 An Improvement in Communications</li><li>5.3.3 Prevention of Errors by Readability</li></ul>                                                                                     | 253<br>253                      |

|     |             | _             | of Code                                                                                                                                                                                                                 | 254                             |

|     |             | 5.4           | Summary Viii                                                                                                                                                                                                            | 254                             |

# Page

# Section

| Page |

|------|

|------|

|     | 6.0<br>7.0 | Che<br>HOL | ckout L<br>Compil             | anguages<br>er Implementation                                      | 254<br>255        |

|-----|------------|------------|-------------------------------|--------------------------------------------------------------------|-------------------|

|     |            | 7.1<br>7.2 | Compi<br>Appro                | ler Problem<br>aches to Efficient Code Generation                  | 255<br>256        |

|     |            |            | 7.2.1                         |                                                                    | 256<br>257        |

|     |            | 7.3        | Impler                        | mentation Factors                                                  | 257               |

|     |            |            | 7.3.1                         | Software Interpreter<br>Hardware Implementation and Use            | 257               |

|     |            |            | 7.3.3                         | of Microprogramming                                                | 258<br>259        |

| 16. | THE        | DESIC      | GN OF AN                      | ADVANCED AEROSPACE EXECUTIVE SYSTEM                                | <b>2</b> 61       |

|     | 2.0        | Desi       | oductic<br>gn Crit<br>ral Des |                                                                    | 261<br>262<br>263 |

|     |            | 3.1<br>3.2 | Identi<br>Execut              | fication of Executive Program Modules<br>ive Operating Environment | 264<br>265        |

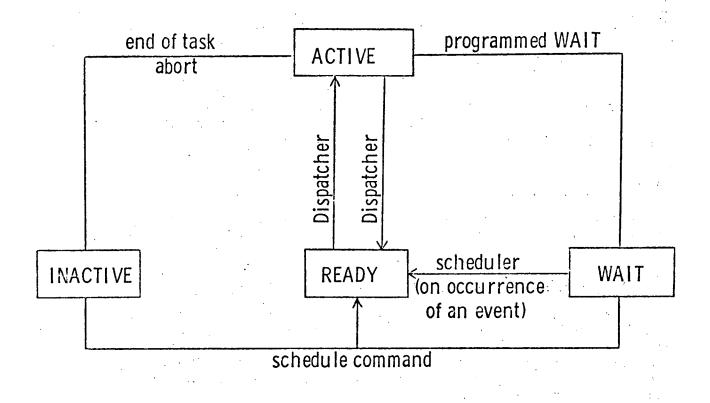

|     | 4.0        | Defi       | nitions                       |                                                                    | 265               |

|     |            | 4.2        | Common                        | ive Queues<br>Data Pool<br>quest Block                             | 266<br>266<br>268 |

|     | 5.0        | Gene       | ral Dis                       | cussion of Executive Design Issues                                 | 268               |

|     |            | 5.1<br>5.2 | Interr<br>Resourc             | upt Handling and Task Dispatching<br>ce Allocation                 | 268<br>270        |

|     |            |            | 5.2.1<br>5.2.2<br>5.2.3       | Deadlock<br>Memory Fragmentation<br>Priority Conflict              | 271<br>271<br>272 |

|     |            | 5.3        | Allocat                       | ion of Specific Resources                                          | 272               |

|     |            |            | 5.3.1<br>5.3.2<br>5.3.3       | Common Data Sharing                                                | 272<br>274<br>278 |

| 6   | 5.0        | Featu      | res of                        | the Executive System                                               | 279               |

|     |            | 6.1        | Directo                       | pries                                                              | 279               |

|     |            | İx         | 6.1.2                         | The Data Set Directory                                             | 279<br>281<br>281 |

| Sect | ion                      |                                                                                                                                                                         | Page                            |

|------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|      |                          | <ul> <li>6.2 Subroutine Linkage</li> <li>6.3 Common Subroutines</li> <li>6.4 Task Priority Levels</li> <li>6.5 Assignment of Core Memory</li> <li>6.6 Events</li> </ul> | 281<br>281<br>282<br>283<br>285 |

|      |                          | 6.6.1 Event Handling                                                                                                                                                    | 285                             |

|      |                          | 6.7 I/O Scheduling<br>6.8 Configuration Management                                                                                                                      | 289<br>290                      |

| 17.  | MICR                     | OSIMULATION IN SYSTEM DESIGN                                                                                                                                            | 293                             |

|      |                          | Introduction<br>Features of the Microsimulator                                                                                                                          | 293<br>294                      |

|      |                          | 2.1 User Options                                                                                                                                                        | 294                             |

|      |                          | 2.1.1 Stress Testing<br>2.1.2 The Coroner Request<br>2.1.3 An Alternative Approach to                                                                                   | 295<br>295<br>0                 |

|      |                          | Diagnostics                                                                                                                                                             | 295                             |

|      |                          | <ol> <li>2.2 The Environment</li> <li>2.3 Rollback</li> <li>2.4 Supporting Software</li> </ol>                                                                          | 296<br>298<br>298               |

|      | 3.0                      | Design Issues and Structure of the<br>Microsimulator                                                                                                                    | 299                             |

|      |                          | 3.1 Logical Structure 3.2 Coding in a Higher Order Language 3.3 Modularity                                                                                              | 299<br>e 303<br>304             |

|      | 4.0                      | The Software Design Process                                                                                                                                             | 305                             |

|      |                          | 4.1 Overuse of Simulation                                                                                                                                               | 307                             |

|      | 5.0<br>6.0<br>7.0<br>8.0 | Simulation and Microprogramming<br>Advantages of Microsimulation                                                                                                        | 307<br>308<br>308<br>309        |

| 18.  | BENCH<br>PERF(           | MARK PROGRAMS AS AN AID TO COMPUTER<br>RMANCE EVALUATION                                                                                                                | 313                             |

|      | 1.0<br>2.0               | Introduction<br>Review of Computer Performance Evalua<br>Techniques                                                                                                     | 313<br>tion<br>315              |

# Section

1

|      |      | 2.2          | Cycle and Add Time Comparisons<br>Instruction Mixes<br>Benchmarks                                                  | 315<br>315<br>319 |

|------|------|--------------|--------------------------------------------------------------------------------------------------------------------|-------------------|

|      |      |              | <ul><li>2.3.1 Kernel Problems</li><li>2.3.2 Existing Programs</li><li>2.3.3 Synthetic Benchmark Programs</li></ul> | 319<br>321<br>321 |

|      |      |              | Simulation<br>Performance Monitoring                                                                               | 322<br>322        |

|      | 3.0  | Revi         | ew of the Problems of Evaluation Techniques                                                                        | 322               |

|      |      | 3.1<br>3.2   | Benchmark Programs and Problems<br>Cost of Determining Performance Evaluation                                      | 323<br>323        |

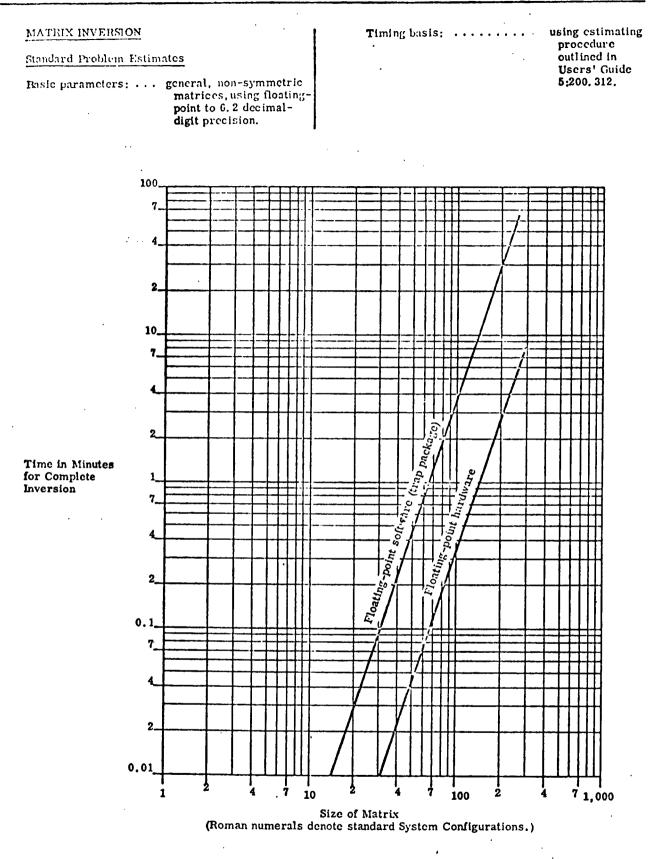

|      | 4.0  | High<br>Data | er Order Language Benchmarks for Aerospace<br>Management Systems                                                   | 324               |

|      |      | 4.1          | Hand Compiled HOL Benchmarks                                                                                       | 324               |

|      |      |              | 4.1.1 Sample FORTRAN Benchmark                                                                                     | 325               |

|      |      | 4.2<br>4.3   | Statistical Approach to HOL Benchmark<br>Problems with the HOL Benchmark Approach                                  | 327<br>330        |

|      |      |              | PART V: FACILITIES                                                                                                 |                   |

| 19.  | FACI | LITIE        | S NEEDED FOR SYSTEM ANALYSIS                                                                                       | 335               |

|      |      | Syst         | oduction<br>em Design Phases<br>ed Facilities                                                                      | 335<br>335<br>336 |

|      |      | 3.1<br>3.2   | The Digital Computer Facility<br>The Hybrid Computer Facility                                                      | 336<br>336        |

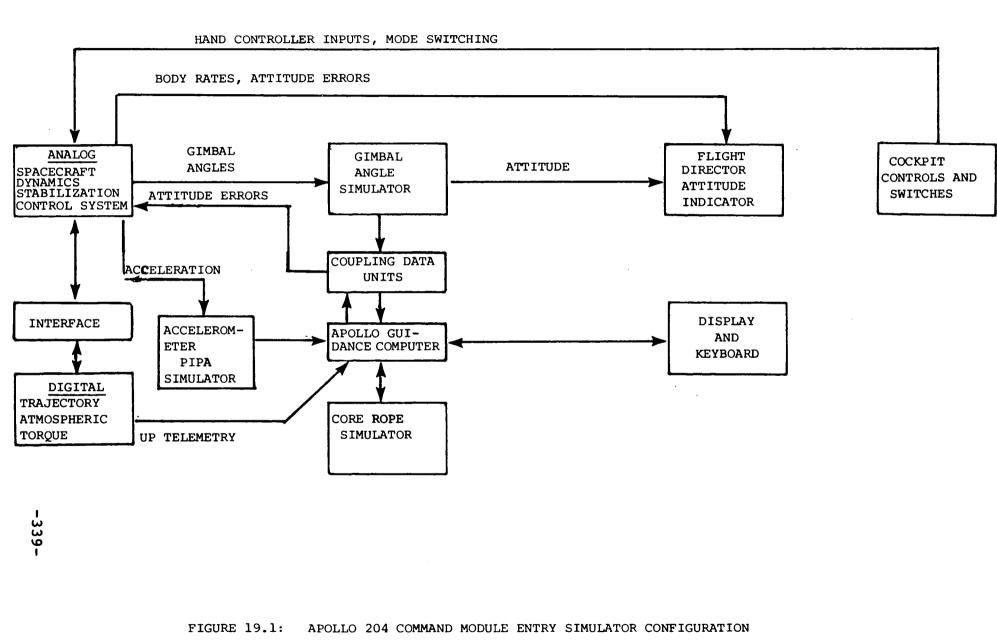

|      |      |              | 3.2.1 Types of Hybrid Computers<br>3.2.2 Apollo Hybrid Simulations<br>3.2.3 An Additional Feature of the           | 337<br>337        |

|      |      |              | 3.2.3 An Additional Feature of the<br>Hybrid Facility                                                              | 338               |

|      |      | 3.3          | The Use of a Microprogramming Computer                                                                             | 338               |

|      |      |              | PART VI: APPENDICES                                                                                                |                   |

| Арре | ndix | A            |                                                                                                                    | 343               |

| Appe | ndix | в            | 1                                                                                                                  | 349               |

|      |      |              |                                                                                                                    |                   |

Page

# TABLE OF ILLUSTRATIONS

| Figur | e                                                                   | Page |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------|------|--|--|--|--|--|--|--|

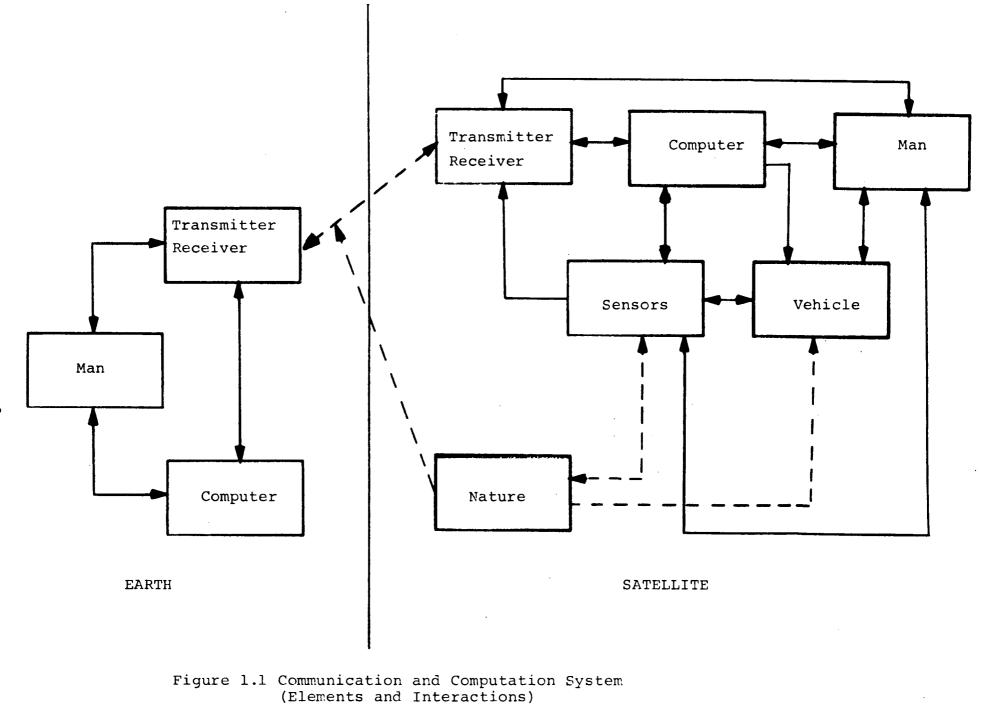

| 1.1   | Communication and Computation System<br>(Elements and Interactions) | 9    |  |  |  |  |  |  |  |

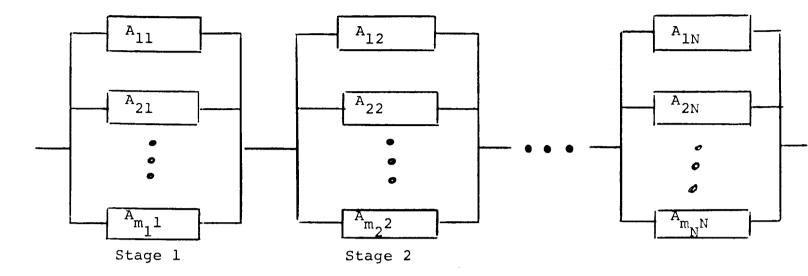

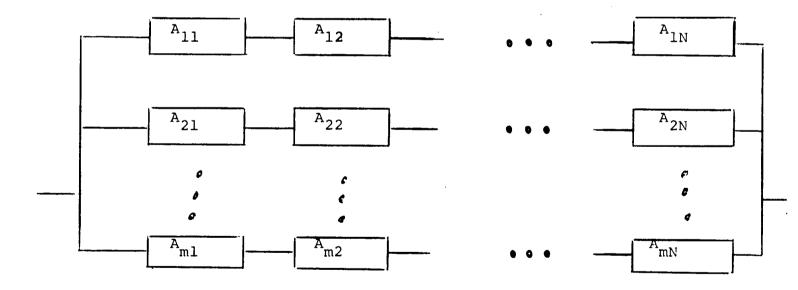

| 4.2   | Parallel-Series Configuration                                       |      |  |  |  |  |  |  |  |

| 4.3   | Dominating Sequence Table for Stages 1 and 2                        |      |  |  |  |  |  |  |  |

| 4.4   | Dominating Sequence Table for all 3 Stages                          |      |  |  |  |  |  |  |  |

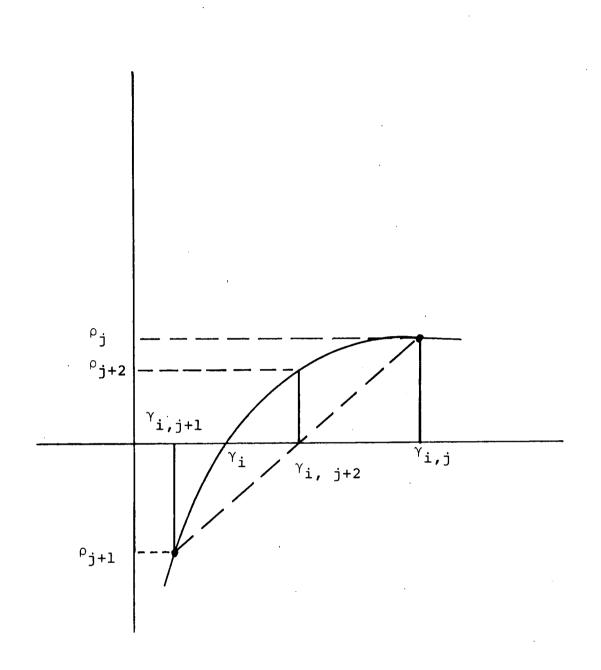

| 4.5   | Regula Falsi Iteration                                              | 57   |  |  |  |  |  |  |  |

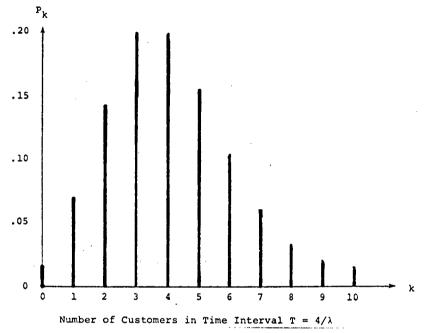

| 5.1   | Poisson Distribution                                                | 63   |  |  |  |  |  |  |  |

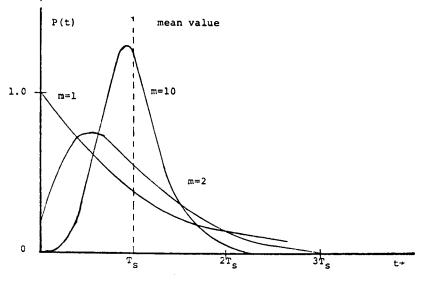

| 5.2   | Erlang-m Distribution                                               | 68   |  |  |  |  |  |  |  |

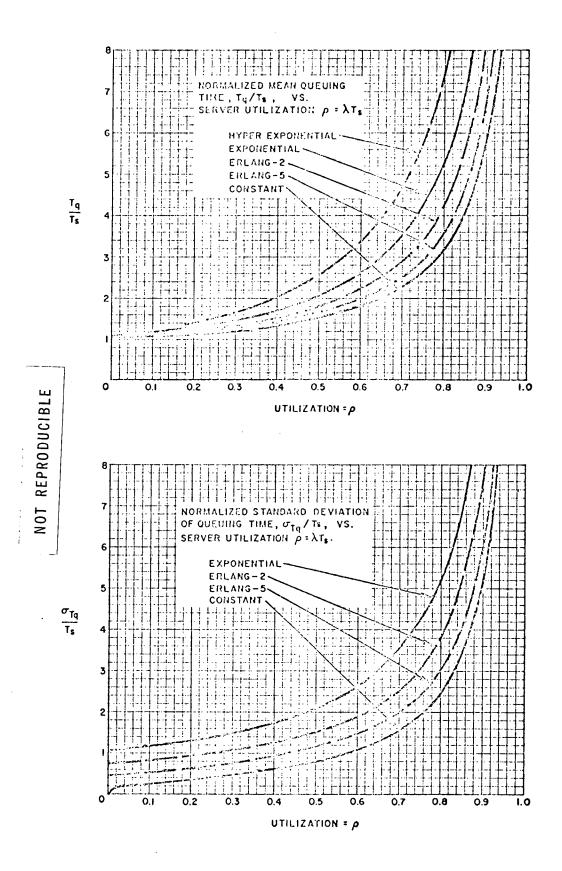

| 5.3   | Queueing Time                                                       | 69   |  |  |  |  |  |  |  |

| 5.4   | Queue Length                                                        | 70   |  |  |  |  |  |  |  |

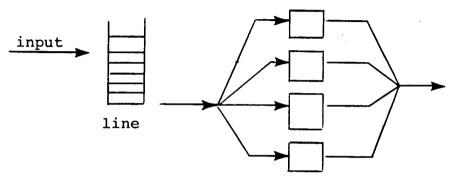

| 5.5   | Multiple Server Queue                                               | , 73 |  |  |  |  |  |  |  |

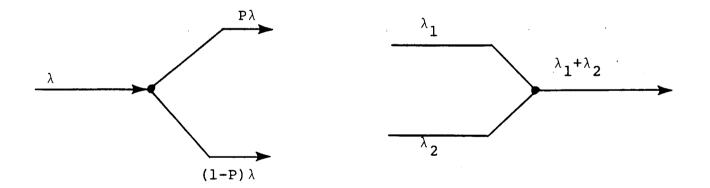

| 5.6   | Branch & Merge Points                                               | 73   |  |  |  |  |  |  |  |

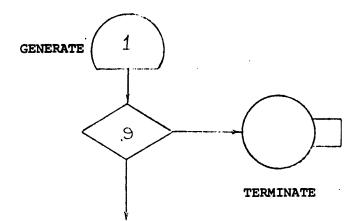

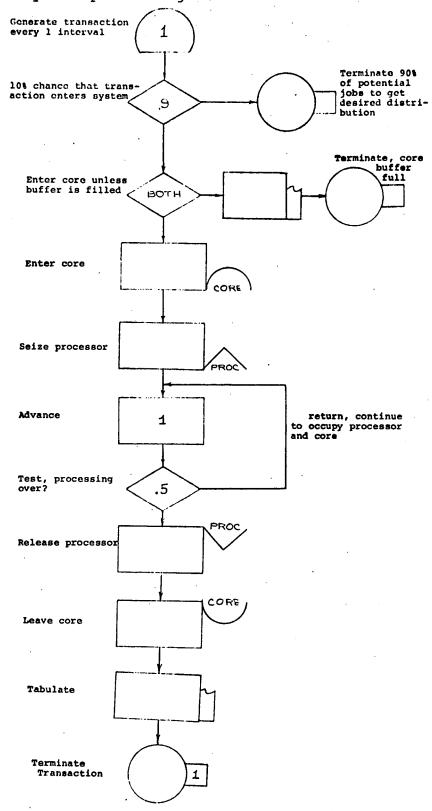

| 6.1   | Creating the Job Stream                                             |      |  |  |  |  |  |  |  |

| 6.2   | Complete Block Diagram                                              |      |  |  |  |  |  |  |  |

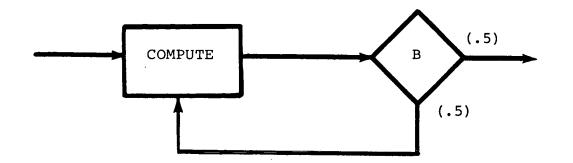

| 7.1   | Subroutine Example                                                  | 90   |  |  |  |  |  |  |  |

| 8.1   | Flowgraph for Subroutine                                            |      |  |  |  |  |  |  |  |

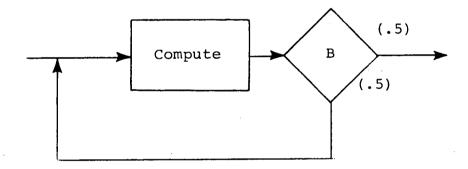

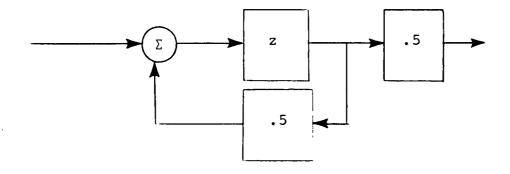

| 8.2   | Block Diagram for Subroutine                                        |      |  |  |  |  |  |  |  |

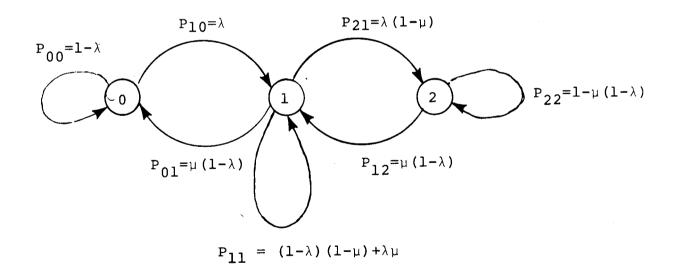

| 8.3   | Transition Diagram for Queueing Example                             |      |  |  |  |  |  |  |  |

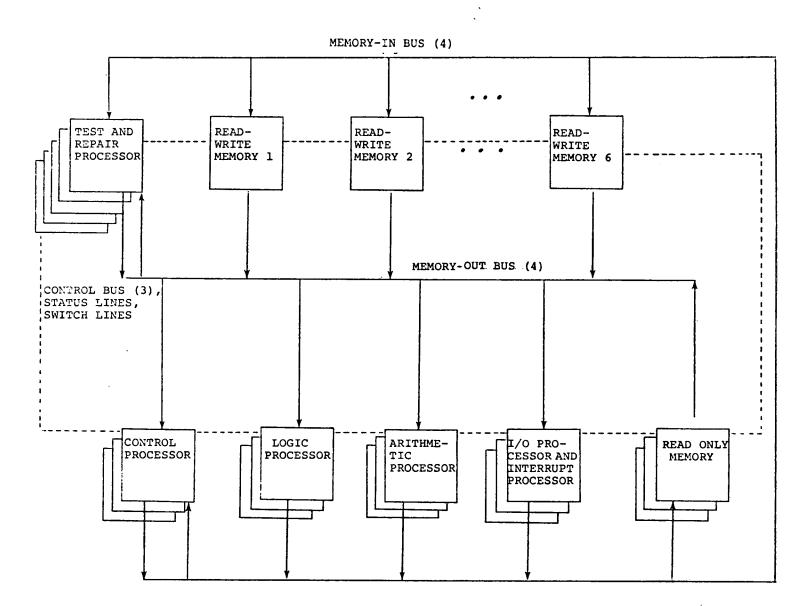

| 9.1   | Architecture of Star Computer                                       |      |  |  |  |  |  |  |  |

| 9.2   | D-Machine Architecture                                              | 113  |  |  |  |  |  |  |  |

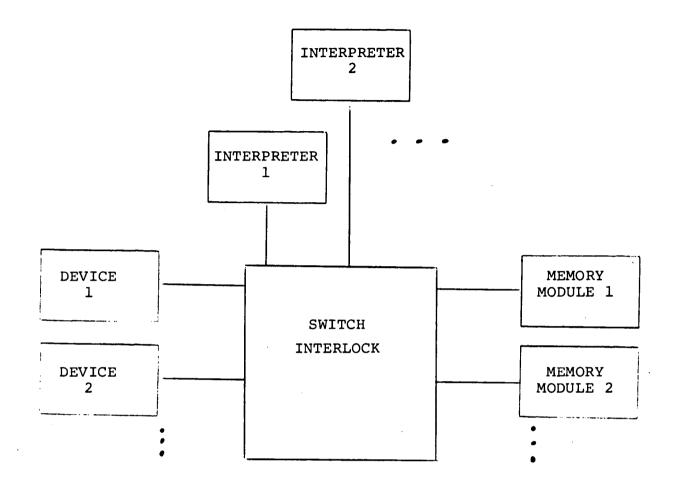

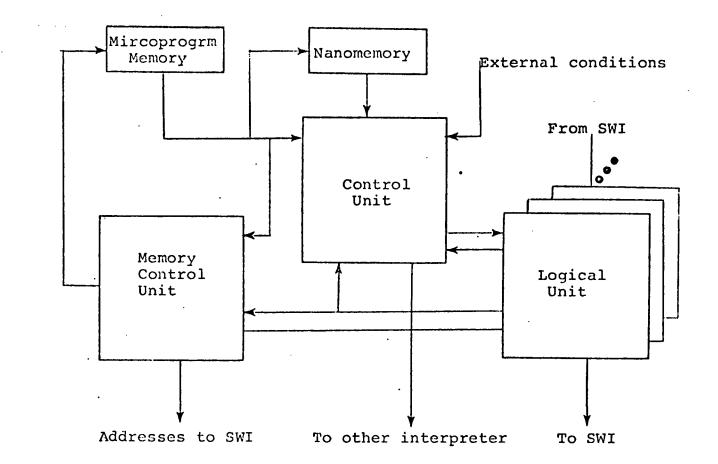

| 9.3   | Interpreter Organization                                            | 114  |  |  |  |  |  |  |  |

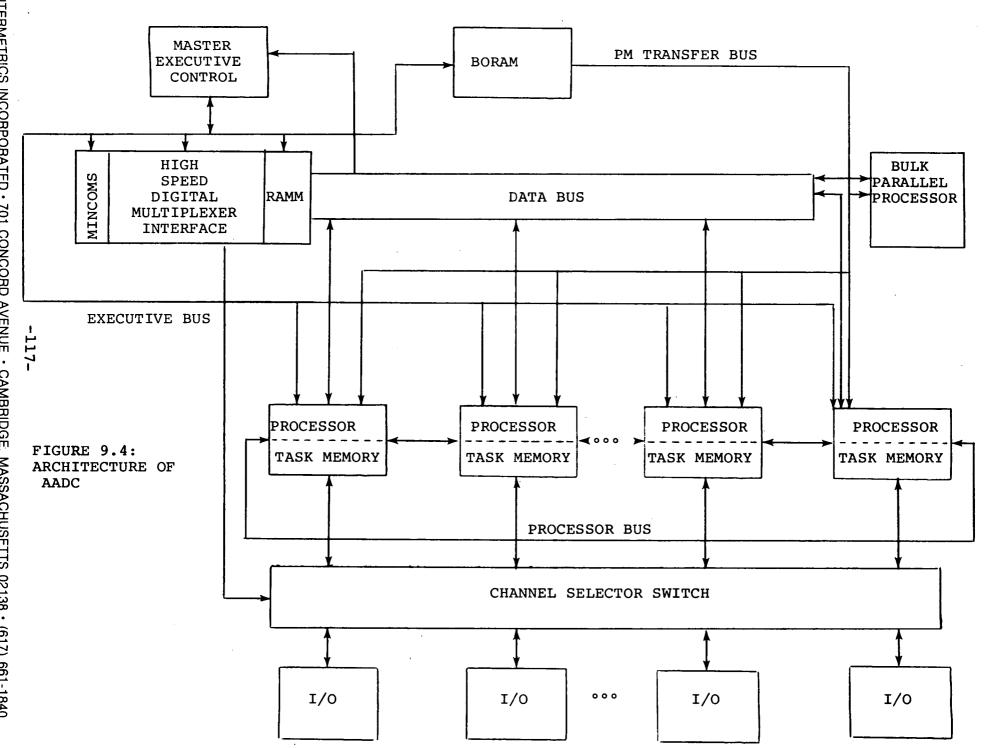

| 9.4   | Architecture of AADC                                                | 117  |  |  |  |  |  |  |  |

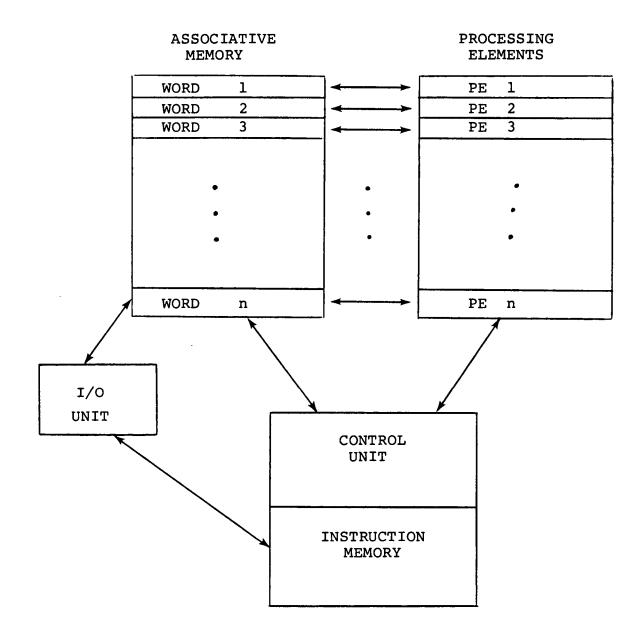

| 9.5   | Organization of an Associative Array Processor                      | 118  |  |  |  |  |  |  |  |

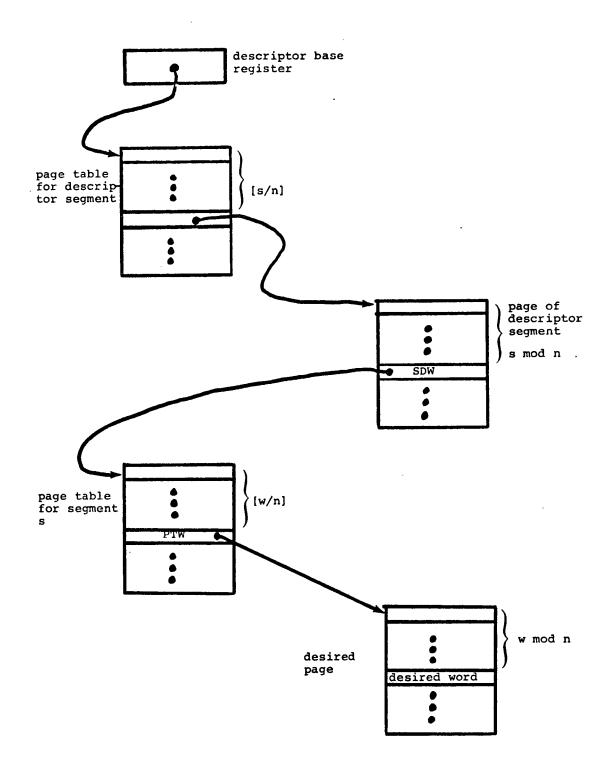

| 10.1  | Translation of address (s,w) by<br>MULTICS, where n = page size     | 124  |  |  |  |  |  |  |  |

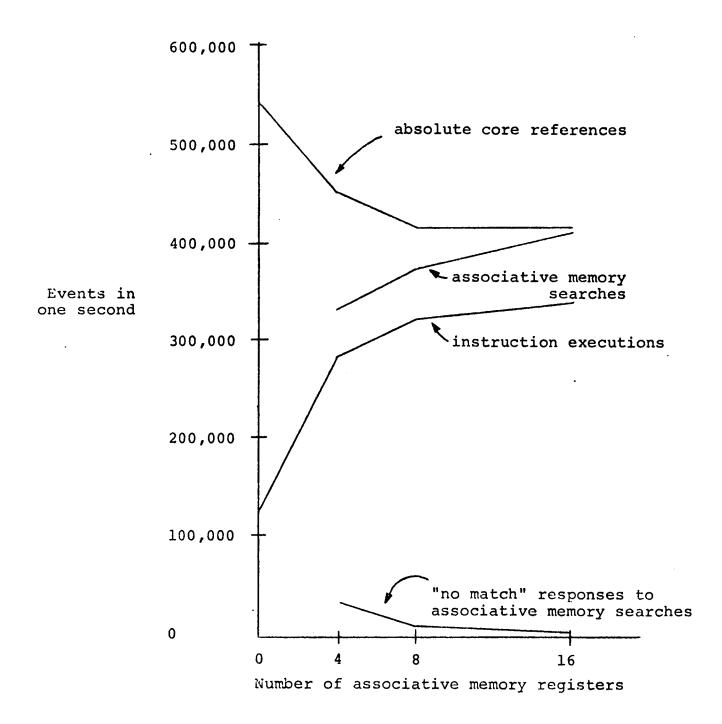

| 10.2  | Multics Performance with Various Associative<br>Memory Sizes        | 126  |  |  |  |  |  |  |  |

| Figure     |                                                                         | Page       |

|------------|-------------------------------------------------------------------------|------------|

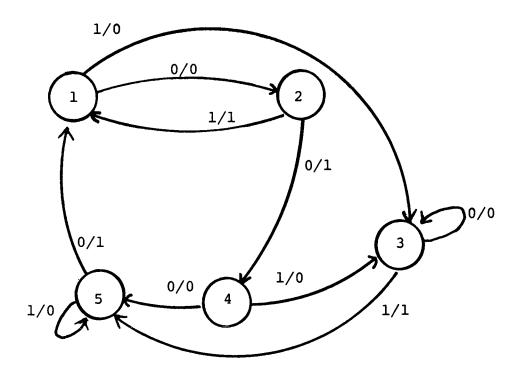

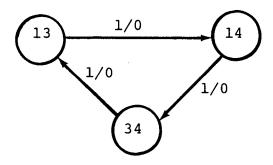

| 11.1       | State Diagram of M <sub>l</sub>                                         | 132        |

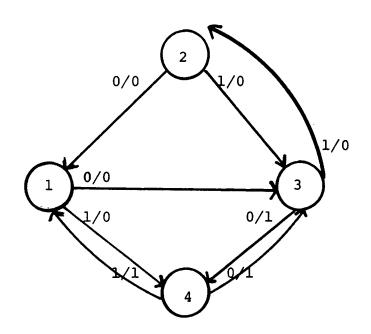

| 11.2       | State Diagram of M <sub>2</sub>                                         | 133        |

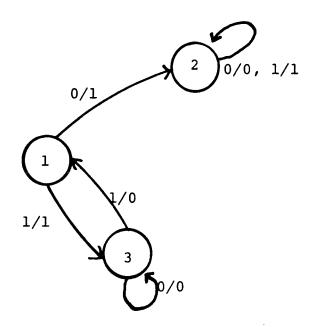

| 11.3       | State Diagram of M <sub>3</sub>                                         | 134        |

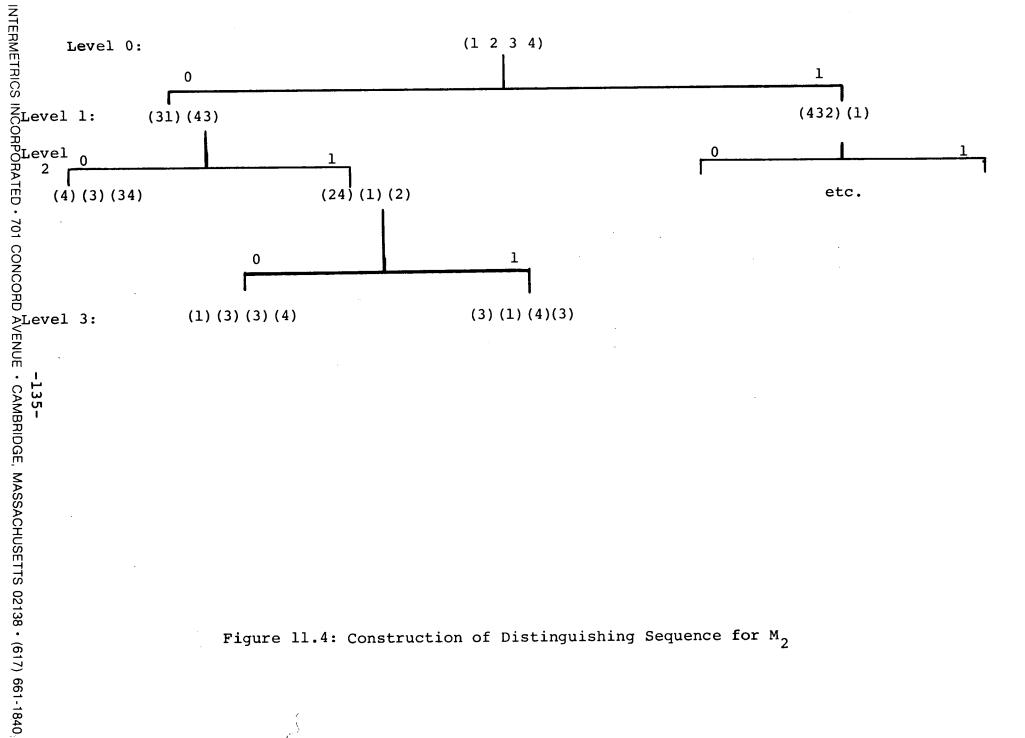

| 11.4       | Construction of Distinguishing Sequence for $M_2$                       | 135        |

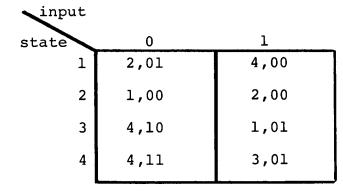

| 11.5a      | State Table for $M_4$                                                   | 137        |

| 11.5b      | Response of $M_4$ to 10                                                 | 137        |

| 11.6a      | Machine M                                                               | 139        |

| 11.6b      | Machine M                                                               | 139        |

| 11.7       | State Diagram of M <sub>5</sub>                                         | 141        |

| 11.8       | Testing Graph of M5                                                     | 143        |

| 11.9       | Voter Configurations                                                    | 146        |

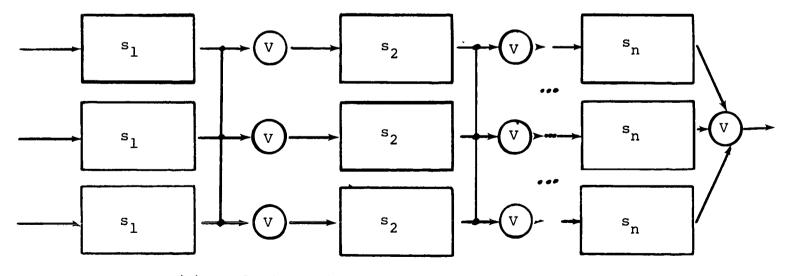

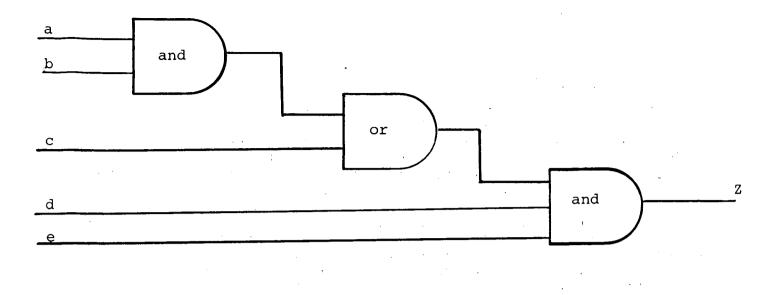

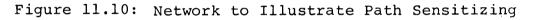

| 11.10      | Network to Illustrate Path Sensitizing                                  | 153        |

| 11.11      | Shift Register to encode $(7,4)$ cyclic code generated by $x^3 + x + 1$ | 153        |

| 12.1       | Hadamard Transform Computational Sequence                               | 180        |

| 12.2       | Computation of One Dimensional,<br>Third Order Hadamard Matrix          | 180        |

| 13.1       | Components of a Digital Control Element                                 | 187        |

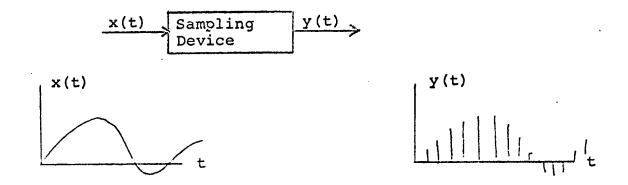

| 13.2       | Waveforms of the Input and Output of a<br>Sampling Device               | 188        |

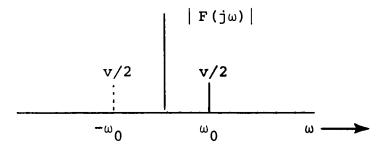

| 13.3       | The Amplitude of the Fourier Transform of x(t)                          | 188        |

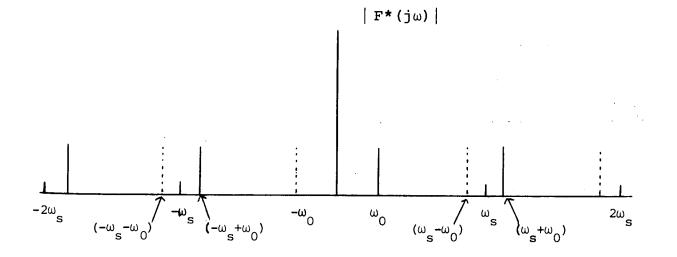

| 13.4       | The Amplitude of the Fourier Transform of y(t)                          | 189        |

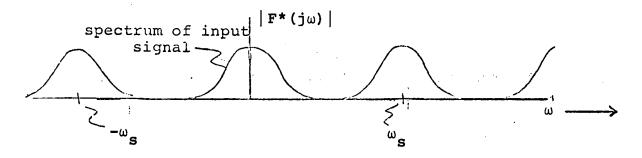

| 13.5       | The Spectrum of a Sampled Signal                                        | 189        |

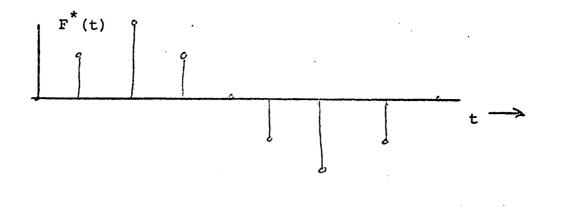

| 13.6       | A Sampled Signal                                                        | 190        |

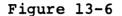

| 13.7       | A Zero'th Order Hold Reconstruction                                     | 190        |

| 13.8       | A First Order Hold Reconstruction                                       | 190        |

| 13.9       | A Smooth Fit                                                            | 191        |

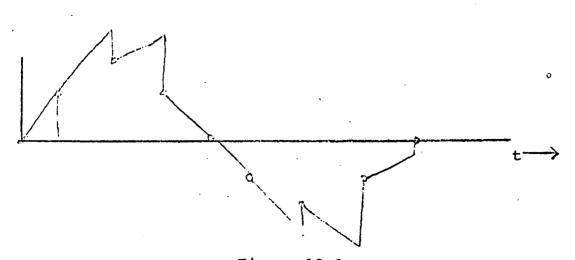

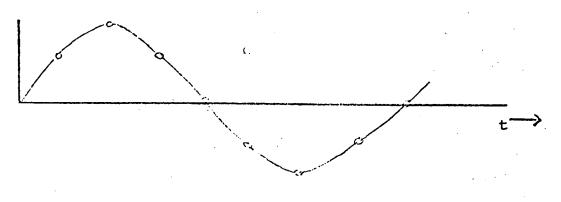

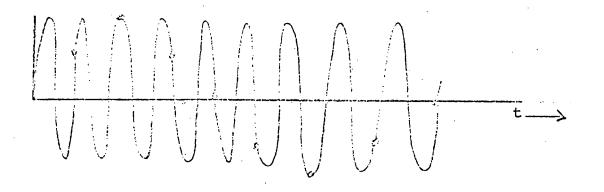

| 13.10      | of Samples XM                                                           | 191        |

| ETRICS INC | COPPORATED , 701 CONCORD AVENUE , CAMPRIDGE MASSACHUSETTS               | 00100 . /6 |

# Figure

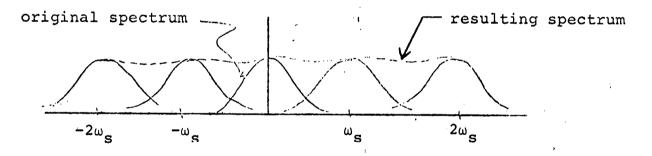

| 13.11 | Effect of the Overlap on the Frequency Spectrum     | 192 |

|-------|-----------------------------------------------------|-----|

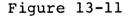

| 13.12 | Aliasing of High Frequency Noise                    | 193 |

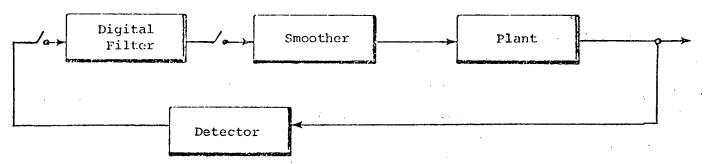

| 13.13 | A Digitally Controlled System                       | 193 |

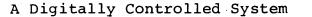

| 13.14 | Continuous Portion of the System                    | 196 |

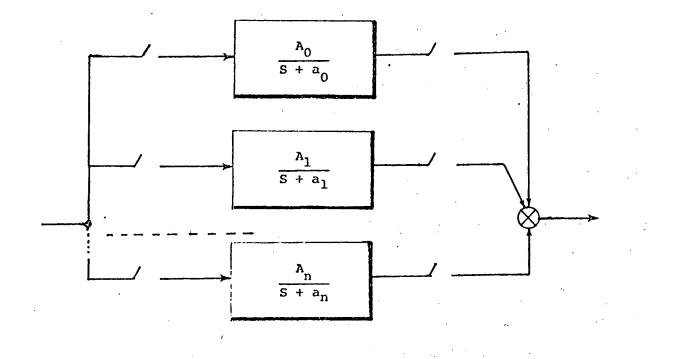

| 13.15 | Partial Fraction Form                               | 197 |

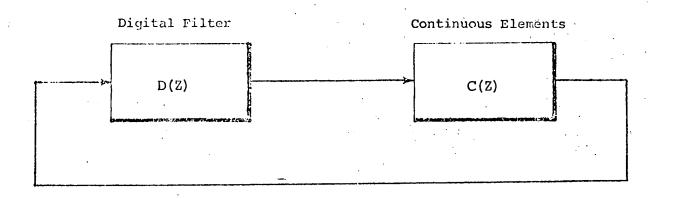

| 13.16 | Reduction to a Discrete System                      | 197 |

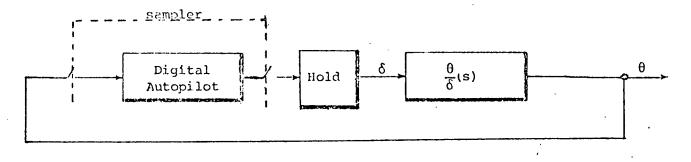

| 13.18 | Pershing Autopilot                                  | 198 |

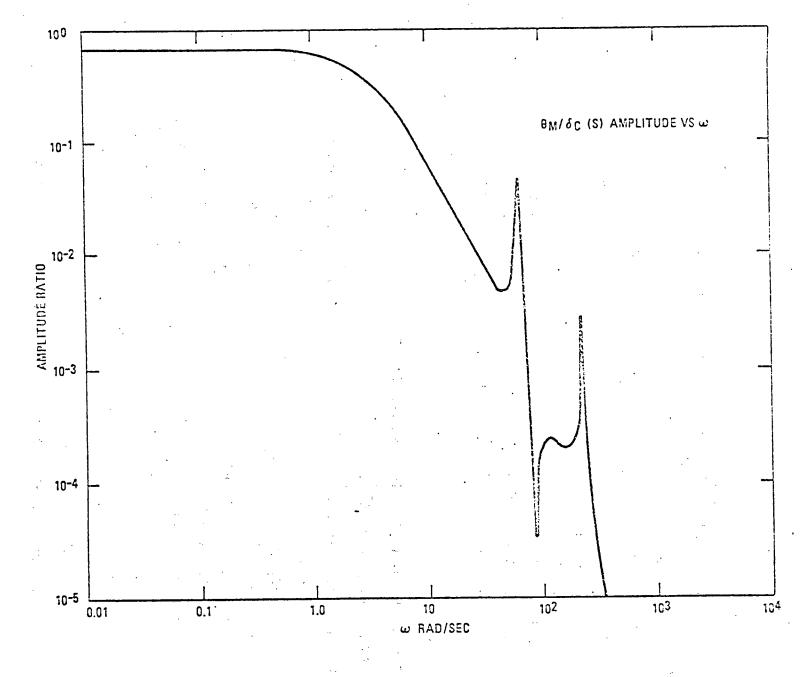

| 13.17 | Continuous Systems                                  | 199 |

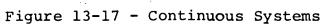

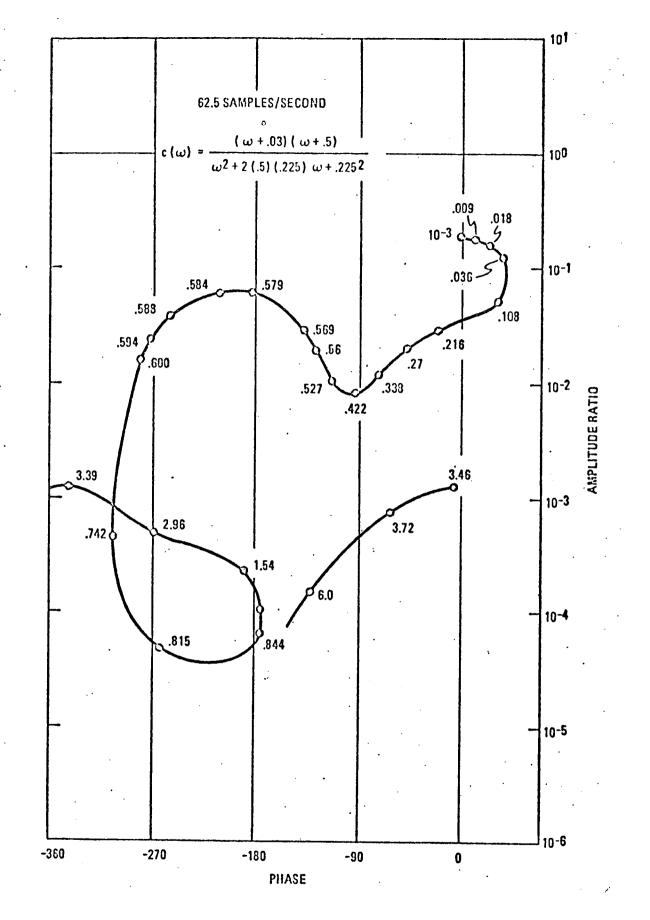

| 13.19 | Bode Plot, Descrete System                          | 201 |

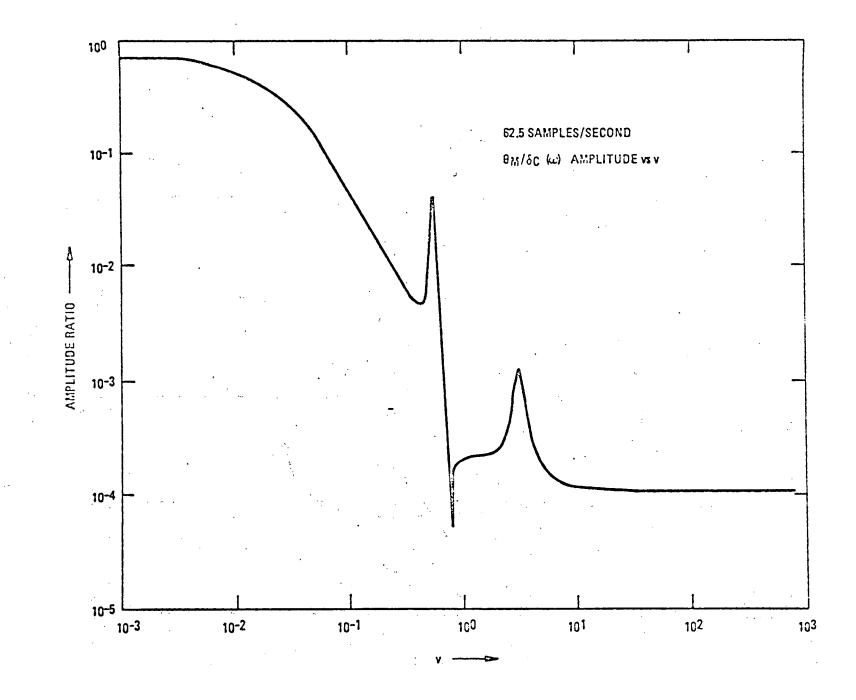

| 13.20 | Nichols Chart Discrete System                       | 202 |

| 13.21 | Nichols Chart Discrete System                       | 204 |

| 13.22 | Filter Implementation                               | 205 |

| 13.23 | Operational Processes                               | 207 |

| 13.24 | Canonic Form                                        | 210 |

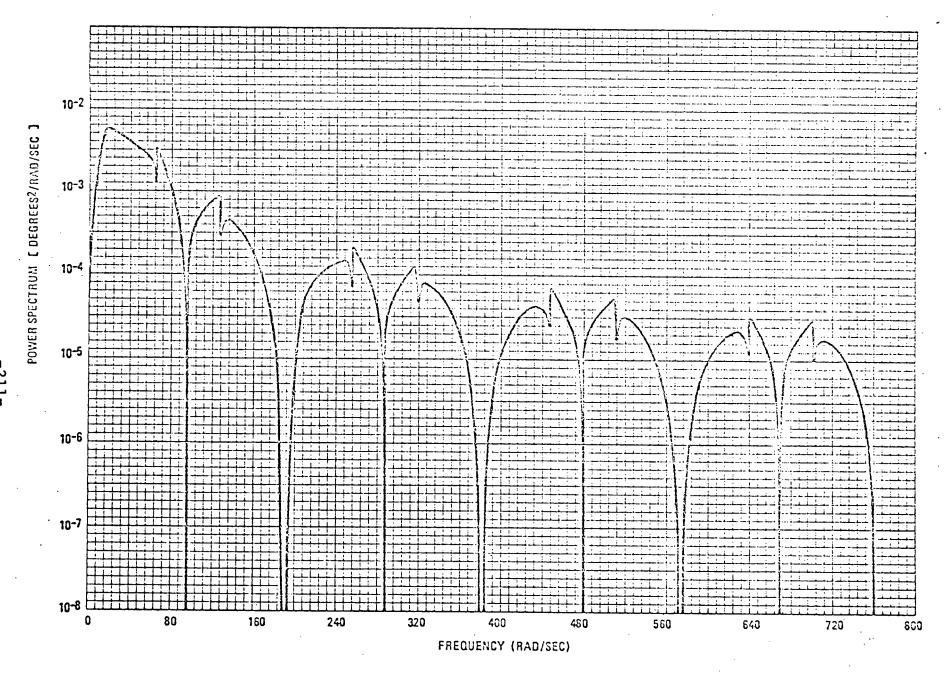

| 13.25 | Pickoff Noise Input 30.5 samples/sec                | 211 |

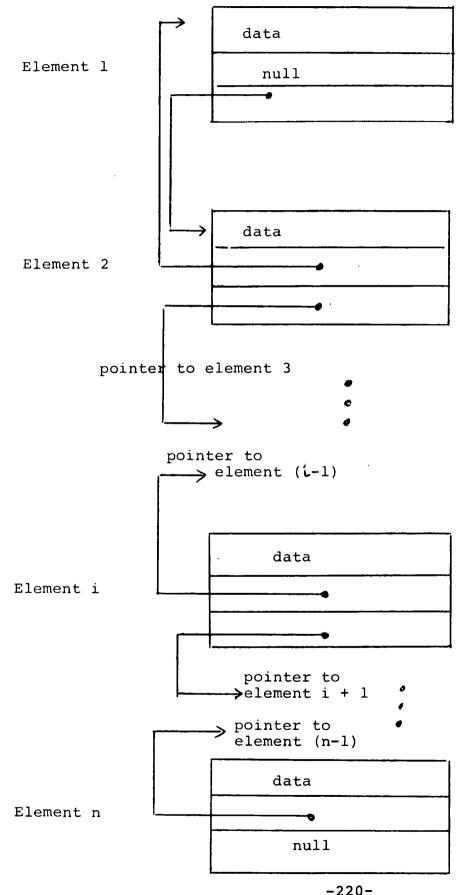

| 14.1  | Threaded List Structure                             | 220 |

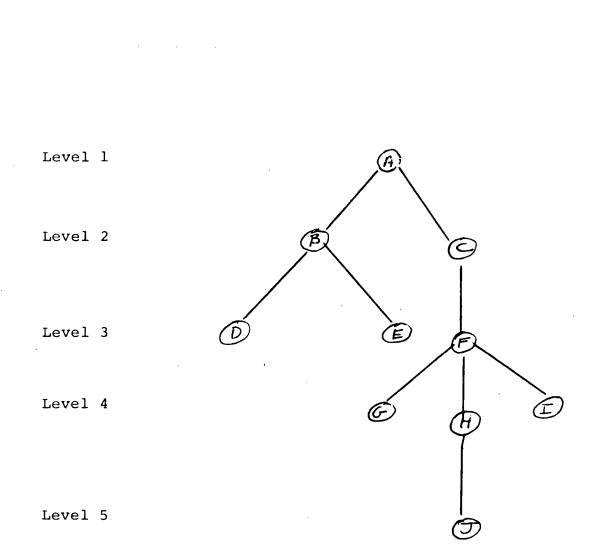

| 14.2  | Example of a Tree Structure                         | 221 |

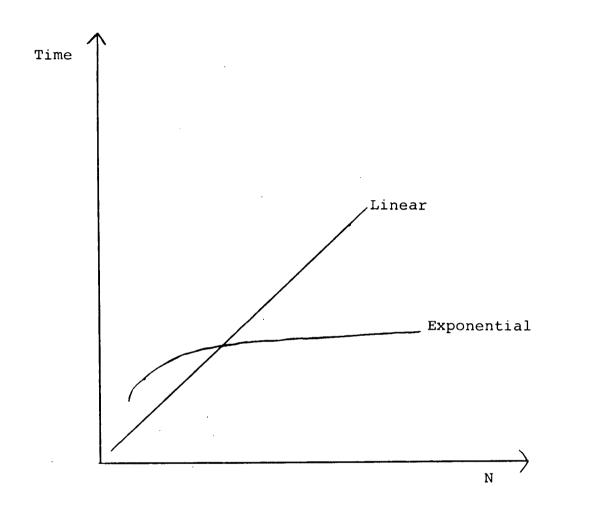

| 14.3  | Comparison of Search Times                          | 224 |

| 14.4  | Example of a Shell Sort                             | 226 |

| 14.5  | Example of a Radix Sort                             | 227 |

| 14.6  | Example of a Partitioned Data Set                   | 229 |

| 15.1  | Program Organization                                | 247 |

| 15.2  | Scope of Names                                      | 248 |

| 15.3  | Example of Name Scope                               | 249 |

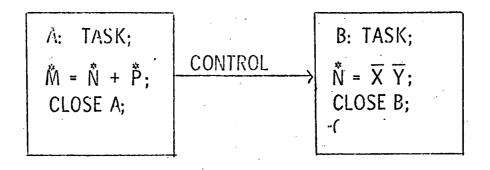

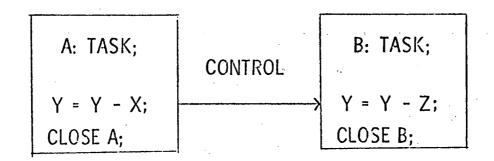

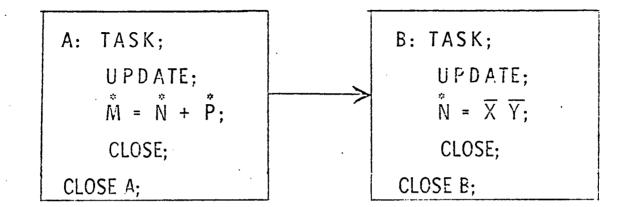

| 15.4  | Background in Problems of Controlled<br>Shared Data | 251 |

| 15.5  | Use of Update Block to Avoid Data Conflicts         | 252 |

| 16.1  | Task State Transition Diagram, $\chi \downarrow V$  | 267 |

# Figure

÷

| 16.2 | Control of Shared Data                                     | 277 |

|------|------------------------------------------------------------|-----|

| 16.3 | System Director Elements                                   | 280 |

| 16.4 | Structure of Operating Memory                              | 284 |

| 16.5 | Format of Event Control Block                              | 286 |

| 16.7 | Format of Event Descriptor Byte                            | 286 |

| 16.6 | Event Handling                                             | 288 |

| 17.1 | The Apollo Digital Simulator                               | 297 |

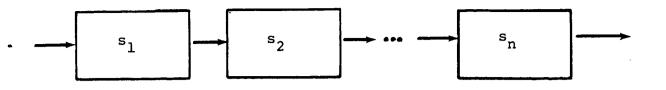

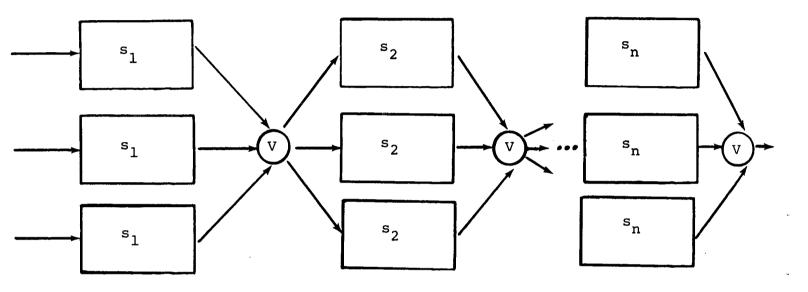

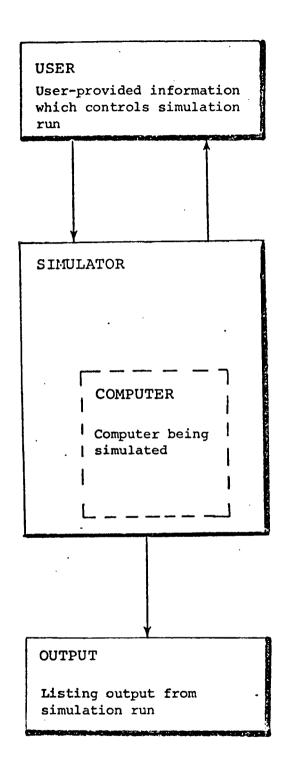

| 17.2 | Basic Simulator: Input, Simulator, Output                  | 300 |

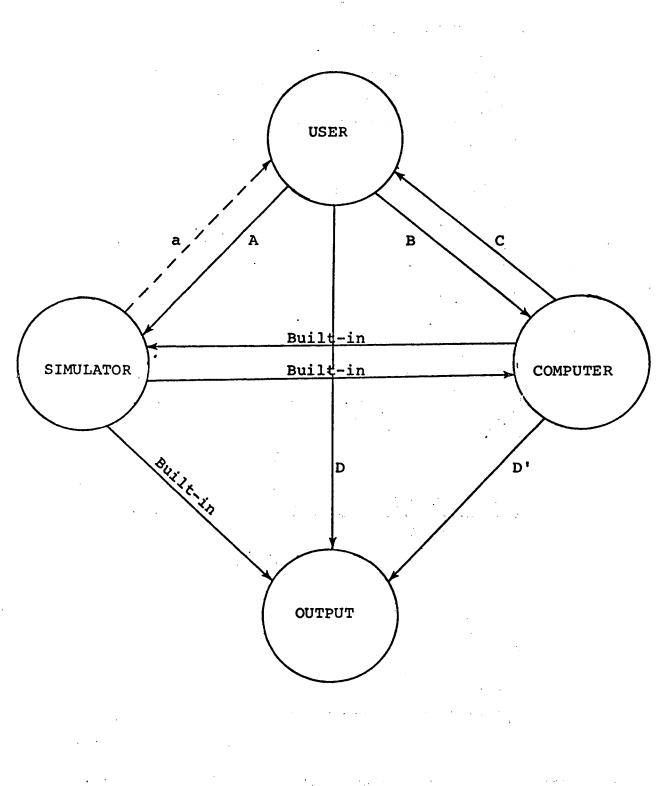

| 17.3 | Simulator Logical Partitions                               | 301 |

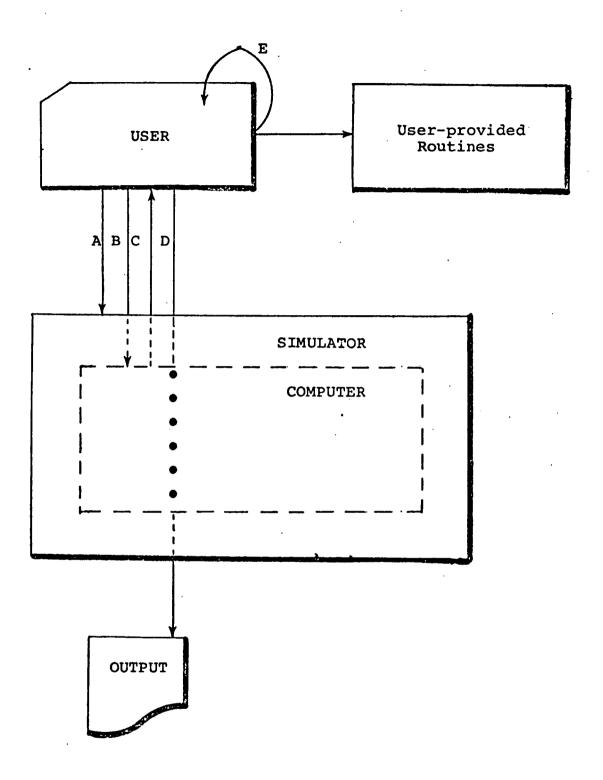

| 17.4 | Simulator Physical Control Flow                            | 302 |

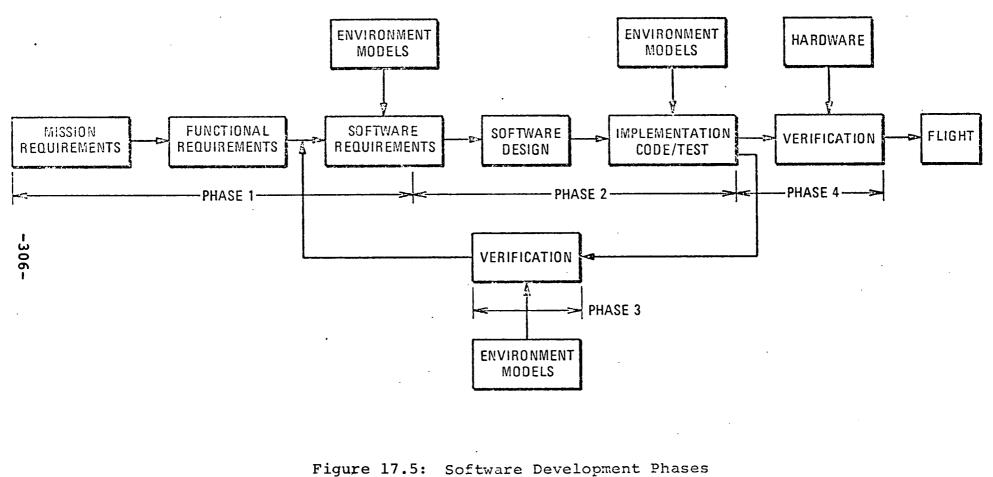

| 17.5 | Software Development Phases                                | 306 |

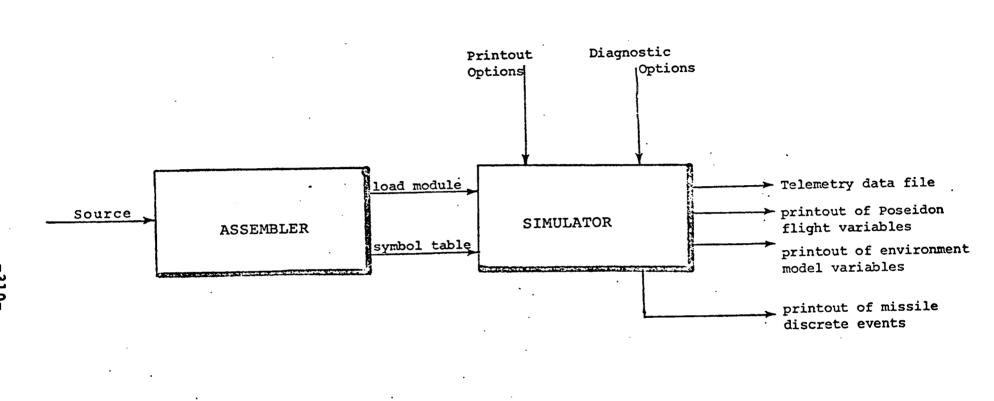

| 17.6 | Poseidon Assembler and Simulator Configuration             | 310 |

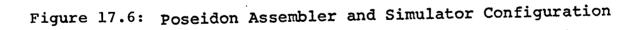

| 17.7 | Poseidon Simulator Configuration                           | 311 |

| 19.1 | Apollo 204 Command Module Entry Simulator<br>Configuration | 339 |

# PART I

## INTRODUCTION

.

,

INTERMETRICS INCORPORATED • 701 CONCORD AVENUE • CAMBRIDGE, MASSACHUSETTS 02138 • (617) 661-1840

•

PRECEDING PAGE BLANK NOT FILMED

## CHAPTER 1

### INTRODUCTION TO SYSTEM ANALYSIS

#### 1-1.0 Introduction

With the continuous advance of technology more and more automation is being introduced into our society. Combined electrical and mechanical systems have been implemented which reach all of us; e.g., billing by computer, satellite communications, medical information, air traffic control, etc. The extent to which these large systems have evolved and influenced our society should not be a surprise. They were predicted by Norbert Wiener [1-3] over ten years ago. Moreover, the future should see more of these systems designed and built to assist man in his everyday life.

The methods that have been developed and used in designing these systems constitute a major part of our engineering literature. However, the system designer wishing to learn these methods faces an enormous literature search to find the significant papers. Hundreds of journals and textbooks dealing with system design have already been published, and many more appear each year. To investigate this entire literature would be a large, time consuming task. So far no publication has summarized the major design techniques and experience in a single volume to aid the student of system design. Indeed such an undertaking would be very ambitious considering the diverse areas in which large systems have been applied. Yet, some of the known design methods in a specific discipline, such as aerospace computer design, could be consolidated in a single volume. If this information is supplemented with practical experience gained in implementing such systems, the resulting publication would be a valuable aid to the aerospace computer designer. He could easily find specific design methods related to his field of interest and the results of having used these methods in the past.

Preceding page blank

The purpose of this document is to provide such an aid for the system designer. Specifically, we will concentrate on analysis techniques for aerospace data management systems. The known analysis and design methods in this area will then be combined with our own experience in designing and implementing the Apollo Guidance System to produce the final contents of this document.

## 1-2.0 Content of Study

Trying to answer the question of "what is system design", in all but the trivial sense, is perhaps as difficult as trying to answer the question of "what is a system". The answer is ellusive because systems take many forms and to include all these in a single definition is difficult. A general purpose computer with all its peripherals is a system, as is its software operating system. Then again, the combined hardware/software may also be considered a system but on a higher level. As a further example consider the navigation and guidance hardware for a spacecraft which includes gyros, accelerometers, autopilot, etc. This is certainly a system composed of each of its subsystems.

We will not attempt a precise definition of a system here. Instead, we will rely on our intuitive concepts of what a system is when discussing data management system analysis and design, the main focus of this document. That intuition tells us that in a trivial sense a system is an organized collection of interacting elements [4]. The word analysis stems from the ancient Greek words that mean "to break up", and the modern usage is best described as "separating a complex into its constituants and examining these elements and their inter-relationships in forming the whole." In this sense, analysis is a feedback procedure in the design of engineering systems: The system must exist before it can be analyzed.

Synthetic procedures for data management systems are not complete enough to be described as a collection of precise procedures. The synthesis or creative process must be, for the most part, left to the genius of the designer. Where synthetic techniques exist, we have included them in this report.

Since systems take many forms; e.g., computation, communication, control, etc., many methods for system design have been developed. Not all these methods are applicable to every system that is to be implemented. However, each method has proven its value under specific design conditions. Examples of these methods are:

- a. simulation

- b. performance monitoring

- c. reliability analysis

- d. redundancy

- e. benchmarks, etc. -4-

In our study we will survey the state of the art of 12 such design techniques. Each chapter will deal with a specific technique, and numerous examples will be cited of how these techniques have been successfully used implementing large systems. No chapter exhausts the known information on a topic since this would require a text devoted to each topic. Hence, a bibliography is provided with each chapter to direct the reader to further information on these design methods. In addition, two appendices provide bibliographies on important areas in which the designer should be knowledgeable but are beyond the scope of this contract to include as chapters of this document.

#### 1-3.0 A Step Toward Unity

There is a certain danger in presenting the variety of topics that we will present in this report. Such a presentation can lead the reader to the conclusion that system analysis is an incohesive process involving the application of seemingly unrelated methods. To avoid this thought we now stress the overall unity that the system design process should have. Each analysis technique that we will present is a part of this overall process, and the designer uses these as appropriate system questions arise. Each step of analysis that he performs using these methods, with which he should be familiar, is an important step bringing him closer to achieving the complete design of his system. We hope the reader will keep this point of view in mind when reading this study.

To unify the system design methods which we will present, we begin by describing a hypothetical system that we wish to build. The statement of the problem will lead us to an understanding of the necessary elements of the system. Then we will see which design methods enable us to optimize the specification of these elements and their interactions.

## 1-3.1 Statement of Problem

A manned scientific laboratory is to be put in orbit around Mars. Its purpose is to observe the planet and conduct scieitific experiments. Visual data of the planet's surface as well as the results of the experiments will be transmitted back to Earth. In addition, the crew on board the laboratory will receive communications sent from Earth to start, stop or modify the experiments based upon previously collected data. This laboratory must be designed for at least five years of use and have safety features to safeguard the lives of its crew. Some of the experiments it will conduct are the following:

- a. study atmospheric phenomena of Mars;

- b. study terrain for possible future landing site;

- c. identify and investigate any life forms on the planet;

- d. monitor quasi-stellar objects existing beyond our solar system;

- e. study the composition and distribution of interstellar matter; etc.

In general, this laboratory will conduct experiments to try to answer some of the important questions of planetary geology and astrophysics [5]. Our problem is to determine the computational systems necessary to support this laboratory. A first step is to understand its computational requirements, and then we can decide upon the needed hardware and software. We begin this analysis by further reflection upon the above problem.

## 1-3.2 Discussion of Problem

The requirements for at least five years of use demands that the system design must employ reliability analysis. Failure detection methods must be built into the system and recovery algorithms established should a failure occur. This detection and recovery is especially important for the life support systems. Since the laboratory will be placed in orbit, size, weight and power consumption might well be constraints around which the overall system must be designed. This fact implies a cost constrained reliability analysis is necessary. That is, the most reliable system is desired which does not exceed the given design constraints.

The large amounts of scientific data that must be transmitted back to Earth could pose a communication bandwidth problem. A solution is to process as much of the data as possible on an airborne computer in the laboratory. Then only the computed results have to be communicated, thus reducing the amount of information that needs to be transmitted. In addition, these results will tell the crew of the laboratory how to optimally conduct their future experiments.

The algorithms for the airborne computer must be designed and their execution rates determined. This information along with reliability requirements will help determine what computer should be chosen. (Computer reliability is crucial since experiments conducted in real time can be invalidated because of a computer failure for a sufficiently long time.) The choice can be aided by constructing a data book containing the characteristics of available aerospace computers. Part of this data would be the results of running benchmark programs on each of the candidate computers. These benchmarks measure performance characteristics under various computational loads. All of this data will then enable an intelligent choice of the airborne computer chosen.

The data may alternatively indicate that there is no available computer that can do the given job. In this case an aerospace computer with the designed characteristics will have to be designed and built.

The use of an airborne computer raises several software system issues. An executive system must be designed and implemented to control execution of the necessary processes. In addition, the data formats to represent scientific information within the computer must be specified so that program design can be optimized. Finally, the software system designer must decide if a higher order language will be used to encode the computer's algorithms. When all these issues have been settled, work on the software system can proceed.

The communication system between the laboratory and Earth raises additional questions. Visual and scientific data will be transmitted to Earth, and the laboratory will receive information from Earth partially directing its experiments. To insure economy in the transmitted data and reduce signal distortion from atmospheric and galactic sources, transform methods might be needed to encode transmitted data. If this is the case, more decisions must be made concerning what transform to use and whether to implement it in hardware or software.

On the other **side** of the communication link the data received on Earth must be further processed to provide

scientists with valuable information on the nature of Mars, the solar system and the galaxy. Since large amounts of data can be expected, a sufficiently powerful computer is necessary to process this data. This computer will probably be a commercial machine with an already existing operating system. However, the software for processing the received data will have to be designed and implemented, depending upon the algorithms provided by the scientists directing the experiments.

Once these systems have been specified, their overall design and performance must be verified. Microsimulation is the best method for the airborne computer. This is a standard way of verifying aerospace computer software. On the other hand, the overall system can be modeled using Markov analysis and queueing theory. Then the model can be simulated on a large commercial computer yielding valuable data on the expected performance of the entire system. Most importantly, this simulation will show if the system has been properly designed by showing whether it can successfully meet the computational needs of the orbiting laboratory.

## 1-4.0 Summary

The overall communication and computation system required is shown in Figure 1.1. We have arrived at the necessary elements and their interactions from an analysis of the given problem combined with our knowledge of system analysis techniques. As we have seen, the design of this entire system has many phases and requires many design and analysis methods. The system designers must be familiar with the proper use of all of these methods. This knowledge combined with an understanding of the given problem will help insure system design.

-9-

#### REFERENCES

- Wiener, N., <u>The Human Use of Human Beings</u>, (Houghton Mifflin Co., Boston, 1950).

- Wiener, N., <u>God and Golem</u>, Inc., (M.I.T. Press, Cambridge, Mass., 1964).

- Wiener, N., <u>Cybernetics</u>, 2nd ed., (M.I.T. Press, Cambridge, Mass., 1961).

- 4. Von Bertalanffy, L., "General System Theory", in <u>Main</u> <u>Currents in Modern Thought</u>, 71(75), 1955.

- 5. Sciama, D.W., Modern Cosmology, (Cambridge University Press, New York, 1971).

.

# PART II

# ANALYTIC TECHNIQUES

.

INTERMETRICS INCORPORATED • 701 CONCORD AVENUE • CAMBRIDGE, MASSACHUSETTS 02138 • (617) 661-1840

-11-

### CHAPTER 2

### RELIABILITY ANALYSIS

## 2.1.0 Introduction

Reliability analysis is one tool in the kit bag of the system designer. It is useful when considering many problems associated with Data Management such as redundancy, on board checkout, switch over policy and so forth. This chapter develops an approach to reliability analysis that is useful under circumstances that arise frequently. These results will then be expanded in Chapter 3.

A typical problem in reliability analysis is the computation of the probability of failure as a function of time of a system of components, each subject to random failure, characterized by a failure rate  $\lambda$  or its inverse, the mean time to failure,  $\tau$ . Solutions to this problem can be obtained in the general literature. This chapter considers a somewhat different problem statement: Suppose that a system of m components are arranged in parallel (redundantly). What is the average time it will take for only n of these components to be left. We will develop a general solution to this problem, a simple approximate solution, and an illustration problem that shows that the formulae derived are useful for a class of problems encountered in space flight.

### 2.2.0 Derivation

We will start with a formula that describes the probability that exactly n systems remain out of m, as a function of time.

$$P_{n/m} = \begin{pmatrix} m \\ n \end{pmatrix} \begin{pmatrix} 1-e^{-\lambda t} \end{pmatrix} m-n \begin{pmatrix} e^{-n\lambda t} \end{pmatrix}$$

(2.1)

The three terms in this product are first: the binomial coefficient which enumerates the number of ways that n specific components can be permutated out of m components, second: the probability that at least m-n components fail, third: the probability that at least n components have not failed.

We now note that the probability that the  $(n+1)^{th}$  component fails in time t+ $\Delta t$ , as a function of t is the probability distribution function for the random variable, the failure of the  $(n+1)^{th}$  component.

Preceding page blank

-13-

This function is the product of the probability that exactly n+1 systems exist at t and that one fails in  $t+\Delta t$ . Using equation (2.1) this can be seen to be

$$P_{[n/m]} = \begin{pmatrix} m \\ n+1 \end{pmatrix} \begin{pmatrix} 1-e^{-\lambda t} \end{pmatrix} m - (n+1) e^{-t(n+1)} (n+1) \lambda, \quad (2.2)$$

where we let  $\Delta t = 1$ .

The terminology P [n/m] is used because the event that the  $(n+1)^{th}$  component fails is the event that the system makes the transition to n systems remaining. Note that P n/m and P [n/m] mean different things and have different formulae. We now compute the mean time to "come down to" n components from m. The mean is by definition:

$$\tau_{n/m} = \int_{0}^{\infty} t P_{[n/m]} (t) dt \qquad (2.3)$$

The integral need only be taken over positive time since  $P_{[n/m]} = 0$  for t<0.

Substituting (2.2) into (2.3) we obtain  $\tau_{n/m} = \lambda \binom{m}{n+1} (n+1) \int_{0}^{\infty} t (1-e^{-\lambda t})^{m-n-1} e^{\lambda t (-n-1)} dt. \qquad (2.4)$

Rearrangements yield

$$\tau_{n/m} = \binom{m}{n+1} (n+1) \int_{0}^{\infty} t (e^{\lambda t} - 1)^{m-n-1} e^{-\lambda tm} dt, \text{ and} \qquad (2.5)$$

the term  $(e^{\lambda t}-1)^{m-n-1}$  can be expanded in a binomial series as

$$(e^{\lambda t} - 1)^{m-n-1} = \sum_{j=0}^{m-n-1} (m-n-1) e^{\lambda t (m-n-1-j)} (-1)^{j}$$

(2.6)

This permits after more manipulation,

$$\tau_{n/m} = \lambda \begin{pmatrix} m \\ n+1 \end{pmatrix} \begin{pmatrix} n+1 \end{pmatrix} \sum_{\substack{j=0 \\ j=0}}^{m-n-1} \left\{ \begin{pmatrix} m-n-1 \\ j \end{pmatrix} \begin{pmatrix} (-1)^{j} \\ -1 \end{pmatrix} \right\}^{\infty} te^{\lambda t \begin{pmatrix} -n-1-j \end{pmatrix}} dt \left\{ \begin{pmatrix} 2.7 \end{pmatrix} \right\}$$

The integral  $\int_{0}^{\infty} te^{-wt} dt can be shown$ to be equal to  $\frac{1}{w^{2}}$ .

Using this fact, we can write

$$\tau_{n/m} = \binom{m}{n+1} \binom{m-n-1}{j} \binom{m-n-1}{j} \binom{(n-1)^{j}}{(n+1+j)^{2}}$$

(2.8)

In equation (2.8) we have stated the desired result nondimensionalized by dividing by  $\tau$ , the mean time to failure. Table 1 presents values of  $\tau_{n/m}$  for values of m, the number of components started with, and n, the number of components which defines the time when the mission must be ended.

|          | n | 1 | 2   | 3    | 4    |

|----------|---|---|-----|------|------|

| ↓<br>End | 0 | 1 | 1.5 | 1.83 | 2.08 |

|          | 1 | 0 | .5  | .84  | 1.1  |

| with     | 2 |   | 0   | .33  | .60  |

|          | 3 |   |     | 0    | .25  |

| → | Start | with |

|---|-------|------|

|   | JLALL |      |

TABLE 1: Values of  $\tau_{n/m}$  for small m, n

Equation (2.8) is not difficult to evaluate numerically for small m and n. However, it can be tedious for large values. We will therefore turn to the evaluation of a somewhat similar parameter which has the virtue of being computable using natural log tables.

We begin again with equation (2.2). This time we compute the time that it is most likely that the system makes the transition from n+1 components unfailed to n components unfailed. The maximum likely-hood occurs where

$$dP_{[n/m]} / dt = 0$$

(2.9)

We solve for condition (2.9) and obtain the desired relationship

$$T_{ml} / \tau = ln(\frac{m}{n+1})$$

(2.10)

We note that T  $_{ml}/\tau$  is single valued, and therefore no question need arrise about relative maxima. Table 2 presents values of T  $_{ml}/\tau$  in a manner similar to Table 1.

|             | m | 1 | 2   | 3   | 4    |

|-------------|---|---|-----|-----|------|

|             | 0 | 0 | .69 | 1.1 | 1.38 |

| ¥           | l |   | 0   | .40 | .69  |

| End<br>With | 2 |   |     | 0   | .28  |

| ¥           | 3 |   |     |     | 0    |

$\rightarrow$  Start with  $\rightarrow$

TABLE 2: Values of

$$T_{ml}/\tau$$

for small m, n

It will be seen that the maximum likelyhood formula yields a smaller T/ $\tau$  than does the mean. In fact, the value  $\tau_n/m/\tau$  lies somewhere between  $\ln(\frac{m}{n+1})$  and  $\ln(\frac{m}{n})$ , which is proved in Chapter 3.

The logarithmic character of the  $T_{ml}/\tau$  formula points out quite clearly the well known difficulty associated with obtaining lifetimes long with respect to  $\tau$ . The ratio of m to n must be squared to double the "lifetime of the system", and so forth.

We now turn to an example problem that illustrates the significance of these results. It has been determined that a piece of equipment is necessary during re-entry from space. It has a  $\tau = 1000$  hours. Re-entry takes one hour. The probability that the equipment fails prior to or during re-entry must be kept below .001. The equipment can be considered to be redundantly spared with no reliability associated with switch over. Compare the redundancy required for the following missions:

- Mission (A): A space flight of 1000 hours. Once the trip begins it cannot be shortened.

- Mission (2): A space flight which can be terminated at any time (by a one hour re-entry) if necessary because of equipment failure. The equipment must be spared such that the average time until termination due to equipment failures is 1000 hours.

We consider mission (B) first.

Step 1: Calculate the number of components necessary at the beginning of re-entry to assure no worse than .001 probability of failure.

$$P_{f} = (1 - e^{-t/\tau})^{n}$$

Try n=1:

$$P_f = .001$$

; which is o.k.

Step 2: We now compute how many we have to start with (m) to end up with the one we need. Table 1 indicates that 4 systems will yield an average lifetime of 1100 hours.

We now turn to mission (A). We compute the probability that all m systems fail in 1001 hours.

$$P_f = (1 - e^{-t/\tau})^m$$

For our problem  $P_f \leq .001$ . We compute:

$$m \leq \frac{\log (P_f)}{\log (1-e^{-1000/1001})}$$

m < 16 + = 17 systems.

We see that 17 systems are required to achieve specification B, while 4 are required to achieve specification B. It makes a difference how the requirements are stated. Mission B is more like what might be desired for a near earth mission such as a space shuttle.

## 2.3.0 Conclusions

This chapter illustrates an approach to reliability analysis which emphasizes the situation where the length of the mission is a random variable whose length can be characterized by statistical parameters. This approach permits the designer some increased latitude in formulating redundancy policy, as shown in the examples. However, one should examine higher statistical moments of equation (2.2) in order to be certain that the standard deviation is stable and that the mean is useful in characterizing the distribution. This has not been done although the method of integration by parts described after equation (2.7) would apply as well to higher moments. Therefore, the obtaining of higher moments is straight forward.

#### CHAPTER 3

## REDUNDANT COMPONENT FAILURE ANALYSIS

## 3-1.0 Introduction

Required system reliability often must be achieved through redundancy of critical subsystems or components. Typical questions then to be answered by the system designer are these. How many redundant components are necessary to provide a specified operating lifetime with a prescribed probability of success? Conversely, what minimum lifetime can be guaranteed with a prescribed confidence level for a given number of redundant components? What mean lifetime can be expected for this number of components? The design parameters of interest are clearly interrelated, and include the following:

- m original number of redundant components

- n number required for successful operation

- T operating lifetime

- $\tau$  mean time to failure

- P probability of success (operation)

- Q 1-P, probability of failure

#### 3-2.0 Summary of Results

A single component exhibiting an exponential failure rate has the following probabilities of successful operation p and failure q during a time interval t,

$$p = e^{-\lambda t}$$

(3.1)

$$q = 1 - p = 1 - e^{-\lambda t}$$

(3.2)

where  $\lambda$  is the mean rate of failure. The mean time to failure  $\tau$  is

$$\tau = 1/\lambda \tag{3.3}$$

The minimum component lifetime T during which the probability of success is  $\geq P$ , or probability of failure is < Q = 1 - P, is

$$T = -\tau \ln P = \tau \left( Q + \frac{1}{2}Q^2 + \frac{1}{3}Q^3 + \dots \right)$$

(3.4)

Given m identical redundant components characterized by the exponential failure rate above, the probability that exactly n remain in operation (i.e., that m-n fail) during a time interval t is

$$P_{n/m} = {\binom{m}{n}} p^{n} q^{m-n}$$

$$= {\binom{m}{n}} (e^{-\lambda t})^{n} (1-e^{-\lambda t})^{m-n}$$

(3.5)

The probability that at least n components remain operational during t (or that at most m-n fail) is

$$p_{n/m}^{+} = \sum_{k=n}^{m} {m \choose k} p^{k} q^{m-k}$$

$$= 1 - \sum_{k=0}^{n-1} {m \choose k} p^{k} q^{m-k}$$

(3.6)

The time of maximum probability that exactly n components remain unfailed, and that probability, are

$$t_{n/m}^{\star} = \tau \ln \frac{m}{n}$$

(3.7)

$$(p_{n/m})_{max} = {m \choose n} n^{n} (m-n)^{m-n}/m^{m}$$

(3.8)

The mean time to failure of one of the remaining n components, i.e., the mean time for the system to degenerate to n-l components, is given by

$$\tau_{n-1/m} = \tau \left(\frac{1}{n} + \frac{1}{n+1} + \dots + \frac{1}{m}\right)$$

(3.9)

This time can be bracketed by logarithmic bounds,

$$\tau \ln \frac{m+1}{n} < \tau_{n-1/m} < \tau \ln \frac{m}{n-1}$$

(3.10)

The standard deviation of this degeneration time is

$$\sigma_{t_{n-1/m}} = \tau \left( \frac{1}{n^2} + \frac{1}{(n+1)^2} + \dots + \frac{1}{m^2} \right)^{1/2}$$

(3.11)

which can be bracketed by similar bounds,

$$\tau \sqrt{\frac{m-n+1}{(m+1)n}} < \sigma_{t_{n-1/m}} < \tau \sqrt{\frac{m-n+1}{m(n-1)}}$$

(3.12)

The minimum system lifetime T during which the probability that at least n components remain equals P, or during which the probability of at most m-n failures equals Q = 1-P, is obtained from

$$Q = \sum_{k=0}^{n-1} {m \choose k} (1-q)^k q^{m-k} \rightarrow q(Q)$$

(3.13)

$$T_{n/m} = -\tau \ ln \ (1-q)$$

(3.14)

When system failure corresponds to all components failed, (i.e., operation requires  $n \ge 1$ ), the minimum system lifetime with probability P = 1 - Q) is

$$T_{1/m} = -\tau \ln (1 - Q^{1/m})$$

$$= \tau (Q^{1/m} + \frac{1}{2}Q^{2/m} + \frac{1}{3}Q^{3/m} + ...)$$

(3.15)

# 3-3.0 Component Failure Statistics

To begin, we presume that the m redundant components are identical, and that they operate (and fail) independently. The probability of success or failure of each component is assumed to be a known function of time:

> p = p(t) = probability of successful operationq = q(t) = probability of failure (3.16)

with

$p + q \equiv 1$

In the most commonly observed case, operating components exhibit an exponential failure rate. The probability that a component will fail in the next instant dt, given that it is operating at t, is a constant independent of how long it has been operating:

Prob

$$[t \leq t_f < t + dt | t_f \geq t] = \lambda dt$$

(3.17)

where  $t_f$  represents the time of failure and  $\lambda$  is a constant which equals the mean failure rate. This probability relation can be expressed as follows,

$$dq = p \lambda dt = (1-q) \lambda dt \qquad (3.18)$$

That is, the incremental probability of failure between t and t+dt equals the probability that no failure has yet occurred, multiplied by a constant times the interval dt. The consequence of (3.18) is evidently

$$p(t) = e^{-\lambda (t-t_0)}$$

(3.19)

$q(t) = 1 - e^{-\lambda (t-t_0)}$

(For simplicity, we henceforth set t = 0.) Hence, the incremental failure probability in the interval dt is

$$dq = e^{-\lambda t} \lambda dt \qquad (3.20)$$

We next define the one-component failure probability density f(t) as follows:

$$f(t) = \frac{d}{dt} q(t) = \lambda e^{-\lambda t}$$

(3.21)

In terms of f, the probabilities of failure and success can be written

$$q(t) = \int_{0}^{t} f(t') dt'$$

(3.22)

$p(t) = 1 - \int_{0}^{t} f(t') dt' = \int_{t}^{\infty} f(t') dt'$

Further, the mean time to failure  $\tau$  for a single component is defined and obtained as

$$\tau \equiv \int_{0}^{\infty} t f(t) dt = \int_{0}^{\infty} t\lambda e^{-\lambda t} dt = \frac{1}{\lambda}$$

(3.23)

For sake of interest we note in Table 1 the success and failure probabilities for a single component as functions of time measured in  $\tau$ -units:

| <u>p(t)</u> | <u>q(t)</u> | <u>t/τ</u> |

|-------------|-------------|------------|

| .999        | .001        | .001       |

| .99         | .01         | .010       |

| .95         | .05         | .051       |

| .90         | .10         | .105       |

| .50         | .50         | .693       |

| .368        | .632        | 1.000      |

| .10         | .90         | 2.303      |

| .05         | .95         | 2.996      |

| .01         | .99         | 4.605      |

Table 1. Probabilities of success and failure of a single component as functions of operating time

The "half-life" of a large number of single components is

$$t_{.50} = .693 \tau$$

(3.24)

### 3-4.0 Redundant Computer Failure Statistics

Consider now m redundant components beginning independent operation at t=0. The joint failure probability density for these m components is the product of the individual densities:

$$f_{m}(t_{1}, t_{2}, \dots, t_{m}) = f(t_{1})f(t_{2})\dots f(t_{m})$$

$$= \lambda^{m} e^{-\lambda(t_{1}+t_{2}+\dots+t_{m})}$$

(3.25)

The probability that specific components 1 to n operate successfully, and components n+1 to m fail, during time t is

$$P_{1 \leftarrow n}(t) = \int_{t}^{\infty} dt_{1} \cdots \int_{t}^{\infty} dt_{n} \int_{0}^{t} dt_{n+1} \cdots \int_{0}^{t} dt_{m} f_{m}(t_{1}, \dots, t_{m})$$

$$= p(t)^{n} q(t)^{m-n}$$

(3.26)

The probability that any n components operate successfully, and the remaining m-n fail, during time t is then

$$p_{n/m} = {\binom{m}{n}} p^n q^{m-n}$$

(3.27)

where the binomial coefficient

$$\binom{m}{n} \equiv \frac{m!}{n! (m-n)!} = \frac{m (m-1) \dots (m-n+1)}{n (n-1) \dots 1}$$

(3.28)

gives the number of different ways that n components can be selected from a total of m. Note that  $p_{n/m}$  is the k=n term in the binomial expansion

$$(p+q)^{m} = \sum_{k=0}^{m} {m \choose k} p^{k} q^{m-k} \equiv 1$$

(3.29)

Equation (3.27) is valid in general for any component failure probabilities q = 1-p. For the exponential failure probabilities (3.19), eq. 3.27) becomes

$$p_{n/m}(t) = {\binom{m}{n}} (e^{-\lambda t})^n (1 - e^{-\lambda t})^{m-n}$$

(3.30)

In either case,  $p_{n/m}$  represents the probability that exactly n of m components remain operational after time t. It is evident that, since no components can fail in zero time,

$p_{n/m}(0) = \begin{cases} 1 & n=m \\ 0 & n < m \end{cases}$  (3.31)

The most probable time at which exactly n of m components remain can be obtained from eqs. (3.16) and (3.27) as follows:

$$\frac{d}{dq} p_{n/m} = {m \choose n} p^{n-1} q^{m-n-1} (m-n-mq) = 0$$

$$q_{n/m}^{\star} = \frac{m-n}{m} \rightarrow t^{\star} n/m$$

(3.32)

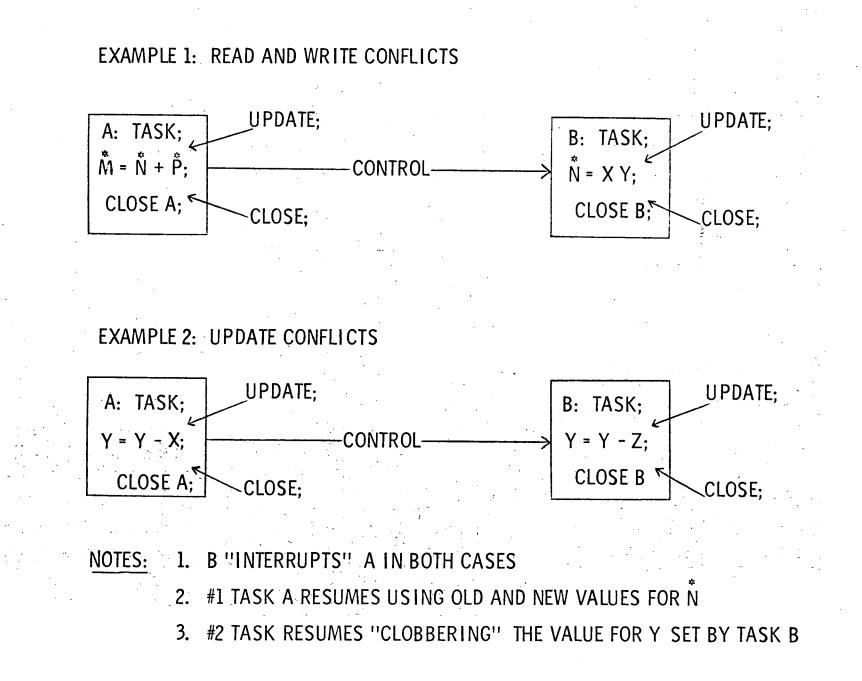

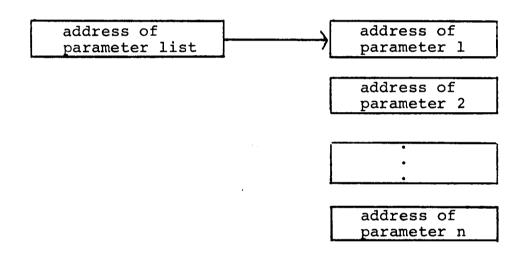

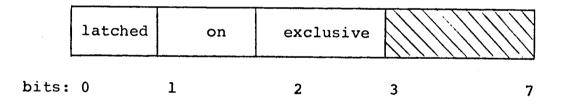

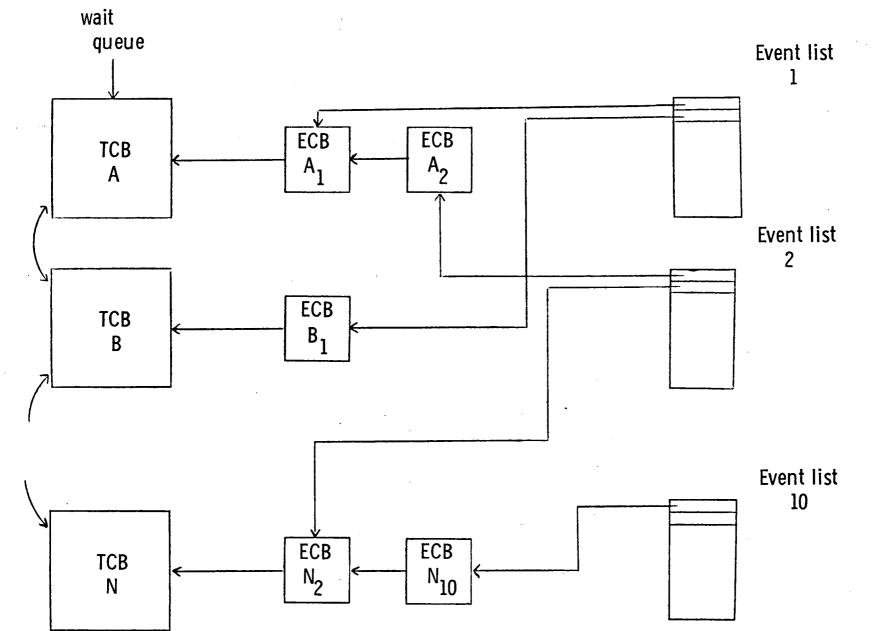

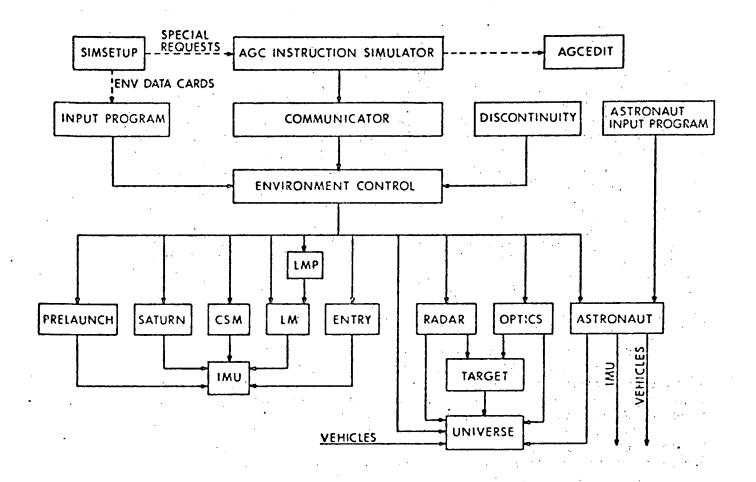

The corresponding maximum probability density at  $t_{n/m}^{\star}$  is