### NEPP Update of Independent Single Event Upset Field Programmable Gate Array Testing

### Melanie Berg, AS&D Inc. in support of the NEPP Program and NASA/GSFC

Melanie.D.Berg@NASA.gov

Kenneth LaBel: NASA/GSFC

Michael Campola: NASA/GSFC

Jonathan Pellish: NASA/GSFC

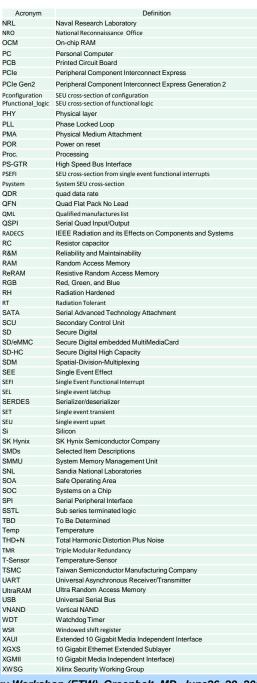

| Acronym                                                                                         | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1MB                                                                                             | 1 Megabit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3D                                                                                              | Three Dimensional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3DIC                                                                                            | Three Dimensional Integrated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ACE                                                                                             | Absolute Contacting Encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AHB                                                                                             | Advanced high performance bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ADC                                                                                             | Analog to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AEC                                                                                             | Automotive Electronics Council                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AES                                                                                             | Advanced Encryption Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AF                                                                                              | Air Force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AFRL                                                                                            | Air Force Research Laboratory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AMD                                                                                             | Advanced Micro Devices Incorporated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AMS                                                                                             | Agile Mixed Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ARM                                                                                             | Acorn Reduced Instruction Set Computer Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AXI                                                                                             | Advanced extensible interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BAE                                                                                             | British Aerospace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BGA                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                 | Ball Grid Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BOK                                                                                             | Body of Knowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BTMR                                                                                            | Block triple modular redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BYU                                                                                             | Brigham Young University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CAN                                                                                             | Controller Area Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CBRAM                                                                                           | Conductive Bridging Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CCI                                                                                             | Correct Coding Initiative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CGA                                                                                             | Column Grid Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CMOS                                                                                            | Complementary Metal Oxide Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CN                                                                                              | Xilinx ceramic flip-chip (CF and CN) packages are ceramic column<br>grid array (CCGA) packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| COTS                                                                                            | Commercial Off The Shelf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CRC                                                                                             | Cyclic Redundancy Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CRÈME                                                                                           | Cosmic Ray Effects on Micro Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CRÈME MC                                                                                        | Cosmic Ray Effects on Micro Electronics Monte Carlo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CSE                                                                                             | Crypto Security Engin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CU                                                                                              | Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D-Cache                                                                                         | defered cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DCU                                                                                             | Distributed Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DDR                                                                                             | Double Data Rate (DDR3 = Generation 3; DDR4 = Generation 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DFF                                                                                             | Flip-flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DMA                                                                                             | Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DSP                                                                                             | Digital Signal Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DOI                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| dSPI                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| dSPI                                                                                            | Dynamic Signal Processing Instrument                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DTMR                                                                                            | Dynamic Signal Processing Instrument Distributed triple modular redundancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DTMR<br>Dual Ch.                                                                                | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DTMR<br>Dual Ch.<br>DUT                                                                         | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DTMR<br>Dual Ch.<br>DUT<br>ECC                                                                  | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DTMR Dual Ch. DUT ECC EDAC                                                                      | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction                                                                                                                                                                                                                                                                                                                                                                                                           |

| DTMR Dual Ch. DUT ECC EDAC EEE                                                                  | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical                                                                                                                                                                                                                                                                                                                                                             |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC                                                             | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control                                                                                                                                                                                                                                                                                                                               |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB                                                        | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge                                                                                                                                                                                                                                                                                                 |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS                                                   | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer                                                                                                                                                                                                                                                                  |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS ESA                                               | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency                                                                                                                                                                                                                                            |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMMB EPCS ESA eTimers                                       | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers                                                                                                                                                                                                                               |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS ESA eTimers ETW                                   | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop                                                                                                                                                                                               |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMAC EMB EPCS ESA eTimers ETW FCCU                          | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit                                                                                                                                                             |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS ESA eTimers ETW FCCU FeRAM                        | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory                                                                                                                          |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS EST ETIW FCCU FCERM FIFER                         | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor                                                                                              |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMMB EPCS ESA eTimers ETW FCCU FeRAM FIRE                   | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor Finite impulse response filter                                                               |

| DTMR Dual Ch. DuT ECC EDAC EEE EMAC EMIB EPCS ESA eTimers ETW FCCU FeRAM FinFET FIR FPGA        | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor Finite Impulse response filter Field Programmable Gate Array                                 |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS EST ETIMETS ETW FCCU FeRAM FinFET FIR FPGA FPU    | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor Finite impulse response filter Field Programmable Gate Array Floating Point Unit             |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS ESA eTimers ETW FCCU FPRAM FinFET FIR FPGA FPU FY | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor Finite impulse response filter Field Programmable Gate Array Floating Point Unit Fiscal Year |

| DTMR Dual Ch. DUT ECC EDAC EEE EMAC EMIB EPCS EST ETIMETS ETW FCCU FeRAM FinFET FIR FPGA FPU    | Dynamic Signal Processing Instrument Distributed triple modular redundancy Dual Channel Device under test Error-Correcting Code Error detection and correction Electrical, Electronic, and Electromechanical Equipment Monitor And Control Multi-die Interconnect Bridge Extended physical coding layer European Space Agency Event Timers Electronics Technology Workshop Fluidized Catalytic Cracking Unit Ferroelectric Random Access Memory Fin Field Effect Transistor Finite impulse response filter Field Programmable Gate Array Floating Point Unit             |

GCR

GEO

GIC

GPIO

GPU

GRC

**GSFC**

GOMACTech

Galactic Cosmic Ray

Conference

geostationary equatorial orbit

Global Industry Classification

General purpose input/output

NASA Glenn Research Center

Goddard Space Flight Center

Graphics Processing Unit

Government Microcircuit Applications and Critical Technology

### aranym

|              | Acronym                                                                       |

|--------------|-------------------------------------------------------------------------------|

| Acronym      | Definition                                                                    |

| GSN          | Goal Structured Notation                                                      |

| GTH/GTY      | Transceiver Type                                                              |

| GTMR<br>HALT | Global TMR Highly Accelerated Life Test                                       |

| HAST         | Highly Accelerated Life Test Highly Accelerated Stress Test                   |

| HBM          | High Bandwidth Memory                                                         |

| HDIO         | High Density Digital Input/Output                                             |

| HDR          | High-Dynamic-Range                                                            |

| HiREV        | High Reliability Virtual Electronics Center                                   |

| HMC          | Hybrid Memory Cube                                                            |

| HOST         | Hardware Oriented Security and Trust                                          |

| HP Labs      | Hewlett-Packard Laboratories                                                  |

| HPIO<br>HPS  | High Performance Input/Output High Pressure Sodium                            |

| HSTI         | High speed transceiver logic                                                  |

| I/F          | interface                                                                     |

| I/O          | input/output                                                                  |

| 12C          | Inter-Integrated Circuit                                                      |

| i2MOS        | Microsemi second generation of Rad-Hard MOSFET                                |

| IC           | Integrated Circuit                                                            |

| I-Cache      | independent cache                                                             |

| JFAC         | Joint Federated Assurance Center                                              |

| JPEG         | Joint Photographic Experts Group                                              |

| JPL          | Jet propulsion laboratory  Joint Test Action Group (FPGAs use JTAG to provide |

| JTAG         | access to their programming debug/emulation functions)                        |

| KB           | Kilobyte                                                                      |

| L2 Cache     | independent caches organized as a hierarchy (L1, L2, etc.)                    |

| LCDT         | NEPP low cost digital tester                                                  |

| LEO          | Low Earth Orbit                                                               |

| LET          | Linear energy transfer                                                        |

| L-mem        | Long-Memory                                                                   |

| LANL<br>LP   | Los Alamos National Laboratory Low Power                                      |

| LUT          | Look-up table                                                                 |

| LVCMOS       | Low-voltage Complementary Metal Oxide Semiconductor                           |

| LVDS         | Low-Voltage Differential Signaling                                            |

| LVTTL        | Low –voltage transistor-transistor logic                                      |

| LTMR         | Local triple modular redundancy                                               |

| LW HPS       | Lightwatt High Pressure Sodium                                                |

| M/L BIST     | Memory/Logic Built-In Self-Test                                               |

| Mil-STD      | Military standard                                                             |

| MAPLD        | Military Aerospace Programmable Logic Device                                  |

| MBMA<br>MFTF | Model-Based Missions Assurance                                                |

| µPROM        | Mean fluence to failure Micro programmable read-only memory                   |

| µSRAM        | Micro SRAM                                                                    |

| Mil/Aero     | Military/Aerospace                                                            |

| MIPI         | Mobile Industry Processor Interface                                           |

| MMC          | MultiMediaCard                                                                |

| MOSFET       | Metal-Oxide-Semiconductor Field-Effect Transistor                             |

| MP           | Microprocessor                                                                |

| MP           | Multiport                                                                     |

| MPFE         | Multiport Front-End                                                           |

| MPSoC        | Multiprocessor System on a chip                                               |

| MPU<br>Msq   | Microprocessor Unit message                                                   |

| MTTF         | Mean time to failure                                                          |

| NAND         | Negated AND or NOT AND                                                        |

| NASA         | National Aeronautics and Space Administration                                 |

| NASA STMD    | NASA's Space Technology Mission Directorate                                   |

| Navy Crane   | Naval Surface Warfare Center, Crane, Indiana                                  |

| NEPP         | NASA Electronic Parts and Packaging                                           |

| NGSP         | Next Generation Space Processor                                               |

| NOR          | Not OR logic gate                                                             |

| Definition                                | N' A SYA |

|-------------------------------------------|----------|

| Naval Research Laboratory                 |          |

| National Reconnaissance Office            |          |

| On-chip RAM                               |          |

| Personal Computer                         |          |

| Printed Circuit Board                     |          |

| Peripheral Component Interconnect Express |          |

|                                           |          |

### **Outline**

- FPGA test guidelines

- Microsemi RTG4 heavy-ion results.

- Xilinx Kintex-UltraScale heavy-ion results.

- Xilinx UltraScale+ single event effect (SEE) test plans.

- Development of a new methodology for characterizing SEU system response.

- NEPP involvement with FPGA security and trust.

### NEPP – Processors, Systems on a Chip (SOC), and **Field Programmable Gate Arrays (FPGAs)**

#### State of the Art COTS **Processors**

- Sub 32nm CMOS. FinFETs, etc

- ·Samsung, Intel, **AMD**

#### "Space" FPGAs

- Microsemi RTG4

- Xilinx MPSOC+

(future)

ESA Brave (future) "Trusted" FPGA

#### **Graphics Processor Units (GPUs)**

- Intel, AMD, Nvidia

- Enabling data processing

#### **COTS FPGAs**

- Xilinx Kintex+

- Mitigation evaluation

- •TBD: Microsemi **PolarFire**

#### Radiation Hardened **Processor Evaluation**

- •BAE

- Vorago (microcontrollers)

Best **Practices** and Guidelines

#### **Partnering**

- Processors: Navv Crane, BAE/NRO-

- •FPGAs: AF, Aerospace, SNL, LANL, BYU,...

- Microsemi, Xilinx. **Synopsis**

- Cubic Aerospace

#### Potential future task areas:

artificial intelligence (AI) hardware, Intel Stratix 10

To be presented by Melanie Berg at the NASA Electronics Parts and Packaging (NEPP) Electronics Technology Workshop (ETW), Greenbelt, MD, June26–29, 2017

- Impact to community:

- Currently it is difficult to compare device under test (DUT) test data because of differences in test vehicle and test methodology

- The FPGA SEU Test Guidelines Document creates standardized test methodologies and provide a means for data comparison across organizations and FPGA types.

- The FPGA SEU Test Guidelines Document points out best practices for DUT test structures, monitoring DUT functional response, visibility in DUT operation, DUT control, and DUT power.

- Update of the test guidelines will be available by December 2017.

- Additional test structures.

- Embedded processor testing techniques.

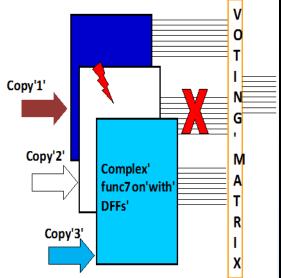

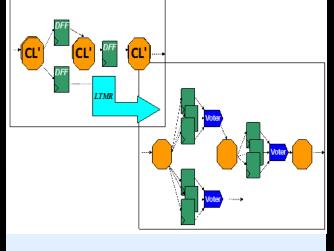

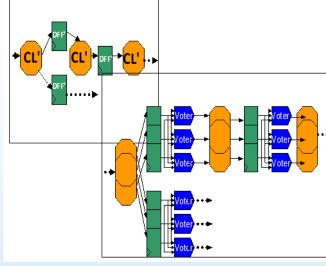

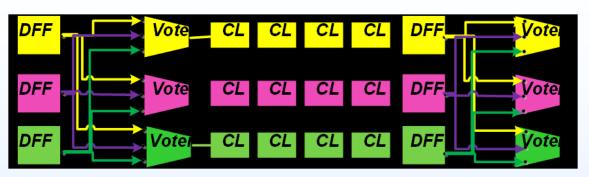

# Various Triple Modular Redundant (TMR) Schemes Implemented in FPGA Devices

Block diagram of block TMR (BTMR): a complex function containing combinatorial logic (CL) and flip-flops (DFFs) is triplicated as three black boxes; majority voters are placed at the outputs of the triplet.

Block diagram of local TMR (LTMR): only flip-flops (DFFs) are triplicated and datapaths stay singular; voters are brought into the design and placed in front of the DFFs.

Block Diagram of distributed TMR (DTMR): the entire design is triplicated except for the global routes (e.g., clocks); voters are brought into the design and placed after the flip-flops (DFFs). DTMR masks and corrects most single event upsets (SEUs).

TMR can be embedded in the FPGA or user inserted.

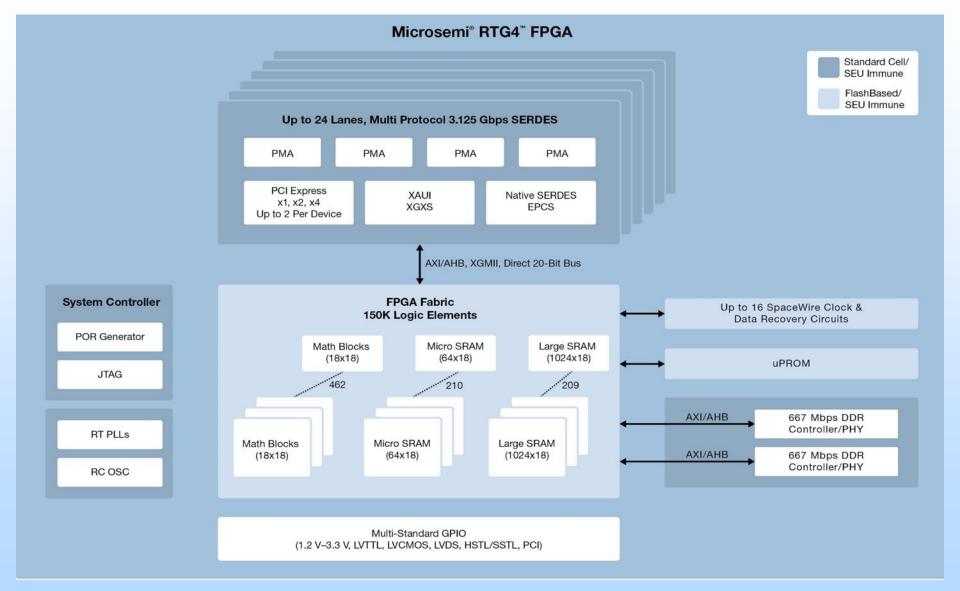

### FPGA Devices Manufactured as Space-Grade Products: Microsemi RTG4 FPGA

### Impact to Community Microsemi RTG4 FPGA

- Next generation to the spacegrade Microsemi RTAXs.

- I/O interfaces are significantly more robust versus prior

Microsemi space-grade FPGAs devices.

- Embedded mitigation, packaging, and qualification process makes this device space-grade.

- Flash based configuration hence configuration is essentially SEU immune.

- Embedded flip-flop (DFF) SEU hardening.

NEPP performs an independent study to determine the level of SEU susceptibility for the various RTG4 components.

# Microsemi RTG4: Device Under Test (DUT) Details

- New Entry into the Aerospace Market with Space-grade Expectation.

- Bulk UMC 65nm CMOS process with an epitaxial layer. Flash based configuration.

- Qualified to MIL-STD-883 Class B, and Microsemi will seek QML Class Q and Class V qualification.

- The DUT : RT4G150-CG1657M.

- We tested Rev B and Rev C devices.

- The DUT contains;

- 158214 look up tables (4-input LUTs);

- 158214 flip-flops (DFFs); 720 user I/O;

- 210K Micro-SRAM (uSRAM) bits;

- 209 18Kblocks of Large-SRAM (LSRAM);

- 462 Math logic blocks (DSP Blocks);

- 8 PLLs; and 48 global routes (radiation-hardened global routes);

LUT: look up table.

SRAM: sequential random access memory.

DSP: digital signal processing.

PLL: phase locked loop.

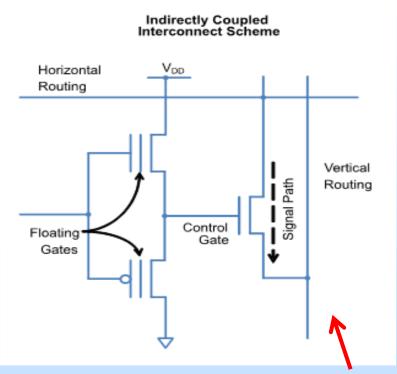

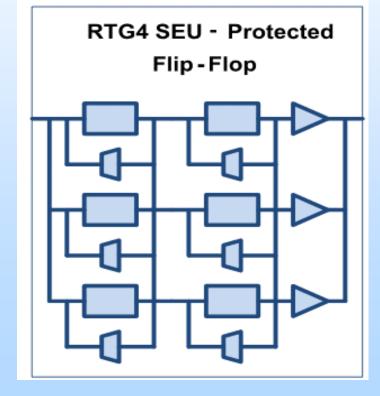

### Microsemi RTG4: Device Under Test (DUT) Embedded Hardening

Hardened configuration flash cell

DFFs are radiation hardened using LTMR and SET filters placed at the DFF data input.

## NASA

### Microsemi RTG4 Study Objectives

- This is an independent investigation that evaluates the single event destructive and transient susceptibility of the Microsemi RTG4 device.

- Design/Device susceptibility is determined by monitoring the DUT for Single Event Transient (SET) and Single Event Upset (SEU) induced faults by exposing the DUT to a heavy ion beam.

- Potential Single Event Latch-up (SEL) is checked throughout heavy-ion testing by monitoring device current.

- The objectives of this study are the following:

- Analyze flip-flop (DFF) behavior in simple designs such as shift registers. Compare SEU behavior to more complex designs such as counters and finite impulse response (FIR) filters. Evaluating data trends helps in extrapolating test data to actual designs.

- Analyze global route behavior clocks, resets.

- Analyze configuration susceptibility.

### **DUT Preparation**

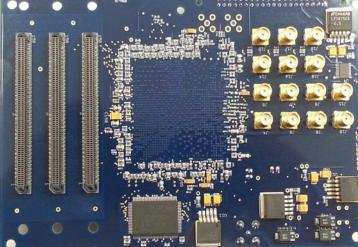

### Top Side of DUT

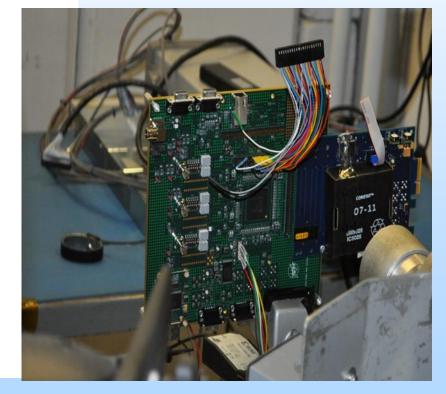

- NEPP has populated two Rev B and four populated Rev C boards with RT4G150-CG1657M devices.

- The parts (DUTs) were thinned using mechanical etching via an Ultra Tec ASAP-1 device preparation system.

- The parts have been successfully thinned to 70um – 90um.

### **Challenges for Testing**

TID: total ionizing dose

- Software is new... place and route is not optimal yet. Hence, it is difficult to get high speed without manual placement.

- Microsemi reports that devices show TID tolerance up to 160Krads.

- Although, when testing with heavy-ions, dose tolerance will be much higher.

- TID limits the amount of testing per device.

- Number of devices are expensive and are limited for radiation testing.

- A large number of tests are required.

- We will always need more parts.

- Current consortium participants:

- NEPP (Goddard and JPL),

- Aerospace Corporation, and

- Microsemi.

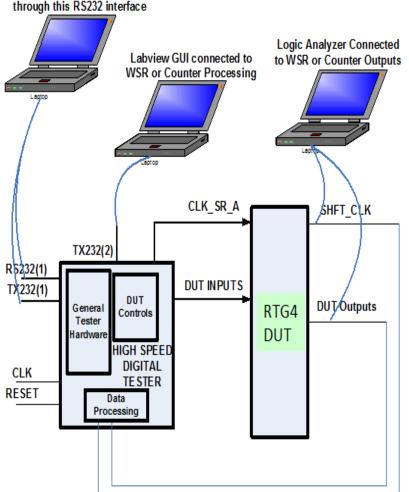

Labview GUI Connected to Memory Processing in HSDT. Commands are also sent (and echoed) to the HSDT through this RS232 interface

### Microsemi RTG4 Designs Tested

| Test Structure                                                   | Frequency Range |

|------------------------------------------------------------------|-----------------|

| Global routes                                                    | 2KHz – 150MHz   |

| Shift Registers (WSRs)                                           | 2KHz – 150MHz   |

| Counters                                                         | 5MHz – 100MHz   |

| Finite impulse response filters (FIRs). Math-block (DSP) testing | 1MHz-100MHz     |

| Embedded SRAM                                                    | N/A             |

Test structures selected in order to investigate specific RTG4 components and data trends across a variety of designs.

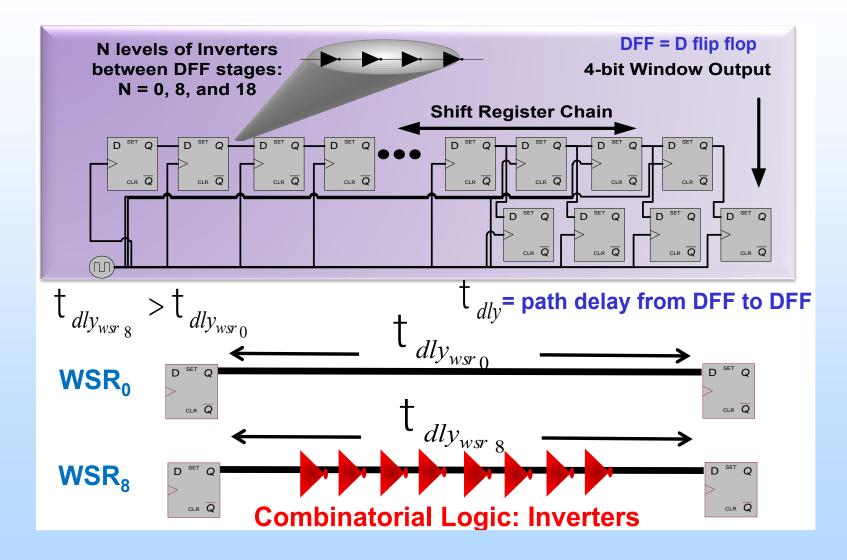

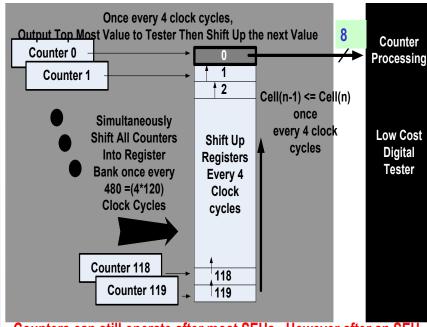

# Windowed Shift Registers (WSRs): Test Structure

### **Counter Arrays**

NASA

- DUT contains two sets of the following:

- 200 8-bit counters

- 200 8-bit snapshot registers

- All counters and snapshot registers are connected to the same clock tree and RESET.

- The clock tree is fed by the CLK input from the LCDT.

- DUT CLK is connected to a DGBIO and a CLKBUF.

- The LCDT sends a clock and a reset to the DUT. The controls are set by the user

Counters can still operate after most SEUs. However after an SEU occurs, the tester must recalculate a new expected value for the affected counter.

2 sets of counter arrays are tested simultaneously

# Test Facility Conditions: Texas A&M University Cyclotron Facility

- 25 MeV/amu tune.

- Flux: 1 x 10<sup>4</sup> to 5 x 10<sup>5</sup> particles/cm<sup>2</sup>·s

- Fluence: All tests were run to 1 x 10<sup>7</sup> particles/cm<sup>2</sup> or until destructive or functional events occurred.

- Test temperature: Room temperature

| lon  | Energy<br>(MEV/Nucleon) | LET (MeV*cm²/mg)<br>0° | LET (MeV*cm²/mg)<br>60 ° |

|------|-------------------------|------------------------|--------------------------|

| Не   | 25                      | .07                    | .14                      |

| N    | 25                      | .9                     | .18                      |

| Ne   | 25                      | 1.8                    | 3.6                      |

| Ar   | 25                      | 5.5                    | 11.0                     |

| Kr   | 25                      | 19.8                   | 40.0                     |

| Xe** | 25                      | 38.9                   | 78.8                     |

\*\*We were unable to obtain Xe during our testing

### Test Facility Conditions: Lawrence Berkeles **National Laboratory Cyclotron Facility**

- 16 MeV/amu tune.

- Flux: 1 x 10<sup>4</sup> to 5 x 10<sup>5</sup> particles/cm<sup>2</sup>·s

- Fluence: All tests were run to 1 x 10<sup>7</sup> particles/cm<sup>2</sup> or until destructive or functional events occurred.

- Test temperature: Room temperature

| Ion | Energy (MEV/Nucleon) | LET (MeV*cm²/mg) 0° |

|-----|----------------------|---------------------|

| N   | 16                   | 1.16                |

| Ne  | 16                   | 2.39                |

| Si  | 16                   | 4.35                |

| Ar  | 16                   | 7.27                |

| V   | 16                   | 10.9                |

| Cu  | 16                   | 16.5                |

| Kr  | 16                   | 25                  |

| Xe  | 16                   | 49.3                |

# Heavy-Ion Configuration Reprogrammability Results

- During this test campaign, tests were only performed up to an LET of 49.3MeVcm²/mg.

- Higher LETs will be used during future testing.

- No re-programmability failures were observed up to an LET of 49.3MeVcm²/mg when within particle dose limits. We did not try to reprogram while the beam was turned on.

### **Heavy-ion Global Route Results**

- Global routes are the backbone of all designs. Hence, it is imperative to investigate global route SEU susceptibility.

- For NEPP DUT test structures, clock trees were connected to a variety of global clock tree sources:

- Direct clock I/O

- Internal Oscillator

- Clock conditioning circuit (PLL)

- TMR clock conditioning circuit (TMR PLL)

- Summary of global route results starting from best performance:

- Direct clock I/O had the lowest SEU susceptibility (best performance.

- Clock conditioning circuit had higher SEU susceptibility than direct clock I/O. However, performance can still be acceptable for critical missions.

- TMR clock conditioning circuit (TMR PLL) did not appear to reduce susceptibility and might have higher susceptibility at higher frequencies.

- Internal OSC is SEU soft and should not be used in critical circuits.

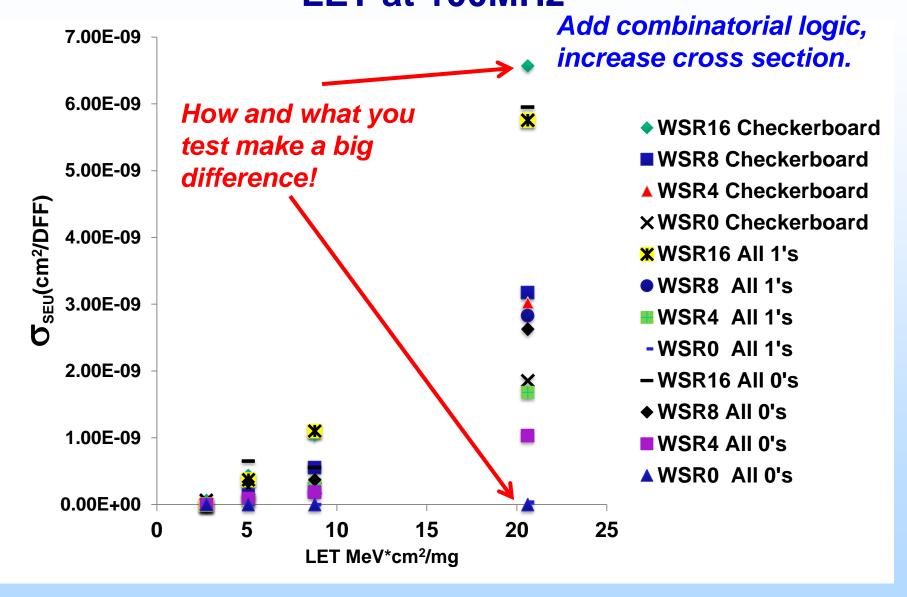

### Rev C: WSRs with SET FILTER versus LET at 100MHz

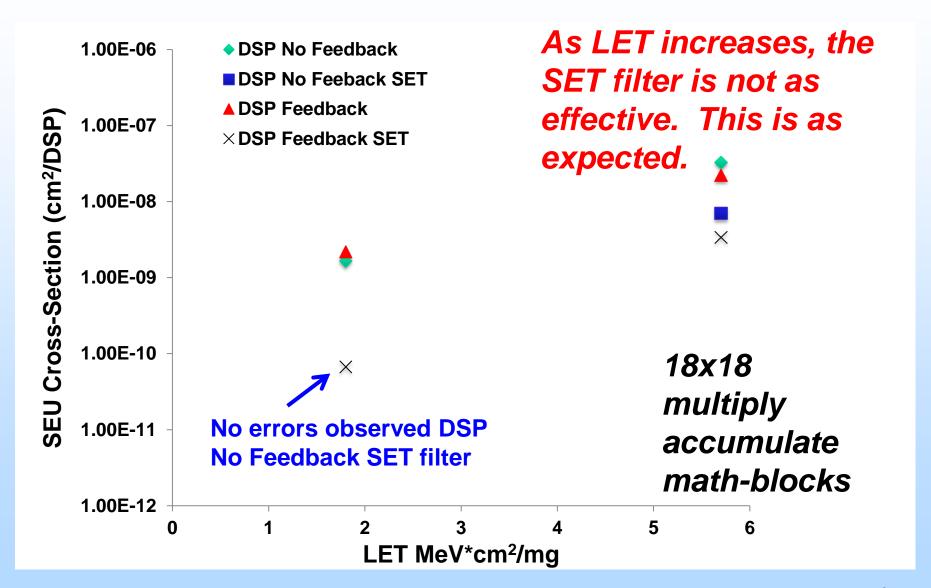

### WSR and Counter Accelerated Radiation Test Data Observations

- WSR chains showed a variety of dependencies (all are as expected):

- Increase clock frequency—increase failures.

- Increase combinatorial logic increase failures.

- Increase data change rate increase failures.

- Use of flip-flop SET filter decrease failures.

- Use of flip-flop SET filter decreases system operation speed.

- As LET increases, the effectiveness of the SET filter decreases. This is because generated SETs become wider (more energy) and have more power to defeat the SET filter.

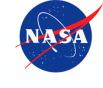

- Results (SET filter on) are in-line with the Microsemi SEU radiation hardened predecessor – Microsemi RTAXs family.

- However, the Microsemi RTAXs family had slightly better SEU performance.

# RTAX4000D and RTAX2000 WSRs at 80MHz with Checkerboard Pattern

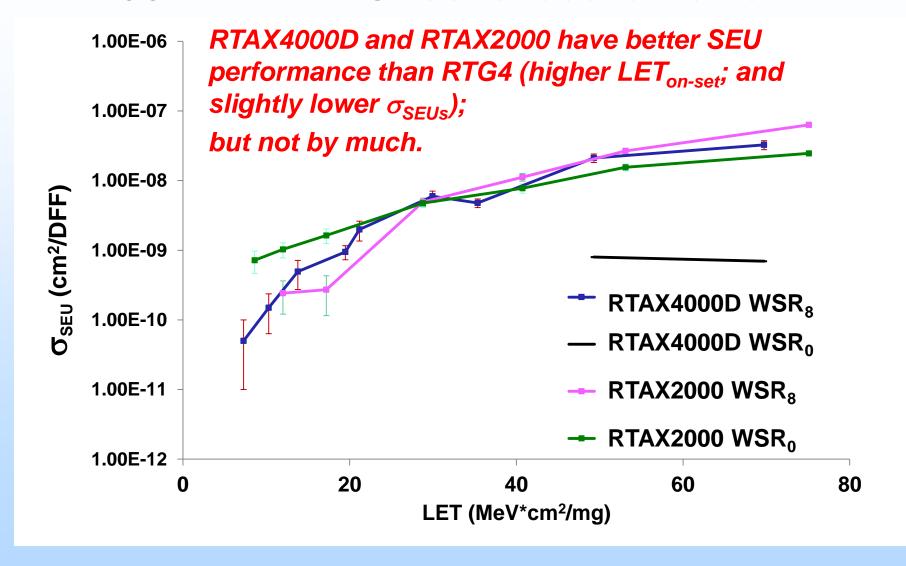

### Microsemi SRAM SEU Cross-Section

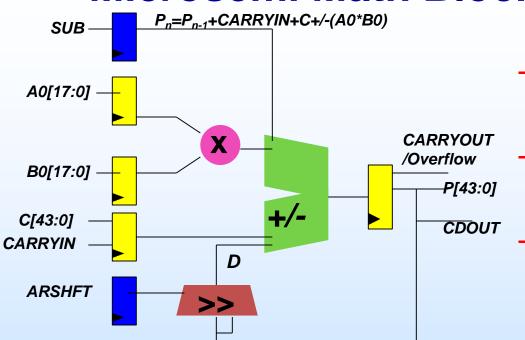

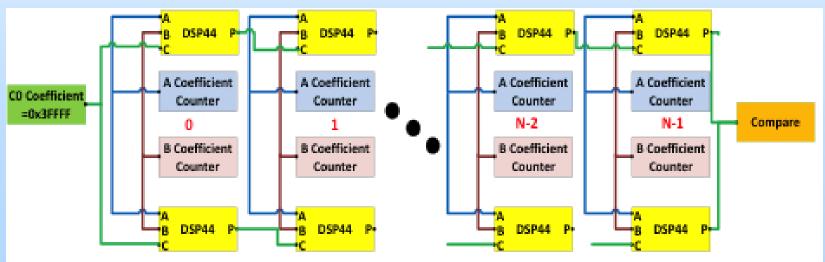

### Microsemi Math Block Test Structures

- 18x18 multiply accumulate math-blocks.

- Dual redundant chains with a compare.

- Coefficients are shared.

# RTG4 Math-block (DSP) SEU CrossSections versus LET

# Deliverables: Microsemi RTG4 Test Report Submission and Data Summary

- Two versions of reports have been submitted.

- Third version will be completed by June 2017.

- As a summary:

- RTG4 is not as SEU hardened as it's predecessor (RTAXs).

However, fairly close.

- Exception: embedded SRAM with EDAC is better in the RTG4.

- Embedded TMR PLL does not operate as expected. No improvement in SEU susceptibility.

- Internal Oscillator PLL is highly susceptible to SEUs.

- Designs implemented in the RTG4 device do not operate as fast as they do when implemented in the RTG4's predecessor (RTAXs).

This is most likely due to the place and route software. However, this is unexpected.

- TBD for NEPP to perform more testing. At this point, additional testing is assumed to be funded by partners or missions.

# SRAM-based FPGA Mitigation Study using Xilinx Kintex-Ultrascale (XCKU040-1LFFVA1156I) (1) Single event latch-up (SEL) and (2) Mitigation

### Impact to Community Kintex-UltraScale

$\sigma_{SEU}$ : SEU Cross-section

IP: intellectual property

- Next generation of FPGA devices from the commercial Xilinx-7 series.

- I/O interfaces are significantly more robust

- There are no embedded mitigation. However, additional gatecount better allows the user to insert mitigation into the design.

- There is no embedded processor. However, the user can embed a soft-core or use the Zync-UltraScale (contains hard-IP processor cores).

$$P(fS)_{system} \ \, \sqcup P_{Configuration} + P(fS)_{functionalLogic} + P_{SEFI}$$

Design  $\sigma_{SEU}$  Configuration  $\sigma_{SEU}$  Functional logic SEFI  $\sigma_{SEU}$

$\sigma_{\sf SEU}$

NEPP performs an independent study to determine the level of SEU susceptibility for the various FPGA components.

### **Xilinx Kintex-Ultrascale**

New Entry into the Aerospace Market with COTS Expectation ... 20 nm planar process (TSMC).

### Data Transfer Is Key for Our New System Applications: UltraScale Transceivers

|                      | Kintex-Ultra                     | scale                            | Virtex UltraS                    | cale                                                 |

|----------------------|----------------------------------|----------------------------------|----------------------------------|------------------------------------------------------|

| Туре                 | GTH                              | GTY                              | GTH                              | GTY                                                  |

| Quantity             | 16-64                            | 0-32                             | 20-60                            | 0-60                                                 |

| Maximum Data<br>Rate | 16.3Gb/s                         | 16.3Gb/s                         | 16.3Gb/s                         | 30.5Gb/s                                             |

| Minimum Data<br>Rate | 0.5Gb/s                          | 0.5Gb/s                          | 0.5Gb/s                          | 0.5Gb/s                                              |

| Key Applications     | Backplane<br>PCIe<br>Gen4<br>HMC | Backplane<br>PCIe<br>Gen4<br>HMC | Backplane<br>PCIe<br>Gen4<br>HMC | 100G+Optics<br>Chip-to-Chip<br>25G+ Backplane<br>HMC |

# Xilinx Kintex-UltraScale Study Objectives

- This is an independent investigation that evaluates the single event destructive and transient susceptibility of the the Xilinx Kintex-UltraScale device.

- Design/Device susceptibility is determined by monitoring the DUT for Single Event Transient (SET) and Single Event Upset (SEU) induced faults by exposing the DUT to a heavy ion beam.

- Potential Single Event Latch-up (SEL) is checked throughout heavy-ion testing by monitoring device current.

- This device does not have embedded mitigation. Hence, user implemented mitigation is investigated using Synopsys mitigation tools.

- FPGA part# XCKU040-1LFFVA1156I.

- Collaboration: Xilinx and Synopsys.

Beam time was limited: SEL, configuration, and Mitigation.

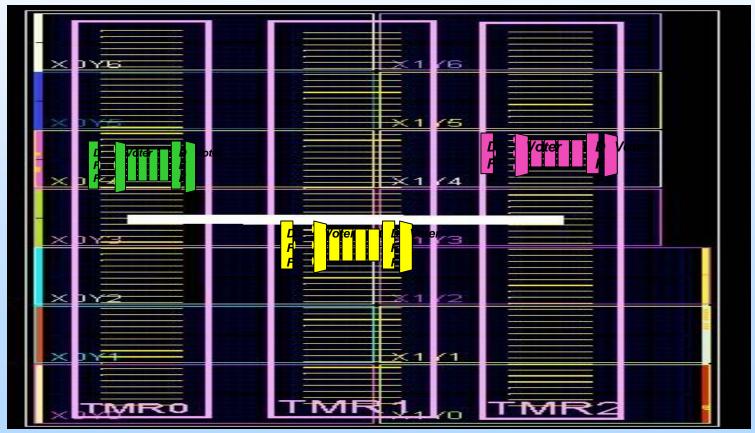

### TMR Descriptions CL: Combinatorial Logic

NASA

DFF: Edge triggered flip-flop;

| TMR<br>Nomenclature | Description                                                                                                         | TMR<br>Acronym  |

|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------|

| Block TMR           | Entire design is triplicated. Voters are placed at the outputs.                                                     | BTMR            |

| Local TMR           | Only the DFFs are triplicated. Voters are placed after the DFFs.                                                    | LTMR            |

| Distributed TMR     | DFFs and CL-data-paths are triplicated. Similar to a design being triplicated but voters are placed after the DFFs. | DTMR            |

| Global TMR          | DFFs, CL-data-paths and global routes are triplicated. Voters are placed after the DFFs.                            | GTMR or<br>XTMR |

Note: It has been suggested to separate (partition) TMR domains in SRAM based designs so that there are no overlapped shared resources. Shared resources become single points of failure.

### **DTMR Partitioning**

SEUs that occur in one TMR domain are expected to be mitigated.

### **Kintex-Ultrascale Designs Tested**

| Test Structure                       | Frequency Range |

|--------------------------------------|-----------------|

| Counter Array No TMR                 | 50MHz           |

| Counter Array DTMR with partitioning | 50MHz           |

| Counter Array DTMR no partitioning   | 50MHz           |

| Counter Array BTMR with partition    | 50MHz           |

| Counter Array LTMR with partition    | 50MHz           |

NEPP has the only current heavy-ion data for the Synopsys mitigation tool.

### **Test Facility Conditions**

- Facility: Texas A&M University Cyclotron Single Event Effects Test Facility, 25 MeV/amu tune).

- Flux: 1 x 10<sup>4</sup> to 5 x 10<sup>5</sup> particles/cm<sup>2</sup>·s

- Fluence: All tests were run to 1 x 10<sup>7</sup> particles/cm<sup>2</sup> or until destructive or functional events occurred.

- Test temperature: Room temperature

| lon  | Energy<br>(MEV/Nucleon) | LET (MeV*cm²/mg)<br>0° | LET (MeV*cm²/mg)<br>60 ° |

|------|-------------------------|------------------------|--------------------------|

| Не   | 25                      | .07                    | .14                      |

| N    | 25                      | .9                     | .18                      |

| Ne   | 25                      | 1.8                    | 3.6                      |

| Ar   | 25                      | 5.5                    | 11.0                     |

| Kr   | 25                      | 19.8                   | 40.0                     |

| Xe** | 25                      | 38.9                   | 78.8                     |

### We were unable to obtain Xe during our testing

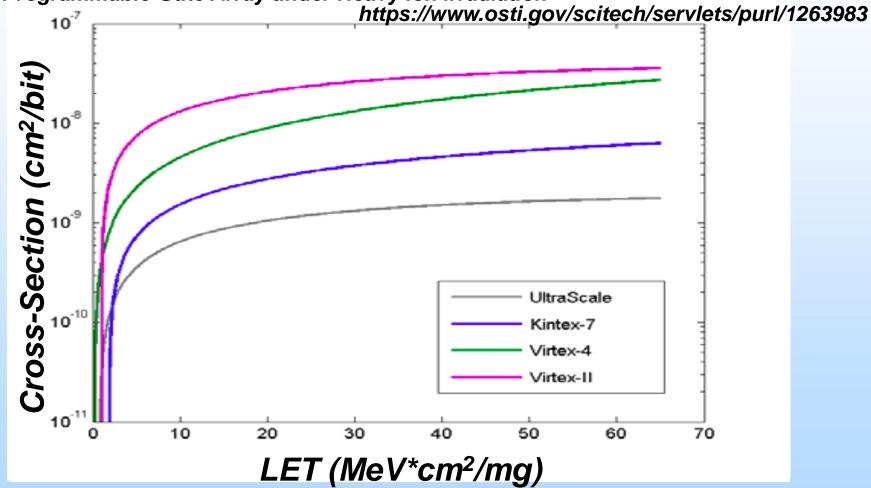

# Xilinx Scaling Family Trends for Configuration Bits in Heavy Ions

David Lee et. al. "Single-Event Characterization of the 20 nm Xilinx Kintex UltraScale Field-Programmable Gate Array under Heavy Ion Irradiation"

Daily upsets in configuration in LEO and GEO are expected.

# History of Xilinx and Single Event Latchup (SEL) or Latchup-Like Events: Virtex 2 through UltraScale Series

- Xilinx Virtex 2: Latchup-like events have been observed in flight. Most likely due to embedded half-latches in the device.

- Xilinx Virtex 5: Half-latches were removed. No latchuplike events observed during SEE testing or in flight.

- Xilinx 7-series: Is it SEL or latchup-like? Observed only on 7-series devices that contained 3.3V I/O. Devices that do not contain such I/O have no latchup-like events.

- Xilinx UltraScale series no latchup-like event observed.

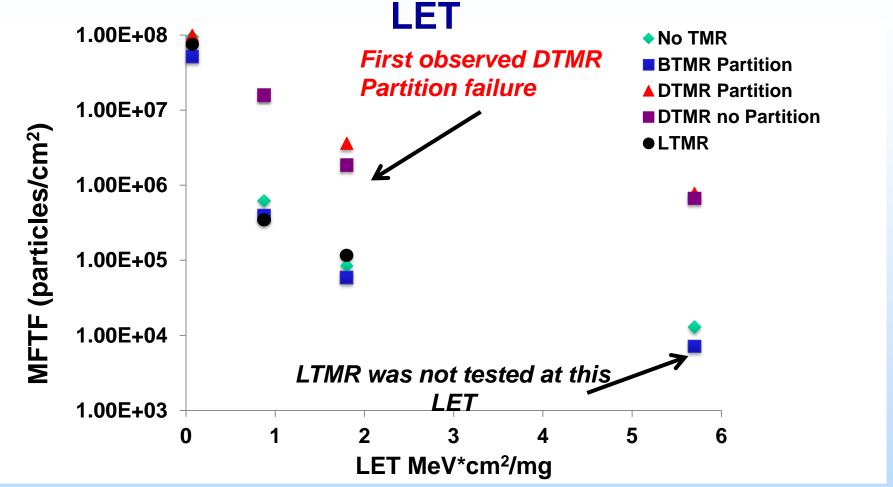

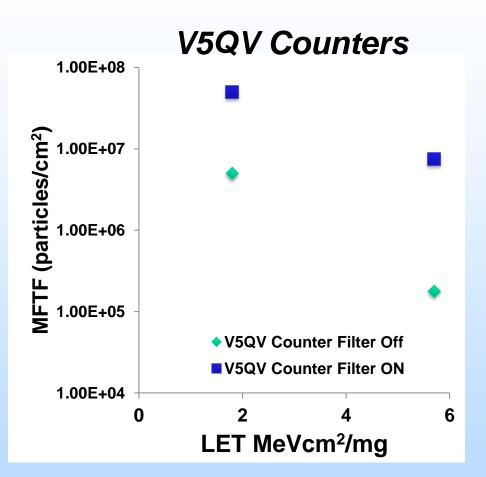

# Kintex-UltraScale Mitigation Study: Counter Arrays Mean Fluence to Failure (MFTF) versus

Kintex-UltraScale Data drops off quicker than radiation hardened Xilinx Virtex (V5QV).

More SEU testing should be performed for more detailed comparisons.

# Comparison of V5QV and Kintex UltraScale with Mitigation

Synopsys results are looking good.

## Summary of Mitigation Application to Kintex- UltraScale during SEU-Heavy-Ion Testing

SEFI: single event functional interrupt

- Mitigation study proves DTMR is the strongest mitigation scheme implemented in an SRAM-based FPGA.

- However, for flushable designs BTMR might be acceptable.

- LTMR is not acceptable in SRAM-based FPGAs for any design.

- Partitioning may not be necessary.

- Although GTMR has been implemented in V5 families and earlier Xilinx device families, NEPP has suggested to avoid GTMR because clock skew is difficult to control.

- In 2015-2016, via heavy-ion SEU testing, It has been observed in the Xilinx 7-series, that race conditions due to clock skew are unavoidable.

- This is due to the speed of combinatorial logic and route delays in the 7series versus earlier Xilinx FPGA device families.

- Synopsis tool has improved for simple designs. They are still working on IP core instantiations and other challenges.

- Mitigation and IP cores are still a major concern!!!!!!!!!!!!

# Deliverables: Xilinx Kintex-UltraScale Test Report Submission and Data Summary Test Report

The full Kintex-UltraScale SEU dataset is still currently being analyzed and will be available by June 2017.

### As a summary:

- NEPP has provided insight into Xilinx potential latchuplike events.

- Through previous testing and design experience, NEPP has provided Synopsys with information for sufficient mitigation strategies per FPGA.

- TBD for NEPP to perform more testing. At this point, additional testing is assumed to be funded by partners or missions.

- New Entry into the Aerospace Market with COTS Expectation.

- 16nm FinFet vertical process (TSMC).

- Depending on mission requirements, additional mitigation may be required.

- Zync UltraScale+ Includes:

- Dual and quad core variants of the ARM Cortex-A53 (APU).

- Dual-core ARM Cortex-R5 (RPU).

- Dedicated ARM graphics processing unit (GPU).

SRAM based Configuration. No radiation hardening is applied to flip-flops. However, manufacturer hopes FinFET technology will reduce SEU susceptibility.

### Xilinx Kintex-Ultrascale+ Transceivers

## Data Transfer Is Key for Our New System Applications: UltraScale+ Transceivers

|                      | Kintex-Ultrascale+               |                                                         | MPSoC UltraScale+               |                                  |                                                         |

|----------------------|----------------------------------|---------------------------------------------------------|---------------------------------|----------------------------------|---------------------------------------------------------|

| Туре                 | GTH                              | GTY                                                     | PS-GTR                          | GTH                              | GTY                                                     |

| Quantity             | 20-60                            | 0-60                                                    | 4                               | 0-44                             | 0-28                                                    |

| Maximum<br>Data Rate | 16.3Gb/s                         | 32.75Gb/s                                               | 6.0Gb/s                         | 16.3Gb/s                         | 32.75Gb/s                                               |

| Minimum<br>Data Rate | 0.5Gb/s                          | 0.5Gb/s                                                 | 1.25Gb/s                        | 0.5Gb/s                          | 0.5Gb/s                                                 |

| Key<br>Applications  | Backplane<br>PCIe<br>Gen4<br>HMC | 100G+Optics<br>Chip-to-Chip<br>25G+<br>Backplane<br>HMC | PCIe<br>Gen2<br>USB<br>Ethernet | Backplane<br>PCIe<br>Gen4<br>HMC | 100G+Optics<br>Chip-to-Chip<br>25G+<br>Backplane<br>HMC |

## Xilinx UltraScale+ Schedule

- We plan to test two platforms:

- MPSoC evaluation board.

- Custom Kintex-Ultrascale+ daughter card. Designed by NEPP.

- We currently have one evaluation board. MPSoC evaluation boards (ready for testing) will be in hand in June 2017.

- Proton testing using the MPSoC evaluation board is planned for August 2017 timeframe.

- Custom board is planned to be completed October 2017.

- Heavy ion testing will occur FY17 and FY18.

- Current Partners:

- NASA Goddard Science Data Processing Branch,

- JPL, and

- Sandia National Laboratory

- Xilinx

- We are looking for additional collaboration.

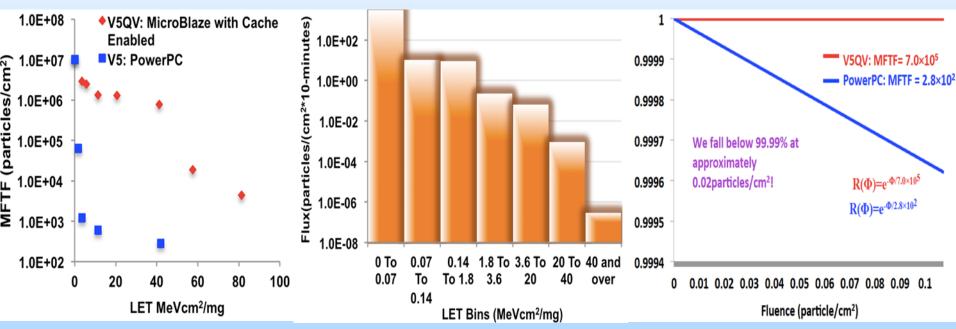

## Development of New Methodology for Characterizing SEU System Response (1)

- This study transforms proven classical reliability models into the SEU particle fluence domain. The intent is to better characterize SEU responses for complex systems.

- Will be discussed in further detail in another ETW presentation.

- Deliverables:

- Development of analysis (ongoing).

- Guidelines manual delivery in FY18.

# Development of New Methodology for Characterizing SEU System Response (2)

- The proposed method does not rely on data-fitting and hence removes a significant source of error.

- The proposed method provides information for highly SEUsusceptible scenarios; hence enabling a better choice of mitigation strategy.

- This methodology expresses SEU behavior and response in terms that missions understand via classical reliability metrics.

#### Presentations:

- Government Microcircuit Applications and Critical Technology Conference (GOMACTech) 2017 in Reno, NV.

- Single Event Effects (SEE)/Military Aerospace Programmable Logic Devices (MAPLD) 2017 in San Diego, CA.

- Submission to IEEE Radiation and its Effects on Components and Systems (RADECS) 2017. Conference will be held in Geneva, SUI.

## **FPGA Security and Trust**

- Goal: Support the U.S. government concerns regarding security and trust in FPGAs.

- Conference participation:

- Xilinx Security Working Group (XSWG) 2016 in Longmont, CO.

- Government Microcircuit Applications and Critical Technology

Conference (GOMACTech) 2017 in Reno, NV.

- Hardened Electronics and Radiation Technology (HEART) 2017 in Denver, CO.

- Hardware-Oriented Security and Trust (HOST) 2017, McLean,

VA.

- Joint Federated Assurance Center (JFAC) FPGA working group: Trusted Microelectronics Special Topic: Field Programmable Gate Array Assurance Workshop, McLean, VA.

- Collaboration with Aerospace Corporation, JFAC, and other agencies.

- Meetings, consultations, and presentations.

## **Questions?**