## Darwish, Ahmed and Holliday, Derrick and Finney, Stephen (2017) Operation and control design of an input-series-input-parallel-outputseries conversion scheme for offshore DC wind systems. IET Power Electronics. ISSN 1755-4535 , http://dx.doi.org/10.1049/iet-pel.2016.0885

This version is available at https://strathprints.strath.ac.uk/60570/

**Strathprints** is designed to allow users to access the research output of the University of Strathclyde. Unless otherwise explicitly stated on the manuscript, Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Please check the manuscript for details of any other licences that may have been applied. You may not engage in further distribution of the material for any profitmaking activities or any commercial gain. You may freely distribute both the url (<u>https://strathprints.strath.ac.uk/</u>) and the content of this paper for research or private study, educational, or not-for-profit purposes without prior permission or charge.

Any correspondence concerning this service should be sent to the Strathprints administrator: <a href="mailto:strathprints@strath.ac.uk">strathprints@strath.ac.uk</a>

**Research Article**

# Operation and control design of an inputseries–input-parallel–output-series conversion scheme for offshore DC wind systems

## Ahmed Darwish<sup>1</sup> , Derrick Holliday<sup>1</sup>, Stephen Finney<sup>1</sup>

<sup>1</sup>Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, UK E-mail: ahmed.mohamed-darwish-badawy@strath.ac.uk

**Abstract:** High-power converters for high-voltage direct current transmission systems and collecting networks are attracting increasing interest for application in large offshore wind farms. Offshore wind farms are capable of generating more electric energy at lower cost when compared with onshore wind systems. In this study, DC/DC voltage conversion should be achieved with a power converter that uses readily available semiconductor devices. A modular DC/DC converter can achieve the required system currents and voltages without exceeding semiconductor ratings. In this study, the operation and control strategy for an input-series–input-parallel–output-series (ISIPOS) energy conversion system for wind systems are presented. The ISIPOS system allows the direct connection of wind turbines to the DC grid. In this research, the design process to control the input and output currents and voltages is explained. In addition, a new method to ensure voltage and current sharing between the different modules is presented and explained. The basic structure, control design, and system performance are tested using MATLAB/SIMULINK. Practical results validate the control design flexibility of the ISIPOS topology when controlled by a TMSF280335 DSP.

## 1 Introduction

Presently, >3000 offshore wind turbines have been installed in the European sector with total capacity of ~11 GW. In 2015, the allocated investment for offshore wind farm projects exceeded £14bn [1]. Offshore wind farms are preferred over onshore farms for many reasons, including increased power capability, lower environmental impact and the ability to install larger wind turbines [2, 3]. Therefore, it is expected that offshore farms will form approximately one-third of the total generated wind power in the near future [2]. Thus, the international trend towards offshore wind farms necessitates long distance and large transmission networks with high power ratings.

For wind farms located >75 km offshore, advanced highvoltage direct current (HVDC) transmission systems become more promising. This is because HVDC systems require fewer transmission lines when compared with AC architectures, in addition to their stability and controllability [4]. The absence of reactive power circulation in the submarine cables of HVDC systems reduces power losses in the cables and increases the total efficiency [5]. Moreover, large-scale offshore wind power systems form weak connection points where HVDC system can assist with grid code compliance, increasing the power quality onshore and dealing with the voltage and current unbalance at high power levels [4]. Considered as important merits in weak grids, HVDC transmission systems offer the capability of black start as well as the ability to operate at relatively low wind speeds [4].

Presently, the most common configuration for offshore wind farms with an HVDC transmission network uses an AC collection network to connect all the wind turbines to an offshore AC/DC platform [6, 7]. However, this configuration has high total cost and size because it requires a bulky low-frequency AC transformer. For this reason, replacing the AC collection network with a DC network can add additional advantages. First, the circulating reactive currents will be eliminated and hence, the total efficiency will be improved. Second, DC collection networks will omit the need for the line-frequency AC transformer and hence, the total footprint of the system can be reduced. In this paper, the main challenge of this configuration would be the ability to boost the wind turbine low voltage to the desired transmission level. The DC/DC converters proposed to achieve this should have acceptable efficiency and offer the same reliability when compared with the eliminated AC transformer [8].

Modular DC/DC converters for medium-voltage applications have been discussed extensively in the literature [9-14]. Due to their capability to operate with zero-voltage switching, phase-shift full-bridge converters are widely used for high-power applications [12]. Many configurations for parallel and series connection of several modules are proposed in order to reduce the current and voltage stresses in the semiconductor devices and hence, the device technologies that are readily available in the market can be used in the implementation. Therefore, each module is exposed to a small fraction of the total voltage and current and hence, the semiconductor devices can operate at relatively high switching frequency (>10 kHz). In addition, the turn's ratio of the isolation transformers can be reduced if the converter outputs are series connected. This leads to a lower leakage inductance in each module. These types of DC/DC converter are suitable for both unidirectional and bidirectional power applications. Traditionally, the configurations of multi-module DC/DC converters can be classified into four main types: input-parallel-output-parallel, input-parallel-output-series (IPOS), input-series-output-parallel and input-series-output-series (ISOS) [14].

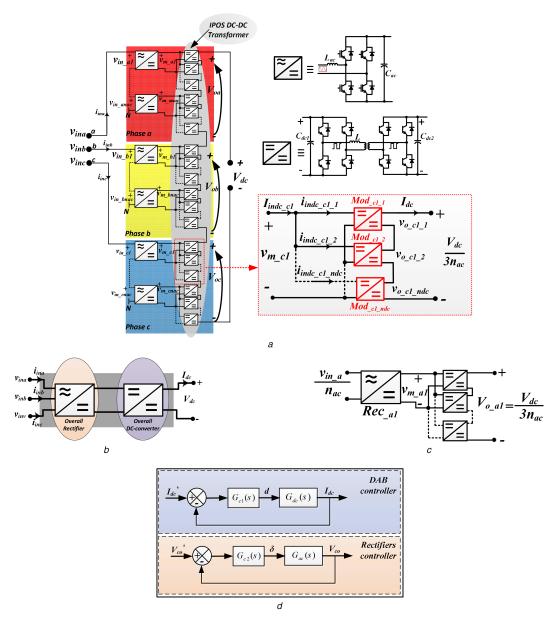

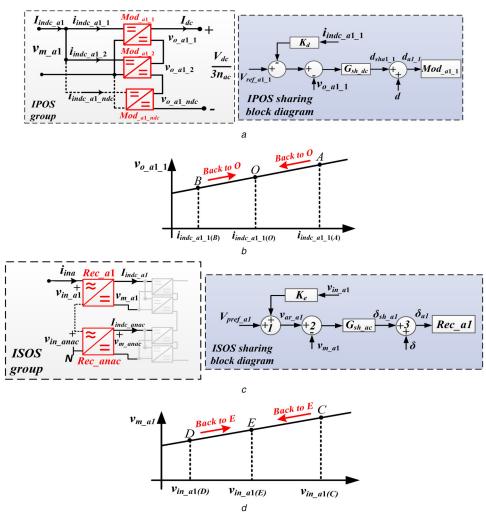

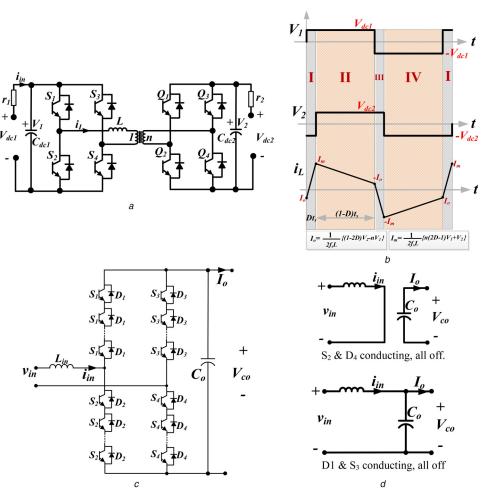

A novel configuration for a modular energy conversion system has been presented [3] where each phase of the AC system is connected to several single-phase power stacks, as shown in Fig. 1*a*. Each stack consists of an AC/DC converter followed by an IPOS DC/DC converter cluster. Then, the output of each phase is connected in series to maximise the output DC voltage and consequently, parallel or series connection of the power devices will be avoided. Accordingly, the design of the modular singlephase converters will not be complicated. Although offshore wind turbine systems require unidirectional power flow, this configuration can be used for other applications where the bidirectional power flow is required. The whole configuration can be viewed as an input-series–input-parallel–output-series (ISIPOS) AC/DC converter. The modularity of this converter provides high reliability, internal module fault tolerance and it allows for correct operation at different terminal voltages. Moreover, current and

ISSN 1755-4535 Received on 9th December 2016 Revised 3rd April 2017 Accepted on 26th April 2017 doi: 10.1049/iet-pel.2016.0885

www.ietdl.org

Fig. 1 ISIPOS AC/DC energy conversion system

(a) Full system, (b) Simplified AC-DC ISIPOS system, (c) Single rectifier with its DC/DC converter, (d) Simplified block diagrams of overall controllers

voltage ripples in the passive components can be reduced significantly when interleaved modulation of the sub-modules is used, leading to better performance. However, the control strategy of this configuration should achieve three main objectives:

- i. Controlled power flow between the input and output sides while keeping the converters voltages and currents within the acceptable limits.

- ii. A fast dynamic response during abnormal operating conditions.

- iii. Voltage and current sharing between the different sub-modules.

Generally, two main control techniques have been used for these types of converters, namely, fixed frequency and variable frequency techniques. Variable frequency control adds to the complexity of controller design, as well as creating undesired EMI components which necessitate increased filtering [15–17]. However, fixed frequency control, such as phase-shift control (PSC) [18, 19], avoids these disadvantages and offers better performance, especially for the DC/DC converter part of the system. Using the fixed frequency control approach, this paper explains the operation and modelling of the previously mentioned ISIPOS AC/DC converter for medium-voltage applications. In addition, the paper identifies important issues in the

implementation of control algorithms to satisfy both simplicity and desired performance using classical proportional + integral (PI) control loops. The remaining of this paper is organised as follows: Section 2 describes the system under investigation and explains its basic structure and operation. Section 3 discusses the control methodologies of the system from the perspective of overall power transfer control as well as power sharing control. In power transfer control, the AC/DC rectifiers and DC/DC converter modules are considered as if their series semiconductor switches operate simultaneously, and any small voltage and current mismatches are neglected. In power sharing control, the decentralised controllers are responsible for ensuring equal power sharing between the different rectifiers and modules in order to improve the modularity and reliability. MATLAB/SIMULINK simulations for power transfer and power sharing controllers are presented in Section 3. Section 4 presents the experimental results of the ISIPOS system when controlled with a TMS320F28335 DSP.

#### 2 System description

The symbols and variables used to describe the system shown in Fig. 1*a* are listed in Table 1 and the overall AC/DC system is shown in Fig. 1*b*. For practical operation at 5 MW and a DC collecting voltage of 50 kV, the input and output currents and voltages of the system are listed in Table 2. A single rectifier with

its DC/DC group is shown in Fig. 1*c* where  $n_{ac}$  is the number of rectifiers per phase,  $n_{dc}$  is the number of DC/DC converters per rectifier and  $N_{dc}$  is the total number of DC/DC converters in the system. For the dual-active bridge (DAB) DC/DC converter circuit, it is preferable to operate the converter in the condition that the input and output voltages are close to each other to ensure that the circulating current and the converter inductor values are as low as possible [20].

Therefore, the intermediate voltage  $V_{\rm m}$  is chosen as

$$V_{\rm m} = \frac{V_{\rm dc}}{N_{\rm dc}} = \frac{V_{\rm dc}}{3n_{\rm dc}n_{\rm ac}} \tag{1}$$

To ensure reliable operation, the de-rating factor of the switches should be ~70%. In view of this, the IGBT switches for the rectifiers and DC/DC converters are rated at 1.7 and 1.2 kV/200 A, respectively. The number of modules and the operating conditions

Table 1 System variables

| Symbol                                                                                                                                 | Variable                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| n <sub>ac</sub>                                                                                                                        | number of rectifiers per phase                                                                                          |

| n <sub>dc</sub>                                                                                                                        | number of DC/DC converter modules per<br>rectifier                                                                      |

| N <sub>dc</sub>                                                                                                                        | total number of DC/DC converter modules                                                                                 |

| $v_{\mathrm{in}k} k \in \{a, b, c\}$                                                                                                   | phase k AC voltage                                                                                                      |

| $i_{\mathrm{in}k} k \in \{a, b, c\}$                                                                                                   | phase k AC current                                                                                                      |

| $k \in \{a, b, c\}$ $v_{\text{in}\_kp} p \in \{1, 2, \dots, n_{\text{ac}}\}$                                                           | AC voltage of the <i>p</i> th AC/DC rectifier in phase <i>k</i>                                                         |

| $k \in \{a, b, c\}$ $v_{\underline{m}_k p} p \in \{1, 2, \dots, n_{ac}\}$                                                              | DC voltage of the <i>p</i> th AC/DC rectifier in phase <i>k</i>                                                         |

| $k \in \{a, b, c\}$ $I_{indc\_kp} p \in \{1, 2,, n_{ac}\}$                                                                             | DC current of the <i>p</i> th AC/DC rectifier in phase <i>k</i>                                                         |

| $k \in \{a, b, c\}$ $i_{indc\_kp\_j} p \in \{1, 2,, n_{ac}\}$                                                                          | input current of the <i>j</i> th DC/DC module of the <i>p</i> th rectifier in phase <i>k</i>                            |

| $j \in \{1, 2,, n_{dc}\}$ $k \in \{a, b, c\}$ $v_{o\_kp\_j}p \in \{1, 2,, n_{ac}\}$ $j \in \{1, 2,, n_{dc}\}$                          | output voltage of the <i>j</i> th DC/DC module of the <i>p</i> th rectifier in phase <i>k</i>                           |

| $\begin{aligned} k \in \{a, b, c\} \\ Mod_{\_kp\_j}p \in \{1, 2,, n_{\mathrm{ac}}\} \\ j \in \{1, 2,, n_{\mathrm{dc}}\} \end{aligned}$ | DC/DC module number <i>j</i> connected to the<br><i>p</i> th rectifier in phase <i>k</i>                                |

| $k \in \{a, b, c\}$ $Rec_{kp} p \in \{1, 2, \dots, n_{ac}\}$ $j \in \{1, 2, \dots, n_{dc}\}$                                           | AC/DC rectifier number <i>p</i> in phase <i>k</i>                                                                       |

| $k \in \{a, b, c\}$<br>$V_{o_k p} p \in \{1, 2,, n_{ac}\}$                                                                             | total output DC voltage of DC/DC series<br>converters group connected to the <i>p</i> th<br>rectifier in phase <i>k</i> |

| $V_{o\_k} k \in \{a,b,c\}$                                                                                                             | total output DC voltage of DC/DC series converter group in phase <i>k</i>                                               |

| V <sub>dc</sub>                                                                                                                        | total output DC voltage                                                                                                 |

| / <sub>dc</sub>                                                                                                                        | output DC current                                                                                                       |

| Table 2   | Main characteristics of the system under |

|-----------|------------------------------------------|

| considera | ation                                    |

| Parameter          | Value               |

|--------------------|---------------------|

| P <sub>rated</sub> | 5 MW                |

| Vac                | 4 kV (line-to-line) |

| i <sub>in</sub>    | 722 A (rms)         |

| V <sub>dc</sub>    | 50 kV               |

| l <sub>dc</sub>    | 100 A               |

| power factor       | 0.99                |

are listed in Table 3. The inductor value *L* is selected to transfer the module power at a duty ratio D = 0.25 while the other passive elements are chosen to allow for <10% ripple across the capacitors and inductors.

#### 3 Control structure

Overall, the system under investigation can be viewed as a twostage power converter, as shown in Fig. 1*b*. For such a system, controller design becomes complex for several reasons. The overall system bandwidth of the power transfer controller is restricted to guarantee that undesired voltages and currents at the resonance frequencies are not excited because of the existence of the resonant poles. Consequently, the dynamics and transient response of the system are limited. In addition, other control loops should be inserted to assure equal current and voltage sharing between the series and parallel modules. These loops should respond more quickly than the main power controller and should not interact with it. This adds to the complexity of the control design process. In this context, the control system can be divided into two parts:

- Overall controller which controls the power transfer from the input to the output sides and sets the operating points of the system.

- Module-based controller to ensure equal power sharing between the modules and to cater for the small mismatches in the different power modules.

The following subsections will discuss the design process for these loops in order to achieve correct operation, acceptable transients and suitable dynamic response during faults and abnormalities, as well as to achieve correct sharing between the different power modules.

#### 3.1 Overall control

Assuming that all the passive components of the converters are identical and that all converters have the same duty ratio and gate drive signals, i.e. all the semiconductor switches are switched on and off in the same time, the equivalent circuit of the IPOS DC converter will be as the DAB circuit shown in Fig. 8*a* with  $C_1 = C_{dc1}/n_{dc}$ ,  $C_2 = n_{dc}C_{dc2}$ , and  $L = L/n_{dc}$ . In the same way, the equivalent circuit of the ISOS AC converter will behave as the circuit shown in Fig. 8*c*. In other words, the series–parallel combinations of AC and DC converters are viewed as two cascaded converters (Appendix).

**3.1.1 DC converter control**: The closed-loop block diagram of the overall DC converter is shown in Fig. 1*d* (the accompanying mathematical analysis can be found in Appendix), where

$$G_{c1}(s) = K_{p1} + \frac{K_{i1}}{s}$$

(2)

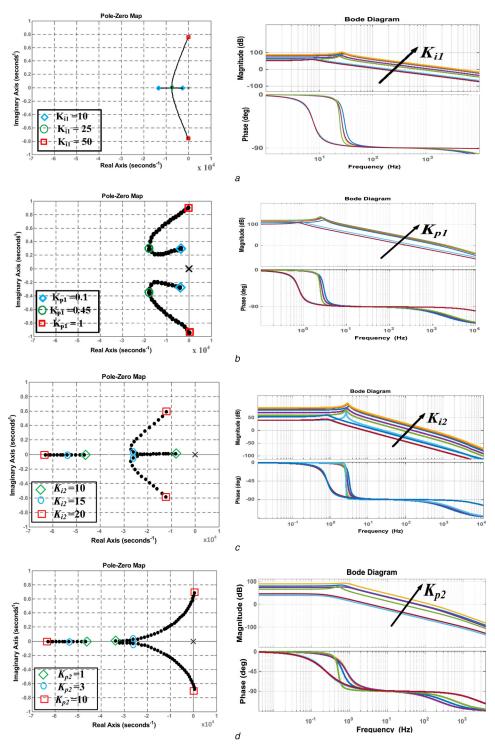

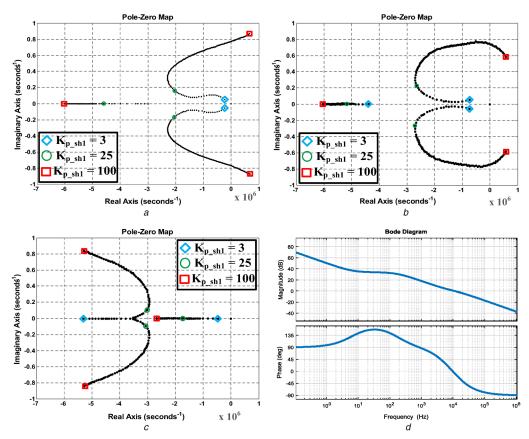

(see (3)) where *d* is the small-signal duty ratio of the DAB converter and *D* is equilibrium duty ratio where its maximum value  $D_{\text{max}} = 0.5$ . To ease the gain selection process, a point at the middle of the trajectory, D = 0.25, is selected to be the equivalent operating point. Then, the root loci of the closed-loop system can be drawn in two ways. In the first way, the proportional gain  $K_{p1}$  is kept constant at 0.5 while the integral gain  $K_{i1}$  is changed in the range of [10:50]. In the second way,  $K_{i1}$  is constant at 15 and  $K_{p1}$  is changed from 0.1 to 1. The resulting loci are shown in Figs. 2*a* and *b*. The ranges of the gains are selected initially to keep the system stable. From the presented analysis, the system always has real poles and no oscillations. The controller gains are selected to be  $K_{p1} = 0.45$  and  $K_{i1} = 25$  to give acceptable dynamics and 90° phase margin.

3.1.2 AC converter control: Using the same approach, the equivalent circuit of the series-connected AC converters can be considered to be as shown in Fig. 8*c*, with  $L_{in} = n_{ac}L_{ac}$  and  $C_o =$

#### IET Power Electron.

This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

$C_{\rm ac}/n_{\rm ac}$ . Therefore, the overall AC control system can be expressed as shown in Fig. 1*d*. Figs. 2*c* and *d* show the frequency domain analysis of the control loops. The gain values are selected as  $K_{\rm p2} =$ 3 and  $K_{\rm i2} = 15$  to ensure fast response (acceptable bandwidth) and to reduce system oscillations

$$G_{c2}(s) = K_{p2} + \frac{K_{i2}}{s}$$

(4)

$$G_{\rm ac}(s) = \frac{\tilde{v}_{\rm co}}{\tilde{\delta}} = \frac{G_{14}}{G_{14}(1 + C_0 L_{\rm in} s^2) + L_{\rm in} s} V_{\rm in}$$

where

$$L_{\rm in} = L_{\rm ac} \cdot n_{\rm ac}, \quad C_0 = C_{\rm ac}/n_{\rm ac}$$

(5)

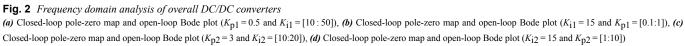

Fig. 3a shows the MATLAB/SIMULINK simulation results for the system using these parameters and control gains. Fig. 3b shows the simulations for the case when 80% pole-to-pole fault occurs at the DC collection terminals.

#### 3.2 Module-level control

Equal power sharing inside the converter modules may be disturbed during normal operation and switching transients. Voltage and/or current control balancing techniques should be employed to ensure equilibrium between the series or parallel connected converters [21]. In this section, decentralised power sharing techniques are implemented in parallel with the overall voltage and current control, i.e. module-level control works separately but alongside the overall AC and DC control schemes. To ensure that the overall control, which is responsible for controlling the output total voltages and currents, is not affected by module-level control schemes, the latter should be fast and have high bandwidth with respect to the main overall controllers.

**3.2.1** *IPOS DC/DC converter controller:* Considering the first DC/DC converter cluster of phase *a* as a case study (see Fig. 4*a*), it is necessary to ensure that either the voltages  $(v_{0,a1,1}, v_{0,a1,2}, ..., v_{0,a1,ndc})$  or the currents  $(i_{indc,a1,1}, i_{indc,a1,2}, ..., i_{indc,a1,ndc})$  are evenly shared. It is well known that for input-parallel connected systems, input-current sharing (ICS) between the different modules satisfies output-voltage sharing (OVS) and vice versa.

Table 3 Power module characteristics

| Parameter                             | Value       |

|---------------------------------------|-------------|

| n <sub>ac</sub>                       | 6           |

| n <sub>dc</sub>                       | 4           |

| N <sub>dc</sub>                       | 72          |

| voltage stress (rectifier)            | 695 V       |

| voltage stress (DC converters)        | 695 V       |

| current stress (rectifier)            | 1 kA (peak) |

| current stress (DC converters)        | 100 A       |

| switching frequency fs                | 50 kHz      |

| DAB inductance value L                | 13 µH       |

| operational duty ratio D              | 0.25        |

| transformer turns ratio n             | 1           |

| Lac                                   | 100 µH      |

| C <sub>ac</sub>                       | 180 µF      |

| C <sub>dc1</sub> and C <sub>dc2</sub> | 2 µF        |

However, it is reported in [22] that OVS cannot be stable for this configuration. In this work, ICS is achieved using decentralised droop controllers where the individual output voltages and input currents are sensed. Note that the total output voltage is controlled by the aforementioned overall DC controller. The droop controller for module 1 is shown in Fig. 4*a*. The main purpose of the proposed controller is to ensure that the total voltage of the cluster ( $V_{dc}/3n_{ac}$ ) is equally distributed across the individual output voltages of the modules ( $v_{0\_a1\_1}$ ,  $v_{0\_a1\_2}$ , ...,  $v_{0\_a1\_ndc}$ ). Taking module 1 as an example, the reference voltage  $V_{ref\_a1\_1}$  is calculated from the actual total voltage  $V_{dc}$ .

It is important to highlight the relationship between the duty ratio of the DC/DC modules and their currents and voltages. Under steady-state conditions, the relationship between the output and input voltages and currents can be written as

$$\begin{cases} v_{o_{a1_{-1}}} = f(d_{a1_{-1}})v_{m_{-a1}} \\ v_{o_{-a1_{-2}}} = f(d_{a1_{-2}})v_{m_{-a1}} \\ \vdots \\ v_{o_{-a1_{-}ndc}} = f(d_{a1_{-}ndc})v_{m_{-a1}} \end{cases}$$

(6)

For DAB circuits,  $f(d_{a1_i})$  is an increasing function of  $d_{a1_i}$ . From the power balance equations

$$\begin{cases} i_{\text{indc}\_a1\_1} = f(d_{a1\_1})I_{\text{dc}} \\ i_{\text{indc}\_a1\_2} = f(d_{a1\_2})I_{\text{dc}} \\ \vdots \\ i_{\text{indc}\_a1\_n\text{dc}} = f(d_{a1\_n\text{dc}})I_{\text{dc}} \end{cases}$$

(7)

For module number k in the group, the proportion of individual input current  $i_{indc\_a1\_k}$  to the total input current of the group  $I_{indc\_a1}$  can be expressed as

$$P_{k} = \frac{i_{\text{indc}\_a1\_k}}{i_{\text{indc}\_a1}} = \frac{f(d_{a1\_k})I_{\text{dc}}}{\sum_{j=1}^{n_{\text{dc}}} f(d_{a1\_j})I_{\text{dc}}}$$

$$= \frac{f(d_{a1\_k})}{f(d_{a1\_k}) + \sum_{j=1, j \neq k}^{n_{\text{dc}}} f(d_{a1\_i})}$$

(8)

From (8), a perturbation increase in the duty ratio of module kleads to an increase in its input current. In other words, the individual input current  $i_{indc_a1_k}$  and individual output voltage  $v_{0 a1 k}$  are monotonous increasing functions of the duty ratio  $d_{a1 k}$ . As depicted in Fig. 4*a*, the duty ratio of  $Mod_{a1_1}$  is composed of two parts, namely d and  $d_{\text{shal }1}$ . d is common for all different modules and generated from the overall central controller, whereas  $d_{\text{shal 1}}$  is generated from the IPOS sharing controller for *Mod* <sub>*a*1 1</sub>. Assume that all the converters have the same parameters and that Mod  $a_{1,1}$  is operating at the equilibrium point 'O' as shown in Fig. 4b. The module output voltage  $v_{0_a1_1}$  then increases as the result of a perturbation. Due to output current  $I_{dc}$  passes through all modules, Mod al 1 will now be delivering increased power. Consequently,  $\bar{i}_{indc\_a1\_1}$  will start to increase and the operating point moves to 'A'. However, the controller will force  $d_{sha1\_1}$  to decrease because of the negative feedback of the controller at summing point 1 (Fig. 4a), leading the operation point to move back towards 'O'. The opposite operation is true for point 'B' when  $v_{0 a1 1}$  decreases.

The ICS PI controller  $G_{sh dc}(s)$  can be expressed as

$$\begin{aligned} G_{\rm dc}(s) &= \frac{I_{\rm dc}}{d} \\ &= \frac{LC_1 V_{\rm dc1} f_{\rm s} r_1 (1-2D) s - (2D-1) (V_{\rm dc2} r_2 D(D-1) + L V_{\rm dc2} f_{\rm s})}{(C_1 C_2 L^2 f_{\rm s}^2 r_1 r_2) s^2 + L^2 f_{\rm s}^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_{\rm s}^2)} \end{aligned}$$

(3)

IET Power Electron.

This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

$$G_{sh\_dc}(s) = K_{p\_sh_1} + \frac{K_{i\_sh_1}}{s}$$

(9)

The transfer function of the closed-loop system  $T_{sh1}(s)$  can be deduced from

$$g_{11}(s) = \frac{\tilde{v}_{o\_a1\_1}}{\tilde{v}_{r\_a1\_1}} = \frac{G_{sh\_dc}(s)G_{23}(s)}{1 + G_{sh\_dc}(s)G_{23}(s)}$$

(10.1)

$$\tilde{v}_{r\_a1\_1} = \tilde{V}_{ref\_a1\_1} - K_{d} \tilde{i}_{indc\_a1\_1}$$

(10.2)

$$T_{\rm sh}(s) = \frac{\tilde{v}_{\rm o\_a1\_1}}{\tilde{V}_{\rm ref\_a1\_1}} = \frac{g_{11}(s)}{1 + K_{\rm d}g_{11}(s)g_{13}(s)}$$

(10.3)

where

$$g_{13}(s) = \frac{i_{\text{indc}\_a1\_1}}{\tilde{v}_{o\_a1\_1}} = G_{11}(s)/G_{14}(s)$$

$$= \frac{(C_1C_2L^2f_8^2r_2)s^2 + L^2f_8^2C_1s + D^2(r_2D^2 - 2r_2D + r_2)}{L^2f_8^2(sC_2r_2 + 1)}$$

(10.4)

The droop gain  $K_d$  affects the gradient of the droop controller regulation characteristic and hence, increasing its value can

IET Power Electron.

This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

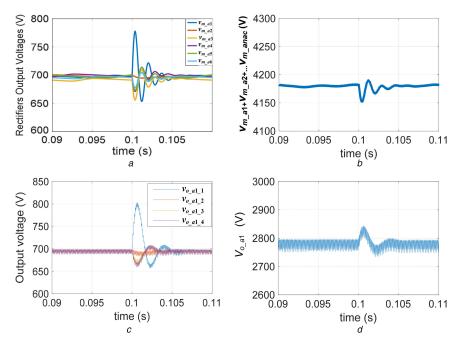

**Fig. 3** *MATLAB simulations of AC/DC ISIPOS system* (*a*) Normal operation, (*b*) With 80% sudden drop in terminal voltage

theoretically provide faster current sharing. To avoid prolongation, examination of the specific effect of  $K_d$  on the sensitivity of the sharing technique will be postponed until a future publication. The stability limits of the controller gains  $K_{p\_sh1}$ ,  $K_{i\_sh1}$  and  $K_d$  can be found using the Routh-Hurwitz stability criterion or using the MATLAB/SISOTOOL toolbox. Fig. 5 shows the closed-loop pole trajectories in response to variation of the controller gain  $K_{p \text{ sh}1}$ and with different values of  $K_{i\_sh1}$  and  $K_{d}$ . The values are changed until the desired characteristics of the controller are been found. These characteristics should achieve the lowest oscillation, stable operation, and increased bandwidth in comparison with the overall DC controller mentioned in Section 2. With this large bandwidth, the DC converter sharing techniques should not affect the main overall control of active power transfer. The gain values are selected as  $K_{p\_sh1} = 25$ ,  $K_{i\_sh1} = 200$  and  $K_d = 500$  to provide relatively stable operation and bandwidth equal to ten times that of the overall DC controller.

**3.2.2 ISOS AC/DC converter controller:** Considering AC/DC converter group of phase *a* as a case study, the input voltages

$(v_{in\_a1}, v_{in\_a2}, ..., v_{in\_anac})$  and the output voltages  $(v_{m\_a1}, v_{m\_a2}, ..., v_{m\_anac})$  have to be shared equally. Generally for input-parallel connected systems, input-voltage sharing (IVS) is sufficient to achieve OVS [23]. Under steady-state conditions, the relationship between the output and input voltages can be written as

$$\begin{cases}

v_{m_a1} = f(\delta_{a1})v_{in_a1} \\

v_{m_a2} = f(\delta_{a2})v_{in_a2} \\

\vdots \\

v_{m_anac} = f(\delta_{anac})v_{in_anac}

\end{cases}$$

(11)

For module number k in the group, the proportion of individual input voltage  $v_{in_ak}$  to the total input voltage of the group  $v_{ina}$  can be expressed as

$$S_{k} = \frac{v_{\text{in}\_ak}}{v_{\text{in}a}} = \frac{1}{1 + f(\delta_{ak})\sum_{j=1, j \neq k}^{n_{\text{dc}}} f(\delta_{ai})}$$

(12)

IET Power Electron. This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

#### Fig. 4 Converters and rectifier power sharing

(a) Block diagram of IPOS droop controller, (b) Regulation characteristic of IPOS controller, (c) Block diagram of ISOS droop controller, (d) Regulation characteristic of ISOS controller

From (12), a perturbation increase in the duty ratio of module k leads to a decrease in its input voltage in relation to the other rectifier input voltages. As depicted in Fig. 4c, the duty ratio of  $Rec_{a1}$  is composed of two parts, namely  $\delta$  and  $\delta_{sh_a1}$ .  $\delta$  is common for all phase a rectifiers and generated from the overall central controller while  $\delta_{sh_a1}$  is generated from the ISOS sharing controller for  $Rec_{a1}$ .

In this research, IVS can be achieved using the decentralised droop controllers shown in Fig. 4*c*. Unlike the previous IPOS sharing technique, the ISOS technique has positive feedback at summing point 1 (Fig. 4*c*) in order to give the positive droop regulation characteristics as shown in Fig. 4*d*. The IVS PI controller  $G_{\text{sh ac}}(s)$  can be expressed as

$$G_{sh_{ac}}(s) = K_{p_{sh_{2}}} + \frac{K_{i_{sh_{2}}}}{s}$$

(13)

The transfer function of the closed-loop system  $H_{sh1}(s)$  can be deduced from

$$g_{21}(s) = \frac{\tilde{v}_{\text{m}\_a1}}{\tilde{v}_{ar\_a1}} = \frac{G_{\text{sh}\_ac}(s)g_{\text{rec}}(s)}{1 + G_{\text{sh}\_ac}g_{\text{rec}}(s)}$$

(14.1)

$$g_{\rm rec}(s) = \frac{\tilde{v}_{\rm m\_a1}}{\tilde{\delta}_{\rm sh\_a1}} = \frac{G_{14}(s)}{G_{14}(s) \cdot (1 + C_{\rm ac}L_{\rm ac}s^2) + L_{\rm ac}s}$$

(14.2)

$$\tilde{V}_{ar\_a1} = \tilde{V}_{\text{pref}\_a1} + K_{\text{e}}\tilde{v}_{\text{in}\_a1}$$

(14.3)

$$H_{\rm sh}(s) = \frac{\tilde{v}_{\rm m\_a1}}{\tilde{v}_{\rm pref\_a1}} = \frac{g_{21}(s)}{1 - K_{\rm e}g_{21}(s)g_{\rm rec}(s)}$$

(14.4)

The same approach as that for the IPOS sharing technique with the analysis shown in Fig. 5 was followed, and the controller gains are selected as  $K_{p\_sh2}=5$ ,  $K_{i\_sh2}=120$  and  $K_e=750$  to provide relatively stable operation and a bandwidth equal to seven times that of the overall AC controller. The presented sharing methods are decoupled from the power transfer process and they do not require communication between the different modules and rectifiers. The system modularity and flexibility are therefore improved. The regulation features of the sharing controllers are not affected by the variation of input and output voltages or currents. The sharing controllers can achieve IVS and ICS of the AC/DC rectifiers and DC/DC modules during transients and under steady-state conditions.

Figs. 6a and b show the MATLAB simulations of the sharing technique for one IPOS group consisting of four of the DC/DC DAB converters shown in Fig. 4a.

At t=0.1 s, a perturbation occurs and output voltage  $v_{o1}$  increases. It can be seen that the total output voltage was not significantly affected and the controller succeeded in restoring normal operation. Figs. 6c and d show the MATLAB simulations of the sharing techniques for one ISOS group consisting of four DC/AC rectifiers. At t=0.1 s, a perturbation occurs and output voltage  $v_{m1}$  increases. The controller is able to share the output voltage between the different rectifiers equally.

**Fig. 5** *Variation of IPOS DC converter closed-loop poles with controller proportional gain*  $K_{p\_sh1}$ (*a*)  $K_d = 100$ ,  $K_{i\_sh1} = 200$ ,  $K_{p\_sh1} = 3$ ,...,100, (*b*)  $K_d = 500$ ,  $K_{i\_sh1} = 200$ ,  $K_{p\_sh1} = 3$ ,...,100, (*c*)  $K_d = 500$ ,  $K_{i\_sh1} = 200$ ,  $K_{p\_sh1} = 3$ ,...,100, (*d*) open-loop Bode plot at  $K_d = 500$ ,  $K_{i\_sh1} = 200$  and  $K_{p\_sh1} = 25$

Fig. 6 Simulated output voltage of ISOS and IPOS sharing technique during voltage perturbations (a) Individual output voltages of one ISOS group, (b) Total output voltage of one ISOS group, (c) Individual output voltages of one IPOS group, (d) Total output voltage of one IPOS group

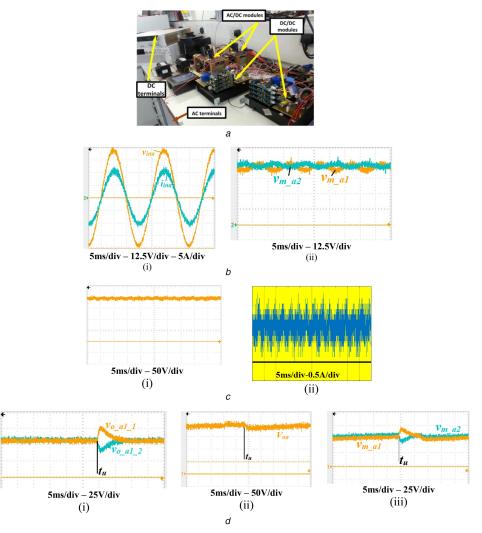

## 4 Experimental results

A 1 kW prototype controlled with TMS320F28335DSP was built, as shown in Fig. 7*a*, to validate the presented concept, mathematical analysis and control schemes. The system parameters in this case are shown in Table 4. FGY75N60SMD IGBTs have been employed for the semiconductor switches while RURG3060 diodes have been used for the anti-parallel diodes. During the normal operation shown in Figs. 7*b* and *c*, power is transferred from the input AC side to the output DC side through the ISIPOS system. Fig. 7b(i) shows that phase *a* current  $i_{ina}$  is in phase with the input AC voltage  $v_{ina}$ . However, the power factor is controlled over the full range according to the operation. Fig. 7b(ii) shows the output voltages of the rectifiers. As shown, these voltages have oscillating components beside the desired DC components. However, as long as these components are small they will not affect the normal operation of the system as the rectifier voltage

Fig. 7 Experimental results

(a) Experimental setup, (b) (i) input current with input voltage and (ii) rectifiers output voltages, (c) (i) total output voltage from phase a and (ii) sampled output current from the controller, (d) (i) and (ii) IPOS sharing technique and (iii) ISOS sharing technique

| Table 4 Circuit conditions of experimental setu | Table 4 | Circuit conditions of experimental setup |

|-------------------------------------------------|---------|------------------------------------------|

|-------------------------------------------------|---------|------------------------------------------|

| Parameter                               | Value                |

|-----------------------------------------|----------------------|

| n <sub>ac</sub> and n <sub>dc</sub>     | 2                    |

| switching frequency fs                  | 50 kHz               |

| DAB inductance value L                  | 30 µH                |

| transformer turns ratio n               | 1                    |

| L <sub>ac</sub> and C <sub>ac</sub>     | 1 mH and 45 $\mu$ F  |

| C <sub>dc1</sub> and C <sub>dc2</sub>   | 20 µF                |

| v <sub>in</sub> and <i>i</i> in         | 50 V and 10 A (peak) |

| K <sub>p1</sub> and K <sub>i1</sub>     | 0.25 and 10          |

| $K_{p2}$ and $K_{i2}$                   | 1 and 8              |

| $K_{p\_sh1}, K_{i\_sh1}$ and $K_{d}$    | 10, 80 and 200       |

| $K_{p\_sh2}$ , $K_{i\_sh2}$ and $K_{e}$ | 2, 40 and 300        |

will be converted using the next stage (IPOS groups). Fig. 7*c*(i) shows the output DC voltage of the system, whereas Fig. 7*c*(ii) shows the output current. The oscillating component of the output current can be eliminated either by increasing the value of output filter capacitance or by using simple resonant controllers tuned at the oscillation frequency. The efficiency of the total system is 95% in this case. The results can be compared with the MATLAB simulations in Fig. 3. Fig. 7*d* shows the results when an intended unbalance occurs at time instant ' $t_u$ ' in the first module of the IPOS DC/DC converter in phase *a*. In Fig. 7*d*(i), the output voltages of the DC/DC modules were forced back to the equilibrium operating

point again after a very short duration by the sharing controllers. Fig. 7d(ii) shows that the total output of the DC/DC group of phase 'a' has not been significantly affected by the sudden unbalance. Fig. 7d(iii) shows that the output voltages of the ISOS AC/DC rectifiers in phase a have been restored to their desired equal sharing values shortly after the sudden unbalance.

#### 5 Conclusion

In this paper, control schemes suitable for a modular ISIPOS AC/DC energy conversion system are presented and analysed. ISIPOS AC/DC converters are considered as promising solutions for medium-voltage high-power wind energy applications. However, because of their modularity, they can be extended to other applications, such as high-voltage high-power applications. Unfortunately, because the ISIPOS energy conversion system consists of many stages, control design becomes complicated and not straight forward. In this research, the control scheme comprises two main parts, namely, overall control and module-level control. In the overall AC/DC converter control, the series connected AC/DC rectifiers of the input-parallel output-series connected modules are viewed as equivalent AC/DC and DC/DC modules, and the mismatches between the system parameters are neglected. The duty ratios of the different modules are fed from central controllers. In the module-level controllers, each module has its own controller to cater for small mismatches between the different parameters, and to ensure equal voltage and current sharing between the power converters. System-level MATLAB simulations have been conducted to show the effectiveness of the proposed controller design. In addition, scaled-down experiments verify the presented mathematical analysis and simulation results using a 1 kW prototype controlled with TMS320F280335 digital signal processor.

## 6 Acknowledgments

This work was supported by the Engineering and Physical Sciences Research Council (EPSRC) under grant EP/K035096/1.

#### 7 References

- EWEA Association.: 'Wind in power 2015 statistics', Available at: http:// www.ewea.org/fileadmin/files/library/publications/statistics/EWEAAnnual-Statistics-2015.pdf

- [2] Wu, B., Wu, L., Zargari, N., et al.: 'Power conversion and control of wind energy systems' (Wiley, 2011)

- [3] Barrenetxea, M., Baraia, I., Adam, G.P., *et al.*: 'Analysis, comparison and selection of DC–DC converters for a novel modular energy conversion scheme for DC offshore wind farms'. EUROCON, 2015

- [4] ABB: 'HVDC Light® It's time to connect', Available at: https:// library.e.abb.com/public/2742b98db321b5bfc1257b26003e7835/ Pow0038%20R7%20LR.pdf

- [5] Zubiaga, M., Abad, G., Barrena, J.A., et al.: 'Energy transmission and grid integration of AC offshore wind farms InTech', 2012

- [6] Holtsmark, N., Bahirat, H., Molinas, M., et al.: 'An all DC offshore wind farm with series-connected turbines: an alternative to the classical parallel AC model?', *IEEE Trans. Ind. Electron.*, 2013, 60, (6), pp. 2420–2428

- [7] Barrenetxea, M., Baraia, I., Larrazabal, I., et al.: 'Design of a novel modular energy conversion scheme for DC offshore wind farms'. IEEE EUROCON – Int. Conf. on Computer as a Tool 2015, 2015

- [8] Pan, J., Bala, S., Callavik, M., et al.: 'DC connection of offshore wind power plants without platform'. Presented at the 13th Wind Integration Workshop, Berlin, 2014

- Yiqing, L., Finney, S.J.: 'DC collection networks for offshore generation'. Renewable Power Generation Conf. (RPG 2013), 2nd IET, Beijing, 2013

Stieneker, M., Riedel, J., Soltau, N., *et al.*: 'Design of series-connected dual-

- [10] Stieneker, M., Riedel, J., Soltau, N., et al.: 'Design of series-connected dualactive bridges for integration of wind park cluster into MVDC grids', EPE'14-ECCE Europe, Lappeenranta, 2014

- [11] Adam, G.P., Williams, B.W.: 'Half- and full-bridge modular multilevel converter models for simulations of full-scale HVDC links and multiterminal DC grids', *IEEE J. Emerg. Sel. Top. Power Electron.*, 2014, 2, (4), pp. 1089– 1108

- [12] Lian, Y., Adam, G.P., Holliday, D., et al.: 'Medium-voltage DC/DC converter for offshore wind collection grid', *IET Renew. Power Gener.*, 2016, 10, (5), pp. 651–660

- [13] Chen, W., Huang, A.Q., Li, C., et al.: 'Analysis and comparison of medium voltage high power DC/DC converters for offshore wind energy systems', *IEEE Trans. Power Electron.*, 2013, 28, pp. 2014–2023

- [14] Aboushady, A.A.: 'Design, analysis and modelling of modular mediumvoltage DC/DC converter based systems'. PhD thesis, University of Strathclyde, Glasgow, 2012

- [15] Wong, S.C., Brown, A.D.: 'Analysis, modeling and simulation of seriesparallel resonant converter circuits', *IEEE Trans. Power Electron.*, 1995, 10, (5), pp. 605–614

- [16] Agamy, M.S., Jain, P.K.: 'A variable frequency phase-shift modulated three-level resonant single-stage power factor correction converter', *IEEE Trans. Power Electron.*, 2008, 23, (5), pp. 2290–2300

[17] Chen, H., Sng, E.K., Tseng, K.J.: 'Generalized optimal trajectory control for

- [17] Chen, H., Sng, E.K., Tseng, K.J.: 'Generalized optimal trajectory control for closed loop control of series-parallel resonant converter', *IEEE Trans. Power Electron.*, 2006, 21, (5), pp. 1347–1355

- [18] Sano, K., Fujita, H.: 'Performance of high-efficiency switchedcapacitor-based resonant converter with phase-shift control', *IEEE Trans. Power Electron.*, 2011, 26, (2), pp. 344–354

- Bhat, A.: 'Fixed-frequency PWM series-parallel resonant converter', *IEEE Trans. Ind. Appl.*, 1992, 28, (5), pp. 1002–1009

- [20] Zhao, B., Song, Q., Liu, W., et al.: 'Overview of dual-active-bridge isolated bidirectional DC-DC converter for high-frequency-link power-conversion system', *IEEE Trans. Power Electron.*, 2014, 29, (8), pp. 4091–4106

[21] Giri, R., Choudhary, V., Ayyanar, R., et al.: 'Common-duty-ratio control of

- [21] Giri, R., Choudhary, V., Ayyanar, R., et al.: 'Common-duty-ratio control of input-series connected modular dc-dc converters with active input voltage and load-current sharing', *IEEE Trans. Ind. Appl.*, 2006, 42, (4), pp. 1101– 1111

- [22] Chen, W., Ruan, X., Yan, H., et al.: 'DC/DC conversion system consisting of multiple converter modules: stability, control, and experimental verifications', *IEEE Trans. Power Electron.*, 2009, 24, (6), pp. 1463–1474

- [23] Chen, W., Wang, G.: 'Decentralized voltage-sharing control strategy for fully modular input-series–output-series system with improved voltage regulation', *IEEE Trans. Ind. Electron.*, 2015, 62, (5), pp. 2777–2787

- [24] Mease, K.D., Topcu, U.: 'Two-timescale nonlinear dynamics and slow manifold determination'. Presented at the AIAA Guidance, Navigation, and Control Conf. and Exhibit, San Francisco, CA, August 2005, AIAA, pp. 2005–5846

- [25] Bacha, S., Munteanu, I., Bratcu, A.I.: 'Power electronic converters modeling and control: with case studies' (Springer, 2014)

- [26] Darwish, A., Massoud, A., Holliday, D., et al.: 'Single-stage three-phase differential-mode buck-boost inverters with continuous input current for PV applications', *IEEE Trans. Power Electron.*, 2016, **31**, (12), pp. 8218–8236

#### 8 Appendix

#### 8.1 Average model of bidirectional DAB

$\mathrm{d}V$

d*t*

di<sub>L</sub>

d*t*

dV.

d*t*

Operation when the DAB is controlled with PSC can be explained as shown in Fig. 8*b*. The state-space representation can be arranged as

i I:  $0 \le t \le Dt_s$

$$\begin{cases} = \begin{bmatrix} \frac{-1}{r_{1}C_{1}} & \frac{-1}{C_{1}} & 0\\ \frac{1}{L} & 0 & \frac{1}{nL}\\ 0 & \frac{-1}{nC_{2}} & \frac{-1}{r_{2}C_{2}} \end{bmatrix}^{\left[ V_{1} \right]} \\ + \begin{bmatrix} \frac{1}{r_{1}C_{1}} & 0\\ 0 & 0\\ 0 & \frac{1}{r_{2}C_{2}} \end{bmatrix}^{\left[ V_{dc1} \right]} \\ \end{cases}$$

(15)

ii II:  $Dt_s < t \leq (1-D)t_s$

$$\begin{bmatrix} \frac{dV_{1}}{dt} \\ \frac{di_{L}}{dt} \\ \frac{dV_{2}}{dt} \end{bmatrix} = \begin{bmatrix} \frac{-1}{r_{1}C_{1}} & \frac{-1}{C_{1}} & 0 \\ \frac{1}{L} & 0 & \frac{-1}{nL} \\ 0 & \frac{1}{nC_{2}} & \frac{-1}{r_{2}C_{2}} \end{bmatrix} \begin{bmatrix} V_{1} \\ i_{L} \\ V_{2} \end{bmatrix} + \begin{bmatrix} \frac{1}{r_{1}C_{1}} & 0 \\ 0 & 0 \\ 0 & \frac{1}{r_{2}C_{2}} \end{bmatrix} \begin{bmatrix} V_{dc1} \\ V_{dc2} \end{bmatrix}$$

(16)

Operation in durations (I and II) is symmetrical to that during (III and IV), so durations I and II will be considered.

It can be noted that two states, namely  $V_1$  and  $V_2$ , are varying much more slowly than the third variable  $i_L$ . So, the system under investigation is a two-time scale system [24].

Equating  $(di_L/dt)$  to zero and substituting for  $i_L$  in  $(dV_1/dt)$  and  $(dV_2/dt)$ , the equations yield

$$\frac{dV_{1}}{dt} = \frac{1}{r_{1}C_{1}}V_{dc1} - \frac{1}{r_{1}C_{1}}V_{1} - \frac{1}{C_{1}}i_{L}$$

$$\frac{dV_{2}}{dt} = \frac{1}{r_{2}C_{2}}V_{dc2} - \frac{1}{r_{2}C_{2}}V_{1} - \frac{1}{nC_{2}}i_{L}$$

$$i_{L} = \frac{V_{1} + V_{2}/n}{L}t + \frac{1}{2f_{s}L}[(1 - 2D) - nV_{1}])$$

(17)

where

## Fig. 8 DAB and AC/DC rectifiers

$< t \leq t_s$

(a) Simplified DAB circuit, (b) DAB operation with PSC, (c) AC/DC bidirectional converter, (d) AC/DC bidirectional converter operating modes (positive half cycle of in)

$$\frac{dV_{1}}{dt} = \frac{1}{r_{1}C_{1}}V_{dc1} - \frac{1}{r_{1}C_{1}}V_{1} - \frac{1}{C_{1}}i_{L}$$

$$\frac{dV_{2}}{dt} = \frac{1}{r_{2}C_{2}}V_{dc2} - \frac{1}{r_{2}C_{2}}V_{1} + \frac{1}{nC_{2}}i_{L}$$

$$i_{L} = \frac{V_{1} - V_{2}/n}{L}(t - Dt_{s}) + \frac{1}{2f_{s}L}[V_{2} - n(1 - 2D)V_{1}])$$

(18)

$$\frac{dV_1}{dt} = \underbrace{\frac{-1}{r_1C_1}V_1 + \frac{D^2 - D}{Lf_sC_1}V_2 + \frac{1}{r_1C_1}V_{dc_1}}_{f_1}$$

$$\frac{dV_2}{dt} = \underbrace{\frac{D - D^2}{Lf_sC_2}V_1 + \frac{-1}{r_2C_2}V_2 + \frac{1}{r_2C_2}V_{dc_2}}_{f_2}$$

(20)

The small-signal model can be expressed as [25, 26]

$$\frac{d\tilde{v}_{1}}{dt} = \begin{bmatrix} \frac{\partial f_{1}}{\partial V_{1}} & \frac{\partial f_{1}}{\partial V_{2}} \\ \frac{\partial f_{2}}{\partial V_{1}} & \frac{\partial f_{2}}{\partial V_{2}} \end{bmatrix} \begin{bmatrix} \tilde{v}_{1} \\ \tilde{v}_{2} \end{bmatrix} + \begin{bmatrix} \frac{\partial f_{1}}{\partial V_{dc1}} & \frac{\partial f_{1}}{\partial V_{dc2}} & \frac{\partial f_{1}}{\partial d} \\ \frac{\partial f_{2}}{\partial V_{dc1}} & \frac{\partial f_{2}}{\partial V_{dc2}} & \frac{\partial f_{2}}{\partial d} \end{bmatrix} \begin{bmatrix} \tilde{v}_{dc1} \\ \tilde{v}_{dc2} \\ d \end{bmatrix}$$

(21)

Hence

$$\begin{bmatrix} \frac{d\tilde{v}_{1}}{dt} \\ \frac{d\tilde{v}_{2}}{dt} \end{bmatrix} = \begin{bmatrix} \frac{-1}{r_{1}C_{1}} & \frac{D^{2}-D}{Lf_{s}C_{1}} \\ \frac{D-D^{2}}{Lf_{s}C_{2}} & \frac{-1}{r_{2}C_{2}} \end{bmatrix} \begin{bmatrix} \tilde{v}_{1} \\ \tilde{v}_{1} \end{bmatrix} + \begin{bmatrix} \frac{1}{r_{1}C_{1}} & 0 & \frac{2D-1}{Lf_{s}C_{1}}V_{2} \\ 0 & \frac{1}{r_{2}C_{2}} & \frac{1-2D}{Lf_{s}C_{2}}V_{1} \end{bmatrix} \begin{bmatrix} \tilde{v}_{dc1} \\ \tilde{v}_{dc2} \\ d \end{bmatrix}$$

(22)

Arranging and averaging over the period  $t_s$  gives

$$\begin{bmatrix} \frac{d\bar{V}_{1}}{dt} \\ \frac{d\bar{V}_{2}}{dt} \end{bmatrix} = \begin{bmatrix} \frac{-1}{r_{1}C_{1}} & \frac{D^{2}-D}{Lf_{s}C_{1}} \\ \frac{D-D^{2}}{Lf_{s}C_{2}} & \frac{-1}{r_{2}C_{2}} \end{bmatrix} \begin{bmatrix} \bar{V}_{1} \\ \bar{V}_{2} \end{bmatrix} + \begin{bmatrix} \frac{1}{r_{1}C_{1}} & 0 \\ 0 & \frac{1}{r_{2}C_{2}} \end{bmatrix} \begin{bmatrix} V_{dc1} \\ V_{dc2} \end{bmatrix}$$

(19)

#### 8.2 DAB converter small-signal model

The equations in (19) can be written as

*IET Power Electron.* This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

Therefore, the small-signal transfer functions of the system can be expressed as (see (23a))

(see (23b)) (see (23c)) (see (23d)) (see (24a)) (see (24b)) (see (24c))

### 8.3 Bidirectional AC/DC converter average model

The state-space representation of the circuit can be expressed as

$$\begin{bmatrix} \frac{di_{in}}{dt} \\ \frac{dV_{co}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & \frac{-1}{L_{in}} \\ \frac{1}{C_o} & 0 \end{bmatrix} \begin{bmatrix} i_{in} \\ V_{co} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_{in}} & 0 \\ 0 & \frac{-1}{C_o} \end{bmatrix} \begin{bmatrix} v_{in} \\ I_o \end{bmatrix}$$

(25)

$\delta$ :  $i_{in}$  decreases and  $V_{co}$  increases (25)

$$\begin{bmatrix} \frac{di_{\rm in}}{dt} \\ \frac{dV_{\rm co}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} i_{\rm in} \\ V_{\rm co} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_{\rm in}} & 0 \\ 0 & \frac{-1}{C_{\rm o}} \end{bmatrix} \begin{bmatrix} v_{\rm in} \\ I_{\rm o} \end{bmatrix}$$

(26)

$1-\delta$ :  $i_{in}$  increases and  $V_{co}$  decreases (26).

Similarly, the average equations of the AC/DC rectifier can be written as

$$\tilde{\nu}_{\rm co} = \frac{\tilde{\delta}}{1 + C_{\rm o}L_{\rm in}s^2} V_{\rm in} - \frac{L_{\rm in}s}{1 + C_{\rm o}L_{\rm in}s^2} \tilde{i}_{\rm o}$$

(27)

Equation (27) can be rewritten as

$$\tilde{v}_{co} = \frac{\tilde{\delta}}{1 + C_{o}L_{in}s^{2}}V_{in} - \frac{L_{in}s}{1 + C_{o}L_{in}s^{2}}\frac{\tilde{v}_{co}}{G_{14}}$$

(28)

Rearranging (28)

$$G_{11}(s) = \frac{\tilde{v}_1}{\tilde{v}_{dc1}}$$

$$= \frac{L^2 f_s^2 (sC_2 r_2 + 1)}{(C_1 C_2 L^2 f_s^2 r_1 r_2) s^2 + L^2 f_s^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_s^2)}$$

(23a)

$$= \frac{1}{(C_1C_2L^2f_s^2r_1r_2)s^2 + L^2f_s^2(C_1r_1 + C_2r_2)s + r_1D^2(r_2D^2 - 2r_2D + r_2) + L^2f_s^2}$$

$$G_{12}(s) = \frac{\tilde{v}_1}{\tilde{v}_{dc2}}$$

$$= \frac{DLf_s r_1 (D-1)}{(C_1 C_2 L^2 f_s^2 r_1 r_2) s^2 + L^2 f_s^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_s^2)}$$

(23b)

$$G_{13}(s) = \frac{\tilde{v}_1}{d}$$

LC<sub>2</sub>V<sub>def</sub>f\_r,r\_3(2D - 1)s +r\_3(2D - 1)(V\_1r\_2D(1 - D) + LV\_{def}f\_2)

$$= \frac{2C_2 + 4C_2 + 5(2-2)}{(C_1C_2L^2f_8^2r_1r_2)s^2 + L^2f_8^2(C_1r_1 + C_2r_2)s + r_1D^2(r_2D^2 - 2r_2D + r_2) + L^2f_8^2)}$$

$$G_{14}(s) = \frac{\tilde{i}_{in}}{\tilde{v}_{dc1}}$$

$$= \frac{(C_1 C_2 L^2 f s^2 r_2) s^2 + L^2 f_s^2 C_1 s + D^2 (r_2 D^2 - 2r_2 D + r_2)}{(C_1 C_2 L^2 f_s^2 r_1 r_2) s^2 + L^2 f_s^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_s^2)}$$

(23d)

$$G_{21}(s) = \frac{\tilde{v}_2}{\tilde{v}_{dc1}}$$

$$= \frac{Lf_s r_2 D(1-D)}{(C_1 C_2 L^2 f_s^2 r_1 r_2) s^2 + L^2 f_s^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_s^2)}$$

(24a)

$$G_{22}(s) = \frac{\tilde{v}_2}{\tilde{v}_{dc2}}$$

$$= \frac{L^2 f_s^2 (sC_1 r_1 + 1)}{(C_1 C_2 L^2 f_s^2 r_1 r_2) s^2 + L^2 f_s^2 (C_1 r_1 + C_2 r_2) s + r_1 D^2 (r_2 D^2 - 2r_2 D + r_2) + L^2 f_s^2)}$$

(24b)

$$G_{23}(s) = \frac{v_2}{d}$$

$$= \frac{\mathrm{LC}_1 \mathrm{V}_{dc1} \mathrm{f}_{s} \mathrm{r}_1 \mathrm{r}_2 (1 - 2\mathrm{D}) \mathrm{s} - \mathrm{r}_2 (2\mathrm{D} - 1) (\mathrm{V}_{dc2} \mathrm{r}_2 \mathrm{D} (\mathrm{D} - 1) + \mathrm{LV}_{dc2} \mathrm{f}_s)}{(\mathrm{C}_1 \mathrm{C}_2 \mathrm{L}^2 \mathrm{f}_{s}^2 \mathrm{r}_1 \mathrm{r}_2) \mathrm{s}^2 + \mathrm{L}^2 \mathrm{f}_{s}^2 (\mathrm{C}_1 \mathrm{r}_1 + \mathrm{C}_2 \mathrm{r}_2) \mathrm{s} + \mathrm{r}_1 \mathrm{D}^2 (\mathrm{r}_2 \mathrm{D}^2 - 2\mathrm{r}_2 \mathrm{D} + \mathrm{r}_2) + \mathrm{L}^2 \mathrm{f}_{s}^2)}$$

(24c)

IET Power Electron.

(23c)

This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

$$G_{\rm ac}(s) = \frac{\tilde{v}_{\rm oc}}{\tilde{\delta}} = \frac{G_{14}}{G_{14}(1 + C_{\rm o}L_{\rm in}s^2) + L_{\rm in}s}V_{\rm in}$$

(29)