provided by Elsovier - Bublisher Connecte

Fabian Radulescu, Paul Miller, Liam Cunnane\*, Mark Harris\*, Hien Lam\* and Charles Bowers\*\*

TriQuint Semiconductor,

2300 NE Brookwood, Hillsboro,

OR 97124,

e-mail: fradulescu@tqs.com,

ph: 503-615-9443

\*Trikon Technologies,

Ringland Way, Newport,

NP18 2TA, UK

\*\*Eco-Snow Systems,

Livermore, CA

In spite of the substantial progress made in the last decade, the GaAs IC industry is still far from reaching the high manufacturing yields established by the Si fabs. High volume applications that target the large consumer electronics market bring a new challenge to the ordinary GaAs manufacturing line and the lure to be more "Si-like" is the motivation for many new process developments. However, adopting Si methods often requires a hard re-thinking of the traditional paradigms established in the early years of

GaAs IC processing. By implementing an all-sputtered metallization process in conjunction with CO2 snow metal lift-off, we believe we overcame one such paradigm. We demonstrate that evaporation is not the only suitable method for lift-off patterning and show that sputtering could represent an attractive alternative. In this paper we will discuss some of the benefits and difficulties that come from using sputtering as the metal deposition method of choice in a high volume GaAs manufacturing line.

# Complete sputtering metallization for high-volume manufacturing

Over the last decades, the semiconductor industry stuck to a very aggressive trend of continuously increasing the wafer size. Driven by the need to accommodate larger and larger wafers, the batch-style processing lost its popularity because of the increased footprint required for the tools and also because of the extra time required to handle the wafers. Single-wafer, cassette-to-cassette processing proved to be the better solution for a large number of applications. In the particular case of III-V metallization, the most prevalent batch processing technique is evaporation, mainly performed in large dome systems.

However, this method doesn't suit itself for single wafer processing so most cassette-to-cassette cluster metallization tools are based on sputtering. The single-wafer sputtering tools generally employ a load-lock system and the deposition takes place in a relatively small, well controlled chamber. This configuration offers several advantages over the typical e-beam batch evaporation:

- a) Higher vacuum levels are easier to maintain

- b) Increased deposition repeatability

- c) Less particles generated by melting metals or by exposed moving mechanisms

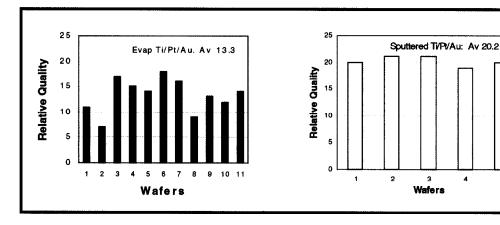

Figure 1. Relative quality, meander structures patterned by lift-off. 52% increase in RQ by sputter vs. evaporation.

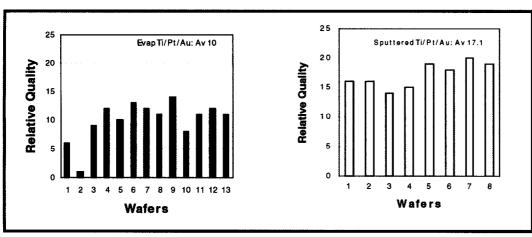

Figure 2. Relative quality, comb structures patterned by lift-off. 72% increase in RQ by sputter vs. evaporation.

- d) Integrating pre-metallization, in-situ processing steps is straightforward (e.g. adding extra modules for sputter etch clean)

- e) Reclaiming precious metals is more efficient

- f) Less extensive manual wafer handling

The Si industry has adopted sputtering as the metallization method of choice for numerous applications and batch evaporation is hardly employed at all. In contrast, sputtering could not be adopted easily by the III-V industry mainly because it was considered unsuited for the liftoff patterning method. The need to increase the wafer size to 150 mm brought new processing challenges and also made us rethink this past limitation. During this development effort we learned that actually sputtering and lift-off patterning could be integrated into a robust and efficient process. In this paper we will present data that demonstrates reduced defectivity levels with the introduction of sputtering metals. The lift-off integration issue will be analyzed along with new equipment developments that made it possible. Potential problems associated with stress and microstructural differences will also be discussed.

# **Defectivity**

One particular advantage of sputtered metallization is the improvement in defectivity levels compared to an evaporator. Evaporators and their associated tooling typically contribute high particle counts plus a high density of metal "splashes" as the melt spits. Comb and meander tests graphically demonstrate the reduction in defectivity seen by moving to an all-sputter lift-off process, Figures 1 and 2. For these tests, Ti/Pt/Au comb and meander structures were deposited by sputtering and

evaporation and then patterned by lift-off. Resist removal and post resist clean up followed the same procedure in both cases. Data was normalized to a metric called Relative Quality (RQ), representing the number of sites passing the test. Figure 1 shows RQ for the meander structure for evaporated and sputtered metal, demonstrating a 52% increase in good die for the sputtered metal. Figure 2 shows a similar benefit for the sputtered comb structures with a 72% increase in good die. We believe that the improved comb data for sputtered metal is due to much-reduced particles and therefore reduced shorts. The high meander RQ is due to the absence of metal spits and therefore no opens. This trend is also confirmed by our SPC particle check tests that are performed regularly in the manufacturing line. In this respect, the sputtering tools performance is net superior to their evaporation equivalents employed on the 100-mm line.

### Metal lift-off

In general, the increased non-directionality of the sputtered metal will increase the sidewall coverage of the patterned resist in relation with its evaporated counterpart. This makes the traditional solvent lift-off process more difficult. As a result, this has been the main barrier in utilizing sputtered metallization in fabricating GaAs IC's. Superior sidewall coverage prevents solvent penetration to dissolve the photoresist layer, resulting in longer solvent soak cycle times, increased solvent usage, or inconsistent lift-off.

However, several recent equipment developments have addressed this issue, and have opened up the potential for use of sputtering processes in place of evaporative. Directional

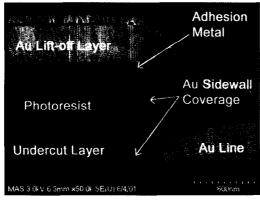

Figure 3. Cross sectional SEM image of sputtered metal line prior to lift-off.

sputtering and the use of efficient backside wafer cooling, followed by a CO2 snow liftoff process have made sputtered metal processes reliable.

The CO2 snow lift-off removes the unwanted metal from the wafer by initiating a thermal expansion mismatch between the metal layer and the photoresist. This causes the metal to crack and delaminate at the photoresist interface. The loosened metal is then carried off the wafer surface by the CO2 snow.

# **Challenges**

New metallization challenges faced by the Si industry, like the need for high aspect ratio via bottom fill, sparked off developments in directional sputtering, (e.g. long throw, collimation, ionized sputtering) [1, 2]. The same approach was applied to sputtering metals for lift-off patterning and an example of such a structure is presented in Figure 3. This example shows a profile with reduced sidewall metal coverage that is suited for lift-off.

solvent liftoff. But, through the use of CO2 snow lift-off, this problem has been overcome.

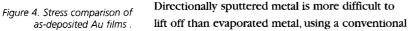

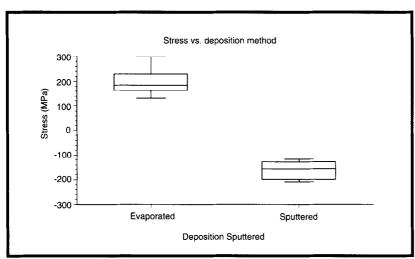

By switching the metal deposition method to sputtering, the growth of the metal films is dramatically changed. In relation with evaporation, sputtering metal deposition involves a higher kinetic energy flux of neutral and charged species. Furthermore, the presence of the sputtering gas during the deposition opens up the possibility that gas molecules could get incorporated into the metals grain matrix. This will modify the microstructure of these films and this difference will translate into altered electrical and mechanical properties. However, we were able to find solutions to these problems but integrating an all-metals sputtering system had to take into account the new, microstructurally different material. For example, the stress of the asdeposited sputtered metal is generally more compressive than the stress of the evaporated metal films and this could have great implications on the mechanical integrity of the whole IC thin film stack. Figure 4 illustrates the stress comparison between evaporated Au and sputtered Au.

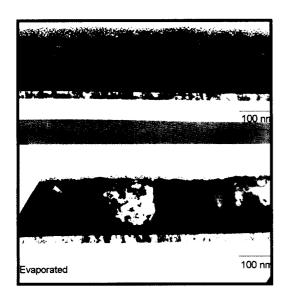

This stress difference could be correlated with the microstructure of evaporated Au in comparison with sputtered Au. The TEM cross-sections presented in Figure 5 show the anisotropical columnar grain structure of the sputtered material. In contrast, a closer to equilibrium and potentially more stable Au film can be noticed in the equiaxial grain microstructure obtained by evaporation.

### **Conclusions**

We've established that single-wafer sputtering can be integrated successfully along with lift-off patterning and to the best of our knowledge, this is the first such system reported. In doing that, we've demonstrated improved yields by lowering the defectivity levels along with reliable lift-off. Also, some difficulties associated with controlling the microstructure and stress of the sputtered films were presented.

# **Acknowledgements**

We greatly acknowledge the work of numerous engineers from TriQuint Semiconductor that were deeply involved into this project. The contributions of Dr. Jeremy Middleton, Dr. Jinhong Yang, Dr. Rick Morton and Jerry Mahoney of TriQuint Semiconductor were crucial to the success of this work.

We would also like to thank Moreen Minkoff from TriQuint Semiconductor for the defectivity data and Materials Analytical Services for the SEM work.

The tedious TEM prep and analysis was performed by Zhenkun Ren and Dr. Jack McCarthy at Oregon Graduate Institute, ECE Dept and we

Figure 5. TEM cross-sectional micrographs of evaporated and sputtered Au films

greatly acknowledge their contribution. We also received valuable suggestions and support from David Butler of Trikon Technologies.

### References

- 1. "High Performance, High Productivity Interconnect by Sputtered Metal and Dry Carbon Dioxide Lift-off Techniques". D.C. Butler et al, CS-Max 2001.

- 2. "Sputtering process gives III-V devices a performance boost". Andy Bavin, Compound Semiconductor Oct 2001, vol 7, #9. pp 73-76.

## **Acronyms**

IC: Integrated Circuit

RQ: Relative Quality

SEM: Scanning Electron Microscopy

TEM: Transmission Electron Microscopy

CO2: Carbon Dioxide

RES No.117 – USE THE FAST NEW ENQUIRY SERVICE @ www.three-fives.com