DIAMOND RELATED MATERIALS

CrossMark

Diamond & Related Materials 65 (2016) 168-175

Contents lists available at ScienceDirect

**Diamond & Related Materials**

journal homepage: www.elsevier.com/locate/diamond

# Single crystal diamond wafers for high power electronics

# Shinichi Shikata

Kwansei Gakuin University (KGU), 2-1 Gakuen, Sanda, Hyogo, 669-1337, Japan

#### ARTICLE INFO

Article history: Received 11 February 2016 Received in revised form 14 March 2016 Accepted 15 March 2016 Available online 18 March 2016

*Keywords:* Single crystal diamond Diamond wafer Power device

# ABSTRACT

According to international energy proposal, about 25% of the total CO2 reduction should come from "end use efficiency". Hence, low loss power devices are an important technology for the 21st century. Diamond-based devices have the potential, but this would require fast development in order to contribute to the CO2 reduction plan early in this century. Here, we present a clear target for the R&D of diamond wafer. According to the expected applications of diamond devices with a vertical structure, the required target properties for first stage diamond wafers are; a killer defect density less than 0.1 cm<sup>-2</sup>, resistivity less than 0.005  $\Omega$  cm and a size of 4 in. For the final commercialization stage, targets of zero killer defects, resistivity of 0.001  $\Omega$  cm and a size of 6 in. are proposed. The challenges and proposal solutions are reviewed for each technology.

© 2016 The Author. Published by Elsevier B.V. This is an open access article under the CC BY-NC-ND licenses (http://creativecommons.org/licenses/by-nc-nd/4.0/).

#### 1. Introduction

The threat of global warming is becoming more and more critical; recently CO2 concentrations observed in Hawaii exceeded 400 ppm [1]. In the recent "Conference of Parties (COP)" 21 climate meeting, the participating countries submitted and adopted "Intended Nationally Determined Contribution (INDC)" [2] targets for CO2 reduction, for example, 40% in 2030 (vs. 1990) for EC, 26-28% in 2025 (vs. 2005) for US, and 26% in 2030 (vs. 2013) for Japan. According to the latest report by the International Energy Agency (IEA), "World Energy Outlook", the world temperature is likely to rise 5.3 °C by the end of the 21st century if new CO2 reduction policies are not implemented. To follow the "delayed" 450 ppm CO2 scenario, several technical policies are expected and the largest contribution is obligatory "end use efficiency" target that is intended to be responsible for 49% of the total worldwide emission reduction by 2030 [3]. This is three times larger than the "Renewable energy" target of 17%. Undoubtedly, the low loss power electronics will play a major role in improving "end use efficiency".

In 2013, Mitsubishi Electric delivered a practical railcar power supply system that incorporated the world's first silicon carbide (SiC) power modules using Schottky barrier diode (SBD). Very fast and low power loss device allows the system to achieve many advantages of 30% less power loss, with the additional advantages of 20% smaller and 15% lighter power module. The Mitsubishi system also reduces transformer noise by 4 dB due to a 35% improvement in the distortion rate of output voltage waveforms [4]. In December 2015, the full SiC power modules consisting of SBD and metal oxide semiconductor field effect transistors (MOSFET) were introduced into "Yamanote line" railway; saving 17% power losses during powered operation [5]. The full SiC modules are currently under testing for use in Shinkansen in the near future [6]. For automotive applications, Toyota has announced their plan to introduce full SiC modules in 2020 in hybrid electric vehicle (HEV) systems [7]. Since the beginning of R&D of SiC devices, the achievement of low loss was expected however, many additional advantages were observed, such as power regeneration during high speed running and very light weight modules. These characteristics come from the high frequency operation of SiC due to very small "charge transfer" of unipolar device, and the small sizes of the reactive L and capacitor C.

Diamond is also a hopeful candidate material for next generation power devices due to its favorable properties such as a high breakdown field, high thermal conductivity, high mobility and low dielectric constant [8,9]. There are several big material challenges to overcome for the practical application of diamond devices. In particular, the fabrication of a single crystal wafer with large size, dislocation free, and low resistivity. In addition, there are some drawbacks such as deep acceptor (B: 0.37 eV) and donor (P: 0.57 eV) level with imperfect doping for donor. However, at elevated temperatures such as from 200 to 250 °C; that is the selfheating temperature of the power devices, increased numbers of activated carriers with high mobility such as 240 cm<sup>2</sup>/Vs at 250 °C contribute to a reduction in conduction losses [10]. This is based on a new concept of unipolar power devices that do not require "cooling systems". The present status of the R&D on diamond materials for power devices is somewhat disjointed; it is considered beneficial to discuss definite target with diamond devices in order to accelerate research and contribute to the global CO2 reduction plan. In this paper, we review the current status of

http://dx.doi.org/10.1016/j.diamond.2016.03.013

0925-9635/© 2016 The Author. Published by Elsevier B.V. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

E-mail address: SShikata@kwansei.ac.jp.

diamond wafer R&D and propose targets with respect to the existing challenges for fabricating large size wafers with low dislocation density and low resistivity [11].

# 2. Applications of diamond power devices and specifications of diamond wafer

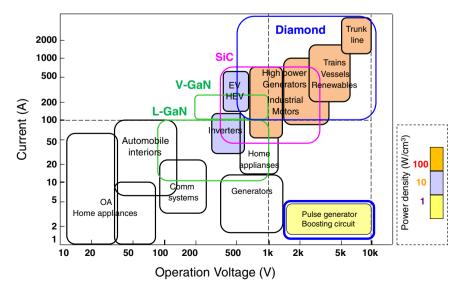

The wafer specifications for power device applications differ depending on the application. In this section, the expected applications for the diamond devices are reviewed before discussing the detailed specifications. Possible applications are summarized with respect to current–voltage map, as shown in Fig.1. As described in the introduction, the recent replacement of Si by SiC devices suggests a future transition to diamond devices.

Firstly, we predict applications for diamond devices in the high voltage field, such as high power generators and inverters for trains, ships, renewable energy systems, and power trunk line systems. The realization of SiC unipolar devices using both SBD and MOSFET for high voltage applications enabled low loss devices compared to previous Si bipolar devices. This is due to the accumulation and recombination of minority carriers in the bipolar device, whereas the charge transfer in unipolar devices only depends on the depletion and transferred charges. In the higher voltage region, wide bandgap bipolar devices suffer high forward loss of Von  $\times$  Ion, due to high "on voltage" such as over 4 V for SiC. Hence, diamond unipolar devices with low losses might find applications in the high voltage field.

Another important factor that allows SiC devices to realize low losses is the fast switching or high frequency operation, typically several microseconds [12]. This fast switching enables electric power regeneration during the high speed running mode of trains that avoids using the mechanical break system. Low loss unipolar diamond power devices may have faster switching compared to SiC devices; this has been partly verified by SBD [13]. Additionally, fast switching also implies smaller power module with small size capacitor C and reactor L of high frequency operation. A total volume reduction for SiC module of 55% can be attained compared to Si IGBT and pn diode modules [12].

For extremely high voltage applications over 10 kV device, wide bandgap bipolar devices are expected to open up new opportunity in the future [14], diamond bipolar devices are a hopeful candidate owing to their favorable characteristics. Diamond that uses deep energy level carriers has increased numbers of carriers at high temperature. The tradeoff in carrier increases with the mobility decrease brought by "carrier scattering", resulting in a constant current between 150 and 250 °C [15]. This characteristic has inspired new type of high output power device module operating at self-heating temperatures; which are thermally insulated without cooling. In addition, there exist numerous applications in lower voltage range including ultra and super high frequency fields. Here, AlGaN/GaN HEMT devices are already used for many applications incorporating high mobility two dimensional electron gas (2DEG) channel.

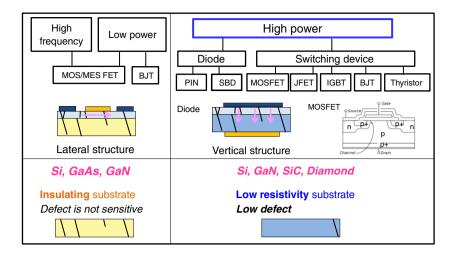

Some applications and their corresponding device structures are shown in Fig.2. For the low power devices including high frequency applications, the lateral structure is adopted for the devices such as field effect transistors (FET). AlGaN/GaN HEMT power devices are commercialized for high frequency application using insulating substrates. Dislocations are not critical for this application, because of the lateral current flow. On the other hand, the vertical structure is adopted for high power applications to meet the requirements for high current densities. In the vertical structure, current flows from the substrate surface to the electrode at the back surface, thus the majority of the substrate acts as a resistive power loss layer and simultaneously a thermally resistive layer. In order to fabricate low loss devices for high power devices, a low resistivity substrate is essential, often requiring a final back-lap process to thin the substrate.

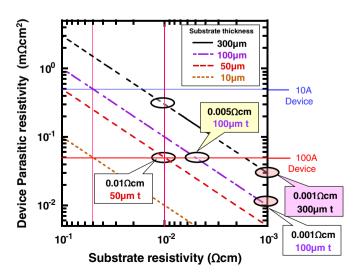

The parasitic resistivity of devices as a function of substrate resistivity and thickness are shown in Fig.3. The dotted lines show data for substrate thicknesses of 300 µm, 100 µm, 50 µm and 10 µm after the back lap process. A thickness of 50 µm is technically possible for the R&D purposes; however, 100 µm is considered as the limit for mass production. 10 A and 100 A lines only show conventional standard image of resistivity. A final target for substrate resistivity could be 0.001  $\Omega$  cm, corresponding to the devices over 100 A with a substrate thickness of 300 µm. A first target could be 0.005  $\Omega$  cm corresponding to 100 A device with a substrate thinned down to 100 µm; this resistivity is comparable to that of present SiC wafers. Doping with B to achieve a resistivity of 0.01  $\Omega$  cm is already possible using conventional MPCVD for thin films, and thicker films grown up to 50 µm can correspond to 100 A class devices.

Another critical property of the substrate for power devices is the dislocation density, as the current flows from the substrate surface to the back electrode in the case of a vertical structure device. The dislocation density of current 4H SiC wafers [16] compared to the expected final target is shown in Table 1. Micro pipes (MP), threading screw dislocations (TSD) and basal plane dislocations (BPD) are the critical dislocations to device performance, where these dislocation densities are <1, 300–600 and 1–10 for the typical commercially available wafers, respectively. In particular, MPs are the famous killer defects in SiC, the existence of which is inevitable for all types of devices. The numbers of

Fig. 1. Application possibilities in current- voltage map.

Fig. 2. Device applications and corresponding device structures and wafer.

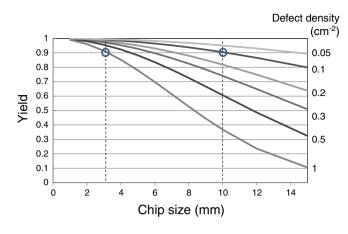

malfunction device is influenced by the numbers of killer defects as well as the device active area. It is given by the following Murphy plot for killer defects and it is extremely effective when the chip size is large, that is, a high current for the power device, as shown in Fig.4.

$$\mathbf{Y} = \exp(-\mathbf{A}\mathbf{D}) \tag{1}$$

Here, Y is the yield of device, A is the area of the device and D is the defect density. As can be seen from the figure, the devices yield decreases significantly, even at the lowest defect densities. For the first target, a defect density of 0.1  $\text{cm}^{-2}$  is assumed, that is a 90% yield for a 10 mm  $\times$  10 mm size chip, corresponding to >100 A device. The final target is of course, zero killer defects. The final target dislocations densities have been concluded as a result of private communications with many researchers in the SiC field; zero dislocations are expected for MP and BPD with small numbers remaining for TSD. Considering the aforementioned circumstances in SiC that is capable of supplying the first stage devices in the market suffering present wafer defects, it is reasonable to set the first target for dislocation numbers in diamond to the present value for SiC, that is, <500 cm<sup>-2</sup>. In addition, the final target for diamond might follow that of SiC,  $<10 \text{ cm}^{-2}$ . In the early stages of R&D, testing of 10 A devices is important for the verification of the properties of diamond devices, thus dislocation densities  $<5000 \text{ cm}^{-2}$  might be a suitable criterion in this case. To summarize, the expected specifications

Fig. 3. Device parasitic resistivity dependence of substrate resistivity with varieties of final substrate thickness.

of diamond wafers, such as resistivity, dislocation density, and wafer size are shown in Table 2. Here, R&D target implies the wafer target to support R&D for a 10 A class power device that is suitable for evaluating the properties of the diamond devices. The first target is set considering the expected characteristics of wafers for small scale mass production of devices comparable to present SiC wafer fabrication. The final target is based on a full mass production case.

## 3. Large size wafers

Recent development of diamond wafers has been summarized in a special issue of MRS journal [17]. Hetero-epitaxial growth techniques using large hetero-substrates such as MgO [18], SrTiO3 [19], Al2O3 [20] and YSZ/Si [21] are hopeful for its original substrate size. A drawback of hetero-epitaxial growth is the high dislocation density, far beyond that of single crystals, that originates from the coalescence of crystal plates. Several trials are now underway trying to resolve this problem. Using a sophisticated growth technique on Ir/YSZ/Si for thick films up to 1 mm, the dislocation density reduced three orders of magnitude, from  $10^{10}$  cm<sup>-2</sup> to  $10^{7}$  cm<sup>-2</sup> [18], where an order of magnitude increase in thickness corresponded to an order of magnitude reduction in the dislocation density. Another method likely to reduce dislocation density is the epitaxial lateral overgrowth (ELO) of diamond on Ir(001) / MgO(001) substrates, as it was demonstrated using the patterned nucleation and growth method [22]. The reduction of dislocation density down to the order of 10<sup>3</sup> cm<sup>-2</sup> is expected for hetero-epitaxial growth technique in the future.

Another promising technology to realize large wafer production is the mosaic wafer fabrication method [23–25]. The size of present mosaic wafers fabricated by AIST is from  $2 \times 2 \text{ cm}^2$  to  $4 \times 6 \text{ cm}^2$ , where the largest one is a little larger in area than a 2 in. f wafer. Mosaic wafers are consist of several plates of approximately 1 cm<sup>2</sup> single crystal diamond fabricated by a copying technique using ion implantation and lift-off [26]. Power device fabrication is avoided on the crystal boundary of the joined region; therefore, unusable area of a mosaic wafer may be very high when the

Table 1

Dislocation density image of present 4H SiC wafer and expected final target.

|                 | Typical comm. available wafer $(cm^{-2})$ | Final target $(cm^{-2})$ |

|-----------------|-------------------------------------------|--------------------------|

| Micropipe       | 0-0.02                                    | 0                        |

| Threading screw | 300-600                                   | <10                      |

| Basal plane     | 1–10                                      | 0                        |

| MP + TS + BP    | 301-610                                   | <10                      |

| Threading edge  | 3 k-6 k                                   |                          |

a) Image of multi-joined wafer

Fig. 4. Killer defect density dependence of the device yield. (Assuming the square chip).

device size differs from the plate size. In the worst case, up to 40% of the wafer area will not be used for the device. This is schematically shown in Fig.5a). Accordingly, such a "multi-joined wafer" cannot be used for mass production. However, the center-joined wafer shown in Fig.5b) can be used as conventional wafer, because the joint boundary area exists on the dicing lines of the center chips. In this case, the size of the plate is half the wafer size, e.g. a 1 in. plate for 2 in. wafer, and a 2 in. plate for 4 in. wafer. Thus the enlargement of single crystal plate size associated with the low dislocation density is very important for the mosaic wafer.

To realize large plates up to 1-3 in., the vertical growth of bulk crystal is an urgent challenge to be addressed. This is directly associated with the low dislocation density growth as it is in the case in Silicon Carbide; well known as the repeated A face (RAF) bulk crystal growth method [27]. The largest drawback for bulk growth of diamond is the non-equilibrium growth accompanied by very large temperature gradients of 900 °C within the diamond crystal, that is; 1000 °C on the growth front of bulk edge facing high temperature plasma ball of up to 2800 °C, and 100 °C on the other bulk edge which is adjacent to water cooled holder. This large temperature gradient introduces large strain in the bulk diamond. During the last ten to twenty years, several techniques have been investigated that might be applicable for diamond wafers, such as pulsed plasma processing and electron cyclotron resonance (ECR) plasma processing. Pulsed plasma processing can provide variations in the electron temperature, electron density, and gas temperature by changing the frequency and duty ratio of an input pulse [28-32], and high quality diamond was reported using this technique [29]. The pulsed operation method was also employed in ECR mode plasma processing, where a high growth rate was observed with low temperature deposition [33]. Currently, research activities using pulsed plasma are not common for the growth of large diamond wafers, because the input plasma power is not large enough to cover the low duty ratio conditions. For instance, 3 kW deposition with 10% duty ratio requires initial power of 30 kW for the generator, which is not yet achieved for 2.45 GHz. However, the recent development of devices including "all solid" generators using semiconductor high frequency amplifiers will find a possible method to meet the requirements of high power generators. Most of the plasma CVD systems used in diamond growth use 915 MHz and 2.45 GHz ISM (Industrial, Scientific and Medical) bands for microwave-based growth equipment. Several trials scaling up the

Table 2

Expected specification of single crystal diamond wafer for power device application.

|                                    | R&D target                          | First target                                      | Final target                           |

|------------------------------------|-------------------------------------|---------------------------------------------------|----------------------------------------|

| Wafer size                         | 2 in¢                               | 4 in¢                                             | >6 in¢                                 |

| Resistivity<br>Dislocation density | 0.01 Ω cm<br><5000 cm <sup>-2</sup> | $0.005 \ \Omega \ {\rm cm} < 500 \ {\rm cm}^{-2}$ | $0.001 \ \Omega \ cm$ $< 10 \ cm^{-2}$ |

| Killer defect density              | $<1 { m cm}^{-2}$                   | $< 0.1 \text{ cm}^{-2}$                           | $0  {\rm cm}^{-2}$                     |

Fig. 5. Diamond wafer images using mosaic technique.

plasma size demonstrated the possibility for large scale deposition [34]. However, additional bands were allocated for ISM band by ITU [35] for lower frequencies such as 862-875 MHz, 433.05–434.79 MHz and 312-315 MHz. These bands provide longer wavelengths that can respond to larger size plasma excitation, such as a wavelength of 69.1 cm for 433 MHz plasma. Of course, some of the non-plasma systems reviewed in the previous paper [36] are also good candidates and further research into these methods is highly required.

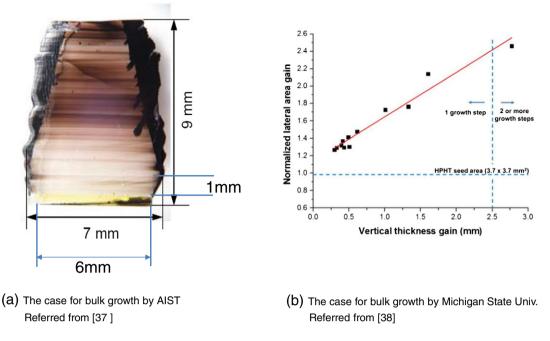

To realize large area single crystal diamond plates up to 1–3 in., both lateral growth and vertical growth are important. In Fig.6, two figures are shown, which are reproduced from papers on CVD bulk crystal growth by AIST [37] and Michigan State University [38]. In both cases, the bulk diamond growth rate in the lateral direction is similar to that in the vertical direction; such as 1.17 times the lateral growth during 1 mm vertical growth and 1.4 times the lateral gain during 2.5 mm of vertical growth. The limitation in the growth rate is due to the polycrystalline rims that grow in periphery of the single crystal region. Use of recessed holders [39,38] will be helpful to reduce this polycrystalline rim. For further improvements, reduction of gas turbulence and the concentration of plasma near the crystal edge, as well as optimization of the growth parameters are the new challenges [39–41].

#### 4. Low dislocation density wafers

We can learn the history of SiC wafer development to find solutions for the challenges in the development of vertical structure high output power diamond devices. The commercialization of 1 in. SiC wafers occurred in 1991, and that of 2 in. in 1996, both by a US company CREE. It took 8 years further to commercialize Schottky barrier diode (SBD) of 3 to 6 A class devices for power factor correction (PFC) circuit applications in 2003 by the German company SICED. This period coincided well with the development of compound semiconductors such as GaAs and InP. 2 inch diameter GaAs devices began a small-scale mass production in 1981, and the AlGaAs/GaAs high electron mobility transistor (HEMT) was introduced in receivers for satellite broadcast systems in 1987. Also, 1.55 µm DFB lasers became popular for optical fiber communication systems in 1989 using 2 in. InP wafers that achieved small scale mass production in 1981 [43,44]. Both AlGaAs/GaAs HEMT and DFB lasers are small lateral type device sand they suffer in a very small way from the influence of wafer dislocations and defects. However, the first introduction of over 100 A class SBD high output power devices to train systems was in the Tokyo Metro in 2013 [4]. This was 17 years after the commercialization of 2 in. wafer. To emphasize this again, the R&D time to apply 3 A device and 100 A devices was 8 years and 17 years, respectively. This is mainly due to the R&D time required for the reduction of the dislocation densities. In the early age of SiC, it suffered from "micro-pipe" defect around 100 cm<sup>-2</sup> in 1996, and it took 7 years to achieve a micro-pipe free wafer by "Repeated A Face (RAF)"

Fig. 6. Lateral growth of diamond.

method in 2003 [42]. After the reduction of micro-pipes, it took 10 years to realize 100 A class vertical devices by reducing dislocations and other defects that negatively influence the device characteristics. Of course, other dislocations and defects were also important issues in SiC wafer development during this period. TSD and BPD dislocations are very critical for MOSFET characteristics [45], TSD leads to lower breakdown voltages [46] and BPD influences the forward characteristics in bipolar devices [47,48]. Some residual BPDs can be converted to TEDs, by high temperature annealing of epitaxial layers [49]. In addition, it is known that some of the TSDs can be converted to Frank partial dislocations by sophisticated epitaxial growth technology [50]. Many TEDs exist in SiC wafers; however, this is not very critical to the device performance.

For diamond devices, research activities on dislocation reduction are currently in a very early stage. Since the methods of X ray topography were first applied to diamond in 1944 [51], other methods have been proposed [52-54] and some studies have been carried out for dislocation analysis. A study on CVD homo epitaxial layers on HPHT substrate showed that large numbers of dislocations originate from the interface [55], resulting from the immature CVD technique presently used for diamond growth, in particular the surface treatment prior to the growth. The analysis of Burger's vector of dislocations was carried out using X ray topography with synchrotron radiation (SR) for the HPHT substrates and CVD films, and "edge" and "mixed" type dislocations were identified [56–58]. By comparing the data with cathode-luminescence (CL) mapping results, the well-known "band A" emission showed good agreement with the "mixed" type dislocation in p- layer deposited on Ib HPHT crystal [57]. Dislocation densities of conventional HPHT substrates have been estimated to be from  $10^3 \text{ cm}^{-2}$  to  $10^8 \text{ cm}^{-2}$ , most likely from  $10^4$  cm<sup>-2</sup> to  $10^6$  cm<sup>-2</sup> [59], however it is difficult to quantify the exact numbers because of the existence of dislocation bundles. Defect observed by birefringence appeared as bundles of ten or more defects after etching by O2/H2 plasma [60]. Dry etching with various gases such as CO2/H2, is used to evaluate dislocation densities [61], however, there are no standard methods for evaluating the density. The lack of an effective wet etchant for diamond is making the evaluation and understanding of dislocations very difficult. It is important to establish a standard dry etching procedure in order to understand and promote the R&D for the reduction of dislocations. In addition, the studies on the relationship between the dislocation detected by topography and dry etched pits are very much required to understand the types of dislocations and their density.

There are several emerging methods for reducing dislocation densities. The first is to reduce dislocation densities of HPHT seed crystals, and using low density area as the seed crystal in second HPHT growth, IIa type crystal with very low dislocations has been developed with a dislocation density estimated to be as low as 47 cm<sup>-2</sup> [62,63]. Using a low dislocation density crystal as the seed, copying by CVD using ion implantation and the lift-off method was undertaken [59]. Starting from a  $< 100 \text{ cm}^{-2}$  mother crystal, the dislocation density of an obtained daughter wafer was  $400 \text{ cm}^{-2}$ . There was some increase in dislocation density; however, the value obtained was far below that of conventional CVD substrates. This increase in dislocation density is presumably due to the downfall of particle from the chamber as well as the surface scratch occurred during surface polishing and cleaning. In the early days of GaAs and SiC epitaxial growth, macro-defects induced by particles falling on the substrates were commonly observed. To eliminate downfalls, sophisticated deposition system well equipped with sophisticated gas flow, slow leak, and the "load-lock type" chamber is required. For the surface polishing and cleaning, techniques to reduce dislocations originating from the epitaxial layer and bulk interface are important. A recently developed fine polishing technique is nominated as one of the candidate techniques. This technique is assisted by UV light and has been shown to reduce the dislocation originating from the interface that certainly [62–66]. During this polishing process, CO and CO2 gases were detected, presumably generated from the ozone which are developed from O2 under UV exposure. Also, the plasma etching using RIE has been demonstrated to improve diamond quality and reduce dislocation density [67,68].Further techniques for surface finishing are required for the reduction of dislocation densities.

The leakage current analysis of SBD have been studied and compared with the dislocation types, however, we cannot make decisive conclusions at this stage [69,68]. Further research activities on the influence of dislocations to the device performance for both unipolar and bipolar devices are very important in order to distinguish the characteristics of the dislocations. It may change the research target of dislocation density in the future.

B doped single crystals grown by HPHT have been realized by several companies in Russia and other countries, with the largest size of 8 mm had been realized [70]. A study on the crystallinity of such crystals indicated that there are many stacking faults and dislocations [71]. The dislocation density investigated by X ray topography was high up to  $5 \times 10^4$  cm<sup>-2</sup>. The doping concentration of the commercially available substrate is not high, with a resistivity around 0.06  $\Omega$  cm. The initial B doped bulk grown by CVD from B doped HPHT seed crystal was very interesting due to the small difference in lattice constants that led to small residual strains in bulk crystal. Thus, the development of high quality B doped HPHT crystal is expected in the near future.

Growing thick bulk materials by CVD is an essential technique to obtain B doped substrates, regardless of the initial HPHT crystal. To achieve a low resistivity substrate for the power devices, there are two major technological challenges to overcome, the high doping concentration required and the subsequent soot formation during processing.

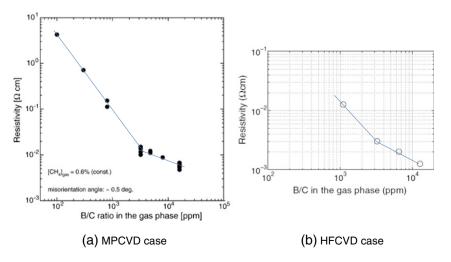

The first challenge is the high concentration doping required to obtain the final target resistivity of 0.001  $\Omega$  cm, with high crystallinity and low dislocations. High doping is usually accompanied by high strain, which needs to be reduced to produce quality devices. The highest B doping concentrations that have been achieved by microwave plasma CVD are 0.0015  $\Omega$  cm at 2.4  $\times$  10<sup>21</sup> cm<sup>-3</sup> [72] and 0.003  $\Omega$  cm at  $8 \times 10^{20}$  cm<sup>-3</sup> [73]. In the high B containing gas phase, B concentrations incorporated in the film tend to reduce with increasing B concentration, which limits reduction of the resistivity [74]. Recently, an experimental trial was carried out for high B doping using hot filament (HF) CVD and a low resistivity of 0.0012  $\Omega$  cm at 12,820 ppm in B/C gas ratio was observed [75]. The dependence of the resistivity on the dopant gas for HFCVD growth is linearity at higher concentrations, indicating possibility to realize 0.001  $\Omega$  cm. The resistivity dependence measured at RT of the B doped films produced using MPCVD and HFCVD is shown in Fig.7 with the linear relationship indicated by the trend line. High doping of B also induces lattice constant mismatch to the substrate, known as Vegard's law [76], especially in the case of using undoped diamond as the seed crystal. Thus, high quality and highly doped HPHT seed crystals are important to realize low resistivity diamond wafers.

The second challenge is the continuous growth of a thick bulk layer to overcome the technical drawback of soot formation from introducing a high concentration boron source in the chamber. Very thick CVD grown layers with high B doping have been carried out by the CNRS group using 40 W/cm<sup>3</sup> microwave plasma CVD and they succeeded in fabricating bulk diamond more than 300 µm in thickness [77–79]. The B doping concentration was 5000 ppm and the resistivity was expected

to be several tens of m  $\Omega$  cm. Long deposition times with high concentrations of B result in soot formation in the chamber, especially at the surface of the quartz window where the microwave is introduced [80, 81]. This phenomenon leads to an increase of microwave reflection at the quartz window that induces a malfunction of the growth system. In addition, time consuming cleaning of the chamber is required to remove the soot after deposition, which lowers the productivity of the machine. Instrumental improvements are required for microwave plasma CVD systems. The developments of other kinds of CVD methods including HFCVD are required for this purpose.

#### 6. Conclusion

According to the IEA energy proposal, about 25% (49% in total 50% reduction is expected for end use efficiency) of CO2 reduction should come from "end use efficiency", and energy savings with the use of low loss power device modules could be an important technology for achieving this goal. Following the success of replacing Si by SiC devices for low loss, high frequency operation at high voltage, the fast development of diamond devices is required to produce improved modules with lower losses.

The expected applications for diamond devices are high voltage, high output power devices with the possibility of high temperature operation. The vertical device structure is inevitable for these applications, and corresponding diamond wafer is necessary. For the killer defects, we propose the defect density of  $0.1 \text{ cm}^{-2}$  for the first target that corresponds to 90% yield for 10 mm  $\times$  10 mm size 100 A device chips. The final target is of course, zero killer defects. For the less critical dislocations, the targets were set as to follow those presented for SiC. For vertical structure devices, there is a trade-off between substrate resistivity and thickness. To achieve a device over 100 A, a resistivity of 0.001  $\Omega$  cm with a 300 µm thick substrate is a reasonable target. A target of a 6 inch. wafer size is desirable using the center-joint for the case of mosaic type wafers.

The market size of power device modules is expected to be 30 trillion US dollars in 2020 and is also expected to increase every year. Diamond has the considerable advantage of consisting of carbon, hence it is free from natural resource depletion problems and are truly an important material of the 21st century.

#### **Prime novelty**

25% of the global CO2 reduction should come from "end use efficiency", and diamond-based power devices will play an important role early in this century. However, the research focused on diamond materials for

Fig. 7. High B doping for (001) by MPCVD and HFCVD method [75,76] Blue lines are given in this paper.

power devices is somewhat disjointed and it is considered beneficial to define clear target in order to accelerate research. In this paper, we reviewed the current status of diamond wafer R&D and proposed clear targets with respect to the existing challenges for fabricating large size wafers with low dislocation density and low resistivity.

## Acknowledgement

This research was partially supported by the Ministry of Education, Science, Sports and Culture, Grant-in-Aid for Kakenhi 25249036.

Author would like to thank Drs. H. Umezawa, S. Ohmagari, Y. Kato, H. Yamada, N. Tsubouchi, Y. Mokunon and A. Chayahara of AIST and Prof. Ohtani of Kwansei Gakuin University for fruitful discussions.

#### References

- [1] http://www.esrl.noaa.gov/gmd/ccgg/trends/.

- [2] http://www4.unfccc.int/submissions/INDC/Submission%20Pages/submissions.aspx.

[3] http://www.worldenergyoutlook.org/.

- [4] http://www.mitsubishielectric.com/news/2013/0326-a.html.

- [5] http://www.mitsubishielectric.com/news/2015/0622-a.html.

- [6] http://www.railjournal.com/index.php/asia/new-yamanote-line-emu-to-enter-service-this-month.html.

- [7] http://newsroom.toyota.co.jp/en/detail/2656842.

- [8] B.J. Baliga, Semiconductors for high voltage, vertical channel field effect transistors, J. Appl. Physiol. 53 (1982) 1759.

- [9] A.Q. Huang, New unipolar switching power device figures of merit, IEEE Electron Device Lett. 25 (2004) 298–301.

- [10] S. Shikata, H. Umezawa, Development of diamond based power device, Synthesiology 6 (2013) 147–157.

- [11] S. Shikata, R&D development subjects of diamond wafer for power device application, New Diamond 31 (2015) 5–10 (in Japanese).

- [12] S. Yamakawa, S. Nakata, Recent Developments in SiC Devices and Its Applications, Conf. Advanced power semiconductors, JSAP, Proceedings, 2015 40 (in Japanese).

- [13] T. Funaki, M. Hirano, H. Umezawa, S. Shikata, High temperature switching operation of a power diamond Schottky barrier diode, IEICE Electronics Express 9 (2012) 1835–1841.

- [14] H. Miyake, T. Okuda, H. Niwa, T. Kimoto, J. Suda, "21-kV SiC BJTs with spacemodulated junction termination extension", IEEE Electron Device Lett. 33 (11), 1598-1600

- [15] S. Shikata, Oyo-Buturi, Recent R&D Toward Diamond Power Switching Device, 2013 299–304 (in Japanese).

- [16] T. Kimoto, J.A. Cooper, Fundamentals of Silicon Carbide Technology, IEEE & Wiley, 2014 156 Table 5.5.

- [17] M. Schreck, J. Asmussen, S. Shikata, J.-C. Arnault, N. Fujimori, Large-area high-quality single crystal diamond, MRS Bull. 39 (2014) 504–510.

- [18] C. Stehl, M. Fischer, S. Gsell, E. Berdermann, M.S. Rahman, M. Traeger, O. Kleain, M. Schreck, Appl. Phys. Lett. 103 (2013) 151905.

- [19] M. Schrek, H. Roll, B. Stritzker, Appl. Phys. Lett. 74 (1999) 650.

- [20] C. Bednarski, Z. Dai, A.P. Goding, Diam. Relat. Mater. 12 (2003) 241.

- [21] M. Fischer, S. Gsell, M. Schreck, R. Brescia, B. Stritzker, Diam. Relat. Mater. 17 (2008) 1035.

- [22] Y. Ando, T. Kamano, K. Suzuki, A. Sawabe, Jpn. J. Appl. Phys. 51 (2012) 090101.

- [23] H. Yamada, A. Chayahara, H. Umezawa, N. Tsubouchi, Y. Mokuno, S. Shikata, Fabrication and fundamental characterizations of tiled-clones of single crystal diamond with 1-inch size, Diam. Relat. Mater. 24 (2012) 29–33.

- [24] H. Yamada, A. Chayahara, Y. Mokuno, N. Tsubouchi, S. Shikata, Uniform growth and repeatable fabrication of inch size wafers of single-crystal diamond, Diam. Relat. Mater. 33 (2013) 27–31.

- [25] H. Yamada, A. Chayahara, Y. Mokuno, Y. Kato, S. Shikata, A 2-in. mosaic wafer made of a single-crystal diamond, Appl. Phys. Lett. 104 (2014) 102110.

- [26] Y. Mokuno, A. Chayahara, H. Yamada, Synthesis of large single crystal diamond plates by high rate homoepitaxial growth using microwave plasma CVD and liftoff process, Diam. Relat. Mater. 17 (2008) 415–418.

- [27] D. Nakamura, I. Gunjishima, S. Yamaguchi, T. Ito, A. Okamoto, H. Kondo, S. Onda, K. Takatori, Ultrahigh quality silicon carbide single crystals, Nature 430 (2004) 1009–1012.

- [28] K. Tsang, E. Hyman, A. Drobot, B. Lane, Pulsed plasma processing of CVD diamond, IEEE Plasma Science Proc., (1995), http://dx.doi.org/10.1109/PLASMA.1995.531675.

- [29] M. Noda, J. Indian, Formation of diamond films by pulsed discharge plasma chemical vapor deposition, Instr. Sci. 81 (2001) 627–636.

- [30] A. Gicque, K. Hassouni, G. Lombardi, X. Dutenl, A. Rousseaum, New driving parameters for diamond deposition reactors: pulsed mode versus continuous mode, Mat. Res. 6 (2003), http://dx.doi.org/10.1590/S1516-14392003000100006.

- [31] A. Tallaire, J. Achard, F. Silva, A. Gicquel, Effect of increasing the microwave density in both continuous and pulsed wave mode on the growthof monocrystalline diamond films, Phys. Status Solidi 202 (2005) 2059–2065.

- [32] O. Brinza, J. Achard, F. Silva, X. Duten, A. Michau, K. Hassouni, A. Gicquel, Improvement of energetic efficiency for homoepitaxial diamond growth in a H2/CH4 pulsed discharge, Phys. Status Solidi 204 (2007) 2847–2853.

- [33] A. Hatta, K. Kadota, Y. Mori, T. Ito, T. Sasaki, A. Hiraki, S. Okada, Pulse modulated electron cyclotron resonance plasma for chemical vapor deposition of diamond films, Appl. Phys. Lett. 66 (1995) 1602–1604.

- [34] D. King, M.K. Yaran, T. Schuelke, T.A. Grotjohn, D.K. Reinhard, J. Asmussen, Scaling the microwave plasma-assisted chemical vapor diamond deposition process to 150-200 mm substrates, Diam. Relat. Mater. 17 (2008) 520–524.

- [35] htttp://www.itu.int/en/ITU-R/Pages/default.aspx

- [36] M. Schwander, K. Partes, A review of diamond synthesis by CVD process, Diam. Relat. Mater. 20 (2011) 1287–1301.

- [37] Y. Mokuno, A. Chayahara, H. Yamada, N. Tsubouchi, Large single crystal diamond plates produced by microwave plasma CVD, Mater. Sci. Forum 615–617 (2009) 991–994.

- [38] S. Nad, Y. Gu, J. Asmussen, Growth strategies for large and high quality single crystal diamond substrates, Diam. Relat. Mater. 60 (2015) 26–34.

- [39] H. Yamada, A. Chayahara, Y. Mokuno, Y. Horino, S. Shikata, Simulation of temperature and gas flow distributions in region close to a diamond substrate with finite thickness, Diam. Relat. Mater. 15 (2006) 1738–1742.

- [40] H. Yamada, A. Chayahara, Y. Mokuno, Y. Horino, S. Shikata, Numerical analysis of a microwave plasma chemical vapor deposition reeactor for thick diamond syntheses, Diam. Relat. Mater. 15 (2006) 1389–1394.

- [41] H. Yamada, A. Chayahara, Y. Mokuno, Y. Horino, S. Shikata, Predominant physical quantity dominating macroscopic surface shape of diamond synthesized by microwave plasma CVD, Diam. Relat. Mater. 16 (2007) 576–580.

- [42] H. Yamada, A. Chayahara, Y. Mokuno, S. Shikata, Numerical microwave plasma discharge study for the growth of large single crystal diamond, Diam. Relat. Mater. 54 (2015) 9–14.

- [43] http://www.sei.co.jp/sc/history/index.html (in Japanese)

- [44] M. Fukuda, Oyo-Buturi, 62 (1993) pp. 779-785 (in Japanese)

- [45] J. Senzaki, K. Kojimma, T. Kato, A. Shimozato, K. Fukuda, Effects of Dislocations on Reliability of Thermal Oxides Grown on n-Type 4H-SiC Wafer, Mater. Sci. Forum 661 (2005) 483–485.

- [46] Q. Wahab, A. Ellison, A. Henry, E. Janzen, C. Hallin, J. DiPersio, R. Martinez, Influence of epitaxial growth and substrate-induced defects on the breakdown of 4H–SiC Schottky diodes, Appl. Phys. Lett. 76 (2000) 2725–2727.

- [47] J.P. Bergman, H. Lendernmann, P. Nilsson, U. Lindefelt, P. Skytt, Crystal defects as source of anomalous forward voltage increase of 4H SiC diodes, Mater. Sci. Forum 299 (2001) 353–356.

- [48] M. Skowronski, S. Ha, Degradation of hexagonal silicon-carbide-based bipolar devices, J. Appl. Physiol. 99 (2006) 011101.

- [49] X. Zhang, H. Tsuchida, Conversion of basal plane dislocations to threading edge dislocations in 4H-SiC epilayers by high temperature annealing, J. Appl. Physiol. 111 (2012) 123512.

- [50] H. Tsuchida, M. Ito, I. Kamata, M. Nagano, Formation of extended defects in 4H-SiC epitaxial growth and development of a fast growth technique, Phys. Status Solidi B 246 (2009) 1553–1568.

- [51] G.N. Ramachandran, X ray topographs of diamond, Proc. Indian Acad. Sci. Sect. A 19 (1944) 280–292.

- [52] A.R. Lang, Topographic methods for studying defects in diamonds, Diam. Relat. Mater. 2 (1993) 106–114.

- [53] M. Moore, Synchrotron radiation topography, Radiat. Phys. Chem. 45 (1995) 427-444.

- [54] M. Moore, Imaging diamond with X rays, J. Phys. Condens. Matter 21 (2009) 364217.

- [55] M.P. Gaukroger, P.M. Martineau, M.J. Crowder, I. Friel, S.D. Williams, D.J. Twitchen, X-ray topography studies of dislocations in single crystal CVD diamond, Diam. Relat. Mater. 17 (2008) 262–269.

- [56] H. Umezawa, Y. Kato, H. Watanabe, A.M.M. Omer, H. Yamaguchi, S. Shikata, Characterization of crystallographic defects in homoepitaxial diamond films by synchrotron X-ray topography and cathodoluminescence, Diam. Relat. Mater. 20 (2011) 523–526.

- [57] Y. Kato, H. Umezawa, H. Yamaguchi, S. Shikata, Structural analysis of dislocations in type-Ila single-crystal diamond, Diam. Relat. Mater. 29 (2012) 37–41.

- [58] Y. Kato, H. Umezawa, H. Yamaguchi, S. Shikata, X-ray Topography Used to Observe Dislocations in Epitaxially Grown Diamond Film, Jpn. J. Appl. Phys 51 (2012) 090103.

- [59] Y. Mokuno, Y. Kato, N. Tsubouchi, A. Chayahara, H. Yamada, S. Shikata, Nitrogen doped low-dislocation density free-standing single crystal diamond plate fabricated by lift-off process, Appl. Phys. Lett. 104 (2014) 252109.

- [60] N. Tsubouchi, S. Shikata, Evaluation method for grown-in dislocations in CVD single crystal diamond using plasma surface treatment, Jap. J. Appl. Phys. 53 (2014) 068010.

- [61] C. Stehl, M. Fischer, S. Gsell, E. Berdermann, M.S. Rahman, M. Traeger, O. Klein, M. Schreck, Efficiency of dislocation density reduction during heteroepitaxial growth of diamond for detector application, Appl. Phys. Lett. 103 (2013) 151905.

- [62] H. Sumiya, K. Tamasaku, Large defect-free synthetic type IIa diamond crystals synthesized via high pressure and high temperature, Jap. J. Appl. Phys. 51 (2012) 090102.

- [63] M. Kasu, R. Murakami, S. Masuya, K. Harada, H. Sumiya, Synchrotron X-ray topography of dislocations in high pressure high temperature grown single-crystal diamond with low dislocation density, Appl. Phys. Express 7 (2014) 125501.

- [64] A. Kubota, S. Fukuyama, Y. Ichimori, M. Touge, Surface smoothing of single-crystal diamond (100) substrate by polishing technique, Diam. Relat. Mater. 24 (2012) 59–62.

- [65] A. Kubota, S. Nagae, S. Motoyama and M. Touge "Two-step polishing technique for single crystal diamond (100) substrate utilizing a chemical reaction with iron plate", Diam. Relat. Mater. 60 (2015) 75–80.

- [66] Y. Kato, H. Umezawa, S. Shikata, M. Touge, Effect of an ultraflat substrate on the epitaxial growth of chemical vapor deposited diamond, Appl. Phys. Express 6 (2013) 025506.

- [67] P.N. Volpe, P. Muret, F. Omnes, J. Achard, F. Silva, Defect analysis and excitons diffusion in undoped homoepitaxial diamond films after polishing and oxygen plasma etching, Diam. Relat. Mat. 18 (2009) 1205–1210.

- [68] J. Achard, A. Tallaire, V. Mille, M. Naamoun, O. Brinza, L. William, A. Gicqul, Improvement of dislocation density in thick CVD single crystal diamond films by coupling H2/O2 plasma etching and chemo-mechanical or ICP treatment of HPHT substrates, Phys. Status Solidi 211 (2014) 2264–2267.

- [69] H. Umezawa, N. Tatsumi, Y. Kato, S. Shikata, Leakage current analysis of diamond Schottky barrier diodes by defect imaging, Diam.Relat. Mater. 40 (2013) 56–59.

- [70] Y. Kato, H. Umezawa, S. Shikata, X ray topographic study of defect in p-diamond layer of Schottky barrier diode, Diam. Relat. Mater. 57 (2015) 22–27.

- [71] V.D. Blank, M.S. Kuznetsov, S.A. Nosukhin, S.A. Terentiev, V.N. Denisov, The influence of crystallization temperature and boron concentration in growth environment on its distribution in growth sectors of type IIb diamond, Diam. Relat. Mater. 16 (2007) 800–804.

- [72] K. Srimongkon, S. Ohmagari, Y. Kato, V. Amornkitbamrung, S. Shikata, Boron inhomogeneity of single-crystal diamond substrates caused by structural defects: confocal micro-Raman mapping investigations, Diam. Relat. Mater. (2015) Available online 28 Sept.

- [73] M. Werner, R. Locher, W. Kohly, D.S. Holmes, S. Klose, H.J. Fecht, The diamond Irvin curve, Diam. Relat. Mater. 6 (1997) 308–313.

- [74] J.P. Lagrange, A. Deneuville, E. Gheeraert, Activation energy in low compensated homo-epitaxial boron-doped diamond films, Diam. Relat. Mater. 7 (1998) 1390–1393.

- [75] N. Tokuda, H. Umezawa, T. Saito, K. Yamabe, H. Okushi, S. Yamasaki, Surface roughening of diamond (001) films during homoepitaxial growth in heavy boron doping, Diam. Relat. Mater. 16 (2007) 767–770.

- [76] S. Ohmagari, K. Srimongkon, H. Yamada, H. Umezawa, N. Tsubouchi, A. Chayahara, S. Shikata, Y. Mokuno, Low resistivity p + diamond (100) films fabricated by hot-filament chemical vapor deposition, Diam. Relat. Mater. 58 (2015) 110–114.

- [77] T. Wojewoda, P. Achatz, L. Ortega, F. Omnes, C. Marcenat, E. Bourgeios, X. Blase, F. Jomard, E. Bustarret, Doping induced anisotropic lattice strain in homoepitaxial heavily boron doped diamond, Diam. Relat. Mater. 17 (2008) 1302–1306.

- [78] J. Achard, F. Silva, R. Issaoui, O. Brinza, A. Tallaire, A. Gicquel, Thick boron doped diamond single crystals for high power electronics, Diam. Relat. Mater. 20 (2011) 145–152.

- [79] R. Issaoui, J. Achard, F. Silva, A. Tallaire, A. Tardieu, A. Gicquel, M.A. Pinault, F. Jomard, Growth of thick heavily boron-doped diamond single crystals: effect of microwave power density, Appl. Phys. Lett. 97 (2010) 182101.

- [80] J. Achard, R. Issaoui, A. Tallaire, F. Silva, J. Barjon, F. Jomard, A. Gicquel, Freestanding CVD boron doped diamond single crystals: A substrate for vertical power electronics devices, Physical Status Solidi A. 209 (2012) 1651–1658.

- [81] S.N. Demlow, R. Rechenberg, T. Grotjohn, The effect of substrate temperature and growth rate on the doping efficiency of single crystal boron doped diamond, Diam. Relat. Mater. 49 (2014) 19–24.