# A Framework for Solving VLSI Graph Layout Problems\*

### SANDEEP N. BHATT AND FRANK THOMSON LEIGHTON

Laboratory for Computer Science and Department of Mathematics,

Massachusetts Institute of Technology,

Cambridge, Massachusetts 02139

Received September 3, 1982; revised February 9, 1983

A new divide-and-conquer framework for VLSI graph layout is introduced. Universally close upper and lower bounds are obtained for important cost functions such as layout area and propagation delay. The framework is also effectively used to design regular and configurable layouts, to assemble large networks of processors using restructurable chips, and to configure networks around faulty processors. It is also shown how good graph partitioning heuristics may be used to develop a provably good layout strategy.

#### 1. Introduction

The tremendous engineering advances made in very large scale integration (VLSI) fabrication technology have stimulated considerable theoretical interest in VLSI circuit layout problems. Most of this effort has centered on minimizing the layout area of a circuit on a chip. This is due, in part, to the fact that layouts which consume large amounts of chip area are more expensive to fabricate, less reliable and harder to test than layouts which consume smaller amounts of chip area.

Other layout-related issues that have been studied include: minimizing propagation delay (either by decreasing wire lengths or by increasing transistor sizes), minimizing the number of wire crossings in a layout, producing regular layouts for gate-arrays, designing chips that can later be configured to realize a large number of circuits, configuring networks around defective cells on a wafer, and assembling large systems of processors from copies of a single basic chip which has few external pin connections.

Most theoretical techniques devised thus far are based on the divide-and-conquer paradigm and require the use of a separator theorem to recursively partition a given circuit. Although separator-based techniques work well for some graphs, they perform very poorly for others.

In this paper we propose an alternative framework for solving VLSI graph layout problems. Like previous approaches, the new framework is based on the divide-and-

<sup>\*</sup>This research was supported by Air Force Contract AFOSR-82-0326 and DARPA Contract N00014-80-C-0622. Tom Leighton was also supported in part by a Bantrell Fellowship.

conquer paradigm. Instead of using a separator theorem to recursively partition a graph, the new framework requires the use of a bifurcator. The difference between bifurcators and separators will, of course, be explained in the paper, but the two primary advantages of bifurcators over separators may be stated here. First, unlike separators, bifurcators may be efficiently computed using either a good graph partitioning heuristic, or from a layout with small area. Second, bifurcators can be used to produce layouts that are efficient in a variety of respects, not layout area alone.

For example, using the notion of bifurcators, an area-efficient layout can be transformed into a layout which is both area-efficient and also has small propagation delay. The same result can also be achieved if, instead of an area-efficient layout, we use an efficient graph bisection heuristic. Separator theorems are inherently weaker than bifurcators for such purposes, and no other approach is known to enjoy the versatility of bifurcators.

This paper is based on, and unifies the work contained in three extended abstracts by Bhatt and Leiserson [3, 4] and Leighton [21]. Although the results are self-contained, some familiarity with recent results in VLSI layout theory would be helpful in reading this paper. A fairly comprehensive list of recent research papers is included in the references. In particular, Ullman [43] provides a good introduction to issues in VLSI layout theory.

The paper is divided into nine sections. In Section 2, we review the layout model and the separator-based approach to VLSI layout. In Section 3, we formally state eight VLSI layout problems and briefly review the progress made on each problem. The combinatorial lemmas proved in Section 4 provide the basis of the new framework described in Section 5. In Section 6, we describe how the framework can be used to efficiently solve the eight layout problems described in Section 3. Section 7 shows how a good graph bisection heuristic can be used to produce a provably good layout strategy. In Section 8, we prove that the upper bounds for area, crossing number and minimax edge length found in Section 6 are existentially optimal. The paper concludes with some remarks and open questions in Section 9.

### 2. BACKGROUND

Thompson [41, 42] provided the first formal model for VLSI circuit layout. The model is simply stated and captures the important aspects of layout problems in a realistic manner. A brief description of the model is included in Subsection 2.1. In addition, Thompson also proved some elementary upper and lower bounds on the area required to lay out an arbitrary graph, which are discussed in Subsection 2.2. More general bounds were obtained later by Leiserson [26, 27] and Valiant [45], who independently developed a divide-and-conquer layout strategy based on separator theorems. Subsection 2.3 summarizes their results and highlights a major deficiency of any general-purpose layout scheme based on separator theorems.

## 2.1. The Layout Model

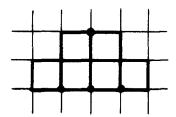

In order to cast VLSI layout problems within a mathematical framework, Thompson [41, 42] developed a formal model for VLSI graph layout. The model is based on, and is consistent with, the VLSI design rules established by Mead and Conway [31]. It is also similar to the widely used Manhattan wiring model. In the Thompson grid model, a layout for a graph is characterized as an embedding within a two-dimensional grid. A two-dimensional grid is a collection of horizontal and vertical tracks spaced apart at unit intervals. A layout for a graph G is specified by an embedding which assigns nodes of G to points in the grid where horizontal and vertical tracks intersect, together with an (incidence-preserving) assignment of the edges of G to paths in the grid. The paths of the layout are restricted to follow along grid tracks and are not allowed to overlap for any distance (although a vertical path segment may cross a horizontal path segment). In addition, the paths may not cross nodes to which they are not adjacent. For obvious reasons, we restrict our attention to graphs in which no node has degree greater than four. As an example, Fig. 1 shows a layout for the complete graph on four nodes.

Remark. The results in this paper easily extend to variants of the Thompson grid model. For example, graphs with bounded valence greater than four may be laid out by mapping each node to a region of the grid, instead of a single grid point. The results are also applicable to networks with large processors. Techniques for dealing with large processors are described more fully in the discussion of Problem 5 in Sections 3 and 6.

## 2.2. Elementary Bounds on Layout Area

Although there are a variety of important engineering considerations in choosing one layout for a graph over other possible layouts, the best understood, and perhaps the most desirable cost measure to minimize is *layout area*. The area of a layout is most naturally defined as the area of the "bounding-box" around the layout, and equals the product of the number of vertical tracks and the number of horizontal tracks that contain a node or wire segment of the graph. For example, the layout of Fig. 1 has area 15. This is not the minimum possible; there is another layout with area 9.

Fig. 1. A layout with area 15.

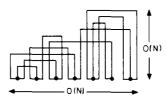

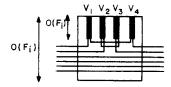

How much area does an N-node graph require? Clearly, the area cannot be less than the number N of nodes. On the other hand, by embedding nodes at equally spaced intervals along a line, and using a distinct horizontal track for each edge (as shown in Fig. 2), it is clear that the area required for an N-node graph is no greater than  $O(N^2)$ . These bounds are independent of the structure of the graph and hold for all N-node graphs. In general, however, the minimum area needed to lay out a graph depends on the graph.

Thompson [41, 42] identified bisection width as an important property of graphs that affects minimum layout area. The bisection width of a graph is the minimum number of edges which must be removed from the graph in order to disconnect it into two equal-size pieces. (Two graphs are said to be of equal size if the difference in the numbers of nodes is no more than one.) Thompson showed that, up to a constant factor, the layout area can be no less than the square of the bisection width. Therefore, if the bisection width for a graph is known, a lower bound on area can be easily computed. By showing that certain computationally powerful graphs such as the shuffle-exchange graph have large bisection width, Thompson showed that these graphs require large area. In fact, Thompson extended this observation to obtain area-time tradeoffs for computing certain functions.

Leighton [19, 20] identified crossing number as another general property that affects layout area. The crossing number of a graph is defined as the minimum number of edge crossings in any drawing of the graph in the plane. It is easy to see that the crossing number of a graph is a lower bound on layout area. Using more sophisticated arguments for special graphs, Leighton also directly obtained lower bounds on total wire length (the sum of the lengths of the wires in a layout), which of course is a lower bound on layout area. These techniques are heavily dependent on the recursive structure of the special graphs and will be generalized in Section 8.

## 2.3. Layouts Based on Separator Theorems

Leiserson [26, 27] and Valiant [45] investigated general properties that provide effective upper bounds on layout area. They independently developed a divide-and-conquer strategy for graph layout and showed, for example, that every N-node tree can be laid out in O(N) area and that every N-node planar graph can be laid out in  $O(N \log^2 N)$  area. Their technique is based on the notion of separator theorems for graphs.

Fig. 2. Every N-node graph can be laid out in  $O(N^2)$  area.

DEFINITION. A class of graphs which is closed under the subgraph relation is said to have an f(x)-separator theorem if there exist constants a and b where  $0 < a \le \frac{1}{2}$  and b > 0 such that every N-node graph in the class can be partitioned (by the removal of at most bf(N) edges of the graph) into disjoint subgraphs having a'N and (1-a')N nodes, where  $a \le a' \le 1-a$ .

Given a class of graphs for which a separator theorem is known (e.g., trees have a 1-separator theorem [28] and planar graphs have a  $\sqrt{x}$ -separator theorem [29]), it is possible to construct a layout for any N-node graph in the class by using a simple divide-and-conquer approach. For example, Leiserson [26, 27] proved the following upper bounds on layout area:

| $x^{\alpha}$ -separator theorem | layout area        |

|---------------------------------|--------------------|

| $\alpha < \frac{1}{2}$          | O(N)               |

| $\alpha = \frac{1}{2}$          | $O(N\log^2 N)$     |

| $lpha>rac{1}{2}$               | $O(N^{2\alpha})$ . |

Remark. The complete recursive decomposition of a graph must be provided as input before layouts achieving the desired area bounds can be constructed by the procedure. There is no polynomial time algorithm known that achieves the area bounds if the decomposition is not provided. This severely limits the applicability of separator-based layout strategies to classes of graphs (such as trees or planar graphs) for which actual decompositions are known.

How good are the preceding area bounds? Thompson [41, 42] and Leighton [19, 20] showed that none of the bounds can be improved. More precisely, they showed that within each class, there is a graph for which the bound is optimal. But this does not mean that the bounds are optimal for every graph within a class. In fact, while the bounds are existentially optimal, they are not universally optimal. For example, an N-node square grid requires area N, but since the minimum separator theorem for the class of square grids is  $\sqrt{x}$ , the best bound obtainable by separator-based layouts is  $O(N \log^2 N)$ , which is off by a factor of  $O(\log^2 N)$  from the optimal. Of course, since N-node graphs require area at least N, the bounds for graphs with  $x^{\alpha}$ -separator theorems, where  $\alpha < \frac{1}{2}$ , are asymptotically universally optimal.

For graphs with larger separator theorems, the discrepancy between the minimum layout area and that given in the table can be much worse. Consider, for example, the N-node graph  $S_N$  which consists of  $N/\log N$  disjoint  $\log N$ -node expander graphs. We define an m-node expander graph to be a graph for which any subset of k nodes is linked by  $\Theta(\min(k, m-k))$  edges to the m-k nodes outside the subset. The bisection width of such a graph is  $\Omega(m)$ , and hence the minimum separator theorem is  $\Theta(x)$ . The existence of trivalent graphs that satisfy this definition has been known for a long time [12, 15, 44]. In fact, almost all trivalent graphs satisfy this definition. We caution the reader that the term "expander graph" has two definitions in the literature. The other definition is sufficient for our purposes and probably more standard but requires graphs with higher node degrees. Since each  $\log N$ -node

expander graph can be trivially laid out in  $O(\log^2 N)$  area, the layout area of  $S_N$  is no greater than  $O(N \log N)$ . However, Leighton [21] showed that the minimum separator theorem for the class of graphs  $S_N$  exceeds  $\Omega(x/\log^2 x)$ , so that the area bound from the table above is  $O(N^2/\log^4 N)$ , which is much worse than the optimal bound of  $O(N \log N)$ .

Remark. The careful reader will notice (as did the referee) that any class of graphs closed under the subgraph relation and containing  $S_N$ , must also contain expander graphs. Hence, the minimum separator for the class is  $\Theta(x)$ . In order to get around such technicalities with the definition, the concept of a separator is often just applied to a single graph and the subgraphs produced by its recursive decomposition. Using the less restrictive (but more useful) definition, it is possible to show that  $S_N$  has an  $O(N/\log N)$ -separator. The log N-node expander graphs are split in the upper levels of the decomposition and never appear intact as subgraphs in the lower levels of the decomposition. Leighton proved that even using the most liberal definition, the minimum separator for  $S_N$  is at least  $\Omega(N/\log^2 N)$ . Any bound on layout area for  $S_N$  based on the minimum separator can be no less than  $\Omega(N^2/\log^4 N)$ .

Thus, while the divide-and-conquer strategy based on separator theorems gives existentially optimal bounds, the bounds can be unacceptably poor in a universal sense. It was the discovery of such large discrepancies that led to the search for an alternative framework for VLSI layout. Within the new framework presented in Section 5 we shall see how these large discrepancies are overcome.

# 3. EIGHT VLSI GRAPH LAYOUT PROBLEMS

As mentioned earlier, there are many important considerations in choosing one layout over a multitude of other possible layouts. The problems in this section are motivated by some of the basic engineering concerns. Although this list is not meant to be exhaustive, it covers most of the theoretical issues studied recently. Many of the problems are known to be *NP*-complete, so the solutions we later obtain will, of course, not be optimal. Rather, the major emphasis of this paper is the development of a general framework for handling layout problems efficiently and in a uniform manner. Within the framework, solutions to some problems are close to optimal. For other problems, good heuristics are developed and/or general bounds are obtained.

# PROBLEM 1. Given a graph G, produce an area-efficient layout for G.

As mentioned before, minimizing area is a critical concern in VLSI circuit layout. In addition to the work on area-efficient layouts described in the previous section, Dolev, Leighton, and Trickey [9] have shown that determining the minimum layout area of a forest of trees is *NP*-complete.

PROBLEM 2. Given a graph G, produce an area-efficient layout for G with minimax edge length.

Besides area, speed is another critical factor in chip performance. Signals do not propagate instantaneously across wires, and the longer the wire, the longer the propagation delay. In pipelined or systolic systems, the effect of propagation delays is even more dramatic. The maximum delay determines the clockperiod, and hence the throughput, of the system. To maximize throughput we need to minimize the maximum delay. In short, we must produce layouts so that the longest edge is as short as possible. The minimum, over all layouts, of the length of the longest edge is called the *minimax* edge length.

Paterson, Ruzzo, and Snyder [34] studied the problem of minimizing edge lengths for complete binary trees. They showed that the minimax edge length of an N-node complete binary tree is  $\Theta(\sqrt{N}/\log N)$ . Adopting a different strategy based on separator theorems, Bhatt and Leiserson [3] subsequently extended the upper bound portion of the result to arbitrary trees, and to all graphs with small (i.e.,  $x^{\alpha}$ ,  $\alpha < \frac{1}{2}$ ) separator theorems. Bhatt and Cosmadakis [2] showed that computing the minimax edge length of a tree is NP-complete.

PROBLEM 3. Given a graph, produce an area-efficient layout in which each wire has bounded delay in the capacitive model.

Although it is certainly true that propagation delay across a wire depends on the length of the wire, there has been little consensus on how fast propagation delay grows as a function of wire length. Thompson [41, 42] assumes propagation delay to be constant, independent of wire length. This might seem unreasonable given the ultimate speed-of-light limitation which indicates that the delay increases linearly with length. The speed-of-light limitation, however, greatly exaggerates the importance of wire delay in determining the speed of circuits. Mead and Conway [31] take into account some of the electrical characteristics of interconnections on MOS integrated circuits, and emphasize the role of wire *capacitance* in determining progagation delay. Recent analysis by Bilardi, Pracchi, and Preparata [5] strongly supports the belief that capacitive effects play the predominant role in determining the speed of MOS circuits.

In a capacitive model, each wire is assumed to present a purely capacitive load to the transistor that drives a signal across the wire. This load is proportional to the length of the wire plus the area of the transistor that receives the signal. The delay is proportional to this load divided by the area of the driving transistor. By increasing the size of the driving transistor, it is therefore possible to bound the propagation delay, independent of the length of the wire. A second well-known technique for reducing delay across a long wire is to "ramp" the wire with a geometrically increasing series of inverters [31]. The number of intermediate drivers, and hence the delay, is logarithmic in the length of the wire, but an attractive feature is that this process can be carried out without the need to resize the original transistors in the circuit.

Of course, increasing the size of one transistor or introducing new transistors might force some wires to be stretched to avoid the enlarged transistor area. In other words,

decreasing the delay across one wire might force an increase in delay over other wires. Leiserson [24] and Mehlhorn [32] independently posed the question of whether or not the transistors in a layout could be resized so that every wire in the layout has constant propagation delay. Ramachandran [36] investigated the problem of introducing intermediate drivers along long wires to decrease delays, but under the constraint that the topology of the layout remain unchanged. With the restriction that wires cannot be rerouted, she showed that logarithmic delay can be achieved, but at the expense of squaring the layout area in the worst case. We allow the layout topology to be changed, and obtain significantly better results.

# PROBLEM 4. Given a graph G, produce a layout for G with few wire crossings.

An undesirable feature of layouts is the presence of a large number of wire crossings. When two wires cross, they must be on different layers. For faster operation, and less power dissipation, it is advantageous to maximize the total amount of wiring on a layer of low resistance, e.g., the metal layer, while minimizing the wiring on a layer of high resistance, e.g., the polysilicon layer. The net wiring on one layer may be reduced by laying wires on that layer only just before and after two wires cross. If the number of wire crossings is small, the number of contact-cuts which connect wire segments on different layers is small so that the area of the layout is not blown up by the contact cuts which occupy large area. In addition, long wires that are crossed by many other wires are susceptible to cross-talk when all the crossing wires simultaneously carry the same signal.

The crossing number of a graph is defined to be the minimum number of wire crossings in any drawing of the graph on the plane. Leighton [19, 20] proved upper and lower bounds on crossing numbers and then used the results to find bounds on layout area. Garey and Johnson [14] showed that determining the crossing number of bipartite graphs is NP-complete.

PROBLEM 5. Given a graph, produce an area-efficient regular layout for the graph.

Some design methodologies, most notably gate-arrays, require that processors be located at fixed positions on a chip. In gate-arrays the processors are placed in a grid pattern with uniform spacing between processors adjacent along every row and column. Such layouts are said to be regular. An important advantage of this design restriction is its flexibility: even if the size of every processor is increased, the wiring between processors remains unaffected and the total area remains proportional to the sum of the wire area (as computed with unit-size processors) and the processor area. This is because only the  $\sqrt{N}$  rows and columns containing the N unit-size processors need to be expanded to accomodate the non-unit-size processors. In non-regular layouts, every row and column might have to be expanded since there might be a node in every row and in every column. Increasing the linear dimension of the processors by a factor of s could result in an  $\Theta(s^2)$  increase in layout area.

Previous divide-and-conquer layout strategies do not produce regular layouts. Hence, they are not useful in laying out circuits with non-unit-size processors. A good strategy for producing regular layouts would solve the nagging problem of how to cope with variable-size processors.

PROBLEM 6. Design area-efficient chips that can be configured to realize a large number of graphs.

Because it is expensive to make one chip, but cheap to make many copies, manufacturers of custom chips have been encouraged to make configurable designs such as gate-arrays, ROMs and PLAs. In such designs, the entire chip is prefabricated except for one layer. The customer then specifies a configuration for the chip, and the final layer of metalization connects up the circuitry in that particular way. Hence, most of the design and fabrication costs can be factored over many custom chips. Similarly, the fast emerging laser-restructuring technology [35] provides another economical way to customize chips after fabrication is complete. Laser restructuring allows connections between wires to be made or broken after the chip has been fabricated. In either case, it is desirable to design layouts that can be configured from one of a few basic patterns.

PROBLEM 7. On a wafer which has arbitrarily distributed defective cells, realize a given graph on the good cells.

In any fabrication process, it is expected that some of the processing cells will be defective. In a two-dimensional array of cells on a wafer in which defective cells are arbitrarily distributed, it may still be possible to use the wafer by configuring wires around the defective cells. This may, for example, be performed by laser restructuring techniques [35]. Given this ability to isolate defective cells, it is important to consider how a graph may be realized on the remaining good cells. This problem has received considerable attention recently [17, 22, 38]. The problem is similar to the general graph layout problem in the Thompson model but with the important restriction that nodes of the circuit can only be mapped to a restricted set of nodes in the grid.

PROBLEM 8. Given a graph G, assemble G using the minimum number of copies of a single chip having few external pin connections.

A number of very large networks have been proposed in recent years for implementing priority queues [25], for searching [1], for direct execution of applicative programming languages [30], and for recognizing regular expressions [11]. Some of these networks are too large to fit on a single chip. For example, the tree-structured network of [30] is envisioned to contain as many as one million processing elements. Clearly, such networks must be partitioned over many interconnected chips, so that each chip realizes a small portion of the network.

The technology for packaging chips severely limits the number of external pin

connections on a chip. While chips with over a million components are forseeable in the near future, no one predicts a chip with over two hundred external pin connections. This poses a pressing problem in assembling large networks of processors.

Even if a network could be partitioned so that each portion has only a few external connections, it would be economically infeasible to design each chip individually. For instance, it would be prohibitively expensive to design one thousand different chips, each containing a thousand processing elements, to assemble a network of one million processors. For this reason, it is necessary to assemble large systems using copies of a few configurable or restructurable chips. One solution to the problem of assembling large tree structures using copies of a single, area-efficient, restructurable chip with few external pin connection was given by Bhatt and Leiserson [4].

Within the new framework, efficient solutions are provided for each of these problems. In fact, a single layout simultaneously solves many of these problems efficiently. The framework provides a two-step strategy for solving these problems. First, the graph to be laid out is embedded within a very special network called the tree of meshes. For the tree of meshes it is possible to solve all these problems efficiently. In the second step therefore, a good layout for the tree of meshes also solves these problems for the embedded graph.

#### 4. Combinatorial Lemmas

This section contains three combinatorial lemmas which provide the foundation for the framework presented in the next section.

LEMMA 1. Consider any two-ended string of n colored pearls of k different colors, and let  $n_i$  be the number of pearls which are color i for  $1 \le i \le k$ . For any integer  $r \ge 2$ , the pearls can be partitioned into two sets by cutting the string in no more than  $9r^k$  places such that the total number of pearls in each set is  $\lfloor n/2 \rfloor$  or  $\lfloor n/2 \rfloor$ , the number of pearls of color 1 in each set is  $\lfloor n_1/2 \rfloor$  or  $\lceil n_1/2 \rceil$ , and such that the number of pearls of color i > 1 in each set lies between  $\lceil (\frac{1}{2} - (1/2r)) n_i \rceil$  and  $\lceil (\frac{1}{2} + (1/2r)) n_i \rceil$ .

**Proof.** Let i be a number between 1 and k and let T(i) denote the number of cuts necessary to divide the set of all pearls into two sets that satisfy the constraints of the theorem for colors 1, 2,..., i. Other than requiring that the total number of pearls be split in half by the cuts, we have made no constraints on the distribution of pearls with colors greater than i. We wish to find a good bound on T(i) in the worst case, i.e., over all choices of n,  $k \ge i$ , and all possible colorings. In what follows, we will show that T(1) = 2 and that

$$T(i) \leq rT(i-1) + 4r + 7$$

for i > 1. As a consequence, we can solve the recurrence to conclude that  $T(i) \le 9r^i - 15$  for  $r \ge 2$ . Thus for i = k, at most  $9r^k$  cuts are required, as claimed.

For i=1, it is easy to show that two cuts are sufficient. Consider a "window" of size  $\lfloor n/2 \rfloor$  positioned at the left end of the string. Without loss of generality, assume that the window covers less than  $\lfloor n_1/2 \rfloor$  of the pearls colored 1. Move the window to the right, one pearl at a time until the window covers  $\lfloor n_1/2 \rfloor$  pearls of color 1. Since the right half of the string contains more than one-half of all pearls of color 1, there must, by continuity, exist a placement when the window covers exactly one-half of all pearls of color 1. By cutting the string at the endpoints of the window, the portion of the string under the window will contain half of the total number of pearls and half of the pearls colored 1. Hence T(1) = 2, as claimed.

For a given i > 1, break the string into r segments  $S_j$ ,  $1 \le j \le r$  (making r - 1 cuts) so that each segment contains at least  $\lfloor n_i/r \rfloor$  pearls of color i. Next split each  $S_j$  into two subsets  $S_{j0}$  and  $S_{j1}$  (making a total of rT(i-1) cuts) so that each split satisfies the theorem locally for colors 1, 2, ..., i-1.

Without loss of generality, assume that  $S_{j0}$  contains no fewer pearls of color i than  $S_{j1}$ . At this stage, we divide the set C of all pearls into two subsets  $C_1$  and  $C_2$  as follows. Initially, let  $C_1 = \bigcup S_{j0}$ . If  $C_1$  contains more than  $\lfloor (\frac{1}{2} + (1/2r)) \, n_i \rfloor$  pearls of color i, remove  $S_{10}$  from  $C_1$  and add  $S_{11}$ . Repeat this procedure, successively switching  $S_{20}$  with  $S_{21}$ ,  $S_{30}$  with  $S_{31}$ , and so on until the first time  $C_1$  has at most  $\lfloor (\frac{1}{2} + (1/2r)) \, n_i \rfloor$  pearls of color i. Such a stage must occur since the number of pearls of color i in  $C_1$  will eventually fall below  $\lfloor n_i/2 \rfloor$  if  $C_1$  and  $C_2$  are completely interchanged. The number of pearls of color i in  $C_1$  after the final switch cannot be less than  $\lfloor (\frac{1}{2} - (1/2r)) \, n_i \rfloor - 2$  since every  $S_j$  contains no more than  $\lfloor n_i/r \rfloor$  pearls of color i. If the number of pearls of color i in  $C_1$  is  $\lfloor (\frac{1}{2} - (1/2r)) \, n_i \rfloor - 1$  or  $\lfloor (\frac{1}{2} - (1/2r)) \, n_i \rfloor - 2$ , then move either one or two pearls of color i from  $C_2$  to  $C_1$ , making no more than four cuts.

We also have to ensure that the total set of pearls and the pearls of the first i-1 colors are divided as required. The pearls with colors between 2 and i-1 are divided correctly because they were divided correctly at the recursive step. The counts of pearls of color 1 in  $C_1$  and  $C_2$  may differ in size by r, however. To balance the number of pearls with color 1 in each set, we need only remove up to  $\lfloor r/2 \rfloor$  pearls colored 1 from the excess set (making at most r cuts) and put them in the deficient set. To balance the difference in the overall sizes of the sets (which now might be as large as 2r+4), we need only extract up to r+2 pearls from the larger set (making no more than 2r+4 cuts) and put them in the smaller set. Of course, these pearls must be chosen carefully so that each set retains the required minimum number of pearls of each color. Since pearls are extracted only from the larger set, it is clear that this requirement may be easily satisfied. The total number of cuts made by the procedure is rT(i-1)+4r+7, as claimed.

Using an elegant topological argument, Goldberg and West [16] recently proved that k cuts suffice to divide the pearls of each color exactly in half. In contrast to Lemma 1, this is a dramatic reduction in the number of cuts. We state their result in Lemma 2, although we cannot include the proof here. We will use the stronger result in the paper since it facilitates the proofs and results in far smaller constants. It is

very important to note, however, that all of our layout results may be proved with the weaker Lemma 1. (In fact, we have done so using r = 3, but will not go through the details in this paper.) Since the Goldberg-West result has not yet appeared, we have included Lemma 1 both for completeness and so that our results will not depend on as-yet unpublished work. Both results are implementable in polynomial time when the number of colors is fixed, as is the case throughout this paper.

LEMMA 2. Consider any two-ended string of n pearls,  $n_i$  of which are colored i,  $1 \le i \le k$ . By cutting the string in k places it is possible to divide the pearls into two sets so that each set has a total of  $\lfloor n/2 \rfloor$  or  $\lceil n/2 \rceil$  pearls, and  $\lfloor n_i/2 \rfloor$  or  $\lceil n_i/2 \rceil$  pearls of color i for all i,  $1 \le i \le k$ .

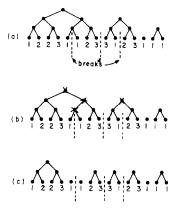

The following lemma recasts Lemma 2 in terms of complete binary trees. This form is particularly useful since the recursive decomposition of a graph may be viewed as a tree. In the following we define the *height* of a tree to be the length of the longest path from the root to a leaf. The *height* of a forest is defined to be the maximum height of a tree in the forest. Finally, the *level* of a node in the forest is defined to be the height of the forest minus the length of the longest path from the node to a leaf. (Note that the top level is level zero.)

LEMMA 3. Consider a forest of complete binary trees whose n leaves are colored arbitrarily with k colors. Let  $n_i$  be the number of leaves colored i for  $1 \le i \le k$ . By removing no more than k nodes (as well as all incident edges) from each internal level of the forest, it is possible to produce a new forest of complete binary trees, some subset of which contains  $\lfloor n/2 \rfloor$  or  $\lceil n/2 \rceil$  leaves, and  $\lfloor n_i/2 \rfloor$  or  $\lceil n_i/2 \rceil$  nodes of color i for each i,  $1 \le i \le k$ .

*Proof.* Draw the trees in the canonical manner and place them side-by-side, in any order, so that the leaves of all trees are placed along a line. By applying Lemma 2 to the induced left-to-right ordering on the leaves of the forest, it is possible to break the ordering in no more than k places such that the union of the leaves contained in every other segment contains the desired total number of leaves and the desired number of leaves of each color.

For each break, remove the nodes (and incident edges) which are simultaneously ancestors of the leaf immediately to the left of the break and the leaf immediately to the right of the break. It is easily seen that at most one node is removed from each internal level of the forest for each break. Therefore, no more than k total nodes are removed from each internal level. In addition, the removal of the common ancestors of the leaves neighboring a break divides the associated tree into two or more complete binary trees, at least one on each side of the break. Thus the removal of all such nodes produces a forest of complete binary trees, subsets of which correspond precisely to the sets of leaves between pairs of adjacent break points. Thus the union of the subsets of trees corresponding to every other segment of leaves contains the desired number of leaves of each color.

Fig. 3. An illustration of the procedure described in Lemma 3.

Figure 3 illustrates the proof of Lemma 3 with a simple example. Initially, the forest consists of four complete binary trees with seven leaves colored 1, four colored 2, and four colored 3. Figure 3a shows a leveled drawing of the forest along with three breaks (denoted by dashed vertical lines) in the line of leaves. The union of leaves in the first and third intervals contains three leaves colored 1, two of color 2, and two of color 3. In Fig. 3b the internal nodes to be removed are marked X. Figure 3c shows the new forest produced by the removal of the marked internal nodes.

### 5. THE NEW FRAMEWORK

In this section, we describe the new framework for solving VLSI graph layout problems. We start by defining the notions of decomposition trees and bifurcators for graphs. Using the combinatorial lemmas from Section 4, we devise procedures for balancing decomposition trees and bifurcators. In Subsection 5.3, balanced decomposition trees are used to embed graphs within the tree of meshes. Subsection 5.4 provides efficient layouts for the tree of meshes. Taken together, the embedding of a graph in the tree of meshes and the layout for the tree of meshes induce a layout for the original graph.

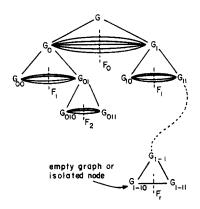

# 5.1. Decomposition Trees and Bifurcators

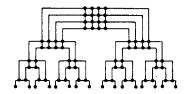

The recursive decomposition of a graph into smaller and smaller subgraphs may be viewed as a decomposition tree. In particular, we say that a graph G has an  $(F_0, F_1, ..., F_r)$ -decomposition tree if G can be decomposed into two subgraphs  $G_0$  and  $G_1$  by removing no more than  $F_0$  edges from G, and, in turn, both  $G_0$  and  $G_1$  can be decomposed into smaller subgraphs by removing no more than  $F_1$  edges from each,

and so on until each subgraph is either empty or an isolated node. Figure 4 illustrates this recursive decomposition.

As one might expect, the decomposition of a graph by separator theorems may be viewed as a decomposition tree. It follows by definition that if a class of graphs has an f(x)-separator theorem, then there are constants  $\alpha$  and  $\beta$  such that each graph in the class has a decomposition tree of the form  $(\beta f(N), \beta f(\alpha N), \beta f(\alpha^2 N),..., \beta f(1))$ . The converse is not necessarily true. Subgraphs generated at each step of a decomposition by a separator theorem are constrained to be proportional in size, whereas decomposition trees need not satisfy this constraint. Of course, if the decomposition tree has precisely log N levels, then subgraphs at each level must be equal in size.

We shall be particularly interested in a special class of decomposition trees, namely *bifurcators*, that is distinct from the class of separators.

DEFINITION. An N-node graph has an  $\alpha$ -bifurcator of size F (more simply, an  $(F, \alpha)$ -bifurcator) if it has an  $(F, F/\alpha, F/\alpha^2, ..., 1)$ -decomposition tree.

Of particular interest is the class of  $\sqrt{2}$ -bifurcators. By the definition, we know that an N-node graph has a  $\sqrt{2}$ -bifurcator of size F if and only if it has an  $(F, F/\sqrt{2}, F/2,..., 1)$ -decomposition tree. The depth of this tree is no greater than  $2 \log F$ . In order to completely decompose an N-node graph into individual nodes, the height of any decomposition tree cannot be less than the  $\log N$ . Thus, F must always be at least  $\sqrt{N}$ . On the other hand, F is always less than 2N since every N-node graph with maximum node degree four has at most 2N edges.

If a class of graphs has an  $x^{\alpha}$ -separator theorem, where  $\alpha \leqslant \frac{1}{2}$ , and the corresponding decomposition is *balanced* in that every graph is always decomposed into equal-size subgraphs, then it is straightforward to show that every N-node graph in the class has a  $\sqrt{2}$ -bifurcator of size  $O(\sqrt{N})$ . Similarly, if a class of graphs has a balanced separator theorem of size  $x^{\alpha}$  with  $\alpha > \frac{1}{2}$ , then every N-node graph in the class has a  $\sqrt{2}$ -bifurcator of size  $O(N^{\alpha})$ .

Fig. 4. An  $(F_0, F_1,..., F_r)$ -decomposition tree.

The converse is not true even if we consider only bifurcators whose corresponding decomposition trees are balanced so that every graph is decomposed into equal-size subgraphs. For example, the N-node graph  $S_N$  defined in Subsection 2.3 has a balanced  $\sqrt{2}$ -bifurcator of size  $O(\sqrt{N\log N})$  but the smallest separator for this class of graphs is  $\Omega(x/\log^2 x)$ .

When translated into bounds on layout area, this seemingly minor difference between bifurcators and separators is greatly magnified. Graphs with small layout area always have small  $\sqrt{2}$ -bifurcators, but do not always have small separators. This is formalized in Lemma 4. Later on we will prove the converse: graphs with small  $\sqrt{2}$ -bifurcators always have small layout area.

LEMMA 4. If a graph G can be laid out in area A, then G has a  $(\sqrt{A}, \sqrt{2})$ -bifurcator.

*Proof.* Consider a vertical cut of length  $\sqrt{A}$  through the center of the layout. Next, cut each of the sublayouts horizontally through the center. Continuing this sequence of alternating vertical and horizontal cuts, it is easy to see that at the *i*th step no more than  $\sqrt{A}/2^{i/2}$  edges are cut from each subgraph. This sequence of cuts yields a  $(\sqrt{A}, \sqrt{2})$ -bifurcator for G.

## 5.1.1. Special Cases

Many graphs have decomposition trees in which the number of cuts decreases very slowly as we go lower down the tree. In such cases, the number of cuts at higher levels of the tree may be very small. On the other hand, in decomposition trees corresponding to bifurcators, the number of cuts permitted decreases smoothly as we go down the tree. It is conceivable then, that the bifurcator permits far more cuts at higher levels than are necessary. For example, N-node binary trees have decomposition trees of height  $O(\log N)$  in which no more than 1 cut is required at every level. Since the minimum bifurcator is at least  $\sqrt{N}$ , the decomposition tree corresponding to the bifurcator allows far more cuts at the top levels than needed.

Similarly, some graphs have decomposition trees in which many cuts are required at the top levels, but this number decreases very quickly as we go down the decomposition tree. In such cases, the minimum bifurcator is large so that decomposition trees corresponding to the bifurcator do not underestimate the number of cuts required at the top level. However, they do greatly overestimate the number of cuts at lower levels.

It is useful to separate such extreme cases from a general discussion. Of course, general upper bounds are valid for graphs with extreme decompositions, but they may overestimate the true bound. A particularly important reason for separating these classes is that many computationally useful graphs such as binary trees fall into the first category while cube-connected-cycles and multidimensional meshes fall into the second category.

An N-node graph is defined to have a type  $A\sqrt{2}$ -bifurcator if it has an  $(O(\sqrt{N}), \sqrt{2})$ -bifurcator such that no more than  $O((N/2^i)^\alpha)$  cuts,  $\alpha < \frac{1}{2}$ , are required for each

partition at the *i*th level of the associated decomposition tree. Observe that at the higher levels of the tree,  $i \le \log N$ , the number of cuts is far less than the  $O(\sqrt{N}/2^{i/2})$  cuts allowed by the usual bifurcator.

Similarly, an N-node graph is defined to have a type  $B\sqrt{2}$ -bifurcator if it has an  $(O(N^{\alpha}), \sqrt{2})$ -bifurcator,  $\alpha > \frac{1}{2}$ , such that only  $O((N/2^{i})^{\alpha})$  edges are cut in any partition at the *i*th level. Observe that for the lower levels of the tree,  $i \gg 1$ , this quantity is far smaller than the  $O(N^{\alpha}/2^{i/2})$  cuts allowed by the usual bifurcator.

For simplicity, we will prove results only for general  $\sqrt{2}$ -bifurcators in this paper. However, whenever there is a significant difference, results for the special cases are stated separately. The proofs for these special cases are easily worked out, and closely follow the proofs for the general cases. We leave such details to the interested reader.

## 5.2. Balanced Decomposition Trees

Of particular importance to the layout results reported in this paper are decomposition trees where at each step of the decomposition, the two subgraphs are nearly equal in size. This section considers such balanced decompositions and gives an effective procedure for transforming an arbitrary decomposition tree into one that is balanced.

Formally, a decomposition tree for a graph G is balanced if each subgraph  $G_w$  in the tree is the father of two subgraphs  $G_{w0}$  and  $G_{w1}$  such that the number of nodes in the subgraphs differ by at most 1. In addition, we say that a decomposition tree is fully balanced if it is balanced, and if for every subgraph  $G_w$  in the tree, the set of edges connecting  $G - G_w$  to  $G_w$  is divided into two subsets of nearly equal size by the partition of  $G_w$  into  $G_{w0}$  and  $G_{w1}$ . (Here we allow the number of edge connections in the two subgraphs to differ by a small constant, say 5. For the purposes of simplicity, however, we shall often ignore such small differences and assume that the nodes and connections are split evenly between the two subgraphs.)

Somewhat surprisingly, any decomposition tree may be transformed into a fully balanced one at little or no cost. We prove this in Theorem 5 which generalizes earlier results in [4, 19-21].

THEOREM 5. Let G be any N-node graph with an  $(F_0, F_1,..., F_r)$ -decomposition tree T. Then G has a fully balanced  $(F'_0, F'_1,..., F'_{\log N})$ -decomposition tree, such that for  $0 \le i \le \log N$ ,

$$F_i' = 6 \sum_{s=i}^r F_s.$$

*Proof.* Let  $\Gamma$  be a forest of complete binary trees consisting initially of the decomposition tree T. Color the leaves of T with two colors according to whether or not the subgraph of G associated with the leaf is empty. Apply Lemma 3 (k=2) to  $\Gamma$ , removing the indicated nodes and edges of T. Each node of T corresponds naturally

to a set of edges of G, namely the edges whose removal splits the associated subgraph in two. Removing a node of T corresponds to removing this cutset of edges from G. Since no more than 2 nodes are removed from each level of  $\Gamma$ , the number of edges removed from G in applying Lemma 3 does not exceed  $2\sum_{s=0}^{r} F_s$ , which is less than  $F'_0$ .

Further note that G is divided into two disjoint subgraphs of nearly equal size by the removal of these edges. Each subgraph, in turn, corresponds in a natural way to a subforest of complete binary trees in  $\Gamma$ . Consider one such subgraph  $G_0$  and color the leaves of the associated forest of complete binary trees  $\Gamma_0$  using six colors as follows:

If the leaf corresponds to an empty subgraph, color the leaf with color 1. Otherwise, if the single node corresponding to the leaf is incident to exactly j edges of G removed earlier,  $0 \le j \le 4$ , then color the leaf with color j + 2.

By applying Lemma 3 (k=6) to  $\Gamma_0$ , it is clear that  $G_0$  can be decomposed into two disjoint subgraphs  $G_{00}$  and  $G_{01}$  of nearly equal size such that the number of edges from  $G-G_0$  to  $G_{00}$  is nearly equal to the number of edges from  $G-G_0$  to  $G_{01}$ . Since at most 6 nodes were removed from each level of  $\Gamma_0$  and since  $\Gamma_0$  does not contain the root of T, we can conclude that no more than  $6\sum_{s=1}^r F_s = F_1'$  edges were removed from  $G_0$ .

By applying the above argument recursively, the desired fully balanced decomposition tree is easily obtained. The only point to observe is that with each application of Lemma 3, the biggest tree in any forest corresponding to a subgraph decreases in height by at least one. This is because the total number of leaves in each forest is cut in half at each step. A total of  $\log N + 1$  levels are sufficient for the decomposition since the number of nodes in each subgraph is also split in half at each step.

THEOREM 6. Every graph with a  $\sqrt{2}$ -bifurcator of size F has a fully balanced  $\sqrt{2}$ -bifurcator of size  $6(2+\sqrt{2})$  F.

*Proof.* The result follows immediately from Theorem 5, with the observation that  $\sum_{i>0} 2^{-i/2} \le 2 + \sqrt{2}$ .

*Remark.* The procedure described in Theorems 5 and 6 can be implemented in polynomial time.

### 5.3. Embeddings in the Tree of Meshes

Leighton [19, 20] introduced the tree of meshes as an example of a planar graph that cannot be laid out in linear area. He also showed that every N-node planar graph can be embedded in an  $O(N \log N)$ -node tree of meshes. In this section, we define the tree of meshes and describe a general strategy for embedding a graph in the tree of meshes.

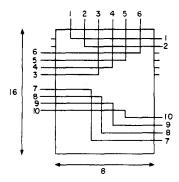

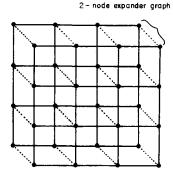

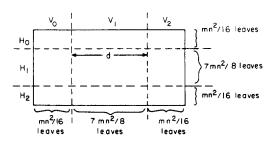

The tree of meshes is formed by replacing each node of a complete binary tree with a mesh and each edge by several edges which connect meshes at consecutive levels. More precisely, the root of the complete binary tree is replaced by an  $n \times n$  mesh (it is assumed that n is a power of 2), the nodes at the second level are replaced by  $n \times n/2$  meshes, those at the third level by  $n/2 \times n/2$  meshes, and so on until the leaves of the tree are replaced by  $1 \times 1$  meshes. As shown in Fig. 5, each edge of the tree is replaced with edges connecting nodes on one side of the higher level mesh to the top row of the mesh at the lower level. The resulting graph is called the  $n \times n$  tree of meshes  $T_n$ . It is not difficult to see that  $T_n$  has  $N = 2n^2 \log n + n^2$  nodes.

For some applications, we need to consider only the top levels of the tree of meshes. We call the subgraph consisting of levels 0, 1,..., p of  $T_n$  a truncated tree of meshes  $T_{n,p}$ . Note that  $p \le 2 \log N$ .

THEOREM 7. There is a constant c such that every N-node graph G with an  $(F,\sqrt{2})$ -bifurcator can be embedded in  $T_{cF,2\log N/F}$ . Moreover, the embedding is regular in the sense that  $F^2/N$  nodes of G are embedded in a regular fashion in each of the  $N^2/F^2$  bottom-level meshes of  $T_{cF,2\log N/F}$ .

*Proof.* We first use Theorem 6 to construct a fully-balanced  $\sqrt{2}$ -bifurcator of size  $6(2+\sqrt{2})$  F for G. We then use the internal meshes of  $T_{cF,2\log N/F}$  to route the edges that were removed in the upper  $2\log N/F$  levels of the fully balanced decomposition tree for G. The subgraphs in the  $(2\log N/F)$  th level of the decomposition tree (each of which has  $|F^2/N|$  or  $|F^2/N|$  nodes) are then embedded in the meshes on the bottom level of the truncated tree of meshes.

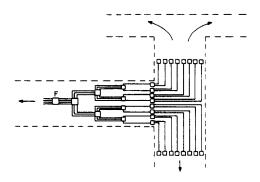

The internal meshes are used in the same manner that complete crossbar switches are used in switching networks. For example, in Fig. 6, six wires enter the mesh through the top, of which four exit from the left side and two from the right. In addition, four wires enter and exit from the sides. No matter what the ordering of the wires, they can easily be routed through the mesh as shown. In general, if the number of wires routed through a mesh does not exceed any side-length of the mesh, a routing may always be found. Similarly, a graph with M nodes can always be embedded in a  $4M \times 4M$  mesh with nodes placed in a regular fashion.

Consider only the top  $2 \log(N/F) + 1$  levels of a fully balanced decomposition tree for G. Each of the subgraphs at level  $2 \log N/F$  of the decomposition tree has  $N(1/2)^{2 \log N/F} = F^2/N$  nodes. (For simplicity we shall assume that  $F^2/N$  is an integer.) Furthermore, if  $E_i$  is the maximum number of edges between  $G - G_i$  and  $G_i$ , where

Fig. 5. The  $4 \times 4$  tree of meshes  $T_4$ .

Fig. 6. Using a mesh in the tree of meshes as a crossbar switch.

$G_i$  is a subgraph in the decomposition tree at level i, then it is easy to see that  $E_0 = 0$  and by Theorem 6, that

$$E_i \leqslant \frac{1}{2} E_{i-1} + 6(2 + \sqrt{2}) \frac{F}{2^{(i-1)/2}}$$

for  $1 \le i \le 2 \log N/F$ . Solving the above recurrence, we obtain

$$E_i \le 6(2+\sqrt{2})\frac{F}{2^{(i-1)/2}}\sum_{s>0}(\sqrt{2}/2)^s,$$

and thus

$$E_i \leqslant 6(2+\sqrt{2})^2 \frac{F}{2^{(l-1)/2}}.$$

We now embed G in  $T_{cF,2\log N/F}$ . First, embed each of the  $(2\log N/F)$ -level subgraps of the decomposition tree in the bottom level meshes. This can be done if the side of each mesh at level  $2\log N/F$  exceeds  $4F^2/N$ . This is true provided

$$cF/\sqrt{2}^{2\log N/F} \geqslant 4F^2/N$$

.

For  $c \ge 4$ , this inequality is easily satisfied.

Next embed the additional edges through the upper-level meshes in the natural way. No more than  $2E_{i+1}$  edges pass through any *i*th level mesh. Thus the routing can be performed if the smaller side of the *i*th level meshes exceeds  $2E_{i+1}$ . In other words, we must have

$$cF/2^{\lceil i/2 \rceil} \geqslant 12(2+\sqrt{2})^2 F/2^{i/2}.$$

A simple calculation shows that the inequality is satisfied for sufficiently large c.  $\blacksquare$  Remark. Throughout the paper, we express bounds using the term  $\log N/F$ . For

all practical purposes, F is much smaller than N and this term is greater than one. Should the value of F be larger, however, we shall still define  $\log N/F$  to be at least one. Similar interpretations are assumed for  $\log \log N/F$  and for  $\log \log \log N/F$ . The conventions avoid the annoying (and trivial) cases when F is very large without complicating the analysis further.

In the preceding embedding, all the nodes of G were mapped to meshes at the bottom level of the truncated tree of meshes. Thus, edges between nodes in different meshes might have to be routed through as many as  $4 \log N/F$  meshes. Such long edges are undesirable for a variety of reasons. It is natural to ask whether an embedding can be found in which each edge can be routed through fewer intermediate meshes. This is answered in the following theorem.

THEOREM 8. There are constants c and k such that every N-node graph G with an  $(F, \sqrt{2})$ -bifurcator can be embedded in  $T_{cF,2\log N/F}$  and such that no edge is routed through more than k intermediate meshes.

**Proof.** We adopt a slight variant of the strategy used in Theorems 5-7. The balancing and embedding are done simultaneously and in the same manner as before, except at levels 0, k, 2k, 3k,..., (where k is a constant specified later). At these levels, we embed the nodes that are incident to edges previously cut, and we cut the previously uncut edges incident to these nodes. Of course, this could triple the number of cut edges every k levels but if k is sufficiently large, this happens infrequently and is not harmful. At all other levels the procedure is the same as before, using 6 colors and Lemma 3 to partition the decomposition tree. The process terminates after  $2 \log N/F$  levels.

As before, the embedding is accomplished by using meshes as switching boxes for routing edges. We must ensure that the number of edges routed through any mesh does not exceed the side lengths of the mesh. The calculation is the same as before except that the number of cut edges is tripled at every kth level. Thus the recurrence for  $E_i$  is

$$E_i \leqslant \frac{1}{2} (3^{1/k}) E_{i-1} + 6(2 + \sqrt{2}) \frac{F}{2^{(i-1)/2}}.$$

Here, we have (without loss of generality) increased number of cut edges by a factor of 3 initially and by a factor of  $3^{1/k}$  at each level instead of increasing the number of cuts by a factor of 3 at every kth level. Solving the recurrence, we find

$$E_i \le 18(2+\sqrt{2})\frac{F}{2^{(i-1)/2}}\sum_{s>0}\left(\frac{\sqrt{2}}{2}3^{1/k}\right)^s.$$

For  $k \ge 4$ , the sum converges to a constant. The remaining analysis is the same as in Theorems 5-7, except that the constants are larger.

Remark. It is worthwhile to point out here that Theorems 7 and 8 could also

have been proved using Lemma 1 as instead of Lemma 2. The nodes of G would still be balanced in the decomposition tree but the cut edges could only be split  $\frac{1}{3} - \frac{2}{3}$  at each decomposition. While this increases the value of the sum, it still converges to a constant. (This is because for sufficiently large k,  $(2\sqrt{2}/3) 3^{1/k} < 1$ .) Hence, k and c would be larger but the statements of the theorems remain the same.

# 5.4. Layouts for the Tree of Meshes

Thus far we have considered only the problem of embedding graphs in the tree of meshes. How do we lay out the tree of meshes efficiently? Clearly, any layout for the tree of meshes also gives a layout for every graph that can be embedded within the tree of meshes. In this section we develop two different layouts for the tree of meshes.

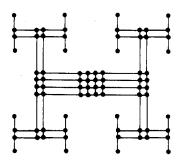

The first layout is a straightforward modification of the "H-tree" layout for complete binary trees [31]. The modified layout is obtained by expanding each node of the complete binary tree into a mesh of the appropriate size. Figure 7 shows this layout. It is easy to see that if S(F) denotes the sides of the layout for  $T_F$ , then S(1) = 1, and

$$S(F) \leq 2S(F/2) + O(F)$$

which gives  $S(F) = O(F \log F)$ . This means that the area of the layout for  $T_F$  is bounded by  $O(F^2 \log^2 F)$ . As shown in [19, 20], this bound is optimal.

For truncated trees of meshes, such as considered in Theorems 7 and 8, a similar result holds.

THEOREM 9. The truncated tree of meshes  $T_{F,2\log N/F}$  has a layout of area  $O(F^2\log^2 N/F)$ .

*Proof.* The obvious restriction of the *H*-layout to the top levels suffices.

Although the mesh edges in the layout shown in Fig. 7 have length 1, the edges between meshes can be quite long (nearly half the side of the layout). By pulling in meshes closer towards the top level, we can reduce the length of the longest edge

FIG. 7. The H-tree layout of the tree of meshes.

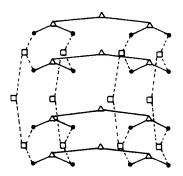

considerably. This technique was introduced in [3] to produce minimax edge length layouts for trees, and generalized to graphs with known separators. In the following theorem we lay out the truncated tree of meshes with shorter edges, using a simplified version of the argument introduced in [3]. This layout will later be used to find layouts with short edges for graphs embedded within the truncated tree of meshes.

THEOREM 10. The truncated tree of meshes  $T_{F,2\log N/F}$  can be laid out in area  $O(F^2\log^2 N/F)$  so that mesh edges have length 1 and edges between meshes have length at most  $O(F\log N/F/\log\log N/F)$ .

*Proof.* Consider the *H*-tree layout of a complete binary tree of height 2 log log log N/F, and having (log log N/F)<sup>2</sup> leaves. Expand each linear dimension by a factor  $\beta = \Theta(F \log N/F/\log \log N/F)$ , so that each edge of the *H*-tree layout becomes a channel of width  $\beta$  and each node becomes a  $\beta \times \beta$  square. The resulting area is  $\Theta((\beta \log \log N/F)^2) = \Theta(F^2 \log^2 N/F)$ .

Since the channels are much wider than the side of any mesh, we can stack many meshes within one channel. In particular, as seen in Fig. 8, we embed the top level mesh at the center of the layout with the second-level meshes on either side. In the first stage of the layout, the meshes in the top levels are placed together in a breadth-first manner. Meshes at successive levels are equally spaced at distance  $\Theta(F \log N/F/\log \log N/F)$  apart.

We need to ensure that every channel is wide enough to accomodate the meshes stacked within it. To this end, let us suppose that all meshes embedded in the first stage are stacked together in the same channel. Of course, this is a gross overestimate, but suffices for our argument. Since the path from the root to a leaf in the original ( $\log \log N/F$ )-leaf H-layout originally has wire length  $\Theta(\log \log N/F)$ , a total of  $c \log \log N/F$  levels of  $T_{F,2\log N/F}$  are embedded in the first stage. The value of the constant c depends on the values of the other constants in the  $\Theta$ -terms and can be made as small as necessary.

The total number of meshes embedded in the first stage is no more than

Fig. 8. An improved layout for the tree of meshes.

$2^{1+c\log\log N/F}$ . Each mesh has side length no greater than F, so to stack all these meshes within one channel of side  $\beta$ , it suffices to have

$$F2^{1+c\log\log N/F} \leqslant O\left(\frac{F\log N/F}{\log\log N/F}\right),$$

which is easily satisfied when  $c \le \frac{1}{2}$ . Hence every channel has sufficient width to stack all the *i*th level meshes across the channel for any  $i \le c \log \log N/F$ .

In the second stage, we embed the remaining meshes in the  $\beta \times \beta$  squares. A total of  $(\log N/F)^c/(\log\log N/F)^2$  copies of an  $O(\log N/F)$ -level  $(F/(\log N/F)^{c/2}) \times (F/(\log N/F)^{c/2})$  truncated tree of meshes must be embedded in each of the  $(\log\log N/F)^2 \beta \times \beta$  regions to accomplish this. Using the layout described in Theorem 9 for each copy, the total area required in each region is

$$\Theta\left(\frac{(\log N/F)^c}{(\log\log N/F)^2}\frac{F^2}{(\log N/F)^c}\log^2 N/F\right) = \Theta\left(\frac{F^2\log^2 N/F}{(\log\log N/F)^2}\right).$$

This is precisely the amount of area available in each  $\beta \times \beta$  region. Hence the embedding is possible.

It remains to verify that the edges between meshes have length  $O(F \log N/F/\log\log N/F)$ . This is easily done since meshes in adjacent levels were spaced distance  $O(F \log N/F/\log\log N/F)$  apart in the first stage, and since meshes in adjacent levels were located in the same  $\beta \times \beta$  region in the second stage.

### 6. Solutions to the Eight Problems

Using the framework described in Section 5, we are now ready to present general solutions to the eight problems posed in Section 3. Not surprisingly, the methods of the previous section apply almost directly to these diverse problems. This supports the belief that the divide-and-conquer strategy based on bifurcators is an efficient paradigm for VLSI graph layout, and that the tree of meshes is a versatile network for solving layout problems. The solutions presented in this section are evaluated by comparing them with lower bounds. Some of the lower bounds are new; to maintain continuity, their proofs are deferred to Section 8.

The first two problems, concerning area-efficient layouts and minimax edge length layouts, were already addressed directly in the previous section.

PROBLEM 1. Given a graph G, produce an area-efficient layout for G.

By Theorem 7 in Subsection 5.3, every N-node graph with an  $(F, \sqrt{2})$ -bifurcator can be embedded in the truncated tree of meshes  $T_{O(F),2\log N/F}$ . Next, by Theorem 9 in Subsection 5.4, the truncated tree of meshes can be laid out in  $O(F^2 \log^2 N/F)$  area. Therefore, every N-node graph with an  $(F, \sqrt{2})$ -bifurcator can be laid out in  $O(F^2 \log^2 N/F)$  area.

As a simple consequence of Lemma 4, every N-node graph whose smallest  $\sqrt{2}$ -bifurcator is F, must occupy at least  $F^2$  area. For otherwise the graph would have a  $\sqrt{2}$ -bifurcator strictly smaller than F. Therefore, for every graph the upper bound is at most a factor of  $O(\log^2 N/F)$  worse than optimal. As we shall see in Section 8, the upper bound is also existentially optimal in that there are N-node graphs with  $(F,\sqrt{2})$ -bifurcators for all N and F with minimum area  $\Omega(F^2 \log^2 N/F)$ .

Special Cases. Graphs with  $(F, \sqrt{2})$ -bifurcators with either of the special forms described in Subsection 5.1.1 have  $O(F^2)$ -area layouts.

PROBLEM 2. Given a graph G, produce an area-efficient layout for G with minimax edge length.

From Theorem 8 we know that every N-node graph with an  $(F, \sqrt{2})$ -bifurcator can be embedded in the truncated tree of meshes  $T_{O(F),2\log N/F}$  so that no edge passes through more than a constant number of intermediate meshes. Furthermore, the layout for the truncated tree of meshes given in Theorem 10 guarantees that every edge between meshes has length bounded by  $O(F\log N/F/\log\log N/F)$ , and that every edge within a mesh has length one. Combining these two theorems, we see that every N-node graph with an  $(F, \sqrt{2})$ -bifurcator has an  $O(F^2 \log^2 N/F)$ -area layout with maximum edge length bounded by  $O(F\log N/F/\log\log N/F)$ .

This bound is also existentially optimal, as will be seen in Section 8. However, the bounds are not guaranteed to be universally close. The only general lower bound on minimax edge length for N-node graphs whose minimum  $\sqrt{2}$ -bifurcator is F, is  $\Omega(F^2/N)$ . (This lower bound is also existentially optimal, as will be shown in Section 8.)

The problem of minimizing maximum edge length appears to quite difficult. Although the preceding bounds are disappointingly weak, they are the best known. Bhatt and Cosmadakis [2] show that even determining if a tree can be laid out with minimax edge length one, is *NP*-complete.

Special Cases. The minimax edge length bounds for graphs with special  $(F, \sqrt{2})$ -bifurcators are  $O(\sqrt{N}/\log N)$  for type  $A\sqrt{2}$ -bifurcators and O(F) for type  $B\sqrt{2}$ -bifurcators.

PROBLEM 3. Given a graph, produce an area-efficient layout in which each wire has bounded delay in the capacitive model.

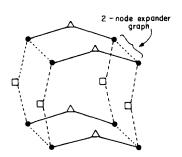

First we formalize some details of the model. As usual, a graph describes a connection of processors, with an edge corresponding to a bidirectional link between two processors. Each node is a processing element which contains one driver and one receiver for each incident edge. Every transistor in a processing element has the same size. Thus, in our layouts, a node may be represented by a long and skinny box of constant thickness, with length equal to the area of an internal transistor. Since each node has bounded degree, a box will be just big enough to contain all the transistors in the corresponding processor. Note that different nodes in the layout will have

different lengths, but the same thickness. We assume that the grid spacing is adjusted so that nodes and edges have unit thickness and may be laid along grid lines. Although wires are allowed to cross, we will not allow nodes to cross; this corresponds to transistors not overlapping. Similarly, wires and nodes may not cross. The propagation delay over a wire of length l driven by a transistor of area D with capacitive load A is proportional to (l+A)/D. The capacitive load presented to a transistor equals the sum of incident wire lengths and areas of adjacent transistors.

THEOREM 11. Every N-node graph G with an  $(F, \sqrt{2})$ -bifurcator has a bounded-delay layout of area  $O(F^2 \log^2 N/F)$ .

*Proof.* As in Theorem 8 of Section 5.4, embed G in a tree of meshes so that adjacent nodes are mapped to meshes no more than a constant number of levels apart. Since the dimensions of meshes at successive levels, as well as the lengths of edges connecting adjacent meshes in the layout of Theorem 9, decrease at the same geometric rate, we know that the length of an edge of G is proportional to the side lengths of the meshes that contain the corresponding nodes. Assign to each node an area that is proportional to the side lengths of the mesh in which it is embedded. Thus, the capacitive load on any node, which equals the sum of the areas of all the incident edges and adjacent nodes, is proportional to the area of the node. In other words, every wire in the layout has bounded delay.

We need to ensure that each enlarged node can be accommodated in its assigned mesh without blowing up the area of the layout by more than a constant factor. This can be done by increasing the dimensions of each mesh by a constant factor, and laying out the nodes and incident edges as shown in Fig. 9. Notice that the nodes do not overlap other nodes or wires. The area of each node remains proportional to the side lengths of the mesh containing it, and thus the delay across every wire is bounded.

Special Cases. Similarly, graphs with special  $(F, \sqrt{2})$ -bifurcators have  $O(F^2)$ -area bounded-delay layouts.

Theorem 11 means that the area bounds for bounded-delay layouts are no worse than the best known *general* area bounds described for Problem 1. However, it is not known whether or not there exists a graph for which any bounded-delay layout requires asymptotically greater area than the minimum area layout. In Corollary 12 we show that the required increase in area is not very large.

Fig. 9. Laying out expanded nodes in a mesh.

COROLLARY 12. Any layout of area A for an N-node graph can be transformed into a bounded-delay layout of area  $O(A \log^2 \sqrt{A}/N)$ .

**Proof.** By Lemma 4 of Subsection 5.1, every graph with a layout of area A has a  $(\sqrt{A}, \sqrt{2})$ -bifurcator which can be quickly found. Then by Theorem 11, we can construct a bounded-delay layout with area  $O(\mathscr{A} \log^2 \sqrt{A}/N)$ .

Remark. Unlike the previous area bounds which can be obtained only when the bifurcator for a graph is already known, Corollary 12, for transforming a layout into a bounded-delay layout, can be efficiently implemented.

PROBLEM 4. Given a graph G, produce a layout for G with few wire crossings.

The layouts for the truncated tree of meshes in Theorems 9 and 10 do not have any edge crossings. Since every N-node graph G with an  $(F, \sqrt{2})$ -bifurcator can be embedded within the truncated tree of meshes  $T_{O(F),2\log N/F}$ , this means that the number of crossings in the layout for G cannot exceed the number of nodes in  $T_{O(F),2\log N/F}$ . In other words, the number of crossings in the layout for G is bounded by  $O(F^2 \log N/F)$ .

In Section 8 we will see that this bound is existentially optimal. We will also show that for every N-node graph with a minimum  $\sqrt{2}$ -bifurcator of size F, the number of crossings plus the number of nodes is at least  $\Omega(F^2)$ . Thus, if F is asymptotically greater than  $\sqrt{N}$ , the number of crossings in the layout for G is no worse than a factor  $O(\log N/F)$  times optimal.

Special Cases. Graphs with special  $(F, \sqrt{2})$ -bifurcators can be laid out with  $O(F^2)$  crossings.

PROBLEM 5. Given a graph, produce an area-efficient regular layout for the graph.

In Theorem 7, we showed how to embed any N-node graph G with an  $(F, \sqrt{2})$ -bifurcator in  $T_{cF,2\log N/F}$  for some constant c. Moreover, the nodes of G were divided evenly among the  $N^2/F^2$  bottom-level meshes of  $T_{cF,2\log N/F}$  and in each bottom-level mesh, the nodes of G were embedded in a regular fashion. Thus to produce an  $O(F^2\log^2 N/F)$ -area layout for G that is regular, we need only produce a layout for  $T_{cF,2\log N/F}$  for which the nodes at the  $(2\log N/F)$ th level are located in a regular fashion. In fact, we can do much better, as we show in the following theorem.

THEOREM 13. The truncated tree of meshes  $T_{O(F),2\log N/F}$  can be laid out in  $O(F^2\log^2 N/F)$  area so that, for every level i, all nodes within ith level meshes are placed in a regular fashion.

**Proof.** The first step is to construct a  $\Theta(\log N/F)$ -layer three-dimensional layout [23] of the truncated tree of meshes. Fold the connections between the root of the tree of meshes and each of its two sons so that the sons fit naturally on a second layer over the root mesh. Fold the connections to each of the meshes at the next lower level

so they fit, on the third layer, directly over the meshes on the second layer, and so forth. This generates a  $\Theta(\log N/F)$ -layer three-dimensional layout, with each layer occupying linear area. By projecting the three-dimensional layout onto the plane in the manner of Thompson [42, pp. 36-38], the result follows. (The same layout can be constructed by interleaving the meshes at each level.)

Special Cases. The  $O(F^2)$ -area layouts for graphs with special  $\sqrt{2}$ -bifurcators are also regular.

PROBLEM 6. Design area-efficient chips that can be configured to realize a large number of graphs.

In Subsection 5.3 we showed that every N-node graph with an  $(F, \sqrt{2})$ -bifurcator can be embedded in a truncated tree of meshes such that the nodes of the graph are embedded in a regular fashion in the bottom-level meshes of  $T_{cF,2\log N/F}$ . In fact, the nodes can be mapped to fixed positions within the meshes. Therefore, if we lay out the truncated tree of meshes on a chip with processors at these fixed positions, we have a configurable chip for all graphs with the corresponding bifurcator. This yields the following result. Observe that the area bounds for configurable layouts are the same as for unrestricted layouts.

THEOREM 14. Every N-node graph with an  $(F, \sqrt{2})$ -bifurcator has a configurable layout of area  $O(F^2 \log^2 N/F)$ .

*Proof.* Simply make the connections in the meshes after the rest of the chip has been fabricated. Recall that we used the meshes as crossbar' switches in Theorem 7.

Special Cases. Similarly, graphs with special bifurcators have  $O(F^2)$ -area configurable layouts.

PROBLEM 7. On a wafer which has arbitrarily distributed defective cells, realize a given graph on the good cells.

In Subsection 5.3 (Theorem 7), we showed how to embed any N-node graph G with an  $(F, \sqrt{2})$ -bifurcator in the truncated tree of meshes  $T_{O(F), 2\log N/F}$ . The embedding had the property that nodes of the graph could be mapped to fixed positions within the meshes at the bottom level. Accordingly, we fixed processors at each of these positions.

Faulty processors on a wafer therefore correspond to faulty processors in the truncated tree of meshes, the correspondence being induced via the layout for the tree of meshes. It is clearly no longer possible to realize G in the faulty tree of meshes. However it is possible to realize a smaller graph with a similar structure using only the functioning processors.

More formally, consider a class of graphs for which any N-node graph in the class has a  $\sqrt{2}$ -bifurcator of size O(f(N)) where the function f is such that  $f(x)/\sqrt{x}$  is nondecreasing for increasing x. For example,  $f(x) = \sqrt{x}$  for the class of square meshes (as well as for the class of trees or the class of planar graphs). In what follows, we will show how to embed any M-node graph from the class in any  $T_{cf(N),2\log N/f(N)}$  that has M functioning processors where  $N \geqslant M$  and c is a sufficiently large constant. In particular, we will show how to embed  $T_{f(M),2\log M/f(M)}$  in the structure. By the results in Subsection 5.3, this will be sufficient to prove the claim. Thus the layout strategy developed in Section 5 is impervious to the existence of faulty processors. This result substantially generalizes and simplifies a similar result proved by Leighton and Leiserson for embedding meshes around faults in [22].

Theorem 15. Given the preceding constraints on N, M, c, and f, a completely functioning truncated tree of meshes  $T_{f(M),2\log M/f(M)}$  with M processors can be embedded in any partially functioning truncated tree of meshes  $T_{cf(N),2\log N/f(N)}$  with N processors (M of which are functioning) so that the processors of the former are mapped onto the functioning processors of the latter.

*Proof.* Label the functioning processors in each tree of meshes from 1 to M by counting from left to right across the bottom level of each graph. (Recall that the processors are evenly distributed on the bottom level.) Map the kth processor of  $T_{f(M),2\log M/f(M)}$  onto the kth functioning processor of  $T_{cf(N),2\log N/f(N)}$ . Route the edges of the former graph through the meshes of the latter in the usual way, at the same time embedding meshes of the former in blocks within the meshes of the latter.

It remains to show that the capacity of each mesh in  $T_{cf(N),2\log N/f(N)}$  is sufficient for the embedding. Consider a mesh X on the ith level of  $T_{cf(N),2\log N/f(N)}$ . This mesh has side lengths  $cf(N)/2^{i/2}$  and at most  $N/2^i$  functioning processors below it in the bottom level of the graph. The only meshes and edges of  $T_{f(M),2\log M/f(M)}$  that are embedded in X are those that correspond to roots of the forest of complete binary trees formed by removing the corresponding interval of (at most  $N/2^{i}$ ) processors in  $T_{f(M),2\log M/f(M)}$ . These roots are identified by splitting  $T_{f(M),2\log M/f(M)}$  (as in Lemma 3) at the two endpoints of the interval. There are at most two roots at each level in the resulting forest and the sum of their side lengths (a geometrically decreasing sum) is proportional to  $f(M)/2^{j/2}$ , where j is such that  $M/2^{j} \leq N/2^{i}$ . (Remember that there are at most  $N/2^i$  processors in the leaves of the forest so that the height of the largest complete binary tree in the forest is j, where  $M/2^{j} \leq N/2^{i}$ .) Thus the sum of the side lengths of the meshes embedded in X is  $O((f(M)/2^{i/2})\sqrt{N/M})$  which, for sufficiently large c, is less than  $cf(N)/2^{i/2}$  (this is the side length of X), since  $N \ge M$  and  $f(x)/\sqrt{x}$  is a nondecreasing function. Hence X is large enough and the embedding is possible.

Special Cases. A similar argument works for graphs with special bifurcators.

PROBLEM 8. Given a graph G, assemble G using the minimum number of copies of a single chip having few external pin connections.

Suppose that we wish to assemble N-node graphs with  $(F, \sqrt{2})$ -bifurcators but that each chip contains only m nodes, where m < N. Consider a chip consisting of a truncated tree of meshes  $T_{O(\sqrt{m}F/\sqrt{N}),\,O(\log\sqrt{mN}/F)}$ , with the m processors divided equally among the bottom-level meshes, and external pin connections to the top of the top level mesh. Two copies of this chip may be wired together to form a truncated tree of meshes with 2m processors. Thus, graphs with twice as many processors can be assembled with two chips than can be assembled on a single chip. More generally, we have the following result.