#### Available online at www.sciencedirect.com

## **ScienceDirect**

Procedia

Computer Science

Procedia Computer Science 93 (2016) 132 – 138

6th International Conference On Advances In Computing & Communications, ICACC 2016, 6-8 September 2016, Cochin, India

# Analysis of electrical parameters of Ge/Si heterojunction GeOI FinFETs

Rajashree Das<sup>a</sup>, Srimanta Baishya<sup>a</sup>

<sup>a</sup>Department of Electronics and Communication Engineering, National Institute of Technology Silchar, Silchar 788010, India

#### Abstract

This paper proposes for the first time three heterojunction structures of FinFET, each structurally different from the other. The first structure is a heterojunction FinFET with Germanium fin, dual gate material and dual gate dielectric, where a Silicon layer near the source end creates a heterojunction. The second structure is a modification of the first one with the Silicon layer placed near the source and drain ends. The second structure further modifies into the third with the introduction of a gate-drain underlap. The third heterojunction FinFET having a gate-drain underlap on the drain shows the improved I<sub>ON</sub>/I<sub>OFF</sub> and low leakage current compared to the other two structures. Therefore, a further detailed analysis is done for the third geometry, that is, dual gate material dual dielectric gate-drain underlap heterojunction FinFET. Analysis of the transfer characteristics are carried out for this structure for variations in gate-drain underlap length, concentration of both Silicon layers on source and drain ends, and fin width.

© 2016 The Authors. Published by Elsevier B.V. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

Peer-review under responsibility of the Organizing Committee of ICACC 2016

Keywords: heterojunction (HJ); dual gate material; dual gate dielectric; FinFET; I<sub>ON</sub>/I<sub>OFF</sub>; subthreshold swing.

#### 1. Introduction

The short channel effects have become a major issue of concern in MOSFETs, and hence, the semiconductor industry in on the lookout for alternatives. FinFET is one such device which has come into focus as a possible substitution of MOSFET due to its reduced SCEs and corner effects. Tremendous scaling down of dimensions causes vertical gate high direct tunneling current<sup>1</sup>. FinFET is superior to MOSFET because of its wrapping around nature of

<sup>\*</sup> Corresponding author. Tel.: +91-9854143810. E-mail address:rajashree18das@gmail.com

the gate around the channel. Since the gate wraps around from all the sides, it can better control the channel and as result shows a less effect on short channel effects and leakage current<sup>2</sup>.

Moreover, FinFETs exhibit reduced DIBL, less Subthreshold Swing (SS), high on current (I<sub>ON</sub>), and less off current (I<sub>OFF</sub>). All these characteristics depend on the dimensions and shape of the fin. There are various structures of FinFET which have been designed to show better functionality, some of them being DG FinFET<sup>3,4,5</sup>, TG FinFET<sup>6,7</sup>, triangular shaped FinFET<sup>8</sup>, dual material gate FinFET<sup>9</sup>, tapered tri-gate FinFET<sup>10</sup>, trapezoidal triple gate FinFET<sup>11</sup>, GAA FinFET<sup>12,13</sup>, omega shaped gate nanowire finFET<sup>13</sup>, and halo implant MuGFET<sup>14</sup>.

In this work, we propose a set of three heterojunction structures. The three structures are compared and the outcomes are reported. In these structures, gate dielectric stack, gate material stack and gate underlap on drain side are used.

Sections 2 and 3 describe the device architecture of the three different structures with simulation setup. Section 4 mentions the comparative results and discussion of the three structures. Section 5 concludes the work.

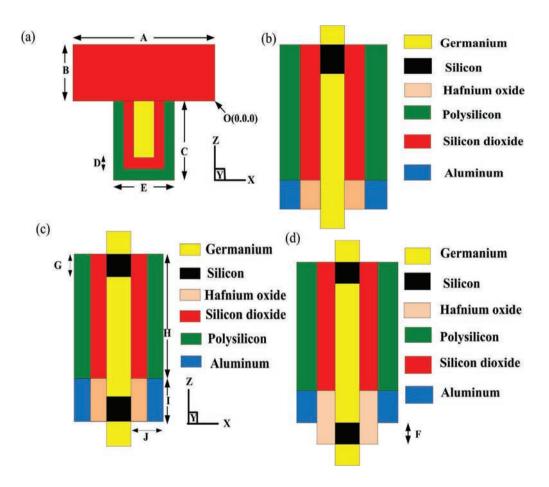

Fig. 1 Cross section of the devices of (a) front view of the three structures, (b) top view of Structure I, (c) top view of Structure II, (d) top view of Structure III

#### 2. Device architectures

The cross sections of three different structures of FinFET are shown in Fig. 1. All the three structures have Ge-Si-Ge body. The first structure, Structure I, is the dual gate material dual dielectric heterojunction FinFET, where Si layer is placed in the channel near the source region. The second structure, Structure II, is similar to Structure I except that Si layer in the channel is placed both near the source and drain regions. A gate underlap on drain with Si layer present on both source and drain side is reported in Structure III. The dimensions of all the three structures are listed in Table I. For all the three structures a low-k dielectric material SiO<sub>2</sub> (k=3.9) with 30nm and high-k dielectric material (k=22) with 10 nm are placed sideways. Polysilicon ( $\Phi_m$ =4.25 eV) and Aluminum ( $\Phi_m$ =4.1 eV) are used as gate materials placed laterally having lengths of 30 nm and 10 nm respectively. But in Structure III, the length of Aluminum is 3 nm and the underlap length on drain is 7 nm. The source and drain are each having length of 5nm and the total channel length of 40 nm in all the three structures. The doping concentrations of source ( $n^+$ ) and drain ( $n^+$ ) are  $1 \times 10^{20}$  cm<sup>-3</sup>, and the channel and silicon layer are having a concentration of  $1 \times 10^{19}$  cm<sup>-3</sup>.

## 3. Simulation setup

The simulation results of three different structures have been taken out from Synopsys TCAD<sup>15</sup>. To simulate the structures, Fermi Dirac Statistics, Bandgap Narrowing Model, and Doping Dependent Mobility Model are used <sup>15</sup>.

#### 4. Results and discussions

## 4.1. Comparison of transfer characteristics of proposed heterojunction structures

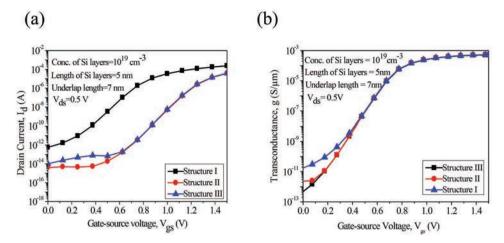

This section includes the comparative analysis of the proposed structures of FinFET. The transfer characteristics and the transconductance versus gate to source voltage of three different structures are shown in Fig. 2. Table 2 consists of various parameters extracted from the outcomes which are shown in the Fig. 2.

| OC 11 | 1 D: |         | CT.     | 4   |

|-------|------|---------|---------|-----|

| Table | )1me | ensions | of Fig. | - 1 |

|       |      |         |         |     |

| Parameters | Dimensions (nm) |  |  |

|------------|-----------------|--|--|

| A          | 60              |  |  |

| В          | 20              |  |  |

| C          | 31              |  |  |

| D          | 2               |  |  |

| E          | 22              |  |  |

| F          | 7               |  |  |

| G          | 5               |  |  |

| Н          | 30              |  |  |

| I          | 10              |  |  |

| J          | 6               |  |  |

Table 2. Comparison of on current, off current,  $I_{ON}/I_{OFF}$ ,  $V_{th}$  and SS of three different structures of Fig. 1

| Structures    | $I_{ON}(A)$           | $I_{OFF}(A)$            | $I_{\rm ON}/I_{\rm OFF}$ | $V_{th}\left(V\right)$ | SS (mV/dec) |

|---------------|-----------------------|-------------------------|--------------------------|------------------------|-------------|

| Structure I   | 2.38×10 <sup>-4</sup> | 5.76×10 <sup>-13</sup>  | 4.13×10 <sup>8</sup>     | 1.00456                | 76.36       |

| Structure II  | 2.34×10 <sup>-4</sup> | $7.242 \times 10^{-14}$ | $3.2 \times 10^9$        | 1.019                  | 96.78       |

| Structure III | 2.25×10 <sup>-4</sup> | $1.70 \times 10^{-14}$  | $1.32 \times 10^{10}$    | 1.038                  | 87.03       |

From the above mentioned Table 2, it can be understood that Structure III has higher on and off current ratio than Structures I and II; Structure III shows the highest  $I_{ON}/I_{OFF}$  due to its minimum leakage current. The introduction of a

Fig. 2 (a) Transfer characteristics of the three structures, (b) Transconductance versus gate-source voltage of three structures

high band gap Si layer at the channel-drain junction of Structure II reduces the off current by a considerable amount. The gate-drain underlap further plays a role in reducing the off current in Structure III due to reduced proximity between gate and drain. Fig. 2 shows the transfer characteristics and the transconductance versus gate-source voltage of the three structures. From the above drawn figure it can be concluded that the gate-drain underlap heterojunction structure show better performance compared to other two structures. Due to the underlap region, the gate fringing field lines emanates from the gate electrode and terminates on the drain underlap region. In this structure, a phenomenon called gate fringe induced barrier lowering (GFIBL) occurs<sup>16</sup>, due to gate-electrode thickness of gate material which lowers the barrier and as a result more electrons can flow from the source to drain through channel<sup>16</sup>, resulting in less I<sub>OFF</sub> current which can be shown from the Fig. 2 (a).

Since in this structure, a high k dielectric material (HfO<sub>2</sub>) (k=22) as well as a low work function gate material (Al) ( $\Phi_m$ =4.1eV) is used, they take part in enhancing the lowering of barrier. The high k dielectric material improves the electric field coupling between the gate electrode and the channel region including the underlap region, which intensify the  $I_{ON}^{16,\ 17}$ . The transconductance versus gate-source voltage curve is shown in the Fig. 2 (b). Transconductance (g) can be written as

$$g = \frac{\partial I_D}{\partial V_{GS}} \tag{1}$$

The transconductance to drain current ratio shows the efficiency of the device, because transconductance measures the amplification of the device and the drain current represents the power. Therefore, transconductance-to-drain current ratio is referred to as the quality factor of the device<sup>19</sup>. The nature of the transfer characteristics of Fig. 2 (a) ultimately results in similar transconductance values at gate voltage greater than 0.5 V.

## 4.2. Analysis of variation of doping and dimension parameters of Structure III

Of the three structures of FinFETs proposed in this work, Structure III exhibits the highest on-off current ratio and lowest off current. Hence, Structure III is considered for various analysis in this section.

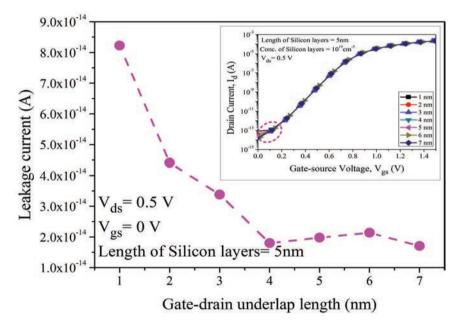

## 4.2.1. Variation of gate-drain underlap length

From Fig. 3, it is observed that the off state leakage currents decreases with increase in gate-drain underlap lengths. The increase in distance between gate and drain allows a less control of the gate over the population of carriers near the drain; as a result, the off current reduces<sup>20</sup>. So, in this work, an optimized value of gate-drain underlap length of 7 nm is considered which has low  $I_{OFF}$  and excellent  $I_{ON}/I_{OFF}$ .

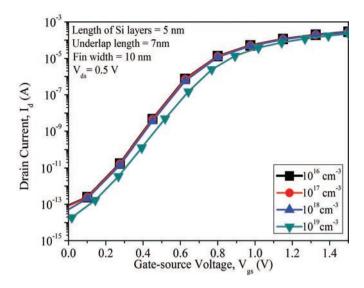

#### 4.2.2. Variation in doping concentration of silicon layer

Fig. 4 shows the transfer characteristics, where doping concentrations of the p-type Silicon layer are varied. It is noticeable from the figure that with the increase of doping concentration, the drain current reduces but  $I_{ON}/I_{OFF}$  ratio increases due to less value of  $I_{OFF}$ . When the concentration is  $10^{16}$  cm<sup>-3</sup>, the  $I_{OFF}$  is  $1.27\times10^{-13}$  A, and when the concentration is  $10^{19}$  cm<sup>-3</sup>, the value of  $I_{OFF}$  is  $9.96\times10^{-14}$  A i.e. there is a drastic change in  $I_{OFF}$ . It can be shown from the figure that the curves for  $10^{16}$  cm<sup>-3</sup>,  $10^{17}$  cm<sup>-3</sup>, and  $10^{18}$ cm<sup>-3</sup> are superimposing because the barrier between the channel and drain are similar whereas in case of  $10^{19}$ cm<sup>-3</sup> the barrier height increases at the channel-drain junction.

#### 4.2.3. Variation in fin width

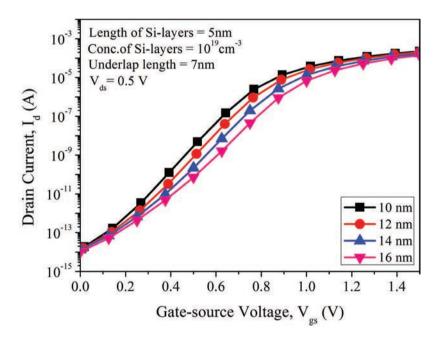

Fig. 5 shows the transfer characteristics where the drain current reduces with the increase of fin width but the  $I_{ON}/I_{OFF}$  for the entire fin widths are of the same order. As the fin width increases, control of the gate decreases<sup>21</sup>. Since the structure is double gate FinFET structure, the channel is controlled by two side wall gates. So, when the fin width is increased the control of a midpoint in the channel decreases<sup>21</sup>. Therefore, the drain current reduces with the increase of fin width.

Fig. 3. Leakage currents vs. underlap length

Fig. 4. Transfer characteristics for different doping concentration of the Silicon layers

Fig. 5. Transfer characteristics for different fin widths

#### 5. Conclusion

From the analyzed work in the paper, it can be concluded that the dual gate material dual dielectric gate-drain underlap heterojunction FinFET shows better  $I_{\text{ON}}/I_{\text{OFF}}$  greater than  $10^{10}$  compared to the other two structures. The  $I_{\text{ON}}/I_{\text{OFF}}$  ratio increases by two orders of magnitude and the leakage current decreases by one order of magnitude. Moreover, the presence of Silicon layer on both the ends also shows significant results compared to the structure of presence of Silicon layer near the source end. The values of  $V_{\text{th}}$ , and SS are proper for the dual gate material dual dielectric gate-drain underlap heterojunction FinFET structure.

## References

- G. Pei, J. Kedzierski, P. Oldiges, M. Ieong, and E. C.-C. Kan. FinFET Design Considerations Based on 3-D Simulation and Analytical Modeling. IEEE Trans Electron Devices 2002;49:1411–19.

- 2. V. Subramanian, B. Parvais, J. Borremans, A. Mercha, D. Linten, P. Wambacq, J. Loo, M. Dehan, C. Gustin, N. Collaert, S. Kubicek, R. Lander, J. Hooker, F. Cubaynes, S. Donnay, M. Jurczak, G. Groeseneken, W. Sansen, and S. Decoutere. Planar Bulk MOSFETs Versus FinFETs: An Analog / RF Perspective. *IEEE Trans Electron Devices* 2006;53:3071–79.

- D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. J. King, J. Bokor, and C. Hu. FinFET-A Self-Aligned Double-Gate MOSFET Scalable to 20 nm. IEEE Trans Electron Devices 2000;47:2320–25.

- B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C.-Y. Yang, C. Tabery, C. Ho, Q. Xiang, T.-J. King, J. Bokor, C. Hu, M.-R. Lin, and D. Kyser. FinFET Scaling to 10 nm Gate Length. IEDM 2002:251–4.

- A. Datta, A. Goel, R. T. Cakici, H. Mahmoodi, D. Lekshmanan, and K. Roy. Modeling and Circuit Synthesis for Independently Controlled Double Gate FinFET Devices. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst 2007;26:1957

–66.

- T. Rudenko, V. Kilchytska, N. Collaert, M. Jurczak, A. Nazarov, and D. Flandre. Carrier Mobility in Undoped Triple-Gate FinFET Structures and Limitations of Its Description in Terms of Top and Sidewall Channel Mobilities. *IEEE Trans Electron Devices* 2008;55: 3532–41.

- M. A. Pavanello, J. A. Martino, E. Simoen, R. Rooyackers, N. Collaert, and C. Claeys. Evaluation of Triple-Gate FinFETs with SiO<sub>2</sub>-HfO<sub>2</sub>-TiN Gate Stack Under Analog Operation. Solid-State Electron 2007;51:285-91.

- 8. B. D. Gaynor, and S. Hassoun. Fin Shape Impact on FinFET Leakage With Application to Multithreshold and Ultralow-Leakage FinFET Design. *IEEE Trans Electron Devices* 2014;61:2738–44.

- 9. Y. Hong, Y. Guo, H. Yang, J. Yao, J. Zhang, and X. Ji. A Novel Bulk-FinFET With Dual-Material Gate. 12th IEEE International Conference on Solid state and Integrated Circuit Technology 2014:10–12.

- 10. M. D. Ko, C. W. Sohn, C. K. Baek, and Y. H. Jeong. Study on a Scaling Length Model for Tapered Tri-Gate FinFET Based on 3-D Simulation and Analytical Analysis. *IEEE Trans Electron Devices* 2013;60:2721–27.

- 11. J. P. Duarte, N. Paydavosi, S. Venugopalan, A. Sachid, and C. Hu. Unified FinFET Compact Model: Modelling Trapezoidal Triple-Gate FinFETs. *International Conference on Simulation of Semiconductor Process and Devices* 2013:135–8,.

- Y. F. Lim, Y. Z. Xiong, N. Singh, R. Yang, Y. Jiang, D. S. H. Chan, W. Y. Loh, L. K. Bera, G. Q. Lo, N. Balasubramanian, and D. L. Kwong. Random Telegraph Signal Noise in Gate-All-Around Si-FinFET With Ultranarrow Body. *IEEE Electron Device Lett* 2006;27:765–68

- 13. Y. Li, H. M. Chou, and J. W. Lee. Investigation of Electrical Characteristics on Surrounding-Gate and Omega-Shaped-Gate Nanowire FinFETs. *IEEE Trans Nanotechnology* 2005;4:510–16.

- M. Nawaz, P. Haibach, and W. Molzer. Optimization of Halo Implant Using 3D TCAD for Nanoscale MuGFETs. International Conf SISPAD 2006:176–9.

- 15. Sentaurus Device User, Synopsys; (2009) 2009.

- A. B. Sachid, C. R. Manoj, D. K. Sharma, and V. R. Rao. Gate Fringe-Induced Barrier Lowering in Underlap FinFET Structures and its Optimization. IEEE Electron Device Lett; 2008;29:128–30.

- 17. V. Trivedi, J. G. Fossum, and M. M. Chowdhury. Nanoscale FinFETs With Gate-Source/Drain Underlap. *IEEE Trans Electron Devices* 2005; **52**:56–62.

- K. Majumdar, R. S. Konjady, R. T. Suryaprakash, and N. Bhat.. Underlap Optimization in Hfinfet in Presence of Interface Traps. IEEE Trans Nanotechnology 2011;10:1249–53.

- 19. N. B. Balamurugan, K. Sankaranarayanan, and M. Fathima John. 2D transconductance to drain current ratio modeling of dual material surrounding gate nanoscale SOI MOSFETs. *Journal of Semiconductor and Technology Science* 2009;9:110–6.

- A. Nandi, A. K. Saxena, and S. Dasgupta. Impact of Dual-K Spacer on Analog Performance of Underlap FinFET. Microelectron J 2012:43:883-7.

- 21. R. Das, R. Goswami, and S. Baishya. Tri-Gate Heterojunction SOI Ge-FinFETs. Superlattices Microstruct 2016;91:51-61.