https://ntrs.nasa.gov/search.jsp?R=19640019274 2020-03-24T06:16:10+00:00Z

X-544-64-138

TM X-55068

# EGO BALLOON EXPERIMENT DATA PROCESSOR

# MAY 1964

37

GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND

OTS PRICE

XEROX MICROFILM

\$

#### EGO BALLOON EXPERIMENT

.

•

#### DATA PROCESSOR

Authors and Designers:

Paul Heffner John Cole

Design Supervisor:

Harold H. Levy

Data Instrumentation Development Branch

Data Systems Division

GODDARD SPACE FLIGHT CENTER Greenbelt, Maryland May 1964

## CONTENTS

-----

| I.    | INTRODUCTION                                                       | 1  |

|-------|--------------------------------------------------------------------|----|

| II.   | SPECIFICATIONS                                                     | 4  |

| ш.    | DATA FORMAT                                                        | 6  |

| IV.   | OPERATING INSTRUCTIONS                                             | 7  |

| v.    | THEORY OF OPERATION                                                | 11 |

|       | A. General                                                         | 11 |

|       | B. Binary-to-Decimal Conversion                                    | 12 |

|       | C. Recognition of a Data Point Which Exceeds a Preselected Number  | 13 |

|       | D. Compensation for Tape Skew                                      | 14 |

| VI.   | DESCRIPTION OF LOGIC                                               | 18 |

|       | A. Control Unit                                                    | 18 |

|       | B. Registers A, B, and C                                           | 19 |

| VII.  | SIGNAL SIMULATION                                                  | 20 |

| VIII. | POWER                                                              | 21 |

| IX.   | CONVENTIONS AND SYMBOLS USED IN THE DRAWINGS<br>AND THE LITERATURE | 22 |

| X.    | MODIFICATIONS TO HEWLETT-PACKARD DIGITAL COUNTERS<br>AND PRINTER   | 25 |

| XI.   | REFERENCES                                                         | 26 |

i

# ILLUSTRATIONS

| Figure |                                                       | Page |

|--------|-------------------------------------------------------|------|

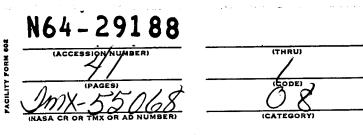

| 1      | EGO Data Processor, Overall Unit                      | 2    |

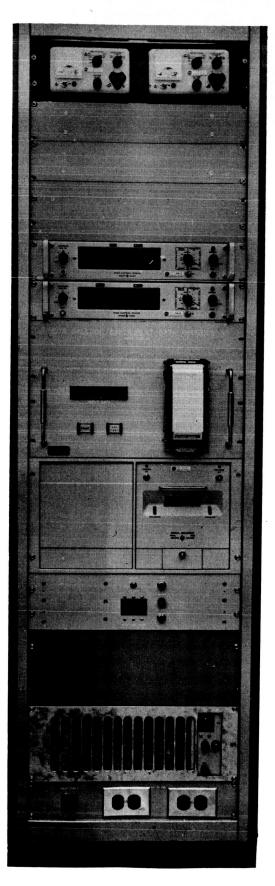

| 2      | Pull-Out View of Arithmetic Unit                      | 3    |

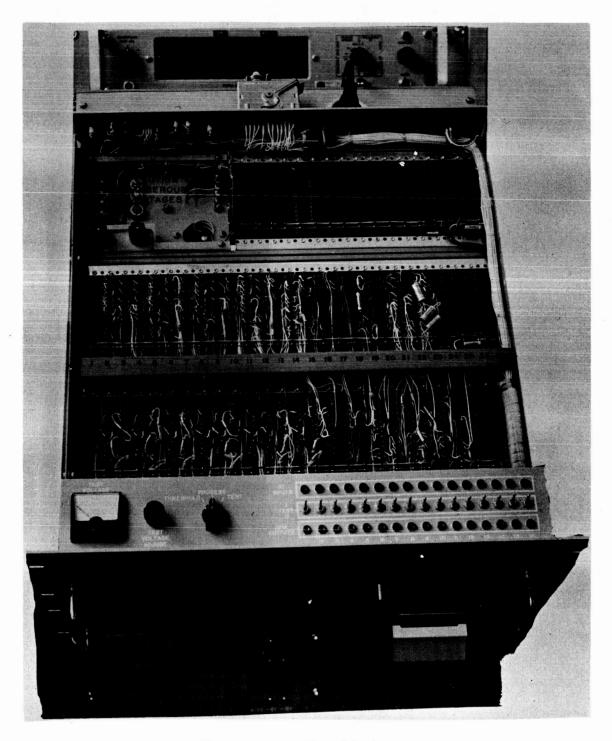

| 3      | The NAND Function                                     | 14   |

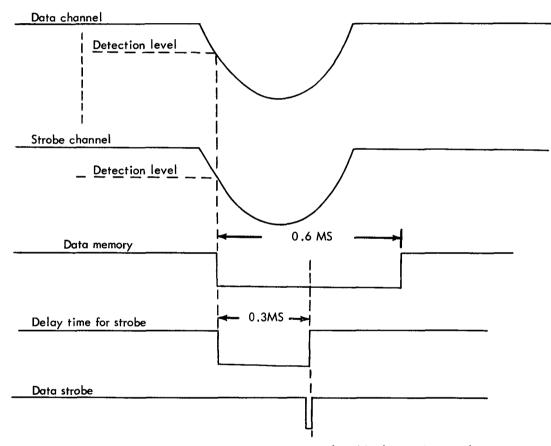

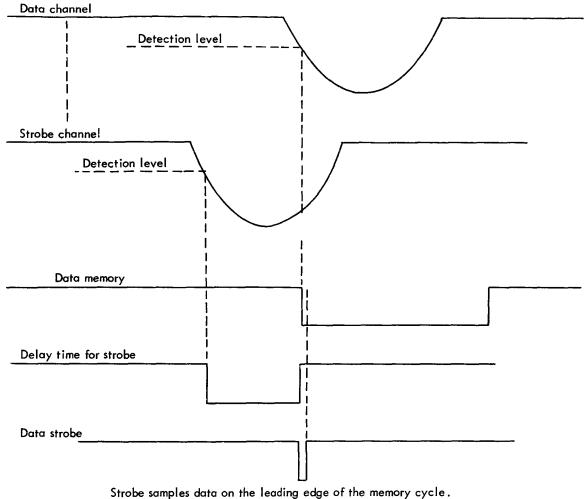

| 4      | Bit Detection With 0° Skew                            | 15   |

| 5      | Bit Detection With -108° Skew                         | 16   |

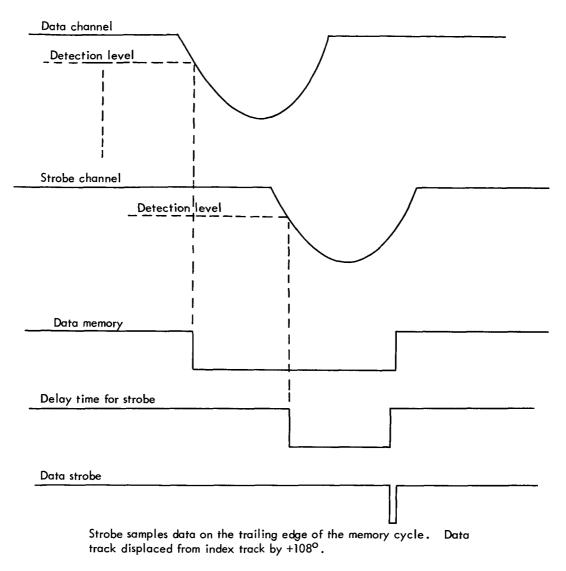

| 6      | Bit Detection with $+108^{\circ}$ Skew                | 17   |

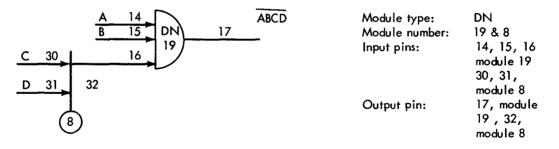

| 7      | NAND Circuit Symbol                                   | 22   |

| 8      | NAND Circuit With Extended Fan-In Symbol              | 22   |

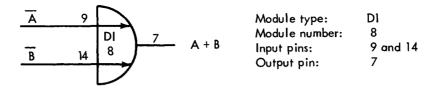

| 9      | NOR Circuit Symbol                                    | 22   |

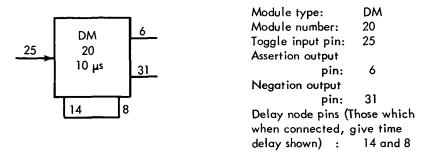

| 10     | Monostable Multivibrator Circuit Symbol               | 23   |

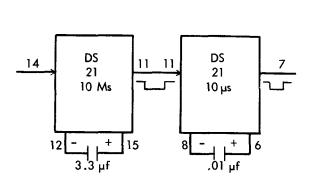

| 11     | Delayed Pulse Generator Symbol                        | 23   |

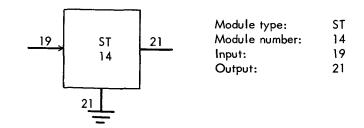

| 12     | Schmitt Trigger Symbol                                | 23   |

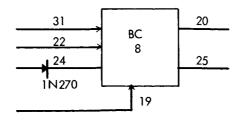

| 13     | Binary Counter Circuit Symbol                         | 24   |

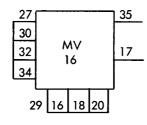

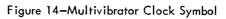

| 14     | Multivibrator Clock Symbol                            | 24   |

| 15     | Light Indication Symbol                               | 24   |

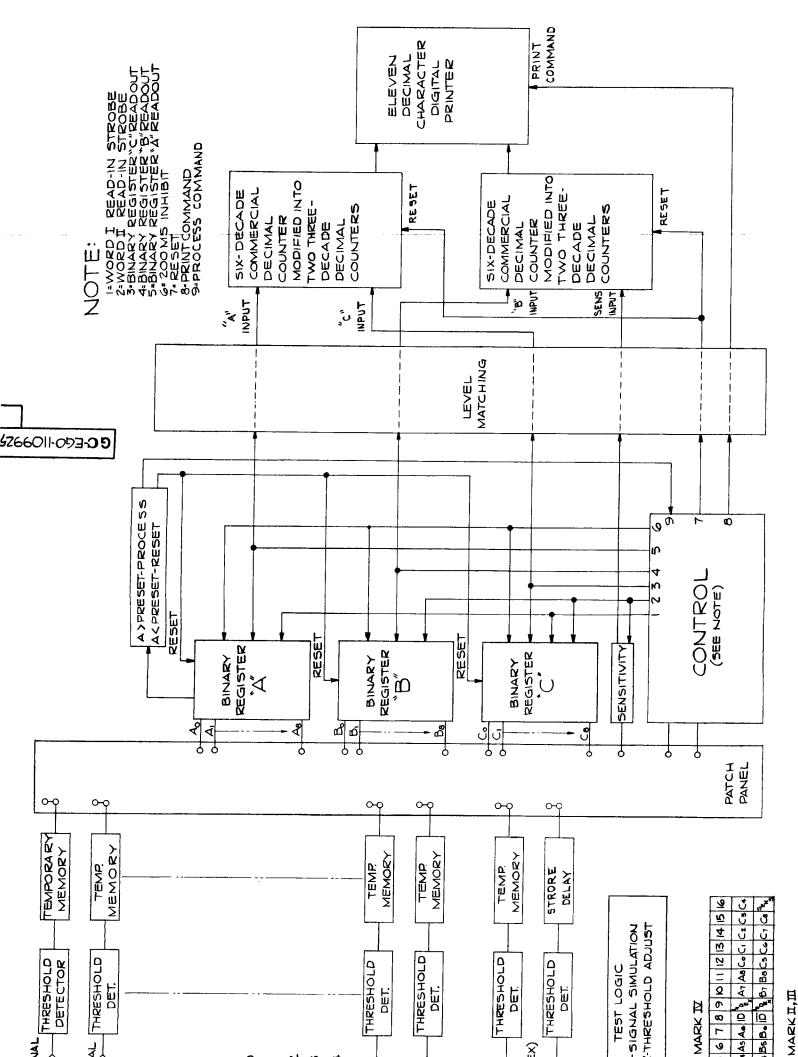

| 16     | EGO Data Processor, Block Diagram (GC-EGO-1109925)    | 27   |

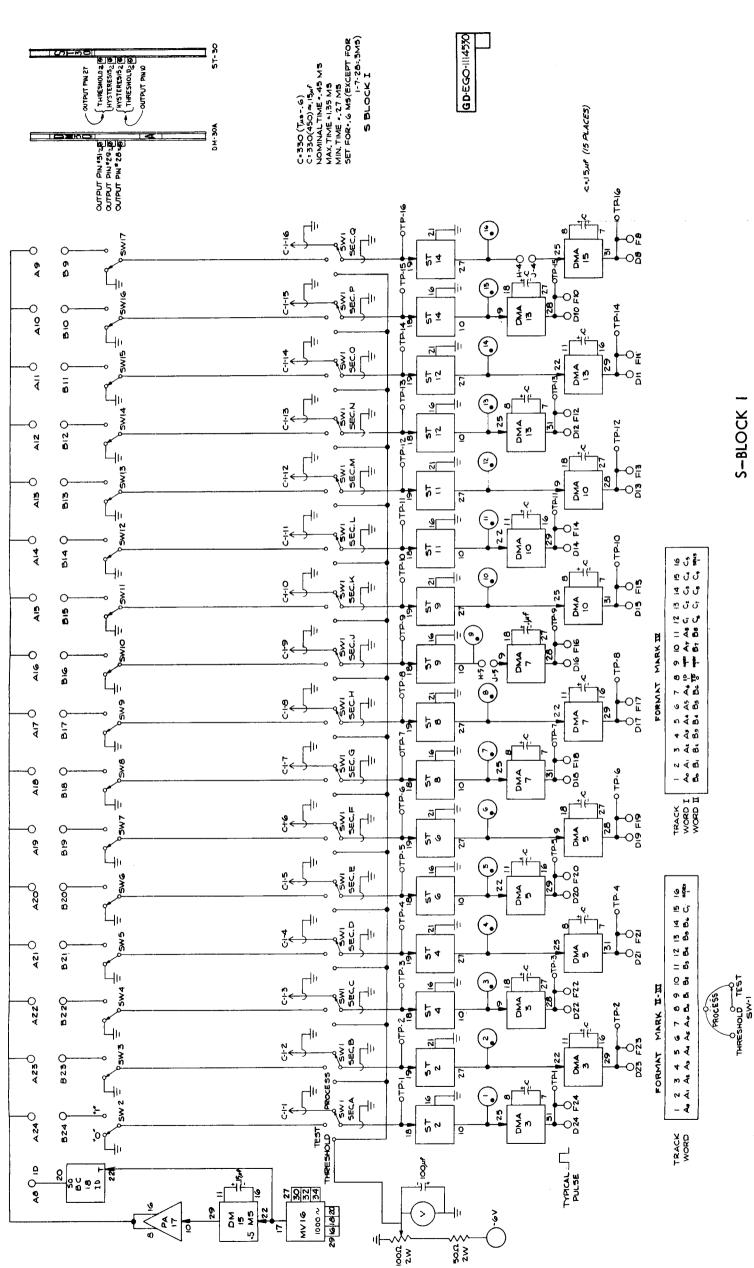

| 17     | Input Detection and Simulation Logic (GD-EGO-1114530) | 28   |

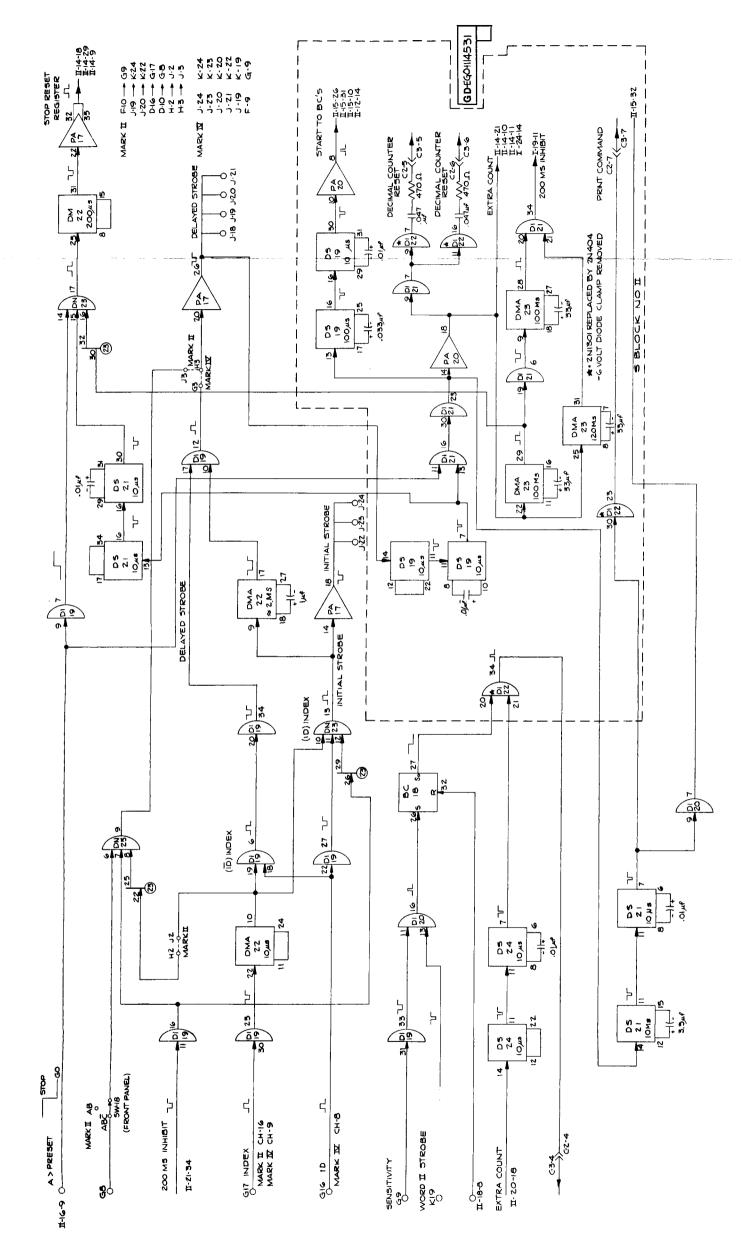

| 18     | Control Logic (GD-EGO-1114531)                        | 29   |

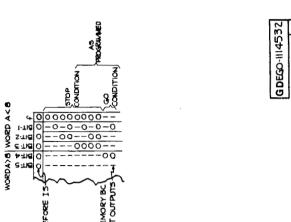

| 19     | Word A Logic (GD-EGO-1114532)                         | 30   |

| 20     | Word B Logic (GD-EGO-1114533)                         | 31   |

| 21     | Word C Logic (GD-EGO-1114534)                         | 32   |

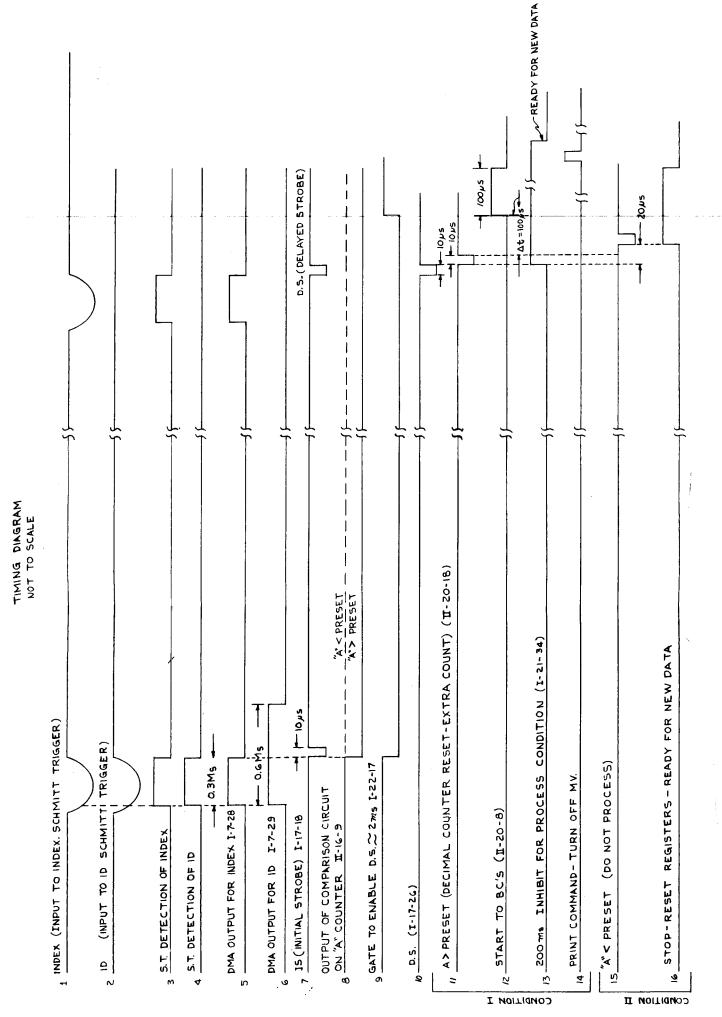

| 22     | Timing Waveforms                                      | 33   |

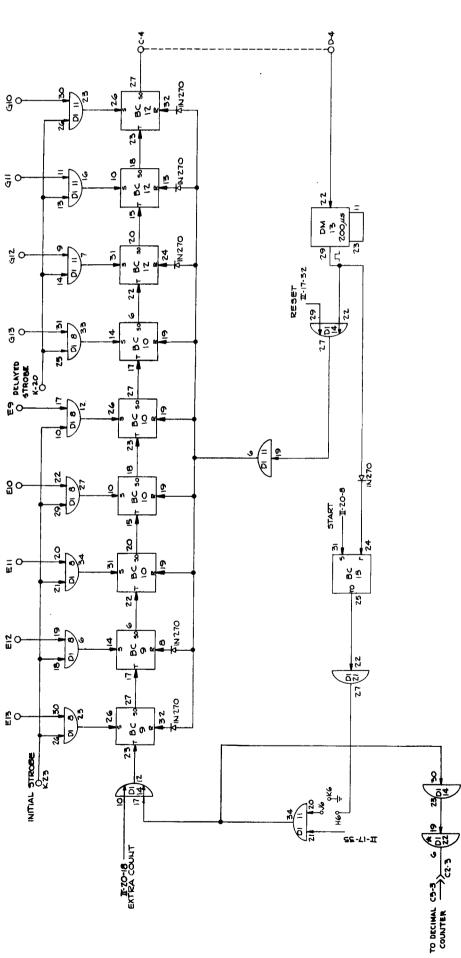

| 23     | Programming (GD-EGO-1109652)                          | 34   |

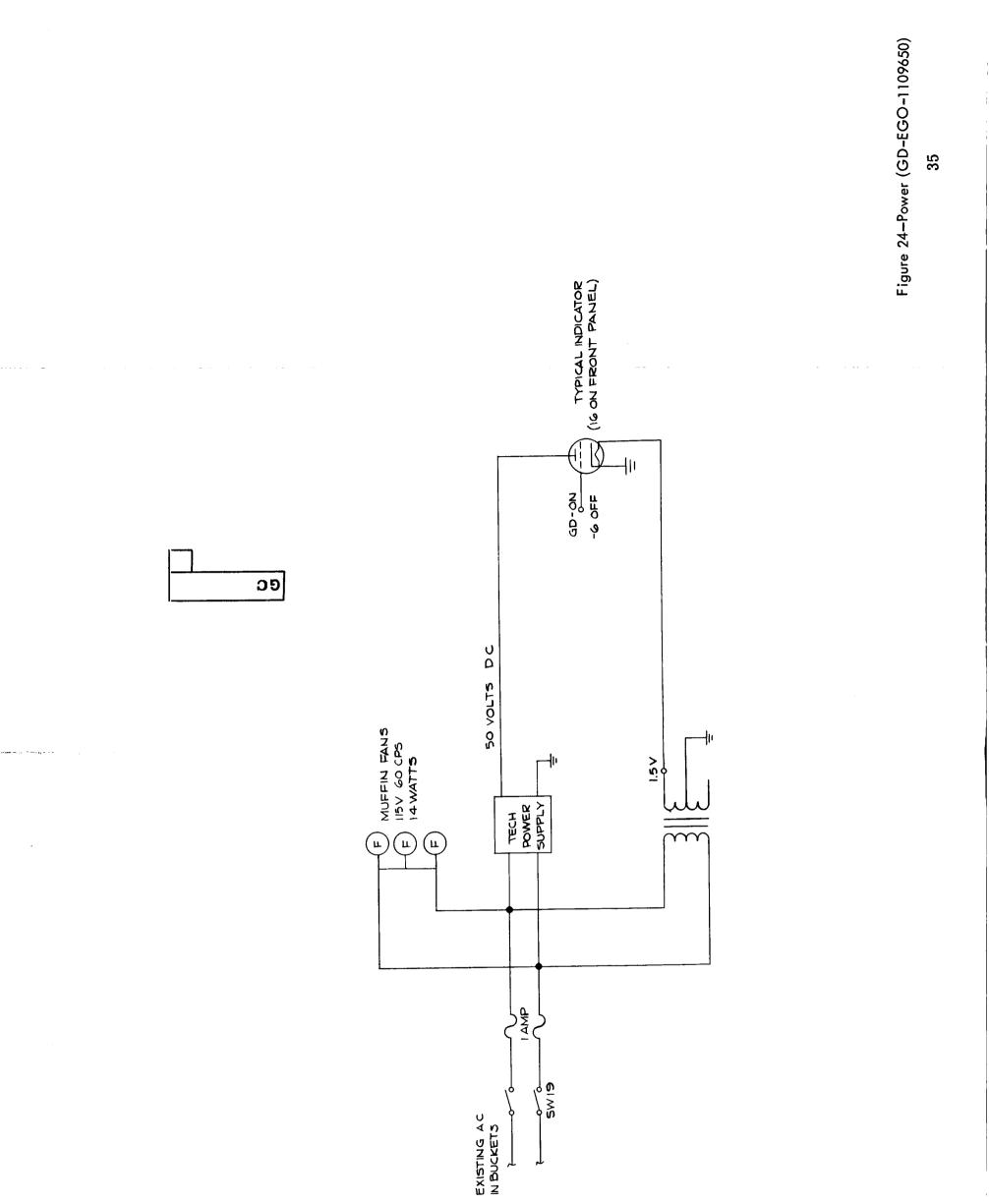

| 24     | Power (115 vac) (GD-EGO-1109650)                      | 35   |

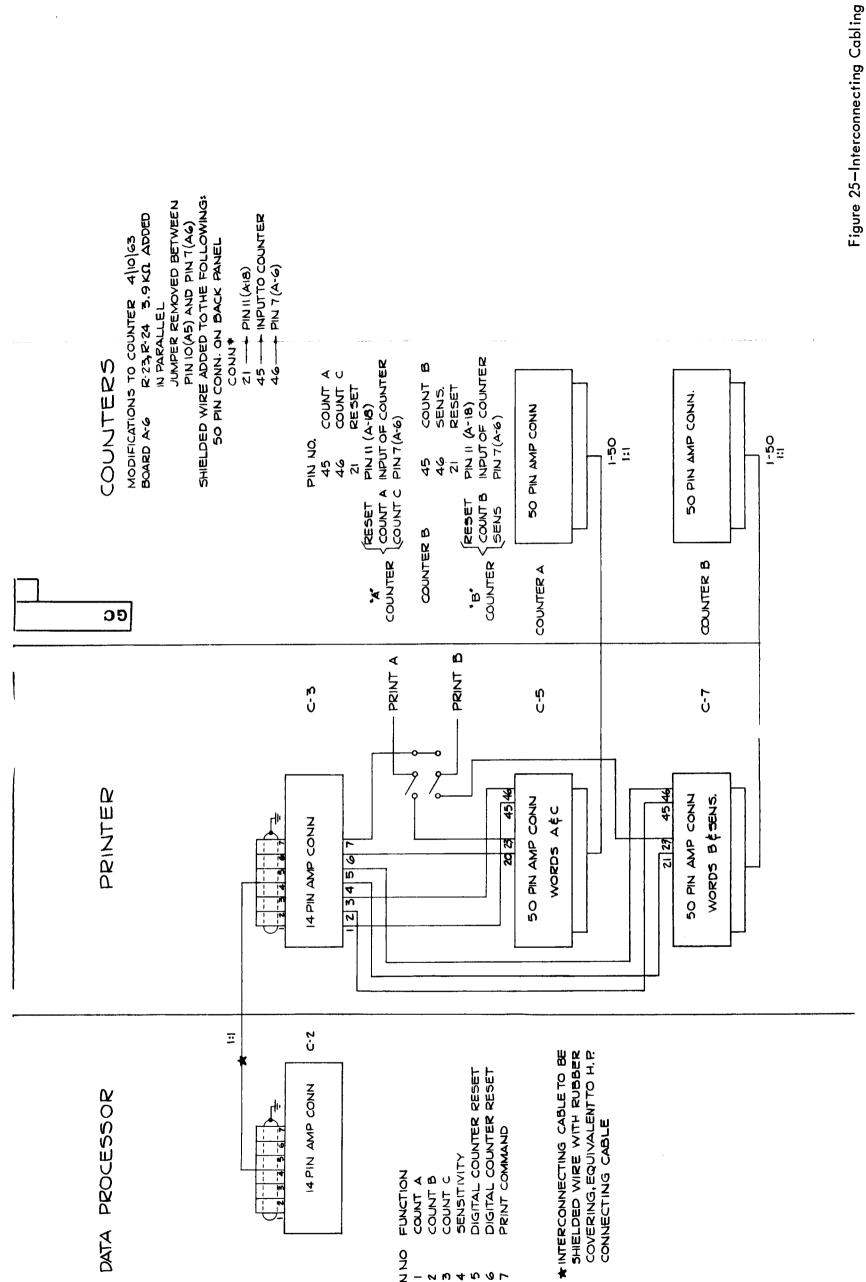

| 25     | Interconnecting Cabling (GD-EGO-1109651)              | 36   |

ĺ

# TABLES

۹.

٠,

-

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| 1     | Mark II and Mark III Format                | 6    |

| 2     | Mark IV Format                             | 6    |

| 3     | Mark II-III Printout                       | 8    |

| 4     | Mark IV Simulation Printout                | 9    |

| 5     | Truth Table for Word A Greater than Preset | 14   |

iii

#### EGO BALLOON EXPERIMENT DATA PROCESSOR

29184

#### I. INTRODUCTION

The EGO balloon experiment data processor (Figure 1) is designed to operate on prelaunch data for the EGO series satellites: specifically, experiments Mark II, Mark III, and Mark IV. These experiments, carried by balloon flights into the upper atmosphere, provide experimental data concerning identification of particles and measurement of their energies which are recorded on magnetic tape (Figure 2). Upon retrieval of the recorded tapes, the EGO data processor serves as a quick-look facility in the field by processing samplings of the data throughout each tape, converting each sampling to decimal form for both decimal display and decimal printout.

Input signals to the EGO data processor are the reproduce-amplifier signals from the tape transport. The processor detects the signals of each channel, assembles the information, and by digital techniques converts the data when the data point is logically determined to be of value to the experimenter or the field technician. The data formats processible by the unit, for similar experiments, are made programmable by a patch panel, which also controls selection or rejection of a data point. The unit is designed to tolerate transport skew, transport speed variation, signal noise, and signal amplitude variation. A simulation mode for rapid checkout in the field is incorporated in the processor.

auth .

Figure 1–EGO Data Processor, Overall Unit

à

Figure 2-Pull-out View of Arithmetic Unit

#### **II. SPECIFICATIONS**

#### SYSTEM INPUTS:

#### Parallel binary data entered on 16 separate data lines

Experiment data events:

Events occur asynchronous with time. For Mark II and Mark III, one event consists of one entry of 16 bits in parallel. For Mark IV, one event consists of the entry of two groups of 16 bits in parallel.

#### Index and ID timing:

Presence of a data word is indicated by an index marker on any specified line. The first part of the event of Mark IV is indicated by the presence of an index marker plus an identification (ID) marker.

The second part of the event of Mark IV is indicated by an index marker that has been preceded in the first part of the event by a time greater than 0.8 millisecond but less than 1.2 msec, and the absence of an ID marker.

Index and ID pulse:

Pulsed-negative excursion from the dc level of the steady-state signal The magnitude of the excursion must be between -1 and -10 volts.

#### Binary one:

Pulsed-negative excursion from the dc level of the steady-state signal occurring in coincidence with an index marker

The magnitude of the excursion must be between -1 volt and -10 volts.

Binary zero:

Absence of a negative excursion from the steady-state signal when the index marker is present

Repetition rate:

Asynchronous, between 0 cps and 1000 cps

Maximum skew:

$\pm 108$  degrees of the maximum repetition rate (1000 cps) cycle, referenced to the index marker

#### Maximum speed variation:

±10 percent of nominal speed

Input impedance:

lí

| -1.0 volt  | 5,000 ohms minimum  |

|------------|---------------------|

| -2.0 volts | 10,000 ohms minimum |

#### Data line input:

24-pin Amphenol connector

#### SYSTEM OUTPUTS:

- Decimal display by Nixie tubes

- Decimal printout

Maximum printout rate is 5 prints per second.

#### **POWER REQUIREMENTS:**

105 to 125 volts ac; 58 to 62 cycles per second; 600 watts maximum

#### **TEMPERATURE RANGE:**

0°C to 50°C

#### DIMENSIONS:

Panel height:

System requires 37-1/4 inches of panel height.

Maximum depth:

21-3/4 inches

#### Maximum width:

19-1/4 inches

#### Weight:

135 lb.

#### **MOUNTING:**

All units are mountable in a standard 19-inch relay rack. The main unit, containing the 3-C modules, is provided with chassis-track slides for accessibility.

#### **OPERATING CONTROLS:**

- Programmable patch panel on front panel

- Normal operating controls on front panel

- Simulation and system calibration controls are mounted on the rear of the front panel of the arithmetic unit.

#### III. DATA FORMAT

#### MARK II AND MARK III

The Mark II and Mark III EGO balloon experiment presents asynchronous parallel binary data entered on 16 separate data lines. The parallel 16-bit entry is subdivided into two 7-bit words, an identification bit (C), and an index bit that indicates the presence of the parallel data. One 16bit parallel entry consitutes an event<sup>1</sup>. The format is shown in Table 1. The subscript indicates the relative significance of the binary bit.

| Table 1 |   |     |      |     |        |  |  |  |  |

|---------|---|-----|------|-----|--------|--|--|--|--|

| Mark    | Π | and | Mark | III | Format |  |  |  |  |

| Track Number | 1              | 2              | 3              | 4              | 5              | 6              | 7              | 8              | 9              | 10             | 11             | 12             | 13             | 14             | 15 | 16    |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|-------|

| Word I       | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | A <sub>4</sub> | A <sub>5</sub> | A <sub>6</sub> | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | B <sub>5</sub> | B <sub>6</sub> | С  | Index |

#### MARK IV

The Mark IV EGO balloon experiment presents asynchronous parallel binary data entered on 16 separate data lines, an event consisting of two 16-bit words. One event is composed of 28 data bits, two ID bits, and two index bits. The event is multiplexed in the form of two words, Word I and II; Word II follows Word I by a fixed time interval. Words I and II are subdivided into three 9-bit words plus a sensitivity bit. The other four positions are used to indicate the presence of a word and to differentiate between Word I and Word II. An index bit appears each time a word is present; when an ID bit is present, it indicates that the word is Word I. The other four a word II. The absence of an ID bit when a word is present indicates that the word is Word II. The format is shown in Table 2.

Table 2 Mark IV Format

| Track Number | 1              | 2              | 3              | 4              | 5              | 6              | 7              | 8  | 9     | 10                    | 11             | 12             | 13             | 14             | 15             | 16             |

|--------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|-------|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Word I       | A <sub>0</sub> | A <sub>1</sub> | $A_2$          | A <sub>3</sub> | A <sub>4</sub> | A <sub>5</sub> | A <sub>6</sub> | ID | Index | <b>A</b> <sub>7</sub> | A <sub>8</sub> | C <sub>0</sub> | C <sub>1</sub> | C <sub>2</sub> | C <sub>3</sub> | C <sub>4</sub> |

| Word II      | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B4             | B <sub>5</sub> | B <sub>6</sub> | ĪD | Index | В <sub>7</sub>        | B <sub>8</sub> | C <sub>5</sub> | C <sub>6</sub> | С <sub>7</sub> | C <sub>8</sub> | Sens.          |

<sup>1</sup>An event is one set of experimental measurements, constituting one data point.

#### IV. OPERATING INSTRUCTIONS<sup>1</sup>

#### CABLE CONNECTIONS:

#### Rear connections:

All rear connections should be made with the power turned off.

Connect the six-pin dc power cable from the Computer Control Company power-supply unit to the data-processor unit.

Connect the ac power cable to a 117-volt 60-cycle source.

Connect the tape-reproduce amplifiers to the 24-pin Amphenol connector (C-1) of the data processor unit.

Connect the 14-pin Amphenol connector (C-2) from the data-processor unit to the printer.

Connect the 50-pin Amphenol connector (C-5) from the printer to counter "A".

Connect the 50-pin Amphenol connector (C-6) from the printer to counter "B".

#### OPERATING PROCEDURE:

Turn on all power.

Set the commercial counter-selector switches to START of the MANUAL mode.

Set the commercial counter SENSITIVITY controls to "3".

Throw toggle switch on rear of printer to the EGO position.

Set main unit THRESHOLD - PROCESS - TEST switch to the PROCESS position.

(A) Insert the programmable patch panel for Mark II, and Mark III.

(B) Insert the programmable patch panel for the Mark IV experiment.

(A) Set the mode control to either  $AB\overline{C}$  or AB. ( $AB\overline{C}$  is the mode in which data will be processed only if C is an "0"; AB is the mode in which data will be processed regardless of the state of C.)

(B) This control is inoperative for the Mark IV mode of operation.

Throw printer RECORD switch to ON.

#### TEST PROCEDURE:

Set the commercial counters and printer for normal EGO operation as given in the operating instructions. Do not set main unit THRESHOLD – PROCESS – TEST switch to the PROCESS position.

Set the THRESHOLD - PROCESS - TEST control to the THRESHOLD position.

Adjust the meter to read the desired threshold voltage by varying the TEST VOLTAGE ADJUST control. The voltage is normally set for 2 volts for best noise immunity. If all the indicator lights on the front panel do not light, refer to the Calibration Section for threshold level adjustment.

Set the THRESHOLD - PROCESS - TEST control to the TEST position.

<sup>&</sup>lt;sup>1</sup>Paragraphs with an "A" refer to Mark II and Mark III. Paragraphs with a "B" refer to Mark IV. Paragraphs without an "A" or a "B" refer to all three, Mark II, Mark III, and Mark IV.

(A) Throw the toggle switch in the index track (track 16) to the "1" position. Place all other toggle switches in the "0" position.

(B) When testing for Mark IV, the ID channel (track 8) toggle switch must be thrown to the "1" position in addition to throwing the index track (channel 9) to the "1" position.

Throw each switch, in a chronological order, to the "1" position for 5 seconds and then to the "0" position. The appropriate front panel lamp should light for the time the switch is in the "1" position, and the digital printout should read as follows:

| Switch number in the "1" position<br>(all others in the "0" position | Di     | gital Printo | out    |

|----------------------------------------------------------------------|--------|--------------|--------|

| except the index track)                                              | Word A | Word B       | Word C |

| 1                                                                    | 001    | 000          | 0      |

| 2                                                                    | 002    | 000          | 0      |

| 3                                                                    | 004    | 000          | 0      |

| 4                                                                    | 008    | 000          | 0      |

| 5                                                                    | 016    | 000          | 0      |

| 6                                                                    | 032    | 000          | 0      |

| 7                                                                    | 064    | 000          | 0      |

| 8                                                                    | 000    | 001          | 0      |

| 9                                                                    | 000    | 002          | 0      |

| 10                                                                   | 000    | 004          | 0      |

| 11                                                                   | 000    | 008          | 0      |

| 12                                                                   | 000    | 016          | 0      |

| 13                                                                   | 000    | 032          | 0      |

| 14                                                                   | 000    | 064          | 0      |

| 15                                                                   | 000    | 000          | 12     |

| 16 (index track<br>ON AT ALL TIMES)                                  | 000    | 000          | 0      |

Table 3 Mark II – III Printout

<sup>2</sup>This figure will not print if the front panel control is set for the ABC mode.

| Switch number in the "1" position<br>(all others in the "0" position<br>except index channel (9) and ID<br>channel (8)) | Word A | Word B | Word C | Sens. |

|-------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|

| 1                                                                                                                       | 001    | 001    | 000    | 0     |

| 2                                                                                                                       | 002    | 002    | 000    | 0     |

| 3                                                                                                                       | 004    | 004    | 000    | 0     |

| 4                                                                                                                       | 008    | 008    | 000    | 0     |

| 5                                                                                                                       | 016    | 016    | 000    | 0     |

| 6                                                                                                                       | 032    | 032    | 000    | 0     |

| 7                                                                                                                       | 064    | 064    | 000    | 0     |

| 10                                                                                                                      | 128    | 128    | 000    | 0     |

| 11                                                                                                                      | 256    | 256    | 000    | 0     |

| 12                                                                                                                      | 000    | 000    | 033    | 0     |

| 13                                                                                                                      | 000    | 000    | 066    | 0     |

| 14                                                                                                                      | 000    | 000    | 132    | 0     |

| 15                                                                                                                      | 000    | 000    | 264    | 0     |

| 16                                                                                                                      | 000    | 000    | 016    | 1     |

Table 4 Mark IV Simulation Printout

#### CALIBRATION:

#### Threshold level adjustment

The THRESHOLD – PROCESS – TEST control must be in the THRESHOLD position to make this adjustment. Each level-detector threshold can be adjusted by varying a potentiometer<sup>3</sup> that will light a front-panel indicator.

The TEST VOLTAGE meter should be set by varying the TEST VOLTAGE ADJUST control for the desired threshold voltage (2 volts usually give the best noise immunity).

The potentiometer<sup>4</sup> on the module associated with the indicator should then be set so that the indicator light is just beyond the threshold of being turned on. This is accomplished by turning the module potentiometer counterclockwise (CCW) until the appropriate indicator light turns on, then backing off clockwise (CW) on the potentiometer until the light extinguishes. When the potentiometer is in this position, it should be turned slowly CCW until the light just turns on. The potentiometer is now at the optimum setting.

#### Adjustment of the temporary memories (DMA's)

The THRESHOLD – PROCESS – TEST control must be in the TEST position and the toggle switch of the track being adjusted must be in the "1" position.

<sup>&</sup>lt;sup>3</sup>Refer to Figure 17 in the section containing diagrams, for appropriate potentiometer adjustment.

<sup>&</sup>lt;sup>4</sup>Refer to Figure 17 for appropriate potentiometer adjustment.

The output of each temporary memory can be monitored by an oscilloscope connected to the appropriate DMA OUTPUT pin jack on the rear of the front panel. The duration of each temporary memory (DMA), with the exception of the index bit, is set for 0.6 millisecond by adjusting a potentiometer on the appropriate module.<sup>4</sup> The maximum duty cycle of these modules is 67 percent. For a maximum data-repetition rate of 1 kc, the maximum delay can be set for 0.67 millisecond, but the normal setting is 0.6 msec. The delay of the index bit is set for one-half of the data-bit temporary memory delay, or 0.3 msec. The trailing edge of this pulse is used to strobe the information into a storage register. Placing the strobe in the center of the temporary memory-storage cycle allows for maximum skew.<sup>5</sup>

<sup>&</sup>lt;sup>5</sup>See Section V-D for discussion of setting the index bit for optimum data recovery.

#### V. THEORY OF OPERATION

#### A. GENERAL

The EGO balloon experiment data processor is designed to operate on 16 parallel signals from a 16-track magnetic-tape reproducer. The signals of each channel carry information in binary form, a "one" being represented by one half-wave rectified sinewave pulse having a period of 1 millisecond and a peak amplitude of -5 millivolts at the reproduce heads. A zero is represented by the absence of any signal excursion when an index pulse is present. Before entering the processor, each channel is amplified by 60 db so that a "one" pulse is a -5v peak half-wave rectified sinewave pulse.

The block diagram<sup>1</sup> for the EGO balloon shows that each experiment data processor amplified channel is applied to a threshold detector. The threshold detectors are employed to recognize the leading edge of the negative excursion of a "one" pulse. The detectors are normally set to recognize only those signals which exceed a negative 2 volts. In tandem with each detector is a temporary memory which serves the purpose of storing the occurrence of a "one" pulse for a finite length of time. This technique is employed to compensate for tape skew.<sup>2</sup>

The output of the detector on the index channel (the signal which indicates to the processor the presence of a parallel word) is applied to the strobe delay, initiating a delayed read pulse through the control portion to the temporary memories. The read pulse stores the complement of the state of each bit memory into the appropriate binary register by way of the patch panel. The assembly of the experiment words (in one's complement form) is generated by two parallel input words for Mark IV and a single parallel input word for Mark II and Mark III. To distinguish between the initial word and the delayed word for Mark IV, the identification channel carries an ID pulse for the initial word and an ID pulse for the delayed word. The control section recognizes the presence of the index and the ID to assemble word I, and the presence of the index and ID to assemble word II.

With the appropriate assembly of experiment words in one's complement form in registers A, B, and C, and the storage of the sensitivity bit in the decimal counter, the control section provides a serial count pulse to each of the three experiment word binary registers<sup>3</sup> converting the one's complement representation to two's complement representation. Following this is a serial readout of each of the binary registers into modified commercial decimal counters.<sup>4</sup> The numbers stored in the decimal counter will then be the decimal equivalent of the binary experiment word.<sup>5</sup> The sensitivity bit is stored in the decimal counter also. Storage of each word and the sensitivity bit are kept independent from each other through modification of the decimal counters.

The magnitude of the word stored in register A before serial readout determines whether the data point (the information contained in all registers) will be accepted.<sup>6</sup> If the magnitude of the count stored in register A is greater than a patched preset number, the information will be accepted and serial readout will proceed; if the count is less than the patched preset number, then the processing of information for that data point will be stopped and cleared so that the next event or parallel input word will be accepted.

After the experiment words are stored in decimal form in the decimal counters, a print-command pulse is generated to a commercial printer<sup>7</sup> which prints the information stored in the counters. The print cycle requires 200 milliseconds. During the time of printing, the control section

<sup>&</sup>lt;sup>1</sup>See Figure 16 in section containing schematic diagrams.

<sup>&</sup>lt;sup>2</sup>See discussion on tape skew, part D of this section.

<sup>&</sup>lt;sup>3</sup>For Mark II and Mark III, only two experiment words (A and B) are employed.

<sup>&</sup>lt;sup>4</sup>Hewlett-Packard Model 5532A.

<sup>&</sup>lt;sup>5</sup>See discussion in Section V-B on conversion of binary to decimal form.

<sup>&</sup>lt;sup>6</sup>See discussion in Section V-C on recognition of a data point that exceeds a preselected number.

<sup>&</sup>lt;sup>7</sup>Hewlett-Packard Model 562A.

generates a lockout pulse that inhibits the generation of new data strobes, thereby preventing the entrance or processing of any new data until the termination of printing.

Incorporated in the EGO balloon experiment data processor is a simulation mode in which the data-line inputs are switched out and simulated data are applied to the threshold detectors. By observation of front panel indicator lights and operator control of simulated data words, the unit can be checked for proper operation.

#### B. BINARY-TO-DECIMAL CONVERSION

A translation can be made from the binary to the decimal system by first placing the 2's complement of the binary number into a register which also can operate as a binary counter, then applying a serial train of pulses simultaneously to both the binary counter and a decimal counter. The conversion is obtained by counting the number of counts in the decimal counter required to clear or recycle the binary register.

An algorithm\* for determining the complement of a number N is:

$\overline{N} = r$ 's complement =  $r^n - N$

where: n = number of digits in the number N

N =the number

r = the radix or base

Transposing:  $\overline{N} + N = r^n$

Since a counter can count to  $r^{n}-1$ , the counter has to pass through a zero count or recycle if the original number is serially added to the complement previously stored in the register; i.e., if N counts are added to a binary counter storing  $\overline{N}$  (the two's complement of N in this case), then the counter will end in a "0" state.

For ease of implementation, the 1's complement is entered into the binary register and this number is converted to 2's complement by adding a count to the counter.

An algorithm for relating 2's complement (radix complement) to 1's complement (diminished radix complement) is:

$\overline{\overline{N}} = r^{n} - N - r^{-m}$  $\overline{N} = \overline{N} - r^{-m}$

where:  $\overline{N}$  = diminished radix complement

For the 1's complement, m = 0, so that

```

\overline{\overline{N}} = r^n - N - 1= \overline{N} - 1\overline{\overline{N}} = \overline{\overline{N}} + 1

```

$\mathbf{or}$

\*Reference 1.

The translation to decimal form by serial readout begins after the 1's complement has been converted to the 2's complement. As an illustration, consider the conversion of the binary number 0011101  $(29_{10})$  that is stored in a seven-stage binary register to a decimal number:

#### C. RECOGNITION OF A DATA POINT THAT EXCEEDS A PRESELECTED NUMBER

The limited speed of the digital printer makes it necessary to obtain printouts of only good data points, because these printouts represent only 0.5 percent of the maximum data rate. In the Mark II, Mark III, and Mark IV experiments there are certain conditions under which low counts can be discarded before the time-consuming conversion begins. When accepting data, the data processor will determine whether or not a data point exceeds a predetermined level. When the processor decides to accept a data point for processing, a lockout or inhibit mode is generated which prevents the processor from accepting any additional data points until the digital print cycle is completed.

The decision process is illustrated by the truth table on the following page.

The 1's complement of the data point is stored in the binary register. The set side of the most significant bits of the register are connected to a gate that generates a "stop" condition when all of the inputs are true (1), and a "go" condition if any one of the inputs is false (0). The logic is illustrated in Figure 3.

For example, consider a situation in which any data point with a count less than 8 can be discarded. The set side of the register from bit  $4(2^3)$  to bit  $n(2^{n-1})$  is programmed to the gate. When all the inputs are true (1), which corresponds to a digital number of less than 8, a stop condition is generated. When any stage of the set side of the register programmed to the gate becomes false (0), the number equals or exceeds 8 and a go condition is generated.

| Bit 6 2 <sup>5</sup> | Bit 5 2 <sup>4</sup> | Bit 4 $\overline{2^3}$ | Bit 3 $\overline{2}^2$ | Bit 2 2 <sup>1</sup> | Bit 1 20 | Output of Gate | Digital Equivalent |

|----------------------|----------------------|------------------------|------------------------|----------------------|----------|----------------|--------------------|

| 1                    | 1                    | 1                      | 1                      | 1                    | 1        | 0              | 0                  |

| 1                    | 1                    | 1                      | 1                      | 1                    | 0        | 0              | 1<br>2             |

| 1                    | 1                    | 1                      | 1                      | 0                    | 1        | 0              | 2                  |

| 1                    | 1                    | 1                      | 1                      | 0                    | 0        | 0              | 3                  |

| 1                    | 1                    | 1                      | 0                      | 1                    | 1        | 0              | 4                  |

| 1                    | 1                    | 1                      | 0                      | 1                    | 0        | 0              | 5                  |

| 1                    | 1                    | 1                      | 0                      | 0                    | 1        | 0              | 6                  |

| 1                    | 1                    | 1                      | 0                      | 0                    | 0        | 0              | 7                  |

| 1                    | 1                    | 0                      | 1                      | 1                    | 1        | 1              | 8                  |

| 1                    | 1                    | 0                      | 1                      | 1                    | 0        | 1              | 9                  |

Table 5Truth Table for Word A Greater Than Preset

Figure 3—The NAND Function

The processor can be programmed to recognize any data point that has a count exceeding  $2^n$  where n equals zero or any integer. There is also a provision which enables the processor to process all data, regardless of the count.

#### D. COMPENSATION FOR TAPE SKEW

To recover the maximum amount of data when skew problems are present, the incoming data bits are stored in temporary memories at a fixed time interval after occurrence of the INDEX bit, and the information is simultaneously strobed from all the bit memories into binary registers for further processing.

A delay multivibrator with a 67-percent duty cycle is used as a temporary memory device. For a maximum repetition rate of 1 kc, the maximum memory duration that can be obtained is 0.67ms. As a margin of safety, all the data memories are preset to provide a storage time of 0.60ms, and the data-strobe delay generator is preset to provide a delay equal to half the memory duration, or 0.3 ms. This is the optimum setting for recovering data with the greatest symmetrical skew. If the recorded tape has static skew or if the playback head stack is misaligned, the strobe pulse can be elongated or shortened, depending on the time bias introduced by the skew.

The following examples illustrate data recovery with dynamic skew.

#### Example 1:

In Figure 4, the data-information pulse is in phase with the index pulse that generates the datasampling strobe. The data could, therefore, be strobed at the center of the data memory-storage cycle as shown. This would be the setting of the data strobe delay for an ideal situation where no skew or misaligned data pulses are present.

Strobe samples data in the center of its memory cycle. No skew – data tracks and index track displaced by  $0^{\circ}$ .

Figure 4—Bit Detection with  $0^{\circ}$  Skew

#### Example 2:

In Figure 5, the information pulse from the data channel was delayed by 108° (0.3 msec) with reference to the pulse that produces the generated strobe. The sampling strobe, which is generated from the trailing edge of the delayed strobe pulse, will sample the data pulse at the leading edge of the data memory pulse.

Data track displaced from index track by  $-108^{\circ}$ .

Figure 5-Bit Detection with -108° Skew

#### Example 3:

In Figure 6, the information pulse from the data channel precedes the pulse that generates the strobe by  $108^{\circ}$  (0.3 msec). The sample strobe now samples the data pulse at its trailing edge.

Under actual operating conditions, all three of the examples can happen simultaneously; i.e., for a given word the data pulses in the various tracks can lead, lag, and be in phase with the index pulse that generates the strobe. When the memories and strobe delay are set for the values previously mentioned, the system will accurately process data that vary within  $\pm 108^{\circ}$  with reference to the index bit that produces the sampling strobe.

- - - -

Figure 6-Bit Detection with +108° Skew

#### VI. DESCRIPTION OF LOGIC

A. Control Unit

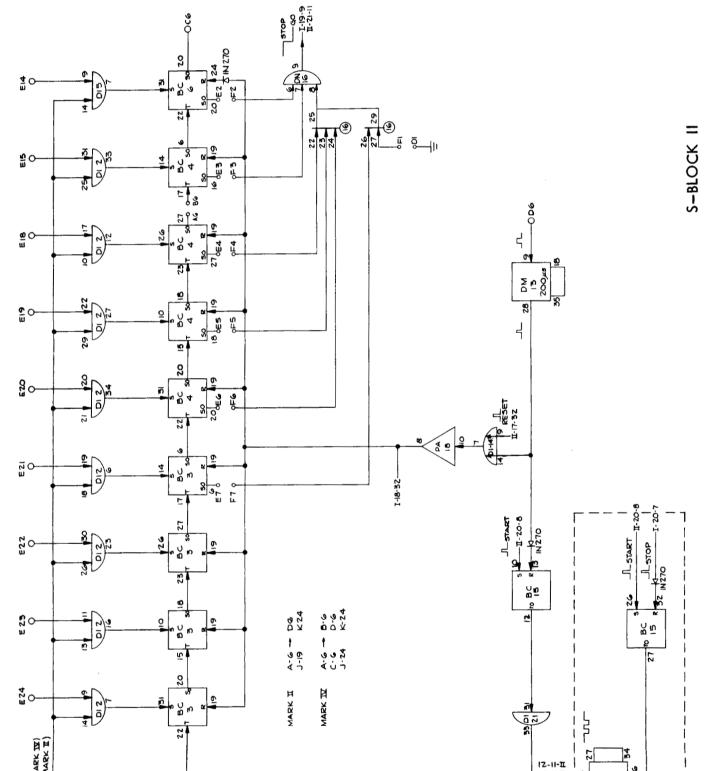

#### Mark IV Control Logic<sup>1</sup>

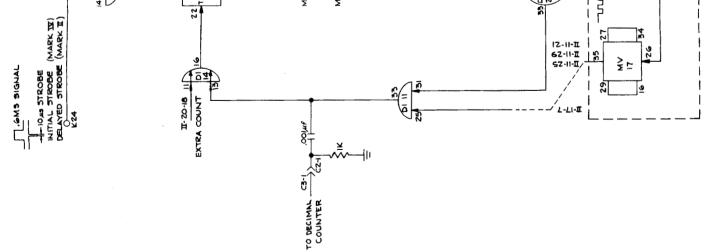

The incoming data signals, after being detected by the Schmitt triggers, are stored in a temporary memory (delay multivibrator) until the complement of the data word is strobed into a binary register. The index and the ID pulses are detected by their respective Schmitt triggers (I-8-27 and I-9-10). When they are in coincidence, an initial strobe (I-23-13) is generated from the trailing edge of the index pulse (TLN-7).<sup>2</sup>

The initial strobe (I.S.) generates a gating pulse approximately 2 msec long (I-22-17). When another index pulse appears within this interval and no ID pulse is present, a delayed strobe (DS) pulse is produced (TLN-10).

The initial strobe (IS) samples the incoming data lines and enters the complement of the data in the appropriate binary registers. A comparison is made between the data word entered in the "A" register and a preprogrammed word;<sup>3</sup> if the incoming data word is equal to or greater than the programmed word, a gate is enabled that allows the delayed strobe (DS), with a  $10-\mu$ s delay (II-21-16), to add an extra count to the three binary registers, reset the commercial decimal counters, and (after a  $100-\mu$ s delay) gate a multivibrator's output to the input of the three registers. The data are then passed through level-matching circuits to the inputs of the decimal counters.<sup>4</sup>

The sensitivity bit is gated with the delayed strobe (I-20-16) to set a flipflop (I-18-27), whose output is gated with the extra count pulse through a level-matching circuit directly to the split input of the decimal counter. The sensitivity word has only two states, true (-6 volts) and false (0 volts). The true condition in the printout is represented by a decimal "1", the false condition by a "0".

The same pulse that gated the multivibrator's output to the registers also initiates a 10-msec delay pulse (I-21-11) that turns off the multivibrator after the conversion.

The pulse that generated the extra count (TLN-11) initiates a 200-msec inhibit (II-21-34) that disables the control input (I-23-13) so that new data will not be accepted for processing while the printer is operating.

If the data word entered in the "A" register is less than the preset number, the delayed strobe, with an additional 20- $\mu$ sec delay, is used to generate a 200- $\mu$ sec pulse (I-22-31) that resets the binary registers and allows the system to accept new data.

#### Mark II-III Control Logic<sup>5</sup> (Refer to diagram GD-EGO-111-4531)

The index pulse is detected by the Schmitt trigger and the leading edge of the pulse is delayed by approximately 0.3 msec and this edge is used to generate a  $10-\mu$  sec strobe pulse (I-22-10). The strobe pulse is gated with the  $\overline{C^6}$  bit (I-23-9) in the ABC mode of operation. When in the ABC mode of operation and with the absence of the C bit ( $\overline{C}$ ), the  $10-\mu$  sec pulse is used to strobe the complement of the data into the appropriate binary registers. If the C bit is present, the

<sup>&</sup>lt;sup>1</sup>See Figures 18 and 19 in the section containing diagrams.

<sup>&</sup>lt;sup>2</sup>The notation TLN- will be used to refer the reader to the timing line numbers on Figure 22 in the section containing diagrams.

<sup>&</sup>lt;sup>3</sup>Refer to Figure 23 for appropriate programming.

<sup>&</sup>lt;sup>4</sup>The six-stage decimal counters are split internally into two three-stage counter circuits, so that each counter can accept two different inputs and can convert binary numbers to an equivalent decimal count of 999.

<sup>&</sup>lt;sup>5</sup>See Figure 18 in the section containing diagrams.

<sup>&</sup>lt;sup>6</sup>The control switch ABC-AB is located on the front panel.

$10-\mu$ sec pulse is inhibited and no further processing occurs. When in the AB mode, all data are processed regardless of the condition of the C bit.

After entry of the complement of the data word into A register, the processing is the same as in the Mark IV mode of operation.

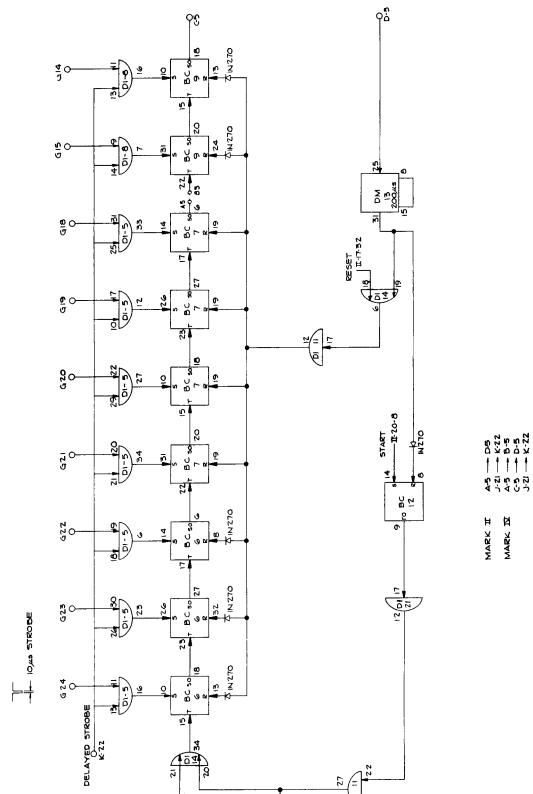

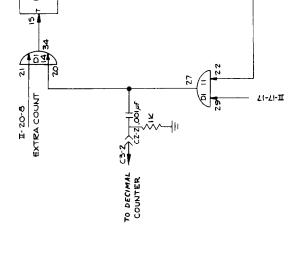

B. REGISTERS A, B, AND C

(Diagrams GD-EGO-1114-532, 533, 534)<sup>1</sup>

Register A (Diagram GD-EGO-1114-532)

The output of the Schmitt trigger data detection circuit is connected to a gate whose output, when strobed, sets the dc-set side of a binary register. When no data pulse is present at the occurrence of an input word, the gate is enabled and the initial data strobe<sup>2</sup> sets each binary register of the counter to the complement of the input. When a data pulse is present, the gate is inhibited and the register is left in the reset or the false condition; i.e., the register is set to true (-6 volts) when the input data line is false, or to false (0 volts) when the input data line is true.

After data have been entered into register A, a comparison against a programmed number is performed. If the stored data in register A are equal to or greater than the programmed number, the output of the comparison gate (II-16-9) is true (-6 volts), which indicates a "go" or "process data" condition.

Upon acceptance of data for processing, an extra count pulse is added to the binary registers through an "OR" gate (II-14-16), making the stored number in the register the two's complement of the data word.

A start pulse from the control logic sets a flipflop (II-15-27) which provides a synchronous start for the free-running multivibrator (II-17-35) that counts out the contents of the register. The multivibrator is turned off after 10 msec by resetting the control flipflop with a pulse generated by a delay multivibrator. The start pulse from the control logic also sets a flipflop (II-15-12) that gates the output of the multivibrator to the binary register and the decimal counters. Upon recycling, the output of the binary register (II-6-20) produces a pulse whose leading edge triggers a delay multivibrator that resets flipflop (II-15-12), thereby turning off the gated output to both the decimal and binary counters.

(Registers B and C, diagrams DG-EGO-1114-533 and -534, operate the same as register A but do not have a comparison circuit to evaluate the incoming data. The free-running multivibrator used for reading out register A is shared by all three registers and is turned off 10 msec after the start command.)

<sup>&</sup>lt;sup>1</sup>See Figures 19, 20, 21 in section containing diagrams.

<sup>&</sup>lt;sup>2</sup>For the Mark IV experiment, the data strobe to register A is the initial strobe; for the Mark II-III experiments, the data strobe is the delayed strobe. (The initial strobe is not generated for these two experiments.)

#### VII. SIGNAL SIMULATION

The Mark IV simulated signal is generated by a free-running multivibrator (MV-16) set for 1000 cycles per second, the maximum data-reduction frequency of the processor. The output of the multivibrator triggers a delay multivibrator (DM-15) which generates a pulse 0.5-msec long. This pulse, after being inverted through a power-amplifier stage (PA-17), is used to simulate the index and the data pulses. The ID pulse which occurs at one-half the frequency of the index pulse is generated by connecting the MV output to a binary counter (BC-18) which divides the MV frequency by two. The output of the binary counter is connected to the ID channel. A coincidence of the index and the ID channels creates a Word I strobe; an index and an  $\overline{ID}$  create a Word II strobe. A "one" is detected by the level detectors if the individual toggle switch for that channel is thrown to the "one" position and the master control switch\* is in the "test" position.

Mark II-III simulation differs from the Mark IV in that the BC output is not used; the PA output is used to generate all the signals to be detected by the level detectors.

<sup>\*</sup>The toggle switches and the master control switch are located on the rear of the front panel.

#### VIII. POWER

#### (Diagram GC-EGO-1109-650)\*

The data processor uses 115-volt 60-cycle single-phase power. The processor unit has an ON-OFF toggle switch that connects the ac power through a 1-ampere fuse to the Muffin fans, the Technipower power supply, and a 1.5v step-down transformer.

The indicator thyratron tubes on the front panel derive a 50-volt dc plate potential from the Technipower power supply, and their 1.5v ac filament voltage from the step-down transformer. The 3-C RP30 power supply uses 115v 60-cycle single-phase power. An interconnecting cable between the 3-C power supply and the processor is used to supply the -6, -18, and +12 volts of dc current between the two units.

<sup>\*</sup>See Figure 24 in the section containing diagrams.

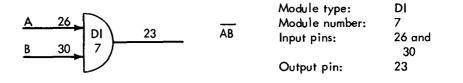

#### IX. CONVENTIONS AND SYMBOLS USED IN THE DRAWINGS AND THE LITERATURE

The EGO data processor system uses Computer Control Company's S-Pac 1-Mc digital modules. The 3-C (Computer Control Company) reference manual should be used when referring to the detail logic diagrams. When reference is made to a circuit on the drawing, its location is designated by the S-bloc within the unit, the module's position number, and the pin number in that order; e.g., III-4-8 refers to S-bloc III, module 4, pin 8.

Configurations for several circuits which bear explanation are shown here by examples:

Figure 7-NAND Circuit Symbol

Figure 8-NAND Circuit with Extended Fan-In Symbol

Figure 9-NOR Circuit Symbol

Figure 10-Monostable Multivibrator Circuit Symbol

| Module type:      | DS              |

|-------------------|-----------------|

| Module number:    | 21              |

| Toggle input:     | 14              |

| Assertion output: | 11 (delay time) |

| Assertion output: | 7 (output pulse |

| with indicated de | elay) 12 and    |

| 15 determine the  | delay time; 8   |

| and 6 determine   | the output      |

| pulse width.      |                 |

|                   |                 |

Figure 11-Delayed Pulse Generator Symbol

Figure 12-Schmitt Trigger Symbol

| Module type:         | BC |  |  |  |

|----------------------|----|--|--|--|

| Module number:       | 8  |  |  |  |

| Complementary toggle |    |  |  |  |

| input pin:           | 22 |  |  |  |

| Set input:           | 31 |  |  |  |

| Reset input (common  |    |  |  |  |

| to 4 BC circuits:    | 19 |  |  |  |

| Reset input (for     |    |  |  |  |

| individual circuit): | 24 |  |  |  |

| Set output:          | 20 |  |  |  |

| Reset output:        | 25 |  |  |  |

Figure 13-Binary Counter Circuit Symbol

| Module type:                     | MV              |  |  |  |  |

|----------------------------------|-----------------|--|--|--|--|

| Module number:                   | 16              |  |  |  |  |

| <b>MV</b> output:                | 17              |  |  |  |  |

| MV output:                       | 35              |  |  |  |  |

| Determination of                 |                 |  |  |  |  |

| frequency range:                 | Pin 27 to 30,   |  |  |  |  |

| 32,34, and 29 to                 | 16, 18, 20      |  |  |  |  |

| (Frequency can be                | e varied within |  |  |  |  |

| overall range by a potentiometer |                 |  |  |  |  |

| on top of the module.)           |                 |  |  |  |  |

The number within the circle gives the location of the light on the front panel.

Figure 15-Light Indicator Symbol

### X. MODIFICATIONS TO HEWLETT-PACKARD DIGITAL COUNTERS AND PRINTER

(Diagram GC-EGO-1109-651)\*

Modifications to counters:

- 1. Board A-6

- (a) R23, R24 3.9-K ohm resistor added in parallel

- (b) Jumper removed between pin 10 (A-5) and pin 7 (A-6)

- 2. Shielded wire added to the following

Pin connections on the 50-pin connector on rear of counter:

|             | FROM              | то               |

|-------------|-------------------|------------------|

|             | 45 (count A)      | Input to Counter |

| "A" Counter | 46 (count C)      | Pin 7 (A-6)      |

|             | 21 (reset)        | Pin 11 (A-18)    |

|             | 45 (count B)      | Input to counter |

| "B" Counter | 46 (sensitivity)  | Pin 7 (A-6)      |

|             | <b>21</b> (reset) | Pin 11 (A-18)    |

Modifications to digital printer:

A double-pole double-throw toggle switch was added to the back of the printer to enable acceptance of the print command from the processor in the EGO position, and from the electronic counters in the NORMAL position. The two reset lines and the sensitivity (or Word C count) line from the processor are routed to the decimal counters via the printer through the Amphenol connectors and the counter-printer interconnecting cables. The lines from the processor to the printer are brought in by a 14-pin Amphenol connector.

\*See Figure 25 in section containing diagrams.

XI. REFERENCES

- 1. Chu, Yaohan, Digital Computer Design Fundamentals, McGraw-Hill Book Company, Inc., New York (1962)

- 2. Instruction Manual for S-Pac Digital Modules, 3C Computer Control Company, Inc.

- 3. Preliminary Operating and Servicing Manual (for Hewlett-Packard Company Model 5232A/ 5532A electronic counter)

- 4. Operating and Service Manual (for Hewlett-Packard Company 562A digital recorder)

Block Diagram (GC-EGO-1109925) 27

Figure 16–EGO Data Processor,

.

| CK 1<br>PLIFIED SIGNU | х<br>х<br>м 4 м 0 г б = 5 | SIGNAL              | CK B (ID)<br>SIGNAL<br>SIGNAL | 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 4 5 2 3 5 2 3 4 5 2 3 5 2 3 4 5 2 3 5 2 3 5 2 3 4 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 5 2 3 | - 2 3 4 5<br>2 A, A: A: A: A |

|-----------------------|---------------------------|---------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| AMPL<br>AMPL<br>TRACK | F<br>A                    | TRAC<br>AMP<br>TRAC | AMP 9                         | TRACK<br>WORD I<br>WORD I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TRACK<br>WORD I              |

Figure 17-Input Detection and Simulation Logic

٢.

1

, ,

S-BLOCK

Figure 18-Control Logic (GD-EGO-1114531)

29

• •

Figure 19-Word A Logic (GD-EGO-1114532) 30

1 1

|

**a** 1

GD-EGO-114533

MARK 10

i i

GDEGO114534

\*-6 VOLT CLAMPING DIODE REMOVED 2NISOI TRANSISTORS REPLACED DY 2N404

Mark IV J.6 -- H.6 C.4 -- D.4

ŧ

MARK II J. K. + K.6

32

CONDITION I - REGISTER "À GREATER THAN PRESET COUNT PROCESS DATA AND INHIBIT NEW DATA FOR 200 ms CONDITION I - REGISTER "A" LESS THAN PRESET COUNT DO NOT PROCESS DATA RESET ALL REGISTERS AND ACCEPT NEW DATA. Figure 22-Timing Waveforms

33

s **s**

1 (

D-5 (TURNOFF "B" REGISTER) D-6 (TURNOFF "A" REGISTER) K-6 (GROUND"C"REGISTER) DMA- 16) DMA- 9) G-9 ('C' INHIBIT PRINT) K-19 ('C" STROBE) K-22('M" STROBE) K-24('B" STROBE) 11 G-8 ("C"INHIBIT) G-17(INDEX) J-2 (STROBE) J-3 (STROBE) H-5 (ST-9 H-4 (ST-16 E-21 A3 E-20 A4 E-19 A5 E-24 4. E-23 4. E-22 42 ପ-ସ ପ-ସ ք FROM 61-7 02-7 12-7 тт<u>р</u>тт и и б б б и и A-I A-Q-A A-9 すらう A- 13 A- 12 A-5 **۵**-6 MARK II ں ہ TEST OPERATE **D**9 TO BE PROCESSED COUNT MUST BE 2 N K-19 (SENS"DELAYED STROBE) K: 24 ("A" INITIAL STROBE) K-23 ("C"INITIAL STROBE) K-22 ("BUDELAYED STROBE) K-20 ("C" DELAYED STROBE) PROCESS ALL DATA 6 բ 1-23 12-1 1-20 1-20 FROM J-24 OPERATE 8-5 (9 STAGE REGISTER 'B') 8-6 (9 STAGE REGISTER 'A') C-6 (TURN OFF A'REG.) C-4 (TURN OFF A'REG.) C-5 (TURN OFF A'REG.) C-5 (TURN OFF A'REG.) C-5 (TURN OFF A'REG.) C-5 (TURN OFF A'REG.) C-6 (TURN OFF A'REG.) C-7 (TURN OFF A'REG.) C-6 (TURN OFF A'REG.) C-7 (TURN OFF A'REG.) C-6 (TURN OFF A'REG.) C-7 (TURN OF G-3 (DELAYED STROBE) + DMAIG) (6 MMG + U-6 (COUNT'C' START) NDEX SENS **--5** (́ST-9 — ů ľ 000000° ŝ ů ů 9,1 õ മ გოოოფოფიიიიიიიიიი 2.2.2.2.2.0 დავიჭრე = ებე <u>6</u> 0 6-14 G-13 G-12 5 6.9 6

Figure 23–Programming (GD-EGO-1109652)

34

| <u>×</u> | <ul> <li>4 4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0</li></ul> | πητητητητητητη τττ<br>22250000000τουτου ου 4υ |

|----------|------------------------------------------------------------|-----------------------------------------------|

| MAR      | OPERATE                                                    |                                               |

.

36

(GD-EGO-1109651)

# DATA PROCESSOR

٩

| てつこうかうし | COUNT A | COUNT B | COUNT C | SENSIT IVITY | DIGITAL COL | DIGITAL COL | PRINT COMM |  |

|---------|---------|---------|---------|--------------|-------------|-------------|------------|--|

|         | -       | 2       | 'n      | 4            | S           | હ           | 7          |  |

٦.

#