## NASA CR-111838

# BEAM LEAD TECHNOLOGY

by T. W. Fitzgerald et al.

## NASA CONTRACTOR REPORT

March 15, 1971

Prepared by

GTE LABORATORIES, INCORPORATED

Waltham, Massachusetts

for

Langley Research Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

Hampton, Virginia

## BEAM LEAD TECHNOLOGY

By T. W. Fitzgerald, K. Anderson, V. J. Barry, N. Cerniglia, J. Coulthard, J. DiMauro, H. J. Ramsey, and R. Tonner

Prepared under Contract No. NAS 1-10226 by WALTHAM RESEARCH CENTER GTE LABORATORIES, INCORPORATED 40 Sylvan Road Waltham, Massachusetts 02154

for Langley Research Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

#### PREFACE

This report, based on an extensive and critical literature survey and the personal experience of the writers, has been compiled by the members of the Technical Staff of General Telephone & Electronics Laboratories under the technical direction of Dr. Brian Dale. Mr. John Coulthard was the program manager and Mr. T. Fitzgerald acted as the key person.

In addition to internal reports and documents, the information upon which the report is founded has come from literature searches by our own libraries, the Defense Documentation Center, NASA Scientific and Technical Information Division, and personal visits by several of the authors to companies actively engaged in beam lead work. The authors wish to express their gratitude for the courtesy and cooperation extended them by the personnel of RCA, Sommerville, New Jersey, Bell Telephone Laboratories, Allentown, Pennsylvania, Motorola Semiconductor Products, Inc., Phoenix, Arizona, and Texas Instruments, Dallas, Texas, during these visits.

## CONTENTS

|                                                 | Page |

|-------------------------------------------------|------|

| PREFACE                                         | iii  |

| SUMMARY                                         | 1    |

| INTRODUCTION                                    | 2    |

| BEAM LEAD MATERIALS                             | 3    |

| Metallurigeal Systems                           | 3    |

| Substrates                                      | 8    |

| PASSIVATION                                     | 16   |

| Introduction                                    | 16   |

| Silicon Dioxide Passivation                     | 17   |

| Silicon Nitride Properties                      | 18   |

| Dielectric Processing                           | 21   |

| Summary                                         | 28   |

| PROCESSING                                      | 29   |

| Passivation Processing                          | 29   |

| Metallization Processing                        | 33   |

| Slice Thindown                                  | 39   |

| Silicon Etch-Through                            | 41   |

| Aluminum System                                 | 41   |

| BONDS AND BOND TESTING                          | 42   |

| Introduction                                    | 42   |

| Thermo-compression Bonding                      | 43   |

| Bonding Methods For Beam Leads                  | 45   |

| Bond Testing                                    | 55   |

| RELIABILITY                                     | 59   |

| MECHANICAL DESIGN CONSIDERATIONS                | 62   |

| Thermal Resistance                              | 62   |

| Dimensional Standardization and Recommendations | 64   |

| SUMMARY AND CONCLUSIONS                         | 70   |

| Introduction                                    | 70   |

| Passivation                                     | 70   |

| Metallurgy                                      | 70   |

| Substrates                                      | 71   |

| Processes                                       | 72   |

| Bonding                                         | 72   |

| Major Future Development Areas                  | 73   |

| REFERENCES                                      | 75   |

| BIBLIOGRAPHY                                    | 83   |

#### BEAM LEAD TECHNOLOGY

By T. W. Fitzgerald, K. Anderson, V. J. Barry,

N. Cerniglia, J. Coulthard, J. DiMauro,

H. J. Ramsey, and R. Tonner

GTE Laboratories, Incorporated

### SUMMARY

Although the acceptance of the beam lead approach to microcircuit interconnection since its introduction in 1964 has not been as widespread as early predictions would have it, nevertheless there has been considerable effort expended in its application and further development. It is the purpose of this paper to present the present status of the beam lead technology in the areas of Metallization Systems, Surface Passivation, Processing, and Bonding. Additionally, there are sections concerned with the important subject of reliability, and recommendations on the design considerations of the beams themselves.

Much of the subsequent work has been concerned with the practical aspects of the method and, generally, few successful substitutions have been used for the original Titanium-Platinum-Gold metallization in combination with the silicon nitride surface passivation.

A large effort has been expended in the study of bonding beam leads. Many techniques, mostly some form of thermocompression bonding, have been developed for bonding these devices to suitable substrates, and here again gold beams are preferred to those of other metals, including aluminum. The testing of these joints is not entirely satisfactory at this time owing to the lack of a suitable nondestructive test method.

While preliminary data on the reliability aspects are highly encouraging, sufficient information has not been accumulated to accurately establish the hierarchy of values between beam lead and other forms of flip-chip or standard flying wire interconnections. Many of the people actively involved in beam lead work anticipate, perhaps expectedly, that the reliability of beam leaded semiconductor devices with silicon nitride passivation will be at least equal to the best performance previously obtained in any high reliability device and without a hermetic package in the traditional sense.

More recent developments have been concerned with the application of beam leads to surface sensitive devices such as MOS transistors and insulated gate field effect transistors.

## INTRODUCTION

While the beam lead approach is but one of several methods of flip-chip technology which have been developed in recent years, it is the purpose of this study to present a critical evaluation of the current developments in the beam lead technology, including device passivation and protection from hostile ambients. Discussed, in turn, are metallization systems and their performance and evaluation, substrates and their qualities as determined by geometry, bonding and thermal properties of beam lead devices, the present status of reliability information, and, finally, a section on the recommended mechanical design considerations for these devices. A complete discussion of the processing used in the preparation of silicon nitride passivated beam lead devices is also included. The final section presents the conclusions drawn from the study and our recommendations as to areas where additional developments are likely to be required.

#### BEAM LEAD MATERIALS

## Metallurgical Systems

Introduction. — Beam lead technology was originally developed by Lepselter et al. (ref. 1) to improve the reliability of conventional wire-bonded silicon planar devices. Since the prime consideration, at that time, was the selection of a metallizing system that would be compatible with silicon planar technology, practically all of the beam leaded devices reported to date are silicon planar devices ranging from simple discrete devices to complex arrays and integrated circuits. There have been, however, several attempts to modify the original beam lead metallurgy to make it compatible with other semiconductor materials. The only successful attempts reported in the literature have been with germanium and gallium aresenide.

The first device to be beam leaded, other than silicon, was a germanium Esaki diode reported by Davis and Gibbons in 1967 (ref. 2). This device had gold-plated beams on sputtered titanium and platinum but used arsenic-tin contacts. A similar device was later reported by Schultz (ref. 3) in 1969 using the identical metallurgy but utilizing a different processing technique.

The first successful attempt to beam lead gallium arsenide was reported by Lynch and Furnanage (ref. 4) in 1967. This device was an electroluminescent array utilizing the conventional beam lead metallurgy but using zinc-gold for P contacts and tin-gold for N contacts.

Since these two devices are the only other semiconductor devices reported in the literature, the rest of this report will concern itself with silicon beam lead technology.

It has been generally accepted throughout the industry that a good beam lead metallurgical system must meet the following conditions:

- (1) Resistivity less than  $10\mu$ -ohm-cm.

- (2) Good adhesion to silicon and dielectrics.

- (3) Low contact resistance to P-type and N-type silicon.

- (4) Does not form degrading intermetallics between metal layers.

- (5) Resists electro-migration.

- (6) Resists normal or electrochemical corrosion.

- (7) Readily deposited and defined.

- (8) Introduces a minimum amount of damage or surface instability while being deposited.

- (9) Be compatible with multilevel processing.

- (10) Beams must be ductile and easily bonded.

Since the original Lepsetter beam lead metallurgy was reported in 1964, there have been a number of new metallurgical systems reported that claim to be superior because they minimize radiation damage associated with deposition, simplify fabrication, or reduce material and processing costs. While it is true that these systems have desirable characteristics, they generally introduce some other undesirable characteristics which limit their application or decrease their reliability.

Since the properties of a metal demanded by each function vary markedly, it is difficult to find a simple metallurgical system that will satisfy all the requirements. With the exception of the all-aluminum beam lead metallurgy (refs. 5, 6), all other metallurgical systems reported are composed of three or more metals; the contact metal, the bond metal, the diffusion barrier metal, and the beam metal.

The contact metal. — A good contact metal must have high conductivity, low contact resistance, will not degrade at high temperature or high current density, and is easily deposited and defined.

The metals most commonly used for contacts are aluminum, chromium, molybdenum, platinum, palladium, and nickel. Aluminum makes good ohmic contact to P-type silicon and low resistivity N-type as well as performing all of the other functions required. However, as a contact metal, aluminum has some shortcomings, e.g., it dissolves silicon rapidly at high temperatures, which may be augmented by high current densities and it forms rectifying contacts on N-type silicon above 0.1 ohm-cm. Chromium is an excellent contact metal as well as a good bond metal but forms recitfying contacts on P-type silicon over 0.02 ohm-cm. Nickel also makes rectifying contact on high-resistivity Ptype silicon and suffers from degrading intermetallic compounds at high temperature. Molybdenum is a good contact material and has good temperature stability but does form rectifying contacts on high-resistivity N- and P-type silicon, above 0.01 ohm-cm. Of all the metals studied, platinum comes the closest to the ideal contact material. It does, however, have one property that limits its use. Due to its very high melting point, it must be evaporated by electron beam or sputtered so that X-rays are present during the deposition which can cause damage to MOS-type devices. Recently, palladium has been suggested (ref. 7) as a replacement for platinum on MOS devices since it can be evaporated from a tungsten filament thus eliminating any possibility of X-ray damage. Since palladium has similar characteristics to platinum and can usually be etched,\* it may prove to be a better all-around contact metal than platinum.

<sup>\*</sup>Palladium can be etched in concentrated sulphuric acid at 60°C.

Platinum silicide has been formed at  $550\,^{\circ}$ C and at  $700\,^{\circ}$ C with no significant change in contact resistance. The higher temperature is necessary where a thin residual SiO<sub>2</sub> layer may exist under the platinum.

The contact resistances of various metals to silicon, with and without platinum silicide, are presented in Table 1. The deposition techniques reported include filament and electron beam evaporation and dc sputtering and were chosen according to the metals being deposited. While specific processing parameters are not given, the results point to the significant reduction in contact resistance resulting from the use of platinum silicide.

The bond metal. — The bond metal must have two basic characteristics. First, it must adhere to metals, silicon, silicon compounds and dielectrics such as oxides, nitrides, or glass. Secondly, it must not react with any material it comes in contact with in a manner that would degrade the metallurgical system either electrically or mechanically. It is important, therefore, that the bond metal does not diffuse rapidly into either the contact metal or the diffusion barrier metal. Although titanium is being used for most beam lead devices without any serious limitation, there are a number of other metals such as chromium, aluminum, zirconium, and hafnium, which could be considered as bond metals because of their adhesive qualities. Aluminum, in fact, has been used by itself to form a complete beam lead system. This system, however, is limited to low current (< 10<sup>5</sup> amps/cm<sup>2</sup>) and low temperature (400°C). Since all of these beam metals are very active, they are subject to corrosive undercutting during defining; therefore, they must be deposited in very thin layers.

[ref. 8]

| Si Resistivity, | Metal and Metal + PtSi |      |        |      |         |      |         |      |          |                               |

|-----------------|------------------------|------|--------|------|---------|------|---------|------|----------|-------------------------------|

| $\Omega$ – cm   | Al                     | PtSi | Мо     | PtSi | Ni      | PtSi | Cr      | PtSi | Ti       | PtSi                          |

| N-Type Si       |                        |      |        |      |         |      |         |      |          | www.www.wam.welicoclinicolini |

| 0.001           | 0.09                   | 0.02 | 0.08   | 0.02 | 0.02    | 0.02 | 0.03    | 0.03 | 0.01     | 0.01                          |

| 0.01            | 6 (R)                  | 0.1  | 5 (R)  | 0.4  | 2       | 0.3  | 3 (R)   | 0.2  | 4        | 0.2                           |

| P-Type Si       |                        |      |        |      |         |      |         |      |          |                               |

| 0.002           | 0.03                   | 0.02 | 0.06   | 0.03 | 0.02    | 0.04 | 0.04    | 0.04 | 0.01     | 0.01                          |

| 0.04            | 1                      | 0.7  | 3 (R)  | 1    | 4 (R)   | 2    | 8 (R)   | 1    | -        | 0.9                           |

| 0.08            |                        |      |        |      | 45 (R)  | 4    |         |      | AMER WHO | 3                             |

| 0.5             | 20                     | 10   | 80 (R) | 10   | 100 (R) | 20   | 200 (R) | 15   |          | 15                            |

<sup>(</sup>R) indicates rectifying contact.

Diffusion barrier metal. — The function of a diffusion barrier is to prevent the formation of degrading intermetallic compounds between the beam metal and the underlying metals. This metal must be relatively inert, form no undesirable compounds with the metals it contacts, and the beam metal must have a low diffusion rate into it. Since this layer must be thick to minimize pinholes and prevent the beam metal from diffusing through, it must be corrosion-resistant to resist attack during processing and environmental testing. Actual interdiffusion rates for many of the metal combinations used in beam lead systems have not been published. The diffusion constant for gold into platinum,  $7.8 \times 10^{-11}$  cm<sup>2</sup>/sec at 900°C, is an order of magnitude less than gold into palladium,  $1.2 \times 10^{-10}$  cm<sup>2</sup>/sec at 900°C. Palladium, however, has not as yet had the extensive investigation necessary to determine whether any reliability problems due to interdiffusion will arise.

Platinum, palladium, molybdenum, tungsten, nickel, and tungsten-titanium (ref. 9) have all been used successfully in this application. For nonhermetic packages, however, where severe corrosive environments may be encountered platinum is generally selected because of excellent corrosion resistance.

Molybdenum has been used extensively (ref. 10) to fabricate a variety of beam leaded devices. These devices have now been in the commercial market for a number of years with excellent life test data when used in hermetic packages. Molybdenum is also a good diffusion barrier and has the added advantage of being inexpensive and readily defined by chemical etching in the presence of the gold beam, eliminating several costly fabricating steps. Tests have shown molybdenum-gold metallization to be severely corroded in 85°C, 85% R.H. ambients in 48 hours, where platinum-gold metallizations have exceeded 1000 hours in the same atmosphere.

Beam metal. — Since the beam is the contact medium between chip and substrate, special consideration must be given to its compatibility with the substrate metallurgy as well as the chip metallurgy. In general, a beam metal must have the following characteristics:

- (1) Good mechanical strength.

- (2) Easily deposited in thick layers (> 50,000 Å).

- (3) Easily defined by controlled deposition or etching.

- (4) High corrosion resistance.

- (5) Low yield point.

- (6) Coefficient of expansion near to that of silicon or high elongation to overcome mismatch.

- (7) High conductivity.

- (8) Easily bonded.

Gold, aluminum, nickel (ref. 11), and copper are most often suggested as potential beam metals that could be used in conjunction with a variety of bond and barrier metals. Unfortunately, however, many of these metals systems deteriorate rapidly in corrosive environments which are accelerated if the metals are under electrical bias.

Table 2, compiled by L. Terry (ref. 12), shows the effect of electrical bias on some of these metal systems while submerged in a boiling 1% solution of ammonium hydroxide in deionized water. The vehicles used for testing the metals listed were silicon dice upon which had been patterned parallel "dogbone" conductors to which suitable bonded connections were made. A potential of 10 volts was applied to pairs of the strips while chips were submerged in the electrolyte.

TABLE 2

ELECTROCHEMICAL CORROSION TEST RESULTS

| Metal    | Type of Failure           | Time    | Remarks                          |

|----------|---------------------------|---------|----------------------------------|

| Al       | All contacts open         | < 5 min | (_) Terminal somewhat faster     |

| Ti-Pt-Au | Resistance Increase       | > 3 hr  | Au deplates (+) terminal         |

| l i      | į į                       |         | ~                                |

| Ti-Pt    | Slight Resistance Change  | > 24 hr | Au wire bond opened              |

| Ti-Rh    | Slight Resistance Change  | > 24 hr | Au wire bond opened              |

| Cr-Ag-Au | Open (Cr)                 | < 5 min | Cr from under Ag-Au, even with   |

|          |                           |         | glass or Si $_3$ N $_4$ overcoat |

| Ti-Ag    | Large Resistance Increase | < 5 min | Ag corrodes but not removed      |

| Hf-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Ti-Ag-Au | Resistance Increase       | > 3 hr  | Au deplating (+)                 |

| Ti-Mo-Au | Open (Mo)                 | < 5 min | Mo from between Ti and Au        |

| Ti-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Mo-Au    | Open (Mo)                 | < 5 min | Mo from under Au, even with      |

|          | •                         |         | glass overcoat                   |

| Cr-Au    | Open (Cr)                 | < 5 min | Cr from under Au                 |

| W-Au     | Resistance Increase       | 2-3 hr  | W removed≅ same rate as Au       |

| Zr-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Nb-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Ta-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Ni-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| Co-Au    | Resistance Increase       | > 3 hr  | Au deplates (+)                  |

| V-Au     | Open (V)                  | < 5 min | V removed (+) from under Au      |

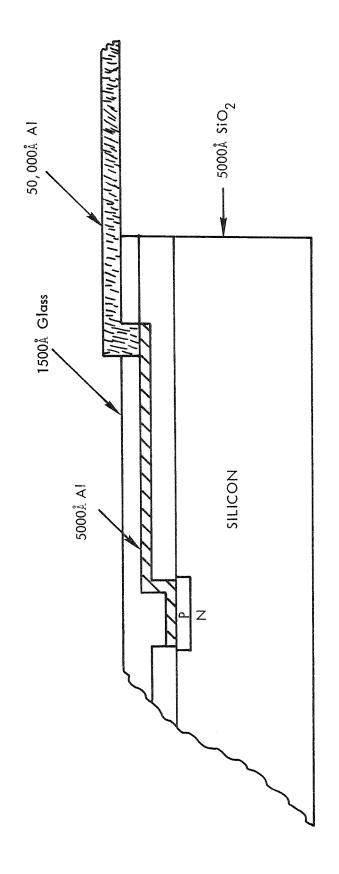

Although the all-aluminum beam lead system has too many restrictions for general use, it does offer a simple, inexpensive metallurgy for low current applications. A typical all-aluminum system as proposed by C. Mai (ref. 6) consists of a conventional integrated circuit on which a layer of silane glass is deposited and windows are opened over the bonding pads (see Figure 1). This is followed by a multiple source deposition of aluminum until a 5- to 10-micron layer is deposited. The aluminum is then defined and the slice thinned and etched through (see processing section). While these devices did not pass environmental testing, they were able to pass storage and operating life tests at low current density. Failure by electromigration can occur at current densities above  $10^5 \ \rm amps/cm^2$ .

Platinum and palladium have not been evaluated as beam metals but they have potential in this application for high-reliability devices which are subjected to very severe corrosive environments. The cost would be higher and the bonding would be more difficult but the thermal expansion mismatch would be less and the corrosion resistance would be far superior to any other metal system.

For most applications, however, gold beams are almost the unanimous choice throughout the industry because of the ease of bonding, ease of fabrication, and relatively high corrosion resistance of the gold beam. While gold on titanium and platinum is preferred by most investigators, there have been some recent reports on gold beams on other metal systems such as aluminum (ref. 6) and molybdenum-aluminum (ref. 13).

Generally, these systems have an oxide layer between the beam metal and the underlying metals. This allows beams to be attached to standard chips since a window can be opened over the bonding pads and the beam metal can make contact to the pad through the window and be insulated from the rest of the metallization by the oxide.

Summary. -- The titanium, platinum, gold beam lead metallurgical system has become the industry standard. The all-aluminum system is interesting because of its low cost and simpler processing but is limited to hermetically-sealed packages and low current, low temperature applications. Palladium may be a possible substitute for platinum because it can be evaporated from a filament eliminating any possible X-ray damage.

## Substrates

Introduction. -- At the present time, the fabrication of beam-leaded devices has been much better defined that the packaging technology with which they are to be used. A number of packaging schemes have been developed for hybridization of discretely packaged semiconductor devices. These technologies are currently being examined for their ability to accept unpackaged beam-leaded components, and new technologies are being developed with beam leading in mind.

Techniques for providing interconnection patterns compatible with beams and the substrates to form the package are discussed in this section.

• 5, 11,

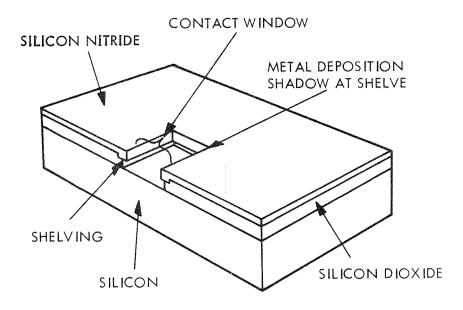

Figure 1. Aluminum Beam Lead System with Separately Deposited Beams

Substrate materials. -- Substrate materials generally fall into two classes for beam leads. Hard substrates, such as ceramics and glasses, are required for high temperature processing, such as screen and fire techniques. Soft substrates, PC boards and other organics, have the advantage of lower costs but lack some of the advantages of the hard substrates. These disadvantages would include poorer thermal conductivity and unsuitability for hermetic sealing. The choice of bonding methods is limited by the inability of this type substrates to withstand bonding temperatures. Some of these substrates, along with their advantages and disadvantages, are discussed below.

Ceramic: Ceramic is probably the most commonly used substrate material for beam-leaded devices. It has the strong advantage of being able to withstand high temperatures and stresses. This property makes all of the beam lead bonding methods practical with ceramic substrates including thermal pulse bonding. It also allows the attachment of heavy external leads and glass hermetic seals. In addition, screen and fire techniques are normally used only on ceramic substrates.

The ceramic most often reported is either 96% alumina (such as Alsimag 664) or 99.5% alumina (such as Alsimag 772). The higher alumina content improves the heat conducting properties. However, the other constituents provide better adhesion for the metals which obtain their adhesive properties on oxides by partial reduction of the oxide. Chromium and titanium are two of these metals.

Surface texture also plays an important role in adhesion. The lower alumina content ceramics are generally supplied with rougher surface finishes (25- $\mu$ in and greater). The rougher surfaces provide a mechanical factor in metal adhesion. This adhesion becomes important when heavy external metal leads are attached. Glazed alumina provides very poor adhesion for external leads, and other mechanical adhesion aids such as resins are needed with glazed ceramic substrates.

In addition to adhesion, surface finish is critical for thin-film components and metallization. A much thicker thin film (2500 Å) is required for electrical continuity across a 25- $\mu$ in surface than would be required for a glazed surface (only a few hundred Å). For this reason, selective glazing has been used on ceramic substrates where both thin-film components and adhesive metal films for external leads are required.

Another disadvantage of ceramic substrates is the lack of surface flatness. This is especially true with glazed ceramic. Undulating surfaces lead to variations in line widths, particularly with photoresist defined patterns where the mask does not come in uniform contact over the entire surface. Projection exposure techniques now being developed in the industry may help solve this problem.

The final substrate size is usually formed by sawing with a diamond fritted wheel. Grooved substrates are available which can be broken into predetermined size. However, since the grooving is done in the green state, the accuracy of the pattern dimensions after firing is not easily controlled.

Glass: Glass substrates do not have the problems of surface finish that ceramics do, and are ideally suited for thin-film work and fine geometry interconnections. However, it is difficult to bond external leads to glass and usually a conductive epoxy resin is used for this purpose.

The two glasses most commonly used are Corning 7059 and Corning 0211, the latter primarily because of its low sodium content. It has been reported (ref. 14) that thin glass substrates (15 mil) result in thermal bonds which deteriorate with time, presumably due to stress relief in the glass. Thermal cycling reduces this problem. Thicker substrates (48 mils) do not show this bond weakening phenomenon.

Organic substrates: The printed circuit board is the most widely used of the organic substrates. However, it has several drawbacks as far as beam-leaded devices are concerned. In the first place, the pattern generation techniques most commonly used are too crude to produce the bonding areas for most beam leads. Secondly, the material yields under heat and pressure making thermal bonding techniques impractical. Ultrasonic bonding such as done with ultrasonic wobble tools may be usable, but this has not yet been established.

Other organic substrates, such as Kapton, are rumored to be under development as substrate materials, but have not yet been reported.

<u>Substrate Metallization</u>. -- The vast majority of beam leads are gold and almost all of the substrate metallization systems reported for beam leads incorporate gold as the metal to which the beams are to be bonded. This eliminates any problems with intermetallics that might arise with other metals. In addition, gold interconnections are desirable because of their excellent corrosion resistance.

However, there are annumber of different methods for deposition and definition of these interconnections.

Vacuum deposited systems: Vacuum deposited gold requires another metal to provide adhesion to the substrate. The most widely used of these adhesive metals are titanium, chromium, and nichrome. Besides providing good adhesion, they are easily defined by etching. These layers are kept thin (100 to 500  $\mathring{\rm A}$ ) to reduce lateral corrosion since they are not required for conduction.

The gold itself is either deposited thick (10,000 Å) or, more commonly, deposited thin (500 to 3,000 Å) and electroplated to the desired thickness, usually about 0.5 mil.

Definition is usually accomplished photolithographically by etching.\* Direct definition by deposition through metal masks has been reported (ref. 15). However, a limit of five mils on pattern size was observed.

<sup>\*4</sup> KI, 1 I, 4 Deionized Water

The vast majority of literature describes deposition of the gold followed by photoresist masking and etching. However, much finer geometry control can be obtained by vacuum depositing the initial gold and adherent metal and plating up the gold through a photoresist mask. The plated gold acts as a mask for the chemical etching of the excess thin film metals. The technique is similar to the chemical definition of beam leads (p.37).

Thick film conductors: Thick film conductors deposited as inks or pastes are used extensively throughout the industry for hybrid circuits. A large variety of inks are available commercially (ref. 16) including many gold pastes which would be compatible with gold beam leads (ref. 17). Ceramic substrates are used for these materials because of the high (750 to 1000°C) firing temperature required. Definition is obtained by either screening or photolithographic techniques.

Screening is the most commonly used method of defining thick films. However, geometry control limits by this technique are marginal for beam leads, although line widths and spaces of 0.002 to 0.005 inch have been reported in the laboratory (ref. 18). The standards recommended in another section (Dimensional Standardization and Recommentation Section) of this report have been set up to allow for screened substrate metallization providing good control of line widths is present. These fine lines were achieved using 325 mesh screens; finer screens resulted in separation of the components of the ink while coarser meshes gave poorer resolution. Metal masks have also been used to produce fine geometries (ref. 19), but the masks have the disadvantages of being expensive and short-lived.

Photolithographic techniques have also been used to obtain finer resolution with thick films (ref. 16). As with etch-defining electroplated gold, this technique is limited by the undercutting obtained on etching thick (0.001 inch) conductors.

In general, the state-of-the-art in thick films limits geometries to 5-mil lines with 5-mil spaces (ref. 20). With this in mind, presently proposed standards call for 10-mil beam spacings. (See Dimensional Standardization and Recommendations Section.)

In addition to gold inks, MoMn interconnections have been successfully used with plated gold for conductivity and bonding. A major advantage of this system is that the MoMn can be used in multilayered ceramics for multilevel interconnections.

Decals: Decals are lithographic interconnection patterns on paper or plastic sheets which can be transferred to substrates by either pressure, liquid, or heat transfer processes. A typical metallization system would be moly-manganese with an organic binder. Discontinuities in the patterns which occur during the firing for binder removal step are a major defect mechanism with the decal process (ref. 21).

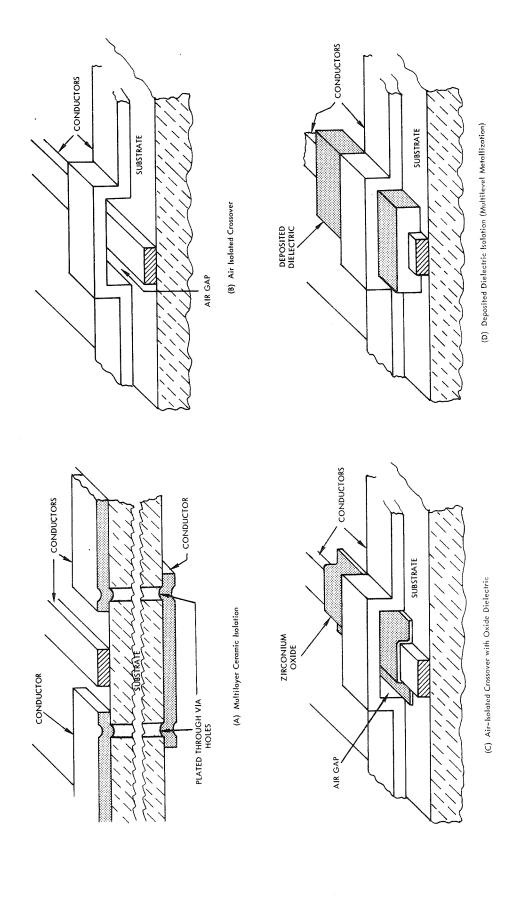

<u>Multilevel interconnections.</u> -- Multilevel interconnections and crossovers are presently being obtained by three techniques: Multilayered substrates, air isolated crossovers, and deposited insulators (See sketch in Figure 2).

Figure 2. Interconnection and Isolation Methods

Deposited insulators: Deposited thin-film insulators, such as those used on semiconductors, have not found wide use on substrates. Deposited insulators for crossovers have generally been screened materials. Thick insulators are required to minimize pinholes and capacitive coupling. Photoresist has been used as a binder and definitive media for small geometry insulating pads but this process is still in the experimental stages.

Multilayered ceramic: Multilayered ceramics have been proven as a multilevel interconnection system for beam leads (ref. 22) but are expensive. Screen and fire metallizations along with via-hole plating are used for this technology.

Air isolated crossovers developed at Bell Labs (ref. 23) are not true multilevel interconnections in that all interconnections are on one plane. However, fairly complex metallizations are possible with this technique. The Bell process includes a base gold plated interconnection system, a copper plated spacer, gold pillars plated up through holes etched in the copper, and a gold plated microbridge connecting the pillars. The copper is subsequently etched away to form an air gap.

A similar process (ref. 24) has been developed and uses a gold plated base interconnection pattern, a copper plated spacer, and a second gold plate to thicken the base interconnection and form the bridges.

A thin-film Ti-Zr alloy can be used with the air isolated crossover which, when oxidized, forms a protective insulator over the bottom lead of the crossover in case a bridge is deformed during subsequent processing. The air isolated crossover has the advantage of being capable of much finer geometries than those formed by screening techniques. The process is also being used directly on integrated circuit chips.

Conformal coatings. — With nitride passivated beam-leaded integrated circuits, hermetic sealing for the sake of preventing chip degradation is unnecessary. However, for many applications where either the die is not nitrided or where protection of external metallization is required, conformal coatings (ref. 25) have been developed both as a sealant and for mechanical protection. More specifically, it is used for reducing thermal resistance as covered elsewhere in this report. A first layer of silicone resin 0.5 to 1.0 mils thick is used as a moisture barrier. This resin is also chosen for its adherence to the die and its ability to penetrate under a face-down mounted die. It must be capable of performing under extended periods at elevated temperatures (1000 hours at 300°C). A second layer of RTV silicone rubber 5 to 10 mils thick is used for mechanical protection not only for the die but also to protect external leads.

Beam-leaded substrates. -- A substrate and interconnection system for mounting conventional chips with connections made by beams formed on the substrate has been developed at Lincoln Laboratory, M.I.T. In this process, holes to accommodate individual die are punched in green ceramic. After firing, the holes are filled with glass to form a continuous surface. The substrate is then metallized and interconnections are formed, including beams extending over the glass. The glass is subsequently

etched away leaving the beams extending over holes. More recently Riston (E.I. Dupont), a photosensitive sheet material has been used to bridge the etched holes in the glass. The beam leads are formed over the Riston, which is later removed either by dissolution or cleaning in a plasma asher. Reliability problems, caused by metal thinning at the step at the bridge edge, can be experienced unless due care is exercised in the preparation and developing of the Riston film. (ref.26).

Individual integrated circuit die are first mounted on molybdenum tabs (for heat sinking) which are then mounted in predetermined locations on a blank ceramic. The beam-leaded ceramic is then joined to the ceramic containing the die with an epoxy so that the beams are aligned with the bonding pads on the die. Bonds are then made either by thermocompression or by ultrasonic techniques.

Both aluminum and gold interconnection systems have been used for beam-leaded substrates. Aluminum has the advantage of compatibility with the aluminum metallization on conventional die. However, the vacuum deposition of adequately thick aluminum beams is a drawback compared to the relative ease of depositing thick gold beams by electroforming. Gold beams can be thermo-compression bonded to standard aluminum chip metallization, but the possibility of Al-Au intermetallic formation exists if high temperature processes, such as cap sealing, take place after the bonds have been formed. The process also lends itself to solder coating beam leads where suitable metal pads have been provided on the device surface to permit reflow soldering to be used as a chip connection technique.

Recently, polyamide films, particularly Dupont's Kapton, have been used instead of ceramics. Multilevel interconnections have been formed by using successive layers of polyamide and connecting layers by bonding beams in windows.

### **PASSIVATION**

#### Introduction

Passivating dielectric films perform an important function in any planar device structure. This is to protect device junctions which terminate at the surface from ambient moisture and ionic impurities along with maintaining stable device characteristics during field and temperature stress. The following criteria should be met by a passivating film:

- (1) High dielectric strength, and high resistivity to allow for stable device performance.

- (2) Favorable thermal expansion properties that do not cause high degree of thermal expansion mismatch with semiconductor materials.

- (3) Chemical stability, and uniform high density structure which is impervious to contaminants such as ionic impurities, moisture, or organics.

- (4) Good interface properties to minimize interface charge instabilities especially in MOS where it governs critical device performance and reliability.

- (5) Ease of etching using semiconductor photolithographic processing.

The most universally used dielectric in planar technology is silicon dioxide. It is deposited in the majority of cases thermally by oxidizing the semiconductor silicon material. Although its properties have been optimized by improvements in processing, such as high purity furnace muffles, improved cleaning procedures, and the use of dry oxidizing ambients, it has inherent disadvantages in its lack of resistance to ion migration (1000 Å of SiO $_2$  penetrated by Na in 20 minutes at 300°C) of alkali metals and permeability by moisture and certain dopant materials. These would include gallium and aluminum.

These facts conflict with the emergence of MIS devices and the need for improved reliability of the dielectric gate, and have caused accelerated investigations of other gate and passivating materials. Silicon nitride, when used as a complement to SiO<sub>2</sub>, has been found to remedy many of the shortcomings of the oxide alone. Silicon nitride films have not completely replaced silicon dioxide but are deposited over silicon dioxide and readily complement the interface state properties of silicon dioxide.

#### Silicon Dioxide Passivation

The fact that silicon dioxide has a high permeability toward impurities is by far the most serious drawback of this universally used dielectric. Due to its porous structure, impurities migrate quite readily through silicon dioxide (ref. 27). Sodium ions (the most common ionic impurity) are highly mobile in silicon dioxide. With the addition of applied fields ( $10^5$  to  $10^6$  volts/cm) cations will drift in the direction of the field. This field migration of impurities is accelerated greatly by elevated temperatures. The movement of this ionic charge toward the silicon-silicon dioxide interface and the subsequent buildup and termination of an ionic-induced field within the semiconductor material results in degradation of both bipolar and MOS devices.

The presence of cation impurities within the silicon dioxide layers will alter the underlying semiconductor material, depending on the type, in the following ways:

- (1) Accumulation Within an N-type region, electrons will be attracted to the surface due to positive ions in the oxide near the silicon-silicon dioxide interface. This field attraction of majority carrier electrons will cause an excess carrier concentration or "accumulation" at the surface.

- (2) Depletion The same positive ion contaminants in the oxide over a P-type region will repel holes, thus causing a reduction of majority carrier concentration at the surface or an effective lowering or "depletion" at the surface.

Both accumulation and depletion of the semiconductor surfaces alter the carrier concentrations from their bulk values, and hence affect those device parameters which are surface related, e.g., low current gain, reverse leakage current, breakdown voltage, etc. (ref. 28).

(3) Inversion - This effect results from deep depletion of majority carriers (in P-type silicon holes) at the surface. This would be caused by a very high field induced by a large ionic contamination level near the siliconsilicon dioxide interface. With the positive ion concentration, the attraction of the minority carriers to the surface can be high enough to exceed that of the majority carriers (holes). When the concentration of electrons at the surface exceeds that of holes, this surface region changes type. This condition is known as "inversion". This situation will cause the well-known "channeling", or excess current flow, between N-regions previously isolated by a P-region.

In bipolar device structures and integrated circuits, this ionic oxide contamination causes degradation of junction characteristics due to the previously mentioned accumulation, depletion, or inversion effects. Accumulation generally results in lowered breakdown voltage. Inversion, as mentioned, causes increase in leakage current.

Interface charge increases surface recombination velocity which, in turn, lowers transistor gain, especially at low currents.

In MOS transistors, the effect of positive ion contamination can alter the gate threshold voltage (that is, the voltage to induce a channel from source to drain). This can be readily demonstrated in an N-channel enhancement mode device. In order to turn the device on, positive gate bias is applied which attracts minority electrons to the surface until the surface is inverted and a conductive channel is formed. Thus, if positive ionic contamination is present, the positive gate bias will cause these ions to drift toward the silicon-silicon dioxide interface. This ionic charge will attract additional electrons to the silicon surface and terminate this charge at the ionic charge center even after bias is removed. The result of this effect is an unstable threshold voltage which varies with the level of contamination as well as voltage, temperature, and time to which devices were subjected.

Historically, contamination problems in planar devices have been met by first assuming the planar devices would be protected by its own silicon oxide masking. This, combined with protective "glassivation" together with hermetic encapsulation, gave a large measure of reliability improvement. The impetus of MOS technology has developed ultraclean low interface state density silicon oxides. This development has required processing improvements that have proved difficult to maintain, especially in production.

Treating the silicon dioxide surface with  $P_2O_5$  prior to metallization has improved the stability of silicon dioxide. The phosphorus is deposited from a vapor on the silicon dioxide in a diffusion furnace at temperatures from 900°C to 1100°C for times of the order of five minutes. The phospho-silicate glass forms on the device surface as a result of this procedure. It has been established in our laboratories, as well as through the industry, that this treatment will stabilize the silicon dioxide by gettering ionic impurities distributed through the oxide as well as gettering to some degree additional contaminants from the external environment. Depending on the oxide quality and the  $P_2O_5$  treatment (temperature and time), phosphorus can also neutralize sodium ion contamination near the silicon-silicon dioxide interface (ref. 29).

In MOS integrated circuits, uncontaminated  ${\rm SiO}_2$  is susceptible to external contaminants even with a phosphorous glass coating. Phosphorous glass has limitations on its usefulness because of polarization effects which have been found to be the cause of some device instability in MOST's.

## Silicon Nitride Properties

Impetus has been given to the development of silicon nitride processing mainly for two important reasons:

(1) Unlike silicon dioxide, silicon nitride has been found to be a barrier to field-enhanced ( $10^5$ V/cm) sodium diffusion even at elevated temperature ( $400^{\circ}$ C).

(2) The highly dense nature of silicon nitride has made it possible to consider eliminating hermetic packaging. This would be replaced with junction sealed hermetic chips. This, of course, will improve the reliability of plastic packaging and increase the use of chips in an unpackaged form.

It also can work as a mask against gallium and aluminum diffusion for which silicon dioxide is not effective (refs. 30, 31) and as a dielectric composite makes feasible development of nonvolatile MOS memory elements (ref. 32).

In addition to silicon nitride's extreme resistance to ionic contaminants, its properties include a high degree of chemical inertness, high temperature strength, extreme hardness, and thermal shock resistance. In fact, silicon nitride does suffer from cracking due in part to its extreme hardness. This cracking does not present any problem unless the thickness of deposit exceeds 2000 Å.

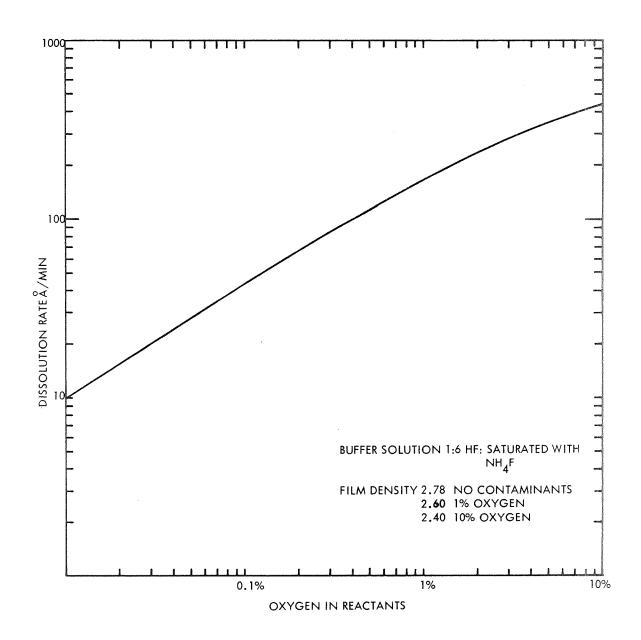

Table 3 presents a comparison of properties of silicon dioxide and silicon nitride. It has been found that thin film deposited silicon nitride has physical, chemical, and electrical properties that vary quite markedly depending on deposition process and conditions. In general, device passivating silicon nitride can be monitored by its etch rate in buffered hydrofluoric acid solution. Details on the process conditions and measurements are to be found in the section on Processing.

Silicon nitride would appear to be a logical replacement for silicon dioxide since it is an improvement over silicon dioxide as both a diffusion mask and as a passive dielectric. Its shortcoming is the instability of the Si-Si<sub>3</sub>N<sub>4</sub> interface. Such structures exhibit charge instability due to tunneling and trapping at the interface. Hysteresis in surface behavior and the charge instability are eliminated by the use of a silicon dioxide-silicon nitride composite film. Thin layers of thermally grown silicon dioxide covered with a film of silicon nitride eliminates these problems. This composite takes advantage of the excellent diffusion barrier of silicon nitride and the ordered interface properties of clean annealed silicon dioxide (ref. 33). Since silicon nitride does not have as high a dc resistivity as silicon dioxide, this composite system also improves the resistivity over silicon nitride structures alone (ref. 34).

The higher dielectric constant of silicon nitride in a thin silicon dioxide-silicon nitride composite has the beneficial effect of lowering the gate threshold voltage of IGFET structures. In the past, not only the instability of gate threshold voltage but interface problems with other logic elements have limited the growth of MOS devices. The use of silicon nitride with the proper thickness of silicon dioxide (200 Å to 400 Å) results in lower gate threshold voltages compatible with logic levels used with TTL and other bipolar logic circuits. Thus, besides the expected improvement in surface stability inherent in the dense silicon nitride dielectric, MOS technology has received impetus from the improved device performance of SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub> gated MOS structures.

TABLE 3

SUMMARY OF PHYSICAL PROPERTIES

[ref. 35]

|                                                                              | ${ m SiO}_2$                                    | $^{\mathrm{Si}}3^{\mathrm{N}}4$           | $^{\mathrm{Si}_{3}\mathrm{N}_{4}}$                 | Si-O <sub>x</sub> N <sub>y</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              | Amorph.                                         | Cryst.                                    | Amorph.                                            | Amorph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Melting Point (°C)                                                           | ~1600                                           | ~1900                                     | Manaday salamed                                    | Marie and the second se |

| Density g cm <sup>-3</sup>                                                   | 2.2                                             | 3.4                                       | 3.1                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Index of Refraction                                                          | 1.46                                            | 2.1                                       | 2.05                                               | 1.60-1.88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dielectric Constant                                                          | 3.8-3.9                                         | 9.4                                       | 7.5                                                | 4.77-6.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dielectric Strength<br>V cm <sup>-1</sup>                                    | ~5 × 10 <sup>6</sup>                            |                                           | ~1 × 10 <sup>7</sup>                               | ~5 × 10 <sup>6</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Infrared Absorption Band $\mu m$                                             | 9.3                                             | 10.6                                      | 11.5-12.0                                          | 9.3-12.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Energy Gap (e.v.)                                                            | 8                                               | 3.9-4.0                                   | ~5.0                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Thermal Expansion<br>Coeff./°C                                               | $5.6\times10^{-7}$                              | 3.0-3.5<br>× 10 <sup>-6</sup>             |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Thermal Conductivity cal cm <sup>-1</sup> sec <sup>-1</sup> °C <sup>-1</sup> | 0.0032                                          | 0.067                                     |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

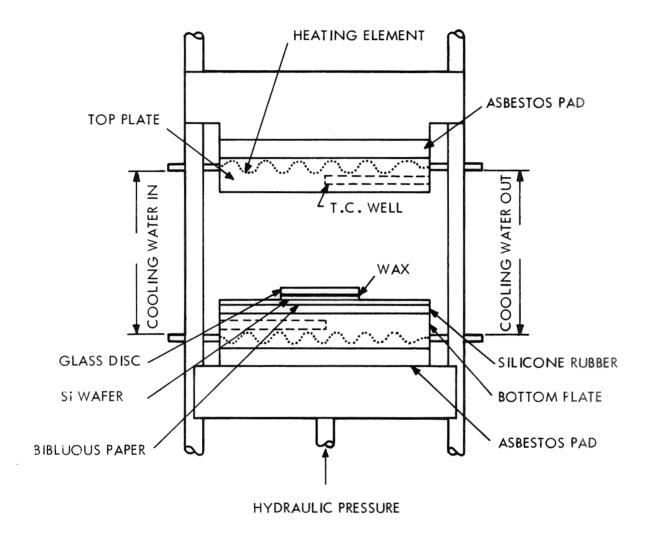

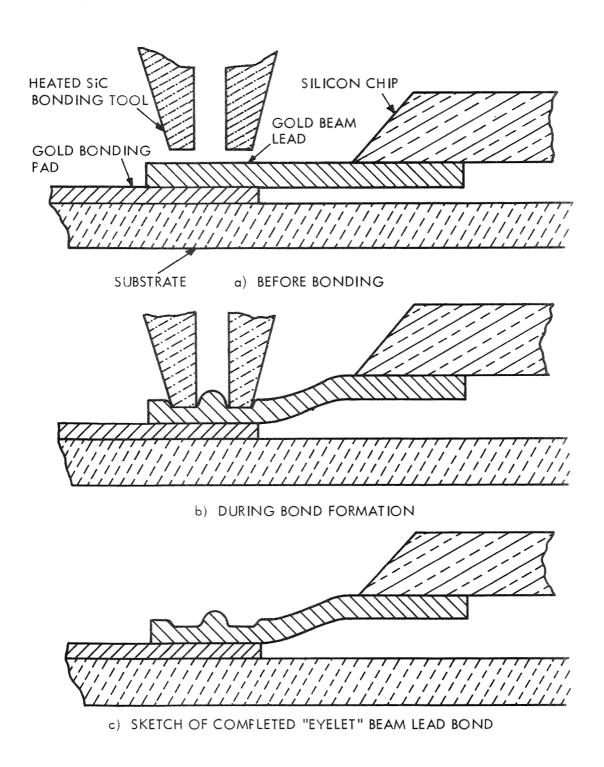

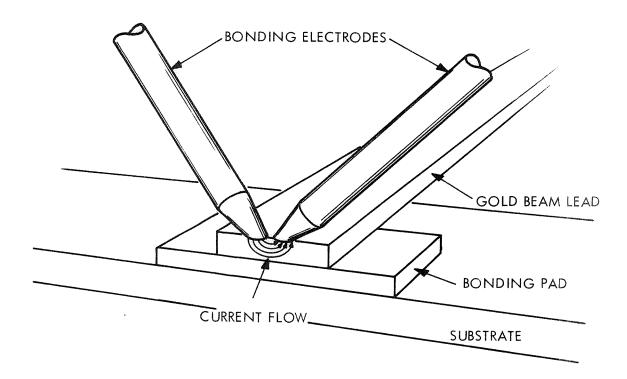

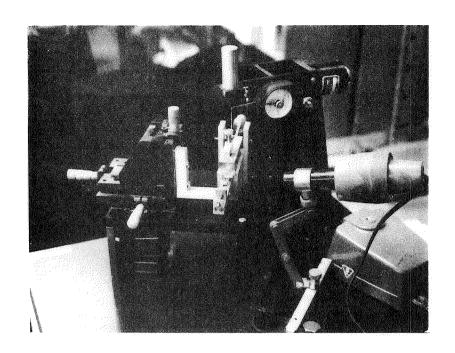

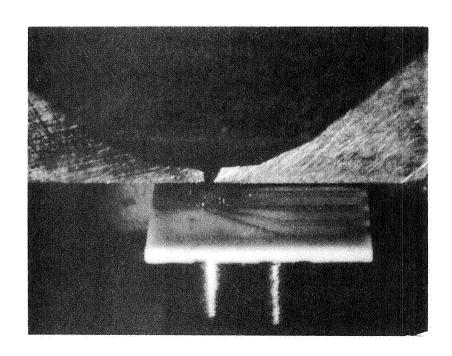

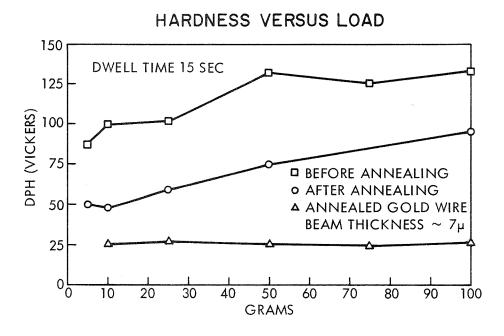

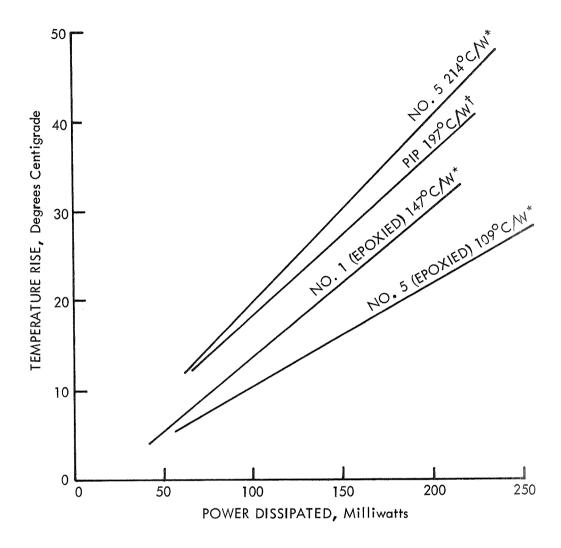

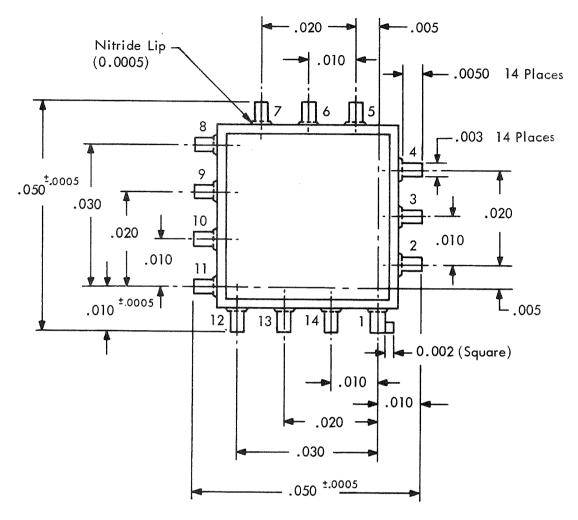

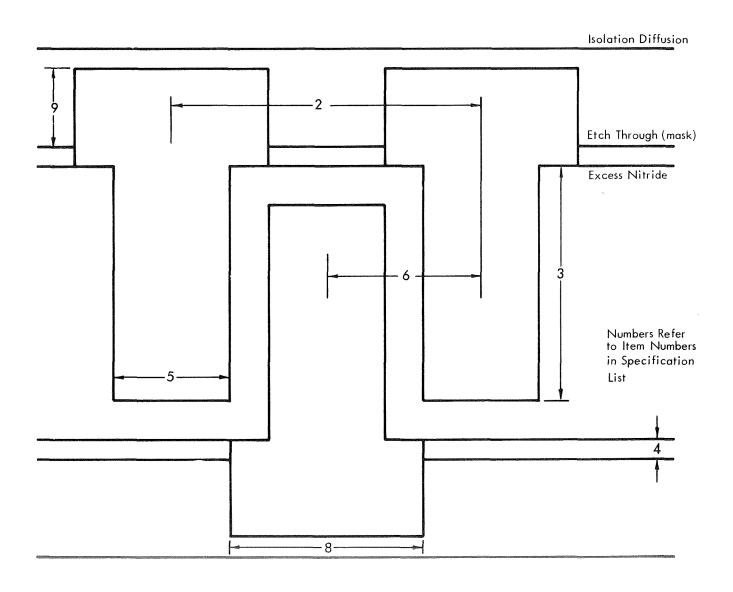

| dc Resistivity ohm-cm<br>at 25°C<br>at 250°C<br>at 300°C<br>at 350°C         | 10 <sup>14</sup> - 10 <sup>16</sup><br><br><br> | 10 <sup>15</sup><br><br>~10 <sup>13</sup> | ~10 <sup>14</sup><br><br><br>~2 × 10 <sup>13</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |