July 1

20 copies

NASA TECHNICAL MEMORANDUM

NASA TM X-58063 Volume III

NA SA TM X-58063 Volume 111

PROCEEDINGS OF THE SPACE SHUTTLE INTEGRATED

**ELECTRONICS CONFERENCE**

NASA Manned Spacecraft Center Houston, Texas May 11-13, 1971

| 1.71 - 35052                      | N71-35068  |

|-----------------------------------|------------|

| (ACCESSION NUMBER)                | (CODE)     |

| E (NASA CR OR TMX OR AD NUMBER)   | (CATEGORY) |

| NATIONAL TECHNIC INFORMATION SERV |            |

| 1  | Report No TM X-58063 - Volume III                                                                                                                                                      | 2 Government Access     | ion No       | 3 Recipient's Catalog                | ) No        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|--------------------------------------|-------------|

| 4  | Title and Subtitle                                                                                                                                                                     |                         |              | 5 Report Date                        |             |

|    | PROCEEDINGS OF THE SPACE SHUTTLE INTI<br>ELECTRONICS CONFERENCE                                                                                                                        |                         | EGRATED -    | 6 Performing Organiz                 | zation Code |

| 7  | 7 Author(s)                                                                                                                                                                            |                         |              | 8 Performing Organization Report No  |             |

|    |                                                                                                                                                                                        |                         |              | 10 Work Unit No                      |             |

| 9  | Performing Organization Name and Address                                                                                                                                               |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              | 11 Contract or Grant                 | No          |

| 12 | Sponsoring Agency Name and Address                                                                                                                                                     |                         |              | 13 Type of Report ar<br>Technical Me |             |

| '` |                                                                                                                                                                                        | Administration          |              | rechnicar Me                         | smorandum   |

|    | National Aeronautics and Space Administration Washington, D.C. 20546                                                                                                                   |                         |              | 14 Sponsoring Agency                 | Code        |

| 15 | Supplementary Notes                                                                                                                                                                    |                         |              |                                      |             |

|    | Held at the NASA Manned Spacecraft Center, May 11-13, 1971                                                                                                                             |                         |              |                                      |             |

| 16 | Abstract                                                                                                                                                                               |                         |              |                                      |             |

|    | The symposium encompassed five specific categories within the general category of space shuttle integrated electronics. The five categories are published in three volumes as follows: |                         |              |                                      |             |

|    | Volume I - Electronics Overview and Guidance, Navigation, and Control II - Instrumentation and Power Distribution and Communications III - Data Systems                                |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    | •                                                                                                                                                                                      |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      | ,           |

| 17 | Key Words (Suggested by Author(s))  18 Distribution Statement                                                                                                                          |                         |              |                                      |             |

|    | Unclassified - unlimited                                                                                                                                                               |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

|    |                                                                                                                                                                                        |                         |              |                                      |             |

| 19 | Security Classif (of this report)                                                                                                                                                      | 20 Security Classif. (c | f this page) | 21 No. of Pages                      | 22 Price*   |

|    | Unclassified                                                                                                                                                                           | Unclassified            | <u> </u>     | 398                                  |             |

## PRECEDING PAGE BLANK NOT FILMED

#### FOREWORD

As a follow-up of the Space Transportation System Technology Symposium held at the NASA-Lewis Research Center, Cleveland, Ohio, July 15-17, 1970, a series of discipline-oriented conferences was planned, with the Office of Advanced Research and Technology/Office of Manned Space Flight (OART/OMSF) Space Shuttle Integrated Electronics Technology Conference being held at the NASA Manned Spacecraft Center, Houston, Texas, May 11-13, 1971. The Conference goal was to present a timely review of the status of Space Shuttle technology in the major areas of electronics and power systems for the benefit of the industry, Government, university, and foreign participants considered to be contributors to the program. In addition, the Conference offered an opportunity to identify the responsible individuals already engaged in the program. The Conference sessions were intended to confront each presenter with his technical peers as listeners, and this was substantially accomplished.

Because of the high interest in the material presented, it is being published essentially as it was presented, utilizing mainly the illustrations used by the presenters along with brief words of explanation. The document is unclassified, and each of the authors has determined that his paper can be published in this manner. This publication is aimed at revealing the substance and significance of the work in this manner now, rather than in a more refined form much later.

## PRECEDING PAGE BLANK NOT FILMED

## CONTENTS

|                                                                                                                                                                         | Page   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| DATA SYSTEMS                                                                                                                                                            |        |

| MODULAR SPACEBORNE PROCESSORS  W. R. Wadden and H. S. Zieper, RCA Advanced Technology  Laboratories; J. M. Gould and R. Asquith, NASA-Marshall Space  Flight Center     | . 3 🗸  |

| FAULT-TOLERANT COMPUTER DESIGN FOR SPACE SHUTTLE Irving Goodman, General Electric                                                                                       | . 27   |

| CONFIGURATION ALTERNATIVES FOR DATA BUS SUBSYSTEM INTERFACE UNITS Edward Chevers and William Mallary, Manned Spacecraft Center                                          | . 47   |

| DATA BUS CONCEPTS FOR THE SPACE SHUTTLE John R. Lane, General Electric Company                                                                                          | . 71   |

| DATA BUS TO SERVICED EQUIPMENT AND SENSOR INTERFACE Berry S. Yolken, TRW Systems                                                                                        | . 87 🗸 |

| SELF-SEQUENCING DATA BUS TECHNIQUES FOR SPACE SHUTTLE Robert H. Hardin, Martin Marietta Corporation                                                                     | . 111  |

| SOFTWARE DEVELOPMENT AND VERIFICATION TECHNOLOGY H. Trauboth and B. Hodges, NASA-Marshall Space Flight Center                                                           | . 141  |

| SYNCHRONOUS EXECUTIVE AND BUS CONTROL SOFTWARE FOR REDUNDANT DATA MANAGEMENT SYSTEMS T. E. Daly, TRW Systems                                                            | 179    |

| HAL, A COMPILER LANGUAGE FOR SHUTTLE Fred H. Martin, Intermetrics, Incorporated                                                                                         | 191    |

| DESIGN OF CRT DISPLAYS FOR THE SPACE SHUTTLE  G. F. Conron, Norden Division of United Aircraft Corporation                                                              | 221 🗸  |

| ONBOARD DATA STORAGE FOR SPACECRAFT  J. E. Holthaus and L. B. Gangawere, Westinghouse Defense and Space Center                                                          | 251    |

| MULTI-PURPOSE DISPLAYS FOR SPACE SHUTTLE  A. P. Yeager and Z. G. Tygielski, IBM/FSD Electronics Systems  Center; and F. L. Holmes, IBM/FSD Electronics Systems Center . | 289    |

| SELF-TEST TECHNIQUES FOR REDUNDANT DATA MANAGEMENT SYSTEMS Myron Kayton and H. S. E. Tsou, TRW Systems Group                                                            | 309 Î  |

|                                                                                                              | Page |

|--------------------------------------------------------------------------------------------------------------|------|

| UNIFIED TEST EQUIPMENT A CONCEPT FOR THE SHUTTLE GROUND TEST SYSTEM Edgar A. Dalke, Manned Spacecraft Center | 329  |

| A STANDARD LANGUAGE FOR TEST AND GROUND OPERATIONS Henry C. Paul, NASA-John F. Kennedy Space Center          | 355  |

| SOLID STATE SEQUENCER SYSTEM David E. Leck, Martin Marietta Corporation                                      | 359  |

| ATTENDEES OF THE SPACE SHUTTLE INTEGRATED ELECTRONICS TECHNOLOGY CONFERENCE                                  | 379  |

~

1

ಲು ಭಾ

## MODULAR SPACEBORNE PROCESSORS

W. R. Wadden, H. S. Zieper

RCA Advanced Technology Laboratories Camden, New Jersey

J. M. Gould, and R. Asquith

NASA-Marshall Space Flight Center Huntsville, Alabama The challenge which confronts computer system designers in developing the data processing configurations for support of the next generation of space missions is to design a mechanized capability which provides a spectrum of graded application throughput while delivering a significantly higher level of system availability than ever realized in the past. This capability must be available without serious penalty to the spacecraft environment (in terms of heat and power loads) and must not usurp undue volume and weight allowances. Such system realizations are now both feasible and economical with the use of the direct outgrowths of prior NASA-sponsored technological development in large-scale instrumentation (LSI) technology, supportive design automation aids, and system-level explorations. This paper presents a review of the LSI COS/MOS technology base upon which such a highly reliable baseline computer system is being developed. Extensions of the design technique are directly applicable to wide application areas where customized digital logic subsystems are required. Ongoing developments not only assure growth in the computer capability, but also will lead to the reduction to practice of the newer forms of MOS technology and packaging, thus assuring a state-of-the-art technology time line in the future.

### THE TECHNOLOGY BASE

The MOS technology offers a natural response to the needs of the digital spacecraft hardware designer. Its many forms offer:

- 1. High packing density

- 2. Low standby power

- 3. Ability to modulate active power according to application speed needs

- 4. Ready means of device modeling and characterization

- 5. Appropriate levels of circuit speed

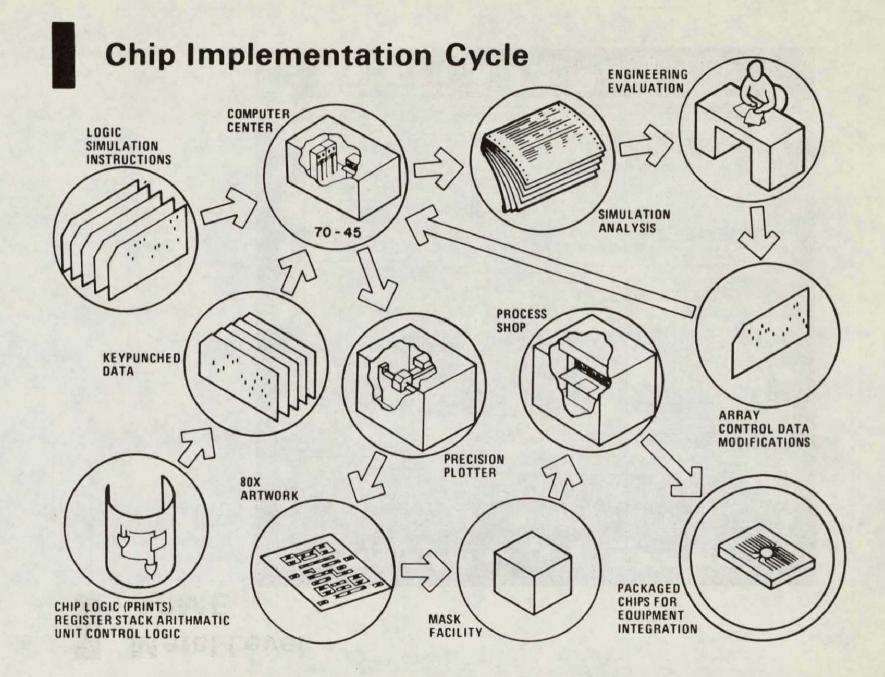

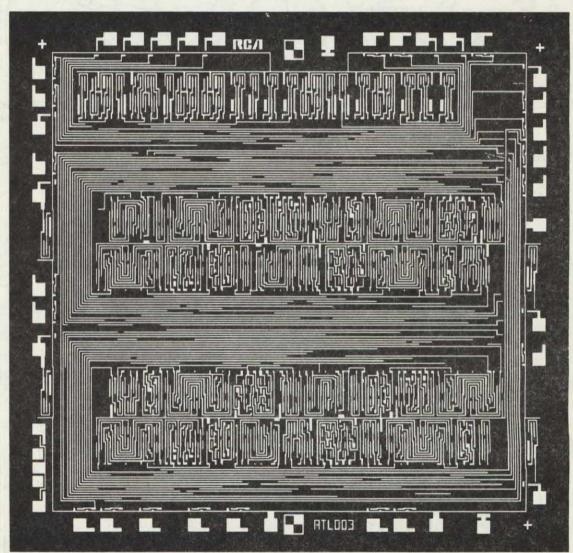

A design automation system provides the mechanism by which the designer can readily translate system needs into economical hardware. Input to the system is by partitioned logic diagrams which the software automatically translates to a customized functional circuit layout; provides a series of user-oriented, confidence-building intermediate reports; accepts user-desired modifications; and produces the magnetic tape output required to drive an automatic precision artwork generator. After plotting, the artwork is ready for the mask fabrication,

4

wafer processing, part packaging, and testing cycle. The software system permits both P- and C-MOS LSI arrays to be implemented with totally arbitrary functional logic keyed to the specific user needs. The only limits are chip size and package pin count, both of which are constantly expanding with the rapid maturing of the technology. The design aid system places at the user's disposal the high efficiency of truly custom-made circuit layout coupled with the fast-computer-paced turn-around cycle for such costly and error-prone actions as placement, routing, and artwork command creation. It is thus practical to implement system improvements in logic and to quickly take advantage of new technology availability such as the SOS and silicon gate variants. A particular advantage is the ability to implement reliable, economical switching mechanisms that permit subsystem redundancy for reliability enhancement of system operation. Logic is presented to the design and system in a form consistent with the usual manner of logic detail, that is, partitioned to a chip level by user-convenient functions and sketched with conventional symbols.

The first step in the implementation cycle is to translate the user logic into a standard cell notation and prepare the input data decks (a matter of 1 or 2 hours of coordination effort followed by a short keypunch session). Translation is accomplished by a simple reference to a circuit catalogue. Each page contains the logic data and provides circuit configuration, timing, and the cell size which is used in estimating chip size. This catalogue contains a wide variety of standard logic circuits (cells) in both P- and C-MOS forms. As will be discussed shortly, the catalogue, which represents a technological library, is expandable by the user so that the new needs which will arise in the future can readily be included in the library set.

Once the logic has been prepared for input, the software generates an optimum placement of circuits for array fabrication; routes the interconnecting wires, using metal and P tunnels; and configures the emerging chip in an approximately square shape. A series of reports is generated which permits the user engineer to evaluate his degree of satisfaction with the software-generated chip configurations. For those cases where pads should be relocated or special critical leads must be run in particular ways, a manual intervention capability is available. In some cases, human intervention can effect significant chip size reduction by specific wiring relocation. Again, the manual intervention feature permits the user to exercise his options. This intervention procedure permits the ideal blend of large-scale automatic action while taking advantage of the unique pattern recognition capability of the human to meet those special cases where a computer algorithm is not maximally effective.

After acceptance by the user, the proposed chip configuration is translated to a tape containing the artwork commands, and the layout is plotted. Interface exists to both GERBER and D. W. MANN precision plotting systems. By means of simple control parameters, plots can be made at any convenient scale. Typically GERBER plots are made at 80%; D. W. MANN plots are at 10%. With the current state of the art, chips with the feature shown in the following table are practical.

| Parameter              | C-MOS                 |

|------------------------|-----------------------|

| Number of pins         | 16, 24, 40            |

| Active area            | 150×150 mils          |

| Total chip area        | $170 \times 170$ mils |

| Number of devices      | 400 to 800            |

| 2-input NOR equivalent | 80 to 200             |

A key notion referred to in the preceding text is that of the standard logic circuit (cell). This is a circuit designed such that its topology conforms to a set of predetermined rules that have been chosen to blend technology parameters and software needs together in an optimum fashion. Since all circuits are of a constant height, a simple computation of total cell length permits the user to estimate chip size. The variation is a function of the wiring complexity. It is within the cell area that the digital-to-analog system takes advantage of the area efficiency of custom layout. Each cell is designed to compress the specific function into the minimum area required to meet pad and fanout drive constraints.

A key point must be presented with respect to part qualification. The circuits are:

- 1. Designed once and stored on a tape library

- 2. Subjected to extensive characterization during design

- 3. Based on the basic process design geometry rules

Once the <u>wafer</u> process and packaging scheme is space qualified, any manner of logic array can be qualified since the circuit designs are fixed, tested, and replicated at each and every use with exact faithfulness. There is simply no variation of circuit geometry from spot A on a chip to spot B on a chip. Variations in circuit actions are based solely on process tolerance, not artwork.

Clearly, the design of LSI arrays requires the highest confidence in design philosophy and detail. Two key supports to the design automation system discussed previously are a circuit level and a gate (logic) level simulation. The circuit simulation, FETSIM, is the key to the cell design method and is used to develop the majority

of circuit behavior data supported by appropriate laboratory evaluation. Inputs to the FETSIM program are: process parameters, model characteristics, and exercising waveforms. The output data provide use, full times, et cetera.

Correlation between the prediction of simulation and laboratory evaluation was obtained by implementing a test vehicle. This laboratory in miniature not only confirmed the simulation predictions, but also served as a process evaluation and comparison vehicle. It is to be noted that the ability to model and simulate the MOS circuit accurately is the key factor that permits an unlimited variety of circuits to be included in the cell library - the limit being user need.

Because the cell library is really a carefully maintained file of geometric data, it is a direct matter for the user to add a new cell. Such an addition is made to implement specific functions that will provide a specific area saving, speed improvement, or simply a function replicated many times as local logic islands. Starting with a circuit sketch, a geometric layout is made on a grid medium. The coordinates are keypunched, checkplots made, the design reviewed, and a library addition made. FETSIM is liberally used to make optimum selection of device sizes needed to match system specifications.

Specific to the logic level of design, validation of function is accomplished by means of the LOGSIM simulator. This simulation permits the designer to create in software a laboratory version of the logic, to exercise the laboratory version in any form that is desirable, and to observe the action at any series of points of interest. The program analyzes any static or dynamic configuration, permits specific timing to be assigned to elements based on system use, and provides user-oriented reports with appropriate levels of data reduction. Input to the program is exhaustively checked for clerical accuracy in order to help build confidence in design validity.

Programs at the algorithm and subsystem levels provide the final layer of design support needed to implement digital systems.

### GENERAL CONSIDERATIONS

Spaceborne processors will be employed to implement a wide range of tasks such as:

- 1. Display support applications

- 2. On-board control of mission experiments

- 3. Monitoring of system condition

- 4. Local display interfacing

- 5. Navigation

- 6. Dedicated experiment control

- 7. Communication control

- 8. Data-link format conversion

- 9. Overall format conversion

- 10. Overall analysis and system control

- 11. Environment control

Such processors are expected to be components in the full spectrum of spacecraft from small, unmanned (e.g., TIROS) configurations to the large systems typified by an orbiting space station. Depending on the nature of the spacecraft, a single processor or a federated complex of such systems acting in consort with a large central multiprocessor may be required.

Technology, power budgets, and system organization interact to define the range of capability attainable for single-processor systems utilizing the current state of the COS/MOS technology. The processing speed lower limit of 10,000 operations per second indicates either that system clock speed has been reduced drastically or that serial machine organization is used. At a processing speed of 100,000 instructions per second, machine organization is parallel with clock rates in the 1- to 2-MHz region.

Φ

Analyses conducted to date show that for the throughput toward the low end of the spectrum, 500 to 1000 words of memory permit single dedicated tasks to be implemented. At the higher processing speeds, more tasks can be implemented, but additional storage is required. Current state-of-the-art technology will permit the designer to reach processing speeds of 200,000 operations per second if the power budget is appropriately modified and the machine organization suitably enhanced. For those applications where the small real-time system structure is still appropriate, a higher level of total system processing capability can be obtained by linking a number of microprocessors together in a network structure. In such a system network, the central control processor (which may indeed be a large-scale multicomputer) directs the total system and contains the large software base associated with large-scale operating systems oriented toward large file control. The multicomputer will contain massive operating systems, validation systems, and total resource allocation programs which implement the required fail-safe modes of operation such as subsystem task reassignment. Each of the local task processors then is assigned a small set of dedicated tasks to implement. The communication bus is used to pass status data and interim system reports upward in the chain of data management software. Such a system structure permits local task reassignment in the event of a single task subsystem failure. Because the federation of processors is in reality a "loosely coupled" structure, the net aggregate of capability of N task processors can be higher than that achieved in a multiprocessor connection of an equivalent processor capability. Such a federated network is not intended to eliminate the multiprocessor, rather it is intended to provide a complementary ability to do dedicated, relatively unsophisticated local tasks.

Another way to broaden the range of system capability that can be implemented in a single microprocessor is to extend the functional capability coded within a single instruction. A specific illustration of this technique is to implement a branch control feature within each instruction. Such capability, for example, permits an ADD instruction to be implemented with a built-in test for the nature of the result, and a branch made under specified conditions. This idea can be extended in sophistication to allow index control as well as to provide for combinations of such tests. The improvement in speed capability comes by virtue of the lack of need for staticizing time for the branch instructions, with the additional possibility of simultaneous branch algorithm execution, thus reducing the time for total function execution. System structures like this have been demonstrated to be effective in a family of real-time computers.

To meet the evident need for a family of computer systems tailored to specific levels of system performance a generalized system structure (the SUMC organization) has been evolved which:

- 1. Is modular at the sub-byte level

- 2. Facilitates realization of a variety of specific architectures

- 3. Permits availability of a wide gradation of functional capability

- 4. Takes advantage of the capabilities of MOS LSI technology

#### COMPUTER PARTICULARS

The connections of versatility and reliability are modular organization and a firmware implementation technique for control structures. With these key concepts as a base, a variety of system architectures can be implemented by using a common base-level machine organization, and the spectrum of system reliability techniques can be overlayed to yield the total system availability factors needed for advanced space missions.

The heart of the machine organization is a modular, generalized data path configuration. Typical of the generalized features provided by this structure are:

- 1. Dual, cascaded adders for high-speed address calculation

- 2. Transfer paths designed to implement multiple-bit multiplication, division, and specialized arithmetic operations

- 3. Partitioning at the sub-byte level so that user-desired word lengths may be efficiently handled

- 4. Requirement of only three chip types for implementation

- 5. Logic structures that match advances in memory technology

- 6. Efficient means of implementing central processor unit (CPU) mechanized input-output with a variety of interface widths for those systems where separate input-output programs are not warrented

Supporting this data path are a scratch pad memory unit, a two-level microprogram control unit, and a large main memory subsystem. The interface to the user environment is a real-time interrupt system and a set of input-output capabilities featuring both channel and programmed type.

Central to the concept of a real-time system structure is the priority interrupt feature. The capability of the LSI processor provides for servicing of a multiplicity of programs on a priority basis. The primary purposes of the priority-interrupt system are to eliminate the need for program-controlled scheduling and status testing on input-output transfers, and to segregate programs on an execution-priority basis.

The complete set of indicator flags is examined, simultaneously with the execution of each instruction, to determine which program demanding attention had the highest priority. When the currently active program has the highest priority of those demanding attention, the program proceeds without interruption. Otherwise, the system automatically transfers, at the completion of the current instruction, to the program with the highest priority.

During the priority-interrupt cycles, the machine logic ensures that the address of the next instruction of the interrupt program is saved in its instruction-location counter. Because the register complement (including the status, program counter, and input-output channel registers) is located in a scratch pad memory and is replicated for each interrupt level, there are no programming constraints on the application software. When all the higher priority demands are satisfied, control returns to the interrupted program, and the latter proceeds oblivious of the interruption. In this way, the priority-interrupt feature enables the data processor to interleave a number of different programs.

Programmed input-output routines for the LSI processor are generally short and often consist of a single instruction. Once the data have been transferred to memory, suitable programs are called to process the new information. The various input-output and data-handling routines are assigned different priority levels; therefore, the programmer need not perform periodic tests for the arrival of data. The priority-interrupt system automatically activates the proper program to process the new data which have been transferred into the memory by other programs.

Because of these considerations, assignment of relative priority among the various input-output programs and devices is principally based on the allowable waiting time between data transfers. Computing programs are assigned lower priorities than those of input-output programs, and the priorities may be assigned arbitrarily, within this constraint, by the user. The lowest priority program, automatically executed when the flag register is cleared, is usually a self-check routine which automatically exercises and tests the computer during idle time.

This type of input-output operation provides a simple, low-throughput transfer mechanism particularly suited for background level application modules (in particular, communication between processors connected in a multicomputer network where the interrupt mechanism provides a natural asynchronous control technique). Provision for large-scale data transfers is made by means of a selector channel configuration.

The simultaneous input-output operations are performed with the CPU processing on a cycle-steal basis to the main memory. Channel command words are set up by the program prior to executing an I/O instruction. For each data transfer between the main memory and the peripheral device, the control words stored in scratch pad memory are accessed and updated. When the total amount of data requested by the program have been transferred, the peripheral device will generate an interrupt indicating that the desired transfer has been completed.

The complete input-output transfer is performed under read-only memory (ROM) control by using two channel control registers. Channel control register I (CCR I) contains the input-output command and the main memory address of the next data to be transferred. Channel control register II (CCR II) contains the physical address of the peripheral device (obtained from the I/O instruction) and the remaining count of data yet to be transferred.

Once the two control registers are set up in scratch pad memory, the input-output operation is initiated with a START DEVICE instruction. After initiation, the peripheral device will generate a service request when it is ready to transfer data. The CPU checks for the presence of a service request upon the completion of an instruction execution. If one is present, the microprogram control will jump to an input-output service routine prior to executing the next instruction. At any time, the input-output operation can be halted by the execution of a HALT DEVICE instruction.

As presented in the succeeding discussion on expandability, this basic channel structure can be replicated to provide massive data throughput capability. The basic architecture of the demonstration baseline is compatible with current third-generation structures. The baseline is a 16-bit system using a balanced subset of this family of architectures.

The demonstration vehicle is implemented to provide a variety of methods in which the capability of the CPU may be increased. Such expansion may be accomplished by several hardware additions, use of firmware, and the normal use of software.

The baseline capability may be directly enhanced by hardware additions which:

- 1. Increase the main memory to a maximum of 65,000 words possible (2<sup>28</sup> words possible with a 32-bit interface)

- 2. Expand the data path width

- 3. Provide a faster ROM and less scratch pad cycle time

- 4. Increase the number and width of the scratch pad and ROM words

- 5. Increase the number of user interrupt levels

- 6. Expand the width of the input-output interface and add to the number of trunks

- 7. Supply floating-point and field instructions

For specialized architecture variants, the data path configuration can be expanded in increments, although the most direct change to maintain compatibility with third-generation architecture would be a doubling of a data path. Use of the baseline logic and system structure is unchanged; only the number of chips is increased. Current design of the timing structure of the baseline permits changes in scratch pad and ROM timing to be made, each of which will provide a system speedup. This independence permits advances in LSI memory technology to be taken advantage of in the most cost effective manner.

By increasing the size of the local scratch pad memory, the programming power of the system is increased, and the number of interrupt levels available to the user is increased. The combination of these provides real advantages in complex real-time programs. Expansion of the input-output interface, culminating in the inclusion of an independent input-output processor module, permits the DV vehicle to be expanded to meet the total needs of an advanced space station complex.

Several levels of firmware modification provide yet another dimension of baseline growth. These are:

- 1. Extended precision algorithms using the 16-bit data path

- 2. Extended repertoire

- 3. Specialized functions such as square root, e<sup>X</sup>, sin, cos, et cetera

- 4. Diagnostic and recovery features

For any size data path, such additions are made easily for extended precision by adding ROM words. Inclusion of floating-point and field-organized instructions will require one or two new control chips in addition to more ROM.

Extensions of the system to include diagnostic and recovery features will require chip modification and new chips and will represent the more advanced capabilities which can be added.

# System Structure

# Metal Level APME

# SUMC Parameters

| TYPE OF CPU       | DIGITAL, STORED PROGRAM,        | TYPĮCAL SPĘEDS        | RX ADD 3 μSEC                   |  |

|-------------------|---------------------------------|-----------------------|---------------------------------|--|

|                   | SYNCHRONOUS BINARY,             |                       | RX MPY 8 µSEC FULLY INDEXED     |  |

|                   | PARALLEL STRUCTURE              | •                     | BC 3 μSEC                       |  |

|                   |                                 | , <u>,</u>            |                                 |  |

| INSTRUCTION FORMS | FULL SPECTRA 70, RCA SERIES 2-7 | MPX CHANNEL RATE      | 2.6 x 10 <sup>6</sup> BYTES/SEC |  |

|                   | AND SYSTEM 360/370              |                       |                                 |  |

|                   | NONPRIVELLEGED COMPATIBLE       | SELECTOR CHANNEL RATE | 5 x 10 <sup>6</sup> BYTES/SEC   |  |

|                   | A 414.                          | ,                     | ,                               |  |

| DATA FORMATS      | 16/32/64/128 BIT ORGANIZATION   | , MAIN MEMORY ORG     | 4096 WORDS/MODULE               |  |

|                   |                                 | ,                     | (2 <sup>28</sup> WORDS MAX)     |  |

| ARITHMETIC FORMS  | EDACTIONAL DINADY DECIMAL       |                       | (2 HORDS MAX)                   |  |

| ANTIMIETIC PONIIS | FRACTIONAL BINARY, DECIMAL,     | <b>~</b>              |                                 |  |

|                   | BYTE (ASCII) AND FLOATING POINT | CONTROL TYPE          | ROM-PLANNED FOR EMULATION       |  |

|                   |                                 |                       |                                 |  |

| I/O TYPE          | CHANNEL COMMAND ORIENTED        | REGISTER STOCK        | 16 GENERAL REGISTERS/LEVEL      |  |

|                   |                                 |                       |                                 |  |

| INTERRUPT TYPE    | USER CONTROLLABLE,              | SIZE                  | 300 IN <sup>3</sup>             |  |

| *3                | 16 INDEPENDENT LEVELS           | WEIGHT                | 10 LB CPU                       |  |

|                   | PER CPU                         | POWER                 | 15 WATTS )                      |  |

# Major System Features

- 16/32 bit word formats

- Spectra 70 non privileged opcodes

- 32 bit main memory

- ROM control scheme

- Data path modularity from 16 bits in 4 bit increments

- Add on floating point option

- Add on byte handling option

- Add on decimal option

- Provision to add specialty instructions (e<sup>X</sup>, SINX, etc.)

- Multicomputer option

- Natural multiple precision modes

- Independent I/O processor capability

- Growth to total R215 software systems

#### PART II

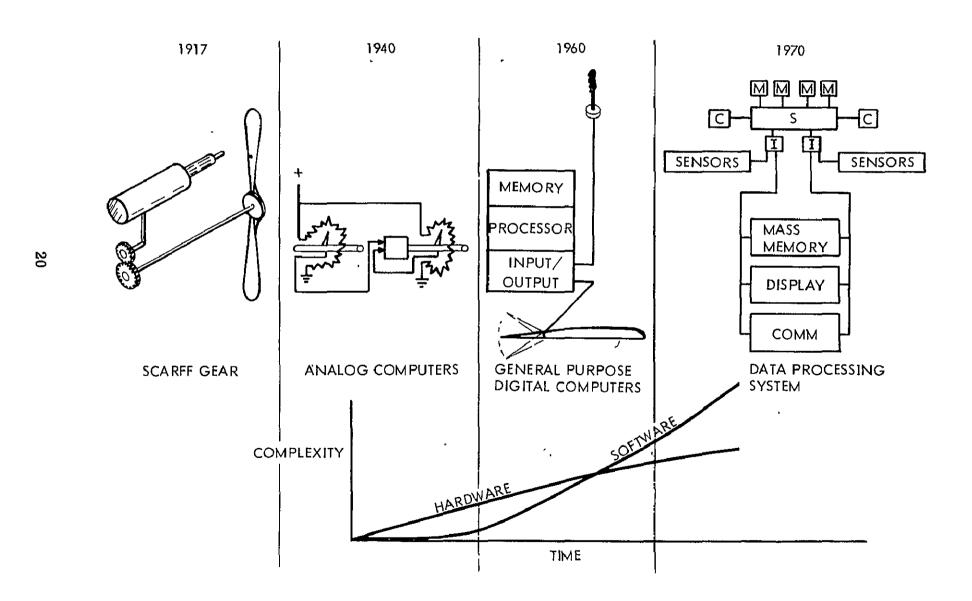

## AIRBORNE COMPUTER TECHNOLOGY

Advances in integrated circuit technology in the 60s has made possible the fabrication of general purpose, stored program, digital computers of small size and weight suitable for airborne applications. With these computers, it has been possible to solve problems for a variety of applications using standard hardware configurations with custom designed software. This departure from the previous practice of custom designing hardware for each new problem has shifted the emphasis in the complex and time consuming aspects of system design from the hardware design to the software design.

Further advances in component technology in the areas of medium and large scale arrays make possible far more sophisticated computer architectures for airborne and spaceborne programs in the 70s thereby permitting significantly more difficult problems to be addressed. The attendant increased complexity of software design and validation is cause for concern in project planning particularly in the case of the Space Shuttle where performance goals are in excess of anything previously attempted in airborne or space environments. Clearly the problem of software development must be addressed at the early stages of baseline specification.

## **Airborne Computer Technology**

## APPROACH TO SOFTWARE DEVELOPMENT

The requirement for autonomous operation of the Space Shuttle imposes on the computer software the management functions of autòmatic checkout, mission planning and mode control, error management and configuration control of redundant subsystems, and communications management in addition to guidance navigation and flight control. Clearly a large scale software effort is indicated.

To execute the software development in a timely manner at low cost and risk requires the application of software skills and disciplines that are state-of-the-art in industry. Also, previous experience on large software projects must be utilized to avoid repeating old mistakes. Specifically, the single factor that contributes most to software failures is attempting to do too much too soon with insufficient resources: Other factors that create problems are the tendency to underestimate the problem during the early stages and the failure to provide for enough expansion in memory and processing capability to accommodate the total problem as it becomes defined.

Flexibility, then, should be the single most important feature of the Space Shuttle computer/software baseline. Consistent with this approach is the selection of a general purpose operating system as the baseline software structure for the shuttle management functions. The operating system functions include the executive with multiprogramming capability, data management, display management, file/query management, error management, and system support modules. For the initial capability, the baseline has a separate minor executive for guidance, navigation, and control that operates in parallel with but under control of the prime executive. This separation of tasks by major categories of management and real time control functions simplifies the design of the system software and the design and verification of the application software.

# Approach to Software Development

LARGE-SCALE

**PROGRAMMING**

**EFFORT**

### SCOPE OF TASKS

GUIDANCE AND NAVIGATION

FLIGHT CONTROL

DISPLAY CONTROL

DATA PREPROCESSING

CONFIGURATION MANAGEMENT

EXPENDABLES MANAGEMENT

MISSION PLANNING

ERROR DETECTION AND RECOVERY

### REQUIRES MODERN OPERATING SYSTEM

MULTIPLE USERS UNDER SINGLE EXECUTIVE EFFICIENT MANAGEMENT OF RESOURCES WELL DEFINED USER INTERFACES EXTENSIVE TEST AND SIMULATION

### OPERATING SYSTEM SCHEDULES

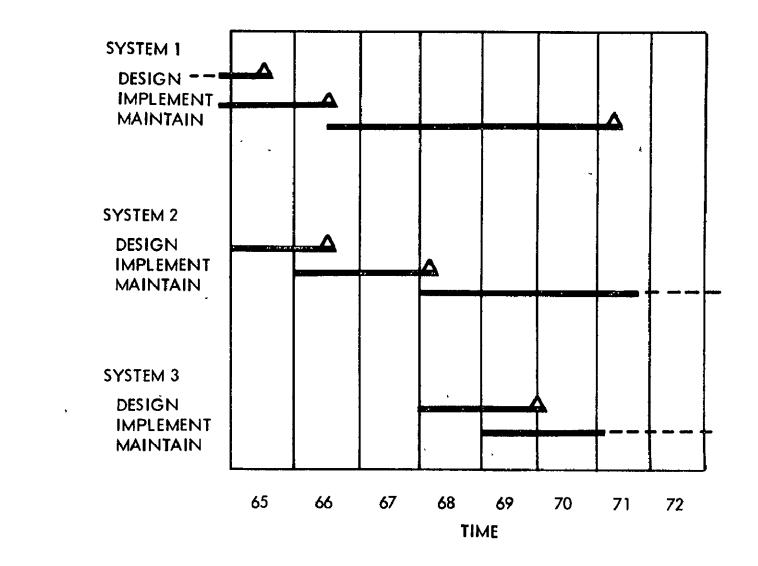

To illustrate the problems associated with the development of a complex operating system, the development schedules for three commercial operating systems developed for the same computer system are shown. Typically, a period of 1 to 2 years is spent in initial specification and design, an additional 1 to 2 years in implementation and test, and then the system is released. At regular intervals, the system is upgraded to incorporate corrections of program errors in the previous release and additions of new features or improvements. The complexity and performance of the operating system is increased in a significant way each time a new system is introduced but the total process is one of gradual evolution to increased capability.

These schedules point out the urgency in getting software development started early and suggest the value of gradual evolution to total capability with usable operating systems of increasing complexity available as required during development and operational phases of the Space Shuttle.

24

### DUAL JOB STREAM BASELINE

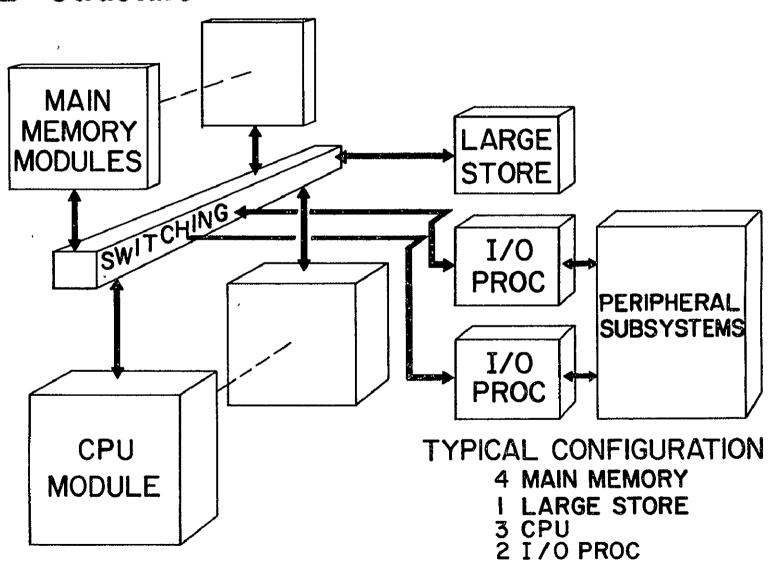

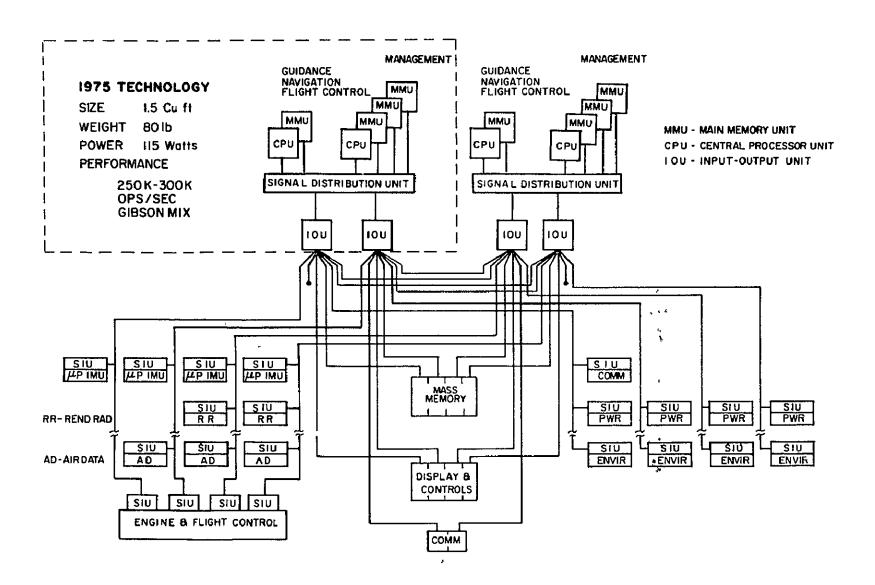

An approach to the implementation of the data management functions for the Space Shuttle is shown which features a centralized computer complex of modular design. The total processing load is pre-partitioned into dual job streams of nearly equal peak load with each job stream assigned a central processor unit. One processor is assigned guidance, navigation, and flight control functions. The other processor is assigned management functions such as mission planning, mode control, display and resource management, communications, data storage and retrieval and checkout.

The centralized approach permits the computer system to make use of common spare units to satisfy the reliability requirement of fail operational, fail operational, fail safe with the attendant reduction in total number of units required to implement the system compared to a distributed computer approach.

The approach to redundancy is to provide redundancy at the unit level (CPU, MMU, IOU) in such a way as to permit the functional use of the redundant units, specified under program control, to be total duplication of the function of a principal unit or to share the total processing load with another identical unit and have the total system performance degrade as units fail, retaining a minimum essential level of capability up to a fixed number of failures.

The baseline computer depicted is the RCA 215 which is totally compatible with the RCA Spectra line of commercial computers, thereby capturing the total system and support software from the Spectra line. Another advantage of total compatibility with a major commercial computer system is that application software can be designed, tested, and validated using commercial computers and transferred directly to the space computer, thereby significantly reducing development time and costs.

## **Dual Job Stream Baseline**

26

N71-35054

## FAULT-TOLERANT COMPUTER DESIGN

FOR SPACE SHUTTLE

Irving Goodman

General Electric Utica, New York

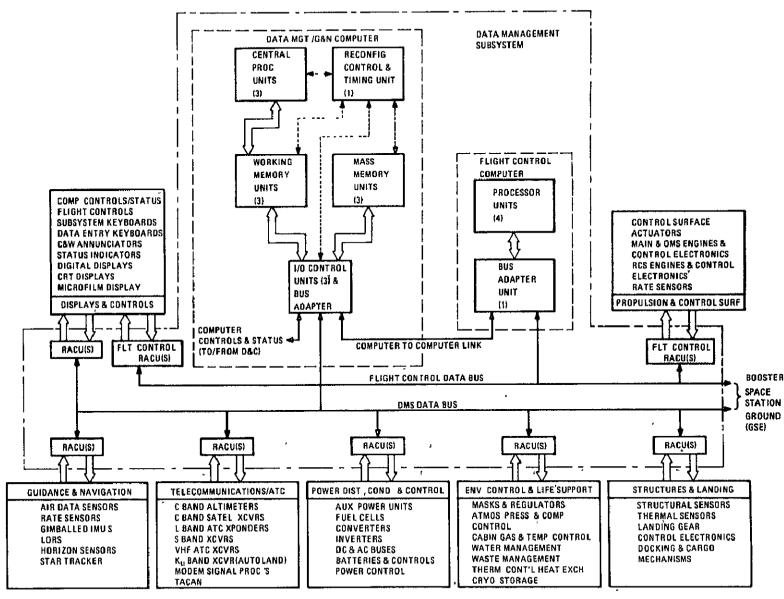

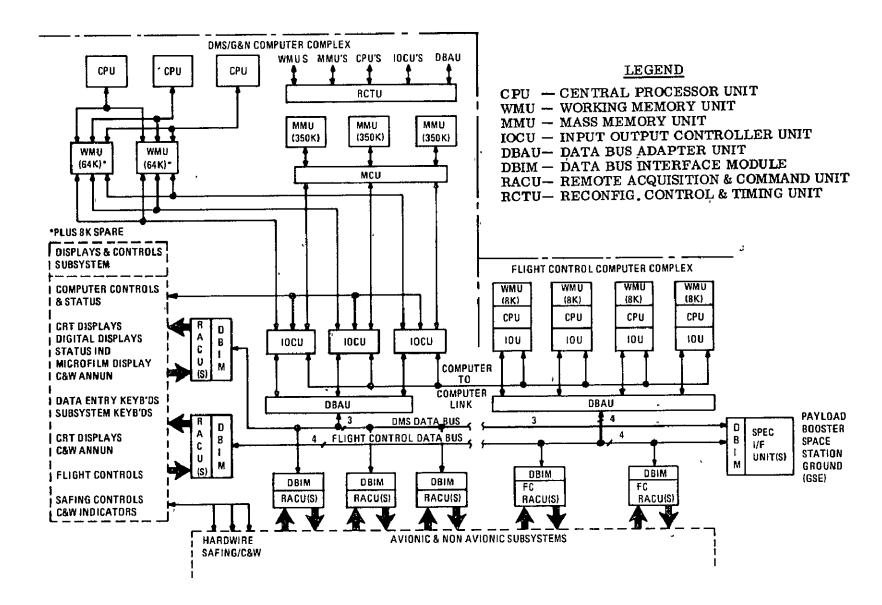

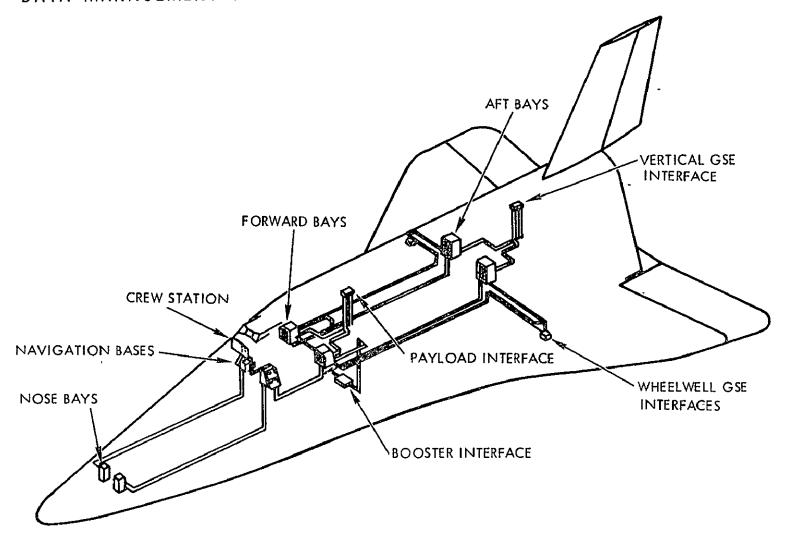

#### BASELINE AVIONICS SYSTEM

This chart is shown primarily to indicate the hardware scope of the Data Management Subsystem within the SSS Avionics System. Design of the DMS for fault tolerance must consider:

- . Solution rates, computation speeds, and memory capacities

- . Required speed of error detection/isolation and error recovery

- . Nature and criticality of computational and checkout functions for all mission phases

- Geographical distribution/location of avionics and non-avionics subsystems serviced by the DMS

- Man/machine interaction speed and capacity.

- . Flight safety and abort capability needs

- . Degree of autonomy

The tools used by the DMS designer to achieve fault tolerance with these considerations are:

- . Reliability and redundancy

- . Architecture for hardware/software modularity and interaction

- Economical balance between hardware/software fault detection and error recovery configuration control

These considerations and tools will be reviewed in more detail in the following charts.

2

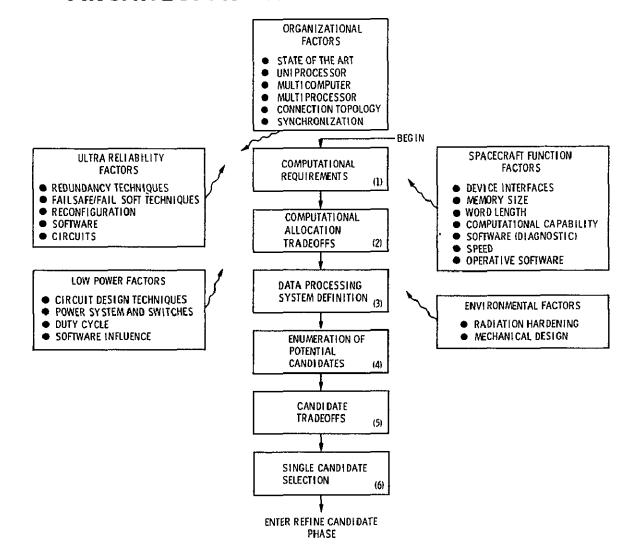

#### ARCHITECTURE SOLUTION STUDY FLOW

Selection of candidate computer organizations for Space Shuttle encompasses utilization of many disciplines and applying a satisfactory tradeoff methodology. The diagram highlights many of the factors which impact the candidate selection. Selection starts with assessing the state of the art and the basic standard configurations, such as the uniprocessor, multicomputer, multiprocessor and ascertaining their relevance in meeting computational requirements. (Box 1). Standard interconnection topology networks are similarly assessed.

A computational allocation tradeoff (Box 2) is initiated. Its objective is to minimize hardware/software complexities by sharing the load through the use of centralized and decentralized regional computers.

The Data Processing System (Box 3) is finally arrived at by combining and weighting all the relevant factors, most of which are enumerated in the Study Flow Figure.

Several candidates are acceptable (Boxes 4, 5, 6), so a "fine tuning" process is needed. Establishing rejection thresholds such as utilizing a power-speed figure of merit helps to eliminate candidates. It is worth noting that most of the selection criteria enumerated will be used again during refining of the design of a selected candidate.

## ARCHITECTURE SELECTION STUDY FLOW

31

## COMPUTER ORGANIZATION SIMPLEX CANDIDATES

Shown here are some of the types of computer required/available performance parameters which must be considered in DMS design for fault tolerance.

### COMPUTER ORGANIZATION SIMPLEX CANDIDATES

HIGH PERFORMANCE G & N/DMS CENTRAL COMPUTER

(32 BIT MACHINE)

• 30 - 150 LSI BIPOLAR CHIP CONSTRUCTION (4K MEMORY)

• 15 - 20 LBS WEIGHT

● 400 - 500 CU INCHES VOLUME

ADD TIME

MPY TIME

DVD TIME

DVD TIME

7 usec

• MTBF  $\approx$  20,000 HRS \*\*

DEDICATED FLIGHT CONTROL COMPUTER (16 BIT MACHINE)

• 50 - 75 LSI MOS CHIP CONSTRUCTION (2K MEMORY)

• 0.5 LB WEIGHT

8 CU INCHES VOLUME

• 10 WATTS POWER

ADD TIME 2µsec

MPY TIME 11µsec

DVD TIME 19µsec

• MTBF  $\approx$  35,000 HRS \*\*

\*\*MTBF NOT KNOWN - ESTIMATES ARE PROJECTIONS. FAILURE RATES GIVEN FOR LSI CHIPS - 30 PARTS/109 HRS. AND APPLYING A DERATING EXPERIENCE FACTOR

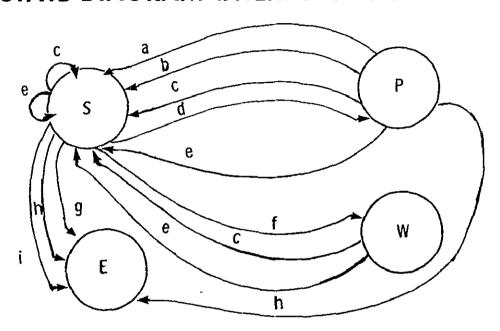

#### STATE DIAGRAM INTERRUPT PROCESSING

The hardware/software error program must consider:

- Operating system programs (Supervisor State)

- Application-oriented programs (Problem State)

Error operations are basically interrupt driven. Interrupt processing is featured in most major computer hardware/software systems. This state diagram of interrupt processing of a typical operating system shows computational transitions. The emergency state interests us. It is in this state that reconfiguration of resources takes place.

### STATE DIAGRAM INTERRUPT PROCESSING

- a) PROGRAM INTERRUPTS (PROBLEM STATE)

- b) SVC INTERRUPTS (PROBLEM STATE)

- c) I/O INTERRUPTS

- d) INITIATING PROBLEM PROGRAM EXECUTION

- e) EXTERNAL INTERRUPTS

- f) IDLE

- g) PROGRAM INTERRUPTS (SUPERVISOR STATE)

- h) MACHINE CHECK INTERRUPTS

- i) SVC INTERRUPTS (SUPERVISOR STATE)

- S = SUPERVISOR STATE

- P = PROBLEM STATE

- W = WAIT STATE

- E = EMERGENCY STÂTE

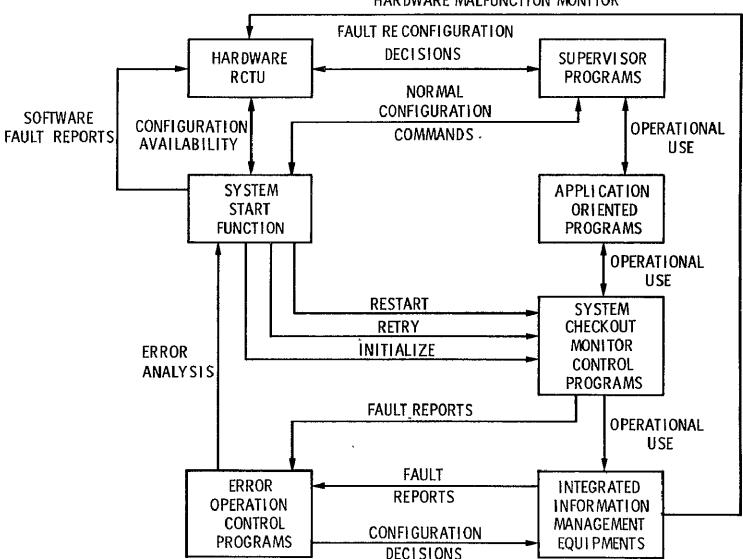

#### GENERIC EQUIPMENT/SOFTWARE ERROR PROGRAM RELATIONSHIP

Reconfiguration decisions fall under operating system error operation programs. These programs are imbedded in WMU and RCTU storage resources. Normal operation features transitions between System Check and Monitor programs and application-oriented programs. Error operations programs are distinguished by fault monitoring, configuration sequencing restart, retry and initializing options. The accompanying diagram highlights these aspects by functional flow.

# GENERAL EQUIPMENT/SOFTWARE ERROR PROGRAM RELATIONSHIP

HARDWARE MALFUNCTION MONITOR

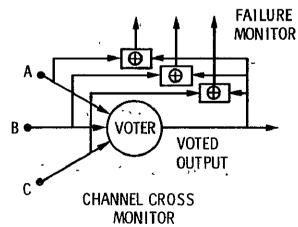

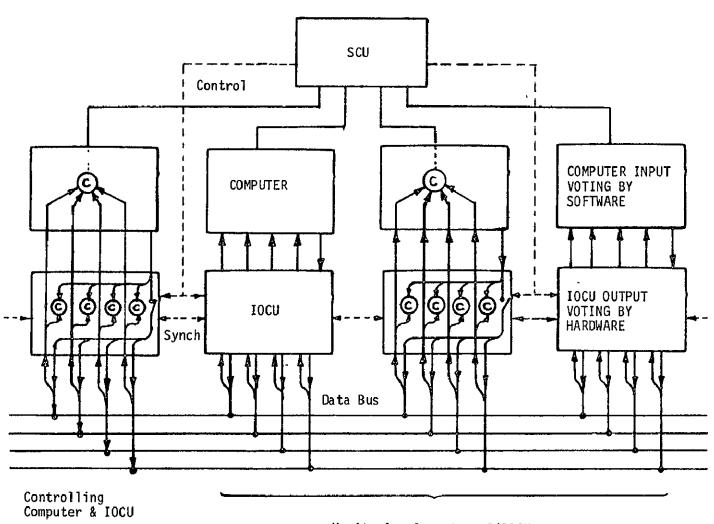

Two hardware techniques are illustrated in this and the following slide. One is based on concurrent error detection delayed diagnosis and recovery - the Reconfiguration Switching Technique; the other represents concurrent error detection, immediate error diagnosis, and correction - the Error Masking and Voting technique.

These techniques have been chosen to enhance the reliability of the proposed fault tolerant computer complexes. The fault masking technique is mandatory for the critical mission requirements of the Flight Control Computer complex. The G&N/DMS Computer complex has an alternative option, however, due to its ability to withstand equipment down times and delayed recoveries. Instead of utilizing a separate dedicated functional hardware reconfiguration module, some systems, particularly multiprocessors, have assigned this function to one of the operating processors. It is our contention that fault recovery is slower using this technique, and multiprocessors have been known to fail exercising this function.

## HARDWARE RECONFIGURATION MODULE

#### 40

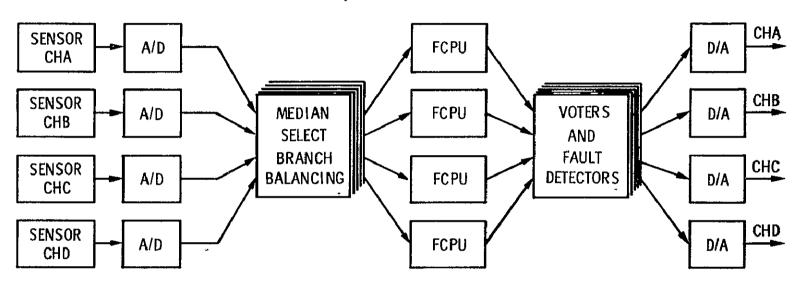

#### QUADRUPLEX CONNECTIONS (FO/FO/FS) FOR F/C COMPUTERS

Quadruplex voting for flight control computer computations is indicated by this slide. Triplex voting is much simpler because of less sophisticated switching. The Flight Control Error Control is predicated on reaching a single nonredundant processing case after the third failure. Shown also is cross channel error monitoring. Balancing of data received from redundant sensors is also indicated. The zero to three error case logic equations follow. Isolating the third error requires self-test backup.

| ERROR<br>CASE | LOGIC OPERATION                                                                                          |

|---------------|----------------------------------------------------------------------------------------------------------|

| . 0           | ABC V ABD ACD V BCD = 1 $\frac{a}{c}$ V                                                                  |

| 1             | A = 0; BC V BD V CD = 1<br>B = 0; AC V AD V CD = 1<br>C = 0; AB V AD V BD = 1<br>D = 0; BC V BD B CD = 1 |

| 2             | A = 0 B = 0 C = 0 D = 0<br>BC = 1 AB = 1 AB = 1 AB = 1<br>BD = 1 AC = 1 AD = 1 AC = 1 b                  |

| 3             | SELF- TEST DECISIONS                                                                                     |

# QUADRUPLEX CONNECTIONS (FO/FO/FS) FOR F/C COMPUTERS

#### 42

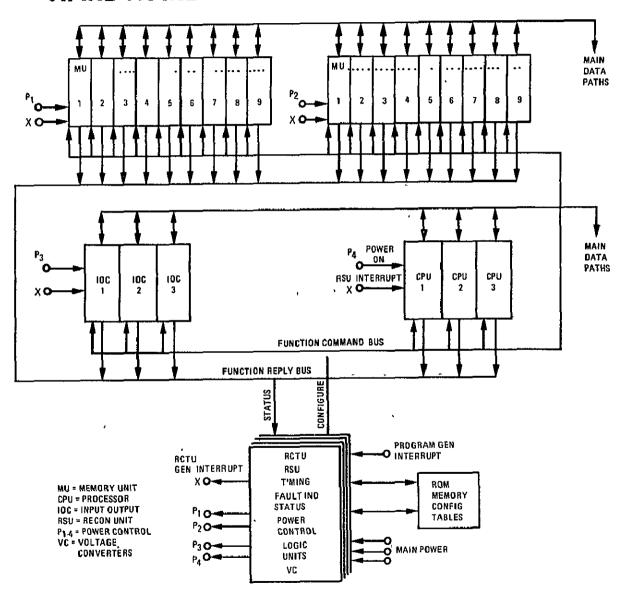

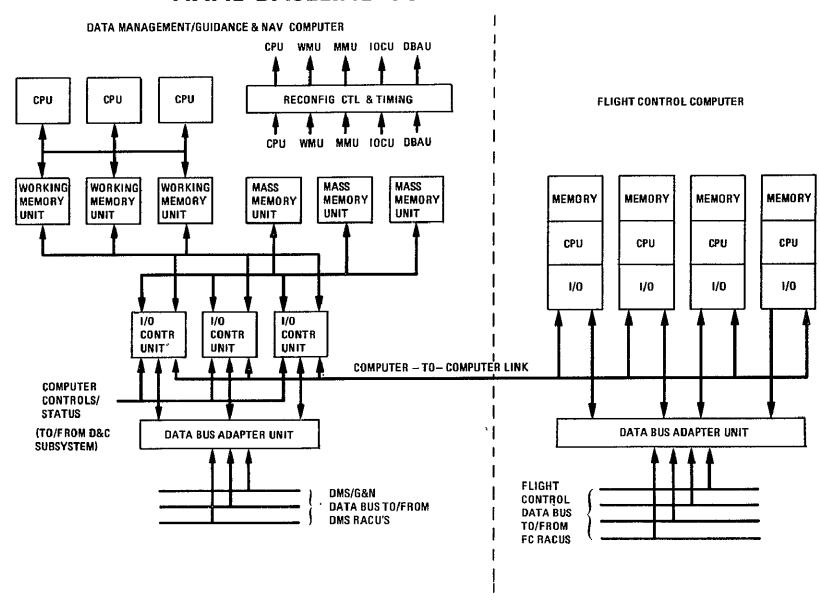

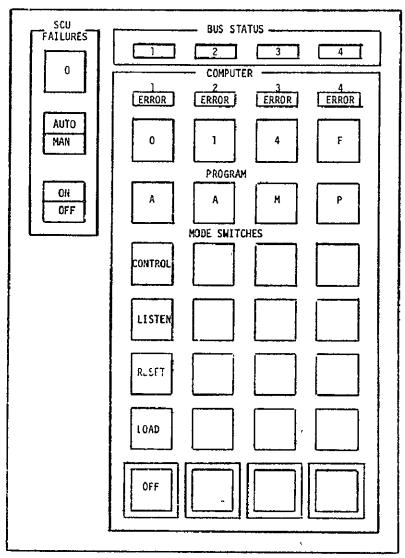

#### FINAL BASELINE COMPUTER COMPLEX

Utilizing this fault-tolerant DMS design technique, the following baseline SSS DMS system was designed. It features:

- A modular central computer with hardware/software error recovery reconfiguration within 1 second and a redundant uniprocessor, multicomputer, and multiprocessor hybrid computation capability

- . A quadruplex uniprocessor flight control dedicated computer with voter error masking recovery of 10 milliseconds

- . A dedicated quadruplex party line data bus for flight control

- . A triplex command/response line data bus for the central computer

Other redundancy features are as shown on this slide.

### FINAL BASELINE COMPUTER COMPLEX

#### CONCLUSIONS

Redundancy techniques must be used in order to meet the mission reliability objectives. A candidate architecture which has been proposed has resulted in evaluation of various techniques to be used. Emphasis is placed on practicality of the technique.

Because of the reliability objectives for the Space Shuttle, space and aircraft redundancy techniques are applied. In one part of the computer system, reconfiguration and standby redundancy techniques are suggested. In the more critical flight areas, system transients are not allowed so masking techniques are emphasized. This is the basis for the architecture.

Meeting flight control objectives (aircraft redundancy criteria) reduces the burden on central computer operation. Flight critical areas have been defined as such.

- . Multiple redundancy system and module concepts are employed such that system transients caused by components or (modules) failures are minimized or eliminated

- . The computer will be defined such that the system will be operational after failure of the two most critical components and failsafe after the third failure

The table suggests applicable techniques to enhance computer system reliability. These techniques are suggested as a minimum for incorporation into the computer assemblies.

# RELIABILITY ENHANCEMENT TECHNIQUES STUDIED AND APPLICABLE

- REDUNDANCY AT MODULE AND COMPONENT LEVELS

- RECONFIGURATION SWITCHING AND STANDBY SPARING

- ERROR DETECTION CODES (RESIDUE, PARITY)

- SELF-CHECKING MICROPROGRAMS (RETRY, ROLLBACK, SELF-TEST, ETC.)

- TRIPLICATION VOTING , DUPLICATION COMPARISON CHECKS

- OUT OF TOLERANCE CHECKS ANALOG TYPES, POWER CLOCK, SENSING

- SINGLE BIT CORRECTION TECHNIQUE (HAMMING & RESIDUE)

Z

# CONFIGURATION ALTERNATIVES FOR DATA BUS SUBSYSTEM INTERFACE UNITS

EDWARD CHEVERS AND WILLIAM MALLARY

MANNED SPACECRAFT CENTER

HOUSTON, TEXAS

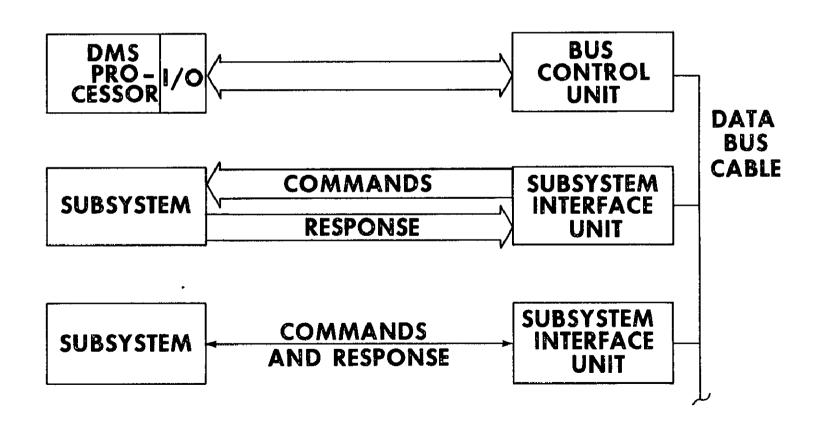

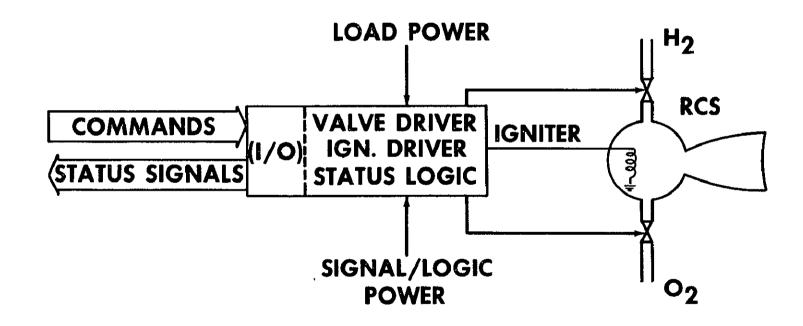

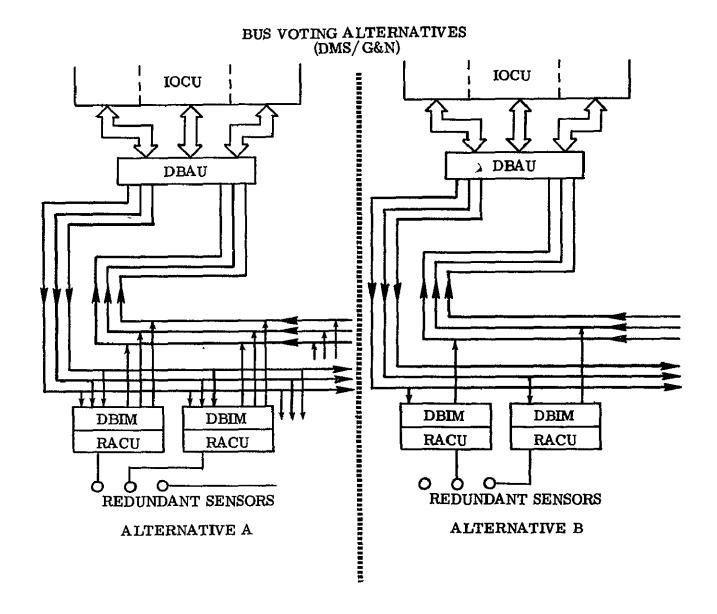

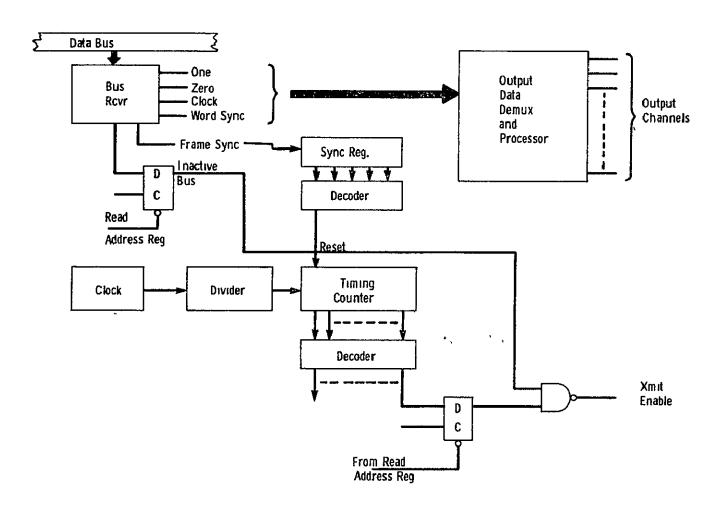

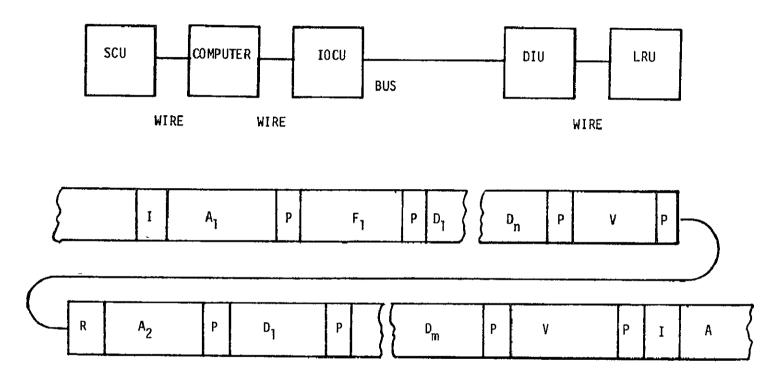

The current space shuttle study and development efforts have evolved data management concepts which utilize a data bus system to acquire data from and to distribute data and commands to the vehicle subsystems. The data bus substantially reduces vehicle wiring by using time division multiplexing and pulse code modulation techniques to transfer data serially between the vehicle data management subsystem (DMS) central processors and the other vehicle subsystems. As illustrated on the following page, the data bus control unit (BCU) interfaces with the central processor and distributes data and commands over a twisted-shielded-pair cable to subsystem interface units (SIU's) which interface with the subsystems. In a similar manner, the SIU's, under BCU control, acquire data from the vehicle subsystems and transmit the data to the BCU where it is provided to the central processor.

This presentation will review three basic approaches to the solution of how to implement the functions of the SIU. Two configurations convert the digital data into analog voltages or discrete mode commands. The third configuration in effect utilizes a sub-bus to distribute commands and acquire data from the individual subsystem channels. For each configuration, the relative impact on data acquisition, command distribution, pertinent advantages and disadvantages of interfacing, reliability, and software implications will be noted.

No attempt is made to define an optimal solution. Our effort in this paper is directed toward presentation of the considerations necessary to effect a final design for a functional unit which all too often is looked upon as merely another black box in the data path. The Electronic Divisions at the Manned Spacecraft Center consider the SIU to be probably the single most important element in the integrated avionics functional path. This is the unit which bridges the gap between the nebulose world of computers and software and the very real world of hardware sensors, controllers, and actuators.

## DATA MANAGEMENT SUBSYSTEM SIGNAL FLOW

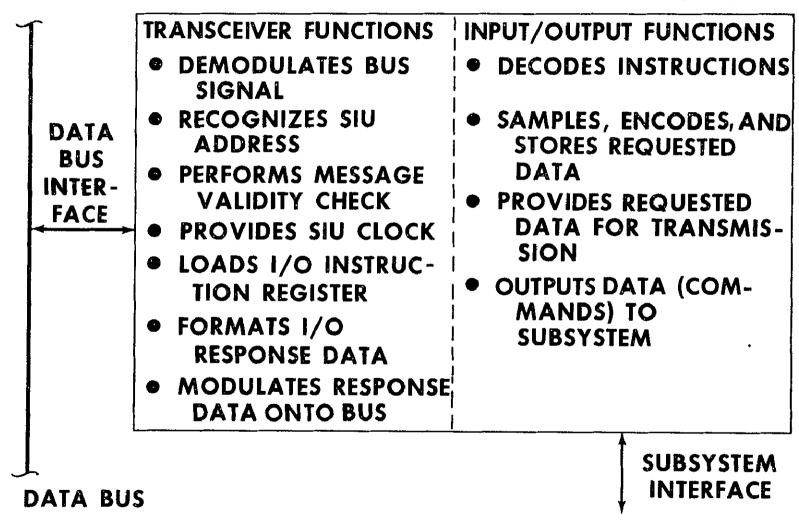

The SIU's, then, function in the shuttle to interface the DMS central processors with the vehicle subsystems via the data bus. To fulfill this requirement, the SIU's must accomplish the following tasks:

- a. Signal demodulation The SIU must interface with the data bus cable and derive data from the bus signal.

- b. Address recognition The SIU must decode the received data to determine if it is the intended destination of the bus message.

- c. Message validation The SIU must determine that the received message is error-free.

- d. Data acquisition The SIU must respond to data request instructions by sampling the requested data point, encoding or converting it to a digital form, and sending it via the data bus to the DMS data processor.

- e. Command/data distribution The SIU must respond to command instructions by converting the command or data into a form usable by the vehicle subsystem and outputting it from the designated signal buffer. The SIU must also provide an indication to the BCU that the command was executed.

- f. Signal transmission The SIU must convert the SIU response data into a form compatible with the data bus modulation scheme.

- g. Checkout The SIU design and operation must provide the BCU a means to ascertain that the SIU is operating properly.

## SUBSYSTEM INTERFACE UNIT FUNCTIONS

In addition to the previously discussed operating requirements, the SIU must satisfy shuttle reliability requirements which dictate that the DMS, which includes the SIU's, must permit the shuttle vehicle to perform its design mission after two failures and permit the shuttle to return to base after three failures. To satisfy this requirement, the current shuttle DMS design concepts use a data bus which incorporates four levels of redundancy. In general, four data bus cable sets interface with an SIU which contains four levels of redundancy. The SIU in turn interfaces with the subsystem which may also incorporate up to four levels of redundancy, depending on its mission criticality.

The SIU, then, is required to interface with four data bus cables and with up to four levels of subsystem redundancy in a manner which will permit the SIU to perform its functional requirements after as many as three failures.

There are three SIU design alternatives which are currently being considered by MSC. Each satisfies the basic requirements for redundant operation but imposes restrictions on DMS operation. The following text describes these alternatives in terms of the partitioning of SIU functions and then discusses the impact of each design on critical DMS and vehicle subsystem considerations.

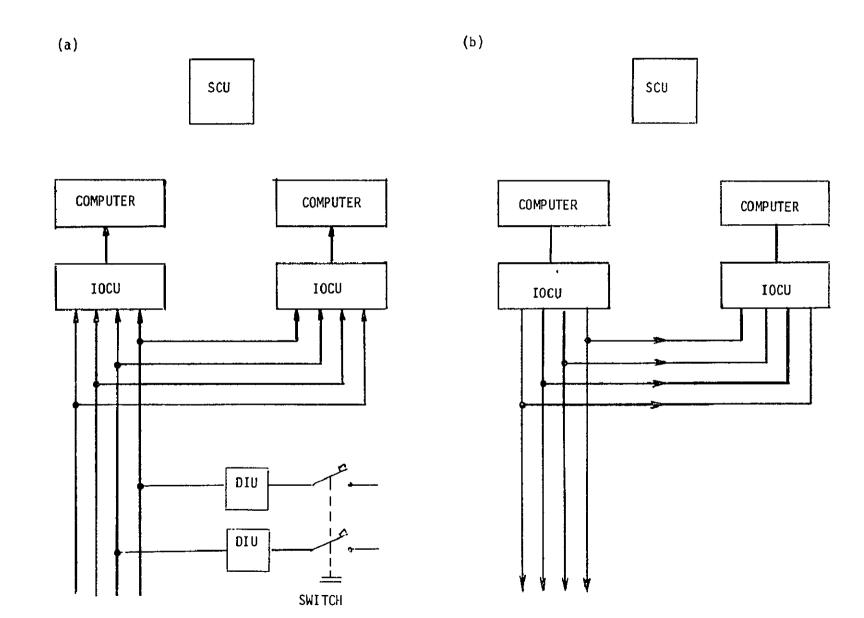

To form a basis for describing each SIU design alternative, the SIU functions are categorized as either transceiver or input/output functions, and the SIU is partitioned into two functional elements. Each SIU design configures the SIU transceiver and input/output functions differently. For reference purposes, these alternatives will be designated as configurations 1, 2, and 3.

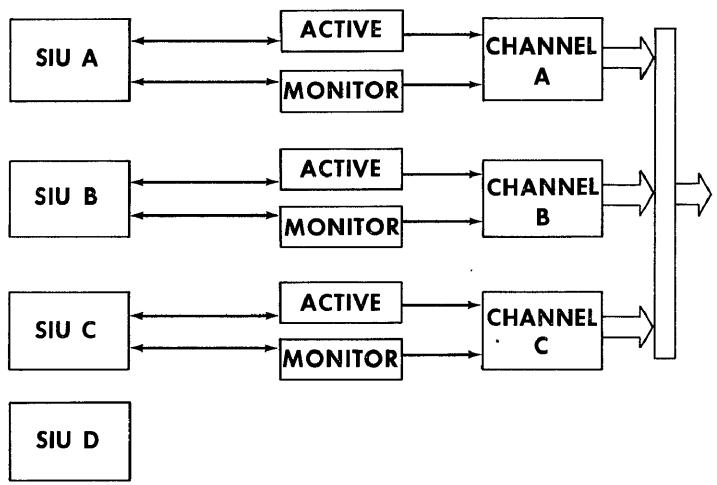

## REDUNDANT SIU INTERFACES

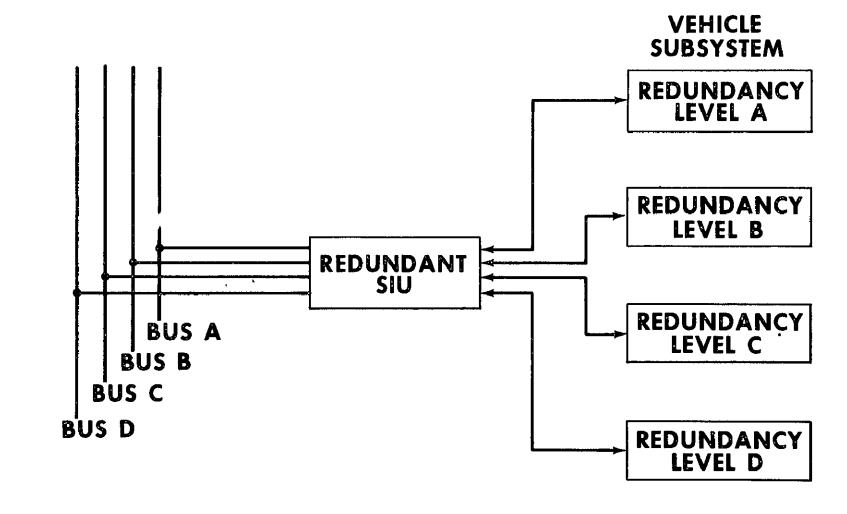

OI Cor Configuration 1, which is illustrated on the following page, is the simplest of the three approaches to satisfying the shuttle redundancy requirements. A simplex (non-redundant) SIU interfaces with each data bus cable and each level of subsystem redundancy. No cross coupling is used at either the data bus/SIU interface or the SIU/subsystem interface. Data transfer between the DMS processor and a subsystem redundancy level is restricted to the single path provided by the associated SIU and data bus cable. Complete isolation is easily maintained between redundant levels of the data bus and subsystem.

In this configuration, the DMS processor may either acquire data from and output commands to the redundant subsystem elements simultaneously, over all four bus cables and associated SIU's, or it may address each subsystem redundancy level individually. In the case of simultaneous addressing, both the DMS processor and the vehicle subsystem would use voting techniques to determine the validity of the received data and/or commands.

Simultaneous addressing also necessitates some form of data buffering at the BCU or each computer input/output so that each feedback signal from the SIU's can be kept isolated until ready for processing in the DMS processor.

### CONFIGURATION 1

- SIMPLEX INTERFACE WITH EACH DATA BUS CABLE

- SIMPLEX INTERFACE WITH EACH SUBSYSTEM CHANNEL

- SUBSYSTEM CHANNELS MAY BE ADDRESSED

INDIVIDUALLY OR SIMULTANEOUSLY

- COMPLETE ISOLATION BETWEEN BUSES AND SUBSYSTEM CHANNELS

### SIU CONFIGURATION 1

ន

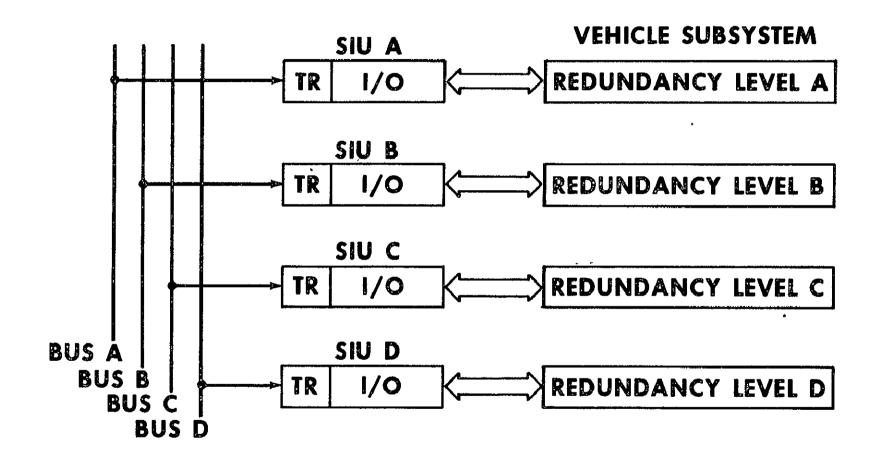

Configuration 2 differs from configuration 1 in that each SIU interfaces with all four bus cables. The SIU's incorporate redundant transceiver sections to provide interbus isolation. Each input/output section, however, is still simplex and interfaces with only a single subsystem redundancy level.

The DMS processor is now able to communicate with any subsystem redundancy level via any of the four data bus cables. Like configuration 1, the DMS processor may address the subsystem redundancy elements either individually or simultaneously. Each SIU must, however, have a unique address, and SIU complexity increases because of the additional transceiver circuits and the requirement for the SIU to know which data bus to transmit on. The primary advantage to configuration 2 is the protection against bus cable failures due to the multiple signal paths provided by cross coupling in the data bus/SIU interface.

### **CONFIGURATION 2**

- EACH SIU INTERFACES WITH ALL FOUR DATA **BUS CABLES**

- SIMPLEX INTERFACE WITH EACH SUBSYSTEM **CHANNEL**

- SUBSYSTEM CHANNELS MAY BE ADDRESSED INDIVIDUALLY OR SIMULTANEOUSLY

- EACH SIU REQUIRES A UNIQUE ADDRESS PLUS GROUP ADDRESS RECOGNITION CAPABILITY IF SIMULTANEOUS ADDRESSING USED

## **F**

#### SIU CONFIGURATION 2 BUS **VEHICLE SUBSYSTEM** SIU A TR-A **REDUNDANCY** TR-B 1/0 TR-C LEVEL A TR-D BUS SIU B TR-A **REDUNDANCY** TR-B 1/0 TR-C LEVEL B TR-D BUS SIU C TR-A REDUNDANCY TR-B 1/0 TR-C **LEVEL C** TR-D SIU D BUS TR-A

TR-B

TR-C

TR-D

1/0

**REDUNDANCY**

LEVEL D

ÖŢ

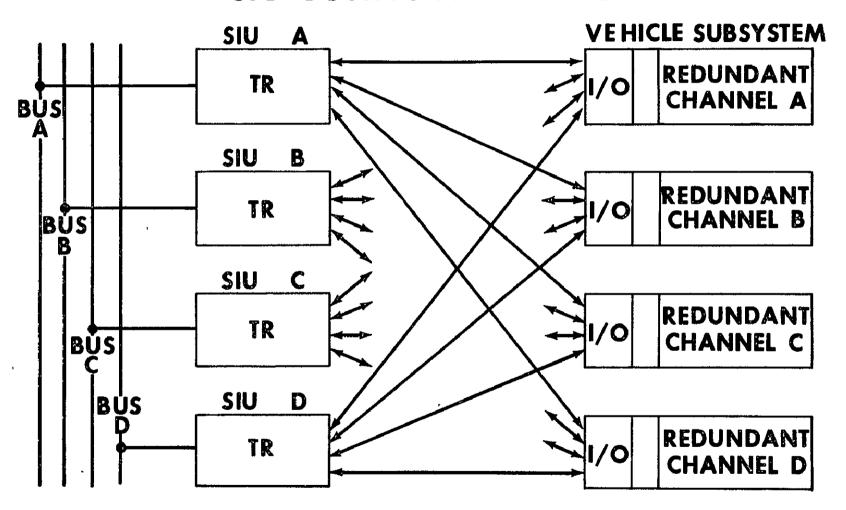

Configuration 3 actually involves two different techniques which are extensions of configurations 1 and 2. The diagram shows configuration 1 expanded to allow cross coupling of each SIU to each subsystem channel. This permits the DMS processor to address each subsystem channel through any one of the four data bus cables even after three successive SIU failures. Again, system flexibility is increased but at the expense of increased hardware and software complexity. The DMS processor now must address both an SIU station and a specific subsystem channel behind the SIU. The primary advantage of this configuration is the ease with which a transition may be made from four data buses to any level "n" of subsystem redundancy.

The increase in interconnection complexity is readily apparent in the diagram and is a significant disadvantage. However, this particular cross-coupling technique does appear to be the most practical approach for access to and usability of all the inherent reliability provided by a multiply redundant subsystem such as the triply redundant hydraulic actuators and quadruply redundant electromechanical actuators being considered for the shuttle.

The other variation of configuration 3 is an extension of the configuration 2 technique to allow cross coupling at both the data bus/SIU interface and the SIU/subsystem interface. This particular configuration is not considered a likely candidate for flight application since overall system flexibility is virtually unaffected when compared to the basic concept, and total system reliability may actually be decreased as a result of the additional hardware and interconnections. There are no firm reliability numbers to prove this argument; however, preliminary laboratory breadboard investigations tend to support the decreased reliability assumption.

#### **CONFIGURATION 3**

- SIMPLEX INTERFACE WITH EACH DATA BUS CABLE

- CROSS COUPLING OF EACH SIU TO EACH SUBSYSTEM CHANNEL

- SUBSYSTEM CHANNELS MAY BE ADDRESSED INDIVIDUALLY OR SIMULTANEOUSLY WITH GROUP ADDRESSING

- REQUIRES BOTH SIU ADDRESS AND SUBSYSTEM CHANNEL ADDRESS

- PERMITS EASY TRANSITION FROM FOUR DATA BUSES TO ANY NUMBER OF SUBSYSTEM CHANNELS.

## SIU CONFIGURATION 3

<del>5</del>9

The software impact of configurations 1 and 2 is very nearly the same. The DMS processor will first select a subsystem channel to access for information or to issue commands. In configuration 1, the processor then selects one of the four buses to match the subsystem channel, and we are now assuming the processor has available sufficient information as to the operational health of each SIU/subsystem pair. When a command is issued, the SIU must have the capability to determine the validity of the command before releasing it to the subsystem for execution. This may be done through error detection codes and requests for retransmission, error correction codes, voting on multiple commands, verification by echo checking, plus numerous variations of one or more of these techniques. The error detection/correction codes and voting techniques all tend to increase SIU and subsystem hardware complexity, whereas the echo check decreases available data bus capacity. Studies are planned at the Manned Spacecraft Center to define the relative impact of each technique on both hardware and software for each of the mentioned data security methods, but initial investigations tend to indicate a slightly lower software penalty for techniques incorporating echo checks. This seems to be a result of continuously available information in the central processor in regard to the health status of each data bus cable/SIU combination.

Configuration 2 has essentially the same degree of software complexity as configuration 1. The only difference in this case is the available knowledge of SIU/subsystem interface status and reference to a data bus priority table in the computer memory. Interfacing each SIU with all four data buses does permit voting at the SIU of simultaneous messages, but again this tends to increase SIU hardware complexity. This would be especially true if all data bus traffic was not bit synchronized at the bus control unit. However, bit synchronization increases BCU and input/output controller complexity; therefore, changes in one area must be traded off against resulting impacts in other areas of the system.

As might be suspected, configuration 3 does impose the most severe software penalty. This is the price which must be paid to achieve the high level of flexibility available from this interconnect configuration. The DMS processor must maintain a status record of each SIU, each subsystem channel, plus the interconnecting cables between SIU's and subsystem channels. The added complexity of keeping a record of the cables is to prevent the needless discard of a good subsystem channel because a cable has failed, when there is an alternate path into the subsystem from each of the other SIU's.

From the descriptions of the three SIU configurations, it is evident that the number of selectable data paths between the DMS processor and subsystem redundancy elements is increased at the cost of both hardware complexity and bus operational efficiency. Also affected is the rate at which redundant data can be acquired from the vehicle subsystems. Configuration 1 permits the simultaneous operation of all four of its redundant data paths, and data can be acquired from all subsystem redundancy levels at the same time. Even when one or more signal paths fail, sufficient data are presented to the DMS processor to permit computation.

Configuration 2 can also simultaneously acquire data from all subsystem redundancy levels. The normal mode of operation, however, is the sequential acquisition of data from one subsystem redundancy level at a time, utilizing a single data bus cable. This mode is normally used because a substantial reduction in SIU transceiver electronics can be obtained when it is not necessary to decode bus signals from more than one data bus at a time. Bus efficiency does suffer, however, because the time required for the DMS processor to acquire data increases as a factor of the number of subsystem redundancy levels sampled.

Configuration 3, like configuration 2, acquires data from each subsystem redundancy level in a sequential manner. Effective data acquisition rates are further reduced in this configuration by the increase in bus message overhead caused by the requirement to uniquely address both the SIU transceiver and imput/output sections.

The distribution of DMS processor-generated commands and data to the vehicle subsystems is also affected by the choice of STU configurations. Configurations 1 and 3 are equally efficient in terms of command rates, as each can output simultaneous commands to each subsystem redundancy level within a single instruction time. Configuration 1 accomplishes this by transmitting simultaneous commands to each subsystem redundancy level over all four data buses. Configuration 3 does as well by transmitting a single command containing an input/output group address which causes all input/output sections to generate identical data or commands.

Configuration 2 outputs data to only one subsystem redundancy level at a time. A simultaneous command capability is possible by requiring that the SIU's respond to a group address code. This is not normally considered, however, because of hardware complexity considerations.

A comparison of redundancy levels between configurations 1, 2, and 3 is somewhat dependent on where in total system flow a redundancy boundary is drawn. By this we mean, at what point does the subsystem begin and the DMS and/or data bus end. For purposes of this presentation, the subsystem will be considered to include the SIU and its interface with the data bus. This approach is taken because of the various interface techniques being considered and the fact that data bus cable failures have significant impacts in both DMS software and the subsystem redundancy.

Configuration 1 is the least reliable when considered from a straight reliability string approach. This is a result of having the data bus, SIU transceiver, SIU input/output, and subsystem channel all in a single string. Therefore, a failure in any one of the four units renders the entire string useless. It should be noted that a failure of the data bus cable is even more significant since it not only eliminates the subsystem channel near the fault but also all other channels which are attached to that particular bus.

The one main advantage of configuration l is the relative simplicity of the hardware which does serve to offset some of the unreliability of a single string system. Power, packaging, and interconnections can all be simplified in this configuration, and subsystem reliability improved through good quality control procedures.

Configuration 2 tends to improve overall system reliability by eliminating the loss of one channel in all subsystems as a result of a single data bus cable failure. The penalty paid is increased hardware complexity at the SIU transceiver input. As mentioned earlier, care must be taken with this approach to insure against a failure at one input propagating across to all inputs such that a failure condition exists on all four data buses.

For each of these configurations, the most unreliable part of the SIU will normally be the transceiver section. This is especially true if linear emplifiers and drivers must be used for the transmitters and receivers. Therefore, configuration 2 should be more reliable than configuration 1 since the most unreliable portion has been made redundant. However, this configuration still permits the loss of a good subsystem channel in the event of a failure in the SIU input/output section. Also, the increase in reliability must be calculated carefully with due consideration for the added hardware complexity and circuit design incorporated with quadruply redundant transceiver sections. If high power components and extreme accuracy are necessary to satisfy design goals, it is possible to arrive at a quadruply redundant unit which is less reliable and an order of magnitude more expensive than the simplex SIU in configuration 1.

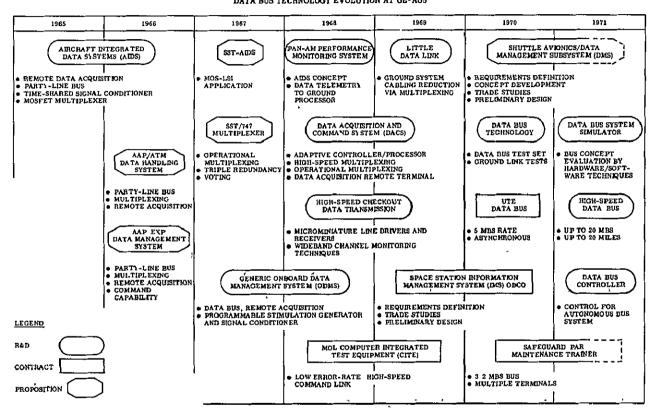

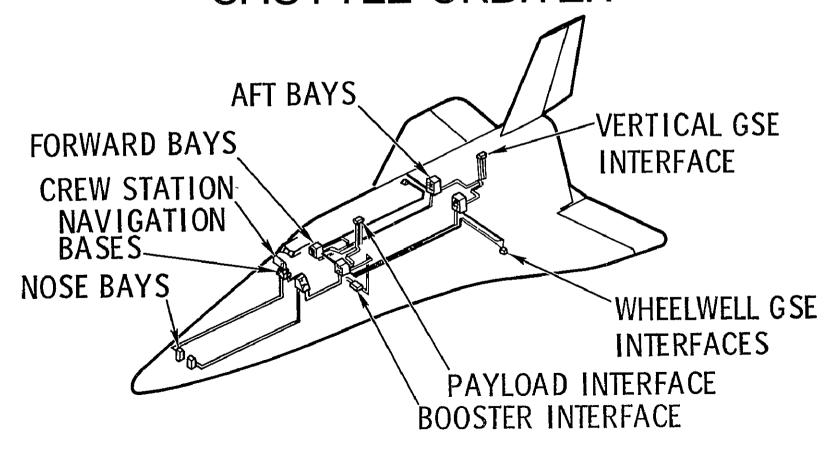

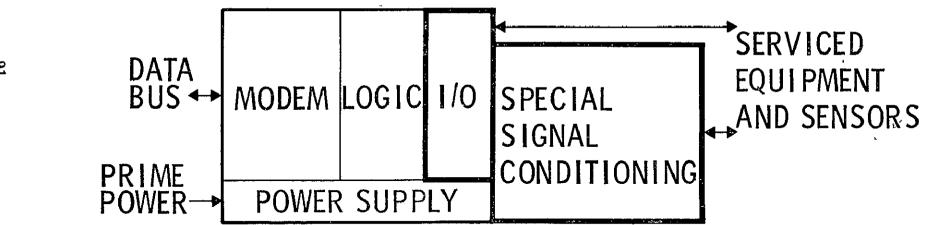

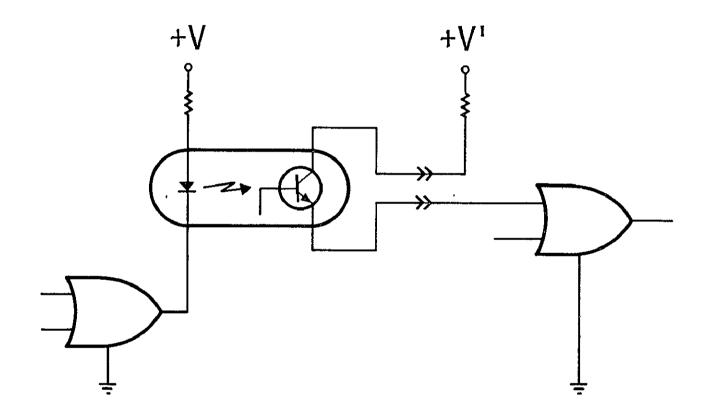

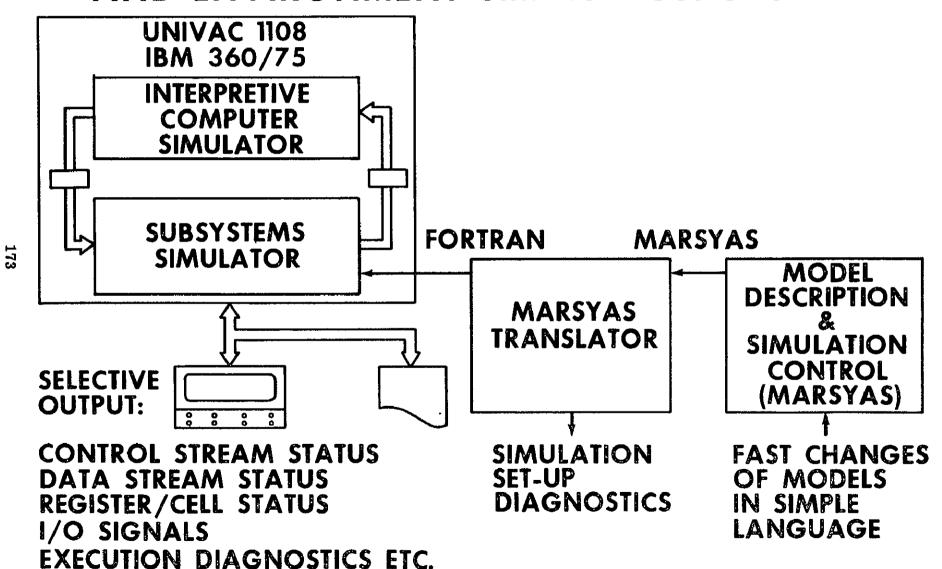

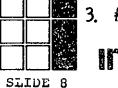

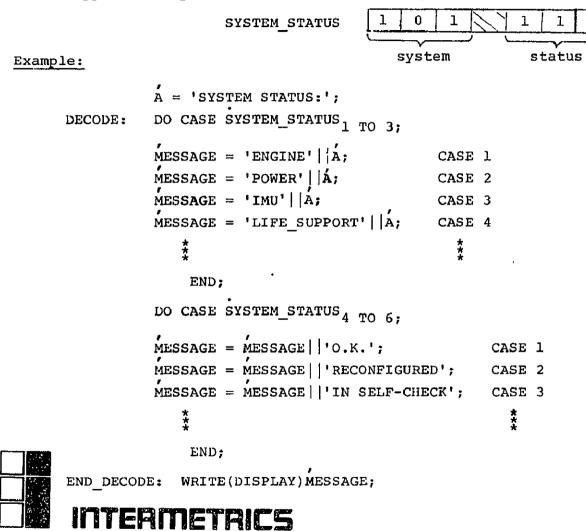

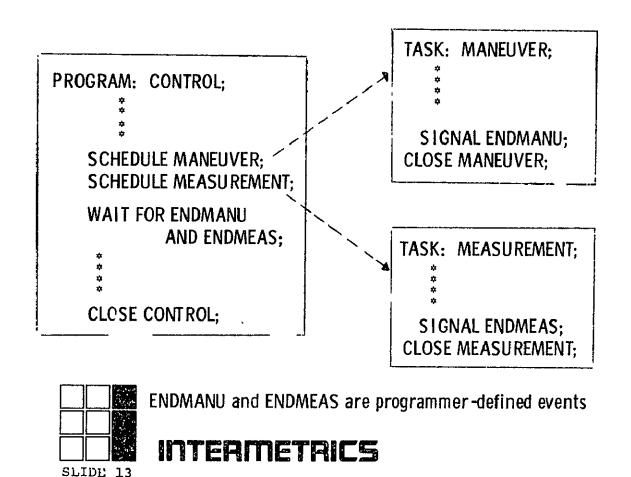

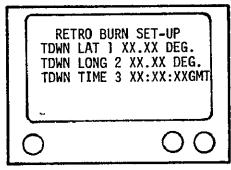

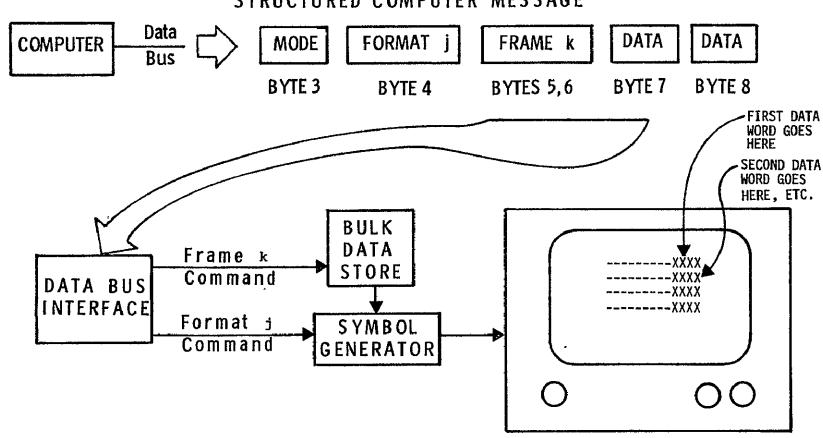

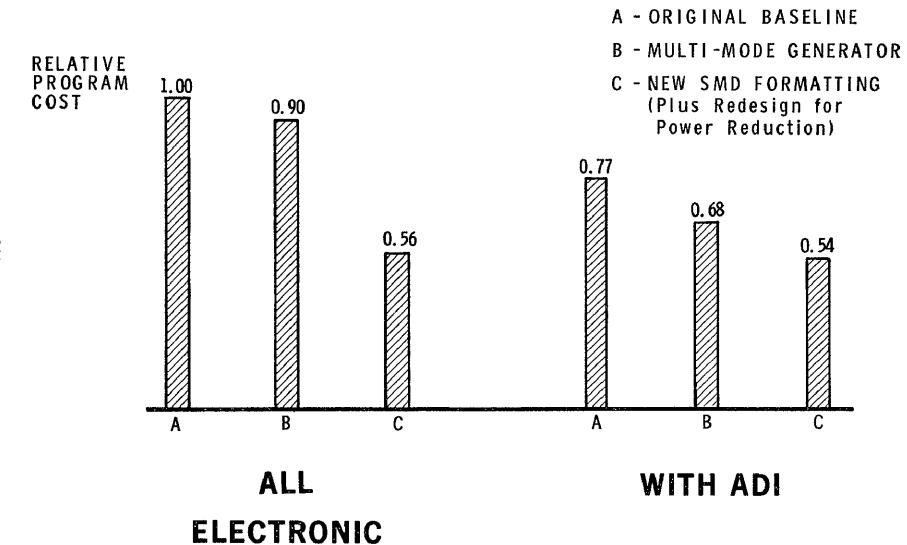

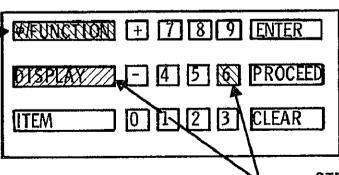

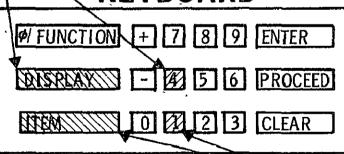

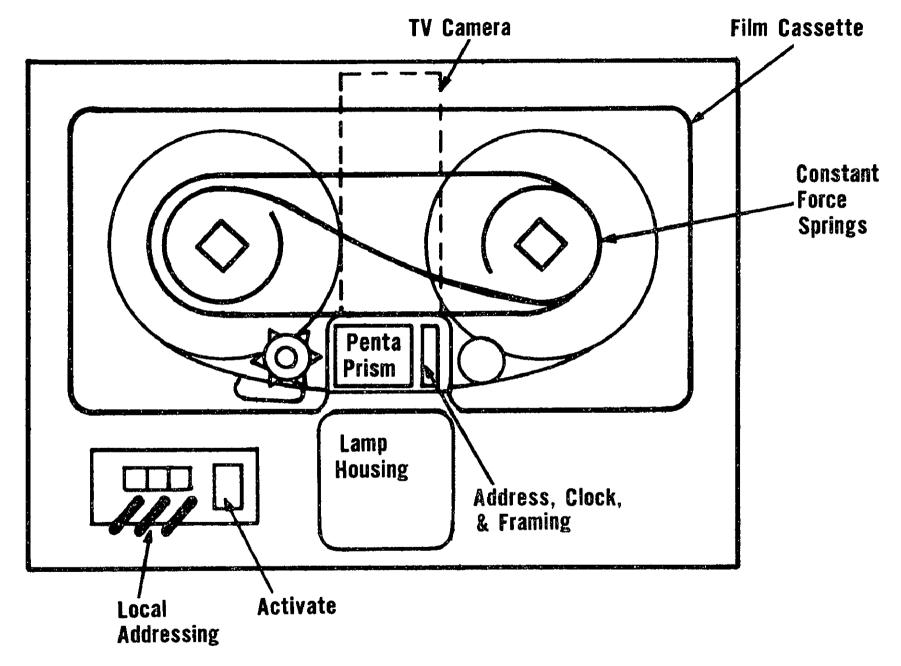

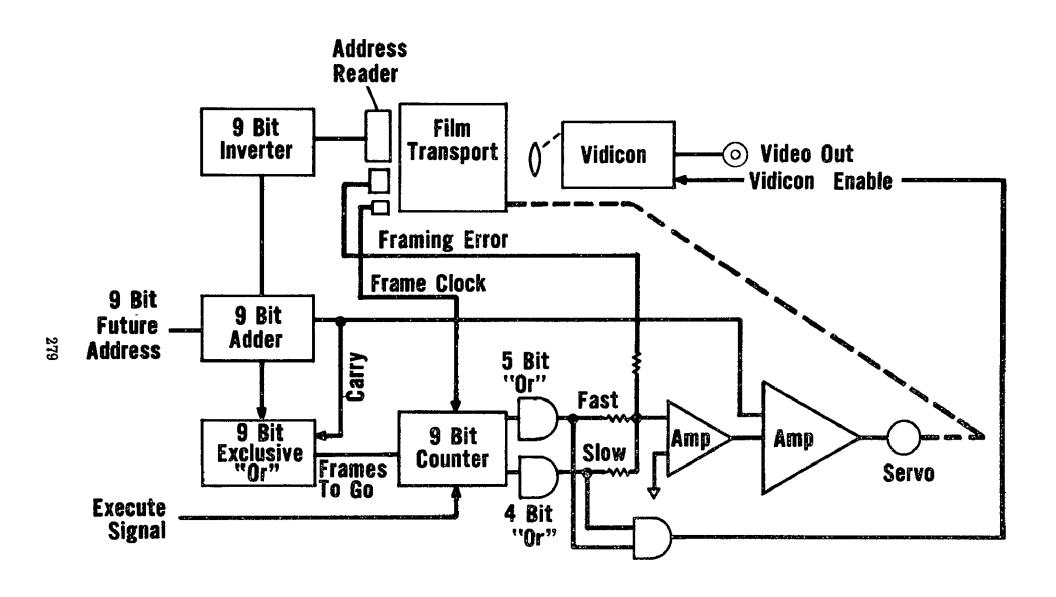

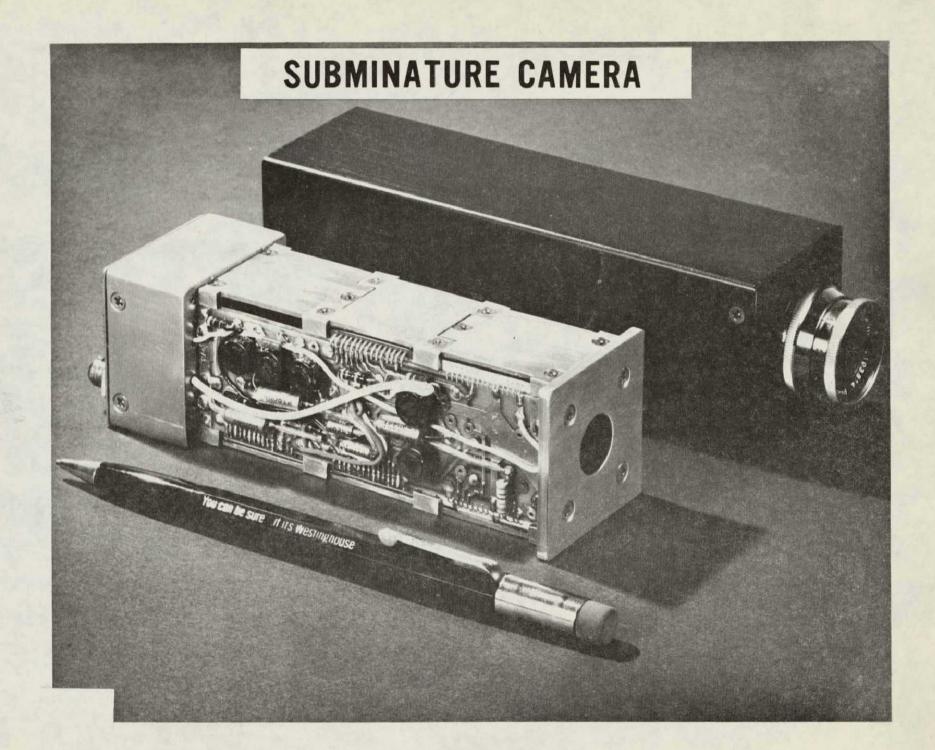

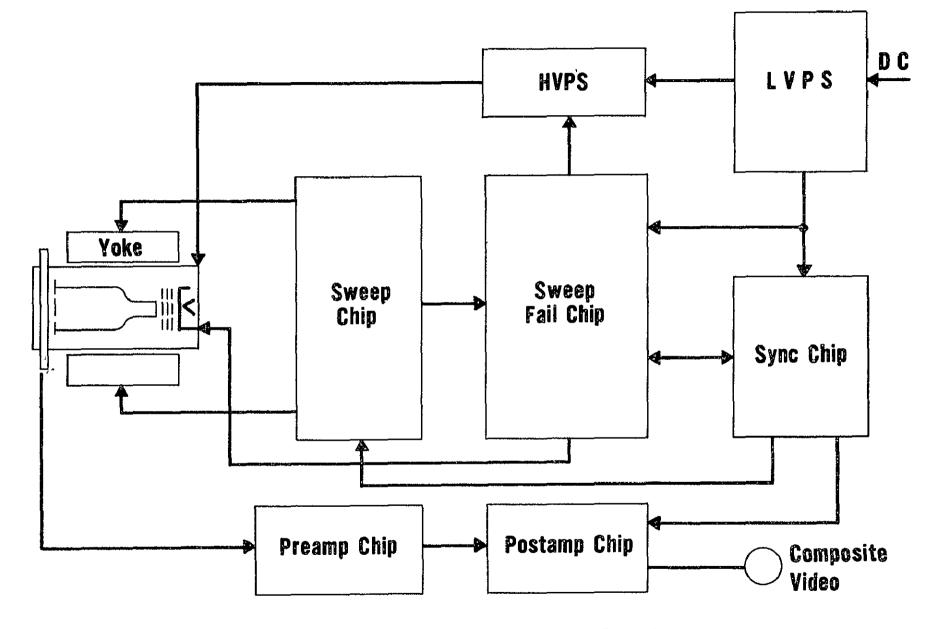

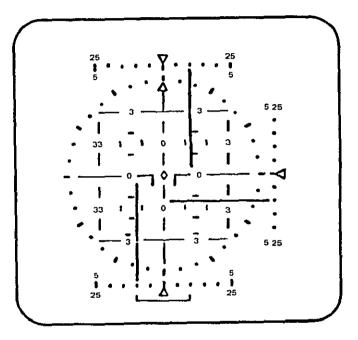

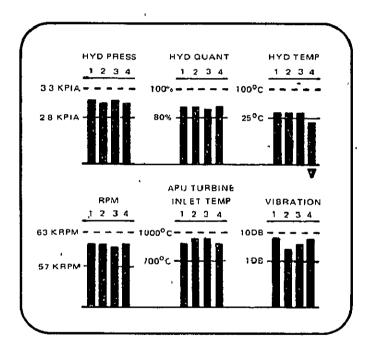

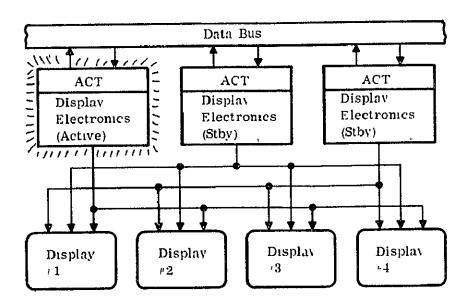

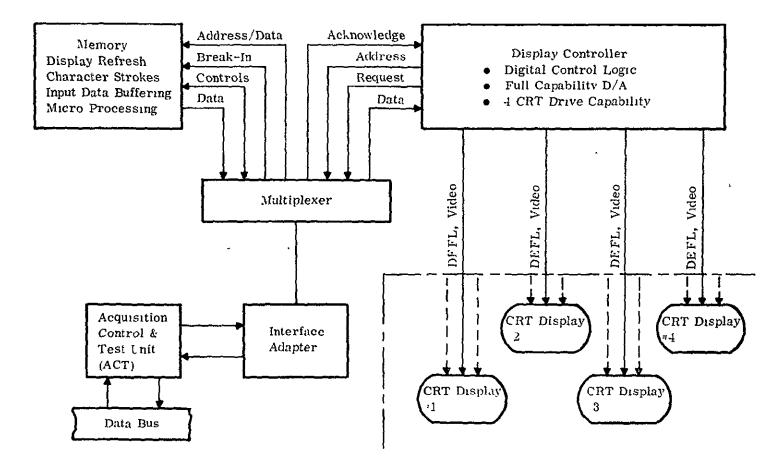

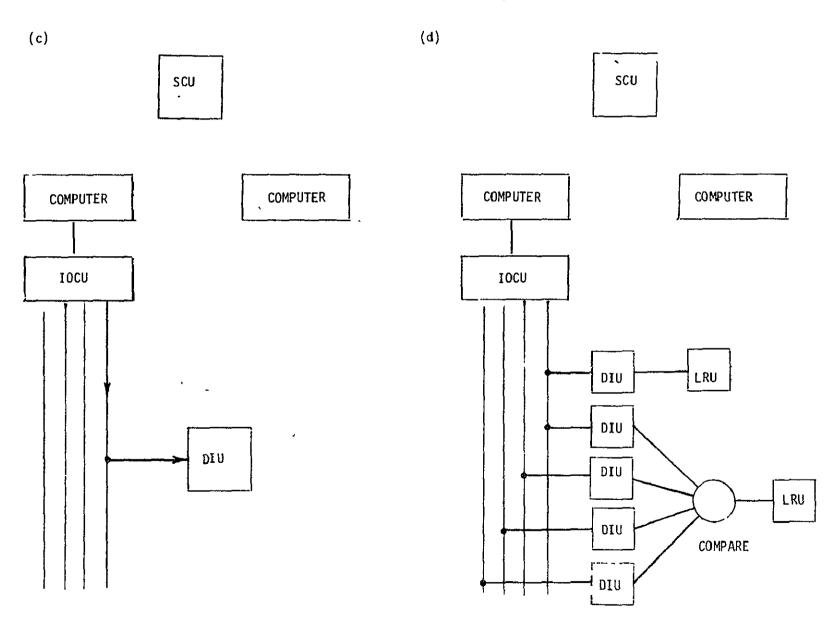

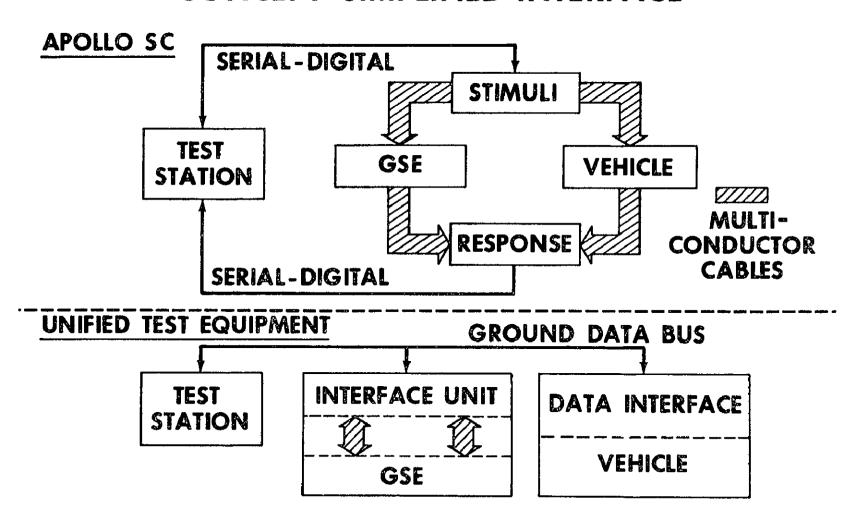

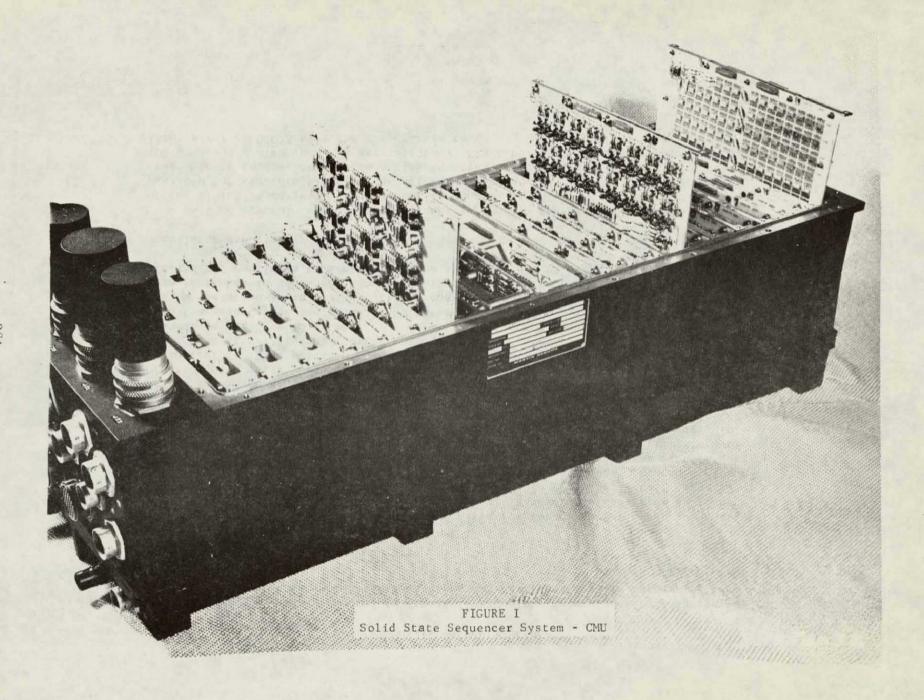

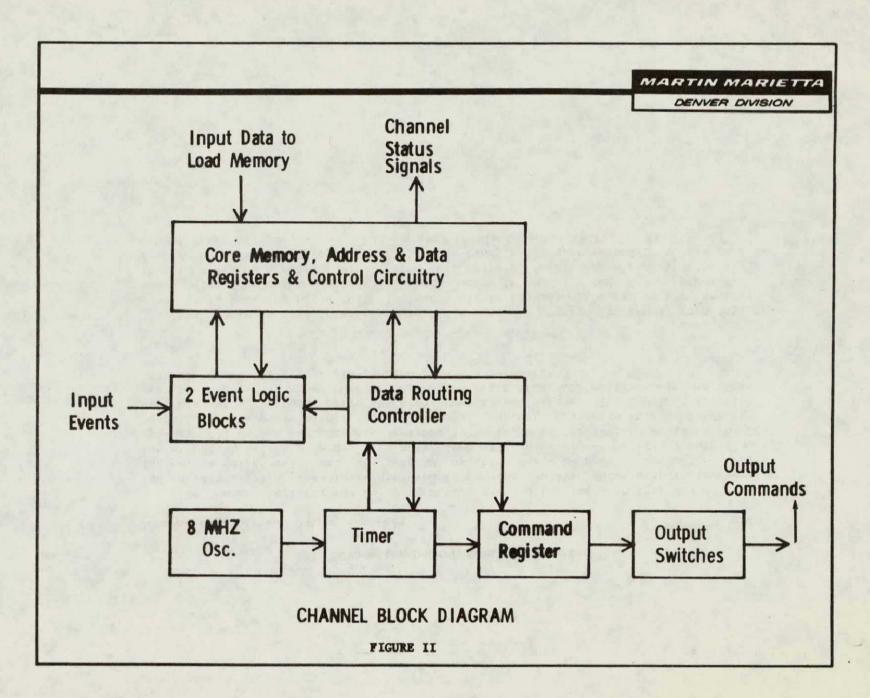

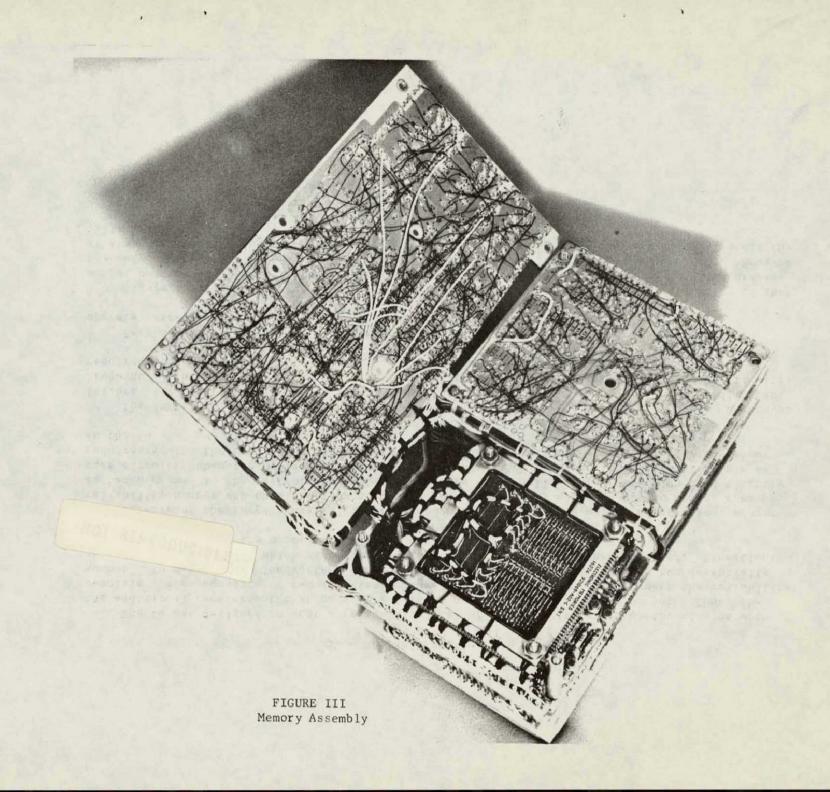

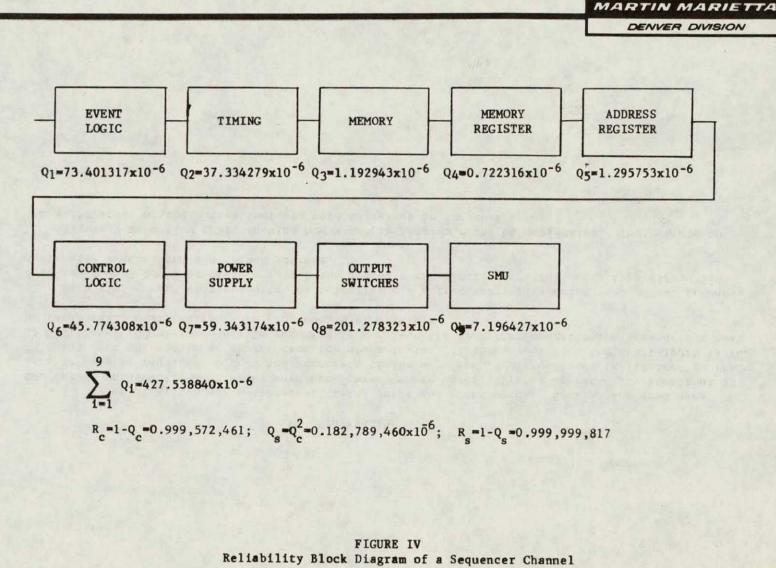

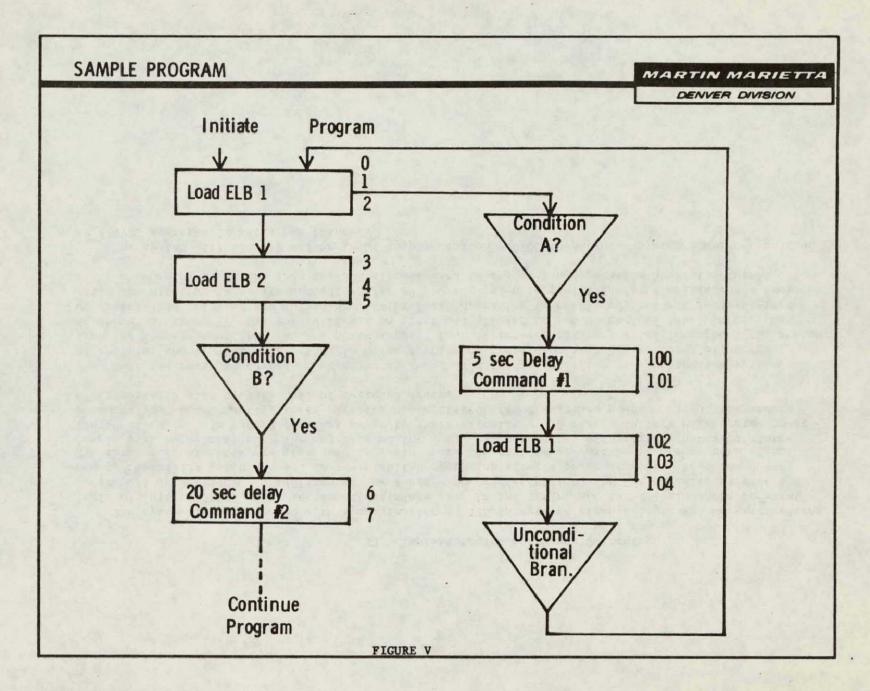

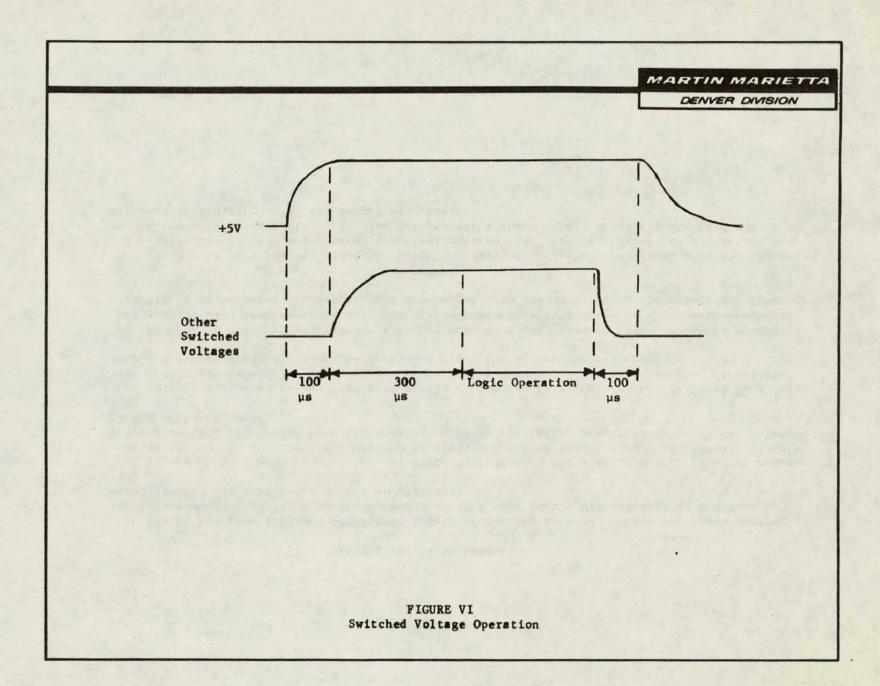

Configuration 3, like configuration 2, does provide the capability of being able to use each subsystem channel after failures in the data bus cable or the SIU transceiver section. The single transceiver section of configuration 3 tends to reduce the hardware complexity which provides some increase in system reliability when compared with configuration 2; however, this gain is offset to a certain extent by the interconnections required between the SIU transceivers and subsystem channel input/output sections. Therefore, the penalty paid for the high level of redundancy with configuration 3 is the unreliability of multiple connections, increased software complexity in checkout, and increased software complexity for inflight failure monitoring.