NASA 12-2198 CR 120832

N72-33210

# CASE FILE COPY

FINAL REPORT

DEVELOPMENT OF A HIGH SPEED POWER THYRISTOR THE GATE ASSISTED TURN-OFF THYRISTOR

by

D. R. Hamilton, J. Brewster, D. Frobenius and T. Desmond

WESTINGHOUSE ELECTRIC CORPORATION

Semiconductor Division

Youngwood, Pennsylvania 15697

prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

July 31, 1972

CONTRACT NAS 12-2198

NASA Lewis Research Center

Cleveland, Ohio

Dr. Francis C. Schwarz and Julian F. Been

| 1. Report No.                                                                                                                                                                                                     | 2. Government Accession                                                                  | No.                                                                      | 3. Recipient's Catalog                                  | No.                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|

| NASA CR 120832 4. Title and Subtitle                                                                                                                                                                              | <u> </u>                                                                                 | <del></del>                                                              | 5. Report Date                                          |                                             |

| 4. Title and Subtitle                                                                                                                                                                                             |                                                                                          | Ì                                                                        | July 31, 19                                             | 72                                          |

| DEVELOPMENT OF A HIGH SPEED POWER TURN-OFF THYRISTOR                                                                                                                                                              | . THYRISTOR - THE GA                                                                     | TE ASSISTED                                                              | 6. Performing Organiz                                   |                                             |

| 7. Author(s)                                                                                                                                                                                                      |                                                                                          |                                                                          | 8. Performing Organiz                                   | ation Report No.                            |

| D. R. Hamilton, J. Brewster, D. F                                                                                                                                                                                 | robenius and T. Des                                                                      | mond                                                                     | IO. Work Unit No.                                       |                                             |

| 9. Performing Organization Name and Address                                                                                                                                                                       |                                                                                          |                                                                          |                                                         |                                             |

| Westinghouse Electric Corporati                                                                                                                                                                                   | on                                                                                       |                                                                          | 11. Contract or Grant                                   | No.                                         |

| Semiconductor Division                                                                                                                                                                                            |                                                                                          |                                                                          | NAS 12-2198                                             |                                             |

| Youngwood, Pennsylvania                                                                                                                                                                                           |                                                                                          |                                                                          | 13. Type of Report an                                   | d Period Covered                            |

| 12. Sponsoring Agency Name and Address                                                                                                                                                                            |                                                                                          |                                                                          | Contractor                                              | Report                                      |

| National Aeronautics and Space<br>NASA Lewis Research Center<br>Cleveland, Ohio                                                                                                                                   | Administration                                                                           | -                                                                        | 14. Sponsoring Agency                                   |                                             |

| 15. Supplementary Notes                                                                                                                                                                                           |                                                                                          |                                                                          |                                                         |                                             |

| Project Managers Dr. Francis C.<br>NASA Lewis Research Center, Cle                                                                                                                                                |                                                                                          | F. Been,                                                                 |                                                         |                                             |

| 16. Abstract                                                                                                                                                                                                      |                                                                                          |                                                                          |                                                         |                                             |

| turn-off thyristor was rated at<br>delivered for evaluation in a se<br>relate to the series inverter ap<br>work it was determined that the<br>However, improvements and/or cha<br>must be made in order to effect | ries inverter circu<br>plication were buil<br>basic device design<br>nges in fabrication | it. In addition, t and demonstrated is more than adequatechnology, which | test circuits de<br>. In the course<br>wate to meet the | esigned to<br>e of this<br>e specifications |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   | •                                                                                        |                                                                          | •                                                       | ·                                           |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   | •                                                                                        |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          | •                                                                        |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

| ·                                                                                                                                                                                                                 |                                                                                          | •                                                                        |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

| ·                                                                                                                                                                                                                 |                                                                                          |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          | •                                                                        |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         | 1                                           |

|                                                                                                                                                                                                                   |                                                                                          | •                                                                        |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

|                                                                                                                                                                                                                   |                                                                                          |                                                                          |                                                         |                                             |

| 17. Key Words (Suggested by Author(s))                                                                                                                                                                            | 118                                                                                      | 3. Distribution Statement                                                |                                                         |                                             |

| 17. Key Words (Suggested by Author(s))  Series Inverter  High Speed Power Thyristor  Gate Assisted Turn-off Thyristo                                                                                              |                                                                                          | 3. Distribution Statement Unclassified - Un                              | limited                                                 |                                             |

| Series Inverter                                                                                                                                                                                                   |                                                                                          |                                                                          | limited                                                 |                                             |

| Series Inverter<br>High Speed Power Thyristor<br>Gate Assisted Turn-off Thyristo                                                                                                                                  | r                                                                                        | Unclassified - Un                                                        |                                                         | oo Price*                                   |

| Series Inverter<br>High Speed Power Thyristor                                                                                                                                                                     |                                                                                          | Unclassified - Un                                                        | limited  21. No. of Pages 84                            | 22. Price*                                  |

<sup>\*</sup> For sale by the National Technical Information Service, Springfield, Virginia 22151

# FOREWORD

The research described herein was done by the Westinghouse Electric Corporation, Semiconductor Division, Youngwood, Pa., on Contract NAS 12-2198. The work was started under Drs. F. C. Schwarz and C. A. Renton, formerly of the NASA Electronics Research Center, 575 Technology Square, Cambridge, Massachusetts, and completed under Dr. F. C. Schwarz and Mr. J. F. Been, NASA Lewis Research Center, Cleveland, Ohio.

# TABLE OF CONTENTS

|    |                                                                                                                                                                                                                                    | PAGI                     |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A. | CONTRACT OBJECTIVE                                                                                                                                                                                                                 | iii                      |

| в. | SUMMARY OF PERFORMANCE TOWARD THE CONTRACT REQUIREMENTS                                                                                                                                                                            | ii                       |

| c. | RECOMMENDATIONS FOR FUTURE WORK                                                                                                                                                                                                    | v                        |

| 1. | INTRODUCTION                                                                                                                                                                                                                       | 1                        |

|    | <ul> <li>1.1 Power Processing</li> <li>1.2 The Series Inverter</li> <li>1.3 The Thyristor and the Gate Assisted Thyristor</li> <li>1.4 The Gate Assisted, Fast Turn-Off Thyristor Switch</li> <li>1.5 Statement of Work</li> </ul> | 1<br>2<br>11<br>12<br>21 |

| 2. | PROCESSING                                                                                                                                                                                                                         | 25                       |

|    | 2.1 Introduction 2.2 Standard Processing 2.3 Process Improvements 2.4 Blocking Voltages                                                                                                                                            | 25<br>25<br>30<br>30     |

| 3. | CHARGE EXTRACTION AND GATE-EMITTER CHARACTERISTICS                                                                                                                                                                                 | 36                       |

|    | 3.1 Introduction 3.2 Gate-Emitter Leakage 3.3 The Limits of Charge Extraction                                                                                                                                                      | 36<br>37<br>46           |

| 4. | TESTING                                                                                                                                                                                                                            | 50                       |

|    | 4.1 Introduction 4.2 Static Characteristics 4.3 Dynamic Measurements 4.4 Conclusions                                                                                                                                               | 50<br>51<br>57<br>76     |

| 5. | DEVICE DATA                                                                                                                                                                                                                        | 77                       |

| 6. | CONCLUSIONS AND RECOMMENDATIONS                                                                                                                                                                                                    | 82                       |

| 7. | NEW TECHNOLOGY                                                                                                                                                                                                                     | 83                       |

|    | REFERENCES                                                                                                                                                                                                                         | 84                       |

# LIST OF ILLUSTRATIONS

| FIGURE   |                                                                             | PAGE       |

|----------|-----------------------------------------------------------------------------|------------|

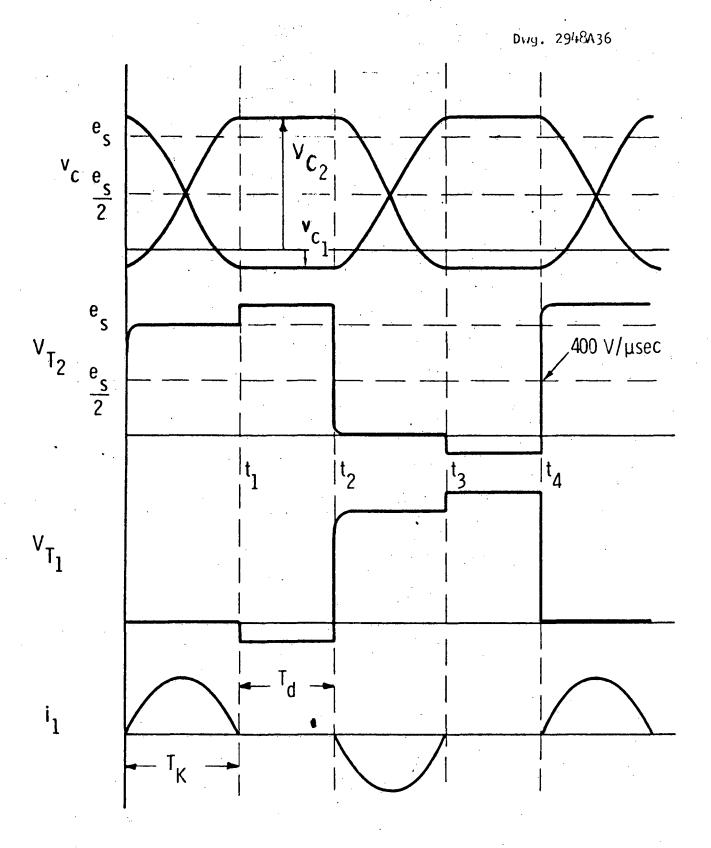

| 1        | Load Insensitive Series Inverter Waveforms                                  | 4          |

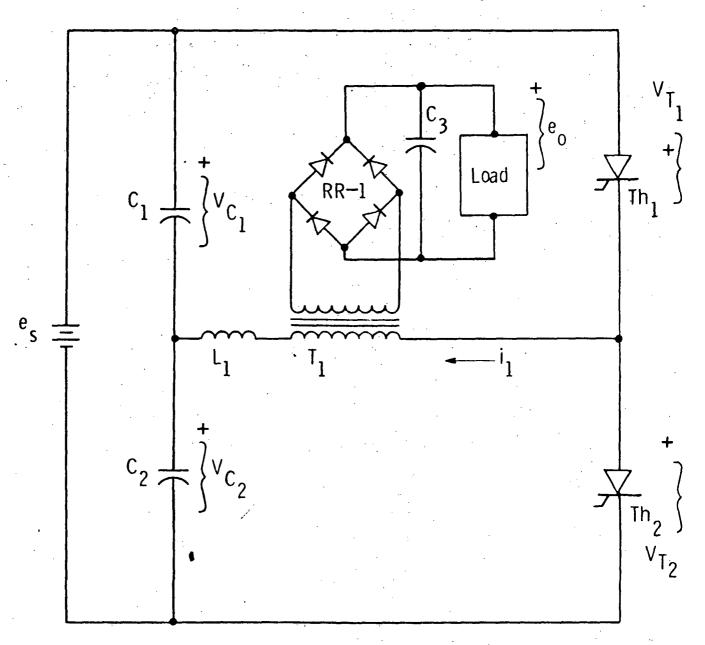

| 2        | Load Insensitive Series Inverter                                            | 7          |

| 3        | Load Insensitive Series Inverter Waveforms                                  | 8          |

| 4        | Nomenclature for Turn-off Waveforms                                         | 16         |

| 5        | Lateral Voltage Drop Under the Cathode                                      | 20         |

| 6        | Sweep-out with Reverse Current and Decay of Charges                         | 22         |

| 7        | Current Fall with Gate Drive                                                | 23         |

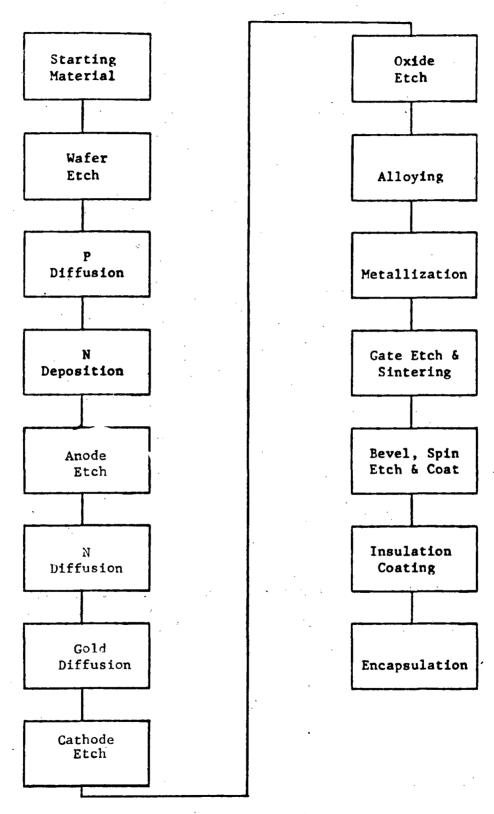

| 8        | Process Flow for GATT                                                       | 26         |

| 9        | Compression Bonding Encapsulation                                           | 28         |

| 10       | Pre-encapsulation Assembly                                                  | 29         |

| 11       | Blocking Voltage Versus Temperature                                         | 31         |

| 12       | Sections of GATT 52B and 52C Showing WB                                     | 33         |

| 13       | Resistivity Profile of GATT Run 52B                                         | 34         |

| 14       | Resistivity Profile of GATT Run 52C                                         | 35         |

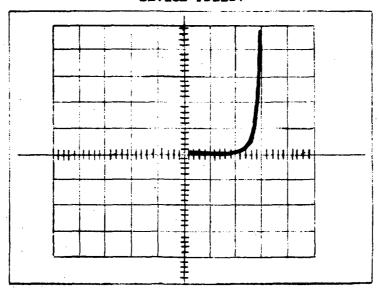

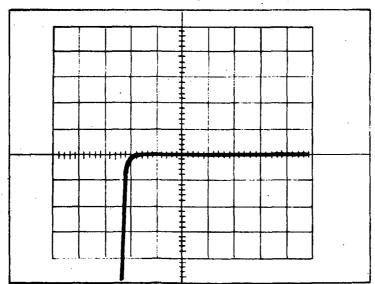

| 15       | Gate-Cathode Forward and Reverse Characteristics                            | 53<br>54   |

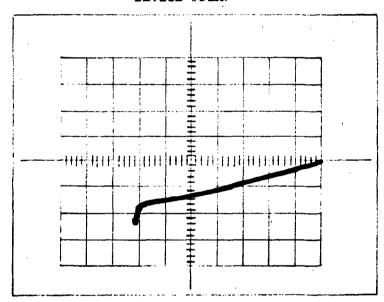

| 16<br>17 | Equivalent Gate Leakage Resistance Device 52A7 Reverse Gate-Cathode         | 54<br>55   |

| 18       |                                                                             | 59         |

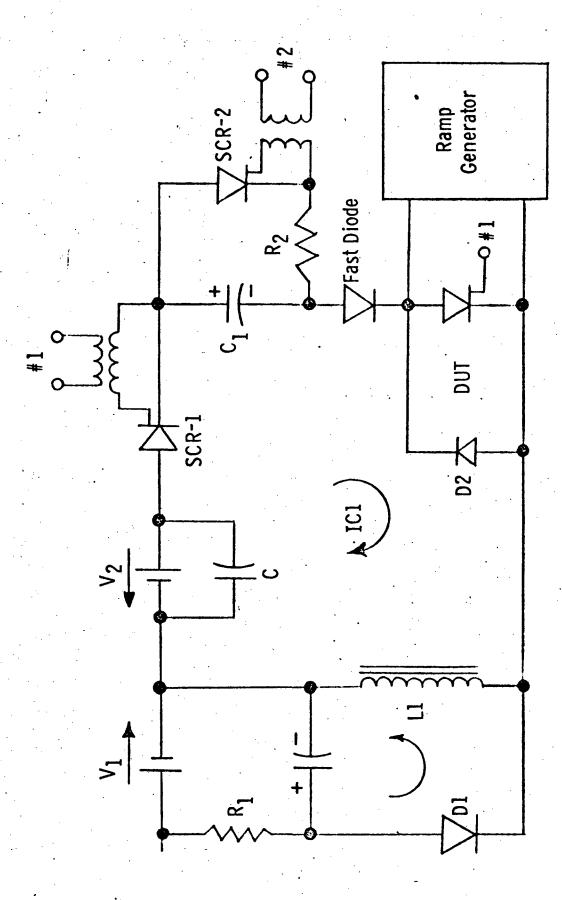

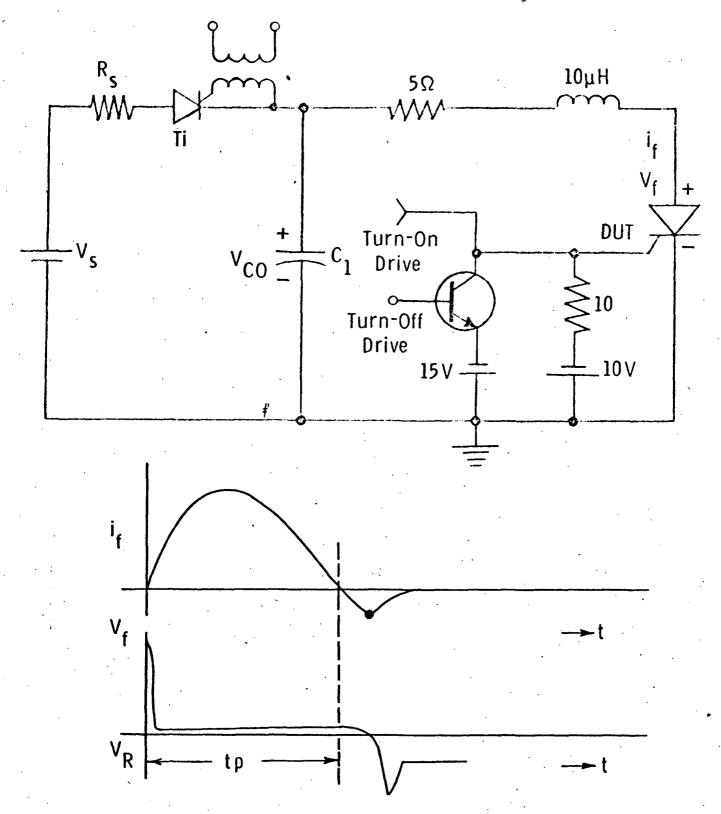

| 16<br>19 | Dynamic Turn-on as a Function of Gate Drive  Electrical Test Circuit #1     | 60         |

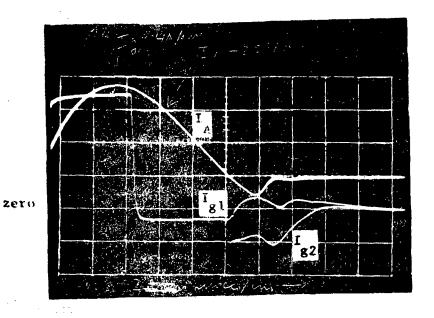

| 20       | GATT Turn-off Waveforms                                                     | 61         |

| 20<br>21 | Bypass Diodes and GATT Turn-off                                             | 64         |

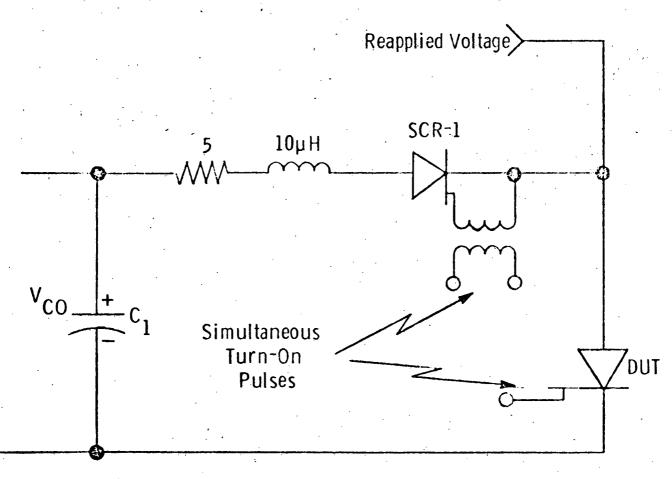

| 22       | Test Circuit #2                                                             | 65         |

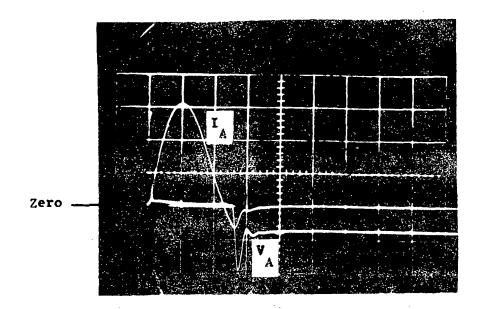

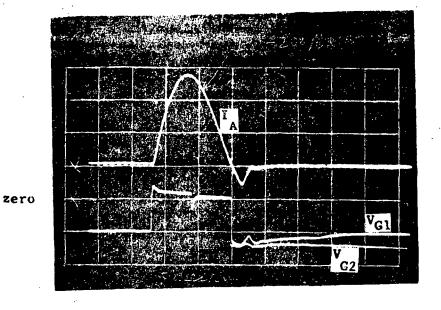

| 23       | Performance in Test Circuit #2                                              | 67         |

| 24       | Reverse Anode Recovery and Turn-on Conditions                               | 67         |

| 25       | Effect of Continuous Biasing to $V_C = -10V$ with $10\Omega$ R <sub>G</sub> | 68         |

| 26       | GATT Operating in Turn-off Mode                                             | 70         |

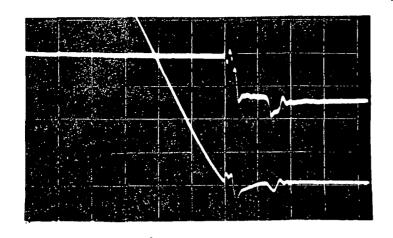

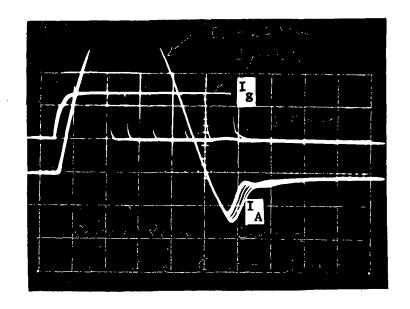

| 27       | Test Circuit #2 with SCR Isolation                                          | 72         |

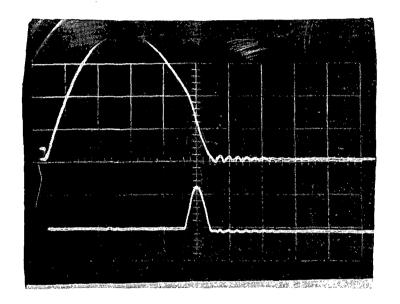

| 28       | Turn-off with Gate Assist                                                   | 73         |

| 29       | Turn-off with Gate Assist, no Reverse Current                               | 75         |

| TABLE    |                                                                             |            |

| 1        | Design Objectives for the GATT Device                                       | 13         |

| 2        | Design Differences Between 52B and 52C                                      | 32         |

| 3        | Variability in Emitter Finger Characteristics                               | <b>3</b> 8 |

| 4        | Maximum Turn-off Capability of Eight Fingers on a Single Wafer              |            |

| 5        | GATT Turn-off Tests; tgr and Peak Anode Current                             | 63         |

| 6        | GATT Static Tests, Four Devices                                             | 78         |

| 7        | GATT Static Tests, Nine Devices                                             | 79         |

| 8<br>9   | GATT Dynamic Tests, Nine Devices                                            | 80         |

| 9        | Flectrical Characteristics of Devices Delivered to NASA Lewis               | Ol         |

#### A. CONTRACT OBJECTIVE

The objective of this contract was to develop a thyristor type of switch that will recover its forward current blocking capability within 2 microseconds when used in a series inverter.

#### B. SUMMARY OF PERFORMANCE TOWARD THE CONTRACT REQUIREMENTS

Westinghouse has successfully accomplished the objective of the contract and completed the work requirements stated in Section C of the contract. The work statement includes four items, which are discussed below in sequence:

<u>Item 1 -- To formulate a philosophy of thyristor design consistent with</u> the objective of meeting the following specifications:

| Max. Forward and Reverse<br>Blocking Voltage | V<br>max        | 600V         |

|----------------------------------------------|-----------------|--------------|

| Max. Anode Current                           | I <sub>av</sub> | 50A          |

| Recovery Time                                |                 | 2 μ <b>s</b> |

| dv/dt                                        |                 | 400V/μs      |

| $v_{\mathbf{f}}$                             |                 | 2V @ 50A     |

Such a design was formulated and devices were made and delivered in accordance with Item 2 below.

Item 2 -- Device fabrication. The original contract calling for ten (10) devices was extended and the required number was increased by twelve (12), making a total of twenty-two (22) units in all. These twenty-two (22) units were delivered along with an additional two (2) units to be used for display purposes. Of the twenty-two (22) good units, nineteen (19) met all of the

specifications stated in Item 1 above, one (1) unit met the requirements except for  $V_F$ , which was 2.3 volts at 50 amps rather than the desired value of 2.0 volts at 50 amps, and two (2) had low reverse blocking voltage at 100°C. In view of the difficulty experienced in making thyristor type switches that will recover their forward current blocking capability within two microseconds, Westinghouse feels that such minor deviations from the  $V_F$  and voltage specifications are acceptable within the limits expected for a development contract of this type and that the contract requirements have been met.

Item 3 -- Test circuits. The required testing circuits were built and performed in an entirely acceptable manner. The circuits were specifically designed to relate to the series inverter of Schwarz, discussed in Section 1.2 of this report, and units so tested are expected to perform adequately in that circuit when it is built.

Item 4 -- Identification of areas for future investigation. This item is discussed more completely in a later section. In summary, the problem areas relate particularly to the manufacturability and encapsulation of the device. The basic design of the npnp silicon sandwich from which the device is fabricated has proved to be more than adequate. The problems encountered in the fabrication, however, dictate a minor but -- in terms of manufacturability -- significant departure from the mesa structure now employed. These problem areas are well defined because of the present contract and future work should result in a completely manufacturable device.

Westinghouse has also met the terms of the contract in the delivery of reports and in Inspection and Acceptance criteria.

#### C. RECOMMENDATIONS FOR FUTURE WORK

A natural recommendation for future effort on the gate assisted turn-off thyristor (GATT) device is the extension of the device capability to higher levels in terms of blocking voltage, current handling capability, and switching speed. The results of the present effort, however, show that a careful re-examination of the process techniques should accompany any further development efforts.

Four types of process problems were encountered during the contract work.

- 1) Cathode Mesas

- a) the mesa formation itself,

- b) cathode mesa leakage currents, and

- c) contacting of the mesas.

- 2) Diffusion

- a) control of bulk lifetime, and

- b) reproducibility of the p-diffusion

- 3) Blocking Voltage Degradation induced by non-optimum processing and encapsulation.

- 4) Device Encapsulation

In its detailed interaction with the selected mesas.

All of these problem areas are fabrication/processing problems. Although they do indeed impact the device design, the net effect must be considered as a yield problem since the devices that were successfully completed did, in fact, meet specification, and improvements in parameter performance can be projected based on well known principles of PNPN device design.

To approach the fabrication problems, we recommend that:

- 1) The cathode-gate junctions be prepared by a planar technique, obviating present problems in control of the mesa etch, the cathode-gate geometry, and various mesa etch mask defects.

- 2) All of the junctions be provided with an inorganic passivation.

- 3) Thick cathode and gate metallization techniques be developed to relieve packaging stress problems.

- 4) Devise more reproducible p-diffusion and lifetime control processes.

- 5) Improve package design to relieve local stress problems.

#### 1. INTRODUCTION

## 1.1 Power Processing

A broad area of the field of power processing deals with the conversion of dc power from one level of voltage to another. In some systems, the prime power is supplied by relatively low voltage exotic sources producing dc output voltages too low and too variable to be used directly. In others, the dc source is the rectified output of an ac line which must be adjusted to the desired voltage level and then regulated at that point.

Much technology has been generated in this field, making possible a solution to almost any system problem presented. However, when examined critically from the standpoints of equipment size, weight, reliability, and efficiency, each circuit solution represents a certain compromise of desired properties. It is always desirable, therefore, to advance the art with new technology which offers an improved compromise of the system evaluation criteria described.

Circuits for the conversion of dc power from one level to another must of necessity interrupt dc currents. This can be done by inserting an active switching device in the dc line, or alternatively by utilizing an energy storage device. At present, no solid-state dc switch is available for use at high power levels, so the technique normally used for the former is to force commutate a thyristor. This technique, although feasible, results in high energy transients which are detrimental to efficiency and reliability, and contribute heavily to undesirable electromagnetic interference. Circuits of this type also suffer disadvantages in size and weight and are limited in internal operating frequency by the recovery times of the thyristors, which are rather long.

A more desirable circuit configuration employs lossless energy storage devices, such a inductors and capacitors, to effectively interrupt dc currents by natural commutation. In such circuits, solid-state devices without turn-off properties, such as thyristors, may be employed without the need for commutating circuitry. Because commutation takes place naturally, no large voltage or current transients need occur, increasing reliability and efficiency.

Circuits of this type do work well and exhibit all of the previously discussed advantages. They are, however, limited in size and weight by the maximum internal carrier frequency, which is in turn limited by the relatively long recovery times of the thyristors used. A considerable improvement in circuit performance would result from the use of a solid-state switching device which, upon current interruption by external means, would require only a short interval before forward voltage may be reapplied. It need not include the ability to interrupt current by application of a gate signal.

The gate assisted turn-off thyristor (GATT) is such a device. It was developed on this contract.

#### 1.2 The Series Inverter

The intended use for the GATT device of this contract is a series inverter circuit. Although the device proposed will be useful in any series inverter configuration, it will be assumed for the purposes of this program that the specific circuit under consideration is that described by Schwarz <sup>1,2</sup>. The basic motivation for the system described by Schwarz was the need to develop a power conversion system useful for space application. Of foremost interest in such designs are the considerations of efficiency, power density, and reliability.

After first studying various solid state switches, it was concluded by Schwarz that resonant circuits are best suited for the utilization of thyristors in power conditioning systems. Of foremost consideration in this selection were the surge capacity of thyristors and the ability to be turned 'on' and 'off' at pulse repetition rates in excess of ten kilohertz, yet with smaller power dissipation than transistors in parallel inverters. Recent advances with thyristors have enabled turn-on at high repetition rates and high rates of rise of current; and, thyristors may be turned off by natural commutation, with low losses in the process.

The dissipation features of thyristors versus transistors were aptly demonstrated by the use of a ten megahertz bandwidth wattmeter.  $^3$ The turn-off dissipation properties of the naturally commutated thyristor thus obtained were instrumental in selection of the series inverter as the power conditioner with which to transform dc power to ac power. inherent property of the series inverter to provide natural commutation of the thyristor currents results in relatively low thyristor dissipation which is almost independent of the pulse repetition rate at constant duty cycle. The ensuing power dissipation in the thyristor is substantially lower than that normally experienced with transistors or force commutated thy-The framework of the inverter efficiency design is then based upon this independence of power dissipation from frequency due to the low dissipation experienced during turn-on and turn-off phases of the switching processes. The selection of the switch then leads to the selection of the circuit which works best with the useful properties of the switch: the thyristor-series inverter combination.

The operating point of the series inverter is next considered from the standpoint of efficiency. Figure 1 shows the series inverter current waveform (i<sub>1</sub>). The form factor of the current waveform may be expressed as

1) Form Factor =

$$\rho_1 = \frac{i_{rms}}{i_{av}} = \frac{\pi}{2\sqrt{2}} \sqrt{1 + T_d/T_k} = \frac{\pi}{2\sqrt{2}} \sqrt{1 + \frac{T_d}{\pi LC}}$$

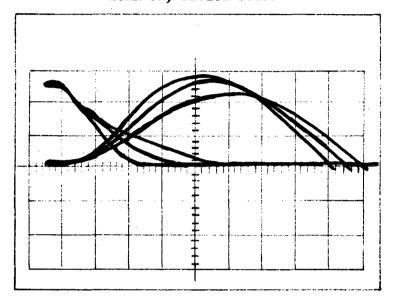

Fig. 1 —Load insensitive series invertor waveforms

J. W. Brewster I.m.-m.j. 5-21-71 where  $T_d = delay$  time between end of conduction of thyristor 1 and start of conduction of thyristor 2.

> $T_k$  = half period of the natural resonant frequency of the system = V LC where L and C are equivalent series inductance and capacitance of the series inverter.

From Schwarz, the relative power loss in the system can be approximated by

2)

$$1 - h = \rho_1^2 \frac{R_S}{R_L^1 + R_S}$$

where h = the efficiency of the system

$R_S$  = equivalent inverter series resistance  $R_L^{1}$  = equivalent inverter load resistance

Once the series inverter design is fixed, losses can be minimized by reducing the current form factor  $\rho_i$ . From (1), the form factor is minimized by reduction of T, which, as already defined, is limited to a greater value than toff, the standard turn-off time of a thyristor under self-commutating performance. Before development of the gate-assisted thyristor, recovery times of conventional thyristors were limited to 10  $\mu s$ .

Such devices, with 10 µsec turn off time, however, allowed Schwarz to construct a series inverter with efficiency in excess of 95%, power output of 2kW, and power density of 0.4 kW/kg. The purpose of this contract was to develop a thyristor which would recover its forward blocking properties after normal self commutation within 2 us. With this device, Schwarz contemplates an improved inverter with efficiencies of the order of 95%, similar power output, and power densities of 1 kW/kg. He assumes the series inverter natural frequency could be increased to 50 kHz, and that economies of size will result from the 50 kHz frequency due to reduction of physical size and weight of transformers and of the associated energy storage elements. It is also expected that efficiencies will not deteriorate.

As a concluding point, the availability of high current thyristor switches reduces the need for unreliable paralleling. Thus, the reliability of the Schwarz inverter design has additional merit because the paralleling of groups of solid state switches, with their attendant increase in number, reduces the probability of failures.

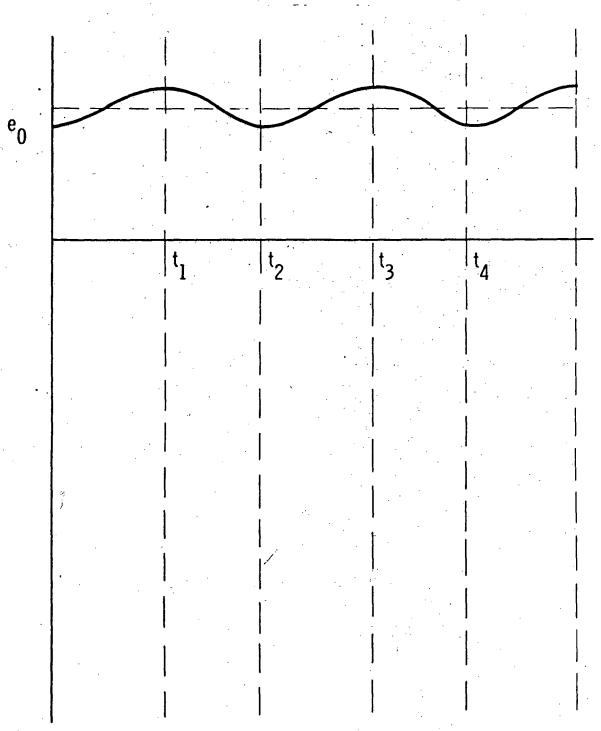

A symbolic schematic of the series inverter is shown in Figure 2. Waveforms derived from Figure 2 are shown in Figures 1 & 3. The arrangement is conventional and consists of two series inverter circuits for which components  $L_1$  and load transformer  $T_1$  are shared by both circuits. Operation consists of the alternate sharing of current by switch  $\operatorname{Th}_1$  and  $\operatorname{Th}_2$ . As an example, when Th<sub>1</sub> conducts, C<sub>1</sub> provides half of the load current pulse by discharging from some value greater than e to a negative voltage which is some fraction of e. At the same time, capacitor C2 resonantly charges from some negative potential which is some fraction of e to a positive value greater than  $e_s$ . Capacitors  $C_1$  and  $C_2$  resonate with inductor  $L_1$ , and the sum of potentials across C1 plus C2 is always e3. The waveforms in Figure 1 illustrate the sequence of events of the inverter operation. Assuming operation starts at time  $t_1$ , then  $c_2$  is charged to  $e_s + \Delta v$  and  $c_1$  is charged to  $-\Delta$  v. At time  $t_1$  thyristor  $Th_1$  is naturally commutated and a delay time  $T_d \ge t_{off}$  must exist before  $Th_2$  can be triggered. The delay time of  $T_d$  is shown in Figure 1. After the delay time, Th<sub>2</sub> is triggered and at the instant that Th, is triggered, Th, experiences a rise in anode voltage at a rate which is less than or equal to 400V per microsecond. Capacitor C2 discharges producing a negative going current pulse through transformer  $T_1$ . During the conduction of  $\mathrm{Th}_2$ , the voltage across  $\mathrm{C}_2$  falls resonantly from  $\mathrm{e}_\mathrm{s} + \Delta \, \mathrm{v}$ to -  $\triangle v_1$  and the voltage across  $C_1$  rises from - $\triangle$  v to  $e_s$  +  $\triangle$ v. Hence at time  $t_3$  the potentials of  $C_1$  and  $C_2$  have reversed from their position at time  $t_1$ . After a delay  $T_d$ , thyristor  $Th_1$  conducts, provides a positive current pulse through transformer  $T_1$  and the potentials of  $C_1$  and  $C_2$  return to their values they assumed at time  $t_1$ . In this cycle, an ac current pulse was developed through  $L_1$  and transformer  $T_1$ . Rectifier RR-1 in the secondary of  $T_1$  reconverts the pulsating current to unipolar pulses which charge  $C_3$ to a level of e.

Fig. 2-Load insensitive series invertor

Fig. 3 -Load insensitive series invertor waveform

The series inverter is well known for its poor regulation features when operated at a constant pulse rate. The inverter discussed in this report regulates the frequency of thyristor triggering to maintain output voltage constant. This is achieved by the standard usage of comparators, voltage controlled oscillator, and triggering systems. One other novel system of the Schwarz inverter is the use of two anti-parallel thyristors placed across inductor  $L_1$  and transformer  $T_1$  in such fashion as to "secure a contained excursion of the capacitor voltage waveform and an approximately constant efficiency for a given load and for variations of the same voltage e." The two auxiliary thyristors are triggered during conduction of a main thyristor such that main thyristor current is reduced to zero and energy stored in L1 causes continued circulation of load current through T1 and ultimately into the load. Discussion of the inverter control system and voltage stabilization methods are found in the literature 1,2 and are not germane to the requirements of the gate assisted thyristor. These topics will not therefore, be further amplified.

The primary interest of the gate assist thyristor development is the relationship of the GATT device performance to the requirements of the series-inverter. In general it is required that the GATT performance as a thyristor at least equate to the comparable thyristors used by Schwarz, except for recovery time. These are the thyristors spoken of with 10 µs recovery periods and which were run at 20 kHz. A one for one correspondence between standard thyristor and gate assist thyristor does not exist, although many characteristics and ratings are similar. The maximum 10 kHz operating frequency of the series inverter and the contemplated 50 kHz operating frequency demand full concurrent frequency characterization for either range. This characterization is considered outside the scope of the gate assist development and requires additional effort. Most thyristors with full frequency characterization use some form of "amplifying gate" structure to achieve fast turn-on. Full turn-on drive is supplied to annular power gates through auxiliary gates which receive drive from the anode source.

The gate assisted thyristor uses a long emitter-gate edge because of the finger emitter structure which enhances extraction of P-base charge, but which also requires a large drive for effective turn-on. Since drive to the long emitter periphery does not originate with the anode as with the amplifying gate, high drive for effective turn-on must be supplied from the actual gate of the gate assist thyristors. This is as large as a 15A pulse.

Another feature of gate-assist thyristor which alters normal thyristor performance is the lack of gate emitter shunts which are used to obtain high dv/dt rating. Since these shunts would simply act to bypass gate assist drive, making the gate assist process more difficult, shunts are not used. While gate assist performance is helped, transient susceptibility deteriorates. However, the effect of gate-emitter shunts may be obtained if the devices are always operated with an external bias resistor combination between gate and emitter such that dv/dt ratings in excess of 400 V/ $\mu$ s are obtained. The bias source voltage is always less than the gate emitter avalanche voltage and losses due to the bias are small.

Several parameters of the GATT switch bear inter-related characteristics which should be understood when testing and applying these units. The characteristics reflect the normal design trade-offs required to product a gate-assist switch. As an example, latching currents for gate-assist units could be as high as six amperes. In general, units optimized for turn-off will sacrifice some switching performance. Hence, the current level at which the sum of the alphas equals one could be much higher than the normal thyristor. As a consequence, other performance is influenced by this feature. Minimum gate voltage ( $V_{\rm GT}$ ) and gate current ( $I_{\rm GT}$ ) to cause turn-on or firing are impeded by high latching current. If a gate-assist device with a minimal gate drive and high latching current is tested at current levels below the latching current, there may result a condition in which the device is

forward biased but not truly switched; yet a high anode voltage and relatively high anode current of several amperes may exist in the device. Such testing has frequently resulted in catastrophic failure due to the high dissipative nature of the combination of conditions extant. As a result, the characteristics of  $V_{GT}$  and  $I_{GT}$  are normally not tested for this device. Latching currents are also measured at anode voltage levels no higher than 25 volts to avoid excessive dissipation if the latching current is high. If operation is required at current levels below the latching current level, a continuous drive of at least one-quarter of the latching current level must be supplied.

# 1.3 The Thyristor and the Gate Assisted Thyristor

In the above type of circuit, the thyristor is always at a disadvantage when compared with a device with gate control. To obtain a short turn-off time with a thyristor, the stored charge must be swept out by the application of a large reverse bias voltage with the accompanying flow of reverse current. The circuit under consideration does not provide the required reverse voltage, with the result that the thyristor turn-off times realized are long. When a GATT device is used, however, reverse gate current is applied during the interval  $0 \le t \le t_1$  as defined in Figure 6, when anode voltage is essentially zero. As a result of this current, some of the charge stored in the device is swept out. The remaining charge is swept out when forward anode voltage is reapplied, but at this time, sweepout takes place in the presence of the flow of reverse gate current, which is the normal condition of operation of a GATT. As a result, the GATT operates in its normal mode in this circuit and optimum performance is obtained, as opposed to use of even the fast-switching thyristor, which is not operated in optimum fashion by this circuit and yields nonoptimum performance. The only circuit change necessary for use of the GATT will be the inclusion of a reverse bias gate pulse generator that will apply reverse bias to each GATT following anode current commutation.

# 1.4 The Gate Assisted, Fast Turn-Off Thyristor Switch

The circuit requirements of a typical series inverter circuit as discussed in Section 1.2 can be summarized in the two major specifications, namely, the recovery time and the rate of reapplied forward blocking voltage. Very few, if any, commercially available 50A fast turn-off thyristors have turn-off times less than 10  $\mu s$ , when the rate of reapplication of voltage is 50 or 100 V/ $\mu s$ . At a 400 V/ $\mu s$  rate of reapplied voltage, their turn-off times become much longer. The design of a specially constructed thyristor was therefore necessary. This section describes the objectives and the direction of the design philosophy which achieved them, while the next section delineates the testing goals.

# 1.4.1 Design Objectives and Philosophies

The objectives for the GATT device are given in Table 1. Certain parameters usually given in thyristor specifications, holding current, gate current to fire, gate voltage to fire, and turn-off time with anode voltage are missing from the list because of their limited meaning in the context of a GATT type of device. The limitations are in part theoretical, and in part practical, as will now be shown.

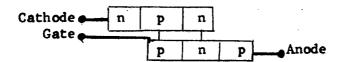

Four-layer pnpn switches are commonly discussed in terms of their two-transistor analogs, which involves an npn and a pnp transistor combined.

From this model, the static forward voltage blocking characteristic,  $V_{BO}$ , is developed as is the  $V_{CEO}$  of a transistor, and depends upon the anode current  $I_A$ , as

$$I_{A} = \frac{\alpha \text{ pnp} \quad I_{g} + I_{CBO} + I_{CBO}}{1 - \alpha_{npn} - \alpha_{pnp}}$$

(1)

Table 1 -- Design Objectives for the GATT Devices

| PARAMETER                                                                          |              | SYMBOL               | VALUE |

|------------------------------------------------------------------------------------|--------------|----------------------|-------|

| Maximum Forward Blocking Voltage                                                   | Volts        | V <sub>FB</sub>      | 600   |

| Maximum Reverse Blocking Voltage                                                   | Volts        | $v_{RB}$             | 600   |

| Maximum Forward Drop at $I_A = 50$ A                                               | Volts        | $v_{\mathbf{F}}$     | 2.0   |

| Maximum Junction Temperature                                                       | •c           | Tj                   | 125°  |

| Maximum Crest Anode Current                                                        | Amps         | IA                   | 50    |

| Recovery Time (See Fig. 4)                                                         |              |                      | •     |

| after $I_A = 50A$ is circuit                                                       |              |                      |       |

| commutated off                                                                     | με           | t <sub>r</sub>       | 2     |

| Maximum Initial Rate of Reapplied                                                  |              |                      |       |

| Voltage Rise , Exponential to $V_{\overline{FB}}$ Maximum, at $T_j = 100^{\circ}C$ | <b>V</b> /µ8 | dV <sub>RM</sub> /dt | 400   |

| Maximum Rate of Current Removal                                                    | A/µs         | di/dt                | 10    |

In this model, and even in more realistic extensions, the separate  $\alpha$ 's, or common base current gains of the separate component transistors figure very prominently. Switching of the thyristor into the on state occurs when the  $\alpha$ 's sum to unity, or greater.

$$\alpha_{\text{npn}} + \alpha_{\text{pnp}} \geq 1$$

(2)

Once switched on, the pnpn device will remain on so long as equation 2 is satisfied.

Design of a thyristor for specific applications entails proper selection of the geometrics and resistivities to specify compn and copp for the characteristics desired. Thyristors of "standard" design typically involve compn  $\cong 10$  coppn at the switching point. The  $\alpha$ 's are current dependent, as is the case in any transistor, and gate turn-on triggering is accomplished by base drive of the npn transistor to raise its current level, and thereby its  $\alpha$  to the point where equation 2 is satisfied. In the design of a gate assisted turn-off thyristor, it is equally necessary that the gate have control over the switching characteristics; therefore, the junction designs are also selected so that

$$\alpha npn > \alpha pnp$$

Fast turn-off is required of the GATT device, and to accomplish this, the units were gold-doped. By thus shortening the lifetime, the values of compn and compn at any given current level are reduced. Thus, in general, the current drive to cause switching is greater for faster turn-off device capability.

Once switched on, a thyristor will conduct until the current drive is reduced so that equation 2 is no longer satisfied. At this point, the device switches off and the minimum current required to keep it on is known as the holding current. In these fast, high power devices, the holding current is much greater than for "standard" devices, and in most cases, when we endeavored to determine its value, the devices were destroyed by a second-breakdown type of fault; i.e., as is the case

with a transistor, transit-time through the safe operating area is significant for a GATT device. The common technique for measuring holding current compares to a "dc" transient, and resulted in device destruction due to the high dissipation involved.

Similarly, efforts to determine minimum gate current and gate voltage to fire also involve operation of the device in a dissipative mode, and resulted in device destruction.

Determination of these parameters will be essential for eventual safe application of the GATT device. Since, however, their determination is frequently destructive to the device itself, they must be approached in the same fashion as are the surge current and di/dt ratings of conventional thyristors. That is, by a statistical study of a stable production line.

Determination of turn-off time with anode voltage was not made, since no application of the device is this mode was foreseen.

One final area of device design current gain, where the GATT device differs significantly from a conventional thyristor, deserves comment, and is treated below. We now define the test conditions used in device characterization.

Referring to Figure 4, the gate drive pulses are defined on the basis that the turn off is circuit-initiated, i.e., the anode voltage goes through zero. This time and rate of current removal are dependent on the components in the series inverter such as the capacitance, leakage inductance, and switching times of the diodes, etc. However, the start of current decrease can be used to trigger the assisting turn-off pulse applied to the gate. This voltage has a minimal source impedance; thus the voltage will not exceed the breakdown voltage of the gate-cathode junction throughout the entire t, period.

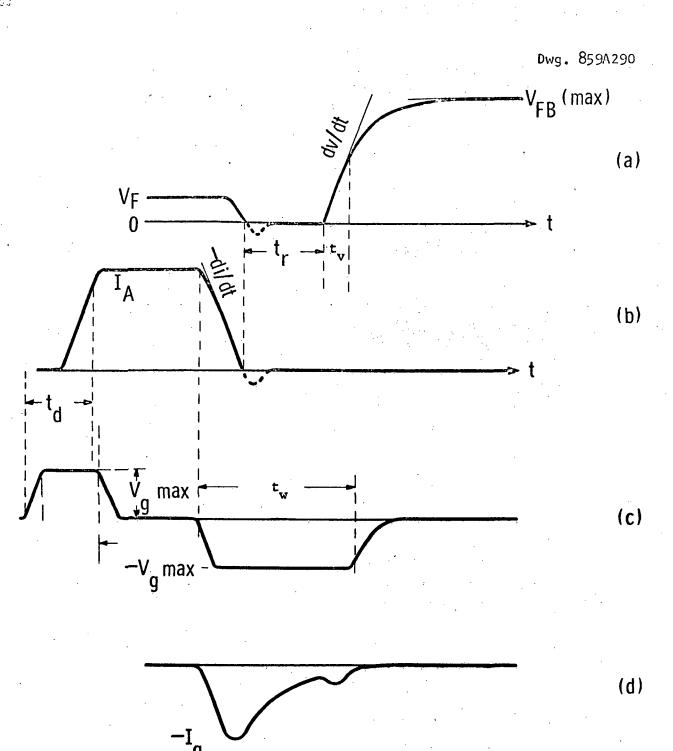

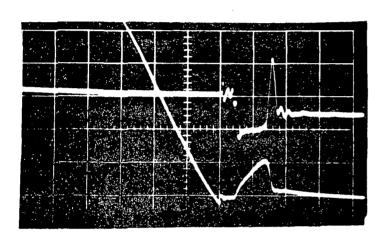

Figure 4 - Nomenclature for turn-off waveform.

- a) Anode Cathode Voltage

- b) Anode Current

- c) Gate Cathode Voltage

- d) Gate Current

The  $t_{\rm W}$  is the time in which the assisting gate pulse must be applied; not only will it extract the remaining stored charges, it should also remove the d (CV)/dt current when the forward blocking voltage is reapplied. The gate current is really a dependent variable since the magnitude of the current is controlled by the available charges from the device. Thus the gate current will reach a peak and will decrease as the charge supply dwindles. For this reason, we do not use as a criterion the ratio of steady maximum anode current to instantaneous peak gate reverse current,  $I_{\rm A}/I_{\rm G}$ , which is commonly and misleadingly called "turn-off gain".

## 1.4.2 Device Design Consideration

The turn-off limitations of conventional thyristors are due mainly to the residual stored charge in the device. If this charge can be removed more rapidly through the application of a supplementary drive signal to the gate, the delay time before the forward blocking voltage can be reapplied is significantly reduced.

## Function of Gate Control

The conventional thyristor is a regenerative device; its gate is used to initiate cathode injection, which in turn causes anode injection. This action continues as regenerative feedback to drive its blocking junction into deep saturation for forward conduction. The gate loses its control once the regeneration takes effect. After the area adjacent to the gate is triggered "on", while the more remote regions are still blocking, some lateral flow of current will occur. This divergence of the current flow provides the required triggering current for its neighboring area to trigger it on. The "on" region thus spreads out to cover the whole junction area, permitting the device to carry hundreds of amperes. The spreading mechanism has been experimentally verified and its velocity determined for certain types of construction.

This mechanism superficially gives an extremely high "turn-on gain" of a thyristor and is generally independent of its maximum current capability.

In a filamentary section of PNPN where lateral spreading is not a factor, although the gate is not needed to keep the device in conduction due to its internal regenerative feedback, it is possible to draw enough current out of the gate to disrupt its regenerative cycle and to return it to the blocking or "off" state. In the same way, the gate of a thyristor can be reverse-biased to prevent it from injecting charge carriers or to remove excess carriers due to regeneration at high temperatures or to remove d(CV)/dt current, especially when dv/dt is high.

The last stated characteristics are compatible with series inverters. However, in a high current, large area device where the current spreading feature is used, only a small area surrounding the gate electrode can be effectively controlled. The limitation is due to lateral voltage drop in the gate.

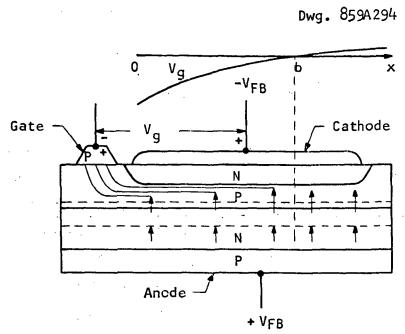

## Lateral Voltage Drop

of forward blocking voltage  $V_{FB}$  will cause the space charge region to widen toward a new equilibrium value. In doing so, it develops a current d(CV)/dt uniformly over the whole area. This current is in a sense equivalent to a positive gate current in the P-base region with no external gate connection. Now if a reverse bias is present prior to the application of  $V_{FB}$ , the cathode-gate junction may be already cut off (depending on -di/dt), and there can be no injection from the cathode. With this reverse gate voltage, the current d(CV)/dt or the displacement charge d(CV), will be swept toward the gate electrode. The P-base region, however, has a certain resistivity due to its level of doping. If a unit length of this section is considered and if b is a point where the voltage drop is zero (Figure 5), the voltage drop  $V_{CB}$  at the edge is

(Figure 5), the voltage drop

$$V_{go}$$

at the edge is

$$V_{go} = \frac{Rb^2}{2} = \frac{d(CV)}{dt}$$

(1)

If the gate drive voltage  $V_g$  is greater than  $V_{go}$ , the x=b point will shift further from the gate into the cathode area to increase the distance b so that  $V_{go}=V_g$ . More gate current will be drawn since total  $I_g$  is proportional to b.

However, the displacement current in the region x > b cannot be swept out. In that area, the cathode junction is thus forward biased and may permit the device to turn on. In other words, the gate has no control over this area.

Figure 5 - Lateral voltage drop under the cathode.

It is obvious that higher negative gate voltages can control larger cathode areas. However, the quadratic relationship soon will demand voltages at  $\mathbf{x} = \mathbf{0}$  greater than the breakdown voltage of the cathode gate junction.

Since the breakdown voltage and the P-base resistivity o are usually fixed for a thyristor, the most profitable approach to render full gate control is to make the cathode in narrow strips with the gate surrounding it. The width of the strip can be easily calculated from Equation 1 and the doping profile.

In conclusion, the basic requirement for the gate to maintain control of a large area device is to use long and narrow cathode emitters. This is the essence of the GATT device. The maximum utilization of these and the electrical contact that permits uniform distribution of gate current have been central to this contract.

## Removal of Stored Charges

In the foregoing discussion, we have assumed that the circuit commutation is fully effective. In other words, the cathode junction is blocking and gate assistance is to draw out the d(CV)/dt current. However, if the circuit voltage and current merely drop to zero without effective reverse sweeping of the excess charges in the device, the gate may function differently.

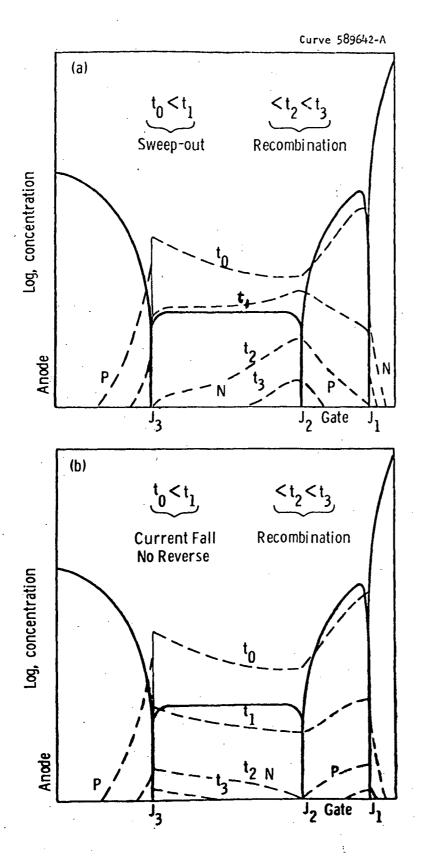

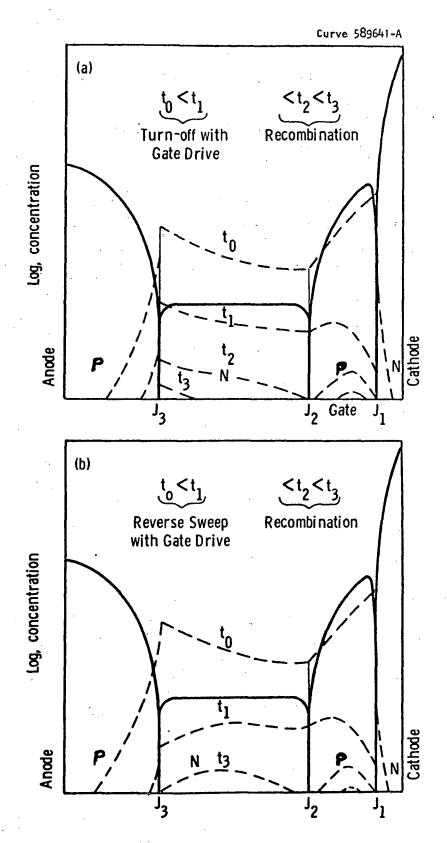

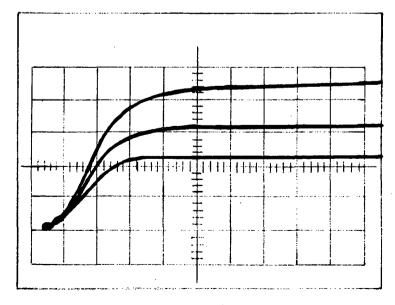

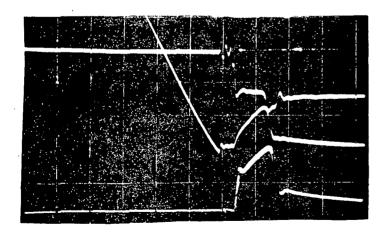

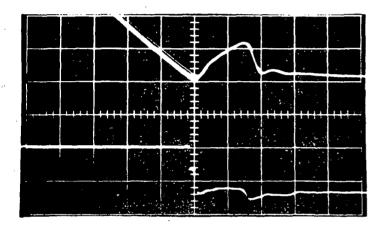

Using the charge control approximation, the switching characteristics in general have been calculated (References 6 and 7). Similarly, the charge distribution under our specific conditions can be illustrated. Figure 6 shows the charge decay without gate control: Fig. 6a shows the effect of forced commutation with reverse sweep-out current; Figure 6b shows the natural commutation turn-off as current decreases to zero. With the gate drive and natural commutation, the turn-off is shown in Figure 7a. If reverse drive is available then the residual charge can be reduced even faster. The excess charge left in the base region will determine the time when the fast dv/dt can be reapplied. For this reason, the dotted line in Figure 4b indicates that a circuit arrangement which would allow some reverse current may be desirable.

## 1.5 Statement of Work

These are the broad philosophies of thyristor design which we believe to be consistent with the meeting of the objective specifications: a 600-volt, 50-amp thyristor which will recover in  $2\mu s$  in the face of a reapplied dv/dt of  $400V/\mu s$  after conducting with a 2-volt forward drop. Two major portions of the work on this contract were aimed at the implementation of these design philosophies and the delivery of 10 or more thyristors meeting the specifications. A third task was the development of test circuitry to verify the specifications, to simulate the use of these devices in the series inverter. Finally, it was expected that the

Figure 6 — (a) Sweep-out with reverse current and decay of charges.

(b) Current fall without reverse sweep-out and blocking recovery.

Figure 7 — (a) Current fall with gate drive. (b) Reverse sweep-out with gate drive.

performance of the contract would lead to a deeper understanding of the developments required to improve the switch beyond its present ratings, to higher voltages, higher currents, shorter recovery times and lower forward drops.

Westinghouse Electric Corporation has not only fulfilled but has indeed exceeded most of the objectives of this contract. GATT devices were delivered very early in the performance of the contract, devices which met the majority of the final specifications. Not only first but also second generation tests and simulation circuits have been designed and put into operation. The problem areas are now clearly defined and the potential solutions well understood.

#### 2. PROCESSING

#### 2.1 Introduction

GATT processing is intermediate between thyristors and transistors. The steps are related to thyristors, for the GATT unit is a four layer device, blocking voltage and handling current much like a thyristor. The steps are related to transistors, for turn-off, in current sweepout, the device is functioning in a three layer mode through the gate and emitter contacts which are interdigitated like a transistor. Much of our processing development related to the latter characteristics in particular to the nature of the fingers, the mechanical contact to them, and the ultimate capability for sweeping out stored charge. These problems were of such primary importance that a separate section is devoted to them alone. In the following, we describe the standard processing and control and some of the developments and improvements made in this. These changes are not related directly to the finger problem itself.

# 2.2 Standard Processing (See Figure 8)

We now outline the major process steps.

- 1) Silicon of 0.91" diameter, n-type conductivity, (111) orientation, and  $10^3/\text{cm}^2$  or fewer dislocations is the starting material.

- 2) P Diffusion is effected by depositing gallium and then driving it into cleaned slices of silicon in two closed tube diffusions. Sheet resistivity and junction depths are measured after these steps.

- 3) Phosphorus Deposition is done by forming phosphorus glass on both sides of the diffused slices in a furnace from a source of ammonium phosphate maintained at 780° to 1230°C. Subsequent to this the phosphorus deposited glass is removed from the anode side by a short silicon etch. Phosphorus drive into the cathode side in an oxygen rich atmosphere provides the basic emitter region. The diffusion is slow cooled. Slices are then removed and are etched in HF to remove the oxide and glass surface layers. Sheet resistivity

Figure 8 - Process Flow for GATT

- and junction depth measurements relative to the phosphorus diffusion are made.

- 4) <u>Lifetime Control</u> is obtained by evaporation of gold on the anode side and then diffusing it into the silicon at a temperature ranging from 820 to 880°C, depending on the desired degree of lifetime reduction. Residual gold is removed and the wafers cleaned.

- 5) Mesa Etch of the emitter fingers is done by a long slow silicon etch, designed to maintain a flat surface while removing 15 to 18 microns of silicon. This exposes the P-gate region and defines the raised emitter fingers.

- 6) Alloying with a 0.94" diameter aluminum preform to a 50 mil thick moly slug of the same diameter is performed in a vacuum furnace. Subsequent to this the fusion is cleaned and aluminized by evaporation on the cathode emitter side. The metallization is photomasked and etched back to define the areas of aluminum contact. After this the aluminum is sintered above 500°C.

- 7) Bevel, Spin Etch, and Coat are standard thyristor operations.

- 8) Gate Insulation will be discussed in greater detail in the following section. The units are essentially complete at this point and may be stored, tested, etc.

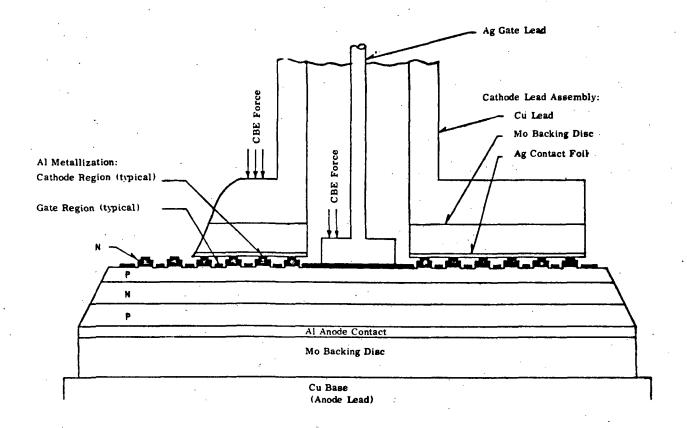

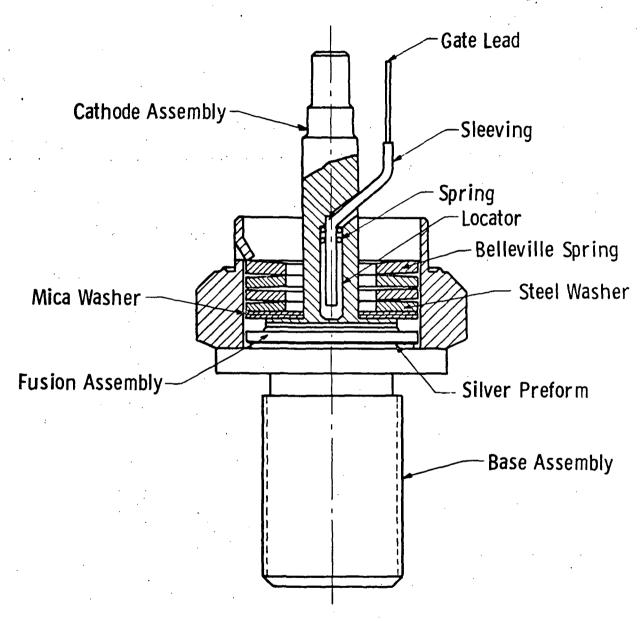

- 9) Contacting and Encapsulation are the last operations. The proprietory Westinghouse "Compression Bonded Encapsulation" system is used as illustrated in Figure 9. In this approach a copper cathode contact is pressed on a silver foil atop the fusion which itself is resting in the package base as shown in Figure 10. The ceramic cap is welded over the top, effecting an hermetic seal. The basic design and its adaptations have been discussed at length in the final report on contract F33615-68-C-117 with the Air Force Aeropropulsion Laboratory, Wright Patterson Air Force Base, Ohio.

Figure 9 — Technique used in Compression Bond Encapsulation (CBE), an exclusive Westinghouse system.

Dwg. 859A291

Figure 10-Preencapsulation assembly.

#### 2.3 Process Improvements

These are the major processing steps by which GATT devices are made. As will be discussed in the following paragraphs and in the next section, some basic alterations in the sequence were found advantageous. In addition to this, there was specific work performed on the relationship of blocking voltage and the gold doping level, on the relationship of blocking voltage and the quality of bevel lapping (a mechanical system), and on base resistivity and thickness. Of these, bevel lapping is the simplest to treat. This angle bevel is required because the junctions at the surface will have higher blocking voltage capability if they intersect the surface of the silicon at an angle other than normal. For this reason, and also to eliminate the diffused short between anode and cathode base, the silicon slice and its molybdenum backing plate are ground around the edge to an angle between 10 and 30°. We discovered during this work that the GATT slices, which are somewhat thinner than normal for thyristors because of the early gate etch, were suffering from minor cracking and breakage at the outer edge of the silicon molybdenum junction. Blocking voltage suffered. A better quality lapping machine was found and when this was used, average blocking voltages increased by approximately 200 volts.

### 2.4 Blocking Voltages

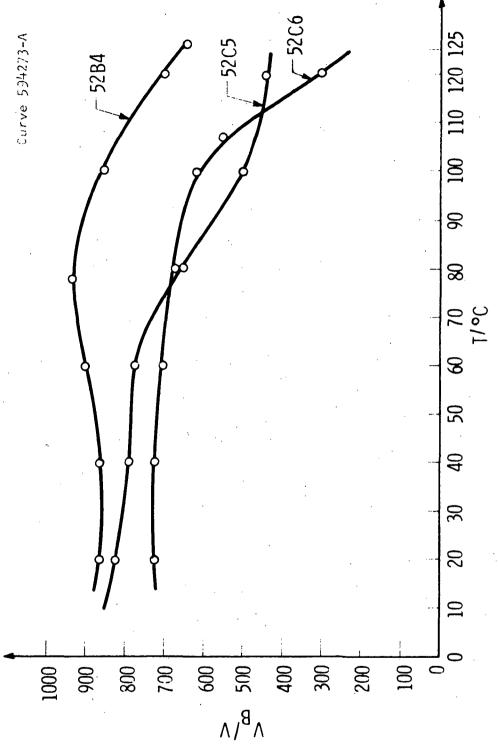

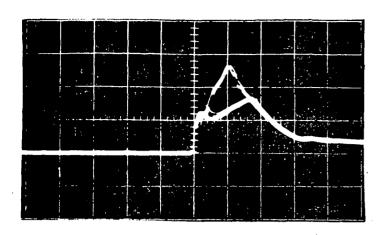

The degree of lifetime reduction by gold diffusion, the P base resistivity and thickness relate directly to the blocking capability. This is particularly true of V<sub>RB</sub> and its dependence on junction operating temperature. When gold is present, higher generation currents are required and the internal or bulk leakage of the device at a given temperature is in general higher than its counterpart without gold. These leakage currents rise exponentially with temperature. Thus if one specifies a safe current level and uses this to define a blocking voltage, then this blocking voltage will be relatively constant up to that junction temperature at which the exponential rise in leakage suddenly becomes apparent. Above that temperature, the blocking voltage must of necessity decrease sharply. Figure 11 shows this dependence for three devices, one from run 52B and two from run 52C.

Fig. 11 - Blocking voltage versus temperature for 600 V GATTS

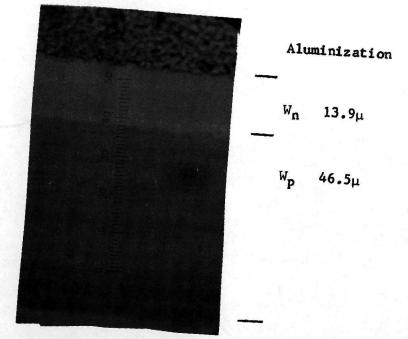

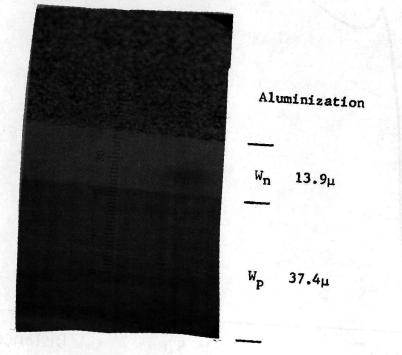

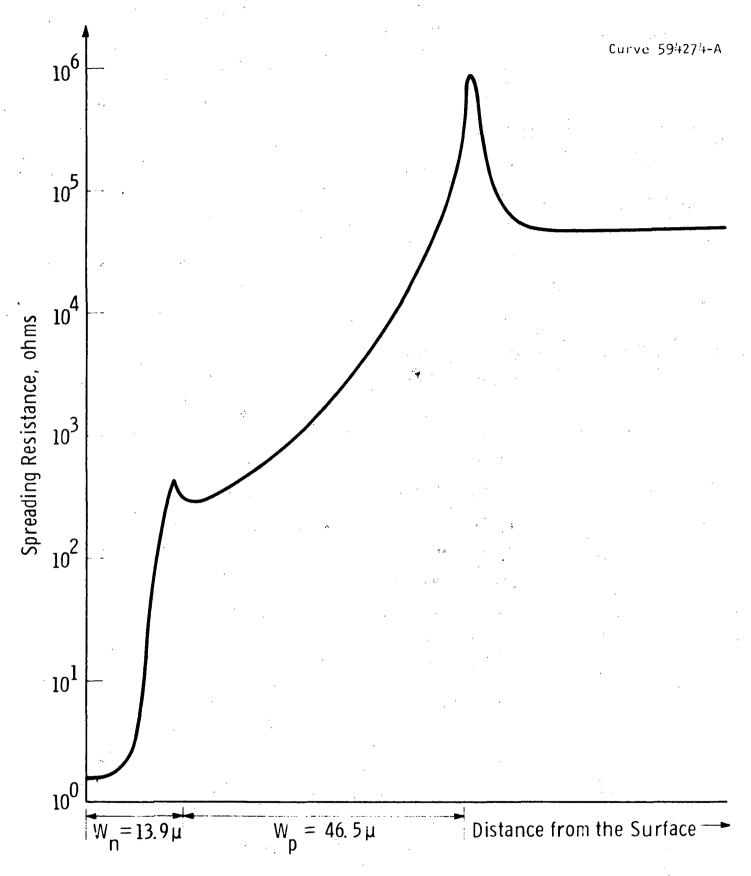

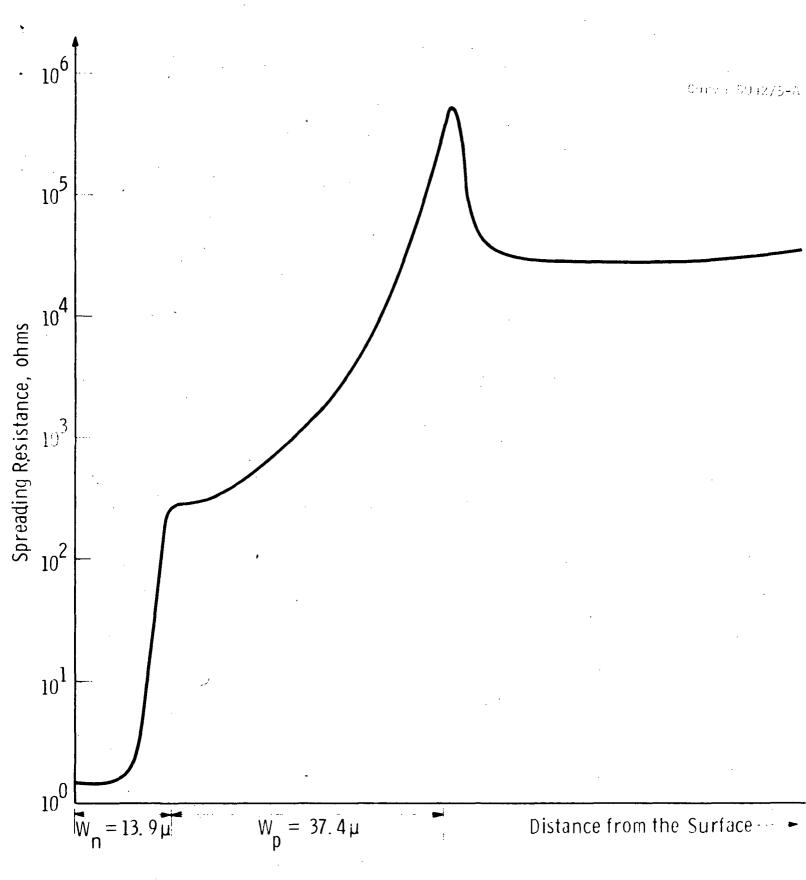

These devices differed primarily in their p-base width, as can be seen from Figures 12a and 12b. The differences are shown in Table 2 and also in the resistivity profiles in Figure 13 and 14.

The crucial point is the expected and good correlation between the p-base width and the blocking ability. Run 52B has the wider base width and clearly blocks higher voltages at all temperatures and especially at 125°C. Run 52B4 with its 46 micron base width is capable of withstanding well in excess of 600 volts in the reverse direction at all temperatures whereas 52C5 and 52C6, at 37 microns, are at best 450 volts at T, = 125°C. Overall, the characteristics in Figure 11 are typical of GATT devices and are consistent with the dependency generally reported in the literature for gold doped thyristors. The most notable departure is the lower temperature of the breakpoint. For GATT devices this is about 80°C while for thyristors generally, with their lower level of gold, the breakpoint is usually somewhat higher, perhaps 110°C or 120°C. The GATT devices in general require the higher level of gold responsible for this difference to improve their recovery. With this exception we have found the blocking voltage trade-offs in GATT devices closely parallel those for thyristors generally. GATT devices have no unusual traits in this respect.

Table 2 - Design Differences Between 52B and 52C

|     | W <sub>B</sub> (μm) | ρ <sub>p</sub> (ohm-cm) | N+ (cm <sup>-3</sup> ) | ρ <sub>N</sub> (ohm-cm) |

|-----|---------------------|-------------------------|------------------------|-------------------------|

| 52B | 46                  | 0.1                     | 10 <sup>20</sup>       | 60                      |

| 52C | <b>37</b> ·         | 0.1                     | 10 <sup>20</sup>       | 34                      |

|     |                     |                         |                        |                         |

Figure 12A. 52B

Figure 12B. 52C

Fig. 13 — Diffusion profile of Run 52B

\_ 34 .

W. D. Frobenius I. m. 7-31-70

Curve 594274-A

Fig. **14**—Diffusion profile of Run 52C

W. D. Frobenius I. m. 7-31-70 - 35 -

Curve 594275-A

# 3. CHARGE EXTRACTION AND GATE-EMITTER CHARACTERISTICS

### 3.1 Introduction

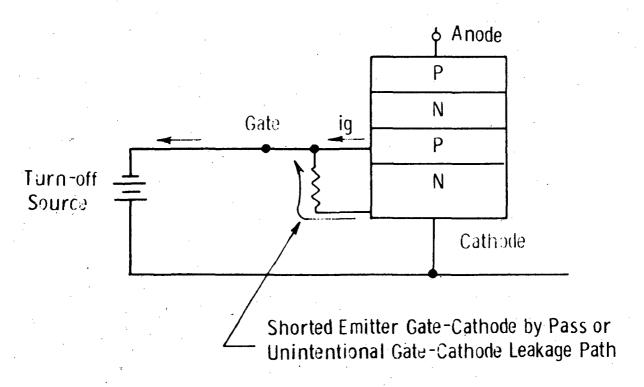

To extract charge from the commutating device, the gate emitter junction must be driven towards and even through its avalanche voltage. The gate surrounds the emitter fingers and extracts charge from underneath the emitter contact area, thus allowing this junction to recover. Except for this mechanism, recovery of the device and its ability to face reapplied dv/dt would be determined primarily by carrier lifetime. Since lifetime has already been reduced considerably by the gold diffusion, charge extraction through the gate becomes the vital difference between the GATT device and a conventional thyristor. The GATT device differs also from the transistor in that removal of the latter's base drive is sufficient to cause it to drop out of conduction. GATT devices do not do this. Therefore, considerable time and effort has been spent upon improving the efficiency of charge extraction and in understanding the mechanisms that govern it so that the maximum rates are obtained.

If the gate emitter junction is leaky, then not all the gate current drawn is residual stored charge and higher gate drives will be necessary to accelerate commutation. We early observed that many encapsulated devices had soft avalanche characteristics and leakages in the order of several amperes, a current that is substantial when compared to the extracted charge. Under these circumstances, much of the gate drive signal is diverted into ohmic losses. Examination of individual devices soon revealed that although the reverse leakages of most of the thirty-six individual emitter fingers were excellent, there were a few with disastrously high leakages, 100 milliamps or even one ampere. Such leaky fingers are very prone to turn-on failure which will occur when dv/dt is reapplied.

Simultaneously, an investigation of the peak currents achievable from back biasing individual non-leaky fingers, as a measure of charge extraction, was performed. It revealed that there was a parallel variation in this capability. Some fingers extracted charge notably better than others. We discuss the leakage situation first.

# 3.2 Gate-Emitter Leakage

Recognition of gate emitter leakage as an individual finger problem rather than a distributive one, led to the examination of the steps in processing where fingers might degrade. We found that immediately following etching of the emitter finger mesas, the leakages were low and uniform in the order of microamperes. On the other hand, prior to encapsulation the leakages were variable and some were in the ampere range. For example, twelve wafers alloyed to molybdenum would reach the finger test out of 25 starts. In one particularly good run, one unit of the twelve had four fingers with leakages so high that they could be considered shorted; the remainder had microamp leakages. Two units had one finger each shorted, the balance exhibiting virtually no leakage. Two additional units had one finger each which measured leakages in the milliampere range, the balance good. All fingers of the seven remaining wafers had leakages in the microamp range. Thus we are speaking of a total of eight fingers, half of which are completely inoperable. Thus, although the yield to microampere leakage on a device (or wafer) basis is less than 50%, the yield on a finger basis is very high.

Typical data for a single wafer is shown in Table 3.  $I_{\rm gt}$  at  $V_{\rm BR}=12.5 {\rm V}$  is shown for the eighteen shorter fingers first and then for the eighteen longer ones. The leakages range from 0.5 ma to 0.18 amperes, with one shorted finger. Excepting this one, all could be made to turn off individually, although the device could not function properly as a unit. By both following material forward through the line and working backward from encapsulation, we pinpointed two sources of degradation. The first was the physical handling of the fusion after finger etch. We demonstrated that once the bare junction is exposed, it is extremely vulnerable to physical damage. In the initial process sequence this junction was unprotected during alloying and bevel lap operations. Specifically, the surface was exposed to powdered graphite and an abrasive lapping compound in these steps. Elsewhere, experiments showed that handling with steel tweezers and even plastic ones,

Table 3--Variability in Emitter Finger Characteristics on a Typical Wafer. Throughout,  $I_A$ =10A,  $V_{BR}$ =12.5V and  $I_g$ =3.5A.

| SHORT FINGERS    |                      |                      | LONG FINGERS       |                  |                      |                      |           |  |

|------------------|----------------------|----------------------|--------------------|------------------|----------------------|----------------------|-----------|--|

| Finger<br>Number | t <sub>s</sub><br>μs | t <sub>f</sub><br>μs | Igt in mA<br>@ VBR | Finger<br>Number | t <sub>s</sub><br>μs | t <sub>f</sub><br>µs | Igt in mA |  |

| 1                | 0.8                  | 1.0                  | 0.5                | 1                | 1.0                  | 3.5                  | 50        |  |