2 (mix) MEN CR- 130/14

**MDC E0648**

# FINAL REPORT FOR

# DIGITAL RECEIVER STUDY AND IMPLEMENTATION

1 JUNE 1971 — 1 JUNE 1972

CONTRACT NO.: NAS5-11424

(NASA-CR-130174) DIGITAL RECEIVER STUDY AND IMPLEMENTATION Final Report, 1 Jun. N73-17185

1971 - 1 Jun. 1972 (McDonnell-Douglas

Astronautics Co.) 302 p HC \$17.25

Unclas ·

CSCL 09B G3/08 63392

PREPARED BY

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY • EAST

St. Louis, Missouri 63166

NATIONAL TECHNICAL INFORMATION SERVICE

US Department of Commerce Springfield, VA. 22151

**FOR**

**GODDARD SPACE FLIGHT CENTER** GREENBELT, MARYLAND

COPY NO. 36

# FINAL REPORT FOR

# DIGITAL RECEIVER STUDY AND IMPLEMENTATION

1 JUNE 1971 — 1 JUNE 1972

**CONTRACT NO.: NAS5-11424**

**GODDARD SPACE FLIGHT CENTER**

CONTRACTING OFFICER: K.G. WILLIAMS CODE 245

TECHNICAL MONITOR:

W. ALFORD

**CODE 563**

PREPARED BY

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY - EAST

St. Louis, Missouri 63166

MCDONNELL DOUGLAS)

CORPORATION

D.A. FOGLE, DR. G.M. LEE, J.C. MASSEY

**FOR**

GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND

#### **ABSTRACT**

Computer software is developed which makes it possible to use any general purpose computer with A/D conversion capability as a PSK receiver for low data rate telemetry processing.

Carrier tracking, bit synchronization, and matched filter detection are all performed digitally. To aid in the implementation of optimum computer processors, a study of general digital processing techniques was performed which emphasized various techniques for digitizing general analog systems.

In particular, the phase-locked loop was extensively analyzed as a typical non-linear communication element. Bayesian estimation techniques for PSK demodulation were studied. A hardware implementation of the digital Costas loop was developed.

#### TABLE OF CONTENTS

|    |                                            |         | PAG                                                         | E |  |

|----|--------------------------------------------|---------|-------------------------------------------------------------|---|--|

|    | TABL                                       | E OF CO | ONTENTS                                                     |   |  |

|    | LIST                                       | OF FIG  | GURES                                                       |   |  |

| 1. | INTR                                       | ODUCTIO | ON                                                          |   |  |

| 2. | DEVELOPMENT OF DIGITIZED PHASE-LOCKED LOOP |         |                                                             |   |  |

|    | 2.1                                        | Synthe  | esis of Equations                                           |   |  |

|    |                                            | 2.1.1   | Choice of Phase-Locked Loop Filter                          |   |  |

|    |                                            | 2.1.2   | Analysis of Linear Loop 4                                   |   |  |

|    |                                            | 2.1.3   | Differential Equation Approach 6                            |   |  |

|    |                                            | 2.1.4   | Difference Equation Formulation                             |   |  |

|    | 2.2                                        | Develo  | opment of Computer Programs                                 |   |  |

|    | 2.3                                        |         | rison of Techniques                                         |   |  |

|    |                                            | 2.3.1   | Non-Linear Phase-Locked Loop                                |   |  |

|    |                                            | 2.3.2   | Linear Filters                                              |   |  |

|    | 2.4                                        |         | dination of System Constraints                              |   |  |

|    | 2.7                                        | Determ  | inaction of System Constraints                              |   |  |

|    |                                            | 2.4.1   | Sampling Rate                                               |   |  |

|    |                                            | 2.4.2   | Quantization                                                |   |  |

|    |                                            | 2.4.3   | Scale Factor                                                |   |  |

|    | 2.5                                        | Automa  | tic Gain Control (AGC)40                                    |   |  |

|    |                                            | 2.5.1   | Bandpass Limiter                                            |   |  |

|    |                                            | 2.5.2   | Closed Loop AGC                                             |   |  |

|    |                                            | 2.5.3   | Comparison of Techniques                                    |   |  |

|    | 2.6                                        | Acquis  | ition                                                       |   |  |

|    |                                            | 2.6.1   | Swept Frequency Method                                      |   |  |

|    |                                            | 2.6.2   | Fast Fourier Transform Acquisition                          |   |  |

|    |                                            | <b></b> | runororm requireferon , , , , , , , , , , , , , , , , , , , |   |  |

# TABLE OF CONTENTS (Continued)

|    |      |         |                                               | PAGE |

|----|------|---------|-----------------------------------------------|------|

|    |      | 2.6.3   | Free Running Acquisition                      | 57   |

|    |      | 2.6.4   | Comparison of Techniques                      | 57   |

|    | 2.7  | Hybrid  | Simulation                                    | 61   |

|    |      | 2.7.1   | Input Filter                                  | 61   |

|    |      | 2.7.2   | Results                                       | 66   |

|    | 2.8  | Evalua  | tion of Performance                           | 70   |

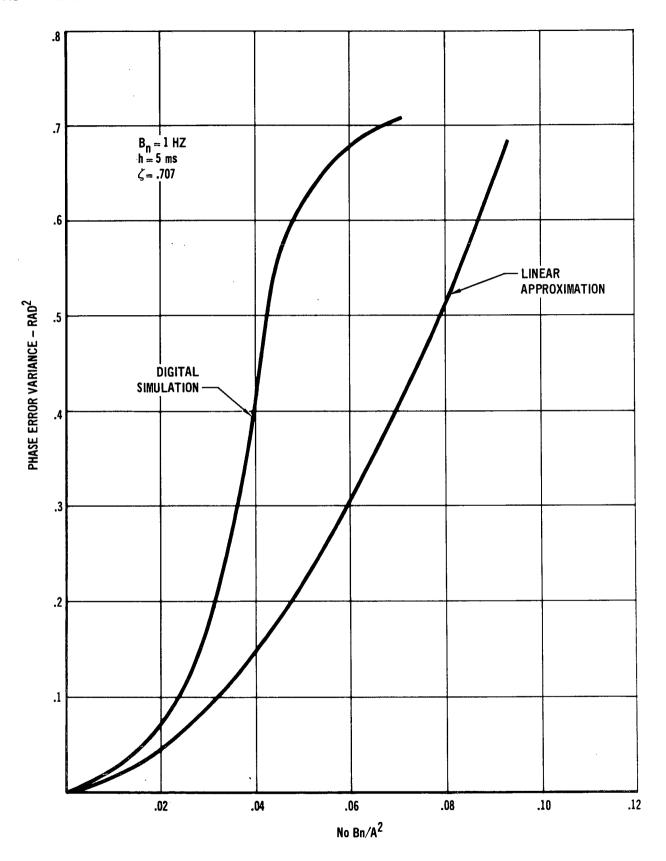

|    |      | 2.8.1   | Phase Error Variance                          | 71   |

|    |      | 2.8.2   | Phase-Locked Loop Threshold                   | 73   |

|    |      | 2.8.3   | Acquisition                                   | 75   |

| 3. | DEVE | LOPMENT | OF DIGITIZED PSK RECEIVER                     | 79   |

|    | 3.1  | Synthe  | sis of PSK Receiver Software                  | 79   |

|    |      | 3.1.1   | Sampling and A/D Conversion of Data           | 79   |

|    |      | 3.1.2   | Rejection of DC Bias                          | 84   |

|    |      | 3.1.3   | Input Filter Design                           | 86   |

|    |      | 3.1.4   | Generation of PSK Modulated Noisy Carrier     | 88   |

|    |      | 3.1.5   | Study of Carrier Synchronization              | 89   |

|    |      | 3.1.6   | Automatic Gain Control                        | 100  |

|    |      | 3.1.7   | Study of Bit Synchronization                  | 103  |

|    |      | 3.1.8   | Development of Integrated Program             | 137  |

|    |      | 3.1.9   | Study of Acquisition Techniques               | 147  |

|    | 3.2  | Digita  | l PSK System Analysis                         | 156  |

|    |      | 3.2.1   | Sampling Losses                               | 157  |

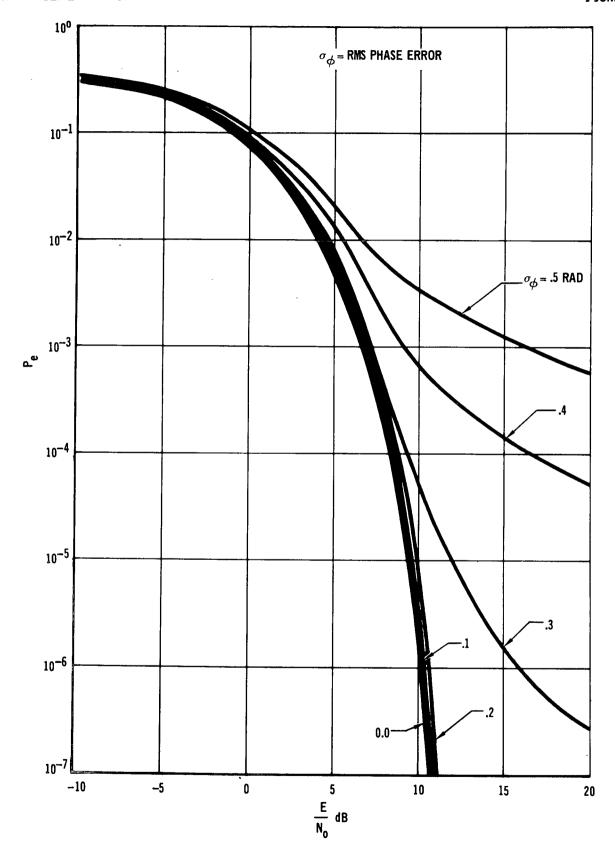

|    |      | 3.2.2   | Losses Due to Imperfect Phase Synchronization | 164  |

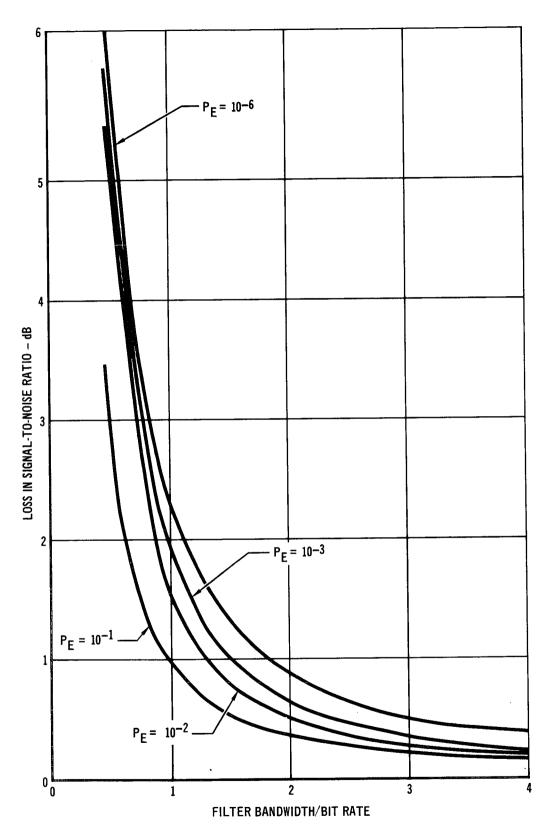

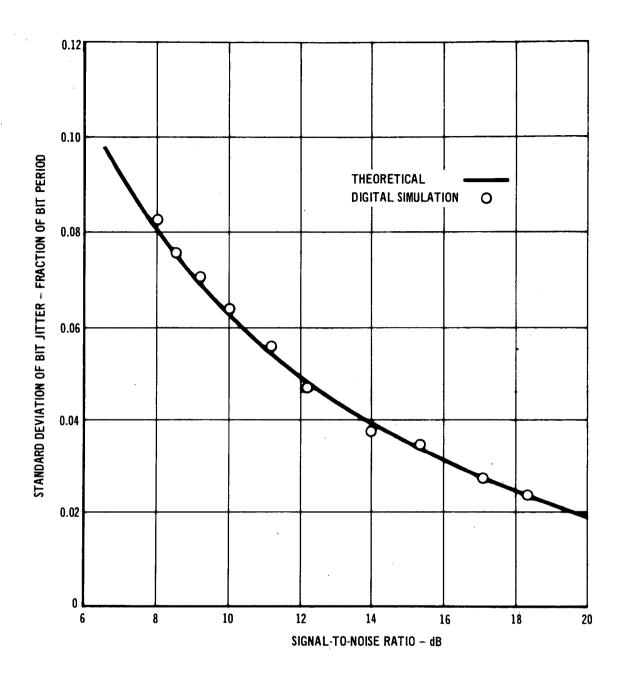

|    |      | 3.2.3   | Losses Due to Imperfect Bit Synchronization   | 167  |

|    |      | 3.2.4   | Performance Evaluation                        | 171  |

|    |      |         |                                               |      |

| DIGITAL RECEIVER STUDY AND IMPLEMENTATION                                                            | MDC E0648<br>1 JUNE 1972 |

|------------------------------------------------------------------------------------------------------|--------------------------|

| TABLE OF CONTENTS (Continued)                                                                        | PAGE                     |

| 4. STUDY OF NON-ANALOG SYNTHESIS TECHNIQUES                                                          | . 179                    |

| 4.1 Bayesian Estimation                                                                              | . 179                    |

| 4.2 Performance Evaluation                                                                           | . 186                    |

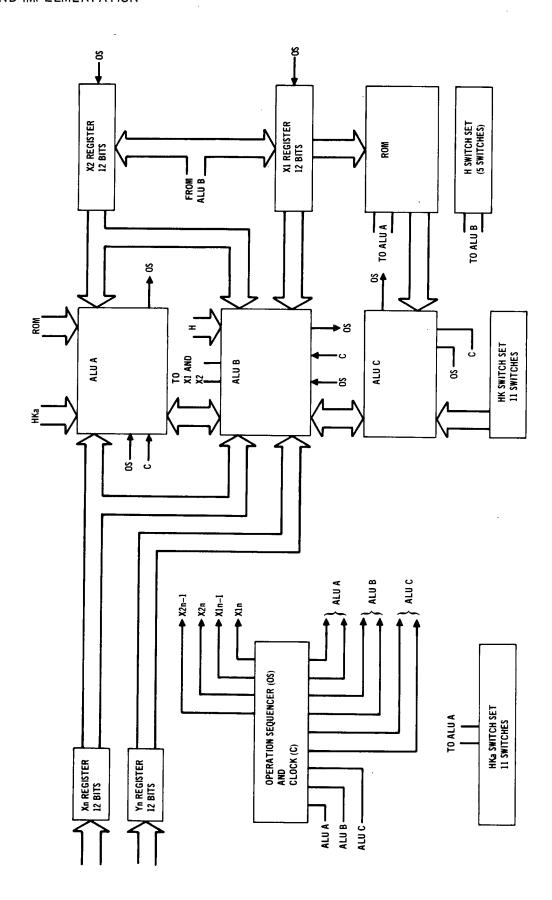

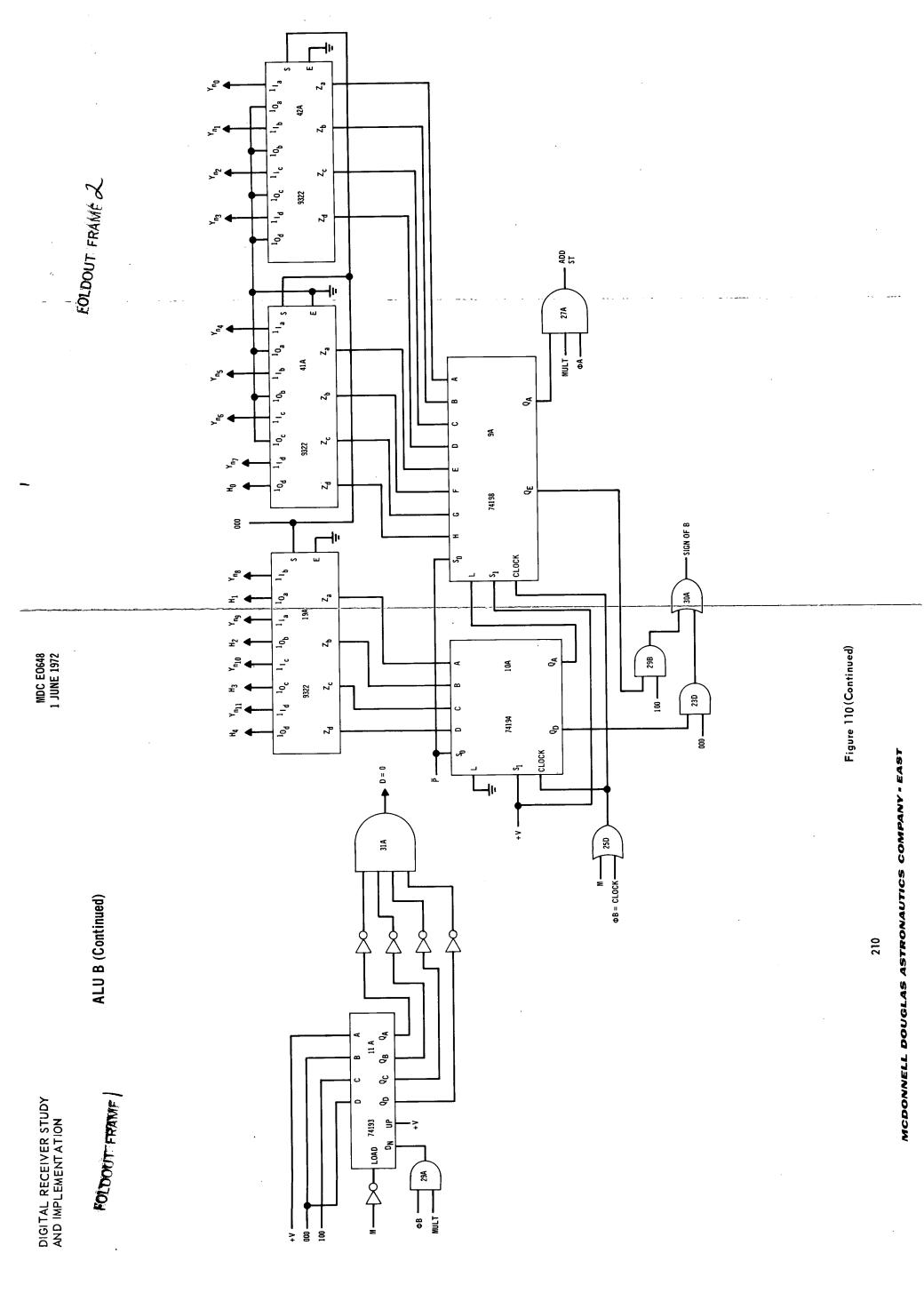

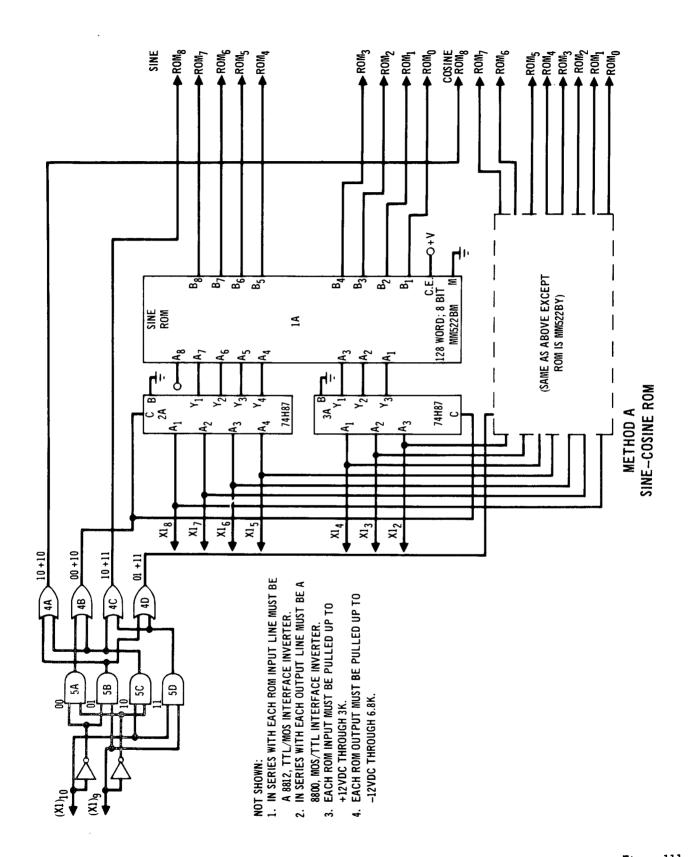

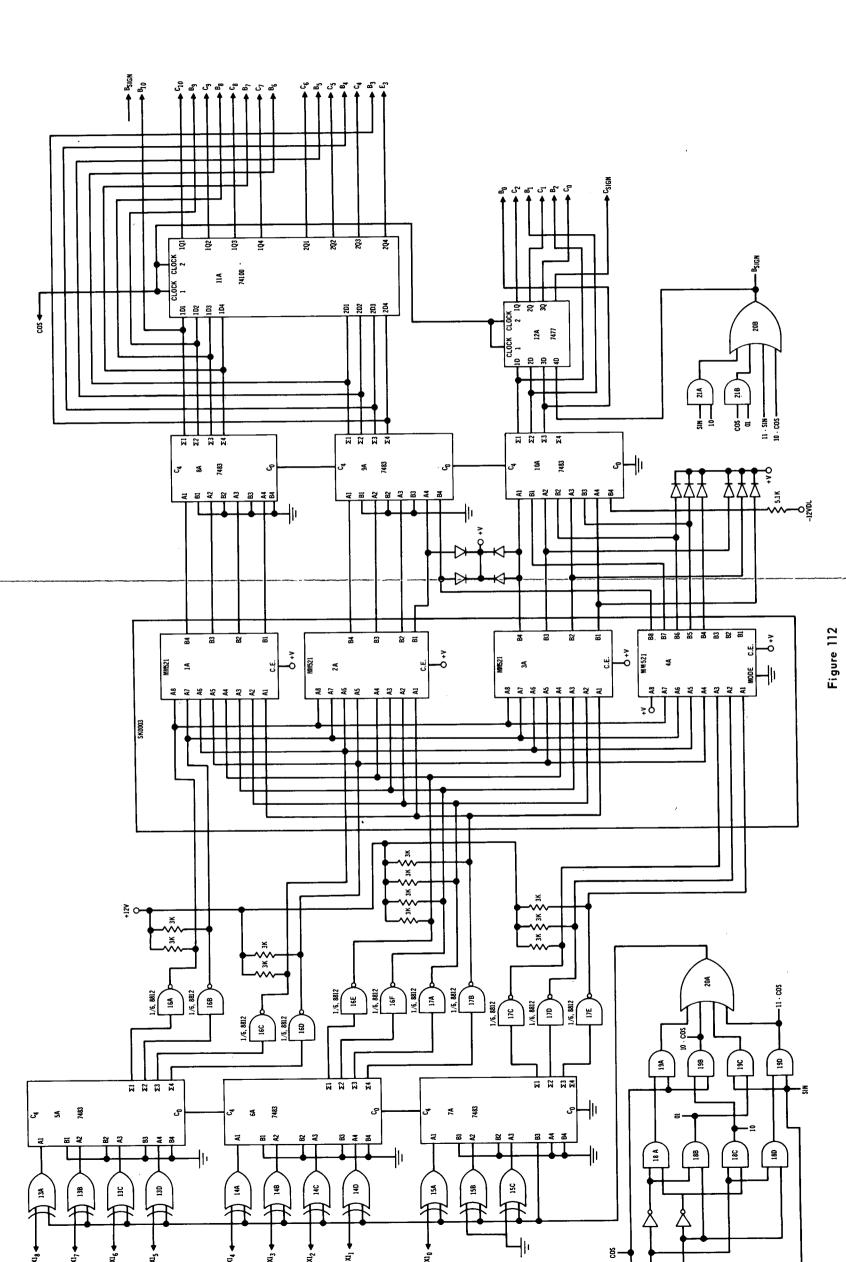

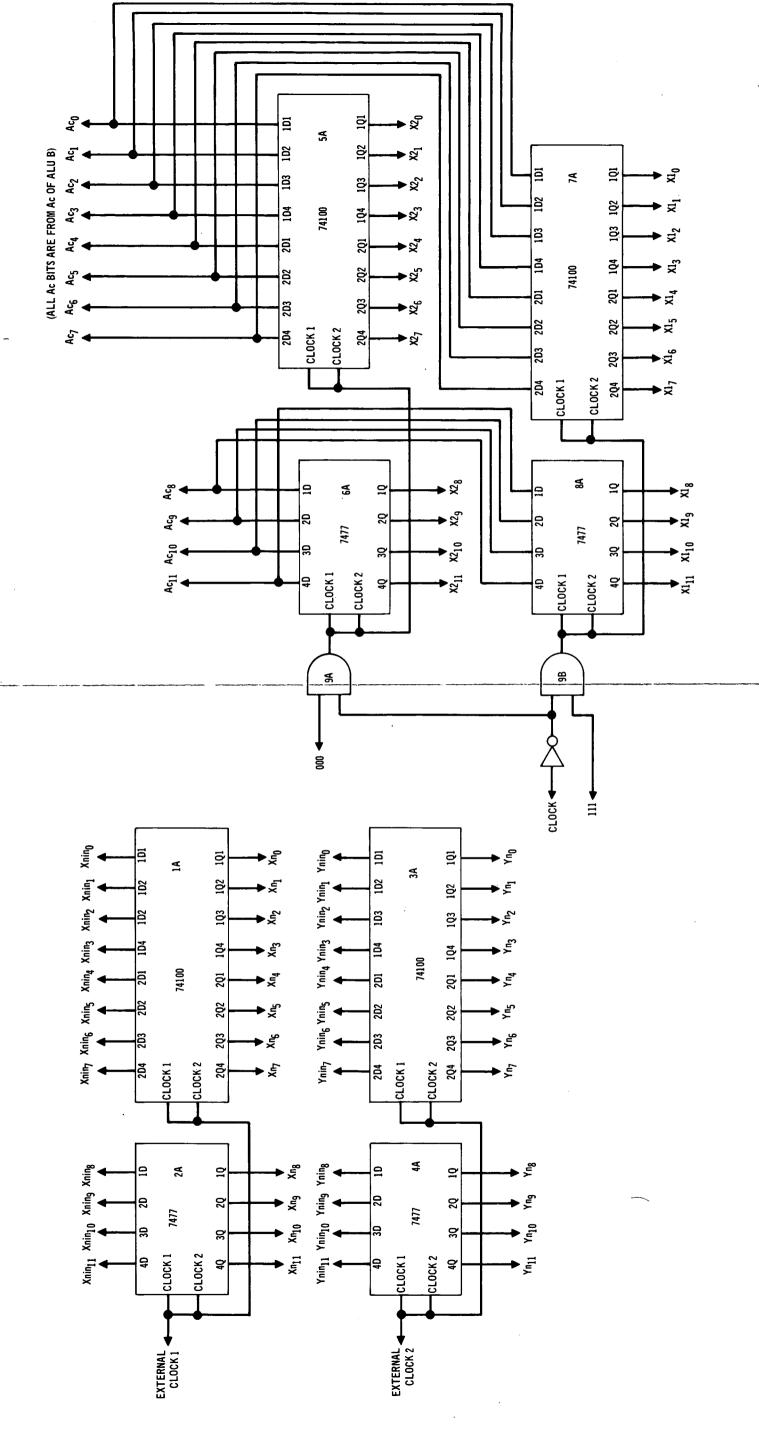

| 5. DEVELOPMENT OF HARDWARE COSTAS LOOP                                                               | . 193                    |

| 5.1 Machine Organizations                                                                            | . 195                    |

| 5.2 Parallel, 3 Arithmetic Logic Unit Design                                                         | . 195                    |

| 5.2.1 General Description                                                                            | . 197                    |

| 5.2.2 Function Block                                                                                 | . 198                    |

| 5.2.3 Logic Diagrams                                                                                 | . 202                    |

| 5.2.4 Cost Estimate                                                                                  | <b>2</b> 19              |

| 5.3 Future Effort                                                                                    | 219                      |

| REFERENCES                                                                                           | 220                      |

| APPENDIX I - ANDERSON, BALL, VOSS METHOD                                                             | I-1                      |

| APPENDIX II - DERIVATION OF DIFFERENCE EQUATIONS FOR LINEAR FILTERS .                                | II-1                     |

| APPENDIX III - BIT SYNCHRONIZATION ERROR                                                             | III <b>-1</b>            |

| APPENDIX IV - LISTING OF DIGITAL RECEIVER WITHOUT SAMPLE STORAGE BIT                                 |                          |

| SYNCHRONIGATION                                                                                      | IV-1                     |

| APPENDIX V - LISTING OF DIGITAL RECEIVER WITH SAMPLE STORAGE BIT                                     |                          |

| SYNCHRONIGATION                                                                                      | V <b>-</b> 1             |

| APPENDIX VI - LISTING OF DIGITAL RECEIVER WITH SAMPLE STORAGE BIT SYNCHRONIGATION (SPLIT-PHASE DATA) |                          |

| APPENDIX VII - LISTING OF BASEBAND DIGITAL RECEIVER                                                  | VI-1                     |

| APPENDIX VIII - LISTING OF DIGITAL RECEIVER WITH SWEPT                                               | VII-1                    |

| FREQUENCY ACQUISITION                                                                                | VTTT_1                   |

#### LIST OF PAGES

Title Page

ii thru xii

1 thru 222

I-1 thru I-3

II-1 thru II-9

III-1 thru III-6

IV-1 thru IV-6

V-1 thru V-11

VI-1 thru VII-1

VII-1 thru VII-5

VIII-1 thru VIII-10

#### LIST OF FIGURES

| FIGURE NO. | <u>TITLE</u> <u>PAG</u>                                                        |

|------------|--------------------------------------------------------------------------------|

| 1          | Linearized Phase-Locked Loop                                                   |

| 2          | Phase-Locked Loop Block Diagram 6                                              |

| 3          | Differential Equation Implementation 8                                         |

| 4          | Finite Difference Model of Phase-Locked Loop 9                                 |

| 5          | Computer Program for Runge-Kutta Method 13                                     |

| 6          | Computer Programs for Euler's and the Z- Transform Method                      |

| 7          | Computer Program for Tustin's and ABV Method 15                                |

| 8          | Mechanization of the Z-Transform Method 16                                     |

| 9          | Mechanization of Euler's Method 17                                             |

| 10         | Routine for Calculating Sine 18                                                |

| 11         | Accuracy of Sine Wave Generator                                                |

| 12         | Comparison of Numerical Methods for a Ramp Input 22                            |

| 13         | Comparison of Numerical Methods for a Step Input 22                            |

| 14         | Methanization of the ABV Method and Tustin's Method                            |

| 15         | Comparing Numerical Methods for Ramp Input as a Function of Computation Time   |

| 16         | Comparing Numerical Methods for Step Input as a Function of Computation Time   |

| 17         | Comparison of Numerical Techniques for Linear Filter with Ramp Input           |

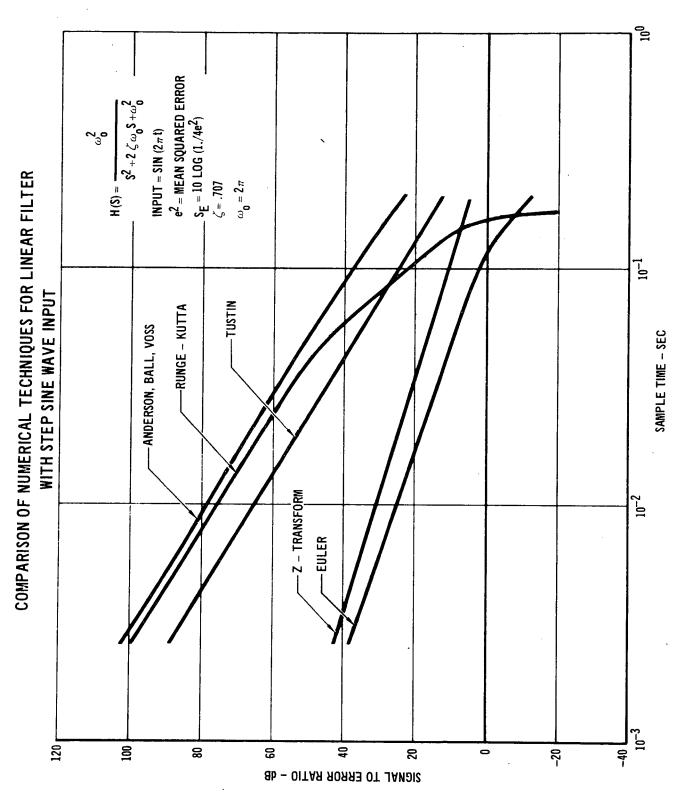

| 18         | Comparison of Numerical Techniques for Linear Filter with Step Sine Wave Input |

| 19         | Phase Variance Versus Sample Interval                                          |

| 20         | Phase Error Curve (Digital Simulation)                                         |

| FIGURE NO. | <u>TITLE</u> <u>PAGI</u>                                                    |

|------------|-----------------------------------------------------------------------------|

| 21         | Mean Squared Error Versus Offset Frequency for Different Sample Intervals   |

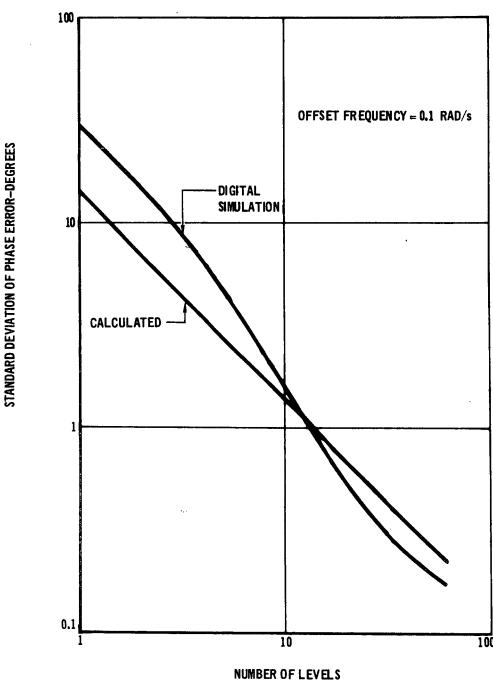

| 22         | Standard Deviation of Phase Output Versus the Number of Quantization Levels |

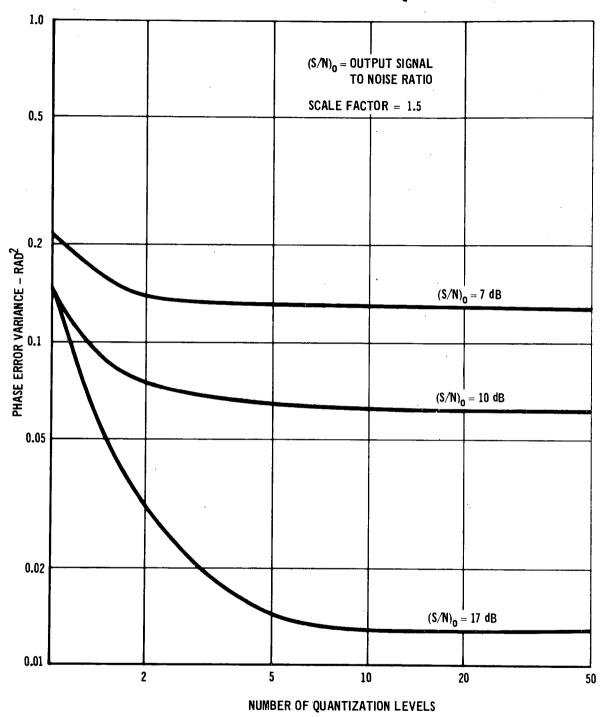

| 23         | Phase Error Variance Versus the Number of Quantization Levels               |

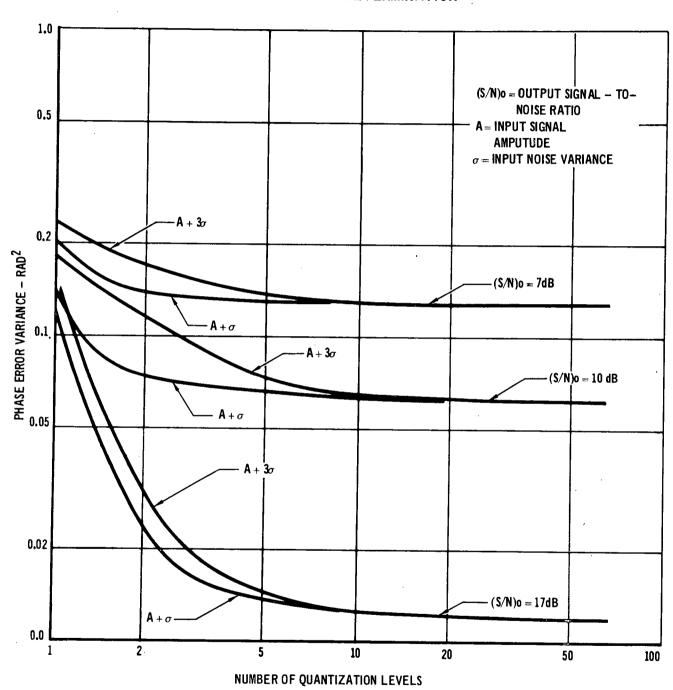

| 24         | Scale Factor Determination                                                  |

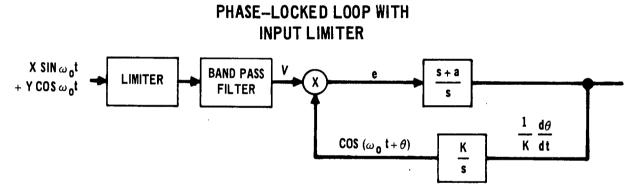

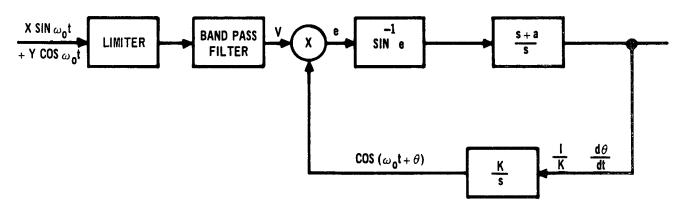

| 25         | Phase-Locked Loop with Input Limiter 40                                     |

| 26         | Sawtooth Comparator                                                         |

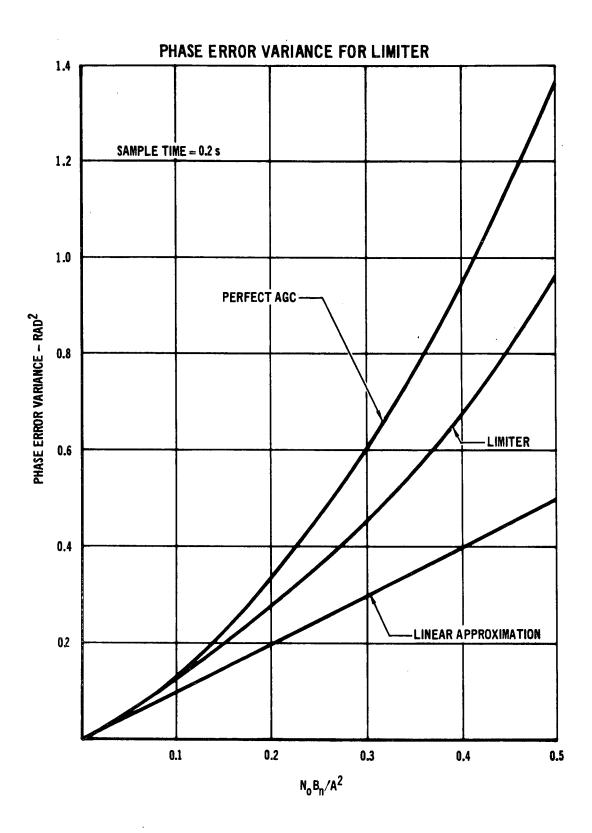

| 27         | Phase Error Variance for Limiter                                            |

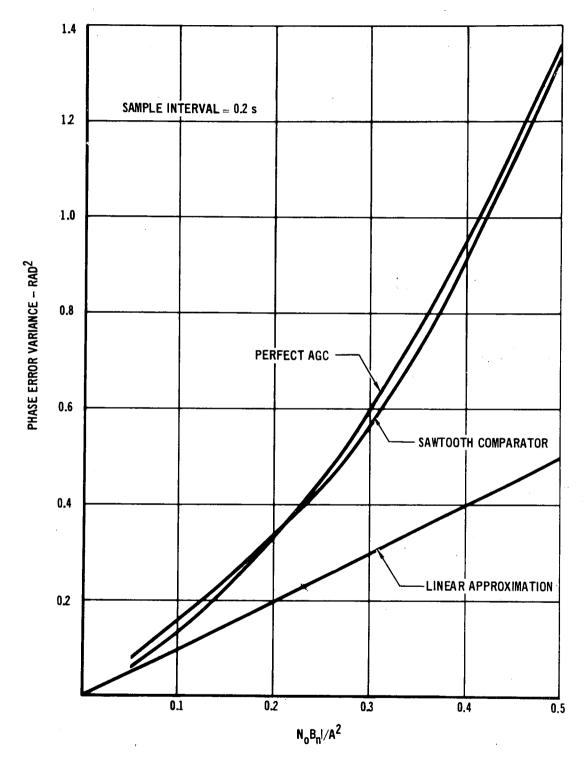

| 28         | Phase Error Variance for Sawtooth Comparator 45                             |

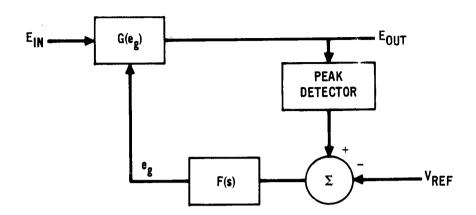

| 29         | Closed Loop Analog AGC                                                      |

| 30         | Implementation Diagram for AGC Loop 47                                      |

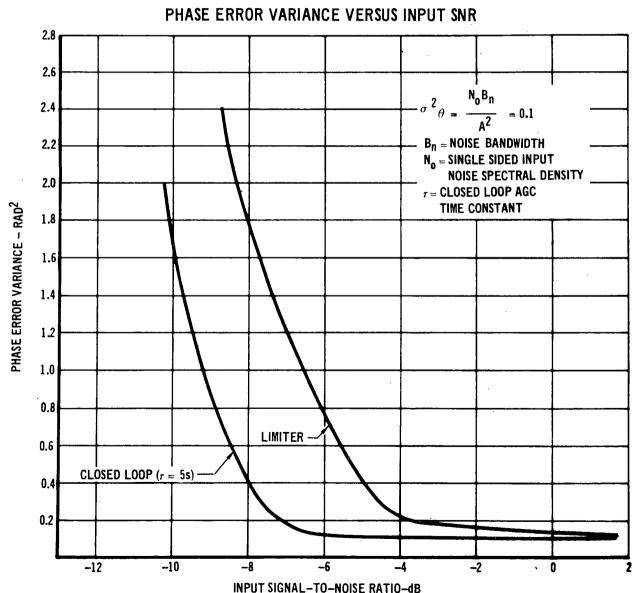

| 31         | Phase Error Variance Versus Input SNR 49                                    |

| 32         | Swept Frequency Acquisition 51                                              |

| 33         | Determining Relationship Between LPF Band-width and Sweep Rate              |

| 34         | Computer Program for Acquisition 54                                         |

| 35         | Digital Computer Program for FFT Generation 55                              |

| 36         | Mean Pull-in Time Versus Offset Frequency 58                                |

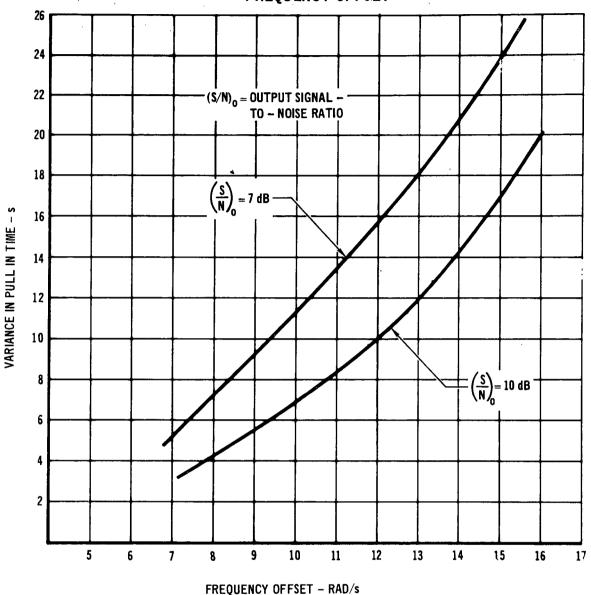

| 37         | Variance in Pull-in Time Versus Frequency Offset                            |

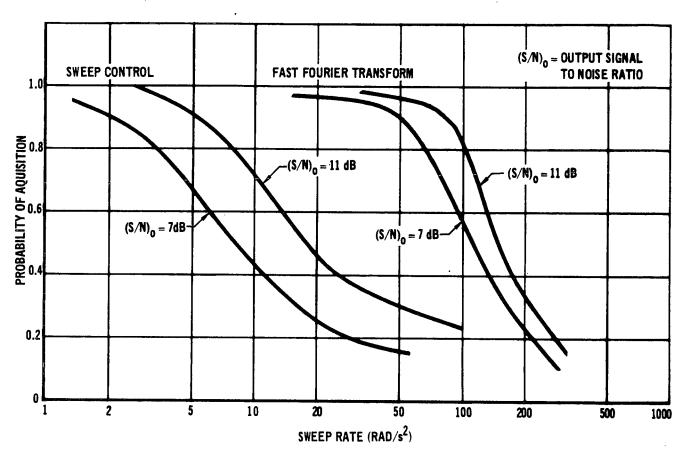

| 38         | Probability of Acquisition Versus Sweep Data 60                             |

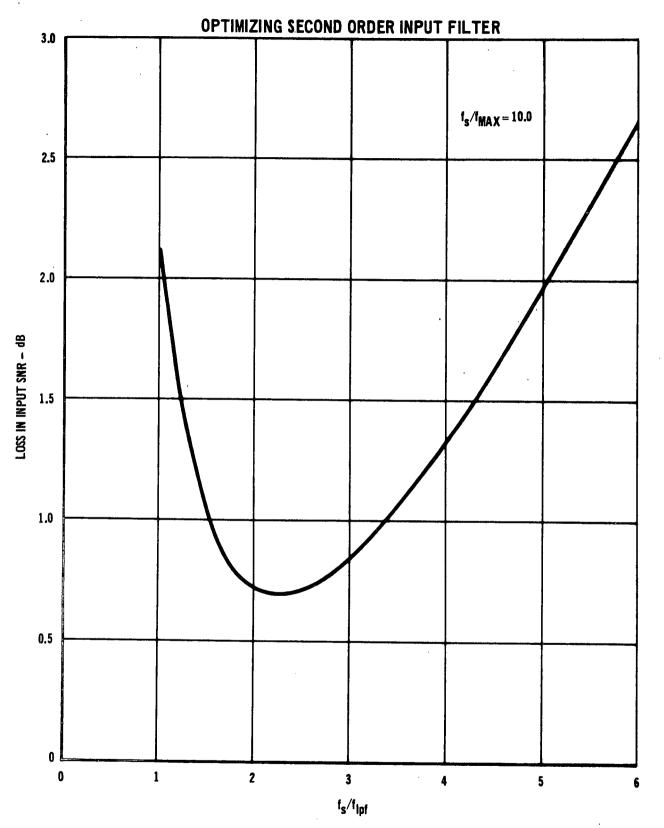

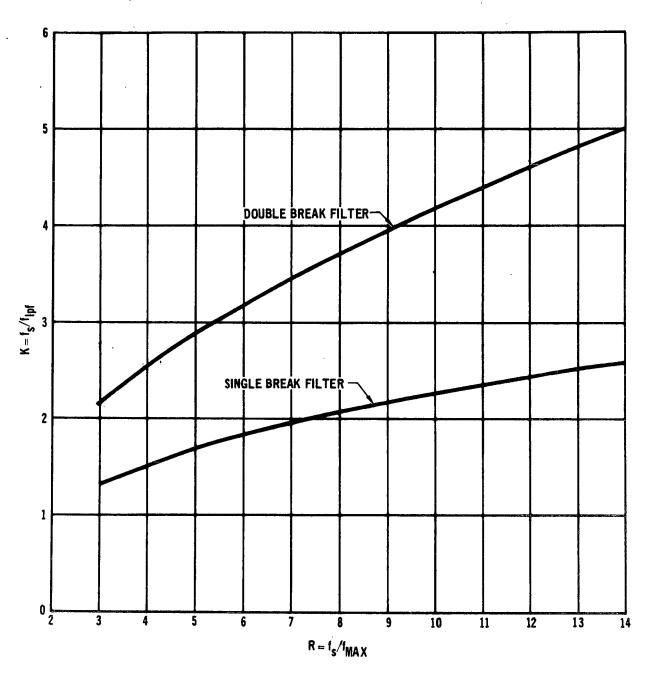

| 39         | Optimizing Second Order Input Filter 64                                     |

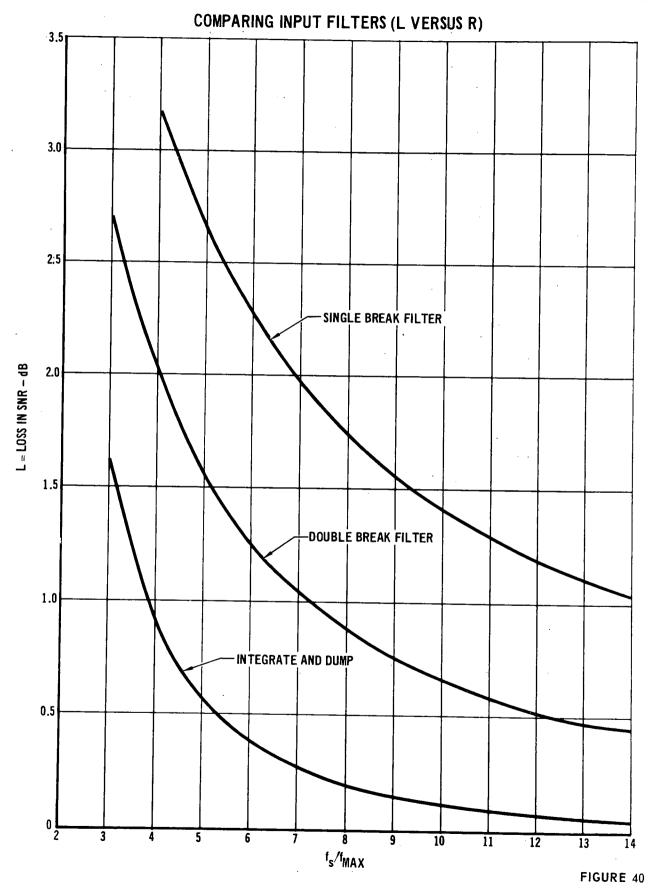

| 40         | Comparing Input Filters (L Versus R)65                                      |

| 41         | Comparing Input Filters (K Versus R) 66                                     |

| 42         | Hybrid Configuration 67                                                     |

|            | 4.4.4                                                                       |

| FIGURE NO. | <u>TITLE</u> <u>PAGE</u>                                                            |

|------------|-------------------------------------------------------------------------------------|

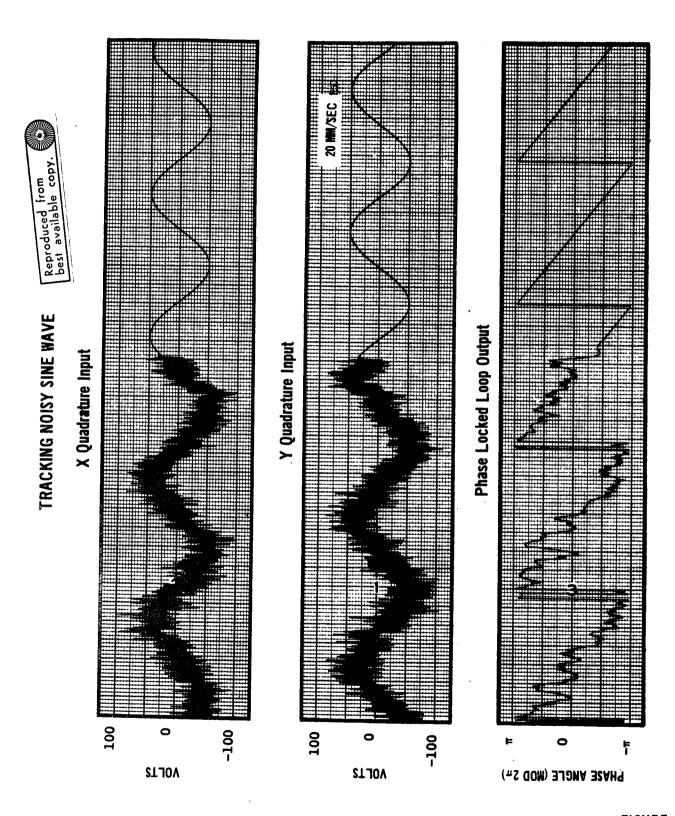

| 43         | Tracking Noisy Sine Wave                                                            |

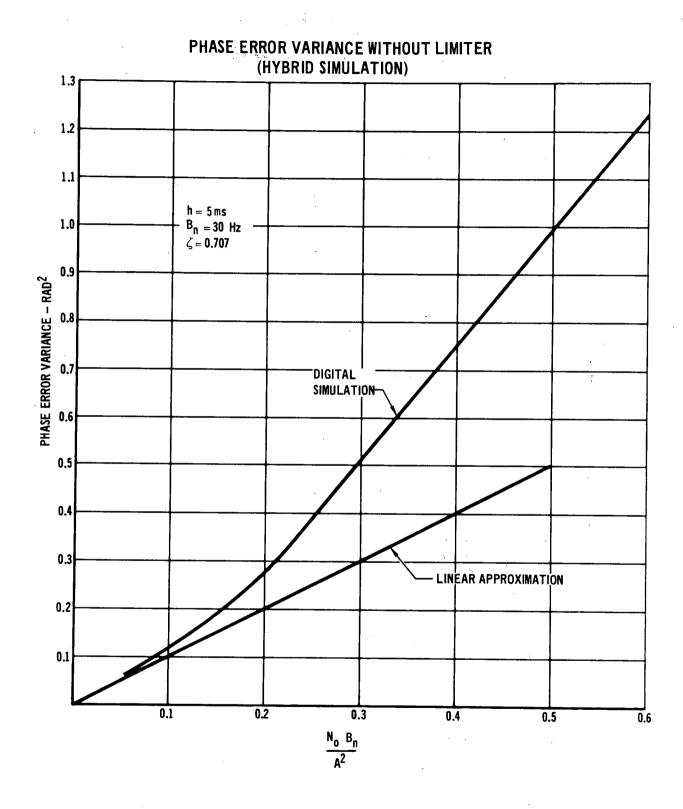

| 44         | Phase Error Variance without Limiter (Hybrid Simulation) 69                         |

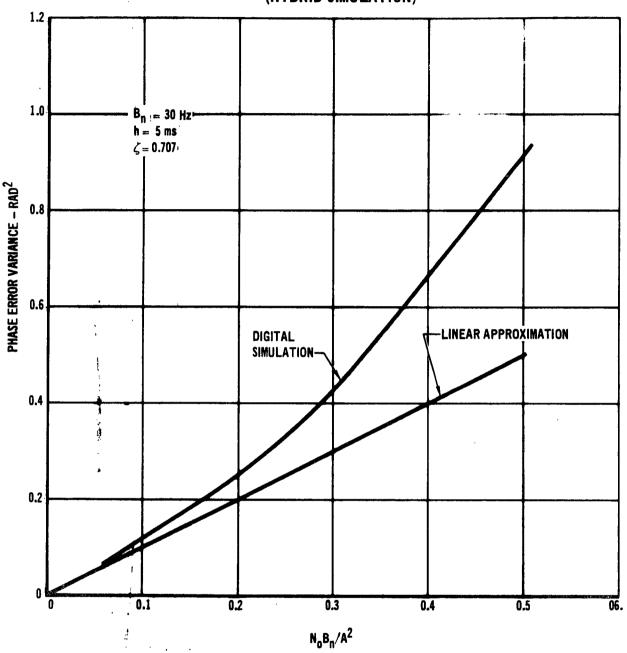

| 45         | Phase Error Variance with Limiter (Hybrid Simulation)                               |

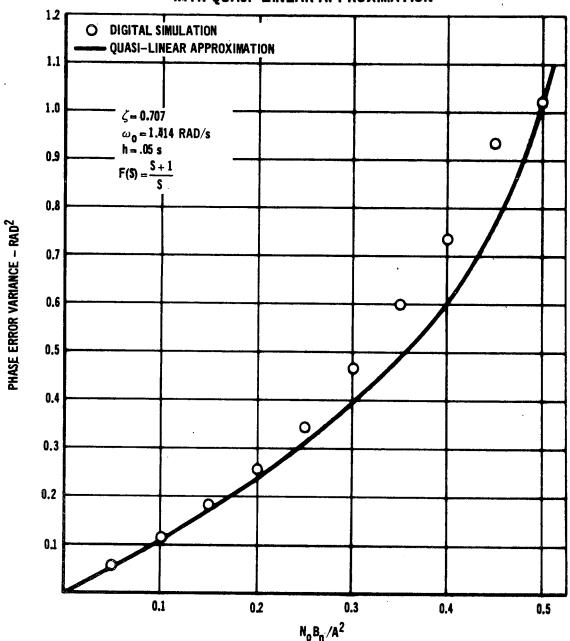

| 46         | Comparing Digital Simulation Results with Quasi-Linear Approximation                |

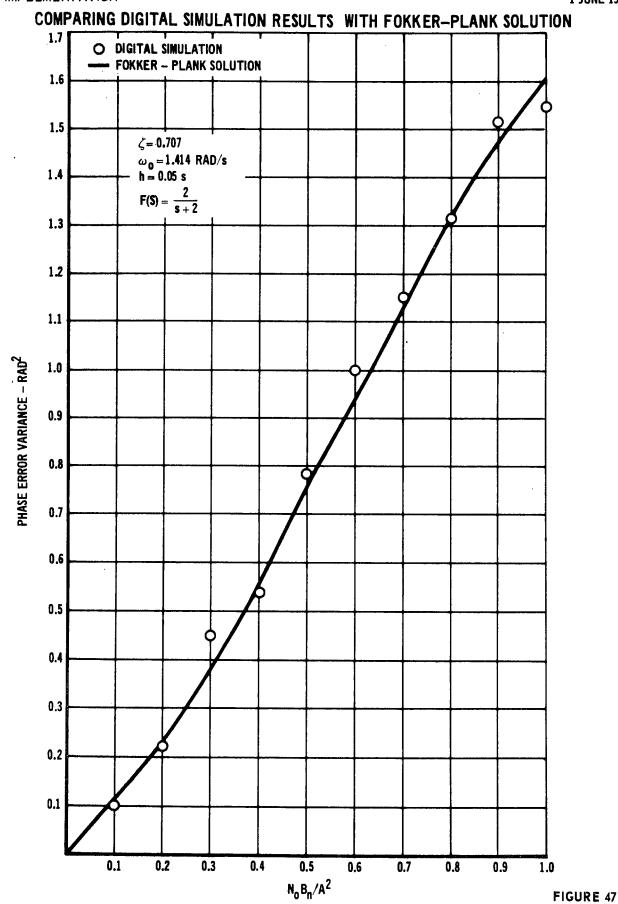

| 47         | Comparing Digital Simulation Results with Fokker-Plank Solution                     |

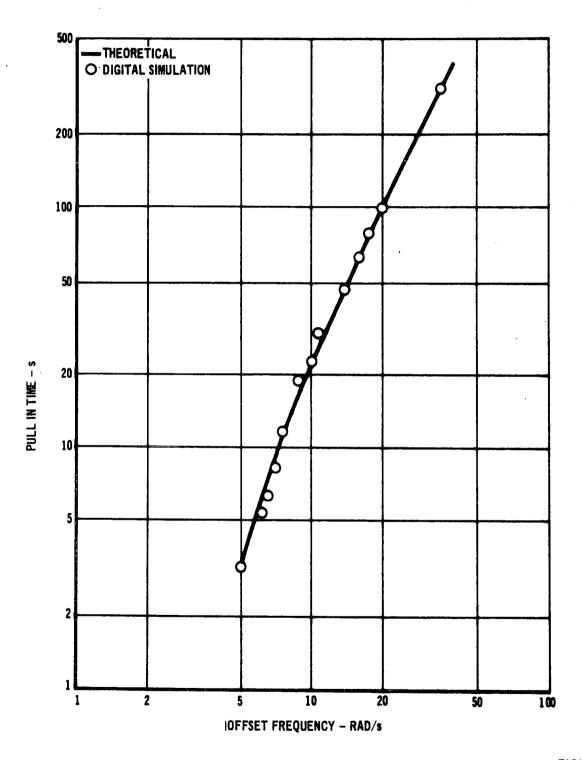

| 48         | Comparing Measured and Calculated Pull-in Time 76                                   |

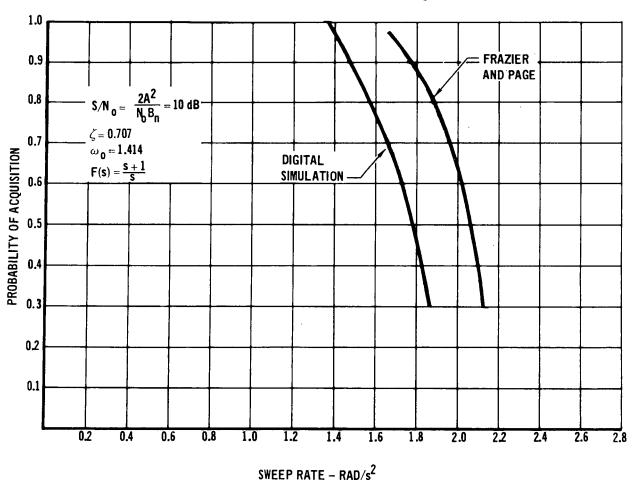

| 49         | Comparing Digital Simulation and Theoretical Results for Probability of Acquisition |

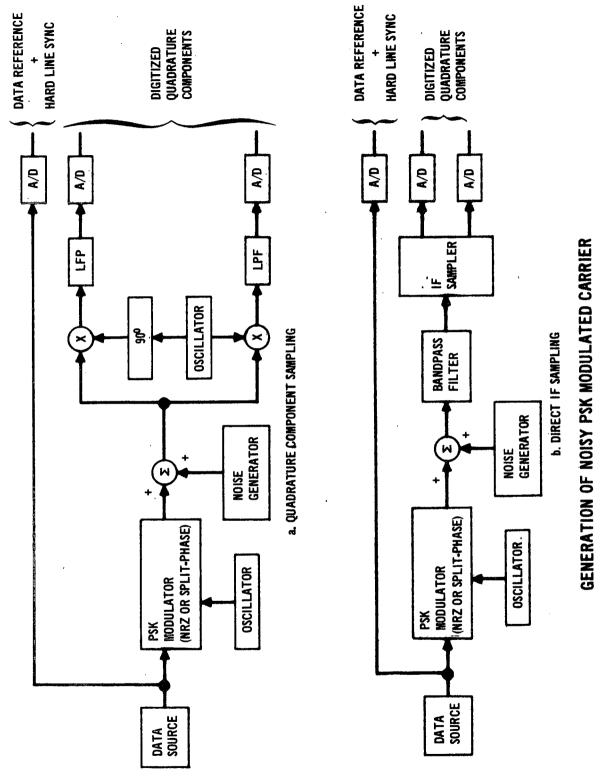

| 50         | Generation of Noisy PSK Modulated Carrier 80                                        |

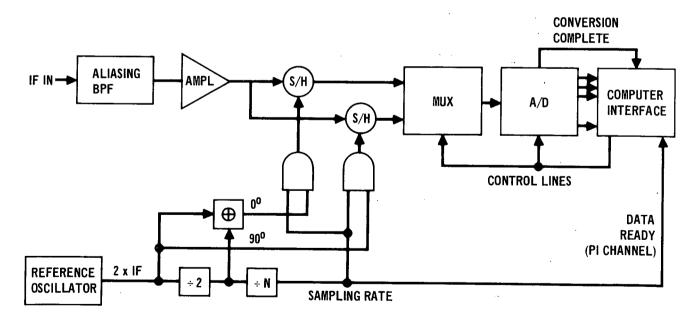

| 51         | Direct IF Sampling and A/D Conversion 81                                            |

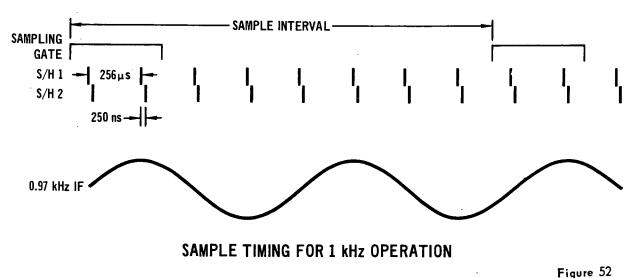

| 52         | Sample Timing for 1 kHz Operation 83                                                |

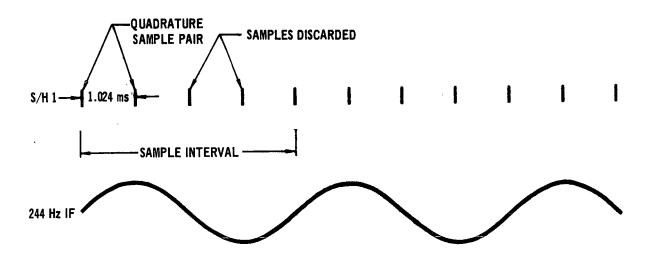

| 53         | Sample Timing for 244 Hz Operation 84                                               |

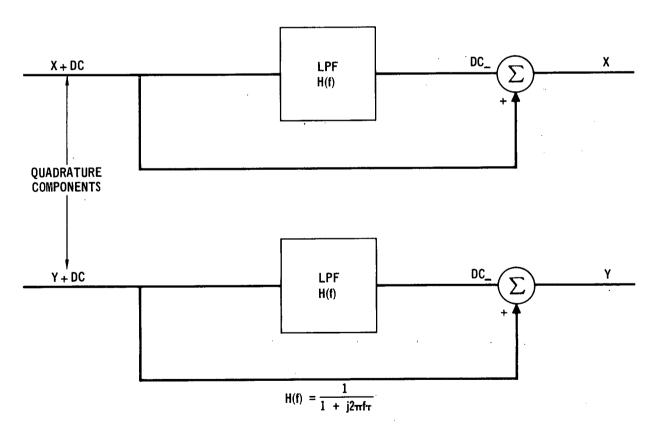

| 54         | DC Bias Remover                                                                     |

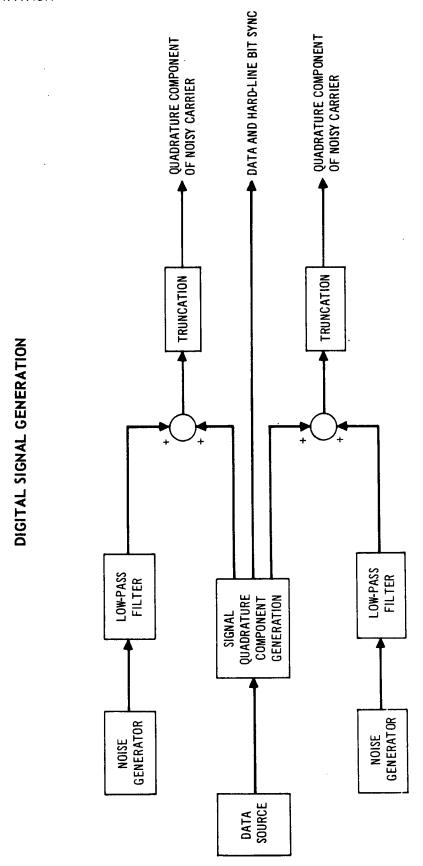

| 55         | Digital Signal Generation                                                           |

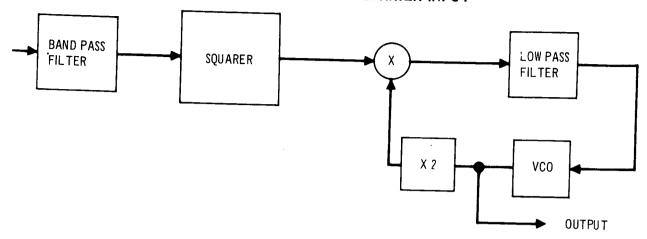

| 56         | The Squaring Loop for Phase-Tracking a Binary-Modulated Suppressed-Carrier Input 91 |

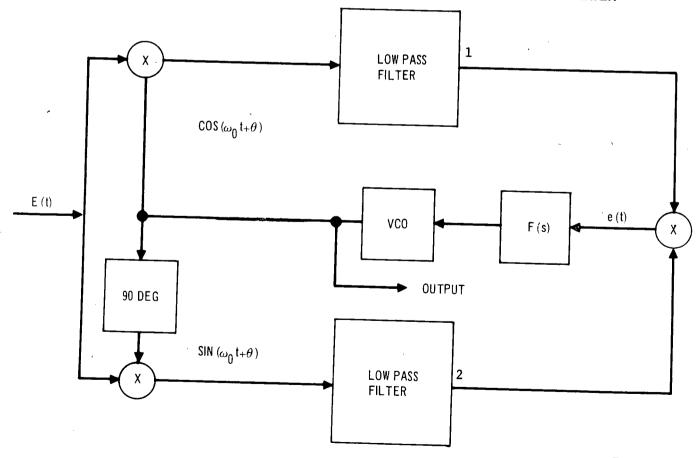

| 57         | The Costas Loop for Phase-Tracking a Binary PSK Carrier                             |

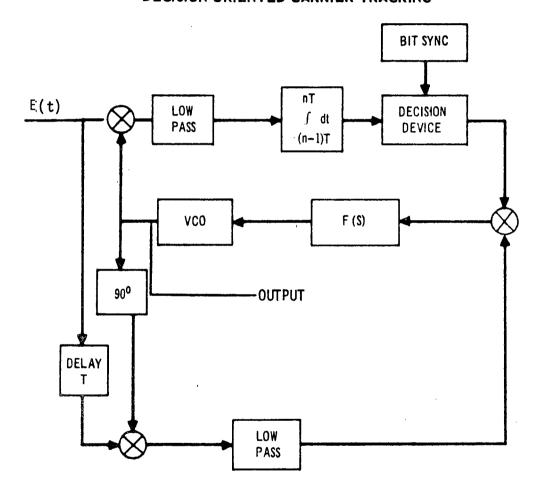

| 58         | Decision-Oriented Carrier Tracking 92                                               |

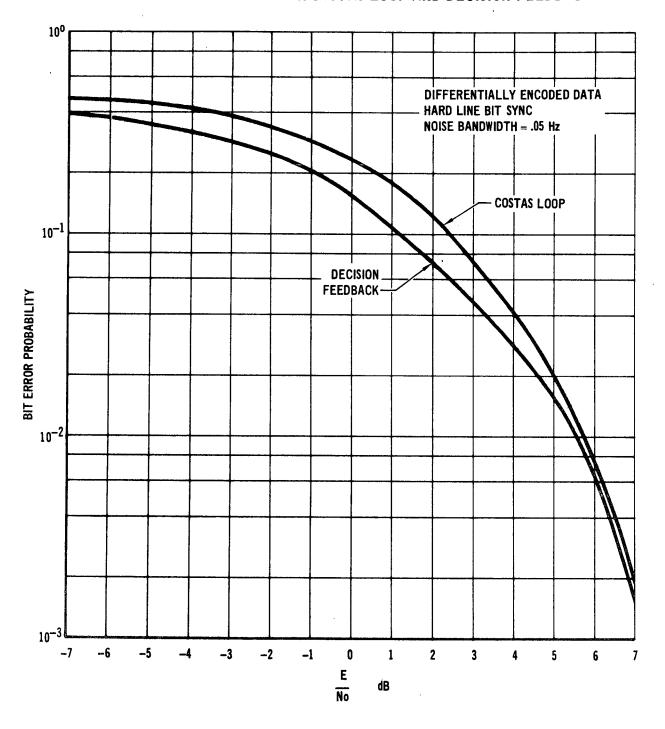

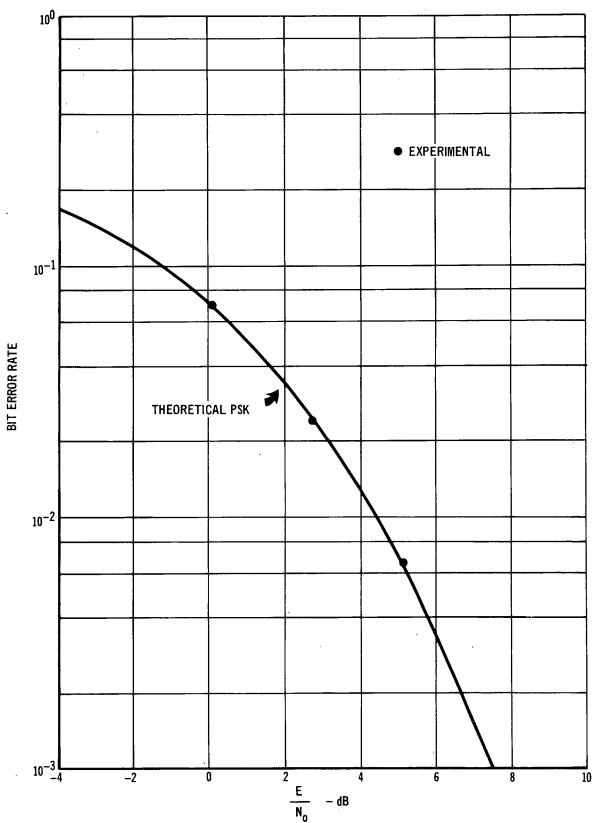

| 59         | Bit Error Probability for Costas Loop and Decision Feedback                         |

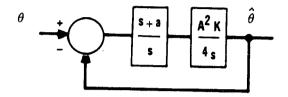

| 60         | Linearized Costas Loop                                                              |

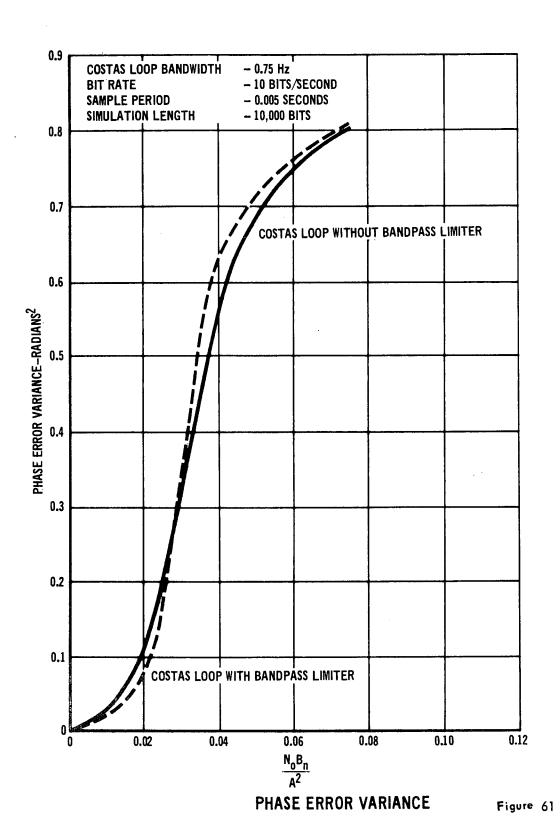

| 61         | Phase Error Variance                                                                |

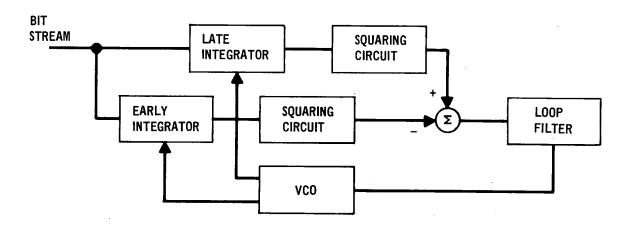

| 62         | Square Law Bit Synchronizer                                                         |

| FIGURE NO. | TITLE                                                                                        |      | PAGE |

|------------|----------------------------------------------------------------------------------------------|------|------|

| 63         | Delay and Multiply Bit Synchronizer                                                          | •    | 107  |

| 64         | Autocorrelation Function for Output of Delay and Multiply Bit Synchronizer                   | •    | 107  |

| 6 <u>5</u> | Gate Location                                                                                | •    | 109  |

| 66         | Gated Bit Synchronizer                                                                       | •    | 109  |

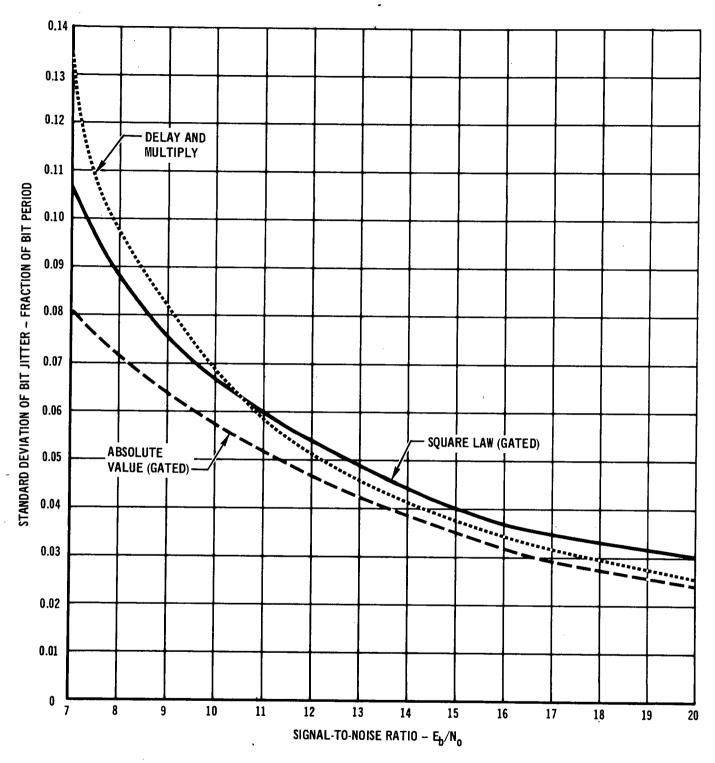

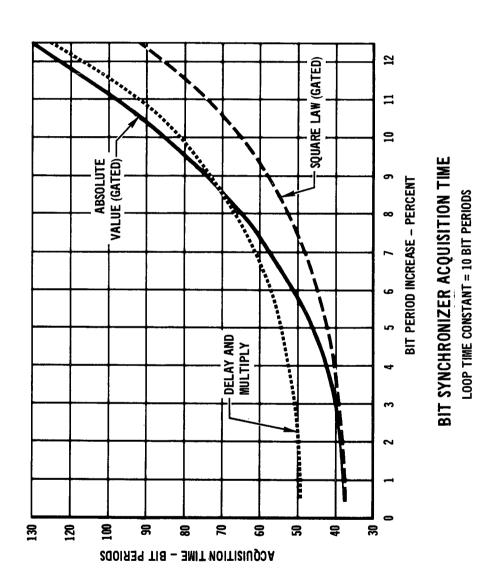

| 67         | Comparison of Bit Synchronizers                                                              | •    | 111  |

| 68         | Bit Synchronizer Acquisition Time                                                            | •    | 112  |

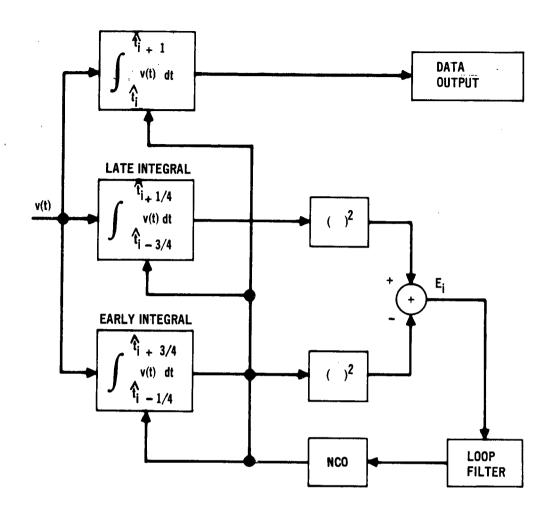

| 69         | Bit Synchronization Loop                                                                     | •    | 114  |

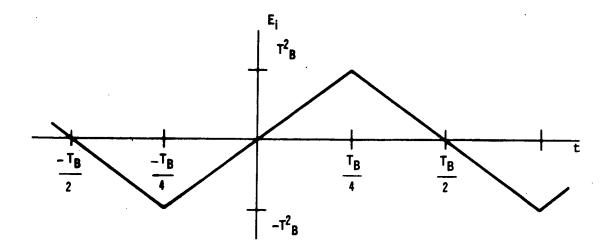

| 70         | Loop Error Signal                                                                            | •    | 116  |

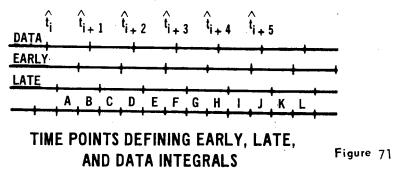

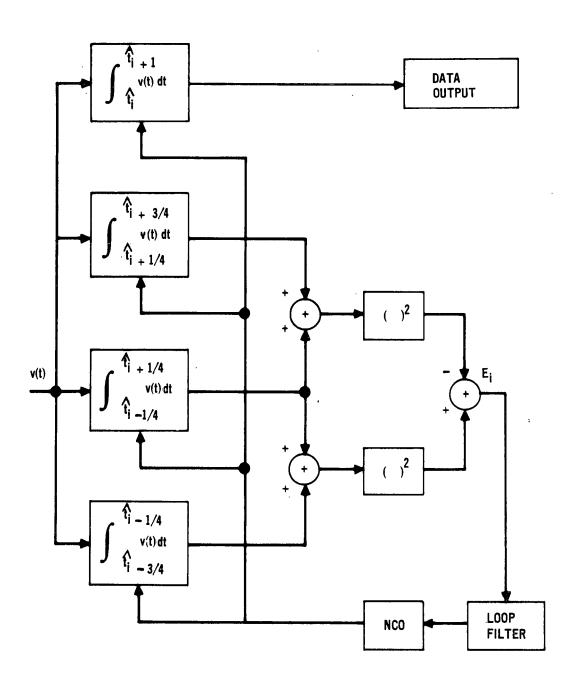

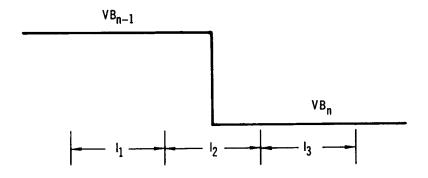

| 71         | Time Points Defining Early, Late, and Data Integrals                                         | •    | 117  |

| 72         | Reduced Bit Synchronization Loop                                                             | •    | 118  |

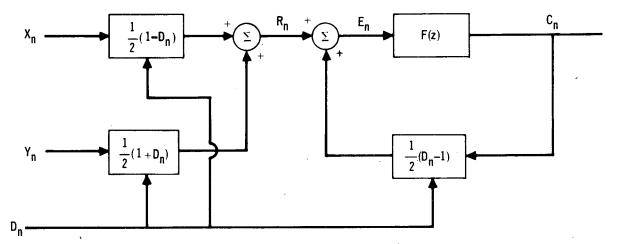

| 73         | Bit Synchronization Feedback Loop                                                            | •    | 120  |

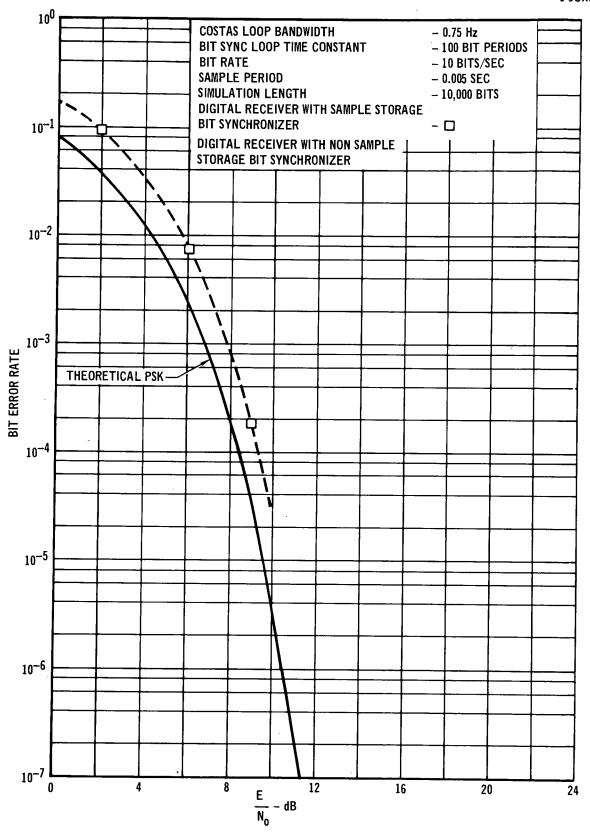

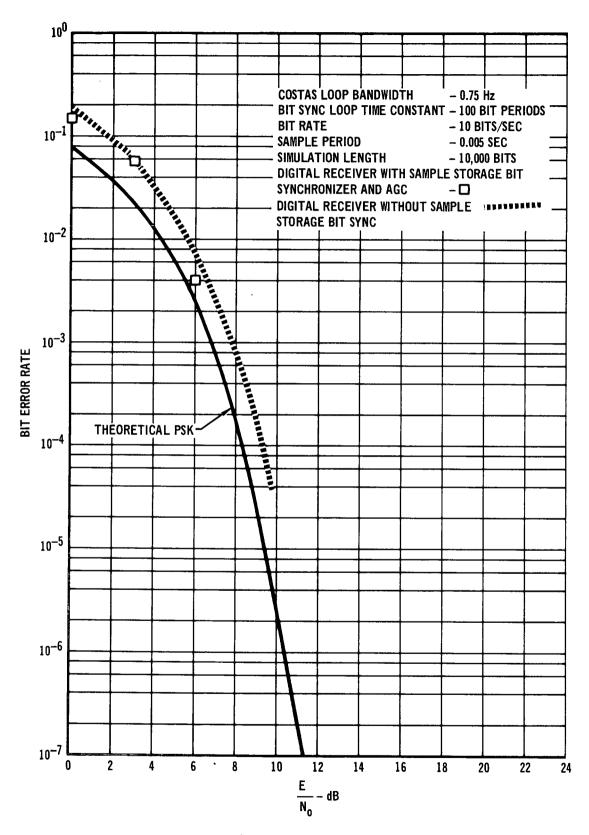

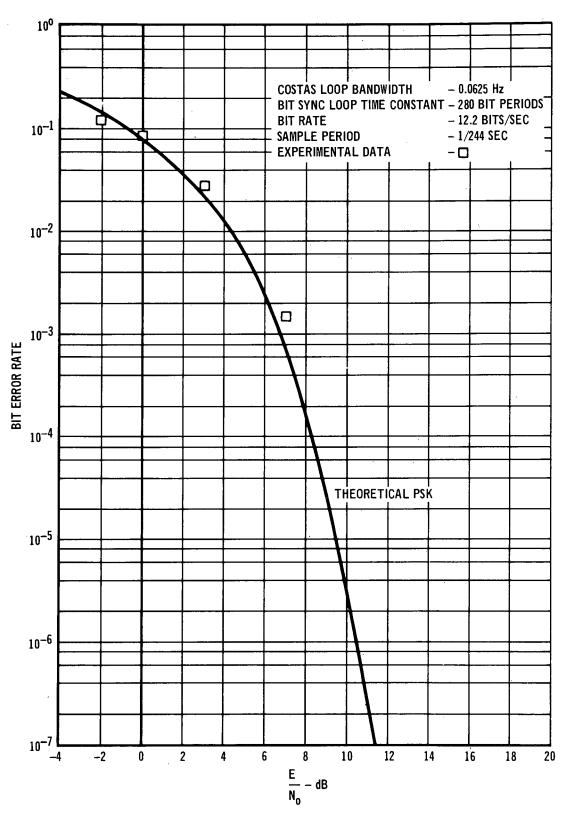

| 74         | Bit Error Rate for Digital Receiver with and without Sample Storage Bit Synchronizer · · · · | •,   | 125  |

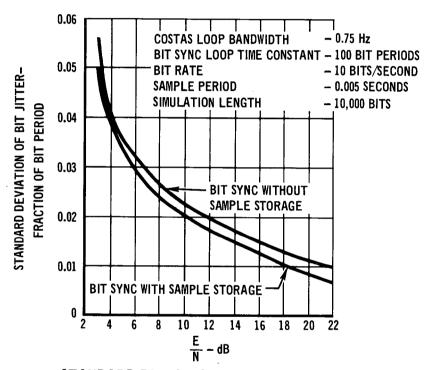

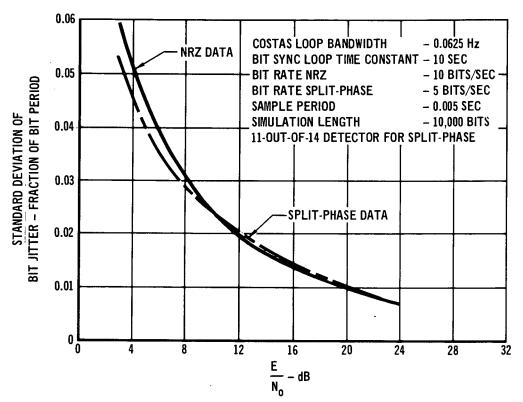

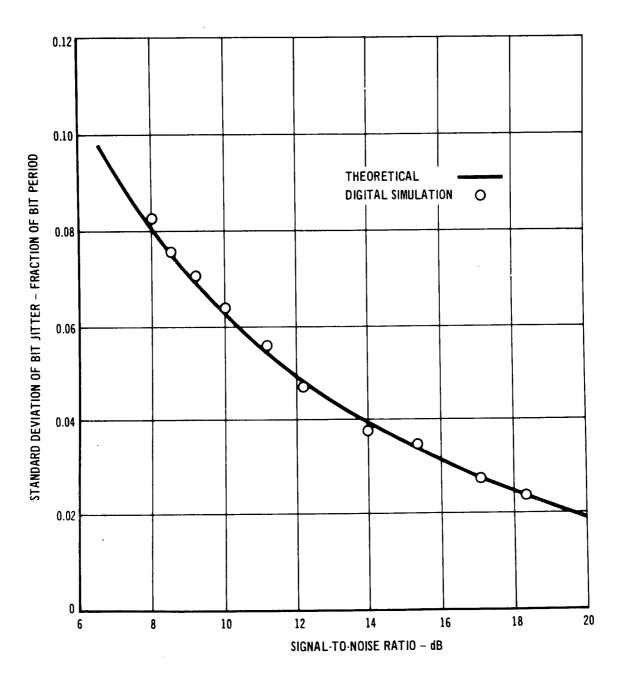

| 75         | Standard Deviation of Bit Jitter                                                             | .• • | 126  |

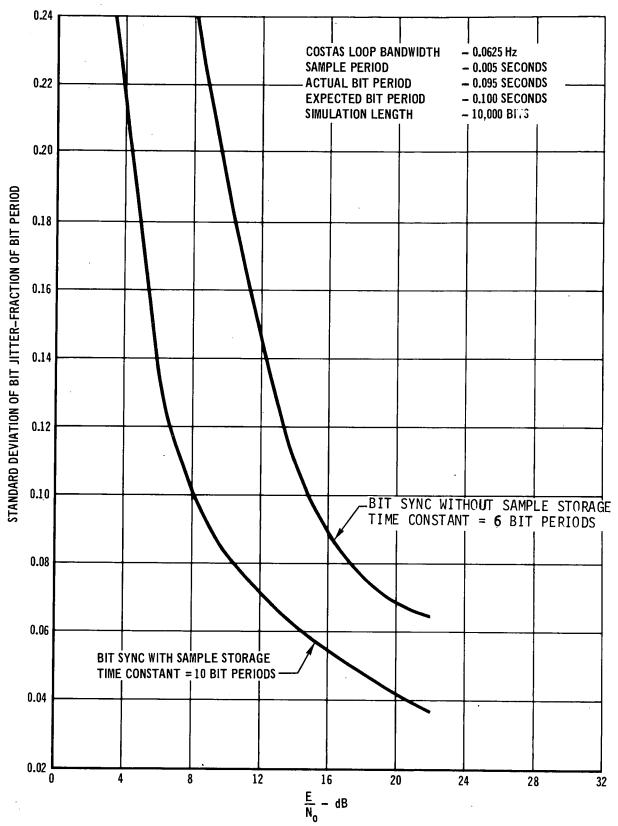

| 76         | Standard Deviation of Bit Jitter - 5% Timing Error                                           | •    | 127  |

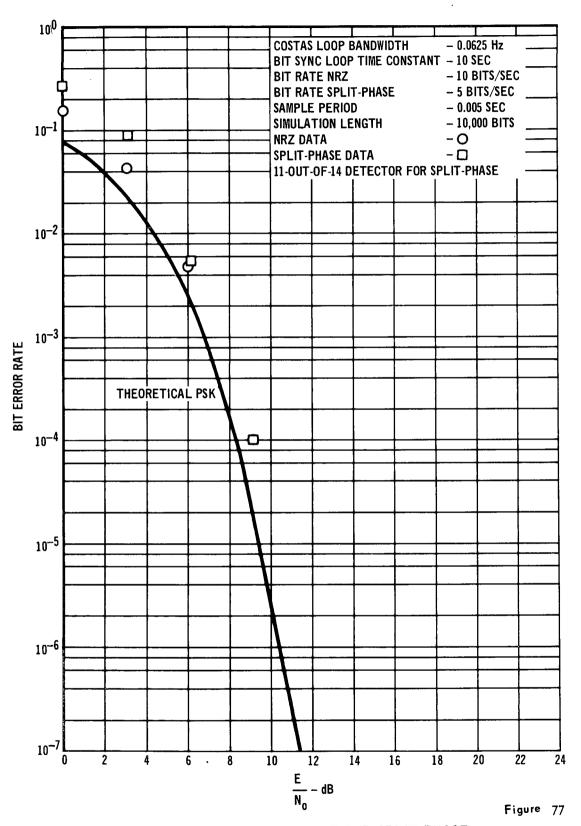

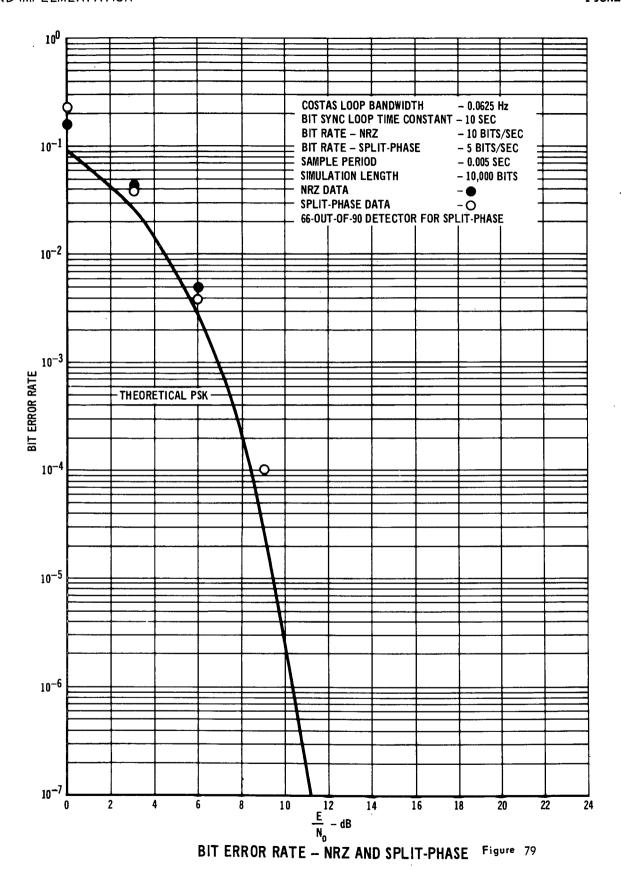

| · 77       | Bit Error Rate - NRZ and Split-Phase                                                         |      | 130  |

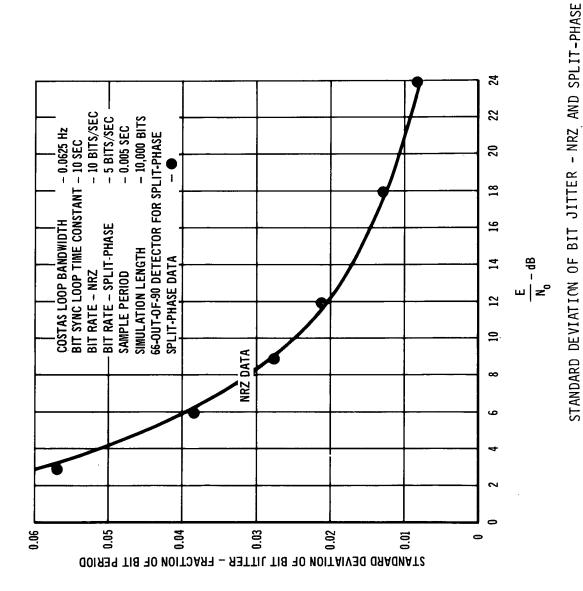

| 78         | Standard Deviation of Bit Jitter - NRZ and Split-Phase                                       | •    | 131  |

| 79         | Bit Error Rate - NRZ and Split-Phase                                                         | •    | 132  |

| 80         | Standard Deviation of Bit Jitter - NRZ and Split-Phase                                       |      | 133  |

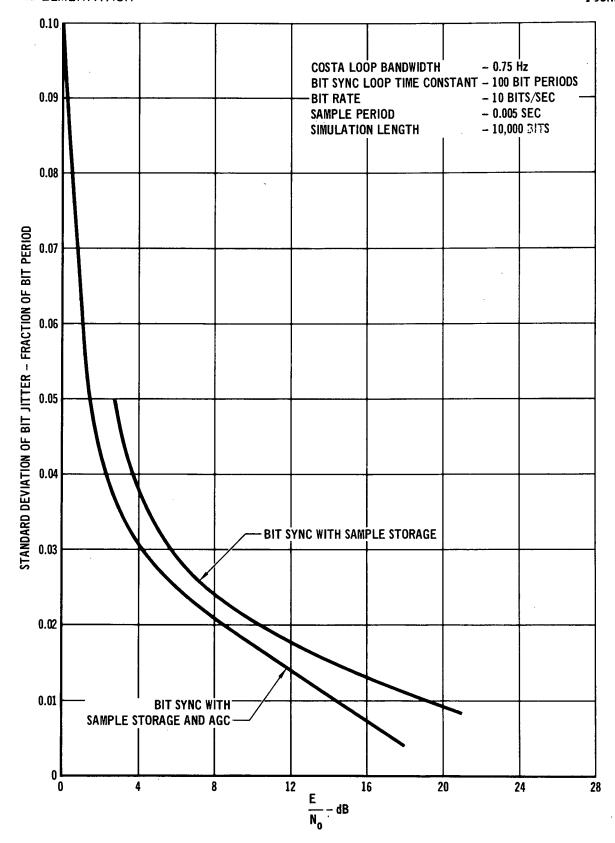

| 81         | Standard Deviation of Bit Jitter; AGC and No AGC                                             | •    | 135  |

| 82         | Digital Receiver with Sample Storage Bit Synchronizer and AGC                                | •    | 136  |

| FIGURE NO. | <u>TITLE</u> PA                                                                         | AGE |

|------------|-----------------------------------------------------------------------------------------|-----|

| 83         | Costas Loop with Hard Line Sync                                                         | 38  |

| 84         | Flow Chart of Digital PSK Receiver with Data Derived Sync                               | 40  |

| 85         | Acquisition Indicator - Simulation 1                                                    | 50  |

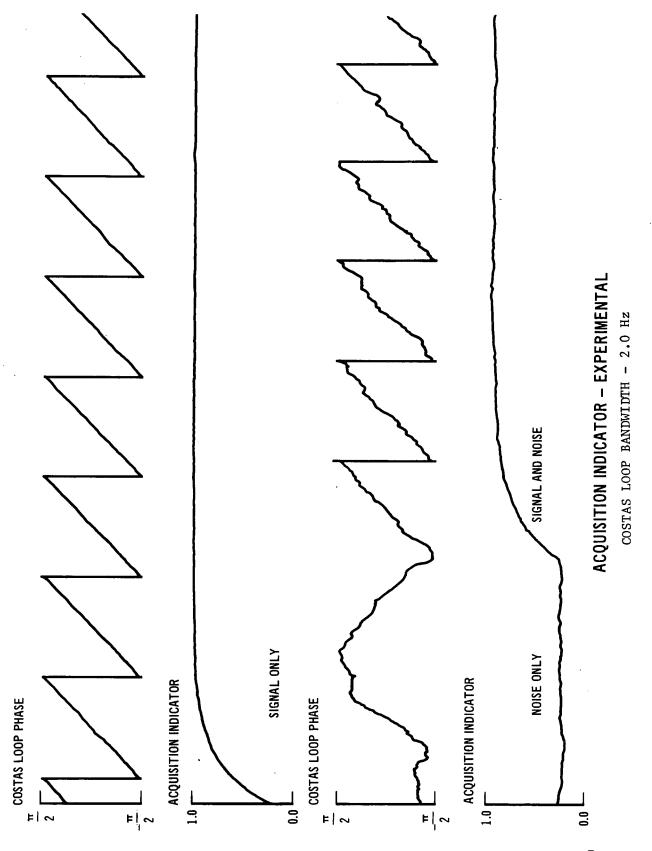

| 86         | Acquisition Indicator - Experimental 1                                                  | 51  |

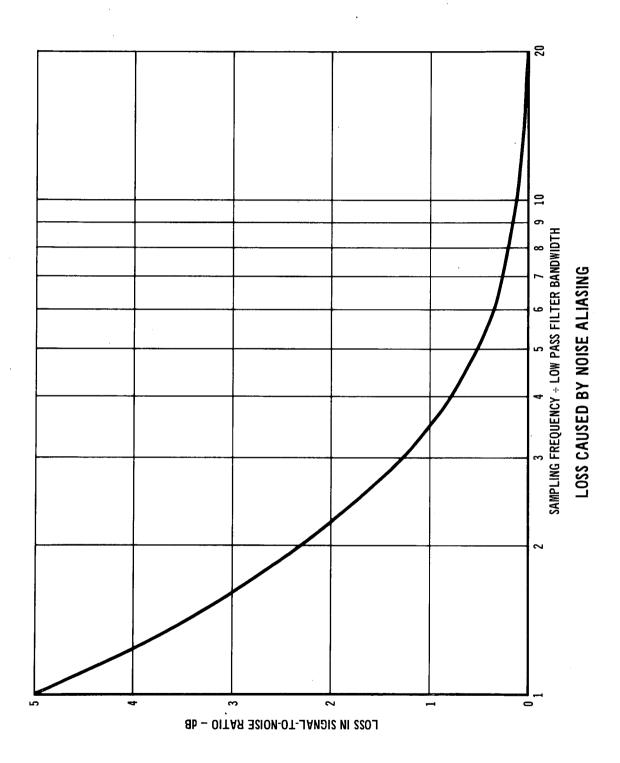

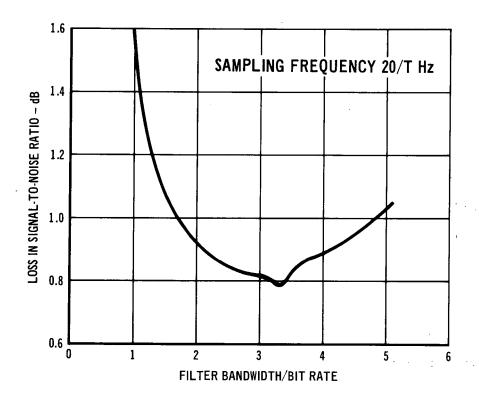

| 87         | Loss Caused by Noise Aliasing 1                                                         | 59  |

| 88         | Loss Caused by Intersymbol Interference 16                                              | 60  |

| 89         | Total Sampling Loss 16                                                                  | 51  |

| 90         | Costas Loop Phase Error Variance 16                                                     | 56  |

| 91         | Probability of Error with a Noisy Phase Reference                                       | 58  |

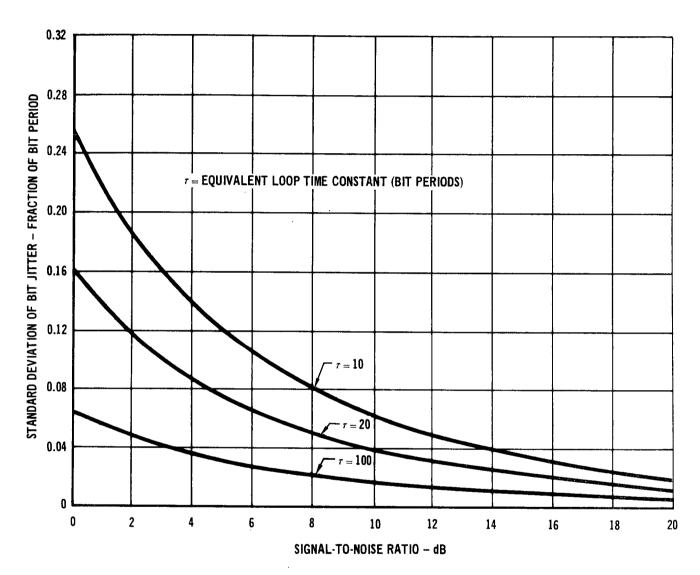

| 92         | Standard Deviation of Bit Jitter Versus Sig-<br>nal-to-Noise Ratio                      | 59  |

| 93         | Bit Synch Error Versus Signal-to-Noise Ratio (Theoretical)                              | 70  |

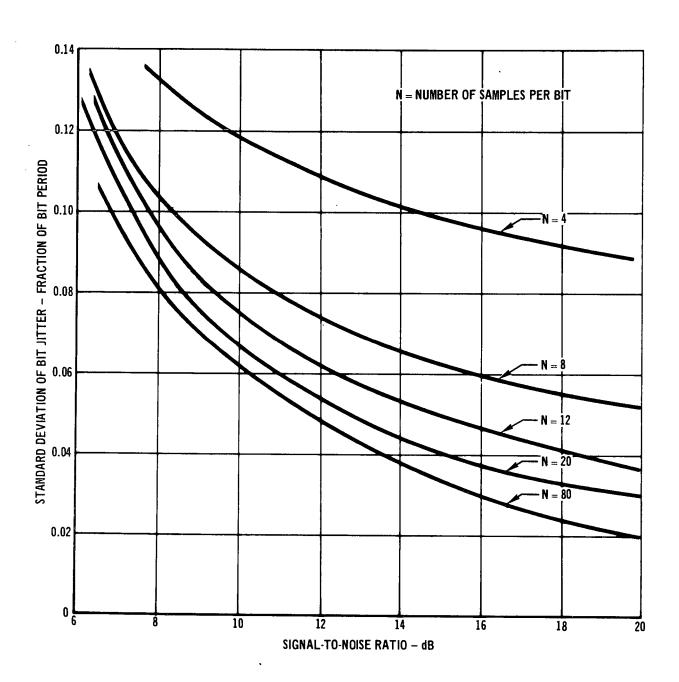

| 94         | Effect of Sample Rate on Bit Sync Error 17                                              | 72  |

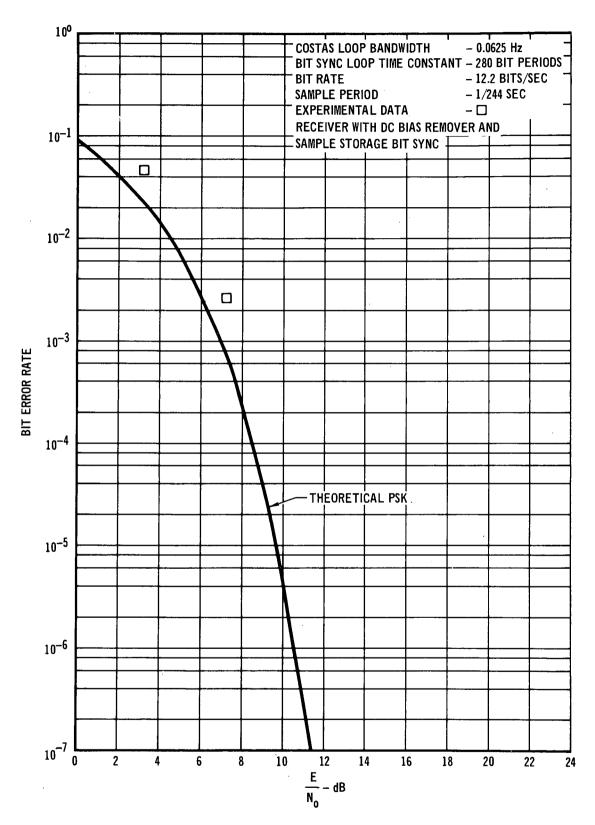

| 95         | Bit Error Rate - Sample Storage Bit Sync 17                                             | 13  |

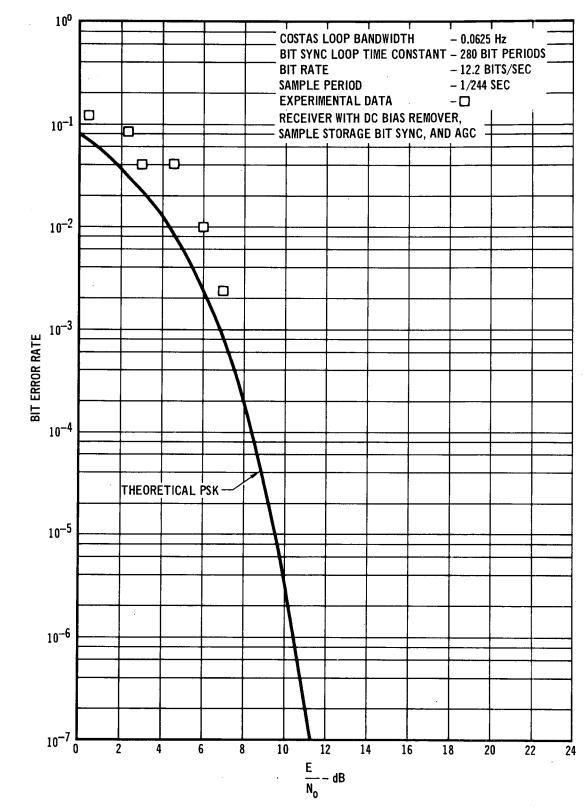

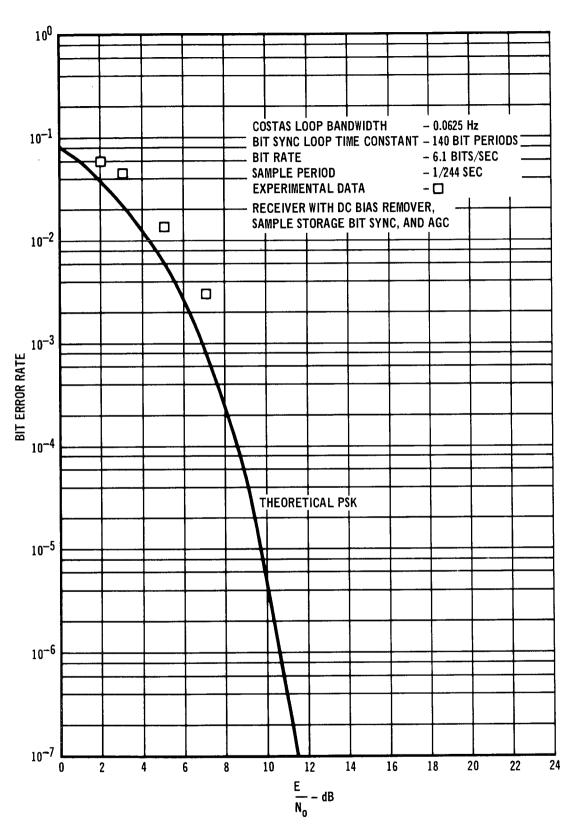

| 96         | Bit Error Rate - AGC                                                                    | '5  |

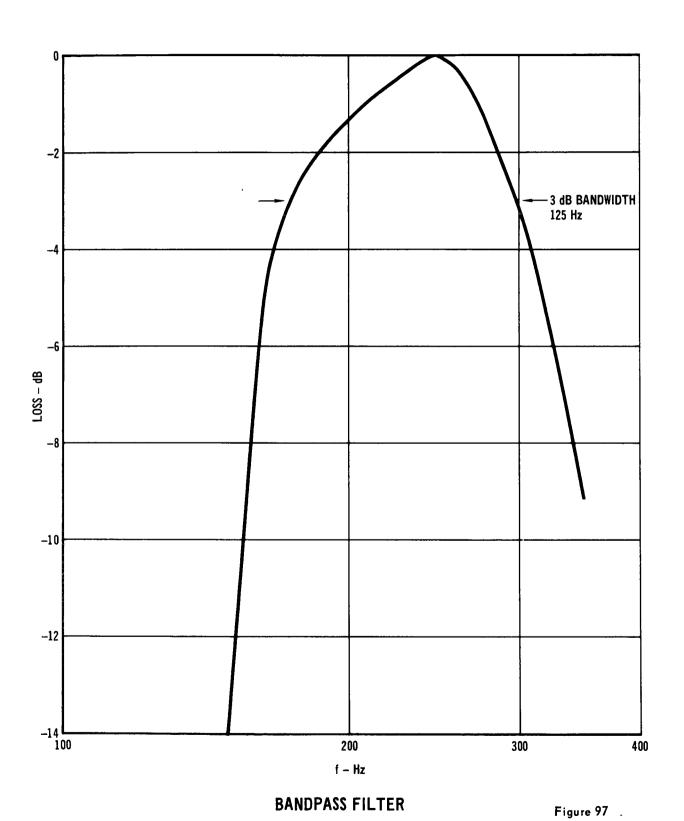

| 97         | Bandpass Filter                                                                         | '6  |

| 98         | Bit Error Rate - Optimized IF Filter 17                                                 | 7   |

| 99         | Bit Error Rate Split-Phase Data 17                                                      | '8  |

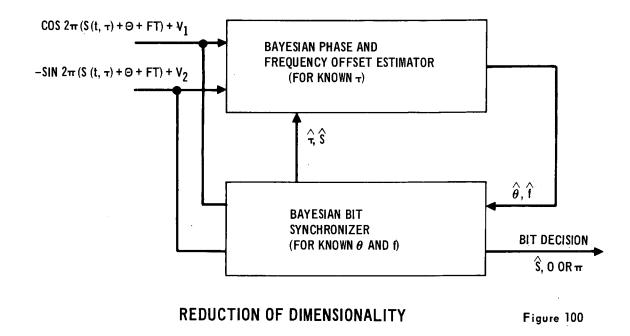

| 100        | Reduction of Dimensionality 18                                                          | 3   |

| 101        | Probability of Bit Error with Bayesian Estimation • • • • • • • • • • • • • • • • • • • | 1   |

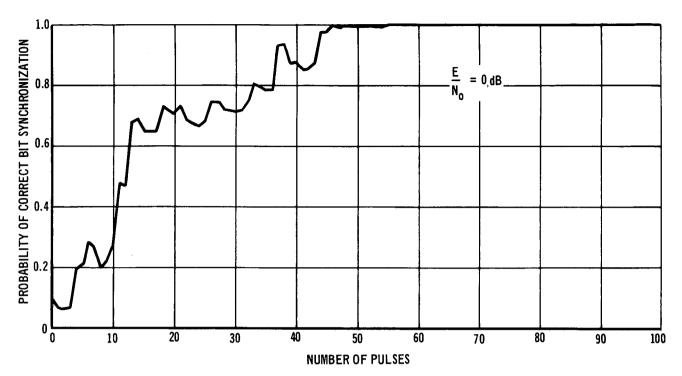

| 102        | Typical Learning Curve for Bit Synchronization 19                                       | 2   |

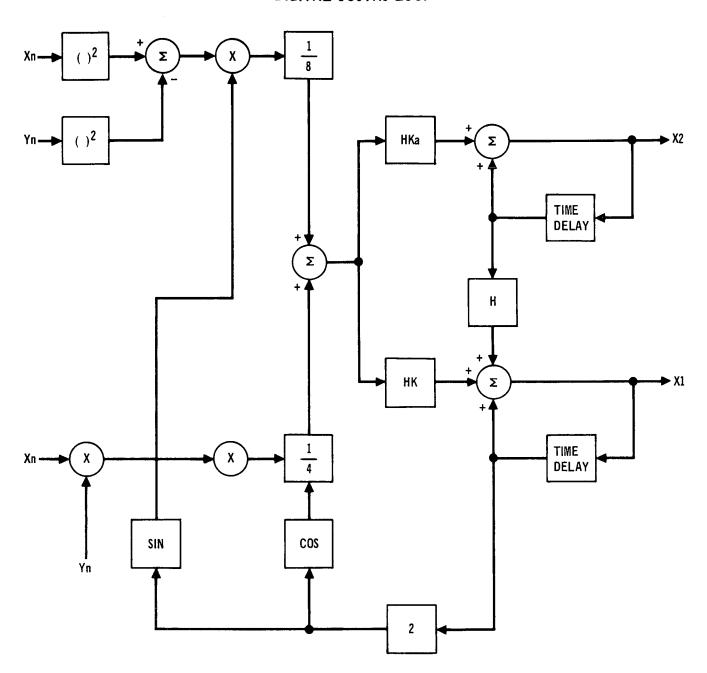

| 103        | Phase Estimation Processor 19                                                           | 4   |

| 104        | Candidate Systems Versus Speed 19                                                       | 6   |

| FIGURE NO. | <u>TITLE</u> PA                                               | <u>GE</u> |

|------------|---------------------------------------------------------------|-----------|

| 105        | Time Slot Operations 19                                       | 6         |

| 106        | Functional Block Diagram 19                                   | 9         |

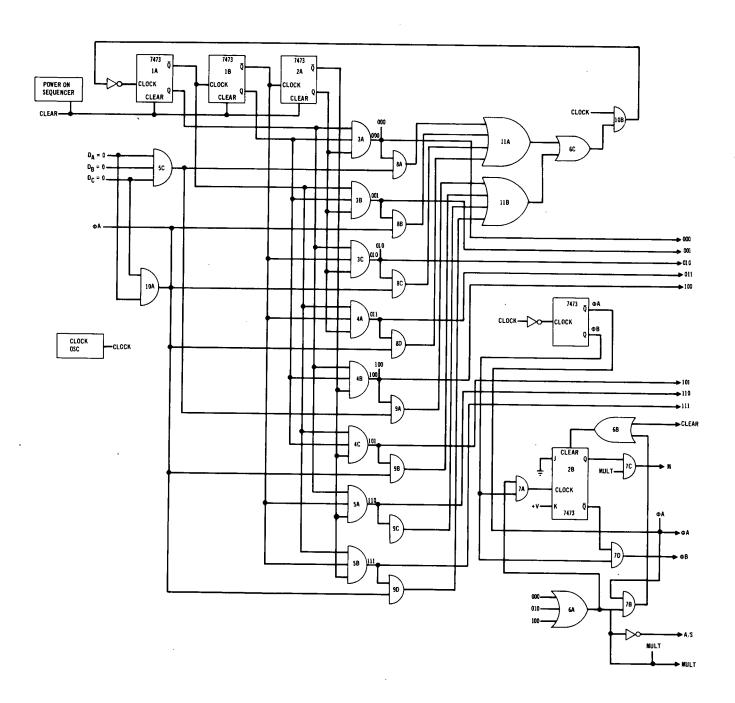

| 107        | Operation Sequencer and Clock 20                              | 3         |

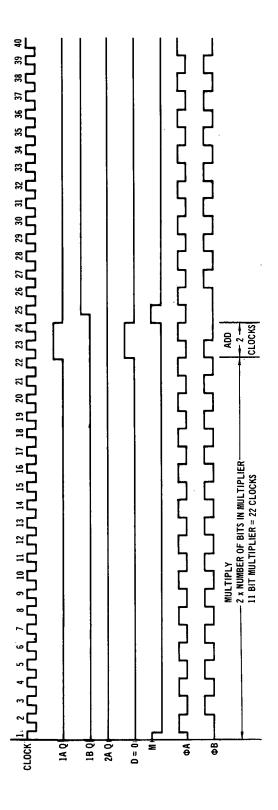

| 108        | Timing Diagram 20                                             | 5         |

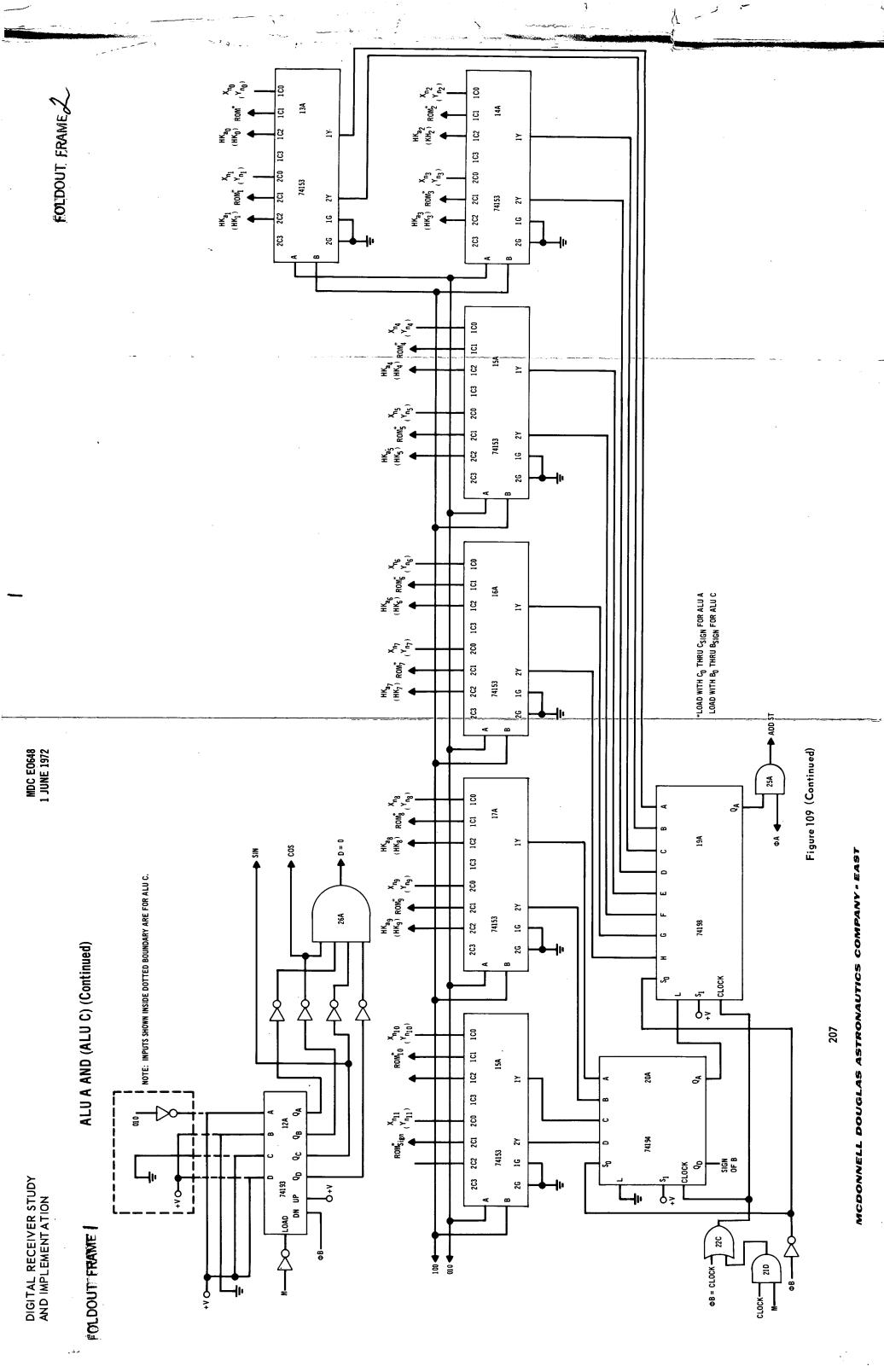

| 109        | Arithmetic Logic Units A and C 20                             | 6 .       |

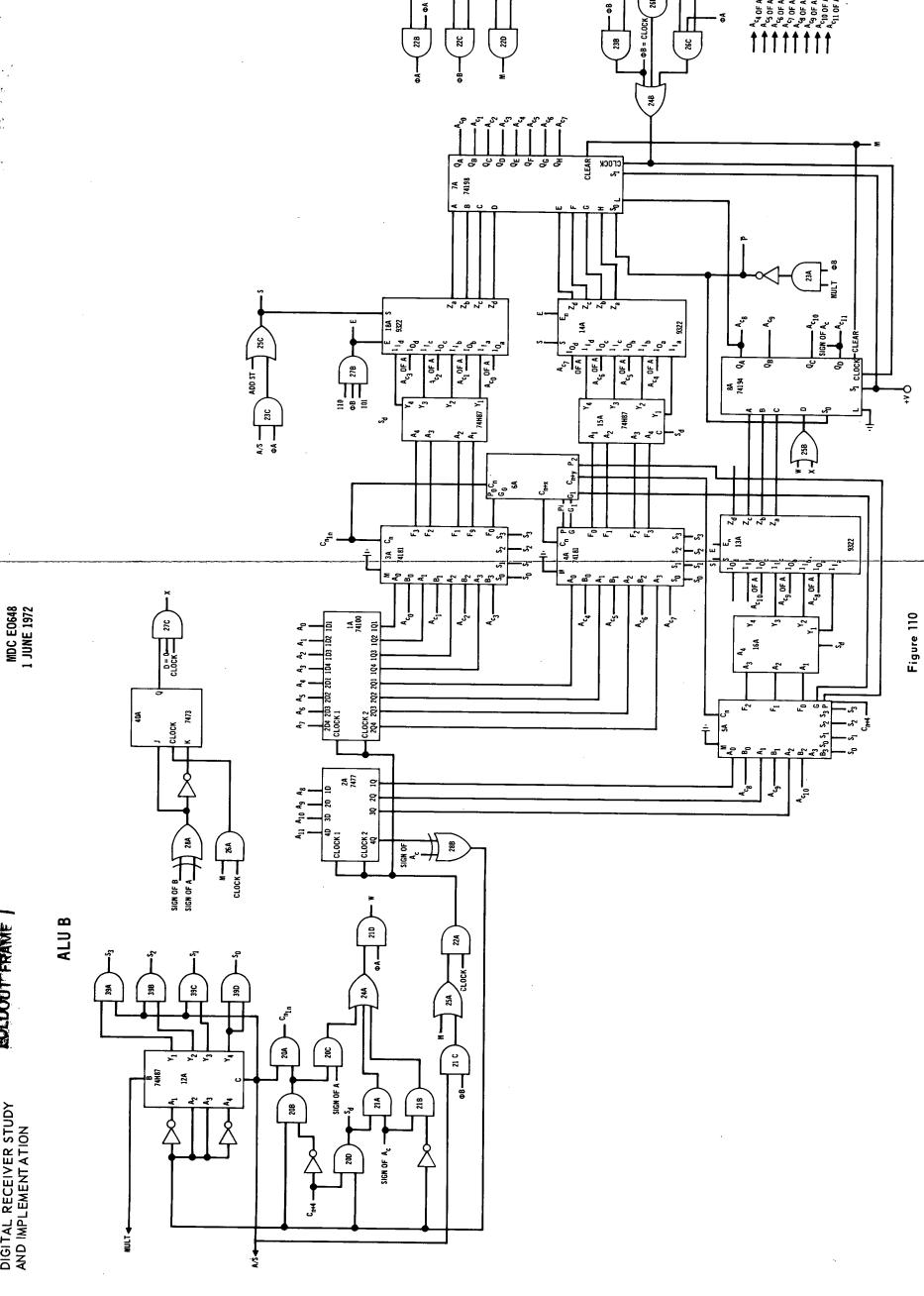

| 110        | Arithmetic Logic Unit B 20                                    | 9 ·       |

| 111        | Method A Sine-Cosine ROM 21                                   | 4         |

| 112        | Method B Sine-Cosine ROM 21                                   | 6         |

| 113        | Input-Output Registers 21                                     | 7         |

| IIII       | Bit Synchronization Model III                                 | [-1       |

| III2       | Bit Synchronization Integrals III                             | [-4       |

| 1113       | Standard Deviation of Bit Jitter Versus Signal-to-Noise Ratio |           |

# 1. INTRODUCTION

Potential applications of digital computers in communications systems continue to expand. Many ground stations have ready access to general purpose computers that could be used as data processors. In this study, we have developed the digital signal processing techniques necessary for performing all the functions of an analog communication receiver.

The computer software developed for the MDAC Digital PSK receiver makes it possible to use any general purpose computer (with A/D conversion capability) as a receiver for low data rate telemetry processing. The first step in the receiver processing is sampling and A/D conversion. The sampling can either be performed directly on the IF signal, or on the quadrature components of the IF signal derived from mixing the IF with a frequency oscillator. We have operated our receiver with both sampling techniques without any noticeable difference in performance.

The sampled quadrature components are A/D converted for further processing by a set of digital algorithms which are roughly equivalent to a digital Costas loop. The output of the Costas loop is mixed with the input signal to develop the NRZ video signal. Bit synchronization is performed by a set of digital algorithms which constitute an early-late gate type synchronizer. The bit synchronizer uses four offset integrators to perform phase detection along with a digital phase locked loop for tracking. A digital integrator and threshold is then used for bit detection.

The logic speed of general purpose computers makes this software useful for data rates of 0-100 bits/second. Very low bit rates are difficult to demodulate with analog processors due to the need for very long time constant filters, precise component values, and very stable timing references. Thus,

the digital software discussed in this report provide a low cost, efficient, and versatile solution to the low data rate receiver problem. This software can also easily be modified to incorporate any data format desired. Measurements of receiver performance (i.e., probability of error/bit) indicate that the Digital PSK Receiver will operate as close to the theoretical optimum as the logic speed and tracking bandwidths will permit.

The Digital Receiver Study and Implementation conducted under contract NAS5-11424 for NASA GSFC, included the optimization of the MDAC digital PSK receiver software (developed under contract NAS5-21021), an expanded study of digital bit synchronization algorithms, and a preliminary study of digital processing techniques which have no real analog equivalent. This report also contains the principal results from the previous contract NAS5-21021, the study of Digital Phase Lock Techniques. The results of both contracts were combined since they are highly interrelated and are both incomplete without the other. All system simulations for both contracts were performed on the MDAC CDC 6400 and CDC 6600 computers, and all receiver software was optimized for the GSFC CDC 3200 computer.

#### 2. DEVELOPMENT OF DIGITIZED PHASE-LOCKED LOOP

This effort consisted of designing, implementing, and evaluating a digitized phase-locked loop capable of tracking a carrier imbedded in wide band noise. As part of the design effort, we compared the various numerical techniques available for implementing a digital filter, synthesized and analyzed the loop equations, and evaluated the performance by determining curves of phase error variance as a function of the signal-to-noise ratio, sampling rate, and quantization interval size. We also investigated digital techniques for implementing AGC and acquisition circuits.

#### 2.1 Synthesis of Equations

We selected a phase-locked loop filter by considering its effect on transient response (damping), bandwidth, and steady state tracking-offset for a ramp input. Utilizing this filter, we analyzed the linear loop in order to determine the filter and gain constants as a function of the damping factor ( $\zeta$ ), and the undamped natural frequency ( $\omega_0$ ). Finally, we analyzed the non-linear loop and developed numerical equivalents for it using both the differential and difference equation approach.

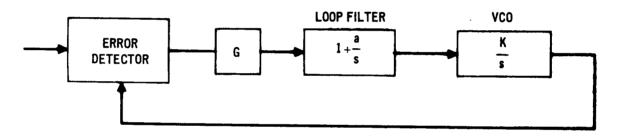

#### 2.1.1 Choice of Phase-Locked Loop Filter

The filter in a second order phase-locked loop can have any of the forms given in Equations (1-3).

$$F_1(s) = \frac{b}{s+b} \tag{1}$$

$$F_2(s) = \left(\frac{b}{a}\right) \frac{(s+a)}{(s+b)}$$

(2)

$$F_3(s) = \frac{s+a}{s} \tag{3}$$

We determined the effect of the three phase-locked loop filters on the transient response (damping), bandwidth, and steady state tracking offset for a ramp input to the associated phase-locked loop. The filter represented by Equation (1) was not chosen because the bandwidth and phase offset both depend on the loop gain and thus cannot be chosen independently. filter given in Equation (2) is utilized, the filter constant (a) and the loop gain are chosen to give the proper bandwidth and damping, and the filter constant (b) is chosen to give an acceptable phase offset. Since the phase offset will normally be made small, the constant (b) for  $F_2(s)$  will be near zero, and  $F_3(s)$  and  $F_2(s)$  are essentially the same. Therefore, the choice must be made in terms of implementation complexity. Since the digital implementation of  $F_{\mathfrak{I}}(s)$  requires one less multiplication, it was selected as the phase-locked loop filter.  $F_2(s)$  would be our choice for an analog implementation because of the difficulty associated with implementing the open loop integrator associated with  $F_3(s)$ . This decision is also supported by the fact that for an input consisting of a ramp of phase the third filter form minimizes the mean squared error at the loop output.

#### 2.1.2 Analysis of Linear Loop

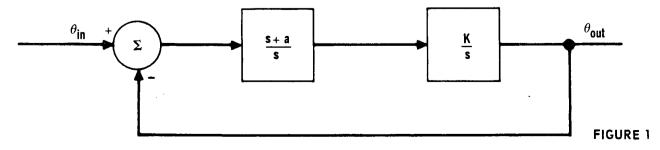

A block diagram of the linearized phase-locked loop is given in Figure 1 where the input signal is assumed to be of the form A  $\sin(\omega_0 t + \Theta_{in})$ .

#### LINEARIZED PHASE - LOCKED LOOP

The loop transfer function can then be determined as shown in Equations (4) and (5).

$$\frac{\theta_{\text{out}}}{\theta_{\text{in}}} = \frac{\frac{AK(s+a)}{s^2}}{1 + \frac{AK(s+a)}{s^2}}$$

(4)

$$\frac{\theta_{\text{out}}}{\theta_{\text{in}}} = \frac{AK(s+a)}{s^2 + AKs + aAK}$$

(5)

This transfer function can then be put in the standard form given in Equation (6).

$$\frac{\theta_{\text{out}}}{\theta_{\text{in}}} = \frac{2\zeta\omega_0 s + \omega_0^2}{s^2 + 2\zeta\omega_0 s + \omega_0^2}$$

(6)

$$AK = 2\zeta\omega_0 \tag{7}$$

$$aAK = \omega_0^2 \tag{8}$$

If the input amplitude, the damping factor ( $\zeta$ ), and the undamped natural frequency ( $\omega_0$ ) are known, the phase-locked loop gain and filter constant can be determined from Equations (7) and (8) and are given in Equations (9) and (10).

$$K = \frac{2\zeta\omega_0}{A} \tag{9}$$

$$a = \omega_0/2\zeta \tag{10}$$

The response of the above loop to a ramp input of slope  $\omega$  is given in Equation (11).

$$\theta_{\text{out}}(t) = \omega t - \frac{2\omega\delta^2}{\omega_0\sqrt{1-\zeta^2}} e^{-\delta\omega_0 t} \sin \omega_0 \sqrt{1-\zeta^2} t \qquad (11)$$

The above result shows that the effective time constant of the loop is  $\frac{1}{\delta\omega_0}$  seconds. The noise and 3 db bandwidth of the above loop are given in Equations (12) and (13).

Noise Bandwidth =

$$B_N = \omega_0 \left( \frac{2\zeta + \frac{1}{2\zeta}}{4} \right)$$

Hz (12)

3 db Bandwidth =

$$\frac{\omega_0}{2\pi} \sqrt{(2\zeta^2 + 1) + \sqrt{(2\zeta^2 + 1)^2 + 1}}$$

Hz (13)

#### 2.1.3 Differential Equation Approach

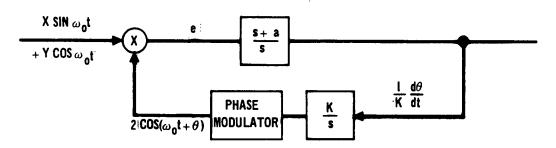

With the loop parameters established in terms of standardized functions, we proceeded to develop the numerical equivalents for the differential equations which describe the loop operation. From the block diagram of the phase-locked loop presented in Figure 2, the loop equations can be derived as shown in Equations (14-17).

# PHASE – LOCKED LOOP BLOCK DIAGRAM

FIGURE 2

$$e = 2(X \sin \omega_0 t + Y \cos \omega_0 t) \cos (\omega_0 t + \theta)$$

(14)

$$e = -X \sin \theta + Y \cos \theta + (second harmonic terms)$$

(15)

$$\frac{d^2\theta}{dt^2} = K(\frac{d}{dt} + a)e \tag{16}$$

$$\frac{d^2\theta}{dt^2} = aK \left[ Y \cos \theta - x \sin \theta \right] + K \frac{d}{dt} \left[ Y \cos \theta - X \sin \theta \right]$$

(17)

To avoid taking the derivative of the quadrature components, the above equation can then be converted to the form shown in Equations (18) and (19).

$$\frac{dc}{dt} = aK \left( Y \cos \theta - X \sin \theta \right) \tag{18}$$

$$\frac{d\theta}{dt} = c + K (Y \cos \theta - X \sin \theta)$$

(19)

One discrete time technique that was used to solve the above equations is the Runge-Kutta Method. Using results obtained from Scarborough<sup>1</sup>, the equations for this technique are shown in **Figure 3.** A second technique investigated was Euler's Method. The equations for this method are also given in Figure 3. A comparison of these and other techniques is presented in Section 2.3.

# DIFFERENTIAL EQUATION IMPLEMENTATION

```

= INPUT SINE WAVE AMPLITUDE

= TIME INCREMENT

= OUTPUT PHASE AT TIME tn

= DUMMY VARIABLE C AT TIME tn

= QUADRATURE COMPONENTS OF INPUT SIGNAL AT TIME t<sub>n</sub>

= 2\zeta\omega_0/A

=\omega_0/2\zeta

RUNGE - KUTTA METHOD

F(\theta, X, Y) = Kh (Y COS \theta - X SIN \theta)

= F(\theta_{n-2}, X_{n-2}, Y_{n-2})

= hC_{n-2} + G_1

A_1

= aG<sub>1</sub>

В

= F(\bar{\theta}_{n-2} + A_1/2, X_{n-1}, Y_{n-1})

= h[C_{n-2} + B_1/2] + G_2

= F(\bar{\theta}_{n-2} + A2/2, X_{n-1}, Y_{n-1})

= h[C_{n-2} + B2/2] + G_3

A<sub>3</sub>

= aG<sub>3</sub>

= F(\hat{\theta}_{n-2} + A_3, X_n, Y_n)

= h[C_{n-2} + B_3] + G_4

= C_{n-2} + (B_1 + 2B_2 + 2B_3 + B_4)/6

=\theta_{n-2}+(A_1+2A_2+2.A_3+A_4)/6

EULER'S METHOD

= Y_{n-1} \cos \theta_{n-1} - X_{n-1} \sin \theta_{n-1}

G

= \theta_{n-1} + h C_{n-1} + KhG

= C_{n-1} + aKhG

C<sub>n</sub>

```

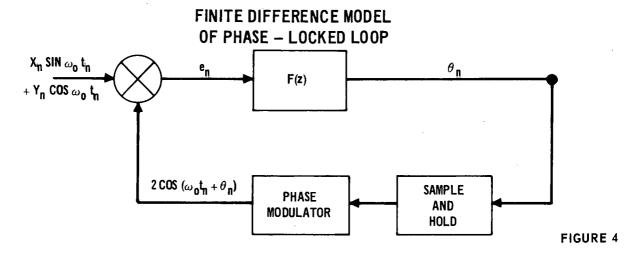

#### 2.1.4 <u>Difference Equation Formulation</u>

The difference equation approach is basically a method of determining the present value of the phase-locked loop output in terms of past output values and past and present input values. In order to formulate the difference equations for the phase-locked loop, the block diagram of Figure 4 is utilized.

The difference equations for the above model can be written as shown in Equations (20-23).

(20-23).

$$e_n = 2(X_n \sin \omega_0 t_n + Y_n \cos \omega_0 t_n) \cos (\omega_0 t_n + \Theta_n)$$

(20)

$$e_n = -X_n \sin \theta_n + Y_n \cos \theta_n + (second harmonic terms)$$

(21)

$$\frac{\theta(z)}{e(z)} = \frac{A_2 z^2 + A_1 z + A_0}{B_2 z^2 + B_1 z + B_0}$$

(22)

$$\Theta_{n} = \frac{1}{B_{2}} (A_{2}e_{n} + A_{1}e_{n-1} + A_{0}e_{n-2} - B_{1}\Theta_{n-1} - B_{0}\Theta_{n-2})$$

$$z = Z-Transform operator$$

(23)

The first technique we investigated for implementing difference equations was the Z-Transform method. In order to use this technique a hold circuit must be placed in front of the phase-locked loop filter. F(z) can then be determined as shown

$$F(z) = (1-z^{-1}) \quad Z \qquad \boxed{\frac{Ks + aK}{s^3}}$$

(24)

$$F(z) = \frac{(2Kh + aKh^2)z + (aKh^2 - 2Kh)}{2(z^2 - 2z + 1)}$$

(25)

The difference equation for the loop can be written as shown in Equations (26-28).

$$e_{n-1} = Y_{n-1} \cos \theta_{n-1} - X_{n-1} \sin \theta_{n-1}$$

(26)

$$e_{n-2} = Y_{n-2} \cdot \cos \theta_{n-2} - X_{n-2} \sin \theta_{n-2}$$

(27)

$$\Theta_{n} = 2\Theta_{n-1} - \Theta_{n-2} + \frac{1}{2} (2Kh + aKh^{2}) e_{n-1} + \frac{1}{2} (aKh^{2} - 2Kh) e_{n-2}$$

(28)

The second technique investigated was Tustin's Method. This technique corresponds to trapezoidal rule integration. In order to obtain the difference equation from the transfer function, the integration operators are replaced by

$$\frac{1}{s} \frac{h(1+z^{-1})}{2(1-z^{-1})}$$

(29)

$$\frac{1}{s^2} \xrightarrow{\frac{h^2(1+z^{-1})^2}{4(1-z^{-1})^2}}$$

(30)

F(z) can then be obtained

$$F(s) = \frac{\theta(s)}{e(s)} = \frac{Ks + aK}{s^2} = K(\frac{1}{s}) + aK(\frac{1}{s^2})$$

(31)

$$F(s) = \frac{\theta(s)}{e(s)} = \frac{Ks + aK}{s^2} = K(\frac{1}{s}) + aK \left(\frac{1}{s^2}\right)$$

$$F(z) = F(s)$$

$$\frac{1}{s^2} = \frac{h^2(1+z^{-1})^2}{4(1-z^{-1})^2}, \frac{1}{s} = \frac{h(1+z^{-1})}{2(1-z^{-1})}$$

(32)

$$F(z) = \frac{\theta(z)}{e(z)} = \frac{2Kh(z^2-1) + aKh^2(z^2+2z+1)}{4(z^2-2z+1)}$$

(33)

Since the phase output  $\theta_n$  depends on  $e_n$ , a unit delay must be added in the feedback path. The results are given in Equations (34-37).

$$e_n = Y_n \cos \theta_{n-1} - X_n \sin \theta_{n-1}$$

(34)

$$e_{n-1} = Y_{n-1} \cos \theta_{n-2} - X_{n-1} \sin \theta_{n-2}$$

(35)

$$e_{n-2} = Y_{n-2} \cos \theta_{n-3} - X_{n-2} \sin \theta_{n-2}$$

(36)

$$\theta_{n} = 2\theta_{n-1} - \theta_{n-1} + \frac{1}{4} (2Kh + aKh^{2}) e_{n} + \frac{1}{2} aKh^{2} e_{n-1} + \frac{1}{4} (aKh^{2} - 2Kh) e_{n-2}$$

(37)

The final technique considered was the Anderson, Ball, Voss Method. This technique consists of approximating the input signal by a polynomial in t and then computing the response at the output of the filter. The input signal was approximated by a second order polynomial, and the resulting difference equation is given in Equations (38-41). The unit delay is again added in the feedback path because of the problem mentioned with respect to Tustin's Method. Because of the complexity associated with this technique, the derivation of this result appears in Appendix I.

$$e_n = Y_n \cos \theta_{n-1} - X_n \sin \theta_{n-1}$$

(38)

$$e_{n-1} = Y_{n-1} \cos \theta_{n-2} - X_{n-1} \sin \theta_{n-2}$$

(39)

$$e_{n-2} = Y_{n-2} \cos \theta_{n-3} - X_{n-2} \sin \theta_{n-3}$$

(40)

$$\theta_{n} = 2\theta_{n-1} - \theta_{n-2} + (\frac{1}{2} Kh + \frac{1}{12} aKh^2) e_{n}$$

$$+\frac{5}{6} \text{ aKh}^2 \text{ e}_{n-1} + (\frac{1}{12} \text{ aKh}^2 - \frac{1}{2} \text{ Kh}) \text{ e}_{n-2}$$

(41)

Equations (38-41) show that the Anderson, Ball, Voss technique gives results that are almost identical with those obtained using Tustin's Method. Therefore, for this particular filter, the higher order approximation used with the Anderson, Ball, Voss technique does not increase the accuracy of the result. We also investigated the Madwed-Truxal and the Boxer-Thaler Techniques. These

methods are similar to Tustin's method except that different approximations are used for the higher order integration operators. Our results showed that these techniques give only an insignificant increase in accuracy and are more unstable than Tustin's method. Therefore, it was concluded that these techniques did not merit further consideration.

#### 2.2 Development of Computer Programs

We developed digital computer programs for the five techniques considered in Section 2.1. These programs were written in the Fortran IV language which is compatible with the CDC 3200 computer. The Runge-Kutta Method is shown in Figure 5; Euler's Method and the Z-Transform technique is shown in Figure 6; and Tustin's Method and the Anderson, Ball, Voll (ABV) Method is illustrated in Figure 7. In these figures ADC (01) and ADC (02) represent the digitized values of the sampled quadrature components which have been sent through the analog to digital converters.

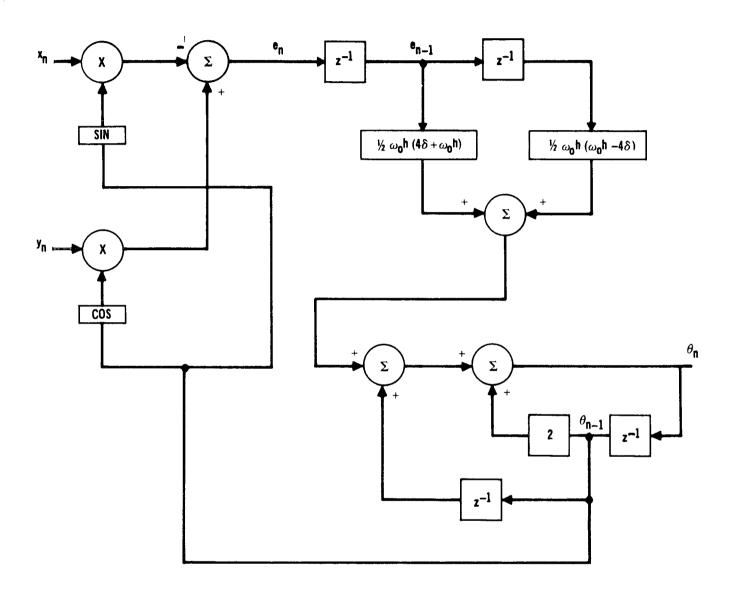

Mechanization block diagrams for the Z-Transform technique and for Euler's method are shown in Figures 8 and 9 respectively. As is shown in the following section, these two approaches give near optimum results for the non-linear phase-locked loop. The blocks containing Z<sup>-1</sup> represent a storage register which delays the signal by one sample period.

The most complex and time consuming portion of these implementations is the sine and cosine calculation. One possible method of simplifying this calculation is to compute new values of the sine and cosine from the previous values by using the small angle approximation as shown in Equations (42) and (43).

## **COMPUTER PROGRAM FOR RUNGE - KUTTA METHOD**

```

ADC(01) = DIGITIZED VALUE OF X QUADRATURE COMPONENT FROM ANALOG CIRCUITRY

ADC(01) = DIGITIZED VALUE OF Y QUADRATURE COMPONENT FROM ANALOG CIRCUITRY

Н

= TIME BETWEEN SAMPLES

AK

= KH

AA

= a

C6

= H/2

Т

=\theta_{\mathsf{n}}

TM1

=\theta_{n-1}

TM2

=\theta_{n-2}

= \cdot \mathbf{C_n}

С

CM1

= \cdot c_{n-1}

CM2

= C<sub>n-2</sub>

XM

= Xn

YM

= Yn

SMI

≈ ·Xn-1

YMI

= y_{n-1}

XM2

= ·x<sub>n-2</sub>

YM2

= y_{n-2}

XM

= ADC(01)

YM

= ADC(02)

C3

= CM2 * H

C2

= AK * (XM2 * SIN(TM2) -YM2 * COS(TM2))

A1

= C3 + C2

B1

= AA * C2

C4

= TM2 + .5 * A1

C2

= AK * (XM1 * SIN(C4) - YM1 * COS(C4))

A2

= C3 + C6 * B1 + C2

B2

= AA * C2

X4

= TM2 + .5 * A2

C2

= AK * (XM1 * SIN(C4) -YM1 * COS(C4))

A3

= C3 + C6 * B2 + C2

B3

= AA * C2

C4

= TM2 + A3

C2

= AK * (XM * SIN(C4) -YM * COS(C4))

A4

= C3 + H * B3 + C2

B4

= AA * C2

= TM2 + (A1 + 2 * (A2 + A3) + A4)/6.

Т

C

= CM2 + (B1 + 2 * (B2 + B3) + B4)/6.

YM2

= YM1

XM2

= XM1

YM1

= YM

XM1

= XM

TM2

= TM1

TM1

= T

CM2

= CM1

CM1

= C

```

#### COMPUTER PROGRAMS FOR EULER'S AND THE Z-TRANSFORM METHOD

```

EULER'S METHOD

H = TIME BETWEEN SAMPLES

AK = KH

AA = a

T = \theta_n

X = ADC(01)

Y = ADC (02)

TEMP = AK * (Y * COS(T) - X * SIN(T))

T = T + C * H + TEMP

C = C + AA * TEMP

Z - TRANSFORM METHOD

H = TIME BETWEEN SAMPLES

A1 = KH + \frac{1}{2}aKH^2

A2 = \frac{1}{2}aKH^2 - KH

T = \theta_n

TM1 = \theta_{n-1}

TM2 = \theta_{n-2}

EM1 = e_{n-1}

EM2 = e_{n-2}

x_{n-1} = x_{n-1}

y_{n-1}

XM1 = ADC(01)

YM1 = ADC(02)

EM1 = YM1 * COS(TM1) - XM1 * SIN(TM1)

T = 2 * TM1 - TM2 + A1 * EM1 + A2 * EM2

TM2 = TM1

TM1 = T

EM2 = EM1

```

# COMPUTER PROGRAM FOR TUSTIN'S AND ABV METHOD

```

T = \theta_n

TM1 = \theta_{n-1}

TM2 = \theta_{n-2}

EM1 = e_{n-1}

EM2 = e_{n-2}

XM = x_{n-1}

YM = y_{n-1}

TUSTIN'S METHOD

H = TIME BETWEEN SAMPLES

C1 = KH/2 + aKH^2/2

C2 = aKH^2/2

C3 = aKH^2/4 - KH/2

XM = ADC(01)

YM = ADC(02)

EM = YM * COS(TM1) -XM * SIN(TM1)

T = 2 * TM1 - TM2 + C1 * EM + C2 * EM1 + C3 * EM2

EM2 = EM1

EM1 = EM

TM2 - TM1

TM1 = T

ANDERSON, BALL, VOSS METHOD (ABV)

H = TIME BETWEEN SAMPLES

C1 = KH/2 + aKH^2

C2 = 5aKH^2/6

C3 = aKH^2/12 - KH/2

XM = ADC(01)

YM = ADC(01)

EM = YM * COS(TM1) - XM * SIN(TM1)

T = 2 * TM1 - TM2 + C1 * EM + C2 * EM1 + C3 * EM2

EM2 - EM1

EM1 - EM

TM2 =: TM1

TM1 = T

```

FIGURE 7

# MECHANIZATION OF THE Z-TRANSFORM METHOD

FIGURE 8

## MECHANIZATION OF EULER'S METHOD

FIGURE 9

$$\cos (\Theta + \Delta \Theta) = \cos \Delta \Theta \cos \Theta - \sin \Delta \Theta \sin \Theta$$

(42)

$$\sin (\Theta + \Delta \Theta) = \sin \Delta \Theta \cos \Theta + \cos \Delta \Theta \sin \Theta$$

(43)

If  $\Delta\Theta$  is small, this result can be simplified as shown in Equations (44) and (45).

$$\cos (\Theta + \Delta\Theta) = \cos \Theta - \Delta\Theta \sin \Theta$$

(44)

$$\sin (\Theta + \Delta\Theta) = \sin \Theta + \Delta\Theta \cos \Theta$$

(45)

Starting with an initial value for  $\sin\theta$  and  $\cos\theta$ , the above formulas can be used to recursively evaluate the sine and cosine if  $\Delta\theta$  is small. However, Larimore shows that this technique will become unstable unless a correction

factor is applied to the above calculation. He suggests that this correction factor make the sum of the squares of the sine and cosine equal to one as shown in Equations (46-51).

K = correction factor

$$K^{2} \left[\cos^{2} (\Theta + \Delta\Theta) + \sin^{2} (\Theta + \Delta\Theta)\right] = 1 \tag{46}$$

$$K = 1/\left[\cos^2(\Theta + \Delta\Theta) + \sin^2(\Theta + \Delta\Theta)\right]^{\frac{1}{2}}$$

(47)

let

$$E = \cos^2 (\Theta + \Delta\Theta) + \sin^2 (\Theta + \Delta\Theta) - 1$$

(48)

...

$$K = 1/\sqrt{1+E}$$

=  $(1+E)^{-\frac{1}{2}}$  (49)

$$K \approx 1 - \frac{1}{2} E \tag{51}$$

A Fortran program for continuously making the above calculation is given in Figure 10.

#### ROUTINE FOR CALCULATING SINE

CMI = PREVIOUS VALUE OF SINE

SMI = PREVIOUS VALUE OF COSINE

DTHE =  $\Delta\theta$

SM = PRESENT VALUE OF SINE

CM = PRESENT VALUE OF COSINE

CMP = CMI - DTHE \* SMI

SMP = SMI + DTHE \* CMI

DN = 1.5 - 0.5 \* (SMP \*\*2 + CMP \*\*2)

CM = DN \* CMP

SM = DN \* SMP

CMI = CM

SMI = SM

FIGURE 10

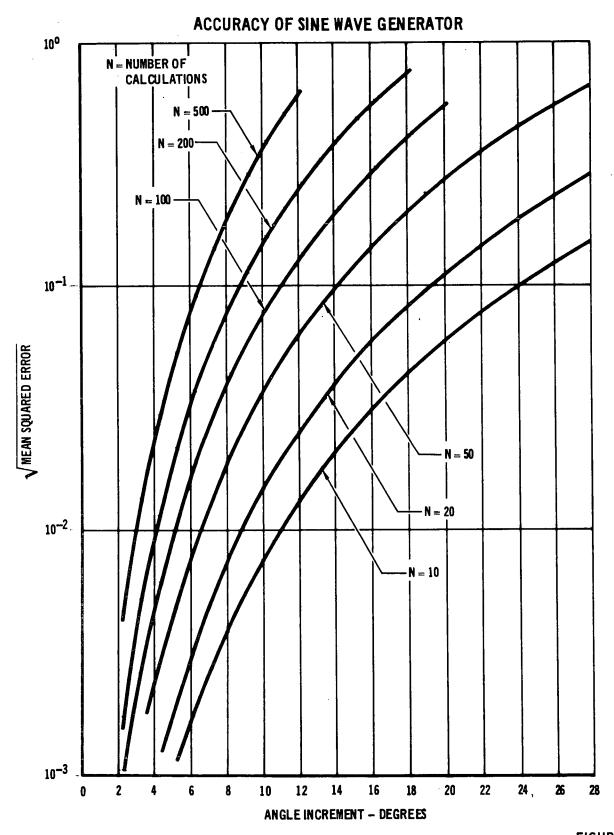

Utilizing the CDC 6400 computer, a timing calculation was made for both the above routine and the standard subroutine used in the 6400 for computing the sine and cosine. The results showed that the simple technique required 49  $\mu sec$  of central processor time per iteration, while the more complex method required 251 usec per iteration. Although the simple technique is 5 times faster, its accuracy degrades as a function of both the number of calculations and the increment size, as shown in Figure 11. If we sample at a rate ten times the maximum offset frequency, the average output phase change would be 36°. Therefore, from the results given in Figure 11, it would be necessary to update the sine and cosine generator after only a small number of iterations, thus making the usefulness of this technique questionable. One possible method of updating the calculation would be to store several values of the sine and cosine uniformly spaced between zero and ninety degrees, and then selecting the nearest angle after a fixed number of calculations. In order to implement this approach logic statements must be added to the program, which would result in an increased computation time. A transient will also occur in the phase-locked loop each time an update is made. A better solution to this problem might be to write a more efficient routine for generating the sine and cosine or to use a table look-up technique. A trade-off between accuracy and speed could then be made to determine the optimum approach. Designing an optimum sine and cosine generator for use in this phase-locked loop program represents a prime area for further study.

FIGURE 11

#### 2.3 Comparison of Techniques

In this section the five selected numerical techniques are compared on the basis of accuracy and speed for two linear second order filters and a phase-locked loop with various inputs. The second order filter and phase-locked loop were chosen because they represent a typical linear and non-linear subsystem component. The analog linear filter output can easily be calculated and thus the error of the discrete filter measured.

## 2.3.1 Non-Linear Phase-Locked Loop

As a first step in comparing the five numerical methods described in Sections 2.1 and 2.2, we determined the central processor time required for one iteration of each of the candidate techniques using the standard machine subroutine for sin and cos. These times, which apply to our CDC 6400 computer, are given below.

| Euler                | 240.3  | μsec |

|----------------------|--------|------|

| Tustin               | 273.7  | μsec |

| Anderson, Ball, Voss | 273.7  | μsec |

| Z-Transform          | 311.9  | μsec |

| Runge-Kutta          | 1334.0 | μsec |

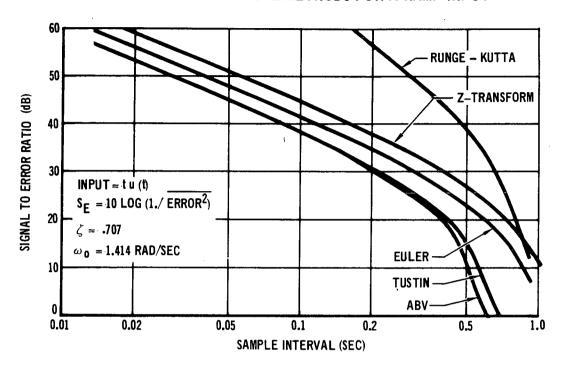

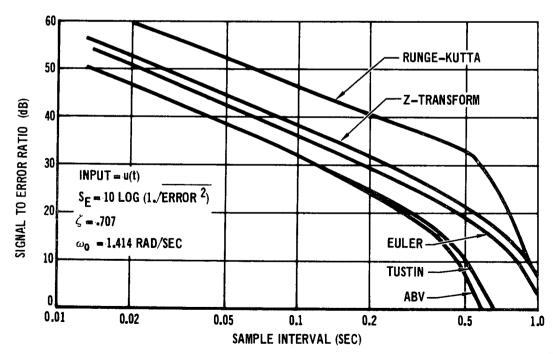

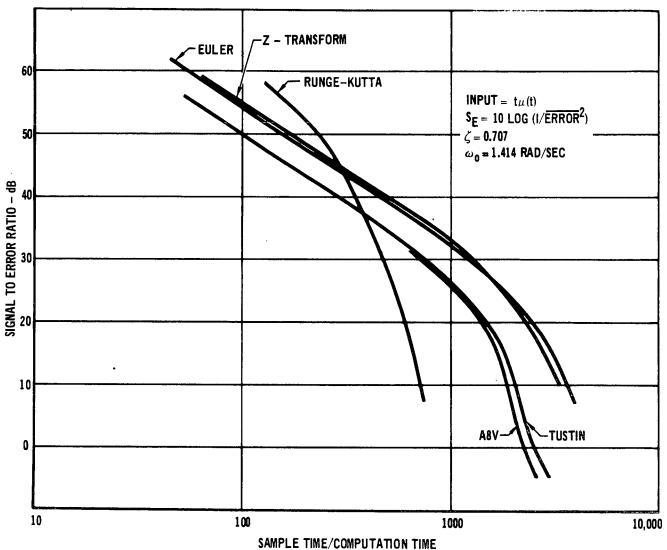

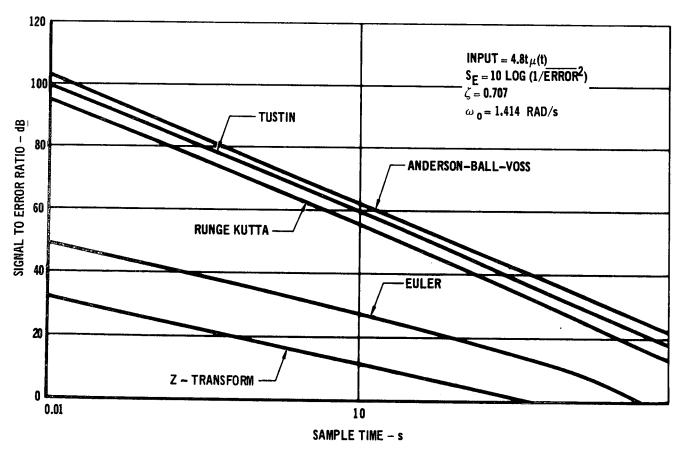

We also determined the mean-squared error between the output of a continuous loop and the digitized implementation for both ramp and step inputs. The ramp input signal was started at a sample point, while the step input was begun at a point halfway between the sample points. The results of this comparison are given in Figures 12 and 13. These curves indicate that Tustin's Method and the Anderson, Ball, Voss Method, two techniques which normally give high accuracy, show results considerably below the other candidate approaches. The reason is that a unit delay must be added in the feedback path because of the non-linearity associated with the phase-locked loop. In Section 2.3.2, the above techniques are compared for two linear filters, and the increased accuracy of Tustin's Method and the ABV Method is evident.

# COMPARISON OF NUMERICAL METHODS FOR A RAMP INPUT

1

FIGURE 12

# COMPARISON OF NUMERICAL METHODS FOR A STEP INPUT

FIGURE 13

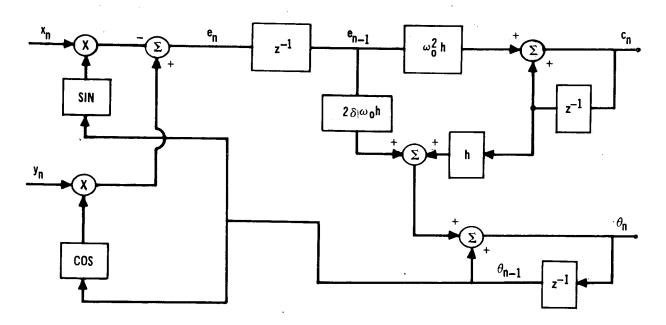

The complexity of the candidate techniques was assessed by drawing block diagrams, using the unit delay element, showing how the different methods can be implemented. Diagrams for Euler's Method and the Z-Transform Method were given previously in Figures 8 and 9. A block diagram showing the implementation of Tustin's Method and the ABV Method is given in Figure 14. One diagram suffices for these two techniques since they differ only by the value of the constants.

The numerical techniques described above were then compared using the preceding information on accuracy, complexity, and speed as the criteria of goodness. The Runge-Kutta Method was immediately discarded because of its complexity and slowness. Tustin's Method and the ABV Method were discarded because of low accuracy. This leaves the Z-Transform Method and Euler's Method, two techniques which give very similar performance as is evidenced by the preceding results. A more quantitative indication of this fact can be obtained by determining the central processor times (per .2 second interval) for a constant value of error. The Z-Transform technique with a sample time of 1/5 the loop time constant was chosen as a reference. This choice was made because 1/5 the loop time constant is a near optimum sample time for the phaselocked loop as will be shown in the next section, and also because this point is on the linear portion of Figure 12 and 13. The results are given below for both the step and ramp input. Note that for a fixed error the Z-Transform requires a slightly greater central processor usage than Euler's Method for a step input and slightly less usage for a ramp input.

#### Ramp Input

Z-Transform =  $311.9 \mu sec$

Euler =  $331.5 \mu sec$

Step Input

Z-Transform =  $311.9 \mu sec$

Euler =  $292.3 \mu sec$

$\theta$ e n-2 **MECHANIZATION OF THE ABV METHOD** e \_\_\_\_ AND TUSTIN'S METHOD 8

FIGURE 14

$\theta_n = 2\theta_n - \theta_{n-2} + A_1 \ e_n + A_2 \ e_{n-1} + A_3 \ e_{n-2}$

A more complete comparison of the numerical techniques is given in Figures 15 and 16 where the signal to error ratio is plotted versus the ratio of sample time to computation time. The above results indicate the near equality between the techniques in terms of speed and accuracy. Since Euler's Method is slightly easier to implement than the Z-Transform Method (the former technique requires three unit delay elements whereas the latter necessitates four), Euler's technique was selected and is used to determine the simulation results given in subsequent sections.

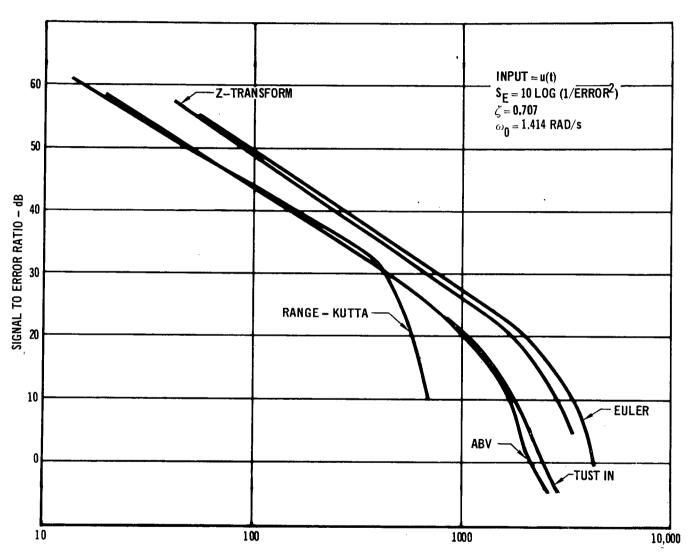

#### 2.3.2 Linear Filters

We also applied the five numerical techniques described above to the two second order filters given in Equations (52) and (53).

$$H_{2}(s) = \frac{2\zeta\omega_{0}s + \omega_{0}^{2}}{s^{2} + 2\zeta\omega_{0}s + \omega_{0}^{2}}$$

(52)

$$H_1(s) = \frac{{\omega_0}^2}{s^2 + 2\zeta\omega_0 s + {\omega_0}^2}$$

(53)

The difference equations for each of the numerical techniques is derived in Appendix II for  $H_1(S)$  and  $H_2(S)$ . Utilizing these formulas, the central processor time for the CDC 6400 computer was determined for each of the methods and is given below.

| Euler       | 35.0  | μsec |                      |

|-------------|-------|------|----------------------|

| Z-Transform | 50.9  | μsec |                      |

| Tustin      | 62.9  | μsec |                      |

| ABV         | 62.9  | μsec |                      |

| Runge Kutta | 214.5 | μsec | [H <sub>2</sub> (s)] |

|             | 274.1 | μsec | [H,(s)]              |

# COMPARING NUMERICAL METHODS FOR RAMP INPUT AS A FUNCTION OF COMPUTATION TIME

# COMPARING NUMERICAL METHODS FOR STEP INPUT AS A FUNCTION OF COMPUTATION TIME

SAMPLE TIME/COMPUTATION TIME

We also determined the mean-squared error between the output of the continuous filter and its digitized equivalent for ramp and step sine wave inputs, where the step occurred at a sample point. Since the filter is linear, the output of the continuous filter with the above inputs was calculated. Graphs showing the signal to error ratio versus sampling rate for the two filters are shown in Figures 17 and 18. Thus for a linear system Anderson, Ball, Voss Method is significantly better than Euler's Method due to greater accuracy. However, the non-linearity in the phase lock loop makes Anderson, Ball, Voss unappropriate for our application.

# COMPARISON OF NUMERICAL TECHNIQUES FOR LINEAR FILTER WITH RAMP INPUT

FIGURE 18

#### 2.4 Determination of System Constraints

The effect of sampling rate, quantization noise, and dynamic range on digital phase-locked loop performance is determined in this section.

#### 2.4.1 Sampling Rate

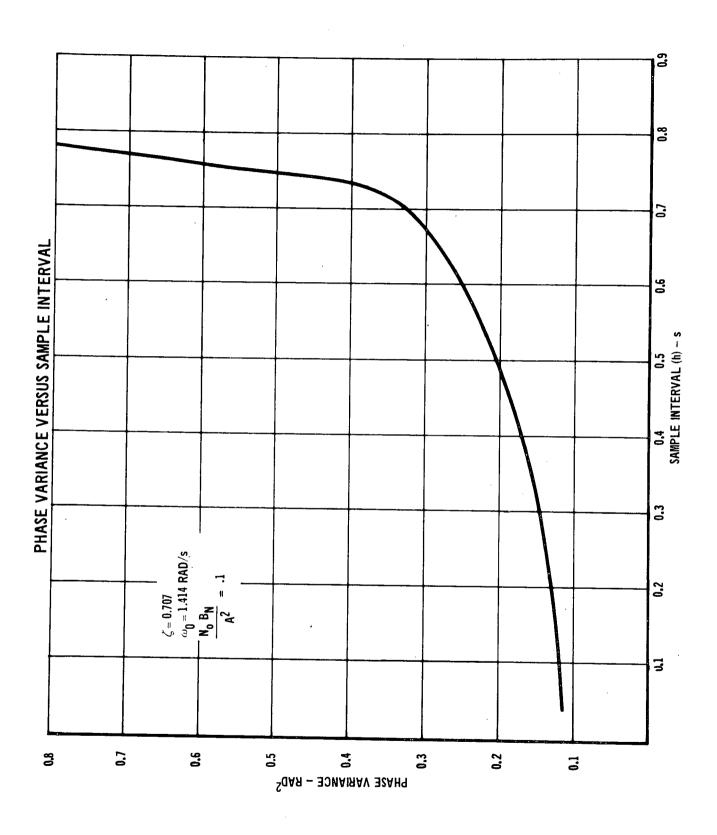

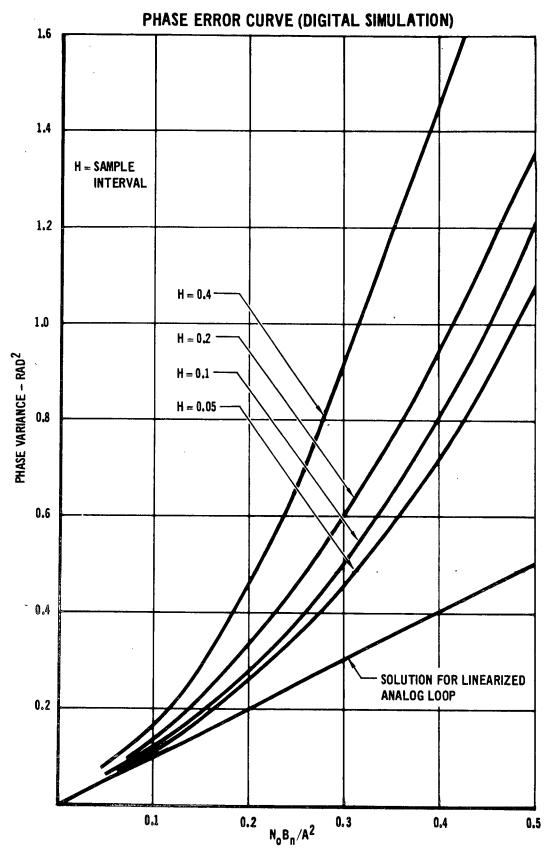

The necessary sampling rate depends on the numerical technique being used, the bandwidth of the phase-locked loop, and the offset frequency at the input to the loop. Since Euler's Method has already been selected as the numerical method, only the latter two effects will be considered here. The effect of sampling rate was determined by measuring phase variance versus sample interval for a fixed input noise spectral density using an all digital simulation. The input noise was generated using a Gaussian random number generator. It was assumed for all digital simulations in Section 2 of this study that the quadrature components were prefiltered with an integrate and dump filters. The resulting curve, Figure 19, shows that for the phase-locked loop being considered ( $\zeta = 0.707$  and  $\omega_0 = 1.414$  rad/sec) the sample interval must be less than 70% of the loop time constant to keep the loop from going unstable. We also determined a graph of phase variance versus  $\frac{(N B)}{\Delta^2}$ , the

loop signal-to-noise ratio, as a function of the sampling rate using an all digital simulation. This graph, which is shown in Figure 20, indicates that a serious degradation occurs for sample intervals between 20% and 40% of the loop time constant. Therefore, a sampling interval of 20% of the loop time constant represents a nearly optimum selection for the case of no offset frequency since this value is well below the point of instability and also allows the digital phase-locked loop to operate at a point where its transient performance approaches that of the continuous analog loop. We next determined the effect of an offset frequency on the sampling rate requirements. This was accomplished by computing the mean squared value of the difference between the continuous loop output and the

FIGURE 19

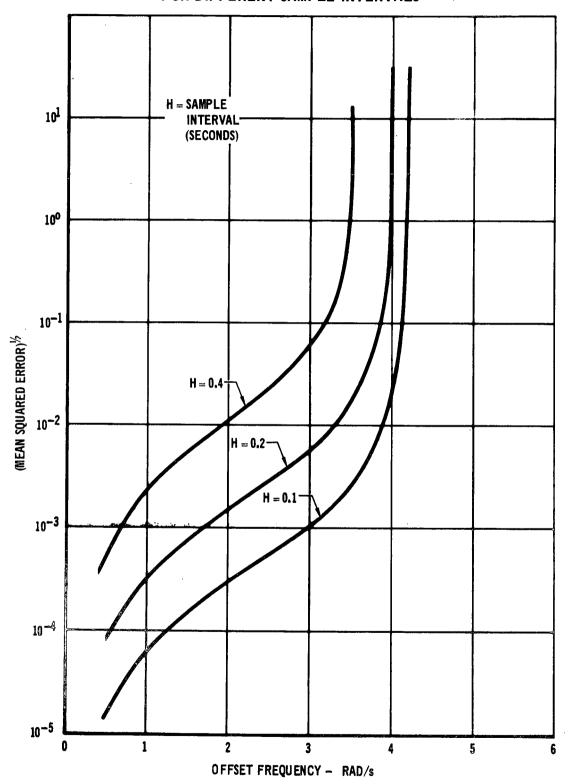

digitized loop for different frequency offsets. A graph showing the error versus the offset frequency for two different sampling rates is given in Figure 21.

This curve shows that decreasing the sampling interval from 20% to 10% of the loop time constant does not increase the accuracy significantly and also does not allow operation at a much higher offset frequency. Therefore, if the offset frequency is within the bandwidth of the loop, a sampling interval of 20% of the loop time constant gives adequate results. For frequency offsets much greater than the loop bandwidth, the sampling rate is dependent on both the input filter and the frequency of the offset. This dependency will be given more attention in the section on input filters.

#### 2.4.2 Quantization

In order to determine the effect of quantization on the operation of the phase-locked loop, we analytically determined the phase error variance as a function of the number of quantization levels. If the quantization error is assumed to be uniform, the noise variance caused by this error is given by the following formula.

$$\sigma_{Q}^{2} = \frac{a^{2}}{12}$$

(54)

$$\mathbf{a} = \frac{\mathbf{V}\mathbf{p}}{\mathbf{L}} \tag{55}$$

V<sub>p</sub> = peak voltage

L = number of positive quantization levels

If it is assumed that adjacent samples of the quantization noise are independent, the phase variance at the output of the linearized phase-locked loop can be determined as shown below. It is also assumed that the noise samples are held for one sample interval.

$$\sigma_{\phi}^{2} = \frac{\frac{N_{o}B_{n}}{A^{2}}}{(56)}$$

N<sub>o</sub> = Spectral density of quantization noise

$$N_o = 2 \sigma_Q^2 h$$

## MEAN SQUARED ERROR VERSUS OFFSET FREQUENCY FOR DIFFERENT SAMPLE INTERVALS

h = sample interval

A = amplitude of input sine wave

$B_n =$  noise bandwidth of PLL

$$q^{2} = \frac{V_{p}^{2} h B_{n}}{6 A^{2}L^{2}}$$

(57)

The phase variance was also determined using a digital simulation to check the analytical results. In order to get worst case results the offset frequency of the input sine wave was made small (.1 rad/sec). For low offset frequencies adjacent samples of quantization noise are no longer independent causing the loop to be less effective in filtering out quantization noise. A graph of phase variance versus the number of quantization levels for both the theoretical and the digital simulation results is shown in Figure 22. As the number of levels is increased, adjacent samples of quantization noise become more decorrelated and the two curves approach each other. The interaction between thermal noise and quantization noise was investigated using a digital simulation to determine the output phase variance as a function of the number of quantization levels for different values of the output signal-to-noise ratio  $(\frac{A^2}{2N B})$ . This graph, which is given in Figure 23, shows that the output phase variance is approximately independent of the number of quantization levels if the number of levels is greater than 16. Figure 23 shows that for 16 or more levels the standard deviation of the phase output is less than 1 degree for a wide range of signal-to-noise ratios. A phase error of this value in a PSK system would cause less than a 2  $\times$  10 $^{-3}$  dB reduction in the effective output signal-to-noise ratio.

#### 2.4.3 Scale Factor

Another important system constraint is the dynamic range of the A/D converter which precedes the digital computer. If the signal amplitude is greater than the dynamic range of the converter, signal energy will be lost resulting in a lower effective

## STANDARD DEVIATION OF PHASE: OUTPUT VERSUS THE NUMBER OF QUANTIZATION LEVELS

# PHASE ERROR VARIANCE VERSUS THE NUMBER OF QUANTIZATION LEVELS

input signal-to-noise ratio. If the dynamic range is made much greater than the signal amplitude, the quantization noise will be increased because of the increased size of the quantization interval. Therefore, the dynamic range of the converter should be set somewhere between the above extremes. We determined the output phase variance as a function of the number of quantization intervals for several different dynamic range settings. These results showed that the output phase variance was independent of the dynamic range if it was greater than  $(A = 3\sigma)$ , where A was the input sine wave amplitude, and  $\sigma$  is the input noise variance. A graph of the output phase variance versus the number of quantization levels as a function of the output signal-to-noise ratio and the dynamic range of the A/D converter is shown in Figure 24. This curve shows that the phase variance is reduced for a low number of quantization intervals as the dynamic range approaches the input singal amplitude. Our results indicate that a dynamic range of  $(A + 2\sigma)$  is a good compromise value.

# SCALE FACTOR DETERMINATION

#### 2.5 Automatic Gain Control (AGC)

Two AGC techniques were investigated. The first approach consisted of placing a bandpass limiter at the input to the phase-locked loop. We also investigated a slight variation of this method, using a sawtooth comparator in combination with the bandpass limiter. The second technique considered was to use a closed loop AGC preceding the phase-locked loop. Both of these techniques are analyzed in Sections 2.5.1 and 2.5.2, and computer implementations are determined.

#### 2.5.1 Bandpass Limiter

A block diagram of the phase-locked loop preceded by a bandpass limiter is given in Figure 25.

FIGURE 25

Assuming that the input signal is a narrow band process and that the higher harmonics will be removed by the bandpass filter following the limiter, the phase locked loop input will have the form given in Equation (58).

$$V = \sin \left(\omega_{o} t - \tan^{-1} \frac{Y}{X}\right) \tag{58}$$

The error signal at the input to the filter is given in Equations (59) and (60). It should be noted that the 1/2 factor resulting is omitted and considered part of the loop gain.

$$e = \sin \left( \tan^{-1} \frac{Y}{X} - \theta \right) \tag{59}$$

$$e = \frac{Y}{\sqrt{X^2 + Y^2}} \cos \theta - \frac{X}{\sqrt{X^2 + Y^2}} \sin \theta$$

(60)

The loop equation is then determined as shown in Equations (61) and (62).

$$\frac{\mathrm{d}}{\mathrm{d}t} \left( \frac{1}{K} \frac{\mathrm{d}\theta}{\mathrm{d}t} \right) = \left( \frac{\mathrm{d}}{\mathrm{d}t} + a \right) \mathrm{e} \tag{61}$$

$$\frac{d^2\theta}{dt^2} = aKe + K \frac{de}{dt}$$

(62)

To avoid taking the derivative of the input signal, the above equation can be written as two first order equations by making the substitution  $\frac{dc}{dt}$  = aKe.

$$\frac{dc}{dt} = aK \left[ \frac{Y}{\sqrt{X^2 + Y^2}} \cos \theta - \frac{X}{\sqrt{X^2 + Y^2}} \sin \theta \right]$$

(63)

$$\frac{d\theta}{dt} = c + K \frac{Y}{\sqrt{X^2 + Y^2}} \cos \theta - \frac{X}{\sqrt{X^2 + Y^2}} \sin \theta \tag{64}$$

Using Euler's Method, the difference equation for numerically solving the above equations will have the form given in Equations (65-67).

$$G = \frac{1}{\sqrt{X_{n-1}^2 + Y_{n-1}^2}} \left[ Y_{n-1} \cos \theta_{n-1} - X_{n-1} \sin \theta_{n-1} \right]$$

(65)

$$\theta_{n} = \theta_{n-1} + hC_{n-1} + KhG \tag{66}$$

$$C_n = C_{n-1} + aKhG \tag{67}$$

Using the Equations (65-67), a Fortran computer program was written for Euler's method and is given below.

H = h = sample interval

AK = Kh

AA = a

T = phase output of loop

$$XXA = ADC(01)$$

YYA = ADC(02)

XNOR = SQRT(XXA\*\*2 + YYA\*\*2)

XA = XXA/XNOR

YA = YYA/XNOR

TEMP = AK\*(YA\*COS(T) - XA\*SIN(T))

T = T + C\*H + TEMP

C = C + AA \* TEMP

A slight variation on the preceding technique consists of using a bandpass limiter preceding the phase-locked loop and a sawtooth comparator (inverse sine circuit) in front of the loop filter. The resulting block diagram is presented in Figure 26.

#### SAWTOOTH COMPARATOR

FIGURE 26

Using the same methods as were employed for the limiter, Equations (68) and (69) were derived.

$$\frac{dc}{dt} = aK \left( tan^{-1} \frac{Y}{X} - \theta \right)$$

(68)

$$\frac{d\theta}{dt} = c + K \left( \tan^{-1} \frac{Y}{X} - \theta \right) \tag{69}$$

A Fortran computer implementation of this technique is given below.

H = h = sample interval

AK = Kh

AA = a

T = phase output of loop

XXA = ADC(01)

YYA = ADC(01)

ANG2 = ATAN2 (YYA, XXA)

ANG2 = ASIN (SIN(ANG2-T))

TEMP = AK\*ANG2

T = T + C\*H + TEMP

C = C + AA\*TEMP

A curve showing the output phase variance as a function of the input noise spectral density for a phase-locked loop with, and without, a limiter is shown in Figure 27. This curve shows that as the input noise spectral density increases, the limiter reduces the gain of the loop, and as a result the output phase variance is reduced with respect to the loop with perfect AGC. A similar curve for the sawtooth comparator is shown in Figure 28. Since the sawtooth comparator exhibits more gain for large phase offsets than a loop with a sinusoidal comparator and a input limiter, the phase variance is greater for the sawtooth comparator configuration as low input signal-to-noise ratios. It should also be noted that the sawtooth comparator will track the input variations more effectively than the techniques described previously.

#### 2.5.2 Closed Loop AGC

A block diagram for an analog configuration of a closed loop AGC is given in Figure 29.

#### PHASE ERROR VARIANCE FOR SAWTOOTH COMPARATOR

#### **CLOSED LOOP ANALOG AGC**

FIGURE 29

The incremental transfer function for this loop will have the form given in Equations (70) and (71) according to Povejsil, Raven, and Waterman.

$$\frac{\Delta E_{\text{out}}}{\Delta E_{\text{in}}} = \frac{1}{1 + K_2 F(s)}$$

(70)

$$K_{2} = \frac{dE_{out}}{de_{g}}$$

$$E_{in} = constant$$

(71)

In order to keep the loop gain independent of the input level, an exponential gain characteristic was used. An integrator was chosen for the loop filter to reduce the steady-state offset between  $E_{\rm out}$  and  $V_{\rm ref}$  to zero. The resulting loop transfer characteristic is given in Equations (72-75).

$$\frac{\Delta E_{\text{out}}}{\Delta E_{\text{in}}} = \frac{s}{s + K_2} \tag{72}$$

$$E_{\text{out}} = G(e_g) E_{\text{in}}$$

(73)

$$G(e_g) = e^{Be} \tilde{s} \tag{74}$$

$$\frac{\partial E_{\text{out}}}{\partial E_{\text{eg}}} = \text{constant} = K_2 = E_{\text{in}} Be^{Be} g$$

(75)

A block diagram of the digital implementation of this circuit is shown below in Figure 30.

# IMPLEMENTATION DIAGRAM FOR AGC LOOP $X \longrightarrow X$ $Y \longrightarrow X$

FIGURE 30

A Fortran computer program for implementing the above technique is given below.

EIT = EITM + ERR\*H

EITM = EIT

H = h = sample interval

G = EXP (-GAIN\*EIT)

TEMP = AK\*(X\*COS(T) - Y\*SIN(T))

T = T + C\*H + TEMP

C = C + AA\*TEMP

#### 2.5.3 Comparison of Techniques

In order to show that the two AGC implementations given above performed properly, we tested each technique by jittering the amplitude of the input signal and measuring the variance in the gain of the phase-locked loop. For a 5% input amplitude variance the gain of the loop varied by 3.4%for the closed loop configuration and 1.1% for the limiter. This result would be expected since the limiter has an effective time constant which is infinitely small, while the closed loop configuration that was investigated had a time constant of 5 seconds. The operation of the AGC circuit was also demonstrated by showing the effect of the input signal to noise ratio on the tracking ability of a phase-locked loop preceded by one of the above AGC circuits. Utilizing a digital simulation, a sine wave phase input was applied to the loop, and the phase error variance was determined as a function of the input signal-to-noise ratio. A graph of these results is shown in Figure 31. For input signal-to-noise ratios above zero dB the output phase variance approaches the theoretical value for white noise passed through a linear loop. This indicates that the phase-locked loop is tracking the input sinusoidal phase variation with negligible error. As the input signal-to-noise ratio is reduced, the loop gain is reduced and the input phase variations can no longer be tracked. Figure 31 indicates that the threshold occurs at an input signal-to-noise ratio of -4 dB for the limiter and - 7 dB for the closed loop AGC with a 5 second time constant. Therefore, although the limiter

FIGURE 31

AGC reduces the gain variations by more than the closed loop configuration, it has a higher threshold than the latter method.

These results indicate that the limiter gives better regulation than the closed loop AGC, but it has a higher threshold. The previous Fortran computer programs showed that the limiter type AGC is faster and less complex than the closed loop approach. Since speed and complexity are important considerations in implementing a digitized receiver, the limiter AGC was chosen as the optimum method of obtaining automatic gain control.

#### 2.6 Acquisition

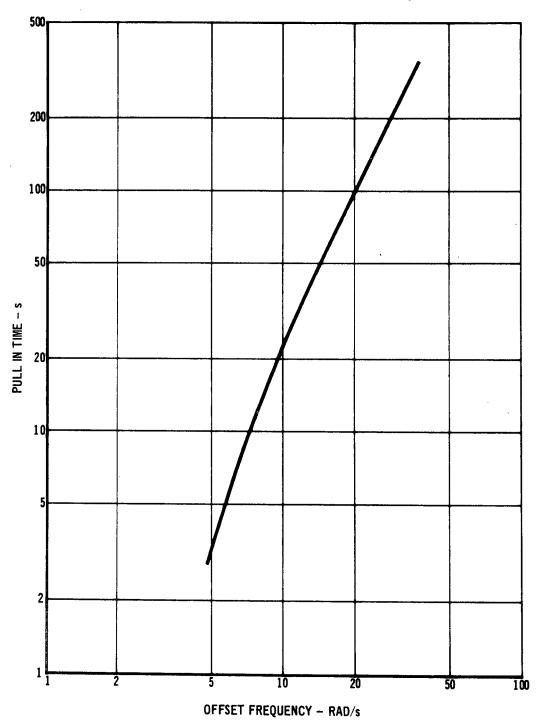

We analyzed and compared three approaches to phase-locked loop acquisition; the swept frequency method, the Fast Fourier Transform method, and the free-running mode. The first technique consists of beating the input signal with a swept frequency oscillator and passing the resultant signal through a low pass filter and a threshold detector. The second approach consists of computing the FFT of N input samples and then determining the Fourier coefficient of maximum amplitude. The final method allows the phase-locked loop to pull-in with no external controls.

#### 2.6.1 Swept Frequency Method

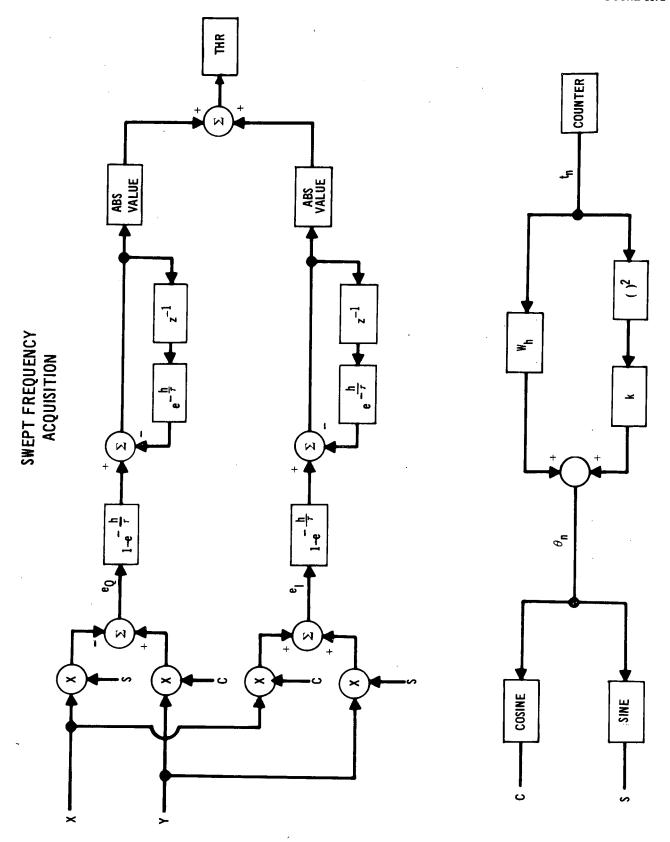

The first technique, which was studied by Sterling<sup>4</sup>, consists of beating the input signal with two oscillators that are 90° out of phase, filtering the resultant signal, and performing a threshold detection to determine when the swept frequency equals the input frequency. The two out-of-phase oscillators are necessary since the phase of the input signal is not known and thus a zero output could result if only one oscillator was used. A block diagram of this configuration is shown in Figure 32. The input multiplications shown in this figure are derived in Equations (76-81).

$$E_{i} = X \sin \omega_{i} t + Y \cos \omega_{i} t$$

(76)

$$E_{VCO} = \cos \left(\omega_{O} t + \theta\right) \tag{77}$$

$$\theta = \omega_0 t - kt^2 \tag{78}$$

$$k = \frac{\mathbf{w}h}{\mathbf{T}} \tag{79}$$

T = sweep time

$$e_{g} = E_{i}E_{yCO} = -X \sin \theta + Y \cos \theta \tag{80}$$

$$e_{\vec{1}} = E_{i}E_{vco} = X \cos \theta + Y \sin \theta$$

(81)

FIGURE 32

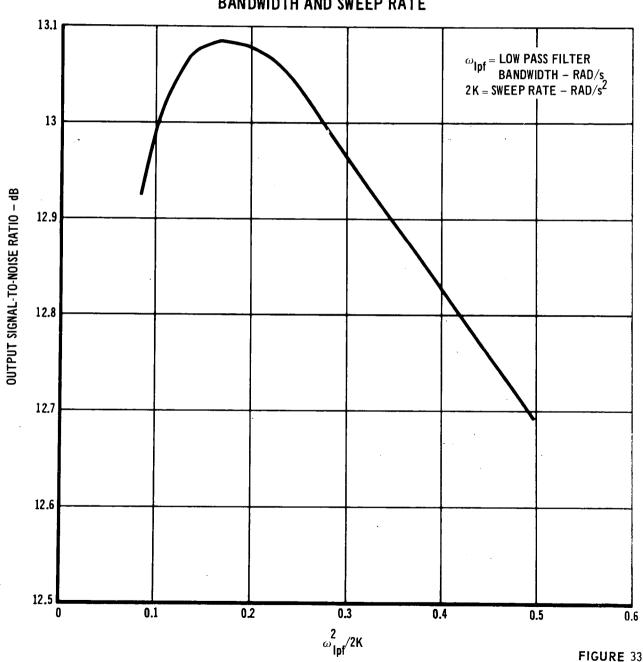

Each of the quadrature components is passed through a low pass filter and an absolute value circuit. The resultant sum signal is applied to a threshold detector. The frequency of the sweep at the time the threshold is crossed is used as the initial condition on the frequency of the phaselocked loop. If this frequency is within the pull-in range of the phaselocked loop, the loop will almost instantaneously acquire the signal. The time constant of the low pass filter was chosen to maximize the ratio between the peak signal at the input to the threshold detector and the standard deviation of the noise at the output of the low pass filter. The measurement of peak signal to rms noise at the filter output is only an approximation of the actual signal-to-noise ratio since the noise should be taken at the input to the threshold detector. However, the absolute value ctrcuit makes this difficult, and thus the approximate measurement was made. A graph of the signal-to-noise ratio versus the ratio of the low pass filter bandwidth squared to the sweep rate is shown in Figure 33. This graph shows that the signal-to-noise ratio is maximized for  $(\omega_{1,p}^{\,2}/2K)$  equal to 0.1715. However, this ratio can be varied between 0.1 and 0.275 with a resulting loss in signal-to-noise ratio of less than 0.1 dB. A computer program for the above acquisition circuitry with the phase-locked loop included is shown in Figure 34. When the variable E is greater than the threshold, the variable C is set equal to the swept frequency at that time, and the phase-locked loop calculations are begun at statement 2.

## 2.6.2 Fast Fourier Transform Acquisition

A second method for performing phase-locked loop acquisition is to utilize the Fast Fourier Transform (FFT). This technique consists of reading N samples into the computer and calculating the Discrete Fourier

Transform (DFT) which is given in Equation (82).

$$A_{r} = \sum_{k=0}^{N-1} X_{k} \exp(-2\pi j r k/N)$$

$$r = 0, 1, ---, N-1$$

(82)

$X_k = input samples$

### DETERMINING RELATIONSHIP BETWEEN LPF BANDWIDTH AND SWEEP RATE

#### **COMPUTER PROGRAM FOR ACQUISITION**

```

= SWEEP START FREQUENCY AND ONE HALF OF SWEEP RANGE

RK = TWICE THE SWEEP RATE

= TIME INTERVAL

AK = LOOP GAIN

= FILTER CONSTANT

THR = ACQUISITION THRESHOLD

CON = e^{-\omega} lof^{-h}

TTT = SWEEP TIME

3

IF (E. LT. THR) GO TO 1

= WH - 2. * RK * TT

GO TO 2

1

= ADC(01)

= ADC(02)

THET = WH*TT - RK*(TT**2)

CS = COS (THET)

SS

= SIN (THET)

XX = X*CS + Y*SS

YY = \neg X*SS+Y*CS

EX = XX + (EIX - XX) * CON

EIX = EX

EY = YY + (EIY - YY) * CON

EIY = EY

= ABS (EX) + ABS (EY)

TT = TT + H

IF (TT \cdot GT \cdot TTT) TT = 0

GO TO 3

2

= ADC(01)

= ADC(02)

TEMP = AK * (Y*COS(T) - X*SIN(T))i

= T + C* H + TEMP

= C + AA * TEMP

GO TO 2

```

FIGURE 34

The FFT algorithm removes redundant operations from the calculations and reduces the number of operations from  $N^2$  to  $2N \log_2 N$ . For large values of N this is an extremely significant reduction. The listing of a digital computer program for implementing the FFT algorithm is given in Figure 35.

# DIGITAL COMPUTER PROGRAM FOR FFT GENERATION

```

C

COMPLEX W, X, Y

C

N = NUMBER OF SAMPLES

C

N = 2**L

C

X(J) = INPUT DATA

PI = 3.141592653589793

BBN = N

AR = 2.* PI/BBN

MM = 0

K = 1

NA = N/2

KK = NA

D0 2 J = 1. L

IF (MM. EQ.1) GO TO 9

MM = 1

D0 1 I = 1, K

IM = (I - 1) * KK

AA = IM*AR

W = CMPLX (COS (AA), - SIN (AA))

D01II = 1, KK

NZ = 11 + 1M

NQ = NZ + IM

Y (NZ) = X (NQ) + W^* X (NQ + KK)

Y (NZ + NA) = X (NQ) - W* X (NQ + KK)

1

CONTINUE

GO TO 12

9

MM = 0

D0\ 10\ I = 1, K

IM = (I - 1) * KK

AA = iM*AR

W = CMPLX (COS (AA), - SIN (AA))

D0\ 10\ II = 1,KK

NZ = II + IM

NQ = NZ + IM

X (NZ) = Y (NQ) + W*Y (NQ + KK)

X (NZ + NA) = Y (NQ) - W*Y (NQ + KK)

10

CONTINUE

12

KK = KK/2

K = 2*K

2

CONTINUE

С

X(J) = OUTPUT DATA IF L IS EVEN

C

Y(J) = OUTPUT DATA IF L IS ODD

```

FIGURE 35

The program, which was written in Fortran IV, determines the FFT of a sequence of N complex input samples X(K). This program uses complex input samples which

is of great advantage since the Fourier Transform of the IF signal (X cos  $\omega_0$ t + Y sin  $\omega_0$ t) can be obtained by frequency shifting the transform of (X + jY) as is shown in Equations (83) and (84).

$$F(X + 1Y) = F(\omega)$$

(83)

$$F (X \cos \omega_{o}t + Y \sin \omega_{o}t) = \frac{1}{2} F^{*}(\omega - \omega_{o})$$

$$+ \frac{1}{2} F (\omega + \omega_{o})$$

$$(84)$$

The sampling rate must be greater than twice the maximum frequency of the sampled signal. The total number of samples determines the separation between the discrete spectral components. The program shown in Figure 35 has been written such that N must be an integral power of two  $(N=2^L)$ . This constraint is not usually restrictive in using this program for acquisition since the number of samples can usually be increased such that N becomes an integral power of two. The preceding program stores the DFT of the input signal in either the X or Y matrix depending on whether L is even or odd. The relationship between the coefficients  $A_r$  and the elements of the output matrix (assumed to be X for this example) is given below.

$$A_{r} = X(r + 1)$$

If the function (X + jY) is transformed, where X and Y are the quadrature components of the input signal, the complex value of the various spectral components are found in the storage locations given in Equation (85).

$$f_1 = \frac{1}{Nh} \tag{85}$$

h = sample interval

N = number of samples

$$X(1) \longrightarrow f_0 - f_1$$

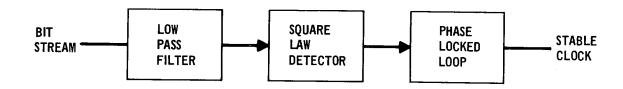

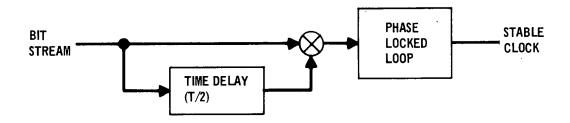

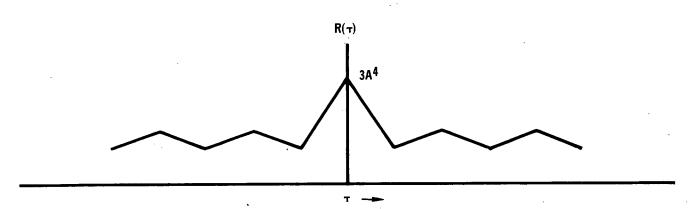

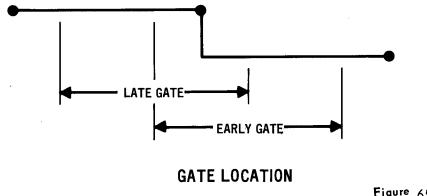

$$X(2) \longrightarrow f_0 + f_1$$