# Politecnico di Torino

# Porto Institutional Repository

[Article] Overview of Signal Integrity and EMC Design Technologies on PCB: Fundamentals and Latest Progress

Original Citation:

Wu, Tzong-Lin; Buesink, Frits; Canavero, Flavio (2013). *Overview of Signal Integrity and EMC Design Technologies on PCB: Fundamentals and Latest Progress.* In: IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY, vol. 55 n. 4, pp. 624-638. - ISSN 0018-9375

Availability:

This version is available at : http://porto.polito.it/2647377/ since: September 2016

Publisher: IEEE

Published version: DOI:10.1109/TEMC.2013.2257796

Terms of use:

This article is made available under terms and conditions applicable to Open Access Policy Article ("Public - All rights reserved"), as described at <a href="http://porto.polito.it/terms\_and\_conditions.html">http://porto.polito.it/terms\_and\_conditions.html</a>

Porto, the institutional repository of the Politecnico di Torino, is provided by the University Library and the IT-Services. The aim is to enable open access to all the world. Please share with us how this access benefits you. Your story matters.

(Article begins on next page)

# Overview of Signal Integrity and EMC Design Technologies on PCB: Fundamentals and Latest Progress

Tzong-Lin Wu, Frits Buesink, and Flavio Canavero

*Abstract*—This paper reviews the fundamentals and latest progress of modeling, analysis, and design technologies for signal integrity and electromagnetic compatibility on PCB and package in the past decades. Most results in this field are based on the very rich and highly educational literature produced by Prof. C. Paul in his long scientific career. The inclusion of parameters variability effects is also considered, and it is demonstrated how statistical simulations can become affordable by means of recently-introduced stochastic methods. Finally, the necessity of practical training of designers is mentioned, and an experience relying on realistic PCB demonstrators is illustrated.

*Index Terms*—Circuit demonstrator, crosstalk, differential signaling, eye diagram, macromodeling, mode conversion, paramter variability, PCB, polynomial chaos, practical training, signal integrity, TDR, trace discontinuity.

### I. INTRODUCTION

**E** LECTROMAGNETIC compatibility (EMC) and signal integrity (SI) are one of the crucial technologies in the future for the electronic product design. The main reasons are high data bandwidth demand for next generation high performance computing (100+ Gbps), cloud communication/computing (50+ Gbps), and client devices (20+ Gbps). EMC and SI technologies on PCB or package will be one of the bottlenecks to achieve such high data bandwidth.

Paul made several pioneering contributions to the field of EMC and SI. He condensed the fundamental theory and required knowledge for EMC and SI design in two masterpiece books [1], [2]; then, in more recent times, he published a series of three books [3]–[5], especially for the design of high-speed digital systems. These references not only guided the direction of EMC and SI research on PCB in past decades and inspired several novel technologies, but are still presently unsurpassed

F. Buesink is with the Faculty of Telecommunication Engineering, University of Twente, Enschede 7522 NH, The Netherlands (e-mail: frits.buesink@utwente.nl).

F. Canavero is with the Dipartimento di Elettronica e Telecomunicazioni, Politecnico di Torino, Torino 10129, Italy (e-mail: flavio.canavero@polito.it).

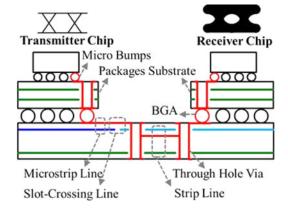

Fig. 1. An example of a link path which starts at a transmitter chip and ends at a receiver chip.

and will impact the development of electronics and systems for many years to come.

In this paper, the fundamentals and latest progress of EMC and SI design technologies on PCB are overviewed. In addition, methods and tools for the simulation of a circuit, with the inclusion of parameters' variability effects on its electrical behavior, are needed to avoid very expensive refabrication. Finally, EMC engineering education is a fundamental step to achieve welldesigned and performing devices. "Seeing is believing" particularly applies to the design for EMC, where most effects are felt as "black magic" and teaching using only texts and equations is insufficient. The IEEE EMC education manual [6] proved to be an indispensible tool for teaching practical skills and Paul was a great inspirator for the EMC community also in this respect.

This paper is organized as follows. The link path modeling, analysis, and design technologies are reviewed in Section II, differential signaling design and common-mode noise issues are presented in Section III, discontinuities due to nonideal return paths are treated in Section IV, assessment of parameters variations are discussed in Section V, and an educational experience for PCB design is reported in Section VI.

## II. LINK-PATH MODELING AND ANALYSIS

A link path includes a whole electrical interconnect starting from a chip sending a signal and terminating at a chip receiving the signal. The signal integrity could be kept perfect if the link path could behave as a lossless transmission line. In reality, the link path usually consists of several conductive wires in different geometries. Fig. 1 shows an example of a link path. It starts

T.-L. Wu is with the Department of Electrical Engineering and Graduate Institute of Communication Engineering, National Taiwan University, Taipei 10617, Taiwan (e-mail: wtl@cc.ee.ntu.edu.tw).

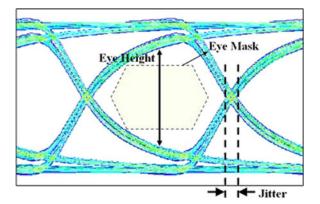

Fig. 2. An example of an eye diagram with the indication of eye height, jitter, and eye mask.

at a transmitter chip, passes through micro bumps, packages substrate, BGA balls, vias, microstrip lines or strip lines on PCB, and ends at a receiver chip. The signals will be distorted both in amplitude and timing due to the nonideal effects of the link path, such as frequency-dependent loss of package and PCB substrate, impedance variance, crosstalk coupling, etc.

An eye diagram is a common way for evaluating the quality of signals propagating on a link path. It is constructed by slicing a long stream of pseudorandom bit sequences (PRBS) and superimposing the different segments of symbols with one or two bits in length. Fig. 2 shows an example of a received eye diagram. Two metrics, eye height and timing jitter, are used to characterize quantitatively the voltage and timing errors, respectively, as shown in Fig. 2. In order to ensure the received signal can be recovered successfully, the jitter must be small enough to provide the receiver a sufficient sampling duration. Also, the eye height must be sufficiently large to ensure the voltage levels meet the threshold region. For some applications, an eye mask representing a forbidden region is defined as a signal quality specification, as shown in Fig. 2. The signal quality will not pass if the eye diagram overlay the mask.

Accurate modeling and characterization of the link path is important for eye diagram behavior prediction. The two books Paul edited at the end of his career [4], [5] provide an excellent summary of the significant developments. He contributed on the fundamental principles of circuit theory and electromagnetics needed to build physically consistent models. Intuitively, the link path can be described by multiport scatteringparameters (S-parameters) or impedance/admittance parameters in frequency domain, which can be obtained from either measurements or full-wave EM simulations [7]. It is sometimes very time-consuming to produce the S-parameters of the overall chip-package-PCB link path by full-wave simulation. Typically, the cascaded S-parameters are employed to take the overall link path into account [8]. However, for transient analysis in digital circuits, some signal processing techniques, such as inverse fast Fourier transform (IFFT) of the link-path S-parameters and a convolution algorithm, are required as an additional approach.

The concept of macromodeling for the partial or full link path has been thus developed to solve such mixed frequency/time domain problems [9]–[16]. The SPICE-compatible macromodels generally produce the same frequency response as the full-wave results in the frequency band of interest, but have no direct relations with the physical structure. The macromodel extraction techniques are based on the rational function approximation for the tabulated S-parameters, that can be implemented in various forms, from the basic vector-fitting [10] to more sophisticated algorithms like Z-domain-based orthonormal vector fitting [16]. However, several intrinsic properties of the original link path may not be preserved by the approximated macromodel, such as stability, causality, or passivity [17]. It has been shown that the overall signal integrity simulation will fail when these fundamental properties are lost because of measurement or simulation errors. Two suggestions are given to avoid the problem. First one is certifying any raw dataset to be self-consistent, causal, and passive before proceeding to further modeling steps. Second, any macromodeling algorithm also has to preserve the properties. On the other hand, it has been shown that passivity is the strongest requirement implying both causality and stability. Approaches for passivity enforcement techniques of macromodeling have also been proposed based on linear or quadratic optimization [18]-[20] or Hamiltonian matrix perturbation [21], [22]. Besides that, a systematic approach has also been proposed for systematically synthesizing the macromodel of interconnects according to the time-domain reflected waveform either measured by time-domain reflectometry (TDR) or simulated by the finite-difference-time-domain method [23]-[26].

As mentioned previously, the worst case eye diagram has to be produced by PRBS input with every possible bit sequence. It is typically time consuming. Another challenging topic for signal integrity modeling on link path regards efficient methodologies to predict the eye diagram properties, such as jitter and eye height [27]–[33]. One of the major reasons for the degradation of the eye diagram is due to the frequency-dependent loss leading to the data-dependent jitter, or so-called intersymbol interference (ISI) [34]. The effect can be caught by the peak distortion analysis [27]. Using the unit pulse or step response of the link path, we can predict the worst case eye height and deterministic jitter. Such approach can be extended for the matched lossy line [28], multireflected line [29]–[31], and lines with crosstalk [32].

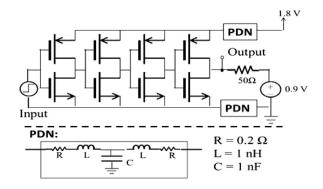

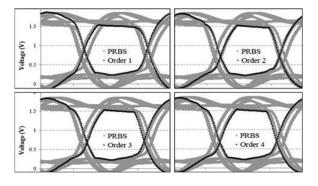

Most of those methods are developed based on the linear system assumption for the link path ignoring the nonlinear effect of the driver circuits inside the chip. Latest studies proposed a fast method that could predict the eye diagram considering the interaction between the nonlinear I/O circuits and power distribution network (PDN) noise [33]. Based on the superposition of multiple bit pattern responses (SMBP) concept, an algorithm is developed to fast predict the eye diagram that theoretically captures any nonlinearity in the circuit. As shown in Fig. 3, a test circuit with PDN was constructed to examine the performance of this algorithm. The experiment results, as shown in Fig. 4, indicate a good agreement with the results simulated by long PRBS in HSPICE, for SMBP order higher than two [33].

Passive equalization is still an important topic in SI design of PCB, especially for Gbps signal transmission. Most of the passive equalization techniques are based on a high-pass filter design, such as T-junction [35]–[37], series RL [38], [39], parallel

Fig. 3. A test circuit consists of four CMOS inverters as an output driver and two T-model RLC power distribution networks [33].

Fig. 4. Four Comparison of eye diagrams between 1000-bit PRBS result (gray line) and SMBP estimations of different orders (black lines). Top left: order 1. Top right: order 2. Bottom left: order 3. Bottom right: order 4 [33].

RC structures [38], implemented by the lumped RLC elements. Coupled traces [40] or defected ground concept [41], [42] on the PCB were recently proposed to replace the *L* element with a lower cost. Several algorithms to accurately find the *RLC* values were also discussed in [38], [43].

Crosstalk is another critical issue that could degrade the SI (or eye diagram) performance. Theoretical deviations and discussions for the crosstalk mechanism through the magnetic or electrical coupling have been well investigated [1], [2], [44]–[46]. Several researchers have discussed the methods to reduce the crosstalk, such as spiral layout scheme [47], serpentine microstrip line method [48], or using guard trace [49]–[51].

### **III. DIFFERENTIAL SIGNALING**

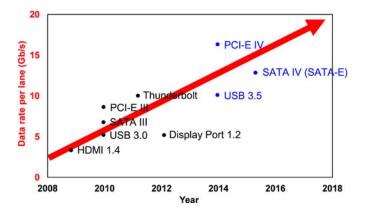

The differential signaling scheme has become required in high-speed digital systems due to its high immunity to noise and high tolerance to link path discontinuities [52], [53]. Fig. 5 shows the data rate trend for differential signals on PCB or cables, such as serial advanced technology attachment (SATA), peripheral component interconnect express (PCI-e), universal serial bus (USB), etc. The projection is far beyond 20 Gbps in the next decade. Typically, a differential (or balanced) line is composed of three conductors (two signal conductors and one ground conductor) that support two fundamental modes, differential (or odd) mode and common (or even) mode [2]. In differential signaling systems, the common-mode signal is usually regarded as the noise, which will degrade the signal integrity

Fig. 5. Summary of latest high-speed I/O interfaces and their evolution. (Specifications with black words are the known information; those with blue words are the anticipation.)

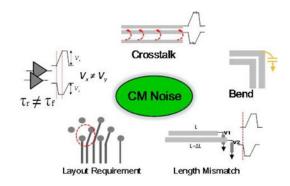

Fig. 6. Root-cause of common-mode noise from a variety of asymmetric geometries in real-world designs.

or cause EMI problems. Asymmetry in the differential link path is the main reason for exciting the common mode noise. The asymmetry includes the rising/falling time mismatch or amplitude difference in the I/O driver circuit, trace length mismatch between two signal conductors, unavoidable imbalance routing such as bending or via transition, etc. [54], as illustrated in Fig. 6.

With the trend of increasing data rates above several GHz, the discontinuity effect of the differential vias cannot be ignored. Numerical modeling or full-wave simulation based on PEEC [55]–[57], MoM [58], [59], cylindrical wave expansion method [60], etc., is one of the high accuracy ways to understand or predict the electrical behavior of the differential via, though it is time-consuming. Another way is developing equivalent circuit models, which can be linked directly with SPICE or other similar circuit simulators. The equivalent model can be constructed by space-mapping neural network [61], macromodels through time-domain [25], frequency-domain responses [62], [63], or physical models that are related to the via geometry [64]–[66]. In addition, the effective characteristic impedance of differential via transition can also be defined and designed with the help of an equivalent circuit model [67].

Another interesting research direction is on the design of the differential serpentine delay line, which is a common layout technique to equalize the timing delay among different pairs of differential signals. The common-mode noise usually is excited

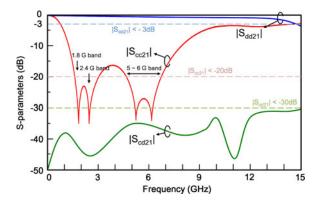

Fig. 7. Typical behavior of a common-mode filter in terms of S-parameters.

TABLE I CHALLENGING CMF SPECIFICATIONS FOR NEXT GENERATION HIGH-SPEED INTERFACES

| Parameters                                    | Specifications              |

|-----------------------------------------------|-----------------------------|

| Differential mode,   S <sub>dd21</sub>        | < -3 dB below 15 GHz        |

| Common mode,   S <sub>cc21</sub>              | < -20 dB for specific bands |

| Mode conversion, $ S_{cd21} $                 | < -30 dB below 15 GHz       |

| Group delay of differential mode, $\tau_{dd}$ | Variation less than 10 %    |

in the serpentine delay lines due to a plurality of bends, which is one of the imbalance factors to cause the mode conversion. A flat spiral routing scheme was proposed to improve the signal integrity [68]. The common-mode noise could be mitigated by the compensation capacitance, or inductance on the bending corner [69], [70], tightly coupled and tapered lines at partial segment [71], [72]. The phase delay performance of the serpentine differential line can be improved by the shielded structure [73].

On the other hand, connectors and cables are always required for the high-speed interface or peripherals to deliver the signals between devices. Due to the inevitable asymmetry structure, common-mode current on the ground structure combining the PCB, connector, and cables will be excited and result in common-mode radiation [1], [74]-[78]. As the signaling raises up to several GHz, the spectrum of the radiation could cover the wireless communication bands, such 2.4 GHz and 5 GHz of WLAN and 1.5 GHz for GPS. This common-mode radiation, which is commonly called radio-frequency interference (RFI), will degrade signal-to-noise ratio (SNR) or the sensitivity of the transceivers [79]. Suppressing the common-mode noise before entering the connectors by using the common-mode choke (CMC) [80] or common-mode filter (CMF) [81]-[88] is one of the effective ways to solve such an RFI issue. Fig. 7 shows the typical behavior in terms of S-parameters for CMC or CMF. They include the insertion loss for differential mode  $(|S_{dd21}|)$ , stopband for common-mode  $(|S_{cc21}|)$ , mode conversion  $(|S_{cd21}|)$ , and the group delay of differential mode  $(\tau_{dd})$ . For next generation high-speed interfaces, the challenging specifications, as shown in Table I, are  $|S_{dd21}| < -3$  dB from DC to 15 GHz,  $|S_{cc21}| < -20$  dB for the specific bands,  $|S_{cd21}| < -30$  dB, and  $\tau_{dd}$  variation is less than 10%. Based on wire winding around ferrite material, CMC is a popular component for the common-mode noise suppression, but the challenge and cost significantly increases for such devices.

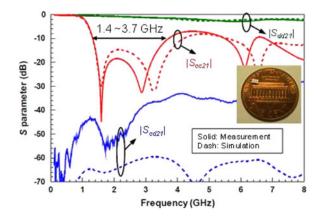

Fig. 8. Compact (much smaller than a 1-cent coin) common-mode filter design based on LTCC substrate, and its performance [88].

Recently, several works were devoted to CMF development based on defect ground structure [81], [82], split ring resonator [83], and metamaterials with negative permittivity [84]. Also, coplanar electromagnetic bandgap structure [85] was proposed to suppress the common-mode noise. These concepts have been demonstrated effective in common-mode noise mitigation without degrading the differential signal quality either on PCB level [86] or component level [87], [88]. Fig. 8 shows a compactsize CMF design based on LTCC substrate, and its S-parameter performance [88].

## IV. DISCONTINUITIES

Discontinuities are always inevitable in a practical link path. They lead to discontinuous impedance, result in reflection loss, crosstalk coupling, high-order mode conversion, and dramatic radiated emission, and thus cause significant signal integrity issues. Besides the aforementioned macromodeling method in Section II, analytical or numerical modeling and design techniques for some specific structures have been proposed and will be introduced here. It is worth mentioning a scholar contribution of Paul on loop and partial inductance, summarized in his recent book [3].

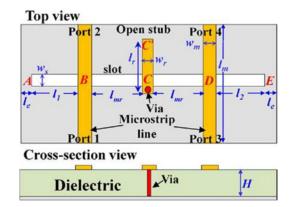

One of the common discontinuities in link path is the nonideal return path for slot-crossing signal line. A heterogeneous integration system requires different dc power supplies. One of the layers in PCBs or packages is usually split to accommodate separate power supplies, for example 5, 3.3, 2.5, or 1.8 V. Splitting of planes also happens when the ground and power planes are located on the same layer. On the other hand, EMC engineers sometimes make use of slot structures to supply inductive impedance on the reference ground and avoid the noise coupling from the noisy digital to the sensitive analog circuits via reference ground. These slits result in incomplete reference planes and nonideal return current paths and cause severe signal degradation and radiated emission. Etching slots on the power/ground planes have been verified to be an effective and low-cost solution to these problems [89]-[92]. All the aforementioned reasons demonstrate that the existence of slot structure is now unavoidable in most system designs. Several EMC issues, including SI [54] and EMI problems [93], arise due to the slot-crossing traces and need to be investigated. For SI issues, the slotted reference plane results in substantial parasitic effects, which degrade the signal transmission especially for high-frequency components. Meanwhile, the electromagnetic coupling between slot-crossing signal lines is significant in the crossed slotline structure [54]. Moreover, once the frequency of the coupled noise meets the resonant frequency of the slotline, considerable EM radiation will be generated due to the excitation of the antenna-like slotline. This will lead to serious EMI problems and may fail EMC compliance test.

For accurately modeling the EM characteristic of slotline structures, the approximate analysis, transverse method, Galerkin method, and even full-wave numerical simulation have been employed [94]–[96]. Besides, the investigations of slotline discontinuities including the slot-to-microstrip transition, short/open-end effect have both been widely discussed [97]–[99]. Based on the electrical behavior of the slotline, the transmission-line model [100], [101] demonstrates the SI issues induced by signal traces crossing a common slotline. Through the constructed model, the signal distortion and coupled crosstalk can be both quantitatively determined.

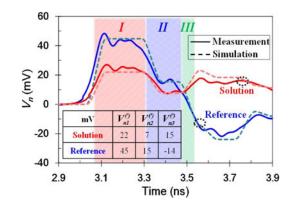

Besides using differential signaling, for the case of a singleended line crossing a gapped reference plane, shorting bridges [102], and stitching capacitors [90] are the most common solutions for providing additional reference paths, which can further be extended to the cases of common-mode noise carried by differential lines. Although placing a shorting bridge underneath the signal lines to connect the split planes is the most intuitive method [102], the use of shorting bridges is not appropriate for two power planes with different voltage levels. In addition, the shorting bridges greatly degrade the isolated efficiency of a slotline at low-frequency [92], which obviously violates the initial purpose of slotted reference planes. Replacing the shorting bridges with decoupling capacitors is now the most predominant technique in industry [90]. This solution can actually avoid those problems induced by shorting bridges and provide return current paths at high frequency. However, its equivalent series inductance significantly dominates the impedance behavior of the decoupling capacitor, which limits its effectiveness to only below the GHz range. In [103], a circuit model has been recently proposed to explain the crosstalk behavior of the signal lines crossing the slotline. A novel solution by using branched reflector, as shown in Fig. 9, shows good capability for reducing the coupled crosstalk. The branched reflector is a slot-crossing open stub with the other end grounded by a via. The crosstalk has been proved to be significantly reduced, as shown in Fig. 10.

Besides the slot-crossing signal lines, the via-plates transition is another discontinuity with nonideal return path. In a multilayer PCB, the increasing integrated components and the complicated layout routing make the via transition through parallelplate structure inevitable. However, the vertical via transition results in signal distortion and EMI because of excitation of the cavity modes [104]. The modeling of the interaction between the vias and the parallel-plate is thus important. The interaction can be described by an analytical formula for a constrained parallelplate shape [105], [106] or full-wave simulation with larger computation resources [104], [107]. Recently, a physics-based

Fig. 9. Concept of the branched reflector for a signal passing a slotline.

Fig. 10. Crosstalk reduction by the branched reflector in time domain [103].

via model was proposed with reasonable accuracy and computing efficiency [108]–[112]. This approach combines the parallelplate impedance based on the cavity model [113], [114] and the via-to-plane capacitance formula [110]. An advantage of the physics-based via model is that it is convenient for producing signal and power integrity cosimulation [112], [115].

# V. ASSESSMENT OF PARAMETERS VARIATION EFFECTS ON PCB SIGNALS

A fundamental step to perform right-the-first-time designs is the availability of efficient methods for the numerical simulation of interconnect structures. Several tools are available, although they are usually deterministic, hence strongly limited whenever manufacturing tolerances or uncertainties on design parameters cannot be neglected. Therefore, stochastic analysis is highly desirable in the early design phase for the prediction of the system performance and for setting realistic design margins. The typical resource allowing to collect quantitative information on the statistical behavior of the circuit response is based on the application of the brute-force Monte Carlo (MC) method [116]. Such an approach, however, is computationally expensive, and this fact prevents us from its application to the analysis of complex realistic structures. Recently, an alternative technique overcoming the previous limitation has been proposed. This methodology is based on the polynomial chaos (PC) theory and on the representation of the stochastic solution of a dynamical systems in terms of orthogonal polynomials [117]. An extension of PC theory to interconnects described by transmission-line equations [118], and a SPICE implementation of this methodology to lumped circuit elements has been recently provided [119].

#### A. Stochastic Formulation

In order to account for uncertainties affecting the wave propagation along distributed transmission lines, we refer to the theory of telegraph equations, to which Paul significantly contributed and rigorously and elegantly described in [2]. The transmission line governing equations in the Laplace domain

$$\frac{d}{dz} \begin{bmatrix} \mathbf{V}(z,s) \\ \mathbf{I}(z,s) \end{bmatrix} = - \begin{bmatrix} 0 & \mathbf{Z}(s) \\ \mathbf{Y}(s) & 0 \end{bmatrix} \begin{bmatrix} \mathbf{V}(z,s) \\ \mathbf{I}(z,s) \end{bmatrix}$$

(1)

become stochastic differential equations, leading to randomly varying voltages and currents along the line. In (1), s is the Laplace variable, while  $\mathbf{V} = [\dots, V_i(z, s), \dots]^T$  and  $\mathbf{I} = [\dots, I_i(z, s), \dots]^T$  are vectors collecting the voltage and current variables along the multiconductor line (z coordinate). Moreover,  $\mathbf{Z} = \mathbf{R} + s\mathbf{L}$  and  $\mathbf{Y} = \mathbf{G} + s\mathbf{C}$  are the p.u.l. impedance and admittance matrices, depending on the geometrical and material properties of the structure. When the problem becomes stochastic, we must consider the p.u.l. parameters as random quantities, with entries depending on the random variable  $\xi$ . In turn, (1) becomes a stochastic differential equation, leading to randomly varying voltages and currents along the line. Therefore, they also depend on  $\xi$ .

Any function H, carrying the effects of variability, can be approximated by means of the following truncated series [120]

$$H(\ldots,\xi) = \sum_{k=0}^{P} H_k(\ldots) \cdot \phi_k(\xi)$$

(2)

where  $\{\phi_k\}$  are suitable orthogonal polynomials expressed in terms of the random variable  $\xi$ . The aforementioned expression is defined by the class of the orthogonal bases, by the number of terms P + 1 (limited to the range from 2 to 20 for practical applications, depending also on the number of random variables considered) and by the expansion coefficients  $H_k$ .

The expansion (2) of the p.u.l parameters and of the unknown voltage and current variables in terms of Hermite polynomials, yields a modified version of (1), whose second row becomes

$$\frac{d}{dz} (\mathbf{I}_{0}(z,s)\phi_{0}(\xi) + \mathbf{I}_{1}(z,s)\phi_{1}(\xi) + \mathbf{I}_{2}(z,s)\phi_{2}(\xi))

= -(\mathbf{Y}_{0}\phi_{0}(\xi) + \mathbf{Y}_{1}\phi_{1}(\xi) + \mathbf{Y}_{2}\phi_{2}(\xi))(\mathbf{V}_{0}(z,s)\phi_{0}(\xi)

+ \mathbf{V}_{1}(z,s)\phi_{1}(\xi) + \mathbf{V}_{2}(z,s)\phi_{2}(\xi))$$

(3)

where a second-order expansion (i.e., P = 2) is assumed; the expansion coefficients of electrical variables and of p.u.l. parameters are readily identifiable in the aforementioned equation.

Projection of (3) and of the companion relation arising from the first row of (1) on the first three Hermite polynomials leads to the following augmented system, where the random variable  $\xi$  does not appear explicitly, due to integral projection:

$$\frac{d}{dz} \begin{bmatrix} \tilde{\mathbf{V}}(z,s) \\ \tilde{\mathbf{I}}(z,s) \end{bmatrix} = - \begin{bmatrix} 0 & \tilde{\mathbf{Z}}(s) \\ \tilde{\mathbf{Y}}(s) & 0 \end{bmatrix} \begin{bmatrix} \tilde{\mathbf{V}}(z,s) \\ \tilde{\mathbf{I}}(z,s) \end{bmatrix}. \quad (4)$$

Fig. 11. Example of high-speed data link.

Fig. 12. Microstrip cross section for the transmission lines in Fig. 11.

In the previous equation, vectors  $\tilde{\mathbf{V}} = [\mathbf{V}_0, \mathbf{V}_1, \mathbf{V}_2]^T$  and  $\tilde{\mathbf{I}} = [\mathbf{I}_0, \mathbf{I}_1, \mathbf{I}_2]^T$  collect the different coefficients of the PC expansion of the voltage and current variables. The new p.u.l. matrix  $\tilde{\mathbf{Y}}$  turns out to be

$$\tilde{\mathbf{Y}} = \begin{bmatrix} \mathbf{Y}_0 & \mathbf{Y}_1 & 2\mathbf{Y}_2 \\ \mathbf{Y}_1 & (\mathbf{Y}_0 + 2\mathbf{Y}_2) & 2\mathbf{Y}_1 \\ \mathbf{Y}_2 & \mathbf{Y}_1 & (\mathbf{Y}_0 + 4\mathbf{Y}_2) \end{bmatrix}$$

(5)

and a similar relation holds for matrix  $\mathbf{Z}$ .

It is worth noting that (4) is analogous to (1) and plays the role of the set of equations of a multiconductor transmission line with a number of conductors that is (P + 1) times larger than those of the original line. It should be also remarked that the increment of the equation number is not detrimental for the method, since for small values of P (as typically occurs in practice) the additional overhead in handling the augmented equations is much less than the time required to run a large number of MC simulations.

As far as the solution of the stochastic problem is concerned, the augmented chain parameter matrix, relating the coefficients of the voltage and current variables at the line extremities, becomes

$$\tilde{\mathbf{T}}_{\mathrm{TL}}(\mathcal{L}, s) = \exp\left(-\begin{bmatrix} 0 & \tilde{\mathbf{Z}}(s) \\ \tilde{\mathbf{Y}}(s) & 0 \end{bmatrix} \mathcal{L}\right)$$

(6)

where expm denotes the matrix exponential and  $\mathcal{L}$  is the line length.

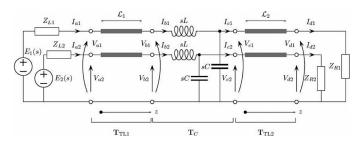

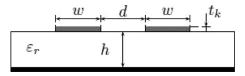

# B. Application Example

The proposed technique is applied to the analysis of the structure of Fig. 11, where the transmission lines have lengths  $\mathcal{L}_1 = \mathcal{L}_2 = 5$  cm and the cross section of Fig. 12 with the following nominal parameters:  $w = 100 \,\mu\text{m}$ ,  $d = 80 \,\mu\text{m}$ ,  $h = 60 \,\mu\text{m}$ ,  $t_k = 35 \,\mu\text{m}$ , and  $\varepsilon_r = 3.7$ . The depicted scheme provides an exemplification of a typical high-speed data link composed by two transmitters (represented by the Thévenin sources on the left) driving a distributed–possibly multiconductor–interconnect terminated by digital receivers (here assumed linear and simply described by their  $Z_{R1,2}$  input impedances). The interconnect

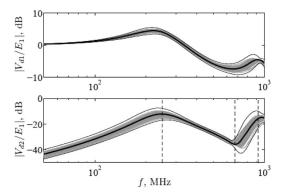

Fig. 13. Magnitudes of  $|V_{d1}(j\omega)/E_1(j\omega)|$  and  $|V_{d2}(j\omega)/E_1(j\omega)|$  for the variability of substrate parameters and connector capacitance. Solid black thick line—deterministic response, solid black thin line— $\pm 3\sigma$  limits of the third-order PC expansion, gray lines—a sample of responses obtained by means of the MC method (limited to 100 curves, for graph readability).

is supposed to be composed by two identical sections linked by a connector represented by a simple *LC* equivalent. The values of the connector parameters are L = 3 nH and C = 0.4 pF. The line is excited by ideal linear drivers (one active and one off), whose equivalent series impedances are  $Z_{L1} = Z_{L2} = 25 \Omega$  and  $Z_{R1} = Z_{R2} = sC_L$ , being  $C_L = 10$  pF.

The randomness is provided by the substrate parameters, i.e., h and  $\varepsilon_r$ , that are considered to be the same for both the transmission lines, as well as by the lumped capacitance C. These parameters are considered as three independent Gaussian random variables with a relative standard deviation of 10%. The total number of terms P + 1 (corresponding also to the magnification of the size with respect to the original system) is given by

$$P + 1 = \frac{(p+n)!}{p!n!} \tag{7}$$

where n is the number of random variables and p is the order of accuracy, that represents the maximum degree of the polynomials used for the expansion.

Three augmented models are built for the distributed lines and the intermediate lumped section, which are indicated by their transmission matrices  $T_{TL1,2}$  and  $T_C$ , respectively. Approximate relations were used to numerically compute the PC expansion of the p.u.l. parameters of the coupled microstrips, whereas the expansion of the chain parameter matrix for the lumped block is obtained analytically.

In the first example, the structure is analyzed in frequency domain. Fig. 13 shows the transfer functions between the voltage source and the two right-end terminations. Clearly, the parameter variations lead to a spread in the transfer function, that is well predicted by the estimated  $3\sigma$  limits.

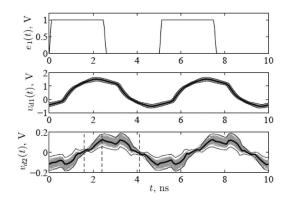

Fig. 14 shows the results for a time-domain analysis on the same structure. In this case, the time-domain voltage source  $e_1(t)$  is a trapezoidal wave with an amplitude of 1 V, rise and fall times of 100 ps, duty cycle 50%, and a total period of 5 ns. Harmonic superposition with N = 30 harmonics is considered for the calculations.

Often the knowledge of the standard deviation represents a limited information, since the quantitative information about

Fig. 14.  $v_{d1}(t)$  and  $v_{d2}(t)$ . Solid black thick line—deterministic response, solid black thin line— $\pm 3\sigma$  limits of the third-order PC expansion, gray lines— a sample of responses obtained by means of the MC method (limited to 100 curves, for graph readability).

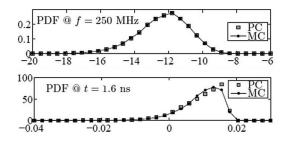

Fig. 15. Probability density function of  $|V_{d2}(j\omega)/E_1(j\omega)|$  for 250 MHz (upper panel) and of  $v_{d2}(t = 1.6\text{ns})$  (lower panel). The distributions marked MC refer to 40,000 MC simulations, whereas those marked PC refer to the response obtained via a third-order PC expansion.

how the values are distributed is missing. Nonetheless, from the analytical PC model, we can also obtain the probability density function (PDF) of the system responses. Fig. 15 shows the PDF of  $|V_{d2}/E_1|$  computed for 250 MHz (upper panel) and the PDF of  $v_{d2}(t = 1.6ns)$  (lower panel).

The good agreement between the actual and the predicted PDFs, as shown in Fig. 15, and the accuracy in reproducing the tails and the large variability of non-Gaussian shapes of the reference distributions, confirm the potential of the proposed method. For this example, it is also clear that a PC expansion with order 3 (i.e., P + 1 = 20) is already accurate enough to capture the dominant statistical information of the system response. Finally, we observe that the speed-up of PC with respect to MC is over two orders of magnitude.

However, when the number of random variables of interest increases, the efficiency of the PC appraoch tends to decrease, due to the increased number of terms, according to (7). A possible solution consists in performing preliminary tests to identify the most influential variables to be included in the model [121]. Yet, other alternatives less sensitive to the number of random parameters exist. A possible example is the response surface modeling (RSM) approach, based on the fitting of a system response using polynomial terms, whose coefficients are computed in a least-square sense starting from a reduced set of samples. A comparison of PC and RSM applied to the stochastic analysis of a commercial multiconductor flex cable with uncertain parameters described by independent uniform random variables has demonstrated their high efficiency with respect to MC, and the additional flexibility of RSM, that provided good results for a large number of random parameters [122].

# VI. EDUCATION FOR PRINTED CIRCUIT BOARD DESIGN

This Section illustrates an experience that one of the Authors<sup>1</sup> started some twenty years ago with the aim of providing practical EMC training for intermediately trained technicians.

In the early times, experiments were focused at cabinet level designs, using demonstrators with wires and sheet metal [123], heavily leaning on the propositions contained in the EMC education manual [6], of which Paul was the inspirer, and on the few available textbooks [124] and [125]. A few years later, PCB designers joined the class and it became apparent that it is vital to provide experiments matching the attendees view of the world. Crosstalk was demonstrated by means of experiments with wires, but the question on how the shown phenomenon relates to PCB structures was always popping up. Hence, all experiments had to be "ported" to PCB versions. To complicate the issues, the level of education had to be lifted from 'lumped elements" (LE) to "per unit length" (PUL) versions, since the primary reason to educate the PCB designers was a disastrous transition from traditional trace layout craftsmanship to computer aided development (CAD) tools that did not (yet) have transmission line effects on board. These tools were advertised to help with a shorter time to market and savings in terms of reduced PCB production complexity. In order to achieve such results, however, a fast reeducation of the layout engineers was needed on these more elevated subjects and this is where the EMC textbook of Paul came in handy [1]. It also showed the absolute requirement of management awareness in these matters.

The EMC curriculum was then expanded to include "long line" effects using some experimental printed circuit boards already designed using the concepts of ground bounce and partial inductance developed by Paul [1, pp.775–785]. These boards were used for in-company education and the yearly Dutch EMC courses at the Technical University of Eindhoven.

For high-speed work, it is absolutely essential to not only keep signals and return together but also not to disturb the geometry of the interconnection impedance to avoid reflections. Printed circuits are definitely more stable in this respect than their wired counterparts. For the educational demonstrations, however, this posed a challenge to demonstrate the good and the bad approach preferably in one circuit board. A master student was set to work on a consistent set of PCB demonstrations, resulting in an initial set in 2005 [126]. The initial boards are shown in Fig. 16.

These boards were a huge success at sessions with board designers, but a reservation was frequently raised, since these boards did not look like the boards currently manufactured for products. There was apparently a need to give them a more "professional" look in order to make the demonstration boards acceptable for the management-oriented attendees. So, an improved set was built with the help of several students in the 2008–2009 time frame [127] and the preparations for the Kyoto conference paper [131], resulting in

Fig. 16. The initial printed circuit board set.

Fig. 17. Selection of the new professional EMC demonstration boards.

sixteen different boards, accompanied by a user manual [128]. A selection of the new boards is shown in Fig. 17.

The EMC Printed Circuit Board Experiments can be performed either in the time domain or in the frequency domain. The former using the TDR approach, the latter using a spectrum analyzer with a tracking generator.

## A. Time Domain Experiments

The most challenging audience are the digital high-speed designers. Many of them have had little or no education in analogue phenomena as reflections and crosstalk and the measures

Fig. 18. Home-made time domain reflectometer with scope and generator (Shown with Crosstalk Experiment Board).

to avoid problems. The task for the high-speed digital designers is to transport a critical timing signal from one point to another on a board without distortions. They predominantly think in terms of time. Distortions are created by discontinuities in the transmission line used for the transport, creating partial reflections, or by means of crosstalk from a signal on another trace on the board. The digital designer is usually less interested in the behavior of his or her creation in the frequency domain.

A time domain reflectometer contains a generator to send a fast "zero-to-one" digital transition down a coaxial line, matched to the impedance of the generator, usually 50  $\Omega$ . The coaxial line has an open end that is monitored by a fast oscilloscope and also connects to the transmission line under study. Any discontinuity (from the 50  $\Omega$  impedance) on this transmission line combination generates a reflection that shows on the monitoring oscilloscope. The location of the discontinuity can be calculated from the time delay between the rising edge and the occurrence of the reflection. An animation of the TDR process is shown on Wikipedia [132], and a short tutorial can be found in [133]. Fig. 18 shows how a TDR can be assembled from a scope and a generator (see also [1], Fig. 4.26).

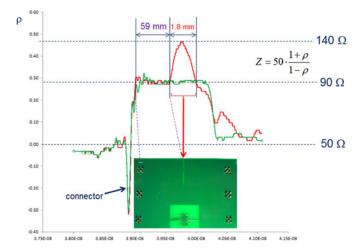

The resolution of the TDR measurement depends directly on the rise-time of the oscillator transition traveling down the line under study. As a rule of thumb, the smallest discontinuity visible has a length equal to the distance traveled by the wave during the oscillator's rise-time. The PCB experiments at the University of Twente are usually performed by students using the TDR of Fig. 18, assembled from a square wave generator with a  $\tau_r = 3$  ns risetime and a 200 MHz bandwidth oscilloscope. The generator is described in [123]. The transmission lines on PCBs are microstriplines having a propagation delay of about  $\tau_{PD} = 5$  ns/m. The "resolution" is  $\tau_r / \tau_{PD}$  and equals approximately 60 cm (24 inches). However, it is not enough for the small discontinuities usually encountered on PCB, as shown in Fig. 19. To evaluate those boards in the time domain, a faster TDR is required. Instruments with a signal rise-time under 50 ps, giving a distance resolution of approximately 0.01 m (0.4 in), are required.

The board in Fig. 19 contains a 1.8 mm reference plane gap under a trace. Based on the propagation speed of 5 ns/m for

Fig. 19. Effect of trace crossing narrow aperture in ground.

Fig. 20. The board showing Lenz's law.

the trace, the 1.8 mm would be traveled in 9 ps. The actual displayed time is 400 ps, 44 times longer, but still too short to be seen on a 200 MHz oscilloscope that needs a transient of several nanoseconds to make it visible. The effect responsible for this extra delay is the additional induction introduced by the anomaly in the transmission-line geometry. The signal traveling down the transmission line is a specific energy flow, determined by the effective signal voltage and current. When the geometry changes into the large loop formed by the trace and the gap in the ground reference plane, the p.u.l. inductance  $L_{PUL}$  of the line suddenly increases while the respective capacitance  $C_{PUL}$  goes down. This, in turn, increases the local line characteristic impedance  $Z_0 = \sqrt{L_{\rm PUL}/C_{\rm PUL}}$ . The additional inductance now has to be "filled with magnetic flux" in order to make the line current possible. This process takes time and results in a delay for the pulse propagation.

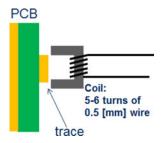

This *inductive effect* is now explained by the "self-induction" and "Lenz law" demonstration boards. The former is a movable wire over a ground reference plane that can be manipulated to show more or less "spiking" on the TDR (even on the model in Fig. 18). The latter is a board with a U-shaped ground reference strip and seven traces which are layed-out as shown in Fig. 20. Here, the traces cannot be moved and changes on the TDR display are only visible when the TDR signal line is connected to the seven input connectors in sequence. The output connector is not used and normally loaded with 50  $\Omega$ .

Fig. 21. Small magnetic field probe.

For further demonstrations, a magnetic field probe can be used on the second channel of the oscilloscope/TDR. The probe is made of a small ferrite C-core with a few turns of wire (not critical), as shown in Fig. 21, and it is loaded with 50  $\Omega$ .

The probe is used to show where fields are present. For the traces far removed from the reference trace, a high value is measured near the trace and on the edge of the reference strip. If the scope is triggered on the TDR signal feeding the trace, an inverse polarity can be observed. On the rightmost trace (input 7) in Fig. 20, only a small spike is measured if the probe is right on the trace. This demonstrates that, if a return path is available directly under the trace, the return current will prefer to flow there (proximity effect). This demonstrates to the students that currents naturally prefer paths producing as little induction as possible. The field probe of Fig. 21 could also be used on the bottom of the board, on the opposite side of the reference strip to show that the skin effect prevents fields generation from the current in trace 7.

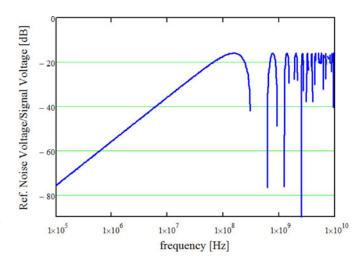

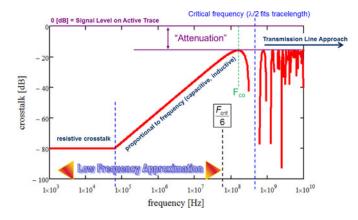

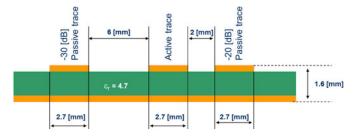

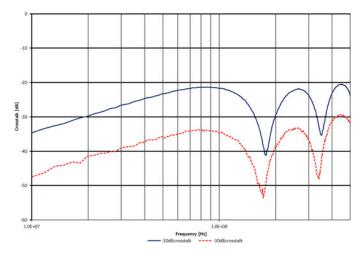

## **B.** Frequency Domain Experiments

Although all boards can be approached either in the time domain or in the frequency domain, there is an effect that can only be shown in the frequency domain. It is a crosstalk experiment with an active trace, escorted by two passive traces: a "20 dB" trace and a "30 dB" trace. The board is shown in Fig. 18, and its trace geometry (cross section) is displayed in Fig. 25. The motivation for this demonstration resides in the fact that digital layout engineers have problems separating their traces. The signal-to-noise transformation effect [129] helps with the explanation. In fact, this is the concept of transfer impedance for transmission lines, focused on PCB's. It is defined as the ratio of the noise voltage appearing over the return conductor of a transmission line and the signal voltage transferred over the line. The line is assumed to be terminated in its characteristic impedance. This ratio is shown in Fig. 22. In [129], this "ground lift" voltage is then used as driving voltage to an antenna formed by cables connected to the reference conductor at either side of this section of PCB transmission line. Using the equations for wire antennas, the generated field (e.g., in the far field) is calculated. The interesting aspect is the asymptotic leveling of the ground lift voltage for high frequencies. The level of this asymptote can be calculated from the transmission line geometry.

Analyses and experiments have shown that this same model can be used to calculate the crosstalk between two adjacent PCB traces over a common ground reference plane. Here, too, the crosstalk asymptotically approaches a fixed level, starting at the frequency at which the active transmission line length cor-

Fig. 22. Signal-to-noise transformation for a PCB transmission line.

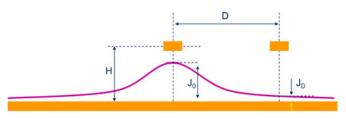

Fig. 23. Geometry of a line with two traces over a reference plane, and current density distribution in the plane.

responds to a quarter wavelength. This is called the "cross-over frequency". The level of the horizontal asymptote for crossstalk is the maximum crosstalk level for the given line geometry for frequencies above the cross over value (determined by the length over which the lines run in parallel and the propagation speed). Obviously, if the original signal on the active line has no components in this frequency range, the actual crosstalk will be lower, thus confirming the basic EMC rule–use no higher frequencies than absolutely necessary. The maximum crosstalk level can be determined using per unit length parameters for the two adjacent lines. Assuming two identical lines, running in parallel at a fixed separation, the ratio of the line inductance,  $L_{\rm PUL}$  and the mutual inductance  $M_{\rm PUL}$  is needed. This ratio is [130]

$$\frac{M_{\rm PUL}}{L_{\rm PUL}} = \frac{J_D}{J_0} \approx \frac{1}{1 + (\frac{D}{H})^2} \tag{8}$$

and Fig. 23 represents the line geometry and the current density distribution in the reference metal plane. The proposition here is to replace the current density  $J_0$  in the ground reference plane under the active trace by the per unit length inductance  $L_{\rm PUL}$  of the trace, because the two quantities are proportional. The remaining current density  $J_D$ , under the passive trace, is then replaced by the per unit length mutual inductance  $M_{\rm PUL}$  between the active and the passive trace.

The asymptotic crosstalk level (referenced to the signal level in the active trace as 0 dB) can be interpreted as an attenuation, depending on the PCB trace configuration, i.e.

Attenuation =

$$20 \log \frac{L_{\text{PUL}} + M_{\text{PUL}}}{M_{\text{PUL}}}$$

(9)

Fig. 24. Crosstalk between two identical terminated PCB traces.

Fig. 25. Trace geometry (cross section) for crosstalk experiment board.

Fig. 26. -20 and -30 dB crosstalk demonstration by measurements on the side traces of the experiment board of Fig. 25.

and is shown in Fig. 24. Using this approach to crosstalk, its envelope in the frequency domain can be easily drawn using the maximum value of (9) for frequencies above  $F_{CO}$  and values decreasing proportional to frequency below it. Although the analysis is valid only for properly terminated lines, which is almost never the case in digital boards, at least there is a lot of insight to be gained from this experiment. Fig. 25 illustrates the cross section of the experiment board (2.7 mm-wide traces are needed to achieve a 50  $\Omega$  impedance to match the available standard test cabling). The two cases -20 and -30 dB have been designed for the crosstalk board in the experiment set. The experiment is performed using a spectrum analyzer with tracking generator that is first calibrated to 0 dB with the input 11

interconnected to the generator. The result for the two traces is shown in Fig. 26.<sup>2</sup> This demonstration is intended for helping layout engineers to determine their trace separations, once they know how much crosstalk their design can afford. This information can then be extracted from signal levels, susceptibility thresholds and the bandwidth of the system active signals.

## VII. CONCLUSION

In this paper, three main topics (link path, differential signal, and discontinuities) related to SI and EMC for PCB or package have been outlined and reviewed from the points of view of modeling, analysis, and design. The inclusion of parameters variability effects has also been considered, and it has been demonstrated that recently introduced stochastic methods allow simulations of interconnects with several statistical parameters. Finally, an educational experience for PCB design has been illustrated, and a description of a small sample of demonstration boards has been provided. Nevertheless, it should be mentioned that the University of Twente EMC group makes available the boards for whomever wishes to use them, in the spirit of Paul's IEEE EMC education manual and for the promotion of EMC knowledge and of the techniques to achieve it.

In future, further research for the cosimulation and codesign to take signal integrity, power integrity, EMC, RFI into account will be one of the crucial directions that both industry and academia should pursue.

#### REFERENCES

- C. R. Paul, *Introduction to Electromagnetic Compatibility*. New York, NY, USA: Wiley, 1992, (2nd ed., 2006).

- [2] C. R. Paul, Analysis of Multiconductor Transmission Lines. Hoboken, NJ: Wiley, 1994, (2nd ed., 2008).

- [3] C. R. Paul, Inductance: Loop and Partial. New York, NY, USA: Wiley, 2010.

- [4] C. R. Paul, Transmission Lines in Digital and Analog Electronic Systems: Signal Integrity and Crosstalk. New York, NY, USA: Wiley, 2010.

- [5] C. R. Paul, Transmission Lines in Digital Systems for EMC Practitioners. New York, NY, USA: Wiley, 2010.

- [6] H. W. Ott and C. R. Paul, Eds. (1992). EMC Education Manual, Piscataway: The Education Committee of the IEEE EMC Society, [Online]. Available: http://www.ewh.ieee.org/soc/emcs/pdf/EMCman.pdf

- [7] M. A. Kolbehdari, M. Srinivasan, M. S. Nakhla, Q.-J. Zhang, and R. Achar, "Simultaneous time and frequency domain solutions of EM problems using finite element and CHF techniques," *IEEE Trans. Microw. Theory Tech.*, vol. 44, no. 9, pp. 1526–1534, Sep. 1996.

- [8] H.-H. Chuang, W.-D. Guo, Y.-H. Lin, H.-S. Chen, Y-C Lu, J. Hong, C.-H. Yu, A. Cheng, J. Chou, C.-J. Chang, J. Ku, T.-L. Wu, and R.-B. Wu, "Signal/power integrity modeling of high-speed memory modules using chip-package-board co-analysis," *IEEE Trans. Electronmagn. Compat.*, vol. 52, no. 2, pp. 381–391, May 2010.

- [9] M. Nakhla and R. Achar, "Simulation of high-speed interconnects," *Proc. IEEE*, vol. 89, no. 5, pp. 693–728, May 2001.

- [10] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," *IEEE Trans. Power Del.*, vol. 14, no. 3, pp. 1052–1061, Jul. 1999.

- [11] W. Beyene and J. Schutt-Aine, "Accurate frequency-domain modeling and efficient circuit simulation of high-speed packaging interconnects," *IEEE Trans. Microw. Theory Tech.*, vol. 45, no. 10, pp. 1941–1947, Oct. 1997.

<sup>2</sup>The unused passive trace should be terminated to prevent resonance effects. Also, it should be noted that most spectrum analyzers have a linear frequency scale, obscuring the low-frequency "proportional to frequency" crosstalk behavior.

- [12] K. L. Choi and M. Swaminathan, "Development of model libraries for embedded passives using network synthesis," *IEEE Trans. Circuits Syst. II*, vol. 47, no. 4, pp. 249–260, Apr. 2000.

- [13] M. Elzinga, K. Virga, and J. L. Prince, "Improve global rational approximation macromodeling algorithm for networks characterized by frequency-sampled data," *IEEE Trans. Microw. Theory Tech.*, vol. 48, no. 9, pp. 1461–1467, Sep. 2000.

- [14] S. Grivet-Talocia and M. Bandinu, "Improving the convergence of vector fitting for equivalent circuit extraction from noisy frequency responses," *IEEE Trans. Electromagn. Compat.*, vol. 48, no. 1, pp. 104–120, Feb. 2006.

- [15] D. Deschrijver and T. Dhaene, "Broadband macromodeling of passive components using orthonormal vector fitting," *Electron. Lett.*, vol. 41, no. 21, pp. 1160–1161, Oct. 2005.

- [16] B. Nouri, R. Achar, and M. S. Nakhla, "z-domain orthonormal basis functions for physical system identifications," *IEEE Trans. Adv. Packag.*, vol. 33, no. 1, pp. 293–307, Feb. 2010.

- [17] P. Triverio, S. Grivet-Talocia, M. S. Nakhla, F. G. Canavero, and R. Achar, "Stability, causality, and passivity in electrical interconnect models," *IEEE Trans. Adv. Packag.*, vol. 30, no. 4, pp. 795–808, Nov. 2007.

- [18] B. Gustavsen and A. Semlyen, "Enforcing passivity for admittance matrices approximated by rational functions," *IEEE Trans. Power Syst.*, vol. 16, no. 1, pp. 97–104, Mar. 2001.

- [19] R. Achar, P. K. Gunupudi, M. Nakhla, and E. Chiprout, "Passive interconnect reduction algorithm for distributed/measured networks," *IEEE Trans. Circuits Syst. II*, vol. 47, no. 4, pp. 287–301, Apr. 2000.

- [20] D. Saraswat, R. Achar, and M. Nakhla, "Global passivity enforcement algorithm for macromodels of interconnect subnetworks characterized by tabulated data," *IEEE Trans. VLSI Syst.*, vol. 13, no. 7, pp. 819–832, Jul. 2005.

- [21] S. Grivet-Talocia, "Passivity enforcement via perturbation of hamiltonian matrices," *IEEE Trans. Circuits Syst. I*, vol. 51, no. 9, pp. 1755–1769, Sep. 2004.

- [22] S. Grivet-Talocia and A. Ubolli, "On the generation of large passive macromodels for complex interconnect structures," *IEEE Trans. Adv. Packag.*, vol. 29, no. 1, pp. 39–54, Feb. 2006.

- [23] T.-L. Wu, C.-C. Kuo, H.-C. Chang, and J.-S. Shie, "A novel systematic approach for equivalent model extraction of embedded high-speed interconnects in time domain," *IEEE Trans. Electromagn. Compat.*, vol. 45, no. 3, pp. 493–501, Aug. 2003.

- [24] T.-L. Wu, C.-C. Kuo, C.-C. Wang, S.-M. Wu, and C.-P. Hung, "A novel time-domain algorithm for synthesizing broadband macromodels of coupled interconnects," *IEEE Trans. Adv. Packag.*, vol. 27, no. 1, pp. 224– 232, Feb. 2004.

- [25] T.-L. Wu, C.-C. Wang, C.-C. Kuo, and J.-S. Hsieh, "A novel time-domain method for synthesizing broadband macromodels of differential via," *IEEE Microw. Wireless Compon. Lett.*, vol. 15, no. 5, pp. 378–380, May 2005.

- [26] C.-C. Wang, C.-W. Ku, C.-C. Kuo, and T.-L. Wu, "A time-domain approach for extracting broadband macromodels of differential via holes," *IEEE Trans. Adv. Packag.*, vol. 29, no. 4, pp. 789–797, Nov. 2006.

- [27] B. K. Casper, M. Haycock, and R. Mooney, "An accurate and efficient analysis method for multi-Gb/s chip-to-chip signaling schemes," in *Proc. IEEE Symp. Very Large Scale Circuits*, Jun. 2002, pp. 54–57.

- [28] W.-D. Guo, J.-H. Lin, C.-M. Lin, T.-W. Huang, and R.-B. Wu, "Fast methodology for determining eye diagram characteristics of lossy transmission lines," *IEEE Trans. Adv. Packag.*, vol. 32, no. 1, pp. 175–183, Feb. 2009.

- [29] W. Yu, R. Shi, and C.-K. Cheng, "Accurate eye diagram prediction based on step response and its application to low-power equalizer design," *IEICE Trans. Electron.*, vol. E92-C, no. 4, pp. 444–452, Apr. 2009.

- [30] J. F. Buckwalter, "Predicting microwave digital signal integrity," *IEEE Trans. Adv. Packag.*, vol. 32, no. 2, pp. 280–289, May 2009.

- [31] Y.-S. Cheng and R.-B. Wu, "Direct eye diagram optimization for arbitrary transmission lines using FIR filter," *IEEE Trans. Compon. Packag.*, *Manuf. Technol.*, vol. 1, no. 8, pp. 1250–1258, Aug. 2011.

- [32] J. Buckwalter, B. Analui, and A. Hajimiri, "Data-dependent jitter and crosstalk-induced bounded uncorrelated jitter in copper interconnects," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2004, vol. 3, pp. 1627– 1630.

- [33] C.-C. Chou, H.-H. Chuang, T.-L. Wu, S.-H. Weng, and C.-K. Cheng, "Eye prediction of digital driver with power distribution network noise," in *Proc. IEEE 21th Topical Meet. Electr. Perform. Electron. Pack.*, Tempe, AZ, USA, Oct. 2012, pp. 131–134.

- [34] A. Deutsch, P. W. Coteus, P. E. Dahlen, D. L. Heckmann, and D. W. Duan, "Frequency-dependent losses on high-performance interconnections," *IEEE Trans. Electromagn. Compat.*, vol. 43, no. 4, pp. 446– 465, Nov. 2001.

- [35] W. Humann, "Compensation of transmission line loss for Gbit/s test on ATEs," in Proc. IEEE Int. Test Conf., Oct. 2002, pp. 430–437.

- [36] Maxim Integrated Products, "Designing a simple, small, wide-band and low-power equalizer for FR4 copper links," in *Proc. Design Con*, 2003, pp. 1–14.

- [37] R. Sun, J. Park, F. O'Mahony, and C. P. Yue, "A low-power, 20-Gb/s continuous-time adaptive passive equalizer," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2005, vol. 2, pp. 920–923.

- [38] K. J. Han, H. Takeuchi, and M. Swaminathan, "Eye-pattern design for high-speed differential links using extended passive equalization," *IEEE Trans. Adv. Packag.*, vol. 31, no. 2, pp. 246–257, May 2008.

- [39] L. Zhang, W. Yu, Y. Zhang, R. Wang, A. Deutsch, G. A. Katopis, D. M. Dreps, J. Buckwalter, E. S. Kuh, and C. K. Cheng, "Low power passive equalizer design for computer memory links," in *Proc. 16th IEEE Symp. High Perform. Interconn.*, Aug. 2008, pp. 51–56.

- [40] E. Song, J. Cho, W. Lee, M. Shin, and J. Kim, "A wide-band passive equalizer design on PCB based on near-end crosstalk and reflections for 12.5 Gbps serial data transmission," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 12, pp. 794–796, Dec. 2008.

- [41] Y. Shim, W. Lee, E. Song, J. Cho, and J. Kim, "A compact and wideband passive equalizer design using a stub with defected ground structure for high speed data transmission," *IEEE Microw. Wireless Comp. Lett.*, vol. 20, no. 5, pp. 256–258, May 2010.

- [42] Y.-J. Cheng, H.-H. Chuang, and T.-L. Wu, "A novel differential-mode equalizer with broadband common-mode filtering for GHz differentialsignal transmission," *IEEE Trans. Compon. Packag., Manuf. Technol.*, DOI: 10.1109/TCPMT.2013.2246275.

- [43] L. Zhang, W. Yu, Y. Zhang, R. Wang, A. Deutsch, G. A. Katopis, D. M. Dreps, J. Buckwalter, E. S. Kuh, and C. K. Cheng, "Analysis and optimization of low-power passive equalizers for CPU-memory links," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 1, no. 9, pp. 1406– 1420, Sep. 2011.

- [44] D. J. Riley and L. D. Bacon, "On the limitation of the weak-coupling assumption for crosstalk analysis based on quasi-TEM propagation," *IEEE Trans. Electromagn. Compat.*, vol. 32, no. 1, pp. 28–37, Feb. 1990.

- [45] R. B. Wu and F. L. Chao, "Laddering wave in serpentine delay line," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 18, no. 4, pp. 644– 650, Nov. 1995.

- [46] J. S. Sohn, J. C. Lee, H. J. Park, and S. I. Cho, "Empirical equations on electrical parameters of coupled microstrip lines for crosstalk estimation in printed circuit board," *IEEE Trans. Adv. Packag.*, vol. 24, no. 4, pp. 521–527, Nov. 2001.

- [47] R. B. Wu and F. L. Chao, "Flat spiral delay line design with minimum crosstalk penalty," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 19, no. 2, pp. 397–402, May 1996.

- [48] K. Lee, H. K. Jung, H. J. Chi, H. J. Kwon, J. Y. Sim, and H. J. Park, "Serpentine microstrip lines with zero far-end crosstalk for parallel highspeed DRAM interfaces," *IEEE Trans. Adv. Packag.*, vol. 33, no. 2, pp. 552–558, May 2010.

- [49] I. Novak, B. Eged, and L. Hatvani, "On the problem of using guard traces for high frequency differential lines crosstalk reduction," *IEEE Trans. Comp. Packag. Technol.*, vol. 30, no. 1, pp. 67–74, Mar. 2007.

- [50] Y.-S. Cheng, W.-D. Guo, C.-P. Hung, and R.-B. Wu, "Enhanced microstrip guard trace for ringing noise suppression using a dielectric superstrate," *IEEE Trans. Adv. Packag.*, vol. 33, no. 4, pp. 961–968, Nov. 2010.

- [51] G. H. Shiue, J. H. Shiu, and C. M. Hsu, "Improvements of time-domain transmission waveform and eye diagram of serpentine delay line using open-stub type guard traces in embedded microstrip line," *IEEE Trans. Compon. Packag. Technol.*, vol. 1, no. 11, pp. 1706–1717, Nov. 2011.

- [52] Y. Massoud, J. Kawa, D. MacMillen, and J. White, "Modeling and analysis of differential signaling for minimizing inductive crosstalk," in *Proc. IEEE Des. Autom. Conf.*, 2001, pp. 804–809.

- [53] G.-H. Shiue and R.-B. Wu, "Reduction in reflections and ground bounce for signal line over slotted power plane using differential coupled microstrip lines," *IEEE Trans. Adv. Packag.*, vol. 32, no. 3, pp. 581–588, Aug. 2009.

- [54] S. H. Hall and H. L. Heck, Advanced Signal Integrity for High-Speed Digital System Design. Hoboken, NJ, USA: Wiley, 2009.

- [55] A. E. Ruehli, "Equivalent circuit models for three-dimensional multiconductor systems," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-22, no. 3, pp. 216–221, May 1974.

- [56] R. B. Wu and L. L. Wu, "Exploiting structure periodicity and symmetry in capacitance calculations for three-dimensional multiconductor systems," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-36, no. 9, pp. 1311– 1318, Sep. 1988.

- [57] R. B. Wu, C. N. Kuo, and K. K. Chang, "Inductance and resistance computations for three-dimensional multiconductor interconnection structures," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-40, no. 2, pp. 263– 271, Feb. 1992.

- [58] S.-G. Hsu and R.-B. Wu, "Full wave characterization of a through hole via using the matrix-penciled moment method," *IEEE Trans. Microw. Theory Tech.*, vol. 42, no. 8, pp. 1540–1547, Aug. 1994.

- [59] S.-G. Hsu and R.-B. Wu, "Full-wave characterization of a through hole via in multi-layered packaging," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 5, pp. 1073–1081, May 1995.

- [60] H. Chen, Q. Lin, L. Tsang, C.-C. Huang, and V. Jandhyala, "Analysis of a large number of vias and differential signaling in multilayered structures," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 3, pp. 818–829, Mar. 2003.

- [61] Y. Cao, L. Simonovich, and Q.-J. Zhang, "A broadband and parametric model of differential via holes using space-mapping neural network," *IEEE Microw. Wireless. Compon. Lett.*, vol. 19, no. 9, pp. 533–535, Sep. 2009.

- [62] G. Antonini, "SPICE equivalent circuits of frequency-domain responses," *IEEE Trans. Electromagn. Compat.*, vol. 45, no. 3, pp. 502– 512, Aug. 2003.

- [63] H. Chen, Q. Li, L. Tsang, C. C. Huang, and J. Vikram, "Analysis of a large number of vias and differential signaling in multilayered structures," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 3, pp. 818–829, Mar. 2003.

- [64] E. Laermans, J. Geest, D. De Zutter, F. Plyslager, S. Seru, and D. Morlion, "Modeling differential via holes," *IEEE Trans. Adv. Packag.*, vol. 24, no. 3, pp. 357–363, Aug. 2001.

- [65] H. Shi, W. T. Beyene, J. Feng, B. Chia, and X. Yuan, "Properties of mixedmode parameters of cascaded balanced networks and their applications in modeling of differential interconnects," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 1, pp. 360–372, Jan. 2006.

- [66] L. Simonovich, E. Bogatin, and Y. Cao, "Differential via modeling methodology," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 1, no. 5, pp. 722–730, May 2011.

- [67] Y. Jeng, W. Guo, G. Shiue, C. Lin, and R. Wu, "Reflectionless design for differential-via transitions using neural network-based approach," in *Proc. IEEE Conf. Electr. Perform. Electron. Packag.*, Atlanta, GA, USA, Oct. 2007, pp. 143–146.

- [68] W. D. Guo, G. H. Shiue, C. M. Lin, and R. B. Wu, "Comparisons between serpentine and flat spiral delay lines on transient reflection/transmission waveforms and eye diagrams," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 4, pp. 1379–1387, Jun. 2006.

- [69] G. H. Shiue, W. D. Guo, C. M. Lin, and R. B. Wu, "Noise reduction using compensation capacitance for bend discontinuities of differential transmission lines," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, pp. 560– 569, Aug. 2006.

- [70] C. H. Chang, R. Y. Fang, and C. L. Wang, "Bended differential transmission line using compensation inductance for common-mode noise suppression," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 2, no. 9, pp. 1518–1525, Sep. 2012.

- [71] C. Gazda, D. Vande Ginste, H. Rogier, R.-B. Wu, and D. De Zutter, "A wideband common-mode suppression filter for bend discontinuities in differential signaling using tightly coupled microstrips," *IEEE Trans. Adv. Pack.*, vol. 33, no. 4, pp. 969–978, Nov. 2010.

- [72] G. H. Shiue, Y. C. Tsai, C. M. Hsu, and J. H. Shiu, "Common-mode noise reduction schemes for differential serpentine delay microstrip line in high-speed digital circuits," in *Proc. IEEE Conf. Electr. Perform. Electron. Packag.*, San Jose, CA, USA, Oct. 2011, pp. 211–214.

- [73] W. Fan, A. Lu, L. L. Wai, and B. K. Lok, "Characteristics of phasedelay time on meander differential signal lines and shielded meander differential signal line," in *Proc. 18th Int. Zurich Symp. Elecromagn. Compat.*, Dec. 2007, pp. 217–220.

- [74] D. M. Hockanson, J. L. Drewniak, T. H. Hubing, T. P. Van Doren, F. Sha, and M. Wilhelm, "Investigation of fundamental EMI source mechanisms driving common-mode radiation from printed circuit boards with attached cables," *IEEE Trans. Electromagn. Compat.*, vol. 38, no. 4, pp. 557–566, Nov. 1996.

- [75] Y. Kayano, M. Tanaka, and H. Inoue, "An equivalent circuit model for predicting EM radiation from a PCB driven by a connected feed cable," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Portland, OR, USA, Aug. 2006, pp. 166–171.

- [76] S. Connor, B. Archambeault, and J. Diepenbrock, "The impact of external RF energy on high-speed differential signal quality of long cables," in *Proc. IEEE Int. Electromagn. Compat. Symp.*, Detroit, MI, USA, Aug. 2008, pp. 1–4.

- [77] X. Duan, B. Archambeault, H.-D. Bruens, and C. Schuster, "EM emissions of differential signals across connected printed circuit boards in the GHz range," in *Proc. DesignCon*, 2009, pp. 50–55.

- [78] T. Matsushima, O. Wada, T. Watanabe, Y. Toyota, and L. R. Koga, "Verification of common-mode-current prediction method based on imbalance difference model for single-channel differential signaling system," in *Proc. Asia-Pacif Int. Symp. Electronmagn. Compat.*, Singapore, May 2012, pp. 409–412.

- [79] Intel, USB 3.0\* Radio Frequency Interference Impact on 2.4 GHz Wireless Devices, White Paper, Apr. 2012.

- [80] Internet page. (2010). [Online]. Available: http://www.global.tdk.com/ news\_center/press/aah31600.htm

- [81] W.-T. Liu, C.-H. Tsai, T.-W. Han, and T.-L. Wu, "An embedded common mode suppression filter for GHz differential signals using periodic defected ground plane," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 4, pp. 248–250, Apr. 2008.

- [82] S.-J. Wu, C.-H. Tsai, and T.-L. Wu, "A novel wideband common-mode suppression filter for GHz differential signals using coupled patterned ground structure," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 4, pp. 848–855, Apr. 2009.

- [83] J. Naqui, A. Fernandez-Prieto, M. Duron-Sindreu, J. Selga, F. Medina, F. Mesa, and F. Marton, "Common-mode suppression in microstrip differential lines by means of complementary split ring resonators: Theory and applications," *IEEE Trans. Microw. Theory Tech.*, vol. 60, no. 10, pp. 3023–3034, Oct. 2012.

- [84] C.-H. Tsai and T.-L. Wu, "A broadband and miniaturized commonmode filter for gigahertz differential signals based on negative permittivity metamaterials," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 1, pp. 195–202, Jan. 2010.

- [85] F. de Paulis, L. Raimondo, S. Connor, B. Archambeault, and A. Orlandi, "Compact configuration for common mode filter design based on planar electromagnetic bandgap structures," *IEEE Trans. Electromagn. Compat.*, vol. 54, no. 3, pp. 646–654, Jun. 2012.

- [86] C.-Y. Hsiao, C.-H. Tsai, C.-N. Chiu, and T.-L. Wu, "Radiation suppression for cable-attached packages utilizing a compact embedded commonmode filter," *IEEE Trans. Compon. Packag., Manuf. Technol.*, vol. 2, no. 10, pp. 1696–1703, Oct. 2012.

- [87] I.-I. A.-Ieong, C.-H. Tsai and T.-L. Wu, "An ultra compact commonmode filter for RF interference control in 3G wireless communication systems," in *Proc. IEEE Int. Symp. Trans. Electromagn. Compat.*, Fort Lauderdale, FL, USA, Jul. 2010, pp. 776–779.

- [88] C.-H. Tsai, J.-Z. Hsu, and I.-I. A. Ieong, T.-L. Wu, "A novel common mode choke and its application for 5 Gbps USB 3.0," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Aug. 2011, CA, USA, pp. 888–891.

- [89] T. Sudo, H. Sasaki, N. Masuda, and J. L. Drewniak, "Electromagnetic interference (EMI) of system-on-package (SOP)," *IEEE Trans. Adv. Packag.*, vol. 27, no. 2, pp. 304–314, May 2004.

- [90] J. Kim, H. Lee, and J. Kim, "Effects on signal integrity and radiated emission by split reference plane on high-speed multilayer printed circuit boards," *IEEE Trans. Adv. Packag.*, vol. 28, no. 4, pp. 724–735, Nov. 2005.

- [91] T. L. Wu, H. H. Chuang, and T. K. Wang, "Overview of power integrity solutions on package and PCB: Decoupling and EBG isolation," *IEEE Trans. Electromagn. Compat.*, vol. 52, no. 2, pp. 346–356, May 2010.

- [92] C. Wei, F. Jun, R. Yong, S. Hao, J. L. Drewniak, and R. E. DuBroff, "DC power bus noise isolation with power-plane segmentation," *IEEE Trans. Electromagn. Compat.*, vol. 45, no. 2, pp. 436–443, May 2003.

- [93] K. Slattery and S. Skinner, Platform Interference in Wireless System: Model, Measurements, and Mitigation. New York, NY, USA: Elsevier, 2008.

- [94] C. Gupta, R. Garg, and I. J. Bahl, *Microstrip Lines and Slotlines*, 2nd ed. Norwood, MA, USA: Artech House, 1996.

- [95] J. B. Knorr and K. D. Kuchler, "Analysis of coupled slots and coplanar strips on dielectric substrates," *IEEE Trans. Microw. Theory Tech.*, vol. 23, no. 7, pp. 541–548, Jul. 1975.

- [96] C.-T. Wu, G.-H. Shiue, S.-M. Lin, and R.-B. Wu, "Composite effects of reflections and ground bounce for signal line through a split power plane," *IEEE Trans. Adv. Packag.*, vol. 25, no. 2, pp. 297–301, May 2002.

- [97] J. B. Knorr, "Slot-line transition," IEEE Trans. Microw. Theory Tech., vol. 22, no. 5, pp. 548–554, May 1974.

- [98] B. Schuppert, "Microstip/slotline transitions: Modeling and experimental investigation," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 8, pp. 1272–1282, Aug. 1988.

- [99] G. Duchamp, L. Casadebaig, S. Gauffre, and J. Pistre, "An alternative method for end-effect characterization in shorted slot lines," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 11, pp. 1793–1795, Nov. 1998.

- [100] F. Xiao, Y. Nakada, K. Murano, and Y. Kami, "Crosstalk analysis model for traces crossing split ground plane and its reduction by stitching capacitor," *IEICE Trans. Electron.*, vol. J89-C, no. 11, pp. 885–893, 2006.

- [101] C. Caloz, H. Okabe, T. Iwai, and T. Itoh, "A simple and accurate model for microstrip structures with slotted ground plane," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 3, pp. 127–129, Mar. 2004.

- [102] T. E. Moran, K. L. Virga, G. Aguirre, and J. L. Prince, "Methods to reduce radiation from split ground plane structures," in *Proc. IEEE Electr. Perform. Electron. Packag. Syst. Conf.*, Oct. 1999, pp. 203–206.

- [103] H.-H. Chuang, C.-C. Chou, Y.-J. Chang, and T.-L. Wu, "A branched reflector technique to reduce crosstalk between slot-crossing differential line," *IEEE Microw. Wireless Compon. Lett.*, vol. 22, no. 7, pp. 342–344, Jul. 2012.

- [104] C. Schuster and W. Fichtner, "Parasitic modes on printed circuit boards and their effects on EMC and signal integrity," *IEEE Trans. Electromag. Compat.*, vol. 43, no. 4, pp. 416–425, Nov. 2000.

- [105] J. C. Parker, "Via coupling within parallel rectangular planes," *IEEE Trans. Electromag. Compat.*, vol. 39, no. 1, pp. 17–23, Feb. 1997.

- [106] Z. Z. Oo, E.-X. Liu, E.-P. Li, X. Wei, Y. Zhang, M. Tan, L.-W. Li, and R. Vahldieck, "A semi-analytical approach for system-level electrical modeling of electronic packages with large number of vias," *IEEE Trans. Adv. Packag.*, vol. 31, no. 2, pp. 267–274, May 2008.

- [107] X. Wei, E. Li, E. Liu, and X. Cui, "Efficient modeling of rerouted return currents in multilayered power-ground planes by using integral equation," *IEEE Trans. Electromagn. Compat.*, vol. 50, no. 3, pp. 740–743, Aug. 2008.

- [108] J. Park, H. Kim, Y. Jeong, J. Kim, J. S. Pak, D. G. Kam, and J. Kim, "Modeling and measurement of simultaneous switching noise coupling through signal via transition," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, pp. 548–559, Aug. 2006.

- [109] R. Abhari, G. V. Eleftheriades, and E. van Deventer-Perkins, "Physicsbased CAD models for the analysis of vias in parallel-plate environments," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 10, pp. 1697– 1707, Oct. 2001.

- [110] R. Rimolo-Donadio, X. Gu, Y. H. Kwark, M. B. Ritter, B. Archambeault, F. De Paulis, Y. Zhang, J. Fan, H.-D. Bruns, and C. Schuster, "Physicsbased via and trace models for efficient link simulation on multilayer structures up to 40 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 8, pp. 2072–2083, Aug. 2009.

- [111] Y.-J. Zhang, G. Feng, and J. Fan, "A novel impedance definition of a parallel plate pair for an intrinsic via circuit model," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 12, pp. 3780–3789, Dec. 2010.

- [112] X. Duan, R. Rimolo-Donadio, H.-D. Bruns, and C. Schuster, "A combined method for fast analysis of signal propagation, ground noise, and radiated emission of multilayer printed circuit boards," *IEEE Trans. Electromag. Compat.*, vol. 52, no. 2, pp. 487–495, May 2010.

- [113] G. T. Lei, R. W. Techentin, P. R. Hayes, D. J. Schwab, and B. K. Gilbert, "Wave model solution to the ground/power plane noise problem," *IEEE Trans. Instrum. Meas.*, vol. 44, no. 2, pp. 300–303, Apr. 1995.

- [114] Z. L. Wang, O. Wada, Y. Toyota, and R. Koga, "Convergence acceleration and accuracy improvement in power bus impedance calculation with a fast algorithm using cavity modes," *IEEE Trans. Electromag. Compat.*, vol. 47, no. 1, pp. 2–8, Feb. 2005.

- [115] A. E. Engin, W. John, G. Sommer, W. Mathis, and H. Reichl, "Modeling of striplines between a power and a ground plane," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, pp. 415–426, Aug. 2006.

- [116] Q. Zhang, J. J. Liou, J. McMacken, J. Thomson, and P. Layman, "Development of robust interconnect model based on design of experiments and multiobjective optimization," *IEEE Trans. Electron. Devices*, vol. 48, no. 9, pp. 1885–1891, Sep. 2001.

- [117] D. Xiu and G. E. Karniadakis, "The wiener-askey polynomial chaos for stochastic differential equations," *SIAM J. Sci. Comput.*, vol. 24, no. 2, pp. 619–622, 2002.

- [118] I. S. Stievano, P. Manfredi, and F. G. Canavero, "Parameters variability effects on multiconductor interconnects via hermite polynomial chaos," *IEEE Trans. Compon. Packag. Manuf. Tech.*, vol. 1, no. 8, pp. 1234–1239, Aug. 2011.

- [119] P. Manfredi, I. S. Stievano, and F. G. Canavero, "Alternative spice implementation of circuit uncertainties based on orthogonal polynomials," in

Proc. 19th IEEE Conf. Elect. Perform. Electron. Packag. Syst., San Jose, CA, USA, Oct. 2011, pp. 41–44.

- [120] R. G. Ghanem and P. D. Spanos, *Stochastic Finite Elements. A Spectral Approach.* New York, NY, USA: Springer-Verlag, 1991.

- [121] P. Manfredi and F. G. Canavero, "Polynomial chaos-based tolerance analysis of microwave planar guiding structures," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, Baltimore, MD, USA, Jun. 2011, pp. 1–4.