#### RICE UNIVERSITY

# N-variant Hardware Design

by

#### Yousra Alkabani

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

## **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Keith D. Cooper, Chair

L. John & Ann H. Doerr Chair in Computational Engineering; Professor of Computer Science and Electrical and Computer Engineering

Moshe Y. Vardi

Karen Ostrum George Professor in Computer Engineering

Kartik Mohanram

Assistant Professor of Electrical and Computer Engineering and Computer Science

Bart Sinclair

Associate Dean of Engineering; Lecturer on Electrical and Computer Engineering

Houston, Texas

November, 2010

#### **ADVISORS:**

Keith D. Cooper

L. John & Ann H. Doerr Chair in Computational Engineering;

Professor of Computer Science and Electrical and Computer Engineering

Farinaz Koushanfar

Assistant Professor of Electrical and Computer Engineering;

Assistant Professor of Computer Science

#### ABSTRACT

#### N-variant Hardware Design

by

#### Yousra Alkabani

The emergence of lightweight embedded devices imposes stringent constraints on the area and power of the circuits used to construct them. Meanwhile, many of these embedded devices are used in applications that require diversity and flexibility to make them secure and adaptable to the fluctuating workload or variable fabric. While field programmable gate arrays (FPGAs) provide high flexibility, the use of application specific integrated circuits (ASICs) to implement such devices is more appealing because ASICs can currently provide an order of magnitude less area and better performance in terms of power and speed. My proposed research introduces the *N-variant hardware* design methodology that adds the sufficient flexibility needed by such devices while preserving the performance and area advantages of using ASICs.

The N-variant hardware design embeds different variants of the design control part on the same IC to provide diversity and flexibility. Because the control circuitry usually represents a small fraction of the whole circuit, using multiple versions of the control circuitry is expected to have a low overhead. The objective of my thesis is to formulate a method that provides the following advantages: (i) ease of integration in the current ASIC design flow, (ii) minimal impact on the performance and area of the ASIC design, and (iii) providing a wide range of applications for hardware security and tuning the performance of chips either statically (e.g., post-silicon optimization)

or dynamically (at runtime). This is achieved by adding diversity at two orthogonal levels: (i) state space diversity, and (ii) scheduling diversity. State space diversity expands the state space of the controller. Using state space diversity, we introduce an authentication mechanism and the first active hardware metering schemes. On the other hand, scheduling diversity is achieved by embedding different control schedules in the same design. The scheduling diversity can be spatial, temporal, or a hybrid of both methods. Spatial diversity is achieved by implementing multiple control schedules that use various parts of the chip at different rates. Temporal diversity provides variants of the controller that can operate at unequal speeds. A hybrid of both spatial and temporal diversities can also be implemented. Scheduling diversity is used to add the flexibility to tune the performance of the chip. An application of the thermal management of the chip is demonstrated using scheduling diversity. Experimental results show that the proposed method is easy to integrate in the current ASIC flow, has a wide range of applications, and incurs low overhead.

# Acknowledgment

First I would like to thank my advisor Professor Keith Cooper for the incredible support, help, and advice. I would also like to thank my committee members: Professor Moshe Vardi, Professor Kartik Mohanram, and Professor Bart Sinclair for the great insights they have given me to improve my work.

Professor Joe Warren, the chair of the computer science department has provided me with great support as a student in the computer science department.

I would also like to thank all the professors who taught me classes at Rice university and at Ain Shams university. I would like to specifically thank Professor Luay Nakhleh for being a great teacher.

I would like to thank all the staff in the computer science department. Darnell Price has given me great support, and Bel Martinez has patiently helped me finish all my paperwork.

I also highly appreciate all the help provided to me and all the Rice international students by Dr. Adria Baker and the whole office of international students and scholars (OISS) staff.

I would like to thank my family and friends for their unconditional love and support. I would specially like to thank my mom and dad for giving me all the love, care, and tenderness I needed to keep going through tough times.

At last, I would like to thank the co-authors of my papers for their valuable input on my research during the past years.

# Contents

|   | Abs  | tract    |                                                  | i  |

|---|------|----------|--------------------------------------------------|----|

|   | List | of Illus | strations                                        | ix |

|   | List | of Tab   | les                                              | x  |

|   | List | of Abr   | eviations                                        | xi |

| 1 | Int  | roduc    | ction                                            | 1  |

| _ | 1.1  |          | 3                                                | 3  |

|   | 1.2  |          | ${f ization}$                                    | 6  |

|   |      | 0 -8     |                                                  |    |

| 2 | N-   | Varia    | nt IC Design: Methodology and Applications       | 9  |

|   | 2.1  | Introd   | uction                                           | 10 |

|   |      | 2.1.1    | Motivational example                             | 12 |

|   |      | 2.1.2    | Paper organization                               | 13 |

|   | 2.2  | Backg    | round                                            | 14 |

|   |      | 2.2.1    | FSM                                              | 14 |

|   |      | 2.2.2    | N-variant method                                 | 15 |

|   | 2.3  | N-vari   | ant IC design                                    | 16 |

|   | 2.4  | Applio   | eation-specific management of the N-variants     | 20 |

|   | 2.5  | Exper    | imental results                                  | 22 |

|   |      | 2.5.1    | Implementation of the N-variant method           | 23 |

|   |      | 2.5.2    | Embedded multimedia application                  | 25 |

|   | 2.6  | Conclu   | iding remarks and future directions              | 27 |

| 3 | Act  | tive H   | lardware Metering for Intellectual Property Pro- |    |

|   | • |

|---|---|

|   | 1 |

| v |   |

| tec | tection and Security 30 |                                                 |    |  |

|-----|-------------------------|-------------------------------------------------|----|--|

| 3.1 | Introd                  | luction                                         | 31 |  |

| 3.2 | Prelin                  | ninaries                                        | 34 |  |

|     | 3.2.1                   | Background                                      | 34 |  |

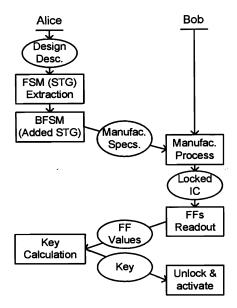

|     | 3.2.2                   | Global flow                                     | 36 |  |

| 3.3 | Relate                  | ed work                                         | 38 |  |

| 3.4 | Active                  | e hardware metering                             | 40 |  |

|     | 3.4.1                   | Method                                          | 41 |  |

|     | 3.4.2                   | Ensuring proper operation                       | 43 |  |

| 3.5 | Low o                   | verhead implementation and obfuscation          | 45 |  |

|     | 3.5.1                   | RUB implementation                              | 46 |  |

|     | 3.5.2                   | BFSM implementation                             | 47 |  |

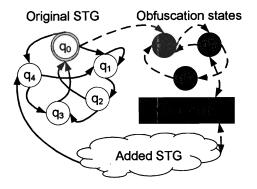

| 3.6 | Attacl                  | k resiliency                                    | 51 |  |

|     | 3.6.1                   | Description of attacks                          | 52 |  |

|     | 3.6.2                   | Counter measures                                | 54 |  |

| 3.7 | Exper                   | imental evaluations                             | 60 |  |

|     | 3.7.1                   | Experiment setup                                | 60 |  |

|     | 3.7.2                   | Overhead of active hardware metering            | 61 |  |

|     | 3.7.3                   | Resiliency against the brute force attack       | 64 |  |

| 3.8 | Poten                   | tial applications                               | 67 |  |

| 3.9 | Concl                   | usion                                           | 68 |  |

| Re  | mote                    | Activation of ICs for Piracy Prevention and Dig | -  |  |

| ita | Righ                    | nt Management                                   | 70 |  |

| 4.1 | Introd                  | uction                                          | 70 |  |

| 4.2 | Relate                  | ed Work                                         | 73 |  |

| 4.3 | Remot                   | te IC Activation                                | 74 |  |

| 11  | Attac                   | lro                                             | 77 |  |

| v | i | i |  |

|---|---|---|--|

|   |   |   |  |

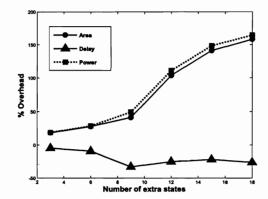

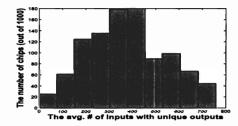

| 4.5.1 Area, delay, and power overheads 4.5.2 Diversity of the keys 4.6 Conclusion  5 Active Control and Digital Rights Management of Integrated Circuit IP Cores 5.1 Introduction 5.2 Related Work 5.3 Flow of the Active Control for IP Cores 5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.5.4 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow |   |     |                                                     |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----------------------------------------------------|-----------|

| 4.5.2 Diversity of the keys 4.6 Conclusion  5 Active Control and Digital Rights Management of Integrated Circuit IP Cores 5.1 Introduction 5.2 Related Work 5.3 Flow of the Active Control for IP Cores 5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow               |   | 4.5 | Experimental results                                | 77        |

| 4.6 Conclusion  5 Active Control and Digital Rights Management of Int grated Circuit IP Cores  5.1 Introduction  5.2 Related Work  5.3 Flow of the Active Control for IP Cores  5.4 IP Control Method  5.4.1 BFSMs  5.4.2 CFSM  5.4.3 PUF  5.5 Implementation  5.5.1 BFSM Implementation  5.5.2 PUF Implementation  5.5.3 CFSM Implementation  5.6 Attacks and Safeguards  5.7 Experimental Results  5.8 Applications  5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding  6.1 Introduction  6.2 Related work  6.3 Flow                         |   |     | 4.5.1 Area, delay, and power overheads              | 77        |

| 5 Active Control and Digital Rights Management of Integrated Circuit IP Cores 5.1 Introduction 5.2 Related Work 5.3 Flow of the Active Control for IP Cores 5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                 |   |     | 4.5.2 Diversity of the keys                         | 79        |

| ### grated Circuit IP Cores  5.1 Introduction  5.2 Related Work  5.3 Flow of the Active Control for IP Cores  5.4 IP Control Method  5.4.1 BFSMs  5.4.2 CFSM  5.4.3 PUF  5.5 Implementation  5.5.1 BFSM Implementation  5.5.2 PUF Implementation  5.5.3 CFSM Implementation  5.6 Attacks and Safeguards  5.7 Experimental Results  5.8 Applications  5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding  6.1 Introduction  6.2 Related work  6.3 Flow                                                                                           |   | 4.6 | Conclusion                                          | 80        |

| 5.1 Introduction 5.2 Related Work 5.3 Flow of the Active Control for IP Cores 5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                         | 5 | Aç  | tive Control and Digital Rights Management of Inte- |           |

| 5.2 Related Work  5.3 Flow of the Active Control for IP Cores  5.4 IP Control Method  5.4.1 BFSMs  5.4.2 CFSM  5.4.3 PUF  5.5 Implementation  5.5.1 BFSM Implementation  5.5.2 PUF Implementations  5.5.3 CFSM Implementation  5.6 Attacks and Safeguards  5.7 Experimental Results  5.8 Applications  5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding  6.1 Introduction  6.2 Related work  6.3 Flow                                                                                                                                         |   | gra | ated Circuit IP Cores                               | 81        |

| 5.3 Flow of the Active Control for IP Cores  5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF  5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                         |   | 5.1 | Introduction                                        | 82        |

| 5.4 IP Control Method 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                        |   | 5.2 | Related Work                                        | 85        |

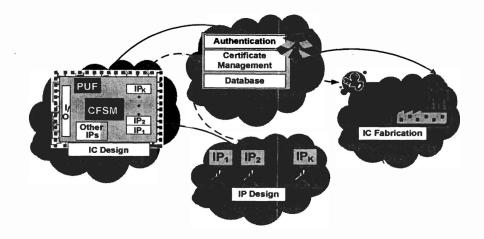

| 5.4.1 BFSMs 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementation 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                              |   | 5.3 | Flow of the Active Control for IP Cores             | 86        |

| 5.4.2 CFSM 5.4.3 PUF 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementations 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                         |   | 5.4 | IP Control Method                                   | 88        |

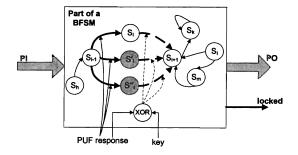

| 5.4.3 PUF  5.5 Implementation  5.5.1 BFSM Implementation  5.5.2 PUF Implementations  5.5.3 CFSM Implementation  5.6 Attacks and Safeguards  5.7 Experimental Results  5.8 Applications  5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding  6.1 Introduction  6.2 Related work  6.3 Flow                                                                                                                                                                                                                                                        |   |     | 5.4.1 BFSMs                                         | 88        |

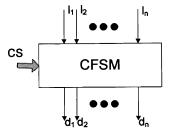

| 5.5 Implementation 5.5.1 BFSM Implementation 5.5.2 PUF Implementations 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                             |   |     | 5.4.2 CFSM                                          | 89        |

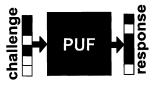

| 5.5.1 BFSM Implementation 5.5.2 PUF Implementations 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                                                 |   |     | 5.4.3 PUF                                           | 90        |

| 5.5.2 PUF Implementations 5.5.3 CFSM Implementation 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                |   | 5.5 | Implementation                                      | 91        |

| 5.5.3 CFSM Implementation  5.6 Attacks and Safeguards  5.7 Experimental Results  5.8 Applications  5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding  6.1 Introduction  6.2 Related work  6.3 Flow                                                                                                                                                                                                                                                                                                                                             |   |     | 5.5.1 BFSM Implementation                           | 91        |

| 5.6 Attacks and Safeguards 5.7 Experimental Results 5.8 Applications 5.9 Conclusion 6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                                                                                                                               |   |     | 5.5.2 PUF Implementations                           | 92        |

| 5.7 Experimental Results 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                         |   |     | 5.5.3 CFSM Implementation                           | 94        |

| 5.8 Applications 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction 6.2 Related work 6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 5.6 | Attacks and Safeguards                              | 94        |

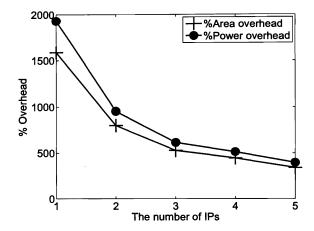

| 5.9 Conclusion  6 N-Version Temperature-Aware Scheduling and Binding 6.1 Introduction  6.2 Related work  6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 5.7 | Experimental Results                                | 96        |

| 6 N-Version Temperature-Aware Scheduling and Binding           6.1 Introduction         6.2 Related work           6.3 Flow         6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 5.8 | Applications                                        | 98        |

| 6.1 Introduction       6.2 Related work         6.2 Flow       6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 5.9 | Conclusion                                          | .00       |

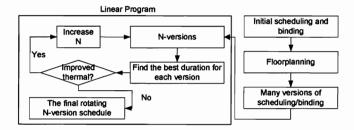

| 6.1 Introduction       6.2 Related work         6.2 Flow       6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 | N-Y | Version Temperature-Aware Scheduling and Binding 10 | <b>)1</b> |

| 6.3 Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     |                                                     | .02       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6.2 | Related work                                        | .03       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6.3 | Flow                                                | .04       |

| or it torbion bonouding / binding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 6.4 |                                                     | .05       |

|   |     | •                           |      |

|---|-----|-----------------------------|------|

|   |     |                             | viii |

|   | 6.5 | Rotational N-version method | 106  |

|   | 6.6 | Experimental evaluations    | 108  |

|   | 6.7 | Conclusion                  | 111  |

| 7 | Co  | nclusion                    | 114  |

|   | 7.1 | Contributions               | 114  |

|   | 7.2 | Future Directions           | 116  |

|   | Bib | oliography                  | 118  |

# Illustrations

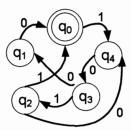

| 1.1 | An example of state space diversity                                    | 3  |

|-----|------------------------------------------------------------------------|----|

| 1.2 | An algorithm and its implementation in hardware                        | 4  |

| 1.3 | An example of spatial diversity.                                       | 5  |

| 1.4 | An example of temporal diversity                                       | 6  |

|     |                                                                        |    |

| 2.1 | A 4-variant Design                                                     | 13 |

| 2.2 | Design of an N-variant circuit                                         | 18 |

| 2.3 | Implementation choice for the experiments                              | 24 |

| 2.4 | Flow of MPEG video compression flow                                    | 25 |

|     |                                                                        |    |

| 3.1 | Example of a STG with five states. The inputs required for             |    |

|     | state-to-state transition are shown next to the edges                  | 35 |

| 3.2 | The global flow of the active hardware metering approach               | 37 |

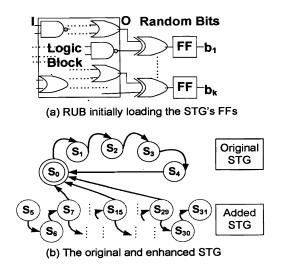

| 3.3 | The boosted FSM (BFSM)                                                 | 43 |

| 3.4 | Illustration of steps for building a sparse 3-bit STG                  | 49 |

| 3.5 | Obfuscation of the original $STG$                                      | 51 |

| 3.6 | Example of a black hole FSM                                            | 55 |

| 3.7 | A simplified SFFSM                                                     | 57 |

| 3.8 | Percentage of (a) power; and (b) area; overheads vs. size after adding |    |

|     | al 5 FFs STG                                                           | 64 |

|     |                                                                        |    |

| 4.1 | FSM with a lock on the replicated state $(S_2)$                        | 72 |

| 4.2 | Close-up of the locking/unlocking mechanism                           | 72  |

|-----|-----------------------------------------------------------------------|-----|

| 4.3 | A non-linear unclonable random unique block                           |     |

| 4.4 | Area, delay, and power overhead for different numbers of extra states |     |

|     | for benchmark s298                                                    | 80  |

| 4.5 | The average number of inputs producing unique output for 1,000        |     |

|     | different RUBs                                                        | 80  |

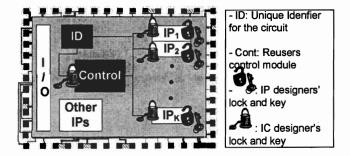

| 5.1 | A reuser's design including multiple IP cores. Each IP may be         |     |

|     | locked/unlocked by the IP designer or the reuser, depending on the    |     |

|     | application                                                           | 84  |

| 5.2 | The flow of the active control for integrated circuits' IP cores      | 87  |

| 5.3 | PUF challenge/response pairs                                          | 90  |

| 5.4 | System block diagram                                                  | 91  |

| 5.5 | Implementation of the BFSM                                            | 91  |

| 5.6 | Implementation of the PUF                                             | 93  |

| 5.7 | Implementation of the CFSM                                            | 94  |

| 5.8 | The change of the overhead with increasing the number of IPs          |     |

|     | sharing the PUF                                                       | 99  |

| 6.1 | Flow of the rotational N-version thermal-aware scheduling and binding | 104 |

# Tables

| 1.1 | List of included published work                                                    | 8   |

|-----|------------------------------------------------------------------------------------|-----|

| 2.1 | Area overhead of the N-variants implementation                                     | 26  |

| 2.2 | Power and delay overheads of the N-variant implementation                          | 27  |

| 2.3 | The overhead for $2^9$ -variants $(m=2)$ , $2^{18}$ -variants $(m=4)$ , and        |     |

|     | $2^{36}$ -variants $(m = 8)$ DCT                                                   | 28  |

| 3.1 | Area overhead of active metering for various benchmarks                            | 62  |

| 3.2 | Delay and power overhead of active metering for various benchmarks.                | 63  |

| 3.3 | Average number of attempts needed for the brute force attack to                    |     |

|     | unlock the added STG                                                               | 65  |

| 3.4 | Percentage of area and power overheads after adding one blackhole                  | 67  |

| 4.1 | Area overhead for adding six extra states for $Random$ and $Heuristic$             |     |

|     | state selection.                                                                   | 78  |

| 4.2 | Delay and power overhead for <i>Random</i> and <i>Heuristic</i> selection methods. | 79  |

| 5.1 | The overhead of BFSM modifications for one IP                                      | 97  |

| 5.2 | CFSM overhead for integration of five IPs                                          | 98  |

| 6.1 | Max temp. improvement (min resources)                                              | 109 |

| 6.2 | Max temp. improvement (add resources)                                              | 110 |

|   | • | • |

|---|---|---|

| v | 1 | 1 |

|   |   |   |

| 6.3 | Area overhead of the N-versions in Table 6.1 | 111 |

|-----|----------------------------------------------|-----|

|     |                                              |     |

## **Abreviations**

- AFSM: Authentication Finite State Machine

- ASIC: Application Specific Integrated Circuit

- BFS: Breadth-First Search

- BFSM: Boosted Finite State Machine

- BLIF: Berkeley Logic Interchange Format

- CA: Certification Authority

- CAR: Capture And Replay

- CDFG: Control DataFlow Graph

- CFSM: Control Finite state Machine

- DAG: Direct Acyclic Graph

- **DFG**: DataFlow Graph

- DRM: Digital Rights Management

- ECC: Error Correction Code

- **FF**: FlipFlop

- **FM**: Flexibility Metric

- FPGA: Field Programmable Gate Array

• FSM: Finite State Machine

• **GD**: Global Diversity

• HLS: High-Level Synthesis

• IC: Integrated Circuit

• **IP:** Intellectual Property

• LD: Local Diversity

• MV: Manufacturing Variability

• NMR: N-Modular Redundancy

• NVP: N-Version Programming

• NVS: N-Version Software

• NVX: N-version eXecution

• PKC: Public Key Cryptography

• PUF: Physically Unclonable Function

• **RB**: Recovery Block

• RFID: Radio-Frequency IDentification

• RTL: Register Transfer Level

• STG: State Transition Graph

# Chapter 1

# Introduction

Lightweight embedded devices have stringent area and power constraints. Such devices need to be portable with long battery life. A designer can consider an ASIC or an FPGA implementation for such devices. The power and area constraints make an ASIC implementation of such devices the natural choice, especially when the mass production of these devices is to be considered. On the other hand, FPGAs can be economical when only a small quantity of the devices is to be manufactured.

Other issues that arise in the design and manufacture of these devices, however, complicate the decision. In many applications, the device would benefit from flexibility that is not available in ASICs derived from conventional designs. For example:

- After manufacturing, the designer might want to tweak the design to improve the performance of an individual chip.

- The designer might also prefer to provide different implementations of the same design that can operate at different points on the energy / performance curve.

- Functionality can be varied (for instance some features can be limited or disabled) depending on the customer who buys the chip.

While an FPGA implementation can easily achieve these goals, it is more difficult to address these points using an ASIC implementation without incurring large overheads. This thesis explores one option to address the problem: embed multiple implementations of the control circuitry in the same design. We call this technique *N-variant hardware design*.

This thesis explores the techniques required to implement N-variant design in a standard ASIC design flow, a necessity if these techniques are to have practical application. It demonstrates how to use N-variant design to achieve two distinct kinds of diversity: state space diversity and schedule diversity. This diversity is useful in its own right, as it allows an ASIC designer to achieve the goals that we laid out earlier. Variants of the control circuitry can be designed to have identical or slightly different functionalities depending on the target application. We can summarize the objectives as follows.

- 1. Using the standard ASIC flow to implement N-variants gives the N-variant methodology all the performance advantages of ASICs.

- 2. Embedding multiple variants of the control circuitry of the design on chip, either by manipulating the state space of the design or by manipulating the schedule of the design, can be used to make the chip more robust and resilient against security attacks.

- 3. The N-variant methodology manipulates the control part of the circuit. Since the control part represents a small fraction of the whole chip (about 1% [1]), the overhead due to the added redundancy is expected to be low.

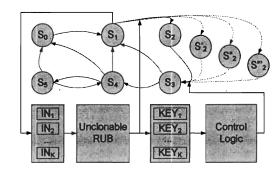

Given the basic tools for N-Variant Design, we can attack more complex design problems. For example, we can use the tools of N-variant design to design ASICs that have chip-specific locks to protect the IC or to protect individual IP cores on the IC. These locks can be used to require a chip specific key that resets the chip's initial state to an operable state, or to check continuously for the presence of a key

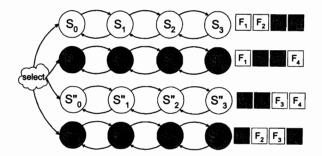

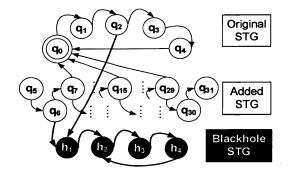

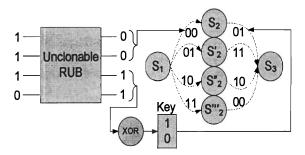

Figure 1.1: An example of state space diversity.

and protect against unauthorized use. These locks exploit individual variation in the ASIC coupled with multiple variant control circuits and circuit obfuscation to create ASICs that require a unique key per manufactured chip to operate. The computation of the key requires both knowledge of the individual chip, obtained from specific test vectors, and knowledge of the obfuscated design, which the designer holds private.

#### 1.1 Thesis

My thesis is that by intelligently embedding different implementations of a part of the design in an IC, one can achieve the flexibility and diversity needed to protect an embedded device or tune its performance while maintaining low overhead and without significantly changing the current design flow.

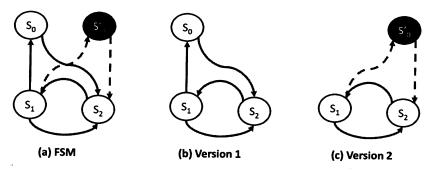

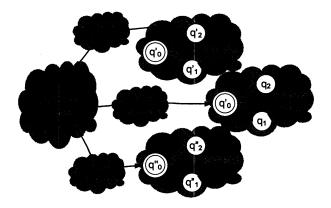

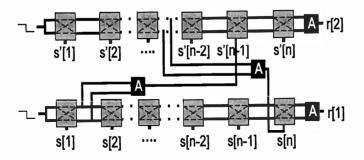

To support this thesis, we propose two different levels of adding diversity to a circuit: state space diversity, and scheduling diversity. State space diversity is achieved by adding states to the finite state machine (FSM) representing the control part of a system. Figure 1.1(a) shows an example of adding state space diversity to an FSM where we make a copy  $S'_0$  (shown in black) of state  $S_0$  and all the transitions to and from it (duplicated transitions are shown as dashed lines). Figures 1.1(b) and (c) show the two different versions of the FSM. In the first version we use states  $S_0$ ,

Figure 1.2: An algorithm and its implementation in hardware.

$S_1$ , and  $S_2$ , and in the second version we use  $S'_0$ ,  $S_1$ , and  $S_2$ . While both versions of the FSM are functionally equivalent,  $S_0$  and  $S'_0$  are represented by different state encodings. Thus, if the designer provides means of checking the state encoding at runtime, and after the initial setting each customer (a chip used) is associated with a version, traversing the edge from  $S_1$  to  $S_0$  or  $S'_0$  can be used to verify the identity of the chip running the design.

Variant FSMs can have different state encodings [2], have different extra FSM parts added to them [3], or differ in a subset of the states and transitions [4]. We show the application of state space diversity to active hardware metering and IP rights protection in [2, 3, 4, 5].

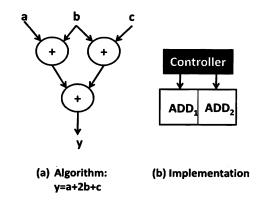

Scheduling diversity is implemented by manipulating the scheduling and binding algorithms used for high-level synthesis of circuits. In high-level synthesis an algorithm is compiled into a hardware circuit by converting it first into a control dataflow graph (CDFG); then scheduling, allocating, and binding the CDFG, and finally, converting the schedule into an FSM representing the controller and a datapath containing the ALUs, memory and communication logic. Figure 1.2(a) shows an example of a CDFG for a simple algorithm that computes y = a + 2b + c. Fig-

Figure 1.3: An example of spatial diversity.

ure 1.2(b) shows the hardware implementation of the algorithm using two hardware adders  $ADD_1$  and  $ADD_2$  and a controller. We manipulate the controller to generate designs with different types of scheduling diversity: spatial and temporal.

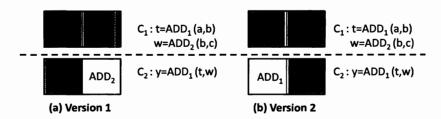

Figure 1.3 shows how we can add spatial diversity to the implementation of the simple algorithm described above. The control steps are shown as  $C_1$  and  $C_2$ . For the first version shown in Figure 1.3(a), the controller uses  $ADD_1$  and  $ADD_2$  to compute the intermediate results t and W respectively. Then it uses  $ADD_1$  in the second control step to compute the final result y. This way  $ADD_2$  is only used in half the control cycles in the first version. In the second version shown in Figure 1.3(b), the controller uses  $ADD_2$  in the second control cycle to compute y. Thus, in the second version  $ADD_1$  is used half the time and we have spatial diversity in the activities of different modules on the chip.

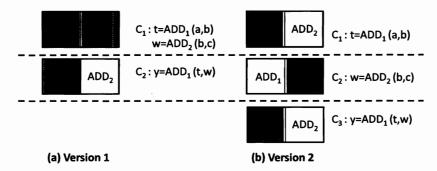

Temporal diversity can be implemented in a similar way as spatial diversity. However, for temporal diversity the controller is manipulated to run at different control steps to generate versions with different delays. Figure 1.4 shows an example for temporal diversity. In the first version shown in Figure 1.4(a), the controller executes the computation of y in two control steps. In the first step it computes t and w, then in the second step it computes the final result y. In the second version shown in Figure 1.4(b), the controller does the computation in three steps. It computes t in the

Figure 1.4: An example of temporal diversity.

first step, w in the second step, and y in the third step. This way, the second version takes an extra control step to compute the result. Temporal diversity can be used in systems that require different deadlines for different tasks. For tasks that have a longer time to execute, one can slow down the system and thus reduce the power consumption by disabling the unused modules. For energy savings, the designer might use the same adder in all three cycles of an operation, thus avoiding any energy cost incurred by enabling and disabling the adders on different cycles. In this scheme, the designer might provide two control FSMs, one that used  $ADD_1$  and the other that used  $ADD_2$ . For heat distribution, the design could cycle between them.

## 1.2 Organization

The rest of this thesis is organized as follows. The use of the N-variant methodology to add state space diversity is presented, along with potential applications, in Chapter 2. That chapter shows a method that automatically replicates the state of a design by duplicating a subset of the logic gates used to implement the design. This method can be applied automatically to any synthesized design that includes an FSM.

Chapters 3 and 4 present two different methods to implement state space diversity. In Chapter 3, we use replication to duplicate states in the controller of a design. The method adds a large number of extra stages to the design by adding extra loops to the original FSM. Manufacturing variability is used in conjunction with state replication to illustrate how to take advantage of state diversity in active hardware metering of ICs. Chapter 4 incorporates state diversity by duplicating a small subset of the states and edges in the design, with remote activation of ICs as an illustrative application.

Chapter 5 shows how to use state diversity to provide a data rights management platform for IP protection.

Chapter 6 illustrates the use of scheduling diversity to control peak temperature of an IC during operation. Finally, Chapter 7 concludes the thesis and suggests future work in this area.

Chapters 2 through 6 have already appeared in print. The content has been reformatted to fit Rice University thesis form, but has not otherwise been changed\*. Table 1.1 shows the proper citations for those chapters, including the collaborators who are co-authors on those papers.

<sup>\*</sup>Because Chapters 2 through 6 reproduce published work, they appear unchanged. A careful reader will note that the overall percentage improvements in those chapters are presented as the average of the improvements. In other areas of Computer Science, these numbers might be computed using the aggregate improvement or the geometric mean.

Table 1.1: List of included published work.

| Chapter   | Citation                                                                 |  |

|-----------|--------------------------------------------------------------------------|--|

| Chapter 2 | Y. Alkabani and F. Koushanfar, N-variant IC design: methodology and      |  |

|           | applications, in Design Automation Conference (DAC), pp. 546-551,        |  |

|           |                                                                          |  |

|           | 2008.                                                                    |  |

| Chapter 3 | Y. Alkabani and F. Koushanfar, Active hardware metering for intellec-    |  |

|           | tual property protection and security, in USENIX Security Symposium,     |  |

|           | pp. 291-306, 2007.                                                       |  |

| Chapter 4 | Y. Alkabani, F. Koushanfar, and M. Potkonjak, Remote activation of       |  |

|           | ics for piracy prevention and digital right management, in IEEE/ACM      |  |

|           | International Conference on Computer Aided Design (ICCAD), pp. 674-      |  |

|           | 677, 2007.                                                               |  |

| Chapter 5 | Y. Alkabani and F. Koushanfar, Y. Alkabani and F. Koushanfar, Active     |  |

|           | control and digital rights management of integrated circuit IP cores, in |  |

|           | ACM/IEEE International Conference on Compilers, Architectures, and       |  |

|           | Synthesis for Embedded Systems (CASES), pp. 227-234, 2008.               |  |

| Chapter 6 | Y. Alkabani, F. Koushanfar, and M. Potkonjak, N-version temperature-     |  |

|           | aware scheduling and binding, in International Symposium on Low          |  |

|           | Power Electronics and Designs (ISLPED), pp. 331-334, 2009.               |  |

# Chapter 2

# N-Variant IC Design: Methodology and Applications\*

#### Abstract

We propose the first method for designing *N-variant* sequential circuits. The flexibility provided by the N-variants enables a number of important tasks, including IP protection, IP metering, security, design optimization, self-adaptation and faulttolerance. The method is based on extending the finite state machine (FSM) of the design to include multiple variants of the same design specification. The state transitions are managed by added signals that may come from various triggers depending on the target application. We devise an algorithm for implementing the N-variant IC design. We discuss the necessary manipulations of the added signals that would facilitate the various tasks. The key advantage to integrating the heterogeneity in the functional specification of the design is that we can configure the variant during or post-manufacturing, but removal, extraction or deletion of the variants is not viable. Experimental results on benchmark circuits demonstrate that the method can be automatically and efficiently implemented. Because of its lightweight, N-variant design is particularly well-suited for securing embedded systems. As a proof-of-concept, we implement the N-variant method for protection of content of portable media players, e.g., iPod. We discuss how N-variant design methodology readily enables new digital

<sup>\*</sup>This work is published in: Y. Alkabani and F. Koushanfar, N-variant IC design: methodology and applications, in Design Automation Conference (DAC), pp. 546-551, 2008.

rights management methods.

#### 2.1 Introduction

N-variant design is the generation of  $N \geq 2$  realizations of the same initial design description. The advantage of the technique is that it provides improved flexibility, robustness, attack resiliency, and design diversity. The strength and usefulness of N-variant designs was previously demonstrated for programs [6], virtual machines [7], and for achieving architectural heterogeneity [7]. While the method was initially intended for providing fault-tolerance, recent applications in security of computer systems, software and data has amplified its importance. Many attacks that take advantage of the specific and stationary nature of the underlying platform, may be eliminated by using N-variants [7, 6].

We propose the first methodology for designing N-variant ICs. The method works at the functional specification level, or by scripts that automatically perform presynthesis alterations. We construct a single hardware design consisting of multiple variants that are planned to have several exploitation sets. Note that it is also possible to do N-variant design post-synthesis. The drawback is that the design would become vulnerable to removal attacks. The advantage of pre-synthesis alternation is that all of the variants become an integral part of the functionality pertinent design, making the removal attack detrimental to the whole structure.

N-variant IC design has a number of important applications.

- (i) Hardware IP protection and digital rights management: New semiconductor business models can be enabled by the N-variant design, e.g., different versions of one design can be sold to various vendors, enabling an automatic way to trace the ICs.

- (ii) Usage and content metering: Alternation of the variants can be used for enumer-

ating the usage of IC components that run software/ media files, or in conjunction with unclonable chip IDs for metering the usage of an ICs.

- (iii) Security: There is a need to prevent the exploits that target a homogeneous design from working on all the ICs [7]. Selection of different variants provides an effective countermeasure against the attacks.

- (iv) Post-silicon optimization: Because of the manufacturing variability, for each IC, the designer can use the testing results to select the variant that has the best power/delay characteristics.

- (v) Self-adaptation: Due to the impact of variability in operational conditions, e.g., aging, the IC can be designed such that it can adapt its structure over time.

- (vi) fault-tolerance: The inherent redundancy provided by N-variants enables fault-tolerance.

Integration of N-variants at the functional level is done by altering the FSM and adding several states to it. By managing (controlling) the inputs to state-transitions, one would be able to select different variants of the design. The management inputs may come from various triggers, that depend on the target task for the N-variant design. We discuss in detail how the management may be altered for the various applications that we are considering.

The key advantage of using FSM is that it is not extractable from the synthesized design. Thus, even for a party who has access to the synthesized hardware IP, changing the FSM or extracting the original single-variant design would need an effort equivalent to redoing all the stages of design and implementation. For our purposes, the FSM can be safely assumed *inextricable*. Another important benefit of FSM is that certain aspects of FSM are inexpensively *verifiable* post-silicon. The inextricability and verifiability properties of the FSM were previously used for water-

marking and for hiding information inside the design, and for remote activation and disabling [8, 9, 4]. As it was shown in the context of watermarking and IC activation/disabling, careful constraint manipulation and don't care planning can greatly reduce the overhead of FSM modifications. The new method is particularly well-suited for lightweight embedded systems applications. This is because the N-variant design enables lightweight mechanisms for protection and security of IP, software and content. The overhead of implementing traditional cryptographic protocols is huge, often overwhelming the constrained resources of an embedded system [10]. As a proof-of-concept, we demonstrate application of N-variant IC design for content usage metering of portable multimedia devices with an embedded MPEG compression module.

#### 2.1.1 Motivational example

Figure 2.1 illustrates a motivational example, where the FSM of the design is shown by a state transition graph (STG) that has four states:  $s_0, s_1, s_2$ , and  $s_3$ . This FSM is the first variant. We replicate this design three times to have:  $s'_1, s'_2, s'_3$ , and  $s'_4$  as the first copy (the second variant),  $s''_1, s''_2, s''_3$ , and  $s''_4$  as the second copy (the third variant), and  $s'''_1, s'''_2, s'''_3$ , and  $s'''_4$  as the third copy (the fourth variant). Thus, we construct a 4-variant circuit. The different copies can share FFs at the synthesis step to reduce the overhead. By careful state assignment, one can ensure that the FFs needed for each variant to function properly are different in at least one FF. This way, even if a FF is corrupted, there are still other copies that can function properly. In Figure 2.1, we show an example of how the FFs can be shared between the different variants. Assume that we implement the design using 4 FFs. The four FFs denoted by  $F_1, F_2, F_3$ , and  $F_4$  are shown in front of each variant. The FFs in white affect

the functionality of the variant, while the FFs in gray do not affect the functionality of the variant (although they can keep flipping all the time for obfuscation reasons depending on the application). For instance, the first variant can use  $F_1$ , and  $F_2$  shown in white, while  $F_3$ , and  $F_4$  do not affect its functionality. However, the second variant is affected by  $F_1$  and  $F_4$ . Thus, if  $F_2$  is corrupted, the first variant will not function properly, but the second will. For the circuit to properly function, it is enough to have one correctly functional variant selected. However, depending on the application, we can choose to switch between different variants, or to prefer a variant over the other based on their performances. Thus, the selection function shown in Figure 2.1 is application dependent as discussed in Section 2.4.

Figure 2.1: A 4-variant Design

#### 2.1.2 Paper organization

In the next section, we discuss the background and related work along the lines of FSM and the N-variant concept. In Section 2.3 we devise an algorithm for efficient integration of the N-variants. Section 2.4 demonstrates how the variant selection inputs can be managed to facilitate various applications. Experimental results evaluating

the overhead of the method on standard benchmarks are presented in Section 6.6. The proof-of-concept implementation for metering multimedia files is also reported. Section 6.7 concludes the paper and outlines a number of future research directions.

#### 2.2 Background

We describe the background and related literature in FSM and N-variant systems that has influenced and inspired our work.

#### 2.2.1 FSM

A FSM is a dynamic discrete system with limited number of states that maps input sequences into output sequences. It can be used to represent a sequential function, e.g., sequential circuits. A FSM is typically defined by a 6-tuple  $M=(\Sigma,\Delta,Q,q_0,\delta,\lambda)$ , where

- $\Sigma \neq \emptyset$  is a finite set of input alphabets;

- $\Delta \neq \emptyset$  is a finite set of output alphabets;

- $Q=\{q_0,q_1,\dots\}\neq\emptyset$  is a bounded set of states;

- $q_0 \subset Q$  is the set of initial states;

- $\delta$  (q, a) is transition function on input a and set  $Q \times \Sigma \to Q$ ;

- $\lambda$  (q, a) is output function for input a and set  $Q \times \Sigma \to \Delta$ ;

The STG is used to represent the state transitions and input/output relations of the FSM; nodes correspond to states and edges define the input/output conditions for state transitions.

FSMs are used for information hiding and watermarking purposes. Oliveira proposes to alter the STG such that a signature is mapped to a spacial topological property in the sequence of states traversed by a sequence of inputs [8]. Yuan and Qu

exploit the existence of redundant transitions and manipulate them to hide information inside the FSM without altering the minimized FSM [9]. Alkabani et al. use a combination of physically unclonable functions and state replication to uniquely lock each IC [4]. The lock is interleaved with combinational and sequential transitions and can be used for enabling/disabling of the IC. The unlocking is done by sequence of inputs that can only be generated by knowing the FSM structure.

The classic way for fault-tolerance FSM design is triple modular redundancy (TMR), where three copies of FSM are concurrently run and the correct output value is determined by voting [11]. Even though TMR may be viewed as a basic N-variant design method, we emphasize that the new N-variant methodology is not a simple replication of the FSMs. Instead, the variants are elegantly interwind within the original design. N-variant design has applications that TMR or other traditional fault-tolerant design methods do not support.

Our N-variant design algorithm is devised to have a low-overhead. A class of methods that is relevant to our work is state assignment and state minimization of large FSM networks [12, 13, 14, 15, 16]. The concepts and methods used in FSM minimization may help to even lower the overhead of N-variant designs in the future.

#### 2.2.2 N-variant method

N-version software development was introduced as early as 1968 [17]. The goal was to achieve fault-tolerance [18, 19]. N-versioning collects N copies of the target software written by different programmers and then runs them in parallel, using the redundancy in the results to achieve fault-tolerance. N-versioning is different from N-variant since N-variant systems include multiple copies within the same design that appear different. So far, the main usage of N-variants has been for security purposes [7, 6].

The motivating idea is that most systems are homogeneous and the same exploit can attack all instances of the system. The specific machine-level characteristics of the attacked computer is used by the binary exploits, e.g, byte order, calling conventions, program load addresses, etc. If the system is not exactly the same, the exploit would not be able to adjust itself and the attack will be halted.

Achieving a heterogeneous computer system by using randomization was first introduced by Forrest et al [20]. Cox et al. present an architectural framework that systematically uses automated diversity that provides detection and disruption of a large class of attacks [6]. Holland et al. extended the idea of achieving heterogeneity by generating the architecture-dependent parts of kernel and standard C library from machine description [7]. Their approach successfully suppresses the risks of code injection attacks and state corruption attacks.

As we have mentioned in Section 2.1, N-variant IC design can enable many more tasks than just security and attack resiliency. Perhaps the most interesting applications are in the domain of IP protection and enabling new business models, and for post-silicon optimization and self-adaptations of the ICs. Furthermore, because the N-variants are embedded into the hardware, the overhead is smaller than embedding them into the virtual machine and/or the architecture. The low overhead of the N-variant IC renders it suitable for embedded systems applications.

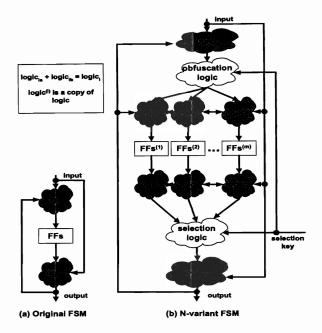

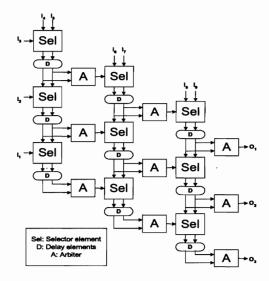

## 2.3 N-variant IC design

In this section we discuss how the N-variant circuit can be designed. Figure 2.2 demonstrates the flow of our design. The implementation steps can be summarized as follows:

1. A single copy of the FSM is implemented as a group of FFs connected to the

input and output through combinational circuits  $logic_1$  and  $logic_2$  respectively, as shown in Figure 2.2(a).

- 2. Modify the FSM as shown in Figure 2.2(b) as follows:

- (a) Select the parameter m representing the number of replications of the FFs in the circuit.

- (b) Partition  $logic_1$  into  $logic_{1a}$  and  $logic_{1b}$  and replicate  $logic_{1a}$  for m times.

- (c) Partition  $logic_2$  into  $logic_{2a}$  and  $logic_{2b}$  and replicate  $logic_{1a}$  for m times.

- (d) Design the obfuscation logic and the selection logic to maintain the correct circuit's functionality. The obfuscation logic is implemented at the input side and is used to distinguish between different variants, and to generate dummy values in the unused FFs. The selection logic is used at the output side to select the output of the target variant. Note that when a variant is not selected it does not have to generate correct outputs.

Selection of the number of replications and the way the combinational circuits are partitioned yield the state-space of all possible implementations. Each choice requires a minimal complexity of the obfuscation and selection logics. It is worth noting here that the choice is also affected by the application targeted by the N-variant design method.

It is clear that the overhead of the implementation varies greatly with the choice of m, the partitioning of the combinational circuit, and the complexity of both the obfuscation and selection logic blocks. The area and power overheads of the methods are affected mainly by m, and by the partitioning of the combinational circuits. The delay is only affected by the selection and obfuscation logic. At one extreme, one can set m = N,  $logic_{ia} = logic_i$ , and  $logic_{ib} = \emptyset$ , while implementing the selection logic as

Figure 2.2: Design of an N-variant circuit.

a multiplexer and discarding the obfuscation logic. This configuration produces the highest area and power overheads, and the lowest delay. At the other extreme, one can set m = 1,  $logic_{ia} = \emptyset$ ,  $logic_{ib} = logic_i$ . This leads to an obfuscated circuit, and produces the lowest area and power overheads, and the highest delays. The potential impact of each of the possible design parameters is as follows.

- FFs. The FFs represent the memory of the FSM, they can be replicated m times where  $m \geq 1$ ; m = 1 means the FFs are all shared and this removes a big part of redundancy in our implementation. However, the method can still have multiple variants by manipulating the logic blocks.

- $Logic_1$ . This circuit component represents the combinational part of the circuit at the input side. It is divided into two parts:  $logic_{1a}$  and  $logic_{1b}$ .  $Logic_{1a}$  is to be replicated m times, and  $logic_{1b}$  is shared. Increasing the size of  $logic_{1a}$  leads to larger

area and power overheads. However, it does not affect the delay overhead. Despite the introduction of more area and power overheads, it can be useful for applications with timing constraint.

- $Logic_2$ . This circuit represents the combinational part of the circuit at the output of the FFs. It is divided into two parts:  $logic_{2a}$  and  $logic_{2b}$ .  $Logic_{2a}$  is to be replicated m times, and  $logic_{2b}$  is shared. Just like the case in  $logic_{1a}$ , increasing the size of  $logic_{2a}$  leads to larger area and power overheads and can be useful for applications targeting performance improvement and fault-tolerance.

- Obfuscation logic. The obfuscation is used to adjust the inputs for different variants. The more FFs are shared between variants, the more complex this part will be. However, in cases where few FFs are shared, this part is used to generate dummy values in the unused FFs. This can be useful for security applications.

- Selection logic. This block is responsible for ensuring that the correct output from the target variant is selected. In case of many FF replications, it can be simply implemented as a multiplexer. However, as the number of shared FFs increases, it becomes increasingly important to interleave this block with the obfuscation logic to guarantee that the correct outputs are obtained regardless of the selected variant.

The nature of the original circuit also affects the significance of the overhead. For instance, if the combinational logic is very small in area, power, and delay, even the slightest replications and the simplest obfuscation and selection logic will yield a significant overhead compared to the original one. Note that the area and power overhead of an FSM (representing the control part of a system) is extremely small compared to the overall area and power overhead of the system.

# 2.4 Application-specific management of the N-variants

In this section, we describe a number of management methods that can enable each of the applications described in Section 2.1. The variant selection contains the following components and structures: • Trigger. A trigger prompts selection of a new variant. It may come from various sources, including the clock signals, an internal counter, a sequence of inputs, or an external signal.

- Storage. The memory can be used in case selection of a variant is dictated by a stored key, or in case a counter should save its state in presence of rests. Also, many binary attacks may exploit a fixed memory address. To defend against this attack, all or some parts of the memory needs to by duplicated.

- *Driver*. The driver uploads the new variant in case a trigger is activated. A driver may be as simple as a multiplexer uploading the variant selection key from a stored location, or it may be a driver FSM, e.g., an obfuscated counter.

The above components can be used in various ways to manage the variant selection suited for a particular application. A few examples are as follows.

- (i) Hardware IP protection and digital rights management. An IC vendor could configure its chips by using a fixed key specific to each customer. This provides a new mechanism to trace back the ICs in the supply chain. Also, many existing hardware IP protection methods can be readily used in N-variant settings. For example, the sequence of traversal among a few variants or within a variant could be utilized as a watermark or for hiding information [8, 9]. As another example, the N-variant structure could be integrated with the unique random number generated on each chip, for fingerprinting or locking the state transitions by the manufacturer [4].

- (ii) Usage and content metering. The N-variants can be used to enforce licensing

agreement for the hardware, software, or content usage. Once the license agreement term is over, the IC would enter a nonfunctional state. The IP rights owner is the only entity that can load a new functional variant if a new license is obtained. A trigger by a clock or an internal counter can be used to save the number of uses or the time constraints. In case a counter is used, the states should be saved in an on-chip nonvolatile memory so the chip's reset would not affect the usage metering. Similar triggers were used for licensing of FPGA IPs [21], where it was noted that the trigger is vulnerable to memory reset/clock reset attacks. One possible countermeasure against this attack is to randomize the counter, so that resetting to zero would not traverse to the zero usage state. Many other counter obfuscation methods are possible. For example, one may initialize the counter by using a PUF, so different configurations will be needed depending on the unique IDs of each chip.

- (iii) Security. The system could be made heterogeneous by frequently alternating the FSM variant [7]. For example, in case of exploits that use a fixed memory address, the memory can be duplicated creating a master and a slave copy. Every time a new variant is selected, the master and the slave copies would switch. The slave would copy its content from the master. If an attack exploits an address on the master copy, it would halt once the master copy is altered.

- (iv) Post-silicon optimization. Because of the variability in CMOS technology, the variant with the best power or delay performance would be different on each IC. A spectrum of new post-manufacturing optimizations can be enabled by using the test data to determine the variant that has the best performance on each IC. For example, one may design the chips to have the maximum possible frequency, by selecting low feature sizes for the gates. Due to variability, some of the delays would be longer than planned, slowing down a few critical paths.

(v) Self-adaptation. The variants could be strategically uploaded using an offline or online monitoring method that manages the upload based on a certain target. For example, to be resilient against aging, one can equalize the amount of usage of the various components. Offline simulation of randomly selected variants can determine which components are used more in one variant. The variants with the largest difference in their usage patterns may be periodically loaded to equalize the aging effect. (vi) fault-tolerance. The flexibility and redundancy of the N-variant design can be utilized for providing fault-tolerance. For example, if a FF is shown to be faulty during the test phase, the configurations that do not use this FF will be uploaded. The fault-tolerance can be implemented in more sophisticated ways, by adding a monitoring mechanism. As an example, a BIST structure can be included which periodically tests the circuit for faults due to aging, NBTI, or HCI effects. The correct variants could be managed accordingly.

# 2.5 Experimental results

In this section, we implement the N-variant method described in section 2.3 on benchmark designs and evaluate its performance. A program is written in C to generate N-variants for each design. The Berkeley SIS tool is used to simulate the results and to estimate the overhead. In the first subsection, we show the experimental results for applying the method on standard MCNC'91 benchmarks. In the second subsection, we demonstrate a DCT example as a proof-of-concept for applying the method to embedded multimedia applications. All the resulting circuits are mapped to the MCNC library.

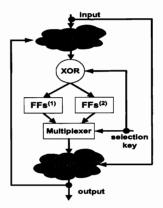

### 2.5.1 Implementation of the N-variant method

Figure 2.3 shows an implementation of the N-variant method for m=2. Our design targets embedding at least one redundant component for each part, while maintaining low area, power, and delay overheads. We present the results for m=2 and m=4 that translate to doubling and quadrupling the number of FFs respectively. The obfuscation logic is implemented as a block of XOR gates that place different values in the unused FFs for each variant. The selection logic is implemented as a multiplexer block. The number of variants generated by this implementation for a circuit with k FFs is  $2^k$  for m=2, and is  $4^k$  for m=4. Our selection of each parameter of the N-variant design (see Section 2.3) and the impact of the choice on the target applications are as follows:

- FFs. We selected m=2 and m=4. Selecting m=2 ensures that the scheme has at least one spare FF for each variant; m=4 provides more redundancy.

- $Logic_1$ . We selected  $Logic_{1a} = \emptyset$ , and  $logic_{1b} = logic_1$ . The choices are made to reduce the area and power overheads. However, fault-tolerance and post-silicon optimization are now only dependent on FF redundancies.

- $Logic_2$ . We devised the following parameters:  $Logic_{2a} = \emptyset$ , and  $logic_{2b} = logic_2$ . The selection is made to reduce the area and to reduce the delay and power overhead. Again, fault-tolerance and post-silicon optimization are only dependent on FFs.

- Obfuscation logic. For m=2 and m=4, only a half, or a quarter of the FFs are shared respectively. We select the obfuscation function to be a block of XOR gates that generate dummy values in the unused FFs. We limit the maximum number of variants to be  $2^k$  (for m=2) and  $4^k$  (for m=4) to keep the function simple and to constrain the delay overhead. Note that some of the variants can be reserved as trap

non-functional FSMs for security and IP protection applications.

• Selection logic. This part is implemented as a multiplexer and is kept simple to avoid large delay overheads.

Note that the parameter choices used in one implementation are driven by the designer's target application. The real results may be affected by many factors such as the original shape of the circuit, the gate library used, and different optimizations done on the circuit after modification.

Figure 2.3: Implementation choice for the experiments.

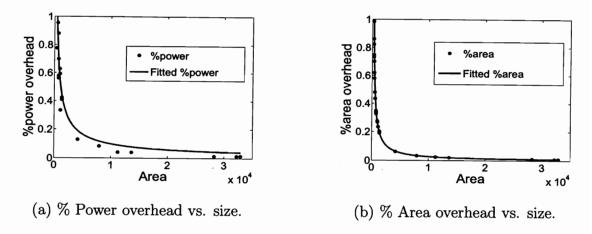

Tables 6.3 and 2.2 show the respective area, power, and delay overheads for m=2 and m=4. The evaluations on the used benchmarks show a maximum area and power overheads of 20% and 19% respectively, while the delay overhead was at most 17% for m=2. The area and power overhead for m=4 goes up to 48% and 62%, and the maximum delay overhead is 21%. It should be noted that the benchmarks with the highest overhead are very small. It is also interesting to note that sometimes the overhead is negative (the circuit is improved) because the resulting circuit maps to fewer gates in the MCNC library. The average area overhead is -0.65% and 12% for m=2 and m=4. The average power overhead increased from -3% for m=2 to 15%

when m=4. As expected the average delay overhead did not change by increasing m; it remained 10% in both cases for the evaluated benchmarks. All modifications to the circuits are done on the netlist before mapping. The relative values are more important than the absolute values as the values in the library can be scaled down.

It is worth noting here that the delay overhead is the only important metric in real designs. This is because the FSM which constitutes the control part of the design is typically only a small part of the design, significantly less than 1% of the power/area [1]. Thus, even if the FSM's area or power is doubled, it will not significantly affect the overall design.

#### 2.5.2 Embedded multimedia application

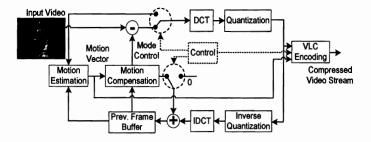

Figure 2.4: Flow of MPEG video compression flow.

We report the results of implementing the N-variant method for content usage metering for embedded multimedia applications. The key observation that facilitates ultra-low overhead implementation is that the N-variants do not need to be instrumented in all parts of the design; only the critical parts of the design can be strategically selected and augmented. In our multimedia example, we implement N-

|                 | Original |    |     | <b>m</b> =2 |      | m=4   |      |       |

|-----------------|----------|----|-----|-------------|------|-------|------|-------|

| BM              | PΙ       | РО | FFs | Area        | Area | %     | Area | %     |

| <b>d</b> k16    | 2        | 3  | 5   | 461         | 482  | 4.6   | 535  | 16.1  |

| <b>k</b> eyb    | 7        | 2  | 5   | 461         | 490  | 6.3   | 535  | 16.1  |

| planet          | 7        | 19 | 6   | 887         | 914  | 3.0   | 975  | 9.9   |

| planet1         | 7        | 19 | 6   | 887         | 914  | 3.0   | 975  | 9.9   |

| pma             | 8        | 8  | 5   | 346         | 382  | 10.4  | 419  | 21.1  |

| s1488           | 8        | 19 | 6   | 880         | 915  | 4.0   | 973  | 10.6  |

| s208            | 11       | 2  | 5   | 148         | 178  | 20.3  | 219  | 48.0  |

| s420            | 19       | 2  | 5   | 148         | 151  | 2.0   | 191  | 29.1  |

| s820            | 18       | 19 | 5   | 429         | 256  | -40.3 | 296  | -31.0 |

| s832            | 18       | 19 | 5   | 427         | 271  | -36.5 | 316  | -26.0 |

| styr            | 9        | 10 | 5   | 633         | 662  | 4.6   | 716  | 13.1  |

| $\mathbf{t}$ ma | 7        | 6  | 5   | 287         | 318  | 10.8  | 362  | 26.1  |

Table 2.1: Area overhead of the N-variants implementation.

variants in the DCT part of the design, the essential component for audio, image, and video signal processing. Figure 2.4 shows a typical MPEG video compression flow which contains both DCT and IDCT components.

Table 2.3 shows the results for applying the implementation described above to the DCT control circuit. The original DCT circuit has 9 FFs. We evaluated N-variant implementations with  $2^9$ -variants (m = 2),  $2^{18}$ -variants (m = 4), and  $2^{36}$ -variants (m = 8). The area, power, and delay overheads for m = 2 are 6%, 5% and 15.5%, respectively. Changing m and keeping the obfuscation and selection logic the

|         | Orig   | ginal | <b>m</b> =2 |       |       |      | m=4    |       |       |      |

|---------|--------|-------|-------------|-------|-------|------|--------|-------|-------|------|

| BM      | Power  | Delay | Power       | %     | Delay | %    | Power  | %     | Delay | %    |

| dk16    | 1649.8 | 97.7  | 1712        | 3.8   | 106.6 | 9.1  | 1935.1 | 17.3  | 107.6 | 10.1 |

| keyb    | 1546.5 | 61.5  | 1635.5      | 5.8   | 67.6  | 9.9  | 1837.3 | 18.8  | 68.4  | 11.2 |

| planet  | 3103.5 | 187.9 | 3156        | 1.7   | 219.4 | 16.8 | 3471.1 | 11.8  | 195.6 | 4.1  |

| planet1 | 3103.5 | 187.9 | 3156        | 1.7   | 219.4 | 16.8 | 3471.1 | 11.8  | 195.6 | 4.1  |

| pma     | 1250.3 | 61    | 1309.8      | 4.8   | 67.9  | 11.3 | 1550.4 | 24.0  | 73.4  | 20.3 |