THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Symbolic Supervisory Control of Resource Allocation Systems

ZHENNAN FEI

Department of Signals and Systems CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2014 Symbolic Supervisory Control of Resource Allocation Systems ZHENNAN FEI ISBN 978-91-7597-007-3

© ZHENNAN FEI, 2014.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie nr 3688 ISSN 0346-718X

Department of Signals and Systems Chalmers University of Technology SE-412 96 Göteborg Sweden Telephone + 46 (0)31 - 772 1000

Typeset by the author using  ${\rm I\!AT}_{\rm E}\!{\rm X}.$

Chalmers Reproservice Göteborg, Sweden 2014

To my family

# Abstract

Supervisory control theory (SCT) is a formal model-based methodology for verification and synthesis of supervisors for discrete event systems (DES). The main goal is to guarantee that the closed-loop system fulfills given specifications. SCT has great promise to assist engineers with the generation of reliable control functions. This is, for instance, beneficial to manufacturing systems where both products and production equipment might change frequently.

The industrial acceptance of SCT, however, has been limited for at least two reasons: (i) the analysis of DES involves an intrinsic difficulty known as the statespace explosion problem, which makes the explicit enumeration of enormous statespaces for industrial systems intractable; (ii) the synthesized supervisor, represented as a deterministic finite automaton (FA) or an extended finite automaton (EFA), is not straightforward to implement in an industrial controller.

In this thesis, to address the aforementioned issues, we study the modeling, synthesis and supervisor representation of DES using binary decision diagrams (BDDs), a compact data structure for representing DES models symbolically. We propose different kinds of BDD-based algorithms for exploring the symbolically represented statespaces in an effort to improve the abilities of existing supervisor synthesis approaches to handle large-scale DES and represent the obtained supervisors appropriately.

Following this spirit, we bring the efficiencies of BDD into a particular DES application domain – deadlock avoidance for resource allocation systems (RAS) – a problem that arises in many technological systems including flexible manufacturing systems and multi-threaded software. We propose a framework for the effective and computationally efficient development of the maximally permissive deadlock avoidance policy (DAP) for various RAS classes. Besides the employment of symbolic computation, special structural properties that are possessed by RAS are utilized by the symbolic algorithms to gain additional efficiencies in the computation of the sought DAP. Furthermore, to bridge the gap between the BDD-based representation of the target DAP and its actual industrial realization, we extend this work by introducing a procedure that generates a set of "guard" predicates to represent the resulting DAP.

The work presented in this thesis has been implemented in the SCT tool Supremica. Computational benchmarks have manifested the superiority of the proposed algorithms with respect to the previously published results. Hence, the work holds a strong potential for providing robust, practical and efficient solutions to a broad range of supervisory control and deadlock avoidance problems that are experienced in the considered DES application domain.

# Acknowledgments

I didn't have time to write a short letter, so I wrote a long one instead. – Samuel Langhorne Clemens (Mark Twain)

In retrospect, coming to study at Chalmers and pursuing PhD in the Automation research group are probably the best decisions I've ever made. Without them, I would never have come cross a lovely girl who later became my wife; I wouldn't have met these good friends who brought me unforgettable joy. Moreover, I wouldn't have had this opportunity to express my deep gratitude to many individuals below who helped me one way or the other in this thesis.

The foremost to mention among others, of course, is my supervisor Prof. Knut Åkesson. I am grateful to him for his guidance, caring, patience, ideas and supervision through the course of my PhD studies. Knut is not just my advisor on research, but also my mentor on my career and many aspects beyond.

I have had the greatest pleasure of being co-supervised by Prof. Spyros Reveliotis from Georgia Tech. I would like to thank him for his excellent guideline and invaluable feedback on the thesis. My deepest appreciation also goes to Prof. Bengt Lennartson for his continuous encouragement and support, and Prof. Martin Fabian for always letting his door open for all kinds of discussions about research and life.

Martin, Knut and Spyros have proofread almost every word of this thesis to make sure that all the pieces are put in the right places with the right sides up. I am very grateful for that.

All of my colleagues at the division of Automatic Control, Automation and Mechatronics deserve a word of appreciation. My special thanks go to the "DK" members in the Automation research group. They are (in alphabetic order): Amir, Daniel, Kristofer, Maziar, Mohammad, Mona, Nina, Oscar, Patrik, Petter, Sahar, Sathya. Also, I wish to express my deep appreciation to Sajed for the inspiring discussions and the sharing moments we have had while visiting Georgia Tech in 2012. Moreover, I would like to acknowledge all the administration staff, with special thanks to Lars, Madeleine, Natasha, Christine and Ingemar.

My life would have been dull if it were not the great friends I met here at Göteborg. I wish to thank Meiling, Jan-Erik, Xiangrui, Xiaolu, Songhe, Binru, Bo, Tong, Jun, Wei, Wanlu, Jingya, Gongpei, Xiaoming, Xinlin, Yutao, Yinan, Yujiao, Li, Yixiao, Xiaosong, Xiaodong, Xuezhi and many others, for all the good times we enjoyed together. I am also indebted to my best friends in China (6385.71 km away), Zhiqiang, Junlong, Xiaoping, Tong, Chao and Wei for always believing in me and backing me

### Acknowledgments

up there.

Finally, I would like to extend my deepest gratitude to my parents and grandma for their never-ending source of love, belief, and encouragement. Last, but certainly not least, my most generous love goes to my wife, Xuan. Words cannot express how grateful I am to you for accompanying me through these years. If I didn't have you, my life would be null. I would be a binary decision diagram without the one-terminal.

Zhennan Fei Göteborg, May 2014

This work was carried out within the Wingquist Laboratory VINN Excellence Centre at Chalmers University of Technology. It was supported by the Vinnova/FFI project "Virtual commissioning of manufacturing systems including PLC logic".

# List of Publications

This thesis is based on the following appended papers:

- Paper 1 Zhennan Fei, Sajed Miremadi, Knut Åkesson, Bengt Lennartson. Symbolic State-Space Exploration and Guard Generation in Supervisory Control Theory. Agents and Artificial Intelligence – Communications in Computer and Information Science, by Joaquim Filipe and Ana Fred (eds), Springer, vol. 271, pp. 161–175, 2013.

- Paper 2 Zhennan Fei, Sajed Miremadi, Knut Åkesson, Bengt Lennartson. Efficient Symbolic Supervisor Synthesis for Extended Finite Automata. IEEE Transactions on Control Systems Technology, in press, 2014.

- Paper 3 Zhennan Fei, Spyros Reveliotis, Sajed Miremadi, Knut Åkesson. A BDD-Based Approach for Designing Maximally Permissive Deadlock Avoidance Policies for Complex Resource Allocation Systems. Submitted for a possible journal publication (under review), 2014.

- Paper 4 Zhennan Fei, Spyros Reveliotis, Knut Åkesson. Symbolic Computation of Boundary Unsafe States in Complex Resource Allocation Systems using Partitioning Techniques. Submitted for a possible journal publication (under review), 2014.

- Paper 5 Zhennan Fei, Knut Åkesson, Spyros Reveliotis. Symbolic Computation and Representation of Deadlock Avoidance Policies for Complex Resource Allocation Systems with Application to Multithreaded Software. Submitted to the 53rd IEEE Conference on Decision and Control (CDC), 2014.

### Other publications

The following publications, authored or co-authored by the author of this thesis, are relevant but not included in the thesis:

Martin Fabian, Zhennan Fei, Sajed Miremadi, Bengt Lennartson and Knut Åkesson. Supervisory Control of Manufacturing Systems using Extended Finite Automata. Formal Methods in Manufacturing, by J. Campos, C. Seatzu and X. Xie (eds), CRC Press / Taylor and Francis, pp. 295–314, 2014. LIST OF PUBLICATIONS

- Sajed Miremadi, Zhennan Fei, Knut Åkesson, Bengt Lennartson. Symbolic Representation and Computation of Timed Discrete Event Systems. IEEE Transactions on Automation Science and Engineering, vol. 11, no. 1, pp. 6–19, 2014.

- Sajed Miremadi, **Zhennan Fei**, Knut Åkesson, Bengt Lennartson. *Symbolic Supervisory Control of Timed Discrete Event Systems*. IEEE Transactions on Control Systems Technology, conditionally accepted, 2014.

- Bengt Lennartson, Francesco Basile, Sajed Miremadi, Zhennan Fei, Mona Noori Hosseini, Martin Fabian, Knut Åkesson. Supervisory Control for State-Vector Transition Models-A Unified Approach. IEEE Transactions on Automation Science and Engineering, vol. 11, no. 1, pp. 33–47, 2014.

- Zhennan Fei, Spyros Reveliotis, Knut Åkesson. A Symbolic Approach for Maximally Permissive Deadlock Avoidance in Complex Resource Allocation Systems. Proceedings of the 12th IFAC - IEEE International Workshop on Discrete Event Systems (WODES), 2014.

- Zhennan Fei, Knut Åkesson, Bengt Lennartson. Modeling Sequential Resource Allocation Systems using Extended Finite Automata. Proceedings of the 7th IEEE International Conference on Automation Science and Engineering (CASE), pp. 444–449, 2011.

- Zhennan Fei, Knut Åkesson, Bengt Lennartson. Symbolic Reachability Computation using the Disjunctive Partitioning Technique in Supervisory Control Theory. Proceedings of IEEE International Conference on Robotics and Automation (ICRA), pp. 4364–4369, 2011.

- Zhennan Fei, Sajed Miremadi, Knut Åkesson, Bengt Lennartson. Efficient Symbolic Supervisory Synthesis and Guard Generation. Proceedings of the 3rd International Conference on Agents and Artificial Intelligence (ICAART), vol. 1, pp. 106–115, 2011.

- Sajed Miremadi, Zhennan Fei, Knut Åkesson, Bengt Lennartson. Symbolic Computation of Nonblocking Control Function for Timed Discrete Event Systems. Proceedings of the 51th IEEE International Conference on Decision and Control (CDC), pp. 7352–7359, 2012.

- Zhennan Fei, Sajed Miremadi, Knut Åkesson, Bengt Lennartson. A Symbolic Approach to Large-Scale Discrete Event Systems Modeled as Finite Automata with Variables. Proceedings of the 8th IEEE International Conference on Automation Science and Engineering (CASE), pp. 502–507, 2012.

- Bengt Lennartson, Sajed Miremadi, Zhennan Fei, Mona Noori Hosseini, Martin Fabian, Knut Åkesson. State-Vector Transition Model Applied to Supervisory Control. Proceedings of the 17th IEEE International Conference on Emerging Technologies & Factory Automation (ETFA), pp. 1–8, 2012.

# List of Acronyms

| BDD                 | — | Binary Decision Diagram                             |

|---------------------|---|-----------------------------------------------------|

| $\operatorname{CF}$ | _ | Characteristic Function                             |

| DAP                 | _ | Deadlock Avoidance Policy                           |

| DES                 | _ | Discrete Event System                               |

| D/C RAS             | — | Disjunctive/Conjunctive Resource Allocation System  |

| EFA                 | — | Extended Finite Automata                            |

| EFSC                | — | Extended Full Synchronous Composition               |

| EST                 | — | Explicit State Transition                           |

| FA                  | — | Finite (State) Automata                             |

| FSC                 | — | Full Synchronous Composition                        |

| OBDD                | _ | Ordered Binary Decision Diagram                     |

| PLC                 | — | Programmable Logic Controller                       |

| PN                  | — | Petri Nets                                          |

| RAS                 | — | Resource Allocation System                          |

| ROBDD               | _ | Reduced Ordered Binary Decision Diagram             |

| R/W RAS             | _ | Resource Allocation System with Reader/Writer Locks |

| SCT                 | _ | Supervisory Control Theory                          |

| TDES                | _ | Timed Discrete Event System                         |

# Contents

| Abstract             | i   |

|----------------------|-----|

| Acknowledgments      | iii |

| List of Publications | v   |

| List of Acronyms     | vii |

| Contents             | ix  |

# I Introductory Chapters

| 1        | Intr | oduction                                        | 1  |

|----------|------|-------------------------------------------------|----|

|          | 1.1  | Challenges                                      | 3  |

|          | 1.2  | Objectives                                      | 4  |

|          | 1.3  | Contributions                                   | 4  |

|          | 1.4  | Outline                                         | 5  |

| <b>2</b> | Sup  | ervisory Control Theory                         | 7  |

|          | 2.1  | Modeling Formalisms                             | 8  |

|          |      | 2.1.1 Deterministic Finite Automata             | 8  |

|          |      | 2.1.2 Extended Finite Automata                  | 10 |

|          | 2.2  | Supervisory Control Theory                      | 13 |

|          |      |                                                 | 14 |

|          |      |                                                 | 19 |

|          | 2.3  | Extensions of the basic SCT                     | 20 |

|          |      |                                                 | 20 |

|          |      | 2.3.2 Supervisor as Guards                      | 22 |

|          |      | -                                               | 23 |

|          | 2.4  | Closing Remarks                                 | 24 |

| 3        | Dea  | dlock Avoidance for Resource Allocation Systems | 25 |

|          | 3.1  | Resource Allocation System                      | 26 |

|          | 3.2  | Supervisory Control of RAS                      | 28 |

|          |      |                                                 | 29 |

## CONTENTS

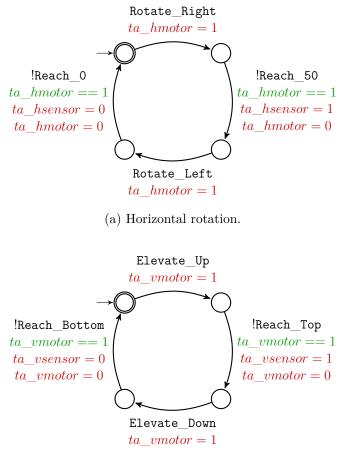

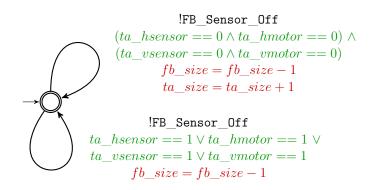

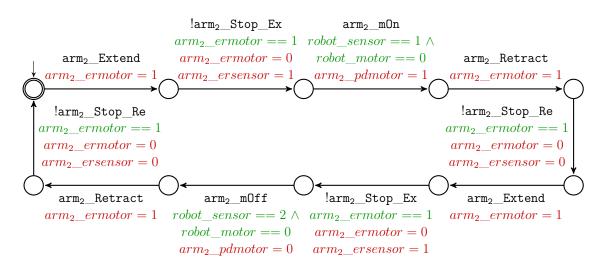

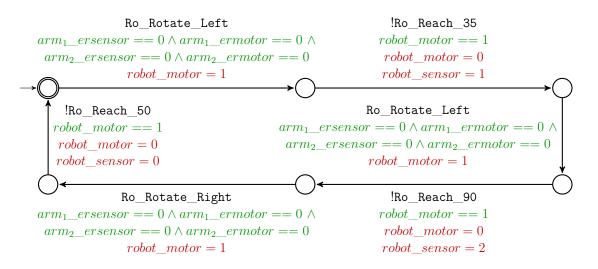

|          |       | 3.2.2 EFA-based Modeling of RAS Dynamics                        | 30 |

|----------|-------|-----------------------------------------------------------------|----|

|          |       | 3.2.3 The Target Maximally Permissive DAP                       | 32 |

|          | 3.3   | Dealing with the NP-Hardness of the Maximally Permissive DAP $$ | 34 |

|          | 3.4   | Closing Remarks                                                 | 37 |

| 4        | Syn   | abolic Representation and Computation                           | 39 |

|          | 4.1   | Binary Decision Diagram                                         | 40 |

|          | 4.2   | Representations of DES Models                                   | 42 |

|          |       | 4.2.1 Characteristic Functions                                  | 42 |

|          |       | 4.2.2 Single Model Representation                               | 43 |

|          |       | 4.2.3 Composed Model Representation                             | 45 |

|          | 4.3   | Symbolic State-Space Exploration                                | 47 |

|          |       | 4.3.1 Symbolic Safe State Synthesis                             | 48 |

|          |       | 4.3.2 State-Space Exploration on Partitioned BDDs               | 50 |

|          |       | 4.3.3 Partial State-Space Exploration for RAS                   | 51 |

|          | 4.4   | Experimental Results                                            | 54 |

| <b>5</b> | Cas   | e Study                                                         | 57 |

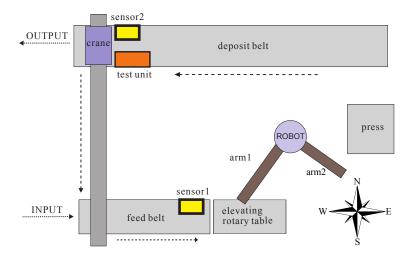

|          | 5.1   | The Manufacturing System                                        | 57 |

|          |       | 5.1.1 The Plant                                                 | 57 |

|          |       | 5.1.2 The Specification                                         | 59 |

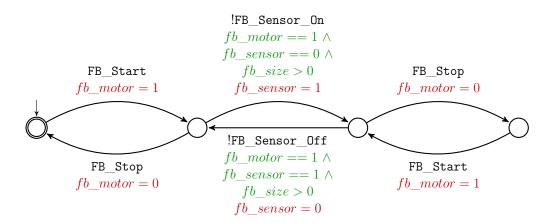

|          | 5.2   | The Model                                                       | 59 |

|          | 5.3   | Synthesis and Guard Extraction                                  | 66 |

|          | 5.4   | Summary                                                         | 68 |

| 6        | Con   | ntributions                                                     | 71 |

| 7        | Con   | clusions and Future Work                                        | 75 |

| Re       | efere | nces                                                            | 77 |

|          |       |                                                                 |    |

|          |       |                                                                 |    |

# II Included Papers

| Paper | 1 Symbolic State-Space Exp                                | loration and | l Guard | Generation in | n   |

|-------|-----------------------------------------------------------|--------------|---------|---------------|-----|

| Sup   | ervisory Control Theory                                   |              |         |               | 91  |

| 1     | Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |              |         |               | 91  |

| 2     | Motivating Example                                        |              |         |               | 92  |

| 3     | Preliminaries                                             |              |         |               | 95  |

|       | 3.1 Supervisory Control Theo                              | ory          |         |               | 95  |

|       | 3.2 Binary Decision Diagrams                              | s (BDD)      |         |               | 96  |

| 4     | BDD-Based Partitioning Comput                             | tation       |         |               | 97  |

|       | 4.1 Efficient State Space Sear                            | ch           |         |               | 98  |

|       | 4.2 Workset Based Strategies                              |              |         |               | 99  |

| 5     | Supervisor as Guards                                      |              |         |               | 101 |

### CONTENTS

|     | 5.1        | Computation of the Basic State Sets                             | 101 |

|-----|------------|-----------------------------------------------------------------|-----|

|     | 5.2        | Guard Generation                                                | 102 |

| 6   | Case       | Studies                                                         | 103 |

|     | 6.1        | Benchmark Examples                                              | 103 |

|     | 6.2        | Approach Evaluation                                             | 104 |

| 7   | Conc       | lusions                                                         | 106 |

| R   | References |                                                                 | 106 |

| Pap | er 2 Ef    | ficient Symbolic Supervisor Synthesis for Extended Finit        | je  |

| A   | utomat     | a                                                               | 111 |

| 1   | Intro      | duction                                                         | 111 |

| 2   | Preli      | minaries                                                        | 113 |

|     | 2.1        | Extended Finite Automata                                        | 113 |

|     | 2.2        | Binary Decision Diagrams                                        | 115 |

|     | 2.3        | Supervisory Control                                             | 116 |

| 3   | A Mo       | otivation Example                                               | 117 |

| 4   | Parti      | tioning of the full synchronous composition                     | 118 |

| 5   | Effici     | ent Reachability Computation                                    | 121 |

|     | 5.1        | Event-based Reachability Algorithm                              | 121 |

|     | 5.2        | Proof for the correctness of Algorithm 11 in Section 5          | 123 |

|     | 5.3        | Algorithm Efficiency                                            | 124 |

| 6   | Case       | Studies                                                         | 125 |

| 7   | Conc       | lusions                                                         | 126 |

| R   | References | •••••••••••••••••••••••••••••••••••••••                         | 128 |

| Pap | er 3 A     | BDD-Based Approach for Designing Maximally Permis               | 5-  |

| -   |            | llock Avoidance Policies for Complex Resource Allocatio         |     |

|     | ystems     | -                                                               | 133 |

| 1   | Intro      | duction                                                         | 133 |

| 2   | Prelii     | minaries                                                        | 136 |

|     | 2.1        | Resource Allocation Systems and the corresponding problem of    |     |

|     |            | Deadlock Avoidance                                              | 136 |

|     | 2.2        | Extended Finite Automata                                        | 138 |

|     | 2.3        | Binary Decision Diagrams                                        | 140 |

| 3   | Mode       | eling the considered RAS as an EFA                              | 141 |

| 4   |            | puting the minimal boundary unsafe states                       | 147 |

|     | 4.1        | An extension of the standard SCT synthesis algorithm for the    |     |

|     |            | computation of reachable boundary unsafe states                 | 148 |

|     | 4.2        | An alternative algorithm for the computation of feasible bound- |     |

|     |            | ary unsafe states                                               | 149 |

|     | 4.3        | Computing the minimal boundary unsafe states                    | 156 |

| 5   | Comp       | putational Results and Evaluation                               | 158 |

| 6   | Conc       | lusions                                                         | 162 |

| R   | References |                                                                 | 164 |

### CONTENTS

| Paper | 4 Symbolic Computation of Boundary Unsafe States in Com-                                        |    |

|-------|-------------------------------------------------------------------------------------------------|----|

| plex  | Resource Allocation Systems using Partitioning Techniques 17                                    | 1  |

| 1     | Introduction                                                                                    | '1 |

| 2     | Preliminaries                                                                                   | '3 |

|       | 2.1 Extended Finite Automata                                                                    | '3 |

|       | 2.2 Binary Decision Diagrams                                                                    | '5 |

| 3     | The Main Algorithm                                                                              | '8 |

| 4     | Extensions                                                                                      | 6  |

| 5     | Conclusions                                                                                     | 6  |

| Refe  | rences                                                                                          | 37 |

|       | Policies for Complex Resource Allocation Systems with Appli-<br>on to Multithreaded Software 19 | 1  |

| 1     | Introduction                                                                                    | 1  |

| 2     | Modeling Gadara Nets as EFA                                                                     | )3 |

|       | 2.1 Gadara Nets                                                                                 | )3 |

|       | 2.2 Extended Finite Automata                                                                    | 14 |

|       | 2.3 Modeling Gadara Nets as EFA                                                                 | 15 |

| 3     | Computing the Minimal Boundary Unsafe States 19                                                 | 17 |

|       | 3.1 Binary Decision Diagrams                                                                    | 18 |

|       | 3.2 Computation of the Minimal Boundary Unsafe States 20                                        | 0  |

| 4     | Representing the Target DAP as Guards                                                           | 13 |

| 5     | Conclusion                                                                                      | 16 |

| Refe  | rences                                                                                          | 16 |

# Part I Introductory Chapters

# Chapter 1 Introduction

In the aftermath of the revolution in computer technology, society nowadays is dependent on dedicated computer-aided systems more than ever to assist us in almost every aspect of daily life. From the very moment of waking up in the morning, we are surrounded with different hardware and software systems such as mobile phones, transportation facilities, communication tools, e-commerce systems, etc.

As such computer-aided devices and automation systems are widely used, designing reliable control logic is of paramount importance. While we may afford minor malfunctioning behavior occurring in our phones or personal computers, high demand on dependability and safety must be put in the design phase of certain critical systems such as air planes, industrial production systems or power plants, where failures might lead to loss of life and economic damages. A recent example of such a failure is the Ariane-5 rocket [1], that exploded on June 4, 1996, less than forty seconds after it was launched. The accident was caused by a software error in the computer that was responsible for calculating the rocket's movement. During the launch, an exception occurred when a large 64-bit floating-point number was converted to a 16-bit signed integer. The floating-point number that was converted had a value greater than what could be represented by a 16-bit signed integer. This resulted in an operand error. The same error also caused the backup computer to fail. As a result, incorrect attitude data was transmitted to the on-board computer, which caused the destruction of the rocket.

The increasing reliance on safety- and business-critical applications necessitates the development of formal methods for the rigorous modeling of the considered system and the accurate assessment of its associated properties. With respect to the modeling, classical control theory deals with systems whose behavior can be modeled using differential or difference equations. On the other hand, at a certain level of abstraction, the logical behavior of systems like automated manufacturing systems, computer networks and embedded control systems can be modeled as sequences of *events*. A system, characterized by a set of *states*, where the state evolution depends entirely on the occurrence of asynchronous events at discrete points in time, is referred to as a *discrete event system* (DES) [2], which is the scope of this thesis. A comprehensible example is the traffic light system, that can be modeled as a DES consisting of three states denoting either green, yellow or red, and a series of events indicating the alternation between the lights, e.g., the light turns green to yellow.

In the last two decades, research in formal methods has led to some promising methodologies that ease the burden of designing reliable systems. One approach towards the correctness of computer-based systems is model checking [3, 4], a formal verification technique allowing for properties of the considered system to be automatically verified on the basis of its model. Model checking usually terminates with a yes or no answer to the satisfiability of the model with respect to given specifications. Synthesis, on the other hand, can directly construct a desirable system where specifications are fulfilled. In 1987, Ramadge and Wonham proposed a model-based framework called supervisory control theory (SCT) [5, 6] for the automatic generation of reliable control logic, referred to as the supervisor, for DES. Having a model of the system to be controlled, the *plant*, and the model of the intended behavior of the controlled system, the *specification*, a supervisor can be automatically *synthesized* to control the plant according to the specification. In SCT, a supervisor is assumed to be maximally permissive in the sense that it restricts the plant behavior only when it is necessary. Furthermore, the SCT framework is facilitated by adopting graphical modeling formalisms such as *Petri nets* (PNs) [7], *finite automata* (FA) [2], *extended* finite automata (EFA) [8], that connect more explicitly the representation of the system behavior to the underlying system structure, and they are, thus, more compact and more amenable to processing during the synthesis phases.

In this thesis, besides studying and developing efficient supervisor synthesis in SCT for general DES, we also focus on a particular DES application domain – deadlock avoidance for *resource allocation systems* (RAS) [9]. In its basic positioning, this problem concerns the coordinated allocation of the system resources to a set of concurrently executing processes so that every process can eventually proceed to its completion. In particular, by utilizing the information about the current allocation of the system resources and the available knowledge about the structure of the executing process types, the applied control policy avoids the visitation of RAS states from which deadlock is inevitable. From an application standpoint, the need for deadlock avoidance arises in many contemporary systems, including material flow control of flexible automated production systems [10, 11, 12], traffic management of unmanned discrete material handling systems [13, 14, 15], traffic control of railway and urban monorail transport systems [16], and the lock allocation that takes place among the various threads of parallelized computer programs [17, 18].

The deadlock avoidance problem can be characterized in the classical SCT framework in a straightforward manner, through (i) expressing the underlying resource allocation dynamics into a deterministic finite automaton, and (ii) requesting the confinement of the RAS behavior to the subspace of this FA that is defined by its maximal strongly connected component that contains the system state where the RAS is idle and empty of any jobs. In fact, this characterization of the problem and its solution establishes also a notion of optimality for the considered problem, since the resulting policy prevents the formation of deadlock while retaining the maximum possible behavior for the underlying RAS.

## 1.1 Challenges

SCT has gained a lot of focus within the academic community, though its industrial acceptance has been scarce. This is a pity, since SCT has showed great promise when it comes to aiding the design and development of industrial control systems. We believe that the reasons for the scarce industrial acceptance of SCT are two-fold. One reason is the necessity to be able to treat systems of industrially interesting sizes. The other is how to efficiently represent the synthesized supervisor.

While normally a given DES application can be modeled as interacting components with each having a manageable size, the standard synthesis needs to consider the interactions of all components in order to explore possible global states, also referred to as the state-space. However, industrial systems nowadays are becoming more and more complex and each subsystem may consist of many interacting components. Synthesizing supervisors for such complex applications through the explicit state-space enumeration quickly becomes a serious impediment. As a matter of fact, the supervisor synthesis problem is NP-hard [19], and thus, it suffers from an inherent difficulty known as the state-space explosion problem, which makes the explicit enumeration of enormous state-spaces for industrial systems intractable due to lack of memory and time. To alleviate the state-space explosion problem, a well-known strategy is to represent the state-space of the considered DES symbolically. Here symbolic representation implies that the state-space is expressed by means of logic constraints or special data structures, which makes it possible to manipulate sets of states rather than single states. One such compact and efficient data structure that is employed in the thesis is the binary decision diagram (BDD) [20, 21], which, under the right conditions, can reach logarithmic compression of the involved state-spaces [21]. Nevertheless, the effective deployment of BDD-based symbolic computation in supervisory control remains a non-trivial task. A straightforward transformation from the explicit state-space enumeration into a BDD-based computation scheme does not result in a synthesis procedure that performs well on relevant problems. Hence, there is a need to develop more intelligent symbolic algorithms where the modularity and structure of DES are exploited more thoroughly.

In addition, even if the computation efficiency brought by the application of BDD makes it possible to synthesize the supervisor for a given industrial application, the supervisor will be symbolically represented as a BDD. Conceptually this symbolic representation of the obtained supervisor lies very far from the actual implementation in an industrial controller, such as a programmable logic controller (PLC). Since the original system models have been reformulated and encoded, it is cumbersome to relate each state with the corresponding BDD variables. Furthermore, the resultant control logic is of centralized nature, a feature that can be deemed as limiting/undesirable in the context of certain applications. These unsolved issues regarding the representation of the synthesized supervisor further prevents acceptance by industrial engineers who are typically not accustomed to DES or SCT. Therefore, it would be better if the representation of the supervisor lies closer to its actual implementation.

CHAPTER 1. INTRODUCTION

## 1.2 Objectives

Many contemporary computer-aided systems such as flexible manufacturing systems, communication systems and transportation systems can at some level of abstraction be described by events that model the transitions between different discrete states. Normally, industrial systems are complex and manual approaches are time-consuming, error prone and not practically feasible. Therefore, automated methodologies such as SCT are desired. On the other hand, to be able to design and implement consistent and reliable control functions for complex industrial applications, it is necessary to develop algorithms that have good performance and scalability.

The first objective of this thesis is to develop and enhance BDD-based symbolic algorithms for the computationally efficient development of control logic for large-scale DES to guarantee that the behaviors of systems fulfill given specifications. Having modeling the considered plant and specifications by using the provided modeling formalisms, the proposed symbolic algorithms encode the obtained model and represent its global behavior as a number of BDDs. The SCT analysis such as verification and synthesis then can be performed symbolically on these BDDs through the usage of the techniques developed in the thesis.

While the approaches mentioned above are targeted for the supervisor synthesis of general DES, this thesis also focuses on one particular DES application domain, i.e., deadlock avoidance for RAS. Briefly speaking, RAS characterize a broad class of applications where the underlying operations can be abstracted to a set of processes that contest for the engagement of the system reusable resources. In this thesis, we aim at developing a framework for the efficient synthesis of the maximally permissive DAP for RAS. Besides the employment of symbolic computation, additional efficiencies for the proposed symbolic algorithms are obtained through the exploitation of the structural properties possessed by the considered RAS classes.

The second objective of the thesis is to represent the result obtained from the proposed symbolic algorithms in a more comprehensible and transparent manner. On a basis of the previously developed procedure that generates Boolean conditions, referred to as guards, to represent the behavior of the synthesized supervisors, the thesis achieves this objective in two directions. For general DES, the guard generation procedure is tailored to work with the proposed symbolic algorithms in order to make it more applicable for industrial systems. By exploiting the structural properties of RAS, the guard generation procedure is extended to generate more comprehensible guards from the maximally permissive DAP.

## **1.3** Contributions

In the light of the above objectives for tackling the mentioned challenges that prevent SCT from having an industrial breakthrough, the thesis has the following contributions:

• It suggests and benchmarks several ways to partition and explore the symbolic

representation of state-space under full synchronous composition of deterministic FA and/or EFA, such that the intermediate blow up of internal nodes in the BDD representation is kept small (Paper 1 and Paper 2).

- It adapts the suggested symbolic synthesis algorithms to the guard generation procedure, making them more applicable for industrially interesting applications. That is, simplified guards can be directly generated from the partitioned presentation of the state-space and attached to the original DES model (Paper 1).

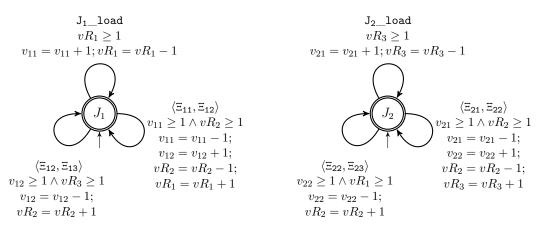

- It introduces a modeling procedure for recasting the dynamics of RAS instances into the EFA modeling framework. This procedure is extended for transforming a special class of Petri nets, Gadara nets [22], that model the primitive lock acquisition and release operations of multithreaded programs, into the equivalent EFA models (Paper 3 and Paper 5).

- It proposes a series of BDD-based symbolic algorithms for the effective and computationally efficient development of the maximally permissive deadlock avoidance policy (DAP) for various RAS classes (Paper 3 and Paper 4).

- It extends the guard generation procedure by utilizing a monotonicity property possessed within the structure of RAS. By attaching them to the original RAS-modeling EFA, the generated predicates guard transitions to the RAS states that dominate some elements in the underlying state set (Paper 5).

- It implements all the proposed approaches and algorithms in Supremica [23, 24, 25], a software tool for automatic verification, synthesis and simulation of discrete event systems.

# 1.4 Outline

The thesis is divided into two parts. Part I serves as a general introduction to this field and puts the appended papers in context. Part II contains the appended papers that constitute the base of the thesis. In Part I, Chapter 2 presents the background material on discrete event systems in general, with focus on the supervisory control theory. Chapter 3 focuses on one discrete event system application domain, deadlock avoidance for resource allocation systems. Chapter 4 gives a overview of symbolic computation using binary decision diagrams for supervisor computation and representation. Through illustrating a number of examples, the chapter informally presents some of the symbolic algorithms that are introduced in the appended papers. A summary of contributions in the appended papers is provided in Chapter 6. Finally, some concluding remarks and future work are given in Chapter 7.

# Chapter 2 Supervisory Control Theory

Discrete event systems (DES) are abstractions of real systems such as manufacturing, traffic control, material handling and embedded systems. DES behaviors are typically modeled in terms of *states* and *events*; states represent certain situations under which specific properties hold, while events represent significant occurrences that change those properties. A DES occupies a single state out of its many possible ones at each time instant, and transits to another on the occurrence of an event. Modeling DES has been facilitated by formalisms such as *finite automata* (FA) [2], *extended finite automata* (EFA) [8], *Petri nets* (PNs) [26, 2] and *process algebra* [27, 28] that connect more explicitly the representation of DES to the underlying system structure.

A main purpose of having DES models is the analysis and design of control functions to achieve some desired behavior. A *supervisor* is a control device for DES that through interaction with the controlled process dynamically restricts events from occurring, so as to keep the closed-loop system within a desired specification. In this way, the supervisor is a safety device; certain activities (events) are hindered from occurring in order to guarantee the safety of the considered system. However, at the same time as it prevents bad things from occurring, the supervisor must allow good things to occur.

Supervisory control theory (SCT) [5, 6, 29, 2], initiated by Ramadge and Wonham in the 80's, is a model-based formal framework for the automatic design of supervisors for DES, such that this supervisor interacting with the plant forms a closed-loop system that is, according to a given specification, correct by construction.

Though SCT has gained a lot of attention within the academic research communities, its industrial acceptance has been scarce. This is a pity, since SCT has a lot to offer when it comes to structuring and supporting the development of control functions for industrial applications. Probable reasons for the scarce industrial acceptance of SCT are two. One is the necessity to be able to model and analyze systems of practical sizes. The other is the representation of the synthesized supervisor.

This chapter introduces a set of preliminaries that are used in this thesis to model DES and synthesize supervisors. In particular, Section 2.1 starts with a discussion of two modeling formalisms. This is followed by Section 2.2 explaining supervisory control theory and the basic algorithms for synthesizing supervisors. With respect

to the issues that prevent SCT from having an industrial breakthrough, Section 2.3 overviews a number of various approaches and techniques developed by the research communities aiming for addressing these issues. Finally, Section 2.4 closes the chapter with a short summary and some comments on the appended papers that are related to the discussions of this chapter.

## 2.1 Modeling Formalisms

There are a certain number of modeling formalisms that can be used to model DES. In this thesis we focus on two of them, finite automata (FA) and extended finite automata (EFA). FA are intuitive, easy to use, since states and transitions are explicitly represented. As used originally in [5], they not only conform well with SCT but also have strong theoretical and practical properties developed over years. EFA are a variant of ordinary FA where integer variables are introduced to improve the compactness of DES models. This richer structure, though with equal expressive power, enables the representation of the DES behavior in a conciser manner than the ordinary FA.

In general, DES can be non-deterministic, meaning that the occurrence of an event may lead the considered system to different states due to some internal, unobservable behavior. For DES with deterministic behaviors, on the other hand, next states are uniquely determined by the current states of the system and the events that are enabled from them. In this thesis, we are interested in deterministic systems, and hence, all models used in this work are considered to be deterministic.

### 2.1.1 Deterministic Finite Automata

**Definition 2.1.** [2] A deterministic finite automaton, denoted by A, is a six-tuple

$$A = (Q, \Sigma, \delta, \Gamma, q_0, Q^m)$$

where:

- Q is the finite set of states.

- $\Sigma$  is the finite set of events, also known as the *alphabet* of A.

- $\delta: Q \times \Sigma \to Q$  is the transition function:  $\delta(q, \sigma) = q'$ , means that there is a transition labeled by event  $\sigma$  from source state q to target state q'; in general,  $\delta$  is a partial function.

- $\Gamma: Q \to 2^{\Sigma}$  is the *active event function*;  $\Gamma(q)$  is the set of all events  $\sigma$  for which  $\delta(q, \sigma)$  is defined and it is called the *active event set* of A at state q.

- $q_0$  is the *initial* state.

- $Q^m \subseteq Q$  is the set of *marked* states.

For the sake of convenience, the word automata will be used to refer to deterministic finite automata in the sequel.

In Definition 2.1, the inclusion of  $\Gamma$  in A is superfluous in the sense that  $\Gamma$  can be derived from  $\delta$ . For this reason, we will sometimes omit explicitly writing  $\Gamma$  when specifying an automaton if the active event set function is not central to the discussion.

For computational considerations, the transition function  $\delta$  of an automaton A sometimes is better to be formulated as the *transition relation*. The elements  $\langle q, \sigma, q' \rangle$  are said to be related if and only if there is a transition from q to q' by the event  $\sigma$ . Therefore, the transition relation of automaton A, denoted by  $\mapsto$ , can be defined as follows:

$$\mapsto = \{ \langle q, \sigma, q' \rangle \in Q \times \Sigma \times Q \mid \delta(q, \sigma) = q' \}.$$

A finite sequence of events is called a *string* of events. An empty string is denoted by  $\varepsilon$  and all possible strings consisting of events from the alphabet  $\Sigma$  is denoted by  $\Sigma^*$ . Through the usage of strings of events, we can conveniently extend  $\delta$  from domain  $Q \times \Sigma$  to domain  $Q \times \Sigma^*$  in the following recursive manner:

$$\begin{split} \delta(q,\varepsilon) &= q\\ \delta(q,s\sigma) &= \delta(\delta(q,s),\sigma) \text{ for } s \in \Sigma^* \text{ and } \sigma \in \Sigma. \end{split}$$

Frequently, a DES can be modeled by a set of FA. The monolithic system is then a *composition* of these subsystems. We will model the composition of two FA  $A_1$ and  $A_2$  by the *full synchronous composition* (FSC) [30], denoted by  $A_1||A_2$ . In the FSC of two FA, a common event is enabled if and only if it is enabled by each of the composed FA.

**Definition 2.2.** [30] Let  $A_1 = (Q_1, \Sigma_1, \delta_1, \Gamma_1, q_0^1, Q_1^m)$  and  $A_2 = (Q_2, \Sigma_2, \delta_2, \Gamma_2, q_0^2, Q_2^m)$  be two automata. The full synchronous composition, FSC, of  $A_1$  and  $A_2$  is defined as

$A_1||A_2 = (Q_1 \times Q_2, \Sigma_1 \cup \Sigma_2, \delta_{1||2}, \Gamma_{1||2}, (q_0^1, q_0^2), Q_1^m \times Q_2^m)$

where  $\delta_{1||2}$  is defined as

$$\delta_{1||2}((p,q),\sigma) = \begin{cases} (p',q') & \text{if } \sigma \in (\Sigma_1 \cap \Sigma_2), \delta_1(p,\sigma) = p', \delta_2(q,\sigma) = q'.\\ (p',q) & \text{if } \sigma \in (\Sigma_1 \setminus \Sigma_2), \delta_1(p,\sigma) = p'.\\ (p,q') & \text{if } \sigma \in (\Sigma_2 \setminus \Sigma_1), \delta_2(q,\sigma) = q'.\\ & \text{undefined otherwise.} \end{cases}$$

The active event set  $\Gamma_{1||2}$  follows from the definition of  $\delta_{1||2}$  and is given by

$$\Gamma_{1||2}((p,q)) = (\Gamma_1(p) \cap \Gamma_2(q)) \cup (\Gamma_1(p) \setminus \Sigma_2) \cup (\Gamma_2(q) \setminus \Sigma_1)$$

The FSC operator is both associative and commutative [2], and hence, can be extended to compose an arbitrary number of automata in a straightforward way.

We should notice from Definition 2.2 that after composition, the size of  $A_1||A_2$ , in terms of the number of reachable states, in the worst case is  $|Q_1| \times |Q_2|$ . Suppose that we compose *n* automata with the number of states in each automaton being

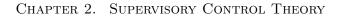

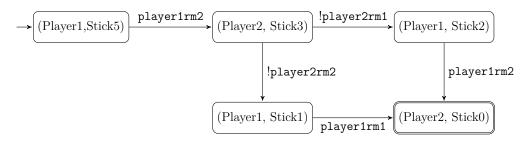

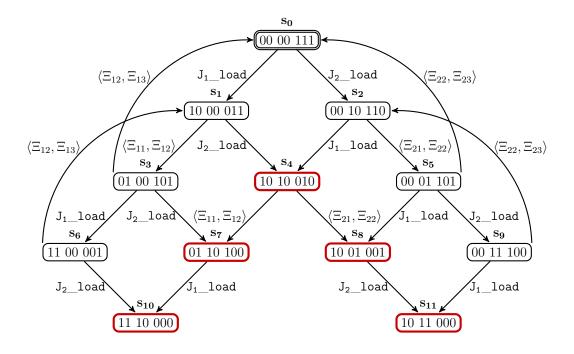

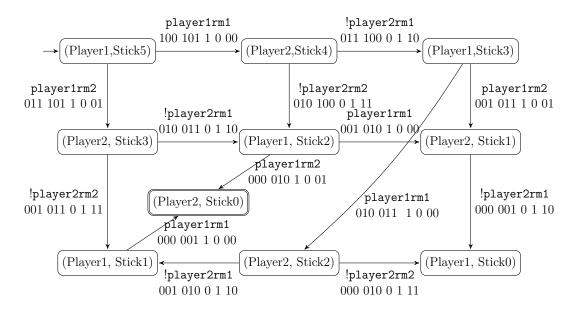

Figure 2.1: FA model of the stick-picking game in Example 2.1

k. The number of states of  $A_1 || \dots || A_n$  in the worst case is then equal to  $k^n$ . This means that the number of states grows *exponentially* as the number of components increases. We will now illustrate how FA can be used to model a simple game.

**Example 2.1.** DES modeling using deterministic FA is exemplified by a simple strategy game, called the stick-picking game. There are five sticks on the table, and two players take turns by removing one or two sticks from the table. The winner is the player who takes the last stick.

Figure 2.1 shows a way to model the stick-picking by deterministic FA. The depicted FA model consists of two automata that respectively capture the dynamics of the sticks and the turn-taking between two players in the game. As an example, the Stick automaton in Figure 2.1a models the way the number of sticks decreases as the game progresses, and it operates as follows. It starts in the initial state Stick5 representing the initial five sticks. Upon the occurrence of an event in  $\Gamma(\text{Stick5}) = \{player1rm1, player1rm2, player2rm1, player2rm2\}$ , the automaton will either transit to state Stick4 or state Stick3 depending on one or two sticks are picked from the table. This process then continues until the marked state Stick0 is finally reached. The complete (monolithic) behavior can be acquired by performing the FSC on the two automata, as shown later in Figure 2.4.

### 2.1.2 Extended Finite Automata

Extended finite automata (EFA) [8] are an augmentation of the ordinary FA with integer variables that are employed in a set of guard predicates and are maintained by a set of actions. A transition in an EFA is enabled if and only if its corresponding

guard is true. Once a transition is taken, updating actions on the set of variables may follow. By utilizing these two mechanisms, an EFA can represent the modeled behavior in a conciser manner than the ordinary FA.

**Definition 2.3.** Let  $v = (v_1, \ldots, v_n)$  be a set of global variables, with each variable  $v_i \in v$  having the finite domain  $D_i$ . An extended finite automaton over the variable set v, denoted by E, is a five-tuple

$$E = (Q, \Sigma, \to, q_0, Q^m)$$

where:

- $Q: L \times D$  is the extended finite set of states. L is the finite set of the model *locations* and  $D = D_1 \times \ldots \times D_n$  is the finite domain of the model *variables* v.

- $\Sigma$  is the finite set of events, also known as the *alphabet* of *E*.

- $\rightarrow \subseteq L \times \Sigma \times G \times A \times L$  is the transition relation, describing a set of transitions that take place among the model locations upon the occurrence of certain events. However, these transitions are further qualified by G, which is a set of guard predicates defined on  $D = D_1 \times \ldots \times D_n$ , and by A, which is a collection of actions that update the variables as a consequence of an occurring transition. Each action  $a \in A$  is an *n*-tuple of functions  $(a_1, \ldots, a_n)$ , with each function  $a_i$ updating the corresponding variable  $v_i$ .

- $q_0 = (\ell_0, v_0) \in L \times D$  is the initial state, where  $\ell_0$  is the initial location, while  $v_0$  denotes the vector of the initial values for the variables v.

- $Q^m \subseteq L^m \times D^m \subseteq Q$  is the set of marked states.  $L^m \subseteq L$  is the set of the marked locations and  $D^m \subseteq D$  denotes the set of the vectors of marked values for the variables v.

In the following, we shall use the notation  $\ell \xrightarrow{\sigma}_{g/a} \ell'$  as an abbreviation for  $(\ell, \sigma, g, a, \ell') \in \rightarrow$ . Also, the symbol  $\xi$  will be used to denote neutral actions that do not update the value of the corresponding variables; i.e., if  $a_i = \xi$ , action  $a_i$  does not update the variable  $v_i$  in v.

For analysis and synthesis purposes, the EFA model in Definition 2.3 is now formulated as an explicit state transition model according to the following definition.

**Definition 2.4.** The explicit state transition model of EFA  $E = (Q, \Sigma, \rightarrow, q_0, Q^m)$ over  $v = (v_1, \ldots, v_n)$ , denoted by EST(E), is a five-tuple

$$EST(E) = (Q, \Sigma, \mapsto, q_0, Q^m)$$

where  $\mapsto \subseteq L \times D \times \Sigma \times L \times D$  is an explicit state transition relation defined as:

$$\mapsto = \{(\ell, v, \sigma, \ell', v') \mid \ell \xrightarrow{\sigma}_{g/a} \ell' \in \to, v \models g, v' = a(v)\}.$$

#### CHAPTER 2. SUPERVISORY CONTROL THEORY

That is, if g holds for the current values of the variables v, i.e.,  $v \models g$ , the transition  $\ell \xrightarrow{\sigma}_{g/a} \ell'$  can be taken and the values of v are consequently updated by the action a, i.e., v' = a(v). Note that if variable  $v_i \in v$  is not updated, i.e.,  $a_i = \xi$ , then  $v'_i = v_i$ . For notational convenience, we shall let  $\mapsto_{\ell \xrightarrow{\sigma}_{g/a} \ell'}$  denote the explicit representation for the transition  $\ell \xrightarrow{\sigma}_{g/a} \ell' \in \rightarrow$ .

An EFA E is deterministic, if whenever there exist  $(\ell, v, \sigma, \ell', v') \in \mapsto_E$  and  $(\ell, v, \sigma, \ell'', v'') \in \mapsto_E$ , then we always have  $(\ell', v') = (\ell'', v'')$ . As mentioned earlier, since we merely focus on deterministic systems, in the sequel, we simply write EFA for deterministic EFA for brevity.

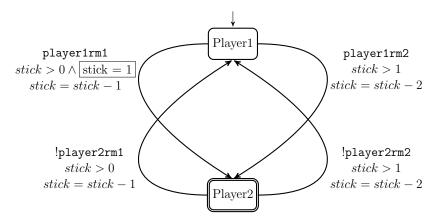

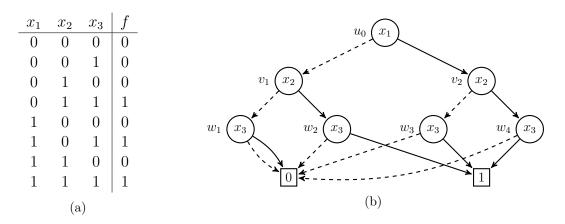

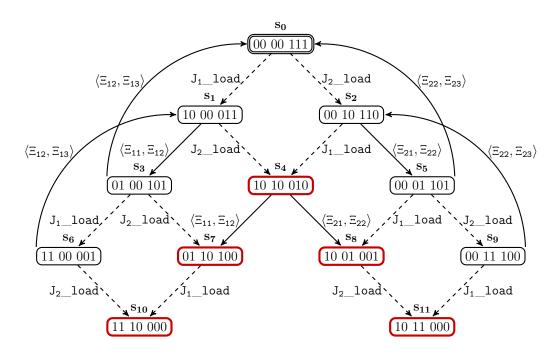

Figure 2.2: EFA model of the stick-picking game where the number of sticks is modeled as a variable stick with 5 as the initial value and 0 as the marked value.

**Example 2.2.** Figure 2.2 shows an EFA model for the stick-picking game introduced in Example 2.1. The depicted EFA contains two locations representing the respective turn of the two players in the game. Each location has two outgoing transitions labeled by events corresponding to the options of removing one or two sticks. Furthermore, an integer variable *stick* is introduced to count the number of sticks on the table. The guard predicates over the variable *stick* determine when the respective events are possible; the actions update the values of this variable when players remove sticks.

To illustrate how a transition of an EFA is represented as its explicit state transition(s), we take the upper right transition of Figure 2.2 as an example. This transition can lead to the following four explicit transitions:

> (Player1, stick = 5, player1rm2, Player2, stick = 3), (Player1, stick = 4, player1rm2, Player2, stick = 2), (Player1, stick = 3, player1rm2, Player2, stick = 1), (Player1, stick = 2, player1rm2, Player2, stick = 0).

Analogous to the FSC for FA in Definition 2.2, the composition of two EFA is defined as the *extended full synchronous composition*. It is assumed that the variables are shared by all EFA with the same initial and marked values.

**Definition 2.5.** Let  $E_1 = (Q_1, \Sigma_1, \rightarrow_1, q_0^1, Q_1^m)$  and  $E_2 = (Q_2, \Sigma_2, \rightarrow_2, q_0^2, Q_2^m)$  be two EFA with a common variable set  $v = (v_1, \ldots, v_n)$ . The extended full synchronous composition (EFSC) of  $E_1$  and  $E_2$  is defined as

$$E_1||E_2 = (Q_{1||2}, \Sigma_1 \cup \Sigma_2, \rightarrow_{1||2}, (q_0^1, q_0^2), Q_{1||2}^m)$$

where  $Q_{1||2}: L_1 \times L_2 \times D$ ,  $Q_{1||2}^m: L_1^m \times L_2^m \times D^m$ ,  $q_0^1 = (\ell_0^1, v_0^1)$  and  $q_0^2 = (\ell_0^2, v_0^2)$  with  $v_0^1 = v_0^2$ , and the transition  $(\ell_1, \ell_2) \xrightarrow{\sigma}_{g/a} (\ell_1', \ell_2') \in \rightarrow_{1||2}$  is defined by the following three rules:

- If  $\sigma \in \Sigma_1 \cap \Sigma_2$  and  $\ell_1 \xrightarrow{\sigma}_{g^1/a^1} \ell'_1 \in \to_{E_1}$  and  $\ell_2 \xrightarrow{\sigma}_{g^2/a^2} \ell'_2 \in \to_{E_2}$  are action consistent, then

- $g = g^1 \wedge g^2,$

- each action function  $a_i$  of a is defined as

$$a_{i} = \begin{cases} a_{i}^{1} & \text{if } a_{i}^{1} \neq \xi \text{ and } a_{i}^{2} \neq \xi, \\ a_{i}^{1} & \text{if } a_{i}^{1} \neq \xi \text{ and } a_{i}^{2} = \xi, \\ a_{i}^{2} & \text{if } a_{i}^{1} = \xi \text{ and } a_{i}^{2} \neq \xi, \\ \xi & \text{if } a_{i}^{1} = \xi \text{ and } a_{i}^{2} = \xi. \end{cases}$$

- If

$$\sigma \in \Sigma_1 \setminus \Sigma_2$$

and  $\ell_1 \xrightarrow{\sigma}_{g^1/a^1} \ell'_1 \in \to_{E_1}$  then  $g = g^1$  and  $a = a^1$  and  $\ell'_2 = \ell_2$ .

- If  $\sigma \in \Sigma_2 \setminus \Sigma_1$  and  $\ell_2 \xrightarrow{\sigma}_{g^2/a^2} \ell'_2 \in \to_{E_2}$  then  $g = g^2$  and  $a = a^2$  and  $\ell'_1 = \ell_1$ .

The transitions  $\ell_1 \xrightarrow{\sigma}_{g^1/a^1} \ell'_1 \in \to_{E_1}$  and  $\ell_2 \xrightarrow{\sigma}_{g^2/a^2} \ell'_2 \in \to_{E_2}$  are action consistent if  $a_i^1 \neq \xi$  and  $a_i^2 \neq \xi$ , then  $a_i^1(v) = a_i^2(v)$  for all  $v \in D, i = 1, \ldots, n$ . Note that if two transitions update any variable  $v_i$  to different values, then the composed transition is not defined. A good modeling practice is that for each variable and for each event, only one EFA is allowed to update the variable with the event, while the same variable can be updated in different EFA with any other event. In this case, the actions are structurally action consistent. Furthermore, the EFSC operator is both commutative and associative [31], and thus it can be extended to handle an arbitrary number of EFA.

### 2.2 Supervisory Control Theory

Given a model of the system to be controlled, the *plant*, and a *specification* of the desired controlled behavior, *supervisory control theory* (SCT) [5, 6, 29, 2] provides a formal framework to automatically compute, that is, *synthesize*, a *supervisor* that interacts with the plant to restrict the behavior such that the specification is satisfied.

Typically a plant is described by a number of sub-plants  $G_1, \ldots, G_n$ , and the monolithic plant G is then given by  $G_1||\ldots||G_n$ . Similarly, the specification K is typically described as a set of sub-specifications,  $K = K_1||\ldots||K_m$ .

An important feature of the SCT is the partitioning of events as *controllable* or *uncontrollable*. The alphabet of a system thus can be partitioned into two disjoint

### CHAPTER 2. SUPERVISORY CONTROL THEORY

subsets  $\Sigma^c$  and  $\Sigma^u$ , which denote the set of controllable events and the set of uncontrollable events, respectively. Note that only controllable events can be prevented from occurring by the supervisor.

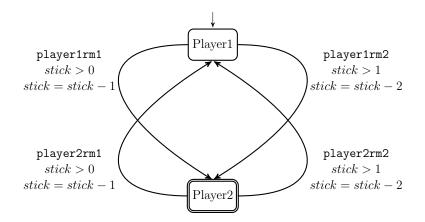

Figure 2.3: The feedback loop of the plant and the supervisor in SCT

Figure 2.3 shows the feedback loop of the plant and the supervisor. In SCT, the plant is assumed to generate all events; the supervisor, as a function  $f(\cdot)$  of the observed sequence of events, can enable or disable any controllable event activated by the plant. Typically it is possible to supervise a given system in many ways, and thus, the supervisor to be synthesized can have multiple realizations depending how restrictive or permissive it is. For instance, supervisors that do not allow anything to happen might also fulfill the specification in the sense that the plant is not allowed to do anything outside the specification. However, such supervisors are not useful. Supervisors in SCT are assumed to be *maximally permissive*, which means that plants are given the greatest amount of freedom to generate events and controllable events are only disabled when necessary in order to prevent systems from reaching undesirable states where a specification is violated. The relevant literature has established conditions under which such a supervisor exists and it is unique with respect to a given plant and specification [32]. Unless otherwise noted, in this work we will only consider synthesis of supervisors with maximally permissive closed-loop behavior.

### 2.2.1 Supervisor Synthesis for Deterministic FA

In the Ramadge & Wonham work [5], the supervisor was realized as a control map  $\Gamma: Q \to 2^{\Sigma}$ . Unfortunately, the presented method for realizing such control map is inefficient. In [33] it was shown that the interaction between the plant and the supervisor can be modeled by the FSC defined in Definition 2.2. That is, the supervisor can also be considered as a deterministic FA. When a supervisor S supervises a plant G, the behavior that S will try to enforce is G||S. Notably, if S is not designed properly, some parts of the plant may not be amenable to the control imposed by S, so the actual behavior may be different. This is the reason why S should be synthesized using formal methods that guarantee that S never tries to control the parts of the plant that can not be controlled or, in other words, that the closed-loop behavior really is G||S. In this thesis, we assume that the supervisor always *refines* the plant, that is, S is structurally equivalent to G||S.

In addition to the basic property that the plant G under the control of the supervisor S should fulfill the given specification K, typically, there are two additional properties that supervisors are desired to have: *non-blocking* and *controllable*.

### Non-blocking

Let  $A = (Q, \Sigma, \delta, q_0, Q^m)$  be a deterministic finite automaton. A state  $q \in Q$  is said to be coreachable to  $Q^m$  if

$$\exists s \in \Sigma^* \text{ and } q_m \in Q^m$$

, such that  $\delta(q, s) = q_m$ .

An automaton is said to be non-blocking if all of its states are coreachable to  $Q^m$ . In other words, an automaton is non-blocking if for every state there exists a path to some marked state.

### Controllability

Let G and K be two deterministic finite automata and  $\Sigma^u$  be the set of uncontrollable events. A state  $(p,q) \in Q_G \times Q_K$  is controllable if

$$\forall \sigma \in \Sigma^u \colon \sigma \in \Gamma_G(p) \Rightarrow \sigma \in \Gamma_{G||K}((p,q)).$$

K is controllable with respect to G if every state (p,q) in the composed system G||K is controllable.

### Synthesis

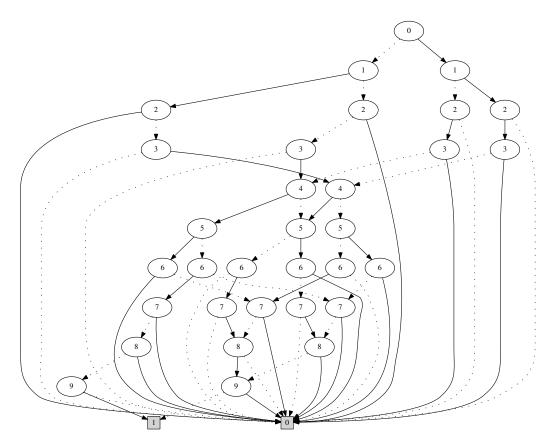

Given a plant G and a specification K modeled by deterministic FA, the synthesis algorithm first builds a supervisor candidate  $S_0$  by computing the closed-loop system G||K. Subsequently, the algorithm removes all the undesired states from  $Q_{S_0}$  until the remaining states are both coreachable and controllable. In this thesis, the synthesis algorithm that is used to calculate the maximally permissive supervisor is called the *safe-state-synthesis*, which was introduced in [34].

Given a set of initial forbidden states  $Q^x$  that is the union of the *explicitly forbidden states* and the *initially* uncontrollable states according to the controllability explained above, the algorithm presented in Algorithm 1 executes as follows. Algorithm 1 iteratively expands the forbidden state set  $Q^x$  by adding all the states that can uncontrollably reach the existing forbidden states and/or non-coreachable states, until a final *fix-point* is reached. In particular, taking as input the state set  $Q_{i-1}^x$ , which is computed from the previous iteration, Algorithm 1 uses Algorithm 2 to compute all the states that are coreachable to the marked states in  $Q^m$  but do not belong to  $Q_{i-1}^x$ . We denote by Q' the set of these coreachable states computed at Line 4. It can be inferred that the complement of Q' with  $Q_{S_0}$ , i.e.,  $Q_{S_0} \setminus Q'$ , contains all the states that are blocking at the current iteration. Subsequently, Algorithm 3 is utilized to identify from  $Q_{S_0}$  all the states that can reach these blocking states through uncontrollable events, and collects them into the set Q'', which later is contained in

### CHAPTER 2. SUPERVISORY CONTROL THEORY

the set  $Q_i^x$ . After the fix-point computation depicted in Lines 2-7 of Algorithm 1 terminates, the safe state set  $Q_S$  can be obtained by removing the states in  $Q_i^x$  from the set  $Q_{S_0}$ . However, this state set may contain some unreachable states that need to be excluded. Hence, a forward reachability search, depicted in Algorithm 4, is employed to remove these safe states that are not reached from the initial state of  $S_0$ . The synthesis of a supervisor using the safe-state-synthesis is demonstrated in the following example.

| Algorithm 1: SAFE-STATE-SYNTHESIS                                     |  |  |

|-----------------------------------------------------------------------|--|--|

| Input: $Q^x$ , $Q^m$ , $S_0$                                          |  |  |

| <b>Output</b> : The set of reachable safe states $Q_S$                |  |  |

| 1 $i := 0, Q_0^x := Q^x;$                                             |  |  |

| 2 repeat                                                              |  |  |

| <b>3</b> $  i := i + 1;$                                              |  |  |

| 4 $Q' := \text{RESTRICTED-BACKWARD}(Q^m, Q^x_{i-1}, S_0);$            |  |  |

| 5 $Q'' := \text{Uncontrollable-Backward}(Q_{S_0} \setminus Q', S_0);$ |  |  |

| $6  Q_i^x := Q_{i-1}^x \cup Q'';$                                     |  |  |

| 7 until $Q_i^x = Q_{i-1}^x$ ;                                         |  |  |

| 8 $Q_S = \text{RESTRICTED-FORWARD}(Q_i^x, q_0^{S_0}, S_0);$           |  |  |

| 9 return $Q_S$ ;                                                      |  |  |

|                                                                       |  |  |

### Algorithm 2: RESTRICTED-BACKWARD

Input:  $Q^m$ ,  $Q^x$  and  $S_0$ Output: The set of states that are coreachable to  $Q^m$  but not in  $Q^x$ 1  $i := 0, Q_0 := Q^m \setminus Q^x$ ; 2 repeat 3  $\begin{vmatrix} i := i + 1; \\ Q_i := Q_{i-1} \cup \{q \in Q_{S_0} \mid \exists q' \in Q_{i-1}, \exists \sigma \in \Sigma_{S_0} \text{ s.t. } \delta_{S_0}(q, \sigma) = q'\} \setminus Q^x$ ; 5 until  $Q_i = Q_{i-1}$ ; 6 return  $Q_i$ ;

### Algorithm 3: UNCONTROLLABLE-BACKWARD

Input:  $Q_x$  and  $S_0$ Output: The set of expanded uncontrollable states 1  $i := 0, Q_0^x := Q^x;$ 2 repeat 3  $\begin{vmatrix} i := i + 1; \\ Q_i^x := Q_{i-1}^x \cup \{q \in Q_{S_0} \mid \exists q' \in Q_{i-1}^x, \exists \sigma_u \in \Sigma_{S_0}^u \text{ s.t. } \delta_{S_0}(q, \sigma_u) = q'\};$ 5 until  $Q_i^x = Q_{i-1}^x;$ 6 return  $Q_i^x;$

#### Algorithm 4: RESTRICTED-FORWARD

Input:  $Q_x$ ,  $q_0$  and  $S_0$ Output: The set of states that are reachable from  $q_0$ 1  $i := 0, Q_0 := \{q_0\};$ 2 repeat 3  $\begin{vmatrix} i := i + 1; \\ Q_i := Q_{i-1} \cup \{q' \in Q_{S_0} \mid \exists q \in Q_{i-1}, \exists \sigma \in \Sigma_{S_0} \text{ s.t. } \delta_{S_0}(q, \sigma) = q'\} \setminus Q_x;$ 5 until  $Q_i = Q_{i-1};$ 6 return  $Q_i;$

**Example 2.3.** Let us consider again the FA model of the stick-picking game introduced in Example 2.1. The objective is to design a strategy for controlling how Player1 picks sticks, in order to win the game. On the other hand, the number of sticks taken by Player2 cannot be controlled. Therefore, all events associated with Player2 are modeled as uncontrollable events, and thus, they cannot be disabled by the supervisor.

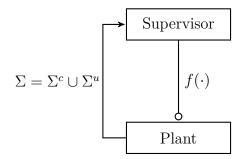

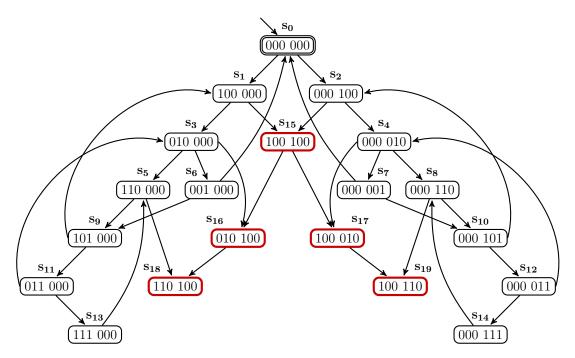

As stated earlier, a first candidate of the supervisor is the composed automaton  $S_0 = \text{Player}||\text{Stick}$ , shown in Figure 2.4. Initially, we notice that no forbidden state is included in the set  $Q^x$ , i.e.,  $Q^x = \emptyset$ , because (i) there are no explicitly forbidden states, and (ii) no specification is involved in the considered FA model. We then apply Algorithm 1 to the automaton Player||Stick. In the first iteration, the sets Q', Q'' and  $Q_1^x$  are:

- Q' = RESTRICTED-BACKWARD({(Player2, Stick0)}, ∅) = {(Player2, Stick0), (Player1, Stick1), (Player1, Stick2), (Player2, Stick2), (Player2, Stick3), (Player2, Stick4), (Player1, Stick5), (Player1, Stick3)}.

- $Q'' = \text{UNCONTROLLABLE-BACKWARD}(\{(\text{Player2, Stick1}), (\text{Player1, Stick0})\})$ = {(Player2, Stick1), (Player1, Stick0), (Player2, Stick2)}.

$Q_1^x = \{$ (Player2, Stick1), (Player1, Stick0), (Player2, Stick2) $\}.$

Since  $Q_0^x \neq Q_1^x$ , a fix-point has not been reached, and the second iteration will be carried out:

- $Q' = \text{RESTRICTED-BACKWARD}(\{(\text{Player2, Stick0})\}, Q_1^x) = \{(\text{Player2, Stick0}), (\text{Player1, Stick1}), (\text{Player1, Stick2}), (\text{Player2, Stick3}), (\text{Player2, Stick4}), (\text{Player1, Stick5})\}.$

- Q" = UNCONTROLLABLE-BACKWARD({(Player2, Stick1), (Player1, Stick0), (Player2, Stick2), (Player1, Stick3)}) = {(Player2, Stick1), (Player1, Stick0), (Player1, Stick3), (Player2, Stick2), (Player2, Stick4)}.

CHAPTER 2. SUPERVISORY CONTROL THEORY

Figure 2.4: The supervisor candidate  $S_0 = \text{Player}||\text{Stick where all the unreachable states are omitted for brevity. Events prefixed with exclamation marks are uncontrollable.$

$Q_2^x = \{$ (Player2, Stick1), (Player1, Stick0), (Player2, Stick2), (Player1, Stick3), (Player2, Stick4) $\}.$

The fix-point has not been reached and thus the computations depicted in Lines 2-8 of Algorithm 1 continue as follows.

- $Q' = \text{RESTRICTED-BACKWARD}(\{(\text{Player2, Stick0})\}, Q_2^x) = \{(\text{Player2, Stick0}), (\text{Player1, Stick1}), (\text{Player1, Stick2}), (\text{Player2, Stick3}), (\text{Player1, Stick5})\}.$

- $Q'' = \text{UNCONTROLLABLE-BACKWARD}(\{(\text{Player2, Stick1}), (\text{Player1, Stick0}), (\text{Player2, Stick2}), (\text{Player1, Stick3}), (\text{Player2, Stick4})\})$

- = {(Player2, Stick1), (Player1, Stick0), (Player2, Stick2), (Player1, Stick3), (Player2, Stick4)}.

- $Q_3^x = \{$ (Player2, Stick1), (Player1, Stick0), (Player1, Stick3), (Player2, Stick2), (Player2, Stick4) $\}.$

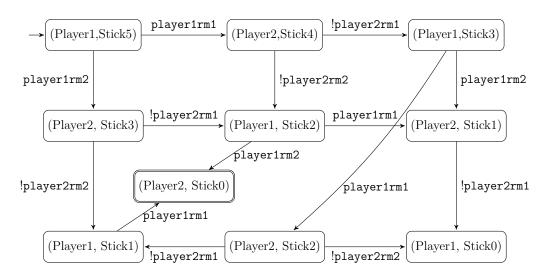

The set of forbidden states  $Q_3^x$  computed from the third iteration is the same as  $Q_2^x$ , and thus, the fix-point is reached. After removing these forbidden states and their associated transitions, the supervisor is obtained, as shown in Figure 2.5. The reader should notice that the depicted supervisor in Figure 2.5 is essentially a sub-automaton of the supervisor candidate  $S_0 = \text{Player}||\text{Stick.}$  Also, the supervisor is controllable with respect to the plant, since it never disables any of the uncontrollable events during supervision.

For a more formal and detailed explanation of the conventional supervisor synthesis, we refer readers to [6, 29, 2, 35].

2.2. Supervisory Control Theory

Figure 2.5: The non-blocking and controllable supervisor for the stick-picking game.

### 2.2.2 Transformation of EFA to FA

In the previous subsection, we explained the basic synthesis algorithm defined on DES modeled as deterministic FA, where transitions are represented explicitly by their states and events. However, due to the introduction of variables, the SCT synthesis performed on FA cannot be applied directly to EFA where states are implicitly represented. Two ways to address the issue are: (i) define a new theoretical framework for EFA, which conforms with the conventional SCT synthesis, or (ii) transform EFA to the corresponding FA and use the existing SCT framework.

In [36], the authors proposed a theoretical framework where, given a plant and a specification both modeled by EFA, the maximally permissive supervisor, represented as another EFA, can be directly synthesized.

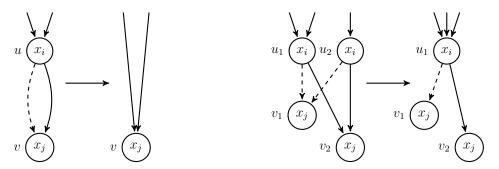

In [8] and [37], the authors proposed an algorithm that transforms any EFA model to the corresponding FA model, such that the SCT analysis defined on FA can be reused. In particular, two kinds of automata, referred to as *location automata* and *variable automata*, are constructed by the algorithm during the transformation. The location automata preserve the same structure as the original EFA without considering the guards and actions. The variable automata, on the other hand, capture how variables are evaluated and updated for the corresponding transitions in the original EFA. More formally, given  $N(=N_1 + N_2)$  EFA defined over *n* variables, with  $N_1$ sub-plants  $E_{G_1}, \ldots, E_{G_{N_1}}$  and  $N_2$  sub-specifications  $E_{K_1}, \ldots, E_{K_{N_2}}$ , the corresponding plant and specification FA, denoted by  $A_G$  and  $A_K$ , respectively, can be computed as follows:

$$A_{G} = (A_{G_{1}}^{loc}||\dots||A_{G_{N_{1}}}^{loc})||(A^{v_{1}}||\dots||A^{v_{n}}),$$

$$A_{K} = (A_{K_{1}}^{loc}||\dots||A_{K_{N_{2}}}^{loc})||(A^{v_{1}}||\dots||A^{v_{n}}),$$

where  $A_{G_1}^{loc}, \ldots, A_{G_{N_1}}^{loc}$  and  $A_{K_1}^{loc}, \ldots, A_{K_{N_2}}^{loc}$  denote the transformed location FA for the EFA  $E_{G_1}, \ldots, E_{G_{N_1}}$  and  $E_{K_1}, \ldots, E_{K_{N_2}}$ , and  $A^{v_1}, \ldots, A^{v_n}$  are the transformed variable FA for the *n* variables.

Subsequently, based on  $A_G$  and  $A_K$ , the conventional SCT can be applied to the model. Recall that in Examples 2.1 and 2.2, we have modeled the sticking-picking game by FA and EFA, respectively. By applying the transformation algorithm in [8] and [37] to the EFA model shown in Figure 2.2, we will get the deterministic FA shown in Figure 2.4, which is actually the composition of the automata shown in Figure 2.1.

CHAPTER 2. SUPERVISORY CONTROL THEORY

Although the algorithm introduced in [8] provides the convenience for reusing the standard SCT synthesis for DES modeled as EFA, its transformation procedure can be very time consuming, especially for complex models with many guards and actions. This is because when constructing the variable automata, the algorithm will first convert guards into the equivalent disjunctive normal forms, and then create one transition for each term of each disjunctive normal form. In the worst case, the number of transitions created by the algorithm for the variable automata can be exponential in the number of transitions included in the considered EFA. In [38] and [Paper 2], two different approaches have been introduced for directly converting an EFA model to the binary decision diagrams (BDDs) that symbolically represent the transition relation of the corresponding FA model.

# 2.3 Extensions of the basic SCT

This section gives an overview of different approaches and extensions of the basic supervisory control formulation.

### 2.3.1 Combating State-Space Explosion

The main obstacle in the analysis of DES is the *state-space explosion problem*. The problem arises when one tries to reason about the global behavior of a DES with little interaction among the components. Since standard synthesis algorithms always build the explicit state-space of the considered system  $S_0 = G||K$  and store all states and transitions in the memory, they are limited by the state-space explosion problem.

The following discussion gives a number of representative approaches and techniques developed by the research community to circumvent the limitations arising from the state-space explosion problem. We notice, however, that the computational complexity of supervisor synthesis is NP-hard [19], given multiple sub-plants and subspecifications. This means that in the worst case we cannot expect a solution that is much faster than the brute-force solution, although in many practical cases, the complexity can be alleviated by exploiting the system structure, or by employing efficient data structures to perform the synthesis procedure. The following approaches have been introduced in the literature for combating the state-space explosion problem for supervisory control problems.

Modular approaches As opposed to monolithic approaches that consider the whole system at once, modular approaches allow for the synthesis of multiple subsupervisors, with each one controlling only parts of the plant. The advantage of modular approaches is that potentially we may never consider the full system at once, and thus the state-space explosion can be avoided. The modular synthesis was introduced in [39] and further developed and strengthened in [40, 41, 42, 43, 44, 45], among others.

- Hierarchical approaches Hierarchical methods strive to divide a system into different levels of hierarchy, where the high-level supervisor is responsible for achieving a broad goal, while the low-level supervisors are responsible for the more detailed problems that are assigned by the high-level supervisor's decisions. Hierarchical supervisory control problems have been treated in [46, 47, 48, 49, 50, 51], among others.

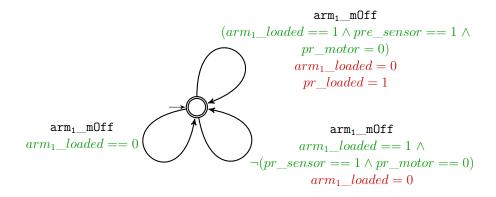

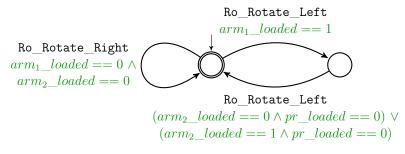

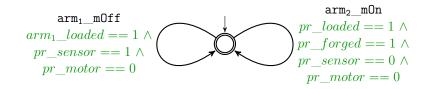

- **Compositional approaches** While modular and hierarchical approaches can be thought to use abstractions in different forms, compositional approaches exploit the abstraction techniques more thoroughly. As a starting point, all original components are simplified by identifying and merging certain states. Some of the abstracted components are then composed and further simplified. The process is repeated until one final relatively simple automaton is obtained. Different compositional methods developed for verification and synthesis properties in the context of SCT can be found in [52, 53, 54, 55, 56].