THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# Cryogenic Ultra-Low Noise InP High Electron Mobility Transistors

### JOEL SCHLEEH

Microwave Electronics Laboratory Department of Microtechnology and Nanoscience - MC2 Chalmers University of Technology Gothenburg, Sweden 2013 Cryogenic Ultra-Low Noise InP High Electron Mobility Transistors

© Joel Schleeh, 2013

ISBN 978-91-7385-944-8

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie Nr 3626 ISSN 0346-718X

Chalmers University of Technology Department of Microtechnology and Nanoscience - MC2 Microwave Electronics Laboratory SE-412 96 Gothenburg, Sweden Tel. +46 (0)31 772 1000

ISSN 1652-0769 Technical Report MC2-263.

Printed by Chalmers Reproservice, Gothenburg, Sweden, November, 2013

## Abstract

Indium phosphide high electron mobility transistors (InP HEMTs), are today the best transistors for cryogenic low noise amplifiers at microwave frequencies. Record noise temperatures below 2 K using InP HEMT equipped cryogenic low noise amplifiers (LNAs) were demonstrated already a decade ago. Since then, reported progress in further reducing noise has been slow.

This thesis presents new technology optimization, modeling, measurements and circuit implementation for the cryogenic InP HEMT. The findings have been used to demonstrate a new record minimum noise temperature of 1 K at 6 GHz. The thesis considers aspects all the way from material, process and device design, to hybrid and monolithic microwave integrated circuit (MMIC) LNAs.

The epitaxial structure has been developed for lower access resistance and improved transport characteristics. By investigating device passivation, metallization, gate recess etch, and circuit integration, low-noise InP HEMT performance was optimized for cryogenic operation.

When integrating the InP HEMT in a 4-8 GHz 3-stage hybrid LNA, a noise temperature of 1.2 K was measured at 5.2 GHz and 10 K operating temperature. The extracted minimum noise temperature of the InP HEMT was 1 K at 6 GHz.

The low-frequency 1/f noise in the 1 Hz to 1 GHz range and gain fluctuations in the 1Hz to 100 kHz range have been measured for six different types of HEMTs, and compared to two different SiGe heterojunction bipolar transistors (HBTs). The results showed that radiometer chop rates in the kHz range are needed for millimeter wave radiometers with 10 GHz bandwidth.

A comparative study of GaAs metamorphic HEMTs (mHEMTs) and InP HEMTs has been performed. When integrated in a 4-8 GHz 3-stage LNA, the InP HEMT LNA exhibited 1.6 K noise temperature whereas the GaAs mHEMT LNA showed 5 K. The observed superior cryogenic noise performance of the InP HEMT compared to the GaAs MHEMT was related to a difference in quality of pinch-off as observed in I-V characteristics at 300 K and 10 K.

To demonstrate the low noise performance of the InP HEMT technology, a 0.5-13 GHz and a 24-40 GHz cryogenic monolithic microwave integrated circuit (MMIC) LNA was fabricated. Both designs showed state-of-the-art low noise performance, promising for future radio astronomy receivers such as the square kilometer array.

**Keywords:** ALD, cryogenic, DC power dissipation, GaAs MHEMT, gain fluctuations, InP HEMT, LNA, low noise, MMIC

# List of publications

### **Appended** papers

The thesis is based on the following papers:

- [A] J. Schleeh, J. Halonen, B. Nilsson, P. Å. Nilsson, L.J. Zeng, P. Ramvall, N. Wadefalk, H. Zirath, E. Olsson and J. Grahn, "Passivation of InGaAs/InAlAs/InP HEMTs using Al<sub>2</sub>O<sub>3</sub> atomic layer deposition", in 23<sup>rd</sup> IEEE International Conference on Indium Phosphide & Related Materials, IPRM, pp. 63-66, May 2011.

- [B] J. Schleeh, G. Alestig, J. Halonen, A. Malmros, B. Nilsson, P. Å. Nilsson, J. P. Starski, N. Wadefalk, H. Zirath, J. Grahn, "Ultra-low power cryogenic InP HEMT with minimum noise temperature of 1 K at 6 GHz", in *IEEE Electron Device Letters*, vol. 33, no. 5, pp. 664-666, May, 2012.

- [C] J. Schleeh, H. Rodilla, N. Wadefalk, P. Å. Nilsson, J. Grahn, "Characterization and Modeling of Cryogenic Ultra-Low Noise InP HEMTs", in *IEEE Transactions on Electron Devices*, vol. 60, no. 1, pp. 206-212, Jan., 2013.

- [D] H. Rodilla, J. Schleeh, P. Å. Nilsson, N. Wadefalk, J. Mateos, J. Grahn, "Cryogenic performance of low-noise InP HEMTs: a Monte Carlo Study", in *IEEE Transactions on Electron Devices*, vol. 60, no. 5, pp. 1625-1631, May, 2013.

- [E] S. Weinreb and J. Schleeh, "Multiplicative and additive low frequency noise in microwave transistors", accepted for publication in *IEEE Microwave Theory and Techniques*, 2013.

- [F] J. Schleeh, H. Rodilla, N. Wadefalk, P. Å. Nilsson, J. Grahn, "Cryogenic noise performance of InGaAs/InAlAs HEMTs grown on InP and GaAs substrate", in *Solid-State Electronics*, vol. 91, pp. 74-77, Jan., 2014.

- [G] J. Schleeh, N. Wadefalk, P. Å. Nilsson, J. P. Starski, J. Grahn, "Cryogenic Broadband Ultra-Low Noise MMIC LNAs for Radio Astronomy Applications", in *IEEE Microwave Theory and Techniques*, vol. 61, no. 2, pp. 871-877, Feb., 2013.

### **Other papers**

The following papers are not included in the thesis due to overlap in content or a content going beyond the scope of this thesis:

- J. Schleeh, N. Wadefalk, P. Å. Nilsson, J. P. Starski, G. Alestig, J. Halonen,

B. Nilsson, A. Malmros, H. Zirath, J. Grahn, "Cryogenic 0.5-13 GHz Low

Noise Amplifier with 3 K mid-band noise temperature", in Proceedings of IEEE MTT-S International Microwave Symposium, 2012.

- [b] J. Schleeh, P. Å. Nilsson, J. P. Starski, N. Wadefalk, J. Grahn, "InP HEMTs Optimized for Ultra Low Noise Operation", Best paper award at *GigaHertz Symposium, Stockholm, Sweden*, 2012.

- [c] J. Schleeh, H. Rodilla, N. Wadefalk, P. Å. Nilsson, J. Grahn, "Cryogenic Ultra-Low Noise Amplification-InP PHEMT vs. GaAs MHEMT", in 25th International Conference on Indium Phosphide and Related Materials (IPRM 2013), p 99-100, 2013.

- [d] H. Rodilla, J. Schleeh, P. Å. Nilsson, J. Grahn, "Optimized InP HEMTs for low noise at cryogenic temperatures", in 24th International Conference on Indium Phosphide and Related Materials (IPRM 2012), p 241-4, 2012.

- [e] P. Å. Nilsson, H. Rodilla, J. Schleeh, N. Wadefalk, J. Grahn, "Influence of gate-channel distance in low-noise InP HEMTs ", in 25th International Conference on Indium Phosphide and Related Materials (IPRM 2013), p 103-4, 2013.

# Notations and abbreviations

### Notations

| $B_{\rm RF}$                    | Pre-detection bandwidth            |

|---------------------------------|------------------------------------|

| $C_{\rm gs}$                    | Gate-source capacitance            |

| $C_{\rm gd}^{\rm gs}$           | Gate-drain capacitance             |

| $C_{\rm ds}^{\rm su}$           | Drain-source capacitance           |

| $C_{\rm pg}$                    | Gate pad capacitance               |

| $C_{\rm pd}$                    | Drain pad capacitance              |

| <sub>pa</sub><br>٤ <sub>r</sub> | Relative permittivity              |

| f                               | Frequency                          |

| $f_{\rm max}$                   | Maximum oscillation frequency      |

| $f_{\rm T}$                     | Cut-off frequency                  |

| $g_{\rm m}$                     | Transconductance                   |

| $G_{ m ds}$                     | Output conductance                 |

| G                               | Gain                               |

| $I_{\rm d}$                     | Drain current                      |

| Ids                             | Drain-source current               |

| $I_{\rm DD}$                    | Drain current to LNA               |

| Ig                              | Gate current                       |

| Ĺg                              | Gate inductance                    |

| $L_{\rm d}$                     | Drain inductance                   |

| $L_{\rm s}$                     | Source inductance                  |

| μ                               | Mobility                           |

| n <sub>s</sub>                  | Sheet carrier concentration        |

| q                               | Elementary Charge                  |

| $R_{\rm c}$                     | Contact resistance                 |

| $R_{\rm d}$                     | Drain resistance                   |

| Rg                              | Gate resistance                    |

| Ri                              | Intrinsic gate-source resistance   |

| Rj                              | Intrinsic gate-drain resistance    |

| $R_{\rm s}$                     | Source resistance                  |

| $R_{\rm sh}$                    | Sheet resistance                   |

| $R_{\rm on}$                    | on-resistance                      |

| $T_{\rm e}$                     | Noise temperature                  |

| $T_{\rm e,min}$                 | Minimum measured noise temperature |

| $T_{\rm e,avg}$  | Average noise temperature               |

|------------------|-----------------------------------------|

| $T_{\rm d}$      | Equivalent drain resistance temperature |

| $T_{ m g}$       | Equivalent gate resistance temperature  |

| $T_{\rm min}$    | Minimum noise temperature               |

| $T_{\rm sys}$    | System noise temperature                |

| $V_{\rm d}$      | Drain voltage                           |

| $V_{\rm ds}$     | Drain-source voltage                    |

| $V_{\rm DD}$     | Drain voltage applied to LNA            |

| $V_{ m g}$       | Gate voltage                            |

| $V_{\rm gs}$     | Gate-source voltage                     |

| $V_{i}$          | Input noise voltage                     |

| $V_{ m IN}$      | Input voltage                           |

| $V_{\rm OUT}$    | Output voltage                          |

| $V_{\mathrm{T}}$ | Threshold voltage                       |

| W                | Transistor width                        |

### Abbreviations

| 2-DEG  | Two Dimensional Electron Gas                  |  |  |

|--------|-----------------------------------------------|--|--|

| ALD    | Atomic Layer Deposition                       |  |  |

| DSN    | Deep Space Network                            |  |  |

| GaAs   | Gallium Arsenide                              |  |  |

| HBT    | Heterojunction Bipolar Transistor             |  |  |

| HEMT   | High Electron Mobility Transistor             |  |  |

| InP    | Indium Phosphide                              |  |  |

| LNA    | Low Noise Amplifier                           |  |  |

| MBE    | Molecular Beam Epitaxy                        |  |  |

| MC     | Monte Carlo                                   |  |  |

| MESFET | Metal-Semiconductor Field Effect Transistor   |  |  |

| MIM    | Metal-insulator-metal                         |  |  |

| MMIC   | Monolithic Microwave Integrated Circuit       |  |  |

| NGAS   | Northrop Grumman Aerospace Systems            |  |  |

| NF     | Noise Figure                                  |  |  |

| mHEMT  | Metamorphic High Electron Mobility Transistor |  |  |

| PECVD  | Plasma Enhanced Chemical Vapor Deposition     |  |  |

| SiGe   | Silicon Germanium                             |  |  |

| SKA    | Square Kilometer Array                        |  |  |

| TFR    | Thin Film Resistor                            |  |  |

| TMA    | Trimethylaluminium                            |  |  |

| VLBI   | Very Long Baseline Interferometry             |  |  |

|        |                                               |  |  |

# Contents

| A  | bstrac  | t                                             | iii |

|----|---------|-----------------------------------------------|-----|

| Li | st of p | oublications                                  | v   |

| N  | otatio  | ns and abbreviations                          | vii |

| 1. | Intro   | oduction                                      | 1   |

| 2. | InP     | HEMT Technology                               | 3   |

|    | 2.1     | Epitaxial design                              |     |

|    | 2.2     | Gate recess design                            | 5   |

|    | 2.3     | Device passivation                            | 7   |

|    | 2.4     | Parasitic access resistances                  | 9   |

|    | 2.5     | State-of-the-art ultra-low noise InP HEMTs    |     |

|    | 2.6     | Conclusions                                   | 12  |

| 3. | InP     | HEMT Characterization                         | 13  |

|    | 3.1     | Noise sources in the InP HEMT                 |     |

|    |         | 1.1 Microwave noise                           |     |

|    |         | 1.2 Low-frequency noise and gain fluctuations |     |

|    | 3.2     | Monte Carlo simulations                       |     |

|    | 3.3     | DC Characterization                           |     |

|    | 3.4     | Microwave Characterization                    |     |

|    | 3.5     | Noise Characterization                        |     |

|    |         | 5.1 Microwave Noise Characterization          |     |

|    | 3.      | 5.2 Low Frequency Noise Characterization      |     |

|    | 3.6        | Conclusions                                                                                                           | . 30 |

|----|------------|-----------------------------------------------------------------------------------------------------------------------|------|

| 4. | GaAs       | mHEMT comparison                                                                                                      | 31   |

|    | 4.1        | DC and microwave comparison                                                                                           | . 31 |

|    | 4.2        | Noise comparison                                                                                                      | . 34 |

|    | 4.3        | Conclusions                                                                                                           | . 35 |

| 5. | InP H      | IEMT MMIC Technology                                                                                                  | 37   |

|    | 5.1        | MMIC design                                                                                                           | .37  |

|    | 5.2<br>5.2 | <ul><li>0.5-13 GHz Ultra Broadband Ultra Low Noise InP MMIC LNA</li><li>1 Measurements and Characterization</li></ul> |      |

|    | 5.3<br>5.3 | <ul><li>24-40 GHz Low Noise InP MMIC LNA</li><li>1 Measurements and Characterization</li></ul>                        |      |

|    | 5.4        | Conclusions                                                                                                           | . 45 |

| 6. | Conc       | lusions                                                                                                               | 47   |

| 7. | Futur      | re Work                                                                                                               | 49   |

### Chapter 1.

### Introduction

Human knowledge is expanding in all directions. Astronomers look deeper into space, and physicists discover new quantum particles. As evidence for these findings often consists of ultra-weak electromagnetic signals, the demand for lower noise reception is substantial. To accommodate this advancement, today's ultra-low noise technology needs to be pushed further.

By cryogenically cooling the low noise amplifier (LNA) to around 10 K, thermal noise is strongly reduced. Today, the indium phosphide high electron mobility transistor (InP HEMT) is the established technology for cryogenic ultra-low noise microwave amplification [1]. Record average noise temperature of 1.8 K in a 4-8 GHz LNA was demonstrated already ten years ago [2]. Since then, reported progress in further reducing noise temperature has been absent.

One reason is a shifted research focus toward higher frequencies, with an attempt to overlap the THz gap. Ultra-scaled HEMTs today have gate lengths of 35 nm and below. These HEMTs enable very high frequency of operation, with  $f_T$  and  $f_{max}$  approaching 1 THz, but suffer from elevated gate leakage currents, reduced quality of pinch-off, and an increased cryogenic noise temperature at microwave frequencies as a result.

A second reason is that cryogenic LNAs normally are designed with InP HEMTs intended for room temperature operation. Excellent noise performance at room temperature does however not necessarily imply good noise performance at cryogenic temperature [3]. To push the ultra-low noise technology even further, the InP HEMT needs to be directly optimized for cryogenic operation at the intended frequency band.

In this thesis, new state-of-the-art cryogenic ultra-low noise InP HEMT is reported. By using an optimized epitaxial design and HEMT process, state-of-the-art device performance has been achieved for cryogenic amplification up to around 40 GHz.

A number of alternative technologies for LNAs have been reported in the literature. The less expensive metamorphic InGaAs/InAlAs/GaAs HEMT has proven competitive with the InP HEMT with respect to cut-off frequency  $f_T$  and noise figure (NF) at room temperature. However, at cryogenic temperature operation, the noise is still considerably higher than the InP HEMT [4]. The more narrow bandgap InAs/AlSb HEMT, with potentially very good low noise properties at extremely low power dissipation, still

suffers from high gate current, high output conductance and impact ionization degrading the noise performance [5]. Also the SiGe heterojunction bipolar transistor (HBT) has been investigated for cryogenic low noise operation. It is suitable for applications requiring extremely stable transconductance  $g_m$ , but tolerating higher noise temperature than the InP HEMT technology [6]. An example is the wideband radiometer which becomes gain stability limited by its chopping rate.

In Chapter 2, a description of the low-noise optimized InP HEMT technology is given. The gate recess, a novel passivation method utilizing atomic layer deposition (ALD), and access resistance considerations are discussed, and concluded with an example of a state-of-the-art noise result. In Chapter 3, the InP HEMT technology is analyzed with respect to DC, RF, low-frequency and microwave frequency noise. The characterization is based on both electrical measurements and Monte Carlo (MC) simulations. In Chapter 4, the InP HEMT technology is compared with the similar GaAs mHEMT technology. Finally in chapter 5, the cryogenic ultra-low noise InP HEMT technology developed in this work is demonstrated in a full MMIC LNA process.

# Chapter 2.

# **InP HEMT Technology**

The noise performance of the cryogenic LNA is intimately coupled to the transistor in use. A key quest for this thesis is therefore to evaluate how the transistor technology can be improved. The InP HEMT technology is today a technology for high-performance transceivers up to several hundreds of GHz. The unique low noise properties are a result of the high gain and transconductance, in combination with the lateral topology reducing electron scattering (opposite to the HBT vertical topology forcing current through interfaces). However, the properties are not necessarily optimized for cryogenic low-noise applications.

In this Chapter, a state-of-the-art cryogenic low noise InP HEMT technology is presented. Four aspects in the InP HEMT have been subject to study: epitaxial design, gate recess formation, device passivation and access resistances. Their impacts on device performance are temperature dependent, which makes them key components in the optimization of cryogenic InP HEMTs.

The InP HEMTs were formed by mesa etching, ohmic contact formation, gate patterning using electron-beam lithography, followed by contact pad formation, device passivation, and air bridge formation. For more details on the device fabrication, see paper [B].

In the end of the chapter, a record noise result obtained by this InP HEMT technology is demonstrated.

### 2.1 Epitaxial design

The purpose of the InP HEMT structure is to increase mobility without loss of sheet carrier concentration by separating the free electrons from their donor impurities. At cryogenic conditions, where the electron mean free path is less limited by thermal scattering, impurity locations and geometric boundaries become even more important design properties.

The epitaxial layers, grown from bottom to top on InP substrate, are buffer, channel, spacer (part of barrier), delta doping, barrier and cap. The purpose of the buffer is to overgrow dislocations and defects of the rough InP wafer and enable a crystalline base

|           | Material                                 | Doping                                                         | Thickness  |

|-----------|------------------------------------------|----------------------------------------------------------------|------------|

| Cap       | In <sub>0.53</sub> Ga <sub>0.47</sub> As | $_{40.47}$ As Si: $5 \times 10^{19}$ cm <sup>-3</sup> 10-20 nm |            |

| Barrier   | $In_{0.52}Al_{0.48}As$                   |                                                                | 8-11 nm    |

| δ-doping  |                                          | Si: $5 \times 10^{12} \text{ cm}^{-2}$                         |            |

| Spacer    | $In_{0.52}Al_{0.48}As$                   |                                                                | 3 nm       |

| Channel   | In <sub>0.65</sub> Ga <sub>0.35</sub> As |                                                                | 15 nm      |

| Buffer    | $In_{0.52}Al_{0.48}As$                   |                                                                | 250-500 nm |

| Substrate | InP                                      |                                                                | 75-100 μm  |

#### TABLE 2.1 EPITAXIAL STRUCTURE OF INVESTIGATED INP HEMTS

for the following epitaxial layers. The indium content of the channel should be maximized without introducing too much strain with risk for reduced mobility or even lattice dislocations. The spacer layer thickness must be carefully optimized to completely separate the delta doping from the 2-dimensional electron gas (2-DEG) without loss of sheet carrier concentration and formation of a parasitic channel. The thickness and composition of the barrier layer highly determines the gate Schottky diode, device transconductance, threshold voltage and access resistance between channel and cap layer. The cap layer should be designed with high doping concentration for lowest possible access resistance.

In general the channel is scaled toward higher indium content, and consequently reduced thickness when aiming for high frequency performance. In the same way a reduction of the barrier thickness improves transconductance, but increases capacitance, limits the breakdown voltage and most importantly increases the gate leakage current. The cap layer is limited in thickness due to gate formation difficulties.

The HEMT epitaxial structure used in this thesis were grown on 2" to 4" InP wafers by molecular beam epitaxy (MBE). The epitaxial structures used are shown in TABLE 2.1.

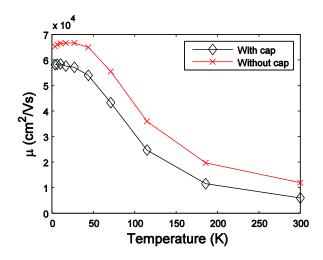

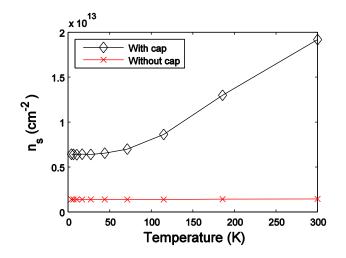

Hall measurements were performed at temperatures between 4 K and 300 K as described in paper [D]. As the majority of the electrons were situated in the highly doped cap layer, this had to be removed to separately measure the channel. The cap removal was done using the succinic acid solution used for the gate recess in section 2.2. The temperature dependence of the electron mobility  $\mu$  and sheet carrier concentration  $n_s$  are plotted in Fig. 2.1 and Fig. 2.2.

At room temperature,  $\mu$  was measured to 6000 cm<sup>2</sup>/Vs with cap, and 12000 cm<sup>2</sup>/Vs with cap etched away. When cooled to 10 K,  $\mu$  improved to 58000 cm<sup>2</sup>/Vs with cap, and 66000 without cap. The sheet carrier concentration  $n_s$ , with cap, dropped from  $19 \times 10^{12}$  cm<sup>-2</sup> at 300 K to  $6.4 \times 10^{12}$  cm<sup>-2</sup> at 10 K. With cap etched away,  $n_s$  was  $1.4 \times 10^{12}$  cm<sup>-2</sup>, independent of temperature.

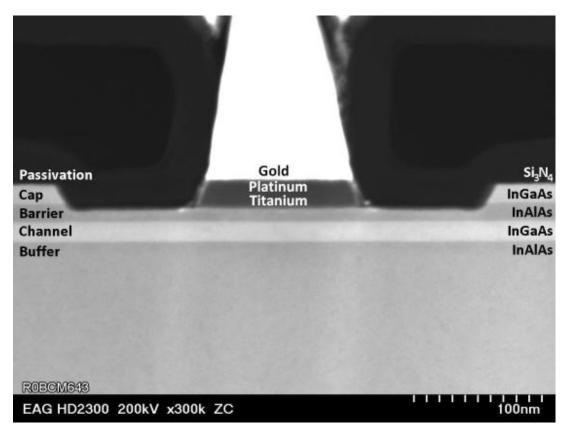

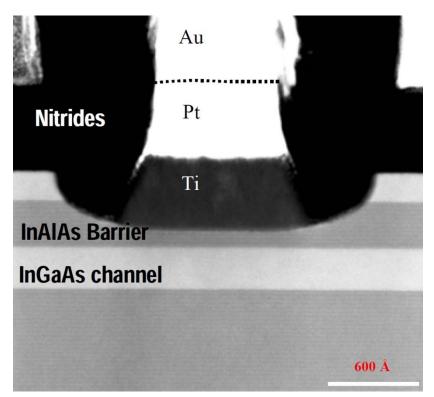

A STEM image of the cross section of the gate region, with marked epitaxial layers, is shown in Fig. 2.3. The micrograph confirms the thicknesses of the designed layers of the InP heterostructure in TABLE 2.1, and shows no sign of material imperfections. Another InP HEMT cross section, developed by Northrop Grumman Aerospace Systems (NGAS) for high frequency operation at room temperature, is shown in Fig. 2.4 [7]. Compared to the epitaxial structure in this thesis, the structure is observably similar, but the layer thicknesses are much larger.

Fig. 2.1. Temperature dependence of electron mobility extracted from Hall measurements of InP HEMT epitaxial structure. The measurement was done both with 20 nm cap layer and with cap etched away using the succinic gate recess solution used in section 2.2. Courtesy of Dr. Helena Rodilla.

Fig. 2.2. Temperature dependence of sheet carrier concentration extracted from Hall measurements of InP HEMT epitaxial structure. The measurement was done both with 20 nm cap layer and with cap etched away using the succinic gate recess solution used in section 2.2. Courtesy of Dr. Helena Rodilla.

### 2.2 Gate recess design

The gate recess is by far the most critical step in the InP HEMT process. The main purpose of the recess is to remove the highly doped cap layer before forming the gate. With cap residues left under the gate, the Schottky contact between gate metal and barrier is deteriorated. As a result, gate leakage current levels are increased and gate control is deteriorated.

Fig. 2.3. Cross sectional STEM image of the gate region of the 130 nm InP HEMT developed in this thesis.

Fig. 2.4. Cross sectional STEM image of the gate region of a 100 nm InP HEMT from Northrop Grumman Aerospace Systems. Compared to Fig. 2.3, the gate recess is more belly shaped due to a different gate recess method. Courtesy of Dr. Richard Lai. [7]

However, even with the entire cap removed, both depth and width of the gate recess influence device characteristics. To avoid unnecessary parasitic capacitance, source, drain and gate potentials need to be separated with a wide enough gate recess. On the other hand, a wide gate recess increases the parasitic access resistance from the contacts to the intrinsic channel. Also the breakdown voltage is affected by the gate recess width as the electric field between the three nodes is increased with decreasing distance.

Another factor limiting the gate recess width, and etch method, is the formation of imperfections and electrical traps deteriorating device performance. By minimizing the recess width, the area with traps is minimized. But to fully suppress their impact, optimized device passivation needs to be performed.

The depth of the recess strongly influences the threshold voltage and the gate leakage current. The closer the gate Schottky barrier is situated to the channel, the more carriers are depleted from the channel, resulting in an increased threshold voltage. Similarly, with a shorter gate to channel distance, the gate Schottky threshold is reduced, meaning a less positive gate potential is needed for a positive gate current. Ultimately, for a useful transistor behavior, the threshold voltage needs to be lower than the gate Schottky threshold voltage; hence giving a limit to the gate recess depth.

In InP HEMT MMIC production, based on carefully extracted transistor models from previous production batches, the gate recess needs to be precisely controlled from wafer run to wafer run. This is done by carefully controlling the etch solution composition, temperature and etch time. If this cannot be done precisely enough, a highly selective etch solution can be used. The selectivity, defined as the ratio between etch speed in the cap and barrier materials, is determined by the relative concentrations of acid and oxidizer in the etch solution. A highly selective etch solution will remove the cap quickly, but slow down when reaching the barrier layer, making etch time less critical. Using a thin InP etch stop layer between the cap and barrier layers can increase the selectivity even further (not done in this work).

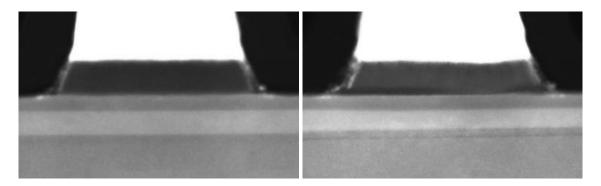

For the gate recesses process in this work, a highly selective succinic acid solution was used. The shape of the gate recess can be seen in Fig. 2.3. In Fig. 2.4, showing the NGAS InP HEMT cross section, a non-selective recess etch is used. Compared to the gate recess of the InP HEMTs in this work, which is wide and flat, the recess is much narrower and has a belly shape.

### **2.3 Device passivation**

The surface created by the gate recess is a crystal boundary, with all its defects, located in direct connection with the intrinsic transistor. Passivation of these surface-related defects is of largest importance for the final electric device performance.

The standard passivation method for InP HEMTs is to deposit  $Si_3N_4$  by plasma enhanced chemical vapor deposition (PECVD) [8, 9]. In this thesis, also a new passivation method for InP HEMTs has been tested. The method, atomic layer deposition (ALD) depositing  $Al_2O_3$  is a previously untested passivation method for InP HEMTs. The benefit with ALD compared to PECVD is the inherent thickness control and uniformity [10]. Improved device performance has been reported for ALD  $Al_2O_3$ passivation of AlGaN/GaN HEMTs and GaAs MESFETs [11, 12].

To compare the two methods, pieces from the same test wafer were either passivated with the standard  $Si_3N_4$  PECVD deposited at 300°C or  $Al_2O_3$  ALD at 250°C with

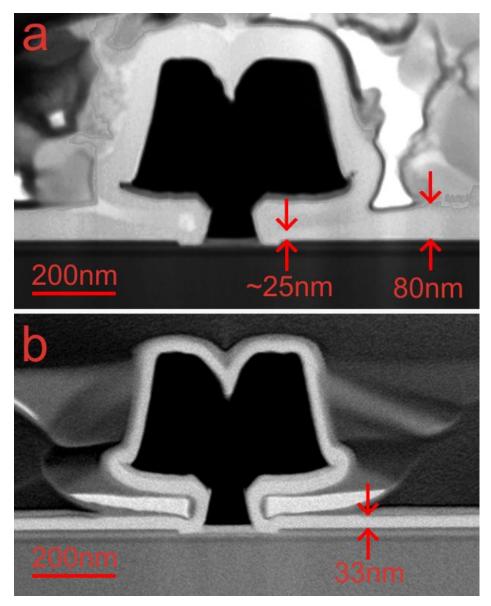

Fig. 2.5: TEM image of the gate region of a)  $Si_3N_4$  PECVD and b)  $Al_2O_3$  ALD passivated InP HEMT. The thickness of the passivation is marked.

trimethylaluminium (TMA) as Al precursor and  $H_2O$  as oxygen precursor. Details about the study are given in paper [A].

Fig. 2.5 shows cross sectional STEM images of two InP HEMTs passivated with either the PECVD or ALD method. As seen in Fig. 2.5a, the thickness of the PECVD deposited  $Si_3N_4$  layer was around 80 nm. The ALD passivation was performed in 300 cycles during one hour resulting in a total  $Al_2O_3$  thickness of 33 nm. As seen in Fig. 2.5, the ALD passivation layer was fully uniform, whereas the PECVD passivation layer thickness was reduced at the most important area under the gate hat.

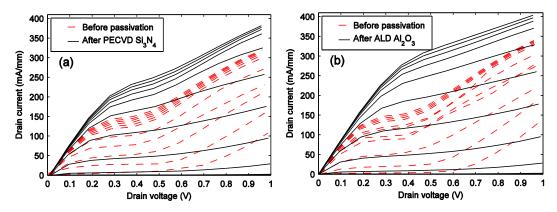

DC measurements were performed both before and after the device passivation. Smallsignal microwave measurements were performed after device passivation. I-V device characteristics before and after passivation are shown in Fig. 2.6. The unpassivated InP HEMT typically exhibited a maximum drain current density of 340 mA/mm. The maximum extrinsic transconductance before passivation was 0.6 S/mm at  $V_{ds} = 1$  V. The

Fig. 2.6: I-V characteristics of  $2x50 \ \mu m$  InP HEMTs before and after passivation with (a) PECVD Si<sub>3</sub>N<sub>4</sub> and (b) ALD Al<sub>2</sub>O<sub>3</sub>. Gate voltage was swept in steps of 0.1 V from -0.4 V (lower curve) to 0.6 V (upper curve).

gate current was around 1  $\mu$ A/mm with a dip to 4  $\mu$ A/mm under impact ionization, which appeared for  $V_{ds}$  above 0.8 V. All unpassivated devices showed the same kink phenomena in accordance with [13]. For this low bias region, this is considered to be a consequence of surface traps in the sensitive recess area adjacent to the gate, and not impact ionization.

Irrespective of passivation method, an increase in maximum drain current density with about 20% was observed; see Fig. 2.6. The change in gate current was negligible for both passivation methods. A significant difference between PECVD and ALD passivated HEMTs was observed in the reduction of the kink in the I-V characteristics; As seen in Fig. 2.6, the kink was fully suppressed for the ALD passivated devices whereas only a minor improvement could be seen for the PECVD devices indicating that the ALD is superior to PECVD in passivation of surface traps in the InP HEMTs. One explanation for the superior ALD passivation is the dramatic reduction of Ga<sup>3+</sup> and As<sup>3+</sup> oxidation states after the first TMA half cycle of ALD as previously reported in Ref. [14] for In<sub>0.2</sub>Ga<sub>0.8</sub>As. Similar mechanisms may also be valid for the passivation of the In<sub>0.4</sub>Al<sub>0.6</sub>As barrier for the InP HEMTs in this study.

A reduction of the output conductance was evident after both passivation methods. An increase in maximum extrinsic transconductance of about 30% was observed regardless of passivation method.

No obvious difference in  $C_{gd}$  (160 fF/mm) and  $C_{gs}$  (800 fF/mm) between ALD and PECVD passivated HEMTs was seen. This is explained by the higher relative permittivity of the thin ALD Al<sub>2</sub>O<sub>3</sub> ( $\varepsilon_r = 9.8$ ) passivation compared to the thicker PECVD Si<sub>3</sub>N<sub>4</sub> ( $\varepsilon_r = 7$ ), resulting in similar effective permittivity. A further reduction of the ALD Al<sub>2</sub>O<sub>3</sub> thickness is expected to reduce the parasitic capacitances and enhance the device RF performance.

#### 2.4 Parasitic access resistances

Access resistances are key parameters in the optimization of low noise HEMTs [3]. One reason for superior performance at cryogenic temperatures is the reduction of parasitic resistances with temperature. As the electron-phonon scattering decreases with temperature, both semiconductor and metal sheet resistances decreases. However, as the

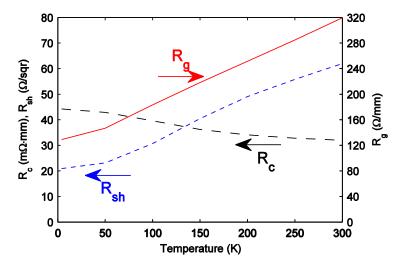

Fig. 2.7: Temperature dependence of  $R_{\rm g}$ ,  $R_{\rm sh}$  and  $R_{\rm c}$ .

ohmic contact resistance  $R_c$  increases with reduced temperature, the total access resistance might not improve at all.

To optimize  $R_c$  and the epitaxial sheet resistances  $R_{sh}$  for the InP HEMTs the thickness and Si doping of the cap layer was increased from 10 nm and  $1 \times 10^{19}$  cm<sup>-3</sup> to 20 nm and  $5 \times 10^{19}$  cm<sup>-3</sup>, respectively. With a metal stack consisting of Ni/Ge/Au and an annealing temperature of 280 °C,  $R_c$  of 0.03  $\Omega$ ·mm at 300 K was obtained. But most importantly as seen in Fig. 2.7, when cooled down to 4 K,  $R_c$  only increased incrementally to 0.04  $\Omega$ ·mm.

The gate resistance  $R_g$ , optimized using a 130 nm T-gate technology, decreased from 320  $\Omega$ /mm at 300 K to 120  $\Omega$ /mm at 4 K. Also  $R_{sh}$  was improved from 60  $\Omega$ / $\Box$  at 300 K to 20  $\Omega$ / $\Box$  at 4 K. Notable is that  $R_{sh}$  and  $R_g$  decrease linearly between 300 K and 50 K, where they start to saturate. This means that at temperatures below 50 K the main limitation for the carrier mobility is not phonon scattering, but rather boundary scattering as the mean free path of the electrons becomes comparable to the geometrically small gate and epitaxial dimensions.

It is observed that  $R_c$  and  $R_{sh}$  obtained in this work are 40-60 % and 50-70%, respectively, better than an optimized 100 nm gate length GaAs MHEMT technology with a very similar temperature dependence [4].  $R_g$  is observed to be similar to [4].

The resulting source and drain resistance  $R_s$  and  $R_d$ , used in small signal modeling, was 0.13  $\Omega$ ·mm and 0.14  $\Omega$ ·mm at 6 K, and 0.24  $\Omega$ ·mm and 0.26  $\Omega$ ·mm at 300 K, respectively.

#### 2.5 State-of-the-art ultra-low noise InP HEMTs

Utilizing the reported above, a new state-of-the-art 130 nm gate length ultra-low noise InP HEMT could be demonstrated, see paper [B]. Key changes were the increase of cap thickness and doping, improved gate recess using highly selective succinic acid and optimized ohmic contacts with small temperature dependence. Since no systematic study on the InP HEMT temperature dependence for different device passivations was carried out, the standard PECVD  $Si_3N_4$  passivation was eventually chosen for the optimized ultra-low noise InP HEMT

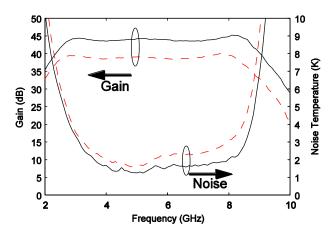

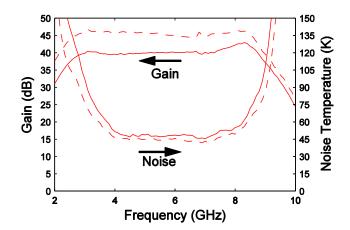

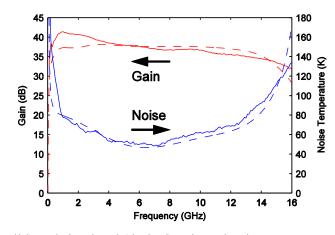

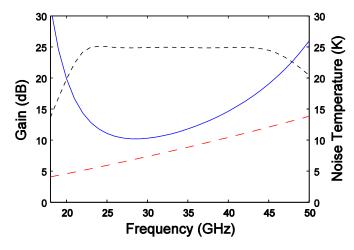

Fig. 2.8: Comparison of gain and noise temperature between 4x50 um InP HEMTs in this study (black curves) and previous state-of-the-art Cryo3 InP HEMTs [2] (red curves) measured at ambient temperature of 10 K in the same LNA in the same measurement system. The amplifier was in both cases biased at optimum low noise bias. Bias for the InP HEMTs in this thesis work was Vd=0.45V and Id=9.3mA. Bias with Cryo3 InP HEMTs was Vd=0.6V and Id=10mA.

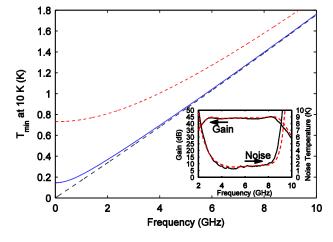

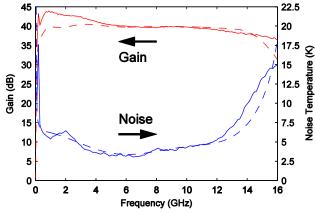

The noise temperature and gain as a function of frequency at 10 K of a 4-8 GHz LNA equipped with these 130 nm InP HEMTs is shown by the solid black curve in Fig. 2.8. [2]. A lowest noise temperature  $T_{e,min}$  of 1.2 K was measured at 5.2 GHz. Across the 4-8 GHz band, the average noise temperature  $T_{e,avg}$  was 1.6 K. Moreover, the average gain of the amplifier was 44 dB, with input and output return loss better than 15 dB, in the entire band. The total power consumption of the LNA at the optimum low noise bias was only 4.2 mW. The extracted  $T_{min}$  at 10 K, shown in Fig. 2.9, was 1 K at 6 GHz.

When the LNA was biased for ultra-low power consumption of 0.33 mW ( $V_{DD} = 0.1$  V,  $I_{DD} = 3.3$  mA), the in-band noise temperature and gain still exhibited numbers of 2.5-4.3 K and 27-34 dB, respectively. At room temperature, the measured LNA noise temperature was typically 25-30 K with a gain of 44 dB at a power consumption of 56 mW ( $V_{DD} = 1.25$  V,  $I_{DD} = 45$  mA).

In TABLE 2.2, the results are compared to previously published state-of-the art LNAs operating in the same frequency band at 10-15 K ambient temperature. When equipped with the InP HEMTs from this work, the 4-8 GHz LNA exhibited a significantly lower  $T_{e,min}$  and  $T_{e,avg}$  than previously published results. The difference in gain per mW dissipated power was even larger, and almost a factor of two higher than the second best result [15].

As the measured noise temperature of cryogenic LNAs is extremely low, measurement uncertainties make indirect comparisons between different labs difficult. To validate the state-of-the-art result, 100 nm gate length InP HEMTs with 4x50  $\mu$ m device size used in [2] (Cryo3 devices) were benchmarked against the InP HEMTs in this thesis using the same 4-8 GHz LNA and identical measurement procedure. The comparison, measured at the optimum low noise bias point of each HEMTs at 10 K, is shown in Fig. 2.8. The average noise temperature with the Cryo3 InP HEMTs was 2.2 K with an average gain of 39 dB. Hence 0.6±0.1 K better LNA noise performance was obtained when equipped with InP HEMTs from this thesis compared to the Cryo3 InP HEMTs used in [2].

The superior low noise performance of the InP HEMT is believed to be a result of the optimized epitaxial structure and gate recess resulting in high transconductance and  $f_{\rm T}$  at low drain current. Also the low access resistances were a prerequisite for this low noise temperature. Finally the low gate current enabled the InP HEMTs to perform well at very

| Ref.      | Freq.<br>(GHz) | $T_{\rm e,min}({\rm K})$ | $T_{\rm e,avg}$ (K) | Gain/stage (dB) | Gain/power<br>(dB/mW) |

|-----------|----------------|--------------------------|---------------------|-----------------|-----------------------|

| This work | 4-8            | 1.2                      | 1.6                 | 14.7            | 10.5                  |

| [2]       | 4-8            | 1.4                      | 1.8                 | 13.5            | 2.5                   |

| [15]      | 4-8            | 3.1                      | 3.5                 | 13.5            | 6.8                   |

| [16]      | 4-12           | 3.3                      | 4.5                 | 11.3            | -                     |

| [17]      | 4-12           | 2.7                      | 3.5                 | 13.7            | 1.7                   |

TABLE 2.2 DATA FOR STATE OF THE ART  $4x50 \mu M$  INP HEMT LNAS AT 10-15 K

Fig. 2.9: Extracted  $T_{min}$  of a 4x50 µm InP HEMT exhibiting 20 nA/mm gate current at 10 K (blue solid) compared with the same device without gate current (black long dash) and with 0.5 µA/mm gate current (red short dash). The InP HEMT was biased at  $V_{ds} = 0.35$  V and  $I_d = 3.1$  mA. Inset shows a comparison between simulated (red dashed) and measured (black solid) noise temperature and gain of the 3-stage LNA using an extracted transistor model.

low frequencies where shot noise from the gate Schottky barrier normally limits performance. In Fig. 2.9 the importance of low gate current is emphasized by showing two modeled InP HEMTs either with zero gate current or with a representative gate current of  $0.5 \,\mu$ A/mm.

### 2.6 Conclusions

Ultra-low-noise InP HEMTs with 130 nm gate length have been designed and fabricated for cryogenic temperature operation. The epitaxial structure has been developed for high mobility and sheet carrier concentration, in combination with minimized access resistances. The gate recess has been optimized for high gate control, low gate leakage current and process repeatability. Compared to the InP HEMT produced by NGAS, the gate recess in this thesis work was flat and wide due to the selective etch method.

Different passivation methods were tested. The ALD method better removed trap related I-V-kinks than the PECVD passivation. With respect to RF, no significant difference was found.

Based on noise measurements of a 4-8 GHz 3-stage hybrid IF LNA, extracted  $T_{min}$  of an InP HEMT fabricated in this thesis work was 1 K at 6 GHz.

## Chapter 3.

## **InP HEMT Characterization**

To characterize InP HEMTs with respect to low noise under cryogenic conditions around 10 K is a complex task. There are several noise sources in the InP HEMT which exhibit both bias and temperature dependence.

This Chapter starts with a brief background to the noise sources in an InP HEMT. A differentiation between low-frequency and microwave noise characterization is done. After this, the Monte Carlo (MC) simulation method is shortly described. The MC simulations, based on experimental results, are used to explain the mechanisms behind the intrinsic transistor behavior. Following, the DC and microwave characteristics, and how they are related to noise performance are discussed. Finally, the chapter is ended with noise results and discussions both related to low-frequency and microwave noise properties.

#### **3.1** Noise sources in the InP HEMT

The most important physical noise sources in semiconductor devices are thermal noise, generation-recombination noise, shot noise, hot-electron noise and low-frequency (1/f) noise [18]. Depending on application and operation, each and every one of these noise sources can be anything from negligible to the solely dominant source. For InP HEMTs, at high frequencies >20 GHz, the hot-electron noise and thermal noise from the heavily scaled transistor geometries are the dominant sources. At intermediate frequencies between 1 and 20 GHz, also shot noise from the gate Schottky diode can become a strong noise source if gate leakage current is present. At even lower frequencies, below 1 GHz, the low-frequency 1/f noise becomes dominant. Moreover, at room temperature, the thermal noise contribution is strong for all frequencies above the 1/f noise limit, while its contribution at cryo temperatures is strongly reduced. In this thesis, a distinction between the low-frequency 1/f noise and microwave frequency noise characterization is made.

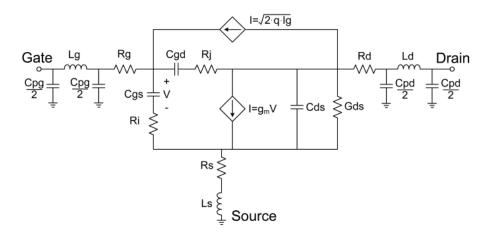

Fig. 3.1: Equivalent circuit of InP HEMT.

#### 3.1.1 Microwave noise

To predict the microwave noise behavior of InP HEMTs in relation to frequency, bias and ambient temperature, noise models based on small signal parameters are widely used [3, 19, 20]. In Fig. 3.1 the small signal model used for the InP HEMTs in this work is shown. For this model, omitting the gate current, an expression for the minimum noise temperature  $T_{min}$  was suggested by Pospieszalski [20]. If all resistive elements in the small signal model are equipped with temperatures and all noise sources are treated as thermal noise sources, an expression for the minimum noise temperature is obtained:

$$T_{min} \approx 2 \frac{f}{f_T} \sqrt{R_t T_g G_{ds} T_d}$$

(1)

$R_t = R_s + R_g + R_i$ ,  $G_{ds}$  is the output conductance and  $T_g$  and  $T_d$  are the gate and drain resistance temperatures respectively.  $T_g$  is usually set to ambient temperature while the  $T_d$  should be considered as a nonphysical fitting parameter accounting for the bias dependent hot electron noise contribution. In opposite to previous models, this model takes the drain current dependent hot-electron noise into consideration

In [3] only  $f_T$  and  $T_d$ , among the parameters in (1), are considered to be strong functions of transistor bias. Hence, the optimal bias for low noise operation is obtained by minimizing the value of

$$f(V_{ds}, I_{ds}) = \frac{\sqrt{I_{ds}}}{g_m} \tag{2}$$

as  $T_d$  to a first approximation is proportional to  $I_d$  and  $f_T$  is proportional to the transconductance  $g_m$ .

To account for the shot noise generated by the gate leakage in an InP HEMT a noise current source can be added to the small signal model in Fig. 3.1. At low leakage currents the shot noise can be treated as ideal Schottky noise and its contribution be estimated as

$$i = \sqrt{2qI_g} \tag{3}$$

where q is the elementary charge and  $I_g$  is the measured gate leakage current.

#### **3.1.2** Low-frequency noise and gain fluctuations

The low-frequency noise (also called 1/f noise, flicker noise or additive noise) has a power spectrum which varies inversely with frequency. The source of the noise is attributed to electrons trapped and released by lattice defects, impurities, and surface states [21, 22].

The gain fluctuation noise, also termed as multiplicative noise, is less well known but is an important factor for radiometer sensitivity and phase noise of oscillators [23]. It is the random fluctuation of the gain of a transistor and is small, of the order of  $10^{-4}$  to  $10^{-6}$  normalized to the average gain. It has a 1/f spectrum similar to that of the low frequency noise.

Since the transistor gain is a function of bias point, and the low-frequency noise affects the bias point, there is a coupling between 1/f noise and gain fluctuations. This coupling depends upon the type of bias circuit, i.e. in the case of FET transistors, constant gate voltage bias or constant drain current bias.

To understand the low frequency noise and gain fluctuations, the output voltage of a noisy amplifier can be written as,

$$V_{OUT} = G \cdot (V_{IN} + V_i) \tag{4}$$

where  $V_{OUT}$  is the rms output voltage, G is the voltage gain of the amplifier,  $V_{IN}$  is an applied rms input voltage from a source, and  $V_i$  is the input noise voltage of the amplifier. The gain fluctuation,  $\Delta G$ , is exposed by applying  $V_{IN} \gg V_i$  and normalizing to a measured  $V_{OUT}$  to give,

$$\frac{\Delta G}{G} = \frac{\Delta V_{OUT}}{V_{OUT}}\Big|_{V_{IN} \gg V_i}$$

(5)

The input noise voltage,  $V_i$ , is determined by setting the applied source voltage to zero and measuring the rms output voltage to give

$$V_i = \frac{V_{\text{OUT}}}{G}\Big|_{V_{IN}=0} \tag{6}$$

This input noise voltage includes the thermal noise of the source, which needs to be subtracted from the measurement.

#### **Radiometer Sensitivity Degradation**

The rms sensitivity,  $\Delta T$ , of a Dicke radiometer, per root Hz of post detection bandwidth (equal to  $1/(2\tau)$  where  $\tau$  is the integration time), can be expressed as

$$\frac{\Delta T}{T_{sys}} = 2 \cdot \sqrt{\frac{2}{B_{RF}} + 4 \cdot W \cdot S \cdot N \cdot \left(\frac{\Delta G}{G}\right)^2}$$

(7)

where  $T_{\text{sys}}$  is the system noise temperature,  $B_{RF}$  is the pre-detection bandwidth,  $\Delta G/G$  is the fractional voltage gain fluctuation per root Hz, N is the number of stages, W is a transistor width scaling factor, and S accounts for the feedback stabilization of gain of each stage. This equation, and the realization that that the power gain fluctuation squared,  $(\Delta G_p/G_p)^2 = 4(\Delta G/G)^2$ , is described in previous works [24, 25].

The factor W is the ratio of transistor width used for fluctuation measurement (i.e. 200um) to width of transistors used in the radiometer and results from the consideration that transistor in parallel will add  $\Delta G$  as root sum squares while G adds linearly; thus,  $\Delta G/G$  increases as root W. The factor N is due to cascading of stages and increases  $\Delta G/G$  as root N. The factor S is due to feedback stabilization in an amplifier where the feedback may be due to source inductance or drain to gate capacitance. It is best determined by a circuit simulation where  $g_m$  is varied and the resulting change in S21 is computed.

It is convenient to express the radiometer sensitivity degradation, D, in terms of the ratio of  $\Delta T$  to the value with no gain fluctuation,

$$D = \sqrt{1 + 2 \cdot W \cdot S \cdot N \cdot B_{RF} \cdot \left(\frac{\Delta G}{G}\right)^2}$$

(8)

As a realistic example of a millimeter wave radiometer with W=200/40, S=0.6, N=9 stages,  $B_{RF}=10$  GHz, and  $\Delta G/G = 20$ ppm at 1 Hz and 2ppm at 1 kHz, we find D=9.3 and 1.2 respectively. Note that the degradation does not depend upon integration time; it depends upon  $\Delta G/G$  at the chop rate of the radiometer. Given the 1/*f* dependence fast chopping rates are needed for wide bandwidth radiometers.

#### **3.2 Monte Carlo simulations**

The MC simulation method is a powerful technique to understand the physical mechanisms behind the InP HEMT operation [26-30]. As the method simulates the electron movements and interactions in the time domain, it can also accurately predict noise performance. This, in combination with accounting for the ballistic transport, present in these devices due to the high mobility of the channel, makes MC the most appropriate simulation technique for studying low-noise properties of InP HEMTs.

The simulations can safely be performed in a two-dimensional environment as the device is homogeneous along the gate width. The MC simulator used in this work, developed by Dr. Rodilla and further described in paper [D], is a development of a previously established 300 K simulator [29, 31, 32].

The conventional operating temperature of cryogenic LNAs is 4-15 K. Due to quantum effects, the MC simulations could not be performed with accuracy at equally low temperatures. Instead, 77 K was chosen due to the large quantity of experimental material data available at this temperature. For the DC and RF experimental behavior of the cryogenic InP HEMT, there is little difference between 77 K and 10 K operation.

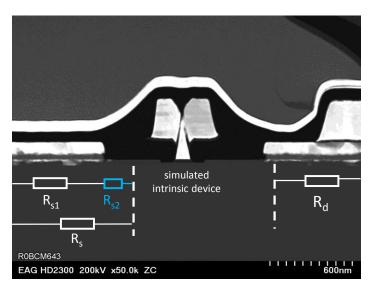

Fig. 3.2. STEM image of the InP-HEMT showing the separation between intrinsic simulated area and external resistances.

To reduce simulation time, only the intrinsic part of the InP HEMT was simulated. The extrinsic part, beyond the limit where it could be treated as simply parasitic resistive, lumped resistive elements contributing to external source and drain resistances were used, see paper [D] for details. A STEM image of the InP HEMT, showing the separation between simulated intrinsic region and external resistances, is shown in Fig. 3.2.

To reproduce the surface charges appearing in the semiconductor/passivation interface on the cap and recess surfaces, a constant surface charge model was considered. The charge denseties in these surfaces were calibrated against the experimental Hall measurements in Fig. 2.1 and Fig. 2.2. The surface charge in the gate recess area was observed to depend on etching process used in the HEMT fabrication.

### **3.3 DC Characterization**

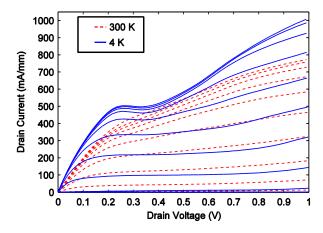

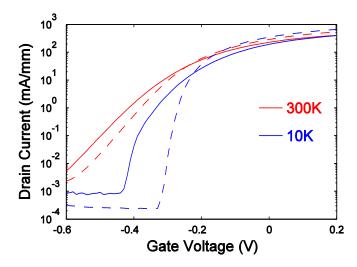

DC and RF characterization was performed at 10 K and 300 K in a Lakeshore model CRX-4K cryogenic probe station. Typical drain current  $I_d$  for 2x10 µm gate width devices are shown in Fig. 3.3. Maximum  $I_d$  at  $V_{ds} = 1$  V was 1 A/mm at 10 K and 0.8 A/mm at 300 K.

At 10 K, a kink is seen in the I–V characteristics at high  $I_d$ . Such behavior has been observed previously [1] when operating InP HEMTs at elevated drain currents under cryogenic conditions. However, since the optimal low-noise bias point of the InP HEMT is around 15 mA/mm, i.e. 1.5% of the maximum  $I_d$ , the kink phenomenon is far from the bias region of interest for most low noise amplifiers.

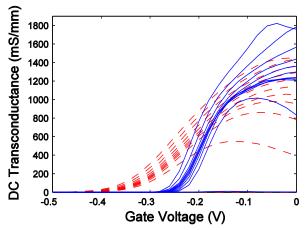

In Fig. 3.4, extrinsic DC  $g_m$  at 10 K and 300 K is shown against gate voltage  $V_g$ . A distinct shift of 0.1 V in threshold voltage  $V_T$ , as well as an increased slope of  $g_m$ , and improved quality of pinch-off was observed when cooling down to 10 K. Maximum extrinsic  $g_m$  at  $V_{ds} = 1$  V was 1.8 S/mm at 10 K and 1.4 S/mm at 300 K.

Both Fig. 3.3 and Fig. 3.4 show the traditional way to plot DC behavior of transistors. For ultra-low noise InP HEMTs, the amount of information available from these graphs is however limited. From equation (2), we know that high  $g_m$  is important. However, to be utilized for low noise, the same bias point also needs to deliver low  $I_d$ . A better way to

Fig. 3.3: Drain current of a 2x10  $\mu$ m gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature.  $V_{gs}$  measured from -0.3 V to 0.6 V in steps of 0.1 V.

Fig. 3.4. Extrinsic DC  $g_m$  of a 2x10 µm gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 4 K (blue solid) ambient temperature.  $V_{ds}$  measured from 0.1 V to 1 V in steps of 0.1 V.

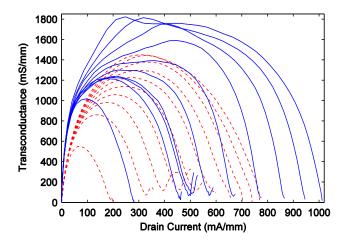

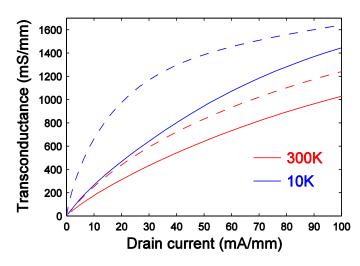

show  $g_m$  is to plot it against  $I_d$ . This dependence is plotted in Fig. 3.5, which shows a very steep  $g_m$  increase at low  $I_d$ . A  $g_m$  of more than 1 S/mm was observed for  $I_d$  of only 50 mA/mm at 4 K. At  $I_d$  of 15 mA/mm,  $g_m$  increases with 75% to 0.6 S/mm when cooled down to 10 K. At 300 K  $g_m$  was around 0.8 S/mm at 75 mA/mm. As seen in Fig. 3.5,  $g_m$  was also observed insensitive to  $V_{ds}$  at low drain current less than 100 mA/mm at both 300 K and 10 K. This, in combination with the high slope of  $g_m$ , enables excellent noise performance at very low power dissipation.

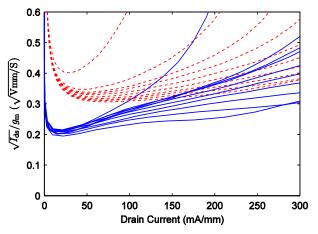

The ratio between  $I_d$  and  $g_m$  described in Eq. (2) is shown in Fig. 3.6. The curves at 10 K exhibit a clear minimum which corresponds to  $I_d$  of 15 mA/mm. At this bias, confirmed by noise measurements, the lowest noise temperature is obtained for the InP HEMT at 10 K. At 300 K, still in agreement with noise measurements, 75 mA/mm was the best low noise bias point. As seen in Fig. 3.6, the minimum was relatively insensitive to  $V_{ds}$ . This enables low power dissipation without severe noise temperature increase.

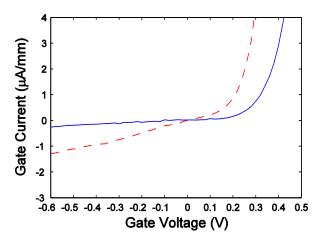

As pointed out in section 3.1, the gate leakage current is of large importance for the InP HEMT noise performance at intermediate frequencies. At optimum low noise bias, the InP HEMT exhibited a very low gate current density  $I_g$  of 20 nA/mm at 10 K and

Fig. 3.5: Extrinsic  $g_m$  versus  $I_d$  of a 2x10 µm gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature.  $V_{ds}$  measured from 0.1 V to 1 V in steps of 0.1 V.

Fig. 3.6:  $\sqrt{I_{ds}/g_m}$  versus Id of a 2x10 µm gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature. Vds measured from 0.1 V (upper curve) to 1 V (lower curve) in steps of 0.1 V.

200 nA/mm at 300 K. The current-voltage characteristics of the gate Schottky diode at  $V_{ds} = 0$  V is shown in Fig. 3.7. As clearly illustrated, the gate leakage current at negative gate voltage was heavily suppressed due to the reduction of thermal emission of electrons over the Schottky barrier when cooled down to 10 K.

As observed in Fig. 3.7, a shift in forward voltage of the gate Schottky diode of 0.1 V was observed when cooling down to 10 K. This shift is due to the temperature dependence of the built in potential of the Schottky diode and has previously been observed both for InP HEMTs and GaAs metamorphic HEMTs [33, 34].

In general, the DC characteristics at 300 K of the InP HEMT presented in Fig. 3.3 to Fig. 3.7 show steep increase in DC gm, high quality of pinch-off, and strongly suppressed  $I_g$ . As seen in these figures, the properties are strongly enhanced when cooling the InP HEMT to 10 K. Such DC behavior is a strong indication for excellent noise performance [3]. Similar temperature dependences have previously been observed for the Cryo3 InP HEMTs in the DC analysis presented in [35]. In the next section, the analysis will be extended with the microwave characteristics of the InP HEMT at cryogenic and room temperature.

Fig. 3.7. Gate current of a 2x10  $\mu$ m gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature.  $V_{ds} = 0$  V.

#### 3.4 Microwave Characterization

To obtain the small signal parameters of the model in Fig. 3.1 and especially equation (1), a direct extraction method was used [36, 37]. The gate resistance  $R_g$ , which is an input parameter in the direct extraction, was obtained from DC measurements of gate through-line test structures. Values of  $R_g$  were 130  $\Omega$ /mm at 10 K and 320  $\Omega$ /mm at 300 K. The gate Schottky current influence on the S-parameters was negligible for the devices and bias levels used in this work. Therefore, the gate Schottky diode in Fig. 3.1 was modeled without a resistor for the gate leakage.

The small signal parameter extraction was focused on drain currents below 100 mA/mm as the bias point for minimum noise temperature of the InP HEMT was 75 mA/mm at 300 K and 15 mA/mm at 10 K. The most important parameters, which this section will focus on, were the ones in equation (1).(2)

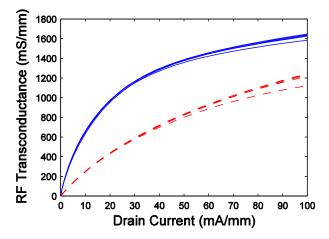

Intrinsic  $g_m$ , shown in Fig. 3.8, was observed to increase by more than 100 % to 0.7 S/mm at the best cryogenic low noise bias when cooled down to 10 K. At the optimum low noise bias at room temperature,  $g_m$  was 0.8 S/mm at 300 K. At both temperatures, the intrinsic low noise  $g_m$  was far below its maximum of 2 S/mm at 10 K and 1.5 S/mm at 300 K, respectively.

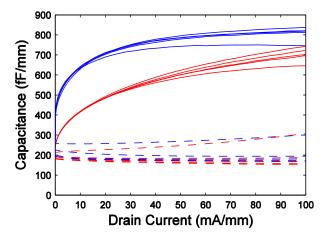

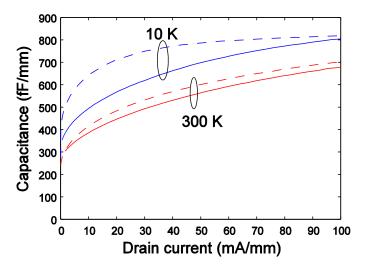

$C_{\rm gs}$  and  $C_{\rm gd}$  are shown in Fig. 3.9.  $C_{\rm gs}$  was observed to be strongly dependent on temperature and drain current when operating close to pinch-off. At  $I_{\rm d}$  of 15 mA/mm,  $C_{\rm gs}$  was observed to increase about 30 % when cooled down to 10 K.  $C_{\rm gd}$  was much less temperature and bias dependent than  $C_{\rm gs}$ .

At pinch-off,  $C_{gs}$  and  $C_{gd}$  approached the same values of 200-250 fF/mm independent of temperature. In forward mode,  $I_d > 200$  mA/mm and not shown in Fig. 3.9,  $C_{gs}$ saturated at 800 fF/mm, whereas  $C_{gd}$  slightly decreased to 150 fF/mm. The transition between these two boundaries was strongly temperature dependent. Compared to 300 K, as seen in Fig. 3.9,  $C_{gs}$  at 10 K increased very abruptly with  $I_d$  and reached the saturated value of 800 fF/mm at much lower  $I_d$  than at 300 K.

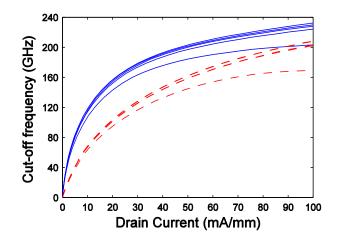

$g_{\rm m}$ ,  $C_{\rm gs}$  and  $C_{\rm gd}$  combined give an estimate of  $f_{\rm T}$ , which is the first parameter in equation (1).  $f_{\rm T}$  is plotted against  $I_{\rm d}$  in Fig. 3.10. A clear improvement of  $f_{\rm T}$  at low  $I_{\rm d}$  was observed when cooling down to 10 K. At the optimum low noise bias at 10 K,  $f_{\rm T}$  increased by 60% from 80 to 130 GHz when cooled down from 300 K to 10 K. At the

Fig. 3.8. Intrinsic  $g_m$  of a 2x100 µm gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature.  $V_{ds}$  measured from 0.2 V (lower curve) to 1 V (upper curve) in steps of 0.2 V.

Fig. 3.9.  $C_{gs}$  (solid) and  $C_{gd}$  (dashed) of a 2x100 µm gate width and 130-nm gate length InP HEMT at 300 K (red) and 10 K (blue) ambient temperature.  $V_{ds}$  measured from 0.2 V (upper curve) to 1 V (lower curve) in steps of 0.2 V.

optimum low noise bias at 300 K,  $f_T$  increased by 60% from 80 to 130 GHz when cooled down from 300 K to 10 K. At the optimum low noise bias at 300 K,  $f_T$  was 185 GHz, i.e. considerably higher than the optimum at 10 K.

The reason for the lower  $f_T$  at the optimum bias at 10 K than at 300 K was the lower bias. As a lower  $I_d$  can achieve a higher  $g_m$ , the balance of equation (2) was shifted toward lower values of both  $I_d$  and  $g_m$  (equivalently  $f_T$ ).

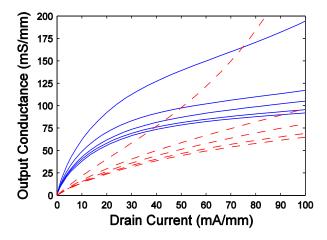

The last bias dependent microwave parameter in equation (1) is the intrinsic  $G_{ds}$ , which is shown in Fig. 3.11.  $G_{ds}$  is found to increase with  $I_d$ , and the way it does depends on temperature. When cooled to 10 K, the magnitude and slope of  $G_{ds}$  at low  $I_d$  is increased, while at higher  $I_d$ , the temperature change in  $G_{ds}$  was very small. As seen in Fig. 3.11, a degradation of  $G_{ds}$  is observed for low  $V_d$  below 0.4 V at both 10 K and 300 K.

The model parameters in Eq. (1) without bias dependence are  $R_s$  and  $R_g$  and their equivalent temperature  $T_g$ . At 300 K,  $R_s$  and  $R_g$  were 0.24  $\Omega$ ·mm and 310  $\Omega$ /mm. At 10 K the values were 0.13  $\Omega$ ·mm and 130  $\Omega$ /mm, respectively. Intrinsic  $R_i$  was fairly insensi-

Fig. 3.10. Intrinsic cut-off frequency  $f_{\rm T}$  at 300 K (red dashed) and 10 K (blue solid) at low  $I_{\rm d}$ .  $V_{\rm d}$  stepped between 0.2 V (lower curve) and 1 V (upper curve) in steps of 0.2 V.

Fig. 3.11. Intrinsic  $G_{ds}$  of a 2x100 µm gate width and 130-nm gate length InP HEMT at 300 K (red dashed) and 10 K (blue solid) ambient temperature.  $V_{ds}$  measured from 0.2 V (upper curve) to 1 V (lower curve) in steps of 0.2 V.

tive to bias but strongly dependent on temperature, and was improved from 0.85  $\Omega$ ·mm at 300 K to 0.45  $\Omega$ ·mm at 10 K.

#### 3.5 Noise Characterization

To accurately measure noise temperature is a challenging task. At low frequencies, very long integration times are needed and radio frequency interference (RFI) deteriorate the spectrum, at intermediate frequencies the noise levels are of the same order as the measurement uncertainties, and at high frequencies the frequency itself makes measurements difficult. Adding to this are the difficulties with impedance mismatch and instability of non-impedance matched HEMT measurements.

In this section, the noise behavior of the InP HEMT at 300 K and 10 K is analyzed at both low frequencies and microwave frequencies, and related to the DC and RF results presented in section 3.3 and 3.4.

#### 3.5.1 Microwave Noise Characterization

At cryogenic microwave conditions, direct noise parameter measurements of InP HEMTs are unreliable. Instead,  $2x100 \mu m$  InP HEMTs were integrated in a 3-stage hybrid 4-8 GHz LNA as described in paper [B]. Noise temperature for the LNA was measured at 10 K using a cold attenuator setup, directly calibrated against a setup at NIST claiming a noise temperature uncertainty of less than 0.18 K and gain uncertainty of less than 0.1 dB [38]. Repeatability of the measurements was better than 0.1 K.

To extract the noise parameters of the InP HEMT, the noise model in Fig. 3.1 was integrated in a calibrated AWR Microwave Office model of the LNA. By setting the physical temperature of all resistive elements except  $G_{ds}$  to ambient temperature, and fitting the measured and simulated noise and gain by tuning  $T_d$ , all noise parameters could be extracted. The gate leakage current noise source between gate and drain in the noise model was set to the DC gate leakage current level at the investigated bias point.

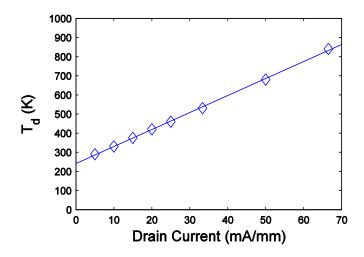

In Fig. 3.12 extracted  $T_d$  is plotted against  $I_d$ . In accordance with [3], where  $T_d$  was extracted at room temperature and  $I_d$  between 40 and 360 mA/mm,  $T_d$  is observed to be almost linearly dependent on  $I_d$  even at 10 K and as low  $I_d$  as 1 mA/mm. At 300 K,  $T_d$  was found to be much higher, in the order of 2000 K for bias as in Fig. 3.12, but still linearly dependent on  $I_d$ . However, due to the increased thermal noise contribution at 300 K, the extraction of  $T_d$  is very sensitive to errors in the small signal extraction of the gate side resistances  $R_g$  and  $R_i$ . Because of this the error in  $T_d$  extraction was much higher at 300 K than at 10 K, and no graph is presented here. Another recent study showing a similar  $I_d$  dependence on  $T_d$  is presented in [39].

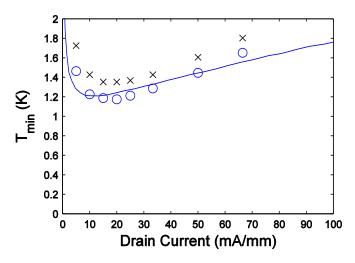

With the extracted  $T_d$  in Fig. 3.12, the minimum noise temperature of the InP HEMT could be extracted. In Fig. 3.13  $T_{min}$  at 6 GHz is plotted against  $I_d$  at 10 K. Without consideration of the shot noise contribution from the gate leakage current, the lowest  $T_{min}$  was less than 1.2 K. When considering the gate current,  $T_{min}$  increased by 0.2 K at 6 GHz.

Independent of the gate current, the optimum low noise bias was  $V_d = 0.6$  V and  $I_d$  around 15 mA/mm. This is also in agreement with the LNA measurements in paper [C], which exhibited a lowest noise temperature of 1.4 K at  $I_d$  of 15 mA/mm per stage. At 300 K the optimum low noise bias was obtained at 75 mA/mm.

To validate the noise model suggested in [20], equation (1) was evaluated with the extracted  $f_{\rm T}$ ,  $R_{\rm t}$ ,  $G_{\rm ds}$  and  $T_{\rm d}$  at 10 K and plotted in Fig. 3.13. This expression of  $T_{\rm min}$  agrees very well with the simulated  $T_{\rm min}$ , as seen in Fig. 3.13.

All extracted model parameters for optimum low noise bias at 10 K and 300 K are shown in Table 3.1. The small variations in parasitic inductances seen in Table 3.1 are due to small resistive and capacitive elements excluded from the model for simplicity. The associated error is estimated to be incremental.

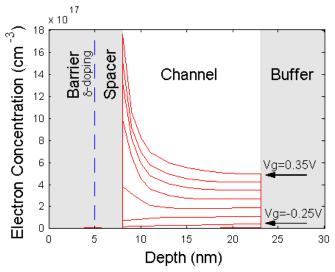

The InP HEMTs in this work are based on a single delta-doping 3 nm above the channel. The principle of this structure is to separate the carriers from the donors using a thin spacer. The result is a high mobility electron gas in the narrow bandgap channel, and a positively charged delta-doping in the wide bandgap barrier. The magnitude and distribution of the electron gas in the channel is influenced by many factors, where the strongest are gate bias, Coulomb attraction between carriers and delta-doping, thermal diffusion, and charged traps.

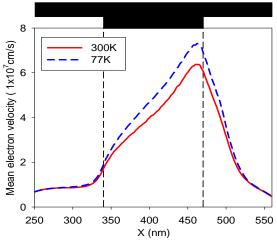

To understand the carrier distribution dependence on gate voltage, Monte Carlo simulations were used. Fig. 3.14 shows the average electron velocity of the electrons in the channel at 300 K and 77 K. Independent on temperature, the velocity peaked at the

Fig. 3.12. Drain resistor temperature  $T_d$  at 10 K extracted at different  $I_d$  densities.  $V_d$  was 0.6 V for all extraction points and  $I_d$  was swept between 1 mA and 13.3 mA for each 2x100 µm InP HEMT.

Fig. 3.13. Extracted  $T_{min}$  at 6 GHz and 10 K with (black x) and without (blue o) consideration of the gate current. The noise model suggested in [20] and based on extracted  $f_{T}$ ,  $R_{t}$ ,  $G_{ds}$  and  $T_{d}$  is shown by the blue curve.

drain side of the gate where the electric field was at maximum. The increase in maximum average electron velocity upon cooling (about 17% as seen in Fig. 3.14), explains part of the observed  $g_m$  increase seen in Fig. 3.4 and Fig. 3.5 [27]. The physical mechanism behind the electron velocity increase is the reduced electron-phonon scattering rate, leading to an increased electron mean electron free path.

The increased electron velocity does however not by itself explain the 100%  $g_m$  increase seen at the optimum cryogenic low noise bias. The second part of the explanation is the vertical electron distribution below the gate. This distribution, simulated with MC, is shown for different gate bias at 77 K in Fig. 3.15. As seen in the graph, when the gate was forward biased, the carriers were distributed in the top part of the channel due to the Coulomb attraction between the negative electrons and the positive delta-doping and gate potential. At reverse bias, the negative gate voltage canceled the attraction from the delta-doping and pushed the remaining electrons toward the buffer.

| LOW        | LOW NOISE BIAS AT 300 K AND 10 K. UNITS ARE V, mA, mS, $\Omega$ , fF, pH and K. |       |       |

|------------|---------------------------------------------------------------------------------|-------|-------|

|            |                                                                                 | 300 K | 10 K  |

| $\sim$     | $V_{ m ds}$                                                                     | 0.6   | 0.6   |

| Bias       | $I_{ m d}$                                                                      | 15    | 3.3   |

| <u>н</u>   | $V_{ m gs}$                                                                     | -0.14 | -0.18 |

|            | $C_{ m gs}$                                                                     | 132   | 138   |

|            | $C_{ m gd}$                                                                     | 34    | 37    |

| sic        | $C_{ m gs} \ C_{ m gd} \ C_{ m ds}$                                             | 52    | 46    |

| Intrinsic  | $g_{ m m}$                                                                      | 213   | 176   |

| Int        | $R_{ m i}$                                                                      | 3.9   | 2.2   |

|            | $R_{ m j}$                                                                      | 33    | 25    |

|            | $G_{ m ds}$                                                                     | 13    | 11    |

|            | $C_{ m pg}, C_{ m pd}$<br>$L_{ m g}$<br>$L_{s}$                                 | 19    | 20    |

|            | $L_{\rm g}$                                                                     | 35    | 46    |

| tics       | $L_s$                                                                           | 0     | 0     |

| asit       | $L_{ m d}$                                                                      | 36    | 47    |

| Parasitics | $R_{ m g}$                                                                      | 5     | 2.2   |

| Π          | $\ddot{R_{d}}$                                                                  | 1.3   | 0.7   |

|            | $R_{ m s}$                                                                      | 1.2   | 0.6   |

| Noise      | $T_{ m d}$                                                                      | 2800  | 400   |

TABLE 3.1 EXTRACTED VALUES FOR THE SMALL-SIGNAL MODEL OF 2X100 µm INP HEMT AT OPTIMUM LOW NOISE BIAS AT 300 K AND 10 K UNITS ARE V mA mS. Q. FF. pH and K

This property of the carrier distribution is also confirmed by the DC and RF measurements in section 3.3 and 3.4. At low current, when the carriers were distributed far away from the gate, gate-to-carrier distance was large and  $g_m$  and  $C_{gs}$  were low as seen in Fig. 3.8 and Fig. 3.9. When the bias was increased, the electron distribution was shifted up towards the gate as seen in Fig. 3.15, and the gate-to-carrier distance was reduced, with increased  $g_m$  and  $C_{gs}$  as a result. When the carriers reached the top of the channel, gate-to-carrier distance became limited by the barrier and spacer thickness, and  $g_m$  and  $C_{gs}$  saturated.

When cooling down to 10 K, the thermal diffusion in the channel becomes strongly reduced. This means that the carrier distribution becomes more dependent on the gate bias and delta-doping attraction. Hence, the mean carrier distribution is expected to shift toward the delta-doping and be more sensitive to gate bias.

From an electrical perspective this means that a smaller depletion potential, and hence less negative gate voltage, is required to pinch the current at 10 K compared to 300 K. As seen in Fig. 3.3 this is confirmed by the distinct shift in  $V_{\rm T}$ .

Also the higher slope of  $g_m$  versus  $V_g$  close to pinch-off in Fig. 3.3 is explained by an increased carrier confinement as a smaller change in  $V_g$  results in an increased change in  $g_m$ .

The improvement of intrinsic  $g_m$  at low drain currents as seen in Fig. 3.8 also indicates a more confined carrier concentration close to the gate when cooling down to 10 K.

Finally, a strong evidence for a change in carrier concentration is the temperature dependence of  $C_{gs}$  at low  $I_d$ . As the gate-to-carrier distance is inversely proportional to  $C_{gs}$ , the location of the carriers is indirectly given by  $C_{gs}$ .

As seen in Fig. 3.9,  $C_{gs}$  varies between two specific on and off values. At pinch-off, where  $C_{gs}$  and  $C_{gd}$  are equal, all carriers in the channel below the gate are depleted and

Fig. 3.14. Monte Carlo mean electron velocity profile along the channel under the gate at 300 K (red continuous line) and 77 K (blue dashed line) for  $V_d$ =0.6 V and  $I_d$ =250 mA/mm.

Fig. 3.15. Monte Carlo simulations showing the gate bias dependence of the electron distribution in the InP HEMT below the gate at 300 K. The epitaxial layers, as well as the delta-doping, are marked in the graph. Extrinsic gate voltage was swept between -0.35 V (lower curve) and 0.35 V (upper curve) in steps of 0.1 V. The corresponding drain currents were 5, 28, 99, 225, 403, 536, 605 and 649 mA/mm.

the capacitance is low. As gate voltage is increased, current starts to flow in the lowest part of the channel as the depletion region retreats, and  $C_{gs}$  increases as gate-to-carrier distance reduce. When the depletion region is fully withdrawn from the channel,  $C_{gs}$  saturates as gate-to-carrier distance cannot reduce further until the barrier is populated.

#### 3.5.2 Low Frequency Noise Characterization

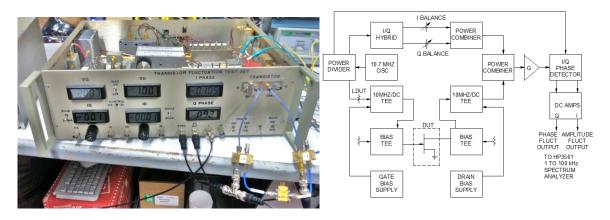

To measure gain fluctuations down to a level of 1ppm, a special test set shown in Fig. 3.16 was used. As the gain fluctuations were assumed independent of RF frequency, a low test frequency of 10.7 MHz was used. A balanced bridge approach was used to cancel AM fluctuations in the source. By using a HP3561 spectral analyzer at the output, the spectral density in  $mW/\sqrt{Hz}$  was measured. To calibrate the measurements, a resistive divider at the output of the DUT was used. When activated, the gain was

Fig. 3.16: Photograph and block diagram of test set for measuring gain fluctuations in transistors. The 10.7 MHz test signal through the transistor is approximately canceled by manual adjustment of I and Q attenuators and the resulting error signal is amplified by G and phase detected to give both amplitude and phase fluctuations.

reduced by 1%. The calibrated gain fluctuations were hence given by dividing the spectral density by the difference obtained with the resistive divider.

The low-frequency noise of the transistors was measured with three different instruments to cover the nine orders of magnitude, 1 Hz to 1 GHz, of frequency range. For the lowest frequencies, 1 Hz to 100 KHz, a HP3561 spectrum analyzer directly measuring the transistor output noise voltage was used. Between 10 kHz and 100 MHz an Agilent E4407B spectrum analyzer was used both in the same direct way as the HP3561 analyzer, and in a Y factor setup together with a Noisecom NC3210 calibrated noise diode source. For the highest frequencies, between 100 MHz and 1 GHz, an automated Y factor method with an Agilent N8975 noise figure analyzer and Agilent N4000A smart noise source was used.

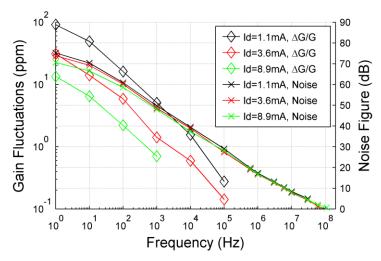

Six types of HEMT and two types of SiGe HBTs were tested; see paper [E] and [40-46] for details. A global view of the data showed that all devices had approximately a 1/f low-frequency noise and gain fluctuation spectrum. The 1 Hz NF were in the relatively small range, 69 to 81 dB, for all the HEMTs in spite of different foundries, gate lengths (35 nm to 130 nm), materials (InP and GaAs, and wide temperature range (300 K to 22 K). The SiGe HBT 1 Hz NF varied between 27.3 dB and 42.8 dB at 300 K.

Although the gross differences between HEMTs were not large, they can have considerable effect upon radiometer sensitivity. The InP HEMTs in this thesis work had 5 to 10 dB lower NF than the other 5 HEMTs at 1 Hz and 300 K. No inherent NF difference between GaAs and InP substrates could be observed.

The gain fluctuations at 300 K and 1 Hz varied from 15 to 110 ppm for all the HEMTs and 3.6 to 4.5 ppm for the HBT's. This variation is significant for radiometers with slow switching rates and would need to be verified by tests of many samples at the desired switch rate. At 1 kHz the fluctuations were in the 1 to 10 ppm range with the lower limit determined by the noise limit of the test set.

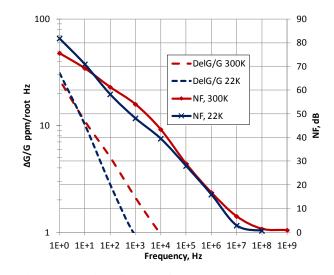

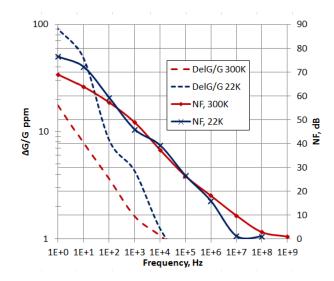

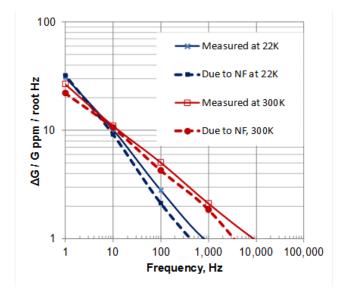

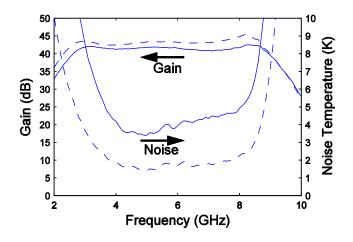

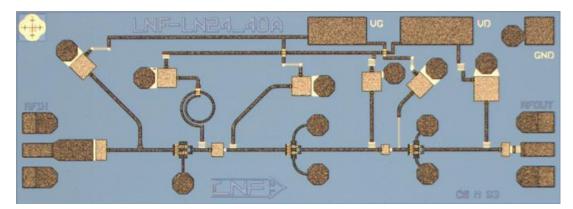

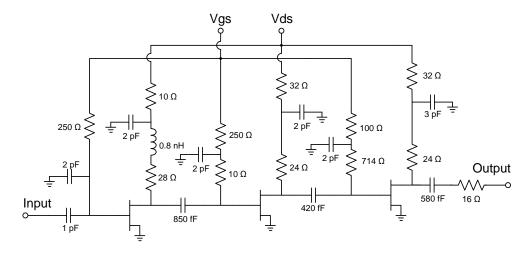

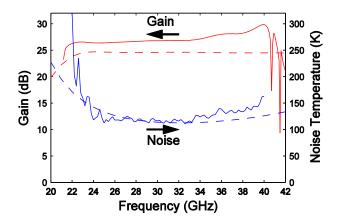

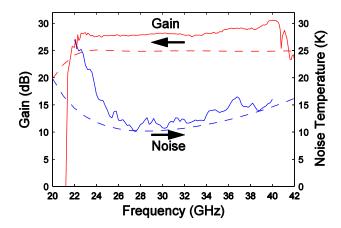

Plots of both noise and  $\Delta G/G$  at 300 K and 22 K for three different HEMTs are shown in Fig. 3.17 and Fig. 3.18. In general the NF curves have 1/f dependence with superimposed temperature-dependent deviations. The deviations can be related to the energy levels of traps as discussed in [21].

The HEMTs had 4 to 8 dB higher 1Hz NF at 22 K than at 300 K except for the TPQ13 where the NF did not change. The 1 Hz gain fluctuations were also higher at 22 K by factors of 1.5 to 8. For frequencies in the 10 Hz to 1 MHz range there was little change

Fig. 3.17. Gain fluctuation and noise figure of OMMIC GaAs HEMT at 300 K and 22 K.  $V_d = 0.6$  V and  $I_d = 12$  mA (80 mA/mm)

Fig. 3.18. Gain fluctuation and noise figure of InP HEMT from this thesis work at 300 K and 22 K.  $V_d = 0.6$  V,  $I_d = 15$  mA (75 mA/mm) at 300 K and  $V_d = 0.6$  V,  $I_d = 3.7$  mA (18.5 mA/mm) at 22 K.

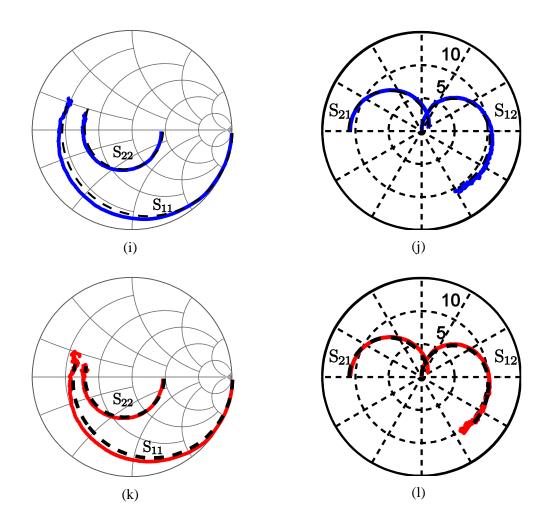

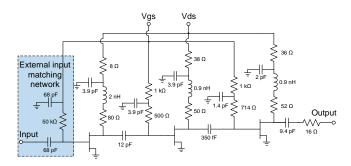

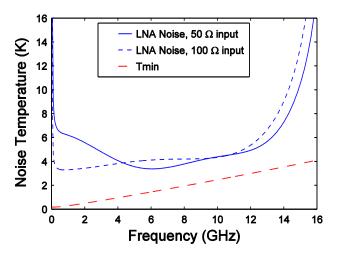

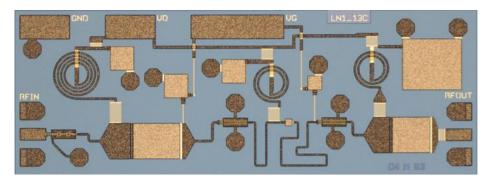

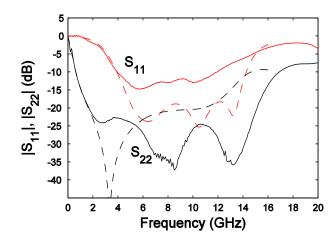

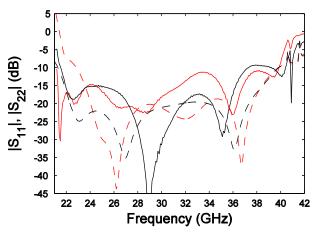

between 22 K and 300 K while above 1 MHz the cold transistors had lower noise due to thermal effects and increased carrier confinement (paper [C]).