# Modelando y verificando diseños de sistemas de tiempo real

Braberman, Víctor Adrián 2000

**Tesis Doctoral**

Facultad de Ciencias Exactas y Naturales Universidad de Buenos Aires

www.digital.bl.fcen.uba.ar

Contacto: digital@bl.fcen.uba.ar

Este documento forma parte de la colección de tesis doctorales de la Biblioteca Central Dr. Luis Federico Leloir. Su utilización debe ser acompañada por la cita bibliográfica con reconocimiento de la fuente.

This document is part of the doctoral theses collection of the Central Library Dr. Luis Federico Leloir. It should be used accompanied by the corresponding citation acknowledging the source.

#### Fuente / source:

Biblioteca Digital de la Facultad de Ciencias Exactas y Naturales - Universidad de Buenos Aires

## Departamento de Computación

Facultad de Ciencias Exactas y Naturales

## Universidad de Buenos Aires

# Modeling and Checking Real-Time System Designs

by

Víctor Adrián Braberman

Director: Ph.D. Miguel Felder

Pabellón 1 - Planta Baja - Ciudad Universitaria (1428) Buenos Aires Argentina

e-mail:vbraber@dc.uba.ar http://www.dc.uba.ar/people/exclusivos/vbraber

# FACULTAD DE CIENCIAS EXACTAS Y NATURALES / UBA

## Departamento de Computación

Facultad de Ciencias Exactas y Naturales

## Universidad de Buenos Aires

# Modelando y Verificando Diseños de Sistemas de Tiempo Real

Autor:

Víctor Adrián Braberman

Director: Doctor Miguel Felder

Pabellón 1 - Planta Baja - Ciudad Universitaria (1428) Buenos Aires Argentina

82274

e-mail:vbraber@dc.uba.ar http://www.dc.uba.ar/people/exclusivos/vbraber

Nº 3 2 8 7

# Abstract

Real-time systems are found in an increasing variety of application fields. Usually, they are embedded systems controlling devices that may risk lives or damage properties: they are safety critical systems. Hard Real-Time requirements (late means wrong) make the development of such kind of systems a formidable and daunting task. The need to predict temporal behavior of critical real-time systems has encouraged the development of an useful collection of models, results and tools for analyzing schedulability of applications (e.g., [109]). However, there is no general analytical support for verifying other kind of high level timing requirements on complex software architectures. On the other hand, the verification of specifications and designs of real-time systems has been considered an interesting application field for automatic analysis techniques such as model-checking. Unfortunately, there is a natural trade-off between sophistication of supported features and the practicality of formal analysis.

To cope with the challenges of formal analysis real-time system designs we focus on three aspects that, we believe, are fundamental to get practical tools: model-generation, model-reduction and model-checking. Then, firstly, we extend our ideas presented in [30] and develop an automatic approach to model and verify designs of real-time systems for complex timing requirements based on scheduling theory and timed automata theory [7] (a well-known and studied formalism to model and verify timed systems). That is, to enhance practicality of formal analysis, we focus our analysis on designs adhering to Fixed-Priority scheduling. In essence, we exploit known scheduling theory to automatically derive simple and compositional formal models. To the best of our knowledge, this is the first proposal to integrate scheduling theory into the framework of automatic formal verification. To model such systems, we present I/O Timed Components, a notion and discipline to build non-blocking live timed systems. I/O Timed Components, which are build on top of Timed Automata, provide other important methodological advantages like influence detection or compositional reasoning.

Secondly, we provide a battery of automatic and rather generic abstraction techniques that, given a requirement to be analyzed, reduces the model while preserving the relevant behaviors to check it. Thus, we do not feed the verification tools with the whole model as previous formal approaches. To provide arguments about the correctness of those abstractions, we present a notion of Continuous Observational Bismulation that is weaker than strong timed bisimulation yet preserving many well-known logics for timed systems like

#### TCTL [3].

er midd i zobil i destand i siste in

Finally, since we choose timed automata as formal kernel, we adapt and apply their deeply studied and developed analysis theory, as well as their practical tools. Moreover, we also describe from scratch an algorithm to model-check duration properties, a feature that is not addressed by available tools. That algorithm extends the one presented in [28].

The state of the s

# Agradecimientos

Agradezco a las instituciones que me permitieron llevar a cabo este proyecto: el Departamento de Computación, la Facultad de Ciencias Exactas y Naturales, UBA y el proyecto FOMEC. Así mismo, extiendo mi agradecimiento a las actuales y pasadas autoridades, integrantes y ex-integrantes del Departamento de Computación quienes me apoyaron incondicionalmente. Merecen una especial mención, por su aporte y compromiso en esta tesis, mi director, el Dr. Miguel Felder, mis jurados: el Dr. Alfredo Olivero, el Dr. Mauro Pezzè y el Dr. Sergio Yovine, los miembros suplentes del jurado: el Dr. Juan Vicente Echague, y el Lic. Gabriel Baum. Tampoco puedo dejar de mencionar al coautor e inspirador del trabajo sobre propiedades de duración, el Dr. Dang Van Hung. Le doy las gracias a los miembros del Politécnico de Milan, del UNU/IIST, y del instituto VERIMAG que gentilmente me recibieron e inspiraron. Agradezco epecialmente a los "tesistas" Gabriela Finkelstein, Diego Garbervetski y Cecilia Schor por su importante contribución en la validación y corrección de parte de las ideas incluidas en esta tesis. Finalmente, por el enorme soporte emocional que me brindaron durante todos estos años, le doy las gracias a mi familia, a mi novia y a mis amigos.

# Contents

| 1 | Int | roducti | on                                             |     |              |      |                |     |    |      |              |          |    | 1  |

|---|-----|---------|------------------------------------------------|-----|--------------|------|----------------|-----|----|------|--------------|----------|----|----|

|   | 1.1 | Prior R | esearch                                        | •   |              |      | 55#55          | ٠   | ٠  | * 2  | <b>3</b> 8   | ie: i    |    | 2  |

|   | 1.2 | Workin  | g Examples                                     | •   | s: 3         | e is |                | *   |    | 8 8  | • //         |          |    | 3  |

|   |     | 1.2.1   | The Active Structural Control System           | ē.  |              |      |                | ¥.  | ×  |      | . 9          |          | 23 | 4  |

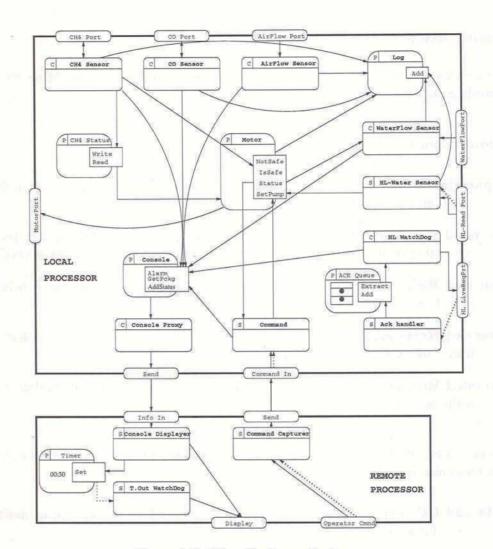

|   |     | 1.2.2   | The Mine Drainage Controller System            | (6) | * 2          | 9.8  | () <u>*</u> () | 80  |    | æ :  |              | <b>.</b> |    | 6  |

|   | 1.3 | Our Ap  | pproach                                        | •   |              |      | •              |     |    | •    |              | •        |    | 9  |

|   |     | 1.3.1   | Summarizing the Achievements                   | *8  | * :          |      | S(*)           | e   | ≋  | SE : | •            | ¥1.      | *  | 12 |

|   | 1.4 | Structu | are of this Thesis                             | •   | ٠.           |      | ٠              | ٠   | ÷  | •    | ٠            | Ŧ.       | ě  | 12 |

| 2 | Bac | kgroun  | d on Timed Systems Theory                      |     |              |      |                |     |    |      |              |          |    | 15 |

|   | 2.1 | Prelimi | nar Definitions                                | 8   |              |      | : ¥1           |     |    | 4 7  |              |          |    | 15 |

|   |     | 2.1.1   | Sequences                                      | ×   | e 2          |      | 9 80           | (*) | œ  |      | 200          | 8        |    | 15 |

|   |     | 2.1.2   | Timed Words                                    | 8   | <b>*</b> (1) |      |                |     | 8  | •    | •            |          |    | 16 |

|   |     | 2.1.3   | Clocks, Constraints and Valuations             |     |              |      | . *            | ×   | œ  |      | ( <b>®</b> ) | *        |    | 16 |

|   | 2.2 | Timed   | Automata                                       |     |              |      |                |     |    | ٠    | ٠            | •        | ٠  | 17 |

|   | 2.3 | Semant  | tics                                           | *   |              |      | : 25           | ×   | i. | 500  |              | × 1      | ×  | 18 |

|   |     | 2.3.1   | Runs and Non Zenoness                          | *   | e 18         |      |                | *   |    | 0.00 | •            | *        |    | 19 |

|   |     | 2.3.2   | From Finite Runs to Finite Transition Language |     |              |      |                |     | :  |      |              | *        | ÷  | 20 |

|   | 2.4 | Paralle | l Composition                                  | *   |              |      |                | *   | æ  |      | *0           | *        | ×  | 21 |

|   | 2.5 | Propos  | itional Valuation of Locations                 |     |              |      |                | 8   |    | ٠    | *5           | •        |    | 23 |

|   | 2.6 | Bisimu  | lations                                        |     |              |      |                |     |    |      |              |          |    | 23 |

| 2.7 | Some Logics for Real-Time Models                         | *****                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|----------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 2.7.1 Timed Computational Tree Logic                     |                                      | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 2.7.2 Linear Duration Invariants                         |                                      | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ext | ensions on Timed Systems Theory                          |                                      | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1 | Property Preserving Simulations                          | *****                                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2 | Property Preserving Bisimulations: CO-Bisimulations      | 910000000                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3 | I/O Timed Components                                     | * * * * * * * * *                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 3.3.1 I/O Components, Composition and Non-Zenoness $$    |                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Des | cribing RTS-Designs and Requirements                     |                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.0.2 Introduction to Fixed Priority Application Model   |                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1 | Describing the System Architecture                       |                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.2 | Task Dynamics                                            | ****                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

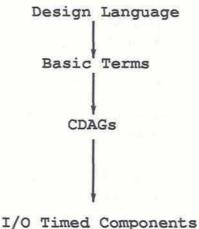

|     | 4.2.1 A Structured Language to Define Task Dynamics: Des | ign Language                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.2.2 The Kernel Language: CDAGs                         |                                      | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.2.3 From Design Language to CDAGs                      |                                      | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

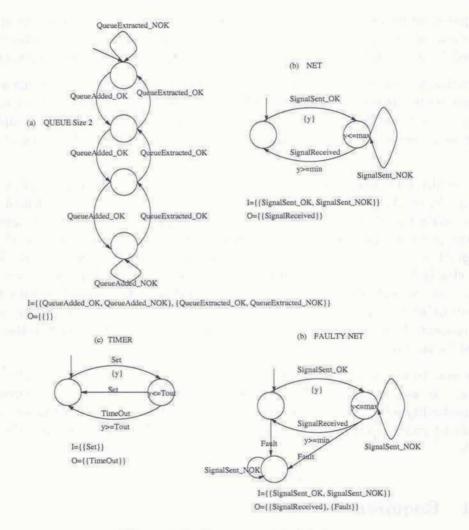

| 4.3 | Communication and Environment: Constraining Components   |                                      | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4 | Requirements                                             |                                      | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

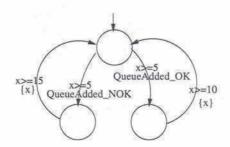

|     | 4.4.1 Safety Event Observers                             |                                      | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.4.2 Büchi Observers                                    |                                      | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.4.3 TCTL Observers                                     |                                      | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | 4.4.4 Linear Duration Observers                          |                                      | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sen | antics of Tasks in terms of I/O Timed Components         |                                      | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1 | The Untimed Semantics                                    |                                      | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.2 | Timed Model                                              |                                      | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3 |                                                          |                                      | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Mo  | del Reductions                                           |                                      | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     | Exter 3.1 3.2 3.3 Desc. 4.1 4.2 4.3 4.4 5.1 5.2 5.3      | 2.7.1 Timed Computational Tree Logic | 2.7.1 Timed Computational Tree Logic 2.7.2 Linear Duration Invariants  Extensions on Timed Systems Theory 3.1 Property Preserving Simulations 3.2 Property Preserving Bisimulations: CO-Bisimulations 3.3 I/O Timed Components 3.3.1 I/O Components, Composition and Non-Zenoness  Describing RTS-Designs and Requirements 4.0.2 Introduction to Fixed Priority Application Model 4.1 Describing the System Architecture 4.2 Task Dynamics 4.2.1 A Structured Language to Define Task Dynamics: Design Language 4.2.2 The Kernel Language: CDAGs 4.2.3 From Design Language to CDAGs 4.3 Communication and Environment: Constraining Components 4.4 Requirements 4.4.1 Safety Event Observers 4.4.2 Büchi Observers 4.4.3 TCTL Observers 4.4.4 Linear Duration Observers  Semantics of Tasks in terms of I/O Timed Components 5.1 The Untimed Semantics 5.2 Timed Model 5.3 The WCCT Calculus |

|   | 6.1    | Exact Abstraction: The Relevance Calculus             | 8  |

|---|--------|-------------------------------------------------------|----|

|   | 6.2    | Conservative Abstractions                             | 3  |

|   | 6.3    | Correctness of Relevance Calculus 9                   | 5  |

| _ | _ ,    | 10                                                    | 4  |

| 7 |        | lucing the Composition of I/O Components 10           |    |

|   | 7.1    | Relevance                                             |    |

|   | 7.2    | The Quotient Automaton                                |    |

|   | 7.3    | Results                                               | 19 |

|   | 7.4    | Examples                                              | .1 |

|   | 7.5    | Conclusions and Discussions                           | 6  |

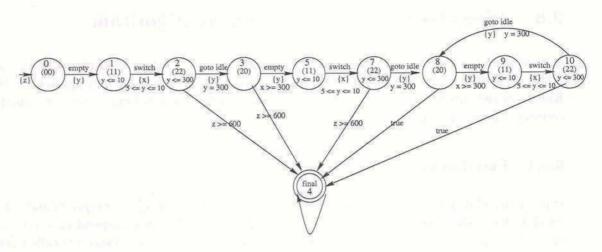

| 8 | Fitt   | ing the Pieces Together 12                            | 3  |

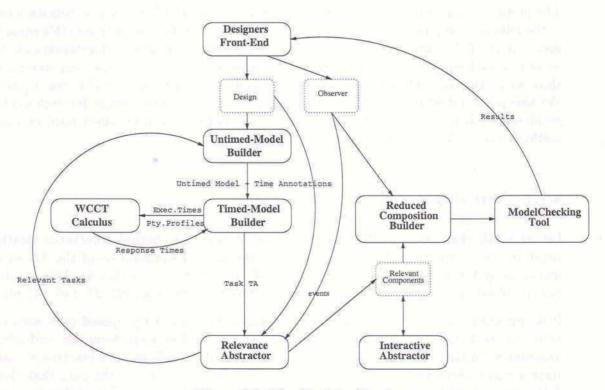

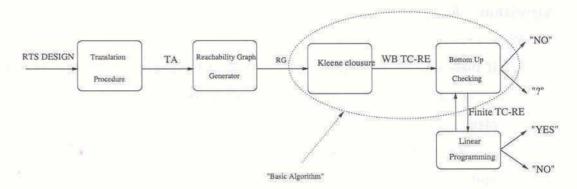

|   | 8.1    | An Architecture for the Checking Tool                 | 23 |

|   |        | 8.1.1 Verifying Safety Observers                      | 24 |

|   |        | 8.1.2 Verifying Büchi Observers                       | 26 |

|   |        | 8.1.3 Verifying TCTL Observers                        | 27 |

|   |        | 8.1.4 Verifying Linear Duration Observers             | 27 |

|   | 8.2    | Summary                                               | 28 |

| 0 | 17     | ifving Duration Properties                            | 00 |

| 9 |        |                                                       |    |

|   | 9.1    | Introduction                                          |    |

|   | 520.20 | 9.1.1 Related Work                                    |    |

|   | 9.2    |                                                       |    |

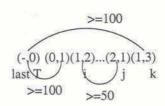

|   | 9.3    | Time Constrained Regular Expressions                  | 33 |

|   | 9.4    | Problem Transformation in terms of TC-RE              | 35 |

|   | 9.5    | Verifying Finite TC-RE                                | 36 |

|   | 9.6    | Infinite TC-RE                                        | 37 |

|   |        | 9.6.1 Well-Behaved TC-RE                              | 38 |

|   | 9.7    | Problem Transformation in terms of Well-Behaved TC-RE | 10 |

|   | 9.8    | Principles for the model-checking Algorithm           | 14 |

|    |      | 9.8.1   | Past-Independence                           | 144 |

|----|------|---------|---------------------------------------------|-----|

|    |      | 9.8.2   | Obtaining Past-Independent Iterations       | 146 |

|    | 9.9  | The B   | asic Algorithm                              | 147 |

|    | 9.10 | Conclu  | isions and Discussions                      | 150 |

|    | 9.11 | Proofs  | of Lemmas and Theorems                      | 151 |

|    |      |         |                                             |     |

| 10 | Con  | clusion | ns and Future Work                          | 155 |

|    | Rih  | liograp | hy.                                         | 160 |

|    | DID. | nograp  | Nice of Land                                |     |

| A  | A S  | urvey   | on RTS Design Notations and Analysis Tools  | 175 |

|    | A.1  | Notati  | ions and Models for Physical Designs of RTS | 175 |

|    |      | A.1.1   | A Tool Classification                       | 176 |

|    |      | A.1.2   | Guiding Features and Characteristics        | 177 |

|    |      | A.1.3   | The Survey                                  | 179 |

|    |      | A.1.4   | Some Remarks                                | 190 |

|    |      |         |                                             |     |

| В  | Abs  | tract   | Code for the Working Examples               | 193 |

# List of Figures

| 1.1 | The Active Structural Control System                                            | 5  |

|-----|---------------------------------------------------------------------------------|----|

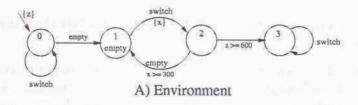

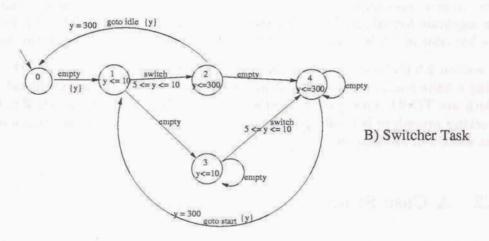

| 1.2 | Mine Drainage Design                                                            | 7  |

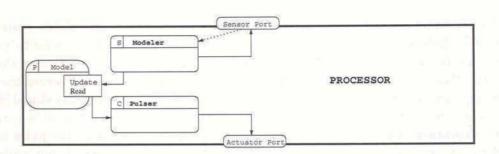

| 1.3 | The Tool Architecture                                                           | 13 |

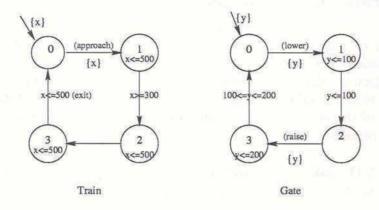

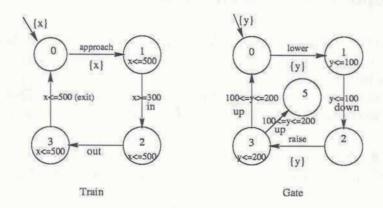

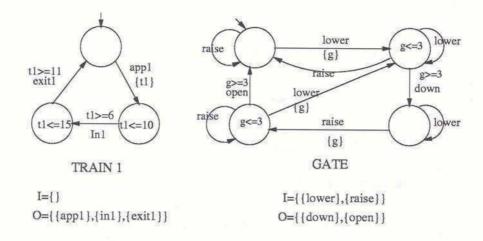

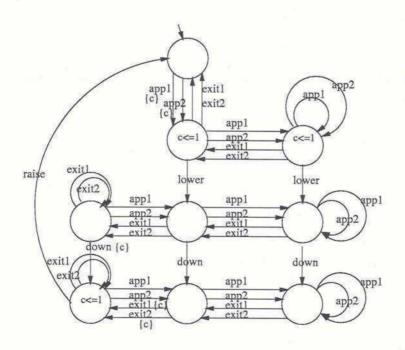

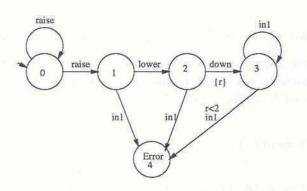

| 2.1 | The Railroad Crossing System                                                    | 22 |

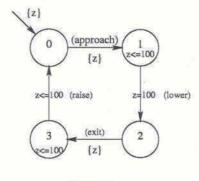

| 2.2 | The Railroad Crossing System with a Trap Location                               | 24 |

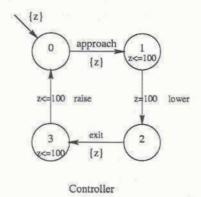

| 3.1 | Two Continuous Observational Equivalent Automata                                | 33 |

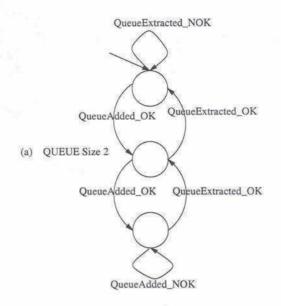

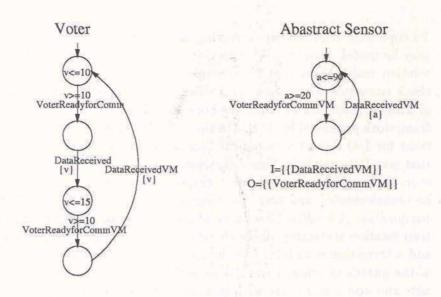

| 3.2 | Two compaible I/O components $\dots$                                            | 41 |

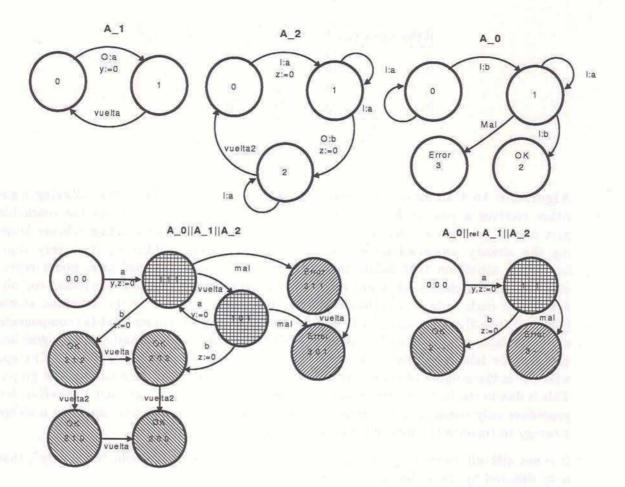

| 3.3 | I/O Components of the RCS $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$        | 42 |

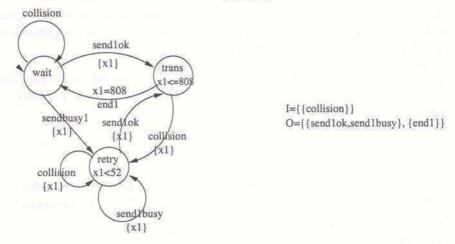

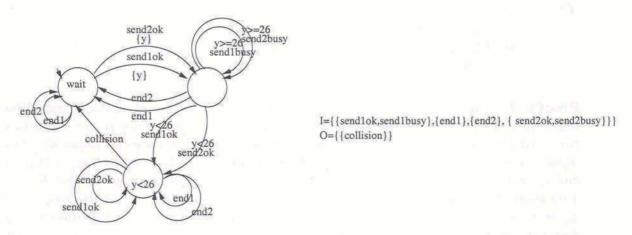

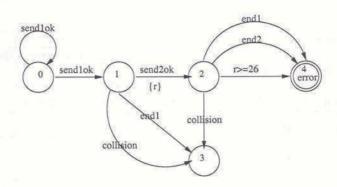

| 3.4 | I/O Components of the CSMA/CD Protocol                                          | 43 |

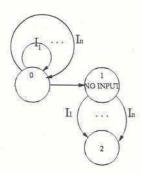

| 3.5 | Observer for Checking Non Zeno Regardless Input                                 | 48 |

| 4.1 | Design Elements                                                                 | 51 |

| 4.2 | Language Levels for Describing Tasks Dynamics                                   | 54 |

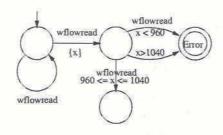

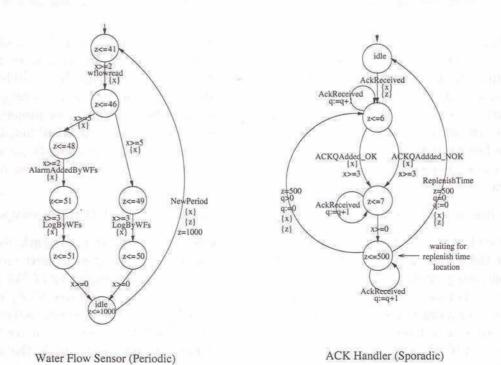

| 4.3 | CDAG for WaterFlow Sensor                                                       | 59 |

| 4.4 | CDAG for ACK Handler                                                            | 59 |

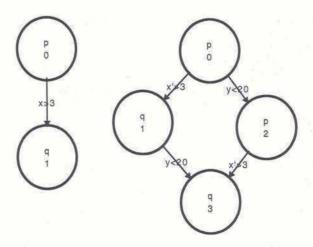

| 4.5 | Connectors Modeled                                                              | 61 |

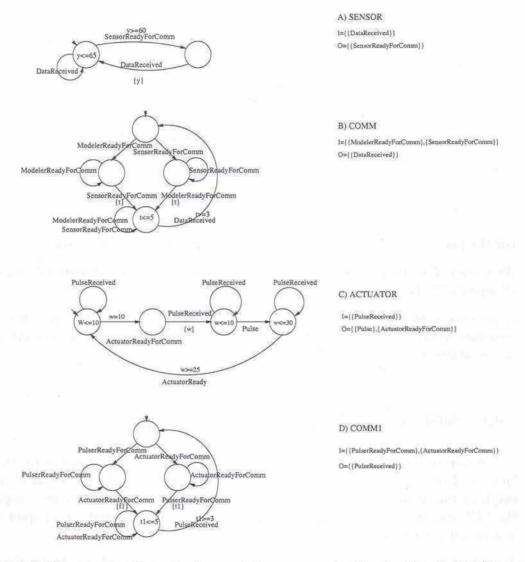

| 4.6 | The sensor, the actuator, and the communication for the Active Structure System | 63 |

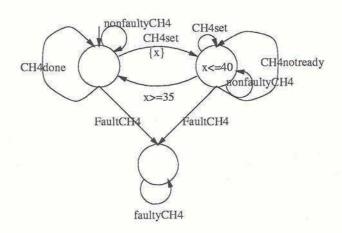

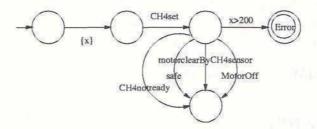

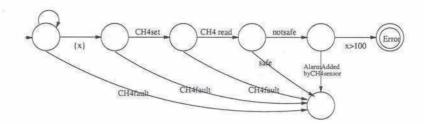

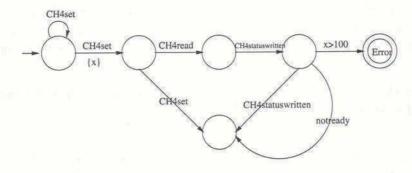

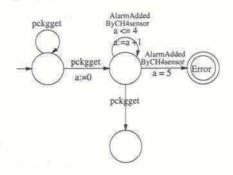

| 4.7 | Assumptions about CH4 sensor                                                    | 64 |

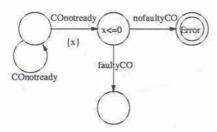

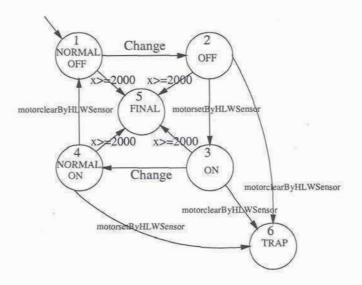

| 4.8 | Assumptions about HLWLevel sensor                                               | 65 |

| 4.9 | Assumptions about the operator                                                  | 65 |

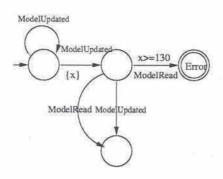

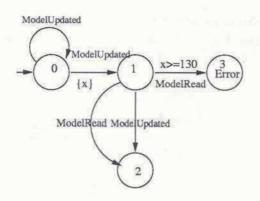

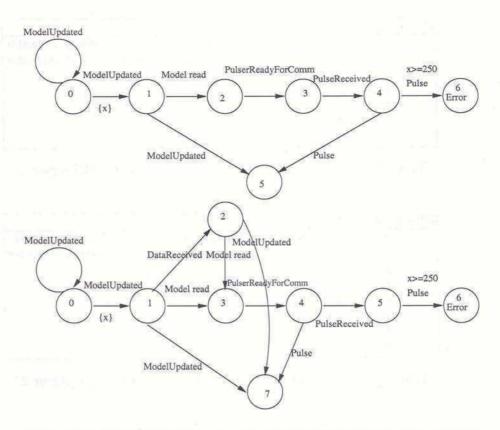

| 4.10 | Observer for Freshness: From a read to an update of the model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

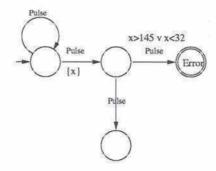

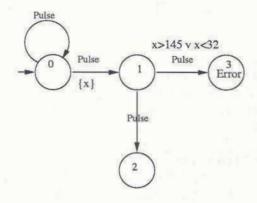

| 4.11 | Observer for The Regularity: InterPulse Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66    |

| 4.12 | Observer for Separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68    |

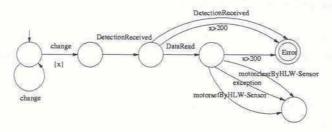

| 4.13 | Observer for Response1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68    |

| 4.14 | Observer for Response2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68    |

| 4.15 | Observer for Response3: From CH4 to Console Proxy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69    |

| 4.16 | Observer for Response3: From Console Proxy to ConsoleDisplay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69    |

| 4.17 | Observer for Freshness 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69    |

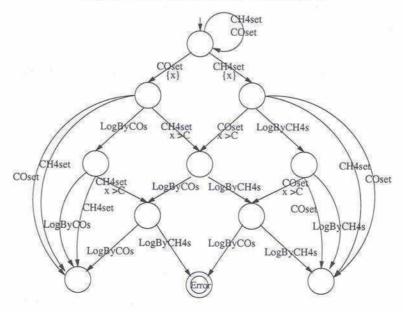

| 4.18 | Observer for Correlation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69    |

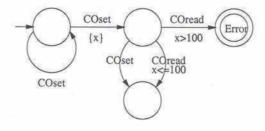

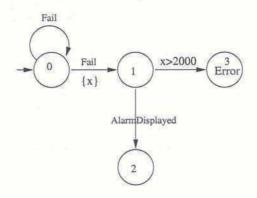

| 4.19 | Observer for False Alarm for CO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70    |

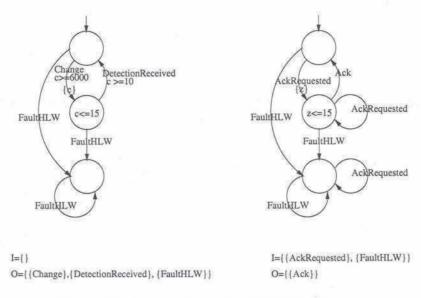

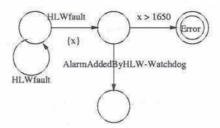

| 4.20 | Observer for Fault Detection HLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70    |

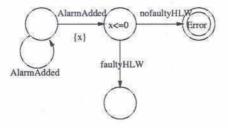

| 4.21 | Observer for False Alarm for HLW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70    |

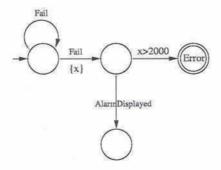

| 4.22 | Observer for Fault Detection NET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70    |

| 4.23 | Observer for Freshness 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71    |

| 4.24 | Observer for Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71    |

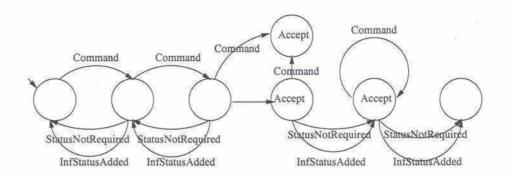

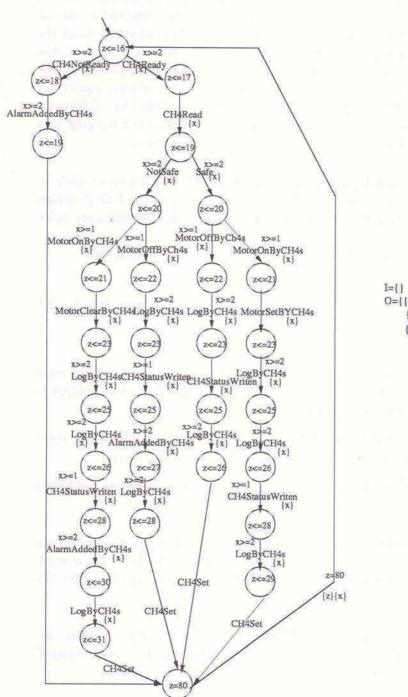

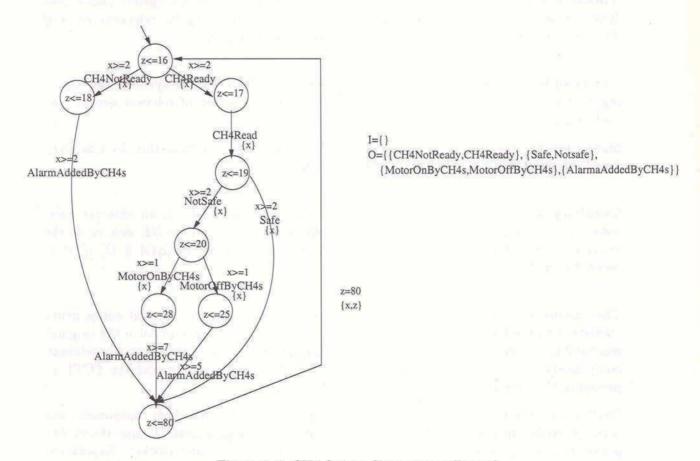

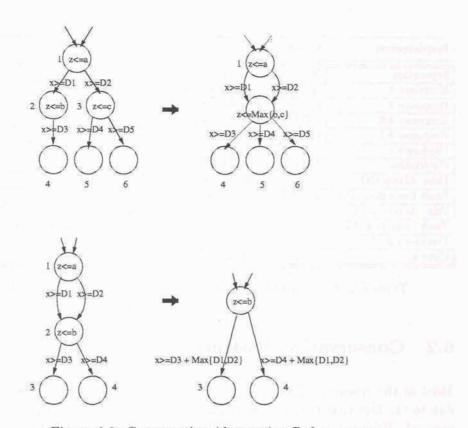

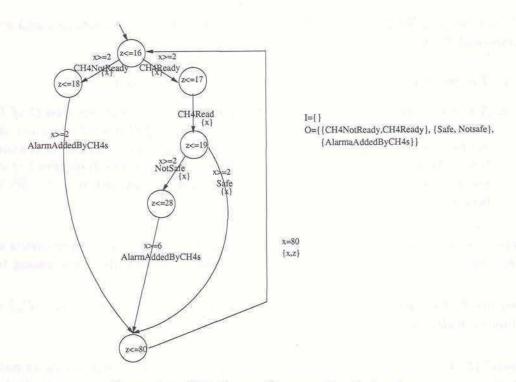

| 4.25 | Büchi Observer: Responsiveness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73    |