# Electrical Characteristics of High Quality La<sub>2</sub>O<sub>3</sub> Gate Dielectric with Equivalent Oxide Thickness of 5 Å

Y. H. Wu, M. Y. Yang, Albert Chin, Senior Member, IEEE, W. J. Chen, and C. M. Kwei

Abstract-Electrical and reliability properties of ultrathin La<sub>2</sub>O<sub>3</sub> gate dielectric have been investigated. The measured capacitance of 33 Å La<sub>2</sub>O<sub>3</sub> gate dielectric is 7.2  $\mu$ F/cm<sup>2</sup> that gives an effective K value of 27 and an equivalent oxide thickness of 4.8 Å. Good dielectric integrity is evidenced from the low leakage current density of 0.06 A/cm<sup>2</sup> at -1 V, high effective breakdown field of 13.5 MV/cm, low interface-trap density of  $3 \times 10^{10} \text{ eV}^{-1}/\text{cm}^2$ , and excellent reliability with more than 10 years lifetime even at 2 V bias. In addition to high K, these dielectric properties are very close to conventional thermal SiO<sub>2</sub>.

Index Terms—High K dielectric, leakage current, reliability.

#### I. INTRODUCTION

CCORDING to scaling rule, high K gate dielectric [1]–[9] with equivalent oxide thickness (EOT) below 10-15 Å will soon be required for sub-0.1  $\mu$ m devices. Unfortunately, the effective EOT value of some high K dielectrics may be limited by the interface reaction region between dielectric and Si. Therefore, the search for thermodynamically stable high K dielectric on Si is the essential factor to achieve a small EOT. In addition to low EOT and leakage current, the high K gate dielectric must have good interface property, high thermal stability, good reliability, and process compatibility to current VLSI technology. Recently, we have developed the Al<sub>2</sub>O<sub>3</sub> material [9] that can satisfy almost all the above requirement and has a  $K(\sim 9)$ higher than Si<sub>3</sub>N<sub>4</sub>. However, further reduction of EOT below 10 Å is difficult because of relatively low K. In this letter, we have studied the dielectric integrity of La<sub>2</sub>O<sub>3</sub> that has a very high effective  $K(\sim 27)$  and better thermodynamic stability on Si than Al<sub>2</sub>O<sub>3</sub>. In additional to the small EOT of 4.8 Å, good dielectric integrity and lifetime longer than ten years at 2 V is achieved.

## II. EXPERIMENTAL

Standard p-type Si wafers were used in this study. After device isolation, native oxide is suppressed by HF-vapor passivation [9]-[11] and *in-situ* thermal desorption followed by amorphous La layer deposition. Low temperature oxidation at temperatures of 400-500 °C for 1 h is performed and annealed at 900 °C in nitrogen ambient. The dielectric thickness is carefully measured by ellipsometer that is calibrated by cross-sec-

Y. H. Wu, M. Y. Yang, A. Chin, and C. M. Kwei are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan,

R.O.C. W. J. Chen is with the Department of Mechanical Materials Engineering, Na-

tional Yun-Lin Polytechnic Institute, Huwei, Taiwa. R.O.C.

Publisher Item Identifier S 0741-3106(00)00532-2.

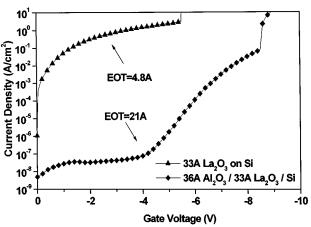

10 33A La<sub>2</sub>O<sub>2</sub> on Si 10 36A AI, O, / 33A La, O, / Si 10 -2 -4 -6 -10 Gate Voltage (V) Fig. 1. J-V characteristics of 33 Å La<sub>2</sub>O<sub>3</sub> and 36 Å Al<sub>2</sub>O<sub>3</sub>/33 Å La<sub>2</sub>O<sub>3</sub> gate dielectrics on Si. The stacked structure is used to reduce the leakage current for further C-V measurement.

tional TEM. The direct oxidation of deposited La to form high  $K La_2O_3$  is a very simple process and similar to conventional thermal SiO<sub>2</sub> in comparison with CVD [12] or sputtering deposited [13] gate dielectric. Al gate is used for MOS devices to reduce gate depletion or accumulation width. Dielectric leakage current,  $D_{it}$ , and reliability are characterized by current-voltage (I-V), capacitance-voltage (C-V), and time-dependent-dielectric-breakdown (TDDB), respectively. Typical device size is 100  $\mu m \times 100 \mu m.$

# **III. RESULTS AND DISCUSSION**

Fig. 1 shows the J-V characteristics of 33 Å La<sub>2</sub>O<sub>3</sub> and 36 Å Al<sub>2</sub>O<sub>3</sub>/33 Å La<sub>2</sub>O<sub>3</sub> MOS devices measured under accumulation. For 33 Å La<sub>2</sub>O<sub>3</sub>, a low leakage current of 0.06 A/cm<sup>2</sup> at -1 V and a high breakdown field of 13.5 MV/cm (by deducting flatband voltage) are obtained that are suitable for sub- $\mu$ m devices application. However, according to the electric displacement continuity at high K dielectric and Si interface

$$\varepsilon_0 K E_d = \varepsilon_{\rm Si} E_{\rm Si}.\tag{1}$$

Significant potential drop in Si is expected that may overestimate the actual breakdown electric field in La<sub>2</sub>O<sub>3</sub> due to the high K. Because the leakage current in  $La_2O_3$  is still too high for quasistatic C-V, we have used the stacked 36 Å Al<sub>2</sub>O<sub>3</sub>/33 Å La<sub>2</sub>O<sub>3</sub>/Si structure to lower the leakage current for  $D_{it}$  measurement.

Fig. 2 shows the C-V characteristics of 33 Å La<sub>2</sub>O<sub>3</sub> and stacked 36 Å  $Al_2O_3/33$  Å  $La_2O_3$  on Si, where effective K and EOT can be calculated by  $t_d C/\varepsilon_o A$  and  $\varepsilon_{ox} t_d/\varepsilon_0 K$ , re-

Manuscript received January 18, 2000; revised April 4, 2000. The work was supported by the National Science Council of Taiwan under Contract 88-2215-E-009-032. The review of this letter was arranged by Editor D. Dumin.

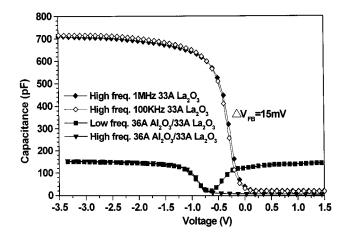

Fig. 2. C-V characteristics of 33 Å La<sub>2</sub>O<sub>3</sub> and 36 Å Al<sub>2</sub>O<sub>3</sub>/33 Å La<sub>2</sub>O<sub>3</sub> gate dielectrics on Si.

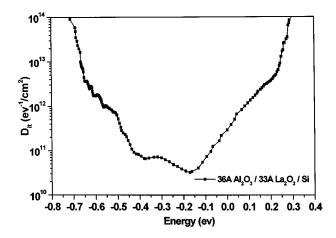

Fig. 3. Interface-trap density of 36 Å  $Al_2O_3/33$  Å  $La_2O_3$  gate dielectric on Si.

spectively. As shown in Fig. 2, a capacitance of 7.2  $\mu$ F/cm<sup>2</sup> is measured that gives 33 Å La<sub>2</sub>O<sub>3</sub> effective K and EOT of 27 and 4.8 Å, respectively. To our best knowledge, the 4.8 Å EOT is the smallest value reported so far. The small frequency dispersion of 15 mV is measured that suggests the good dielectric quality. This very low EOT is believed to be due to the high thermodynamic stability as contact with Si. In conventional thermal SiO2, a ~3 Å thickness deduction by quantum correction (QC) is required from EOT to obtain the actual physical thickness [14].However, a smaller QC is expected in high K dielectric because of the smaller valence band barrier and hole wave function penetration:

$$\Psi \sim \exp(-kx) = \exp\left(-\frac{\sqrt{2m_d^*E}}{\overline{h}}x\right).$$

(2)

An additional 1 Å QC reduction is obtained in high K dielectric if the valence band barrier is lowered to 2 eV. Furthermore, due to the strong electric field and voltage drop [14], [15] in Si shown in (1), the hole wave function can be further pushed closer to interface. Because of lacking important dielectric property and full quantum-mechanical solution, an effective K is used here although a physical K of 39 is obtained by assuming a 1.5 Å QC.

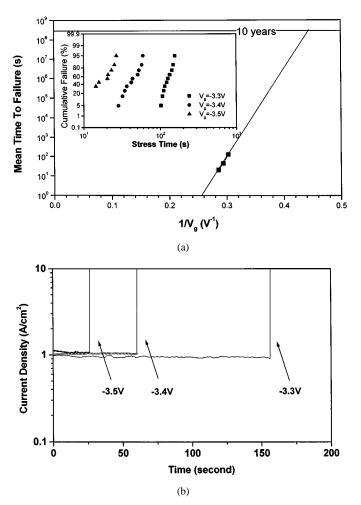

Fig. 4. (a) Extrapolated maximum voltage for ten years lifetime and cumulative breakdown distribution, and (b) the time evolution of gate current for 33 Å  $La_2O_3$  gate dielectrics with different bias voltages.

We have further plotted the  $D_{it}$  as a function of energy from quasistatic and high frequency C-V curves. As shown in Fig. 3, a minimum  $D_{it}$  of  $3 \times 10^{10}$  eV<sup>-1</sup>/cm<sup>2</sup> is obtained that is the same as current advanced oxynitride [16] and close to conventional thermal SiO<sub>2</sub>. This is the lowest reported  $D_{it}$  for high K dielectrics other than oxynitride. Although a flatband voltage shift is expected due to the increased dielectric charge resulted from additional 36 Å Al<sub>2</sub>O<sub>3</sub>, an accurate  $D_{it}$  can still be obtained because  $D_{it}$  is calculated from the difference between quasistatic and high frequencies C-V curves. The low  $D_{it}$  is extremely important for practical CMOS based integrated circuit application, because it is directly related to 1/f noise at low frequencies [16].

We have investigated gate dielectric reliability of 33 Å  $La_2O_3$  with small 4.8 Å EOT and low leakage current. Fig. 4(a) shows the extrapolated operation voltage for ten years lifetime obtained from inserted cumulative TDDB distribution that is calculated from the time evolution of gate current shown in Fig. 4(b). Although charges trapping and de-trapping are observed, no observable soft breakdown is found instead of hard breakdown that may be due to the low electric field inside gate dielectric. The breakdown time increases as decreasing stress voltage from 3.5 to 3.3 V and an operation voltage of 2.3 V is obtained for ten years operation with 50%

mean-time-to-failure. This result suggests  $La_2O_3$  gate dielectric is suitable for continuous operation even at VLSI generations of current 0.18  $\mu$ m and beyond.

## **IV. CONCLUSIONS**

We have developed a new high  $K \operatorname{La}_2 O_3$  with good dielectric integrity formed by a very simple process using direct oxidizing the deposit La on Si.

### REFERENCES

- H.-H. Tseng *et al.*, "Reduced gate leakage current and boron penetration of 0.18 μm 1.5 V MOSFET's using integrated RTCVD oxynitride gate dielectric," in *IEDM Tech. Dig.*, 1998, pp. 793–796.

- [2] S. C. Song *et al.*, "Ultra thin (<20 Å) CVD Si<sub>3</sub>N<sub>4</sub> gate dielectric for deep-sub-micron CMOS devices," in *IEDM Tech. Dig.*, 1998, pp. 373–376.

- [3] C. Hobbs *et al.*, "Sub-quarter micron CMOS process for TiN-gate MOSFET's with TiO<sub>2</sub> gate dielectric formed by titanium oxidation," in *Proc. Symp. VLSI Tech.*, 1999, pp. 133–134.

- [4] B. H. Lee *et al.*, "Ultrathin Hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application," in *IEDM Tech. Dig.*, 1999, pp. 133–136.

- [5] X. Guo et al., "High quality ultra-thin (1.5 nm) TiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> gate dielectric for deep sub-micron CMOS technology," in *IEDM Tech. Dig.*, 1999, pp. 137–140.

- [6] H. F. Luan et al., "High quality Ta<sub>2</sub>O<sub>5</sub> gate dielectrics with T<sub>ox</sub>, eq < 10 Å," in IEDM Tech. Dig., 1999, pp. 141–144.

- [7] Y. Ma, Y. Ono, L. Stecker, D. R. Evans, and S. T. Hsu *et al.*, "Zirconium oxide based gate dielectrics with equivalent oxide thickness of less than 1.0 nm and performance of submicron MOSFET using a nitride gate replacement process," in *IEDM Tech. Dig.*, 1999, pp. 149–152.

- [8] T. Devoivre, C. Papadas, and M. Setton, "A reliable 0.1 μm Ta<sub>2</sub>O<sub>5</sub> transistor manufactured with an almost standard CMOS process," in *Proc. Symp. VLSI Tech.*, 1999, pp. 131–132.

- [9] A. Chin *et al.*, "Device and reliability of high-K Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in Proc. Symp. VLSI Tech., 1999, pp. 135–136.

- [10] Y. H. Wu *et al.*, "Improved electrical characteristics of CoSi<sub>2</sub> Using HF-vapor pretreatment," *IEEE Electron Device Lett.*, vol. 20, pp. 200–202, 1999.

- [11] A. Chin et al., "Thin oxides with in-situ native oxide removal," IEEE Electron Device Lett., vol. 18, pp. 417–419, 1997.

- [12] W. S. Yang *et al.*, "Novel integration technology with capacitor over metal (COM) by using self-aligned dual damascene(SADD) process for 0.15 μm stand-alone and embedded DRAM's," in *Proc. Symp. VLSI Tech.*, 1999, pp. 13–14.

- [13] L. Manchanda *et al.*, "Gate quality doped high K films for CMOS beyond 100 nm: 3–10 nm Al<sub>2</sub>O<sub>3</sub> with low leakage and low interface states," in *IEDM Tech. Dig.*, 1998, pp. 605–608.

- [14] F. Rana, S. Tiwari, and D. A. Buchanan, "Self-consistent modeling of accumulation layers and tunneling currents through very thin oxides," *Appl. Phys. Lett.*, vol. 69, no. 8, pp. 1104–1106, 1996.

- [15] K. Yang, Y. C. King, and C. Hu, "Quantum effect in oxide thickness determination from capacitance measurement," in *Proc. Symp. VLSI Tech.*, 1999, pp. 77–78.

- [16] H. Kimijima *et al.*, "Improvement of 1/f noise by using VHP (vertical high pressure) oxynitride gate insulator for deep-sub micron RF and analog CMOS," in *Proc. Symp. VLSI Tech.*, 1999, pp. 119–120.