#### UNIVERSITY OF FUKUI Fukui, Japan

# Mechanism and Suppression of Current Collapse in AlGaN/GaN High Electron Mobility Transistors

(A1GaN/GaN HEMT における電流コラプスの機構と抑制)

A Dissertation Submitted to the University of Fukui for the Degree of Doctor of Engineering

in

**Electrical and Electronics Engineering**

by

### Md. Tanvir Hasan

Committee in charge: Professor Akihiro Hashimoto, Chair Professor Kazutoshi Fukui Professor Toshio Katsuyama Professor Masaaki Kuzuhara, Advisor

September 2013

Copyright © Md. Tanvir Hasan, 2013

This dissertation is dedicated to my parents and supervisor, who gave me life and inspiration to keep living it.

#### Abstract

### Mechanism and Suppression of Current Collapse in AlGaN/GaN High Electron Mobility Transistors

An AlGaN/GaN-based high-electron-mobility transistor (HEMT) is considered as an excellent candidate for future power devices due to its high breakdown voltage, high saturation drain current and low on-resistance ( $R_{on}$ ). However, current collapse, i.e., dispersion of drain current or increased dynamic  $R_{on}$ , is regarded as one of the most critical issues to be solved for actual power-switching applications. Even though there have been remarkable improvements in growth and device technologies, it is still essential to understand mechanism of current collapse and ways to get rid of it. In this work, I have investigated the effect of passivation on current collapse in AlGaN/GaN HEMTs. A detailed analysis on trapping effects and localization of traps has been made. In order to suppress current collapse in AlGaN/GaN HEMTs, field plate (FP) structured devices have been studied.

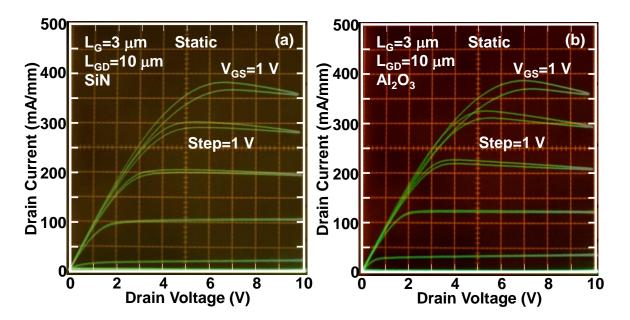

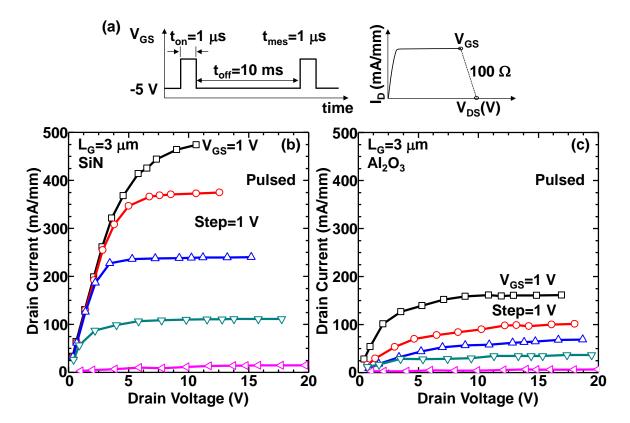

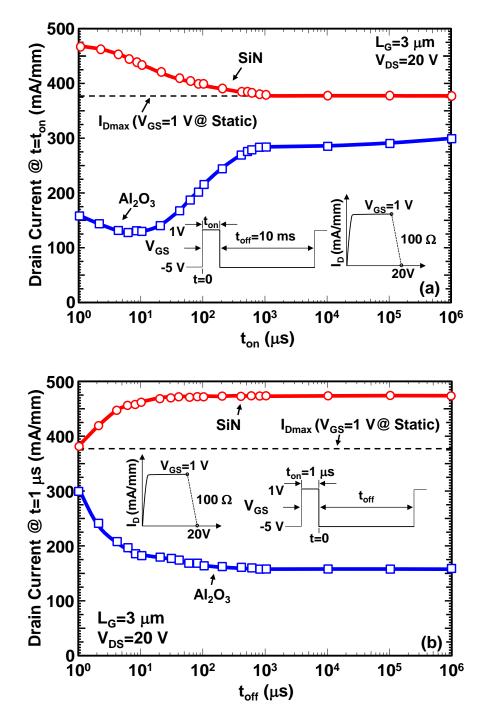

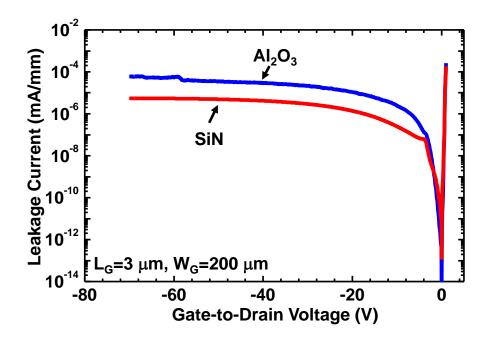

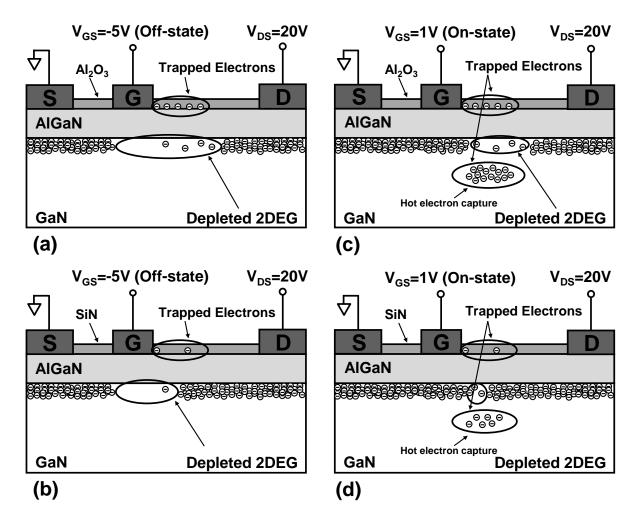

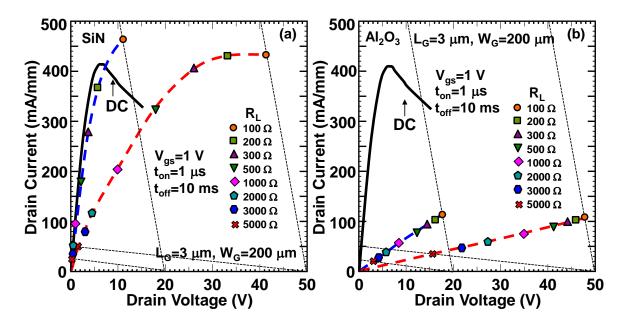

Drain current dispersion measurements have been performed for AlGaN/GaN HEMTs having different passivation films such as SiN and Al<sub>2</sub>O<sub>3</sub>. Passivated devices exhibited dispersion between static and pulsed current-voltage characteristics. The maximum drain current for SiN passivated devices was improved by around 25% at pulsed measurements as compared to its static value, whereas Al<sub>2</sub>O<sub>3</sub> passivated devices exhibited that of around 56% deterioration. The drain current was decreased with increasing on-state duration time for SiN passivated devices, while it was increased for Al<sub>2</sub>O<sub>3</sub> passivated devices. The mechanism responsible for the increase of drain current with on-state duration time by AlGaN surface traps is proposed, while GaN buffer traps reasonably govern the decrease of drain current.

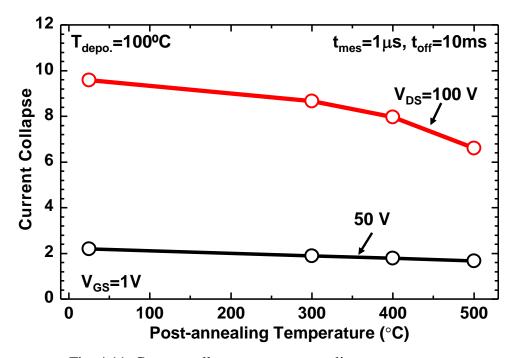

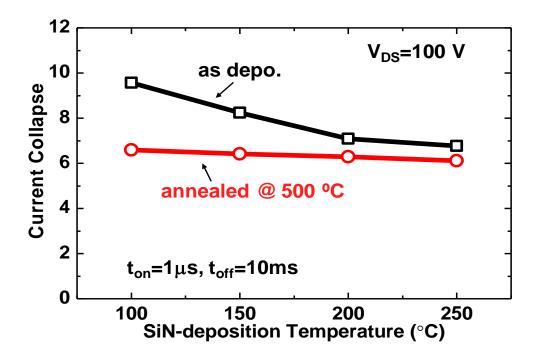

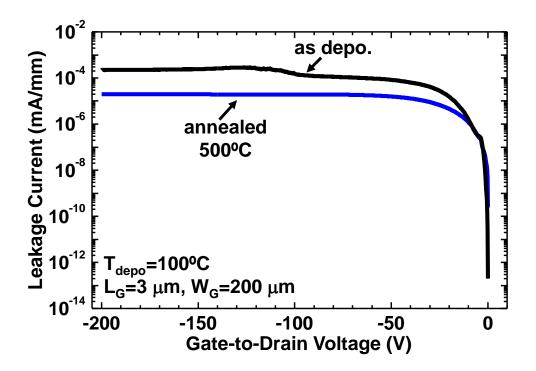

Effects of SiN passivation on current collapse have been studied by monitoring the dynamic change in  $R_{on}$ . The normalized dynamic  $R_{on}$  was decreased with increasing SiN-deposition temperature and became high with increasing off-state drain bias voltages. The normalized dynamic  $R_{on}$  was also decreased with increasing annealing

temperature. These results indicate that the SiN/AlGaN interface trap density is reduced with increasing both SiN-deposition and annealing temperatures.

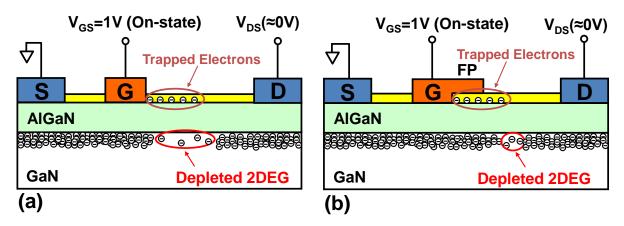

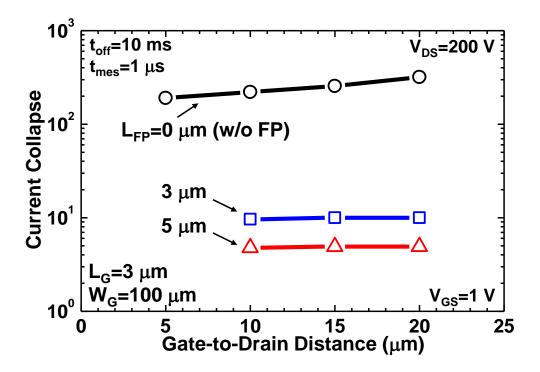

Current collapse measurements have been performed for AlGaN/GaN HEMTs having identical breakdown voltages but with different FP lengths. The results indicated that applying more positive on-state gate biases resulted in pronounced recovery in the dynamic  $R_{on}$  for the FP device, whereas no gate-bias effects were observed for the device without FP. The mechanism responsible for the reduced current collapse by FP is proposed, in which the key role is played during on-state by the quick field-effect recovery of partial channel depletion caused by electron trapping at AlGaN surface states between gate and drain.

The above studies indicate that the current collapse is suppressed by good passivation film and longer FP with more positive on-state gate biases in AlGaN/GaN HEMTs for future high-power applications.

# Contents

| Chapter 1 | Intro      | oduction                                              | 1        |

|-----------|------------|-------------------------------------------------------|----------|

|           | 1.1        | Background                                            | 1        |

|           | 1.2        | Objectives of this work                               | 6        |

|           | 1.3        | Dissertation organization                             | 7        |

|           | Refe       | rences                                                | 8        |

| Chapter 2 | Fund       | damentals of AlGaN/GaN HEMTs                          | 13       |

|           | 2.1        | Introduction                                          | 13       |

|           | 2.2        | High-electron-mobility transistor                     | 13       |

|           | 2.3        | Properties of III-nitride semiconductors              | 14       |

|           | 2.4        | Polarization effects                                  | 17       |

|           | 2.5        | Polarization induced charge                           | 20       |

|           | 2.6        | Formation of 2DEG                                     | 22       |

|           | 2.7        | Velocity-field characteristics                        | 26       |

|           | 2.8        | Principle of operation                                | 28       |

|           | 2.9        | Current collapse                                      | 31       |

|           | 2.10       | Trade-off between on-resistance and breakdown voltage | 36       |

|           | References |                                                       |          |

|           |            |                                                       |          |

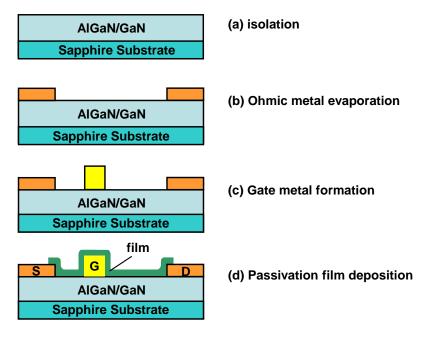

| Chapter 3 | Devi       | ce processing and characterization procedure          | 43       |

|           | 3.1        | Introduction                                          | 43       |

|           | 3.2        | Device fabrication                                    | 43       |

|           |            | 3.2.1 Mesa isolation                                  | 44       |

|           |            | 3.2.2 Ohmic metallization                             | 45       |

|           |            | 3.2.3 Schottky formation                              | 46       |

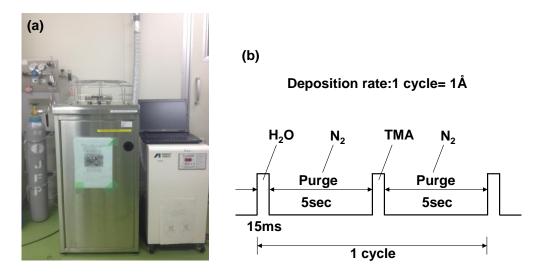

|           |            | 3.2.4 Passivation film deposition                     | 46       |

|           | 3.3        | Device characterization                               | 48       |

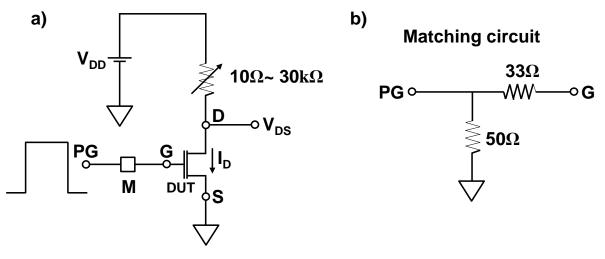

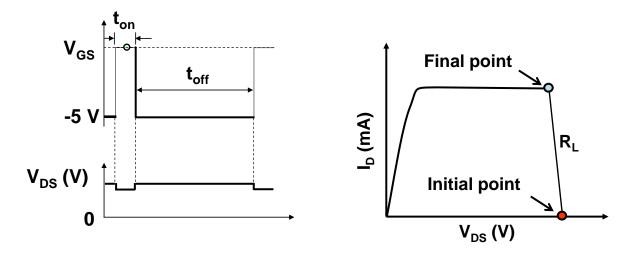

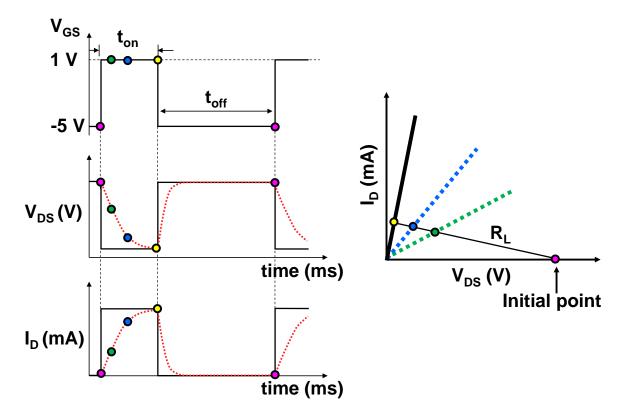

|           |            | 3.3.1 Gate-lag measurements                           | 52       |

|           |            | 3.3.2 Current collapse measurements                   | 52       |

|           | Refe       | rences                                                | 55       |

| Chapter 4 | Effe       | cts of surface-passivation film on current collapse   | 56       |

| Shuptor 4 | 4.1        | Introduction                                          | 56       |

|           | 4.2        | Device <i>I-V</i> characteristics                     | 50<br>57 |

|           | ••-        |                                                       | 51       |

|           |                                        | 4.2.1 Static <i>I-V</i> characteristics                                                                                                                                        | 57                               |

|-----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|           |                                        | 4.2.2 Pulsed <i>I-V</i> characteristics                                                                                                                                        | 57                               |

|           | 4.3                                    | Drain current transients                                                                                                                                                       | 59                               |

|           | 4.4                                    | Mechanism of drain current dispersion                                                                                                                                          | 61                               |

|           | 4.5                                    | Load line: from gate-lag to current collapse                                                                                                                                   | 63                               |

|           | 4.6                                    | SiN-deposition temperature                                                                                                                                                     | 64                               |

|           |                                        | 4.6.1 Dynamic on-resistance                                                                                                                                                    | 65                               |

|           |                                        | 4.6.2 Time dependent current collapse                                                                                                                                          | 67                               |

|           | 4.7                                    | Post-annealing temperature                                                                                                                                                     | 68                               |

|           | 4.8                                    | Summary                                                                                                                                                                        | 71                               |

|           | Refe                                   | erences                                                                                                                                                                        | 72                               |

|           |                                        |                                                                                                                                                                                |                                  |

|           |                                        |                                                                                                                                                                                |                                  |

| Chapter 5 | Cur                                    | rent collapse suppression by gate field-plate                                                                                                                                  | 76                               |

| Chapter 5 | <b>Cur</b><br>5.1                      | rent collapse suppression by gate field-plate                                                                                                                                  | <b>76</b><br>76                  |

| Chapter 5 |                                        |                                                                                                                                                                                |                                  |

| Chapter 5 | 5.1                                    | Introduction                                                                                                                                                                   | 76                               |

| Chapter 5 | 5.1<br>5.2                             | Introduction<br>Fabrication of devices with field-plate                                                                                                                        | 76<br>77                         |

| Chapter 5 | 5.1<br>5.2<br>5.3                      | Introduction<br>Fabrication of devices with field-plate<br>Device characteristics                                                                                              | 76<br>77<br>78                   |

| Chapter 5 | 5.1<br>5.2<br>5.3<br>5.4               | Introduction<br>Fabrication of devices with field-plate<br>Device characteristics<br>Effect of gate field-plate length                                                         | 76<br>77<br>78<br>82             |

| Chapter 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Introduction.Fabrication of devices with field-plate.Device characteristics.Effect of gate field-plate length.Mechanism of current collapse suppression.                       | 76<br>77<br>78<br>82<br>84       |

| Chapter 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Introduction<br>Fabrication of devices with field-plate<br>Device characteristics<br>Effect of gate field-plate length<br>Mechanism of current collapse suppression<br>Summary | 76<br>77<br>78<br>82<br>84<br>86 |

Acknowledgments List of publications

# Chapter 1 Introduction

#### **1.1 Background**

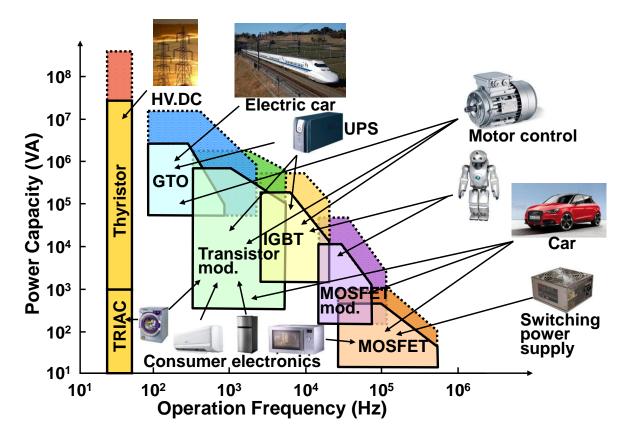

Power electronics is a technological domain that deals with electric power conversion by switching, which plays an important role in the management and control of the electric energy network. Figure 1.1 shows application areas of power electronics, where high-efficiency switching devices are used [1]. The low power loss feature of a switching device is an essential factor in energy conversion. The power loss of a switching device is divided into conduction loss and switching loss. An ideal electrical switch is one that shows zero resistance in the on state, and a resistance of infinity in the off state. However, these two requests always have a trade-off relationship. In the electric power conversion, handling of high voltage is often required, while the power loss should be minimized as much as possible. From these requirements, switching devices are usually qualified by the indices of specific on-resistance ( $R_{on}$ ) and blocking voltage.

Conventionally, power electronics has been developed on the basis of Si devices such as the metal–oxide–semiconductor field effect transistor (MOSFET), gate turn-off thyristor (GTO) and insulated gate bipolar transistor (IGBT); however, the essential limit of these Si devices has been revealed. The expectation for small and low-loss switching devices based on wideband-gap semiconductors such as SiC and GaN has recently increased, owing to their superior material properties. In fact, the innovation has come to exhibit a reality owing to the recent progress of device process and crystal growth technologies for these wide band-gap

Fig.1.1. Various application areas of power electronics, where high-efficiency switching devices are used [1].

semiconductors [1-5]. Table 1.1 shows material parameters for various materials [2]. Especially, wide band-gap GaN-based materials have superior properties as follows. AlGaN/GaN heterostructures have a high density of two-dimensional electron gas (2DEG) due to strong polarization effects. The theoretical peak-electron velocity of GaN reaches  $2.8 \times 10^7$  cm/s at a very high field of 140 kV/cm [6]. Baliga's figure-of-merits [3] clearly show that wide band-gap GaN-based materials have superiority in high-power applications since they have high breakdown field and high mobility compared with Si. Therefore, an AlGaN/GaN-based high-electron-mobility transistor (HEMT) is considered as an excellent candidate for future power devices due to its high breakdown voltage, high saturation drain current, and low R<sub>on</sub> [3]. Recently, impressive device performances in AlGaN/GaN HEMTs have been reported such as high output power of 40 W/mm at 4 GHz [7], current gain cut-off frequency of 370 GHz breakdown voltage of 10400 V [9].

| Parameter                               | Si                | GaAs              | 4H-SiC            | GaN                 |

|-----------------------------------------|-------------------|-------------------|-------------------|---------------------|

| Band-gap (eV)                           | 1.12              | 1.43              | 3.26              | 3.4                 |

| Electron Mobility (cm <sup>2</sup> /Vs) | 600<br>(MOS)      | 6000              | 720<br>(bulk)     | 2000<br>(2DEG)      |

| Peak Elec. Velocity (cm/s)              | $1 \times 10^{7}$ | $2 \times 10^{7}$ | $2 \times 10^{7}$ | $2.8 \times 10^{7}$ |

| Breakdown Field (MV/cm)                 | 0.4               | 0.5               | 2.0               | 3.3                 |

| Dielectric Constant                     | 11.4              | 12.9              | 10                | 9.5                 |

| Baliga FOM*                             | 1                 | 22                | 132               | 1560                |

Table 1.1 Material parameters related for various materials [2]. Baliga's figure of merit is an indicator for power device's performance. Note that all the symbols stand for a meaning in a general nomenclature of device physics.

\*Baliga FOM:  $\varepsilon \mu E_{CR}^{3}$  (Limit for on-resistance power FET)

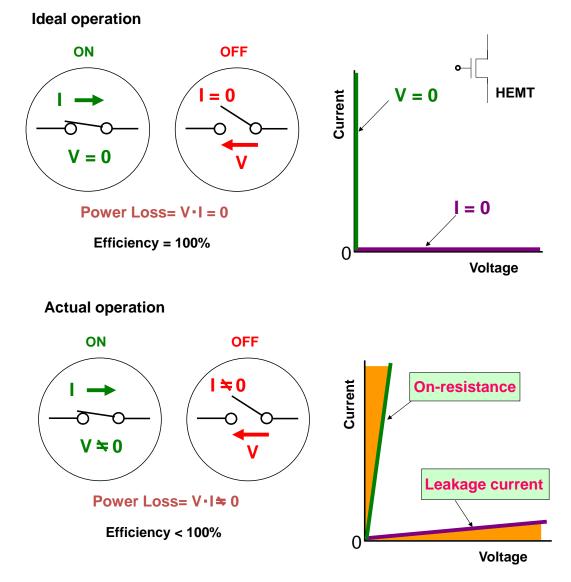

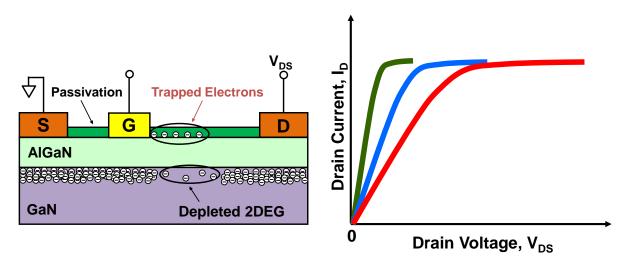

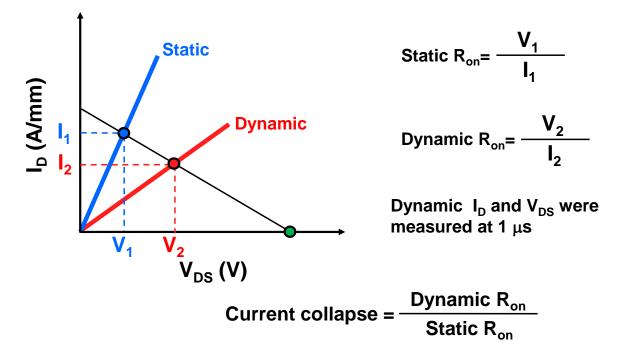

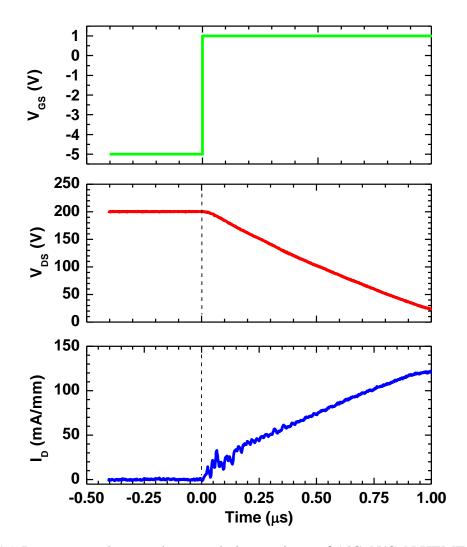

Figure 1.2 shows the power switching operation of a HEMT [2]. For ideal-switching operation of HEMT, the zero off-state current and the zero on-state voltage are required to obtain no power loss with 100% efficiency. However, there is a leakage current in the off state and the R<sub>on</sub> is not zero during on state, as shown in Fig. 1.2. The R<sub>on</sub> becomes a major problem for power-switching applications. In actual operation, additionally increased dynamic R<sub>on</sub>, i.e., current collapse is regarded as one of the most critical issues to be solved [10-15]. One of the main reasons is trapping effect in AlGaN/GaN HEMTs. Figure 1.3 shows a sketch of an AlGaN/ GaN HEMT's current-voltage characteristics with different drain voltage [2]. The dynamic Ron is increased with increasing drain voltage. This effect is recoverable with time. In general, trapping effects mean electron capturing by traps somewhere in AlGaN/GaN heterostructures. The captured electrons reduce the sheet electron density in the channel to keep the overall charge neutrality, leading to increase dynamic R<sub>on</sub>. These traps are mostly related to crystalline imperfection induced during material growth and device processing: (i) defects in the AlGaN/GaN heterostructures are due to lattice mismatch with foreign substrates such as SiC and sapphire, unintentional impurities, and compensation doping; (ii) device fabrication processing can impose thermal, physical, and chemical damage. In addition, the activity of traps changes under high-power operation, degrading static/RF performance of AlGaN/GaN HEMTs. Thus, to minimize

Fig. 1.2 Power-switching operation of a HEMT [2].

trapping effects through control of surface/interface states, development of advanced material growth, advanced device fabrication process techniques and novel device structures are key research themes in AlGaN/GaN HEMTs for power-switching applications.

Fig. 1.3.Sketch of an AlGaN/GaN HEMT and its I-V characteristics with different V<sub>DS</sub> [2].

Many efforts for high performance AlGaN/GaN HEMTs have been made to suppress current dispersion and increased dynamic on-resistance, which are directly related to modification of surface/interface states in AlGaN/GaN heterostructures. These modifications are surface passivation [16-18], a thin AlN barrier layer in AlGaN/GaN interface [19], application of a field plate [20], surface treatments with chemicals or plasma [21], and postgate-annealing [22-23]. It has been reported that possible sources of surface states in GaNbased materials are electrically active states at threading dislocations, and nitrogen vacancies and oxygen impurities as shallow surface donors [24-27]. In addition, many researchers have investigated the origin, location, and density of traps and reported various physical models of trapping mechanisms [14, 28-32]. Among various techniques to engineer electrically active surface states on device performance mentioned above, a popular way is surface passivation with dielectrics such as  $Si_3N_4$  and oxide [17, 18, 28, 33, 34]. Some groups have reported that surface passivation reduces electron trapping near the AlGaN surface [17, 35-36]. The passivation of surface traps has been generally meant for removal of trap states to prevent charge trapping causing current dispersion [17]. However, this explanation can be contradictory to surface donor theory by raising a question of trap sources as well as 2DEG source [31]. The drain current level increase after passivation indicates that 2DEG density increases, and net surface charge and net AlGaN/GaN interface charge become less negative and less positive, respectively. So, several groups suggested that the improved current after

passivation can be attributed to increase in positive charge at dielectric/AlGaN interface [17, 18, 33, 34, 36]. Some more explanations for passivation effects have also been proposed. First, the passivation process increases density of surface states (i.e., donor-likely states). Second, the passivation layer buries traps to become inaccessible to electrons from the gate [28]. Third, the passivation layer reduces edge electric field near the gate at drain side, leading to minimize electron injection from the gate to AlGaN surface [30]. This suppression of the (peak) electric field near the gate edge at drain side is more dominant in field-plate (FP) HEMTs, resulting in increased breakdown voltage and hence reduced electron trapping on the AlGaN surface [20, 37-42]. Evidently, no experimental evidences have been identified to date with respect to the effect of FP on the dynamic switching performance of AlGaN/GaN HEMTs. Thus, it is still very essential to understand the mechanism and suppression of current collapse in AlGaN/GaN HEMTs.

#### **1.2** Objectives of this research

The objectives of this research are the following:

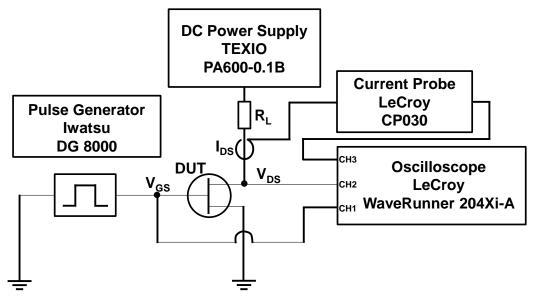

- (i) Develop a pulsed *I-V* system for precise evaluation of AlGaN/GaN HEMTs performance.

- (ii) Investigate the distinct electrical behavior of AlGaN/GaN HEMTs through study on passivation film effects using static and pulsed *I-V* characterization under different pulse widths and quiescent biases. Clarify the electron capture/emission phenomena, interpret effects of measurement conditions on trap activity, and qualitatively analyze trapping effects on AlGaN/GaN HEMTs performance.

- (iii) Investigate the passivation film-deposition temperature effect on dynamic performance in AlGaN/GaN HEMTs. Also, study the post-annealing temperature effect on current collapse.

- (iv) Introduce FP structures for suppression of current collapse in AlGaN/GaN HEMTs.

Also study the mechanism of current collapse suppression.

#### **1.3 Dissertation organization**

Chapter 2 introduces basic properties of III-nitride semiconductors including polarization effects, the formation of 2DEG and velocity-field characteristics. Finally, the operation of AlGaN/GaN HEMTs, current collapse, and trade-off between on-resistance and breakdown voltage are explained.

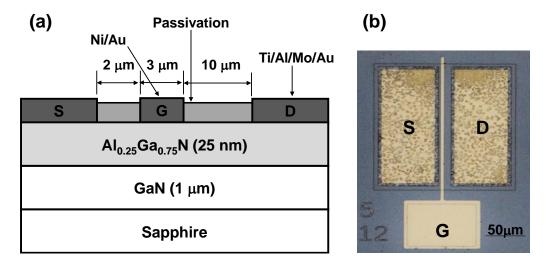

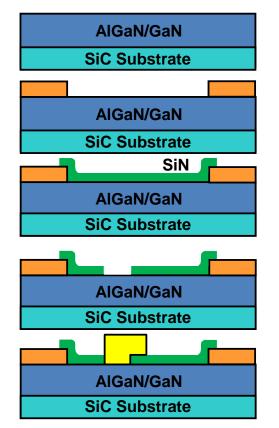

Chapter 3 illustrates the fabrication of AlGaN/GaN HEMT including optimization of etching using ICP-RIE for mesa isolation, photolithography process, ohmic formation, gate metallization, and passivation film-deposition process. The dynamic characterization procedures are also described.

Chapter 4 shows quantitative characterization of trapping effects on AlGaN/GaN HEMTs based on very short pulsed I-V measurements using different quiescent biases (QBs). Various approaches have been made to understand the mechanism of electrons trapping, such as different passivation films, SiN-deposition temperature effect, and post-annealing temperature effect.

Chapter 5 covers suppression of current collapse in AlGaN/GaN HEMTs using FP structure. The device process and characteristics are described. Effects of FP on current collapse in AlGaN/GaN HEMTs are also discussed. A model is proposed to explain the suppression mechanism of current collapse in AlGaN/GaN HEMTs.

Chapter 6 provides the conclusions that can be drawn from the work described in this thesis and provides recommendations for future research.

**Chapter: 1 Introduction**

#### References

- [1] H. Okumura, "Present status and future prospect of wide gap semiconductor high-power devices", Jpn. J. Appl. Phys., vol. 45, pp.9001-9010, 2006.

- [2] M. Kuzuhara, "Nitride power devices: Future perspectives", Int. RCIQE/CREST joint workshop, Hokkaido University, March 1-2, 2010.

- [3] E. Johnson, "Physical limitations on frequency and power parameters of transistors," in IRE International Convention Record, 1965, pp. 27-34.

- [4] I. Akasaki and H. Amano, "Crystal growth and conductivity control of group III nitride semiconductors and their application to short wavelength light emitters", Jpn. J. Appl. Phys., vol. 36, pp.5393-5408, 1997.

- [5] H. Matsunami, "Technological Breakthroughs in Growth Control of Silicon Carbide for High Power Electronic Devices", Jpn. J. Appl. Phys., vol. 43, pp.6835-6847, 2004.

- [6] S. O'Leary, B. Foutz, M. Shur, and L. Eastman, "Steady-state and transient electron transport within the III–V nitride semiconductors, GaN, AlN, and InN: Areview," Journal of Materials Science: Materials in Electronics, vol. 17, pp. 87-126, 2006.

- [7] Y-F Wu, M. Moore, A. Saxler, T. Wisleder, and P. Parikh, "40-W/mm double fieldplated GaN HEMTs", IEEE 64th Device Research Conference proc., 2006, pp.151-2.

- [8] Y.Yue, Z. Hu, J.Guo, B. S.-Rodriguez, G. Li, R. Wang, F.Faria, T. Fang, B. Song, X.Gao, S.Guo, T.Kosel, G. Snider, P. Fay, D. Jena, and H. Xing, "InAlN/AlN/GaN HEMTs with regrown ohmic contacts and f<sub>T</sub>of 370 GHz", IEEE Electron Device Lett., vol. 33, no. 7, pp. 988–990, July 2012.

- [9] M. Yanagihara, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, "Recent advances in GaN transistors for future emerging applications", Phys. Status Solidi A,vol. 206, no. 6, pp. 1221–1227, 2009.

- [10] U. K. Mishra, L. Shen, T. E. Kazior, and W. Yi-Feng, "GaN-Based RF Power Devices and Amplifiers," Proceedings of the IEEE, vol. 96, pp. 287-305, 2008.

- [11] M. A. Khan, Q. Chen, C. J. Sun, J. W. Yang, M. Blasingame, M. S. Shur, and H. Park, "Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors", Appl. Phys. Lett., vol. 68, p. 514, 1996.

- [12] X. Hu, G. Simin, J. Yang, M. A. Khan, R. Gaska, and M. S. Shur, "Enhancement mode

8

**Chapter: 1 Introduction**

AlGaN/GaN HFET with selectively grown pn junction gate", Electron. Lett., vol. 36, no. 8, pp. 753-754, 2000.

- [13] M. A. Khan, M. S. Shur, Q. C. Chen, and J. N. Kuznia, "Current/voltage characteristic collapse in AlGaN/GaN heterostructure insulated gate field effect transistors at high drain bias," Electronics Letters, vol. 30, pp. 2175-2176, 1994.

- [14] P. B. Klein and S. C. Binari, "Photoionization spectroscopy of deep defects responsible for current collapse in nitride-based field effect transistors," J. Phys.: Cond. Matt., p. R1641, 2003.

- [15] N. Q. Zhang, B. Moran, S. P. DenBaars, U. K. Mishra, X. W. Wang, and T. P. Ma, "Effects of surface traps on breakdown voltage and switching speed of GaN power switching HEMTs," in IEDM Technical Digest. International, 2001, pp. 25.5.1-25.5.4.

- [16] Y. Ohno, T. Nakao, S. Kishimoto, K. Maezawa, and T. Mizutani, "Effects of surface passivation on breakdown ofAlGaN/GaN high-electron-mobility transistors," Appl. Phys.Lett., vol. 84, pp. 2184-2186, 2004.

- [17] B. Luo, J. W. Johnson, J.Kim, R. M. Mehandru, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, A. G. Baca, R. D. Briggs, R. J. Shul, C. Monier, and J. Han, "Influence of MgO and Sc<sub>2</sub>O<sub>3</sub>passivation on AlGaN/GaN high-electron mobility transistors," Appl. Phys.Lett., vol. 80, pp. 1661-1663, 2002.

- [18] S.Arulkumaran, T. Egawa, H. Ishikawa, T. Jimbo, and Y. Sano, "Surface passivation effects on AlGaN/GaN high-electron-mobility transistors with SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, and silicon oxynitride," Appl. Phys.Lett.,vol. 84, pp. 613-615, 2004.

- [19] J. S. Lee, J. W. Kim, J. H. Lee, C. S. Kim, J. E. Oh, and M. W. Shin, "Reduction of current collapse in AlGaN/GaN HFETs using AlN interfacial layer," Electronics Lett., vol. 39, pp. 750-752, 2003.

- [20] Y. F. Wu, A. Saxler, M. Moore, R. P. Smith, S. Sheppard, P. M. Chavarkar, T. Wisleder, U. K. Mishra, and P. Parikh, "30-W/mm GaNHEMTs by field plate optimization," IEEE Electron Device Lett,, vol. 25, pp. 117-119, Mar 2004.

- [21] A. P. Edwards, J. A. Mittereder, S. C. Binari, D. S. Katzer, D. F. Storm, and J. A. Roussos, "Improved reliability of AlGaN-GaN HEMTs using an NH<sub>3</sub>/plasma treatment prior to SiN passivation," IEEE Electron DeviceLett., vol. 26, pp. 225-227, 2005.

- [22] N. Miura, T. Nanjo, M. Suita, T. Oishi, Y. Abe, T. Ozeki, H.Ishikawa, T. Egawa, and T.

Jimbo, "Thermal annealing effects on Ni/Au based Schottky contacts on n-GaN and AlGaN/GaN with insertion of high work function metal," Solid-State Electronics, vol. 48, pp. 689-695, May 2004.

- [23] H. Kim, J. Lee, D. Liu, and W.Lu, "Gate current leakage and breakdown mechanism in unpassivated AlGaN/GaN high electron mobility transistors by post-gate annealing," Appl. Phys. Lett., vol. 86, pp. 143505-3, 2005.

- [24] P. J. Hansen, Y. E. Strausser, A. N. Erickson, E. J. Tarsa, P. Kozodoy, E. G.Brazel, J. P. Ibbetson, U. Mishra, V. Narayanamurti, S. P. DenBaars, and J. S. Speck, "Scanning capacitance microscopy imaging of threading dislocations in GaN films grown on (0001) sapphire by metal organic chemical vapor deposition," Appl. Phys. Lett., vol. 72, pp. 2247-2249, 1998.

- [25] H. J. Im, Y. Ding, J. P. Pelz, B. Heying, and J. S. Speck, "Characterization of individual threading dislocations in GaN using ballistic electron emission microscopy," Phys. Rev. Lett., vol. 87, p. 106802, Sep 2001.

- [26] J. W. P. Hsu, M. J. Manfra, D. V. Lang, S. Richter, S. N. G. Chu, A. M. Sergent, R. N. Kleiman, L. N. Pfeiffer, and R. J. Molnar, "Inhomogeneous spatial distribution of reverse bias leakage in GaN Schottky diodes," Appl. Phys. Lett., vol. 78, pp. 1685-1687, 2001.

- [27] D. M. Schaadt, E. J. Miller, E. T. Yu, and J. M. Redwing, "Lateral variations in threshold voltage of an Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN heterostructure field-effect transistor measured by scanning capacitance spectroscopy," Appl. Phys. Lett., vol. 78, pp. 88-90, 2001.

- [28] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," IEEE Trans. Electron Devices, vol. 48, pp. 560-566, 2001.

- [29] O. Mitrofanov and M. Manfra, "Mechanisms of gate lag in GaN/AlGaN/GaN high electron mobility transistors," Superlattices and Microstructures, vol. 34, pp. 33-53, 2003.

- [30] M. Faqir, G. Verzellesi, A. Chini, F. Fantini, F. Danesin, G. Meneghesso, E.Zanoni, and C. Dua, "Mechanismsof RF current collapse inAlGaN/GaN High Electron Mobility Transistors," IEEE Trans. Device and Materials Reliability, vol. 8, pp. 240-247, 2008.

- [31] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN

heterostructure field effect transistors," Appl. Phys.Lett., vol. 77, pp. 250-252, 2000.

- [32] G. Koley, V. Tilak, L. F. Eastman, and M. G. Spencer, "Slow transients observed in AlGaN/GaN HFETs: effects of SiN<sub>x</sub> passivation and UV illumination," IEEE Trans. Electron Devices, vol. 50, pp. 886-893, 2003.

- [33] G. Koley and M. G. Spencer, "On the origin of the two-dimensional electron gas at the AlGaN/GaN heterostructure interface," Appl. Phys.Lett., vol. 86, p. 3, Jan 2005.

- [34] T. R. Prunty, J. A. Smart, E. N. Chumbes, B. K. Ridley, L. F. Eastman, and J. R. Shealy, "Passivation of AlGaN/GaN heterostructures with silicon nitride for insulated gate transistors," in Proc. High Performance Devices, 2000 (IEEE/Cornell Conference) 2000, pp. 208-214.

- [35] Y. Ando, Y. Okamoto, H. Miyamoto, N. Hayama, T. Nakayama, K. Kasahara, and M. Kuzuhara, "A 110-W AlGaN/GaN heterojunction FET on thinned sapphire substrate," in IEDM Technical Digest. 2001, pp. 17.3.1-17.3.4.

- [36] B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, "The effect of surface passivation on the microwave characteristics of undoped AlGaN/GaN HEMTs," IEEE Electron Device Lett., vol. 21, pp. 268-270, 2000.

- [37] Y. Ando, Y. Okamoto, H. Miyamoto, T. Nakayama, T. Inoue, and M. Kuzuhara,"10-W/mm AlGaN-GaN HFET with a field modulating plate," IEEE Electron Device Lett., vol. 24, pp. 289-291, 2003.

- [38] W. Saito, Y. Kakiuchi, T. Nitta, Y. Saito, T. Noda, H. Fujimoto, A. Yoshioka, T. Ohno, and M. Yamaguchi, "Field-plate structure dependence of current collapse phenomena in high-voltage GaN-HEMTs," IEEE Electron Device Lett., vol. 31, no. 7, pp. 659–661, Jul. 2010.

- [39] A. Brannick, N. A. Zakhleniuk, B. K. Ridley, J. R. Shealy, W. J. Schaff, and L. F. Eastman, "Influence of field plate on the transient operation of the AlGaN/GaN HEMT," IEEE Electron Device Lett., vol. 30, no. 5, pp. 436–438, May 2009.

- [40] W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura, and M. Yamaguchi, "Suppression of dynamic On-resistance increase and gate charge measurements in highvoltage GaN-HEMTs with optimized field-plate structure," IEEE Trans. Electron Devices, vol. 54, no. 8, pp. 1825–1830, Aug. 2007.

- [41] H. Ishida, D. Shibata, M. Yanagihara, Y. Uemoto, H. Matsuo, T. Ueda, T. Tanaka, and D. Ueda, "Unlimited high breakdown voltage by natural super junction of polarized semiconductor," IEEE Electron Device Lett., vol. 29, no. 10, pp. 1087–1089, Oct. 2008.

- [42] Z. Tang, S. Huang, Q. Jiang, S. Liu, C. Liu, and K.J. Chen, "High-voltage (600-V) lowleakage low-current-collapse AlGaN/GaN HEMTs with AlN/SiN<sub>x</sub> passivation," IEEE Electron Device Lett., vol. 34, no. 3, pp. 366–368, Mar. 2013.

# Chapter 2 Fundamentals of AlGaN/GaN HEMTs

#### 2.1 Introduction

In recent years AlGaN/GaN high-electron-mobility transistor (HEMT) has attracted much interest for high-power devices. Many active research groups are intensively working and reporting worldwide on AlGaN/GaN HEMTs. Although the performance achieved in AlGaN/GaN HEMTs is remarkable, fundamentals of material and device properties of AlGaN/GaN HEMTs is still a pending issue The value of some of basic material parameters is unknown. Important device properties, such as polarization, gate leakage, electron velocity, are still highly controversial issues. In this chapter, fundamentals of AlGaN/GaN material and its application in HEMTs will be discussed.

#### 2.2 High-electron-mobility transistor

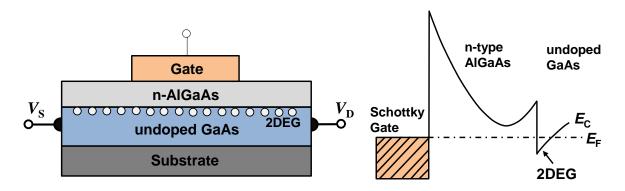

The development of heterostructures in the 1980s offered the opportunity of tremendous progress in the performance of microwave transistors. HEMT is a field effect device based on a heterostructure with different band-gap materials. To describe the structure and operation of a HEMT device, a GaAs-based HEMT is considered. A conventional AlGaAs/GaAs HEMT and its band diagram are illustrated in Fig. 2.1. The wide band-gap AlGaAs material is n-type, but it is depleted of free carriers by the reverse or zero-biased Schottky contact, while the narrow band-gap GaAs material is undoped. At the boundary between two

Fig. 2.1. Conventional AlGaAs/GaAs HEMT structure and its band diagram under zero gate bias.

materials, the band-gap discontinuities cause the conduction band of GaAs to dip below the Fermi level, creating a potential well with a high carrier concentration. This region of high carrier density is very thin, so that it is named two-dimensional electron gas (2DEG). The electrons of 2DEG travel along the GaAs channel without encountering ionized donor atoms. This makes them to have high mobility, favoring fast response times and high-frequency operation.

#### 2.3 Properties of III-nitride semiconductors

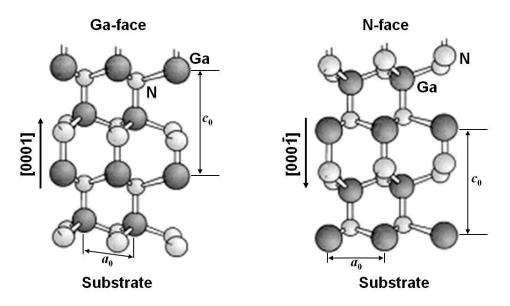

The III-nitrides AlN, GaN, and InN can crystallize in the following three crystal structures: wurtzite, zinc-blende, and rock-salt. The chemical bonds of III-nitride compounds such as GaN are predominantly covalent, which means that each atom is tetrahedrally bonded to four atoms of the other type. Because of the large difference in electronegativity of Ga and N atoms, there is a significant ionic contribution to the bond which determines the stability of respective structural phase. Atomic arrangement in both Ga-face and N-face wurtzite GaN crystal is shown in Fig. 2.2 [1]. There is no inversion symmetry in this lattice along the direction from a Ga atom to the nearest neighbor N atom. Wurtzite GaN crystals have two distinct faces, commonly known as Ga-face and N-face, which correspond to (0001) and (0001) crystalline faces. For N-face material this can be obtained by flipping the Ga-face material upside-down. It has to be noted that for Ga-face material the N atom is stacked

Fig. 2.2. Atomic arrangement in both Ga-face and N-face wurtzite GaN crystal [1].

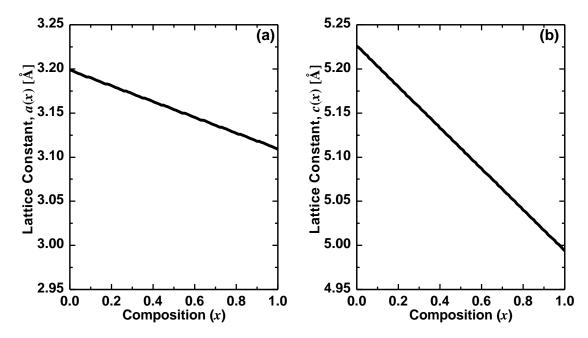

directly over the Ga atom and vice versa for N-face. The two parameters define the wurtzite lattice. These are the edge length of the basal hexagon ( $a_0$ ) and the height of the hexagonal lattice cell ( $c_0$ ) along the [0001] direction. The subscript "0" indicates that these values are those of the equilibrium lattice. The lattice constants a(x) and c(x) of Al<sub>x</sub>Ga<sub>1-x</sub>N are predicted to follow the composition-weighted average between the binary compounds AlN and GaN (Vegard's law) [2]:

$$a_{AIGaN}(x) = (3.1986 - 0.0891x) \stackrel{0}{\text{A}} c_{AIGaN}(x) = (5.2262 - 0.2323x) \stackrel{0}{\text{A}}$$

(2.1)

The graphical representation of the lattice constants a(x) and c(x) of wurtzite III nitride alloys are shown in Fig. 2.3. The calculated values are in good agreement with the reported experimental values [3-6] for wurtzite AlGaN.

Fig. 2.3. (a) The edge length of the basal hexagon, lattice constant a(x) and (b) the height of the hexagonal lattice cell, lattice constant c(x) for wurtzite Al<sub>x</sub>Ga<sub>1-x</sub>N are calculated using the Vegard's law.

Usually, GaN materials are typically grown on a different substrate material using a heteroepitaxial growth technique, since bulk crystal growth of GaN is presently very difficult. Sapphire is a common substrate material for the epitaxial growth of GaN. However, there is a 14% lattice mismatch between hexagonal GaN and sapphire. Careful control of the initial growth conditions is important and low-temperature-grown GaN and AlN are typically used as a buffer layer [3]. SiC is also a widely employed substrate for epitaxial growth of GaN. SiC has a rather small lattice mismatch of 3% with GaN and exhibits a large thermal conductivity of 4.5 W/cm-K, which is very beneficial for high-power device applications. Since GaN is composed of Ga with a large ionic radius and N with a small ionic radius and thus forms a slightly distorted tetrahedral arrangement, it exhibits spontaneous polarization. When AlGaN is grown on GaN, piezoelectric polarization is further added due to the tensile stress generated in the AlGaN layer. With these two polarization effects, a fixed positive charge is generated near the AlGaN/GaN heterointerface in the AlGaN layer and correspondingly two-dimensional electron gas is induced in the GaN layer. The density of free electrons in GaN increases with increasing Al content of AlGaN and reaches about  $1.7 \times$  $10^{13}$  cm<sup>-2</sup> when the Al content is increased to 25 to 30%. It is a unique characteristic of the

AlGaN/GaN heterostructure that a high density of two-dimensional electrons is achieved without the addition of any donor impurities to the AlGaN layer.

#### 2.4 Polarization effects

Polarization in III-nitride materials is a crucial material property that enables and determines the actual operation of nitride based devices. The basis for macroscopic polarization in materials with bound charges is a microscopic polarization of atoms due to bonds between atoms, when the center of negative charge (electrons) shifts away from the center of the positive charge (nuclei) [7]. Such a polarized atom constitutes a dipole with a dipole moment p. Polarization state of a material can be then described by the vector of electric polarization P, which is defined as a total dipole moment of a unit volume. If the dipoles are identical and their concentration is n, the formula can be expressed as

$$\vec{P} = n \vec{p} = \frac{\vec{p}}{\Omega_0}.$$

(2.2)

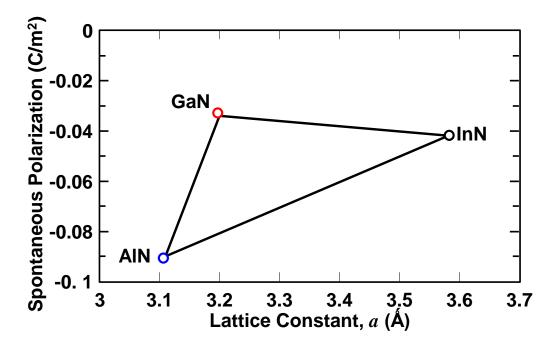

Where,  $\Omega_0$  is a volume that is occupied by a single dipole. If there is no electric field present, most materials have no dipoles or the orientation of the dipoles is random and hence the total polarization is zero. However, in low symmetry compound crystals, this may not be true and the asymmetry of the bonding may form dipoles, which are consequently a source of polarization. A condition for a structure to exhibit piezoelectric polarization  $P_{\text{PE}}$ , which is a polarization originating in a mechanical deformation, is to lack a center of symmetry. Moreover, if the crystal class has either no rotation axis or a single rotation axis, which is not an inversion axis, the bonding in this crystal will be intrinsically asymmetric. Under this condition, the material acts as a pyroelectric and shows a built-in spontaneous polarization  $P_{\text{SP}}$ , even without any mechanical or electrical perturbation. This low symmetry axis in the crystal, parallel with the built-in polarization, is called the pyroelectric axis. Another class of materials that show polarization in absence of the electric field are ferroelectrics. In these materials,  $P_{\text{SP}}$  can be inverted by applying a strong electrostatic field. This effect allows an accurate measurement of the spontaneous polarization,  $P_{\text{SP}}$ , which is not possible in pyroelectrics. Figure 2.4 shows the  $P_{\text{SP}}$  of III-nitride materials.

Fig. 2.4. Spontaneous polarization of III-nitride materials.

In wurtzite crystals, the  $sp^3$  hybridization is not perfect and the bond along the [0001] direction has a different ionicity than the other bonds and hence the wurtzites show the spontaneous polarization. The macroscopic polarization arises in low symmetry crystals due to a perturbation (built-in, mechanical, electrical, etc.) in the crystal symmetry or more accurately, in the bond symmetry. For small strains, the polarization depends on strain linearly. If there is a non-zero polarization at zero strain, we call this polarization spontaneous. There is no other difference between piezoelectric and spontaneous polarization. The total polarization is a sum of both types of polarization,  $P = P_{SP} + P_{PE}$ . The piezoelectric polarization can be expressed, in various ways, e.g., as [8]

$$P_{i}^{PE} = \sum_{jk} d_{ijk} t_{jk} = \sum_{jk} d_{ijk} \left( \sum_{lm} C_{jklm} \varepsilon_{lm} \right) = \sum_{lm} e_{ilm} \varepsilon_{lm} = \sum_{lm} e_{ilm} \left( \sum_{lm} S_{lmjk} t_{jk} \right).$$

(2.3)

Here, piezoelectric constants are denoted as  $e \ (= dC)$ , piezoelectric moduli are  $d \ (= eS)$ , elastic constants (stiffness) are *C* and elastic compliances are  $S \ (= C^{-1})$ . The variables depend on external conditions (electric field *E*, stress *t*, and the resulting strain  $\varepsilon$ ) and therefore can take different forms.

In GaN based HEMT devices, the GaN layer is usually several orders of magnitude thicker than the AlGaN layer, which is only several nanometers thick. Therefore, it is a possible assumption that the GaN layer will be fully relaxed, and hence show no piezoelectric polarization, while the AlGaN layer will be strained. Therefore, strain can be expressed as

$$\varepsilon = \frac{a(0) - a(x)}{a(x)} \tag{2.4}$$

where, *x* is the Al fraction of AlGaN layer. The *a*(0) and *a*(*x*) are lattice constants of an unstrained GaN and strained Al<sub>x</sub>Ga<sub>1-x</sub>N layer, respectively. Figure 2.5 shows the lattice constants (in this simplified drawing, the atoms that have to form bonds are represented by red dots) of an unstrained AlGaN are different from that of an unstrained GaN (left). When AlGaN grows on the top of GaN, the constant of AlGaN has to match the lattice constant of GaN. This exerts a strong stress on the grown AlGaN layer. This stress causes strain (right) in both of the basal plane ( $\varepsilon_1$ ) and the growth ( $\varepsilon_3$ ) directions, respectively. The dashed line represents an unstrained piece of AlGaN. In piezoelectric materials, the strain results in polarization field  $P_{\text{PE}}$ . The Ga-face growth is assumed here. The structure in the middle represents the orientation of the wurtzite structure in the heterostructure. In equation 2.3, the relation

Fig. 2.5. Stain effect of an AlGaN/GaN heterostructure.

between piezoelectric polarization,  $P_{PE}$  and strain,  $\varepsilon$  depends on the form of piezoelectric constant matrix [9] and the equality of strain in basal and growth direction ( $\varepsilon_1 = \varepsilon_3$ ). It means that shear strains are absent in the polarization vector. Therefore,  $P_{PE}$  can be expressed as

$$P_{3}^{\rm PE} = 2e_{31}\varepsilon_{1} + e_{33}\varepsilon_{3} \tag{2.5}$$

and the relation between the strain along the polar axis (in the growth direction)  $\varepsilon_3$  and in the basal plane  $\varepsilon_1$  as

$$\varepsilon_3 = -2\frac{C_{13}}{C_{33}}\varepsilon_1. \tag{2.6}$$

Combining the previous formulas give the expression of piezoelectric polarization as

$$P_{3}^{PE} = 2 \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right) \varepsilon_{1} = 2d_{31} \left( C_{11} + C_{12} - 2 \frac{C_{13}^{2}}{C_{33}} \right) \varepsilon_{1}.$$

(2.7)

In the case of Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN heterostructure, the barrier layer grows with a lateral strain  $\varepsilon_1 \approx 8 \times 10^{-3}$  and stress  $\approx 3.6$  GPa.

#### 2.5 Polarization induced charge

A polarization induced charge density given by  $\sigma = \nabla P$  is associated with a gradient of polarization in space is [10]. In analogy, at an abrupt interface of a top/bottom layer (AlGaN/GaN heterostructures) the polarization can decrease or increase within a bilayer, causing a polarization sheet charge density defined by [10]

$$\sigma = P_{GaN} - P_{AIGaN} = P_{GaN}^{SP} + P_{GaN}^{PE} - P_{AIGaN}^{SP} - P_{AIGaN}^{PE}$$

$$= P^{SP}(0) + P^{PE}(0) - P^{SP}(x) - P^{PE}(x)$$

(2.8)

where, the argument x is the Al fraction of  $Al_xGa_{1-x}N$ . Since the GaN layer is usually several

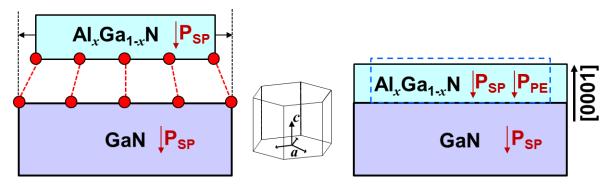

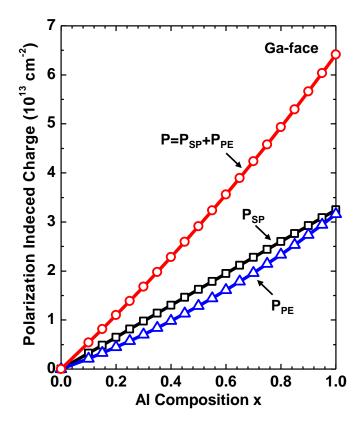

orders of magnitude thicker than AlGaN, it is considered to be relaxed and hence without piezoelectric polarization,  $P_{PE}(0) = 0$ . Since, according to Fig. 2.4, the magnitude of the spontaneous polarization is higher in AlGaN than in GaN, there will be a positive charge at the AlGaN/GaN interface. However, there is usually a material that lacks any polarization (either air or a passivation layer) at the AlGaN surface of the device. Figure 2.6 shows calculated polarization charge (i.e., sheet charge,  $\sigma/e$ ) at the AlGaN/GaN interface caused by the spontaneous and piezoelectric polarization versus alloy composition, proving that the contribution of both kinds of polarization to the sheet charge is nearly the same [1]. For x = 0.25, a remarkably high sheet charge  $\sigma/e$  of  $1.4 \times 10^{13}$  cm<sup>-2</sup>. These calculated sheet charges located at the AlGaN/GaN interface are about ten times higher than in comparable heterostructures of other III–V heterostructures [11] thus high polarization induced sheet carrier concentrations may be expected.

Fig. 2.6. Calculated polarization charge density caused by spontaneous and piezoelectric polarization at the lower interface of a Ga-face GaN/AlGaN/GaN heterostructure vs alloy composition of the barrier.

#### 2.6 Formation of 2DEG

In order to calculate the electronic states and charge density at the interface, the 1D Schrödinger equation coupled with the Poisson's equation needs to be solved self consistently [12-17]. As a result, two major features are observed: there is a charge setback from the interface, and there is an upward shift of the conduction band edge corresponding to formation of a bound state in the presence of the approximately triangular potential well at the interface. Within single band effective mass theory, the 1D Schrödinger wave equation can be written as [18,19]

$$-\frac{\hbar^2}{2}\frac{d^2}{dz^2}\frac{1}{m^*(z)}\phi_i(z) + V(z)\phi_i(z) = E_i\phi_i(z)$$

(2.9)

where,  $m^*$  is the electron effective mass,  $\phi_i$  is the wave function of *i*th subband,  $E_i$  is the energy of *i*th subband, V is the potential energy. The V(z) can be expressed as

$$V(z) = -q\psi(z) + \Delta E_{\rm c} + V_{\rm xc} \tag{2.10}$$

where,  $\psi$  is the electrostatic potential,  $\Delta E_{\rm C}$  is the conduction band discontinuity, and  $V_{\rm xc}$  is the energy of the local exchange-correlation potential. Once the Schrödinger equation is solved for the envelope functions and the subband energy levels, the electron sheet charge density for each subband can be calculated by applying Fermi statistics

$$n_i = \frac{m^* k_{\scriptscriptstyle B} T}{\pi \hbar^2} \ln \left[ 1 + \exp\left(\frac{E_f - E_i}{k_{\scriptscriptstyle B} T}\right) \right], \qquad (2.11)$$

where,  $E_f$  is the Fermi energy. The electron density at position z is then easily calculated by

$$n_{2D}(z) = \sum_{i} n_{i} |\psi_{i}(z)|^{2}.$$

(2.12)

The Poisson equation needs to be solved in terms of the displacement field, D(z)[18]

$$\nabla \cdot D(z) = \rho(z), \tag{2.13}$$

where, total charge density,  $\rho(z) = -[n(z) - p(z) - N_D^+(z) + N_A^-(z)]$ . Here,  $N_D^+$  and  $N_A$  are ionized donor and acceptor densities, respectively. n(z) and p(z) are free electron and hole carrier concentrations, respectively. However, a hole, the donor, acceptor is assumed to be not present in the analysis of AlGaN/GaN. Therefore, the presence of polarization charge density,  $\sigma(z)$ , it can be represented as

$$\rho(z) = -[n(z) - \sigma(z)] \tag{2.14}$$

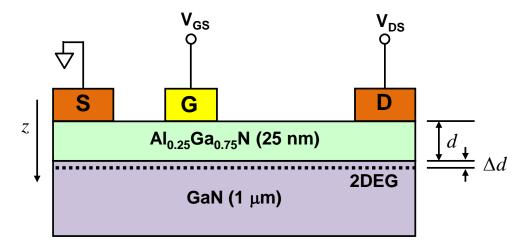

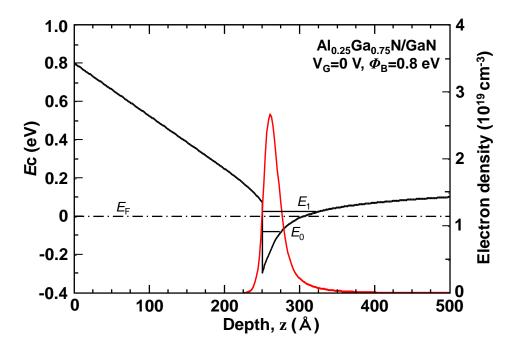

In order to distinguish the two-dimensional electrons in the quantum well region, a cut-off value is used, which is set to the highest subband level used in the Schrödinger equation. The free electron density below this threshold value is set to 0. Equations (2.9) and (2.12) are solved self-consistently until the potential converges. The simulated heterostructure consists of a 25-nm AlGaN and a 1- $\mu$ m GaN layer from the gate to the substrate, as shown in Fig. 2.7. Both GaN and AlGaN layers are assumed undope. A Schottky barrier height,  $\Phi_B$ , of 0.8 eV for the metal-AlGaN interface is considered. Figure 2.8 shows results of the Schrödinger-Poisson self-consistent calculation for Al content of 0.25 in the heterostructure, with gate bias  $V_{GS}=0$  V. The conduction band, the subband energy and the 2D electron density are shown in the figure. Two subbands are taken into account for both cases.

Fig. 2.7 An AlGaN/GaN HEMT.

Fig. 2.8. Results of Schrödinger-Poisson self-consistent calculation at Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN heterostructure.

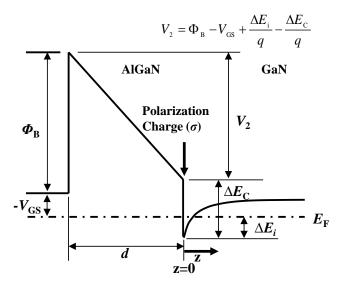

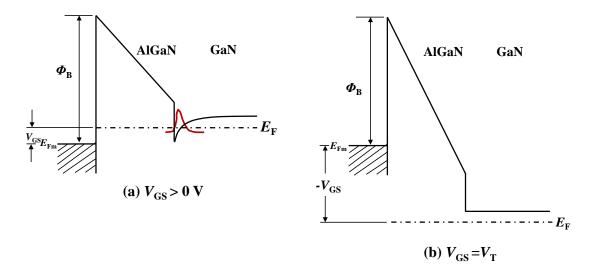

Figure 2.9 shows the conduction band of the AlGaN/GaN heterostructure, where  $\Phi_{\rm B}$  is a Schottky barrier. Under the gate of an AlGaN/GaN HEMT, Schottky barrier is modified by the applied gate voltage.

Fig. 2.9. Vertical cross-section of the conduction band of the A1GaN/GaN heterostructure.

The Fermi level is denoted by  $E_F$  and  $\Delta E_C$  is the conduction band offset. The  $\Delta E_i$  is the subband energy. The boundary conditions are:

If,

$$z=0$$

, then  $V(z)=0$

and  $z=-d$ , then  $V(z)=-V_2$

The potential energy V(z) is found from the solution of Poisson's equation

$$\frac{d^2 V(z)}{dz^2} = -\frac{q\sigma(z)}{\varepsilon},$$

(2.15)

where,  $\varepsilon$  (= $\varepsilon_0 \varepsilon_r$ ) is the dielectric constant of AlGaN layer and  $\sigma(z)$  is the polarization charge density. The conduction band potential of AlGaN is defined by  $V_2$ .

$$V_2 = -F_s \cdot d + \frac{q\sigma d}{\varepsilon} \tag{2.16}$$

where,  $F_s$  is the hetero-surface electric field and *d* is a thickness of the AlGaN layer. By Gauss's theorem, the relationship between  $F_s$  and 2DEG carrier ( $n_{2D}$ ) can be represented

$$qn_{2D} = \varepsilon F_s \tag{2.17}$$

From the equations 2.16 and 2.17,  $F_{\rm s}$  can be replaced and the relationship between  $n_{\rm 2D}$  and  $V_{\rm GS}$  is

$$n_{2D} = \frac{\varepsilon}{qd} \left\{ V_{GS} - \left( \Phi_B - \frac{\Delta E_C}{q} - \frac{q\sigma d}{\varepsilon} + \frac{\Delta E_i}{q} \right) \right\}$$

$$= \frac{\varepsilon}{q(d + \Delta d)} \left\{ V_{GS} - V_T \right\}, \qquad (2.18)$$

where,  $V_{\rm T}$  is the threshold voltage. It can be expressed as

$$V_{T} = \Phi_{B} - \frac{\Delta E_{C}}{q} - \frac{q\sigma d}{\varepsilon} + \frac{\Delta E_{i}}{q}, \qquad (2.19)$$

here,  $\Delta d$  and  $E_{\rm F0}$  are the following:

$$\Delta d = \frac{\mathcal{E}a}{q} \quad , \quad \Delta E_i = E_{F0} + an_{2D}$$

Figure 2.10 shows the conduction band diagram of an AlGaN/GaN HEMT with applied gate bias voltage,  $V_{GS}$ . The on-state (a) and off-state (b) conduction band profiles of a device are also shown.

Fig. 2.10. The conduction band diagram of an AlGaN/GaN HEMT. (a) A fully open channel where the applied  $V_{GS}$  is positive. b) Flat band condition where  $V_{GS}=V_T$ .

#### 2.7 Velocity-field characteristics

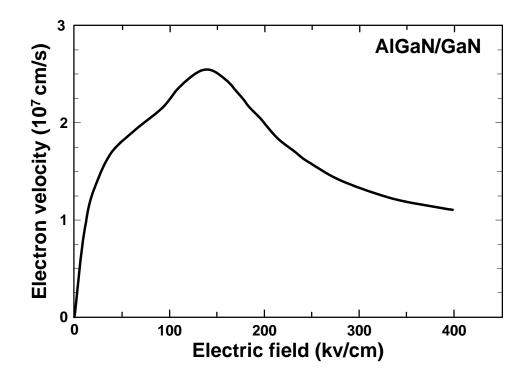

When an electron distribution is subjected to an electric field, the electrons tend to move in the field direction (opposite to the field F) and gain velocity from the field. However, because of imperfections, they scatter in random directions. A steady state is established in which the electrons have some net drift velocity in the field direction. In most electronic devices a significant portion of the electronic transport occurs under strong electric fields. This is especially true of field effect transistors. At such high fields ( $F \sim 1-100 \text{ kV/cm}$ ) the electrons get "hot" and acquire a high average energy. The extra energy comes due to the strong electric fields. The drift velocities are also quite high. The description of electrons at such high electric fields is quite complex and requires either numerical techniques or computer simulations.

For long-channel devices, the field is low enough that the carrier velocity is treated as being proportional to the field, i.e., constant mobility. At low fields the drift velocity increases linearly with the field, and the slope corresponds to a constant mobility ( $\mu = v/F$ ). At higher fields, the carrier velocity deviates from a linear dependence. It becomes lower than simple extrapolation from the low-field slope, and eventually saturates to a value called saturation velocity,  $v_s$ . In drift-diffusion simulations of AlGaN/GaN HEMTs, the use of the proper electron transport model is critical. Traditionally, the high-field transport model of electrons was assumed to follow [20] as

$$v(E) = \frac{\mu F}{\left(1 + \left(\mu F / v_{s}\right)^{\beta_{c}}\right)^{1/\beta_{c}}}.$$

(2.20)

This formula is used for Si and other semiconductors with a similar band structure. Here, parameter  $\beta_C = 1.7$  for GaN [20]. The low-field mobility depends on temperature and doping concentration. Figure 2.11 shows the calculated velocity–field characteristics of an AlGaN/GaN HEMT for steady state condition. At room temperature, high-field mobility,  $\mu$ =1700 cm<sup>2</sup>V<sup>-1</sup>sec<sup>-1</sup> is considered [20]. The peak electron velocity of  $v_s$ =2.5×10<sup>7</sup> cm/s is calculated. However, for transient state condition of devices, mobility is not constant. It depends on different kind of scattering mechanisms such as acoustic phonon scattering, polar and non -polar optical phonon scattering, and piezoelectric scattering [19-20].

Fig. 2.11. Electron velocity versus electric field of an AlGaN/GaN HEMT.

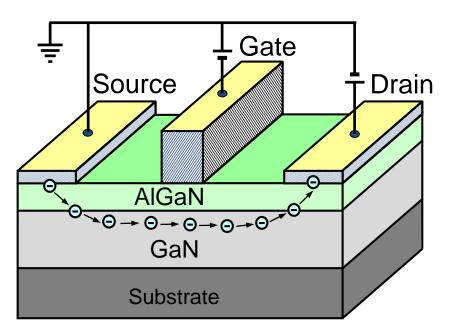

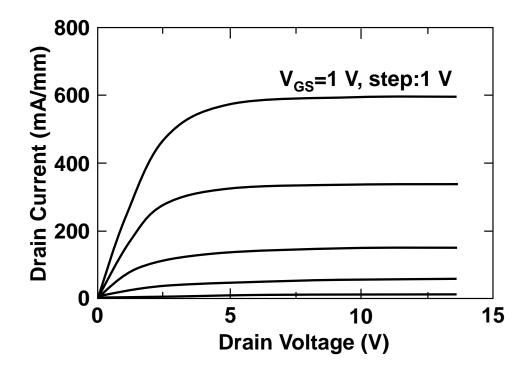

# 2.8 Principle of operation

Figure 2.12 shows a schematic view of an AlGaN/GaN HEMT device. In a real transistor, the length of the device is much larger than the thickness of the AlGaN barrier. The current flows between the ohmic contacts, from drain to source, and it is modulated by the voltage applied at the gate (i.e., Schottky contact). The drain current,  $I_D$  can be represented as a function of  $n_{2D}(x)$  and V(x) in the lateral direction.

$$I_{D} = W_{G}qn_{2D}(x)\mu\left(\frac{\partial V(x)}{\partial x}\right), \qquad (2.21)$$

where,  $\mu$  is the channel electron mobility and  $W_G$  is the gate width. By integrating from source side of the gate edge (x = 0) to drain side of gate edge ( $x = L_G$ ), the I<sub>D</sub> is obtained as

$$I_{D} = \frac{\varepsilon \mu W_{G}}{(d + \Delta d) L_{G}} \left\{ (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right\}$$

(2.22)

Fig. 2.12. Schematic structure of an AlGaN/GaN HEMT device. The figure is not to scale.

where, the drain-to-source voltage is defined as  $V_{DS}$ . When  $V_{DS}$  is small, the electron velocity is simply proportional to the electric field ( $v=\mu F$ ). Further, assuming that the saturation current occurs when the electric field at the drain side of the gate exceeds the saturation velocity ( $v_s=\mu F_s$ ) and the longitudinal field distribution in the channel where the potential is below the saturation voltage. The saturation drain current can be expressed as

$$I_{D}^{s} = \frac{\varepsilon \mu W_{G} E_{s}}{d + \Delta d} \left\{ \sqrt{\left(V_{G} - V_{T}\right)^{2} + E_{s}^{2} L_{G}^{2}} - E_{s} L_{G} \right\}$$

(2.23)

In this equation,  $E_s$  is an electric field that drift velocity reaches a peak speed in electric field characteristic. Moreover, in the short gate HEMT,  $L_g$  is small enough compared to  $(V_{GS}-V_T) / F_s$ , thus, the  $I_D^s$  can be expressed as

$$I_D^s = \frac{\mathcal{E}W_G \mathcal{V}_s}{d + \Delta d} \Big( \mathcal{V}_{GS} - \mathcal{V}_T \Big).$$

(2.24)

If the  $I_D^s$  varies linearly with the  $V_{GS}$ , the  $g_m$  is a constant value, which is proportional to the saturation velocity. It is also inversely proportional to the distance from gate to channel (i.e.,

$d+\Delta d$ ). This distance can be designed to be smaller for obtaining high  $g_m$ . The transconductance  $(g_m)$  is expressed as

$$g_m = \frac{\varepsilon W_G v_s}{d + \Delta d}.$$

(2.25)

It is a major feature of an AlGaN/GaN HEMT. Combine of equations 2.24 and 2.25 are expressed as

$$I_{D}^{s} = g_{m} (V_{GS} - V_{T}).$$

(2.26)

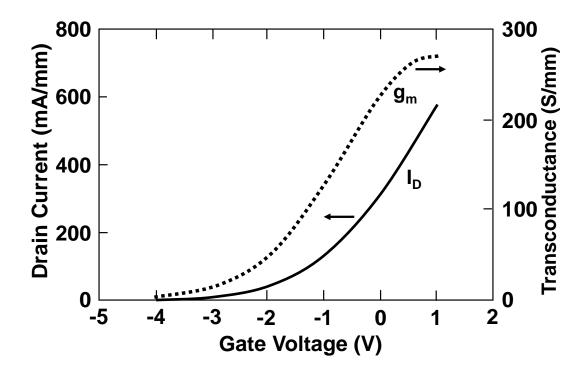

Figs. 2.13 and 2.14 show the current voltage and the transconductance characteristics of an AlGaN/GaN HEMT.

Fig. 2.13 Typical current-voltage characteristics of an AlGaN/GaN HEMT.

Fig. 2.14 Typical drain current and transconductance as a function gate voltage of an AlGaN/GaN HEMT.

# **2.9 Current collapse**

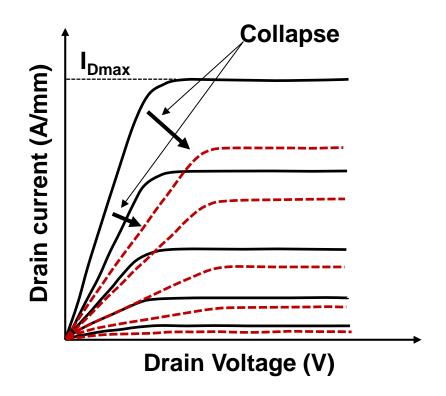

In the literature, the term current collapse is used with two meanings. In a wider sense, it means a class of phenomena that lead to drain current degradation and increased dynamic  $R_{on}$ . Historically, however, it was defined, during the development of GaAs-based HEMTs, as a persistent yet recoverable reduction of the static current at a high drain bias voltage [21]. Some of the other phenomena that fall under the wider meaning of the current collapse are gate and drain lag, and static-pulse dispersion. Gate (drain) lag refers to  $I_D$  transient in response to gate (drain) voltage pulses keeping the drain (gate) voltage constant. The corresponding measurement techniques are combined in the pulsed *I-V* measurements, in which both the gate and drain voltages are pulsed at the same time from a quiescent bias. Figure 2.15 shows a sketch of AlGaN/ GaN HEMT's *I-V* characteristics before (solid lines) and after (dotted lines) current collapse. The leakage current from the gate and carrier trapping in general, into the surface and buffer traps is the physical cause behind the current collapse class of the phenomena.

Fig.2.15 A sketch of AlGaN/ GaN HEMT's current–voltage characteristics before (solid lines) and after (dotted lines) current collapse.

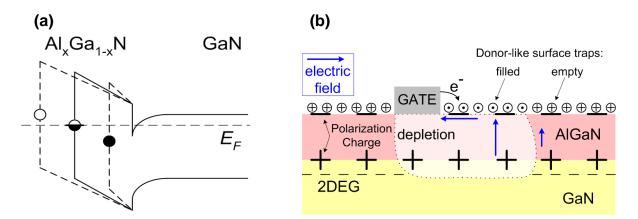

The term traps refers to energy states in the band-gap of a semiconductor. The origin of traps can be a consequence of several factors, e.g., crystal defects, dislocations, or the presence of impurities. These trap states may be empty or occupied by electrons, which has an impact on the charge they carry. Trap states in the upper part (above the neutral level) of the band gap (closer to the conduction band) are acceptor-like, neutral when empty and negatively charged when occupied. Trap states in the lower part (below the neutral level) of the band gap (closer to the valence band) are donor-like, positively charged when empty and neutral when occupied. Traps at the interface or the surface of a device play an important role in the device operation and performance. One of the conclusions of Section 2.4 was that there is large negative charge at the surface of the device. The negative charge would repel the electrons away from the interface and deplete the channel. Moreover, there is a question, what is the origin of the electrons in 2DEG. It was suggested that, after the growth, during the cooling process, free electrons would compensate the polarization-induced charge [22]. As a different solution to both problems, nowadays widely accepted, it

was suggested that surface donor-like traps could be the source of both the channel electrons and the positive charge, screening the large negative polarization-induced charge [23-25]. For thin AlGaN barrier thickness, the surface trap level is below the Fermi level, the traps are occupied and hence neutral as shown in Fig. 2.16 (a). At a critical barrier thickness, the surface traps reach the Fermi level and the electrons from these traps are driven into the Fermi level and the electrons from these traps are driven into the channel by the strong polarization-induced electric field in AlGaN [24]. The band diagram, with the energy level of the surface traps, with varying barrier thickness is shown in Fig. 2.16 (a). As the donor-like traps are emptied, they become positively charged and in effect they reduce (by passivation) the negative charge. In the absence of holes, the energy of these traps has been theoretically predicted to be ~1.65 eV in Al<sub>0.35</sub>Ga<sub>0.65</sub>N [25].

Fig. 2.16. The effect of surface traps on 2DEG creation, reduction of the negative surface charge and current collapse. (a)The trap energy level is below the Fermi level and the states are filled for thin AlGaN barrier [24]. (b) Surface trapping effects [25].

At large negative gate voltage, electrons from gate may leak to the trap states in the ungated surfaces and create a "virtual gate" and modulate the depletion region, as shown in Fig. 2.16 (b). In pulsed operation, the gate voltage changes abruptly and since the response of the trapped electrons is not immediate, it leads to RF drain current collapse phenomenon. The transient time constants depend on the energy level of the traps [26]. The surface donor-like traps used to explain the origin of 2DEG can explain RF current collapse with time constants on the order of seconds [27], as observed experimentally [28].

However, transients with shorter time constants (10-100  $\mu$ s) can be explained by the existence of surface donors with energy level 0.3 eV [27] and 0.25 eV [29].

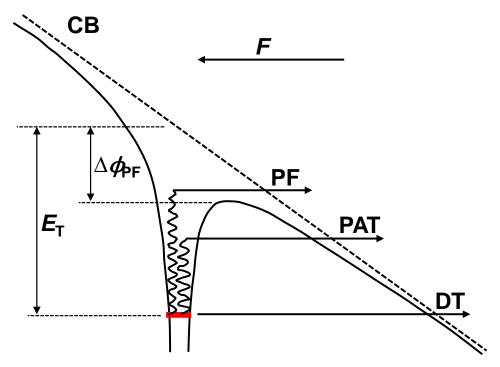

Mantra et. al. has investigated the field-dependence of active traps to interpret trapping/ detrapping in the barrier near the AlGaN surface [30-32]. Figure 2.17 shows energy band diagram of a trapping center in the presence of electric field together with three possible mechanisms of electron emission [32]. First, trapped electrons are thermally ionized over the lowered barrier (Poole-Frenkel effect) on the conduction band and drift down to the channel. Second, combination of thermal energy and electric field can lead to the phonon-assisted tunneling (PAT). Finally, direct tunneling can happen when the bands are sufficiently tilted. If the emission process of trapped charge in AlGaN barrier follows the Poole-Frenkel electron emission among three different-type emissions, the emission rate (*e*) should be proportional to  $\exp(\sqrt{F})$  or  $\exp(\alpha \sqrt{V_D})$ , where *F* is an electric field,  $V_D$  is an applied voltage between gate and drain, and  $\alpha$  is a correlation constant between the applied voltage

Fig. 2.17. Energy diagram of the trapping center in the presence of the electric field. Arrows indicate the possible mechanisms of electron emission: thermal ionization over the lowered barrier (Poole-Frenkel effect), direct tunneling (DT) into the conduction band (CB), and phonon assisted tunneling (PAT).

and the lowering of the trap potential. The relationship between emission rate and  $V_D$  at  $V_{GS}$ = 0 V is derived from the combination of following three equations [32]. First, assuming that the emission is a thermally activated process, the emission rate from trap level can be expressed by the following Arrhenius equation:

$$e = AT^{2} \exp\left(-\frac{E_{i}}{kT}\right).$$

(2.27)

Second, the barrier decrease  $(\Delta \phi_{PF})$  due to the high electric field (Poole-Frenkel effect) is proportional to the square root of the applied electric field (*F*) as follows:

$$\Delta\phi_{\rm PF} = \left(\frac{q^3}{\pi\varepsilon}\right)^{1/2} \sqrt{F} = \beta\sqrt{F}, \qquad (2.28)$$

where, q is a unit of electron charge and  $\varepsilon$  is the dielectric constant. Third, the ionization energy as a function of a field can be written as:

$$E_i(F) = E_i(0) - \beta \sqrt{F}, \qquad (2.29)$$

where,  $E_i(0)=E_T$  is the binding energy of the electron on the trap in zero field. Finally, the field-dependent emission rate equation is deduced as:

$$e(F) = e(0) \exp\left(\frac{\Delta\phi_{PF}}{kT}\right) = e(0) \exp(\beta \sqrt{V_D}).$$

(2.30)

More strictly, the field-dependent emission rate equation should include built-in potential due to polarization field in AlGaN/GaN barrier ( $\sim 10^6$  V/cm). The emission rate can be rewritten as:

$$e(F) = e(0)\exp(\beta \sqrt{V_D + V_{bi}}),$$

(2.31)

where,  $V_{bi}[=(\Phi_{\rm B} - \Delta E_{\rm C} + E_{\rm Fi})/d_{\rm AlGaN}]$  is the built-in voltage across AlGaN barrier,  $\Phi_{\rm B}$  is the barrier height at the AlGaN surface,  $\Delta E_{\rm C}$  is the conduction band offset between AlGaN and GaN, and  $E_{\rm Fi}$  is the difference between Fermi level and GaN conduction band edge at the AlGaN/GaN interface. It is considered that Poole-Frenkel type emission is dominant for the trapped charge near the AlGaN surface. It is inferred that the trapped electrons stay near the AlGaN surface below a certain  $V_{\rm DS}$  ( or  $V_{\rm D}$ ), resulting in channel depletion and drain current collapse, until  $V_{\rm DS}$  is large enough for phonon-assisted field emission or direct field emission from the surface to the channel.

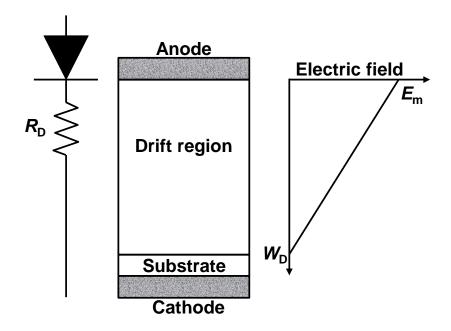

#### 2.11 Trade-off between on-resistance and breakdown voltage

One of the most unique features of power semiconductor devices is their ability to withstand high voltages. The desire to control larger power levels has encouraged the development of power devices with larger breakdown voltages. In a semiconductor, the ability to sustain high voltages without the onset of significant current flow is limited by the avalanche breakdown phenomenon, which is dependent on the electric field distribution within the structure. High electric fields can be created within the interior of power devices as well as at their edges. The design optimization of power devices must be performed to meet the breakdown voltage requirements for the application while minimizing the on-state voltage drop, so that the power dissipation is reduced. The resistance of the ideal drift region can then be related to the basic properties of the semiconductor material. Such semiconductor structure own a triangular electric field distribution, as shown in Fig. 2.18, within a uniformly doped drift region with the slope of the field profile being determined by the doping concentration. The maximum voltage that can be supported by the drift region is determined by the maximum electric field  $(E_m)$ reaching the critical electric field  $(E_c)$  for breakdown for the semiconductor material. The critical electric field for breakdown and the doping concentration then determine the maximum depletion width  $(W_D)$ . The resistance of ideal drift region of area, A, is given by:

$$R \cdot A = \int_{0}^{W_{D}} \rho(x) dx = \int_{0}^{W_{D}} \frac{dx}{q\mu_{n}N_{D}(x)}.$$

(2.32)

Fig. 2.18 An ideal drift region and its electric field distribution.

The specific resistance (resistance per unit area) of the ideal uniformly doped drift region is therefore:

$$R_{on,sp} = \left(\frac{W_D}{q\mu_n N_D}\right). \tag{2.33}$$

The depletion width under breakdown conditions is given by:

$$W_D = \frac{2V_{BR}}{E_C} \tag{2.34}$$

where  $V_{BR}$  is the desired breakdown voltage. The doping concentration in the drift region required to obtain this  $V_{BR}$  is given by:

$$N_D = \frac{\varepsilon_s E_C^2}{2q V_{BR}}.$$

(2.35)

Combining these relationships, the specific resistance of the ideal drift region is obtained:

$$R_{on,-ideal} = \frac{4V_{\rm BR}^2}{\varepsilon_s \mu_n E_c^3}.$$

(2.36)

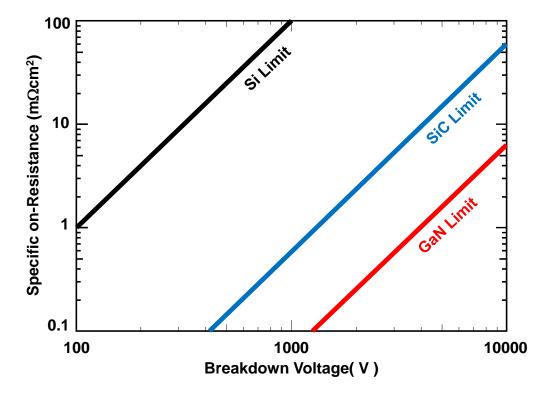

The denominator of this equation ( $\varepsilon_s \mu_n E_c^3$ ) is commonly referred to as Baliga's figure of merit for power devices. It is an indicator of the impact of the semiconductor material properties on the resistance of the drift region. Material parameters are mentioned in chapter 1, Table I. Figure 2.19 shows sum of specific on resistance of the drift region and the ohmic contact resistance versus breakdown voltage for Si, SiC and GaN. The theoretical total specific on-resistance is used as theoretical limits along this work for benchmarking the results in this work with the state-of-the-art devices.

Fig. 2.19. Sum of specific on resistance of the drift region and the ohmic contact resistance versus breakdown voltage for Si, SiC, and GaN.

In switching operation the transistors alternate between on-state were the gate opens the channel and allow the carriers flow through the device and off-state were the gate closes the channel and blocks the current of carriers. At off-state the gate potential,  $V_{GS}$ , is lower than the device's threshold potential,  $V_T$ , and considered as sub-threshold conditions. For efficient switching the off-state operation point conditions should be at high positive drain voltage and negligible drain current therefore a strong gate blocking capability is required. At very high

positive drain voltage condition the blocking capability of the device degrades and gives rise to sub-threshold leakage, (STL), current. The sub-threshold leakage current will increase and become significant then will reduce the efficiency of the switching. A significant leakage current is considered as three orders of magnitude lower than the device's maximal output current therefore a common used value is 0.1 mA/mm. At high voltages, currents that are higher than this value may initiate destructive processes in the device therefore it is considered to be the starting point of the device breakdown. Thus, the breakdown voltage is usually defined as the voltage at which the drain current exceeds the traditional value of 0.1 mA/mm in three terminal measurements. By increasing the potential difference at the drain terminal the charge carriers would drift by electrical forces to the lower potential through intermediate potential levels and states and will reach eventually to the drain terminal. The path of the charge carriers through these intermediate potential states is the device blocking weakness and it determines the mechanisms of the device breakdown.

# References

- [1] O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, et al., "Twodimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures", J. Appl. Phys., vol. 85, pp. 3222–33, 1999.

- [2] A. Zoroddu, F. Bernardini, P. Ruggerone and V. Fiorentini, Phys. Rev. B, Vol. 64, pp. 45208, 2001.

- [3] S-H. Wei, L. G. Ferreira, J. E. Bernard and A. Zunger, Phys. Rev. B, vol. 42, p. 9622, 1990.

- [4] H Angerer et al., Appl. Phys. Lett., vol. 71, p. 1504, 1997.

- [5] T. Peng, J. Piprek, G. Qiu, J. O. Olowolafe, K. M. Unruh, C. P. Swann and E. F. Schubert, Appl. Phys. Lett., vol. 71, p. 2439, 1997.

- [6] L. Bellaiche, S-H Wei and A. Zunger, Phys. Rev. B, vol. 56, p. 13872, 1997.

- [7] F. Bernardini, "Spontaneous and Piezoelectric Polarization: Basic Theory vs. Practical Recipes," in Nitride Semiconductor Devices: Principles and Simulation, J. Piprek, Ed.: Wiley-VCH Verlag GmbH & Co. 2007, ch. 3, pp. 49-68.

- [8] J. F. Nye, Physical Properties of Crystals: Their Representation by Tensors and Matrices: Oxford University Press, USA, 1985.

- [9] F. Bernardini and V. Fiorentini, "Nonlinear Behavior of Spontaneous and Piezoelectric Polarization in III-V Nitride Alloys," Physica Status Solidi (a), vol. 190, no. 1, pp. 65-73, 2002.

- [10] O. Ambacher, B. Foutz, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, et al., "Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures", J. Appl. Phys., vol. 87, pp. 334–44, 2000.

- [11] F. Bernardini and V. Fiorentini, "Nonlinear macroscopic polarization in III-V nitride alloys," Physical Review B, vol. 64, no. 8, p. 085207, 2001.

- [12] P. Feynman and H. Kleinert, "Effective classical partition functions", Phys. Rev. A, vol. 34, pp. 5080-5084, 1986.

- [13] D.K. Ferry, "The onset of quantization in ultra-submicron semiconductor devices", Superlatt. Microstruct., vol. 27, pp. 61-66, 2000.

- [14] I. Knezevic, D.Z. Vasileska, D.K. Ferry, "Impact of strong quantum confinement on the performance of a highly asymmetric device structure: Monte Carlo particle-based simulation of a focused-ion-beam MOSFET", IEEE Trans. Electron Devices, vol. 49, pp. 1019-1026, June 2002.

- [15] L. Shifen, R. Akis, and D.K. Ferry, "Correspondence between quantum and classical motion: comparing Bohmian mechanics with a smoothed effective potential approach", Phys. Lett. A, vol. 274, pp. 75-83, Sep. 2000.

- [16] Y. Li, T. Tang, and X. Wang, "Modeling of Quantum Effects for Ultrathin Oxide MOS Structures with an Effective Potential", IEEE Trans. Nanotechnology, vol. 1, pp. 238-242, Dec. 2002.

- [17] D. Vasileska and S.S. Ahmed, "Narrow-width SOI devices: The role of quantummechanical size quantization effect and unintentional doping on the device operation", IEEE Trans. Electron Devices, vol. 52, pp. 227-236, Feb. 2005.

- [18] F. Sacconi, A.D. Carlo, P. Lugli, and H. Morkoç, "Spontaneous and piezoelectric polarization effects on the output characteristics of AlGaN/GaN heterojunction modulation doped FETs", IEEE Trans. Electron Devices, vol. 48, pp. 450-457, Mar. 2001.

- [19] S. Yamakawa, PhD Thesis, Arizona state University, 2005.

- [20] T. Palacios and U. K. Mishra,"AlGaN/GaN High Electron Mobility Transistors," in Nitride Semiconductor Devices: Principles and Simulation, J. Piprek, Ed.: Wiley-VCH Verlag & Co., 2007, ch. 10, pp. 211-233.

- [21] S. C. Binari, P. B. Klein, and T. E. Kazior, "Trapping effects in GaN and SiC microwave FETs,"Proceedings of the IEEE, vol. 90, no. 6, pp. 1048-1058, 2002.

- [22] P. B. Klein and S. C. Binari, "Photoionization spectroscopy of deep defects responsible for current collapse in nitride-based field effect transistors," J. Phys.: Cond. Matt., p. R1641, 2003.

- [23] I. P. Smorchkova, C. R. Elsass, J. P. Ibbetson, R. Vetury, B. Heying, P. Fini, E. Haus, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization-induced charge and electron mobility in AlGaN/GaN heterostructures grown by plasma-assisted molecular-beam epitaxy," J. Appl. Phys., vol. 86, no. 8, pp. 4520-4526, 1999.

- [24] J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, "Polarization effects, surface states, and the source of electrons in AlGaN/GaN heterostructure field effect transistors," Appl. Phys. Lett., vol. 77, no. 2, pp. 250-252, 2000.

- [25] R. Vetury, N.Q. Zhang, S. Keller, and U.K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," IEEE Trans. Electron Devices, vol. 48, no. 3, pp.560-566, 2001.

- [26] J. M. Tirado, J. L. Sanchez-Rojas, and J. I. Izpura, "Simulation of surface state effects in the transient response of AlGaN/GaN HEMT and GaN MESFET devices," Semiconductor Science and Technology, vol. 21, no. 8, pp. 1150-1159, 2006.

- [27] G. Meneghesso, G. Verzellesi, R. Pierobon, F. Rampazzo, A. Chini, U.K. Mishra, C. Canali, and E. Zanoni, "Surface-related drain current dispersion effects in AlGaN-GaN HEMTs," Electron Devices, IEEE Transactions on, vol. 51, no. 10, pp. 1554-1561, 2004.

- [28] G. Koley, V. Tilak, L. F. Eastman, and M. G. Spencer, "Slow transients observed in

AlGaN/GaN HFETs: effects of  $SiN_x$  passivation and UV illumination," Electron Devices, IEEE Trans. on, vol. 50, no. 4, pp. 886-893, 2003.

- [29] J. M. Tirado, J. L. Sanchez-Rojas, and J. I. Izpura, "Trapping Effects in the Transient Response of AlGaN/GaN HEMT Devices," Electron Devices, IEEE Trans. on, vol. 54, pp. 410-417, 2007.

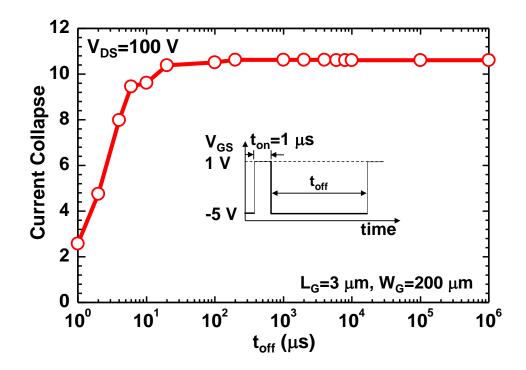

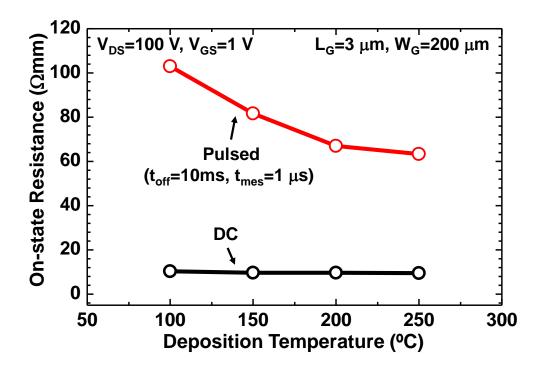

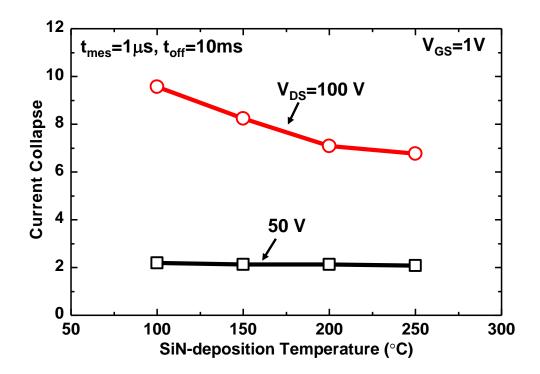

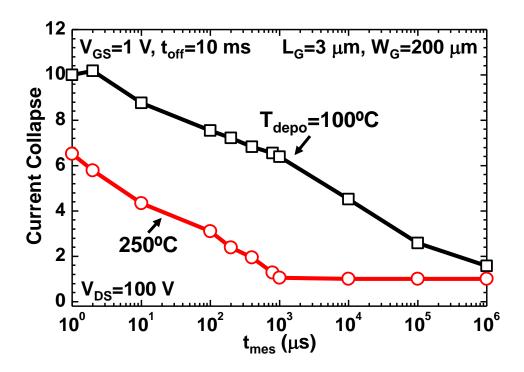

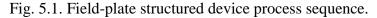

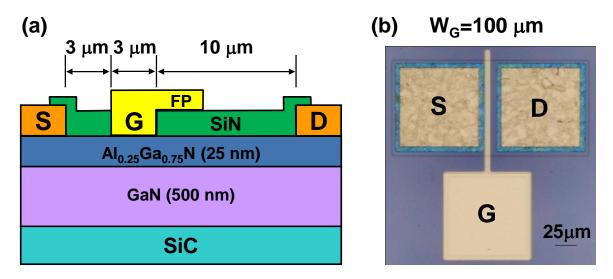

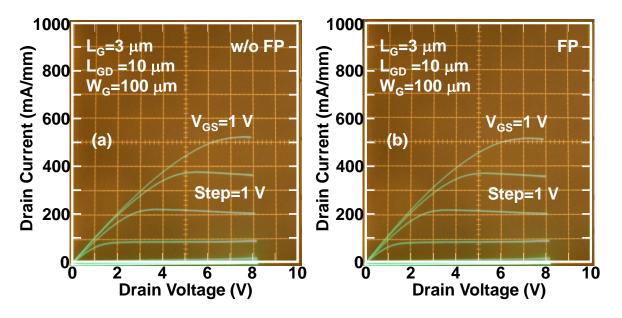

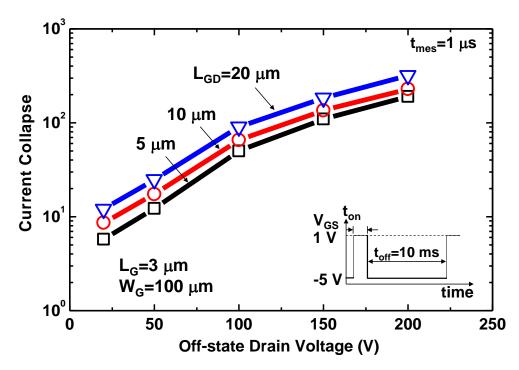

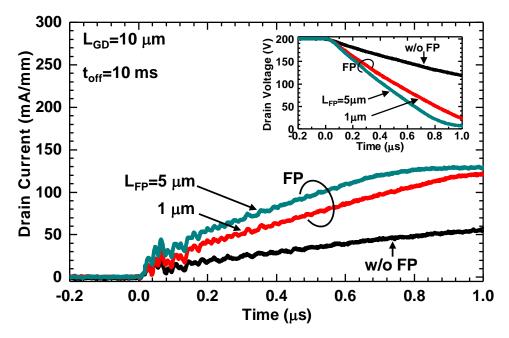

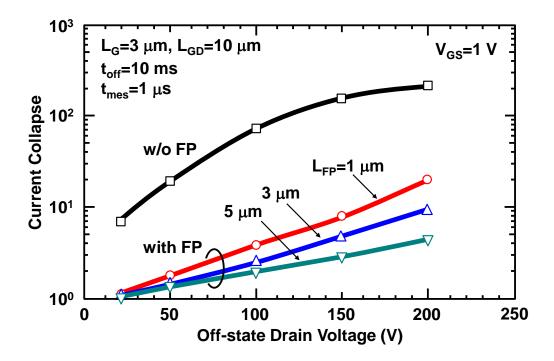

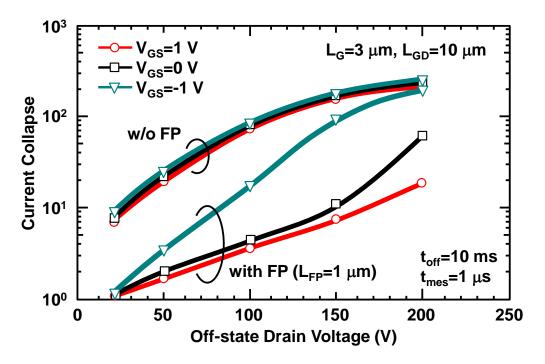

- [30] O. Mitrofanov and M. Manfra, "Mechanisms of gate lag in GaN/AlGaN/GaN high electron mobility transistors," Superlattices and Microstructures, vol. 34, pp. 33-53, 2003.