# ハードウェア記述言語による FPGA 設計の基礎技術の修得

# 第三技術室システム設計班 松山 幸雄

#### 1. はじめに

ハードウェア記述言語 HDL(Hardware Description Language)の出現によりプログラムによってハードウェア回路 (論理回路)を設計できるようになった。また PLD (Programmable Logic Device)の出現により、プログラムにより容易にデジタル IC 回路を専用のオリジナル I Cに創ることができるようになり、民生品や特殊品などの組み込み機器で使用されている。本研修では、FPGA上でVHDL言語による回路作成方法を修得し、応用として 8 ビットCPUソフトマクロPicoBlaze (KCPSM3)を使用して風速計を作成した。

# 2. FPGAについて

大規模な回路が 1 つの PLD 内に作成できるものに CPLD と FPGA があり、その位置づ けは図 1 のようになっている. FPGA(Field Programmable Gate Array)は SRAM ベースの ・PLD (Programmable Logic Device)

・PLD ・・・ AND-OR アレイ構造

・Simple PLD ・・・ ヒューズ (PAL,GAL・・)

・Complex PLD (CPLD) ・・・ EEPROM セル ・・・ altela 社

・FPGA ・・ SRAM ベースの LUT による基本論理ブロックのアレイ構造

SRAM セル,フラッシュメモリ,アンチヒューズ ・・・ xillinx 社

電源切断時プログラム消去 → コンフィグ ROM に書込み

「図 1 ] CPLD と FPGA の位置づけ

LUT(Look Up Table)による基本論理ブロックのアレイ構造セルになっており、例えば LUT に AND ゲートの真理値を書込むことによりセルを AND ゲート化する. 高機能, 高集積、大規模化するにつれユーザの設計開発が長期化すため、その短縮手段として標準回路機能をコアとしてベンダより提供され、それにはプログラムによるソフトマクロ(USB、小規模 CPU(PicoBlaze (8bit)、MicroBlaze (32bit)など)と FPGA 内臓のハードマクロ(DCM(Digital Clock Module)、乗算器、DSP、大規模 CPU(PowerPC (32bit)など)がある.

# 3. VHDL言語について

HDLでよく使われている言語には、記述能力は高くないが記述が簡単な Verilog HDL と記述分

野が広く高い記述能力を持つVHDL(Very High Speed IC DHL)があり、またVHDLにはゲート記述を表すゲートレベル、回路生成を表すレジスタトランスファレベル(RTL)、状態遷移を表すビヘイビアレベル、システム全体を表すアーキテクチャレベルの4つの記述レベルがある。研修ではVHDLでロジック回路設計のためにRTL記述で行った。

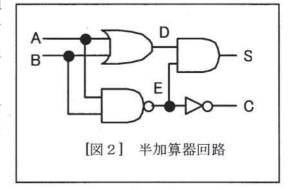

3-1. VHDL プログラム記述

VHDL 言語でのプログラム記述方法を 半加算器回路(図 2)を例として図 3 に示す. 記述は基本的なデザインデータの集まりで ユーザや IEEE 標準のパッケージや算術演 算パッケージ等を呼出すためのライブラリ 宣言, データの方向, データ型やバス幅等 外部との接続を表すエンティティ宣言, 内 部処理, 内部接続や階層間接続など内部動 作を表すアーキテクチャ宣言より構成され る. エンティティ宣言の port 文で, 入力信 号 A,B と出力信号(和信号 S,桁上げ信号 C) の方向, 型を指定する. アーキテクチャ宣 言では, 内部信号 D,E のデータ型, 幅等を

```

-- ライブラリ宣言

library IEEE;

use IÉEE.std_logic_1164.all;

外部とのインターフェース部

--エンティティ宣言

entity HalfAdder is

port (

A,B: in std logic;

S,C: out std logic);

end HalfAdder;

--アーキテクチャ宣言 ・・・ 内部の動作

architecture HalfAdder body of HalfAdder is

signal D.E : std logic:

begin

D \leftarrow A \text{ or } B;

E <= A nand B;

S \le D and E:

C <= not E:

end HalfAdder_body;

[図3] VHDL プログラム

```

指定し、begin 文では演算を行いその結果を出力 D,E,S,C に代入する signal 文は同時に処理される. またこの半加算器回路をコンポーネント化し全加算器回路の階層下として使用できる.

#### 4. 開発ツール

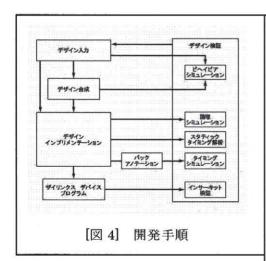

FPGAの設計の手順は、図4に示した様に回路入力、論理合成やデザイン変換、マップ、配置配線を行うインプリメンテーション、各種シミュレーションで検証しながら完成させる.これらを

行う開発ツールは、Xilinx 社の統合 開発環境 ISE(Integrated Software Environment)を使用した.これには DHL(回路)入力、論理合成、シミュレーション、デバイスへの回路データ 書込等の機能がある. 図 5 は ISE 画 面でデザインプログラム構成を示す

[図5] ISEウィンドウ

ソースウィンドウ,開発手順を表すプロセスウィンドウ,各種レポートやソースプログラム表示を するデザインウィンドウ,各種ログ表示するコンソールウィンドウから構成されている.

## 5. KCPSM3

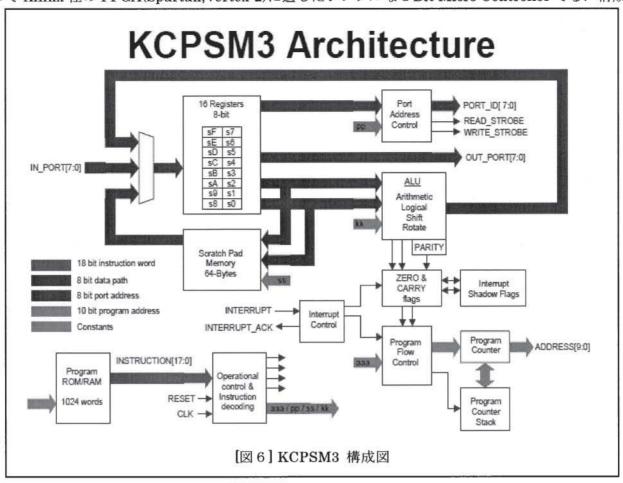

KCPSM3((K)constant Coded Programmable State Machine)は、ソフトマクロ PicoBlaze の一つで Xilinx 社の FPGA(Spartan, Vertex・2)に適したシンプルな 8 Bit Micro Controller でる. 構成

```

Component kcpsm3

Port ( address: out std_logic_vector(9 downto 0); instruction: in std_logic_vector(17 downto 0); port_id: out std_logic_vector(7 downto 0); write_strobe: out std_logic; out_port: out std_logic_vector(7 downto 0); read_strobe: out std_logic; in_port: in std_logic; in_port: in std_logic; interrupt: in std_logic; interrupt_ack: out std_logic; reset: in std_logic; clk: in std_logic; end component;

[図7] KCPSM3 のコンポーネント定義(VHDL)

```

```

component control

Port ( address: in std_logic_vector(9 downto 0);

instruction: out std_logic_vector(17 downto 0);

proc_reset:out std_logic

clk: in std_logic);

end component;

[図8] プログラム ROM のコンポーネント定義

```

は図6のようになっており、命令 長:18bit/word,命令数:21命 令, プログラムメモリ: 1024wod, レジスタ数:16(8bit),入・出 カポート数:各256,スクラッチ・ パッド・メモリ: 6 4 byte(変数領 域), 1 重割込み等の仕様で、ソ フトウェア言語はアセンブラを使 用し、DOS でコンパイルする. KCPSM3 マクロは VHDL ソース (kcpsm3.vhd)で供給されており、 ユーザ VHDL ソースには KCPSM3 のコンポーネントを定 義(図7)すれば良い. 図8はプロ グラム ROM のコンポーネント定 義である.

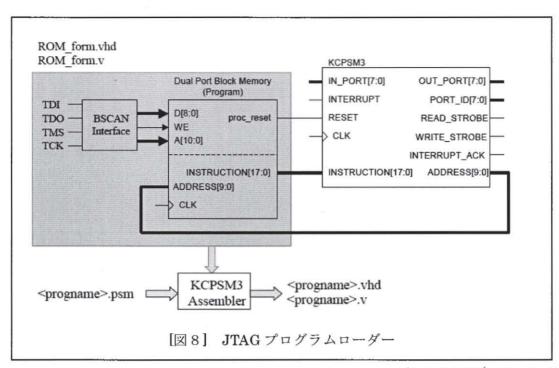

### 5. 1 マイクロプログラムの書込み

プモクム1時2ム直のあ場ブルクの口込理組口リき論のプモ書と,,コ作りのよりのよりのかりでしままとりのは、のからり後のでがあるとがへ込りしたパさ

・kcpsm3 \*\*\*.psm .... compile

・hex2svf \*\*\*.hex \*\*\*.svf .... serial vector format

・svf2xsvf \*\*\*.svf \*\*\*.xsvf ... xilinx svf

・setMode -bscan

・setCable -p auto

・addDevice -position 1 -file \*\*\*.xsvf

・play

・quit

[図 9] コンパイル,ファイル変換 USB 書込み

れる VHDL(or VerilogHDL)ファイルを FPGA の論理合成時に組み込まれる. 2)の場合, プログラムメモリ ROM はデュアルポート RAM を使用しているので、書込みポートから直接書き込みことができる. 図 9 はコンパイル、直接書き込むためのファイル変換、オンボードの USB インタフェースを使

用してJTAGを介してFPGAに書き込むためのバッチファイルで、論理合成する時間が省略される。

応用として風速計を製作した. これは平成14年度専門研修で行った風速計でPICをFPGA

- •FPGA: Spartan3E XC3S500E

- CPLD: CoolRunner XC2C64A

- ·ConfigPROM: XCF04S

- ·64Mbyte DDR SRAM

- •10/100 Ethernet

- ·PS/2 mouse or keyboard

- · VGA display port

- ·9pin RS-232 ports

- ·周波数:50MHz

- ·プログラムダウンロード: USB

- •2行x16文字 LCD

- ·8LEDs

- . 4スライドスイッチ

[図10] スタータキットボードの主な仕様

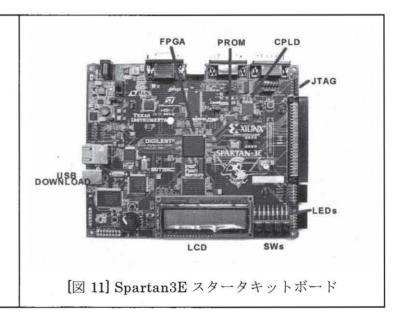

に置き換えて行った. 使用した評価ボードは Xilinx 社の Spartan3E スタータキットボードで FPGA(Spartan 3 E XC3S500E), CPLD(CoolRunner XC2C64A)を核としたメモリ, VGA ポート, RS232 ポート, LCD など図 10 に示した仕様のものが搭載され演習, 実験のみならず, 簡易なパソコンを構築することもできるようになっている. なおビットストリームファイルは USB をとおして, FPGA 又はフラッシュメモリへダウンロードする. ボードの概観を図 11 に示す.

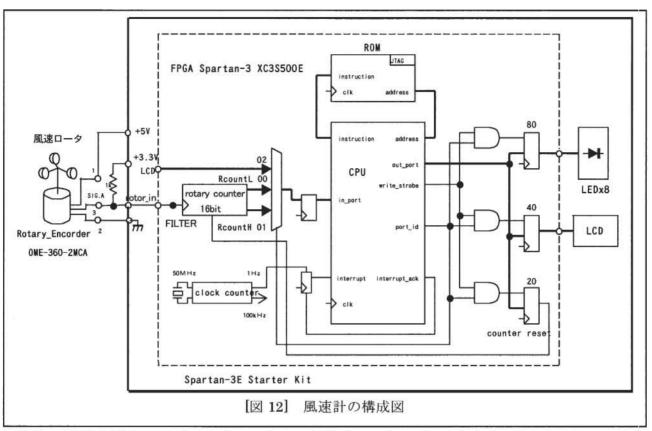

風速計の構成図は図12のようになっており、風速計ロータのパルスをカウンタに入力し、一秒毎に CPU に割り込みをかけ、CPU からカウンタの値を読込み、Anemometer 製品で更正した風速値に換算し、カウンタ値と共に LCD に出力した。また風速計ロータは大和科学教材研究所の理科教材で、それに MEMICON 社のロータリエンコーダ OME-360 を装着し、ロータ出力をパルス出力するように改良した。エンコーダ電源は  $5\,V$  であるが、FPGA 評価ボードの信号入力端子が LVTTL

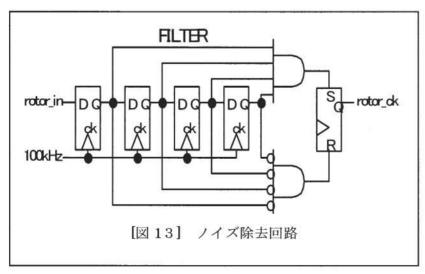

のため、エンコーダのオープンコレクタ出力には3.3Vを抵抗でプルアップした.評価ボードでは風速ロータ出力信号にノイズが含まれるとカウンタに誤差が生じるため、カウンタの前(図12の・FILTER)に図13のようなノイズを除去するフィルタ回路を設けた.フィルタは4ビットのシフトレジスタとANDゲート、SRレジスタより構成され、シフトレジス

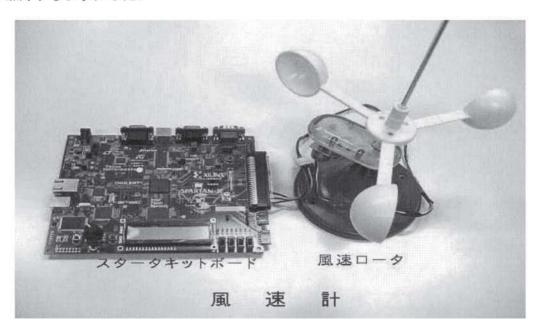

タに 100kHz のクロックを入力することにより  $40 \mu S$  までのノイズを除去した. 風速計の概観は下図のようになっており、1 秒間隔で風速値が認識できるように 8 個の LED で左右 4 個を交互(1 秒毎)に点灯するようにした.

## 7. まとめ

HDLの出現により論理回路がプログラムで記述できライブラリ、マクロ化されるようになってきた. FPGAは高機能,大規模化され使用困難に見えたが高機能な開発ツールや IP マクロの充実で使い易くなった. 今回の研修では VHDL やFPGAを十分使い切ることは不可能であったが、それらを使用するための基礎技術は修得できた. 最後にこの研修の機会を与えてくださった情報メディア工学科森眞一郎先生に深く感謝します.

# [参考文献]

- 1) 長谷川裕恭:改訂「VHDLによるハードウェア設計入門」CQ出版社

- 2) 益田久喜:「FPGA活用チュートリアル」 2006/2007 年版 CQ 出版社

- 3) Spartan-3E スタータキットボードユーザガイド Xilinx Ltd

- 4) PicoBlaze KCPSM3 for 8-bit Micro Controller for Spartan-3, Virtex-2 and Virtex-2 PRO

- 5) PicoBlaze JTAG Loader Quick User Guide Xilinx Ltd