# Topologically Minimal Realization of a Negative Resistor Using Nullors and Positive Resistors

Tadashi MATSUMOTO\*, Kazuhisa HIBINO\*, and Kazuo KANEMAKI\*

( Received June 15, 1977 )

Abstract— Although it is heuristically well-known that a negative resistor can be realized with nullors and positive resistors, the minimal realization of it have not been discussed systematically in detail. In this paper, based upon the general fundamental properties of linear active networks, it is proved systematically that nullors not less than one (two) and positive resistors not less than three (one, respectively) are necessary to realize a negative resistor and there exist only two circuits for the topologically minimal realization disregarding the labelling of nullors and resistors.

#### 1. INTRODUCTION

It has been already known that negative resistors can be realized by means of positive resistors and nullors (where "nullor" is the abbreviation of a pair of a nullator and a norator which from now on are denoted by Nu or 5, and No or 6, respectively) [1]. It seems that none of papers consider the topologically minimal realization of a negative resistor on the basis of the given port characteristics and the general fundamental properties of the nullor-model network. Furthermore, it seems also that the variety in the nullor-model representations of other functional circuits results in the fact that there exist the circuits not less than one for the topologically minimal realization of a negative resistor [2], [3]. Then, it is considered significant to systematize all the topologically minimal realization circuits of a negative resistor from the above viewpoints [4].

In this paper, based upon the general fundamental properties of linear active networks, the least number of elements needed for the topologically minimal realization of a negative resistor and all the topologically minimal realization circuits of it are found systematically.

27

<sup>\*:</sup> Department of Electrical Engineering. But, Kazuo KANEMAKI is now with Electrical Communication Laboratories, Nippon Telegraph and Telephone Public Corporation, Musashino-shi, Japan.

2. PRELIMINARIES

(1) One port considered in this paper consists of nullors and positive resistors and contains no independent sources. Suppose that one port has no redundancy corresponding to the following Lemmata 1 and 2 [5].

[ Lemma 1 ] The following transformations guarantee that the values of all the branch variables in N port remain unchanged before and after the transformations:

(I) If a loop ( cut-set ) consists of only nullators, replace an arbitrary one of them by an open ( a short, respectively ) circuit. (I) Suppose that there exists a loop ( cut-set, respectively ) which consists of nullators more than one and y-branch. If y-branch is a norator, replace it by a short ( an open, respectively ) circuit and further repeat the transformation (I). If y-branch is a regular branch, replace it by an open ( a short, respectively ) circuit.

[Lemma 2] The following transformations guarantee that the values of all the branch variables in N port remain unchanged before and after the transformations except for the current (voltage) values of branches which are included in each loop (cut-set, respectively) : ( $\mathbf{m}$ ) If a loop (cut-set) consists of only norators, or of norators and independent voltage (current) sources, replace an arbitraly one of the norators by an open (a short, respectively) circuit. ( $\mathbf{TV}$ ) Suppose that there exists a loop (cut-set, respectively) which consists of norators more than one and y-branch. If y-branch is a nullator, replace it by a short (an open, respectively) circuit and further repeat the transfomation ( $\mathbf{TT}$ ). If y-branch is a regular branch, replace it by an open (a short, respectively) circuit.

(2) In the graph  $G_{0}$  for N port consisting of nullors and positive resistors, let  $G_{\mathcal{V}}$  ( $G_{\lambda}$ ) be the voltage (current) graph which is obtained from the graph  $G_{0}$  by replacing all nullators (norators) and all norators (nullators, respectively) by short circuits and open circuits , respectively, where the port branches are dealt with in the same way as the resistive branches. Let a common tree  $\mathcal{T}_{c}$  be a set of branches which is a tree of both  $G_{\mathcal{V}}$  and  $G_{\lambda}$ . Furthermore, let  $\mathcal{T}_{c}^{\vee}(\mathcal{T}_{c}^{i})$  be a tree of the graph  $G_{0}$  such that some port tree branches of  $\mathcal{T}_{c}$ , conductive tree branches of  $\mathcal{T}_{c}$  and nullators (norators) branches are taken as the tree branches of the graph  $G_{0}$  and the other port co-tree branches of  $\mathcal{T}_{c}$ , resistive co-tree branches of  $\mathcal{T}_{c}$ , and norators (nullators, respectively) branches, as the co-tree branches of the graph  $G_{0}$ .

(3) If the values of resistors in the network are independent algebraically and all the network variables are uniquely determined for the arbitrary input waveforms, the network is called the non-trivial one in a topological sense. In realizing the active circuit, it is called the topologically minimal realization when the circuit is realized on the basis of the above topological conditions and moreover each element of the realized circuit is essential to specify the given port characteristics.

(4) The statement that one port is topologically non-trivial is equivalent to each of the following statements [6]: Statement 1: There exists a common tree  $\mathcal{O}_{\mathcal{C}}$  in the graphs  $G_{\mathcal{V}}$  and  $G_{\mathcal{C}}$ . Statement 2: There exist  $\mathcal{O}_{\mathcal{C}}^{\mathcal{V}}$  and  $\mathcal{O}_{\mathcal{C}}^{\mathcal{L}}$  in the graph  $G_{\mathcal{O}}$ . Statement 3: Matrices  $\mathcal{F}_{56}$  and  $\mathcal{F}_{65}$  are nonsingular\*.

(5) Since negative resistors have finite immittances and it is assumed in the minimal realization of a negative resistor that there is no redundancy in the network structures, the following assumptions are valid for the realization of a negative resistor without loss of generality:

( ) The graphs  $G_{\mathcal{V}}$  and  $G_{\mathcal{i}}$  for the negative resistor are connected graphs.

(jj) Neither  $G_{v}$  nor  $G_{i}$  for the negative resistor consists of only tree branches or only co-tree branches.

(iii) The port branch of one port is always chosen as a tree branch of  $\mathcal{J}_c^{\downarrow}$  and  $\mathcal{J}_c^{\downarrow}$  in the graph  $G_o$ .

(6) Now, provided that the port branch is chosen as a tree branch of  $\mathcal{G}_c^i$  in the graph  $\mathcal{G}_o$ , let us get the general expression of a negative resistor in terms of the explicit network structures [7]. Suppose from now on that the reference directions for all the branch voltages and all the branch currents including the port branch variables are the associated reference directions [8]. Then, applying KVL and KCL to one port on the basis of  $\mathcal{G}_c^i$  of the graph  $\mathcal{G}_o$ , we have

$\begin{aligned} v^{l} = - \underbrace{F} v^{t} & \text{and} & i^{t} = \underbrace{F}^{T} i^{l}, & (1) \end{aligned}$ where  $v^{l} \triangleq [v_{5}^{T}, v_{7}^{T}]^{T}, i^{l} \triangleq [i_{5}^{T}, i_{7}^{T}]^{T}, v^{t} \triangleq [v_{7}, v_{5}^{T}, v_{7}^{T}]^{T}, i^{t} \triangleq [i_{7}, i_{5}^{T}], \\ i_{7}^{T}]^{T}, \text{ and} & v^{l} (i_{7}^{l}) : \text{ the co-tree branch voltage (current, respectively) vector,} \\ v^{t} (i_{7}^{l}) : \text{ the tree branch voltage (current, respectively) vector,} \\ v_{5} (i_{5}) : \text{ the nullator-branch voltage (current, respectively) vector,} \\ v_{5} (i_{5}) : \text{ the norator-branch voltage (current, respectively) vector,} \\ v_{6} (i_{6}) : \text{ the norator-branch voltage (current, respectively) vector,} \\ v_{7} (i_{7}) : \text{ the conductive branch voltage (current, respectively) vector,} \\ v_{8} (i_{8}) : \text{ the resistive branch voltage (current, respectively) vector,} \\ v_{9} (i_{7}) : \text{ the port-branch voltage (current, respectively) vector,} \\ v_{9} (i_{7}) : \text{ the port-branch voltage (current, respectively) scalar,} \end{aligned}$

<sup>\*:</sup> The matrix  $F_{56}$  is the square matrix defined by eq.(2) and the matrix  $F_{56}$  is the square matrix defined for  $\mathcal{Z}^{\nu}$  in the graph  $G_o$  in the same way as the matrix  $F_{56}$  for  $\mathcal{J}_{c}^{\nu}$ . From now on, the symbols " $\mathcal{A}$ " and " $\mathcal{A}$ " denote the matrix and the scalar, respectively.

and furthermore, <u>F</u> denotes the principal submatrix of the fundamental loop matrix and  $\underline{F}^{\tau}$  denotes the transpose of it. The matrix  $\underline{F}$  is defined in detail by the following equation:

$$F = \frac{N_u}{R} \begin{pmatrix} F SP & F S6 & F S6 \\ F RP & F R6 & F R6 \\ F RP & F R6 & F R6 \\ \end{pmatrix},$$

(2)

where the submatrix  $F_{\alpha\beta}$  denotes the  $|\alpha| \times |\beta|$  matrix which shows whether the fundamental loop with respect to thelpha co-tree branch contains theeta tree branch or not and  $\beta$  and  $|\beta|$  denote the number of set  $\alpha$  and that of set  $\beta$ , respectively. Furthermore, the branch characteristics are as follows:

$y_R = Ri_R$ ,  $i_{e} = Gy_e$ ,  $y_5 = 0$ ,  $i_5 = 0$ ,  $y_6 =$ the arbitrary vector, and  $i_{6}$  = the arbitrary vector, where R and G are the  $|R| \times |R|$  positive diagonal matrix and the  $|G| \times |G|$  posi-

tive diagonal matrix, respectively. Provided that the following matrix  $\underline{K}_{\mathcal{R}}$  is nonsingular, which is guaranteed by the property stated in (7) of the preliminaries, the port characteristics of one port is expressed from eqs.( 1 ), ( 2 ), and ( 3 ) by the following equation:

where  $K_{\mathbf{R}} = \mathcal{R} - \mathcal{F}_{\mathbf{R}6} \mathcal{F}_{\mathbf{5}6} \mathcal{F}_{\mathbf{5}7} - \mathcal{F}_{\mathbf{R}7} \mathcal{F}_{\mathbf{7}6}$  and  $\mathcal{R} = \mathcal{R} + \mathcal{F}_{\mathbf{R}6} \mathcal{G}^{\dagger} \mathcal{F}_{\mathbf{R}6}^{\dagger}$ . Consequently, considering that the reference directions of the port (4)branch variables are the associated reference directions, the condition that eq.( 4 ) satisfies the port characteristic of the negative resistor is obtained as follows:

$F_{RP} \stackrel{}{K_{R}} (F_{R6} \stackrel{}{F_{56}} \stackrel{'}{F_{5P}} - F_{RP}) > 0.$ (5) If there is no conductive tree branches in the graph  $G_{o}$ , eqs.(4) and (5) are rewritten as the following eqs.(4') and (5'), respectively:

and

$$i_{P} = E_{RP} R^{-1} (E_{R6} E_{56} E_{5P} - E_{RP}) v_{P}$$

$$F_{RP} R^{-1} (E_{R6} E_{56} E_{5P} - E_{RP}) > 0.$$

(4')

(5')

(7) Note that it is derived from eq.(5) that the graph  $G_0$  of a negative resistor, that is, one port must contain at least one resistive co-tree branch, and note that the necessary and sufficient condition for the existence of one port is equal to the following: (j) there exist  $\mathcal{G}_{\mathcal{C}}^{\mathcal{V}}$  and  $\mathcal{G}_{\mathcal{C}}^{\mathcal{U}}$  in the graph  $\mathcal{G}_{\mathcal{O}}$  with the port branch chosen as the tree branch or the co-tree branch and (ii) ) the fundamental loop matrix of the resistor subnetwork of one port,  $K_R$  is nonsingular [7].

## 3. NECESSARY AND SUFFICIENT CONDITION FOR THE NUMBER OF ELEMENTS NEEDED FOR THE MINIMAL REALIZATION OF A NEGATIVE RESISTOR

In this section, on the basis of the above preliminaries stated in the section 2, the number of nullors and positive resistors needed for the minimal realization of a negative resistor is discussed in detail.

In order to make it clear, first of all, the necessary condition is given in the next theorem.

[Theorem 1] If negative resistors are realized by means of nullors and positive resistors,  $n_n$  is not less than one and  $n_r$  is not less than three, or  $n_n$  is not less than two and  $n_r$  is not less than one, where  $n_n$ and  $n_r$  denote the number of nullors and the number of positive resistors, respectively.

Proof:

Let us prove this by the contraposition. Then, we shall prove that any negative resistor cannot be realized in each of the following four cases: case(1)  $n_n = 0$  and  $n_r \ge 1$ , case(2)  $n_n \ge 1$  and  $n_r = 0$ , case(3)  $n_n =$ 1 and  $n_r = 1$ , and case(4)  $n_n = 1$  and  $n_r = 2$ .

<u>Cases (1) and (2)</u>: It is clear that any negative resistor can not be realized in the cases (1) [8] and (2) [5].

<u>Case (3)</u>: Consider eqs.(2) and (4) which are expressed on the basis of  $\mathcal{G}_{c}^{i}$ , in which the tree branches are the port branch and a norator branch, and the co-tree branches are a nullator branch and a resistive branch. Then, considering in eq.(2) of this case (3) that there is no redundancy corresponding to Lemmata 1 and 2, we have  $F_{5p} \neq 0$ ,  $F_{Rp} \neq 0$ ,  $F_{R6} \neq 0$ , and moreover  $F_{56} \neq 0$  because the nonsingular matrix  $F_{56}$  is the 1×1 matrix. Furthermore, since the principal submatrix of the fundamental loop matrix defined by eq.(2) is the totally unimodular matrix, without loss of generality, it is assumed that  $F_{56} = F_{5p} = F_{RP} = F_{RE} = 1$ .

If the above conditions are substituted into eq.(4), the coefficient of  $v_p$  in the right-hand side of eq.(4) becomes

$F_{RP}^{T} R^{-1} (F_{R6} F_{56}^{-1} F_{5P} - F_{RP}) = 0$ ,

where R denotes the scalar positive resistance of a resistive co-tree branch. However, since the above equation contradicts the requirement of eq.(5), it is concluded that any negative resistor can not be realized in this case (3).

<u>Case (4)</u>: In this case, both  $G_{\nu}$  and  $G_{\epsilon}$  consist of three branches including the port branch. Since the port branch and a resistive branch must be chosen as a tree branch and a co-tree branch, respectively, of the common tree  $\mathcal{T}_{c}$  in  $G_{\nu}$  and  $G_{\epsilon}$ , the other branch may be chosen as a tree branch or a co-tree branch of  $\mathcal{T}_{c}$ . Then, without loss of generality, this case (4) is divided into the following two cases: (i)  $n_{c} = 2$  and (ii)  $n_{c} = 1$ , where  $n_{c}$  denotes the number of the common tree branches of  $\mathcal{T}_{c}$  in  $G_{\nu}$  and  $G_{\epsilon}$ . <u>Case (4-i)</u>  $n_{c} = 2$ : Consider eqs.(2) and (4) which are expressed on the basis of  $\mathcal{T}_{c}^{i}$ , in which the tree branches are the port branch, a norator branch, and a conductive branch, and the co-tree branches are a nullator branch and a resistive branch. Then, considering in eq.(2) of this case (4-i) that there is no redundancy corresponding to Lemmata 1 32

and 2, we obtain  $F_{R6} \neq 0$ ,  $F_{RP} \neq 0$ ,  $F_{Rq} \neq 0$ , and moreover  $F_{56} \neq 0$  because the nonsingular matrix  $F_{56}$  is the 1×1 matrix in this case (4-i). Furthermore, since the principal submatrix of the fundamental loop matrix defined by eq.(2) is the totally unimodular matrix, without loss of generality, we can assume that  $F_{56} = F_{R6} = F_{RP} = F_{Rq} = 1$ . Substituting the above conditions into eq.(5), we have

$$R + G'(1 - F_{SG}) \Big\}^{-} (F_{SP} - 1) > 0,$$

(6)

or

$$R + G'(1 - F_{56}) > o \text{ and } F_{5p} > 1$$

(7)

$$R + G'(1 - F_{SF}) < o \text{ and } F_{SP} < 1$$

, (8)

where R and G denote the scalar positive resistance of a resistive cotree branch and the scalar positive conductance of a conductive tree branch, respectively. However, the condition of  $F_{5p} > 1$  in eq.(7) and that of R + $\tilde{G}'(1-F_{E,Q'}) < 0$  in eq.(8) contradict the fact that each of  $F_{5P}$  and  $F_{5q}$  is one of the elements of the totally unimodular matrix F defined by eq.(2). Therefore, it is concluded that any negative resistor can not be realized in this case (4 - i). Case  $(4 - i)^n c = 1$  : Consider eqs.(2) and (4) which are expressed on the basis of  $\mathcal{J}_{c}^{i}$ , in which the tree branches are the port branch and a norator branch, and the co-tree branches are two resistive branches. Then, considering in eq.(2) of this case (4-ii) that there is no redundancy corresponding to Lemmata 1 and 2, we have the following conditions;  $F_{5p} \neq 0$ ,  $F_{R6} (\in \mathbb{R}^{2\times 1})^* \neq 0$ , each element of  $F_{Rp} (\in \mathbb{R}^{2\times 1})$ is non-zero, and moreover  $F_{56} \neq 0$  because the nonsingular matrix  $F_{56}$  is the 1/1 matrix in this case (4-#). Furthermore, since the principal submatrix of the fundamental loop matrix defined by eq.(2) is the totally unimodular matrix, without loss of generality, it is assumed that  $F_{SP}$  =  $F_{56} = 1$  and  $\mathcal{F}_{RP}^{T} = [1, 1]$ . Let  $\mathcal{F}_{R6}^{T} = [a, b] \neq \mathcal{Q}$  and  $\mathcal{R} = \text{diag}(\mathcal{R}_{I}, \mathcal{R}_{2})$ , where  $R_1$  and  $R_2$  denote the scalar positive resistances of two resistive co-tree branches, and at least one of a and b is non-zero scalar. Then, substituting the above conditions into eq.(5), we have (0)

$$(a - 1)R_1^{-1} + (b - 1)R_2^{-1} > 0.$$

<sup>(9)</sup>

However, eq.(9) contradicts the fact that the elements of the matrix  $\underline{F}$ , that is,  $\alpha$  and b must be ones of the totally unimodular matrix  $\underline{F}$  defined by eq.(2). Therefore, it is also concluded that any negative resistor can not be realized in this case (4-ii).

The proof of the case (4) is completed by those of the cases (4-i)and (4-i). Then, the proof of this theorem is completed by those of the cases (1), (2), (3), and (4). Q.E.D.

[ Theorem 2 ] The number of elements needed for the minimal realiza-

<sup>\*:</sup>  $\mathcal{R}^{n \times m}$  denotes the  $n \times m$  matrices of real numbers.

tion of a negative resistor is  $n_n = 1$  and  $n_r = 3$ , or  $n_n = 2$  and  $n_r = 1$ . Proof:

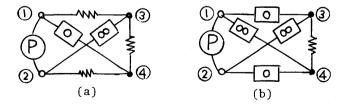

The necessity is proved by the theorem 1, while the sufficiency is clearly proved from the fact that each of the circuits shown in Fig.1 (a) and (b) is the negative resistor. Q.E.D.

4. ALL THE MINIMAL REALIZATION CIRCUITS OF A NEGATIVE RESISTOR

The least number of elements needed for the minimal realization of a negative resistor was given by the theorem 2. In this section, all the minimal realization circuits of a negative resistor with the above least number of elements are found systematically.

[ Theorem 3 ] The minimal realization circuits of a negative resistor by means of nullors and positive resistors are only the two circuits shown in Fig.1 (a) and (b).

Proof:

<u>Sufficiency</u>: It is obvious that each of the circuits of Fig.1 (a) and (b) is the minimal realization circuit of a negative resistor.

<u>Necessity</u>: <u>Case (1)</u>: Let us prove that the minimal realization circuit of a negative resistor by means of a nullor and three positive resistors is only the circuit shown in Fig.1(a). In this case, both  $G_{\nu}$ and  $G_{\nu}$  consist of four branches, and the port branch and at least one resistive branch should be chosen as a tree branch and a co-tree branch, respectively, of the common tree  $\mathcal{T}_{c}$  in  $G_{\nu}$  and  $G_{\epsilon}$ . Then, each of the other two resistive branches may be chosen as a conductive tree branch or a resistive co-tree branch of  $\mathcal{T}_{c}$ , so this case (1) is divided into the following three cases: (j) $n_{c}=3$ , (ii) $n_{c}=2$ , and (iii) $n_{c}=1$ , where  $n_{c}$  denotes the number of the common tree branches. <u>Case(1-i) $n_{c}=3$ </u>: In this case, from the above statements, it is evident that we can select the tree  $\mathcal{T}_{c}^{i}$  which consists of the port tree branch, a norator tree branch, two conductive tree branches, a nullator co-tree branch, and a resistive co-tree branch. Then, considering eq.(2) on the basis of the above  $\mathcal{T}_{c}^{i}$  and the fact that

Fig.1. All minimal realization circuits of a negative resistor. In each figure in this paper,  $\circ$  and  $\infty$  show a nullator and a norator, respectively.

in eq.(2) of this case (1-i) there is no redundancy corresponding to Lemmata 1 and 2, we obtain the following conditions;  $F_{56} \neq 0$ ,  $F_{RP} \neq 0$ , all elements of  $\mathcal{F}_{RF} (\epsilon \mathbb{R}^{N_2})$  are non-zero, and moreover  $F_{56} (\epsilon \mathbb{R}^{N_1}) \neq 0$  because the nonsingular matrix  $\mathcal{F}_{56}$  is the 1×1 matrix in the case (1-i). Furthermore, since the principal submatrix of the fundamental loop matrix defined by eq.(2) is the totally unimodular matrix, without loss of generality it is assumed that  $F_{56} = F_{RG} = F_{RP} = 1$ , and  $\mathcal{F}_{RF} = [1,1]$ . Let  $\mathcal{F}_{5F} = [\alpha,b]$  and  $\mathcal{G} =$ diag( $G_1$ ,  $G_2$ ), where  $G_1$  and  $G_2$  denote the scalar positive conductances of two conductive tree branches. Then, substituting the above conditions into eq.(5), we have

$$R + (1 - a)G_{i}^{i} + (1 - b)G_{2}^{i} \right\} (F_{SP} - 1) > 0, \qquad (10)$$

or

namely

+

$$(1 - a)G_{i}' + (1 - b)G_{2}' > o$$

and  $F_{SP} > 1$  (11)

$R + (1 - \alpha)G_1' + (1 - b)G_2' < 0 \text{ and } F_{5P} < 1,$ (12) where R denotes the scalar positive resistance of a resistive co-tree branch. However, the condition of  $F_{5P} > 1$  in eq.(11) and that of  $R + (1-a)\vec{G_l} + (1-a)\vec{G_l$  $(1-b)G_2^{-1} < 0$  in eq.(12) contradict the fact that  $F_{sp}$ , a, and b are the elements of the totally unimodular matrix  $\frac{F}{\sim}$  . Therefore, it is concluded in the case (1-i) of  $n_c=3$  that any negative resistor can not be realized. Case(1-ii)  $n_c = 2$ : In this case, from the same reason as the case (1-i), it is evident that we can select the tree  $\mathcal{J}_{c}^{i}$  which consists the port tree branch, a conductive tree branch, a nullator co-tree branch, and two resistive co-tree branches. Since the graph Go is assumed to be connected and the number of tree branches of  $\mathcal{J}_{i}^{i}$  is three, the number of all nodes in the nullor-model network is four. In consideration of the bilaterality of the negative resistor, no mutual couplings between the branches in the nullor-model network and no distinction between nullators and norators, it can be assumed that the network structure of the negative resistor seen at the port branch is symmetric. Consider eq.(2) on the basis of the above tree  $\mathcal{J}_{c}^{i}$  and let  $\mathcal{F}_{RP}^{T} = [a_{1}, a_{2}], \mathcal{F}_{RQ}^{T} = [b_{1}, b_{2}], \text{ and } \mathcal{F}_{RG}^{T} = [c_{1}, c_{2}]$ for the simplicity of the explanation . Considering in eq.(2) of this case (1-ii) that there is no redundancy corresponding to Lemmata 1 and 2, we can assume that at least one element of each pair of  $(F_{57}, F_{57})$ ,  $(a_1, a_2)$  $b_1$ ),  $(a_2, b_2)$ ,  $(a_1, a_2)$ ,  $(b_1, b_2)$ , and  $(c_1, c_2)$  is non-zero.

From the above stated, first of all, the port branch, a nullator branch, and a norator branch can be fixed as shown in Fig.1 (a) without loss of generality. Since the nonsingular matrix  $\underline{F_{56}}$  is the 1×1 matrix in this case (1-ii) and is the submatrix of the totally unimodular matrix  $\underline{F}$ , without loss of generality we obtain  $F_{56} = 1$ . Then, a conductive tree branch must be inserted between the node (3) and the node (4) in Fig.1 (a) because the fundamental loop associated with the nullator co-tree branch in  $\Im_{c}^{i}$  must contain a norator tree branch. Hence, we have  $F_{5p} = F_{5q} = 1$ . Secondly, it is assumed that the fundamental cut-set associated with the port tree branch in  $\Im_{c}^{i}$  must contain at least one resistive co-tree branch because of no redundancy corresponding to Lemmata 1 and 2 in the graph  $G_{0}$ . In consideration of the above stated and the elimination of the apparent redundancy ( namely, the each parallel connection of a nullator branch and a resistive branch, a norator branch and a resistive branch, and a conductive branch and a resistive branch ) in the graph  $G_{0}$ , it is assumed that two resistive co-tree branches must be inserted only between the node (1) and the node (3), and the node (2) and the node (4), respectively. Consequently, in this case (1-11) of  $n_{c} = 2$ , the circuit in Fig. 1 (a) is obtained uniquely.

<u>Case (1-jii)  $n_c = 1$ </u>: In this case, from the same reason as the case (1ii), it is evident that we can select the tree  $\mathcal{J}_c^{\downarrow}$  which consists of the port tree branch, a norator tree branch, a nullator co-tree branch, and three resistive co-tree branches. Then, considering eq.(2) on the basis of the above tree  $\mathcal{J}_c^{\downarrow}$  and the fact that there is no redundancy correspoding to Lemmata 1 and 2, we have the followings;  $F_{5p} \neq 0$ , all elements of  $\mathcal{F}_{RP}$  (  $\in \mathbb{Q}^{3\times 1}$ ) are non-zero,  $\mathcal{F}_{R6} (\in \mathbb{Q}^{3\times 1}) \neq \mathcal{Q}$ , and moreover  $\mathcal{F}_{56} \neq 0$  because the nonsingular matrix  $\mathcal{F}_{56}$  is the 1×1 matrix in this case (1-jii). Furthermore, since the principal submatrix of the fundamental loop matrix defined by eq.(2) is the totally unimodular one, without loss of generality, it is assumed that  $\mathcal{F}_{56} = \mathcal{F}_{5p} = 1$  and  $\mathcal{F}_{RP}^{P} = [1,1,1]$ . Let  $\mathcal{F}_{RC}^{T} = [a,b,c]$  and  $\mathcal{R} =$ diag( $\mathcal{R}_1, \mathcal{R}_2, \mathcal{R}_3$ ), where  $\mathcal{R}_1, \mathcal{R}_2$ , and  $\mathcal{R}_3$  denote the scalar positive resistances of three resistive co-tree branches. Then, substituting the above conditions into eq.(5), we have

$(a - 1)R_1' + (b - 1)R_2' + (c - 1)R_3' > 0.$  (13) However, eq.(13) contradicts the fact that a, b, and c are the elements of the totally unimodular matrix  $\underline{F}$ . Therefore, it is concluded in this case (1-iii) of  $n_c = 1$  that any negative resistor cannot be realized.

<u>Case (2)</u>: Let us prove that the minimal realization circuit of a negative resistor by means of two nullors and a positive resistor is only the circuit shown in Fig. 1 (b). In this case, it is evident from the property (4) in the preliminaries that both  $G_{v}$  and  $G_{z}$  consist of the parallel connection of the port tree branch and a resistive co-tree branch. Therefore, consider eq.(2) on the basis of  $V_{c}$  which consists of the port tree branch, two norator tree branches, two nullator co-tree branches, and a resistive co-tree branch. Then, considering in the eq.(2) of this case (2) that there is no redundancy corresponding to Lemmata 1 and 2, we have the followings;  $F_{RP} \neq 0$  and all elements of  $F_{SP}$  ( $\in \mathbb{R}^{2\times 1}$ ) and  $F_{RE}$  (  $\in \mathbb{R}^{2\times 1}$ ) are non-zero. Furthermore, since the principal submatrix of the fundamental loop matrix is totally unimodular, without loss of generality it is assumed that  $\overline{F_{SP}} = [1,1]$ ,  $F_{RP} = 1$ , and  $\overline{F_{R6}} = [1,1]$ . If there exists any one row vector with all non-zero elements in the row vectors of  $F_{S6}$  ( $\in \mathbb{R}^{3\times3}$ ), then the tree path formed by the nullator co-tree branch corresponding to the row vector is equal to that formed by the resistive co-tree branch. Hence, it is clear that there exists redundancy of the parallel connection of the nullator branch and the resistive branch in the graph  $G_0$ . Therefore, all the elements of each row vector of  $\overline{F_{56}}$  should not be non-zero. Similarly all the elements of each column vector of  $\overline{F_{56}}$ should not be non-zero. Then, without loss of generality, it is assumed that the 2x2 nonsingular matrix  $\overline{F_{56}}$  is the diagonal one.

From the above mentioned, all the elements of the principal submatrix  $\underline{F}$  of the fundamental loop matrix are determined and the matrix  $\underline{F}$ becomes

$$E_{\sim} = \begin{pmatrix} F_{SP} & F_{S6} \\ F_{RP} & F_{K6} \end{pmatrix} = \begin{pmatrix} 1 & 0 & 0 \\ 1 & 0 & * \\ 1 & 1 & 1 \end{pmatrix},$$

(14)

where the symbol " \* " denotes the non-zero element. By synthesizing the nullor-model network in accordance with eq.(14), the circuit of Fig.1(b) is uniquely obtained.

The proof of necessity was completed by the proofs of the cases (1) and (2).

Q.E.D.

#### 5. IMPLEMENTATIONS

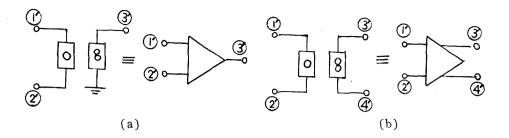

Although it has been already known that the negative resistor can be effectively realized by using operational amplifiers, even all the implementations of the minimal realization circuits in Fig.1 with operational amplifiers are not well-known. In this section, the implementations of the minimal realization circuits using operational amplifiers are considered. First of all, the implementation of the nullor using operational amplifiers is shown in Fig.2. The circuit of Fig.2(a) is a conventional operational amplifier with floating input port and unfloating output port and has widely been put to practical use, while the circuit of Fig. 2(b) is an operational amplifier with floating input and output ports, and had not been almost madepracticable to be on the general market. However, the monolithic integrated nullor corresponding to the circuit tech-

3.6

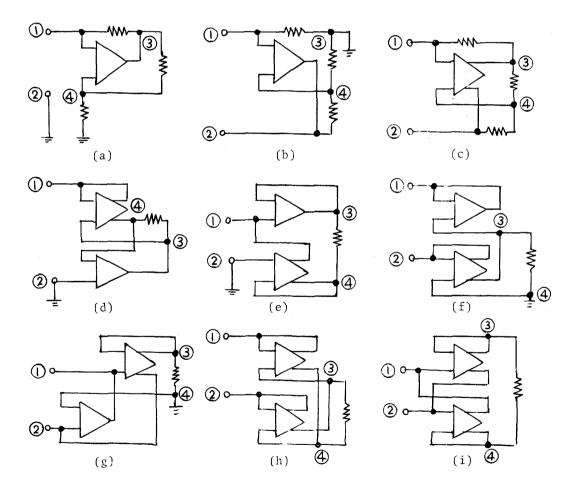

<sup>\*:</sup> The availability of such universal active elements makes it possible to minimize the number of active elements and passive precision elements in implementations of analog system functions, for example, as shown in Fig.3.

Fig.2. Implementations of a nullor using operational amplifiers.(a) A nullor with floating input port and unfloating output port. (b) A nullor with floating input and output ports.

Fig.3. Implementations of the minimal realization circuits of a negative resistor using operational amplifiers. All the nodes (1, 2), (3), and (4) shown in Fig.3 correspond to those shown in Fig.1. Although the polarity of the input terminals in each operational amplifier is omitted, it should be selected by considering the stability of each circuit.

nique [9]. Therefore, it is considered significant to find all the implementations of the minimal realization circuits of a negative resistor in consideration of the existence of the circuit shown in Fig.2(b) in addition to that of the circuit shown in Fig.2(a).

The results of these implementations are easily obtained as shown in Fig.3, in which the circuits of (a), (b), and (c) are derived from that of Fig.1(a) and the circuits of (d), (e), (f), (g), (h), and (i), from that of Fig.1(b). Furthermore, it is to be noted in Fig.3 that the circuits of (b), (c), (f), (g), (h), and (i) are the floating negative resistors in contrast with those of (a), (d), and (e), and that only the circuits of (a) and (b) have been put to practical use. Therefore, we can expect much from the applications of the circuits of Fig.3(c)~(i) to the active network synthesis.

### 6. CONCLUSIONS

This paper has strictly discussed the necessity of the Theorem 3 and guaranteed that all the topologically minimal realization circuits of a negative resistor are only the two circuits shown in Fig.1. Furthermore, all the usefull implementations of the minimal realization circuits by means of operational amplifiers are shown in Fig.3.

Finally, the following fact must be also noted. If the concept of " the chain bond between ports for the active N-port including one port" which gives the necessary and sufficient condition of the existence of transmission path between ports [10] is introduced, the Theorems 1,2, and 3 will be proved more easily and systematically. This will be appeared in detail elsewhere.

#### REFERENCES

- (1) Y.Oono, "Formal realizability of linear networks, "Proc. Symp. on Active Networks and Feedback Systems, p.475, April 1960 and see for example S.K.Mitra, Analysis and Synthesis of Linear Active Networks, New York: Wiley, 1968.

- (2) E.Deprettere, " On the minimal realization of the gyrator by means of nullors and resisters, " PartI, Int.J.Cir.Theor. Appl., Vol.3, p.383 (1975) and PartI, ibid., Vol.4, p.285 (1976).

- (3) T. Matsumoto, "Minimal realizations of controlled sources using nullors and positive resistors," Trans. IECE. Japan, J59-A, No. 5, p.428, 1976.

- (4) T. Matsumoto, K. Kanemaki, and K. Hibino, "Minimal realizations of negative resistors by means of nullors and positive resistors," ibid.,

38

J59-A, No.8, p.676, 1976.

- (5) T. Matsumoto, "Two-port realized by using only nullators and norators," ibid., J60-A, No. 5, p.475, 1977.

- (6) T. Matsumoto and Y. Kato, "Order of complexity and a normal common tree of linear lumped active networks using nullator-norator model," Paper of Tech. Group on CST74-26, IECE. Japan, June 1974.

- (7) T. Matsumoto, " Existence and explicit expressions for matrices of two-port," Trans. IECE. Japan, J59-A, No. 5, p.425, 1976.

- (8) C.A.Desoer and E.S.Kuh, Basic Circuit Theory, McGraw-Hill, 1969.

- (9) J.H.Huijsing and J.de Korte, "Monolithic nullor A universal active network element," IEEE J. Solid-State Circuits, Vol.SC-12, No. 1, p.59, Feb. 1977.

- (10) T. Matsumoto and K. Kanemaki, "New topological necessary and sufficient conditions for N-port parameters to be non-zero," to be appeared in Trans. IECE. Japan.