## 九州工業大学学術機関リポジトリ

| Title      | Development and Qualification of an FPGA-Based Multi-<br>Processor System-on-Chip On-Board Computer for LEO<br>Satellites |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| Author(s)  | Mohamed, Mahmoud Mohamed Ibrahim                                                                                          |

| Issue Date | 2014                                                                                                                      |

| URL        | http://hdl.handle.net/10228/5315                                                                                          |

| Rights     |                                                                                                                           |

Kyushu Institute of Technology Dept. of Applied Science for Integrated System Engineering Graduate School of Engineering

# Development and Qualification of an FPGA-Based Multi-Processor System-on-Chip On-Board Computer for LEO Satellites

By Mohamed Mahmoud Mohamed Ibrahim

A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF ENGINEERING AT KYUSHU INSTITUTE OF TECHNOLOGY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF ENGINEERING IN APPLIED SCIENCE FOR INTEGRATED SYSTEM ENGINEERRING

Graduate School of Engineering, Kyushu Institute of Technology Kitakyushu, Japan 2014 Kyushu Institute of Technology Dept. of Applied Science for Integrated System Engineering Graduate School of Engineering

# Development and Qualification of an FPGA-Based Multi-Processor System-on-Chip On-Board Computer for LEO Satellites

By Mohamed Mahmoud Mohamed Ibrahim

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF ENGINEERING AT KYUSHU INSTITUTE OF TECHNOLOGY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF ENGINEERING IN APPLIED SCIENCE FOR INTEGRATED SYSTEM ENGINEERRING

Thesis Supervisor Assoc. Prof. Kenichi Asami Dept. of Integrated Systems Engineering Kyushu Institute of Technology Kyushu Institute of Technology Dept. of Applied Science for Integrated System Engineering Graduate School of Engineering

Development and Qualification of an FPGA-Based Multi-Processor System-on-Chip On-Board Computer for LEO Satellites

By

Mohamed Mahmoud Mohamed Ibrahim

## A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF ENGINEERING AT KYUSHU INSTITUTE OF TECHNOLOGY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF ENGINEERING IN APPLIED SCIENCE FOR INTEGRATED SYSTEM ENGINEERRING

Approved by the examiners committee:

Prof. Mengu Cho

cho hy

Prof. Keiichi Okuyama

Keilchn' Olaurama

Assoc. Prof. Kenichi Asami

Kenichi Asami

Assoc. Prof. Kazuhiro Toyoda Kazuhiro Toyoda

Assoc. Prof. Motoki Miura

motoki miura

### Acknowledgment

All of the thanks go to the almighty ALLAH for giving me the strength and ability to finish this work. It is all out of his willingness and endowments upon us. May Allah reward us for the time and effort spent in producing this work. I ask for forgiveness in case you find any pitfalls in it and for prayer in case you find it beneficial.

When I joined the Egyptian Space Program (ESP), more than 10 years ago, I was deeply interested in learning more about this field of high fidelity and ultimately critical engineering, namely space engineering. I tried to do all what I could in order to learn and become a real expert in that field. During my struggle to learn, I travelled to many places, knew a lot of things and dealt with many nationalities from the west to the east of this planet. In that pervasive period of intensive education and exposure to different cultures, I learnt that all of us are alike even though cultural differences do exist among us. We are alike in our feelings, in our willingness, in our ambitions, and in our love for peace and justice.

In that journey of education, I did learn the true meaning of working for the sake of the bigger image instead of the narrow field of interests. Work for humanity, in general and without discrimination, to make the life of people better, more affordable and happier. I truly knew the value and meaning of the statement "science has no borders". It is true because science is the resemblance of justice, truth, and equity and those meanings has no borders to cross, they are just intrinsic in good spirits and souls.

The work in this thesis would not have been possible without the support of many staff, organizations and individuals. My words are not sufficiently eloquent to express my gratitude feelings towards them. First, I would like to express my deep gratitude to the ESP and the National Authority for Remote Sensing and Space Sciences (NARSS) at Egypt for giving me the chance to work in the field of space engineering. Special thanks to Prof. Ayman El Dessouki, former chairman of NARSS, for approving and recommending my application to this fellowship through which I was granted my doctoral degree. I do appreciate the efforts and work of all of

the employees at ESP and NARSS and wish them a brilliant future. Thanks to my master degree supervisor, the late Prof. Yousri El Nahas, and to the late Prof. Matar Ali Matar, may their souls rest in peace.

I would like to thank my supervisor, Assoc. Prof. Kenichi Asami, for supervising me during my study at Kyuhsu Institute of Technology (KIT). Words cannot express my gratitude for his kindness, understanding, support and deep guidance. My appreciation and thanks to Prof. Mengu Cho, the scientist, the innovator, the teacher, the motivator and above all the mentor of our success. Deep appreciation for Dr. Werner Balogh at the United Nations Office for Outer Space Affairs (UNOOSA) and all the staff there for the extraordinary efforts in inaugurating the Doctorate in Nano-Satellite Technology (DNST) program in collaboration with KIT.

My appreciation and thanks to the professors at KIT for teaching us and giving us from their effort and time. Thanks to Prof. Keiichi Okuyama, Assoc. Prof. Kazuhiro Toyoda, Assoc. Prof. Motoki Miura and Assoc. Prof. Sozo Inoue. I do appreciate the efforts of the administrative staff at KIT for providing support and help during our study. I would like to thank Kanae Iyama, Kumiko Shirakawa, Michiko Kubota and Seiji Kawano.

Special thanks to my brothers and colleagues at KIT for making my stay in Japan more knowledgeable and much friendly. Thanks to Dr. Yasser Qudaih for all the help and support he gave to me. My great appreciation to the DNST, PNST and SEIC fellows, Amgalanbat Batsuren, Ammarin Pimnoo, Bianca Szasz, Bui Nam Duong, Chen Shiyi Danny, Hala Almubarak, Kateryna Aheieva, Mohamed Alakli, Mohamed Nori Ait, Mohamed Yehia Edris, Pauline Faure, Tejumola Taiwo and Trinh Thang Long. Thanks to my Japanese colleagues for their fruitful cooperation during my study. My thanks to Shinya Kuramoto at NEC, Yuki Seri at Hitachi for building the geometric thermal model, Yuta Okumura at Hitachi for helping with the setup of radiation testing, and Dr. Masui Hirokazu for his guidance in the thermal vacuum and radiation tests.

My mother and father supported me with every possible way. They gave me more than I deserve, all over my life. I respect them, love them, and owe them my success and all what I achieve in my life. My lord, bestow on them your mercy as they did bring me up when I was young. Thanks to my brother and sisters for supporting me and praying for me to finish this work. My deep thanks, appreciation, love and respect for my wife. She did a lot to support me to finish this work. She struggled as much as I did during my study. Sometimes we had difficult times as much stress was over there in my experiments and tests, but she was extremely smart to help us pass all of that smoothly and peacefully. Taking care of three children while I am spending sleepless nights in the lab was a real challenging task. Thank you very much. I dedicate this work to my children Yousof, Jody and Mahmoud, my nephew Yassin and nieces Basmalla and Iten. I wish when they grow up that they would follow the way of science and engineering, May ALLAH bless them all and grant them happiness, success and health.

Thanks to Japan and to Japanese people for the generosity to give me the chance to study here. I do respect and love Japan and Japanese people so much. I wish I can help my country to reach the same level of perfection.

### Abstract

Developing small satellites for scientific and commercial purposes is emerging rapidly in the last decade. The future is still expected to carry more challenging services and designs to fulfill the growing needs for space based services. Nevertheless, there exists a big challenge in developing cost effective and highly efficient small satellites yet with accepted reliability and power consumption that is adequate to the mission capabilities. This challenge mandates the use of the recent developments in digital design techniques and technologies to strike the required balance between the four basic parameters: 1) Cost, 2) Performance, 3) Reliability and 4) Power consumption. This balance becomes even more stringent and harder to reach when the satellite mass reduces significantly. Mass reduction puts strict constraints on the power system in terms of the solar panels and the batteries. That fact creates the need to miniaturize the design of the subsystems as much as possible which can be viewed as the fifth parameter in the design balance dilemma.

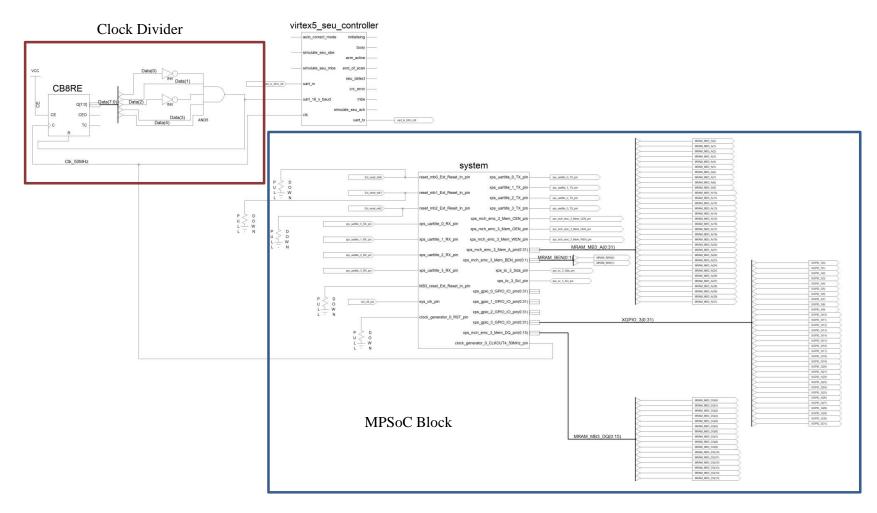

At Kyuhsu Institute of Technology-Japan we are investigating the use of SRAMbased Field Programmable Gate Arrays (FPGA) in building: 1) High performance, 2) Low cost, 3) Moderate power consumption and 4) Highly reliable Muti-Processor System-on-Chip (MPSoC) On-Board Computers (OBC) for future space missions and applications. This research tries to investigate how commercial grade SRAMbased FPGAs would perform in space and how to mitigate them against the space environment. Our methodology to answer that question depended on following formal design procedure for the OBC according to the space environment requirements then qualifying the design through extensive testing. We developed the MPSoC OBC with 4 complete embedded processor systems. The Inter Processor Communication (IPC) takes place through hardware First-In-First-Out (FIFO) mailboxes. One processor acts as the system master controller which monitors the operation and controls the reset and restore of the system in case of faults and the other three processors form Triple Modular Redundancy (TMR) fault tolerance architecture with each other. We used Dynamic Partial Reconfiguration (DPR) in scrubbing the configuration memory frames and correcting the faults that might exist. The system is implemented using a Virtex-5 LX50 commercial grade FPGA from Xilinx. The research also qualifies the design in the ground-simulated space

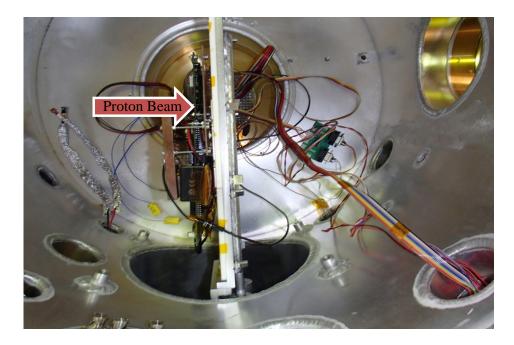

environment conditions. We tested the implemented MPSoC OBC in Thermal Vacuum Chambers (TVC) at the Center of Nano-Satellite Testing (CeNT) at Kyushu Institute of Technology. Also we irradiated the design with proton accelerated beam at 65 MeV with fluxes of 10e06 and 3e06 particle/cm<sup>2</sup>/sec at the Takasaki Advanced Radiation Research Institute (TARRI).

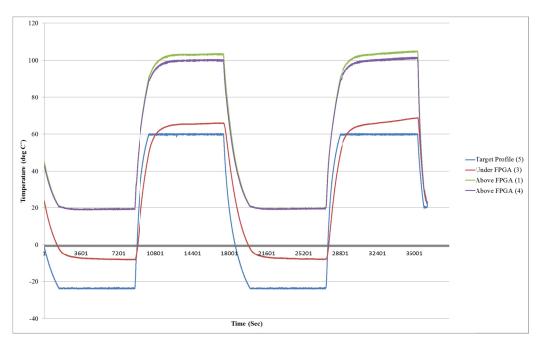

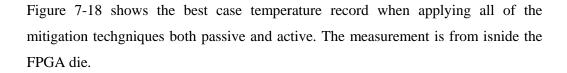

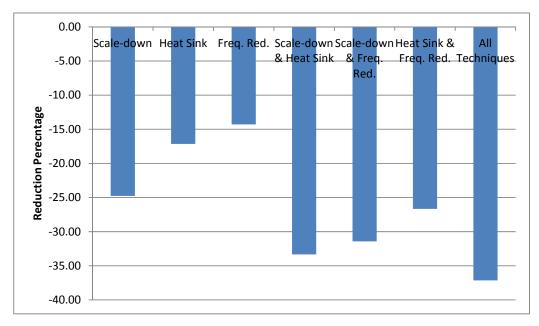

The TVC test results showed that the FPGA design exceeded the limits of normal operation for the commercial grade package at about 105 C<sup> $\circ$ </sup>. Therefore, we mitigated the package using: 1) heat sink, 2) dynamic temperature management through operating frequency reduction from 100 MHz to 50 MHz and 3) reconfiguration to reduce the number of working processors to 2 instead of 4 by replacing the space-redundancy TMR with time-redundancy TMR during the sunlight section of the orbit. The mitigation proved to be efficient and it even reduced the temperature from 105 C<sup> $\circ$ </sup> to about 66 C<sup> $\circ$ </sup> when the heat sink, frequency reduction, and reconfiguration techniques were used together.

The radiation and the fault injection tests showed that mitigating the FPGA configuration frames through scrubbing are efficient when Single Bit Upsets (SBU) are recorded. Multiple Bit Upsets (MBU) are not well mitigated using the scrubbing with Single Error Correction Double Error Detection (SECDED) technique and the FPGA needs to be totally reset and reloaded when MBUs are detected in its configuration frames. However, as MBUs occurrence in space is very seldom and rare compared to SBUs, we consider that SECDED scrubbing is very efficient in decreasing the soft error rate and increasing the reliability of having error-free bitstreams. The reliability was proven to be at 0.9999 when the scrubbing rate was continuous at a period of 7.1 msec between complete scans of the FPGA bitstream. In the proton radiation tests we managed to develop a new technique to estimate the static cross section using internal scrubbing only without using external monitoring, control and scrubbing device. Fault injection was used to estimate the dynamic cross section in a cost effective alternative for estimating it through radiation test.

The research proved through detailed testing that the 65 nm commercial grade SRAM-based FPGA can be used in future space missions. The MPSoC OBC design achieved an adequate balance between the performance, power, mass, and reliability requirements. Extensive testing and applying carefully crafted mitigation techniques

were the key points to verify and validate the MPSoC OBC design. In-orbit validation through a scientific demonstration mission would be the next step for the future research.

## **Table of Contents**

| Acknowledgment                                                       |

|----------------------------------------------------------------------|

| AbstractIV                                                           |

| List of FiguresXI                                                    |

| List of TablesXV                                                     |

| AcronymsXVI                                                          |

| Chapter 1 : Introduction 1                                           |

| 1.1 Research Outline                                                 |

| 1.2 Research Motivation                                              |

| 1.3 Research Objectives                                              |

| 1.4 Research Methodology                                             |

| 1.5 Research Originality and Contributions11                         |

| 1.6 Thesis Overview                                                  |

| Chapter 2 : Background and Literature Review                         |

| 2.1 Space Environment                                                |

| 2.2 Satellite On Board Computers                                     |

| 2.3 Radiation-Induced Fault Mitigation Approaches                    |

| 2.4 SRAM-based FPGAs for Space Applications                          |

| 2.5 Previous Work                                                    |

| Chapter 3 Multi-Processor System-on-Chip On-Board Computer Design 31 |

| 3.1 OBC Architecture Alternatives                                    |

| 3.2 FPGA Reconfiguration Strategies 44                               |

| 3.2.1 Scheduled Maintenance                                          |

| 3.2.2 Emergency Maintenance                                          |

| 3.2.3 Running Repairs                                                |

| 3.3 MPSoC OBC System Design 50                                       |

| Chapter 4 : Space and Time Redundancy Trade-offs  | 65  |

|---------------------------------------------------|-----|

| 4.1 Single Processor Design                       | 66  |

| 4.2 Time and Space Redundancy Check Bench         | 68  |

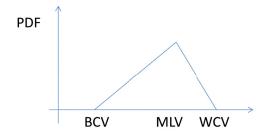

| 4.3 Estimation of Soft-Error Reliability          | 72  |

| 4.3.1 Target Orbit Definition                     | 73  |

| 4.3.2 SEU Rate Estimation                         | 76  |

| 4.3.3 Design Specific SEU Rate                    | 78  |

| 4.3.4 System Failure Rate                         | 78  |

| 4.3.5 Reliability Estimation                      | 79  |

| Chapter 5 : Radiation and Fault Injection Testing | 86  |

| 5.1 Radiation Test Objectives                     | 86  |

| 5.2 Accelerated Proton Beam Radiation Test Setup  | 87  |

| 5.3 Radiation Test procedure                      | 93  |

| 5.3.1 Safety Precautions                          | 96  |

| 5.3.2 Accelerator Parameters                      | 97  |

| 5.3.3 Embedded Software                           | 101 |

| 5.3.4 Upset Rate Estimation                       | 101 |

| 5.4 Fault Injection Test Objectives               | 103 |

| 5.5 Fault Injection Concept                       | 104 |

| 5.6 SEU Fault Injector                            | 106 |

| Chapter 6 : Thermal Vacuum Testing                | 111 |

| 6.1 Space Thermal Environment                     | 111 |

| 6.1.1 Conduction Heat Transfer                    | 113 |

| 6.1.2 Convection Heat Transfer                    | 115 |

| 6.1.3 Radiation Heat Transfer                     | 115 |

| 6.1.4 Radiation View Factors                      | 116 |

| 6.1.5 Equilibrium Temperature                     | 117 |

| 6.2 Thermal Effects on 65 nm Virtex-5 FPGA                 | 119             |

|------------------------------------------------------------|-----------------|

| 6.3 Thermal Control Techniques                             |                 |

| 6.4 Geometric Thermal Model                                | 123             |

| 6.5 Thermal Vacuum Test Objectives                         | 125             |

| 6.6 Thermal Vacuum Test Setup                              | 126             |

| 6.7 Thermal Vacuum Test Procedure                          |                 |

| Chapter 7 : Results and Discussion                         |                 |

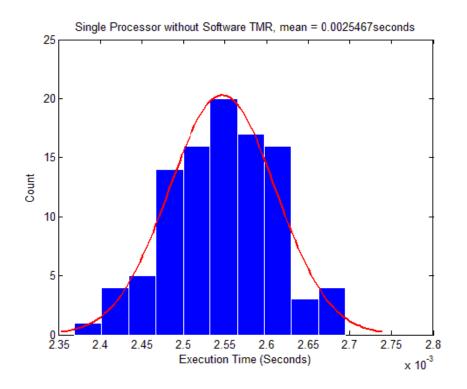

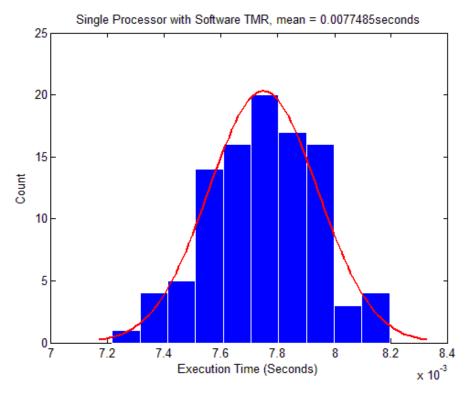

| 7.1 Time and Space Redundancy Performance                  |                 |

| 7.2 Static Cross Section from Accelerated Proton Beam Test |                 |

| 7.3 Fault Injection versus Radiation Tests                 | 149             |

| 7.4 Dynamic Cross Section through Fault Injection Test     | 150             |

| 7.5 Thermal Vacuum Test Results                            | 154             |

| Chapter 8 : Conclusion and Future Perspectives             | 160             |

| 8.1 Conclusion                                             | 160             |

| 8.2 Future Perspectives                                    |                 |

| References                                                 | 169             |

| Appendix A Microprocessor Hardware Specification of the M  | MPSoC 176       |

| Appendix B SEU Controller Connection Schematic             | 192             |

| Appendix C SEU Screening of Spartan-6 FPGA Using Cf-25     | 52 193          |

| C.1 Introduction                                           | 193             |

| C.2 System Design and Test Setup                           |                 |

| C.3 Results and Discussion                                 | 195             |

| C.4 Conclusion                                             | 198             |

| Appendix D Sample Code – MPSoC Embedded Softw              | vare in Thermal |

| Vacuum and Radiation Tests                                 |                 |

| D.1 MicroBlaze – 0 Code                                    |                 |

| D.2 MIcroBlaze 1 – Code                                    |                 |

| D.3        | MicroBlaze 2 – Code                                              | 206 |

|------------|------------------------------------------------------------------|-----|

| D.4        | MicroBlaze 3 (MSCP) – Code                                       | 209 |

| D.5        | Temperature IC Addresses                                         | 219 |

| Appendix   | E Frame Addresses Generation in the Virtex-5 FPGA2               | 221 |

| Appendix   | F Sample Code - Fault Injection of Single Bit Upsets 2           | 224 |

| Appendix   | G Iterations effect on the Cost, Schedule and Reliability of Nar | no- |

| Satellites | Projects 2                                                       | 232 |

| G.1        | Introduction                                                     | 232 |

| G.2        | Dependency Structure Matrix Background 2                         | 234 |

| G.3        | Nano-satellite Project Case Study                                | 236 |

| G.4        | The Simulation Algorithm                                         | 242 |

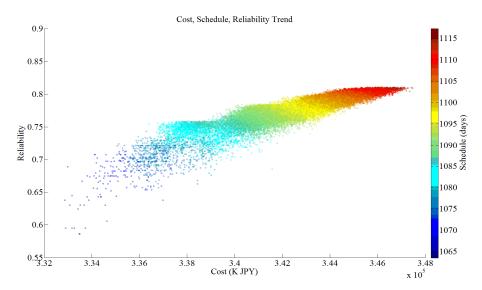

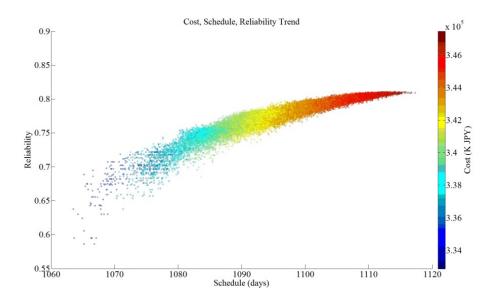

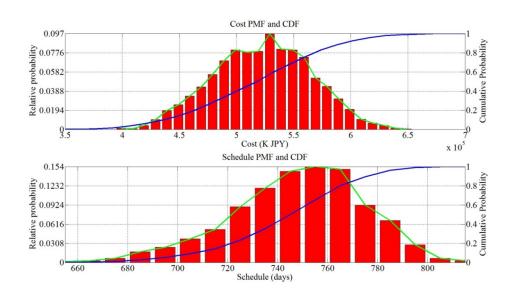

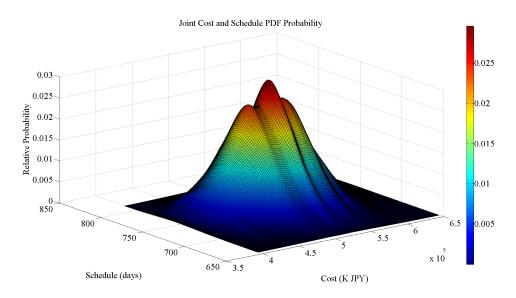

| G.5        | Results and Discussion                                           | 248 |

| G.6        | Conclusion                                                       | 256 |

# List of Figures

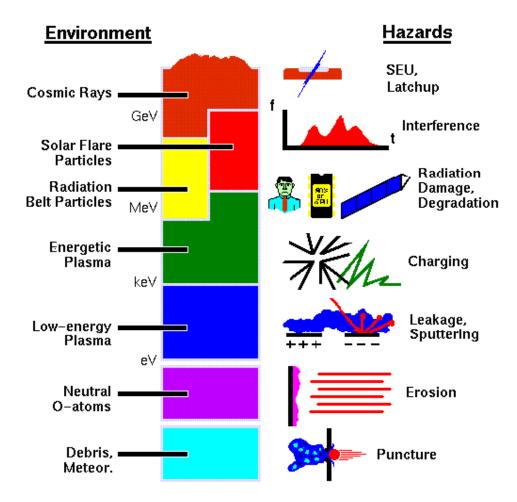

| FIGURE 2-1. HAZARDS IN THE SPACE ENVIRONMENT. SOURCE: EUROPEAN SPACE AGENCY, SPACE ENVIRONMENT AND     |

|--------------------------------------------------------------------------------------------------------|

| EFFECTS ANALYSIS SECTION © ESA                                                                         |

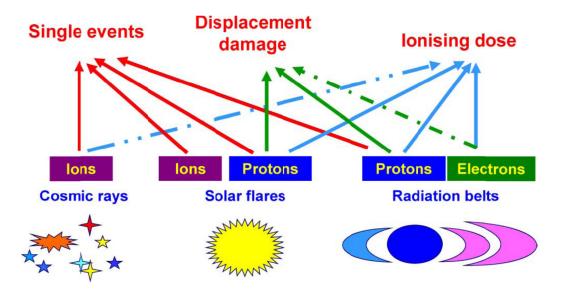

| FIGURE 2-2. CORRESPONDENCE BETWEEN RADIATION SOURCES AND EFFECTS ON COMPONENTS [18] [23] © 2013        |

| IEEE                                                                                                   |

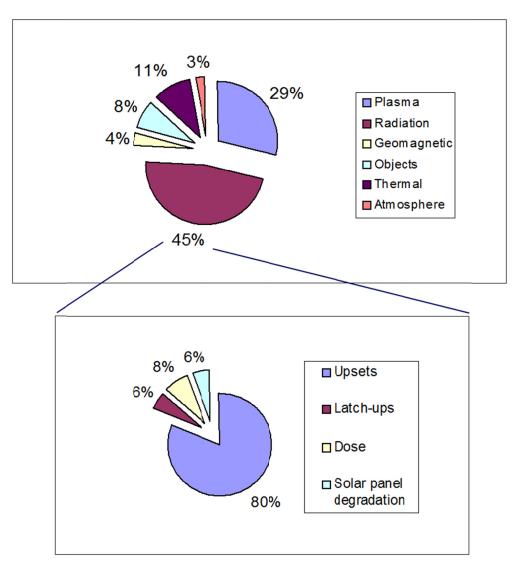

| FIGURE 2-3. PERCENTAGES OF SPACECRAFT ANOMALIES DUE TO THE SPACE ENVIRONMENT [18] [23] © 2013 IEEE. 17 |

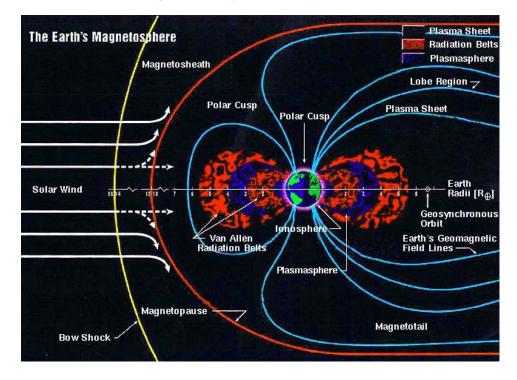

| FIGURE 2-4. EARTH MAGENTOSPHERE AND RADIATION BELTS. SOURCE: SPACE ENVIRONMENTS & EFFECTS PROGRAM,     |

| NASA Marshall Space Flight Center © NASA18                                                             |

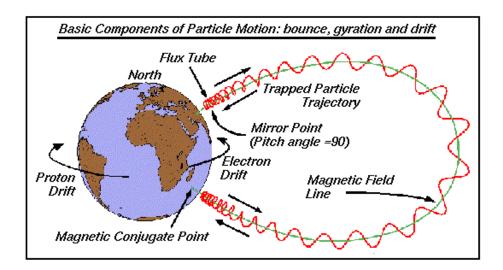

| FIGURE 2-5. MOTION OF THE TRAPPED CHARGED PARTICLES. SOURCE: EUROPEAN SPACE AGENCY, SPACE              |

| Environments and effects analysis section © ESA                                                        |

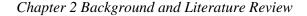

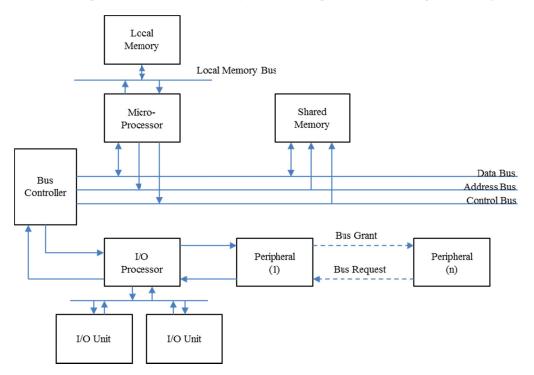

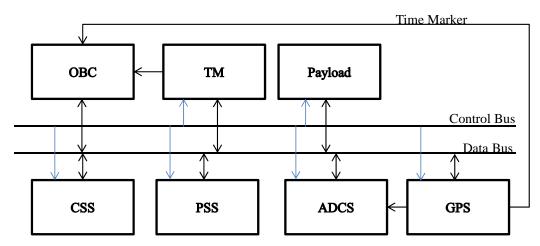

| FIGURE 2-6. TYPICAL OBC BLOCK DIAGRAM                                                                  |

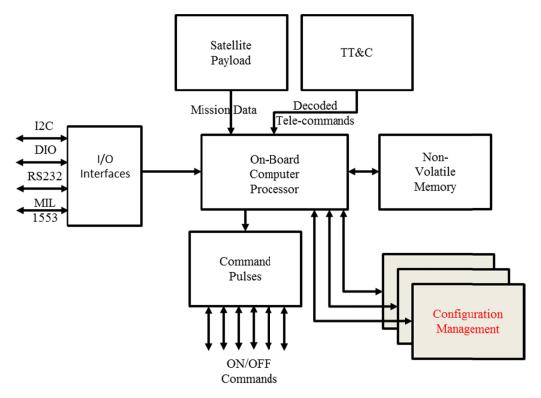

| FIGURE 2-7. XILINX FPGA TYPICAL CONTENTS BREAKDOWN © XILINX                                            |

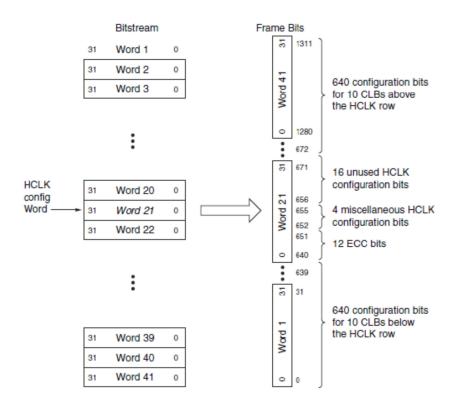

| Figure 2-8. Virtex-5 Configuration Frame Format © Xilinx                                               |

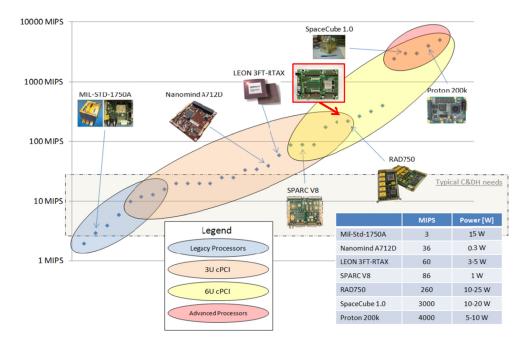

| FIGURE 2-9. SATELLITE PROCESSING TRENDS [14] © NASA – AMES RESEARCH CENTER                             |

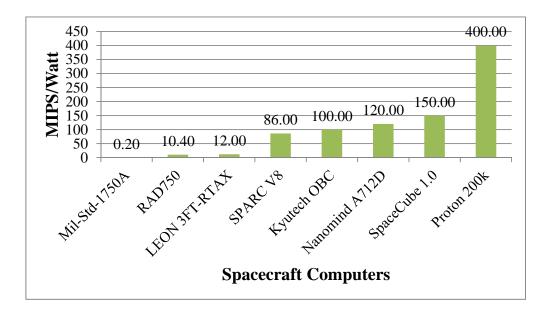

| FIGURE 2-10. SPACECRAFT COMPUTERS COMPARISON BASED ON PERFORMANCE/POWER CONSUMPTION                    |

| FIGURE 3-1. GENERAL EMBEDDED OBC SYSTEM ARCHITECTURE                                                   |

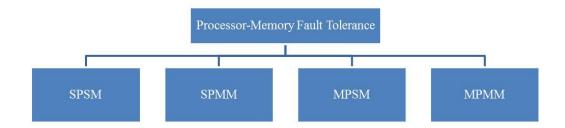

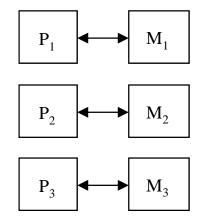

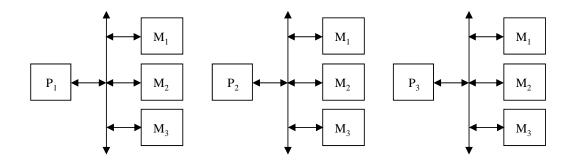

| FIGURE 3-2. ABU ZAID TAXONOMY OF FAULT TOLERANT PROCESSOR-MEMORY INTERFACES [56]                       |

| FIGURE 3-3. MPSM WITH NON-SHARED MEMORY                                                                |

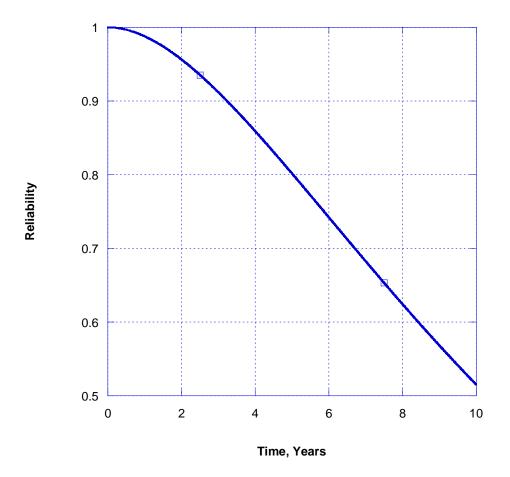

| FIGURE 3-4. MPMM NON-SHARED MEMORY                                                                     |

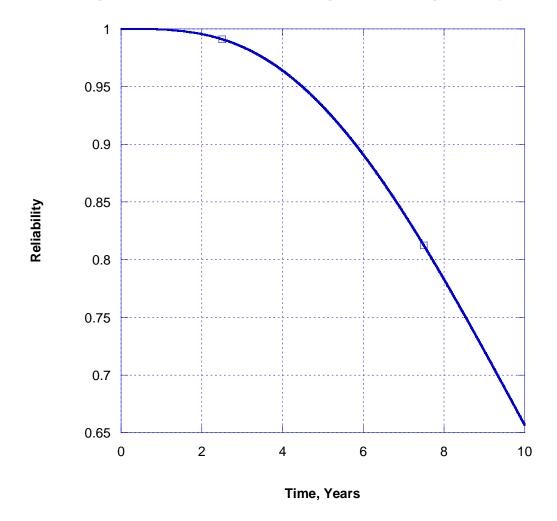

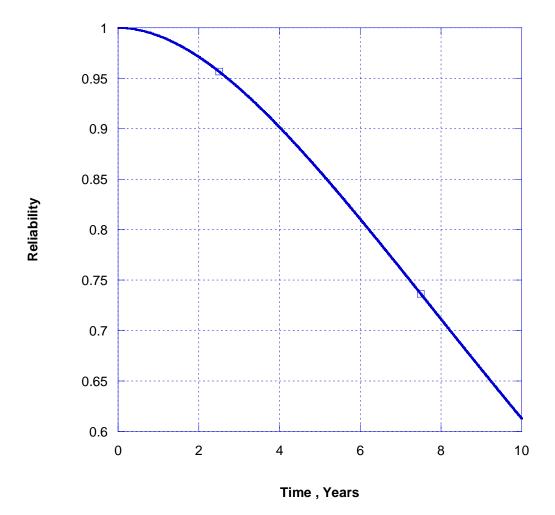

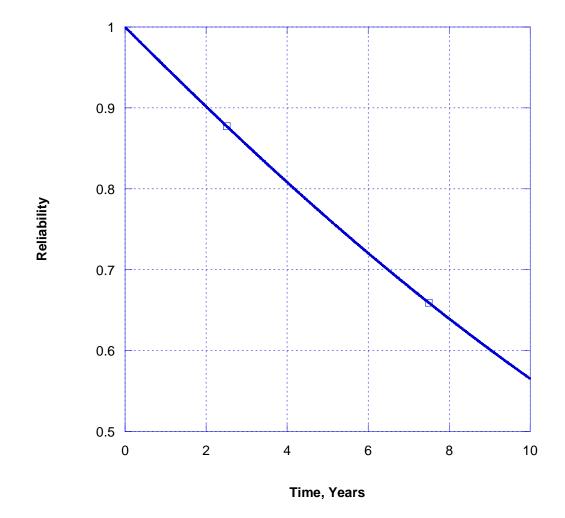

| FIGURE 3-5. MPSM NON-SHARED MEMORY RELIABILITY CURVE                                                   |

| FIGURE 3-6. MPMM NON-SHARED MEMORY RELIABILITY CURVE                                                   |

| FIGURE 3-7. MPMM SHARED MEMORY RELIABILITY CURVE                                                       |

| FIGURE 3-8. MPSM SHARED MEMORY RELIABILITY CURVE                                                       |

| FIGURE 3-9. SOFT ERROR RELIABILITY FOR MP ARCHITECTURES                                                |

| Figure 3-10. Scheduled Maintenance – Reload from External Flash                                        |

| FIGURE 3-11. SCHEDULED MAINTENANCE – RELOAD FROM PLATFORM CONFIGURATION FLASH                          |

| FIGURE 3-12. EMERGENCY MAINTENANCE                                                                     |

| FIGURE 3-13. RUNNING REPAIRS – SELECTION OF AN ACTIVE MODULE                                           |

| FIGURE 3-14. RUNNING REPAIRS – ACTIVE MODULES WITH VOTING.                                             |

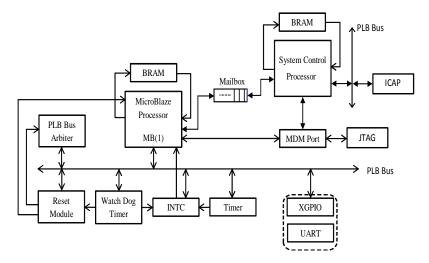

| FIGURE 3-15. MPSOC OBC BLOCK DIAGRAM                                                                   |

| Figure 3-16. Ping/Ack Watchdog Timer [59]                                                              |

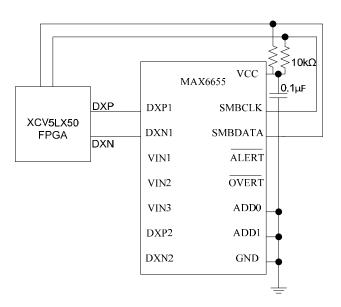

| FIGURE 3-17. INTERFACE WITH TEMPERATURE MEASUREMENT IC                                                 |

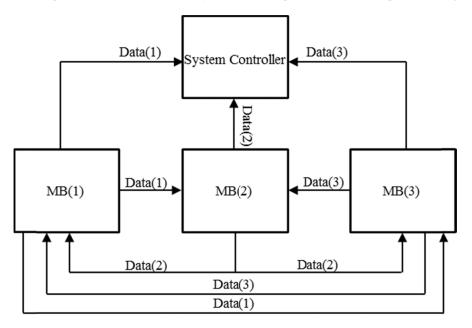

| FIGURE 3-18. TMR WITH FEEDBACK AMONG THE DATA OF THE MPSOC NODES                                       |

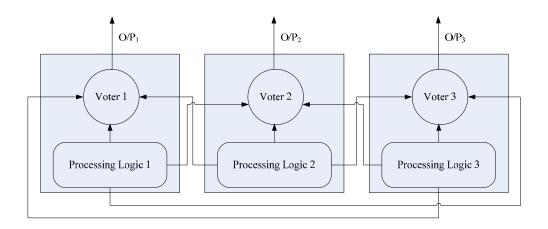

| FIGURE 3-19. DISTRIBUTED VOTING FUNCTION AT REDUNDANT PROCESSORS [59]                                  |

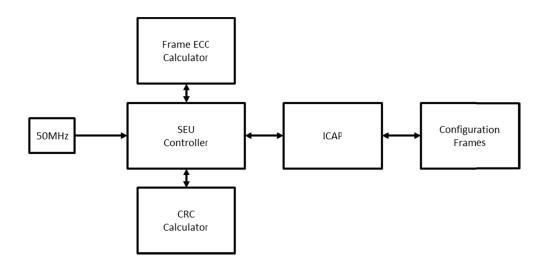

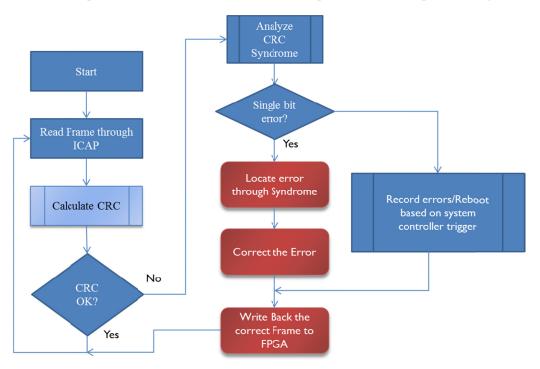

| FIGURE 3-20. FUNCTIONAL BLOCKS FOR CORRECTING SBUS                                                     |

| FIGURE 3-21. SCRUBBING ALGORITHM                                                                       |

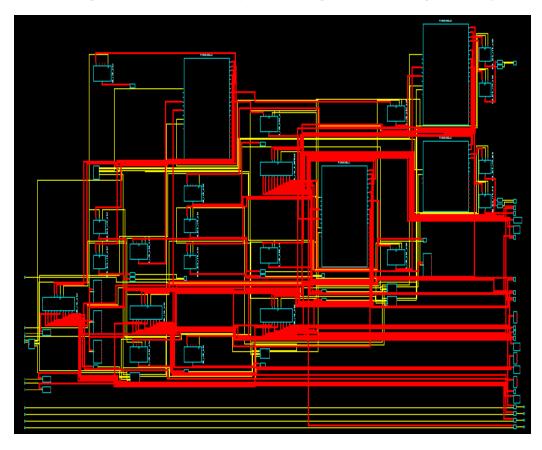

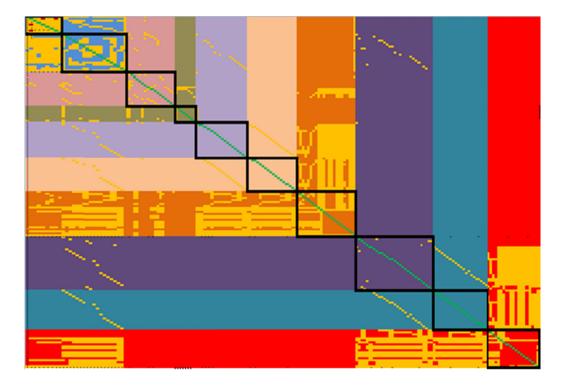

| FIGURE 3-22. SCHEMATIC OF THE MPSOC DESIGN IN THE XC5VLX50-1FFG676C FPGA61                                  |

|-------------------------------------------------------------------------------------------------------------|

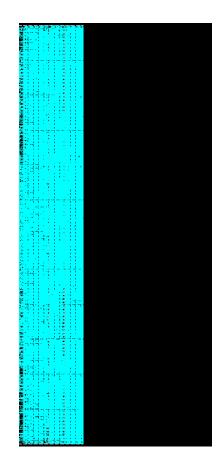

| FIGURE 3-23. FPGA FLOOR PLAN OF THE MPSOC OBC                                                               |

| Figure 4-1. Single Processor System                                                                         |

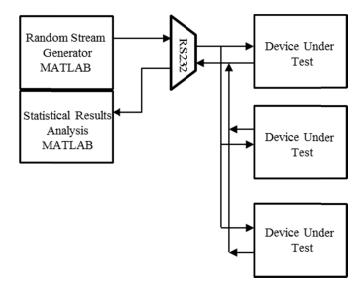

| FIGURE 4-2. TIME AND SPACE REDUDNACY TEST CONFIGURATION                                                     |

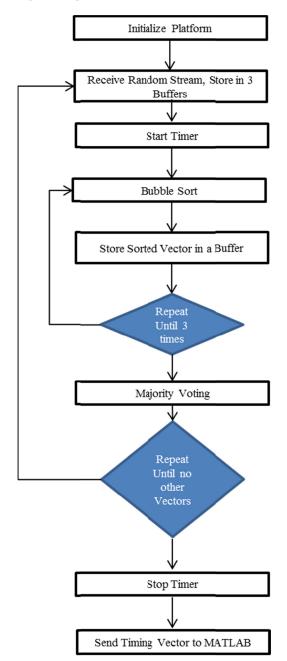

| FIGURE 4-3. TIME REDUNDANCY - SINGLE PROCESSOR                                                              |

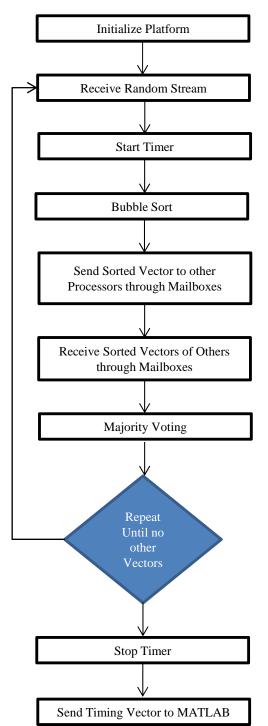

| FIGURE 4-4. SPACE REDUNDANCY - TRIPLE PROCESSORS                                                            |

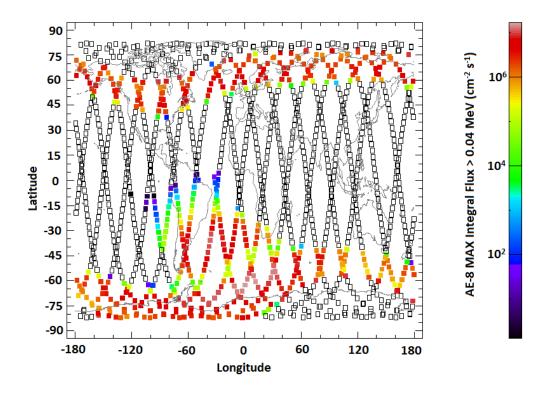

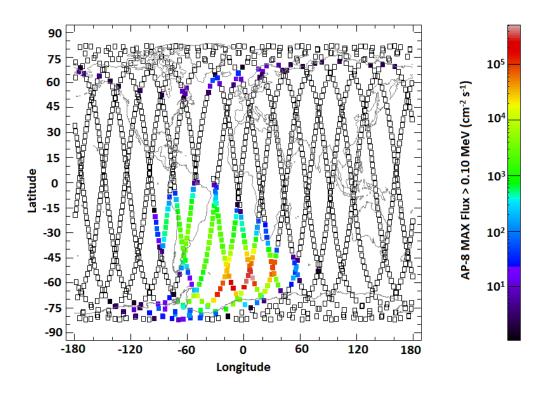

| FIGURE 4-5. AE-8 MODEL TRAPPED ELECTRONS FLUX IN THE ORBIT                                                  |

| FIGURE 4-6. AP-8 MODEL TRAPPED PROTONS FLUX IN THE ORBIT                                                    |

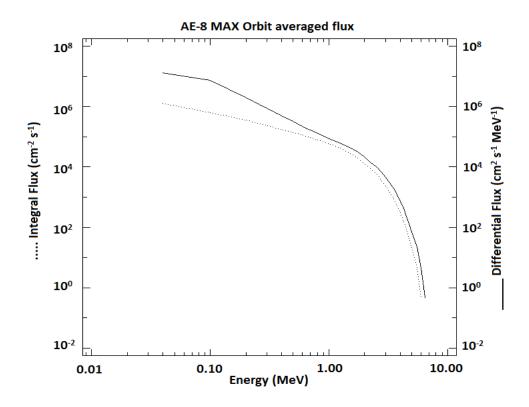

| FIGURE 4-7. TRAPPED ELECTRONS ENERGY SPECTRA VERSUS THE FLUX                                                |

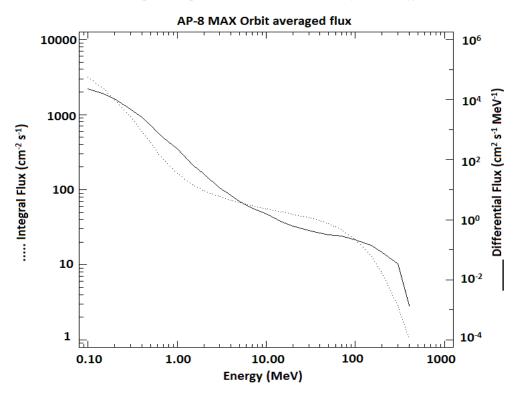

| FIGURE 4-8. TRAPPED PROTONS ENERGY SPECTRA VERSUS THE FLUX                                                  |

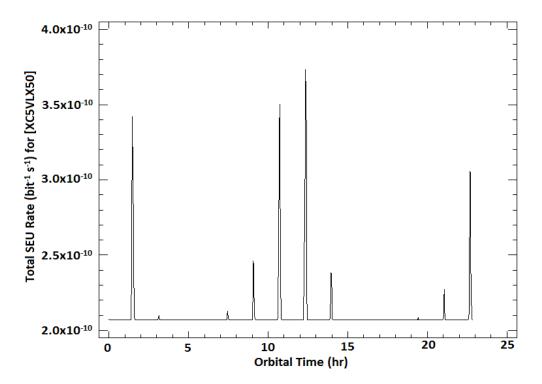

| FIGURE 4-9. IN-ORBIT SEU RATES ESTIMATED BY CREME-96 AND BASED ON REAL RADIATION TEST RESULTS OF THE        |

| XILINX XC5VLX50 FPGA                                                                                        |

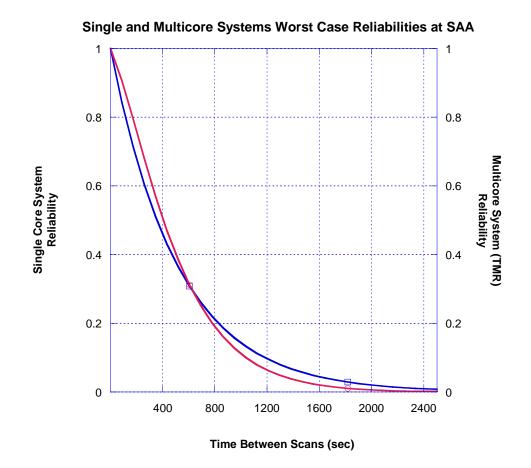

| FIGURE 4-10. SINGLE VERSUS TRIPLE PROCESSOR SYSTEMS SOFT-ERROR RELIABILITY BASED ON IN-ORBIT ESTIMATION. 82 |

| FIGURE 4-11. SINGLE VERSUS TRIPLE PROCESSOR SYSTEMS SOFT-ERROR RELIABILITY BASED ON IN-ORBIT ESTIMATION,    |

| TIME BETWEEN SCANS ≤ 100 SEC                                                                                |

| FIGURE 4-12. SINGLE VERSUS TRIPLE PROCESSOR SYSTEMS SOFT-ERROR RELIABILITY BASED ON IN-ORBIT ESTIMATION,    |

| TIME BETWEEN SCANS ≤ 10 MSEC84                                                                              |

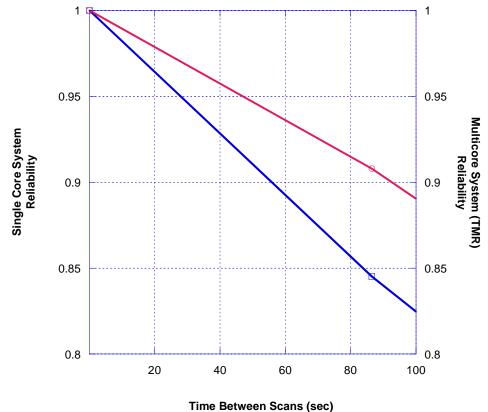

| FIGURE 4-13. TOTAL SYSTEM RELIABILITY OF TMR SYSTEM BASED ON IN-ORBIT SEU RATES AND ASSUMING AN MRAM        |

| Soft Failure Rate of 0.05 failures/year85                                                                   |

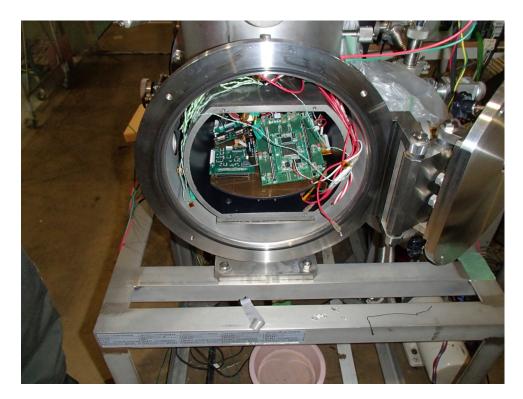

| FIGURE 5-1. BAKING OF BOARDS BEFORE RADIATION TESTING                                                       |

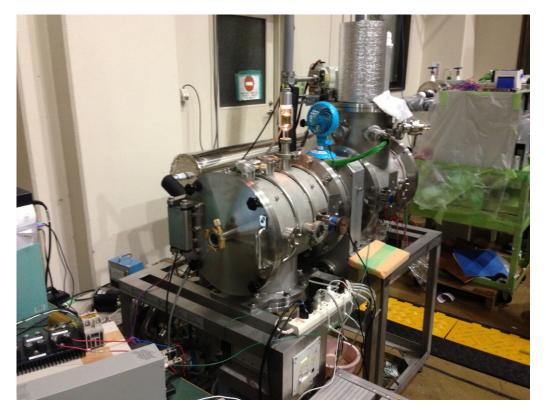

| FIGURE 5-2. RADIATION TEST CHAMBER USED IN ACCELERATED PROTON BEAM TEST                                     |

| Figure 5-3. Proton Beam Line Connected to Test Chamber                                                      |

| Figure 5-4. Beam Centering Grid                                                                             |

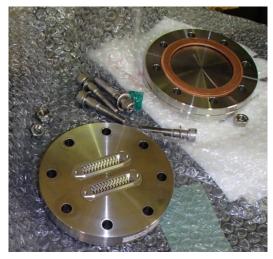

| FIGURE 5-5. INTERFACE FLANGE WITH RADIATION TEST CHAMBER                                                    |

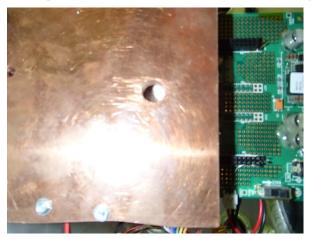

| FIGURE 5-6. COPPER SHIELD IN RADIATION TEST                                                                 |

| FIGURE 5-7. TOP-VIEW DUT IN RADIATION TEST CHAMBER WITH RS-232 INTERFACE                                    |

| Figure 5-8. Outgassing due to External RS-422 Converters                                                    |

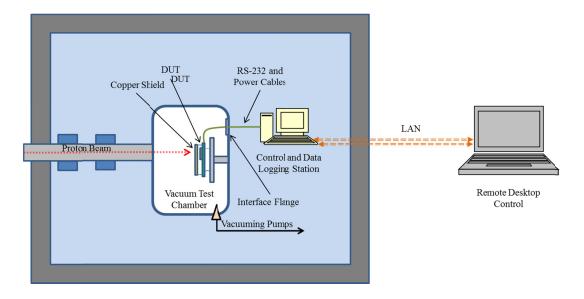

| Figure 5-9. Accelerated Proton Beam Test Setup93                                                            |

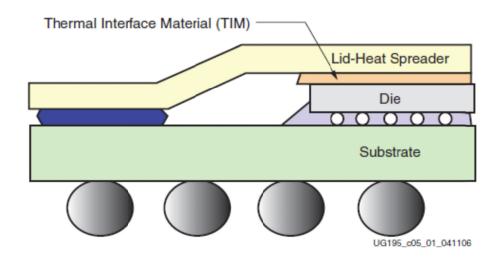

| Figure 5-10. Virtex 5 Layers © Xilinx                                                                       |

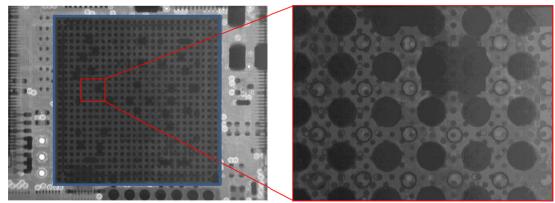

| FIGURE 5-11. X-RAY OF THE XC5VLX50-1FFG676C FPGA95                                                          |

| FIGURE 5-12. FPGA BEFORE AND AFTER DE-CAPSULATION                                                           |

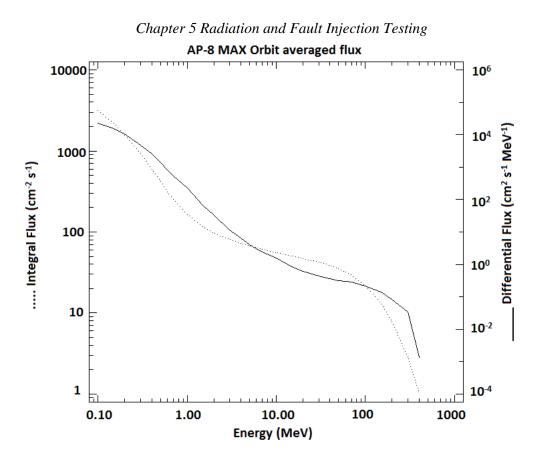

| FIGURE 5-13. PROTON ENERGY SPECTRA VERSUS FLUX LEVEL AT HORYU-2 ORBIT.                                      |

| FIGURE 5-14. SAMPLE OUTPUT FROM THE SEU CONTROLLER DURING RADIATION TEST.                                   |

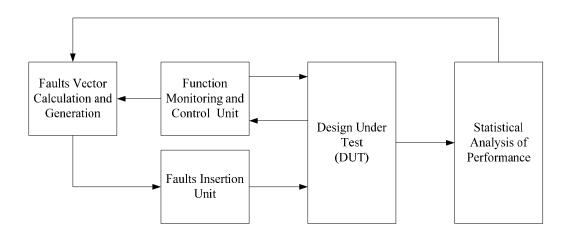

| FIGURE 5-15. FAULT INJECTION CYCLE                                                                          |

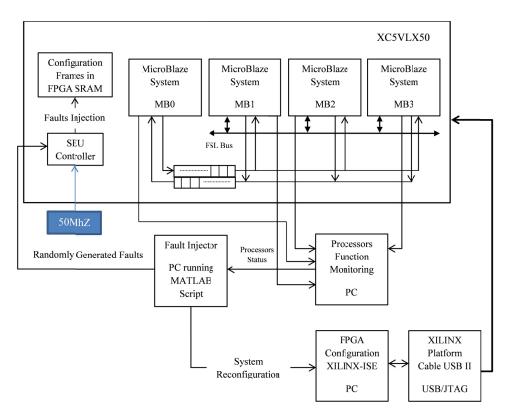

| Figure 5-16. Fault Injector System Architecture                                                             |

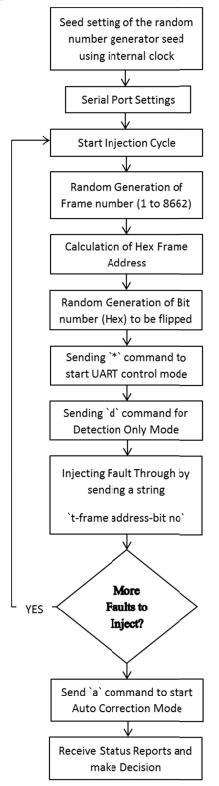

| FIGURE 5-17. FAULT INJECTION TEST FLOW CHART                                                                |

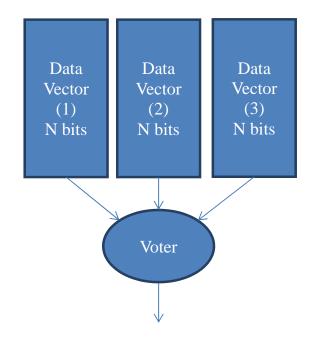

| Figure 5-18. TMR among N bits Vectors                                                                       |

| FIGURE 5-19. PART OF THE MATLAB SCRIPT TO SIMULATE TMR ERRORS                                               |

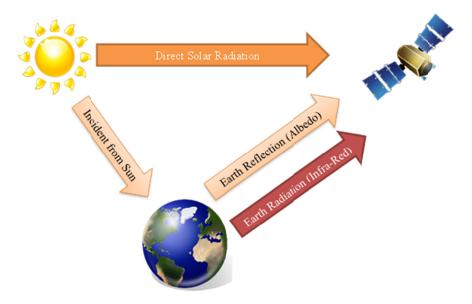

| FIGURE 6-1. SPACE THERMAL ENVIRONMENT                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------|

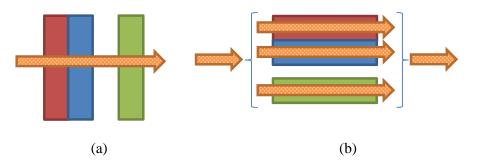

| FIGURE 6-2. A) HEAT FLOW IN SERIES AND B) HEAT FLOW IN PARALLEL                                                                    |

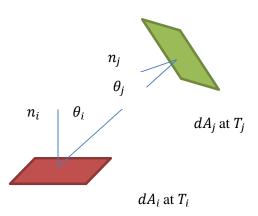

| FIGURE 6-3. VIEW FACTOR CALCULATION GEOMETRY [72]                                                                                  |

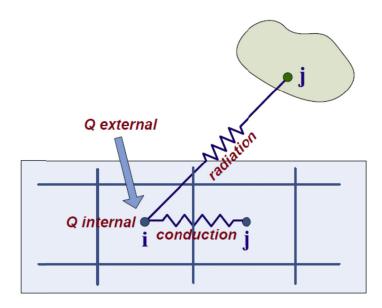

| FIGURE 6-4. THERMAL EQUILIBRIUM ANALYSIS THROUGH MESH NODES [68]                                                                   |

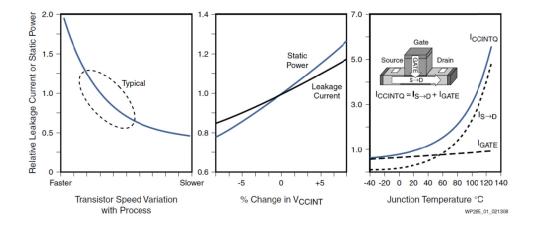

| FIGURE 6-5. CHANGE OF STATIC POWER WITH PROCESS, VOLTAGE AND JUNCTION TEMPERATURE IN 65 NM SRAM-                                   |

| BASED FPGA XILINX VIRTEX-5 [79]120                                                                                                 |

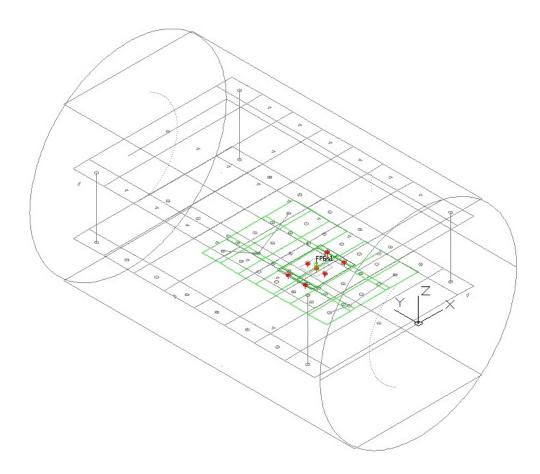

| FIGURE 6-6. MPSOC OBC GEOMETRIC THERMAL MODEL                                                                                      |

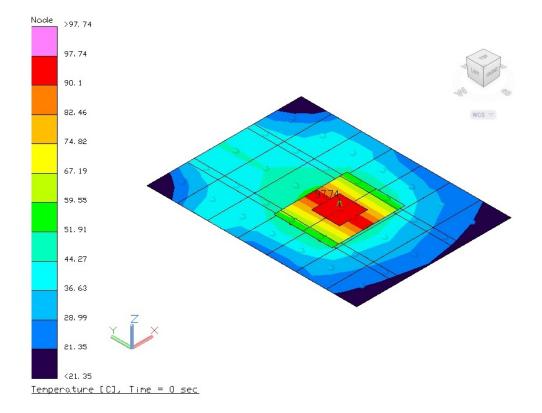

| FIGURE 6-7. THERMAL MATHEMATICAL MODEL SIMULATION RESULTS                                                                          |

| FIGURE 6-8. SMALL THERMAL VACUUM CHAMBER USED DURING THE TESTS                                                                     |

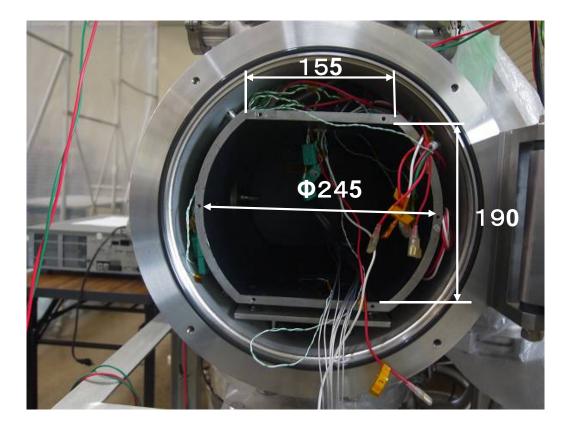

| Figure 6-9. Thermal Vacuum Chamber Shroud Dimensions127                                                                            |

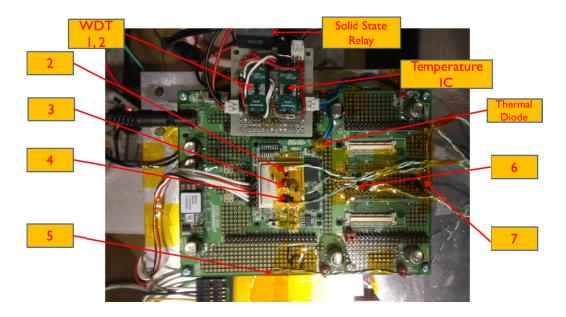

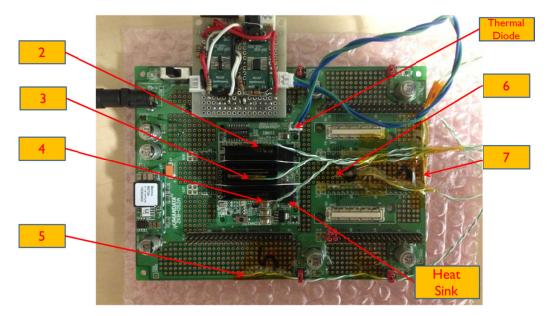

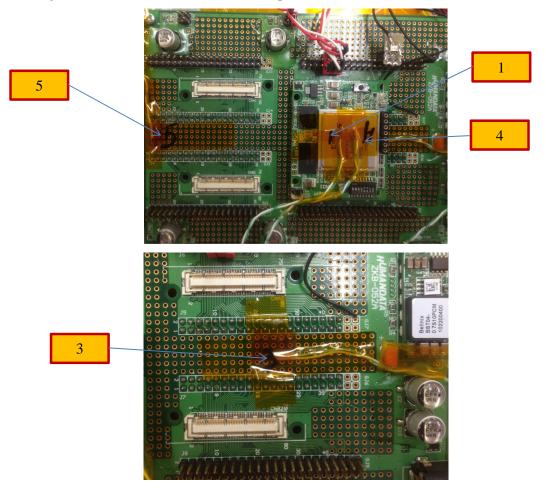

| FIGURE 6-10. THERMOCOUPLES POSITIONS DURING THERMAL VACUUM TESTS - TOP POSITIONS                                                   |

| FIGURE 6-11. THERMOCOUPLES POSITIONS DURING THERMAL VACUUM TESTS - BOTTOM POSITIONS                                                |

| FIGURE 6-12. THERMOCOUPLES POSITIONS DURING THERMAL VACUUM TESTS - TOP POSITIONS - WITH HEAT SINK 129                              |

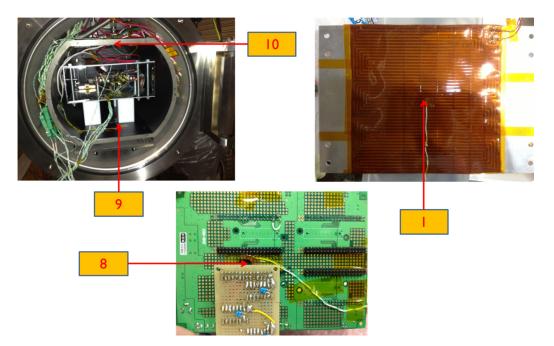

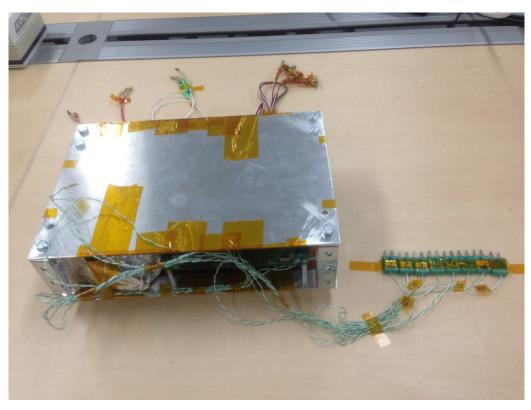

| FIGURE 6-13. ASSEMBLED SANDWICH STRUCTURE BEFORE THERMAL VACUUM TESTING                                                            |

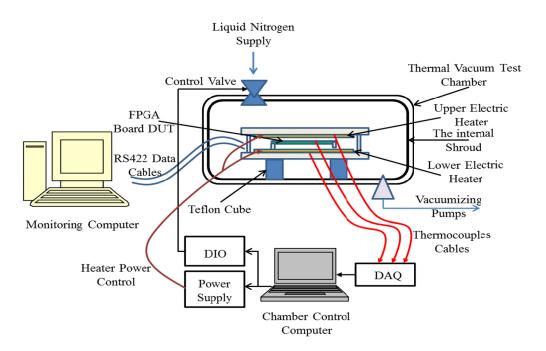

| FIGURE 6-14. THERMAL VACUUM TEST SETUP SCHEMATIC                                                                                   |

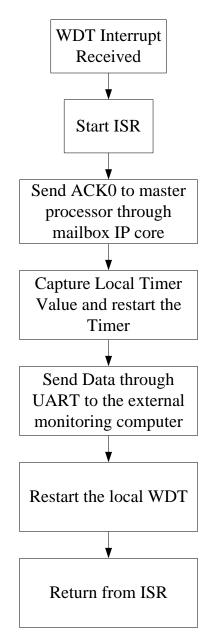

| FIGURE 6-15. ALGORITHM EXECUTED AT THE SLAVE PROCESSOR AT THERMAL VACUUM TEST                                                      |

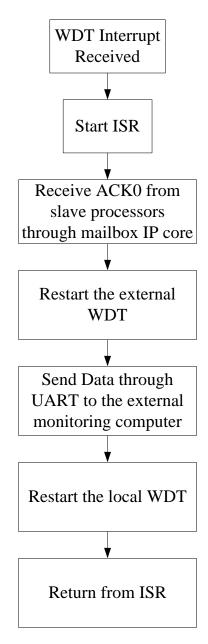

| FIGURE 6-16. ALGORITHM EXECUTED AT THE MASTER PROCESSOR AT THERMAL VACUUM TEST                                                     |

| FIGURE 6-17. INITIAL SCREENING THERMAL VACUUM TEST SENSORS ATTACHEMNT.                                                             |

| FIGURE 6-18. INITIAL SCREENING THERMAL VACUUM TEST RESULTS [67] ©IEEE 2013                                                         |

| FIGURE 7-1. NON-FAULT-TOLERANCE EXECUTION TIME HISTOGRAM                                                                           |

| FIGURE 7-2. TIME REDUNDANCY FAULT-TOLERANCE EXECUTION TIME HISTOGRAM.                                                              |

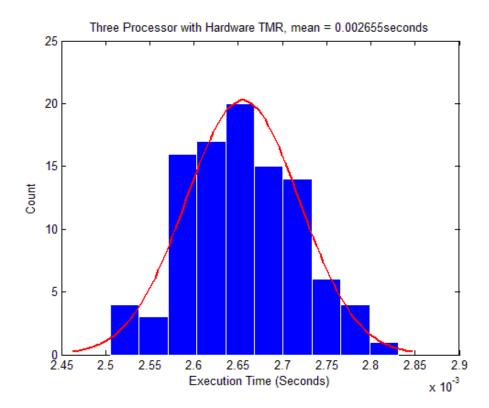

| FIGURE 7-3. SPACE REDUNDANCY FAULT-TOLERANCE EXECUTION TIME HISTOGRAM.                                                             |

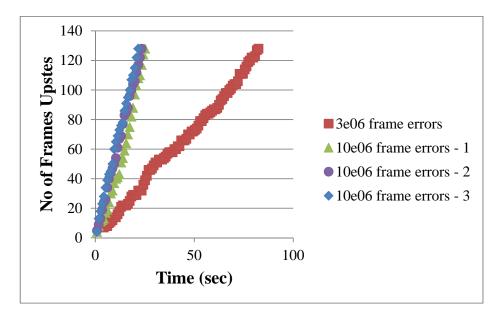

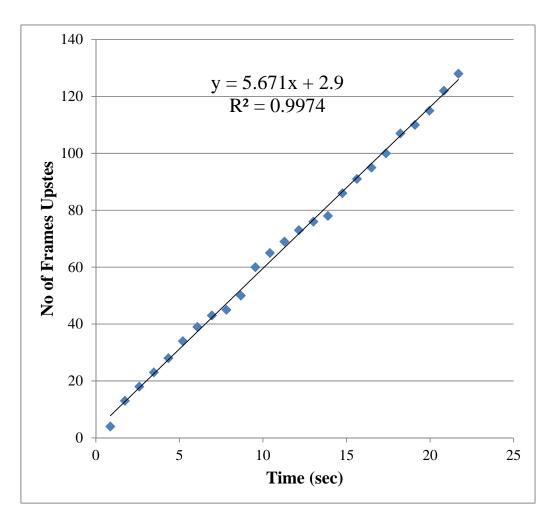

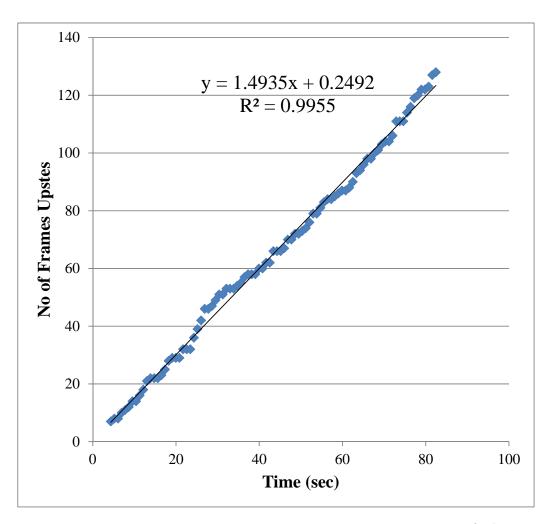

| Figure 7-4. Accumulated No. of Frame Upsets versus Time at Flux Levels of 10e06 and 3e06 (cm $^2$ .s $^{-1}$ ) –                   |

| ENERGY LEVEL OF 65 MEV142                                                                                                          |

| FIGURE 7-5. ACCUMULATED NO. OF FRAME UPSETS VERSUS TIME AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .S <sup>-1</sup> ) – ENERGY LEVEL |

| OF 65 MEV – 1st Trial                                                                                                              |

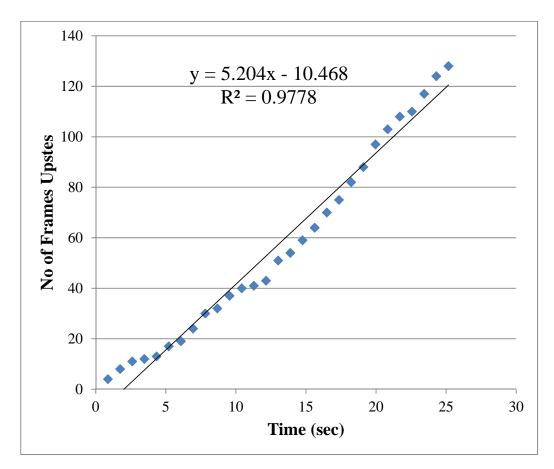

| FIGURE 7-6. ACCUMULATED NO. OF FRAME UPSETS VERSUS TIME AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .S <sup>-1</sup> ) – ENERGY LEVEL |

| OF 65 MEV – 2ND TRIAL                                                                                                              |

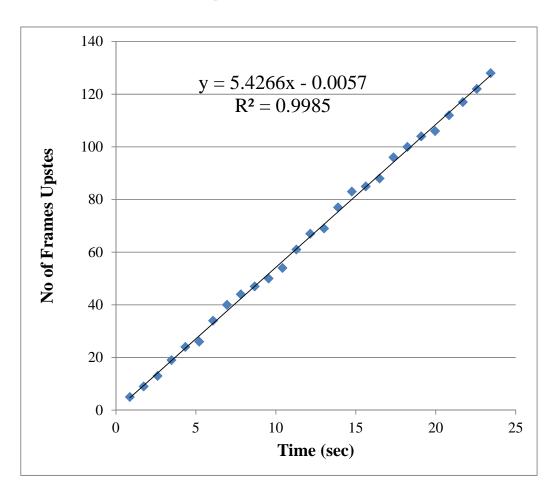

| FIGURE 7-7. ACCUMULATED NO. OF FRAME UPSETS VERSUS TIME AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .S <sup>-1</sup> ) – ENERGY LEVEL |

| OF 65 MEV – 3rd Trial                                                                                                              |

| Figure 7-8. Static Cross Section Calculations at Flux Level of 3e06 (cm $^{-2}$ .s $^{-1}$ ) – Energy Level of 65 MeV.             |

|                                                                                                                                    |

| FIGURE 7-9. RADIATION ANALYSIS CHART                                                                                               |

| FIGURE 7-10. DE-CAPSULATED SPARTAN-6 AND VIRTEX-5 FPGAS FOR CF-252 RADIATION TEST                                                  |

| FIGURE 7-11. FAULT INJECTION RESULTS151                                                                                            |

| FIGURE 7-12. TIME DISTRIBUTION BETWEEN INJECTED FAULTS                                                                             |

| FIGURE 7-13. TMR FAILURE RATE AT DATA VECTOR OF SIZE 2048 BYTES                                                                    |

| FIGURE 7-14. FPGA AUTOMATIC THERMAL PROTECTION                                                                                     |

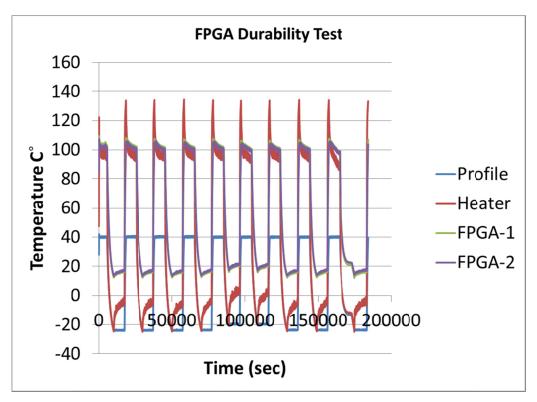

| FIGURE 7-15. FPGA DURABILITY TEST                                                                | . 155 |

|--------------------------------------------------------------------------------------------------|-------|

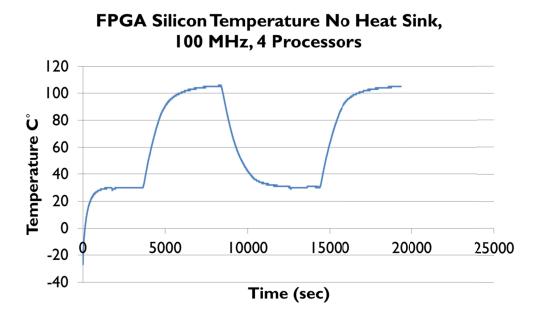

| FIGURE 7-16. THERMAL VACUUM TEST, NO-HEAT SINK, 100 MHz, 4 PROCESSORS – FPGA INTERNAL DIE        |       |

| Temperature                                                                                      | .156  |

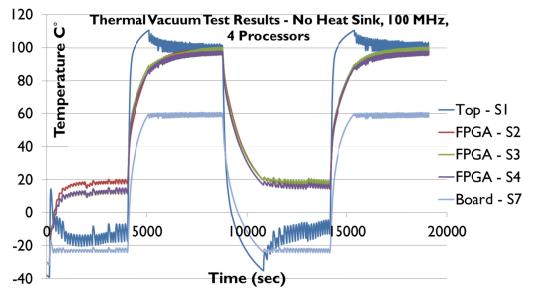

| FIGURE 7-17. THERMAL VACUUM TEST, NO-HEAT SINK, 100 MHz, 4 PROCESSORS – THERMOCOUPLES            | .156  |

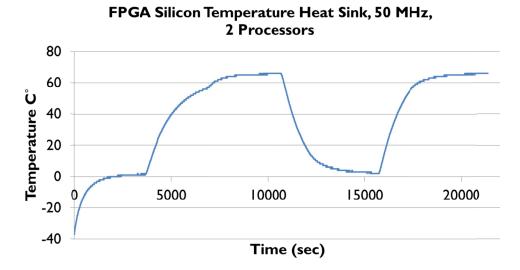

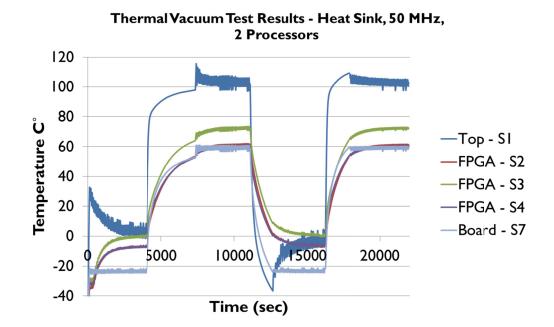

| FIGURE 7-18. THERMAL VACUUM TEST, HEAT SINK, 50 MHz, 2 PROCESSORS – FPGA INTERNAL DIE TEMPERATUR | E.    |

|                                                                                                  | .157  |

| FIGURE 7-19. THERMAL VACUUM TEST, HEAT SINK, 50 MHz, 2 PROCESSORS – THERMOCOUPLES                | . 157 |

| FIGURE 7-20. THERMAL MITIGATION EFFECTIVENESS.                                                   | . 159 |

## List of Tables

| TABLE 2 -1 MAIN SOURCES OF THE NATURAL SPACE RADIATION ENVIRONMENT [18]                                               |                            |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------|

| TABLE 3-1. SCOPE PROTECTED AND THE FAULT TOLERANCE PROTECTION TECHNIQUES.                                             |                            |

| TABLE 3-2. ARCHITECTURE ALTERNATIVES FOR PROCESSOR-MEMORY INTERFACES.                                                 |                            |

| TABLE 3-3. FPGA USED RESOURCES IN THE MPSOC DESIGN.                                                                   | 59                         |

| TABLE 3-4. POWER ESTIMATION OF THE MPSOC DESIGN                                                                       | 60                         |

| TABLE 3-5. FPGA BASED MPSOC OBC SPECIFICATIONS.                                                                       | 62                         |

| TABLE 4-1. SINGLE CORE AND MULTI-CORE POWER CONSUMPTIONS.                                                             | 67                         |

| TABLE 4-2. SINGLE CORE RESOURCES UTILIZATION.                                                                         | 68                         |

| TABLE 4-3. MULTI-CORE RESOURCES UTILIZATION.                                                                          | 68                         |

| TABLE 4-4. HORYU-2 SATELLITE ORBITAL PARAMETERS.                                                                      | 73                         |

| TABLE 4-5. DESIGN SIZE IN BITS AND THE UPSET RATES                                                                    | 78                         |

| TABLE 4-6. SYSTEM FAILURE RATES                                                                                       | 79                         |

| TABLE 5-1. HORYU-2 SATELLITE ORBIT PARAMETERS.                                                                        |                            |

| TABLE 5-2. ACCELERATOR PARAMETERS SETTINGS                                                                            | 101                        |

| TABLE 6-1. LEO THERMAL ENVIRONMENT [68]                                                                               | 112                        |

| TABLE 7-1. STATISTICAL ANALYSIS OF EXECUTION TIMES HISTOGRAMS IN SECONDS.                                             |                            |

| TABLE 7-2. SUMMARY OF TIME AND SPACE REDUNDANCY ARCHITECTURES COMPARISON.                                             |                            |

| TABLE 7-3. STATIC CROSS SECTION CALCULATIONS AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .s <sup>-1</sup> ) – ENERGY LEV | 'el of 65 MeV <del>-</del> |

| 1st Trial                                                                                                             | 144                        |

| TABLE 7-4. STATIC CROSS SECTION CALCULATIONS AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .s <sup>-1</sup> ) – ENERGY LEV | 'EL OF 65 MEV –            |

| 2ND TRIAL                                                                                                             | 145                        |

| TABLE 7-5. STATIC CROSS SECTION CALCULATIONS AT FLUX LEVEL OF 10E06 (CM <sup>-2</sup> .s <sup>-1</sup> ) – ENERGY LEV | 'EL OF 65 MEV –            |

| 3rd Trial                                                                                                             | 146                        |

| TABLE 7-6. STATIC CROSS SECTION CALCULATIONS AT FLUX LEVEL OF 3E06 (CM <sup>-2</sup> .s <sup>-1</sup> ) – ENERGY LEVE | l of 65 MeV. 147           |

| TABLE 7-7. THERMAL VACUUM TEST RESULTS WITH AND WITHOUT MITIGATION TECHNIQUES                                         |                            |

# Acronyms

| ABFT   | Architecture Based Fault Tolerance        |

|--------|-------------------------------------------|

| AES    | Advanced Encryption Standard              |

| AMFT   | Adaptive Middleware for Fault Tolerance   |

| ASIC   | Application Specific Integrated Circuits  |

| AU     | Astronomical Unit                         |

| BB     | Black Box                                 |

| BGA    | Ball Grid Array                           |

| BPI    | Byte Peripheral Interface                 |

| BRAM   | Block Random Access Memory                |

| BSP    | Board Support Package                     |

| BSTI   | Basic Space Technology Iniative           |

| CAN    | Controller Area Network                   |

| CAD    | Computer Aided Design                     |

| CeNT   | Center for Nano satellite Testing         |

| CMOS   | Complementary Metal- Oxide- Semiconductor |

| CFC    | Clock Frequency Control                   |

| Cf-252 | Californium-252                           |

| CLB    | Configuration Logic Block                 |

| COTS   | Commercial Off The Shelf                  |

| CRC    | Cyclic Redundancy Check                   |

| DAQ    | Data Acquisition                          |

| DCM    | Digital Clock Manager                     |

| DDD    | Displacement Damage Dose                  |

| DIO    | Digital Input Output                      |

| DNST   | Doctorate in Nano-Satellite Technologies  |

| DPR    | Dynamic Partial Reconfiguration           |

| DTM    | Dynamic Temperature Management            |

| DUT   | Device or Design Under Test                 |

|-------|---------------------------------------------|

| ECC   | Error Correcting Code                       |

| EDAC  | Error Detection And Correction              |

| EDC   | Error Detection Coding                      |

| EDK   | Embedded Development Kit                    |

| ESA   | European Space Agency                       |

| FAR   | Frame Address Register                      |

| FDR   | Frame Data Register                         |

| FIT   | Failure In Time                             |

| FPGA  | Field Programmable Gate Array               |

| GPIO  | General Purpose Input Output                |

| HPEC  | High Performance Embedded Computing         |

| IC    | Integrated Circuit                          |

| ICAP  | Internal Configuration Access Port          |

| IDE   | Integrated Development Environment          |

| IIC   | Inter-Integrated Circuit                    |

| IO    | Input/output                                |

| IOB   | Input Output Block                          |

| IP    | Intellectual Property soft cores            |

| IR    | Infrared Radiation                          |

| ISR   | Interrupt Service Routine                   |

| JAEA  | Japan Atomic Energy Agency                  |

| JTAG  | Joint Test Action Group                     |

| KURRI | Kyoto University Research Reactor Institute |

| KIT   | Kyushu Institute of Technology              |

| LMB   | Local Memory Bus                            |

| LEO   | Low Earth Orbit                             |

| LET   | Linear Energy Transfer                      |

| LUT   | Look Up Table                               |

| MBU   | Multiple Bit Upset                          |

| MDM    | MicroBlaze Debug Module                            |

|--------|----------------------------------------------------|

| MOSFET | Metal-Oxide Semiconductor Field-Effect Transistor  |

| MPI    | Message Passing Interface                          |

| MPSoC  | Multi-Processor System-on-Chip                     |

|        | · · ·                                              |

| MRAM   | Magneto-resistive Random Access Memory             |

| MSCP   | Master System Control Processor                    |

| MTBF   | Mean Time Between Failures                         |

| NASA   | National Aeronautics and Space Administration      |

| NETS   | Nano-satellite Environment Test Standardization    |

| NVP    | N Version Programming                              |

| OBC    | On-Board Computer                                  |

| РСВ    | Printed Circuit Board                              |

| PLB    | Processor Local Bus                                |

| PNST   | Post-graduate study on Nano-Satellite Technologies |

| RAM    | Random Access Memory                               |

| RAAN   | Right Ascension of Ascending Node                  |

| RB     | Recovery Block                                     |

| RISC   | Reduced Instruction Set Architecture               |

| RM     | Reconfigurable Module                              |

| RP     | Reconfigurable Partition                           |

| RS232  | Recommended Standard 232                           |

| RS422  | Recommended Standard 422                           |

| SAA    | South Atlantic Anomaly                             |

| SBU    | Single Bit Upset                                   |

| SDK    | Software Development Kit                           |

| SECDED | Single Error Correction Double Error Detection     |

| SEB    | Single Event Burnout                               |

| SEE    | Single Event Effect                                |

| SEFI   | Single Event Function Interrupt                    |

| SEGR   | Single Event Gate Rupture                          |

| SEL    | Single Event Latch-up                              |

|        |                                                    |

| SET    | Single Event Transient                                  |

|--------|---------------------------------------------------------|

| SEnT   | Space Environment Testing                               |

| SEU    | Single Event Upset                                      |

| SFT    | Software Fault Tolerance                                |

| SIHFT  | Software Implemented Hardware Fault Tolerance           |

| SMC    | Space and Missile systems Center standard               |

| SoC    | System on Chip                                          |

| SOI    | Silicon On Insulator                                    |

| SPI    | Serial Peripheral Interface                             |

| SPSoC  | Single Processor System-on-Chip                         |

| SRAM   | Static Read Access Memory                               |

| TARRI  | Takasaki Advanced Radiation Research Institute - (JAEA) |

| TID    | Total Ionizing Dose                                     |

| ТММ    | Thermal Mathematical Model                              |

| ТО     | Triple Oxide                                            |

| TMR    | Triple Modular Redundancy                               |

| TRL    | Technology Readiness Level                              |

| TT&C   | Telemetry, Tracking and Command                         |

| UART   | Universal Asynchronous Receiver and Transmitter         |

| UNOOSA | United Nations Office for Outer Space Affairs           |

| USB    | Universal Serial Bus                                    |

| WDT    | Watch Dog Timer                                         |

| XPS    | Xilinx Platform Studio                                  |

ore than 50 years passed since the launching of the first satellite into space [1]. Sputnik-1 carried a simple communication system which was used to send a beep to its ground station. The launching of the first artificial satellite marked the start of a new age. Humans started looking upward to the open skies and forward to the unlimited opportunities form them. Since that event the space age and the embarkation of the space technology had profoundly progressed and advanced concepts as well as applications were introduced [2] [3].

At the early beginnings, space was mostly a scope for contribution by a small number of countries. The technology of building satellites and launchers was a sort of a national security issue. Only several countries were able to fully build, launch and operate their own satellites. The space technology has always used to be an expensive and complicated field. Even after more than 50 years of starting the space age, we still cannot find so many countries that can afford the cost and/or the knowledge for starting a real full-cycle, from launch to operation, space industry [3].

The space race led to unleashing different applications and services that can be provided from the space-borne devices. Satellites are just one form of the devices that can be launched to space. Other devices include space probes, telescopes, and even manned space stations [4]. The applications, scientific achievements, and spin-offs that emerged from using space-borne devices and stations were tremendous and well sounded [5] [6]. Nowadays, the world enjoys real time telecommunication across the globe, earth observation constellations for disaster monitoring and resources exploration, homeland security services, terrestrial and flight navigation, high speed satellite-based internet links and media broadcasting services. These applications were used to be provided by large scale, heavy and high power satellites. However, advances in microelectronics technologies and material engineering enabled the developing of smaller and lighter satellites to provide the same services with even better efficiencies [7] [8] [9] [10]. Even the reuse of technologies developed for other space activities, such as human spaceflight systems, was investigated to develop cost effective small satellites [11].

The advancement in building satellites was associated with a paradigm shift. It was a fact that till the end of the nineties of the previous millennium, satellites and spaceborne devices were used to be developed by space agencies and organizations. The facilities needed in developing, assembling, integrating and testing the space-borne devices had to meet sophisticated requirements. The technical knowledge, as well, was not available outside of these organizations. However, these conditions prevailed until the launching of university-made satellites in the eighties, such as the UoSAT-1 in 1981 [12]. Since then, a new start was remarked through a paradigm shift in the traditional concepts used in building satellites by universities.

The key point that enabled the universities to indulge in the space activities was the use of Commercial-Of-The-Shelf (COTS) components. COTS enabled building low cost satellites while maintaining reliability through design techniques. Nowadays, there are multiples of satellites that were successfully developed by universities and are already rotating in space. Universities helped in developing new techniques to shrink the satellites sizes and make them much more efficient.

International organizations and space agencies became interested in what universities were doing and offered to sponsor their programs. A remarkable example is the Basic Space Technology Initiative (BSTI) that was initiated by the United Nations Office for Outer Space Affairs (UNOOSA). The BSTI is focusing on providing space engineering education especially for developing countries which cannot afford the costs of such an expensive industry. It has a goal of defining a space engineering curriculum that can be used as a guide by academic institutes all over the world to provide standardized space engineering degrees. The BSTI also inaugurated, in collaboration with Kyushu Institute of Technology at Japan, a space education program named the Doctorate in Nano-Satellite Technologies (DNST). The program aims at hosting students from the developing countries and granting them the doctorate degree upon pursuing research in the space engineering field. The program was later promoted to handle master students as well and its name was changed to the Post-graduate study on Nano-Satellite Technologies (PNST). By the intake of 2013, 9 participants from 8 countries are already attending the program and more students would participate in the coming years as it gains more international recognition.

My research is part of the DNST program. I belong to the first batch of the students who were accepted in 2010. In the next few sections, I would discuss the outline of the research and its expected impacts. It might be necessary to point out that the major purpose of this research is to develop and qualify a low cost, high performance, high reliability, and low power on-board computer for in-orbit processing of scientific data and commands. This on-board computer would be used in developing state-of-art small spacecraft technology for future space missions by using Field Programmable Gate Arrays (FPGAs). It would start a new era in developing dynamically reconfigurable space systems to maintain the power requirements and adapt to the space environment conditions.

The research was conducted at the premises of the Kyushu Institute of Technology. Testing was conducted at CeNT, Takasaki Advanced Radiation Research Institute (TARRI) – Japan Atomic Energy Agency (JAEA), and Kyoto University Research Reactor Institute (KURRI). The results of the research recommend the developed onboard computer for in-orbit validation in a technology demonstration mission.

### **1.1 Research Outline**

The challenge in developing small satellites is mainly concerned with keeping the satellite size and mass as minimum as possible. We should take into consideration developing satellites with an area-to-mass (A/M) ratio that would enable re-entrance to the earth atmosphere in less than 25 years. The area-to-mass ratio increment enables more drag force and hence better satellite deorbiting to reduce the problem of space debris. However, minimizing the subsystems mass, area, size and power consumption needs innovative technologies to be applied when developing the satellite subsystems. The density of the material used in developing the subsystem structure as well as the subsystem components have to be carefully selected. The reduction in the subsystem mass would affect the whole satellite. Another aspect is to reduce the power consumed by each of the satellite subsystems to reduce the surface area, and hence the mass, of the solar panels and the sizing of the batteries. This requires using innovative semiconductor manufacturing technologies and lower transistor feature sizes for the electronic components to reduce their static and dynamic power consumptions.

On the other hand reliability is a big concern for all satellite developers. Design techniques as well as subsystems' components should be carefully selected in order to develop high reliability satellites that can serve for the required mission lifetime. The design techniques usually depend on redundancies whether cold or hot backups. The components are better to be selected from the space approved category that has flown on-board previous space missions. The space approved category might include space grade and non-space grade components. Space grade components are usually of low performance compared to COTS components. Depending on the mission requirements, the reliability threshold through the mission lifetime is set. Using redundancies in hot backup regime requires higher power consumption. Therefore, it is always important to design the reliability carefully to match with the power budget as well as the mass budget and size of the satellite.

We need to strike a balance between the reliability, power consumption, mass, size and performance of the space mission. The required balance needs innovative design solutions in order not to sacrifice any of the aforementioned parameters. To achieve this balance, design of digital electronic circuits should make use of three aspects: 1) Advancement in the semiconductor industry through the reduced transistor feature size, 2) Re-programmability of digital designs, 3) On-the-Fly DPR.

Moore's law suggested that the number of transistors in a chip would double every two years. The duplication of the transistors count means that their feature size would reduce in almost the same proportion. Nowadays we have FPGAs and Application Specific Integrated Circuits (ASIC) at the 28 nm scale. Chip manufacturers are working on 7 nm designs. This nano-meter scale enables high density designs to be developed. However, it sets a challenge to reduce the power consumption and the radiation immunity of the overall design. Miniaturization of satellite subsystems should be achieved through using the available nano-meter scale feature size technology. Power consumption, both dynamic and static, are reduced through applying manufacturing and design techniques. Immunity to space radiation is enhanced through fault tolerance and shielding techniques. Reducing the power consumption would reduce the operating temperature of the electronic chips which would enable them to withstand higher thermal conditions while operating in space.

Digital designs of satellite subsystems are usually implemented using components that cannot be changed after launching the satellites. The designs are fixed and whether they contain a fault or not should be fully investigated before launching. Some designs might contain a mistake that is not apparent during ground tests and might cause mission failures. Correcting the design mistakes of digital designs inorbit used to be an impossible task. The most effort that can be done is to reprogram the code in case an unwanted software performance was noticed. This can be done only if the satellite has the feature to reprogram its code. A major advancement in digital designs that appeared in the last decade is to reprogram the hardware. Reprogramming the hardware can be either by loading alternative design modules from an on-board local memory or uploading new designs from the ground stations. Design diversity concept can thus be achieved in a much smaller area, size and mass. However, the re-programmability feature is applicable only through using Static Random Access Memory (SRAM)-based FPGAs. This type of the FPGAs has its own merits and demerits. The major merit is providing re-programmability. While the major demerit is susceptibility to design alteration while operating in space due to Single Event Upset (SEU) induced errors from the space environment radiation.

DPR is a new technique that is introduced by SRAM-based FPGA manufacturers to overcome the problem of switching off the logic whenever a reconfiguration of the FPGA is needed. The technique depends on making part of the logic as static while defining Reconfigurable Partitions (RP) that can hold different Reconfiguration Modules (RM). Whenever a reconfiguration is needed for one of the RPs with any of its associated RMs, the static logic would reload the RP from the external flash memory that holds the RMs hardware designs in the form of partial bitstreams. This technique enables loading and unloading of digital designs when needed thus it can be used to save the power consumption of the satellite. As a matter of fact, not all of the satellite subsystems need all of their components for 100% of the operation time. Some components might be switched off until they are needed to parform a specific function. Switching off using the DPR technique means simply to load a Black Box (BB) design in the RP.

DPR can also be used in developing adaptive subsystems. Adaptation can take place in response to the changes in the space environment, power and thermal operating conditions. For example loading extra redundant modules could be done to provide

higher reliability in case of increased induced soft errors due to radiation. Also, unloading some of the design modules when they are not needed in the current operations might be done to save the power consumption especially if the batteries are on the critical storage limits. The thermal conditions in the sunlight and eclipse regions of the orbit vary drastically. Some modules might be unloaded to reduce the heat emissions while in the sunlight region. Heavy processing designs might defer their processing to the eclipse region by loading the processing modules there. Thus heat emissions might not introduce a problem to the operating temperature of the FPGA and other components in the satellite. This technique provides an adaptive protection through partial reconfiguration. Another approach is to use the DPR to correct the errors in the bitstream frames of the hardware in the FPGA configuration memory. As the satellite operates in space its SRAM-based FPGAs are subjected to soft errors induced through charge accumulation at the memory cells (circuit) nodes. The charge accumulation, if it crosses a certain limit, will flip the logic values stored in the internal SRAM cells of the FPGA which is known as the local configuration memory. The internal SRAM holds the design in the form of binary bitstream and if any bit is corrupted then that might lead to serious design failure issues. Therefore DPR can be used to continuously correct the induced flips through scrubbing in a read-correct-write back process.

If we consider the three illustrated aspects mentioned above, we would recommend SRAM-based FPGAs as a suitable candidate to achieve the required balance between the satellite reliability, power consumption, mass, size and performance. However there still another major issue which is the cost. If we consider space grade SRAM-based FPGAs then it would be very expensive to develop satellites at moderate budgets up to 5 M USD. However, if we use commercial grade then the cost would be reduced ultimately. In fact the price of a space grade component is about 100 times the price of the commercial grade one. Reducing the cost is a great benefit but there is not enough data about the suitability of these components when used in space. Especially if the components are of latest generations which did not fly yet on many space missions thus not enough information about their performance in space is available. Therefore, we need to provide a qualification method for such components that would reveal their suitability and provide sufficient data as well as establishes the mitigation techniques to make them fitting for space missions.

The main theme of the research is to investigate the suitability of using COTS SRAM FPGAs of the 65 nm scale in developing miniaturized High Performance Embedded Computers (HPECs). The direct application of the research is to develop an OBC suitable for small and nano-satellites. Qualification is an essential part of the research as we need to highlight the mitigation techniques needed to support COTS SRAM-based FPGAs while operating in space. In the research we investigated the concept of fault injection to simulate space radiation. Radiation testing and mitigation against soft error through DPR as well as thermal vacuum testing and mitigation through passive and active techniques were thoroughly studied. The research focuses on presenting practical achievements besides theoretical bases. Studying mitigation techniques for space-based applications needs real developments and qualifications to assess their suitability. Therefore, Space Environment Testing (SEnT) was a fundamental constituent in the researched topics. We focused on the development followed by real qualification through SEnT. Qualification is the most crucial aspect in developing working space systems and proving the validity of new concepts and technologies. This research is trying to start a new epoch in using SRAM-based FPGAs to strike the needed balance between cost, reliability, power consumption and performance in addition to flexibility in reprogramming the whole system. Some designs might require ultimate reduction in its power consumption hence reducing its total thermal power while not sacrificing its reliability. That feature was thoroughly studied in the research by investigating the time and space redundancy trade-offs when developing MPSoC and Single Processor System-on-Chip (SPSoC) using 65 nm FPGAs.

Usually satellites cannot be restored after launching. However, in some rare cases, it might be necessary to restore a satellite from its orbit for repair purposes. Nevertheless, such missions are very specific, expensive and not regular and are only performed for very peculiar reasons such as repairing a military satellite or a space telescope. Therefore, as a general rule, satellites should be fully qualified in a thorough approach as much as possible. SEnT is the real manifestation of suitability of designs to operate in space. SEnT is the main feature and differentiator of this research from other designs which are solely validated and approved through simulations.

### **1.2 Research Motivation**

Developing space qualified low cost satellites while maintaining high performance and reliability is the main motivation of this research. Both the academia and industry are welling to achieve good results on this way. Universities and research institutes are developing new missions to help better understanding the space environment and its possible effects on space missions whether manned or unmanned. Innovative profit generating missions are being offered by space companies around the world. Developers of small satellites are struggling to make the systems smaller and better. In addition to that, some countries, especially developing countries, are welling to start making use of space for the benefit of their welfare. We wish to provide accessibility to these countries through low cost and clean technology. As miniaturizing the satellite subsystems would reduce the required number of components to be manufactured and hence reduce the emissions that accompany any manufacturing process. This means we are trying to provide access to space while supporting the concept of green technology on Earth.

Through this research we are providing a platform for In-orbit processing of the huge amounts of scientific data which is collected on-board. This would ultimately reduce the communication link bandwidths and required power on-board the satellites. This powerful processing platform is a true demonstration of the HPEC concept using COTS in space. It would enable future mission to develop further applications using the concept of evolutionary hardware. The hardware that can cure and repair itself from malfunctions while in operation in its orbit. That concept would have multitude of applications in space as well as in other fields such as robotics and medical equipment. Giving the satellites high processing capabilities while being protected against the space environment would certainly boost the research towards developing silicon brains that would enable building autonomous satellites that can take full control on the mission with minimum or no human interaction.

### **1.3 Research Objectives**

In designing devices that would operate in space, we usually have to design the devices from one of two perspectives: 1) Either we design the device to avoid the space environment induced effects, or 2) we design the device to tolerate the space

environment induced effects. The difference between avoidance and tolerance is the type of the used components and their manufacturing grade. Space grade components provide good protection against radiation induced Single Event Effects (SEE), Total Ionizing Doses (TID), and Displacement Damage Doses (DDD). Also their operating temperature range can withstand the thermal vacuum conditions in space. However, our research mainly aims at providing protection to COTS components through applying design mitigation techniques instead of using space grade ones.

The following points would summarize the main objectives of the research:

- Design a well-protected platform that would be used as a HPEC for OBC applications.

- Fully develop the system and qualify its operation and mitigation techniques in SEnT conditions.

- Use the state-of-art low cost reprogrammable COTS SRAM-based FPGAs to provide maximum performance and flexibility.

- Thorough investigation of the best techniques to mitigate the system against radiation induced transient faults as well as provisioned permanent failures.

- Thorough investigation of the best techniques to mitigate the system against the thermal vacuum conditions.

- Start a new epoch in using 65 nm COTS SRAM-based FPGAs, instead of the expensive anti-fused and space grade variants, in developing reliable high performance space devices and subsystems through mitigating all possible space environment effects on their operation.

- Make use of the compactness and re-programmability features of SRAM-based FPGAs in developing miniaturized and flexible systems as well as facilitate the way to develop future satellite-on-chips.

- Investigate the best fault tolerant approach from time and space redundancies to be applied on 65 nm COTS SRAM-based FPGAs.

- Fully characterize the suitability of using 65 nm COTS SRAM-based FPGAs in space applications by revealing the SEnT data.

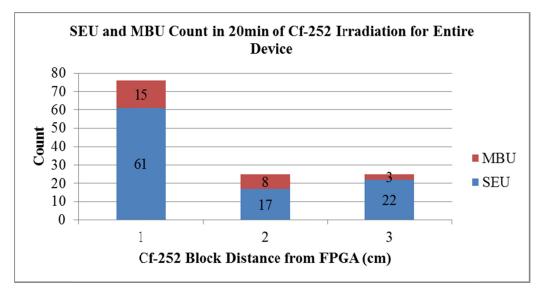

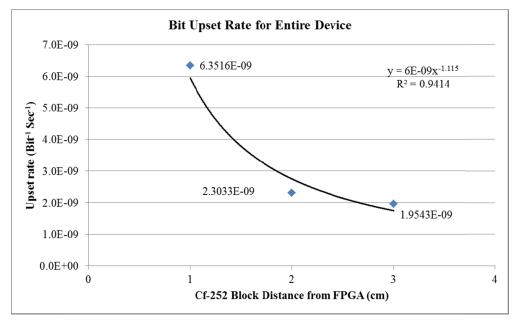

- Investigate the different methods in performing SEnT and the pros and cons of each method in order to provide testing guidelines and procedures to efficiently reduce the test costs and complexity while maintaining the test quality i.e. radiation test with Californium-252 or accelerated proton beam or fault injection.

### **1.4 Research Methodology**

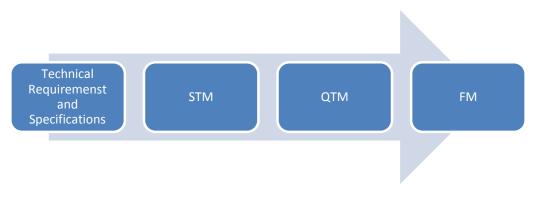

The applied methodology started by thoroughly investigating and studying the theoretical concepts of fault tolerance and modern digital design approaches. The theoretical study was followed by real development and qualification through performing SEnT on the system. Qualification through SEnT is considered as a mandatory step to prove that the design can really work in space. SEnT results were used to practically demonstrate the design operability and suitability for space missions as well as the applicability of the design concepts.

FPGAs provide the capabilities to develop high speed digital designs. Nowadays, computer design packages can be used in designing complete multi-processor embedded systems inside FPGAs. Simulating functional tests as well as developing software is also available through hardware/software integrated simulators and software development environments. The complete MPSoC design and simulation was performed using Computer Aided Design (CAD) tools.

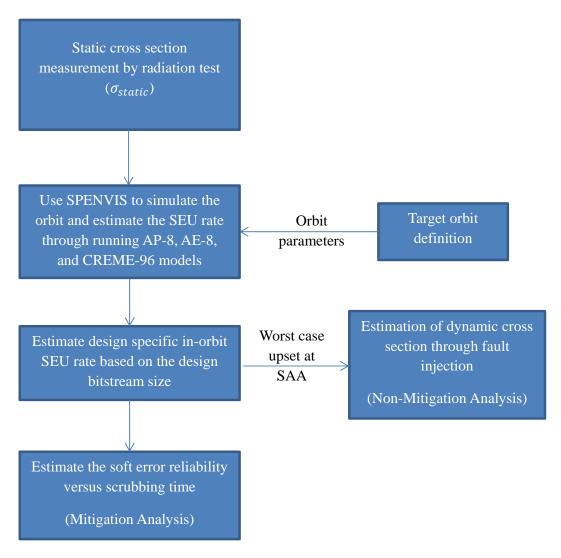

The research methodology proceeded according to the following steps:

- 1) Study of the different time and space redundancy approaches in fault tolerance design.

- 2) Study of hardware fault tolerance mitigation techniques for SRAM-based FPGAs.

- 3) Developing the mitigated hardware of a SPSoC to demonstrate time redundancy.

- 4) Developing the mitigated hardware of an MPSoC to demonstrate space redundancy.

- 5) Developing the software application that would be used in running the hardware during the tests as well as managing the fault tolerant features in the designs.

- 6) Comparison between both the SPSoC and the MPSoC to select the best fault tolerance approach based on power consumption, computation throughput, area utilization, reliability and heat emission.

- Performing radiation tests under proton accelerated beam at the nuclear reactor to estimate the static cross section.

- 8) Specifying a target operation orbit for the system and using that orbit to estimate the charged particles energy spectrum and flux of the protons, electrons and

heavy ions. The SEU rate would be estimated using the static cross section and the charged particles spectrum through space radiation models.

- 9) Developing a fault injection bench to flexibly estimate the dynamic cross section of the system at any time and under any changes of the design without having to repeat the expensive radiation shots.

- 10) Performing fault injection tests to assess the mitigation against radiation induced soft errors.

- 11) Analysis of the system reliability in accordance to radiation induced soft errors.

- 12) Studying thermal vacuum mitigation techniques through active control via Dynamic Temperature Management (DTM) as well as passive control through heat sinks.

- 13) Performing thermal vacuum analysis of the system and running thermal vacuum tests with and without the mitigation techniques to assess their suitability.

- 14) Generalizing the research results to be used as concepts in different design approaches.

- 15) Results dissemination.

### **1.5 Research Originality and Contributions**

The following points summarize the major research contributions and originalities:

- Developing and qualifying a reprogrammable MPSoC using 4 embedded systems in an SRAM-based FPGA with up to 400 MIPS and power consumption of max 5 Watt, soft error reliability 99.99%, mass about 200 gm and ultra-low cost (<2000 USD). The OBC cost can be considered as about 10 % of the total mission cost as estimated in [13]. Therefore our cost reduction would contribute to about 10% of the total budget. However, if our design is used in the payload computer system then we would contribute to more reduction in the total budget as the payload forms about 21% of the mission cost. The more use of our design in other system bus subsystems, the more cost reduction we would achieve compared to the use of the space approved subsystems.

- 2) Using a novel technique for estimating the static cross section during radiation tests through internal scrubbing of the FPGA configuration memory instead of using the traditional external monitoring and configuration module.

- 3) Developing a fault injection bench for flexibility of estimating dynamic cross section in the lab through fault injections to the configuration memory bitstream.

- 4) Applying thermal mitigation through DTM of FPGA operating temperature through controlling the operating frequency and reconfiguring the operating hardware.

- 5) Clarifying the procedural details of space environment testing, radiation and thermal-vacuum, and publishing the results for the class of 65 nm SRAM-based FPGAs.

- 6) Clarifying the analytical details of reliability estimation procedure for induced soft errors based on the static cross section and target orbit.

- Comparative study between suitability of time and space redundancies in developing embedded processor systems on 65 nm FPGAs.

- One of the research publications was cited at NASA's Small Spacecraft Technology. State of Art Report – 2014 [14].

### **1.6 Thesis Overview**

Chapter 1 is the introduction where the research objectives and detailed problem definition are investigated as well as presenting the research contributions and originalities.

Chapter 2 presents the background related to the space environment and possible mitigation techniques of the radiation effects. It overviews the FPGA technology and refers to detailed textbooks and references for the interested reader to grasp the full detailed picture from the rich available literature. It covers the previous work as much as possible, although not exhaustive, to present the trends in developing fault tolerant and new concept OBCs.

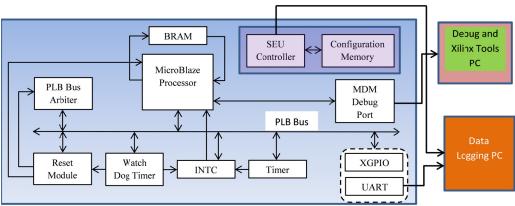

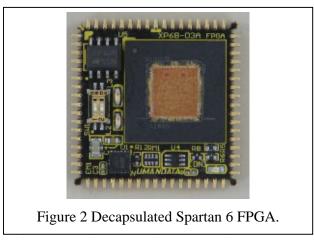

Chapter 3 presents the details of the MPSoC design and operation concept as well as the fault tolerance features applied for mitigation against the induced soft errors. It discusses the operation of the different blocks and the concept of network-on-chip communication through mailboxes to achieve cross-voting through the score-card concept.

Chapter 4 presents the comparison between space and time redundancy in 65 nm SRAM-based FPGAs to select the best technique in terms of power consumption,

resources utilization, performance and reliability. The analytical approach for estimating the soft error reliability due to induced SEUs bit flips in the configuration bitstream of the FPGA is described.

Chapter 5 presents the experimental radiation test procedure at the Takasaki nuclear reactor. The analytical estimation of the system reliability based on the configuration memory scrubbing rate and the expected SEU rates is presented.

Chapter 6 presents the experimental thermal vacuum test procedure at CeNT. The thermal analysis model and the test procedure as well as the mitigation techniques are presented.

Chapter 7 presents the results of evaluating the design performance and discusses the research contribution in developing a well mitigated MPSoC based on the results from the SEnT.

Chapter 8 presents the conclusion and future work. It discusses the idea of satelliteon-chip and its feasibility for developing future high performance and ultra-compact space missions. We call that concept the ultra-space in a reference to currently available ultra-low-size computers.

atellites are subjected to the harsh space environment conditions in their orbits. In this chapter we provide an overview about the radiation threats which affect the satellite electronics including the OBC. We focus on the radiation threats as they are of a probabilistic nature and a system cannot be 100% guaranteed to be radiation-hardened unless it would have been designed using spacegrade components which provide radiation hardening by manufacturing. On contrary to radiation threats, thermal threats are controllable and are well determined so that their effects can be fully mitigated and verified in the design and test phases before the actual in-orbit operation. We illustrate the major functions of the OBC within the satellite to provide a sufficient background about the nature of the tasks which it handles. Fault mitigation is discussed to understand the different approaches for developing a design that can survive radiation-induced faults. As SRAM-based FPGA is used in developing the MPSoC-OBC, a simple background about its building blocks and logic components are illustrated. Previous work for developing fault tolerant OBC designs using SRAM-based FPGAs are presented. The state-of-art for small spacecraft's OBCs in comparison to our design is discussed.

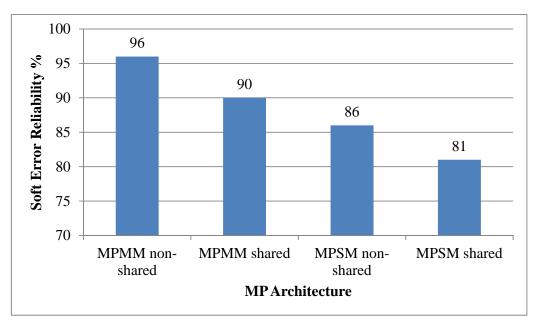

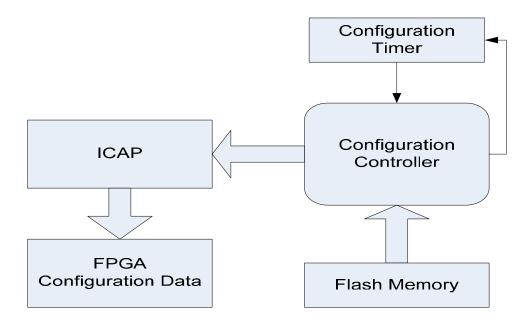

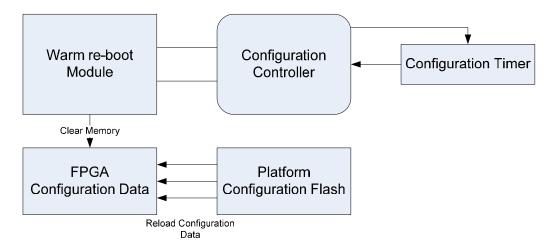

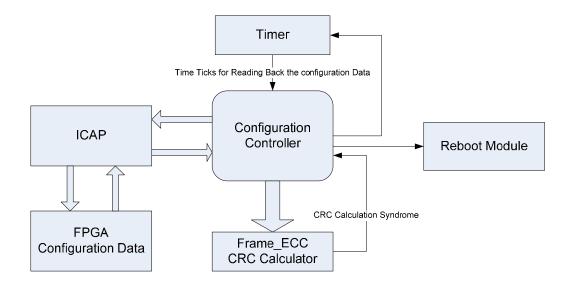

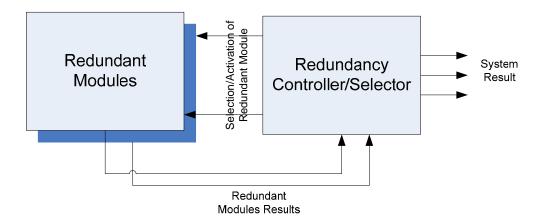

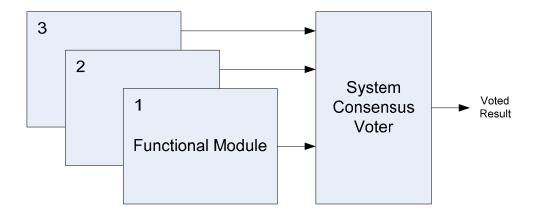

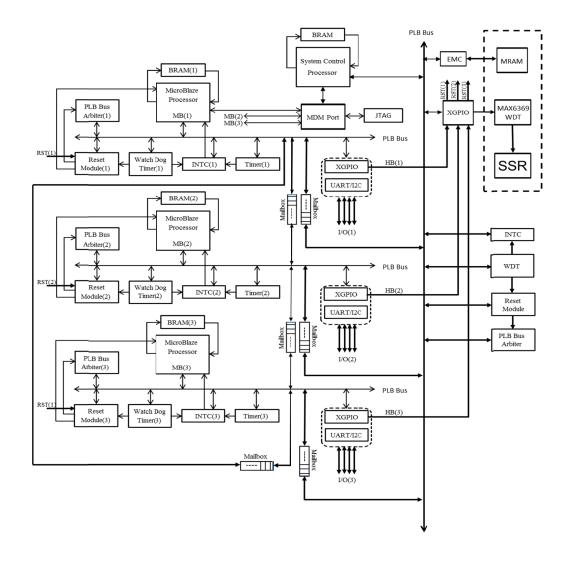

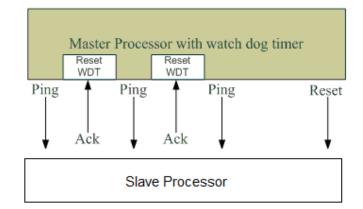

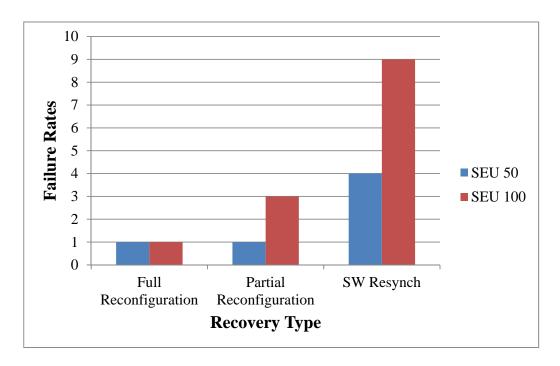

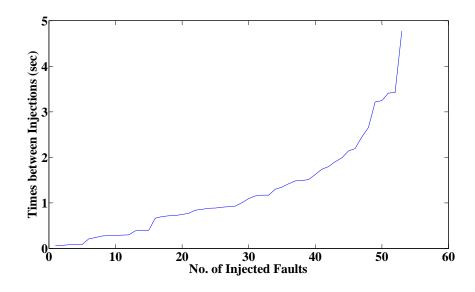

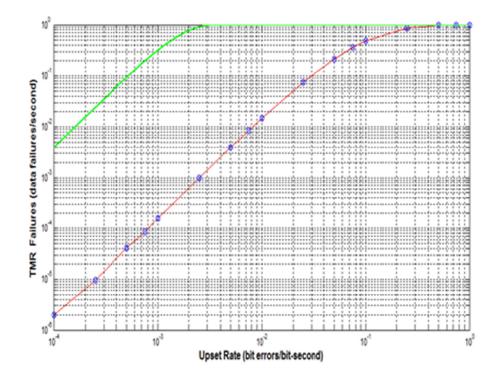

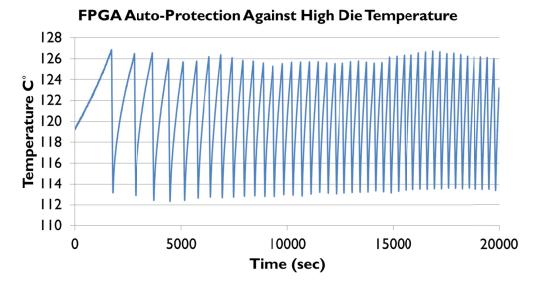

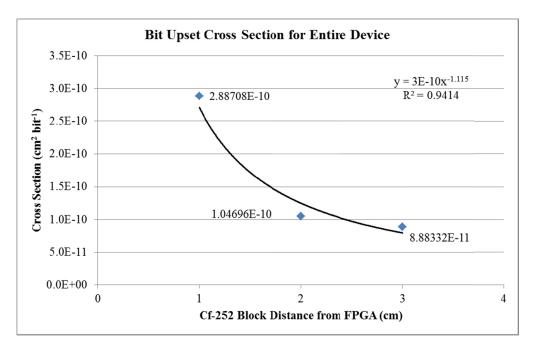

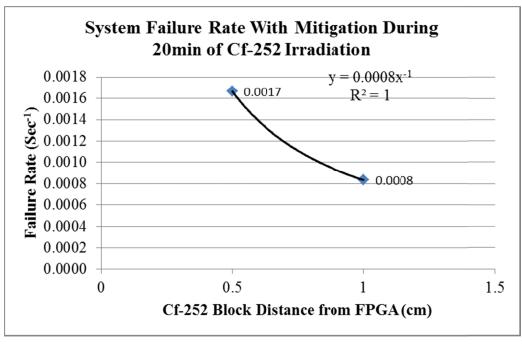

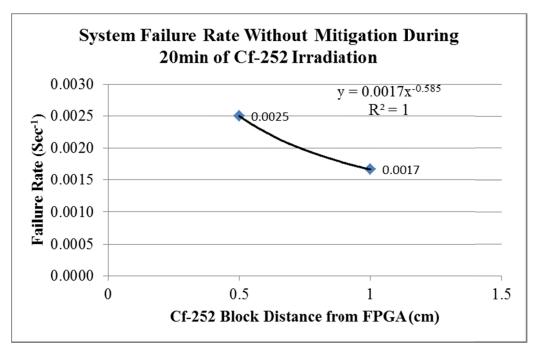

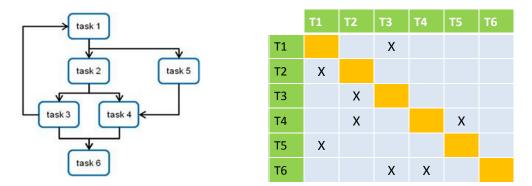

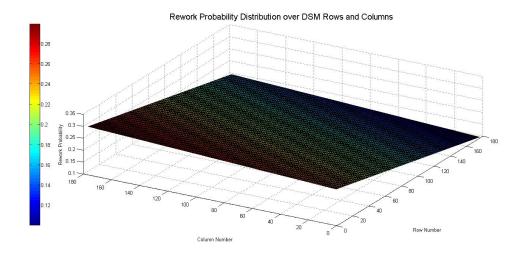

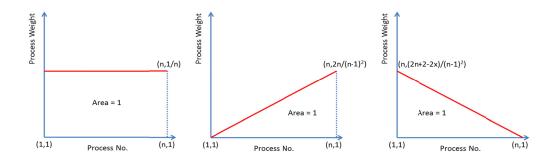

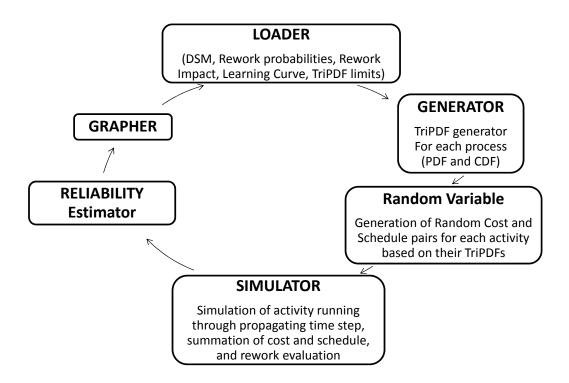

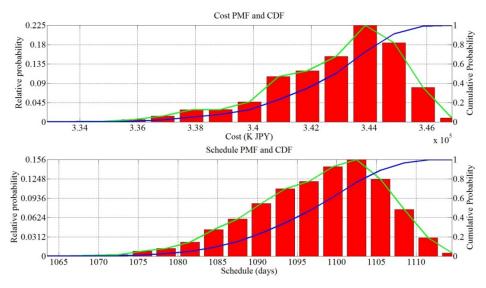

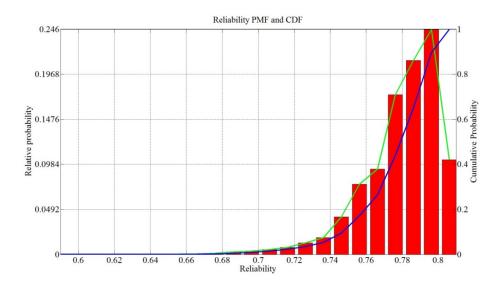

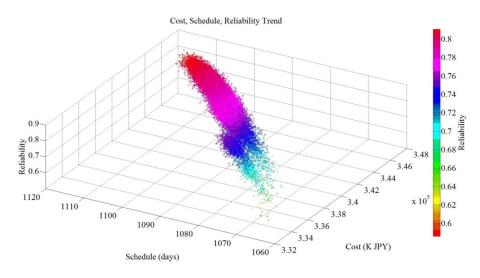

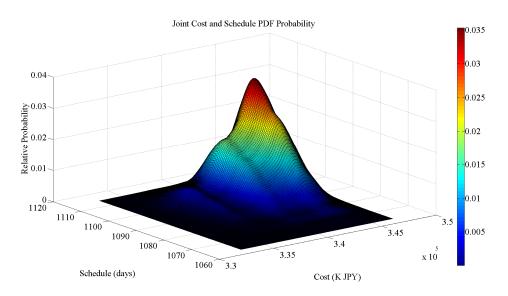

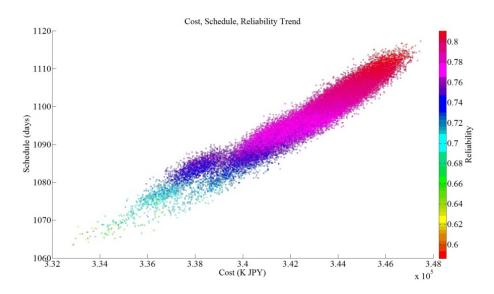

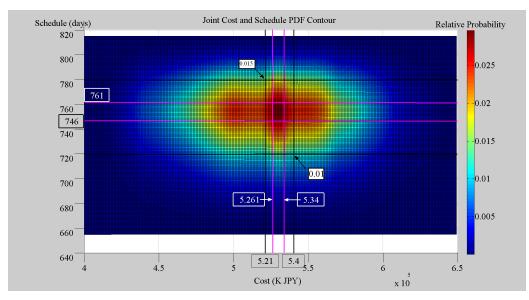

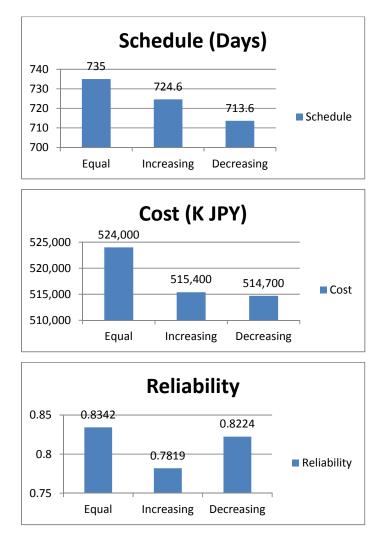

## 2.1 Space Environment