# UNIVERSITÁ DI ROMA "TOR VERGATA"

### FACOLTÁ DI INGEGNERIA

DIPARTIMENTO DI INFORMATICA, SISTEMI e PRODUZIONE

### PHD THESIS

to obtain the title of

### PhD of Science

Specialty: Computer Science

# Satisfying hard real-time constraints using COTS components

Defended by

Emiliano Betti

Course: XXII

A.A. 2009/2010

Thesis Advisor

Dott. Marco CESATI

Coordinator

Prof. Daniel P. BOVET

### Acknowledgments

It is a pleasure to thank those who have made this thesis possible and helped me during my PhD program.

I gratefully thank Marco Cesati, who always guided me since 2003, starting with my Bachelor thesis, and then through my Master's, and now my PhD. His guidance and support drastically impacted the development of my knowledge, notably improving the results I could obtain during my studies.

I also would like to thank Daniel P. Bovet for his precious advice and supervision, and Roberto Gioiosa, whose encouragement and support made a big difference to me. Along with them, I gratefully acknowledge all the other members of the System Programming Research Group at the University of Rome "Tor Vergata", with whom working has been a real pleasure.

Last, but not least, many sincere thanks go to Marco Caccamo and all the members of the "Networked Real Time and Embedded Systems Laboratory" at the University of Illinois at Urbana-Champaign, where I worked over the past two years. Most of this work could not have been done without their knowledge, support, and experience. In particular, I would like to thank Lui Sha, Rodolfo Pellizzoni, Stanley Bak, Bach Dui Bui, and Gang Yao.

# Satisfying hard real-time constraints using COTS components

Real-time embedded systems are increasingly being built using Commercial Off-The-Shelf (COTS) components such as mass-produced peripherals and buses to reduce costs, time-to-market, and increase performance. Unfortunately, COTS hardware and operating systems are typically designed to optimize average performance, instead of determinism, predictability, and reliability, hence their employment in high criticality real-time systems is still a daunting task.

In this thesis, we addressed some of the most important sources of unpredictability which must be removed in order to integrate COTS hardware and software into hard real-time systems. We first developed ASMP-LINUX, a variant of Linux, capable of minimizing both operating system overhead and latency. Next, we designed and implemented a new I/O management system, based on real-time bridges, a novel hardware component that provides temporal isolation on the COTS bus and removes the interference among I/O peripherals. A multi-flow real-time bridge has been also developed to address interperipheral interference, allowing predictable device sharing. Finally, we propose PREM, a new execution model for real-time systems which eliminates interference between peripherals and the CPU, as well as interference between a critical task and driver interrupts. For each of our solutions, we will describe in detail theory aspects, as well as prototype implementations and experimental measurements.

**Keywords:** real-time, COTS (Commercial Off-The-Shelf), operating system, Linux, computer architecture, scheduling, I/O drivers.

### Contents

| C  | onter         | ${ m nts}$                                             | $\mathbf{V}$ |

|----|---------------|--------------------------------------------------------|--------------|

| Li | st of         | Figures                                                | ix           |

| Li | st of         | Tables                                                 | xiii         |

| In | trod          | uction                                                 | 1            |

| 1  | $\mathbf{RT}$ | systems and COTS components                            | 5            |

|    | 1.1           | Real-time systems                                      | 5            |

|    |               | 1.1.1 Hard and soft real-time                          | 6            |

|    |               | 1.1.2 Periodic and event-driver real-time applications | 8            |

|    | 1.2           | Jitter and predictability                              | 10           |

|    | 1.3           | COTS components                                        | 11           |

|    |               | 1.3.1 COTS components' challenges                      | 12           |

|    | 1.4           | Operating system overhead and latency                  | 14           |

|    | 1.5           | Hardware jitter                                        | 17           |

|    | 1.6           | Proposed solutions                                     | 18           |

| 2  | AS            | MP-Linux                                               | 21           |

|    | 2.1           | Multiprocessor systems                                 | 23           |

|    | 2.2           | System partitioning                                    | 27           |

|    | 2.3           | Asymmetric multiprocessor kernels                      | 31           |

|    |               | 2.3.1 Other asymmetric systems                         | 33           |

|    | 2.4           | ASMP-LINUX implementation                              | 33           |

vi Contents

|   |     | 2.4.1 System partitions                       | 35  |

|---|-----|-----------------------------------------------|-----|

|   |     | 2.4.2 Process handling                        | 36  |

|   |     | 2.4.3 Interrupts handling                     | 38  |

|   |     | 2.4.4 Real-time inheritance                   | 41  |

|   |     | 2.4.5 ASMP-LINUX interface                    | 42  |

|   | 2.5 | Experimental data                             | 43  |

|   |     | 2.5.1 Experimental environments               | 44  |

|   |     | 2.5.2 Evaluating the OS overhead              | 48  |

|   |     | 2.5.3 Evaluating the operating system latency | 58  |

|   |     | 2.5.4 Final consideration                     | 65  |

| 3 | Rea | l-time bridge                                 | 67  |

|   | 3.1 | COTS I/O subsystems and real-time             | 68  |

|   | 3.2 | RT I/O Management System Design               | 70  |

|   | 3.3 | Enforcing real-time scheduling                | 71  |

|   | 3.4 | Reservation Controller                        | 76  |

|   |     | 3.4.1 Prototype Details                       | 78  |

|   | 3.5 | Real-time bridge                              | 80  |

|   |     | 3.5.1 Prototype Details                       | 80  |

|   | 3.6 | Architecture's limitations                    | 89  |

|   | 3.7 | Evaluation                                    | 91  |

|   |     | 3.7.1 Network performance and overhead test   | 94  |

|   | 3.8 | Related work                                  | 96  |

| 4 | Rea | l-time management of shared COTS peripherals  | 99  |

|   | 4.1 |                                               | 100 |

|   | 4.2 |                                               | 103 |

Contents vii

|    |       | 4.2.1  | Multi-flow real-time bridge software details | 105 |

|----|-------|--------|----------------------------------------------|-----|

|    | 4.3   | Evalu  | ation                                        | 110 |

|    |       | 4.3.1  | Interference within I/O peripherals          | 110 |

|    |       | 4.3.2  | Network performance                          | 114 |

| 5  | PR    | EM: P  | Redictable Execution Model                   | 117 |

|    | 5.1   | Introd | luction                                      | 118 |

|    | 5.2   | Relate | ed work                                      | 121 |

|    | 5.3   | System | m model                                      | 122 |

|    | 5.4   | Archit | tectural constraints and solutions           | 127 |

|    |       | 5.4.1  | Caching and prefetch                         | 128 |

|    |       | 5.4.2  | Interval length enforcement                  | 132 |

|    |       | 5.4.3  | Scheduling synchronization                   | 132 |

|    | 5.5   | Progra | amming model                                 | 133 |

|    | 5.6   | Evalu  | ation                                        | 136 |

|    |       | 5.6.1  | PREM hardware components                     | 137 |

|    |       | 5.6.2  | Software evaluation                          | 139 |

|    |       | 5.6.3  | Compiler evaluation                          | 140 |

|    |       | 5.6.4  | WCET experiments with synthetic tasks $\ .$  | 143 |

|    |       | 5.6.5  | System-wide coscheduling traces              | 147 |

| Co | onclu | isions |                                              | 151 |

| A  | Full  | expe   | riments data for ASMP-LINUX                  | 155 |

| Bi | bliog | graphy | •                                            | 163 |

# List of Figures

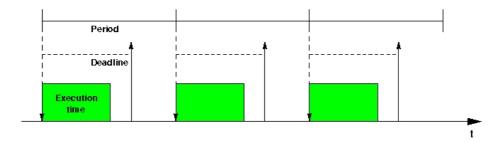

| 1.1  | A real-time periodic task                                 | 8  |

|------|-----------------------------------------------------------|----|

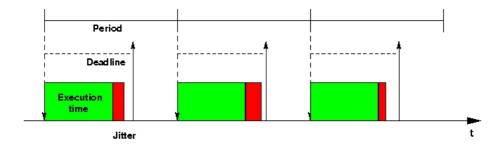

| 1.2  | An example of jitter in a real-time periodic task         | 10 |

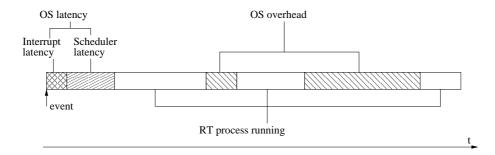

| 1.3  | Jitter                                                    | 15 |

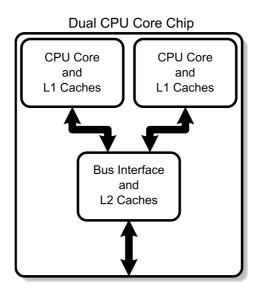

| 2.1  | An example of dual core processor with shared L2          |    |

|      | cache and bus interface [70]                              | 26 |

| 2.2  | Horizontally partitioned operating system                 | 29 |

| 2.3  | Vertically partitioned operating system                   | 30 |

| 2.4  | ASMP-LINUX partitioning                                   | 35 |

| 2.5  | A SMP using Intel IO-APIC                                 | 39 |

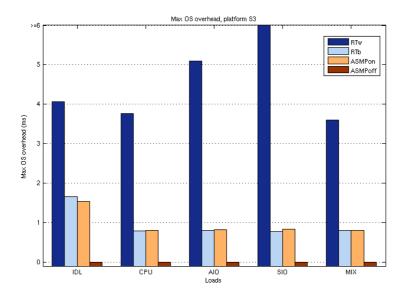

| 2.6  | OS maximum overhead comparison                            | 52 |

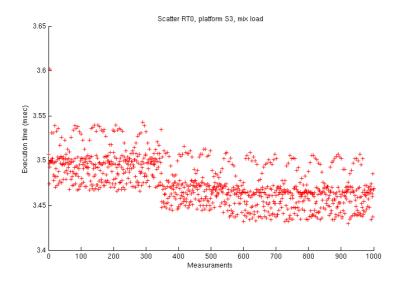

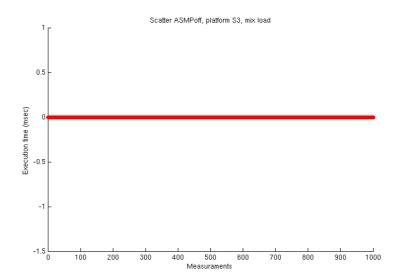

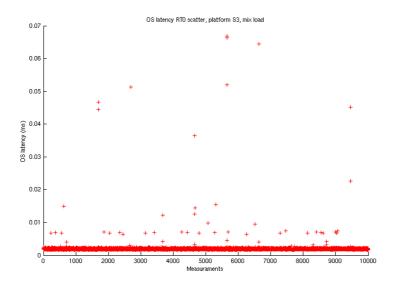

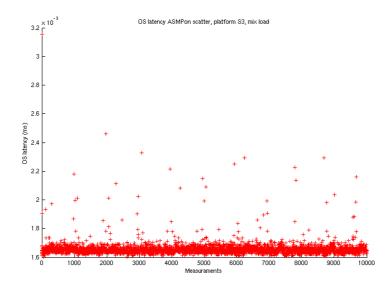

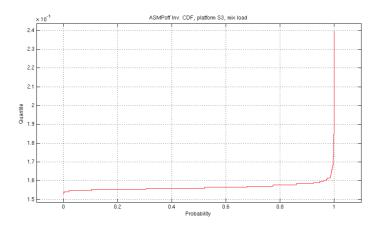

| 2.7  | Scatter $R_w$ graphic for system S3, MIX workload         | 53 |

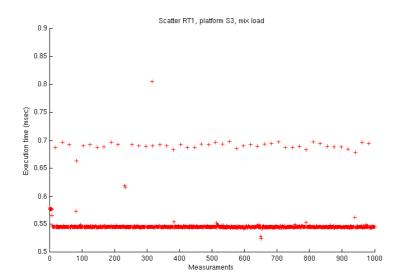

| 2.8  | Scatter $R_{\rm b}$ graphic for system S3, MIX workload   | 53 |

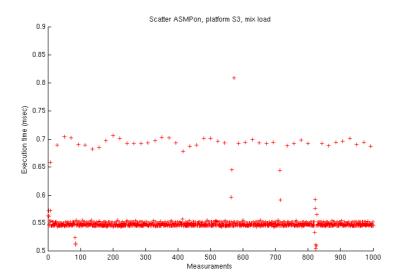

| 2.9  | Scatter $A_{on}$ graphic for system S3, MIX workload      | 54 |

| 2.10 | Scatter $A_{\rm off}$ graphic for system S3, MIX workload | 54 |

| 2.11 | Inverse density functions for overhead on system S3,      |    |

|      | MIX workload, configuration $R_w$                         | 56 |

| 2.12 | Inverse density functions for overhead on system S3,      |    |

|      | MIX workload, configuration $R_b$                         | 57 |

| 2.13 | Inverse density functions for overhead on system S3,      |    |

|      | MIX workload, configuration A <sub>on</sub>               | 57 |

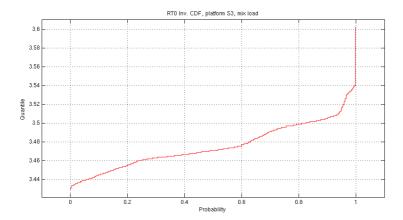

| 2.14 | Inverse density functions for overhead on system S3,      |    |

|      | MIX workload, configuration $A_{\rm off}$                 | 58 |

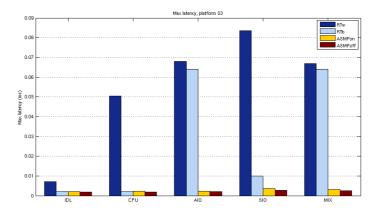

| 2.15 | OS maximum latency comparison                             | 61 |

| 2.16 | Scatter $R_{\rm w}$ graphics for system S3, MIX workload   | 62 |

|------|------------------------------------------------------------|----|

| 2.17 | Scatter $\rm R_b$ graphics for system S3, MIX workload     | 62 |

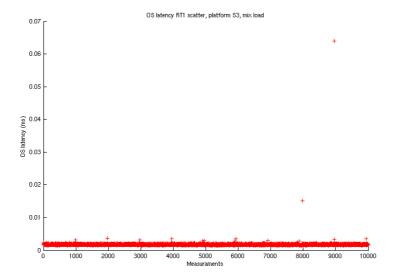

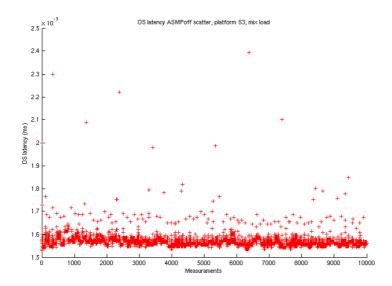

| 2.18 | Scatter $A_{\rm on}$ graphics for system S3, MIX workload  | 63 |

| 2.19 | Scatter $A_{\rm off}$ graphics for system S3, MIX workload | 63 |

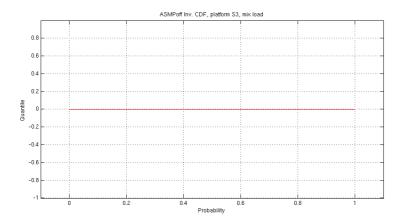

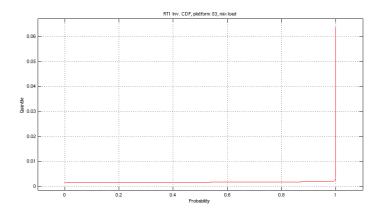

| 2.20 | Inverse density functions for latency on system S3,        |    |

|      | MIX workload, configuration $R_w$                          | 64 |

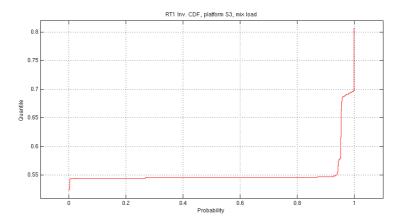

| 2.21 | Inverse density functions for latency on system S3,        |    |

|      | MIX workload, configuration $R_b. \dots \dots \dots$       | 65 |

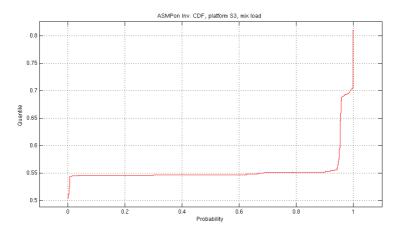

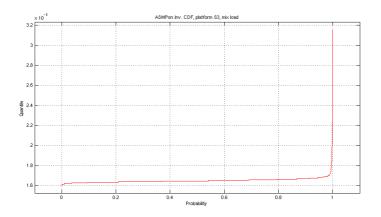

| 2.22 | Inverse density functions for latency on system S3,        |    |

|      | MIX workload, configuration $A_{on}$                       | 65 |

| 2.23 | Inverse density functions for latency on system S3,        |    |

|      | MIX workload, configuration $A_{\rm off}$                  | 66 |

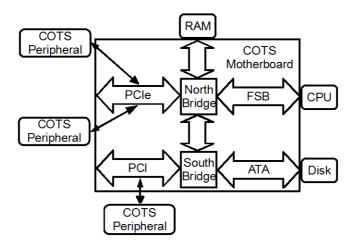

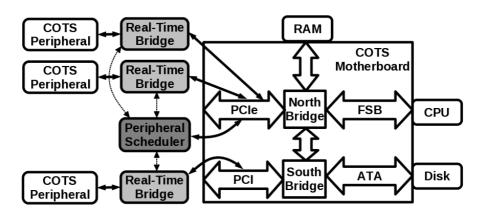

| 3.1  | A common COTS system architecture                          | 71 |

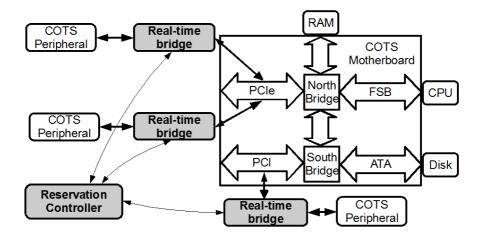

| 3.2  | The proposed real-time I/O management system adds          |    |

|      | a reservation controller and real-time bridge to the       |    |

|      | COTS-based node                                            | 72 |

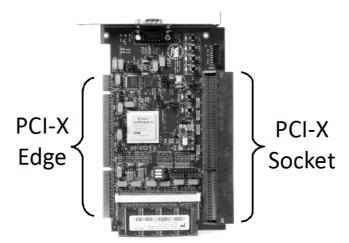

| 3.3  | Since the ML455 FPGA development platform con-             |    |

|      | tains both a PCI-X edge and a PCI-X socket, it can be      |    |

|      | interposed between a PCI-X peripheral and a PCI-X          |    |

|      | COTS bus and therefore function as a real-time bridge.     | 81 |

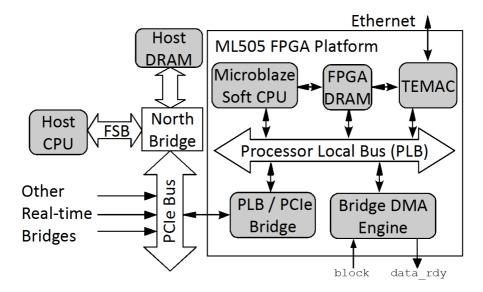

| 3.4  | Our real-time bridge prototype is a System-on-Chip         |    |

|      | implemented on the ML505 FPGA Evaluation Platform.         | 82 |

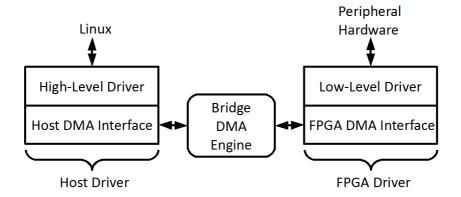

| 3.5  | The real-time bridge software architecture consists of     |    |

|      | a host driver and an FPGA driver                           | 85 |

| 3.6  | Real-time bridge evaluation testbed                        | 92 |

| 3.7 | The trace of a standard COTS I/O system reveals a          |     |

|-----|------------------------------------------------------------|-----|

|     | deadline miss if the tasks are released at a near-critical |     |

|     | instant.                                                   | 94  |

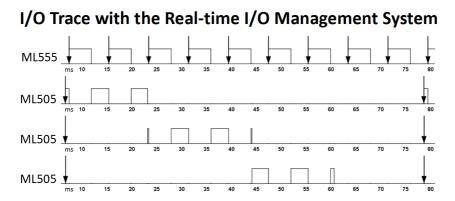

| 3.8 | The trace of the task set running with the real-time       |     |

|     | I/O management shows the system preventing dead-           |     |

|     | line misses by prioritizing traffic                        | 95  |

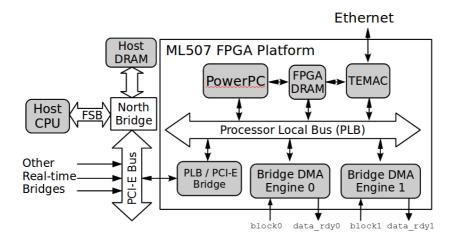

| 4.1 | Our multi-flow real-time bridge prototype is a System-     |     |

|     | on-Chip implemented on the ML507 FPGA Evalua-              |     |

|     | tion Platform. In this case only two real-time flows       |     |

|     | are supported, but more bridge DMA engines could           |     |

|     | be easily added                                            | 104 |

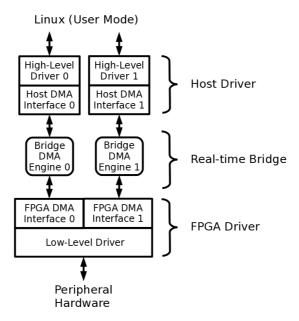

| 4.2 | Software architecture overview of a 2-flow real-time       |     |

|     | bridge                                                     | 106 |

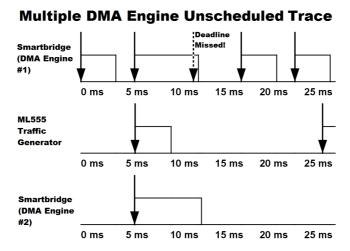

| 4.3 | The bus-access trace of a system with two DMA en-          |     |

|     | gines on the same multi-flow real-time bridge reveals      |     |

|     | the low priority flow interfering with the high priority   |     |

|     | flow, causing a deadline miss                              | 112 |

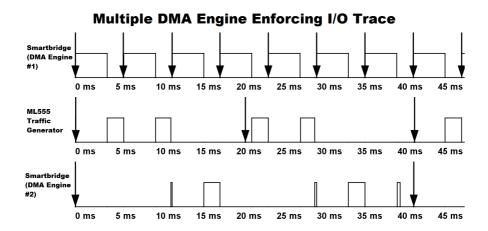

| 4.4 | The bus-access trace of the same task set shows the        |     |

|     | real-time I/O management system prioritizing bus ac-       |     |

|     | cess among real-time flows, preventing a deadline miss.    | 113 |

| 5.1 | Real-Time I/O Management System                            | 123 |

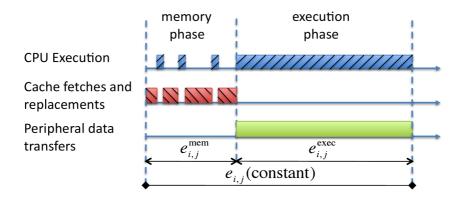

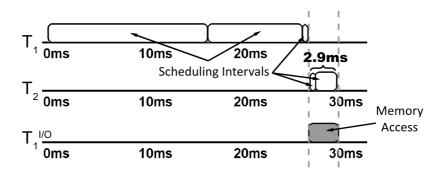

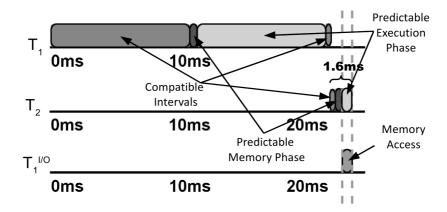

| 5.2 | Predictable Interval with constant execution time          | 125 |

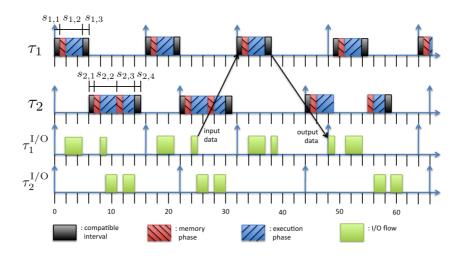

| 5.3 | Example System-Level Predictable Schedule                  | 126 |

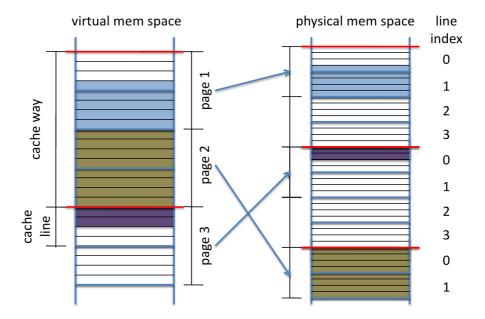

| 5.4 | Cache organization with one memory region                  | 129 |

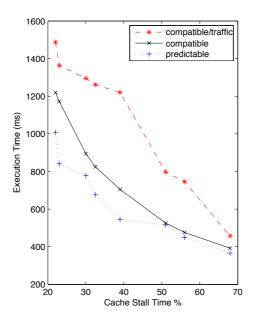

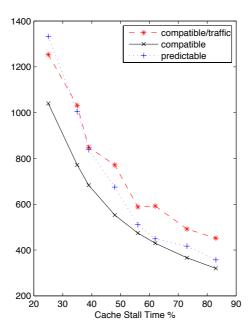

| 5.5 | random_access                                              | 145 |

| 5.6 | linear access                                              | 146 |

5.8

### List of Tables

| 2.1 | Characteristics of the test platforms                | 44         |

|-----|------------------------------------------------------|------------|

| 2.2 | Operating system overheads for the MIX workload (in  | <b>F</b> 0 |

|     | milliseconds) on configuration S1                    | 50         |

| 2.3 | Operating system overheads for the MIX workload (in  |            |

|     | milliseconds) on configuration S2                    | 51         |

| 2.4 | Operating system overheads for the MIX workload (in  |            |

|     | milliseconds) on configuration S3                    | 51         |

| 2.5 | Operating system latencies for the MIX workload (in  |            |

|     | microseconds)                                        | 60         |

| 3.1 | Our experiments using four flows                     | 93         |

| 4.1 | Our second experiment has three flows on two periph- |            |

|     | erals (both bridge DMA engines are on the same pe-   |            |

|     | $ripheral). \ . \ . \ . \ . \ . \ . \ . \ . \ . \$   | 111        |

| 4.2 | TEMAC bandwidth in Mbit/sec mesuared with Net-       |            |

|     | Perf. MTU was set to 1500 bytes                      | 114        |

| 5.1 | DES benchmark                                        | 143        |

| A.1 | Operating system overhead on configuration S1 (in    |            |

|     | milliseconds)                                        | 156        |

| A.2 | Operating system overhead on configuration S2 (in    |            |

|     | milliseconds)                                        | 157        |

|     |                                                      |            |

xiv List of Tables

| A.3 | Operating system overhead on configuration S3 (in                |     |

|-----|------------------------------------------------------------------|-----|

|     | $milliseconds). \dots \dots \dots \dots \dots \dots \dots \dots$ | 158 |

| A.4 | Operating system latency on configuration S1 (in mi-             |     |

|     | croseconds)                                                      | 159 |

| A.5 | Operating system latency on configuration S2 (in mi-             |     |

|     | croseconds)                                                      | 160 |

| A.6 | Operating system latency on configuration S3 (in mi-             |     |

|     | croseconds)                                                      | 161 |

The term real-time pertains to computer applications whose correctness is judged not only on whether the results are the correct ones, but also on the time at which the results are delivered. A real-time system is a computer system that is able to run real-time applications and meet the constraints of the task at hand. In particular, in this thesis, we focus on hard real-time systems, which are high criticality systems, where missing a deadline (in other words, delivering the computation results too late with respect of a predefined time) can lead to catastrophic events. For example, an airbag device is a hard real-time system. When a crash happens the airbag must deploy within a tight range of time: an early or late deployment would be unuseful or even dangerous.

Traditionally, because of these strict requirements where the system must not fail in any situation, hard real-time systems have been constructed from hardware and software components specifically designed for real-time. Developing these systems typically costs millions of dollars, in particular when they are employed in aircraft, and the whole development process can be very long. The main reason is that every single component (from the peripheral up to the operating system) has to be designed, implemented, tested, and integrated with the rest of the system. Moreover, nowadays many hard real-time systems make intense use of media streaming, thus they require significant performance in terms of bus and network bandwidth, processors, and memory. In this scenario, COTS (Commercial Off-

The-Shelf) components are every day becoming more attractive for real-time systems.

A COTS hardware or software component is a ready-to-use product, available in the market. Due to mass production, COTS components are significantly cheaper to produce than their application-specific peers. They also evolve very rapidly, improving in performance much faster than a custom real-time system. For example consider Intel or AMD processors, modern video cards, network interfaces, system buses like PCI-E (PCI-EXPRESS), and even operating systems like Linux.

Obviously, a custom component produced with a (relatively) small number of pieces cannot easily match the performance of its COTS equivalent. As a consequence COTS components are already used in real-time systems with low criticality (also called soft real-time systems<sup>1</sup>), but they are not yet typically employed for hard real-time. The reason is that COTS components are built having as a primary design goal their average performance, and not worst case behaviors and reliability. On the other hand, worst case behaviors and reliability are the most important features for a real-time system, in particular for high criticality systems, where failing or miss a time deadline is unacceptable. For example, modern buses can transfer data at speeds on the order of several Gigabyte per second, but in case more entities are accessing the bus at the same moment, there is no mechanism to prioritize a critical task, which may then be delayed for an excessively long time and even potentially miss its deadline.

<sup>&</sup>lt;sup>1</sup>More accurate definitions of real-time systems are given later, in chapter 1.

Within this PhD program we started addressing some of the most important sources of unpredictability that must be removed in order to integrate COTS hardware and software in a hard real-time system. In particular, we focused on:

- operating system overhead and latency,

- interference among peripherals,

- interference within peripherals (peripheral sharing),

- interference among peripherals and CPU.

The operating system overhead and operating system latency are the first culprits for *software interference*<sup>2</sup> in the execution time of a task. To address this issue we designed and developed a variant of the Linux operating system, called ASMP-LINUX [7], which is described in detail in chapter 2.

Analyzing the system behavior when using COTS hardware components, we identified as crucial the unpredictability caused by the I/O subsystem and main memory. In fact, although COTS processors still have many open problems, they have started to appear in hard real-time systems over the last few years. On the other hand, bus, peripherals, and main memory access can still be bottlenecks for the system, often introducing unpredictable delays.

Interference among peripherals is observable when more than one peripheral asynchronously accesses the bus to read or write data

<sup>&</sup>lt;sup>2</sup>Actually, we will see in chapter 1 that also some hardware interference, very difficult to avoid, can slightly affect the measure of these delays.

from main memory. This problem will be treated in detail in chapter 3, together with our proposed solution: a novel real-time I/O management system, based on real-time bridges [4]. Such a system, transparent to end-user CPU applications, introduces two new types of components into the COTS system, real-time bridges and a reservation controller, to provide temporal isolation on the COTS bus and remove the possibility of interference.

A real-time bridge evolution has been also developed to handle **interference within peripherals**. *Multi-flow real-time bridges* [5], described in chapter 4, deals with peripherals shared among tasks with different criticalities, enforcing a real-time I/O scheduling within shared peripherals and on the PCI-E bus.

Finally, we are currently working on a solution for **interference** between peripheral and the CPU, observed when both access main memory at the same time [45, 44]. Our solution, described in chapter 5, proposes a new execution model, called PREM (PRedictable Execution Model) [48], that combines new compiler techniques and the real-time bridges and is able to enforce predictable memory accesses while avoiding bus interference between tasks running on the CPU and peripherals.

Before we start discussing the challenges just introduced and our proposed solutions, chapter 1 gives an overview of some general concepts on real-time systems, COTS components, and definitions of hardware and software sources of unpredictability.

# Real-time systems and COTS components

This chapter introduces some key concepts regarding real-time systems and COTS (Commercial Off-The-Shelf) components (hardware and operating systems). The main goal is giving the reader an overview of the basic knowledge on these topics. Moreover the main requirements of the real-time systems will be described in the context of the limitations of the COTS components. This will give a general idea of the challenges that we address later in this work.

### 1.1 Real-time systems

In the literature there are many different definitions of real-time systems. The following is the canonical definition from Donald Gillies [2, 26]:

**Definition 1.** "A real-time system is one in which the correctness of the computations not only depends upon the logical correctness of the computation but also upon the time at which the result is produced. If the timing constraints of the system are not met, system failure is said to have occurred."

Along with definition 1, POSIX Standard 1003.1 defines "real-time" for operating systems as:

**Definition 2.** "Real-time in operating systems is the ability of the operating system to provide a required level of service in a bounded response time."

In both definitions is evident how *time* is one of the most important aspects of a real-time system. The main reason for this is that a real-time task is usually running on a, so called, *Cyber-Physical System*, which, in other words, is a system where system's computational interacts with physical elements [67]. It follows that such a task must react to events that take place in the real world, and that the *response time* is the key element of correctness for a real-time system. If the answer to the event is delivered too late, it may be useless, or worse, catastrophic events could happen in the real world.

Finally it is also important to emphasize that "react within a deadline" needs not mean "react fast". The *deadline* within the real-time system must complete its computation and deliver its results could be in the order of milliseconds, seconds, or minutes as well. The only important thing is to complete the task before the deadline is missed.

#### 1.1.1 Hard and soft real-time

Real-time systems and applications can be classified in several ways. One classification scheme divides them into two main classes: "hard" real-time and "soft" real-time.

A hard real-time system is characterized by the fact that meeting the application's deadlines is the primary metric of success. In other words, failing to meet the application's deadlines (timing requirements, quality of service, latency constraints, and so on) is a catastrophic event that must be absolutely avoided.

Conversely, a *soft real-time* system is suitable to run applications whose deadlines must be satisfied "most of the time", that is, the work carried out by a soft real-time application retains some value even if a deadline is missed. In soft real-time systems some design goals, such as achieving high average throughput, may be as important, or more important, than meeting application deadlines.

An example of a hard real-time application is a missile defense system: whenever a radar system detects an attacking missile, the real-time system has to compute all the information required for tracking, intercepting, and destroying the target missile. If it fails, catastrophic events may follow.

A very common example of soft real-time application is a video stream decoder: the incoming data have to be decoded on the fly. If, for some reason, the decoder is not able to translate the stream before its deadline and a frame is lost, nothing catastrophic happens: the user will likely not even take notice of the missing frame (the human eye cannot distinguish images faster than one tenth of a second).

Needless to say, hard real-time applications put many more time and resource constraints on the system than do soft real-time applications; thus hard real-time systems are difficult to design and implement.

In this thesis, we focus on hard real-time systems.

Figure 1.1: A real-time periodic task

### 1.1.2 Periodic and event-driver real-time applications

There exists also a classification scheme that divides real-time applications into "periodic" and "event-driven" classes.

As the name suggests, *periodic* applications execute a task periodically, and have to complete their job by a predefined deadline within each period. In figure 1.1, we can note that the deadline need not coincide with the end of the period.

A nuclear power plant monitor is an example of a periodic hard real-time application, while a multimedia decoder is an example of a periodic soft real-time application.

Conversely, event-driven applications give rise to processes that spend most of the time waiting for some event. When an expected even occurs, the real-time process waiting for that event must wake up and handle it in such a way as to satisfy the predefined time constraints.

The aforementioned missile defense system is an example of an event-driven hard real-time application, while a network router might

be an example of an event-driven soft real-time application.

Dealing with real-time applications, the operating system must guarantee a sufficient amount of each resource (processor time, memory, network bandwidth, and so on) to each application so that it succeeds in meeting its deadlines. Essentially, in order to effectively implement a real-time system for periodic or event-driven applications a resource allocation problem must be solved. Clearly, the operating system should assign resources to processes according to their priorities, so that, for instance a high-priority task will never be delayed by a low-priority task. Real-time scheduling theory is a widely explored field; for an up-to-date survey of real-time theory see [60].

In this thesis we focus on both event-driven and periodic hard real-time applications. In particular we will study the case where hard real-time applications run on COTS hardware and in a generalpurpose COTS operating system, like Linux.

In the following sections we will introduce the concept of *jitter* (section 1.2) and how it affects the system's predictability. In section 1.3, we will describe the characteristics of *COTS* components and why they are used in real-time systems. After that, in section 1.4, operating system overhead and latency will be also discussed as main software sources of jitter. Finally, section 1.5 discusses COTS hardware impact on system's predictability.

Figure 1.2: An example of jitter in a real-time periodic task

### 1.2 Jitter and predictability

In an ideal world a real-time process would run undisturbed from the beginning to the end, directly communicating with the device it is intended to control. In this situation a real-time process will require always the same amount of time T to complete its task. Such a system is said to be deterministic.

In the real world, however, there are several software layers between the device and the real-time process, and other processes and services could be running at the same time competing for hardware resources. Moreover, other devices might require attention and interrupt the real-time execution. As a result, the amount of time required by the real-time process to complete its task is actually  $T_x = T + \varepsilon$ , where  $\varepsilon \geq 0$  is a delay caused by the system (hardware and software). The variation in the values of  $\varepsilon$  is defined as the system's jitter, a measure of the non-determinism of a system. In figure 1.1 an ideal case for a periodic task is showed, instead in figure 1.2 we can see a more realistic case where a variable jitter increases the execution time in a non-deterministic way.

Determinism is a key factor for hard real-time systems: the larger the jitter, the less deterministic the system's response. Thus, jitter is also an indicator of the hard real-time capabilities of a system: if the jitter is greater than some critical threshold, the system can be unsuitable for real-time. As a consequence, a real-time operating system and the associated hardware components must be designed so as to minimize the jitter observed by the real-time applications.

Jitter, by its nature, is not constant and makes the system behavior unpredictable; for this reason, real-time application developers must provide an estimated Worst Case Execution Time (WCET), which is an upper bound (often quite pessimistic) of the real-time application's execution time. A real-time application meets its deadline if  $T_x \leq$  WCET. If it is not possible to estimate an upper bound for the execution time, then the system is unpredictable and cannot be used for real-time applications. In other words, hardware components and operating systems for real-time must be designed to minimize the jitter, as we already said, but also to follow predictable behaviors, in order to have a computable WCET.

### 1.3 Commercial Off-The-Shelf components

With the term Commercial Off-The-Shelf (COTS) we refer to software or hardware products ready-made and available for sale, lease, or license to the general public [66].

Even tough traditionally, hardware and software for real-time systems have been specifically designed, lately real-time embedded systems are increasingly being built using Commercial Off-The-Shelf (COTS) hardware. Also open-source COTS operating system are used, usually after some modifications, and nowadays many commercial real-time operating systems are Linux-based.

Motivations for using COTS components include reduction of overall system development time and costs (as components can be bought or licensed instead of being developed from scratch) and reduced maintenance costs.

Since several years ago, most of the real-time embedded systems that require high computational power make use of COTS processors, mainly for their high performance/cost ratio. Moreover integrating high-speed COTS peripherals within a real-time system offers substantial benefits in terms of cost reduction, time-to-market, and overall performance. Since COTS components are already designed, a system's time-to-market can be reduced by reusing existing components instead of creating new ones. Additionally, overall performance of mass produced components is often significantly higher than custom made systems. For example, a PCI-Express bus [42] can transfer data three orders of magnitude faster than the real-time SAFEbus [31].

### 1.3.1 COTS components' challenges

COTS components are typically designed paying little or no attention to worst-case timing behaviors. Usually COTS designers aim to improve average performance, instead of determinism, predictability, and reliability.

Modern COTS processors are intrinsically parallel and so complex

that it is not possible to predict when an instruction will complete. For example cache misses, branch predictors, pipeline, out-of-order execution, and speculative accesses could significantly alter the execution time of an in-flying instruction.

COTS buses, like PCI-E, can be very fast, but also completely unpredictable. Bus arbitration policies and transactions' scheduling are "black-boxes", and their implementation details are known only by the original manufacturer.

Integrating COTS peripherals within a real-time system is also a daunting task. The main reason is the unpredictable timing of the I/O subsystem: some shared resources, such as the PCI-E bus or the memory controller, require an arbitration among the hardware devices, that is, a lock mechanism. Moreover, low priority data transferred on the bus could steal bandwidth to real-time applications with higher priority. There are also "intrinsic indeterministic buses" used to connect devices to the system or system to system, such as Ethernet or PCI buses [57].

It is worth to say that COTS components have also other kinds of drawbacks, other than the ones related to system's determinism. For example, as personal users we like to often update our system, following every new technology in the market. On the other hand, big companies that sell or use real-time systems can fear to be dependent on a third-party component vendor, because future changes to the product will not be under their control. Moreover components integration can require much more work than it would if every single component was designed for the same specific system.

However, at the end of the day, integration problems and compo-

nents availability on the market can be paid by the fact the producing your own system (hardware and operating system), especially in case of high performance requirements, can be even more expensive or sometimes impossible. Looking at the predictability of the system instead, using COTS components could seem implicitly giving up on strict determinism, but, as a matter of fact, commercial and industrial real-time systems often follow the *five-nines rule*:

**Definition 3.** The system is considered hard real-time if a real-time application catches its deadline 99.999% of the times.

Consequently, real-time industry is already using COTS components. And it is even more important that most of the companies are investing considerable amount of money in research, foreseeing a complete transaction from their dedicated systems to complete COTS based systems.

### 1.4 Operating system overhead and latency

This section gives an overview of the software jitter measured by an operating system. This will help to better understand the characteristics required by a real-time operating system and, consequently, the challenges that have to be faced using a COTS operating system, like Linux. Before starting tough, it must be clear that predictability is not the only feature required by a real-time operating system: it is definitely the most important one, but also other features are required, like fault tolerance, or system partitioning. Anyway, in this

Figure 1.3: Jitter

work we mostly focus on assuring predictability, hence other real-time system's features will not be covered in detail.

As discussed in [29, 51, 72], short, unpredictable activities such as interrupts handling are the main causes of large jitter in computer systems. As shown in Figure 1.3, the jitter seen by an operating system is composed by two main components: the "operating system overhead" and the "operating system latency".

The operating system overhead is the amount of time the CPU spends while executing system's code—for example, handling the hardware devices or managing memory—and code of other processes instead of the real-time process' code.

The operating system latency is the time elapsed between the instant in which an event is raised by some hardware device and the instant in which a real-time application starts handling that event. Also periodic real-time applications suffer from operating system latency: for example, the operating system latency may cause a periodic application to wake up with some delay with respect to the beginning of its real-time period.

The definitions of overhead and latency are rather informal, be-

cause they overlap on some corner cases. For instance, the operating system overhead includes the time spent by the kernel in order to select the "best" process to run on each CPU; the component in charge of this activity is called *scheduler*. However, in a specific case the time spent while executing the scheduler is not accounted as operating system overhead but rather as operating system latency: it happens when the scheduler is going to select precisely the process that carries on the execution of the real-time application. On the other hand, if some non-real-time interrupts occur between a real-time event and the wake-up of the real-time applications, the time spent by the kernel while handling the non-real-time interrupts should be accounted as overhead rather than latency.

As illustrated in Figure 1.3, operating system latency can be decomposed in two components: the "interrupt latency" and the "scheduler latency".

The *interrupt latency* is the time required to execute the interrupt handler connected to the device that raised the interrupt, i.e., the device that detected an event the real-time process has to handle.

The *scheduler latency* is the time required by the operating system scheduler to select the real-time task as the next process to run and assign it the CPU.

Interrupt latency, scheduler latency, and operating system overhead reduce the system's determinism and, thus, its real-time capabilities. It follows that, the main goals of a real-time operating system must be to reduce software latency and overhead, and, over all, to make them predictable. The best optimized operating system could be able to manage operating system overhead with opportune scheduling policies. Anyway, it will still suffer from some operating system latency, because the sources of those delays (interrupt and scheduler latencies) are code that can be executed only between the time when an event happens and its handling deadline expires.

### 1.5 Hardware jitter

As we just said, most of the system's jitter is due to the operating system, and in particular to:

- interrupts handling, and more in general devices related activities,

- hardware resources' sharing (i.e., overhead and latency introduce by a CPU scheduler, or locks needed to synchronize different users on the same resource),

- other periodic or sporadic activities important for the system (i.e., disk cache flushing).

Anyway, while measuring operating system overhead and operating system latency we have to consider that part of those delays could be also accounted to the underline hardware. This is specially true when our system is running on COTS hardware.

Several hardware resources are shared among different hardware components: caches, buses, and main memory, for example, can all be sources of unexpected delays when two different hardware entities are competing for the same resource. The execution time of a real-time process, e.g., could be delayed by a peripheral when both try to

access main memory at the same time: the process in consequence of some cache misses, and the peripheral performing DMA (Direct Memory Access) transactions. In this kind of situations the memory bus and the memory itself would be a bottleneck: one or both of the competing operations could indeed suffer for a delay, potentially missing their deadline.

The indeterminism caused by the hardware cannot be reduced by the software, thus no real-time operating system can have better performances than those of the underlying hardware. In other words, the execution time  $T_x$  of a real-time task will always be affected by some jitter, no matter of how good the real-time operating system is.

### 1.6 Proposed solutions

In this work, in order to obtain hard real-time performance with strict deadline using COTS componets, we propose:

- a variant of the Linux operating system, discussed in chapter

2, that significantly reduces operating system overhead and operating system latency;

- a simple and flexible architectural modification, described in chapters 3 and 4, that completely removes interferences among and within peripherals;

- a new execution model, treated in chapter 5, that faces interferences between CPU and peripherals, schedules drivers activities, and is meant to support and integrate all the previous solutions.

However, we will see how our new architecture does not mean to directly modify COTS hardware components (which will not make sense for COTS' nature), but just to integrate them, in order to make their behavior deterministic. Finally we developed prototypes for each proposed component and, with our experimental results, we can show how our solutions reduce, and in many cases remove, the most important sources of unpredictabilities in COTS systems.

# **ASMP-LINUX**

Multiprocessor systems, especially those based on multi-core processors, and new operating system architectures could satisfy the ever increasing computational requirements of embedded systems. Unfortunately, every time the level of parallelism is increased, more resources have to be shared among different tasks. As we said in section 1.2, predictability is the first requirement of a real-time system, and instead shared resources are the main origin of indeterminism. For example, in [49] the authors experimented an increment of  $\sim 200\%$  in the WCET when 2 cores and peripherals access memory at the same time. In uni-processor systems the measured increment was  $\sim 44\%$  [44]. Hence, this increased unpredictability is among the most important reasons why multiprocessor systems are not very common yet in hard real-time environments.

In this chapter, we present ASMP-LINUX, which stands for ASymmetric MultiProcessor Linux, and is a modified Linux kernel that can be used in COTS multiprocessor embedded systems with hard real-time requirements. It has been developed in 2007 within this PhD program, and in 2008 was presented in the EURASIP Journal on Embedded Systems [7].

ASMP-LINUX provides a high responsiveness, open-source hard

real-time operating system for multiprocessor architectures, using an asymmetric kernel approach. We will see how ASMP-LINUX is capable of providing hard real-time capabilities with COTS multiprocessor while maintaining the code simple and not impacting on the performance of the rest of the system. Moreover, ASMP-LINUX does not require code changing or application re-compiling/re-linking. In a conventional (symmetric) kernel, I/O devices and CPUs are considered alike, since no assumption is made on the system's load. Asymmetric kernels, instead, consider real-time processes and related devices as privileged and shield them from other system activities.

The main advantages offered by ASMP-LINUX to real-time applications are:

- Deterministic execution time (up to a few hundreds of nanoseconds).

- Very low system overhead.

- High performance and high responsiveness.

Clearly, all of the good things offered by ASMP-LINUX have a cost, namely at least one processor core dedicated to real-time tasks. The current trend in processor design is leading to chips with more and more cores. Because the power consumption of single-chip multi-core processors is not exceedingly higher than that of single-core processors, we can also expect that in a near future many embedded systems will make use of multi-core processors. Nowadays, in fact, most of the companies in the real-time industry are investigating multi-core solutions: soft real-time embedded systems are already

available, and satisfing hard real-time constraints in multi-core systems is a very hot topic for modern research. Thus, even though several issues have not to be solved yet, in a near future multi-core systems could become very common for hard real-time systems too, and the hardware requirements of real-time operating systems such as ASMP-LINUX will become quite acceptable as well.

In the rest of this chapter we will first review some background information, so that the reader can better understand ASMP-LINUX and the main idea behind it: Section 2.1 describes the evolution of single-chip multi-core processors; Section 2.2 gives an introduction to system partitioning; Section 2.3 illustrates briefly the main characteristics of other asymmetric kernels developed before ASMP-LINUX. After that ASMP-LINUX will be described in detail. Section 2.4 discusses ASMP-LINUX implementation, and section 2.5 lists the tests performed on different computers and the results obtained.

# 2.1 Multiprocessor systems

As we discussed in the section 1.3, the increasing demand for computational power leaded real-time embedded systems developers to use general-purpose COTS processors, such as ARM, Intel, AMD, or IBM's POWER, instead of micro-controllers or Digital Signal Processors (DSPs).

Furthermore, many hardware vendors started to develop and market *system-on-chip* (SoC) devices, which usually include on the same integrated circuit one or more COTS CPUs, together with other specialized processors like DSPs, peripherals, communication buses, and

memory. System-on-chip devices are particularly suited for embedded systems because they are cheaper, more reliable, and consume less power than their equivalent multi-chip systems. Actually, power consumption can be considered as a very important constraint in some embedded systems [22].

In the quest for the highest CPU performances, hardware developers are faced with a difficult dilemma. On one hand, the Moore's Law does not apply to computational power any more, that is, computational power is no longer doubling every 18 months as in the past. On the other hand, power consumption continues to increase more than linearly with the number of transistors included in a chip, and the Moore's Law still holds for the number of transistors in a chip.

Several technology solutions have been adopted to solve this dilemma. Some of them try to reduce the power consumption by sacrificing computational power, usually by means of frequency scaling, voltage throttling, or both. For instance, the Intel Centrino processor [16] (first generation released in March 2003) has a variable CPU clock rate ranging between 600 MHz and 1.5 GHz, which can be dynamically adjusted according to the computational needs.

Other solutions try to get more computational power from the CPU without increasing power consumption. For instance, a key idea was to increase the *Instruction Level Parallelism* (ILP) inside a processor; this solution worked well for some years, but nowadays the penalty of a cache miss (which may stall the pipeline) or of a miss-predicted branch (which may invalidate the pipeline) has become way too expensive.

Chip-Multi-Thread (CMT) [38] processors aim to solve the problem from another point of view: they run different processes at the same time, assigning them resources dynamically according to the available resources and requirements. Historically the first CMT processor was a coarse-grained multithreading CPU (IBM RS64-II [8, 64]) introduced in 1998: in this kind of processor only one thread executes at any instance. Whenever that thread experiments a long-latency delay (such as a cache miss), the processor swaps out the waiting thread and starts to execute the second thread. In this way the machine is not idle during the memory transfers and, thus, its utilization increase.

Fine-grained multithreading processors improve the previous approach: in this case the processor executes the two threads in successive cycles, most of the time in a round-robin fashion. In this way the two threads are executed at the same time but, if one of them encounters a long-latency event, its cycles are lost. Moreover, this approach requires more hardware resources duplication than the coarse-grained multithreading solution.

In Symmetric MultiThreading (SMT) processors two threads are executed at the same time, like in the fine-grained multithreading CPUs; however, the processor is capable of adjusting the rate at which it fetches instructions from one thread flow or the other one dynamically, according to the actual environmental situation. In this way, if a thread experiments a long-latency event, its cycles will be used by the other thread, hopefully without loosing anything.

Yet another approach consists of putting more processors on a chip rather than packing into a chip a single CPU with a higher

Figure 2.1: An example of dual core processor with shared L2 cache and bus interface [70].

frequency. This technique is called *chip-level multiprocessing* (CMP), but it is also known as "chip multiprocessor"; essentially it implements symmetric multiprocessing (SMP) inside a single VLSI integrated circuit. Multiple processor cores typically share a common second- or third-level cache and interconnections. Figure 2.1 shows an example of a dual core processor with shared L2 cache and bus interface.

In 2001 IBM introduced the first chip containing two single-threaded processors (cores): the POWER4 [65]. Since that time, several other vendors have also introduced their multi-core solutions: dual-core and quad-core processors are nowadays widely used (e.g., Intel Dual Core 2 [69] introduced in 2006, or AMD Opteron [19] introduced in 2005) and single core processors are almost out of the market; hexa-core processors (sometimes called six-core) are already on the

shelves (like Intel Xeon Dunnington [14]), and eight-core processors (also called *octo-core*) are starting to appear (like Intel Xeon Beckton [71]).

In conclusion, McKenney's forecast [39] that in a near future many embedded systems will sport several CMP and/or CMT processors is becoming reality. In fact, the small increase in power consumption is justified by the large increment of computational power available to the embedded system's applications. Furthermore, the actual trend in the design of system-on-chip devices is showing that such chips starts including multi-core processors. Therefore, nowadays an embedded system designer can create boards having many processors almost "for free", that is, without the overhead of a much more complicated electronic layout or a much higher power consumption.

On the other hand real-time theory for multiprocessor systems (about schedulability, static analysis, etc) is not very solid yet and most of the big companies dealing with real-time systems are still afraid of migrating to multiprocessors systems. In this work we show how a *partitioned* multiprocessor system can be used in a real-time environment to reduce and in some case eliminate the unpredictability introduced by the operating system (see section 1.4).

# 2.2 System partitioning

The real-time operating system must guarantee that, when a real-time application requires some resource, that resource is made available to the application as soon as possible. The operating system should also ensure that the resources shared among all processes—

the CPU itself, the memory bus, and so on—are assigned to the processes according to a policy that take in consideration the priorities among the running processes.

As long as the operating system has to deal only with processes, it is relatively easy to preempt a running process and assign the CPU to another, higher-priority process. Unfortunately, as discussed in 1.4, external events and operating system critical activities, required for the correct operation of the whole system, occur at unpredictable times and are usually associated with the highest priority in the system. Thus, for example, an external interrupt could delay a critical, hard real-time application that, deprived of the processor, could eventually miss its deadline. Even if the application manages to catch its deadline, the operating system may introduce a factor of non-determinism that is tough to predict in advance.

Therefore, handling both external events and operating system critical activities while guaranteeing strict deadlines is the main problem in real-time operating systems. Multiprocessor systems make this problem even worse, because operating system activities are much more complicated.

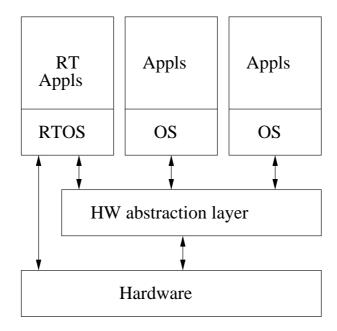

In order to cope with this problem, real-time operating systems are usually partitioned horizontally or vertically. As illustrated in Figure 2.2, horizontally partitioned operating systems have a bottom layer (called hardware abstraction layer, or HAL) that virtualizes the real hardware; on top of this layer there are several virtual machines, or partitions, running a standard or modified operating system, one for each application's domain; finally, applications run into their own domain as they were running on a dedicated machine.

Figure 2.2: Horizontally partitioned operating system

In horizontally partitioned operating systems the real-time applications have an abstract view of the system; external events are caught by the hardware abstraction layer and propagated to the domains according to their priorities. While it seems counter-intuitive to use virtual machines for hard real-time applications, this approach works well in most of the cases, even if the hardware abstraction layer—in particular the partitions scheduler or the interrupt dispatcher—might introduce some overhead. Several Linux-based real-time operating systems such as RTAI [20] (implemented on top of Adeos [79]) and some commercial operating systems like Wind River's VxWorks [54] use this software architecture.

In contrast with the previous approach, in a vertically partitioned

Figure 2.3: Vertically partitioned operating system

operating system the resources that are crucial for the execution of the real-time applications are directly assigned to the application themselves, with no software layer in the middle. The non-critical applications and the operating system activities not related to the real-time tasks are not allowed to use the reserved resources. This schema is illustrated in Figure 2.3.

Thanks to this approach, followed by ASMP-LINUX, the realtime specific components of the operating system are kept simple, because they do not require complex partition schedulers or virtual interrupt dispatchers. Moreover, the performances of a real-time application are potentially higher with respect to those of the corresponding application in a horizontally partitioned operating system, because there is no overhead due to the hardware abstraction layer. Finally, in a vertically partitioned operating system, the non-real-time components never slow down unreasonably, because these components always have their own hardware resources different from the resources used by the real-time tasks.

# 2.3 Asymmetric multiprocessor kernels

The idea of dedicating some processors of a multiprocessor system to real-time tasks is not new. In an early description of the ARTiS system included in [40], processors are classified as real-time and non-real-time. Real-time CPUs execute non-preemptible code only, thus tasks running on these processors perform predictably. If a task wants to enter into a preemptible section of code on a real-time processor, ARTiS will automatically migrate this task to a non-real-time processor.

Furthermore, dedicated load-balancing strategies allow all CPUs to be fully exploited. In a more recent article by the same group [37], processes have been divided into three groups: highest priority (RT0), other real-time Linux tasks (RT1+), and non-real-time tasks; furthermore, a basic library has been implemented to provide functions that allow programmers to register and unregister RT0 tasks. Since ARTiS relies on the standard Linux interrupt handler, the system latency may vary considerably: a maximum observed latency of 120  $\mu$ secs on a 4-way Intel Architecture-64 (IA-64) heavily loaded system has been reported in [37].

A more drastic approach to reduce the fluctuations in the latency

time has been proposed independently in [28] and [10]. In this approach, the source of real-time events is typically a hardware device that drives an IRQ signal not shared with other devices. The asymmetric multiprocessor (ASMP) system is implemented by binding the real-time IRQ and the real-time tasks to one or more "shielded" processors, which never handle non-real-time IRQs or tasks. Of course, the non-real-time IRQs and non-real-time tasks are handled by the other processors in the system. As discussed in [28] and [10], the fluctuations of the system latency are thus significantly reduced.

It is worth noting that, since version 2.6.9 released in October 2004, the standard Linux kernel includes a boot parameter (isolcpus) that allows the system administrator to specify a list of "isolated" processors: they will never be considered by the scheduling algorithm, thus they do not normally run any task besides the per-CPU kernel threads. In order to force a process to migrate on a isolated CPU, a programmer may make use of the Linux-specific system call sched\_setaffinity(). The Linux kernel also includes a mechanism to bind a specific IRQ to one or more CPUs; therefore, it is easy to implement an ASMP mechanism using a standard Linux kernel.

However, the implementation of ASMP discussed in this thesis, ASMP-LINUX, is not based on the isolcpus boot parameter. A clear advantage of ASMP-LINUX is that the system administrator can switch between SMP and ASMP mode at run time, without rebooting the computer. Moreover, as explained in Section 2.4.2, ASMP-LINUX takes care of avoiding load rebalancing for asymmetric processors, thus it should be slightly more efficient than a system based only on isolcpus.

### 2.3.1 Other asymmetric systems

Although in this work we will concentrate on the real-time applications of asymmetric kernels, it is worth mentioning that these kernels are also used in other areas. As an example, some multi-core chips include different types of cores and require thus an asymmetric kernel to handle each core properly. The IBM Cell Broadband Engine (BE) discussed in [12], for instance, integrates a 64-bit PowerPC processor core along with eight "synergistic processor cores". This asymmetric multi-core chip is the hearth of the Sony PS3 PlayStation console, although other applications outside of the video game console market, such as medical imaging and rendering graphical data, are been considered.

# 2.4 ASMP-LINUX implementation

ASMP-LINUX has been originally developed as a patch for the 2.4 Linux kernel series in 2002 [28]. After several revisions and major updates, ASMP-LINUX was implemented as a patch for the Linux kernel 2.6.19.1, the latest Linux kernel version available when this implementation has been done.

One of the design goals of ASMP-LINUX is simplicity: because Linux developers introduce quite often significant changes in the kernel, it would be very difficult to maintain the ASMP-LINUX patch if it was intrusive or overly complex. Actually, most of the code specific to ASMP-LINUX is implemented as an independent kernel module, even if some minor changes in the core kernel code—mainly in the

scheduler, as discussed in Section 2.4.2—are still required.

Another design goal of ASMP-LINUX is architecture-independency: the patch can be easily ported to many different architectures, besides the IA-32 architecture that has been adopted for the experiments reported in Section 2.5.

It should be noted, however, that in a few cases ASMP-LINUX needs to interact with the hardware devices (for instance when dealing with the local timer, as explained in Section 2.4.3). In these cases, ASMP-LINUX makes use of the interfaces provided by the standard Linux kernel; those interfaces are, of course, architecture-dependent but they are officially maintained by the kernel developers.

It is also worth noting that what ASMP-LINUX can or cannot do depends ultimately on the characteristics of the underlying system architecture. For example, in the IBM's POWER5 architecture disabling the in-chip circuit that generates the local timer interrupt (the so-called *decrementer*) also disables all other external interrupts. Thus, the designer of a real-time embedded system must be aware that in some general-purpose COTS architectures it might be simply impossible to mask all sources of system jitter.

ASMP-LINUX is released under the version 2 of the GNU General Public License [25], and it is available at [6] to all the developers who wish to work with it. Actually it is very interesting how, after almost 3 years, we are still receiving feedback from people working on ASMP-LINUX.

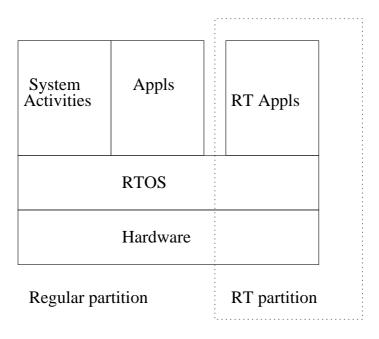

Figure 2.4: ASMP-LINUX partitioning

### 2.4.1 System partitions

ASMP-LINUX is a vertically partitioned operating system. Thus, as explained in Section 2.2, it implements two different kinds of partitions:

**System partition** It executes all the non-real-time activities, such as daemons, normal processes, interrupt handling for non critical devices, and so on.

**Real-time partition** It handles some real-time tasks, as well as any hardware device and driver that is crucial for the real-time performances of that tasks.

In an ASMP-LINUX system there is exactly one system partition, which may consist of several processors, devices, and processes;

moreover, there should always exist at least one real-time partition (see Figure 2.4). Additional real-time partitions might also exist, each handling one specific real-time application.

Each real-time partition consists of a processor (called *shielded CPU*, or shortly S-CPU),  $n_{irq} \geq 0$  IRQ lines assigned to that processor and corresponding to the critical hardware devices handled in the partition, and  $n_{task} \geq 0$  real-time processes (there could be no real-time process in the partition; this happens when the whole real-time algorithm is coded inside an interrupt handler).

Each real-time partition is protected from any external event or activity that does not belong to the real-time task running on that partition. Thus, for example, no conventional process can be scheduled on a shielded CPU and no normal interrupt can be delivered to that processor.

### 2.4.2 Process handling

The bottom rule of ASMP-LINUX while managing processes is the following:

Every process assigned to a real-time partition must run only in that partition; furthermore, every process that does not belong to a real-time partition cannot run on that partition.

It should be noted, however, that a real-time partition always include a few peculiar non-real-time processes. In fact, the Linux kernel design makes use of some processes, called *kernel threads*, which

execute only in Kernel Mode and perform system-related activities. Besides the *idle process*, a few kernel threads such as *ksoftirqd* [9] are duplicated across all CPUs, so that each CPU executes one specific instance of the kernel thread. In the current design of ASMP-LINUX, the per-CPU kernel threads still remain associated with the shielded CPUs, thus they can potentially compete with the real-time tasks inside the partition. As we shall see in Section 2.5, this design choice has no significant impact on the operating system overhead and latency.

The ASMP-LINUX patch is not intrusive because the standard Linux kernel already provides support to select which processes can execute on each CPU. In particular, every process descriptor contains a field named cpus\_allowed, which is a bitmap denoting the CPUs that are allowed to execute the process itself. Thus, in order to implement the asymmetric behavior, the bitmaps of the real-time processes are modified so that only the bit associated with the corresponding shielded CPU is set; conversely, the bitmaps of the non-real-time processes are modified so that the bits of all shielded CPUs are cleared.

A real-time partition might include more than one real-time process. Scheduling among the real-time partition is still achieved by the standard Linux scheduler, so the standard Linux static and dynamic priorities are honored. In this case, of course, it's up to the developer of the real-time application to ensure that the deadlines of each process are always caught.

The list of real-time processes assigned to a real-time partition may also be empty: this is intended for those applications that do

not need to do anything more than handling the interrupts coming from some hardware device. In this case, the device handled in a real-time partition can be seen as a *smart device*, that is, a device with the computational power of a standard processor.

The ASMP-Linux patch modifies in a few places the scheduling algorithm of the standard Linux kernel. In particular, since version 2.6, Linux support the so-called scheduling domains [9]: the processors are evenly partitioned in domains, which are kept balanced by the kernel according to the physical characteristics of the CPUs. Usually, the load in CMP and CMT processors will be equally spread on all the physical chips. For instance, in a system having two physical processors chip0 and chip1, each of which being a 2-way CMT CPU, the standard Linux scheduler will try to put two running processes in such a way to assign one process to the first virtual processor of chip0 and the other one to the first virtual processor of chip1. Having both processes running on the same chip, one on each virtual processor, would be a waste of resource: an entire physical chip kept idle.

However, load balancing among scheduling domains is a time-consuming, unpredictable activity. Moreover, it is obviously useless for shielded processors, because only predefined processes can run on each shielded CPU. Therefore, the ASMP-LINUX patch changes the load balancing algorithm so that shielded CPUs are always ignored.

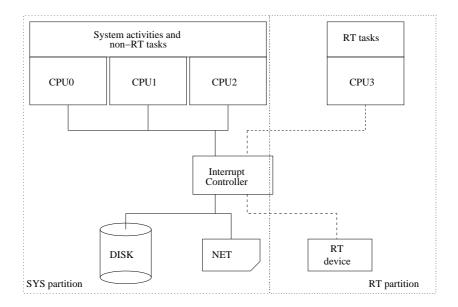

### 2.4.3 Interrupts handling

As mentioned in Section 1.2, interrupts are the major cause of jitter in real-time systems, because they are generated by hardware devices

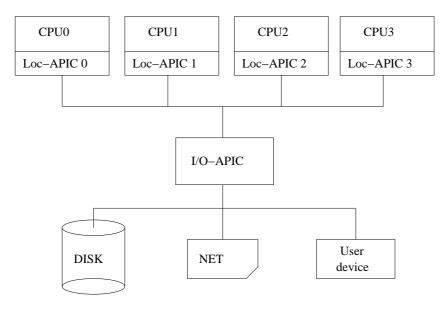

Figure 2.5: A SMP using Intel IO-APIC

asynchronously with respect to the process currently executed on a CPU. In order to understand how ASMP-LINUX manages this problem, a brief introduction on how interrupts are delivered to processors is required.

Most uni-processor and multiprocessor systems include one or more *Interrupt Controller* chips, which are capable to route interrupt signals to the CPUs according to predefined routing policies. Two routing policies are commonly found: either the Interrupt Controller propagates the next interrupt signal to one specific CPU (using, for example, a round-robin scheduling), or it propagates the signal to all the CPUs. In the latter case, the CPU that first stops the execution of its process and starts to execute the interrupt handler sends an acknowledgment signal to the Interrupt Controller, which frees

the others CPUs from handling the interrupt. Figure 2.5 shows a typical configuration for a multiprocessor system based on the IA-32 architecture.

A shielded process must receive only interrupts coming from selected, crucial hardware devices, otherwise the real-time application executing on the shielded processor will be affected by some unpredictable jitter. Fortunately, recent Interrupt Controller chips—such as the I/O Advanced Programmable Interrupt Controller (I/O-APIC) found in the Intel architectures—can be programmed in such a way to forward interrupt signals coming from specific IRQ lines to a set of predefined processors.

Thus, the ASMP-LINUX patch instruments the Interrupt Controller chips to forward general interrupts only to non-shielded CPUs, while the interrupts assigned to a given real-time partition are sent only to the corresponding shielded CPU.

However, a shielded processor can also receive interrupt signals that do not come from an Interrupt Controller at all. In fact, modern processors include an internal interrupt controller—for instance, in the Intel processors this component is called *Local APIC*. This internal controller receives the signals coming from the external Interrupt Controllers and sends them to the CPU core, thus interrupting the current execution flow. However, the internal controller is also capable to directly exchange interrupt signals with the interrupt controllers of the other CPUs in the system; these interrupts are said *Inter-Processor Interrupts*, or IPI. Finally, the internal controller could also generate a periodic self-interrupt, that is, a clock signal that will periodically interrupt the execution flow of its own

CPU core. This interrupt signal is called *local timer*.

In multiprocessor systems based on Linux, Inter-Processor Interrupts are commonly used to force all CPUs in the system to perform synchronization procedures or load balancing across CPUs, while the local timer is used to implement the time-sharing policy of each processor. As discussed in the previous sections, in ASMP-LINUX load balancing never affects shielded CPUs. Furthermore, it is possible to disable the local timer of a shielded CPU altogether. Of course, this means that the time-sharing policy across the processes running in the corresponding real-time partition is no longer enforced, thus the real-time tasks must implement some form of cooperative scheduling.

#### 2.4.4 Real-time inheritance

During its execution, a process could invoke kernel services by means of system calls. The ASMP-LINUX patch slightly modifies the service routines of a few system calls, in particular those related to process creation and removal: fork(), clone(), and exit(). In fact, those system calls affect some data structures introduced by ASMP-LINUX and associated with the process descriptor.

As a design choice, a process transmits its property of being part of a real-time partition to its children; it also maintains that property even when executing an exec()-like system call. If the child does not actually need the real-time capabilities, it can move itself to the non-real-time partition (see next section).

#### 2.4.5 ASMP-LINUX interface

ASMP-LINUX provides a simple /proc file interface to control which CPUs are shielded, as well as the real-time processes and interrupts attached to each shielded CPU. The interface could have been designed as system calls but this choice would have made the ASMP-LINUX patch less portable (system calls are universally numbered) and more intrusive.

Let's suppose that the system administrator wants to shield the second CPU of the system (CPU1), and that she wants to assign to the new real-time partition the process having PID X and the interrupt vector N. In order to do this, she can simply issue the following shell commands:

```

/bin/echo 1 > /proc/asmp/cpu1/shielded

/bin/echo X > /proc/asmp/cpu1/pids

/bin/echo N > /proc/asmp/cpu1/irqs

```

The first command makes CPU1 shielded.<sup>1</sup> The other two commands assign to the shielded CPU the process and the interrupt vector, respectively. Of course, more processes or interrupt vectors can be added to the real-time partition by writing their identifiers into the proper pids and irqs files as needed.

To remove a process or interrupt vector it is sufficient to write the corresponding identifier into the proper /proc file prefixed by the minus sign ("-"). Writing 0 into the file

<sup>&</sup>lt;sup>1</sup>Actually, the first command could be omitted in this case, because issuing either the second command or the third one will implicitly shield the target CPU.

#### /proc/asmp/cpu1/shielded

turns the real-time partition off: any process or interrupt in the partition is moved to the non-real-time partition, then the CPU is unshielded.

The /proc interface also allows the system administrator to control the local timers of the shielded CPUs. Disabling the local timer is as simple as typing:

#### /bin/echo 0 > /proc/asmp/cpu1/localtimer

The value written in the localtimer file can be either zero (timer disabled) or a positive scaling factor that represents how many ticks—that is, global timer interrupts generated by the Programmable Interval Timer chip—must elapse before the local timer interrupt is raised. For instance, writing the value ten into the localtimer file sets the frequency of the local timer interrupt to 1/10 of the frequency of the global timer interrupts.

Needless to say, these operations on the /proc interface of ASMP-LINUX can also be performed directly by the User Mode programs through the usual open() and write() system calls.

# 2.5 Experimental data

ASMP-LINUX provides a good foundation for an hard real-time operating system on COTS multiprocessor systems. To validate this claim, we performed two sets of experiments.

The first test, described in Section 2.5.2, aims to evaluate the operating system overhead of ASMP-LINUX: the execution time of

a real-time process executing a CPU-bound computation is measured under both ASMP-LINUX and a standard Linux 2.6.19.1 kernel, with different system loads, and on several hardware platforms.

The second test, described in Section 2.5.3, aims to evaluate the operating system latency of ASMP-LINUX: the local timer is reprogrammed in such a way to raise an interrupt signal after a predefined interval of time; the interrupt handler wakes a sleeping real-time process up. The difference between the expected wake-up time and the actual wake-up time is a measure of the operating system latency. The test has been carried on under both ASMP-LINUX and a standard Linux 2.6.19.1 kernel, with different system loads, and on several hardware platforms.

## 2.5.1 Experimental environments

Two different platforms were used for the experiments; Table 2.1 summarizes their characteristics and configurations.

| ID | Architecture | CPUs    | Freq. | RAM |

|----|--------------|---------|-------|-----|

|    |              |         | GHz   | GB  |

| S1 | IA-32 SMP HT | 8 virt. | 1.50  | 3   |

| S2 | IA-32 SMP    | 4 phys. | 1.50  | 3   |

| S3 | IA-32 CMP    | 2 cores | 1.83  | 1   |

**Table 2.1:** Characteristics of the test platforms

The first platform is a 4-way SMP Intel Xeon HT [15] system running at 1.50 GHz; every chip consists of two virtual processors (HT

stands for *HyperThreading Technology* [13]). The operating system sees each virtual processor as a single CPU. This system has been tested with HT enabled (configuration "S1") and disabled (configuration "S2").

The second platform (configuration "S3") is a desktop computer based on a 2-way CMT Intel processor running at 1.83 GHz. The physical processor chip contains two cores [17]. This particular version of the processor was the one used in laptop systems, optimized for power consumption.