See discussions, stats, and author profiles for this publication at: http://www.researchgate.net/publication/262642644

# Effect of postdeposition annealing on the electrical properties of β-Ga2O3 thin films grown on p-Si by plasma-enhanced atomic layer deposition

**ARTICLE** *in* JOURNAL OF VACUUM SCIENCE & TECHNOLOGY A VACUUM SURFACES AND FILMS · JULY 2014 Impact Factor: 2.14 · DOI: 10.1116/1.4875935

DOWNLOADS VIEWS

40 28

#### 4 AUTHORS, INCLUDING:

#### Inci Donmez

Barcelona Microelectronics Institute

25 PUBLICATIONS 77 CITATIONS

SEE PROFILE

#### Cagla Ozgit-Akgun

ASELSAN Inc.

42 PUBLICATIONS 106 CITATIONS

SEE PROFILE

#### Necmi Biyikli

**Bilkent University**

117 PUBLICATIONS 845 CITATIONS

SEE PROFILE

Available from: Cagla Ozgit-Akgun Retrieved on: 16 June 2015

# Effect of postdeposition annealing on the electrical properties of -Ga2O3 thin films grown on p-Si by plasma-enhanced atomic layer deposition

Halit Altuntas, Inci Donmez, Cagla Ozgit-Akgun, and Necmi Biyikli

Citation: Journal of Vacuum Science & Technology A 32, 041504 (2014); doi: 10.1116/1.4875935

View online: http://dx.doi.org/10.1116/1.4875935

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvsta/32/4?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Mechanical and electrical properties of plasma and thermal atomic layer deposited Al2O3 films on GaAs and Si J. Vac. Sci. Technol. A **31**, 041502 (2013); 10.1116/1.4804175

Influence of annealing temperature on electronic and dielectric properties of ZrO2 thin films on Si AIP Conf. Proc. **1451**, 242 (2012); 10.1063/1.4732428

Electrical characteristics of Ga 2 O 3 – TiO 2 nanomixed films grown by plasma-enhanced atomic-layer deposition for gate dielectric applications

Appl. Phys. Lett. 87, 082909 (2005); 10.1063/1.2034100

Origin of the stress-induced leakage currents in Al – Ta 2 O 5 SiO 2 – Si structures Appl. Phys. Lett. **86**, 152104 (2005); 10.1063/1.1900955

Electrical conduction transition and largely reduced leakage current in aluminum-doped barium strontium titanate thin films heteroepitaxially grown on Ir MgO Si (100)

Appl. Phys. Lett. 86, 132902 (2005); 10.1063/1.1896448

November 9-14, 2014 🚥 Baltimore, Maryland

### Effect of postdeposition annealing on the electrical properties of $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films grown on p-Si by plasma-enhanced atomic layer deposition

Halit Altuntasa)

Faculty of Science, Department of Physics, Cankiri Karatekin University, Cankiri 18100, Turkey

Inci Donmez, Cagla Ozgit-Akgun, and Necmi Biyikli<sup>b)</sup>

National Nanotechnology Research Center (UNAM), Bilkent University, Ankara 06800, Turkey and Institute of Materials Science and Nanotechnology, Bilkent University, Ankara 06800, Turkey

(Received 6 February 2014; accepted 28 April 2014; published 21 May 2014)

Ga<sub>2</sub>O<sub>3</sub> dielectric thin films were deposited on (111)-oriented p-type silicon wafers by plasma-enhanced atomic layer deposition using trimethylgallium and oxygen plasma. Structural analysis of the Ga<sub>2</sub>O<sub>3</sub> thin films was carried out using grazing-incidence x-ray diffraction. As-deposited films were amorphous. Upon postdeposition annealing at 700, 800, and 900 °C for 30 min under  $N_2$  ambient, films crystallized into  $\beta$ -form monoclinic structure. Electrical properties of the β-Ga<sub>2</sub>O<sub>3</sub> thin films were then investigated by fabricating and characterizing Al/β-Ga<sub>2</sub>O<sub>3</sub>/p-Si metal-oxide-semiconductor capacitors. The effect of postdeposition annealing on the leakage current densities, leakage current conduction mechanisms, dielectric constants, flat-band voltages, reverse breakdown voltages, threshold voltages, and effective oxide charges of the capacitors were presented. The effective oxide charges  $(Q_{\text{eff}})$  were calculated from the capacitance-voltage (C-V) curves using the flat-band voltage shift and were found as  $2.6 \times 10^{12}$ ,  $1.9 \times 10^{12}$ , and  $2.5 \times 10^{12}$  cm<sup>-2</sup> for samples annealed at 700, 800, and 900 °C, respectively. Effective dielectric constants of the films decreased with increasing annealing temperature. This situation was attributed to the formation of an interfacial SiO<sub>2</sub> layer during annealing process. Leakage mechanisms in the regions where current increases gradually with voltage were well fitted by the Schottky emission model for films annealed at 700 and 900°C, and by the Frenkel-Poole emission model for film annealed at 800°C. Leakage current density was found to improve with annealing temperature. β-Ga<sub>2</sub>O<sub>3</sub> thin film annealed at 800 °C exhibited the highest reverse breakdown field value. © 2014 American Vacuum Society. [http://dx.doi.org/10.1116/1.4875935]

#### I. INTRODUCTION

Group III-oxide materials such as gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), aluminum oxide, (Al<sub>2</sub>O<sub>3</sub>) and indium oxide (In<sub>2</sub>O<sub>3</sub>) are potential materials for advanced technologies. Among them, monoclinic gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) is finding rapidly growing applications because of its direct band gap of about 5 eV, its medium dielectric constant, and unique transparency at the visible and ultraviolet (UV) spectral regions. Ga<sub>2</sub>O<sub>3</sub> has five crystalline modifications ( $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$ , and  $\varepsilon$ ), among which  $\beta$ -form is the most stable one starting from room temperature to its melting point of about 1800 °C, while the other forms are metastable within this temperature range.<sup>2</sup> All of these properties make  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> a very good candidate for industrial applications such as dielectric materials for capacitors, high-temperature gas sensors,<sup>3</sup> perfect single-layer antireflection coatings for III-V semiconductor optoelectronic devices (because of its refractive index, which is close to  $\sqrt{n_{\text{GaAs}}}$ ), resistive switch memory devices, spintronic devices, etc. As another advantage,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> single crystal substrates are considered as an alternative to other traditional wide-bandgap semiconductors such as SiC, GaN, and diamond for high power device applications with low-cost and low energy consumptions. Over the last decade, Ga<sub>2</sub>O<sub>3</sub> thin films have been deposited using various techniques such as sputtering,<sup>8</sup> pulsed laser deposition, sol-gel method, molecular beam epitaxy, 11,12 metal-organic chemical vapor deposition, 13 electron beam evaporation, 14 and atomic layer deposition (ALD).4,15-19

As the film thicknesses scaled down to nanometers for industrial applications, an extensive search has begun for a suitable deposition technique. In this regard, ALD has distinguished itself with its ability to deposit ultrathin films with an excellent uniformity over large substrates. ALD is generally defined as a special type of chemical vapor deposition technique, where thin film deposition is based on sequential and self-terminating surface reactions. This distinct growth mechanism results with unique characteristics such as accurate thickness control at the atomic scale, excellent uniformity, and ultimate conformality. Although ALD is already being considered as a low-temperature thin film deposition method, temperatures used in ALD can be further decreased by enhancing the surface reactions using additional energy sources, such as plasma. Plasma-enhanced ALD (PEALD) is a widely used technique, in which plasma source creates highly reactive radicals that contribute to chemical reactions occurring at the surface. When compared to traditional thermal ALD, PEALD provides a wider range of materials. The first study on the PEALD of Ga<sub>2</sub>O<sub>3</sub> thin films was published by Shan et al.,4 in which [(CH<sub>3</sub>)<sub>2</sub>GaNH<sub>2</sub>]<sub>3</sub> and oxygen plasma were used as the reactants. Alternative ALD/PEALD

a)Electronic mail: altunhalit@gmail.com b) Electronic mail: biyikli@unam.bilkent.edu.tr

processes that use different precursor combinations were also studied for the deposition of  $Ga_2O_3$  films. <sup>15–20</sup> Recently, we have reported on the PEALD of  $Ga_2O_3$  thin films using trimethylgallium (TMG) and  $O_2$  plasma. <sup>18</sup>

Here we studied the effect of postdeposition annealing on the electrical characteristics of PEALD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films using current–voltage (I–V) and high-frequency capacitance–voltage (C-V) measurements at room temperature.

#### **II. EXPERIMENT**

Ga<sub>2</sub>O<sub>3</sub> thin films of 22.5 nm thickness were deposited on solvent cleaned p-type Si (111) substrates in a Fiji F200-LL PEALD reactor (Ultratech/Cambridge Nanotech, Inc.) using TMG as the Ga precursor and O<sub>2</sub> plasma as the oxidant. Ar was used as the carrier gas with flow rates of 60 and 200 sccm for TMG and O2, respectively. Depositions were carried out at a base pressure of 0.20-0.25 Torr. Postdeposition annealing of Ga<sub>2</sub>O<sub>3</sub> films was realized in a rapid thermal annealing (RTA) system (ATV-Unitherm, RTA SRO-704) at 700, 800, and 900 °C for 30 min under 100 sccm N2 flow. For structural characterization, grazing incidence x-ray diffraction (GIXRD) measurements were performed in a PANalytical X'Pert PRO MRD diffractometer operating at 45 kV and 40 mA, using Cu Kα radiation. Data were obtained within the 2Theta range of 10°-90° by the summation of eight scans, which were collected using 0.1° step size and 10 s counting time. FEI Tecnai G2 F30 transmission electron microscope (TEM) at an operating voltage of 300 kV was used for the high-resolution TEM (HR-TEM) imaging of Ga<sub>2</sub>O<sub>3</sub> thin films. Selected area electron diffraction (SAED) patterns were also obtained, which provided further crystallographic information. Thermo Scientific K-Alpha spectrometer equipped with a monochromatized Al Ka x-ray source was used to study the elemental compositions of films. Sputter depth profiling was carried out with a beam of Ar ions having an acceleration voltage and spot size of 1 kV and 400  $\mu$ m, respectively.

In order to investigate the electrical properties of annealed films, metal-oxide-semiconductor (MOS) structures were fabricated using PEALD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> as the oxide layer. Top Al rectifier contacts of 80 nm thickness were deposited by thermal evaporation (PVD Vapor-3S Thermal, Vaksis Ltd.), which were then patterned using the lift-off process. The measured capacitor area was 250 × 250  $\mu$ m<sup>2</sup>. For the formation of back Al ohmic contacts, samples were annealed in the RTA system at 450 °C for 2 min under 100 sccm N<sub>2</sub> flow.

#### **III. RESULTS AND DISCUSSION**

## A. Film structure and capacitance–voltage characteristics

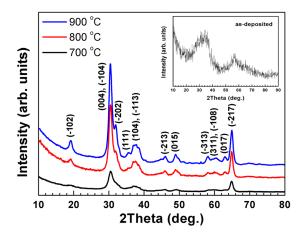

In their as-deposited state, PEALD-grown  $Ga_2O_3$  thin films were amorphous irrespective of the deposition temperature. <sup>18</sup> Figure 1 shows GIXRD patterns of the  $Ga_2O_3$  thin films, which were annealed at different temperatures (700, 800, and 900 °C) under  $N_2$  ambient. All the three patterns revealed the same reflections that correspond to polycrystalline  $\beta$ - $Ga_2O_3$  with a monoclinic structure (ICDD reference code:

Fig. 1. (Color online) GIXRD patterns of  $Ga_2O_3$  thin films, which were subjected to postdeposition annealing at 700, 800, and 900 °C. (Inset) GIXRD pattern of the as-deposited film.

00-011-0370). Crystallinity of the films improved with annealing temperature; as the annealing temperature increased, intensities of the peaks increased and peak profiles became sharper.

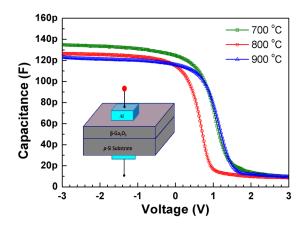

Figure 2 shows the effect of postdeposition annealing temperature on the capacitance–voltage (C-V) characteristics of Al/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitors. High-frequency C-V measurements were carried out at 1 MHz. The MOS capacitor fabricated using as-deposited Ga<sub>2</sub>O<sub>3</sub>, which was shown to exhibit an amorphous structure, did not show any C-V characteristics. C-V curves of the Al/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS capacitors revealed positive flat band voltages due to the negative effective oxide charges (Q<sub>eff</sub>), which is given as Q<sub>eff</sub> = Q<sub>ot</sub> + Q<sub>m</sub> + Q<sub>f</sub>, where Q<sub>ot</sub> is the oxide trapped charge, Q<sub>m</sub> is the mobile charge, and Q<sub>f</sub> is the fixed charge in the oxide films or at the interface. For the calculation of effective oxide charges, first dielectric constant ( $\varepsilon$ <sub>ox</sub>) values were obtained by the accumulation capacitance (C<sub>ox</sub>) formula, which is given as

$$C_{\rm ox} = \frac{\varepsilon_{\rm ox}\varepsilon_{\rm o}A}{t_{\rm ox}},\tag{1}$$

where  $\varepsilon_o$  is the permittivity of vacuum,  $t_{ox}$  is the thickness of the oxide layer (i.e.,  $\sim 22.5 \text{ nm}$ ), and A is the area of

Fig. 2. (Color online) High-frequency C-V curves of the  $\text{Al}/\beta\text{-}\text{Ga}_2\text{O}_3/p\text{-}\text{Si}$  MOS devices fabricated using  $\beta\text{-}\text{Ga}_2\text{O}_3$  thin films obtained via postdeposition annealing at 700, 800, and 900 °C.

Table I. Electrical parameters extracted from the high-frequency C-V curves.

| T <sub>ann.</sub> (°C) | λ-Debye length (cm)                                                  | $C_{\mathrm{FBS}}\left(\mathrm{F}\right)$                                  | $C_{\text{ox}}(F)$                                                   | $C_{\mathrm{FB}}\left(\mathrm{F}\right)$                             | $V_{\mathrm{FB}}\left(\mathbf{V}\right)$ | $\phi_{\rm ms}$ (eV)  | $\varepsilon_{ m ox}$ | $N_{\rm eff}~({\rm cm}^{-2})$                                  | $V_{\text{th}}\left(\mathbf{V}\right)$ |

|------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|-----------------------|-----------------------|----------------------------------------------------------------|----------------------------------------|

| 700<br>800<br>900      | $4.6 \times 10^{-6}$<br>$4.8 \times 10^{-6}$<br>$5.5 \times 10^{-6}$ | $1.42 \times 10^{-10}$<br>$1.35 \times 10^{-10}$<br>$1.19 \times 10^{-10}$ | $1.35 \times 10^{-10}$ $1.26 \times 10^{-10}$ $1.23 \times 10^{-10}$ | $6.91 \times 10^{-11}$ $6.52 \times 10^{-11}$ $6.06 \times 10^{-11}$ | 1.02<br>0.63<br>1.13                     | -0.88 $-0.88$ $-0.88$ | 5.4<br>5.1<br>5.0     | $2.6 \times 10^{12}$ $1.9 \times 10^{12}$ $2.5 \times 10^{12}$ | 1.90<br>1.50<br>1.97                   |

capacitors, which was calculated as  $6.25 \times 10^{-4}$  cm<sup>2</sup> from the optical microscopy images. By substituting these parameters into Eq. (1), the dielectric constants were estimated as 5.49, 5.12, and 5.00 for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films annealed at 700, 800, and 900 °C, respectively. The *p*-type Si surface at the flat-band condition ( $C_{\rm FBS}$ ) is given by

$$C_{\rm FBS} = \frac{\varepsilon_{\rm S\,i}\varepsilon_o}{\lambda},\tag{2}$$

where  $\varepsilon_{Si}$  is the dielectric constant of Si (i.e., 11.8) and  $\lambda$  is the Debye length of *p*-type Si, which is expressed as

$$\lambda = \left(\frac{\varepsilon_{\rm Si}\varepsilon_o kT}{q^2 N_A}\right)^{1/2},\tag{3}$$

where k is the Boltzmann constant, T is the absolute temperature, q is the electronic charge, and  $N_A$  is the doping concentration of p-type Si. The  $N_A$  values were calculated from the slopes of  $I/C^2$ -V graphs, and found as  $7.9 \times 10^{15}$ ,  $7.2 \times 10^{15}$ , and  $5.6 \times 10^{15}$  cm<sup>-3</sup> for capacitors fabricated using  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films annealed at 700, 800, and 900 °C, respectively. Following the calculation of  $C_{\rm FBS}$ , the flat-band capacitance ( $C_{\rm FB}$ ) values were obtained using the series capacitance relationship, which is given as

$$C_{\rm FB} = \frac{c_{\rm ox}c_{\rm FBS}}{c_{\rm ox} + c_{\rm FBS}}.$$

(4)

The flat-band voltage  $(V_{\rm FB})$  is the voltage value that corresponds to  $C_{\rm FB}$  on the high-frequency C-V curve.  $V_{\rm FB}$  values were found as 1.02, 0.63, and 1.13 V for the MOS capacitors fabricated using films annealed at 700, 800, and 900 °C, respectively. As mentioned previously, depending on their type, effective oxide charges  $(Q_{\rm eff})$  shift C-V curves to either left or right.  $Q_{\rm eff}$  values were extracted from corresponding C-V curves according to the equation

$$Q_{\rm eff} = \frac{c_{\rm ox}(\phi_{\rm ms} - V_{\rm FB})}{A},\tag{5}$$

where  $\phi_{\rm ms}$  is the difference between the work functions of metal (Al) and semiconductor (Si). Dividing the  $Q_{\rm eff}$  by q (=  $1.6\times 10^{-19}$  C) yields  $N_{\rm eff}$ , which is the effective density of oxide charges. The calculated parameters are presented in Table I. The  $N_{\rm eff}$  values were found as  $2.6\times 10^{12}$ ,  $1.9\times 10^{12}$ , and  $2.5\times 10^{12}$  cm<sup>-2</sup> for the films annealed at 700, 800, and 900 °C, respectively.

The second step is to present the effect of annealing on the threshold onset voltage  $(V_{\rm th})$  of capacitors. This

parameter, for strong inversion of the MOS device (*p*-type substrate), is given by<sup>21</sup>

$$V_{\text{th}} = V_{\text{FB}} + 1\phi_b + \frac{(4q\varepsilon_{\text{Si}}\varepsilon_o N_A/\phi_b)^{1/2}}{\varepsilon_{\text{ox}}\varepsilon_o/t_{\text{ox}}},\tag{6}$$

where  $\phi_b = (k_B T/q) \ln(N_A/n_i)$  and  $n_i$  is the intrinsic carrier concentration of Si at room temperature (i.e.,  $1.45 \times 10^{10}$  cm<sup>-3</sup>). By the substitution of these parameters into Eq. (6),  $V_{\rm th}$  values were calculated as 1.90, 1.50, and 1.97 V for the MOS capacitors fabricated using films annealed at 700, 800, and 900 °C, respectively. The smallest onset threshold voltage was found for the capacitor fabricated using a Ga<sub>2</sub>O<sub>3</sub> layer annealed at 800 °C.

As already reported in our previous work, 18 thicknesses and optical constants of Ga<sub>2</sub>O<sub>3</sub> thin films were estimated using spectroscopic ellipsometry. Ellipsometric spectra of the as-deposited and annealed Ga<sub>2</sub>O<sub>3</sub> thin films were modeled by the Cauchy dispersion function (within the wavelength range of 300-1000 nm) using a model which consists of three layers, i.e., Si/SiO<sub>2</sub>/Cauchy (Ga<sub>2</sub>O<sub>3</sub>). Thickness of the as-deposited film did not change remarkably upon the postdeposition annealing processes. As-deposited Ga<sub>2</sub>O<sub>3</sub> thin films were amorphous (see inset of Fig. 1). Upon annealing at various temperatures (700-900 °C) for 30 min under the N<sub>2</sub> atmosphere, film crystallized into monoclinic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> phase. As a result of this amorphous-to-crystalline phase transition, refractive index values increased slightly from 2.05-1.86 to 2.09-1.92 within the 300-1000 nm spectral range. 18 Since the refractive index of a material is related to its mass density, an increase in the refractive index values indicates denser films.<sup>22-24</sup> In general, structural enhancement and/or densification of the film should improve the dielectric constant value.<sup>25</sup> However, as seen in Fig. 2, the

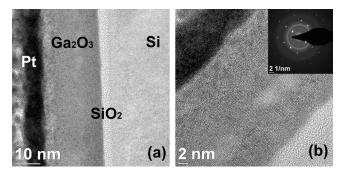

Fig. 3. (a) Cross-sectional TEM, and (b) HR-TEM images of  $Ga_2O_3$  thin film after postdeposition annealing at 900 °C under  $N_2$  ambient. (Inset) SAED pattern of the same sample.

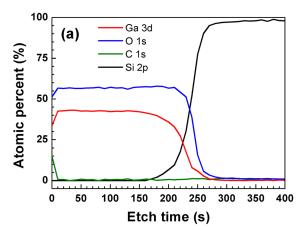

Fig. 4. (Color online) Compositional depth profiles of (a) as-deposited and (b) annealed  ${\rm Ga_2O_3}$  thin films.

oxide capacitance decreased with increasing annealing temperature, which resulted in reduced effective dielectric constant values.

The reduction in effective dielectric constant can be attributed to the formation of an interfacial SiO<sub>2</sub> layer during the postdeposition annealing process as SiO<sub>2</sub> has a lower dielectric constant than that of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. SiO<sub>2</sub> formation at the metal-oxide/Si interface was also reported in literature. 15,26 It occurs due to the susceptibility of Si substrate to oxidation, and the thickness of SiO2 increases with increasing annealing temperatures. In order to obtain information about the thicknesses of interfacial  $SiO_2$  and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layers, cross-sectional HR-TEM imaging was performed (Fig. 3). Cross-sectional HR-TEM image and SAED pattern of the as-deposited film are given elsewhere.<sup>27</sup> The formation of an interfacial SiO<sub>2</sub> layer was observed from the TEM image given in Fig. 3(a). SAED measurements were also carried out, from which crystallographic information was provided. As shown in Fig. 3(b), the Ga<sub>2</sub>O<sub>3</sub> thin film, which was subjected to postdeposition annealing at 900 °C, is polycrystalline. This was further confirmed by SAED, where the diffraction rings indicated a polycrystalline nature [inset of Fig. 3(b)].

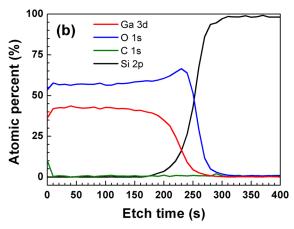

In order to study the uniformity of elemental composition toward the bulk film and Ga<sub>2</sub>O<sub>3</sub>/Si interface, depth profile analyses were performed on both as-deposited and annealed

Table II. Atomic concentrations of Ga, O, and C in the as-deposited and annealed  $Ga_2O_3$  thin films.

|            | As-depo      | osited    | Annealed     |           |  |  |

|------------|--------------|-----------|--------------|-----------|--|--|

|            | Film surface | Bulk film | Film surface | Bulk film |  |  |

| Ga (at. %) | 33.64        | 41.30     | 36.30        | 43.61     |  |  |

| O (at. %)  | 51.42        | 58.70     | 53.60        | 56.39     |  |  |

| C (at. %)  | 14.94        | 0         | 10.10        | 0         |  |  |

| Ga/O       | 0.654        | 0.704     | 0.677        | 0.773     |  |  |

samples ( $T_{ann.} = 900\,^{\circ}\text{C}$ ), results of which are given in Figs. 4(a) and 4(b), respectively. Measurements were recorded for each film using the exact same sputtering procedure. C was detected only at the film surface and was completely removed after 10 s of Ar ion etching, indicating that it originates from surface contamination. Uniform composition throughout the bulk film was observed for all samples and listed in Table II. The highest Ga/O ratio was found for the sample annealed at  $900\,^{\circ}\text{C}$ , which can be attributed to the oxide formation at the  $Ga_2O_3/Si$  interface. O content was also observed to increase at the interface [Fig. 4(b)], featuring the same phenomena.

#### B. Leakage current conduction mechanisms

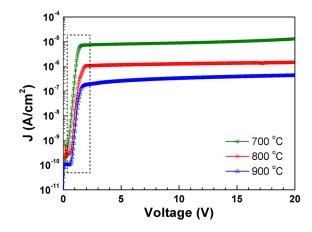

Leakage current characteristics of the PEALD-grown Ga<sub>2</sub>O<sub>3</sub> thin films subjected to postdeposition annealing at 700, 800, and 900 °C are given in Fig. 5. The data clearly show that the leakage current density decreases with increasing annealing temperature. A leakage current density value, as small as 264 pA at 20 V, was measured for the film annealed at 900 °C. In order to comment on the effect of annealing temperature on leakage current, the current conduction mechanisms were explored. In Fig. 5, a rectangular region has been indicated, where leakage current increases rapidly with the gate voltage. The current conduction mechanisms that cause these increases must be explained. As known, three basic conduction mechanisms have been

Fig. 5. (Color online) Leakage current characteristics of  $Al/\beta$ - $Ga_2O_3/p$ -Si MOS devices fabricated using  $Ga_2O_3$  thin films annealed at different temperatures. The region, where leakage currents increase rapidly with the applied voltage, is denoted on the figure.

proposed to explain leakage current in MOS devices.<sup>28</sup> These are Schottky emission (SE), Frenkel–Poole emission (FP), and Fowler–Nordheim (FN) tunneling. FN tunneling generally dominates at high electric fields, while FP and SE dominates at lower fields. The related leakage current expressions are given as follows:

For SE,

$$J \propto A^* T^2 \exp \left[ \frac{-q \left( \phi_{\rm B} - \sqrt{qE/4\pi\varepsilon_r \varepsilon_o} \right)}{k_{\rm B} T} \right], \tag{7}$$

and for FP emission,

$$J \propto E \exp \left[ \frac{-q \left( \phi_{\rm B} - \sqrt{qE/\pi \varepsilon_r \varepsilon_o} \right)}{k_{\rm B} T} \right],$$

(8)

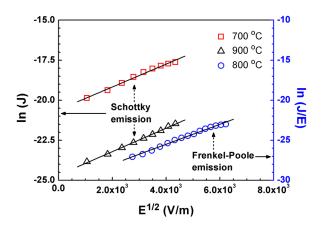

where J is the current density, E is the electric field,  $A^*$  is the effective Richardson constant,  $\phi_{\rm B}$  is the barrier height, and  $\varepsilon_r$  is the dielectric constant of the oxide. These equations were used to analyze leakage current behaviors at the low electric field side, in which current increases rapidly with the gate voltage. Using Eq. (7),  $\varepsilon_r$  value can be calculated from the ln J versus  $E^{1/2}$  plot if SE applies. On the other hand,  $\varepsilon_r$ value can be calculated from the  $\ln J/E$  versus  $E^{1/2}$  plot if FP applies. The leakage current values in the denoted region (Fig. 5) were well fitted with the SE mechanism for thin films annealed at 700 and 900 °C as shown in Fig. 6. From the  $\ln J$  versus  $E^{1/2}$  graph,  $\phi_{\rm B}$  and  $\varepsilon_{r}$  were calculated as 0.52 and 0.65 eV, and 4.4 and 4.1 eV for the films annealed at 700 and 900 °C, respectively. These dielectric constant values are in good agreement with those estimated from high-frequency C-V measurements. Leakage current behavior was found to be different for the Ga2O3 thin film annealed at 800 °C, as the leakage current values in the denoted region were well fitted with the FP mechanism. From the  $\ln J/E$  versus  $E^{1/2}$  plot,  $\phi_{\rm B}$  and  $\varepsilon_{\rm r}$  values were calculated as 0.78 eV and 5.08, respectively. This dielectric

Fig. 6. (Color online) Fitting of the data with Schottky and Frenkel-Poole emission models for the determination of leakage current behaviors of Al/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS devices fabricated using Ga<sub>2</sub>O<sub>3</sub> thin films annealed at different temperatures.

constant value agrees perfectly with the value obtained from the high-frequency C-V measurements (i.e., 5.00). In the Schottky emission, an electron overcomes the potential energy barrier at the metal-oxide or insulator interface. Therefore, this mechanism is controlled by the quality of metal-oxide or insulator interface. However, in the FP emission, electrons tunnel via trap states in the oxide layer. It is apparent from Fig. 5 that the leakage current characteristics improve at higher postdeposition annealing temperatures. This may be caused by several reasons. First, it has been reported in the literature that annealing could change the barrier heights of metal-insulator-semiconductor devices. 25,28-32 Second, as mentioned in our recent work, <sup>18</sup> annealing process increases the bandgap energies of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films. The increase in bandgap energies with postdeposition annealing temperature is consistent with the improvement observed in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film quality. Hence the insulating properties of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films can be said to enhance with increasing annealing temperature, and this behavior might be related to reduced leakage currents. A similar behavior was also observed by Shan et al. Finally, for annealing temperatures ranging from 700 to 900 °C, an interfacial SiO<sub>2</sub> layer forms at the Si/β-Ga<sub>2</sub>O<sub>3</sub> interface. This results in decreased leakage currents since SiO<sub>2</sub> possesses a larger band gap (9 eV) as compared to  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (5 eV). In addition, as the annealing temperature increases to 900 °C, SiO<sub>2</sub> dielectric layer becomes thicker. The total thickness of the dielectric layer therefore increases, which reduces the tunneling probability and results in lower leakage currents. As a result, leakage current density decreases with increasing annealing temperature.

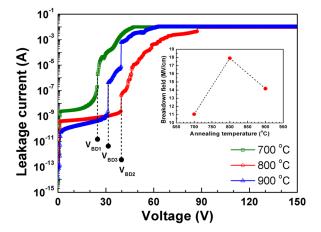

Reverse breakdown curves of the Al/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS devices are given in Fig. 7, where V<sub>BD1</sub>, V<sub>BD2</sub>, and V<sub>BD3</sub> represent the breakdown voltages for the films annealed at 700, 800, and 900 °C, respectively. As can be seen from Fig. 7, V<sub>BD2</sub> > V<sub>BD3</sub> > V<sub>BD1</sub>. On the other hand, the effective oxide charge values were found to be N<sub>BD2</sub> < N<sub>BD3</sub> < N<sub>BD1</sub>, where N<sub>BD1</sub>, N<sub>BD2</sub>, and N<sub>BD3</sub> are the effective oxide charges for the films annealed at 700, 800, and 900 °C, respectively (see

Fig. 7. (Color online) Reverse breakdown curves of the  $Al/\beta$ - $Ga_2O_3/p$ -Si MOS devices. (Inset) Breakdown field as a function of annealing temperature.

Table I). The film annealed at 800 °C was found to exhibit the lowest effective oxide charge and the highest reverse breakdown field. This situation may be attributed to the correlation between the effective oxide charge and the reverse breakdown field of Al/β-Ga<sub>2</sub>O<sub>3</sub>/p-Si MOS structures. Charge trapping is one of the most important parameters for oxide reliability since high charge trapping in oxide eventually leads to breakdown.<sup>33</sup> Similar behaviors have also been reported in literature.34,35 There are only few studies about the electrical characteristics of Ga<sub>2</sub>O<sub>3</sub> thin films. The reported oxide breakdown values for thermally oxidized layers were reported as 0.05-0.10,  $^{36}$  0.65,  $^{37}$  1.00,  $^{38}$  and 3.85 MV/cm,  $^{39}$  where those for thin films deposited using PEALD and e-beam evaporation were given as 1.00-1.50<sup>4</sup> and 3.60 MV/cm, <sup>40</sup> respectively. The oxide breakdown field depends primarily on the deposition method and fabrication technology. In this study, oxide breakdown field for the PEALD-grown β-Ga<sub>2</sub>O<sub>3</sub> thin films was measured as 18 MV/cm, which is higher than the values reported in literature.

#### IV. SUMMARY AND CONCLUSIONS

In this work,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films were successfully deposited on p-type Si substrates by PEALD at low temperatures. Ga<sub>2</sub>O<sub>3</sub> thin films, which were amorphous in their as-deposited state, were then annealed at 700, 800, and 900 °C for 30 min under N<sub>2</sub> ambient in order to obtain polycrystalline  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films with a monoclinic structure. GIXRD results showed that the crystalline quality of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> films improves with the annealing temperature. The effects of postdeposition annealing on the leakage current densities, leakage current conduction mechanisms, dielectric constants, flat-band voltages, threshold voltages, and effective oxide charges of the capacitors were presented. Leakage current density was found to decrease with increasing annealing temperature. Leakage current conduction mechanisms were found as Schottky emission for the films annealed at 700 and 900 °C, and as Frenkel-Poole emission for the film annealed at 800 °C. The smallest effective oxide charge and threshold voltage, and the highest reverse breakdown field values were found for the β-Ga<sub>2</sub>O<sub>3</sub> thin films annealed at 800 °C. The oxide breakdown field value measured for the PEALD-grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films was found to be higher than the values reported in literature. These results suggest that Ga<sub>2</sub>O<sub>3</sub> thin films, when subjected to annealing treatment following their deposition by PEALD at low temperatures, can be used for the fabrication of electrical devices such as MOS capacitors.

#### **ACKNOWLEDGMENTS**

This work was performed at UNAM supported by the State Planning Organization (DPT) of Turkey through the National Nanotechnology Research Center Project. The authors acknowledge M. Guler from UNAM for TEM measurements. N. Biyikli acknowledges Marie Curie International Reintegration Grant (IRG) for funding NEMSmart (PIRG05-GA-2009-249196) project.

- <sup>1</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

- <sup>2</sup>G. A. Battiston, R. Gerbasi, M. Porchia, R. Bertoncello, and F. Caccavale, Thin Solid Films **279**, 115 (1996).

- <sup>3</sup>C. T. Lee and J. T. Yan, Sens. Actuators B **147**, 723 (2010).

- <sup>4</sup>F. K. Shan, G. X. Liu, W. J. Lee, G. H. Lee, I. S. Kim, and B. C. Shin, J. Appl. Phys. **98**, 023504 (2005).

- <sup>5</sup>K. Shimamura, E. G. Villora, K. Domen, K. Yui, K. Aoki, and N. Ichinose, Jpn. J. Appl. Phys. **44**, L7 (2005).

- <sup>6</sup>A. A. Dakhel, Microelectron. Reliab. **52**, 1050 (2012).

- <sup>7</sup>E. G. Villora, K. Shimamura, Y. Yoshikawa, K. Aoki, and N. Ichinose, J. Cryst. Growth **270**, 420 (2004).

- <sup>8</sup>Y. Zhano, J. Yan, Q. Li, L. Zhang, and T. Li, Physica B **406**, 3079 (2011).

- <sup>9</sup>S. A. Lee, J. Y. Hwang, J. P. Kim, S. Y. Jeong, and C. R. Cho, Appl. Phys. Lett. 89, 182906 (2006).

- <sup>10</sup>Y. Kokubun, K. Miura, F. Endo, and S. Nakagomi, Appl. Phys. Lett. 90, 031912 (2007).

- <sup>11</sup>T. Oshima, T. Okuno, and S. Fujita, Jpn. J. Appl. Phys. 46, 7217 (2007).

- <sup>12</sup>O. Bierwagen, M. E. White, M. Y. Tsai, and J. S. Speck, *Molecular Beam Epitaxy: From Research to Mass Production*, edited by M. Henini (Elsevier Science, 2012), p. 347.

- <sup>13</sup>H. W. Kim, N. H. Kim, and C. Lee, J. Mater. Sci. 39, 3461 (2004).

- <sup>14</sup>M. F. Al-Kuhaili, S. M. A. Durrani, and E. E. Khawaja, Appl. Phys. Lett. 83, 4533 (2003).

- <sup>15</sup>G. X. Liu, F. K. Shan, W. J. Lee, B. C. Shin, S. Kim, H. S. Kim, and C. R. Cho, Integr. Ferroelectr. **94**, 11 (2007).

- <sup>16</sup>N. J. Seong, S. G. Yoon, and W. J. Lee, Appl. Phys. Lett. 87, 082909 (2005).

- <sup>17</sup>G. X. Liu, F. K. Shan, W. J. Lee, G. H. Lee, I. S. Kim, and B. C. Shin, Integr. Ferroelectr. **85**, 155 (2006).

- <sup>18</sup>I. Donmez, C. Ozgit-Akgun, and N. Biyikli, J. Vac. Sci. Technol. A 31, 01A110 (2013).

- <sup>19</sup>S. A. Lee, J. Y. Hwang, J. P. Kim, C. R. Cho, W. J. Lee, and S. Y. Jeong, J. Korean Phys. Soc. 47, S292 (2005).

- <sup>20</sup>F. K. Shan, G. X. Liu, W. J. Lee, G. H. Lee, I. S. Kim, and B. C. Shin, Integr. Ferroelectr. **80**, 197 (2006).

- <sup>21</sup>R. S. Muller and T. I. Kamins, *Device Electronics for Integrated Circuits*,

<sup>21</sup> 2nd ed. (Wiley, New York, 1986).

- <sup>22</sup>W. Rzodkiewicz and A. Panas, Acta Phys. Pol. A **116**, S92 (2009).

- <sup>23</sup>N. Kitamura, K. Fukumi, J. Nishii, and N. Ohno, J. Appl. Phys. 101, 123533 (2007).

- <sup>24</sup>K. Taniguchi, M. Tanaka, and C. Hamaguchi, J. Appl. Phys. 67, 2195 (1990).

- <sup>25</sup>W. Yang, J. Marino, A. Monson, and C. A. Wolden, Semicond. Sci. Technol. 21, 1573 (2006).

- <sup>26</sup>See: http://www.doitpoms.ac.uk/tlplib/ellingham\_diagrams/interactive.html

- <sup>27</sup>H. Altuntas, I. Donmez, C. Ozgit-Akgun, and N. Biyikli, J. Alloy Compd. 593, 190 (2014).

- <sup>28</sup>S. M. Sze, in *Physics of Semiconductor Devices* (Wiley, New York, 1981), Chap. 6.

- <sup>29</sup>J. Y. Tewg, Y. Kuo, J. Lu, and T. Wu, J. Electrochem. Soc. **151**, F59 (2004).

- <sup>30</sup>S. Chakraborty, M. K. Bera, S. Bhattacharya, and C. K. Maiti, Microelectron. Eng. 81, 188 (2005).

- <sup>31</sup>J. S. Lee, S. J. Chang, J. F. Chen, S. C. Sun, C. H. Liu, and U. H. Liaw, Mater. Chem. Phys. 77, 242 (2003).

- <sup>32</sup>C. S. Chang, T. P. Liu, and T. B. Wu, J. Appl. Phys. **88**, 7242 (2000).

- <sup>33</sup>R. M. Ayub, S. Norhafizah, A. H. Azman, U. Hashim, and T. Adam, J. Appl. Sci. Res. 9, 3451 (2013).

- <sup>34</sup>Y. H. Wong and K. Y. Cheong, J. Electrochem. Soc. **158**, H1270 (2011).

- <sup>35</sup>B. H. Lee, Y. Jeon, K. Zawadzki, W. J. Qi, and J. Lee, Appl. Phys. Lett. 74, 3143 (1999).

- <sup>36</sup>E. D. Readinger, S. D. Wolter, D. L. Waltemyer, J. M. Delucca, S. E. Mohney, B. I. Prenitzer, L. A. Giannuzzi, and R. J. Molnar, J. Electron. Mater. 28, 257 (1999).

- <sup>37</sup>Y. Zhou *et al.*, Solid State Electron. **52**, 756 (2008).

- <sup>38</sup>L. M. Lin, Y. Luo, P. T. Lai, and K. M. Lau, Thin Solid Films **515**, 2111 (2006).

- H. Kim, S.-J. Park, and H. Hwang, J. Vac. Sci. Technol. B 19, 579 (2001).

M. Passlack *et al.*, J. Appl. Phys. 77, 686 (1995).