## Conception sur silicium de convertisseurs analogique-numérique haut débit pour le radiotélescope SKA

Bruno Da Silva

#### ▶ To cite this version:

Bruno Da Silva. Conception sur silicium de convertisseurs analogique-numérique haut débit pour le radiotélescope SKA. Autre. Université d'Orléans, 2010. Français. <NNT: 2010ORLE2023>. <tel-01128247>

HAL Id: tel-01128247

https://tel.archives-ouvertes.fr/tel-01128247

Submitted on 9 Mar 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ D'ORLÉANS

#### ÉCOLE DOCTORALE SCIENCES ET TECHNOLOGIES

#### STATION DE RADIOASTRONOMIE DE NANCAY

## THÈSE

présentée par :

#### Bruno DA SILVA

soutenue le : 23 septembre 2010

pour obtenir le grade de : Docteur de l'université d'Orléans

Discipline/ Spécialité : Électronique, Microélectronique, Optique et Lasers

option électronique microondes

Conception sur silicium de convertisseurs analogique-numérique haut débit pour le radiotélescope SKA

THÈSE dirigée par :

**RAPPORTEURS:**

Bruno BARELAUD

Nicole CORNILLEAU-WEHRLIN

Stéphane BOSSE

Jacques LECOQ

#### JURY:

Rachid HARBA Directeur du LESI d'Orléans Président du jury Bruno BARELAUD Professeur à l'Université de Limoges Rapporteur Jacques LECOQ Directeur du pôle de microélectronque Rapporteur

à l'IN2P3 de Clermont-Ferrand

Nicole CORNILLEAU-WEHRLIN Directrice de recherche Directrice de thèse

à la station de radioastronomie de Nançay

Stéphane BOSSE Ingénieur de recherche Encadrant de thèse

à la station de radioastronomie de Nançay

Philippe CAIS Ingénieur de recherche Examinateur

au laboratoire d'astrophysique de Bordeaux

## Remerciements

Dans un premier temps je voudrais remercier Mme. Nicole Cornilleau-Wehrlin pour son encadrement au sein de la Station de Radioastronomie de Nançay ainsi que le responsable du service électronique Ivan Thomas.

Un merci tout particulier à toute l'équipe de microélectronique de la Station de Radioastronomie de Nançay et notamment M. Stéphane Bosse responsable de mon encadrement au sein du laboratoire ainsi que Severin Barth , qui ont su me faire confiance et me donner les moyens nécessaires au bon déroulement de cette thèse.

Merci à M. Jacques Lecoq de l'IN2P3 de Clermont-Ferrand et M. Bruno Barelaud du laboratoire de XLIM à Limoges qui ont accepté d'être les rapporteurs de ma thèse.

Je remercie M. Rachid Harba et M. Philippe Caïs d'avoir acceptés d'être membres du jury de ma thèse.

Merci à M. Guillaume Monnerie de l'entreprise NXP d'avoir fait le déplacement pour assister à ma thèse.

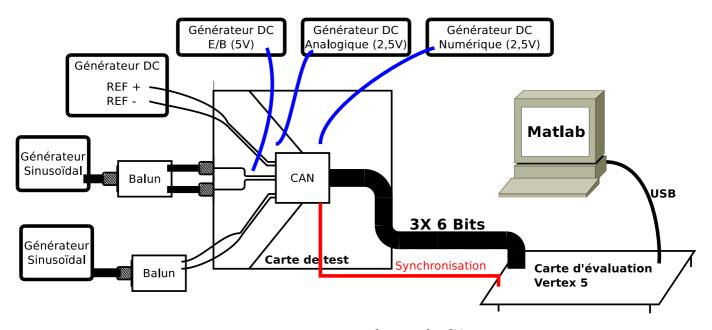

Je remercie aussi M. Cédric Viou qui a programmé le FPGA de la carte de test du premier CAN et apporté des solutions pour la conception du second CAN.

Merci aussi aux personnes du service électronique de la station pour leur aide pour la conception des cartes électroniques et leurs conseils.

Enfin, je tiens à remercier Marion, sans qui, je n'aurais pas pu réaliser cette thèse.

# Table des matières

| R  | emer   | rciements                                                        | iii  |

|----|--------|------------------------------------------------------------------|------|

| Li | iste d | les figures                                                      | xiv  |

| Li | iste d | les tableaux                                                     | xvi  |

| Li | iste d | les abréviations                                                 | xvii |

| Li | iste d | les symboles                                                     | xix  |

| Ir | ntroc  | duction                                                          | 1    |

|    | 0.1    | Contexte scientifique                                            | 2    |

|    | 0.2    | Objectifs                                                        | 5    |

|    | 0.3    | Choix des paramètres du CAN pour le radiotélescope SKA           | 7    |

|    | 0.4    | Organisation du mémoire                                          | 9    |

| Ι  | Ra     | appel sur les notions de base des CAN et les composants utilisés | 11   |

| 1  | Rap    | opel sur les transistors                                         | 13   |

|    | 1.1    | Contrainte technologique                                         | 13   |

|    | 1.2    | Caractéristiques principales des transistors NMOS et PMOS        | 14   |

|    | 1.3    | Caractéristiques principales du transistor Bipolaire SiGeC NPN   | 15   |

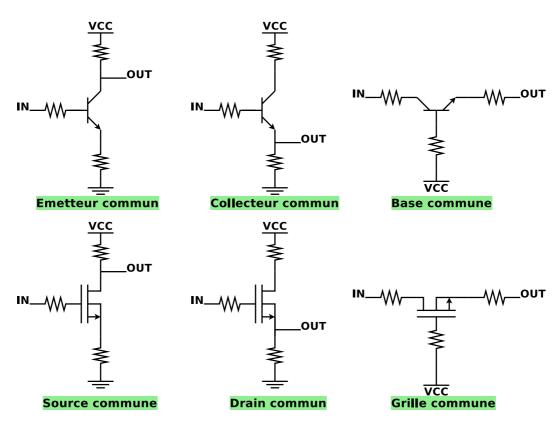

|    | 1.4    | Rappel sur les topologies de base de transistor                  | 16   |

| 2  | Not    | tions de base sur les CAN                                        | 19   |

|    | 2.1    | Caractéristiques générales d'un CAN                              | 19   |

|    | 2.2    | Caractérisation des erreurs                                      | 22   |

|    |        | 2.2.1 Les erreurs statiques                                      | 23   |

|    |        | 2.2.2 Les erreurs dynamiques                                     | 25   |

|    | 2.3    | Les CAN rapides                                                  | 27   |

#### TABLE DES MATIÈRES

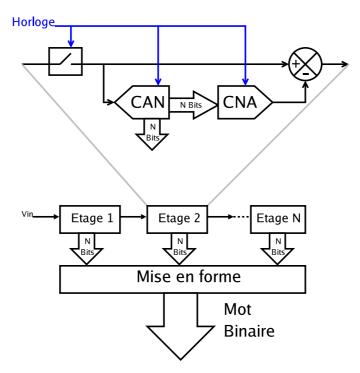

|    |      | 2.3.1  | Le CAN pipeline et le CAN flash                               | 28 |

|----|------|--------|---------------------------------------------------------------|----|

|    | 2.4  | Les di | fférentes améliorations possibles d'architecture du CAN flash | 30 |

|    |      | 2.4.1  | Le CAN flash à temps-entrelacé                                | 30 |

|    |      | 2.4.2  | Le CAN flash à architecture pliée                             | 31 |

|    |      | 2.4.3  | Le CAN flash à architecture interpolée                        | 31 |

|    | 2.5  | Choix  | de l'architecture du convertisseur                            | 32 |

|    |      |        |                                                               |    |

| II |      |        | et réalisation d'un CAN flash à 1 Giga échantillons par sec-  |    |

| Ol | ade  | en tra | ansistors MOS 0,25 $\mu m$                                    | 33 |

| In | trod | uction |                                                               | 35 |

| 3  | Sim  | ulatio | n et réalisation                                              | 37 |

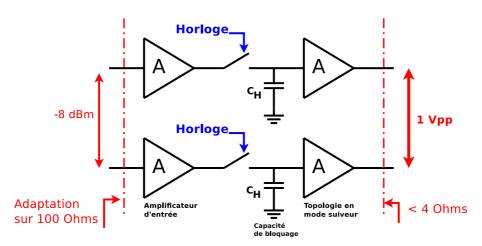

|    | 3.1  | L'Ech  | antillonneur Bloqueur                                         | 37 |

|    |      | 3.1.1  | Définition d'un échantillonneur-bloqueur                      | 37 |

|    |      | 3.1.2  | L'échantillonneur-bloqueur                                    | 38 |

|    |      | 3.1.3  | Les spécifications ciblées pour l'E/B                         | 40 |

|    |      | 3.1.4  | Echantillonneur-bloqueur développé                            | 41 |

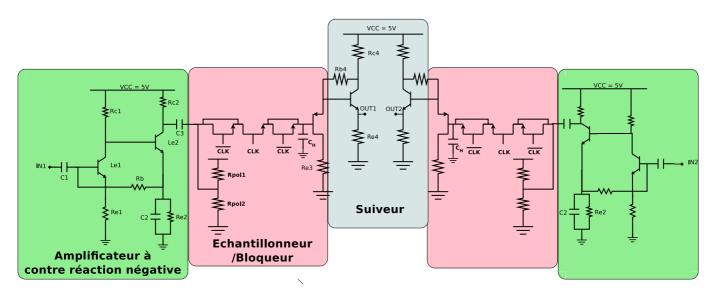

|    |      | 3.1.5  | Topologie entière de l'E/B                                    | 43 |

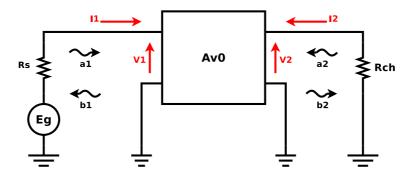

|    |      | 3.1.6  | Amplificateur à contre réaction                               | 44 |

|    |      | 3.1.7  | Rappel sur les paramètres S (Scatterring parameters)          | 46 |

|    |      | 3.1.8  | Impédance de la sortie                                        | 49 |

|    |      | 3.1.9  | Schéma final de l'E/B réalisé et les résultats de simulation  | 50 |

|    | 3.2  | Le cor | mparateur                                                     | 55 |

|    |      | 3.2.1  | Le pré-amplificateur                                          | 55 |

|    |      | 3.2.2  | Le comparateur à verrouillage                                 | 59 |

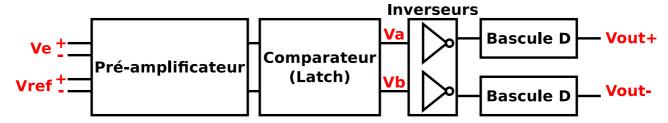

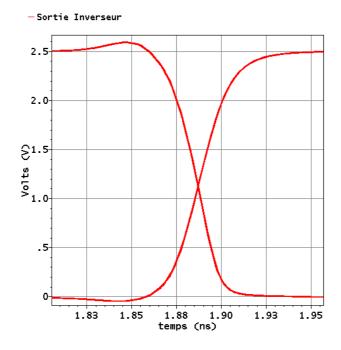

|    |      | 3.2.3  | La remise en forme                                            | 62 |

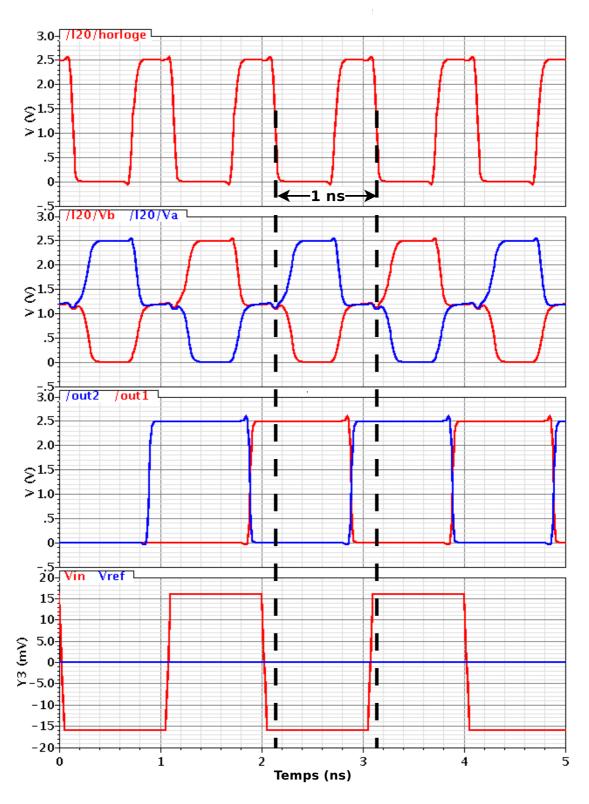

|    |      | 3.2.4  | Schéma final réalisé et résultats de simulation               | 62 |

|    |      | 3.2.5  | Résultat de simulation                                        | 64 |

|    | 3.3  | Échell | e de résistance                                               | 66 |

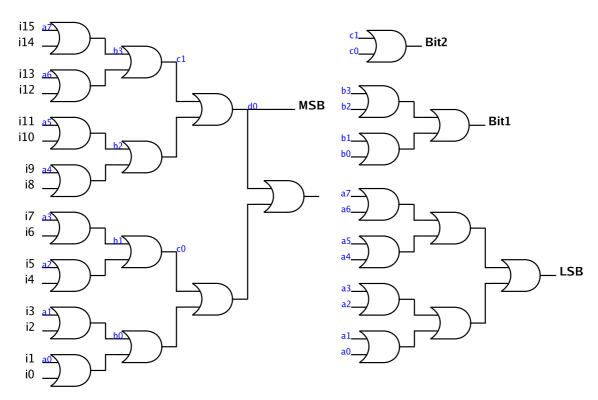

|    | 3.4  | Décod  | lage en mot binaire                                           | 67 |

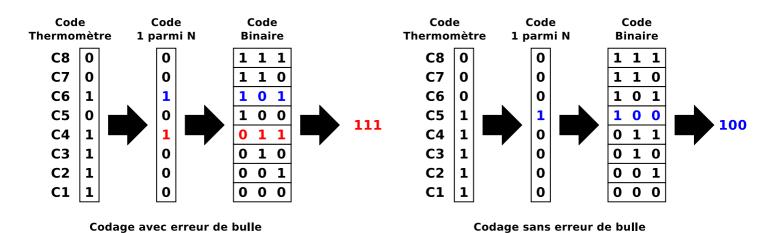

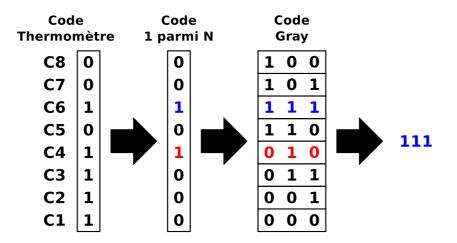

|    |      | 3.4.1  | Correction de bulle                                           | 68 |

|    |      | 3.4.2  | Le décodeur                                                   | 69 |

|    |      | 3.4.3  | Correction de bulle et décodeur choisis                       | 72 |

|    | 3.5  | Éléme  | ents supplémentaires en vue des tests ultérieurs              | 73 |

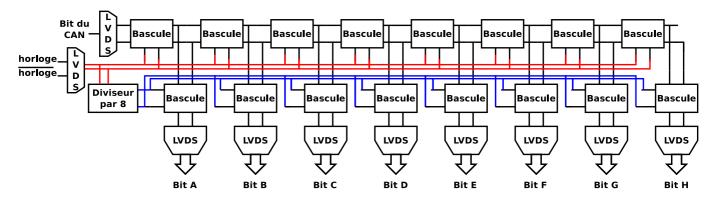

|    |      | 3.5.1  | Registre à décalage                                           | 73 |

|    |      | 3.5.2  | Synchronisation et écriture des données (data ready : DR)     | 74 |

|    | 3.6  | L'horl | Uase                                                          | 75 |

#### TABLE DES MATIÈRES

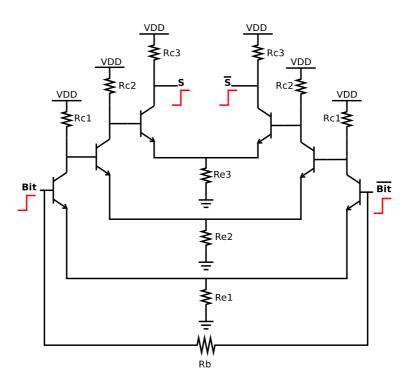

|    | 3.7  | Les sorties LVDS                                                   | 80 |

|----|------|--------------------------------------------------------------------|----|

|    | 3.8  | Simulation du CAN complet et résultats                             | 82 |

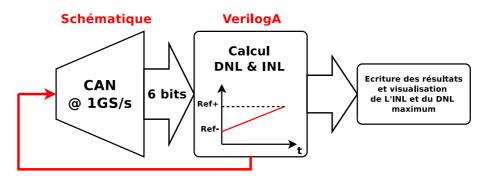

|    |      | 3.8.1 Le banc de test et les résultats de la simulation statique   | 32 |

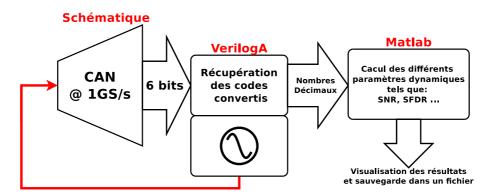

|    |      | 3.8.2 Le banc de test et les résultats de la simulation dynamique  | 84 |

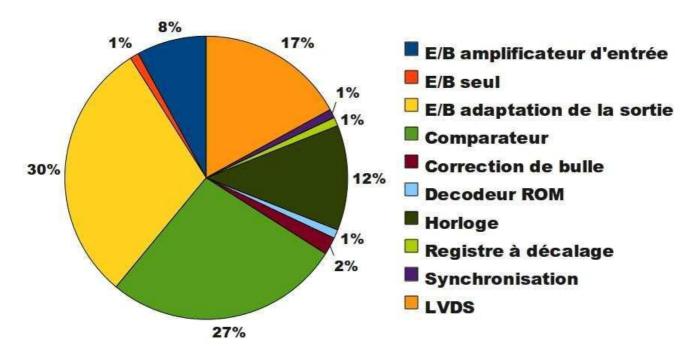

|    |      | 3.8.3 Consommation du circuit                                      | 85 |

| 4  | Des  | ssin de Masques                                                    | 37 |

|    | 4.1  | Introduction                                                       | 87 |

|    | 4.2  | Diminution des éléments parasites et du mésappariement             | 87 |

|    |      | 4.2.1 Les transistors                                              | 87 |

|    |      | 4.2.2 Les tailles des lignes et des vias                           | 88 |

|    |      | 4.2.3 Les résistances                                              | 89 |

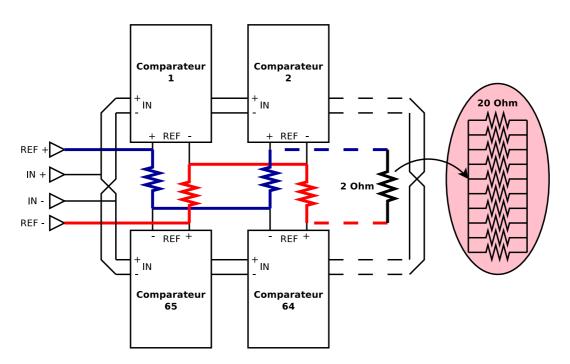

|    | 4.3  | L'échelle de comparateurs du circuit                               | 90 |

|    |      | 4.3.1 Répartition de l'horloge                                     | 90 |

|    |      | 4.3.2 Échelle de résistances                                       | 91 |

|    | 4.4  | Dessin du masque final                                             | 92 |

| 5  | Tes  | t et caractérisation                                               | 93 |

|    | 5.1  | Banc de test                                                       | 93 |

|    | 5.2  |                                                                    | 94 |

|    | 5.3  |                                                                    | 96 |

|    |      |                                                                    |    |

| II |      | Étude et réalisation d'un CAN flash à 3 Giga échantillons par sec- |    |

| O1 | nde  | en transistors bipolaires SiGeC 0,25 $\mu m$                       | 9  |

| In |      | uction 10                                                          |    |

|    |      | ogique ECL                                                         |    |

|    |      | portes Logiques ECL étudiées                                       |    |

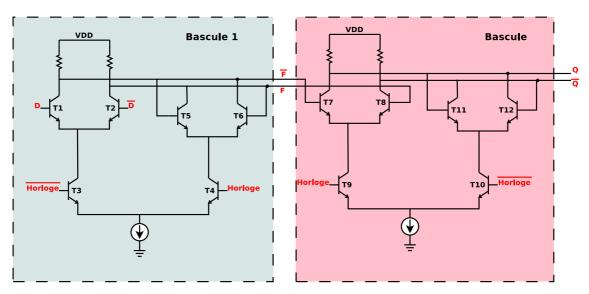

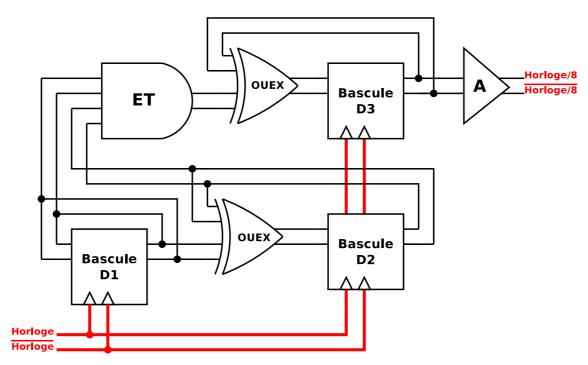

|    | La b | pascule D                                                          | 95 |

| 6  | Sim  | nulation et réalisation 10                                         | )7 |

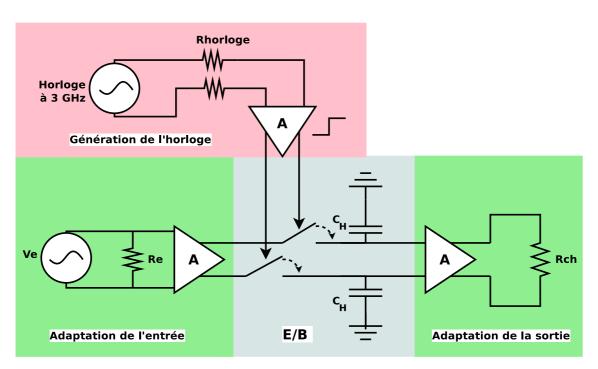

|    | 6.1  | Echantillonneur bloqueur en bipolaire                              | 07 |

|    |      | 6.1.1 Spécifications ciblées pour l'E/B                            | 98 |

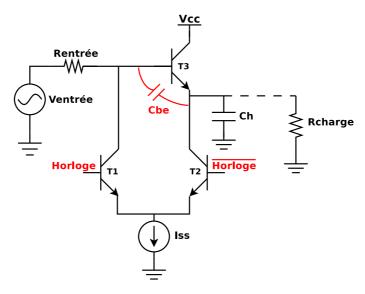

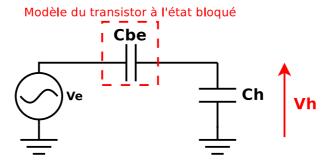

|    |      | 6.1.2 L'interrupteur et la capacité de charge de l'E/B             | 08 |

|    |      | 6.1.3 L'échantillonneur bloqueur développé                         | 12 |

|    |      | 6.1.4 Résultat temporel en simulation                              |    |

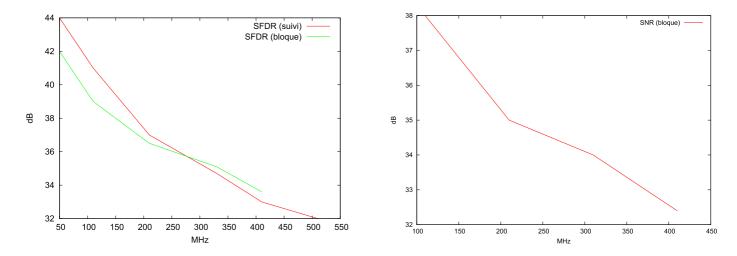

|    |      | 6.1.5 Résultats de simulation dynamique                            | 16 |

|    |      | Le comparateur en topologie bipolaire                              |    |

#### TABLE DES MATIÈRES

|                      |                                   | 6.2.1                                                                 | Le pré-amplificateur                                                                 | <br>. 118                                                                                                              |

|----------------------|-----------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|                      |                                   | 6.2.2                                                                 | Le comparateur bipolaire                                                             | <br>. 120                                                                                                              |

|                      |                                   | 6.2.3                                                                 | Schéma du comparateur réalisé pour le circuit                                        | <br>. 122                                                                                                              |

|                      | 6.3                               | L'échel                                                               | lle de résistances                                                                   | <br>. 124                                                                                                              |

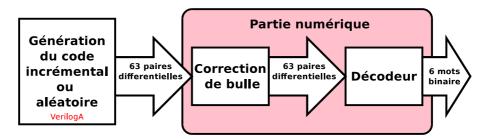

|                      | 6.4                               | Le déc                                                                | odage et la correction d'erreur                                                      | <br>. 125                                                                                                              |

|                      |                                   | 6.4.1                                                                 | La correction de bulle                                                               | <br>. 125                                                                                                              |

|                      |                                   | 6.4.2                                                                 | Le décodeur à arbre                                                                  | <br>. 125                                                                                                              |

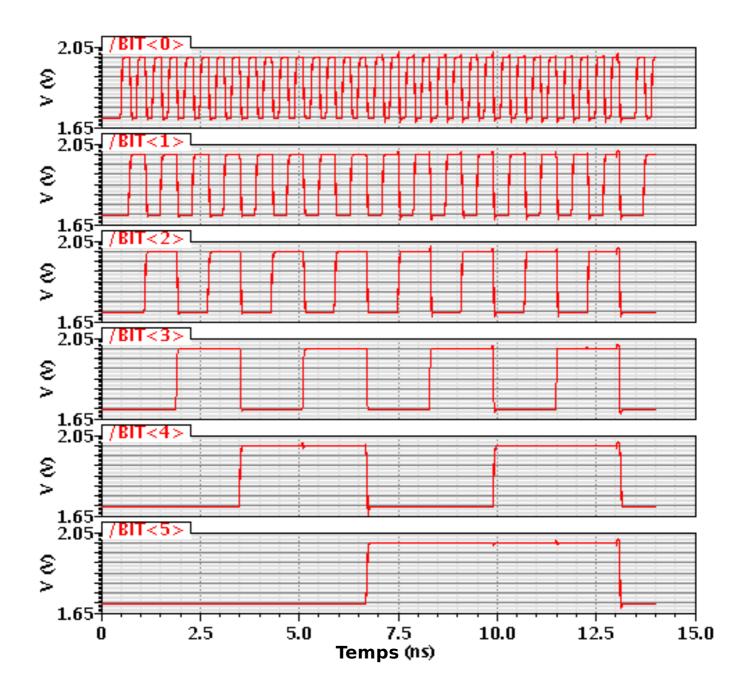

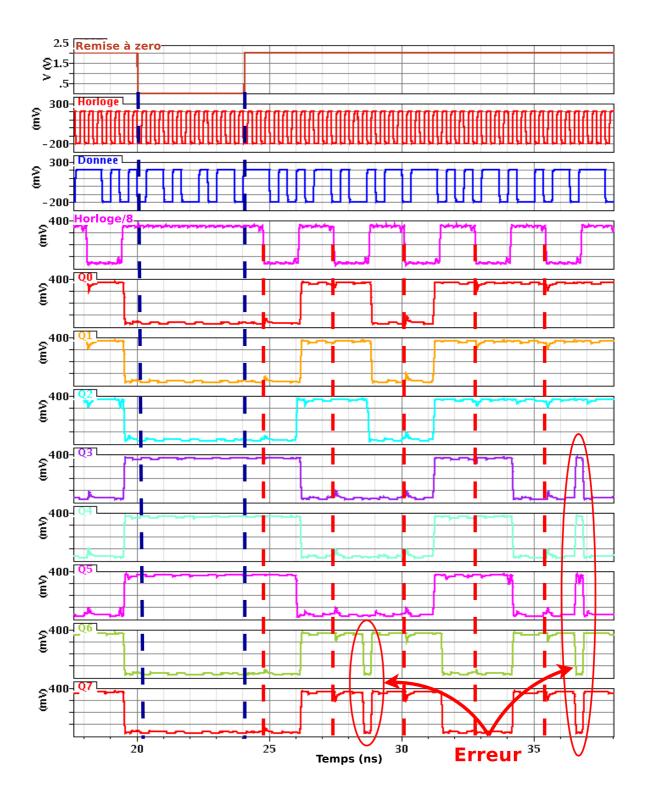

|                      |                                   | 6.4.3                                                                 | Résultats de mesures de la partie numérique                                          | <br>. 126                                                                                                              |

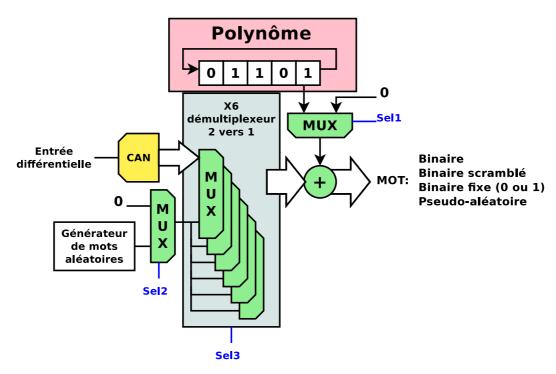

|                      | 6.5                               | Élémei                                                                | nts complémentaires en vue des tests ultérieurs                                      | <br>. 128                                                                                                              |

|                      | 6.6                               | Les son                                                               | cties LVDS                                                                           | <br>. 130                                                                                                              |

|                      | 6.7                               | L'horlo                                                               | oge                                                                                  | <br>. 132                                                                                                              |

| 7                    | Des                               | sin de                                                                | Masques                                                                              | 135                                                                                                                    |

|                      | 7.1                               | Isolatio                                                              | on de cellule                                                                        | <br>. 135                                                                                                              |

|                      | 7.2                               |                                                                       | ntation                                                                              |                                                                                                                        |

|                      | 7.3                               | Syméti                                                                | rie et répartition de l'horloge                                                      | <br>. 137                                                                                                              |

|                      | 7.4                               | Echelle                                                               | e de résistance                                                                      | <br>. 138                                                                                                              |

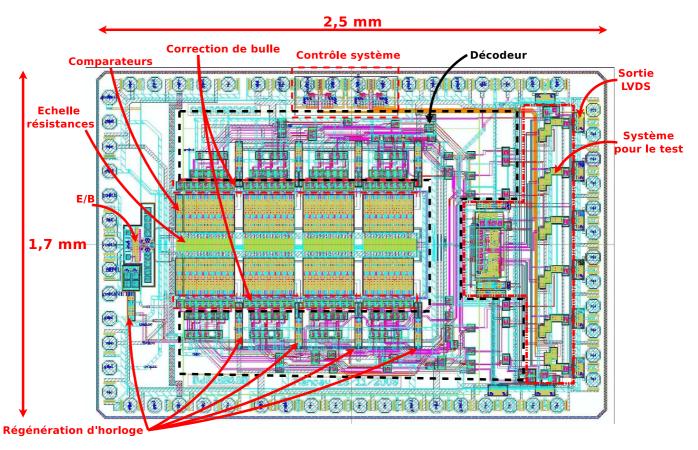

|                      | 7.5                               | Dessin                                                                | du masque final                                                                      | <br>. 139                                                                                                              |

|                      |                                   |                                                                       |                                                                                      |                                                                                                                        |

| 8                    | Car                               | actéris                                                               | ation post-layout et bancs de test                                                   | 141                                                                                                                    |

| 8                    | <b>Car</b> 8.1                    |                                                                       | ation post-layout et bancs de test<br>ats de simulation (post-layout) du CAN complet |                                                                                                                        |

| 8                    |                                   |                                                                       | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>141</li><li>141</li></ul>                                                                                  |

| 8                    |                                   | Résult                                                                | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>141</li><li>141</li></ul>                                                                                  |

| 8                    |                                   | Résult<br>8.1.1                                                       | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>141</li><li>141</li><li>143</li></ul>                                                                      |

| 8                    |                                   | Résult<br>8.1.1<br>8.1.2                                              | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>. 141</li><li>. 141</li><li>. 143</li><li>. 144</li></ul>                                                  |

| 8                    | 8.1                               | Résult.<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar                 | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>. 141</li><li>. 143</li><li>. 144</li><li>. 145</li></ul>                                                  |

| 8                    | 8.1                               | Résult.<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar                 | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>. 141</li><li>. 143</li><li>. 144</li><li>. 145</li></ul>                                                  |

|                      | 8.1<br>8.2<br>8.3                 | Résult.<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar<br>Conclu       | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>. 141</li><li>. 143</li><li>. 144</li><li>. 145</li></ul>                                                  |

| C                    | 8.1<br>8.2<br>8.3                 | Résult.<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar<br>Conclu       | ats de simulation (post-layout) du CAN complet                                       | <br><ul><li>. 141</li><li>. 143</li><li>. 144</li><li>. 144</li><li>. 145</li><li>. 147</li></ul>                      |

| Co<br>A              | 8.1<br>8.2<br>8.3<br>onclu        | Résult<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar<br>Conclu        | ats de simulation (post-layout) du CAN complet                                       | <br><ul> <li>141</li> <li>143</li> <li>144</li> <li>145</li> <li>147</li> </ul>                                        |

| Co<br>A:             | 8.1<br>8.2<br>8.3<br>onclu<br>NNE | Résult<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Prépar<br>Conclusion gé | ats de simulation (post-layout) du CAN complet                                       | <br><ul> <li>141</li> <li>143</li> <li>144</li> <li>145</li> <li>147</li> </ul>                                        |

| Co<br>A:<br>A:<br>A: | 8.2<br>8.3<br>onclu<br>NNE<br>NNE | Résult. 8.1.1 8.1.2 8.1.3 8.1.4 Prépar Conclusion gé                  | ats de simulation (post-layout) du CAN complet                                       | <br><ul> <li>141</li> <li>143</li> <li>144</li> <li>145</li> <li>147</li> <li>149</li> <li>161</li> <li>163</li> </ul> |

# Table des figures

| 1    | a. Récepteur hétérodyne en bande L (CAN « 1 GS/s), b. Récepteur radio simplifié en     |    |

|------|----------------------------------------------------------------------------------------|----|

|      | bande L (CAN $> 3$ GS/s)                                                               | 2  |

| 2    | Struture du Square Kilometer Array                                                     | 3  |

| 3    | Feuille de route du projet SKA                                                         | 4  |

| 4    | Une tuile composée d'antennes Vivaldi avec commandes intégrées                         | 4  |

| 5    | Diagramme récepteur superhétérodyne                                                    | 5  |

| 6    | Diagramme de réception rapide                                                          | 6  |

| 7    | Les deux sites en compétition pour l'accueil du radiotélescope SKA : l'Afrique du sud  |    |

|      | et l'Australie                                                                         | 7  |

| 1.1  | Vue de coupe du transistor MOS                                                         | 14 |

| 1.2  | Vue de coupe du transistor Bipolaire                                                   | 15 |

| 1.3  | Différentes topologies de base pour les transistors NPN et les transistors NMOS avec   |    |

|      | des résistances de polarisations                                                       | 17 |

| 2.1  | Bloc général                                                                           | 19 |

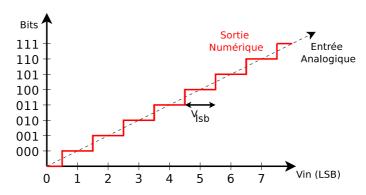

| 2.2  | Fonction de transfert du CAN                                                           | 21 |

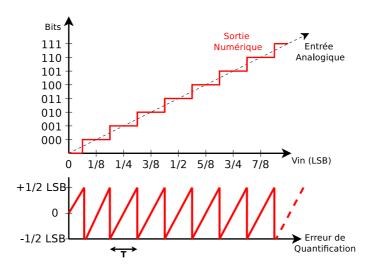

| 2.3  | L'erreur de quantification d'une entrée à rampe                                        | 22 |

| 2.4  | Les erreurs statiques : (a) erreur d'offset (b) erreur de gain                         | 23 |

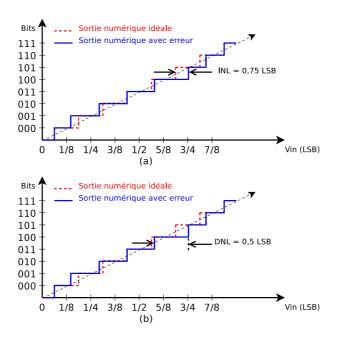

| 2.5  | Les erreurs statiques : (a) non-linarité intégrale, (b) non-linarité différentielle    | 24 |

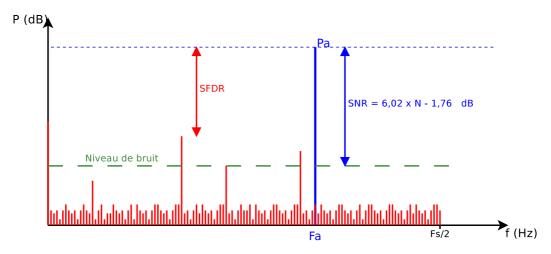

| 2.6  | Analyse Spectrale, description des résultats dynamiques                                | 25 |

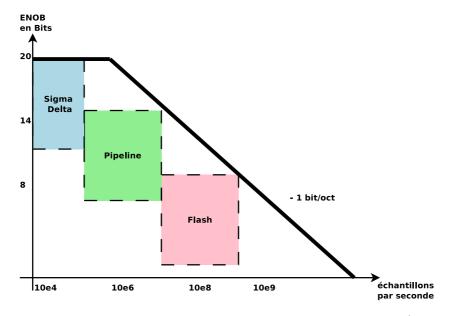

| 2.7  | Classifications des trois architectures les plus rapides des CAN en fonction de l'ENOB |    |

|      | et de la fréquence d'échantillonnage                                                   | 27 |

| 2.8  | Structure Pipeline                                                                     | 28 |

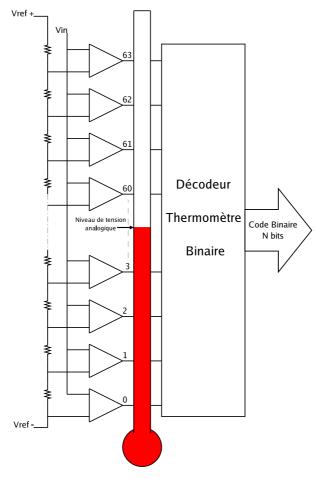

| 2.9  | Structure de l'ADC Flash                                                               | 29 |

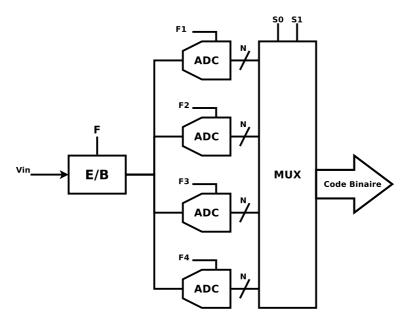

|      | CAN à temps entrelacé                                                                  | 31 |

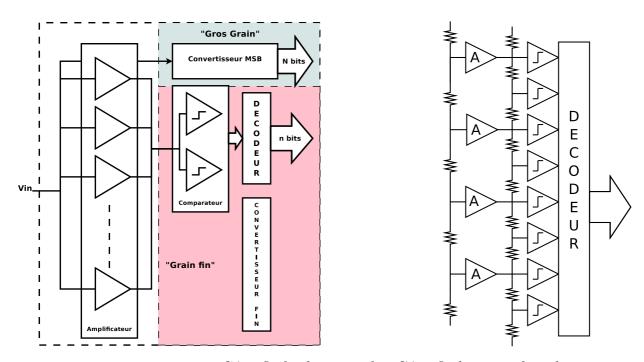

| 2.11 | CAN flash plié à gauche, CAN flash interpolé à droite                                  | 32 |

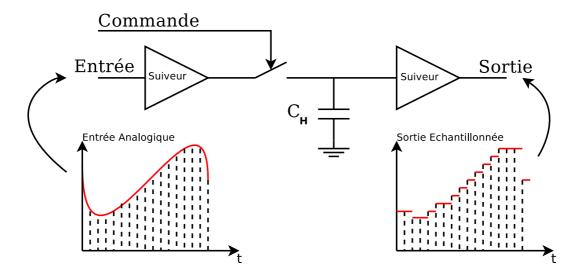

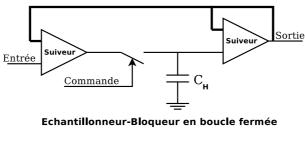

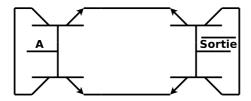

| 3.1  | Schéma de principe d'un échantillonneur-bloqueur en boucle ouverte                     | 37 |

| 3.2  | Schéma de l'échantillonneur-bloqueur en boucle ouverte et en boucle fermée             | 38 |

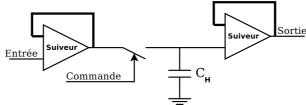

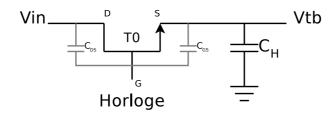

| 3.3  | Echantillonneur-bloqueur idéale en technologie MOS                                     | 39 |

| 3.4  | Résultat temporel du E/B avec impédance de charge infinie $\ \ldots \ \ldots \ \ldots \ \ldots$         | 39 |

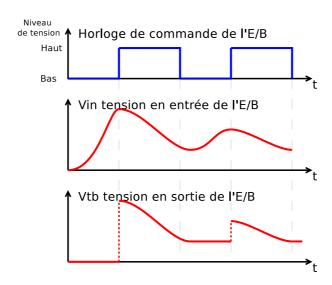

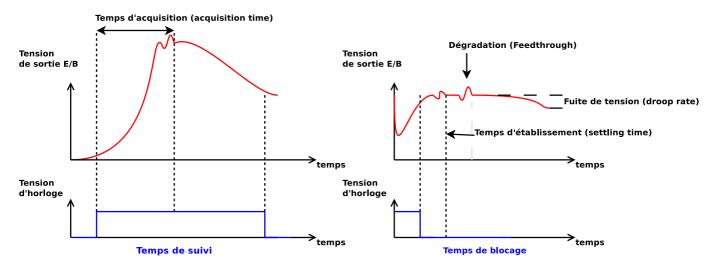

|------|---------------------------------------------------------------------------------------------------------|----|

| 3.5  | Source d'erreurs en mode suivie et en mode bloquée                                                      | 40 |

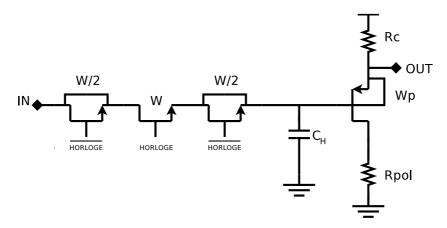

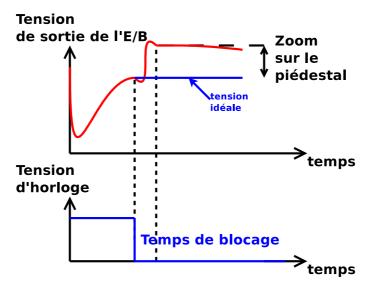

| 3.6  | Echantillonneur Bloqueur en NMOS                                                                        | 41 |

| 3.7  | Le piédestal                                                                                            | 42 |

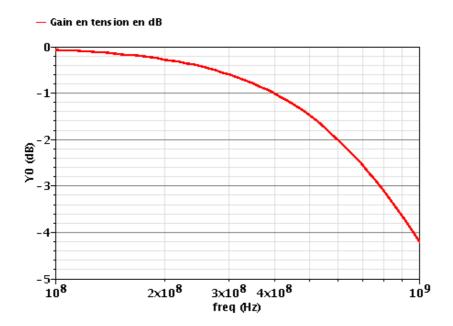

| 3.8  | Gain de l'échantillonneur bloqueur                                                                      | 43 |

| 3.9  | Topologie E/B Boucle sans contre réaction                                                               | 44 |

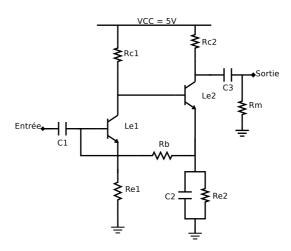

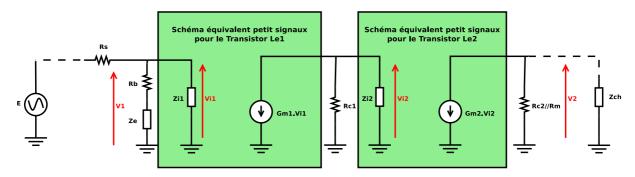

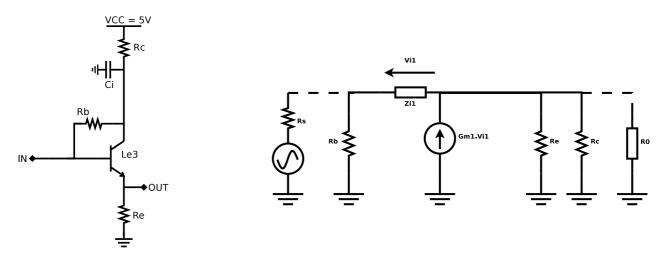

| 3.10 | Topologie d'amplificateur avec des transistors NPN                                                      | 45 |

| 3.11 | Schéma équivalent « petits signaux » pour le calcul du gain en tension                                  | 45 |

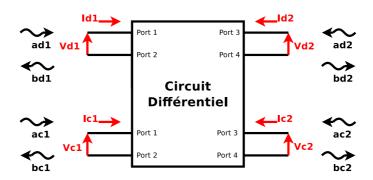

| 3.12 | Représentation d'un quadripôle                                                                          | 46 |

| 3.13 | Représentation d'un quadripôle avec les accès au port différentiel et mode commun                       | 48 |

| 3.14 | A gauche la topologie collecteur commun utilisée, à droite, le schéma collecteur com-                   |    |

|      | mun en « petits signaux »                                                                               | 49 |

| 3.15 | Schéma différentiel de l'échantillonneur bloqueur simulé et défini                                      | 50 |

| 3.16 | A gauche, adaptation de l'entrée différentielle : Sdd11. A droite, l'impédance de sortie                |    |

|      | de l'E/B                                                                                                | 51 |

| 3.17 | A gauche, gain de la structure. A droite, le taux de réjection en mode commun                           | 52 |

| 3.18 | Simulation temporelle pour une fréquence d'entrée de 490 MHz avec un balayage de                        |    |

|      | tension pleine échelle en entrée : (a) sorties de l' $E/B$ en temporel, (b) zoom sur quelques           |    |

|      | périodes des sorties non-différentielles, (c) sortie différentielle en temporel, (d) zoom               |    |

|      | sur quelques périodes de la simulation différentielle                                                   | 53 |

| 3.19 | A gauche le SFDR, à droite le SNR réalisé en simulation                                                 | 53 |

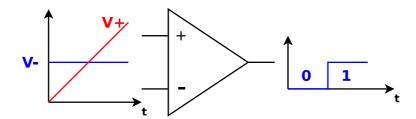

| 3.20 | Schéma de principe d'un comparateur                                                                     | 55 |

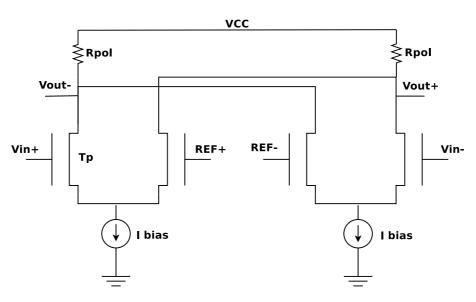

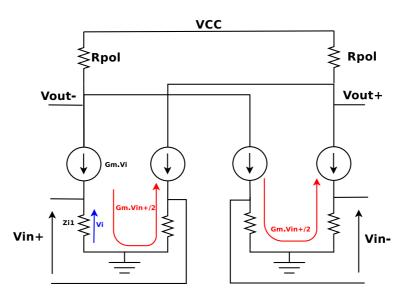

| 3.21 | Schéma électrique du pré-amplificateur                                                                  | 56 |

| 3.22 | Schéma équivalent petits signaux du pré-amplificateur                                                   | 57 |

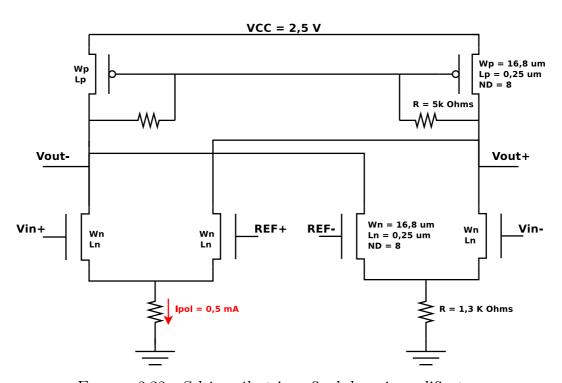

| 3.23 | Schéma électrique final du pré-amplificateur                                                            | 58 |

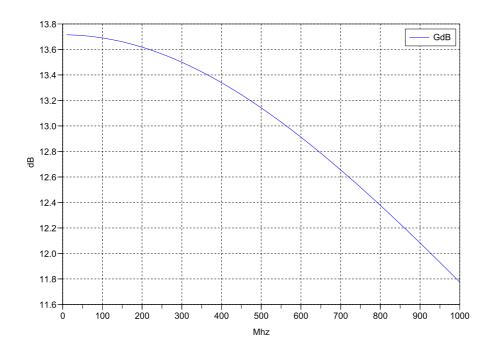

| 3.24 | Gain en régime linéaire du pré-amplificateur obtenu avec $Vdc_{Ref+} = Vdc_{Ref-}$ ,                    |    |

|      | $I_d = 0,5mA$ W = 2,1 $\mu m$ et L = 0,25 $\mu m$ avec un nombre de doigts d'émetteur égal              |    |

|      | à 8                                                                                                     | 59 |

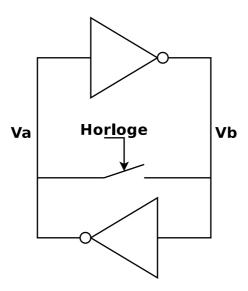

| 3.25 | Schéma simplifié de 2 inverseurs tête-bêche durant l'état bloqué                                        | 60 |

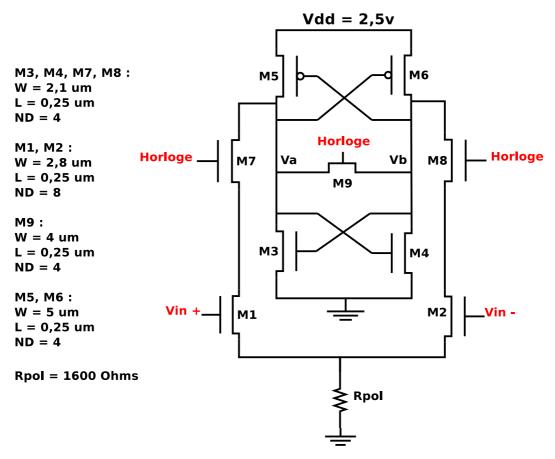

| 3.26 | Le comparateur à vérouillage proposé                                                                    | 61 |

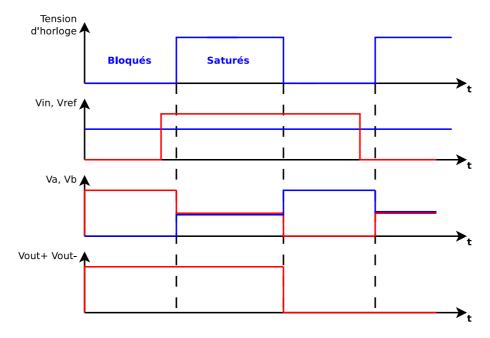

| 3.27 | Chronogramme du fonctionnement du comparateur                                                           | 62 |

| 3.28 | Schéma complet du comparateur                                                                           | 63 |

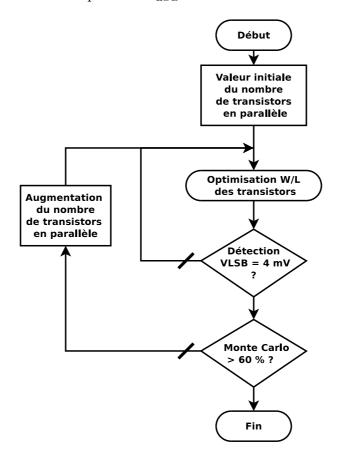

| 3.29 | Processus mis en place pour obtenir un pour<br>centage d'erreur inférieur 40 $\%$                       | 63 |

| 3.30 | Diagramme de l'oeil                                                                                     | 64 |

| 3.31 | Chronogramme des étages du comparateur utilisé                                                          | 65 |

| 3.32 | Tensions de référence, pour $F_{echantillonnage} = 1$ GS/s et $F_{entree} = 100$ MHz, avec en (a)       |    |

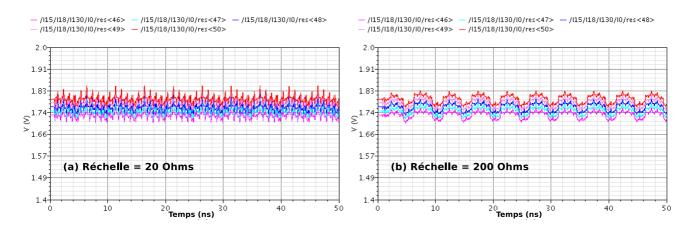

|      | $R_{echelle} = 20 \Omega \text{ et (b)} \ R_{echelle} = 200 \Omega \dots \dots \dots \dots \dots \dots$ | 66 |

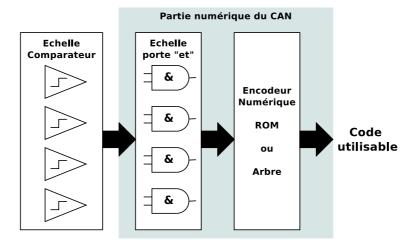

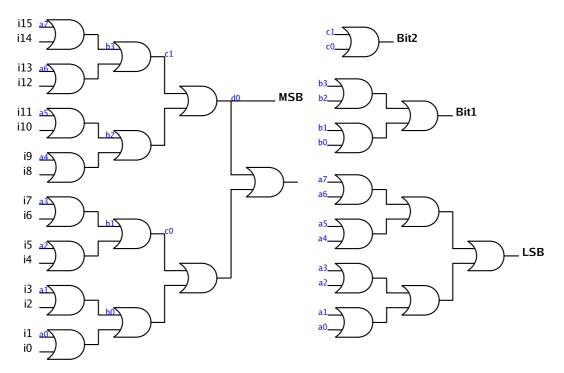

| 3.33 | Schéma de la structure numérique                                                            | 67 |

|------|---------------------------------------------------------------------------------------------|----|

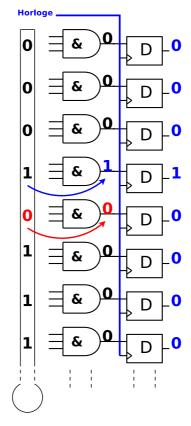

| 3.34 | Correction de bulle                                                                         | 68 |

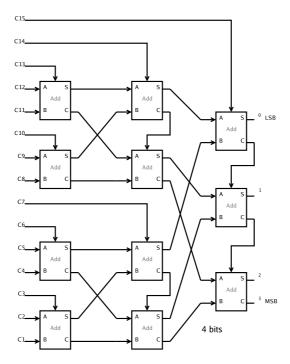

| 3.35 | Décodeur à arbre avec additionneur pour un CAN flash 4 bits                                 | 69 |

| 3.36 | Décodeur à arbre en porte « OU »                                                            | 70 |

| 3.37 | Schéma d'encodage numérique d'une structure 3 bits d'une ROM sans et avec erreur            |    |

|      | de bulle                                                                                    | 70 |

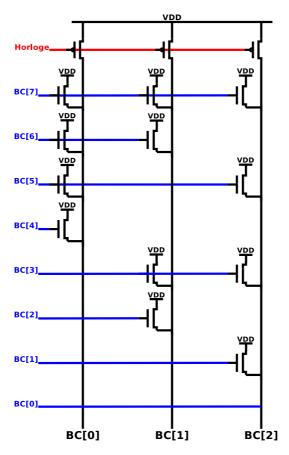

| 3.38 | Architecture mémoire 3 bits (Read Only Memory)                                              | 71 |

| 3.39 | Schéma d'encodage numérique d'une structure 3 bits d'une ROM en code de Gray                |    |

|      | avec erreur de bulle                                                                        | 72 |

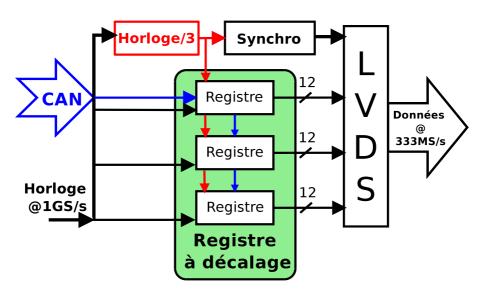

| 3.40 | Système de test en sortie du CAN                                                            | 73 |

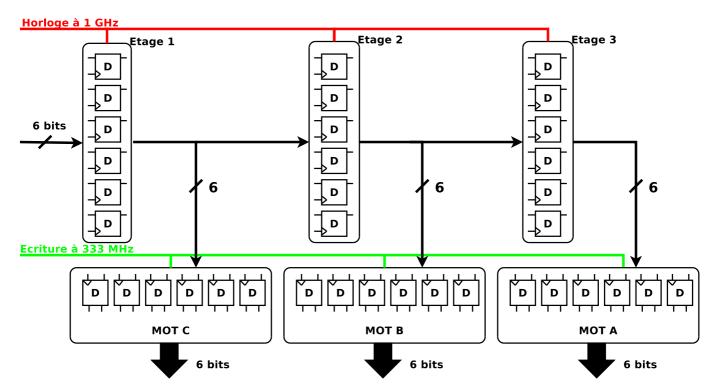

| 3.41 | Registre à décalage                                                                         | 74 |

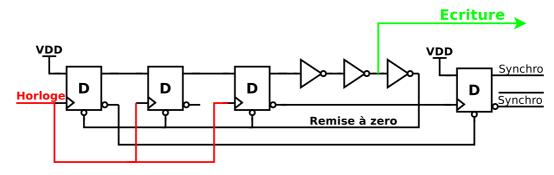

| 3.42 | Synchronisation et validation d'écriture pour le registre à décalage                        | 74 |

| 3.43 | Schéma de l'amplificateur à Trigger de Schmitt avec amplificateur de sortie                 | 75 |

| 3.44 | Caractéristiques de transfert entrée sortie d'un Trigger de Schmitt                         | 76 |

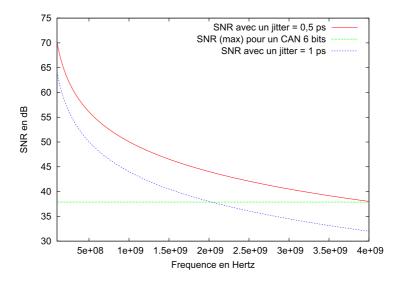

| 3.45 | SNR en fonction de la fréquence pour différentes valeurs de jitter par rapport au SNR       |    |

|      | maximum                                                                                     | 77 |

| 3.46 | SNR en fonction du nombre de bits pour un jitter de 1 ps, une tension de bruit de           |    |

|      | 0,5 V et un DNL de 0,5 LSB $$                                                               | 78 |

| 3.47 | Jitter de l'horloge                                                                         | 79 |

| 3.48 | Schéma inverseur utilisé pour la mise en forme et l'adaptation en tension                   | 79 |

| 3.49 | Schéma LVDS en émission et réception                                                        | 80 |

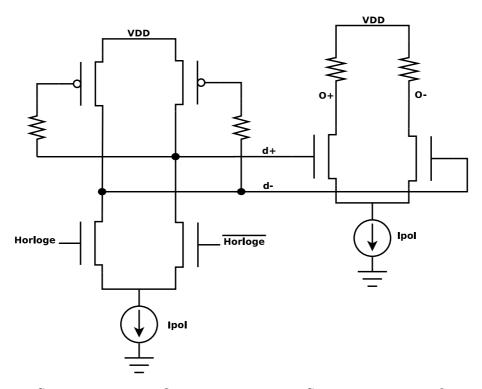

| 3.50 | Schéma de la sortie LVDS utilisée                                                           | 81 |

| 3.51 | Schéma du CAN complet                                                                       | 82 |

| 3.52 | Schéma du test INL et DNL                                                                   | 83 |

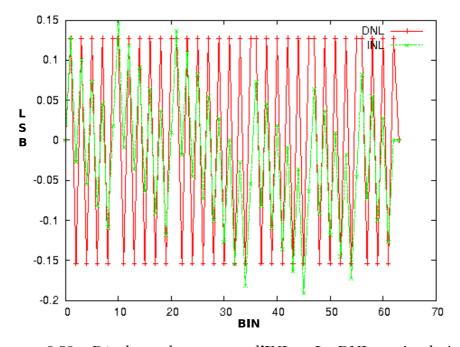

| 3.53 | Résultats obtenus pour l'INL et La DNL en simulation                                        | 83 |

| 3.54 | Schéma de la mesure dynamique                                                               | 84 |

| 3.55 | Le pourcentage de consommation des différents composants du circuit pour une puis-          |    |

|      | sance totale de 2 Watts                                                                     | 85 |

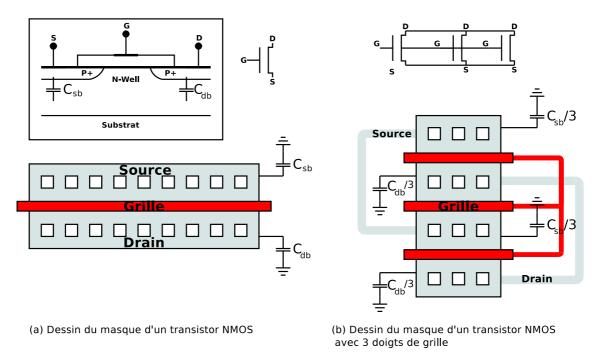

| 4.1  | (a) Transistor NMOS de forte largeur de grille (b) Transistor NMOS équivalent avec          |    |

|      | une faible largeur de grille                                                                | 88 |

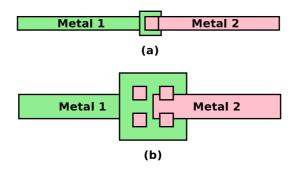

| 4.2  | Dessin de 2 vias : (a) très faible densité de courant, (b) forte densité de courant, 4 fois |    |

|      | plus élevée que (a)                                                                         | 89 |

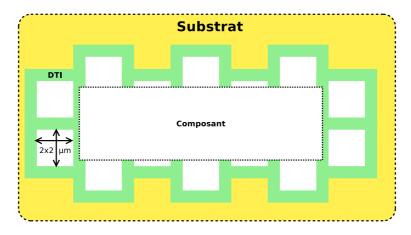

| 4.3  | Représentation du DTI réduisant la capacité du substrat                                     | 89 |

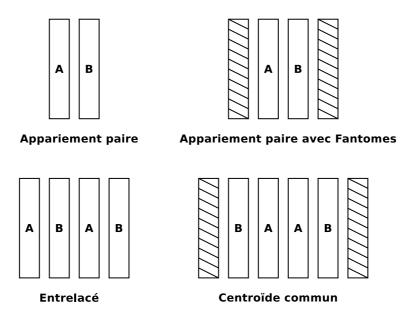

| 4.4  | Les différentes techniques d'appariement des résistances                                    | 90 |

| 4.5  | Répartition de l'horloge                                                                    | 90 |

| 4.6  | Technique utilisée afin d'améliorer le routage de l'échelle de résistance. (a)Connexion     |    |

|      | avec des comparateurs successifs. (b)Connexion avec échelle de résistance pliée             | 91 |

| 4.7  | Dessin du masque final du CAN                                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1  | Carte de test                                                                                                                                                               |

| 5.2  | Banc de test du CAN                                                                                                                                                         |

| 5.3  | Erreur du code observée sur Matlab pour une tension d'entrée de 50 MHz et une                                                                                               |

|      | fréquence d'échantillonnage de 850 MHz                                                                                                                                      |

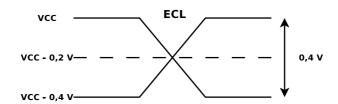

| 5.4  | Niveaux logiques de la norme ECL                                                                                                                                            |

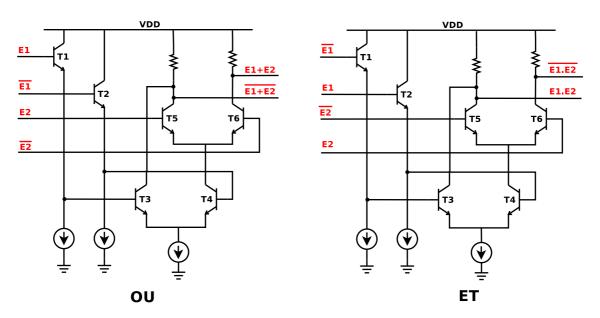

| 5.5  | Porte logique OU et ET avec des transistors bipolaires                                                                                                                      |

| 5.6  | Schéma d'une bascule D avec des transistors bipolaires                                                                                                                      |

| 6.1  | Schéma de principe de l'E/B avec prise en compte de la génération d'horloge 107                                                                                             |

| 6.2  | Schéma de l'émetteur suiveur commuté (SEF)                                                                                                                                  |

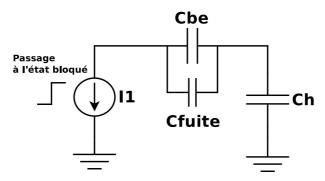

| 6.3  | Modèle simplifié en mode bloqué                                                                                                                                             |

| 6.4  | Anti-feedthrough                                                                                                                                                            |

| 6.5  | Modèle simplifié pour l'erreur du piédestal                                                                                                                                 |

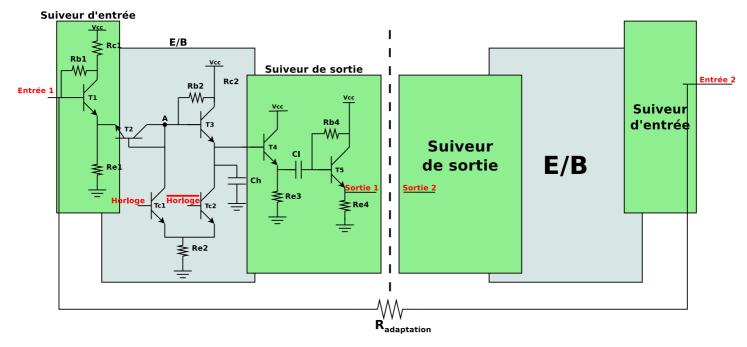

| 6.6  | Schéma réalisé de l'E/B différentiel                                                                                                                                        |

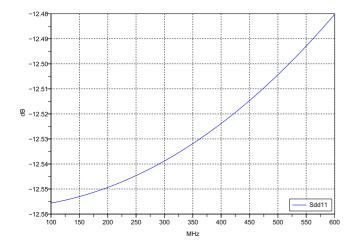

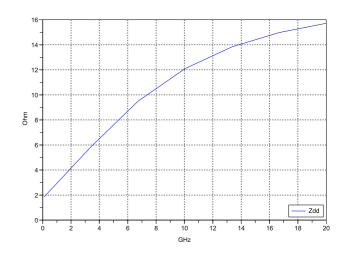

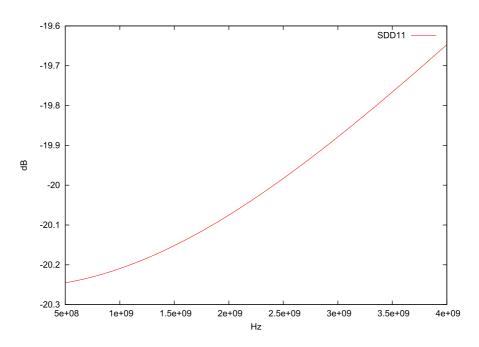

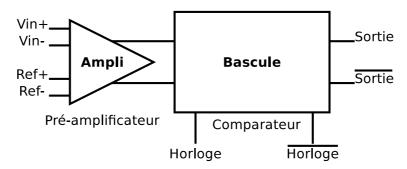

| 6.7  | Simulation du paramètre $Sdd_{11}$ , en entrée de l'E/B $\dots \dots \dots$ |

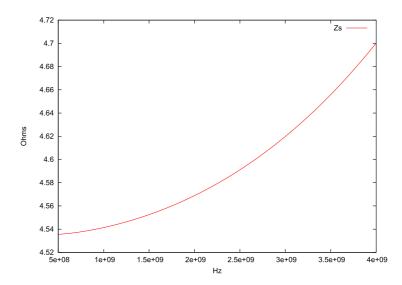

| 6.8  | Impédance de sortie de l'E/B obtenue en simulation                                                                                                                          |

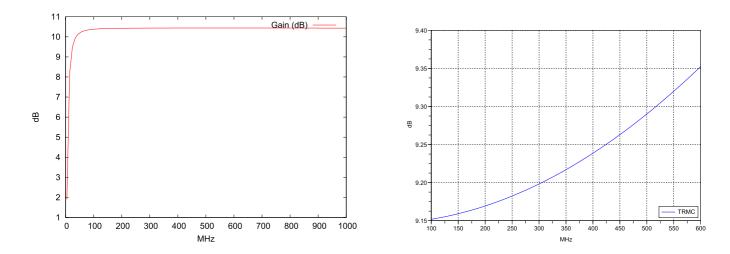

| 6.9  | Gain en tension du mode différentiel et gain en tension du mode commun de l' $\mathrm{E/B}$ 114                                                                             |

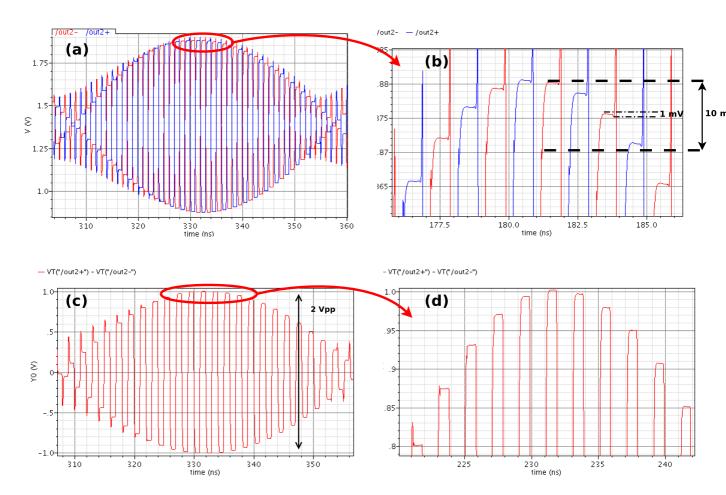

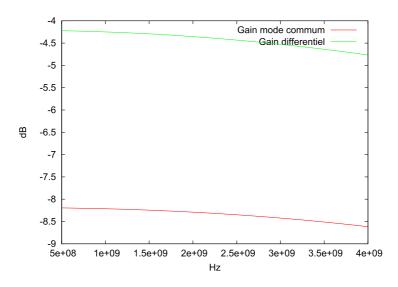

| 6.10 | Simulation temporelle en pleine échelle (Eg = $500 \text{ mV}$ ) avec la fréquence d'entrée                                                                                 |

|      | égale à 1,4 GHz et une fréquence d'horloge égale à 3 GHz avec en : (a) les sorties                                                                                          |

|      | temporelles de l' $E/B$ , (b) le zoom sur un état bloqué d'une des sorties de l' $E/B$ , (c) les                                                                            |

|      | sorties différentielles de l' $\mathrm{E/B}$ , (d) le zoom sur un état bloqué de la sortie différentielle 115                                                               |

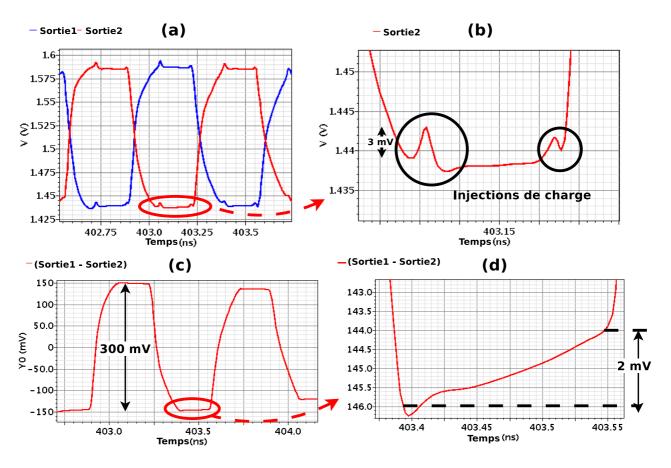

| 6.11 | Schéma de principe du comparateur                                                                                                                                           |

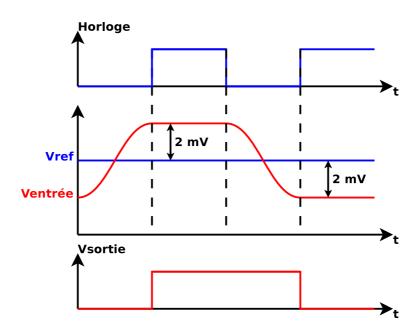

| 6.12 | Chronogramme du résultat à obtenir en temporel                                                                                                                              |

| 6.13 | Schéma électrique du pré-amplificateur bipolaire                                                                                                                            |

| 6.14 | Schéma du pré-amplificateur pour la mesure du gain en tension                                                                                                               |

|      | Gain du pré-amplificateur obtenu en simulation                                                                                                                              |

| 6.16 | Schéma électrique du comparateur bipolaire                                                                                                                                  |

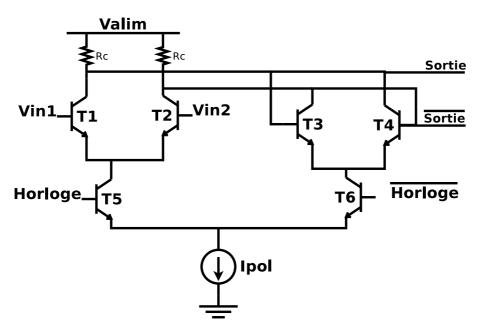

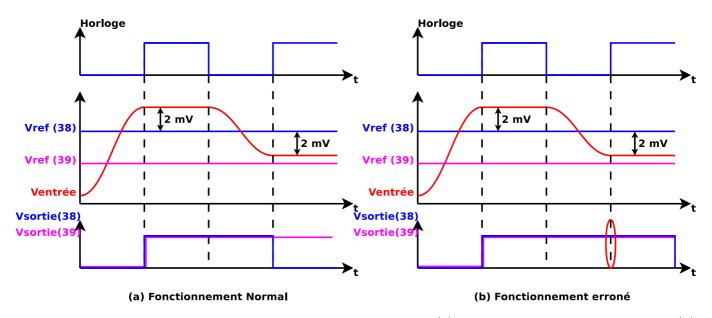

|      | Chronogramme du fonctionnement normal en (a) et du fonctionnement erroné en (b) 122                                                                                         |

| 6.18 | Schéma électrique du comparateur bipolaire                                                                                                                                  |

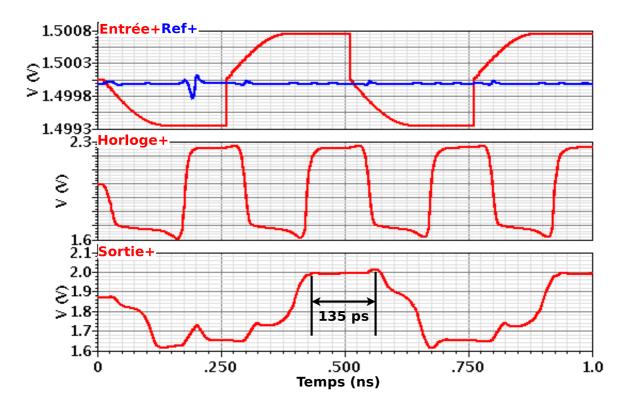

| 6.19 | Résultats de simulation temporelle du comparateur, réalisés avec le générateur d'hor-                                                                                       |

|      | loge réel intégré dans le circuit                                                                                                                                           |

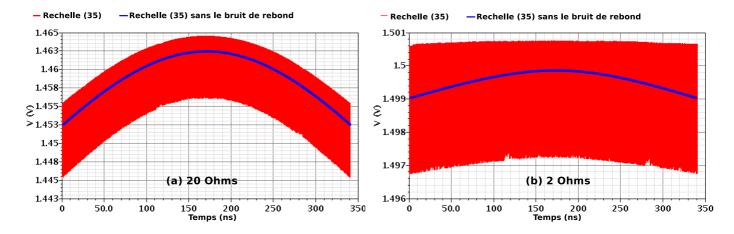

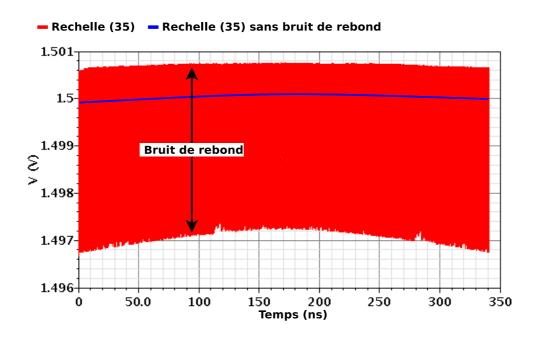

| 6.20 | Résultat temporel aux bornes d'une résistance pour une valeur de 20 $\Omega$ en (a) et 2 $\Omega$                                                                           |

|      | en (b) pour une rampe injectée en entrée, la courbe bleue représente le signal sans                                                                                         |

|      | bruit de rebond, la courbe rouge représente le signal réel                                                                                                                  |

| 6.21 | Schéma du décodeur pour une architecture 4 bits                                                                                                                             |

| 6.22 | Schéma de test de la partie numérique du CAN                                                                                                                                |

| 6.23 | Chronogramme des sorties binaires pour une réponse à code thermomètre en entrée               | 105 |

|------|-----------------------------------------------------------------------------------------------|-----|

|      | cadencée à 5 GHz                                                                              |     |

|      | Système intégré dans la puce pour la réalisation du test                                      |     |

|      | Schéma électrique du démultiplexeur 2 vers 1                                                  |     |

|      | Schéma électrique du OU exclusif                                                              |     |

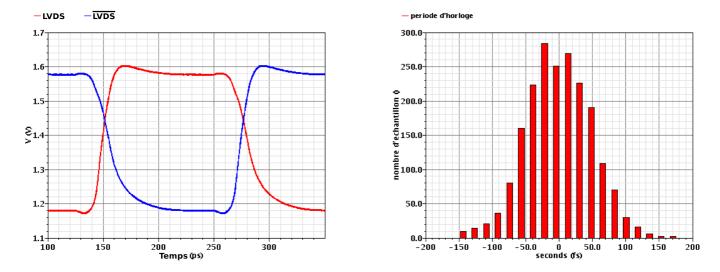

|      | Schéma des sorties LVDS                                                                       |     |

| 6.28 | Gain en tension de la cellule LVDS jusqu'à 20 GHz                                             | 131 |

| 6.29 | Diagramme de l'oeil des sorties différentielles et histogramme du jitter de la sortie         |     |

|      | LVDS temporelle associé pour une fréquence d'entrée de 4 GHz                                  | 131 |

| 6.30 | SNR en fonction de la fréquence pour un jitter d'horloge de $0.5$ ps et $1$ ps                | 132 |

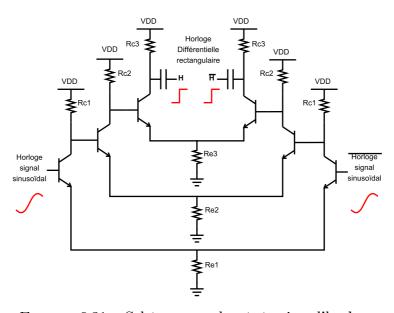

| 6.31 | Schéma pour la génération d'horloge                                                           | 132 |

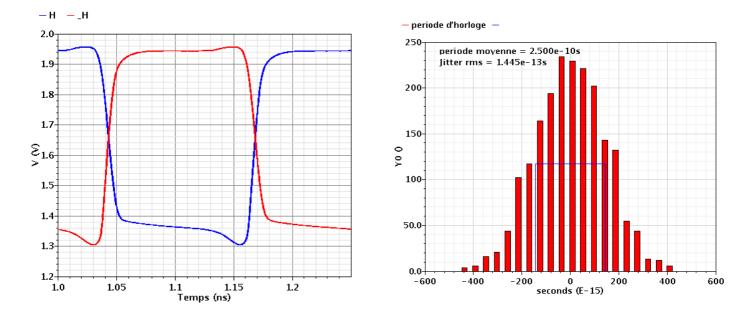

| 6.32 | Diagramme de l'oeil en sortie de la cellule horloge pour un signal différentiel sinusoïdal    |     |

|      | de 120 mV à 4 GHz et le jitter de l'horloge temporelle associée                               | 133 |

|      |                                                                                               |     |

| 7.1  | Anneau de garde avec anneau $p^+$ et anneau $n^+$                                             |     |

| 7.2  | Triple anneaux de garde avec 2 anneaux $p^+$ et un anneau $n^+$                               | 136 |

| 7.3  | Séparation des alimentations et augmentation du nombres de plots analogiques et               |     |

|      | numériques                                                                                    | 137 |

| 7.4  | Symétrie des cellules et répartition de l'horloge sur les différents blocs                    | 138 |

| 7.5  | Echelle résistive avec une connexion entrelacée                                               | 138 |

| 7.6  | Masque de la puce entière : CAN 6 bits à 3GS/s, et le système de test                         | 139 |

| 8.1  | Résultat temporel aux bornes d'une résistance de 2 $\Omega$ de l'échelle pour un signal rampe |     |

|      | en entrée du CAN                                                                              | 142 |

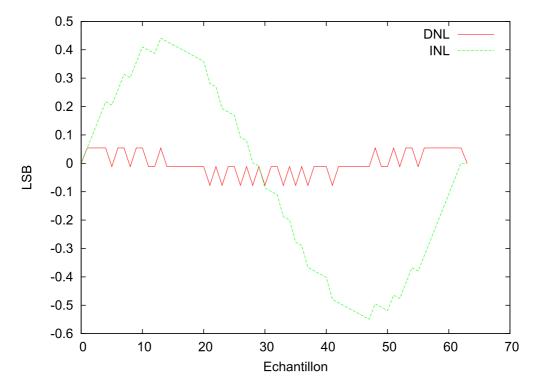

| 8.2  | Résultats de simulations des performances statiques (INL, DNL)                                |     |

| 8.3  | Résultats dynamiques du CAN 6 bits (avec capacités et résistance parasites) à 3 GS/s          |     |

| 0.0  | avec 700 points de mesure                                                                     | 143 |

| 8.4  | Répartition de la consommation totale (3 W) du CAN à 3 GS/s                                   |     |

| 8.5  | Schéma de test avec un flot de données réduit par des démultiplexeurs                         |     |

| 8.6  | Schéma de test avec un flot de données à 3 GS/s                                               |     |

| 0.0  | generia de test avec un not de données à 5 db/s                                               | 140 |

| 8.7  | Schéma du démultiplexeur                                                                      | 161 |

| 8.8  | Schéma du compteur modulo 8                                                                   | 162 |

|      |                                                                                               |     |

| 8.9  | Schéma de l'entrée LVDS                                                                       | 163 |

| 8.10 |                                                                                               |     |

|      | aléatoires                                                                                    | 165 |

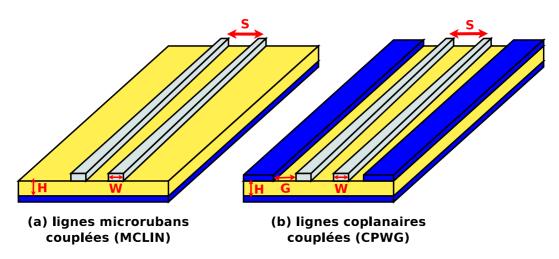

| 8.11 | Schéma des lignes utilisées : (a) lignes microrubans couplées et (b) lignes coplanaires       |     |

| O.11 | couplées                                                                                      | 168 |

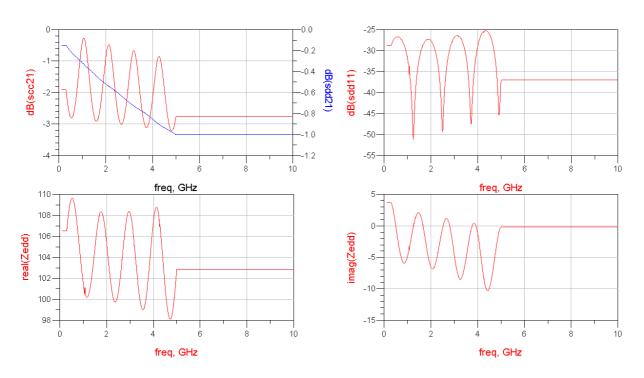

| 8.12 | Résultats de simulation pour une ligne microruban couplée   |  |  | <br> |  |  |  |  | 168 |

|------|-------------------------------------------------------------|--|--|------|--|--|--|--|-----|

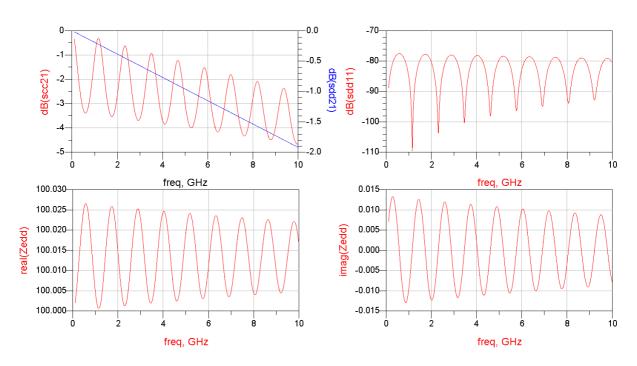

| 8.13 | Résultats de simulation pour une ligne coplanaire couplée . |  |  | <br> |  |  |  |  | 169 |

# Liste des tableaux

| 1.1 | Caractéristiques des transistors NMOS et PMOS                                                |

|-----|----------------------------------------------------------------------------------------------|

| 1.2 | Caractéristiques du transistor bipolaire                                                     |

| 1.3 | Récaptitulatif des caractéristiques des topologies                                           |

| 2.1 | Comparatif d'erreur de quantification par rapport au nombre de bits 20                       |

| 2.2 | Comparatif CAN pipeline et flash                                                             |

| 2.3 | Spécifications ciblées pour le CAN                                                           |

| 3.1 | Spécifications ciblées pour l'échantillonneur-bloqueur                                       |

| 3.2 | Résultats obtenus en simulation pour l'échantillonneur-bloqueur 51                           |

| 3.3 | Résultats de simulation du pré-amplificateur                                                 |

| 3.4 | Résultats de simulation du comparateur complet                                               |

| 3.5 | Correspondance entre les différents codes pour un CAN 3 bits                                 |

| 3.6 | Paramètres du CAN 6 bits                                                                     |

| 3.7 | Résultats dynamiques en simulation à 1 GS/s d'horloge avec 200 points de mesure $84$         |

| 5.1 | Résultats dynamiques après correction des erreurs avec une fréquence d'horloge de            |

|     | 850 MHz à température ambiante $(20^{\circ}C)$                                               |

| 5.2 | Spécifications ciblées pour le CAN                                                           |

| 5.3 | Spécifications de la norme CML                                                               |

| 6.1 | Spécifications ciblées pour E/B                                                              |

| 6.2 | Résultats dynamiques obtenus en simulation avec 2000 points d'échantillon à 3 GS/s . $116$   |

| 6.3 | Résultats obtenus en simulation Monté-Carlo                                                  |

| 6.4 | Résultats obtenus en simulation schématique                                                  |

| 6.5 | Spécifications ciblées pour le comparateur                                                   |

| 6.6 | Résultats de simulations du pré-amplificateur                                                |

| 6.7 | Spécifications du comparateur réalisé en bipolaire                                           |

|     |                                                                                              |

| 8.1 | Variation de l'INL en fonction de la résistance élémentaire de l'échelle de résistance . 141 |

### LISTE DES TABLEAUX

| 8.3 | Caractéristiques du substrat sur FR4             | 167 |

|-----|--------------------------------------------------|-----|

| 8.4 | Résultats obtenus pour les paramètres des lignes | 167 |

#### Liste des abréviations

A Amplificateur

**AAVP** Aperture Array Verification Program

**ADC** Analog Digital Converter

**ASIC** Application Specific Integrated Circuit

BC Base commune

**BiCMOS** BIpolar Complementary Metal-Oxide-Semiconductor logic

**BP** Bande Passante

CAN Convertisseur analogique numérique

CAO Conception Assistée par Ordinateur

**CB** Code Binaire

CC Collecteur Commun

**CML** Current-mode logic

CMOS Complementary Metal-Oxide-Semiconductor logic

CT Code thermomètre

**DC** Tension continue (Direct Current)

**DC** Drain Commun

**DNL** Non linéarité différentielle (Differential Non-Linearity)

**DR** Droop Rate

**DSP** Digital Signal Processing

**DTI** Isolement à tranchée profonde (Deep Trench Isolation)

**EC** Emetteur Commun

EMBRACE Electronic Multi-Beam Radio Astronomy ConcEpt

ECL Logique à emetteurs couplés (Emitter coupled logic)

**ENOB** Nombre de bits effectifs (Effective Number Of Bit)

**ERBW** Résolution effective de la bande passante (Effective Resolution BandWidth)

E/B Echantillonneur-Bloqueur

**FFT** Transformée de Fourier rapide (Fast Fourier Transform)

**FP** Framework Program

**FPGA** Réseau de portes programmables in situ (Field-Programmable Gate Array)

FR4 Composite de résine époxy renforcé de fibre de verre (Flame Resistant 4)

GC Grille Commune

GS/s Giga échantillons par seconde

INL Erreur de linéarité intégrale (Integral Non-Linearity)

LNA Amplificateur faible bruit (Low Noise Amplifier)

LSB Bit le moins significatif (Least significant bit)

LVDS Signalisation différentielle basse-tension (Lot Voltage Differential Signaling)

MSB Bit le plus significatif (Most Significant Bit)

MS/s Mega échantillons par seconde

NDA Accord de non divulgation (Non-Diclosure Agreement)

NMOS N-type Metal-Oxide-Semiconductor logic

**NPN** N-doped P-doped N-doped

**NXP** Next eXPerience

**OSC** Oscillateur

**PMOS** P-type Metal-Oxide-Semiconductor

**PrepSKA** The Preparatory Phase for the SKA

**Q** Quantum

**QFP** Quad Flat Package

**RF** Radio fréquence

**ROM** Mémoire non volatile (Read-Only-Memory)

SC Source Commune

SEF Emetteur suiveur commuté (Switched Emitter Follower)

Si Silicium (Silicon)

SiGeC Silicon Germanium :Carbon

**SKA** Square Kilometre Array

**SKADS** Square Kilometre Array Design Studies

SFDR Plage dynamique sans parasites (Spurious Free Dynamic Range)

SNDR (SINAD Rapport signal sur bruit avec distorsion (Signal to Noise and Distorsion Ratio)

**SNR** Rapport signal sur bruit (Signal to Noise Ratio)

**SOI** Silicium sur isolant (Silicon On Insulator)

SR Vitesse de balayage (Slew Rate)

**THD** Taux de distorsion harmonique (Total Harmonic Distortion)

TRMC Taux de réjection du mode commun

## Liste des symboles

$A_v$  Gain en tension disponible

$A_{vf}$  Gain en tension disponible lorsque l'entrée est adaptée

$A_{INV}$  Gain en tension des inverseurs

$C_{eb}$  Capacité emetteur base

$C_h$  Capacité de charge de l'échantillonneur-bloqueur

$C_{ox}$  Capacité de grille par unité de surface  $(F/m^2)$

$E_{Q_{rms}}$  Erreur de quantification

$F_{BP}$  Bande passante en Fréquence

$F_t$  Fréquence de transition d'un transistor

$F_{max}$  Fréquence maximum d'un transistor

$F_s$  Fréquence d'échantillonnage

$G_m$  Tansconductance (mA/V)

L Largeur du canal d'un transistor MOS

$P_{HDmax}$  Puissance de l'harmonique la plus élevée

$Q_{Ch}$  Charge de la capacité

$R_{Echelle}$  Valeur d'une résistance de l'échelle de résistance

$R_p$  Résistance équivalente de charge

$R_{out}$  Résistance de sortie

$S_{11}$  Coefficient de réflexion en entrée d'un quadripôle

$S_{12}$  Coefficient de transmission de la sortie vers l'entrée d'un quadripôle

$S_{21}$  Coefficient de transmission de l'entrée vers la sortie d'un quadripôle

$S_{22}$  Coefficient de réflexion en sortie d'un quadripôle

$Scc_{21}$  Gain en puissance du mode commun

$Sdd_{11}$  Coefficient de réflexion différentiel en entrée d'un quadripôle

$Sdd_{12}$  Coefficient de transmission différentiel de la sortie vers l'entrée

$Sdd_{21}$  Gain en puissance du mode différentiel

$Sdd_{22}$  Coefficient de réflexion différentiel en sortie d'un quadripôle

$Sortie_{num}$  Code numérique de sortie en fonction des sorties binaires

$T_{latch}$  Temps de basculement nécessaire pour un niveau logique en sortie

$V_A$  Tension d'Early

$V_{LSB}$  Valeur en tension du bit de poids le plus faible

$V_{cc}$  Tension d'alimentation analogique

$V_{dd}$  Tension d'alimentation numérique

$V_{gs}$  Différence de potentiel entre la grille et la source d'un transistor MOS

$V_{IN}$  Tension d'entrée

$V_{IN+}$ ,  $V_{IN-}$  Respectivement la valeur de la tension de l'entrée "+" et de l'entrée "-" d'une entrée différentielle

$V_{in_{dun}}$  Plage dynamique de l'entrée

$V_{Offset}$  Tension d'offset

$V_{pp}$  Tension crête-crête

$V_{REF+}$ ,  $V_{REF-}$  Respectivement la valeur de la tension de l'entrée "+" et de l'entrée "-" de l'échelle de référence

$V_{t0}$  Tension de seuil

W Longueur du canal d'un transistor MOS

$Z_{ch}$  Impédance de charge

$Z_{in}$  Impédance d'entrée

$Z_S$  Impédance de sortie

## Introduction

Le travail décrit dans ce mémoire se situe dans le contexte d'études préparatoires à un projet international de radioastronomie, le projet Square Kilometre Array (SKA).

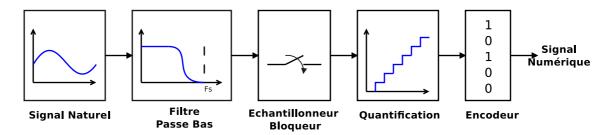

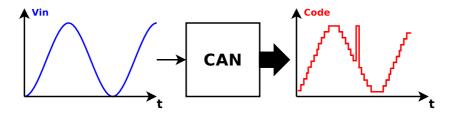

La radioastronomie est une branche de l'astronomie traitant de l'observation du ciel dans le domaine des ondes radioélectriques. Les instruments nécessaires pour cette branche se nomment des radiotélescopes. Ils exigent un développement électronique identique à celui des récepteurs radio, dans lesquels nous trouvons souvent des convertisseurs analogiques numériques (CAN).

Les applications de la radioastronomie demandent des performances électroniques de plus en plus sévères (bruit, dynamique, numérisation). Mon travail de thèse se situe dans ce contexte.

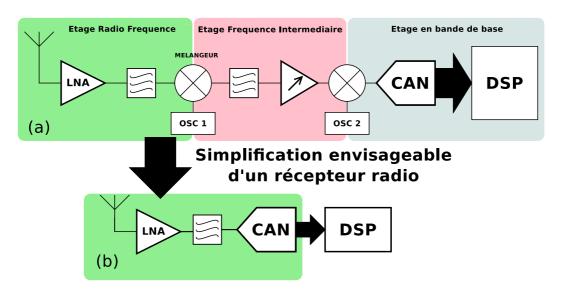

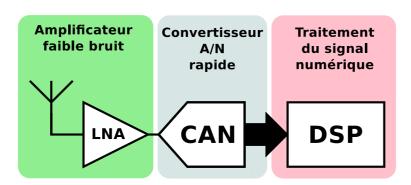

Les divers procédés technologiques utilisés dans l'électronique d'aujourd'hui (téléphonie portable, micro-processeurs ...) permettent la conception de CAN performants fonctionnant en haute fréquence, ou plutôt ce que l'on nomme des CAN ultra-rapides. Ils permettent une simplification de l'aspect système radiofréquence (RF) d'une chaîne de réception en traitant directement toute la bande de fréquence désirée (figure 1). Cette vue d'ensemble simplifiée est innovante et séduit les chercheurs radioastronomes actuels pour regarder librement le ciel dans une large bande de fréquence.

Mes divers travaux effectués pendant ma présence à la station de radioastronomie de Nançay se sont orientés sur la conception de CAN ultra-rapides. La prise en compte des bandes de fréquences d'observations propres aux projets radioastronomiques du futurs (bande L<sup>1</sup>) est très importante pour le choix d'une structure du CAN.

Il existe en effet beaucoup de solutions pour convertir un signal analogique en signal numérique. Nous pouvons citer des convertisseurs à rampes, à approximations successives, sigma delta, pipelines, flash, semi-flash. D'après l'état de l'art des CAN (voir la première partie) à l'heure actuelle, seule une structure flash permet de numériser en une seule fois la bande L (figure 1.b), sans transposer différentes bandes de fréquences en bande de base (figure 1.a).

Parmi les avantages et inconvénients de la structure flash décrits dans le chapitre I, l'accessibilité et le financement d'un procédé technologique sont à considérer fortement. L'accès d'un procédé CMOS et BiCMOS de  $0,25~\mu m$  de finesse de gravure a été choisi dans le laboratoire où j'ai travaillé. Ce critère a permis de scinder en deux l'étude de la conception des CAN.

<sup>1.</sup> La bande L est la partie du spectre électromagnétique définie par les fréquences de 1 à 2 GHz environ. Les fréquences de 1,4 à 1,427 GHz sont attribués à des fins de recherches spatiales et scientifiques, dont la radioastronomie.

FIGURE 1 – a. Récepteur hétérodyne en bande L (CAN « 1 GS/s), b. Récepteur radio simplifié en bande L (CAN > 3 GS/s)

Dans un premier temps, l'usage des transistors CMOS 0,25  $\mu m$  (chapitre II) est apparu utile pour valider une méthode (conceptions/simulations, réalisations et tests) pouvant être appliquée à des technologies MOS de gravures plus fines mais très coûteuses (CMOS 65 nm, 45 nm).

Dans un second temps, l'usage des transistors bipolaires 0,25  $\mu m$  SiGeC a été exploré pour plusieurs raisons (décrites dans le chapitre III). Cela a permis de compléter la méthode de conception des CAN rapides et de montrer la capacité à numériser la bande L en ayant un coût relativement faible.

## 0.1 Contexte scientifique

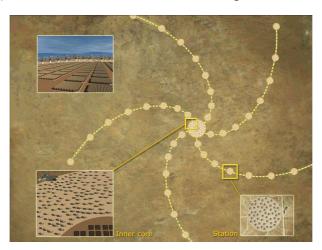

Le projet international Square Kilometre Array (SKA) sera le plus grand radio-télescope jamais construit au monde, composé de plusieurs millions d'éléments de réception. La thématique majeure du radiotélescope SKA sera l'observation des pulsars et des trous noirs, l'exploration des limites de la gravitation [1] [2] [3]. Actuellement le projet Square Kilometre Array (SKA), qui implique la participation de dix-neuf pays, est en cours de développement dans différents laboratoires.

Ce radiotélescope du futur sera 50 fois plus sensible, aura une plus grande résolution angulaire et spectrale que tout ce qui a été construit jusqu'à maintenant. Grâce à sa grande surface collectrice, le radiotélescope sera d'une grande sensibilité. Le radiotélescope SKA sera composé d'un réseau d'antennes radio réparties sur 3000 kilomètres au sol. 50 % de cette surface collectrice sera répartie sur une surface de 5 kilomètres de diamètre, 75 % sur 150 kilomètres de diamètre, et le reste dans différentes stations réparties dans différents endroits du monde (figure 2). Ce projet effectuera des observations dans des bandes de fréquence comprises entre 70 MHz à 25 GHz. Pour cela, différents

instruments seront utilisés, chacun dédié à une bande de fréquence.

FIGURE 2 – Struture du Square Kilometer Array

La surface collectrice la plus importante sera composée d'une matrice d'un kilomètre carré d'antennes appellées « Aperture array » (Réseaux phasés). Un nouveau concept a été utilisé pour cela : un réseau phasé composé de plusieurs tuiles permettra l'observation de l'ensemble du ciel. Ce réseau sera le coeur du radiotélescope. Puis des centaines de stations de 100 à 200 mètres de diamètre composées de paraboles couvriront le reste de la surface prévue pour le radiotélescope. Il sera possible d'analyser 8 champs d'observation indépendants soit 10 objets différents ce qui permettra d'accroître la vitesse des mesures.

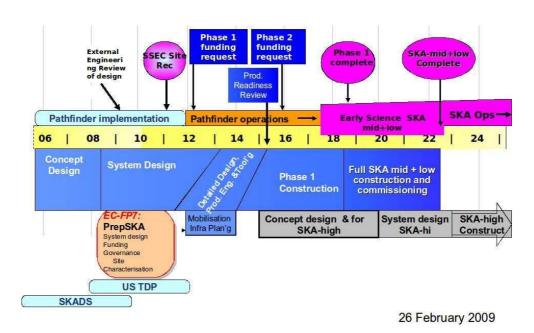

En attendant la réalisation du radiotélescope, SKA devra répondre à des spécifications techniques particulières. La bande de fréquence à couvrir sera de 70 MHz à 25 GHz à l'aide de 3 types de réceptions différentes afin de découper les mesures en 3 bandes de fréquences. Le taux de calcul sera de 1015 opérations par seconde et un taux de sorties de données d'un Téra octet par minute. Il faudra alors 10 ans pour la construction de cet immense radiotélescope avant d'obtenir le résultat final (figure 3).

Afin d'acheminer le projet jusqu'à sa réalisation, plusieurs études sont en cours. Des démonstrateurs et des collaborations européennes permettent de valider des concepts. Les phases de définitions et d'études sont soutenues par la commission européenne, dans le cadre de FP6 (SKADS : SKA Design Study) et FP7 (PrepSKA et AAVP, la poursuite du concept européen de réseaux phasés d'antennes).

Le démonstrateur européen EMBRACE (Electronic Multi-Beam Radio Astronomy ConcEpt) cherche à démontrer la faisabilité du concept à réseau phasé qui compose 50 % du radiotélescope SKA, à travers le consortium européen SKADS [4] [5]. Une partie du démonstrateur est réalisée à la Station de Radioastronomie de Nançay avec une surface collectrice de 80  $m^2$ . L'autre partie est située à Westerbork aux Pays-Bas avec une surface collectrice de 300  $m^2$ . Les 2 sites seront reliés par des fibres optiques afin de réaliser des mesures d'interférométrie pour valider le concept européen.

FIGURE 3 – Feuille de route du projet SKA

Les antennes utilisées pour le projet EMBRACE sont des antennes Vivaldi validées par les Hollandais. [6] a démontré les aspects fondamentaux du concept de réseaux phasés. Les antennes sont regroupées par 72 pour donner lieu à une tuile (figure 4). L'électronique qui lui est associée comporte autant d'amplificateurs faible bruit (LNA) que d'antennes (72) et 18 circuits « beamformers ». Le circuit « beamformer » est l'un des circuits intégrés de l'Unité Scientifique de Nançay (USN) qui a été retenu pour le démonstrateur [7]. Il permet de former 2 champs d'observation : il recombine en phases les signaux voulus en sorties de 4 antennes et permet une variation de gain de 4 dB maximum sur chaque voie Radio Fréquence (RF), cela pour récupérer des erreurs de gain entre les différentes voies.

FIGURE 4 – Une tuile composée d'antennes Vivaldi avec commandes intégrées

L'observatoire de Paris et plus particulièrement la station de radioastronomie de Nançay est fortement impliqué dans les études préparatoires à SKA, à travers :

- Le contrôle-commande du démonstrateur EMBRACE

- Le management

- Fonctionnement du réseau

- Le traitement des données

- Conception de circuit intégré microélectonique

- Fonctionnement du démonstrateur sur site

- Le traitement des interférences

Par conséquent, le laboratoire de microélectronique de la station de radio-astronomie de Nançay développe des LNAs, des filtres, des convertisseurs analogiques numériques, des circuits beamformers et différentes études sur silicium. Cette thèse se place en tant que prospective dans le cadre du projet européen SKADS dont l'objectif à long terme de l'équipe de microélectronique de Nançay est de concevoir un circuit intégré à entrée analogique faible bruit et à sortie numérique haut débit.

## 0.2 Objectifs

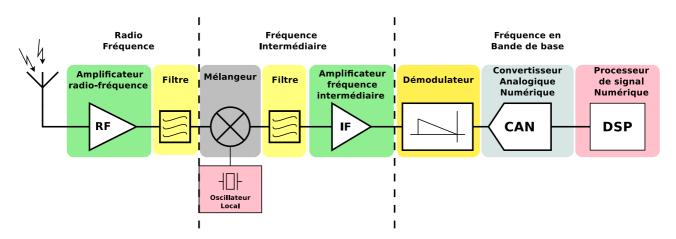

Dans la mesure astronomique comme dans les récepteurs radio, nous utilisons un CAN qui permet de numériser une bande de fréquence à proprement dite. Il existe plusieurs types de récepteurs radio [8] dont le plus connu est le récepteur hétérodyne illustré en figure 5.

FIGURE 5 – Diagramme récepteur superhétérodyne

Cette architecture est scindée en 3 parties :

- la radio-fréquence (antenne et LNA et filtre)

- la fréquence intermédiaire (mélangeur, oscillateur, amplificateur, filtre)

- la fréquence en bande de base (démodulateur)

Cette architecture est complexe et reste difficilement intégrable à cause de la partie filtrage et du mélangeur. Cependant la faisabilité d'un système de réception tout intégré a été démontrée [9].

Un procédé de simplification consiste à enlever la partie « fréquence intermédiaire » et à numériser directement les signaux analogiques avec un CAN rapide, comme l'illustre la figure 6. C'est un système qui reste très flexible car le traitement ne se fait que numériquement et la complexité est moindre. Les contraintes sur le CAN deviennent sévères : pour numériser la bande L jusqu'à 1.5 GHz, il faut une très grande rapidité, ce qui est en opposition avec une large dynamique, comme le montrent des études précédentes : très faible résolution binaire et très haute rapidité [10] et inversement pour [11].

FIGURE 6 – Diagramme de réception rapide

L'objectif principal de cette thèse est de concevoir un CAN capable de numériser les signaux analogiques dans la bande 100 - 1500 MHz. Les principales contraintes pour cette conception sont la bande passante, la consommation, la dynamique, mais aussi le choix technologique qui peut fortement influer sur le coût d'un prototype. De plus, le coût est un élément essentiel dans l'étude d'un projet. Un projet tel que SKA utilise les composants à des milliers d'exemplaires, à terme lors des réalisations finales, le choix de la conception d'ASIC reste à ce jour la solution la plus rentable en terme de coût. Ces diverses contraintes constituent le cahier des charges.

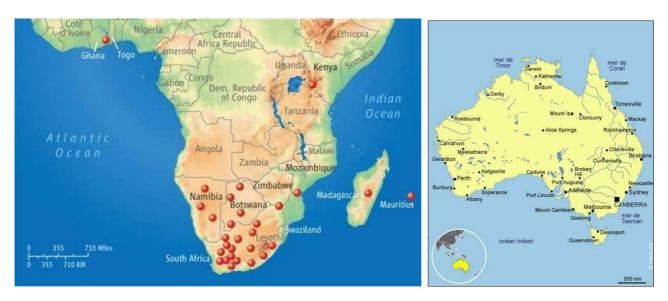

### 0.3 Choix des paramètres du CAN pour le radiotélescope SKA

Le radiotélescope sera installé sur un site radioélectrique relativement propre, deux endroits sont encore en compétition : l'Afrique du sud et l'Australie (figure : 7). Ce choix, en minimisant les interférences d'origine humaine au sol (télévision, radio, téléphones,...), permet de restreindre la dynamique de la chaîne de réception. Ceci permet de limiter la dynamique du CAN, et ainsi de diminuer la consommation du radiotélescope.

FIGURE 7 – Les deux sites en compétition pour l'accueil du radiotélescope SKA : l'Afrique du sud et l'Australie

Dans le papier blanc de SKADS [12] plusieurs critères permettent de faire le choix du CAN : la fréquence d'échantillonnage, la dynamique et la consommation.

### La fréquence d'échantillonnage

Tout d'abord le choix de la technologie est le premier critère de sélection, il définit le coût et la vitesse de fonctionnement. La technologie silicium semble pouvoir atteindre les fréquences de fonctionnement voulues grâce à l'évolution du marché et des exigences en matière de communications à haute vitesse, haute résolution vidéo et tout en gardant une consommation faible. Les CAN rapides atteignant 3 à 3,5 GHz de fréquence d'échantillonnage sont réalisables. C'est la condition nécessaire à l'étude présentée dans ce mémoire, qui en premier lieu veut permettre de simplifier la chaîne de réception en supprimant la transposition de fréquence.

La fréquence d'échantillonnage est un paramètre important car il impose la consommation, plus la fréquence d'échantillonnage est élevée, plus la consommation croît fortement.

#### La dynamique

Les réseaux phasés de tuiles ne requièrent pas une forte résolution en tension, environ 3 bits sont suffisant pour numériser la chaine d'acquisition analogique. Cependant le besoin en résolution binaire augmente avec deux facteurs principaux : les interférences radio fréquence (RFI) et la largeur de la plage analogique. Il est nécessaire de numériser avec précision la plupart des RFI pour maintenir la linéarité et ne pas avoir à jeter un nombre excessif de blocs de données.

Plus la résolution numérique du CAN est élevée plus cela est bénéfique à la chaîne analogique (LNA, Beamformer). On peut avoir une meilleure précision et obtenir une diminution de la plage analogique. Toutefois, une réduction de la plage analogique de tension ajoute des exigences sur la valeur des pas de quantification (Quantum) lors de la numérisation. Le CAN se doit d'être précis afin de ne pas effectuer une erreur lors de cette numérisation. De plus, la précision du CAN engendre une consommation élevée.

Au contraire, une augmentation de la plage analogique d'entrée diminue les exigences du CAN mais demande une surconsommation de la chaine d'acquisition (LNA) et de la partie analogique d'entrée du CAN afin d'acquérir la plage totale de tension.

Un CAN 6 bits à 3 GS/s semble être un bon compromis entre performances pour les mesures astrophysiques de très bonne qualité et consommation [12].

#### La consommation

La consommation est un paramètre crucial dans la conception du CAN, car le futur radiotélescope sera composé de plusieurs CAN par tuile. Dans les versions prototypes comme actuellement EMBRACE et prochainement AAVP, il y a un CAN par faisceau (beam) radiofréquence et par polarisation formés. La consommation totale pour la numérisation dépend entièrement du nombre de faisceaux (beams) radiofréquences réalisés lors de la construction finale du radiotélescope SKA.

D'après [12], un CAN 6 bits à 3 GS/s est raisonnable. Une étude sur un CAN est réalisée par IBM qui montre des bons résultats de simulation avec une technologie silicium très fine (45 nm) mais très coûteuse en prototypage et en production. La consommation pour ce CAN complet est inférieure à 100 mW pour une résolution de 4 bits. Une hypothèse est donc émise avec une technologie silicium en 22 nm avec une consommation inférieure à 70 mW. Ces hypothèses sont le point de départ de l'étude qui suit.

La consommation peut diminuer fortement avec le choix d'une technologie de très fine gravure mais avec un coût de fabrication relativement élevé qui ne devient pas négligeable pour une production de plusieurs centaines de milliers d'exemplaires.

Pour des raisons de coût et d'accès aux technologies fines en prototypage, l'étude est faite sur une technologie  $0,25~\mu m$  en gardant les spécifications en fréquence d'échantillonnage et en dynamique. Cependant, il est impossible d'avoir une faible consommation avec ce type de technologie.

### 0.4 Organisation du mémoire

Après une présentation succincte sur le projet international scientifique SKA pour lequel les CAN rapides devront être utilisés, la suite du mémoire est divisé en trois parties principales.

La première partie, après un rappel sur les notions de bases en électronique et plus particulièrement les transistors utiles à cette étude, donne les contraintes techniques et technologiques. Les caractéristiques ainsi que les différents types de convertisseurs analogiques numériques sont présentés dans ce chapitre. Cela permet de fixer un choix de structure pour les CAN rapides. Le développement de CAN étant le sujet de l'étude décrite dans ce mémoire.

La deuxième partie décrit les différentes parties d'un CAN flash ultra rapide : échantillonneur-bloqueur, comparateur, encodage numérique. Ces différentes parties sont appliquées à la conception du premier CAN flash en technologie CMOS  $0,25~\mu m$  ayant une fréquence d'échantillonnage de  $1~{\rm GS/s}$ , une bande de fréquence de Nyquist de  $500~{\rm MHz}$  et une résolution de  $6~{\rm bits}$ . Outre la caractérisation du CAN flash longuement décrite (INL, DNL, SNR, SFDR, ENOB ...), le dessin du masque du circuit n'est pas à négliger et est aussi expliqué dans la deuxième partie de ce chapitre, comme par exemple l'échelle de résistance. Enfin, ce chapitre se termine par les mesures du circuit réalisé en décrivant brièvement un banc de test et ses difficultés.

La troisième partie, suivant un plan similaire à la deuxième, décrit l'étude et la réalisation d'un CAN flash. La méthodologie de conception est alors appliquée à un CAN flash en technologie bipolaire SiGeC 0,25  $\mu m$  ayant une fréquence d'échantillonnage de 3 GS/s, une bande de Nyquist de 1,5 GHz et une résolution de 6 bits. Les topologies du second circuit diffèrent nettement du premier, que ce soit l'échantillonneur-bloqueur, les comparateurs, mais surtout l'encodage numérique où la rapidité nécessaire n'a pu être réalisée qu'en logique numérique ECL (logique à émetteur commun). Cette partie est décrite dans le troisième chapitre. En suivant la méthode du deuxième chapitre, le dessin du masque est expliqué (l'isolation des cellules) ainsi que la configuration d'un nouveau banc de test adapté à une fréquence d'échantillonnage élevée (supérieure à 1 GS/s).

Enfin une conclusion générale reprend les principaux résultats obtenus et propose des pistes pour de nouvelles études.

# Première partie

Rappel sur les notions de base des CAN et les composants utilisés

# Chapitre 1

# Rappel sur les transistors

Dans le cadre de cette étude, à savoir la conception de CAN très rapides, dans la bande de fréquence 100 - 1500 MHz, plusieurs aspects ont été pris en considération dont le choix technologique effectué par le laboratoire. Avant de décrire un état de l'art sur les CAN, on effectuera un bref rappel sur les transistors et leur topologie de base.

### 1.1 Contrainte technologique

Un accord de non-divulgation (NDA - Non-Disclosure Agreement) a été signé avec NXP Philips Caen pour utiliser leurs technologies. Ainsi, nous avons la possibilité d'utiliser leur technologie Qubic4X 0,25  $\mu m$  BiCMOS. Celle-ci reste abordable par rapport à une technologie 45 nm CMOS qui, à l'heure actuelle, demeure à un prix exorbitant pour la réalisation de circuits. De plus, la 65 nm ou 45 nm ne sont pas prévus pour la conception radiofréquence mais exclusivement pour réaliser des cellules numériques, d'où une difficulté supplémentaire pour des circuits mixtes.

La technologie Qubic4X permet de valider et de réaliser des systèmes complexes avec une consommation qui reste convenable par rapport à une technologie de plus fine gravure. Aussi, la technologie Qubic4X permet l'accès à tous les composants passifs : capacité, inductance et résistance. Enfin, deux types de transistors sont mis à notre disposition (CMOS et bipolaire) dont nous donnons quelques caractéristiques techniques ci-dessous.

### La technologie Qubic4X

Philips a une technologie à base de silicium BiCMOS pour les nouvelles applications à radiofréquences (RF). Elle est basée sur du silicium germanium carbone (SiGeC) avec un  $F_T$  de 130 GHz et un facteur de bruit minimum de 0,4 dB. Son très faible facteur de bruit s'adapte aux récepteurs RF sensibles [13]. En termes de gain et de facteur de bruit, les transistors bipolaires Qubic4X rivalisent avec les transistors sur Arséniure de Gallium pour des fréquences inférieures à 10 GHz.

La technologie de NXP est donc utilisée pour des applications micro-ondes qui nécessitent des bas coûts. La technologie Qubic4X actuelle permet la conception de solutions analogiques et numériques RF plus fortement intégrées.

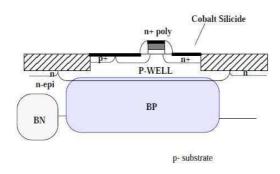

### 1.2 Caractéristiques principales des transistors NMOS et PMOS

Le transistor MOS est un transistor à effet de champ constitué d'un substrat semiconducteur recouvert d'une couche d'oxyde sur laquelle est déposée l'électrode de grille. Une différence de potentiel appliquée entre la grille et le substrat crée un champ électrique dans le semiconducteur qui repousse les porteurs majoritaires loin de l'interface oxyde-semiconducteur. Ce champ laisse diffuser des porteurs minoritaires venus de deux îlots de type complémentaire au substrat, la source et le drain. Ceux-ci forment un canal. Ces charges transitent entre le drain et la source situés aux extrémités du canal [14].

Dans le tableau 1.1 suivant apparaissent les principales caractéristiques des transistors NMOS et PMOS de la technologie Qubic4X, notamment les tensions de seuil, les dimensions et le beta square.

| Paramètres | Taille en $\mu m$ | NMOS  | PMOS   | Unités           | Commentaires     |

|------------|-------------------|-------|--------|------------------|------------------|

| $V_{t0}$   | $10/0,\!25$       | 0,569 | -0,534 | Volts            | Tension de seuil |

| Leff       | 10/0,25           | 0,19  | 0,15   | $\mu m$          | Longueur         |

| Weff       | $10/0,\!25$       | 10    | 10     | $\mu m$          | Largeur          |

| Rota Sa    | 10/10             | 236   | 52 77  | $\mu \Delta/V_2$ | uC.              |

Table 1.1 – Caractéristiques des transistors NMOS et PMOS

Ci-dessous est présentée une vue de coupe du transistor NMOS: 1.1

FIGURE 1.1 – Vue de coupe du transistor MOS

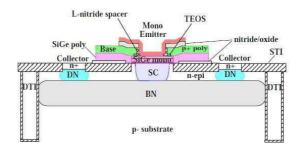

# 1.3 Caractéristiques principales du transistor Bipolaire SiGeC NPN

Le transistor bipolaire NPN est composé de trois zones dopées qui sont l'émetteur fortement dopé « n », la base (fine) dopée « p » et le collecteur faiblement dopé « n ». Il s'agit donc de deux jonctions PN tête-bêche ayant une zone en commun [14]. La technologie QUBIC4X propose plusieurs types de transistors bipolaires NPN sensiblement identiques. Dans le tableau 1.2 suivant apparaissent les principales caractéristiques d'un des transistors NPN, notamment la fréquence de transition, la tension Early et le Beta.

| Paramètres            | Taille en $\mu m$ | NPN   | Unités     | Commentaires  |

|-----------------------|-------------------|-------|------------|---------------|

| $F_T$                 | $0,\!4/10$        | 140   | Giga Hertz | Peak $F_T$    |

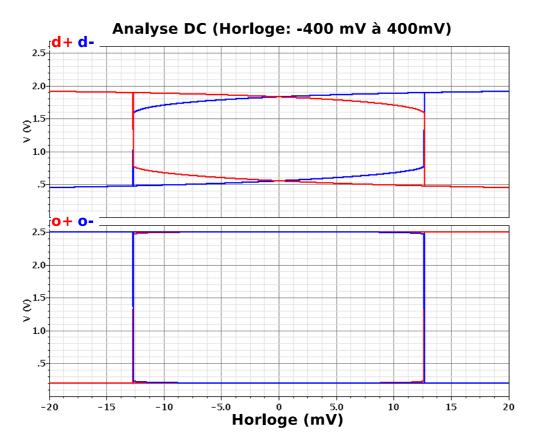

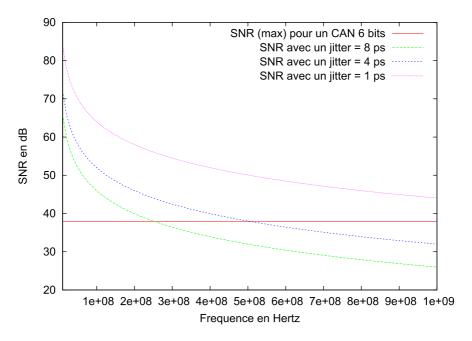

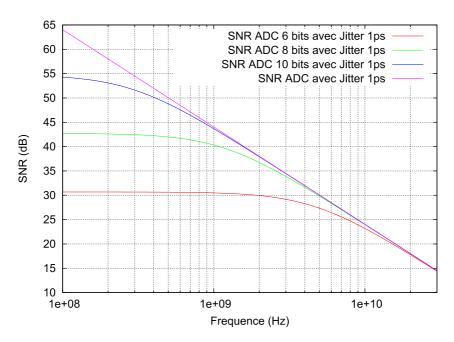

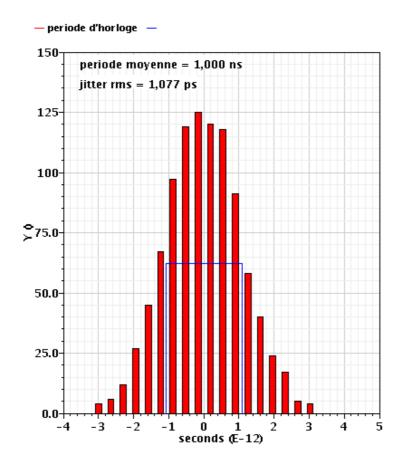

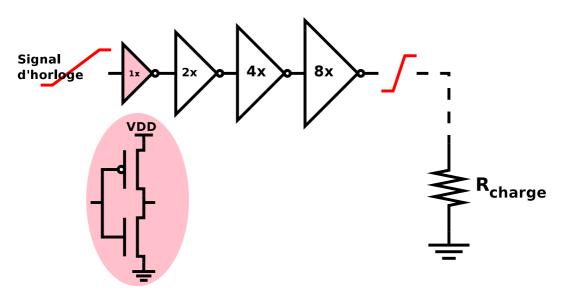

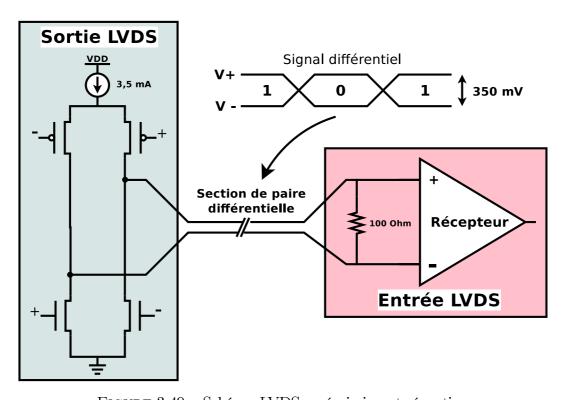

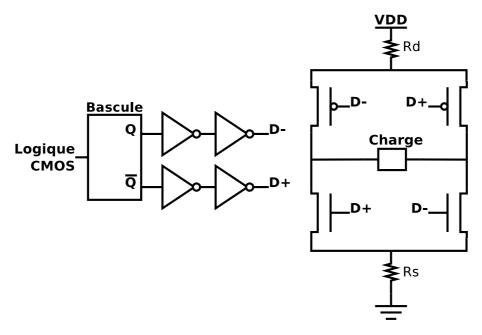

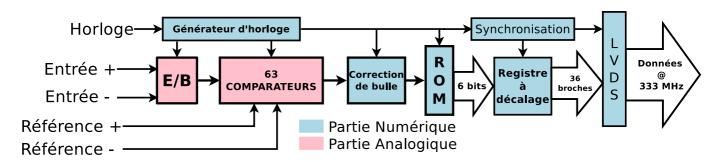

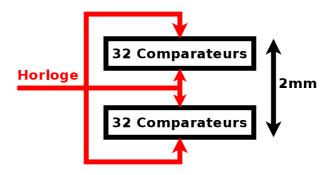

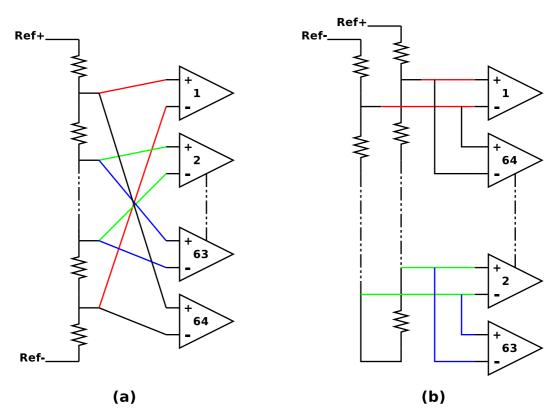

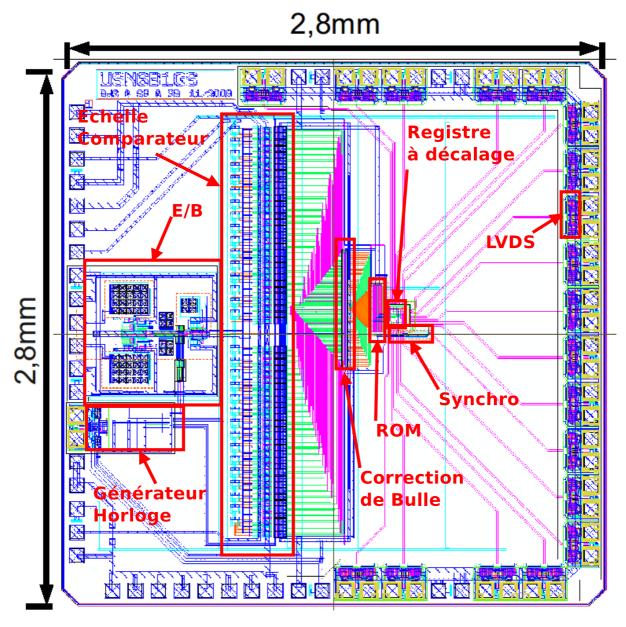

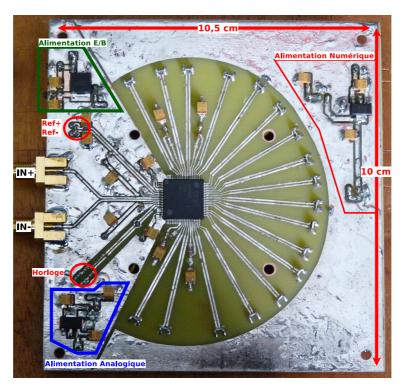

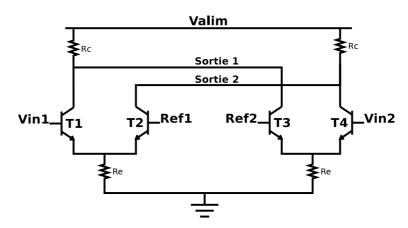

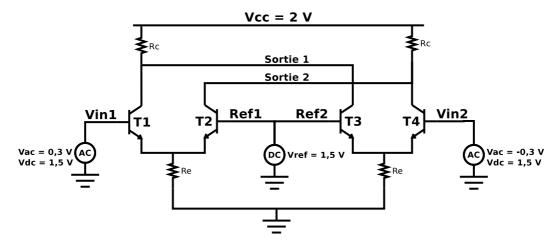

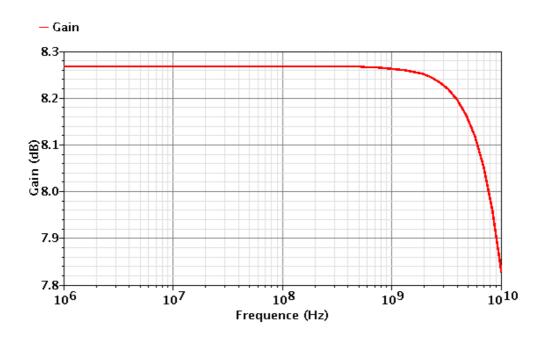

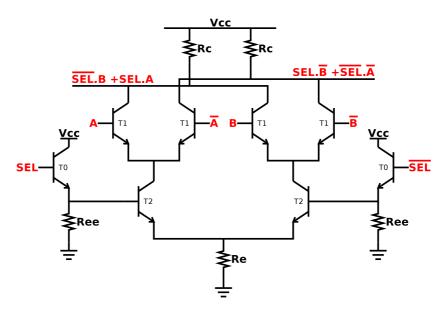

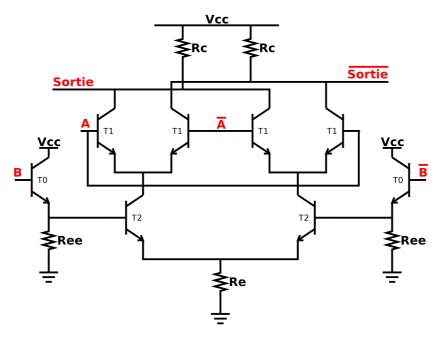

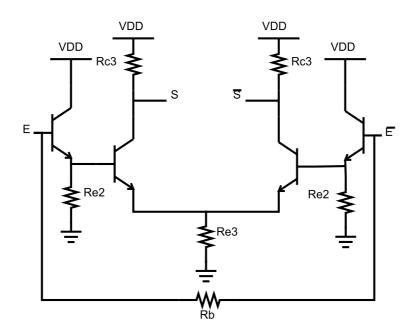

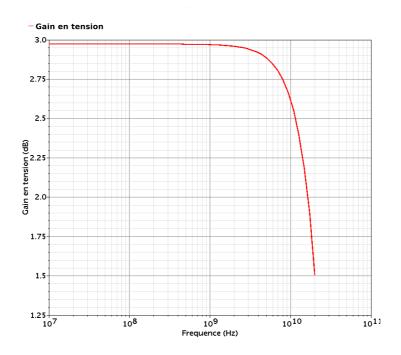

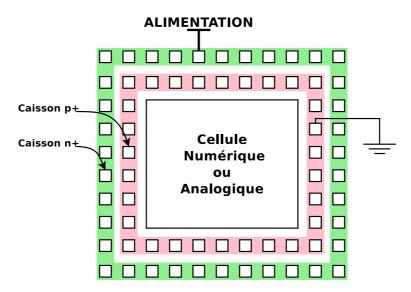

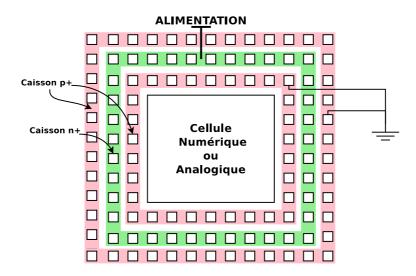

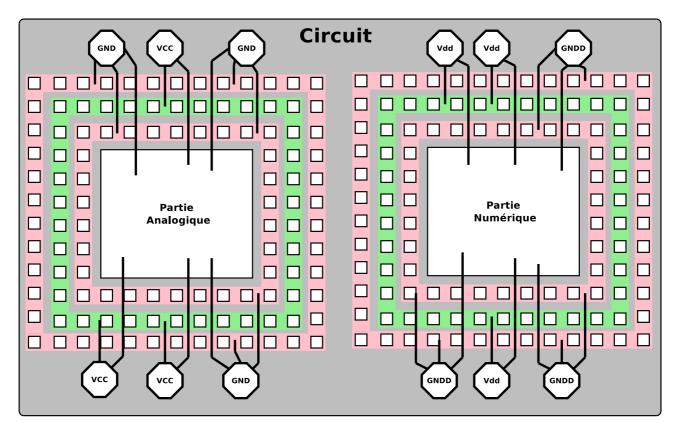

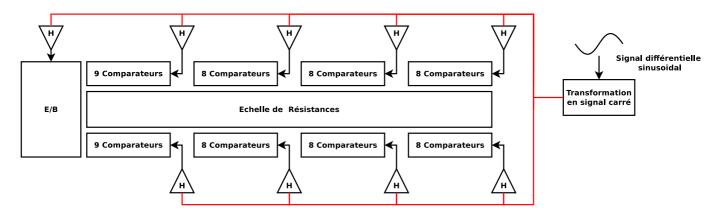

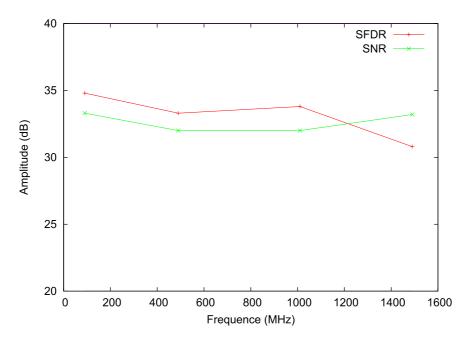

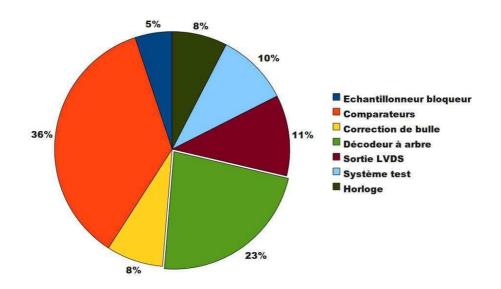

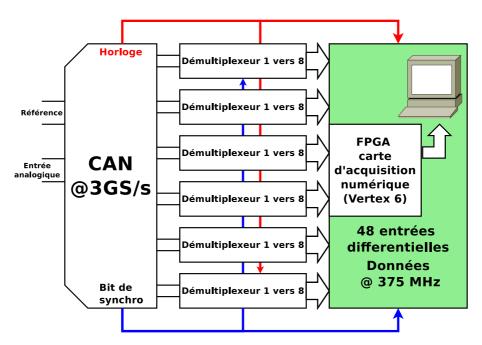

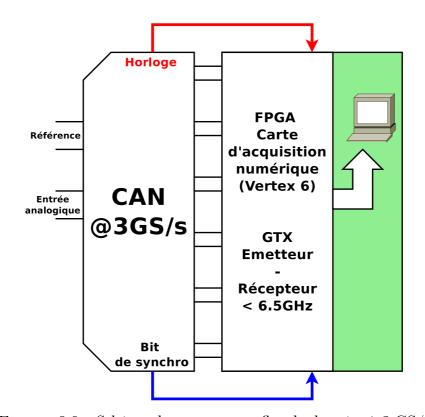

| $F_{max}$             | $0,\!4/10$        | 180   | Giga Hertz |               |