# Contributions aux processeurs multi-coeurs massivement parallèles en technologie en rupture : routage tolérant aux fautes de réseau d'interconnexion et auto-adaptabilité des applications

Fabien Chaix

#### ▶ To cite this version:

Fabien Chaix. Contributions aux processeurs multi-coeurs massivement parallèles en technologie en rupture : routage tolérant aux fautes de réseau d'interconnexion et auto-adaptabilité des applications. Autre. Université Grenoble Alpes, 2013. Français. <NNT : 2013GRENT057>. <tel-00951424>

HAL Id: tel-00951424 https://tel.archives-ouvertes.fr/tel-00951424

Submitted on 24 Feb 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano-Électronique et Nano-Technologies

Arrêté ministériel: 7 août 2006

Présentée par

#### **Fabien CHAIX**

Thèse dirigée par **Michael NICOLAIDIS** et codirigée par **Nacer-Eddine ZERGAINOH**

préparée au sein du laboratoire TIMA, Équipe ARIS, et de l'école doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal

# Contributions for late CMOS many-cores processors: NoC fault-tolerant routing and auto-adaptive applications

Contributions aux processeurs multi-cœurs massivement parallèles en technologie en rupture: Routage tolérant aux fautes du réseau d'interconnexion et auto-adaptabilité des applications

Thèse soutenue publiquement le **28 Octobre 2013**, devant le jury composé de :

Michel RENOVELL, Président

Directeur de Recherche CNRS, LIRMM

Amer BAGHDADI, Rapporteur

Professeur, Telecom Bretagne

Nacer-Eddine ZERGAINOH, Examinateur

Maître de Conférences, Polytech' Grenoble

Michael NICOLAIDIS, Examinateur

Directeur de Recherche CNRS, TIMA

À Renée

# **Foreword**

First of all, I feel very grateful to Professor Renovell and Professor Baghdadi for reviewing this thesis, which required a large amount of their valuable time. Second, I would like to express my gratitude to Professor Nicolaidis and Doctor Zergainoh for offering me the opportunity of this thesis. Their flawless confidence and support have been precious on many occasions. I would like also to acknowledge the efforts of Professor Avresky who was essential on many scientific aspects. Finally, I have much respect for the administrative staff of TIMA, whose diligent efforts provide excellent working conditions to the laboratory researchers.

My thoughts also go to my family and friends who supported me for 5 -long- years. I would like to say how much their presence was essential for me not to fall into the dark side. I particularly thank my basket-ball co-players and my laboratory mates who shared many moments that I will long remember. Finally, I would like to express my gratitude to Madeleine and Alain for their proverbial hospitality.

The manuscript first features a summary in french, as required by the university. Then, english is utilized for the remaining of the thesis. First, an overall introduction presents the context and the motivations of this thesis. The second chapter presents novel fault-tolerant routing algorithms for 2D-Mesh Network on Chips. The third chapter presents techniques for the execution of parallel applications by many-core unreliable processors subject to variability. Finally, the fourth chapter presents the simulator developed during this thesis.

# Resumé

#### I Introduction

#### I.1 Contexte

Les nouvelles technologies ont envahi notre quotidien et de nombreux pays en dépendent sur le plan économique et social. En effet, les capacités de calcul en constante évolution ont permis l'émergence d'applications qui ont amélioré l'efficacité des agents et des moyens de communication, en plus d'ouvrir la porte à de nombreux loisirs dits numériques. Dans le futur, on peut gager que la mise au point de processeurs de calculs plus puissants sera donc nécessaire pour répondre aux besoins croissants de nos sociétés toujours plus connectées. L'utilisation de ces processeurs demandera néanmoins de pallier aux problèmes de fiabilité et de variabilité inhérents aux techniques de fabrication à venir. En effet, ces procédés produiront des circuits intégrés plus hétéroclites et plus sensibles aux conditions environnementales.

#### Évolution des processeurs

L'évolution des processeurs dans les deux prochaines décennies reste cependant très floue, et ce pour plusieurs raisons. Tout d'abord, les **demandes applicatives** évoluent rapidement et souvent de manière surprenante. Ensuite, les **contraintes physiques** donnent lieu à penser qu'un changement radical de l'industrie serait nécessaire; pour autant, les technologues pourraient contourner les limitations physiques actuelles, comme ils l'ont fait de nombreuses fois par le passé. Enfin, **les réalités économiques** influenceront grandement les évolutions futures de l'industrie microélectronique, avec pour objectif principal le retour sur investissement et la garantie de revenus stables pour les entreprises.

L'architecture des processeurs de calcul a longtemps été dictée par les exigences et les pratiques des informaticiens qui les programmaient. Certaines applications phares telles que l'édition de texte, puis la téléphonie mobile, l'internet ou enfin les services mobiles ont beaucoup influencé l'évolution du cahier des charges des processeurs. Plus récemment, l'avènement des téléphones intelligents (*smartphones*) et de fermes de serveurs (*cloud computing*, réseaux sociaux) implique d'exécuter quasi-simultanément de nombreuses tâches ayant des contraintes de fiabilité extrêmement différentes (e.g. transactions bancaires, lecture de flux vidéo, jeux gratuits).

En ce qui concerne les contraintes physiques, on peut relever trois points principaux. Premièrement, l'energie nécessaire à chaque opération diminue avec la tension de seuil des transistors. Comme celleci est liée à la taille de leur canal, cette contrainte a poussé à une miniaturisation effrenée des transistors. Ainsi, dans les dernières technologies industrialisées, le canal des transistors ne mesure qu'une vingtaine de nanomètres, alors que la taille des atomes de silicium est de l'ordre du nanomètre. Deuxièmement, une partie de l'énergie nécessaire à chaque opération est dissipée sous forme de chaleur. Par

conséquent, la concentration extraordinaire de transistors qui est obtenue aujourd'hui pose des problèmes de dissipation thermique. Ainsi, de nombreux experts estiment que la dissipation thermique sera l'obstacle principal pour les futures générations de processeurs [1]. Troisièmement, la fabrication industrielle de transistors de quelques nanomètres est très difficile. En effet, les procédés industriels sont terriblement complexes et coûteux, et nécessitent des investissements énormes pour la contruction d'unités de production. Les masques de lithographie sont également tellement chers qu'il n'est rentable d'utiliser les dernières technologies que pour des puces produites en grande série. Il y a ensuite des problèmes de plus en plus aigus de **variabilité** de la production. Il est en effet impossible de fabriquer en série des puces qui soient constituées de milliards de transistors tous identiques et fonctionnels. Qui plus est, les circuits obtenus sont plus sensibles aux radiations cosmiques et aux variations thermiques et électriques. En bref, il s'agira à l'avenir pour les ingénieurs d'obtenir un maximum de performance avec une énergie limitée et des composants aux caractéristiques disparates.

Les intérêts économiques de l'industrie microélectronique influent également sur l'évolution des processeurs. En effet, les contraintes industrielles de rendement de production, de retours sous garantie et de temps de mise sur le marché modulent beaucoup l'impact des solutions techniques, car il est vital pour les entreprises de garantir le bon fonctionnement des produits vendus, vu l'impact sur leurs finances et leur image. Par conséquent, la validation quasi-exhaustive de l'architecture et le test des puces en production sont des prérequis souvent nécessaires pour l'adoption de nouvelles techniques. Afin de diminuer le nombre de puces non conformes, il est également commun de procéder à un tri en fonction de la performance de chacune, et de les vendre plus ou moins cher en fonction de celle-ci (i.e. *binning*). En dernier recours, les techniques de **tolérance aux fautes** permettent d'augmenter la fiabilité des circuits obtenus, souvent par l'ajout de circuits redondants.

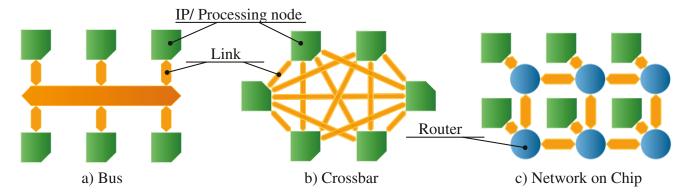

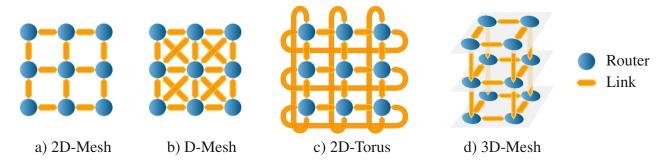

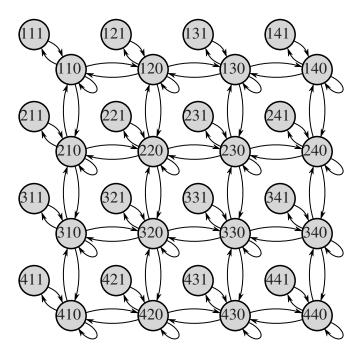

L'évolution future des processeurs sera donc le fruit de contraintes et d'opportunités diverses et changeantes. On peut néanmoins noter plusieurs observations. Tout d'abord, l' **efficacité énergetique** sera une caractéristique essentielle pour répondre aux besoins grandissants de mobilité et aux problèmes de dissipation thermique. Ensuite, les processeurs intégreront de plus en plus de cœurs de calculs ; qu'il s'agisse d'une grosse dizaine de cœurs extrêmement complexes (i.e. processeurs multicoeurs), ou de milliers de cœurs exécutant des opérations très simples (i.e. processeurs massivement parallèles). Dans tous les cas, la quantité de données traitées sera plus importante qu'aujourd'hui, et nécessitera l'utilisation de circuits d'interconnection plus intelligents. Dans le cas où plus d'une centaine de cœurs seront intégrés, il faudra alors recourir aux **réseaux sur puces** ou NoC¹.

#### Réseaux sur puces

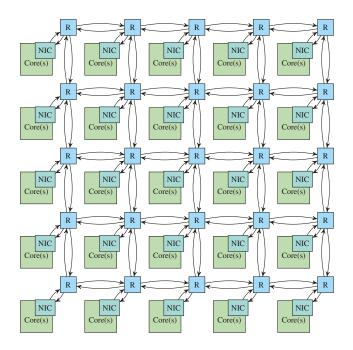

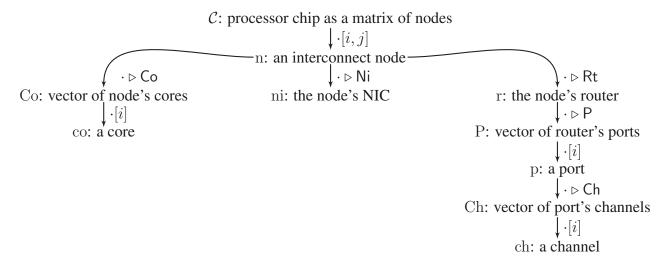

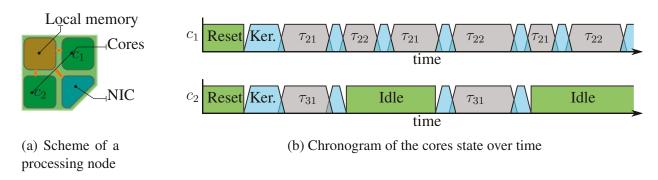

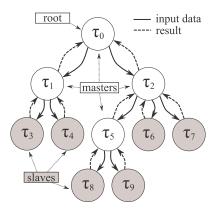

Depuis les années 2000, la perspective de puces composées de dizaines de propriétés intellectuelles ou IPs² a posé le problème de l'extensibilité (*scalability*) de leur interconnection. En effet, l'utilisation d'un bus devient tout à fait inefficace lorsque plus d'une dizaine de maîtres y sont connectés. En se basant sur les travaux préexistants dans les réseaux d'ordinateurs, les réseaux sur puces ou NoCs ont été proposés, notamment par [2]. Les NoCs ont pour fonction de transmettre des données entre différents **nœuds de calcul** eux-mêmes, composés d'un ou plusieurs cœurs, sous forme de paquets. Un exemple de NoC est ainsi présenté à la figure 1. Chaque nœud possède son interface réseau ou NIC³ pour le formatage des données et la gestion des transactions. Des routeurs sont disposés plus ou moins réguliérement, afin de diriger chaque paquet vers sa destination (i.e. routage). Chaque routeur embarque plusieurs **ports de sortie** et **ports d'entrée**, eux-mêmes connectés à un lien, afin de transférer physiquement les messages.

<sup>&</sup>lt;sup>1</sup>Network on Chip

<sup>&</sup>lt;sup>2</sup>Intellectual Propertys

<sup>&</sup>lt;sup>3</sup>Network Interface Circuit

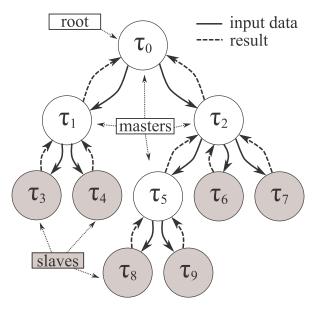

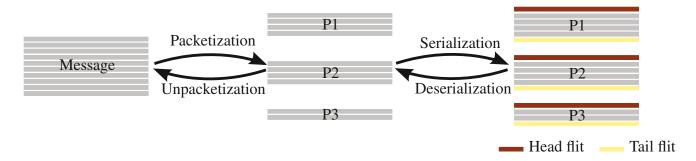

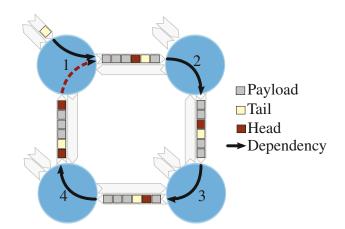

FIGURE 1 – Réseau sur puce en grille 2D

Plusieurs ressemblances existent entre les réseaux sur puce et les réseaux d'ordinateurs. Tout d'abord, le "routage par trou de ver" (wormhole routing) est généralement utilisé. Il s'agit de décomposer chaque message à transmettre en paquets de **flits**, et de transférer ces parties à la suite les unes des autres [3]. Un flit de tête, inséré avant le premier flit de données, contient les informations nécessaires aux routeurs pour sélectionner le chemin adéquat, et un flit de queue signale la fin du message. La segmentation de chaque message permet de réduire significativement les ressources matérielles du réseau, mais elle introduit des problèmes d'interblocage, qui compromettent son bon fonctionnement. La solution la plus commune est alors de restreindre l'algorithme de routage utilisé afin d'éviter l'apparition de "cycles de dépendances". En particulier, l'adjonction de canaux virtuels ou VCs<sup>4</sup> permet de simplifier la mise en oeuvre d'algorithmes de routage sans interblocage et/ou d'améliorer la performance du NoC en permettant la transmission concurrente de plusieurs messages sur un même lien.

#### Architecture des processeurs multicoeurs massivement parallèles

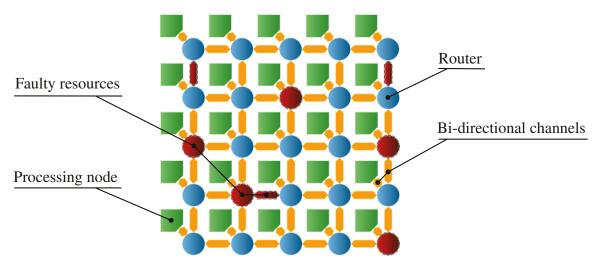

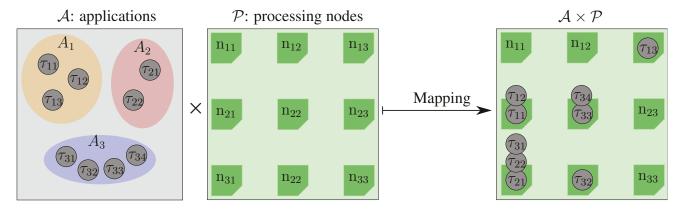

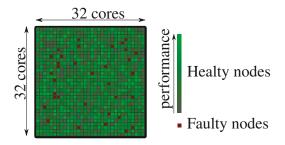

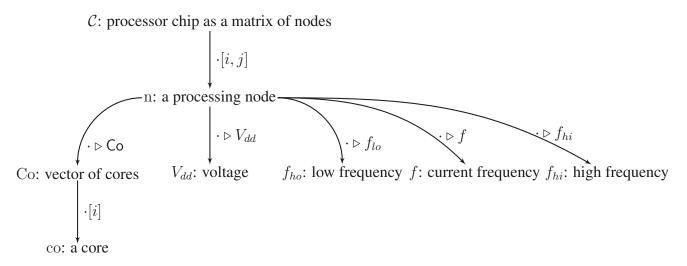

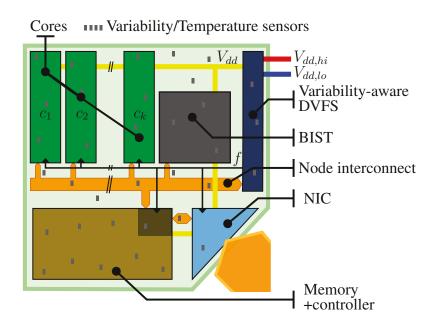

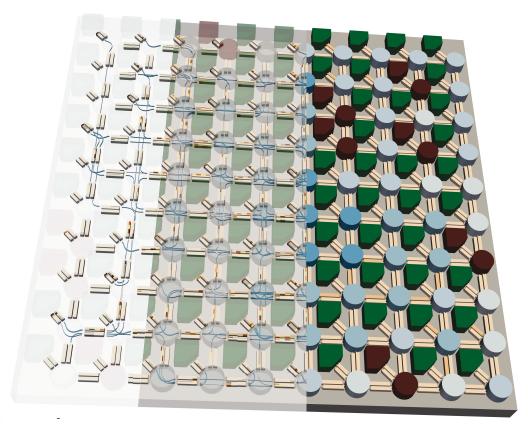

Dans cette thèse, nous considérons des processeurs multicoeurs massivement parallèles, consistant de milliers de cœurs fabriqués dans une technologie agressive, comme illustré par la Figure 2. Dans ce contexte, la variabilité et la faible fiabilité des composants du processeur sont des problèmes importants. Ces processeurs sont basés sur un réseau sur puce en grille 2D munis d'un algorithme de routage tolérant aux fautes tel que proposé dans la Section II.1, dont chaque nœud contient un ou plusieurs cœurs de calcul. La fréquence de chaque nœud est ajustée indépendamment, en fonction des besoins en puissance de calcul et des conditions de variabilité.

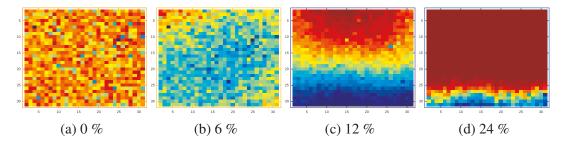

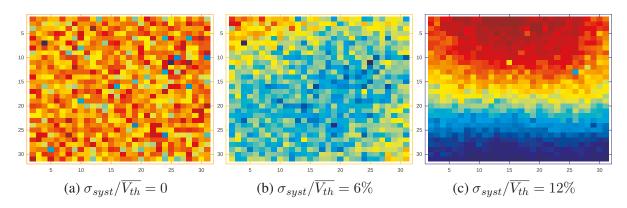

Dans les technologies décananométriques, il existe des variations importantes dans la tension de seuil des transistors, ce qui affecte à la fois la consommation et la performance des circuits. On peut distinguer les **variations aléatoires** et les **variations systématiques**, mais il est actuellement impossible de prévoir quelle sera leur amplitude respective, et surtout leur impact réel sur les circuits créés. On peut par contre envisager plusieurs scénarios, comme dans la Figure 2.

De plus, les fautes permanentes et transitoires menaceront l'exécution des applications, à cause de

<sup>&</sup>lt;sup>4</sup>Virtual Channels

FIGURE 2 – Fréquence maximale des nœuds de calcul dans un processeur soumis à différents niveaux de variabilité systématique

la forte variabilité des procédés d'une part, et d'une sensibilité accrue à la température et aux rayons cosmiques d'autre part. Par conséquent, les puces devront intégrer des circuits de test en ligne (BIST<sup>5</sup>) pour détecter l'occurence de ces fautes. Par souci de simplicité, nous considèrerons ici que lorsqu'un cœur, un routeur ou un lien devient défaillant, il cesse immédiatement d'interférer avec les autres composants (*fail-silent assumption*).

Comme proposé dans [4], les processeurs considérés intègrent une technique de saut de tension à grain fin  $(V_{dd}$ -hopping) au niveau des nœuds. Ainsi, le voltage (et donc la fréquence maximale) de chaque nœud est fixé soit à une valeur haute, soit à une valeur basse si les besoins de calcul sont plus faibles. Les nœuds inutilisés sont eux totalement désactivés (power-gating). Un contrôleur de nœud ajuste la fréquence en fonction des caractéristiques du nœud telles que la tension, la variabilité ou la température, afin d'éviter l'apparition de fautes temporelles.

#### I.2 Motivations

Dans le cadre de cette thèse, nous considérons des processeurs composés de milliers de cœurs réalisés avec un procédé décananométrique. Une telle puce incluerait de nombreux circuits (e.g. cœurs, routeurs, liens) défectueux ou dont les caractéristiques seraient éloignées des spécifications nominales. Malgré tout, la redondance massive en cœurs de calcul offrirait une puissance de calcul exceptionnelle, en exploitant en priorité les cœurs sains les plus performants. En particulier, une adaptation dynamique et locale de la fréquence et de la tension d'alimentation DVFS<sup>6</sup> permettrait d'exploiter pleinement le potentiel de chaque cœur *via* la méthodologie GALS<sup>7</sup>.

Dans ce mémoire, trois contributions sont présentées pour l'utilisation de processeurs multicoeurs massivement parallèles mais peu fiables et sujets à une variabilité importante. Premièrement, plusieurs algorithmes de routage tolérant aux fautes pour les réseaux sur puce en grille 2D sont proposés. Deuxièmement, nous décrivons une technique de gestion d'applications parallèles, tolérante aux variations et aux défaillances des cœurs de calcul. Troisièmement, le modèle de simulation VOCIS<sup>8</sup>, développé durant cette thèse, est présenté avec une attention particulière sur les fonctionnalités qui font son originalité.

Notre approche nécessite tout d'abord de fournir au logiciel exécuté les moyens de fonctionner efficacement, en présence de défaillances multiples et de forte variabilité. En premier lieu, il est essentiel d'offrir aux cœurs embarqués un *média* de communication suffisamment fiable pour supporter l'exécution des applications cibles. Les réseaux sur puces de topologie régulière, dont la plus commune est la **grille 2D**, offrent naturellement la redondance et la simplicité nécessaires pour la tolérance aux

<sup>&</sup>lt;sup>5</sup>Built-In Self-Test

<sup>&</sup>lt;sup>6</sup>Dynamic Voltage Frequency Scaling

<sup>&</sup>lt;sup>7</sup>Globally Asynchronous Locally Synchronous

<sup>&</sup>lt;sup>8</sup>Versatile On-Chip Interconnect Simulation model

fautes des communications inter-coeurs. Dans cette thèse, plusieurs algorithmes de routage tolérant la défaillance d'une partie du NoC sont présentés, pour la topologie grille 2D. Tous garantissent l'absence d'interblocage, mais leur complexité respective leur permet de tolérer plus ou moins de défaillances de routeur et de lien. En particulier, la plus avancée est capable de transmettre les messages tant qu'il existe un chemin valide. Par la suite, diverses techniques sont proposées pour améliorer la performance du NoC en présence de défaillances, ce qui est rarement traité dans la littérature.

En se basant sur un réseau d'interconnection tolérant aux fautes, nous proposons ensuite une méthode de gestion des applications parallèles qui permet de les exécuter efficacement, malgré la défaillance et la forte variabilité de certains cœurs. Cette méthode s'appuie sur la décomposition des applications en tâches hiérarchiques suivant un graphe acyclique dirigé ou DAG<sup>9</sup>. La tolérance aux fautes est garantie par l'utilisation de messages de contrôle IAM<sup>10</sup> et la réallocation des tâches lorsque la défaillance d'un cœur exécutant est détectée. Dans un deuxième temps, le mécanisme de réallocation de tâches est adapté pour prendre en compte la variabilité et la charge des cœurs, ainsi que l'énergie dissipée dans le réseau d'interconnection, afin d'améliorer la consommation énergétique de l'application.

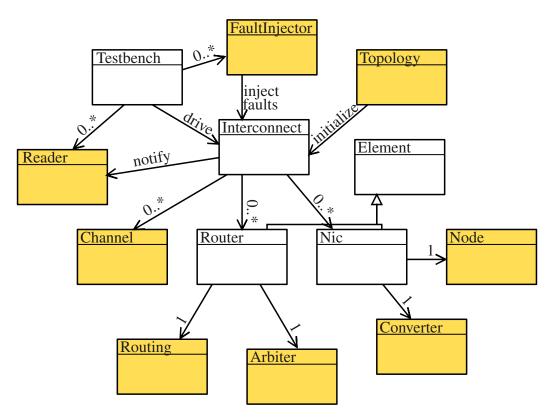

Afin de supporter les travaux de cette thèse, un modèle de simulation de réseau sur puces nommé VOCIS a aussi été developpé. Ce modèle C++/SystemC met l'accent sur la généricité et la réalisation de simulations de tolérance aux fautes. Ce modèle permet l'implémentation générique de nombreux aspects du réseau, et en particulier de tout agorithme de routage tolérant aux fautes. De plus, des outils d'analyse avancés et une interface 3D permettent de visualiser l'effet des différents composants, tout spécialement en présence de fautes multiples.

#### **II** Contributions

## II.1 Réseaux sur puces tolérants aux fautes et performants

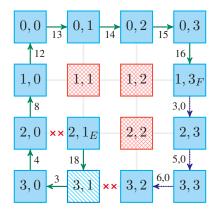

#### Architecture du routeur proposé

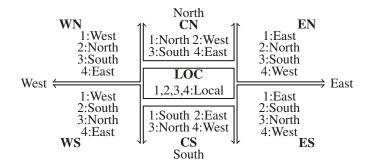

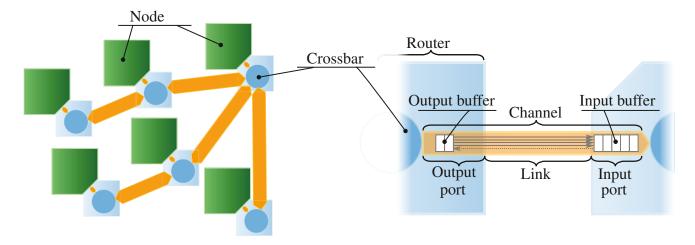

Dans les réseaux sur puces réguliers, tels que les grilles 2D, il est possible de router les messages uniquement avec la connaissance du nœud de destination. Les algorithmes de routage proposés utilisent une liste des ports de sortie disponibles, hiérarchisés en fonction de la destination du paquet. D'autre part, l'absence d'interblocages est obtenue, comme souvent, en restreignant les possibilités de routage. Ces restrictions sont néanmoins néfastes pour la tolérance aux fautes, en ce qu'elles empêchent l'utilisation de certaines routes. Notre solution consiste donc, dans un premier temps, à diviser les ressources matérielles en 2 réseaux virtuels ou VN<sup>11</sup>, avec des restrictions de routage différentes et complémentaires. En choisissant le réseau virtuel adéquat, il est ainsi possible de minimiser l'impact des restrictions sur la tolérance aux fautes.

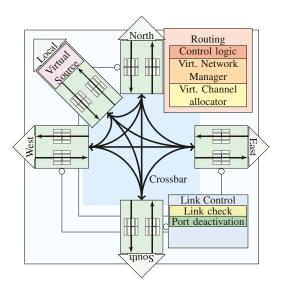

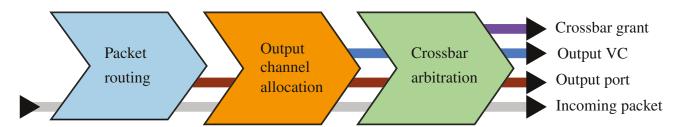

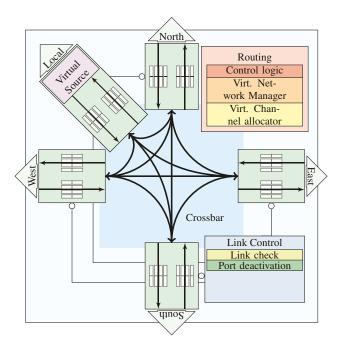

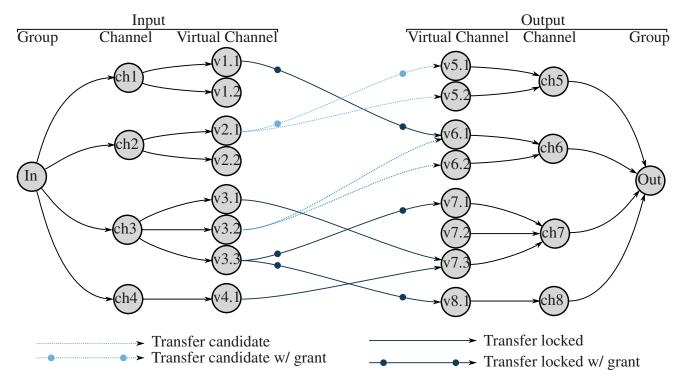

Chaque port du routeur est partagé entre plusieurs canaux virtuels ou VCs. Pour chaque VC et chaque port, les messages sont accumulés dans un mémoire FIFO<sup>12</sup>, comme illustré par la Figure 3, et le lien est multiplexé entre les différents VCs. Finalement, un allocateur de VCs contrôle leur utilisation. Pour nos algorithmes de routage, des **réseaux virtuels** ou VNs sont définis comme des groupes exclusifs de VCs à l'intérieur desquels les messages sont transmis. Dans cette thèse, nous utiliserons 4 canaux virtuels par port, 2 pour chaque réseau virtuel. Quand c'est nécessaire, une source virtuelle ou VS<sup>13</sup>,

<sup>&</sup>lt;sup>9</sup>Directed Acyclic Graph

<sup>&</sup>lt;sup>10</sup>I am Alive Message

<sup>&</sup>lt;sup>11</sup>Virtual Network

<sup>&</sup>lt;sup>12</sup>First-In First-Out

<sup>&</sup>lt;sup>13</sup>Virtual Source

FIGURE 3 – Détails de l'architecture du routeur proposé

introduite dans la Section II.1, permet l'échange de messages entre les VNs, sans permettre l'apparition d'interblocages.

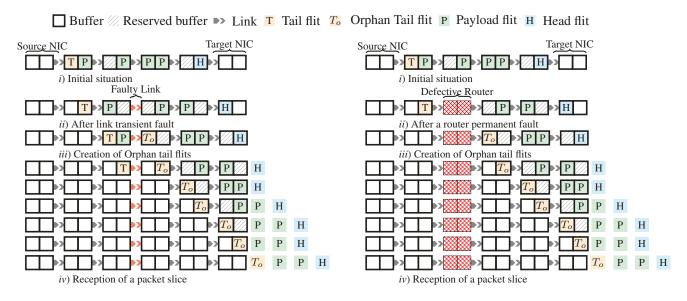

De plus, le routeur embarque un circuit de contrôle des liens, qui gère l'apparition des fautes transitoires et permanentes. En fonction de la technologie et de l'implémentation, la détection des fautes à été traitée par de nombreuses solutions, et ce travail ne prétend pas y innover. Nous considérerons donc un schéma de haut niveau compatible avec la majorité des solutions de la littérature. Un module de détection diagnostique l'état du lien en échangeant périodiquement des flits de contrôle IAM avec les nœuds voisins, et en appliquant un code correcteur sur chaque flit échangé. Lorsqu'une faute permanente est détectée, le module de désactivation inhibe tout trafic dans le port, à l'exception des flits de contrôle.

#### Variante A : hiérarchie des ports de sortie et réseaux virtuels

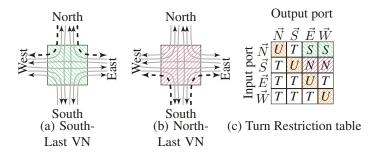

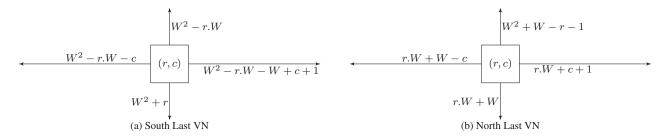

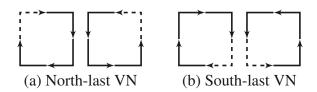

Parmi les algorithmes de routage que nous proposons, la variante A est le plus simple. Elle est basée d'une part sur une hiérachie des ports de sortie, et d'autre part sur deux réseaux virtuels nommés *North-Last* et *South-Last*, qui assurent l'absence d'interblocages.

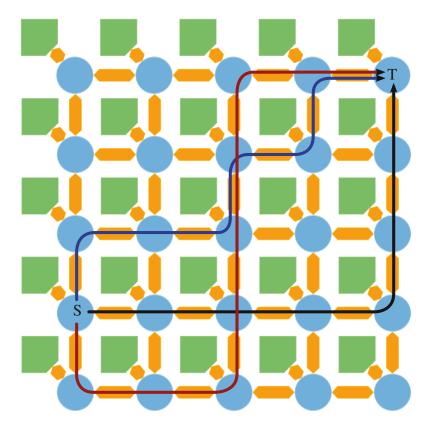

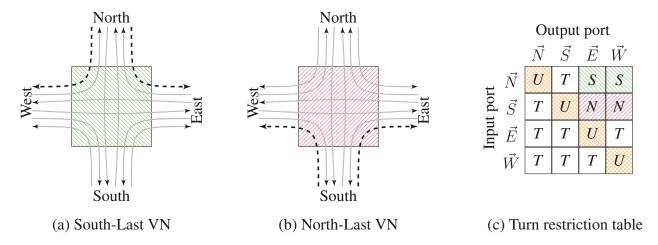

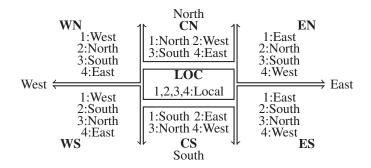

Dans la hiérarchie des ports de sortie présentée à la Figure 4, les directions sont ordonnées selon la relation entre le nœud destination du paquet et la position du routeur. L'algorithme de routage sélectionne le port disponible dont la direction est la plus haute dans la hiérarchie. En partant de la direction la plus haute, le routeur parcourt alors les directions par ordre décroissant de hiérarchie. Pour chaque direction, le routeur vérifie que le port existe et qu'il n'est pas défaillant. En présence de défaillances, il peut arriver qu'aucune direction ne soit disponible pour transmettre le paquet. Dans le cas de la Variante A, le paquet est alors évacué, et un acquittement négatif Nack<sup>14</sup> est renvoyé au nœud source.

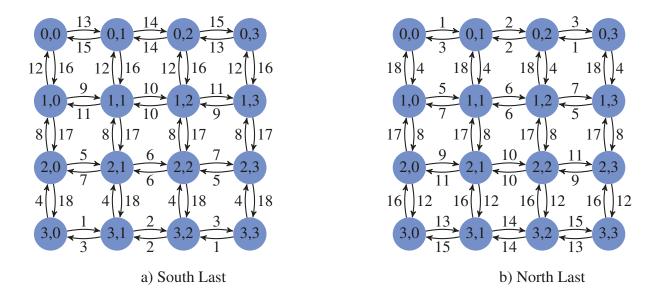

L'absence d'interblocages est basée sur la restriction du routage dans chaque réseau virtuel. Ainsi, les ports de sorties interdits par le réseau virtuel *South-Last* (respectivement *North-Last*) sont tracés en pointillés dans la Figure 5-a (respectivement la Figure 5-b). Cette approche a été prouvée par la numérotation des liens dans un premier temps [5], néanmoins l'approche pratique proposée dans [6] consiste à utiliser une table de restrictions de direction. En effet, il suffit de parcourir une table 4x4 pour savoir si un réseau virtuel interdit une direction de sortie, comme le montre la Figure 5-c. Les

<sup>&</sup>lt;sup>14</sup>Negative Acknowledgement

FIGURE 4 – Hiérarchie des ports de sortie

FIGURE 5 – Ports de sorties interdits par les réseaux virtuels South Last (a) et North Last (b)

demi-tours (marqués U) sont interdits dans les deux VNs. Les restrictions propres à *North Last* (respectivement *South Last*) sont notées N (respectivement S). Les autres transferts, dont ceux à destination ou provenant du port local, sont autorisés (T).

#### Variante B: Insertion des sources virtuelles

Dans la Variante B, afin de réduire le nombre de messages perdus, une **source virtuelle** ou VS est ajoutée à chaque routeur, pour échanger des messages entre les deux réseaux virtuels. En effet, lorsque le NoC présente des fautes de liens et/ou de routeur, le chemin emprunté par les messages peut devenir long et complexe. Lorsqu'un message ne peut être routé sans violer les restrictions, l'utilisation de la source virtuelle lui permet de continuer vers sa destination. Malheureusement, cela impose l'ajout du marquage des routeurs ou RS<sup>15</sup> afin d'éviter que des messages restent indéfiniment dans le réseau.

Les sources virtuelles sont utilisées pour échanger fiablement des messages entre deux réseaux virtuels, ou simplement supprimer le risque d'interblocage dans un même VN. Chaque routeur dispose d'un tampon spécifique appelé tampon VS, où les messages sont stockés intégralement avant d'être reinjectés dans le réseau, ce qui supprime toute dépendance de tampon.

Le marquage des routeurs consiste à stocker dans le message la liste des routeurs traversés, et à les éviter lors des étapes suivantes de routage. Pratiquement, il suffit de sauver la direction de chaque lien emprunté (2 à 3 bits dans une grille 2D), ce qui limite beaucoup l'impact du marquage sur la performance du réseau. Enfin, on peut noter qu'au niveau du nœud destination, le message contient la route utilisée, ce qui sera exploité pour améliorer la performance du réseau dans la Section II.1.

<sup>&</sup>lt;sup>15</sup>Router Stamping

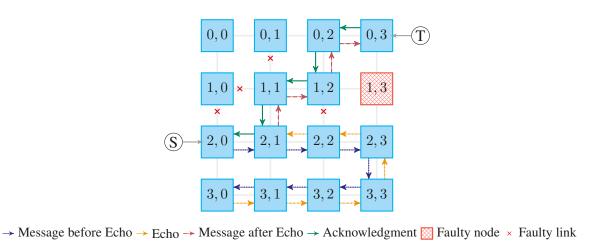

#### Variante C : Addition du mode écho

Bien que la variante B aie le potentiel d'atteindre n'importe quelle destination, elle ne permet pas d'obtenir un taux nul de messages perdus. En effet, il arrive que des messages soient bloqués dans une impasse avec la Variante B, car les routeurs ont seulement une connaissance partielle du réseau. Dans ce cas, la Variante C utilise une source virtuelle pour supprimer les dépendances de tampon, et le message est ensuite routé en mode écho. Dans ce mode, le message retourne successivement dans les nœuds déjà visités, jusqu'à ce qu'une route alternative soit trouvée. Cet algorithme nous permet de répondre aux conditions les plus exigeantes, sans recourir à une table de routage. Par exemple, il est capable de gérer les cas où le réseau est presque partitionné.

#### **Routes explicites**

Dans de nombreuses applications (e.g. applications de flux vidéo/audio), plusieurs messages sont échangés entre un même couple de nœuds source-destination. Nous avons donc introduit les routes explicites (*Explicit Path*) dans [6] pour réduire la latence moyenne des variantes B et C. Cette technique est particulièrement utile pour la variante C, lorsque de nombreux défauts entraînent l'utilisation fréquente du mode écho.

Les routes explicites sont créées dynamiquement lorsque le premier message est reçu par le nœud destination. En effet, le marquage des routeurs (RS) permet au nœud destination de reconstituer la route empruntée par le message. Dans le cas de la Variante C, les liens qui ont été re-traversés en mode écho ne sont pas inclus dans la route. La route est ensuite retournée au nœud source, qui la stocke. Lorsque de nouveaux messages doivent être envoyés à la même destination, ils sont routés en mode explicite, et suivent précisément la route mémorisée.

#### Résultats expérimentaux

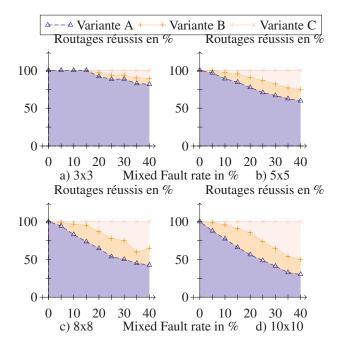

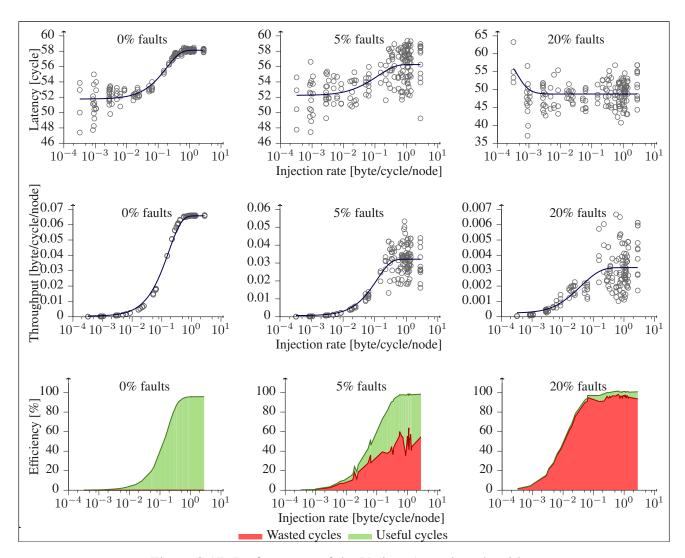

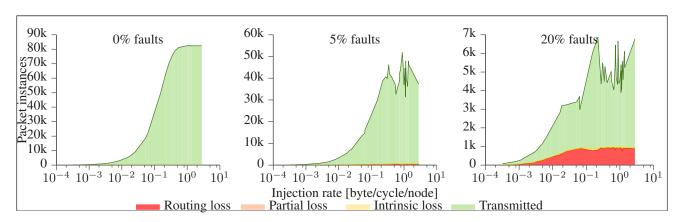

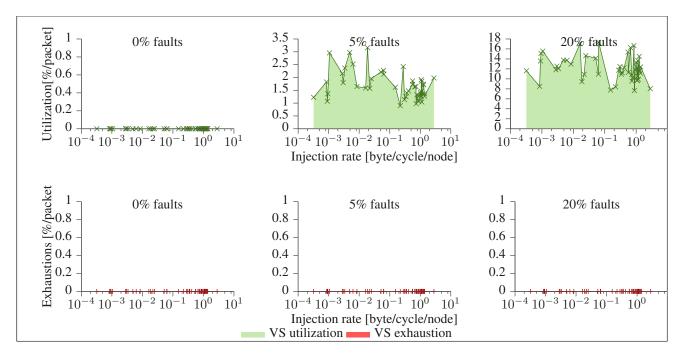

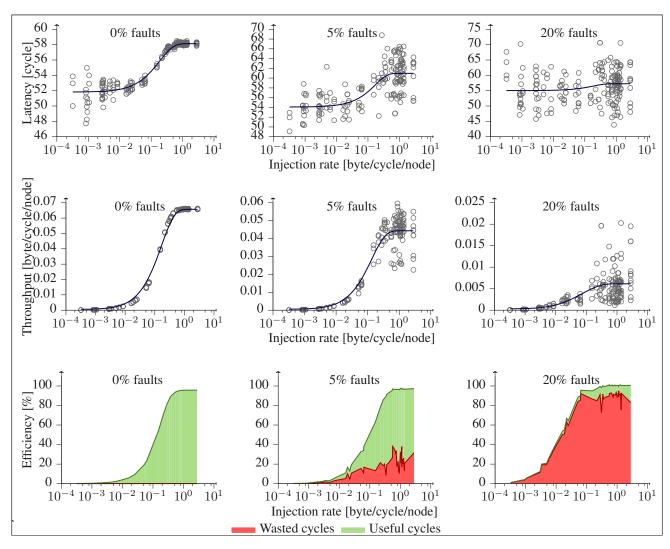

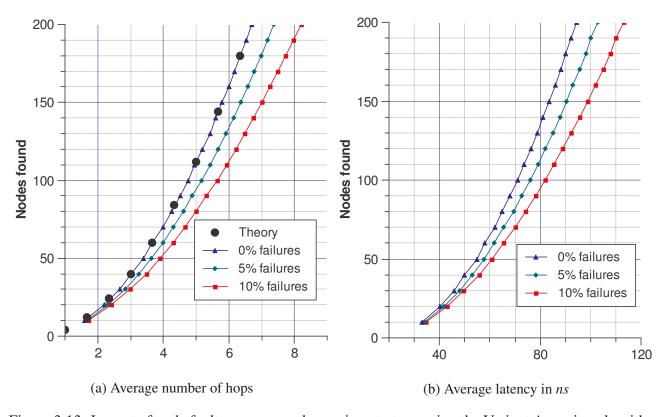

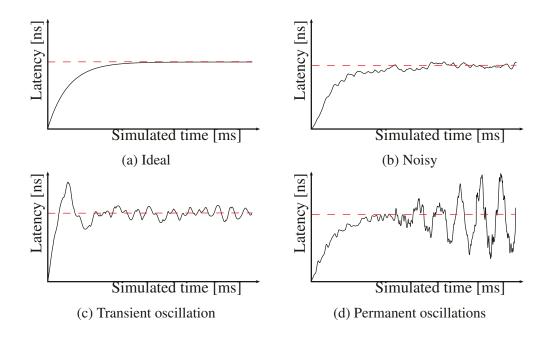

#### Tolérance aux fautes

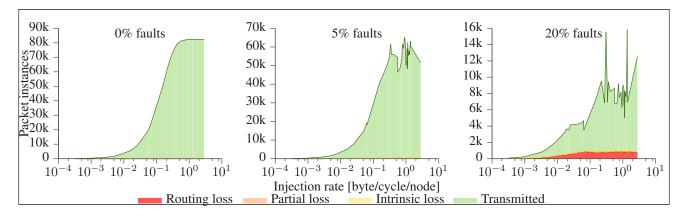

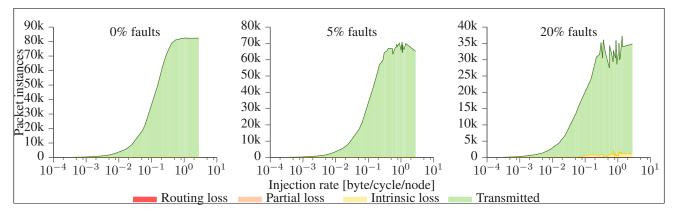

Dans les Figures 6-a,b,c,d, nous montrons le pourcentage de messages perdus pour différentes tailles de réseaux, en utilisant les algorithmes A, B et C. Nous injectons des fautes permanentes de liens et de routeurs. Les résultats montrent que la variante A est suffisament tolérante aux fautes quand le taux de défaillances reste inférieur à 10 %. Lorsque les défauts sont plus nombreux, la tolérance aux fautes peut être améliorée en utilisant la Variante B. Néanmoins, certains messages peuvent être perdus avec cet algorithme, en particulier pour les réseaux les plus larges (i.e. 10x10). Dans cette éventualité, la variante C ne perd aucun message dans les réseaux non partitionnés, même pour un taux extrême de 40 % de défaillances. Il est également important de noter que les algorithmes proposés n'utilisent pas de table de routage et garantissent l'absence d'interblocages.

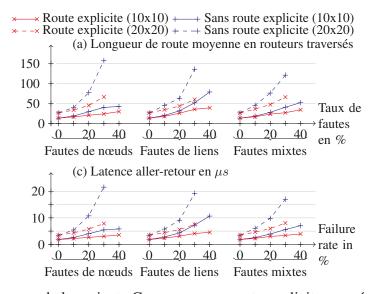

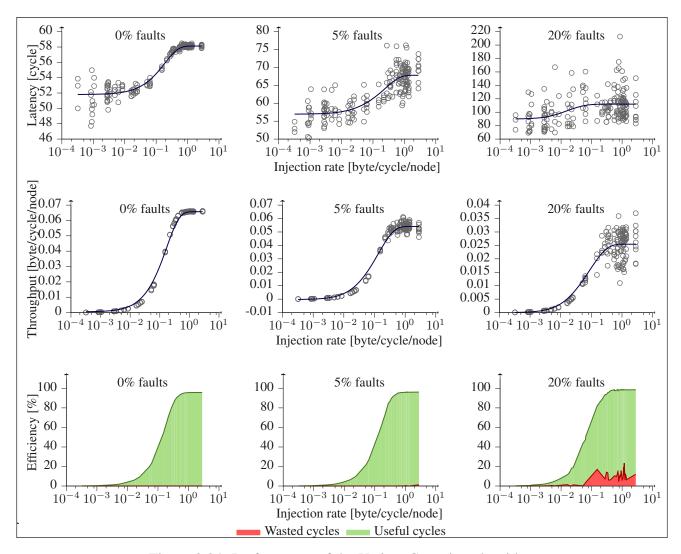

#### **Performance**

Nous avons également simulé l'utilisation de la variante C avec ou sans routes explicites pour deux tailles de réseau (10x10 et 20x20). Pour chaque configuration, nous avons simulé le transfert de 100 messages pour 50 ensembles de fautes différents. Les fautes sont injectées avant le début de la simulation et ne partitionnent pas le réseau. Nous avons considéré des ensembles de fautes de **nœud**, de **lien** ou **mixtes** (i.e. les fautes de lien et de nœud sont équiprobables).

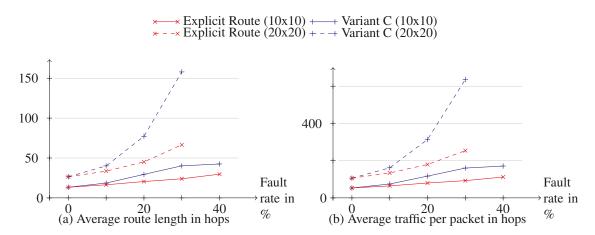

Pour les faibles taux de défaillance, les routes explicites ont peu d'impact sur la longueur de route moyenne (Figure 7-a). Par contre, il y a une amélioration flagrante pour les taux de défaillance à partir

FIGURE 6 – Pourcentage de messages transmis avec les algorithmes de routage A, B et C

de 20%. Finalement, Figure 7-b montre que les routes explicites réduisent la latence de la variante C, particulièrement pour la grille  $20 \times 20$ .

FIGURE 7 – Performance de la variante C avec ou sans route explicite en présence de défaillances

Les figures montrent que la latence moyenne tend à augmenter avec la taille du réseau et le taux de défaillance. Pour les applications de flux, qui transfèrent des messages volumineux entre quelques paires de nœuds, les routes explicites limitent l'augmentation du trafic en présence de défauts. Par conséquent, la latence moyenne serait améliorée significativement par l'emploi de routes explicites, tout en conservant l'absence d'interblocages.

# II.2 Des applications efficaces, tolérantes aux fautes et à la variabilité

La seconde contribution de cette thèse est un ensemble de techniques qui rendent les applications tolérantes aux fautes, tout en prenant en compte la variabilité présente dans les processeurs massivement

FIGURE 8 – Exemple d'application maître-esclave

multicoeurs. Notre approche permet de réduire la consommation des applications, et d'envisager l'intégration d'autres sources d'hétérogénéité.

#### Modèles de programmation tolérants aux fautes

La création d'applications parallèles tolérantes aux fautes nécessite généralement le respect de diverses règles de programmation. Dans notre cas, la technique proposée requiert l'utilisation d'un modèle de programmation de type maître-esclave.

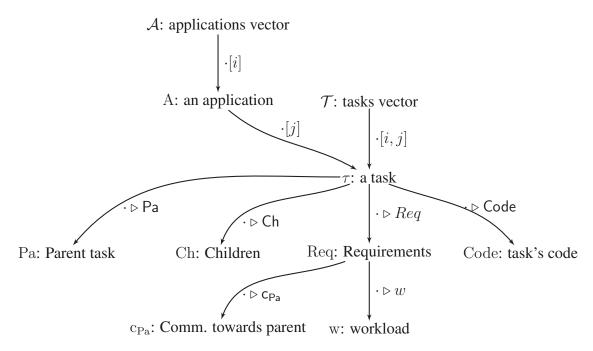

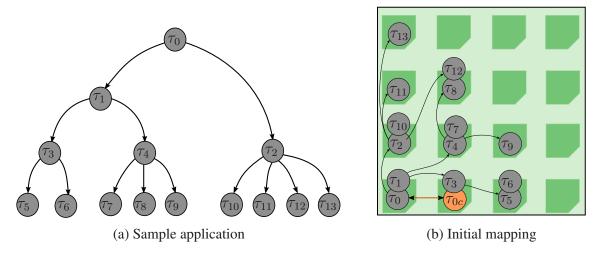

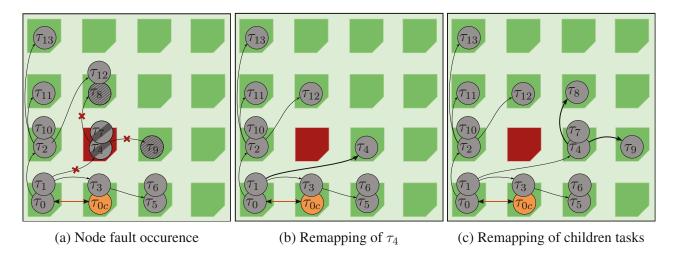

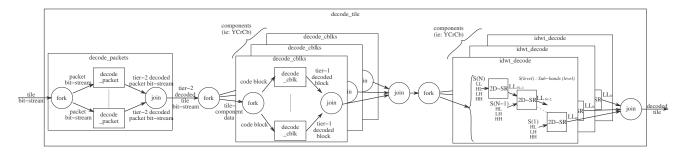

Dans la suite, nous considèrerons une classe d'applications décrites par un graphe dirigé acyclique ou DAG<sup>16</sup>, qui respecte le formalisme maître-esclave [7]. Les sommets du graphe représentent les tâches et les arêtes, les communications entre ces tâches. Ce formalisme est l'un des plus simples et des plus usités pour paralléliser une application en pratique. En outre, il permet de faire apparaître une hiérarchie entre les tâches, ce qui sera nécessaire pour l'approche tolérante aux fautes présentée par la suite. Généralement, une tâche maître sous-traite son travail à plusieurs tâches esclaves, puis assemble les résultats partiels. Le flot d'éxecution est inconnu *a priori* et chaque tâche peut créer de nouvelles tâches esclaves dynamiquement lors de l'exécution. Il est par contre nécessaire de connaître à l'avance une estimation du nombre d'opérations et du trafic généré pour chaque tâche. Dans ce travail, les applications sont périodiques et soumises à des contraintes temps-réel relachées (*soft real-time*), en prenant pour exemple les applications multimédia telles que le codage audio/vidéo ou le traitement d'images.

<sup>&</sup>lt;sup>16</sup>Directed Acyclic Graph

#### Récupération automatique en présence de fautes multiples

#### Protocole de détection et de récupération

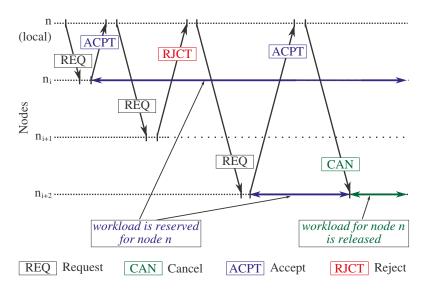

La détection des défaillances est basée sur l'hypothèse que les cœurs arrêtent toute communication lorsqu'ils deviennent défaillants. Chaque tâche envoie périodiquement un message de contrôle nommé IAM<sup>17</sup> à son maître. Si aucun message d'une tâche fille n'a été recu pour une période prédéfinie, elle est considérée comme défaillante, et la tâche maître réaffecte cette tâche sur un autre nœud. Lorsqu'une tâche défaillante possédait elle-même des tâches filles, elles sont également perdues, et devront donc être réaffectées.

En se basant sur le modèle de programmation proposé dans la Section II.2, la technique proposée offre donc un mécanisme simple et localisé permettant de reprendre l'exécution d'une application en présence d'une ou plusieurs défaillances de nœuds.

Le cas particulier d'une défaillance du nœud exécutant la tâche racine (*root*) est traité par la création d'une tâche clone sur un nœud différent. Avec cette technique, la tâche clone ne démarre que lorsque la tâche originale est frappée par un défaut de nœud. Elle crée alors sa propre tâche clone, et reprend l'éxecution de l'application après en avoir re-alloué les tâches.

#### Affectation dynamique des tâches tolérante aux fautes

Lorsqu'une tâche esclave doit être (re-)affectée, le nœud exécutant la tâche maître lance une procédure de recherche de nœud. Il s'agit de trouver un nœud capable d'exécuter la tâche esclave, et si possible en réduisant l'énergie consommée (c.f. Section II.2). Chaque nœud étant capable d'exécuter plusieurs tâches, la recherche commence par interroger le nœud maître afin d'affecter localement la tâche fille.

En se basant sur la littérature, nous utilisons la stratégie du voisin le plus proche (*Nearest Neighbor*) pour rechercher un nœud exécutant. A l'aide de messages spécifiques, chaque nœud est interrogé sur sa capacité à exécuter la tâche fille, en partant du plus proche au plus éloigné, en évitant les nœuds défaillants ou déjà très chargés.

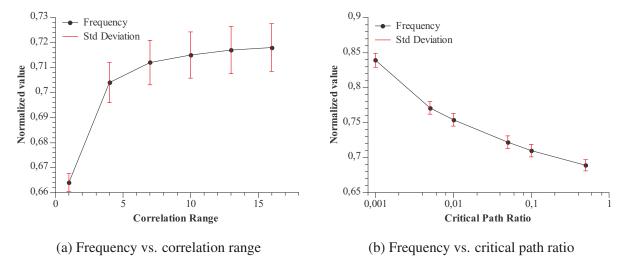

#### Prise en compte de la variabilité du processeur

#### Sélection du nœud racine

Le choix du nœud exécutant la tâche racine d'une application (i.e. nœud racine) a un impact de premier ordre sur la performance de l'application. Dans [8], nous proposons deux stratégies simples. Lorsque la variabilité systématique est faible, choisir un nœud central permet de maximiser le nombre de nœuds voisins lors de l'expansion de l'application. En revanche, si la variabilité systématique est assez forte pour faire apparaître des "régions" de nœuds plus performants comme dans Figure 2-b,c, il est préférable de choisir un nœud à l'intérieur de telles régions.

#### Recherche adaptative de nœud

L'utilisation déterministe de l'algorithme de recherche de nœud aboutit à une consommation énergétique assez importante lorsque la variabilité est importante. Nous proposons donc de prendre en compte l'état du processeur lors de la recherche, afin de réduire la consommation énergétique des applications.

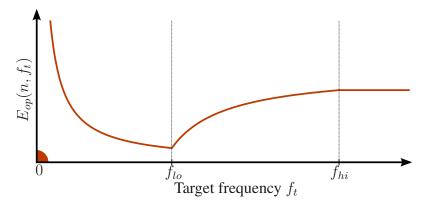

Un critère de recherche prenant en compte la variabilité des cœurs est donc proposé, et met en balance l'efficacité des cœurs avec leur distance vis-à-vis du nœud exécutant la tâche maître. Nous proposons également un critère d'arrêt statistique qui permet de terminer la recherche lorsqu'il devient peu probable de trouver un nœud plus éloigné qui réduise encore le critère de recherche.

<sup>&</sup>lt;sup>17</sup>I am Alive Message

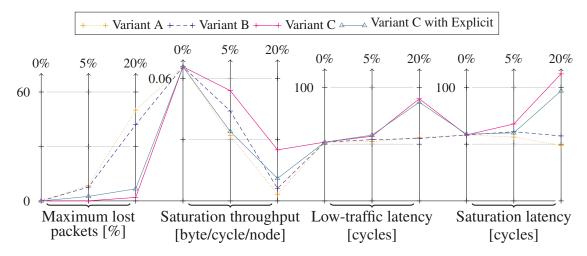

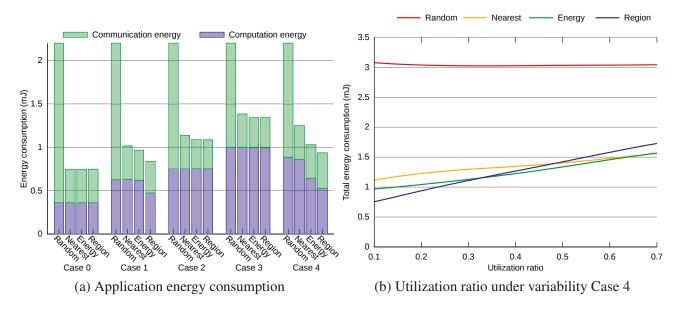

#### Résultats expérimentaux

Dans ces expérimentations, on néglige l'impact de la variabilité sur le NoC<sup>18</sup>. De plus, nous supposons que peu de contentions surviennent dans les routeurs, et donc que la latence et l'énergie consommée pour la transmission d'un message sont proportionnelles au nombre de routeurs traversés.

La technique proposée a été simulée sur un modèle spécifique de haut niveau, où l'utilisation d'un routage tolérant aux fautes (variante A présentée dans la Section II.1) est émulée. Lors des simulations, une application de 100 à 700 tâches est déployée sur un processeur de 1024 cœurs. L'application est générée aléatoirement, graphe et caractéristiques des tâches compris, avec un ratio calcul sur communication proche de 1.

Trois scénarios de variabilité sont utilisés, afin de refléter les différentes évolutions possibles de l'industrie CMOS. Le scénario 1 correspond à une stagnation des variations systématiques et aléatoires à 6% de la valeur moyenne. En tablant sur une augmentation de la variabilité aléatoire à 24% et une annulation de la variation systématique, on obtient le scénario 2. Dans le pire des cas, le scénario 3 donnerait une variabilité aléatoire aussi élevée, avec une variabilité systématique de 12%. Lorsqu'elles sont présentes, les fautes de nœud sont injectées avant le début de la simulation.

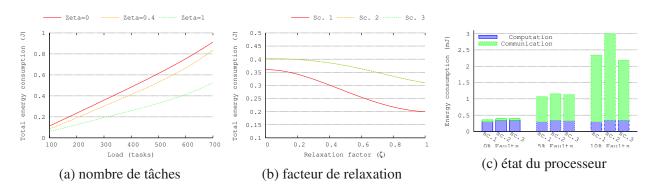

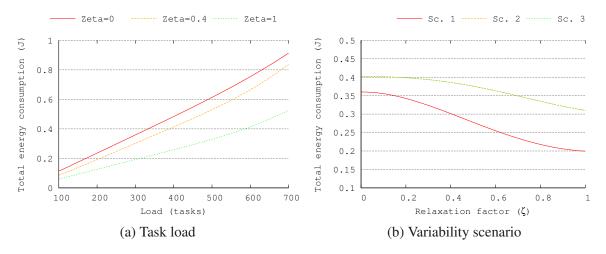

Dans la Figure 9a, la consommation totale de l'application est donnée pour différents nombres de tâches et différents facteurs de relaxation, pour le scénario 2 et en absence de fautes. Le facteur de relaxation  $\zeta$  (Zeta) modifie le critère d'arrêt de la recherche de nœuds, et offre ainsi un compromis entre l'efficacité énergétique de l'application et le coût de la recherche de nœuds en terme de communications. L'énergie consommée est réduite significativement par l'utilisation du critère adaptatif ( $\zeta=0.4,1$ ) par rapport à une recherche de plus proche voisin déterministe ( $\zeta=0$ ).

FIGURE 9 – Consommation de l'application pour différentes configurations

La Figure 9b montre la relation entre consommation énergétique, variabilité et facteur de relaxation. Globalement, lorsque la variabilité et le taux de défaillance augmentent, le facteur de relaxation joue un rôle de plus en plus important. En effet, lorsque les disparités augmentent, il devient profitable de visiter des nœuds de plus en plus éloignés.

Finalement, dans la Figure 9c, l'énergie applicative détaillée est donnée, sous différents scénarios de variabilité et de fautes. La consommation globale augmente avec les fautes et la variabilité, mais notre stratégie de recherche limite cette dégradation, en prenant en compte l'energie utilisée pour les communications, et celle utilisée pour les calculs.

Cette contribution permet donc d'exécuter des applications parallèles sur des processeurs composés de centaines de cœurs peu fiables et sujets à une forte variabilité. Elle déploie les applications dynamiquement, entièrement lors de son démarrage, puis partiellement après qu'une défaillance de nœud

<sup>&</sup>lt;sup>18</sup>Network on Chip

soit survenue. De plus, cette approche généraliste permet de réduire la consommation énergétique en prenant en compte la variabilité des cœurs du processeur.

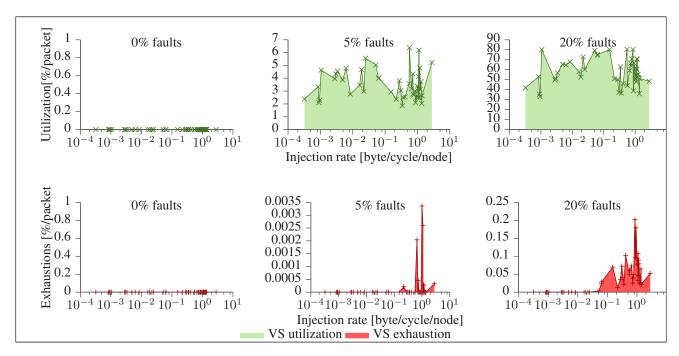

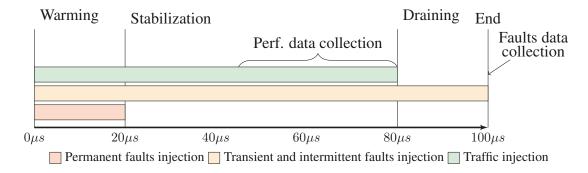

## II.3 VOCIS : un modèle générique de réseaux sur puce tolérants aux fautes

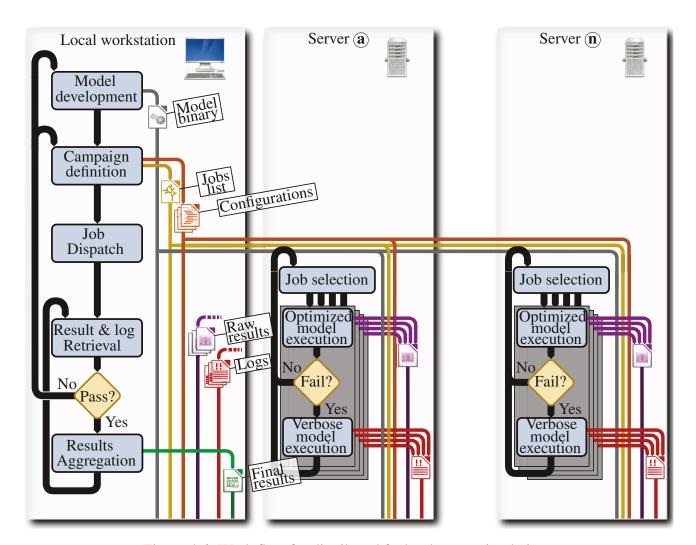

Durant cette thèse, nous avons mis au point un modèle de simulation appelé VOCIS<sup>19</sup>. Ce logiciel avait plusieurs objectifs. Tout d'abord, il s'agissait de proposer un modèle capable de supporter la plupart des topologies et des algorithmes de routage proposés dans la littérature. Ensuite, les travaux présentés dans la Section II.1 exigeaient un simulateur capable d'injecter génériquement des fautes de routeur et de lien. Enfin, il nous fallait des moyens avancés d'analyse pour comprendre et quantifier les résultats de simulations complexes, mêlant trafic important et fautes multiples.

#### Un modèle généraliste

De nombreux travaux sur les réseaux sur puce ou NoCs<sup>20</sup> s'appuient sur des simulateurs, soit développés en interne, soit modifiés *ad hoc*, pour obtenir les résultats expérimentaux nécessaires. Il est donc très difficile de comparer quantitativement les contributions. VOCIS offre un environnement unique pour simuler des propositions hétérogènes, et des fonctionnalités de base réduisant le temps de développement nécessaire à l'ajout d'une nouvelle technique.

#### **Topologies et ports**

VOCIS supporte virtuellement toutes les topologies, en les représentant par un graphe orienté dont chaque sommet correspond à un routeur ou une interface réseau. En particulier, cela inclut les réseaux assymétriques dont certains nœuds ne peuvent pas communiquer dans les deux sens.

VOCIS est également compatible avec une grande variété de ports et de liens. En effet, le modèle permet d'intégrer tout modèle de port implémentant une interface générique. Dans ce modèle, le port de sortie, le lien et le port d'entrée correspondants sont regroupés, afin de simplifier l'implémentation de divers ports et liens.

#### Algorithmes de routage et d'arbitrage

Pour les réseaux sur puce, les contraintes de complexité ont longtemps limité fortement la diversité des algorithmes employés. Néanmoins, il est admis que les futures technologies auront une plus grande capacité d'intégration, et que les problèmes de performance et de tolérance aux fautes pourront justifier l'emploi de solutions plus complexes. En particulier, les algorithmes supportant l'envoi multiple (multicast) ou le routage adaptatif -qui dépend de l'état du réseau- apparaîssent rapidement. On pourra également remettre en question l'utilisation d'algorithmes de routage sans interblocages, et les comparer à des algorithmes avec interblocages combinés à une technique de suppression d'interblocage. En utilisant un mécanisme générique pour l'arbitrage du *crossbar* des routeurs, VOCIS permet de simuler ces solutions sans modification de son noyau.

L'utilisation d'un graphe à la fois pour la topologie et l'arbitrage des routeurs permet d'implémenter diverses fonctionnalités avancées de manière générique, telle que la découverte de meilleurs chemins ou la détection d'interblocages, ce qui facilite la comparaison de solutions exploitant des topologies différentes.

<sup>&</sup>lt;sup>19</sup>Versatile On-Chip Interconnect Simulation model

<sup>&</sup>lt;sup>20</sup>Network on Chips

#### **Trafics**

Lors de simulations de tolérance aux fautes et de performance d'un réseau, le trafic utilisé détermine pour beaucoup les observations obtenues. Il est donc essentiel de soumettre les différentes solutions comparées à un même trafic de paquets. Dans VOCIS, chaque interface réseau (NIC<sup>21</sup>) ou nœud de calcul peut être adapté aux besoins de la simulation, pour modéliser un trafic applicatif ou synthétique et une gestion appropriée des requêtes.

#### Prise en compte des fautes

La simulation d'un NoC en présence de fautes nécessite plusieurs éléments. EN premier lieu, il faut sélectionner un modèle de fautes approprié et de préférence peu coûteux en puissance de calcul. Deuxièmement, l'injection des fautes doit être suffisamment générique pour faire apparaître la vaste diversité des cas de défaillance. En second lieu, il est essentiel que l'injection de fautes soit reproductible, afin de répéter le même scénario avec une solution alternative, ou simplement rejouer la même séquence lorsqu'elle mène à un résultat inattendu. En dernier lieu, plus que dans les simulations de performance pure, la simulation de fautes exige des moyens d'analyse complexes pour comprendre les effets obtenus.

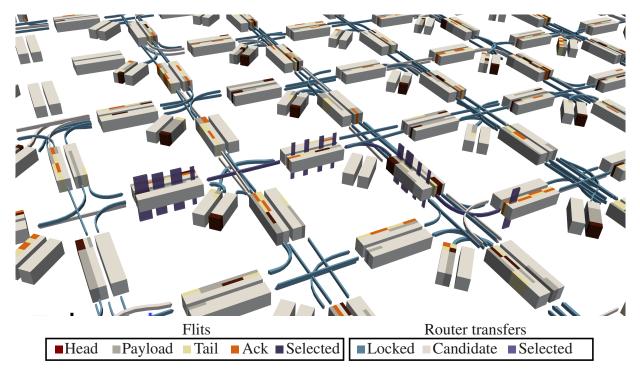

#### Analyse et visualisation graphique

VOCIS a pour objectif la simulation de grands réseaux sur puce (e.g. 10x10) soumis à une variété de fautes (fautes transitoires et/ou permanentes) et à un trafic lourd et hétérogène. On peut également ajouter la complexité des algorithmes pour le routage, l'arbitrage des routeurs et la gestion des transactions. La compréhension et l'obtention de résultats numériques significatifs demandent donc l'utilisation d'outils avancés.

Premièrement, un mécanisme de traçage (*log*) évolué permet de sélectionner les messages à afficher en fonction du module émetteur et de sa gravité.

Ensuite, divers outils statistiques telle que la moyenne glissante ou la régression multilinéaire permettent de traiter des données de sortie fluctuantes. L'automatisation du traitement des données de sortie permet également de générer l'ensemble des graphiques nécessaires rapidement.

Enfin, l'ajout d'une interface graphique en 3D permet de visualiser dynamiquement le comportement du NoC et d'en obtenir des clichés. Cette fonctionnalité est particulièrement intéressante pour la bonne compréhension du comportement de réseaux soumis à un trafic important.

<sup>&</sup>lt;sup>21</sup>Network Interface Circuit

# **III Conclusions**

Dans cette thèse, nous présentons un ensemble cohérent de techniques pour l'utilisation de processeurs futurs constitués de milliers de cœurs de calcul faillibles et sujets à une forte variabilité. Ces travaux ont été validés sur un modèle de simulation de haut-niveau nommé VOCIS, qui regroupe un ensemble de fonctionnalités uniques, permettant l'étude approfondie de réseaux dans des conditions complexes.

Plusieurs algorithmes de routage tolérants aux fautes, sans interblocages et sans tables de routage, sont décrits. Leurs différents niveaux de tolérance aux fautes permettent d'ajuster la complexité du NoC au besoin en fiabilité des applications. En particulier, la variante C garantit l'acheminement des paquets, tant qu'il existe un chemin et que le traffic est limité, et ce jusqu'à 40 % de nœud fautifs. Le débit en présence de fautes est ainsi amélioré sugnificativement. De plus, un méchanisme de routes explicites a été introduit, afin d'améliorer la performance du réseau en présence de fautes.

En se basant sur un réseau muni d'un algorithme de routage tolérant aux fautes et performant, nous élaborons ensuite une technique de gestion des applications parallèles, tolérante aux fautes et à la variabilité des cœurs de calcul. L'affectation dynamique des tâches basée sur une recherche adaptative des nœuds permet de diminuer la consommation énergétique de l'application en présence de défaillances.

# **Contents**

| Re | esumé | ii                                                                           |

|----|-------|------------------------------------------------------------------------------|

|    | I     | Introduction                                                                 |

|    |       | I.1 Contexte ii                                                              |

|    |       | I.2 Motivations                                                              |

|    | II    | Contributions                                                                |

|    |       | II.1 Réseaux sur puces tolérants aux fautes et performants vi                |

|    |       | II.2 Des applications efficaces, tolérantes aux fautes et à la variabilité x |

|    |       | II.3 VOCIS : un modèle générique de réseaux sur puce tolérants aux fautes xv |

|    | III   | Conclusions                                                                  |

| 1  | Intro | oduction 1                                                                   |

|    | 1.1   | Trends in the applications                                                   |

|    |       | 1.1.1 Parallelization                                                        |

|    |       | 1.1.2 Virtualization                                                         |

|    |       | 1.1.3 Criticity heterogeneity                                                |

|    |       | 1.1.4 A future of handheld devices and high-performance servers              |

|    | 1.2   | Physical constraints and opportunities of the CMOS era                       |

|    |       | 1.2.1 Transistor shrinking                                                   |

|    |       | 1.2.2 Power density wall                                                     |

|    |       | 1.2.3 Components fragility                                                   |

|    | 1.3   | Evolutions in processor architecture                                         |

|    |       | 1.3.1 From raw performance to multi-dimensional target                       |

|    |       | 1.3.2 Cores integration                                                      |

|    |       | 1.3.3 Memory integration                                                     |

|    |       | 1.3.4 Smarter Interconnections                                               |

|    |       | 1.3.5 Adaptive chips                                                         |

|    | 1.4   | Contributions for unreliable many-core architectures                         |

|    |       | 1.4.1 Global view                                                            |

|    |       | 1.4.2 Achieving fault tolerance and efficiency in large NoCs                 |

|    |       | 1.4.3 Managing multiple parallel applications in uncertain execution context |

|    |       | 1.4.4 Modeling the fault tolerance and performance of large interconnects    |

| 2  | Sma   | rt routing algorithms for the high fault tolerance of large NoCs             |

|    | 2.1   | An introduction to NoCs                                                      |

|    |       | 2.1.1 History                                                                |

|    |       | 2.1.2 Constitution                                                           |

|    |       | 2.1.3 Elementary notions                                                     |

|    |       | 2.1.4 NoCs in unreliable conditions                                          |

|    |       | 2.1.5 Metrics                                                                |

|    | 2.2   | State of art                                                                 |

|    |       |                                                                              |

|   |      | 2.2.1<br>2.2.2                                                                                                                                           | $\epsilon$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                         |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 2.2  |                                                                                                                                                          | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                                         |

|   | 2.3  | Contex 2.3.1                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                                         |

|   |      | 2.3.1                                                                                                                                                    | Motivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                                         |

|   |      |                                                                                                                                                          | Proposed router architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25                                                                         |

|   | 2.4  | 2.3.3                                                                                                                                                    | Formalism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26                                                                         |

|   | 2.4  |                                                                                                                                                          | g high fault tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                                                         |

|   |      | 2.4.1                                                                                                                                                    | Dynamic recovery from permanent and transient faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                         |

|   |      | 2.4.2                                                                                                                                                    | Variant A: Low-cost fault tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                                                         |

|   |      | 2.4.3                                                                                                                                                    | Variant B: More fault tolerance through virtual buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                         |

|   | 2.5  | 2.4.4                                                                                                                                                    | Variant C: Echo mode and high fault tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                         |